AMBO University Woliso Campus School of Technology & Informatics Department Of Computer Science

# Microprocessor and Assembly Language Programming Module Code CoSc M2041 Course Code CoSc 2043

Prepared By: Mr. Abdisa Lechisa(MSc)

Ambo University Woliso Campus, Woliso, Ethiopia 2012

# **Table of Contents**

| CHAPTER 1- INTRODUCTION TO MICROPROCESSOR AND COMPUTER | 1 |

|--------------------------------------------------------|---|

| Microprocessor & Its Architecture                      | 4 |

| Addressing Modes                                       | 6 |

| Data movement instructions                             | 9 |

| Arithmetic and Logical Instructions                    |   |

| Program control instructions                           |   |

| Summary                                                |   |

| CHAPTER 2: PROGRAMMING THE MICROPROCESSOR              |   |

| Programming the micro-processor                        |   |

| 8086/8088 Hardware Specification                       |   |

| The arithmetic co-processor                            |   |

| Memory Interface                                       |   |

| Memory organization in 8086                            |   |

| Basic I/O Interface                                    |   |

| Comparison of 8086 and 8088 Microprocessor             |   |

| The 8087-Intel co-processor                            |   |

| Bus Interfaces                                         |   |

| Summary                                                |   |

| CHAPTER 3: COMPUTER ORGANIZATION                       |   |

| Comparison of 8086 with 8085                           |   |

| Comparison of 8086 with 8088                           |   |

| Interrupts in 8086                                     |   |

| Registers for 8086                                     |   |

| Summary                                                |   |

| CHAPTER-4: ASSEMBLY LANGUAGES                          |   |

| Machine Language                                       |   |

| Assembly language                                      |   |

# Microprocessor and Assembly Language Programming

| Instruction operands                          | 61  |

|-----------------------------------------------|-----|

| Basic Instructions                            | 67  |

| Assembly Directive                            | 71  |

| Summary                                       | 77  |

| CHAPTER-5- WRITING ASSEMBLY LANGUAGE PROGRAMS |     |

| Control Structures                            |     |

| Comparisons                                   |     |

| Branch instructions                           | 79  |

| The loop instructions                         |     |

| Translating Standard Control Structures       |     |

| While loops                                   |     |

| Do while loops                                |     |

| CHAPTER-6- PROCEDURES AND FUNCTIONS           |     |

| Procedures                                    | 86  |

| Near and Far Procedures                       |     |

| Nested Procedures                             |     |

| Functions                                     |     |

| Saving the state of Machine                   |     |

| Parameters                                    |     |

| Pass by Value                                 |     |

| Pass by Reference                             |     |

| Pass by Value-Returned                        |     |

| Pass by Result                                |     |

| Pass by Name                                  |     |

| Passing Parameters in Registers               | 100 |

| Passing Parameters on the Stack               |     |

| Summary                                       |     |

| CHAPTER-7 INSTRUCTION TYPES                   |     |

| Stack Instructions 1          | 107 |

|-------------------------------|-----|

| PUSH 1                        | 107 |

| POP 1                         | 109 |

| Integral ALU instructions 1   | 111 |

| Arithmetic Instructions 1     | 111 |

| Logical Instruction 1         | 123 |

| Floating Point instructions 1 | 129 |

## **CHAPTER 1-** INTRODUCTION TO MICROPROCESSOR AND COMPUTER

The objective of this chapter is the students will be able to:

- Understand Microprocessor and Computer

- Describe the microprocessor and its architecture

- List addressing modes Data movement instructions

- Arithmetic and Logical Instructions

- Program control instructions

A **Computer** is a programmable machine.

The principal characteristics of a computer are:

- It responds to a specific set of instructions in a well-defined manner.

- It can execute a prerecorded list of instructions (a program).

- The instructions and data are called software.

- The actual machinery wires, transistors, and circuits are called hardware.

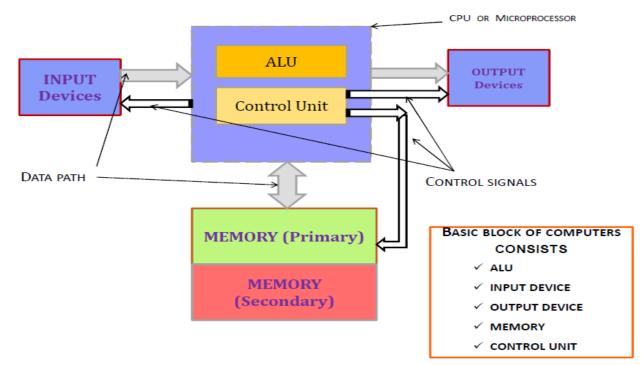

- see computer system graphically below here.

Computer system consists of:

- CPU (central processing unit) which is the heart of the computer.

- ✓ ALU (arithmetic-logic unit)

- ✓ Control Logic

- ✓ Registers, etc....

- Memory

- Input / Output interfaces

The interconnections between these units are through 3 basic buses:

- Address Bus: which select memory location or I/O device for CPU.

- Data Bus: Move information b/n CPU & memory or I/O devices with size from 8 bits to 64 bits in microprocessor.

- Control Bus: generate command signal to synchronize the CPU with I/O or memory.

**Microprocessor**: A microcomputer contains a CPU on a microchip (the microprocessor), a memory system (typically ROM and RAM), a bus system and I/O ports, typically housed in a motherboard. A silicon chip that contains a CPU. In the world of personal computers, the terms *microprocessor* and CPU are used interchangeably. A **microprocessor** (sometimes abbreviated  $\mu$ P) is a digital electronic component with miniaturized transistors on a single semiconductor integrated circuit (IC). One or more microprocessors typically serve as a central processing unit (CPU) in a computer system or handheld device. Microprocessors made possible the advent of the microcomputer. Microprocessors also control the logic of almost all digital devices, from clock radios to fuel-injection systems for automobiles.

Three basic characteristics differentiate microprocessors are:

- Instruction set: The set of instructions that the microprocessor can execute.

- Bandwidth: The number of bits processed in a single instruction.

- **Clock speed**: Given in megahertz (MHz), the clock speed determines how many instructions per second the processor can execute.

| Processor   | Date of | Clock       | Data bus        | Address | Addressable Memory           |

|-------------|---------|-------------|-----------------|---------|------------------------------|

|             | launch  | speed       | Width           | Bus     | Size                         |

| 4004        | 1971    | 740khz      | 4 bits          | 12      | 4 kb                         |

|             |         | I           | 8- Bit Process  | or      |                              |

| 8008        | 1972    | 800khz      | 8 bits          | 14      | 16 kb                        |

| 8080        | 1974    | 2Mhz        | 8 bits          | 16      | 64 kb                        |

| 8085        | 1976    | 3 MHz       | 8 bits          | 16      | 64 kb                        |

|             | I       | -<br>-<br>- | 16- Bit Process | sor     |                              |

| 8086        | 1978    | 5Mhz        | 16              | 20      | 1 M                          |

| 80286       | 1982    | 16Mhz       | 16              | 24      | 16 M                         |

|             |         | •           | 32- Bit Process | sor     |                              |

| 80386       | 1985    | 33 MHz      | 32              | 32      | 4 G                          |

| 80486       | 1989    | 40 MHz      | 32              | 32      | 4 G + 8 k cache              |

| Pentium I   | 1993    | 100 MHz     | 32              | 32      | 4 G + 16 k cache             |

| Pentium II  | 1997    | 233 MHz     | 32              | 32      | 4 G + 16 k cache + L2 256    |

|             |         |             |                 |         | cache                        |

| Pentium III | 1999    | 1.4 Ghz     | 32              | 32      | 4 G + 32 k cache + L2 256    |

|             |         |             |                 |         | cache                        |

| Pentium IV  | 2000    | 2.66 Ghz    | 32 Internal     | 32      | 4 G + 32 k cache + L2 256    |

|             |         |             | 64 External     |         | cache                        |

|             |         | (           | 64- Bit Process | sor     |                              |

| Dual core   | 2006    | 2.66 GHz    | 64              | 36      | 64G + Independent L1 64 Kb + |

|             |         |             |                 |         | Common L2 256 kb Cache       |

| Core 2 Duo  | 2006    | 3 GHz       | 64              | 36      | 64G + Independent L1 128 Kb  |

|             |         |             |                 |         | + Common L2 4 Mb Cache       |

| I7          | 2008    | 3.33 GHz    | 64              | 36      | 64G + Independent L1 64 Kb + |

|             |         |             |                 |         | Common L2 256 kb Cache + 8   |

|             |         |             |                 |         | Mb L3 Cache                  |

The evolutions of Microprocessors are: -

3

### Microprocessor & Its Architecture

When we look microprocessor 8086: -

- It introduced on march 1978.

- It is implemented with 16-bit HMOS microprocessor with 29,000 transistors & operate with 5MHz clock frequency.

- Use HMOS technology & has 40 pins.

- It has 20-bit address lines hence it has  $2^{20} = 1$  Mbytes memory locations.

- It can generate 16-bit address for I/O devices & can address  $2^{16} = 64$  k I/O ports.

- Can operate in 2 modes maximum or minimum mode & has 2 stage pipeline architecture.

- Has 135 number of instructions with eight 8-bit registers & eight 16-bit registers.

- Has +5v DC power supply.

#### Architecture Of 8086

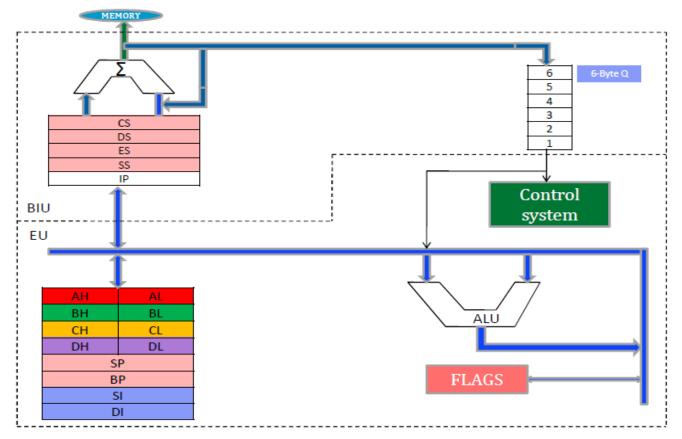

Microprocessor architecture is different from one another. Hence, when we look intel 8086 microprocessor architecture: -

Architecture of 8086 consists of 2 units of Bus Interface Unit (BIU) & Execution Unit (EU).

### **Bus Interface Unit**:

The BIU sends out address and fetches instructions from memory, reads data from ports and memory and return data to ports and memory. In other words, handles all transfers of data and address on the buses for the execution unit

#### **Execution Unit:**

Execution of 8086 tells BIU where to fetch instructions or data from, decodes instructions and executes instructions

- 1. It contains control circuitry which directs internal operations

- 2. A decoder in the EU, translates instructions fetched from memory into a series of actions

- 3. It has 16-bit ALU which does all the arithmetic operations

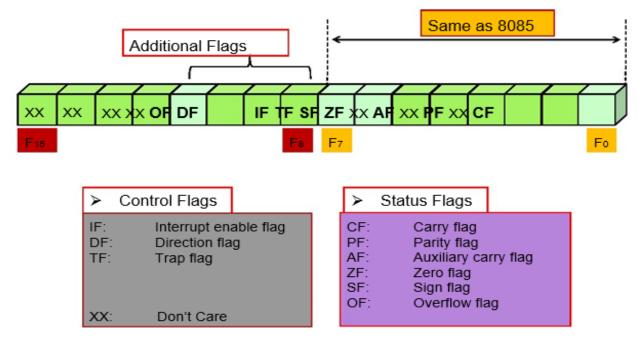

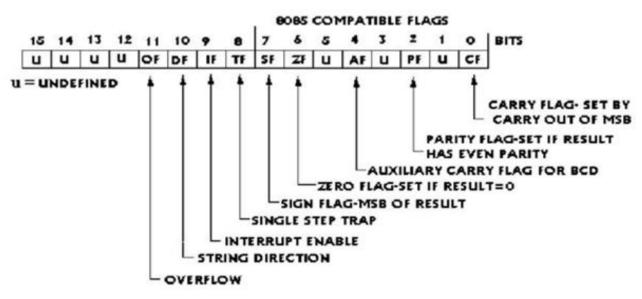

### Flag Register:

A flag is a flip-flop that indicates some status or condition produced by execution of an instruction. There are total 9 flags. Those are Status flags - 6 and Control flags- 3

### **Registers:**

AX, BX, CX, DX are general purpose registers which are of 16-bit size which can be viewed as the combination 2 8bit size.

| Register (16 bit) | 8-bit | 8-bit |

|-------------------|-------|-------|

| AX                | AH    | AL    |

| BX                | ВН    | BL    |

| CX                | СН    | CL    |

| DX                | DH    | DL    |

**Segment Registers**: Unlike 8085, the 8086 addresses a segmented memory of 1MB, which the 8086 is able to address. The 1 MB is divided into 16 logical segments ( $16 \times 64 \times B = 1024 \times B = 1 \times B$ ). Each segment thus contains 64 Kbytes of memory. There are four segment registers, viz. Code Segment Register (CS), Data Segment Register (DS), Extra Segment Register (ES) and Stack Segment Register (SS).

Code segment: It is used to store code in it.

Data segment: It is used to store data of the program.

Stack Segment: A stack is a set of memory set aside to store address and data while a sub programmed is executing. The upper 16 bits of the starting address are kept in stack segment register.

Extra segment: Strings are used in this.

**Pointers and Index Registers:** - The pointers contain offset within the particular segments. The pointers IP, BP and SP usually contain offsets within the code, data and stack segments respectively. The index registers are used as general-purpose registers as well as for offset storage in case of indexed, based indexed and relative based indexed addressing modes. The register SI is generally used to store the offset of source data in DMS while the register DI is used to store the offset of destination in DMS or EMS. The index registers are particularly useful for string manipulations.

### Addressing Modes

The 8086 memory addressing modes provide flexible access to memory, allowing you to easily access variables, arrays, records, pointers, and other complex data types. The different ways in which the location of an operand is specified in an instruction is called as Addressing mode. These generic addressing modes are:

- Immediate mode

- Register mode

- Absolute mode

- Indirect mode

- Index mode

- Base with index

- Base with index and offset

- Relative mode

- Auto-increment mode

- Auto-decrement mode

### **Implementation of Variables and Constants**

#### Variables:

The value can be changed as needed using the appropriate instructions. There are 2 accessing modes to access the variables. They are

- Register Mode and

- Absolute Mode

#### **Register Mode**:

The operand is the contents of the processor register. The name (address) of the register is given in the instruction.

#### Absolute Mode (Direct Mode):

The operand is in a memory location. The address of this location is given explicitly in the instruction. The various addressing modes and their assembler syntax and functions are as shown in figure below:

| Name                       | Assembler syntax | Addressing function  |

|----------------------------|------------------|----------------------|

| Immediate                  | #value           | Operand = value      |

| Register                   | Ri               | EA = Ri              |

| Absolute(direct)           | LOC              | EA =LOC              |

| Indirect                   | (Ri)             | EA = [Ri]            |

|                            | (LOC)            | EA = [LOC]           |

| Index                      | X(Ri)            | EA = [Ri] + X        |

| Base with index            | (Ri, Rj)         | EA = [Ri] + [Rj]     |

| Base with index and offset | X (Ri, Rj)       | EA = [Ri] + [Rj] + X |

| Relative                   | X(PC)            | EA = [PC] + X        |

| Autoincrement | (Ri)+ | EA = [Ri];   |

|---------------|-------|--------------|

|               |       | Increment Ri |

| Autodecrement | -(Ri) | Decrement Ri |

|               |       | EA = [Ri];   |

Figure of Generic addressing modes

#### **Immediate Addressing Mode:**

This addressing mode means the number that we are loading is part of the instruction itself, and is not found in the data memory.

e.g. MOV AX, 334 - will load the AX register with the number 344.

#### **Direct Addressing Mode:**

Operand resides in Memory and its address is given explicitly in the address field of an instruction. e.g. MOV AX, my\_variable - the accumulator AX is loaded with the contents of my\_variable.

### **Register Addressing Mode:**

All CPU's contain some internal registers, which act like local fast data stores. For example, an 8086 type CPU contains 4 general purpose registers called AX, BX, CX and DX. Programmers can access these registers as an integral part of their op-codes.

e.g. MOV AX, BX will move the contents of register BX into register AX.

### **Indirect Addressing:**

This address of the variable that we wish to address is not included in the op-code at all, instead we are given the address of a different variable that contains the address the actual variable that we wish to access. At a low level this is achieved by means of either an INDEX or a POINTER register. In an 8086 one of these registers is called BP or base pointer. If we load BP with a number, then that number can then be used as the address of a variable.

e.g. MOV BP, #344; Load the base pointer with the number 344 MOV AX, [BP]; Load the AX register with the contents of the memory location pointed to by

BP.

### **Relative Addressing**:

8

It is same as index mode. The difference is, instead of general-purpose register, here we can use program counter (PC).

#### **Relative Mode:**

The Effective Address is determined by the Index mode using the PC in place of the general-purpose register. This mode can be used to access the data operand. But it's most common use is to specify the target address in branch instruction. Eg. Branch>0 Loop. It causes the program execution to go to the branch target location. It is identified by the name loop if the branch condition is satisfied.

#### **Additional Modes:**

There are two additional modes. They are

- Auto-increment mode and

- Auto-decrement mode

#### Auto-increment mode:

The Effective Address of the operand is the contents of a register in the instruction. After accessing the operand, the contents of this register is automatically incremented to point to the next item in the list.

#### Auto-decrement mode:

The Effective Address of the operand is the contents of a register in the instruction. After accessing the operand, the contents of this register is automatically decremented to point to the next item in the list.

#### Data movement instructions

The **mov** instruction allows you to copy the contents of one register into another register. Each instruction can be used with different modes of addressing. Some of them are: MOV, MOVS, MOVSB, MOVSW etc.

Move Instruction

Purpose: Data transfer between memory cells, registers and the accumulator.

Syntax:

MOV Destiny, Source

Where Destiny is the place where the data will be moved and Source is the place where the data is. The different movements of data allowed for this instruction are:

9

- Destiny: memory. Source: accumulator

- Destiny: accumulator. Source: memory

- Destiny: segment register. Source: memory/register

- Destiny: memory/register. Source: segment register

- Destiny: register. Source: register

- Destiny: register. Source: memory

- Destiny: memory. Source: register

- Destiny: register. Source: immediate data

- Destiny: memory. Source: immediate data

Example:

| MOV | AX, | 0006h |  |  |

|-----|-----|-------|--|--|

| MOV | BX, | AX    |  |  |

| MOV | AX, | 4C00h |  |  |

|     |     |       |  |  |

INT 21H

This small program moves the value of 0006H to the AX register, then it moves the content of AX (0006h) to the BX register, and lastly it moves the 4C00h value to the AX register to end the execution with the 4C option of the 21h interruption.

#### Loading instructions

They are specific register instructions. They are used to load bytes or chains of bytes onto a register.

### LEA INSTRUCTION

Purpose: To load the address of the source operator

Syntax:

### LEA destiny, source

The source operator must be located in memory, and its displacement is placed on the index register or specified pointer in destiny. To illustrate one of the facilities we have with this command let us write equivalence:

MOV SI, OFFSET VAR1

Is equivalent to:

LEA SI, VAR1

It is very probable that for the programmer it is much easier to create extensive programs by using this last format.

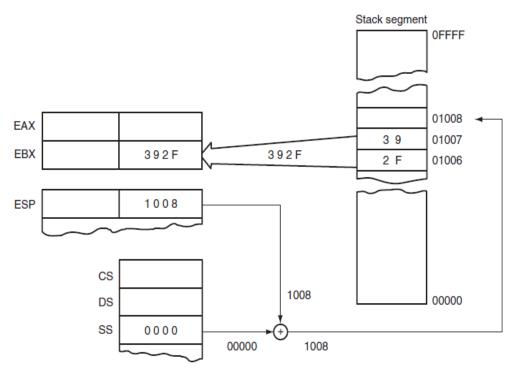

#### **Stack instructions**

These instructions allow the use of the stack to store or retrieve data. E.g. POP & PUSH.

### POP INSTRUCTION

Purpose: It recovers a piece of information from the stack

Syntax:

POP destiny

This instruction transfers the last value stored on the stack to the destiny operator, it then increases by 2 the SP register. This increase is due to the fact that the stack grows from the highest memory segment address to the lowest, and the stack only works with words, 2 bytes, so then by increasing by two the SP register, in reality two are being subtracted from the real size of the stack.

### **PUSH INSTRUCTION**

Purpose: It places a word on the stack.

Syntax:

#### PUSH source

The PUSH instruction decreases by two the value of SP and then transfers the content of the source operator to the new resulting address on the recently modified register.

The decrease on the address is due to the fact that when adding values to the stack, this one grows from the greater to the smaller segment address, therefore by subtracting 2 from the SP register what we do is to increase the size of the stack by two bytes, which is the only quantity of information the stack can handle on each input and output of information.

### Arithmetic and Logical Instructions

### Arithmetic instructions

They are used to perform arithmetic operations on the operators. Those instructions are: ADD, SUB, MUL & DIV

#### ADD INSTRUCTION

Purpose: Addition of the operators.

Syntax:

ADD destiny, source

It adds the two operators and stores the result on the destiny operator.

SUB INSTRUCTION

Purpose: Subtraction.

Syntax:

SUB destiny, source

It subtracts the source operator from the destiny.

#### MUL INSTRUCTION

Purpose: Multiplication with sign.

Syntax:

MUL source

The assembler assumes that the multiplicand will be of the same size as the multiplier, therefore it multiplies the value stored on the register given as operator by the one found to be contained in AH if the multiplier is 8 bits or by AX if the multiplier is 16 bits. When a multiplication is done with 8-bit values, the result is stored on the AX register and when the multiplication is with 16 bit values the result is stored on the even DX:AX register.

### **DIV INSTRUCTION**

Purpose: Division without sign.

Syntax:

DIV source

The divider can be a byte or a word and it is the operator which is given the instruction.

If the divider is 8 bits, the 16 bits AX register is taken as dividend and if the divider is 16 bits the even DX:AX register will be taken as dividend, taking the DX high word and AX as the low.

If the divider was a byte then the quotient will be stored on the AL register and the residue on AH, if it was a word then the quotient is stored on AX and the residue on DX.

### **Logic instructions**

They are used to perform logic operations on the operators. Those instructions are: AND, NEG, NOT, OR, & XOR

OR, & AOR

### AND INSTRUCTION

Purpose: It performs the conjunction of the operators' bit by bit.

Syntax:

AND destiny, source

With this instruction the "y" logic operation for both operators is carried out:

| Source Destiny   Destiny |

|--------------------------|

|                          |

| 11 1                     |

| 10 0                     |

| 01 0                     |

| 0000                     |

The result of this operation is stored on the destiny operator.

#### NEG INSTRUCTION

Purpose: It generates the complement to 2.

Syntax:

NEG destiny

This instruction generates the complement to 2 of the destiny operators and stores it on the same operator.

For example, if AX stores the value of 1234H, then:

NEG AX

This would leave the EDCCH value stored on the AX register.

### NOT INSTRUCTION

Purpose: It carries out the negation of the destiny operator bit by bit.

Syntax:

NOT destiny

The result is stored on the same destiny operator.

### OR INSTRUCTION

Purpose: Logic inclusive OR

Syntax:

OR destiny, source

The OR instruction carries out, bit by bit, the logic inclusive disjunction of the two operators:

| Source Destiny   Destiny |

|--------------------------|

|                          |

| 111                      |

| 10 1                     |

| 01 1                     |

| 0000                     |

|                          |

#### **TEST INSTRUCTION**

Purpose: It logically compares the operators

Syntax:

TEST destiny, source

It performs a conjunction, bit by bit, of the operators, but differing from AND, this instruction does not place the result on the destiny operator, it only has effect on the state of the flags.

### **XOR INSTRUCTION**

Purpose: OR exclusive

Syntax:

XOR destiny, source Its function is to perform the logic exclusive disjunction of the two operators' bit by bit.

Source Destiny | Destiny

#### **Program control instructions**

#### **Jump instructions**

They are used to transfer the flow of the process to the indicated operator. Some of these instructions are: JMP, JA (JNBE), JAE (JNBE), JB (JNAE), JBE (JNA), JE (JZ) and JNE (JNZ)

#### JMP INSTRUCTION

Purpose: Unconditional jump.

Syntax:

JMP destiny

This instruction is used to deviate the flow of a program without taking into account the actual conditions of the flags or of the data.

#### JA (JNBE) INSTRUCTION

Purpose: Conditional jump.

Syntax:

JA Label

After a comparison this command jumps if it is or jumps if it is not down or if not it is the equal.

This means that the jump is only done if the CF flag is deactivated or if the ZF flag is deactivated, that is that one of the two be equal to zero.

JAE (JNB) INSTRUCTION

Purpose: Conditional jump.

Syntax:

JAE label

It jumps if it is or it is the equal or if it is not down. The jump is done if CF is deactivated.

JB (JNAE) INSTRUCTION Purpose: Conditional jump. Syntax:

### JB label

It jumps if it is down, if it is not or if it is the equal. The jump is done if CF is activated.

### JBE (JNA) INSTRUCTION

Purpose: Conditional jump.

Syntax:

JBE label

It jumps if it is down, the equal, or if it is not. The jump is done if CF is activated or if ZF is activated, that any of them be equal to 1.

### JE (JZ) INSTRUCTION

Purpose: Conditional jump. Syntax: JE label It jumps if it is the equal or if it is zero. The jump is done if ZF is activated.

### JNE (JNZ) INSTRUCTION

Purpose: Conditional jump. Syntax: JNE label It jumps if it is not equal or zero. The jump will be done if ZF is deactivated.

### Instructions for cycles: loop

They transfer the process flow, conditionally or unconditionally, to a destiny, repeating this action until the counter is zero. Some of these instructions are: LOOP, LOOPE & LOOPNE.

### LOOP INSTRUCTION

Purpose: To generate a cycle in the program. Syntax: LOOP label The loop instruction decreases CX on 1, and transfers the flow of the program to the label given as operator if CX is different than 1.

#### LOOPE INSTRUCTION

Purpose: To generate a cycle in the program considering the state of ZF.

Syntax:

LOOPE label

This instruction decreases CX by 1. If CX is different to zero and ZF is equal to 1, then the flow of the program is transferred to the label indicated as operator.

#### LOOPNE INSTRUCTION

Purpose: To generate a cycle in the program, considering the state of ZF.

Syntax:

LOOPNE label

This instruction decreases one from CX and transfers the flow of the program only if ZF is different to 0.

#### **Counting instructions**

They are used to decrease or increase the content of the counters. Those instructions are: DEC & INC.

#### DEC INSTRUCTION

Purpose: To decrease the operator.

Syntax:

DEC destiny

This operation subtracts 1 from the destiny operator and stores the new value in the same operator.

#### INC INSTRUCTION

Purpose: To increase the operator.

Syntax:

INC destiny the instruction adds 1 to the destiny operator and keeps the result in the same destiny operator.

### **Comparison instructions**

17

They are used to compare operators, and they affect the content of the flags. This instruction is like CMP instruction.

#### CMP INSTRUCTION

Purpose: To compare the operators.

Syntax:

CMP destiny, source

This instruction subtracts the source operator from the destiny operator but without this one storing the result of the operation, and it only affects the state of the flags.

#### Flag instructions

They directly affect the content of the flags. Those instructions are: CLC, CLD, CLI, CMC, STC, STD & STI

#### CLC INSTRUCTION

Purpose: To clean the cartage flag.

Syntax:

CLC

This instruction turns off the bit corresponding to the cartage flag, or in other words it puts it on zero.

### CLD INSTRUCTION

Purpose: To clean the address flag.

Syntax:

CLD

This instruction turns off the corresponding bit to the address flag.

### CLI INSTRUCTION

Purpose: To clean the interruption flag.

Syntax:

CLI

This instruction turns off the interruptions flag, disabling this way those mask arable interruptions.

A mask arable interruptions is that one whose functions are deactivated when IF=0.

### CMC INSTRUCTION

Purpose: To complement the cartage flag.Syntax:CMCThis instruction complements the state of the CF flag, if CF = 0 the instructions equals it to 1, and if the instruction is 1 it equals it to 0.We could say that it only "inverts" the value of the flag.

#### STC INSTRUCTION

Purpose: To activate the cartage flag. Syntax: STC This instruction puts the CF flag in 1.

### STD INSTRUCTION

Purpose: To activate the address flag.

Syntax:

STD

The STD instruction puts the DF flag in 1.

### STI INSTRUCTION

Purpose: To activate the interruption flag.

Syntax:

STI

The instruction activates the IF flag, and this enables the mask arable external interruptions (the ones which only function when IF = 1).

MOVS (MOVSB) (MOVSW) Instruction

Purpose: To move byte or word chains from the source, addressed by SI, to the destiny addressed by DI. Syntax:

MOVS

This command does not need parameters since it takes as source address the content of the SI register and as destination the content of DI. The following sequence of instructions illustrates this:

MOV SI, OFFSET VAR1

MOV DI, OFFSET VAR2

#### MOVS

First we initialize the values of SI and DI with the addresses of the VAR1 and VAR2 variables respectively, then after executing MOVS the content of VAR1 is copied onto VAR2.

The MOVSB and MOVSW are used in the same way as MOVS, the first one moves one byte and the second one moves a word.

### Summary

- The typical Computer system consists of: ALU (arithmetic-logic unit), Control Logic, memory, input devices and Output devices

- The 8086 logically divided into: BIU & EU

- The flags of 8086 can be divided into two types: Conditional Flags and Control Flags

- Addressing modes is the way in which data is addressed in the operand part of the instruction.

- 8086 has 8 Addressing modes: Immediate addressing, Register addressing, Direct addressing, Register Indirect addressing, Relative Based, Relative Indexed addressing, based indexed addressing & Relative Based indexed with displacement addressing

- 8086 Instructions cab be grouped as Data transfer instructions, Arithmetic instructions, String instructions, Loop and jump instructions etc....

## **CHAPTER 2: PROGRAMMING THE MICROPROCESSOR**

The objective of this chapter is the students will be able to:

- Programming the micro-processor

- Mention 8086/8088 Hardware Specification

- Know the arithmetic co-processor

- List Memory Interface ,Basic I/O Interface & Bus interface

# Programming the micro-processor

Many programs are too large to be developed by one person. This means that programs are routinely developed by teams of programmers. The linker program is provided with Visual Studio so that programming modules can be linked together into a complete program. Linking is also available from the command prompt provided by Windows. This section describes the linker, the linking task, library files, EXTRN, and PUBLIC as they apply to program modules and modular programming.

### The Assembler and Linker

The **assembler program** converts a symbolic **source module** (file) into a hexadecimal **object file**. The assembler dialog that appears as a source module named NEW.ASM is assembled. If a 16-bit assembler and linker are needed, they can be obtained in the Windows Driver Development Kit (DDK). Whenever you create a source file, it should have the extension of ASM, but, that is not always possible. Source files are created by using Notepad or almost any other word processor or editor capable of generating an ASCII file. The assembler program (ML) requires the source file name following ML. the /Fl switch is used to create a listing file named NEW.LST.

The source listing file (.LST) contains the assembled version of the source file and its hexadecimal machine language equivalent. The cross-reference file (.CRF), which is not generated in this example, lists all labels and pertinent information required for cross-referencing. An object file is also generated by ML as an input to the linker program. In many cases we only need to generate an object file, which is accomplished by using the /c switch.

The **linker program**, which executes as the second part of ML, reads the object files that are created by the assembler program and links them together into a single execution file. An **execution file** is created with the file name extension EXE. Execution files are selected by typing the file name at the DOS prompt (C:\). An example execution file is FROG.EXE, which is executed by typing FROG at the command

prompt. If a file is short enough (less than 64K bytes long), it can be converted from an execution file to a **command file** (.COM).

The command file is slightly different from an execution file in that the program must be originated at location 0100H before it can execute. This means that the program must be no larger than 64K–100H in length. The ML program generates a command file if the tiny model is used with a starting address of 100H. Command files are only used with DOS or if a true binary version (for a EPROM/FLASH burner) is needed. The main advantage of a command file is that it loads off the disk into the computer much more quickly than an execution file. It also requires less disk storage space than the equivalent execution file.

#### **PUBLIC and EXTRN**

The PUBLIC and EXTRN directives are very important to modular programming because they allow communications between modules. We use PUBLIC to declare that labels of code, data, or entire segments are available to other program modules. EXTRN (external) declares that labels are external to a module. Without these statements, modules could not be linked together to create a program by using modular programming techniques. They might link, but one module would not be able to communicate to another. The PUBLIC directive is placed in the op-code field of an assembly language statement to define a label as public, so that the label can be used (seen by) by other modules. The label declared as public can be a jump address, a data address, or an entire segment.

The PUBLIC statement used to define some labels and make them public to other modules in a program fragment. When segments are made public, they are combined with other public segments that contain data with the same segment name.

The EXTRN statement appears in both data and code segments to define labels as external to the segment. If data are defined as external, their sizes must be defined as BYTE, WORD, or DWORD. If a jump or call address is external, it must be defined as NEAR or FAR.

#### Libraries

Library files are collections of procedures that are used by many different programs. These procedures are assembled and compiled into a library file by the LIB program that accompanies the MASM assembler program. Libraries allow common procedures to be collected into one place so they can be used by many different applications. The library file (FILENAME.LIB) is invoked when a program is linked with the linker program.

#### Macros

A macro is a group of instructions that perform one task, just as a procedure performs one task. The difference is that a procedure is accessed via a CALL instruction, whereas a macro, and all the instructions defined in the macro, is inserted in the program at the point of usage. Creating a macro is very similar to creating a new opcode, which is actually a sequence of instructions, in this case, that can be used in the program. You type the name of the macro and any parameters associated with it, and the assembler then inserts them into the program. Macro sequences execute faster than procedures because there is no CALL or RET instruction to execute. The instructions of the macro are placed in your program by the assembler at the point where they are invoked. Be aware that macros will not function using the inline assembler; they only function in external assembly language modules. The MACRO and ENDM directives delineate a macro sequence. The first statement of a macro is the MACRO instruction, which contains the name of the macro and any parameters: A and B. The last statement of a macro is the ENDM instruction, which is placed on a line by itself. Never place a label in front of the ENDM statement. If a label appears before ENDM, the macro will not assemble.

### 8086/8088 Hardware Specification

- 8086/8088 μ-p is packaged in a 40-pin Dual in-line Packages (DIP) and it requires a +5.0 V power Intel's supply.

- The 8086/8088 pin architectures use the combined address and data bus format commonly referred as a time multiplexed address and data bus.

- One advantage behind the multiplexed address/data bus is the maximum utilisation of processor pins (since the same pins carry address/data) and it facilitates the use of 40 pin standard DIP package.

- The bus can be de-multiplexed using a few latches and transceivers, whenever required.

- 8086 has a 20-bit address bus and can access up to 1 MB  $(2^{20})$  memory locations.

- 8086 has a 16bit data bus, so it can read or write data to a memory/port either 16bits or 8 bit at a time.

- It provides 16 -bit registers.

- It can pre-fetch up to 6 instruction bytes from memory and queues them in order to speed up instruction execution.

- 8088 has a 20-bit address bus and can access up to 1 MB  $(2^{20})$  memory locations.

- 8088 has a 8-bit external data bus, so it can read or write 8 bit data to a memory/port at a time.

- It provides 16 -bit registers.

- It can pre-fetch up to 4 instruction bytes from memory and queues them in order to speed up instruction execution.

- The 8086/8088 operates in single processor or multiprocessor configuration to achieve high performance.

- 8086/8088 is designed to operate in two modes, **Minimum mode** and **Maximum mode**.

- The pins serve a particular function in minimum mode (single processor mode) and other function in maximum mode configuration (multiprocessor mode).

### Pin Configuration of 8086 Microprocessor

|                                 |    |               |    |                                                       | A  |

|---------------------------------|----|---------------|----|-------------------------------------------------------|----|

| GND ←                           | 1  | $\overline{}$ | 40 | ← V <sub>cc</sub>                                     |    |

| $AD_{14} \leftrightarrow$       | 2  |               | 39 | $\leftrightarrow AD_{15}$                             | L  |

| $AD_{13} \leftrightarrow$       | 3  |               | 38 | $\rightarrow AD_{16} / S_3$                           | _  |

| $AD_{12} \leftrightarrow$       | 4  |               | 37 | $\rightarrow AD_{17} / S_4$                           | m  |

| $AD_{11} \leftrightarrow$       | 5  |               | 36 | $\rightarrow AD_{18} / S_5$                           | li |

| $AD_{10} \leftrightarrow$       | 6  |               | 35 | $\rightarrow AD_{19} / S_6$                           |    |

| $AD_{g} \leftrightarrow$        | 7  |               | 34 | $\rightarrow$ BHE/S,                                  | a  |

| $AD_{a} \leftrightarrow$        | 8  |               | 33 | ← MN/ MX                                              | ot |

| $AD_7 \leftrightarrow$          | 9  |               | 32 | $\rightarrow RD$                                      |    |

| $AD_{\epsilon} \leftrightarrow$ | 10 | 8086          | 31 | $\leftrightarrow$ HOLD ( $\overline{RQ} / GT_0$ )     | d  |

| $AD_s \leftrightarrow$          | 11 |               | 30 |                                                       | ťh |

| $AD_4 \leftrightarrow$          | 12 |               | 29 | $\rightarrow WR$ (LOCK)                               |    |

| $AD_3 \leftrightarrow$          | 13 |               | 28 | $\rightarrow M/\overline{IO}$ ( $\overline{S}_2$ )    | fo |

| $AD_2 \leftrightarrow$          | 14 |               | 27 | $\rightarrow$ DT/ $\overline{R}$ (S <sub>1</sub> )    | D  |

| $AD_1 \leftrightarrow$          | 15 |               | 26 | $\rightarrow \overline{\text{DEN}}$ (S <sub>0</sub> ) |    |

| $AD_{\circ} \leftrightarrow$    | 16 |               | 25 | $\rightarrow ALE$ (QS <sub>0</sub> )                  |    |

| NMI ↔                           | 17 |               | 24 | $\rightarrow \overline{INTA}$ (QS <sub>1</sub> )      | A  |

| INTR →                          | 18 |               | 23 | ← TEST                                                | Н  |

| $CLK \rightarrow$               | 19 |               | 22 | ← READY                                               |    |

| GND ←                           | 20 |               | 21 | ← RESET                                               | m  |

|                                 |    |               |    |                                                       |    |

### AD0-AD15 (Bidirectional) Address/Data bus

| Low order address bus; these are     |

|--------------------------------------|

| multiplexed with data. When AD       |

| lines are used to transmit memory    |

| address the symbol A is used instead |

| of AD, for example A0-A15. When      |

| data are transmitted over AD lines   |

| the symbol D is used in place of AD, |

| for example D0-D7, D8-D15 or D0-     |

| D15.                                 |

|                                      |

| A16/S3, A17/S4, A18/S5, A19/S6       |

| High order address bus. These are    |

| multiplexed with status signals      |

|                                      |

# Microprocessor and Assembly Language Programming

| BHE (Active Low<br>Bus High En<br>It is used to enable data onto the n<br>D8-D15. 8-bit device connected to<br>BHE (Active Low) signal. It is mu                                                                                                                                  | MN/ MX<br>MINIMUM / MAXIMUM<br>This pin signal indicates<br>what mode the processor is<br>to operate in.                                                                                                                                         |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| <b>READY</b><br>This is the acknowledgement from the slow device or memory that they have completed the data<br>transfer. The signal made available by the devices is synchronized by the 8284A clock generator to<br>provide ready input to the 8086. The signal is active high. |                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| RD (Read) (Active Low)<br>The signal is used for read<br>operation. It is an output<br>signal. It is active when low.                                                                                                                                                             | <b>TEST</b><br>$\overline{Test}$ input is tested by the "wait" instruction. 8086 will<br>enter wait state after execution of wait instruction and will<br>resume execution only when the $\overline{Test}$ is made low by an<br>active hardware. |  |  |  |  |  |  |

| RESET (Input)<br>Causes the processor to immediately terminate its present activity. The signal must be active<br>HIGH for at least four clock cycles.                                                                                                                            |                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

### CLK

The clock input provides the basic timing for processor operation and bus control activity. It's an asymmetric square wave with 33% duty cycle.

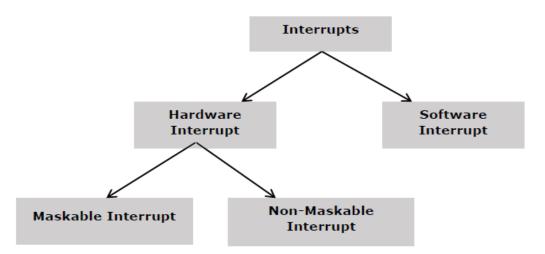

#### **INTR Interrupt Request**

This is a triggered input. This is sampled during the last clock cycles of each instruction to determine the availability of the request. If any interrupt request is pending, the processor enters the interrupt acknowledge cycle. This signal is active high and internally synchronized.

### MN/ MX (Active low)

The 8086 microprocessors can work in two modes of operations: Minimum mode and Maximum mode. In the minimum mode of operation, the microprocessors don't associate with any co-processors and cannot be used for multiprocessor systems. In the maximum mode the 8086 can work in multi-processor or coprocessor configuration. Minimum or maximum mode operations are decided by the pin MN/ MX (Active low). When this pin is high 8086 operates in minimum mode otherwise it operates in Maximum mode. Pins 24-31 for minimum mode operation, the MN/MX is tied to Vcc (logic high). 8086 itself generates all the bus control signals.

$\mathbf{DT}/\overline{\mathbf{R}} \Rightarrow$  (Data Transmit/ Receive) Output signal from the processor to control the direction of data flow through the data transceivers.

**DEN** =>(Data Enable) Output signal from the processor used as output enable for the transceivers

$M/\overline{IO} =>$ (Add ess Latch Enable) Used to demultiplex the address and data lines using external latches  $\overline{WR} =>$ Write control signal; asserted low Whenever processor writes data to memory or I/O port  $\overline{INTA} =>$ (Interrupt Acknowledge) When the interrupt request is accepted by the processor, the output is low on this line

**HOLD**=>Input signal to the processor form the bus masters as a request to grant the control of the bus. Usually used by the DMA controller to get the control of the bus.

**HLDA**=> (Hold Acknowledge) Acknowledge signal by the processor to the bus master requesting the control of the bus through HOLD. The acknowledge is asserted high, when the processor accepts HOLD.

During maximum mode operation, the MN/MX is grounded (Logic low) Pins 24-31 are assigned.

$\overline{S0}$ ,  $\overline{S1}$ ,  $\overline{S2}$  => Status signals; used by the 8086-bus controller to generate bus timing and control signals. These are decoded as shown.

# Microprocessor and Assembly Language Programming

|                  | Status Sig       | ynal             | Machine Cycle            |  |  |  |

|------------------|------------------|------------------|--------------------------|--|--|--|

| $\overline{S}_2$ | $\overline{S}_1$ | $\overline{S}_0$ |                          |  |  |  |

| 0                | 0                | 0                | Interrupt acknowledgment |  |  |  |

| 0                | 0                | 1                | Read I/O port            |  |  |  |

| 0                | 1                | 0                | Write I/O port           |  |  |  |

| 0                | 1                | 1                | Halt                     |  |  |  |

| 1                | 0                | 0                | Code access              |  |  |  |

| 1                | 0                | 1                | Read memory              |  |  |  |

| 1                | 1                | 0                | Write memory             |  |  |  |

| 1                | 1                | 1                | Passive/ inactive        |  |  |  |

$\overline{QS}_{0}$ ,  $\overline{QS}_{1}$ : The status processor provides the status of queue in these lines. The output of  $QS_{0} \& QS_{1}$  can be interpreted as shown in the table.

| Queue Status    |                 | Queue Operation                      |  |  |  |

|-----------------|-----------------|--------------------------------------|--|--|--|

| QS <sub>0</sub> | QS <sub>1</sub> |                                      |  |  |  |

| <br>0           | 0               | No operation                         |  |  |  |

| 0               | 1               | Frist byte of opcode from queue      |  |  |  |

| 1               | 0               | Queue empty                          |  |  |  |

| 1               | 1               | Subsequent byte of opcode from queue |  |  |  |

$\overline{RQ/GT}_{0}$ ,  $\overline{RQ/GT}_{1}$  (bus request/bus grant) these requests are used by other local bus masters to force the processor to release the local bus at the end of the processor's current bus cycle. These pins are bidirectional. The request on  $\overline{GT}_{0}$  will have higher priority than  $\overline{GT}_{1}$ .

**LOCK** an output signal activated by the LOCK prefix instruction. Remains active until the completion of the instruction prefixed by LOCK. The 8086 output low on the  $\overline{LOCK}$  pin while executing an instruction prefixed by LOCK to prevent other bus masters from gaining control of the system bus.

### The arithmetic co-processor

The Intel family of arithmetic coprocessors includes the 8087, 80287, 80387SX, 80387DX, and the 80487SX for use with the 80486SX microprocessor. The family of coprocessors, which is labeled the 80X87, is able to multiply, divide, add, subtract, find the square root, and calculate the partial tangent, partial arctangent, and logarithms.

Data types include 16-, 32-, and 64-bit signed integers; 18-digit BCD data; and 32-, 64-, and 80-bit floating-point numbers. The operations performed by the 80X87 generally execute many times faster than equivalent operations written with the most efficient programs that use the microprocessor's normal instruction set.

#### **Data Formats For The Arithmetic Coprocessor**

These data types include signed integer, BCD, and floating-point. Each has a specific use in a system, and many systems require all three data types. Note that assembly language programming with the coprocessor is often limited to modifying the coding generated by a high level language such as C/C++.

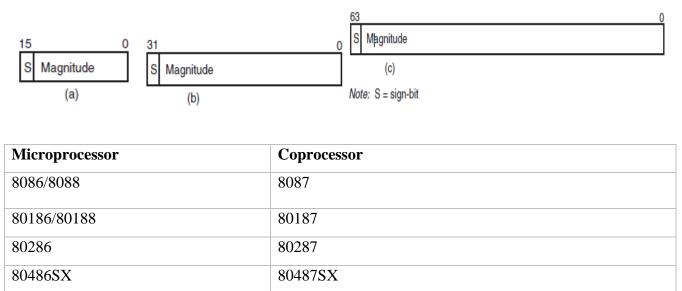

#### **Signed Integers**

Used with the arithmetic coprocessor, signed integers are 16- (word), 32- (double word integer), or 64bits (quad word integer) wide. Positive numbers are stored in true form with a leftmost sign-bit of 0, and negative numbers are stored in two's complement form with a leftmost sign-bit of 1. The word integers range in value from -32,768 to +32,767, the double word integer range is  $\pm 2 \times 109$ , and the quad word integer range is  $\pm 9 \times 1018$ . Integer data types are found in some applications that use the arithmetic coprocessor. The DW directive defines words, DD defines double word integers, and DQ defines quad word integers. Example sees how several different sizes of signed integers are defined for use by the assembler and arithmetic coprocessor.

| 0000 0002              | DATA1 | DW | 2     | ;16-bit integer |

|------------------------|-------|----|-------|-----------------|

| 0002 FFDE              | DATA2 | DW | -34   | ;16-bit integer |

| 0004 000004D2          | DATA3 | DD | 1234  | ;32-bit integer |

| 0008 FFFFF9C           | DATA4 | DD | -100  | ;32-bit integer |

| 000C 00000000005BA0    | DATA5 | DQ | 23456 | ;64-bit integer |

| 0014 FFFFFFFFFFFFFFF86 | DATA6 | DQ | -122  | ;64-bit integer |

Integer formats for the  $80 \times 87$  family of arithmetic coprocessors:

a. Word b. Short and c. long.

80387

80486DX-Core2Built into the microprocessorTable of showing microprocessor and coprocessor compatibility.

### **Binary-Coded Decimal (BCD)**

The binary-coded decimal (BCD) form requires 80 bits of memory. Each number is stored as an 18-digit packed integer in nine bytes of memory as two digits per byte. The tenth byte contains only a sign-bit for the 18-digit signed BCD number.

Note that both positive and negative numbers are stored in true form and never in ten's complement form. The DT directive stores BCD data in the memory. This form is rarely used because it is unique to the Intel coprocessor.

### EXAMPLE

80386

| 0000 0000000000000000000000000000000000 | DATA1 | DT | 200   | ; define 10 byte |

|-----------------------------------------|-------|----|-------|------------------|

| 000A 8000000000000000000000000000000000 | DATA2 | DT | -10   | ; define 10 byte |

| 0014 00000000000000010020               | DATA3 | DT | 10020 | ; define 10 byte |

### **Floating-Point**

Floating-point numbers are often called *real numbers* because they hold signed integers, fractions, and mixed numbers. A floating-point number has three parts: a sign-bit, a biased exponent, and a significant. Floating-point numbers are written in scientific binary notation. The Intel family of arithmetic

coprocessors supports three types of floating-point numbers: single (32 bits), double (64 bits), and temporary (80 bits).

| 79                      |          |          |       |    |    |    |    |    |    |    |    |    | 0  |

|-------------------------|----------|----------|-------|----|----|----|----|----|----|----|----|----|----|

| Sign<br>byte D17 D16 D1 | 5 D14 D1 | 3 D12 D1 | 1 D10 | D9 | D8 | D7 | D6 | D5 | D4 | DЗ | D2 | D1 | Do |

Table of BCD data format for the 80X87 family of arithmetic coprocessors

## Memory Interface

**Memory**: -Store Programs and Data. It includes Primary or Main Memory, processor memory and secondary memory.

#### **Processor Memory**

- Registers inside a microcomputer

- Store data and results temporarily

- No speed disparity

- Cost

#### **Primary or Main Memory**

- Storage area which can be directly accessed by microprocessor

- Store programs and data prior to execution

- Should not have speed disparity with processor => Semi-Conductor memories using CMOS technology

- Contain ROM, EPROM, Static RAM, DRAM

#### **Secondary Memory**

- Storage media comprising of slow devices such as magnetic tapes and disks

- Hold large data files and programs: Operating system, compilers, databases, permanent programs

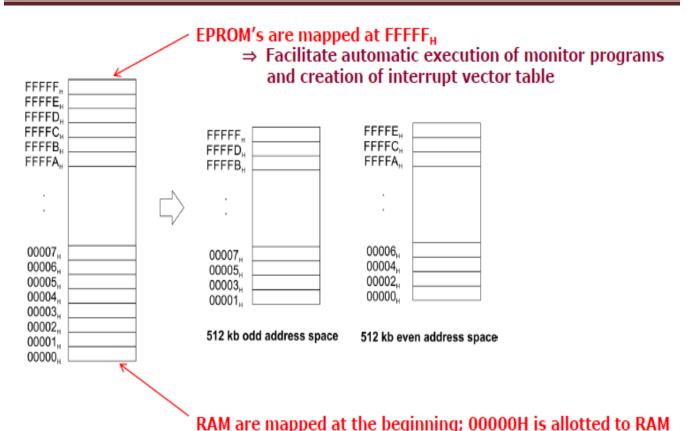

#### Memory organization in 8086

- Memory IC's: Byte oriented

- 8086:16 bit

- Word: stored by two consecutive memory locations for LSB and MSB

- Address of word: Address of LSB

- Bank 0:  $A0 = 0 \implies$  Even addressed memory bank

- Bank 1: BHE = 0 => odd addressed memory bank

|   | Data Bus (D <sub>0</sub> - D <sub>15</sub> )           |     |                |                                                                     |  |  |  |  |  |  |  |

|---|--------------------------------------------------------|-----|----------------|---------------------------------------------------------------------|--|--|--|--|--|--|--|

|   | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |     |                |                                                                     |  |  |  |  |  |  |  |

| / | Address Bus                                            |     |                | _                                                                   |  |  |  |  |  |  |  |

|   | Odd<br>Addressed<br>Memory<br>Bank                     |     |                | Even<br>Idressed<br>Memory<br>Bank                                  |  |  |  |  |  |  |  |

|   | Operation                                              | BHE | A <sub>0</sub> | Data Lines used                                                     |  |  |  |  |  |  |  |

| 1 | Read/ write byte at an even address                    | 1   | 0              | $D_7 - D_0$                                                         |  |  |  |  |  |  |  |

| 2 | Read/ write byte at an odd address                     | 0   | 1              | $D_{15} - D_8$                                                      |  |  |  |  |  |  |  |

| 3 | Read/ write word at an even address                    | 0   | 0              | $D_{15} - D_0$                                                      |  |  |  |  |  |  |  |

| 4 | Read/ write word at an odd address                     | 0   | 1              | $D_{15} - D_0$ in first operation byte from odd bank is transferred |  |  |  |  |  |  |  |

|   |                                                        | 1   | 0              | $D_7 - D_0$ in first operation byte from odd bank is transferred    |  |  |  |  |  |  |  |

- Available memory space = EPROM + RAM

- Allot equal address space in odd and even bank for both EPROM and RAM

- Can be implemented in two IC's (one for even and other for odd) or in multiple IC's

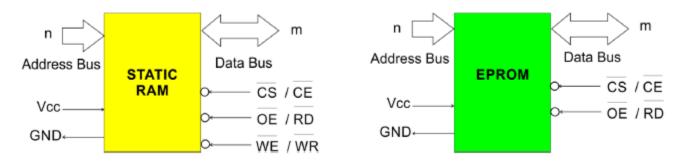

#### Interfacing SRAM and EPROM

- Memory interface => Read from and write in to a set of semiconductor memory IC chip

- EPROM => Read operations

- RAM => Read and Write

In order to perform read/ write operations,

- Memory access time => read / write time of the processor

- Chip Select (CS) signal has to be generated

- Control signals for read / write operations

- Allot address for each memory location

Its typical Semiconductor IC Chip for this is;

| No of   | Memory capacity      |            |         | Range of address in Hexa |

|---------|----------------------|------------|---------|--------------------------|

| address | In Decimal           | In Kilo    | In hexa |                          |

| Pin     |                      |            |         |                          |

| 20      | $2^{20} = 10,48,576$ | 1024k = 1M | 100000  | 00000 – FFFFF            |

## Memory map of 8086

## **Monitor Programs**

- Programing 8279 for keyboard scanning and display refreshing

- Programming peripheral IC's 8259, 8257, 8255, 8251, 8254 etc.

- Initialization of stack

- Display a message on display (output)

- Initializing interrupt vector table

#### Note:

- 8279 Used for Programmable keyboard/ display controller

- 8257 Used for DMA controller

- 8259 Used for Programmable interrupt controller

- 8255 Used for Programmable peripheral interface

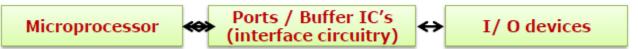

#### Basic I/O Interface

I/O devices are: -

- Used for communication between microprocessor and outside world

- Keyboards, CRT displays, Printers, Compact Discs etc.

- Used for data transfer

- $\checkmark$  data transfer types are:

- Programmed I/O: Data transfer is accomplished through an I/O port controlled by software.

- ✤ Programmed I/O can be memory mapped or I/O mapped.

- Interrupt driven I/O: I/O device interrupts the processor and initiate data transfer.

- Direct memory access: Data transfer is achieved by bypassing the microprocessor.

| Memory Mapping                                      | I/O Mapping                                          |

|-----------------------------------------------------|------------------------------------------------------|

| 20-bit address are provided for I/O devices         | 8-bit or 16-bit address are provided for I/O devices |

| The I/O ports or peripherals can be treated like    | Only IN and OUT instructions can be used for data    |

| memory locations and so all instructions related to | transfer between I/O device and processor            |

| memory can be used for data transmission between    |                                                      |

| I/O device and processor.                           |                                                      |

| Data can be moved from any register to ports and    | Data transfer takes place only between               |

| vice versa                                          | accumulator and ports                                |

| When memory mapping is used for I/O devices,        | Full memory space can be used for addressing         |

| Full memory address space cannot be used for        | memory.                                              |

| addressing memory.                                  |                                                      |

| Useful only for small systems where memory          | Suitable for system which require large memory       |

| requirement is low.                                 | capacity.                                            |

| For accessing the memory mapped devices, the        | For accessing the I/O mapped devices, the            |

| processor executes memory read or write cycle.      | processor executes memory read or write cycle.       |

| M/IO is asserted high                               | M/IO is asserted low                                 |

Comparison of 8086 and 8088 Microprocessor

| 8086 Microprocessor                              | 8088 Microprocessor                              |

|--------------------------------------------------|--------------------------------------------------|

| Similar EU and instruction set                   | Dissimilar BIU                                   |

| 16-bit data bus lines obtained by demultiplexing | 8-bit data bus lines obtained by demultiplexing  |

| $AD_0 - AD_{15}$                                 | $AD_0 - AD_7$                                    |

| 20-bit address bus                               | 8-bit address bus                                |

| 6-bit instruction queue                          | 4-bit instruction queue                          |

| Two banks of memory each of 512kb                | Single memory bank                               |

| Clock speeds; - 5 or 8or 10 MHz                  | 5 or 8 MHz                                       |

| In MIN mode, pin 28 is assigned the signal M/IO  | In MIN mode, pin 28 is assigned the signal IO/M  |

| To access higher byte, BHE signal is used        | No such signal required, since the data width is |

|                                                  | only 1-byte.                                     |

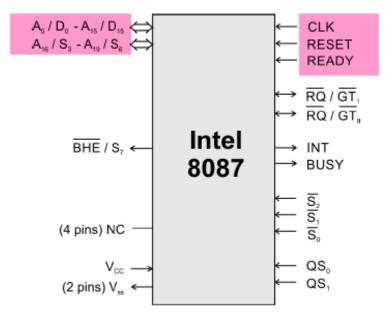

### The 8087-Intel co-processor

Multiprocessor system

- A microprocessor system comprising of two or more processors.

- Distributed processing: Entire task is divided in to subtasks.

#### Advantages

- Better system throughput by having more than one processor

- Each processor has a local bus to access local memory or I/O devices so that a greater degree of parallel processing can be achieved.

- System structure is more flexible. One can easily add or remove modules to change the system configuration without affecting the other modules in the system.

#### 8087 Coprocessors

- Specially designed to take care of mathematical calculations involving integer and floating-point data

- "Math coprocessor" or "Numeric Data Processor (NDP)"

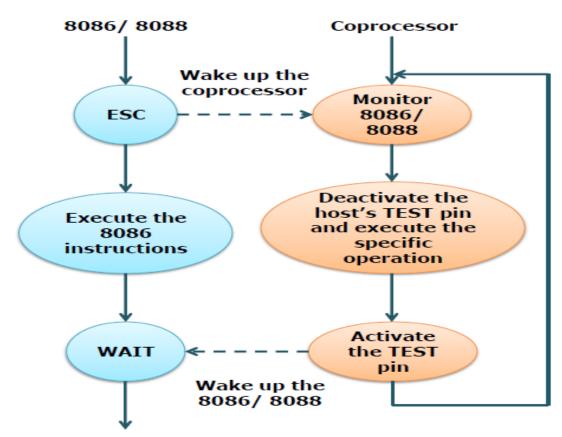

• Works in parallel with a 8086 in the maximum mode

#### Features

- Can operate on data of the integer, decimal and real types with lengths ranging from 2 to 10 bytes

- Instruction set involves square root, exponential, tangent etc. in addition to addition, subtraction, multiplication and division.

- High performance numeric data processor => it can multiply two 64-bit real numbers in about 27µs and calculate square root in about 36 µs

- Follows IEEE floating point standard

- It is multi bus compatible

- 16 multiplexed address / data pins and 4 multiplexed address / status pins.

- Hence it can have 16-bit external data bus and 20-bit external address bus like 8086.

- Processor clock, ready and reset signals are applied as clock, ready and reset signals for coprocessor.

#### BUSY

- BUSY signal from 8087 is connected to the Test input of 8088.

- If the 8086 needs the result of some computation that the 8087 is doing before it can execute the next instruction in the program, a user can tell 8086 with WAIT instruction to keep looking at its TEST pin until it finds the pin low.

- A low on the BUSY output indicates that the 8087 has completed the computation.

#### RQ/GT<sub>1</sub>

• The request /grant signal from the 8087 is usually connected to the request/ grant pin of the independent processor such as 8089

#### RQ/GT<sub>0</sub>

The request /grant signal from the 8087 is usually connected to the request/ grant (RQ/GT<sub>0</sub> or RQ/GT<sub>1</sub>) pin of the 8086.

#### INT

- The interrupt pin is connected to the interrupt management logic.

- The 8087 can interrupt the 8086 through this interrupt management logic at the time error condition exists.

| $\mathbf{S}_2$ | <b>S</b> 1 | So | Status       |

|----------------|------------|----|--------------|

| 1              | 0          | 0  | Unused       |

| 1              | 0          | 1  | Read memory  |

| 1              | 1          | 0  | Write memory |

| 1              | 1          | 1  | Passive      |

#### S0- S2

### $QS_0.QS_1\\$

| QS <sub>0</sub> | $QS_1$ | Status                               |

|-----------------|--------|--------------------------------------|

| 0               | 0      | No operation                         |

| 0               | 1      | Frist byte of opcode from queue      |

| 1               | 0      | Queue empty                          |

| 1               | 1      | Subsequent byte of opcode from queue |

Generally,

#### **Bus Interfaces**

A **bus** is a parallel data communication path over which information is transferred a byte or word at a time. The buses contain logic that the CPU controls. The items controlled are the transfer of data, instruction, and commands between the functional areas of the computer (CPU, Memory, and I/O). The name of the bus or its operation usually implies the type of signal it carries or method of operation. The

direction of signal flow for the different buses. The direction may be **unidirectional** or **bidirectional** depending on the type of bus and type of computer. All computers use those three types of basic buses.

- 1. Data Bus (also called a memory bus)

- 2. Control Bus (also called timing and control bus) and

- 3. Address Bus

#### 1. Data Bus

The bidirectional data bus, sometimes called the memory bus, handles the transfer of all **data** and **instructions** between functional areas of the computer. The bidirectional data bus can only transmit in one direction at a time. The data bus is used to transfer instructions from memory to the CPU for execution. It carries data (operands) to and from the CPU and memory as required by instruction translation. The data bus is also used to transfer data between memory and the I/O section during input/output operations. The size of this bus varies widely in the 8086 family.

The size of the data bus affects **the performance of the system** more than the size of any other bus. (This bus defines the size of the processor) On typical 8086systems, the data bus contains eight 16, 32 or 64 lines. Having an 8-bit data bus does not limit the processor to 8-bit data type. It is simply meaning that the processor can only access one byte of data per memory cycle. The 8-bit bus can only transmit half information per unit time (memory cycle) as the 16-bit bus. The processor with 32-bit bus is naturally faster than processors with a 16-bit data bus.

#### 2. Address Bus

The address bus consists of all the signals necessary to define any of the possible memory address locations within the computer, or for modular memories any of the possible memory addresses locations within a module. An address is defined as a label, symbol, or other set of characters used to designate a location or register where information is stored. Before data or instructions can be written into or read from memory by the CPU or I/O sections, an address must be transmitted to memory over the address bus.

The system designer assigns a unique memory address to each memory elements and I/O device. When software wants to access some particular memory location or I/O address, it places the corresponding

address on the address bus. With single address line, a processor could create exactly 2 unique addresses: Zero and One, with **n** address lines, the processor can provide  $2^n$  unique addresses. The number of bits on the address bus will determine the **maximum number of addressable memory and I/O locations**. The 8086, for example, have 20 bits address busses.

#### 3. Control Bus

The control bus is used by the CPU to direct and monitor the actions of the other functional areas of the computer. It is used to transmit a variety of individual signals (read, write, interrupt, acknowledge, and so forth) necessary to control and coordinate the operations of the computer.

The individual signals transmitted over the control bus and their functions are covered in the appropriate functional area description.

The CPU sends data to memory and receives data from memory on the data bus. "Is it sending/ receiving?" there are 2 lines on the control bus, read and write, which specify the direction of dataflow. Other signals include system clocks; interrupt lines, status lines and so on.

### Summary

- Programming the microprocessor describes the linker, the linking task, library files, EXTRN, and PUBLIC as they apply to program modules and modular programming.

- The assembler program converts a symbolic source module (file) into a hexadecimal object file.

- The Intel family of arithmetic coprocessors includes the 8087, 80287, 80387SX, 80387DX, and the 80487SX for use with the 80486SX microprocessor.

- The family of coprocessors, which is labeled the 80X87, is able to multiply, divide, add, subtract, find the square root, and calculate the partial tangent, partial arctangent, and logarithms.

- The Data types include 16-, 32-, and 64-bit signed integers; 18-digit BCD data; and 32-, 64-, and 80bit floating-point numbers.

- 8086/8088 μ-p is packaged in a 40-pin Dual in-line Packages (DIP) and it requires a +5.0 V

power Intel's supply.

- 8086 has a 20-bit address bus, 16-bit data bus and can access up to 1 MB (2<sup>20</sup>) memory locations.

- All computers use those three types of basic buses like Data Bus (also called a memory bus), Control Bus (also called timing and control bus) and Address Bus.

- Memory is used for storing Programs and Data. It includes Primary or Main Memory, processor memory and secondary memory.

## **CHAPTER 3: COMPUTER ORGANIZATION**

The objective of this chapter is the students will be able to:

- Understand about Memory & CPU

- List and compare 80X86 family of CPUS

- Identify about Interrupts

- Describe Registers

### The 80X86 Family of CPU's

The term **x86** refers to a family of <u>instruction set architectures</u> based on the <u>Intel 8086 CPU</u>. The 8086 was launched in 1978 as a fully 16-bit extension of Intel's 8-bit based <u>8080</u> microprocessor and also introduced <u>segmentation</u> to overcome the 16-bit addressing barrier of such designs. The term x86 derived from the fact that early successors to the 8086 also had names ending in "86". The architecture has been implemented in processors from <u>Intel, Cyrix, AMD, VIA</u>, and many others.

As the term became common *after* the introduction of the <u>80386</u>, it usually implies binary compatibility with the 32-bit <u>instruction set</u> of the 80386. This may sometimes be emphasized as <u>x86-32</u> to distinguish it either from the original 16-bit "x86-16" or from the 64-bit <u>x86-64</u>. Although most x86 processors used in *new* <u>personal computers</u> and <u>servers</u> have 64-bit capabilities, to avoid compatibility problems with older computers or systems, the term *x86-64* (or *x64*) is often used to denote 64-bit software, with the term *x86* implying only 32-bit.

Although the 8086 was primarily developed for <u>embedded systems</u> and small single-user computers, largely as a response to the successful 8080-compatible <u>Zilog Z80</u>, the x86 line soon grew in features and processing power. Today, x86 is ubiquitous in both stationary and portable personal computers and has replaced <u>midrange computers</u> and <u>RISC-based</u> processors in a majority of servers and <u>workstations</u> as well. A large amount of <u>software</u>, including <u>operating systems</u> (OSs) such as <u>DOS</u>, <u>Windows</u>, <u>Linux</u>, <u>BSD</u>, <u>Solaris</u>, and <u>Mac OS X</u> supports x86-based hardware.

Modern x86 is relatively uncommon in <u>embedded systems</u>, however, and small <u>low power</u> applications (using tiny batteries) as well as low-cost microprocessor markets, such as <u>home appliances</u> and toys, lack any significant x86 presence. Simple 8-bit and 16-bit based architectures are common here, although the

x86-compatible <u>VIA C7</u>, <u>VIA Nano</u>, <u>AMD</u>'s <u>Geode</u>, <u>Athlon Neo</u>, and <u>Intel Atom</u> are examples of 32- and 64-bit designs used in some *relatively* low power and low cost segments.

#### Chronology

The table below lists brands of common consumer targeted processors implementing the x86 <u>instruction</u> <u>set</u>, grouped by generations that highlight important points in x86 history. Note: CPU generations are not strict: each generation is roughly marked by significantly improved or commercially successful processor <u>micro architecture</u> designs.

| Generation         | First      | Prominent consumer               | Linear/physical        | Notable (new) features                 |

|--------------------|------------|----------------------------------|------------------------|----------------------------------------|

|                    | introduced | CPU brands                       | address space          |                                        |

| 1                  | 1978       | Intel 8086, Intel 8088           | <b>16-bit</b> / 20-bit | first x86 microprocessors              |

|                    |            | and clones                       | (segmented)            |                                        |

|                    | 1982       | Intel 80186, Intel               |                        | hardware for fast address              |

|                    |            | 80188 and clones, <u>NEC</u>     |                        | calculations, fast mul/div             |

|                    |            | <u>V20</u> /V30                  |                        | etc.                                   |

| 2                  | -          | Intel 80286 and clones           | <b>16-bit</b> (30-bit  | MMU, for protected mode                |

|                    |            |                                  | virtual) / 24-bit      | and a larger address space             |

|                    |            |                                  | (segmented)            |                                        |

| 3 ( <u>IA-32</u> ) | 1985       | Intel 80386 and clones,          | 32-bit(46-bit          | <u>32-bit</u> instruction set,         |

|                    |            | <u>AMD Am386</u>                 | virtual) / 32-bit      | MMU with paging                        |

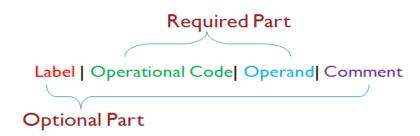

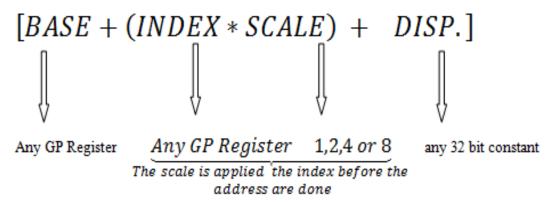

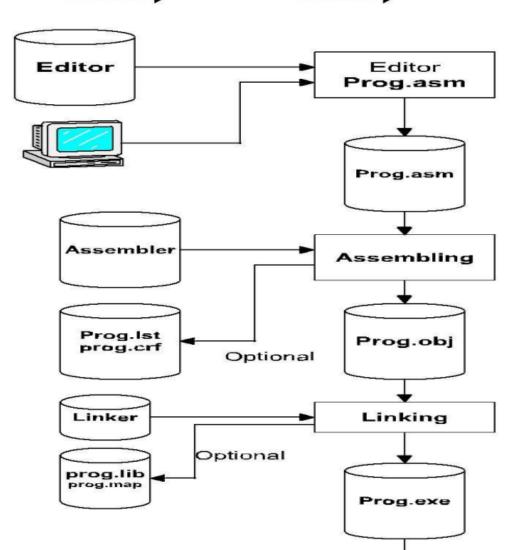

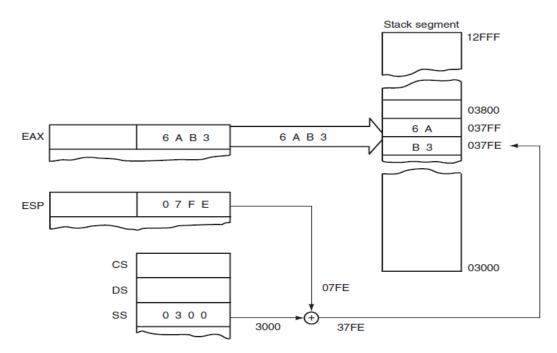

| 4 ( <u>FPU</u> )   | 1989       | Intel486 and clones,             |                        | risc-like <u>pipelining</u> ,          |