Sorin A. Huss Editor

Advances in Design and Specification Languages for Embedded Systems

# ADVANCES IN DESIGN AND SPECIFICATION LANGUAGES FOR EMBEDDED SYSTEMS

# Advances in Design and Specification Languages for Embedded Systems

Selected Contributions from FDL'06

Edited by

SORIN A. HUSS

T.U. Darmstadt, Germany

| A C.I.P. Catalogue record for this book is available from the Library of Congress.                                                                                                                                  |  |

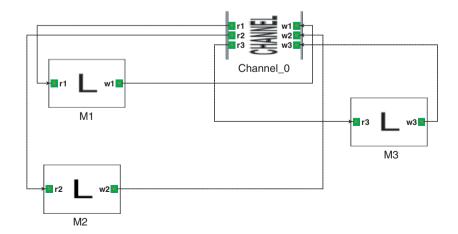

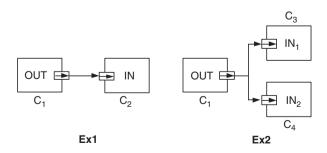

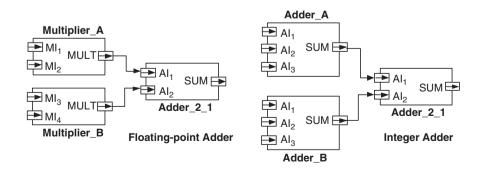

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                     |  |

| ISBN 978-1-4020-6147-9 (HB)<br>ISBN 978-1-4020-6149-3 (e-book)                                                                                                                                                      |  |

| Published by Springer,<br>P.O. Box 17, 3300 AA Dordrecht, The Netherlands.                                                                                                                                          |  |

| www.springer.com                                                                                                                                                                                                    |  |

|                                                                                                                                                                                                                     |  |

|                                                                                                                                                                                                                     |  |

|                                                                                                                                                                                                                     |  |

|                                                                                                                                                                                                                     |  |

|                                                                                                                                                                                                                     |  |

|                                                                                                                                                                                                                     |  |

| Printed on acid-free paper                                                                                                                                                                                          |  |

|                                                                                                                                                                                                                     |  |

|                                                                                                                                                                                                                     |  |

|                                                                                                                                                                                                                     |  |

|                                                                                                                                                                                                                     |  |

| All Rights Reserved © 2007 Springer  No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical photocopying, microfilming, recording |  |

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

## Contents

| Preface                                                                                                                                                                                 | ix |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Part I Analog, Mixed-Signal, and Heterogeneous System Design                                                                                                                            |    |

| Introduction Christoph Grimm                                                                                                                                                            | 3  |

| 1<br>Compact Modeling of Emerging Technologies with VHDL-AMS<br>Fabien Prégaldiny, Christophe Lallement, Birahim Diagne,<br>Jean-Michel Sallese, and François Krummenacher              | 5  |

| 2 Baseband Modeling Using Multidimensional Networks in VHDL-AMS  Joachim Haase                                                                                                          | 23 |

| 3 Verification-Oriented Behavioral Modeling of NonLinear Analog Parts of Mixed-Signal Circuits  Martin Freibothe, Jens Döge, Torsten Coym, Stefan Ludwig, Bernd Straube, and Ernst Kock | 37 |

| 4 Improving Efficiency and Robustness of Analog Behavioral Models Daniel Platte, Shangjing Jing, Ralf Sommer, and Erich Barke                                                           | 53 |

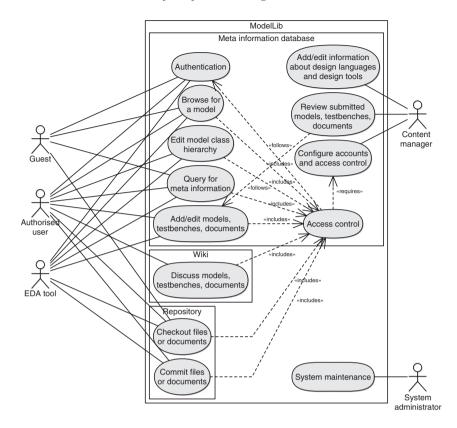

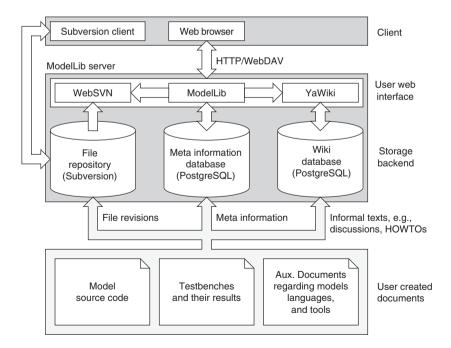

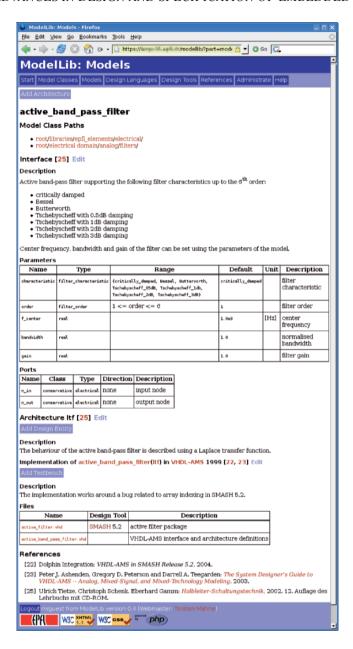

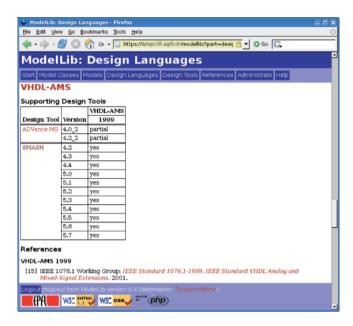

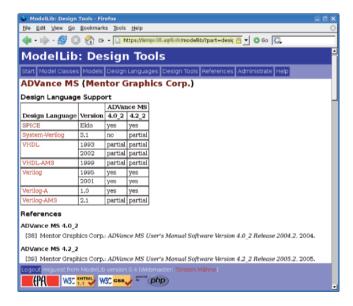

| 5 ModelLib: A Web-Based Platform for Collecting Behavioural Models and Supporting the Design of AMS Systems  Torsten Mähne and Alain Vachoux                                            | 69 |

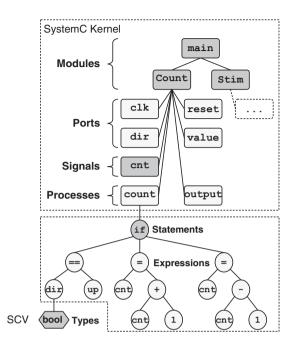

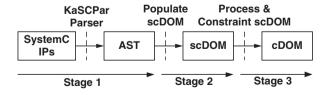

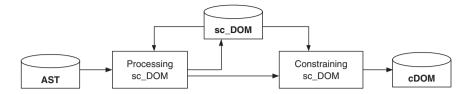

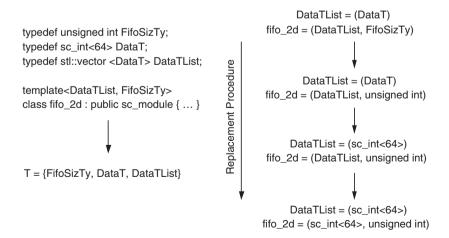

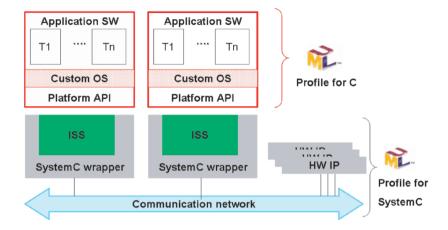

| Part II C/C++-Based System Design Introduction Frank Oppenheimer                                                                                                                        | 91 |

| 6 The Quiny SystemC <sup>TM</sup> Front End: Self-Synthesising Designs Thorsten Schubert and Wolfgang Nebel                                                                             | 93 |

| vi                                                                                                                                                                                                        | EMS |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

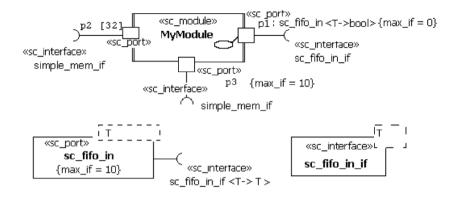

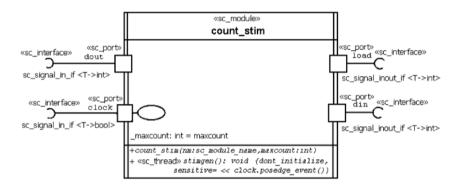

| 7 Mining Metadata from SystemC IP Library Deepak A. Mathaikutty and Sandeep K. Shukla                                                                                                                     | 111 |

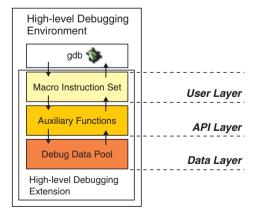

| 8<br>Nonintrusive High-level SystemC Debugging<br>Frank Rogin, Erhard Fehlauer, Steffen Rülke, Sebastian Ohnewald,<br>and Thomas Berndt                                                                   | 131 |

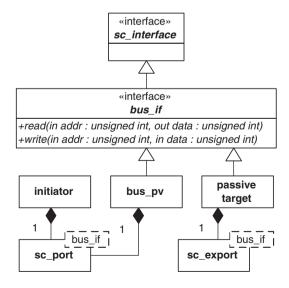

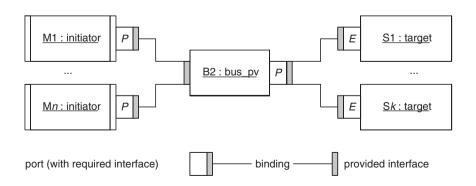

| 9<br>Transaction-Level Modeling in Communication Engine Design:<br>A Case Study<br>Vesa Lahtinen, Jouni Siirtola, and Tommi Mäkeläinen                                                                    | 145 |

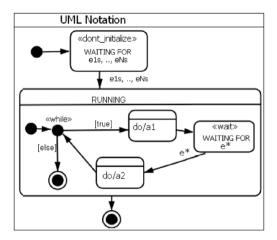

| 10<br>Object-Oriented Transaction-Level Modelling<br>Martin Radetzki                                                                                                                                      | 157 |

| Part III Formalisms for Property-Driven Design Introduction Dominique Borrione                                                                                                                            | 177 |

| An Efficient Synthesis Method for Property-Based Design<br>in Formal Verification: On Consistency and Completeness<br>of Property-Sets<br>Martin Schickel, Volker Nimbler, Martin Braun, and Hans Eveking | 179 |

| 12<br>Online Monitoring of Properties Built on Regular Expressions Sequences<br>Katell Morin-Allory, and Dominique Borrione                                                                               | 197 |

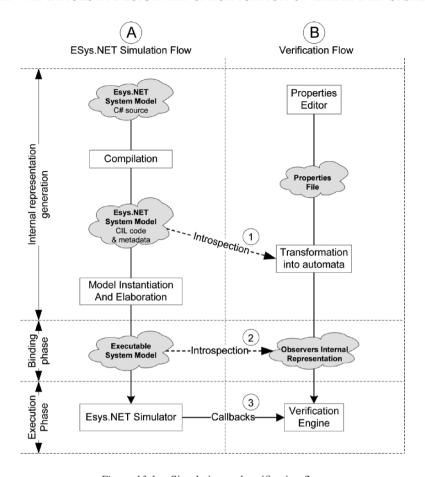

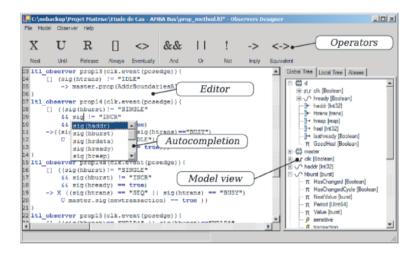

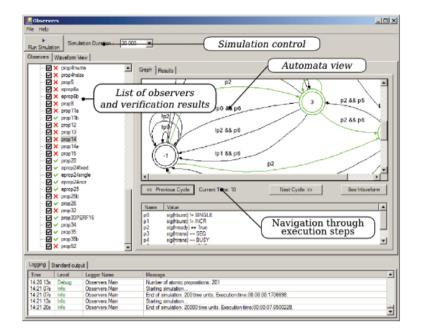

| 13 Observer-Based Verification Using Introspection: A System-level Verification Implementation M. Metzger, F. Bastien, F. Rousseau, J. Vachon, and E. M. Aboulhamid                                       | 209 |

| 14 Formalizing TLM with Communicating State Machines Bernhard Niemann, Christian Haubelt, Maite Uribe Oyanguren, and Jürgen Teich                                                                         | 225 |

| 15 Different Kinds of System Descriptions as Synchronous Programs  Jens Brandt and Klaus Schneider                                                                                                        | 243 |

| Contents                                                                                                                               | vii |

|----------------------------------------------------------------------------------------------------------------------------------------|-----|

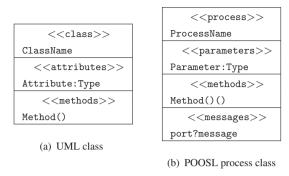

| Part IV UML-Based System Specification and Design<br>Introduction<br>Piet van der Putten                                               | 263 |

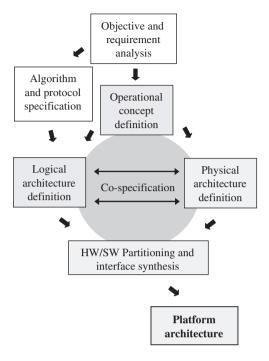

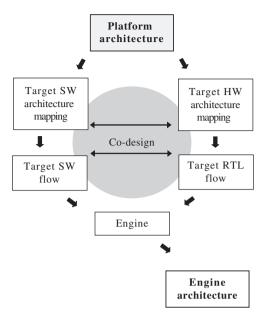

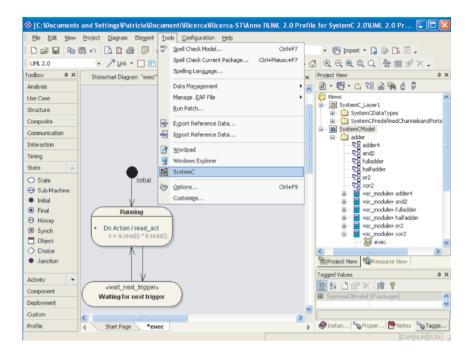

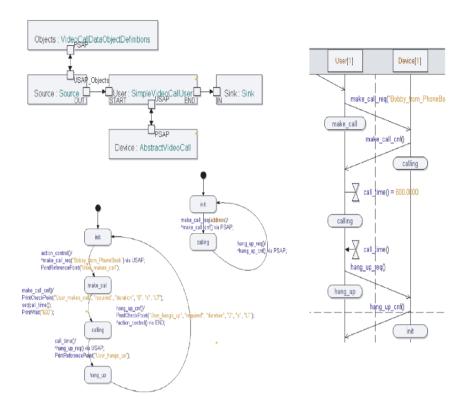

| 16<br>A Model-driven Co-design Flow for Embedded Systems<br>Sara Bocchio, Elvinia Riccobene, Alberto Rosti, and Patrizia Scandurra     | 265 |

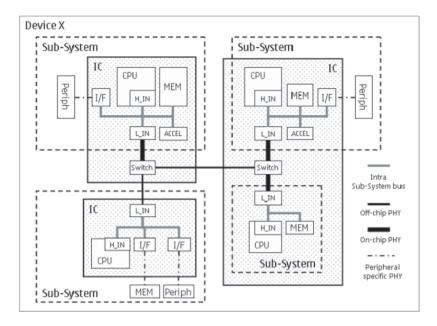

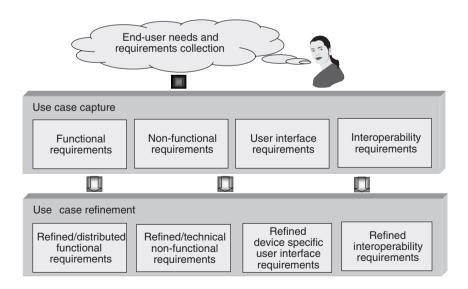

| 17<br>A Method for Mobile Terminal Platform Architecture Development<br>Klaus Kronlöf, Samu Kontinen, Ian Oliver, and Timo Eriksson    | 285 |

| 18 UML2 Profile for Modeling Controlled Data Parallel Applications Ouassila Labbani, Jean-Luc Dekeyser, Pierre Boulet, and Éric Rutten | 301 |

| 19<br>MCF: A Metamodeling-based Visual Component Composition Framework<br>Deepak A. Mathaikutty and Sandeep K. Shukla                  | 319 |

| 20<br>Reusing Systems Design Experience Through Modelling Patterns<br>Oana Florescu, Jeroen Voeten, Marcel Verhoef, and Henk Corporaal | 339 |

#### **Preface**

This book is the latest contribution to the Chip Design Languages series and it consists from selected papers presented at the Forum on Specifications and Design Languages (FDL'06), which took place in September 2006 at Technische Universität Darmstadt, Germany.

FDL, an ECSI conference, is the premier European forum to present research results, to exchange experiences, and to learn about new trends in the application of specification and design languages as well as of associated design and modelling methods and tools for integrated circuits, embedded systems, and heterogeneous systems. Modelling and specification concepts push the development of new methodologies for design and verification to system level, they thus provide the means for a model-driven design of complex information processing systems in a variety of application domains. The aim of FDL is to cover several related thematic areas and to give an opportunity to gain upto-date knowledge in this fast evolving area. FDL'06 is the ninth of a series of successful events that were held previously in Lausanne, Lyon, Tübingen, Marseille, Frankfurt am Main, and Lille.

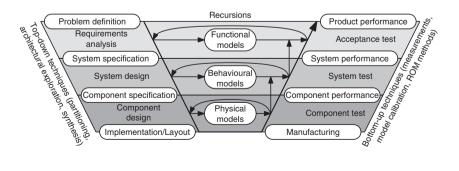

Embedded systems are meanwhile in the focus of industry in quite different application domains such as automotive, avionics, telecom, and consumer products. The need for a shift in design methodologies towards system level design is widely recognised and design flows aimed to an integration of software and hardware specification and implementation approaches are being developed. Standardization efforts, such as SystemC Transaction Level Modelling and Model Driven Architecture of the OMG, provide the foundations of these new design flows. Design and specification languages are of utmost interest in the area of embedded systems and the Forum on Specification and design Languages has been once again been the main European event for the embedded systems and chip design community.

This book presents a collection of the best papers from FDL'06, which were selected by the topic area programme chairs Dominique Borrione, Christoph Grimm, Frank Oppenheimer, and Piet van der Putten. The book is structured into four main parts:

Part I – Analog, Mixed-Signal, and Heterogeneous System Design: Design methodologies that exploit a mix of continuous-time and discrete-event modelling languages such as VHDL-AMS, Verilog-AMS, SystemsC–AMS, or Modelica for the design and verification of heterogeneous systems.

Part II – C/C++ Based System Design: Design methodologies that use C/C++ or dedicated modelling languages such as SystemC, SystemVerilog, Verilog, and VHDL jointly with verification languages such as 'e' or PSL/Sugar for the design and verification of hardware/software systems.

Part III – Formalisms for Property-Driven Design: Verification of functional behaviour, generation of test stimuli, model checking on the reachable state space, and direct synthesis.

Part IV – UML-Based System Specification and Design: Specification and design methodologies such as the Model Driven Architecture that rely on UML to map abstract models of complex embedded systems to programmable hardware platforms and to System-on-a-Chip architectures.

The 20 chapters of this book present recent and significant research results in the areas of design and specification languages for embedded systems, SoC, and integrated circuits. I am sure that this book will be a valuable help and reference to researchers, practitioners, and even to students in the field of design languages for electronic components and embedded systems.

Finally, I would like to express my special thanks to Felix Madlener, who put a lot of work into the preparation of this book.

Sorin Alexander Huss General Chair of FDL'06 Technische Universität Darmstadt Darmstadt, Germany, December 2006

### ANALOG, MIXED-SIGNAL, AND HETEROGENEOUS SYSTEM DESIGN

#### Introduction

The following part of the book focuses the design of analogue and mixed-signal circuits and systems. Compared with the design of digital systems, tools for synthesis are not yet mature or even used in industry. Design of analogue systems is done mostly interactive and done using modelling and simulation. One might think that simulation of analogue circuits with now nearly 50 years of practice and research is mature and stable. However, this is not the case and we see even new challenges. In the following we give a selection of five excellent contributions to hot topics in the modelling, simulation, reuse and verification of analogue and mixed-signal systems.

New technologies like nanotubes are currently emerging and require of course new device models. The first contribution describes the modelling of devices in such emerging technologies and gives the reader an interesting insight into new challenges for at least the next 10 years.

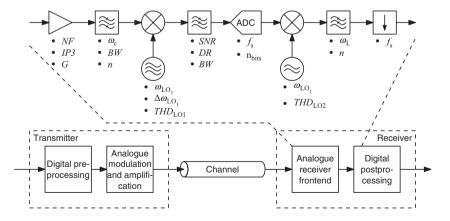

Compared with the design of analogue circuits in the past, we have to analyse the overall behaviour of systems where DSP methods and analogue hardware are interwoven. Today, this is a problem especially when we combine RF components with digital and DSP hardware. The area of baseband modelling is tackled in the second contribution.

Furthermore, system simulation requires behavioural models to get sufficient simulation performance. However, the speed-up of using behavioural models is not yet sufficient. The third contribution describes possible simulator improvements to increase simulation performance of behavioural models.

For the design of analogue systems, there are not yet established tools for synthesis, and analogue design is therefore expensive. An important mean to increase productivity is reuse at different levels of abstraction. The fourth section describes a platform to support the reuse of analogue (and mixed-signal) components by a well-designed web interface with database.

Finally, verification is an important issue – especially with increasing complexity. The fifth contribution describes methods for behavioural modelling with special focus on system verification.

Christoph Grimm

#### Chapter 1

# COMPACT MODELING OF EMERGING TECHNOLOGIES WITH VHDL-AMS

Fabien Prégaldiny<sup>1</sup>, Christophe Lallement<sup>1</sup>, Birahim Diagne<sup>1</sup>, Jean-Michel Sallese<sup>2</sup>, and François Krummenacher<sup>2</sup>

<sup>1</sup>InESS (Institut d'Électronique du Solide et des Systèmes) Parc d'innovation, BP 10413 67412 Illkirch Cedex, France fabien.pregaldiny@iness.c-strasbourg.fr christophe.lallement@ensps.u-strasbg.fr birahim@iness.c-strasbourg.fr

<sup>2</sup>IMM-EPFL CH-1015, Lausanne, Switzerland jean-michel.sallese@epfl.ch francois.krummenacher@epfl.ch

#### Abstract

This paper deals with the compact modeling of several emerging technologies: first, the double-gate MOSFET (DG MOSFET), and second, the carbon nanotube field-effect transistor (CNTFET). For CNTFETs, we propose two compact models, the first one with a classical behavior (like MOSFET), and the second one with an ambipolar behavior (Schottky-barrier CNTFET). All the models have been compared with numerical simulations and then implemented in VHDL-AMS.

**Keywords** Compact model, double-gate MOSFET, CNTFET, VHDL-AMS

#### 1. Introduction

Since the introduction of transistors, continuous reduction of electronic circuit size and power dissipation have been the ongoing theme in electronics industry. The well-known "Moore's law" represents this evolution. However,

as the feature size becomes smaller, scaling the silicon MOSFET becomes increasingly harder. This increasing challenge is often attributed to: (1) quantum mechanical tunneling of carriers through the thin gate oxide; (2) quantum mechanical tunneling of carriers from source to drain and from drain to body; (3) control of the density and location of dopant atoms in the channel and source/drain region to provide high on/off current ratio.

There are many solutions proposed to circumvent these limitations. Some solutions include modifications on the existing structures and technologies in hopes of extending their scalability. The DG MOSFET is recognized as one of the most promising candidates for future very large-scale integrated (VLSI) circuits [1, 2]. In DG MOSFETs, short-channel immunity can be achieved with an ideal subthreshold swing (60 mV/dec). Other solutions involve using new materials and technologies to replace the existing silicon MOSFETs. Among them, new device structures as carbon nanotube-based transistors (CNTFETs) are regarded as an important contending device to replace silicon transistors [3].

These new technologies and devices require the creation of accurate compact models, suited to the circuit design and easily translatable into a hardware description language (HDL) such as VHDL-AMS.

This paper is organized as follows. In Section 2, we present an explicit model for the symmetric DG MOSFET that is simple, inherently continuous, and computationally efficient. By introducing useful normalizations as in the EKV MOSFET model, we have derived simple and clear relationships which are really helpful for the circuit designer [4]. In Section 3, we propose two compact models for CNTFETs, the first one with a conventional behavior (i.e. a MOSFET behavior), and the second one with an ambipolar behavior. The former is based on an existing model developed at Purdue University [5]. Unfortunately, in its present form, this model is not appropriate for circuit simulation. In this paper, we propose an efficient compact model for the designer, with a range of validity clearly defined. The second model is devoted to compact modeling of the CNTFET with an ambipolar behavior (n- or p-type depending of the gate voltage value). This characteristic is quite different from a classic behavior, namely a MOSFET behavior. To our best knowledge, this compact model is the first analytical ambipolar model for CNTFET introduced in the literature. It is a behavioral compact model that simulates in a realistic way the ambipolar characteristic observed with Schottky-Barrier (SB) CNTFETs.

#### 2. Double-Gate MOSFET

#### A Compact Model Dedicated to the Design

For the last decade, a significant research effort in this field has led to the development of physical models for the DG MOSFET [6–8]. These models are of major interest for the design of the device itself but less useful for

circuit simulation since they rely on very complicated formulations. Among the proposed models, Taur's model [9] is one of the best candidates for building a compact model. An exact solution for both charges and current has been proposed and successfully validated. However, such a model, in its current form, is not really suited for circuit simulation because it requires an iterative procedure to compute the mobile charge density, which is generally considered to be time consuming.

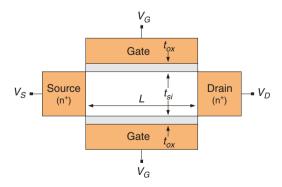

The main assumptions of our new model are the following: the body (i.e. the silicon layer) is undoped or lightly doped, the mobility is constant along the channel and both quantum effects and polydepletion effect are neglected. The last assumption is valid for silicon layer thicknesses down to at least 20 nm. For thinner layers, quantum effects start to play a role [6, 8], but might actually be considered as a correction to the classical derivation. The schematic diagram of the DG MOSFET considered in this work is shown in Fig. 1.1.

Using the normalization of charges, potentials, and current proposed in [4] leads to an important relationship between charge densities and potentials, given by

$$v_g^* - v_{ch} - v_{to} = 4 \cdot q_g + \ln q_g + \ln \left( 1 + q_g \cdot \frac{C_{ox1}}{C_{si}} \right)$$

(1.1)

where  $v_g^*$  is the effective gate voltage (=  $v_g - \Delta \phi_i$  with  $\Delta \phi_i$  the work function difference between the gate electrode and intrinsic silicon),  $v_{ch}$  is the electron quasi-Fermi potential,  $v_{to}$  is the threshold voltage,  $q_g$  is the charge density per unit surface of each gate,  $C_{ox1}$  is the gate oxide capacitance per unit surface of each gate and  $C_{si}$  is the silicon layer capacitance per unit surface.

Such a normalization represents an efficient tool for the analog designer because it is done taking into account the design methodologies requirements [10]. However, (1.1) needs to be solved numerically and this is not desirable

Figure 1.1. Schematic of the DG MOSFET structure.

for circuit simulation (it requires at least several iterations). To overcome this drawback, we have developed a new methodology to compute without any iteration the mobile charge density as an explicit function of bias voltages ( $v_g$  and  $v_d$  or  $v_s$ ) [11]

$$q_g = f(v_g, v_{ch})$$

with  $v_{ch} = v_s$  or  $v_d$  (1.2)

Without entering into details, the numerical inversion of (1.1) can be performed using a reduced set of precomputed parameters that depend only on the "form factor"  $\alpha = C_{ox1}/C_{si}$ . Let us emphasize that our algorithm of numerical inversion fully preserves the physics of (1.1), and therefore its validity is technology-independent [11].

Then, noting that the mobile charge density is twice the gate charge density  $(q_m = -2\,q_g)$  and assuming that the drift-diffusion transport model is valid, the normalized drain current i can be expressed as

$$i = -\int_{v_s}^{v_d} q_m \cdot dv_{ch} \tag{1.3}$$

Integrating (1.3) from source to drain yields

$$i = -q_m^2 + 2 \cdot q_m + \frac{2}{\alpha} \cdot \ln\left(1 - \frac{\alpha \cdot q_m}{2}\right) \Big|_{q_{ms}}^{q_{md}}$$

(1.4)

Finally, the drain current  $I_D$  is obtained after denormalization of (1.4) as outlined in [11].

To conclude this brief description of the model, it should be said that in addition to the static part, a more complete compact model should include the dynamic part, i.e. the transconductances and the whole set of transcapacitances. The derivation of the dynamic model is not within the scope of this paper and the reader is referred to references [12, 13] for full details. However, let us emphasize that the VHDL-AMS code of our model includes both static and dynamic models [11].

#### **VHDL-AMS Implementation**

VHDL-AMS [14] is an HDL which supports the modeling and the simulation of analog and mixed-signal systems. It supports the description of continuous-time behavior. For compact modeling, the most interesting feature of the language is that it provides a notation for describing Differential Algebraic Equations (DAEs) in a fairly general way [15]. The == operator and the way the quantities (bound to terminals or free) are declared allow the designer to write equations in either implicit or explicit format. VHDL-AMS supports the description of networks as conservative-law networks (Kirchhoff's networks)

and signal-flow networks (inputs with infinite impedance, outputs with zero impedance). As such, it supports the description and the simulation of multi-discipline systems at these two levels of abstraction. Conservative-law relationships assume the existence of two classes of specialized quantities, namely *across quantities* that represent an effort (e.g. a voltage for electrical systems), and *through quantities* that represent a flow (e.g. a current for electrical systems).

Listing 1 presents the *entity* part of the VHDL-AMS code for the DG MOS-FET model. The code first contains references to libraries needed to parse the model (lines 1–3). For the model end user (circuit designer), the most important part of the model is the interface, contained in what is called an entity in VHDL-AMS (lines 4–11).

```

(1)

library ieee; library disciplines;

(2)

use disciplines.electromagnetic_system.all;

(3)

use work.all;

entity dg_mosfet is

(4)

(5)

generic(W

:real:= 1.0e-6; -- Gate width [m]

:real:= 1.0e-6; -- Gate length [m]

(6)

tox1 :real:= 2.0e-9; -- Gate oxide thickness [m]

(7)

(8)

tsi :real:= 25.0e-9; -- Si film thickness [m]

(9)

mu0 :real:= 0.1); -- Low-field mobility [m^2/Vs]

(10)

port (terminal g1,g2,d,s :electrical);

(11) end:

```

Listing 1. Interface of the DG MOSFET VHDL-AMS model: the entity.

The model interface includes the specification of generic parameters (lines 5–9) and interface ports (line 10). The generic statement allows the designer to define its own values for the model parameters. Typically, geometrical W and L transistor parameters are defined as generic. The dg\_mosfet entity contains four terminals (g1, g2, d, and s stand for the top gate, bottom gate, drain, and source terminal, respectively), all of electrical type. All the terminals are part of a port statement. The second part of the VHDL-AMS code is self-explicit. The device behavior is defined in an architecture named symmetric (130 lines of code [11]).

#### **Results and Discussion**

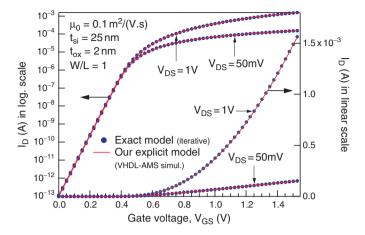

To conclude this section, we present the results obtained with the VHDL-AMS simulations of the DG MOSFET model. Figure 1.2 illustrates the computation of the drain current  $I_D$  at  $V_{DS}=50~\rm mV$  and 1 V. The VHDL-AMS simulation gives evidence for the good numerical behavior of the model in all regions of operation. In particular, the phenomena of volume inversion (i.e. the weak-inversion region) is well described.

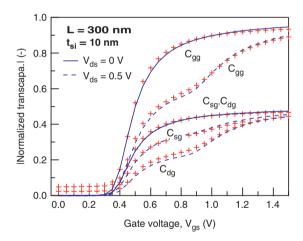

Figure 1.3 shows a common set of normalized transcapacitances (with respect to  $C_{OX}=2WLC_{ox1}$ ) versus the gate voltage. An important point is that all

Figure 1.2. Comparison between the results extracted from a VHDL-AMS simulation and the exact iterative model (dots, cf. [9]) for the drain current  $I_D$  vs.  $V_{GS}$  of a symmetrical DG MOSFET.

Figure 1.3. Comparison between the C-V curves obtained by the explicit model (lines) and 2D simulations (markers).

transcapacitances are continuous between all operating regions without using any fitting parameter, which makes our explicit model numerically robust as well as close to physics. It appears that the model predictions are accurate and fit the 2D simulations in all cases, namely at  $V_{DS}=0$  and  $V_{DS}\neq 0$ . The slight deviation in the subthreshold region results from the increasing influence of the overlap capacitance as the channel length decreases. For devices with  $L\geqslant 1~\mu\mathrm{m}$ , the overlap capacitance is negligible. A further development of the model will include the extrinsic capacitances.

#### 3. CNTFETs

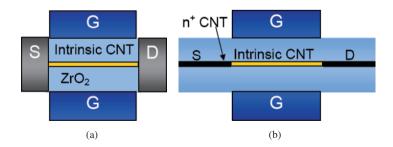

Carbon nanotubes (CNTs) are currently considered as promising building blocks of a future nanoelectronic technology. CNTs are hollow cylinders composed of one or more concentric layers of carbon atoms in a honeycomb lattice arrangement. Single-walled nanotubes (SWCNTs) typically have a diameter of 1-2 nm and a length up to several micrometers. The large aspect ratio makes the nanotubes nearly ideal one-dimensional (1D) objects, and as such the SWCNTs are expected to have all the unique properties predicted for these low-dimensional structures [3]. In addition, depending on the detailed arrangement of the carbon atoms the SWCNTs can be metallic or semiconducting. Two types of semiconducting CNTs are being extensively studied. One of these devices is a tunneling device, shown in Fig. 1.4(a). It works on the principle of direct tunneling through a Schottky barrier at the source-channel (and drain-channel) junction. The barrier width is modulated by the application of gate voltage and thus the transconductance of the device is dependent on the gate voltage. To overcome these handicaps associated with the SB CNTFETs, there have been attempts to develop CNTFETs which would behave like normal MOSFETs [Fig. 1.4(b)]. In this MOSFET-like device, the ungated portion (source and drain regions) is heavily doped and the CNTFET operates on the principle of barrier-height modulation by application of the gate potential. In this case, the on-current is limited by the amount of charge that can be induced in the channel by the gate. It is obvious that the MOSFET-like device will give a higher on-current and, hence, would define the upper limit of performance.

Transport through short nanotubes has been shown to be free of significant acoustic and optical phonon scattering and thus is essentially ballistic at both high and low voltage limits. In the following, we consider MOSFET-like mode of operation, and assume ballistic transport.

The theory of CNT transistors is still primitive and the technology is still nascent. However, evaluation of such high-performance transistors in digital

Figure 1.4. Different types of CNTFETs: (a) Schottky-barrier (SB) CNTFET with ambipolar behavior, and (b) MOSFET-like CNTFET with classic behavior.

circuits is absolutely essential to drive the device design and devise new architectures. However, from the circuit designer's point of view, circuit simulation and evaluation using CNTFETs is challenging because most of the developed models are numerical, involving self-consistent equations which circuit solvers like SPICE are not able to handle.

#### **MOSFET-like CNTFET**

First, we present a compact model for CNTFETs with a classical behavior. This compact model is based on a CNTFET model developed at Purdue University [5]. To our best knowledge, Purdue's model is the first *compact model* (i.e. fully dedicated to circuit simulation) of CNTFET available in the literature. It is a surface potential-based SPICE compatible model that enables to simulate CNTs with ballistic behavior. It has been incorporated in HSPICE but is not well-suited for circuit simulation due to some convergence issues.

In this paper, we propose a modified model with fundamental improvements solving the convergence problems of the original model. The new model is applicable to a wide range of CNTFETs with diameters between 1 and 3 nm and for all chiralities as long as they are semiconducting. The model uses suitable approximations necessary for developing any quasi-analytical, circuit-compatible compact model (see Fig. 1.5). Quasi-static characteristics (I-V) have been modeled and validated against numerical models, with an excellent agreement.

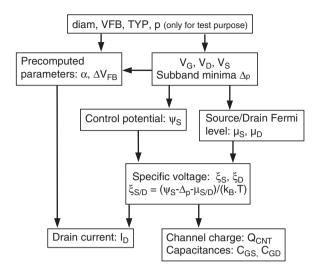

The computional procedure to evaluate the drain current  $I_D$  and the total channel charge  $Q_{CNT}$  is illustrated in Fig. 1.6. The main quantities used in the model are the surface potential  $\psi_S$  (or control potential) and the specific voltage  $\xi_{S(D)}$  that depends on the surface potential, the subbands energy level  $\Delta_p$  and the source (drain) Fermi level  $\mu_{S(D)}$ . The conduction band minima for the first subband is set to half the nanotube bandgap  $\Delta_1$  with  $\Delta_1 \simeq 0.45/{\rm diam}$  (in eV).

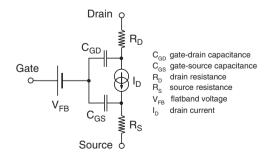

Figure 1.5. Schematic of the CNTFET compact model.

Figure 1.6. Structure of the CNTFET compact model.

The physical parameter diam is the nanotube diameter (in nm); it is one of the only three intrinsic parameters of our model, with the flatband voltage  $V_{FB}$  and the TYP parameter (= +1/-1 for n- or p-type device). Let us emphasize the number of subbands p has been added as an input parameter only for test purpose [16].

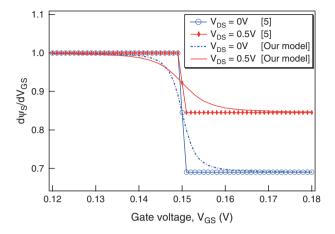

**Determination of the surface potential.** An important step in the model development is to relate the control potential with the gate bias voltage (see Fig. 1.6). The knowledge of  $\psi_S$  is useful to calculate the specific voltage  $\xi$ . This allows us to determine the drain current and the total charge. In [5], the following approximation has been proposed

$$V_{GS} - \psi_S = \begin{cases} 0 & \text{for } V_{GS} < \Delta_1, \\ \alpha \cdot (V_{GS} - \Delta_1) & \text{for } V_{GS} \geqslant \Delta_1. \end{cases}$$

(1.5)

where the parameter  $\alpha$  is given by

$$\alpha = \alpha_0 + \alpha_1 \cdot V_{DS} + \alpha_2 \cdot V_{DS}^2 \tag{1.6}$$

where  $\alpha_0$ ,  $\alpha_1$ , and  $\alpha_2$  are dependent on both CNTFET diameter and gate oxide thickness [16]. Eq. (1.5) is correct to model the relationship between the gate voltage and the surface potential, but is not well-suited for a compact model (problem of discontinuity, as shown in Fig. 1.7). Therefore, we propose

Figure 1.7. Derivative of surface potential  $\psi_S$  vs.  $V_{GS}$ .

an equivalent solution, given by (1.7), but with an excellent behavior of the derivative (see Fig. 1.7)

$$\psi_S = V_{GS} - \frac{\alpha(V_{GS} - \Delta_1) + \sqrt{[\alpha(V_{GS} - \Delta_1)]^2 + 4\epsilon^2}}{2}$$

(1.7)

where  $\epsilon = 5 \cdot 10^{-2}$  is a smoothing parameter.

Then, the total drain current  $I_D$  is obtained as

$$I_D = \frac{4 q k_B T}{h} \sum_{p} \left[ \ln \left( 1 + \exp(\xi_S) \right) - \ln \left( 1 + \exp(\xi_D) \right) \right]$$

(1.8)

where p is the number of subbands,  $k_B$  and h are the constants of Boltzmann and Planck, respectively.

**Quantum-Capacitance Derivation.** With the knowledge of charge and surface potential as functions of gate bias, the gate input capacitance  $C_G$  can be computed in terms of the device parameters and terminal voltages. The gate input capacitance is given by

$$C_G = \frac{\partial Q_{CNT}}{\partial V_{GS}} \Rightarrow C_G = \frac{\partial Q_{CNT}}{\partial \psi_S} \cdot \frac{\partial \psi_S}{\partial V_{GS}}$$

(1.9)

The total charge  $Q_{CNT}$  can be split up into  $Q_S$  and  $Q_D$  and, hence, the total gate capacitance can also be split up into  $C_{GS}$  and  $C_{GD}$  (see Fig. 1.5).

To elaborate an efficient expression of  $C_G$  for a compact model, it is important to first have a closed-form expression of  $Q_{CNT}(\psi_S)$  and continuous derivatives of (1.9) as well. As it is not possible to obtain a closed-form relationship for the

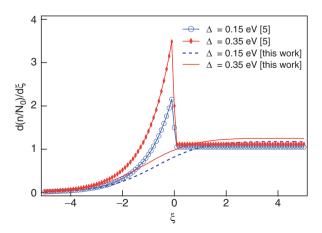

quantum-charge in the channel, an empirical solution (fit) has been proposed in [5]. Noting that the number of carrier n increases almost linearly as  $\xi$  increases and falls off exponentially as  $\xi$  becomes negative, the following relationship has been derived

$$n = \begin{cases} N_0 \cdot A \cdot \exp \xi & \text{for } \xi < 0, \\ N_0 \cdot (B \cdot \xi + A) & \text{for } \xi \geqslant 0. \end{cases}$$

(1.10)

where the parameters A and B are dependent on the energy level  $\Delta$  [5].

Eq. (1.10) is unfortunately not appropriate for circuit simulation because its derivatives are not continuous (Fig. 1.8). Accordingly, the different capacitances determined by (1.10) would not be correct to elaborate the CNTFET dynamic model. In addition, this would lead to numerical problems during simulation and wrong results. In order to solve the numerical problems, we have elaborated a new equation for n, similar to the interpolation function of the EKV MOSFET model [10]. This new expression and its derivatives (Fig. 1.8) are continuous and well-suited for circuit simulation, especially in dynamic operation

$$n_{\text{new}}(\xi) = N_0 \cdot 1.2 \cdot B \cdot \left\{ \ln \left[ 1 + \frac{A}{1.2 \cdot B} \cdot \exp\left(\frac{\xi}{0.96}\right) \right] \right\}^{0.96}$$

(1.11)

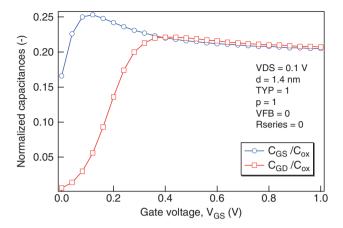

Figure 1.8 shows a comparison between the derivatives of (1.10) and (1.11). Let us note that the greatest difference can be observed around zero, where actually the former overestimates the quantum-charge (see Fig. 4 in [5]). The VHDL-AMS simulation of the capacitances computed with our continuous model is shown in Fig. 1.9.

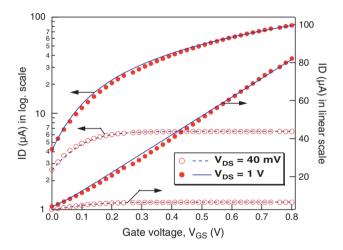

Figure 1.10 shows the drain current of a 1.4 nm diameter CNTFET with  $C_{ox}=3.8~\mathrm{pF/cm}$  as a function of gate voltage. The dots correspond to the

Figure 1.8. Improvement of the numerical behavior.

Figure 1.9. VHDL-AMS simulation of the  $C_{GS}$  and  $C_{GD}$  capacitances for a MOSFET-like CNTFET with  $C_{ox}=3.8$  pF/cm.

Figure 1.10. Comparison between the results extracted from VHDL-AMS and numerical simulations (lines and dots, respectively) for the drain current of a MOSFET-like CNTFET (p=1, diam =1.4, TYP=+1, VFB=0, Reries=0).

numerical solutions performed with the FETToy simulator [17] whereas the lines correspond to our analytical compact model. A good agreement is found, which supports the validity of our approach.

#### **VHDL-AMS Implementation**

First, we have calibrated the model of Purdue with respect to numerical simulations [18, 17]. The best fits were obtained with p=1 (i.e. one subband)

which is coherent because the FETToy simulator only accounts for the lowest subband. So, at the beginning, we fixed p=1 in our model in order to validate it with respect to the numerical simulations. Then, if we consider CNTFETs with diameters ranging from 1 to 3 nm, and with a power supply lower than 1 V, we can set p=5 to accurately describe all cases [16].

The whole VHDL-AMS code of the model requires about 90 lines. Only three intrinsic parameters are necessary: diam, TYP (+1 for n-type, -1 for p-type) and  $V_{FB}$  (lines 5–7 in Listing 2).

```

(1)

library ieee; library disciplines;

(2)

use disciplines.electromagnetic_system.all;

(3)

use work.all;

(4)

entity CNTFET is

(5)

generic(diam

: real := 1.4; -- Nanotube diameter [nm]

: real := 1.0; -- n/p-CNTFET (+1/-1)

(6)

TYP

(7)

: real := 0.0; -- Flatband voltage [V]

(8)

: positive := 1; -- Number of subbands [-]

(9)

Rseries : real := 50.0e3); -- Series resistance [ohm]

(10)

port(terminal g,d,s : electrical);

(11) end:

```

Listing 2. Interface of the CNTFET VHDL-AMS model: the entity.

Let us note that the number of subbands p has been defined as a generic parameter only for test purpose [16]. Rseries corresponds to the total series resitance, that is  $R_{\rm source} + R_{\rm drain}$  with  $R_{\rm source} = R_{\rm drain}$ . The parameters  $\alpha_0$ ,  $\alpha_1$ , and  $\alpha_2$  [see (1.6)] are determined in a precomputed module, with the help of one equation for each of them. For all details about the computation of the parameters  $\alpha$ , the reader is referred to [16].

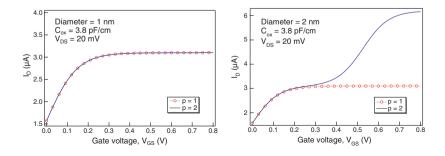

To conclude this section, Fig. 1.11 shows two VHDL-AMS simulations performed for different values of the parameters diam and p, in order to show the effect of the nanotube diameter on the number of subbands p to be accounted for. This behavior may be useful to create novel multiple-valued logic design [19].

Figure 1.11. VHDL-AMS simulations of  $I_D$  vs.  $V_{GS}$  at low drain bias.

#### **Ambipolar CNTFET**

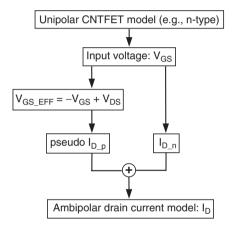

We present, for the first time to our best knowledge, a behavioral compact model that allows to describe the ambipolar characteristic of SB CNTFETs. This model is built using the new model of CNTFET previously presented. As shown in Fig. 1.12, an additional part has been added to the "unipolar" model. The entity (VHDL-AMS) corresponding to this new model is the same as the classical CNTFET model one.

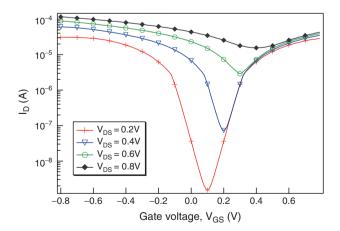

The very particular  $I_D$ – $V_{GS}$  characteristic of the ambipolar CNTFET is illustrated in Fig. 1.13. It should be noted that this behavior is quite similar to the numerical simulation results recently published in [20] and [21]. This

Figure 1.12. Structure of the behavioral model for the ambipolar CNTFET.

Figure 1.13. VHDL-AMS simulation of the drain current as a function of gate voltage for the ambipolar SB CNTFET (p = 1, diam = 1.4, TYP = +1, VFB = 0, Rseries = 0).

ambipolar characteristic should allow circuit designers to devise new architectures using that specific behavior [22, 23]. Our compact model may be of help to this issue.

#### 4. Conclusion

In this paper, different VHDL-AMS models for emerging technologies have been proposed. The DG MOSFET model is still under development, it will be completed with the modeling of additional effects such as quantum effects, extrinsic capacitances, in order to simulate accurately ultra short-channels DG MOSFETs. The second part of the paper dealt with the compact modeling of the CNTFET with VHDL-AMS. Two CNTFET compact models have been presented, the first one for carbon nanotubes with a classical behavior (like MOSFET), and the second one for devices with an ambipolar behavior. Although CNTFET technology is still nascent, these compact models developed in VHDL-AMS are useful tools to help the designers to devise new architectures.

#### Acknowledgment

This work was partially funded by the French Ministry of Research under Nanosys ("Programme ACI Nanosciences").

#### References

- [1] D.J. Frank, R.H. Dennard, E. Nowak, P.M. Solomon, Y. Taur, and H.-S.P. Wong. Device scaling limits of Si MOSFETs and their application dependencies. *Proc. of IEEE*, 89(3):259–288, 2001.

- [2] International technology roadmap for semiconductors 2004 update. [Online]. Available: http://public.itrs.net/ [May 2005].

- [3] P. Avouris, J. Appenzeller, R. Martel, and S.J. Wind. Carbon nanotube electronics. *Proc. of IEEE*, 91(11):1772–1784, 2003.

- [4] J-M. Sallese, F. Krummenacher, F. Prégaldiny, C. Lallement, A. Roy, and C. Enz. A design oriented charge-based current model for symmetric DG MOSFET and its correlation with the EKV formalism. *Solid-State Electron.*, 49(3):485–489, 2005.

- [5] A. Raychowdhury, S. Mukhopadhyay, and K. Roy. A circuit-compatible model of ballistic carbon nanotube field-effect transistors. *IEEE Trans. Computer-Aided Design*, 12(10):1411–1420, 2004.

- [6] L. Ge and J.G. Fossum. Analytical modeling of quantization and volume invesion in thin Si-film double-gate MOSFETs. *IEEE Trans. Electron Devices*, 49(2):287–294, 2002.

- [7] Y. Taur. An analytical solution to a double-gate MOSFET with undoped body. *IEEE Electron Device Lett.*, 21(5):245–247, 2000.

- [8] J.G. Fossum, L. Ge, M-H. Chiang, V.P. Trivedi, M.M. Chowdhury, L. Mathew, G.O. Workman, and B-Y. Nguyen. A process/physics-based compact model for nonclassical CMOS device and circuit design. *Solid-State Electron.*, 48:919–926, 2004.

- [9] Y. Taur, X. Liang, W. Wang, and H. Lu. A continuous, analytic drain-current model for DG MOSFETs. *IEEE Electron Device Lett.*, 25(2): 107–109, 2004.

- [10] C. Enz, F. Krummenacher, and E. Vittoz. An analytical MOS transistor model valid in all regions of operation and dedicated to low-voltage and low-current applications. *Journal of AICSP*, pp. 83–114, 1995.

- [11] F. Prégaldiny, F. Krummenacher, B. Diagne, F. Pêcheux, J-M. Sallese, and C. Lallement. Explicit modelling of the double-gate MOSFET with VHDL-AMS. *Int. Journ. of Numerical Modelling: Elec. Networks, Devices and Fields*, 19(3):239–256, 2006.

- [12] J-M. Sallese and A.S. Porret. A novel approach to charge-based non-quasi-static model of the MOS transistor valid in all modes of operation. *Solid-State Electron.*, 44:887–894, 2000.

- [13] F. Prégaldiny, F. Krummenacher, J-M. Sallese, B. Diagne, and C. Lallement. An explicit quasi-static charge-based compact model for symmetric DG MOSFET. In: NSTI-Nanotech 2006, WCM, vol. 3, pp. 686–691, 2006. ISBN 0-9767985-8-1.

- [14] 1076.1-1999 IEEE Standard VHDL Analog and Mixed-Signal Extensions Language Reference Manual, IEEE Press edition, 1999. ISBN 0-7381-1640-8.

- [15] F. Pêcheux, C. Lallement, and A. Vachoux. VHDL-AMS and Verilog-AMS as alternative hardware description languages for efficient modelling of multi-discipline systems. *IEEE Trans. Computer-Aided Design*, 24(2):204–224, 2005.

- [16] F. Prégaldiny, C. Lallement, and J.-B. Kammerer. Design-oriented compact models for CNTFETs. In: *Proc. of IEEE DTIS'06*, pp. 34–39, 2006.

- [17] NANOHUB online simulations and more, CNT bands. [Online]. Available: http://www.nanohub.org [April 2006].

- [18] J. Guo, M. Lundstrom, and S. Datta. Performance projections for ballistic carbon nanotube field-effect transistors. *App. Phys. Letters*, 80(17): 3192–3194, 2002.

- [19] A. Raychowdhury and K. Roy. Carbon-nanotube-based voltage-mode multiple-valued logic design. *IEEE Trans. Nanotechno.*, 4(2):168–179, 2005.

- [20] J. Knoch, S. Mantl, and J. Appenzeller. Comparison of transport propoerties in carbon nanotube field-effect transistors with Schottky contacts and doped source/drain contacts. *Solid-State Electron.*, 49:73–76, 2005.

- [21] J. Guo, S. Datta, and M. Lundstrom. A numerical study of scaling issues for schottky-barrier carbon nanotube transistors. *IEEE Trans. Electron Devices*, 51(2):172–177, 2004.

- [22] R. Sordan, K. Balasubramanian, M. Burghard, and K. Kern. Exclusive-OR gate with a single carbon nanotube. *App. Phys. Letters*, 88, 2006. 053119.

- [23] F. Prégaldiny, C. Lallement, and J.-B. Kammerer. Compact modeling and applications of CNTFETs for analog and digital circuit design. In: *Proc. of IEEE ICECS'06*, pp. 1030–1033, 2006.

#### Chapter 2

# BASEBAND MODELING USING MULTIDIMENSIONAL NETWORKS IN VHDL-AMS

#### Joachim Haase

Fraunhofer-Institut Integrierte Schaltungen/Branch Lab Design Automation EAS Zeunerstr. 38, D-01069 Dresden, Germany

Joachim.Haase@eas.iis.fraunhofer.de

#### Abstract

Baseband models are widely used to describe the behavior of RF systems. They suppress the RF carrier. Thus, they are many times faster than passband models that evaluate every carrier cycle during the simulation. Nevertheless, passband models are necessary for the component design. To support the top-down design approach, consistent models at baseband and passband level are required. The paper shows how the consistency can be achieved using consequently the possibilities of overloading functions and operators in VHDL-AMS. The mathematical basis is a consistent usage of the describing function theory for baseband modeling. The classical approach of baseband modeling can be extended by completing the waveforms that carry the in-phase and quadrature component by a time-discrete or time-continuous waveform that saves the carrier frequency information. This allows to handle systems with different carriers in different parts of a system or to sweep the carrier frequency during the simulation.

**Keywords** VHDL-AMS, baseband modeling, describing function

#### 1. Introduction

Standard languages as Verilog-A, Verilog-AMS, and VHDL-AMS [1] are available to model the behavior of mixed-signal circuits and systems. They provide greater understanding of systems early in the design process. In order to be able to compare different system architectures a high execution speed of the simulation is required.

Baseband models fulfill these requirements for a wide class of RF systems [3, 7]. They are not as accurate as passband models but they are much faster. The idea behind baseband descriptions is that narrow band analog waveforms with the carrier frequency f can be represented by the following equation

$$x(t) = A(t) \cdot \cos(\omega t + \varphi(t)) = I(t) \cdot \cos(\omega t) - Q(t) \cdot \sin(\omega t) \quad (2.1)$$

that means

$$x(t) = Re\left(\left(I(t) + j \cdot Q(t)\right)e^{j\omega t}\right) \tag{2.2}$$

where  $\omega=2\pi\cdot f$  and Re gives access to the real part of a complex number. All the waveforms x,A,f,I, and Q are scalar real-valued time-continuous waveforms. A special waveform x(t) is characterized by a 3 tupel (I(t),Q(t),f). x is called the passband representation and the 3 tupel carries the information of the baseband representation of the waveform. The set of all waveforms that can be described in this way shall be indicated by  $X_{PB}(f)$  for the passband representation and  $X_{BB}(f)$  for the baseband representation. The sum  $I(t)+j\cdot Q(t)$  be interpreted as a slowly varying phasor [3]. In the following we will try to define the baseband operations so that passband functionality can be mapped in an easy way to the baseband description.

The next section introduces the mapping in a formal way. Afterward, the implementation in VHDL-AMS is described and illustrated with the help of two examples.

#### 2. Baseband Modeling Approach

Linear operations as addition, subtraction, multiplication with a constant, and differentiation (see [10], [3]) in the passband can be easily assigned to linear operations in the baseband.

#### **Functions Without Frequency Shifting**

Considering a unary nonlinear passband map  $m_{PB}$ , then in the general case the range can be built up by the union of the sets characterized by the fundamental, its harmonics, and a static contribution

$$m_{PB}: X_{PB}(f) \to X_{PB}(0) \cup X_{PB}(f) \cup X_{PB}(2 \cdot f) \cup \dots$$

(2.3)

Subharmonics are not considered. Baseband modeling usually introduces the simplification that the associated baseband map  $m_{PB}$  only describes the mapping onto the set of fundamentals. That means

$$m_{BB}: X_{BB}(f) \to X_{BB}(f) \tag{2.4}$$

The modeling decision is whether this simplification can be accepted or not. Many linear and nonlinear maps can be represented using describing functions [5]. The describing function is the phasor representation of the output of a scalar (nonlinear) map at frequency f divided by the phasor representation of the argument of the map at frequency f.

**Modeling procedure.** Assume the describing function  $N(A, f) \in \mathbb{C}$  can be assigned to a passband map  $m_{PB}$  then the associated baseband map  $m_{BB}$  can be carried out in the following way

$$m_{BB}: X_{BB}(f) \rightarrow X_{BB}(f)$$

with  $(I(t), Q(t), t) \mapsto (Re(N(A(t), f) \otimes B(t)), Im(N(A(t), f) \otimes B(t)), f)$

with  $A(t) = \sqrt{I(t)^2 + Q(t)^2}$ ,  $B(t) = I(t) + j \cdot Q(t)$ , the multiplication sign  $\otimes$  in the complex area and access to the real and imaginary part of a complex number with Re and Im resp.  $\square$

#### Example 1

Figure 2.1 shows a nonlinear characteristic that can be used for modeling of low noise amplifiers [3].

$$\tilde{m}_{PB}: x(t) \mapsto \begin{cases} -A_{max} & \text{for } x(t) \leq A_{lim} \\ A_1 \cdot x(t) - A_3 \cdot x(t)^3 & \text{for others} \\ A_{max} & \text{for } x(t) \geq A_{lim} \end{cases}$$

with the real numbers  $A_1$ ,  $A_3$ ,  $A_{lim} = \sqrt{\frac{A_1}{3 \cdot A_3}}$  and  $A_{max} = \frac{2}{3} \cdot A_1 \cdot A_{lim}$ . The describing function based on [5] is given by

$$N(A,f) = \begin{cases} \frac{2}{3 \cdot A} \cdot \left( \tilde{m}_{PB} \left( A \right) + \tilde{m}_{PB} \left( \frac{A}{2} \right) \right) & \text{for } A > A_{lim} \\ A_1 - \frac{3}{4} \cdot A_3 \cdot A^2 & \text{for } others. \end{cases}$$

Figure 2.1. Graph of function  $\tilde{m}_{PB}$ .

Thus, the baseband characteristic can easily be expressed using the procedure introduced above  $(N(A, f) \in \mathbb{R})$

$$\tilde{m}_{BB}: X_{BB}(f) \to X_{BB}(f)$$

with  $(I(t), Q(t), t) \mapsto (N(A, f) \cdot I(t), N(A, f) \cdot Q(t) f)$

where  $A(t) = \sqrt{I(t)^2 + Q(t)^2}$ . This approach seems to be more convenient than only clamping the output amplitude for higher input amplitudes (cf. e.g. [3])  $\square$

It should be considered that using this approach baseband models for several functions as quantizers, general piecewise-linear nonlinearities, limiters, exponential saturation, algebraic saturation, ideal hysteresis functions, and others can be established in a very simple way. This approach also offers the opportunity to start in some of these cases with table-look up descriptions (see also [8]).

#### **Frequency Shifting**

Looking at equation (2.3) it should be mentioned that also X(0) and  $X(n \cdot f)$  (with  $n=2,3,\check{E}$ ) are possible ranges of a baseband map. This way down- or upconversion of the carrier frequency between the system's parts can be handled.

#### Example 2

In the case of a multiplier two alternatives exist. The passband map is described by

$$\bar{m}_{PB}: X_{PB}(f) \times X_{PB}(f) \to X_{PB}(0) \cup X_{PB}(2 \cdot f)$$

with

$$(A_{1}(t) \cdot \cos(\omega t + \varphi_{1}(t)), A_{2}(t) \cdot \cos(\omega t + \varphi_{2}(t)))$$

$$\mapsto \frac{1}{2} \cdot A_{1}(t) \cdot A_{2}(t) \cdot (\cos(\varphi_{1}(t) - \varphi_{2}(t)) + \cos(2\omega t + \varphi_{1}(t) + \varphi_{2}(t)))$$

and  $\omega=2\pi f$ . Thus, the down-conversion baseband characteristic is

$$ar{m}_{BB}: X_{BB}(f) imes X_{BB}(f)

ightarrow X_{BB}(0) ext{ with}$$

$$\left( \left( I_1, Q_1, f \right), \left( I_2, Q_2, f \right) \right) \mapsto \left( \frac{1}{2} \left( I_1 \cdot I_2 + Q_1 \cdot Q_2 \right), 0, 0 \right) \square$$

Baseband modeling can be applied in an easy way if the carrier frequencies of the operands of the baseband characteristics are equal. To shift a representation with carrier frequency  $f_1$  to a representation with carrier frequency  $f_2$  the following

equation for the passband representation should be considered (compare (2.2))

$$Re\left(\left(I\left(t\right)+j\cdot Q\left(t\right)\right)e^{j\omega_{1}t}\right) = Re\left(\left(I\left(t\right)+j\cdot Q\left(t\right)\right)\cdot e^{j\cdot(\omega_{1}-\omega_{2})\cdot t}\cdot e^{j\omega_{2}t}\right) \tag{2.5}$$

Based on (2.5) a shift map for the baseband representation can be defined

$$shift_{BB}: X_{BB}(f_1) \to X_{BB}(f_2)$$

with

$$(I(t), Q(t), t) \mapsto (I(t) \cdot \cos \psi(t) - Q(t) \cdot \sin \psi(t), I(t) \cdot \sin \psi(t) + Q(t) \cdot \cos \psi(t), f_2)$$

and

$$\psi(t) = (\omega_1 - \omega_2) \cdot t \text{ or }$$

$$\psi(t) = (\omega_1 - \omega_2) \cdot t \text{ mod } 2\pi$$

(2.6)

This map should only be applied in baseband modeling for small  $\frac{(\omega_1 - \omega_2)}{\omega_1}$  (see also [7]). Shifting can be interpreted as a map with the describing function  $N(A,f) = \cos \psi(t) + j \cdot \sin \psi(t)$ .

#### **Differentiation**

It is evident that the time domain differential operator  $D_{PB}$  in the passband is given by

$$D_{PB}: X_{PB}(f) \to X_{PB}(f)$$

with

$$I(t) \cdot \cos(\omega t) - Q(t) \cdot \sin(\omega t) \mapsto$$

$$(I'(t) - \omega \cdot Q(t)) \cos(\omega t) - (Q'(t) + \omega \cdot I(t)) \sin(\omega t)$$

(2.7)

where I'(t) and Q'(t) are the time derivatives of I(t) and Q(t) resp. ( $\omega=2\pi f$ ). Thus, the associated differential operator  $D_{BB}$  in the baseband is

$$D_{BB}: X_{BB}(f) \to X_{BB}(f)$$

with

$$(I(t), Q(t), f) \mapsto ((I'(t) - \omega \cdot Q(t)), (Q'(t) + \omega \cdot I(t)), f)$$

(2.8)

If only the steady state is of interest, the time derivatives I'(t) and Q'(t) can be assumed to be 0. In this case,  $D_{BB}$  is characterized by the describing function  $n(A,f)=j\cdot\omega$ . (2.8) is used in [10] to derive baseband descriptions of basic elements as capacitances and inductances. The function can also be used to express general linear transfer functionality in the baseband as will be shown in the following example.

#### Example 3

A Laplace transfer function is given by

$$H(s) = \frac{b_0 + b_1 \cdot s + \dots \cdot b_k \cdot s^k}{a_0 + a_1 \cdot s + \dots \cdot a_n \cdot s^n} = \frac{Y(s)}{U(s)} \qquad (k < n, a_n \neq 0)$$

where s is the Laplace operator. It is well known that a system of ordinary differential equations represents the same behavior in the time domain (see, e.g. [4]). This system of equations describes the behavior using the passband approach

$$x'(t) = A \cdot x(t) + B \cdot u(t)$$

$$y(t) = C \cdot x(t)$$

(2.9)

with

$$x(t) = (x_0(t), x_1(t), \dots x_{n-2}(t), x_{n-1}(t))^T \in \mathbb{R}^n$$

$$A = \begin{pmatrix} 0 & 1 & 0 & \cdots & 0 \\ 0 & 0 & 1 & \cdots & 0 \\ \vdots & & \ddots & \vdots & \vdots \\ 0 & 0 & 0 & \cdots & 1 \\ -\frac{a_0}{a_n} & -\frac{a_1}{a_n} & -\frac{a_2}{a_n} & \cdots & -\frac{a_{n-1}}{a_n} \end{pmatrix}, \quad B = \begin{pmatrix} 0 \\ 0 \\ \vdots \\ 1 \end{pmatrix}$$

$$C = (b_0, b_1, \dots, b_k, 0, \dots, 0)$$

Considering (2.8), the equivalent baseband description can easily be derived. The structure of the system of equations is given by

$$\begin{pmatrix} x_I'(t) \\ x_Q'(t) \end{pmatrix} = \begin{pmatrix} A & \omega \cdot E \\ -\omega \cdot E & A \end{pmatrix} \cdot \begin{pmatrix} x_I(t) \\ x_Q(t) \end{pmatrix} + \begin{pmatrix} B \cdot u_I(t) \\ B \cdot u_Q(t) \end{pmatrix}$$

(2.10)

$$\begin{pmatrix} y_I(t) \\ y_Q(t) \end{pmatrix} = \begin{pmatrix} C & 0 \\ 0 & C \end{pmatrix} \cdot \begin{pmatrix} x_I(t) \\ x_Q(t) \end{pmatrix}$$

(2.11)

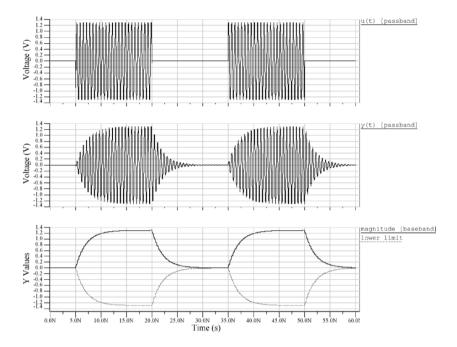

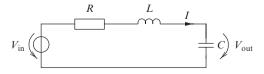

Figure 2.2 shows a bit stream modulated by a 1.575 GHz sinusoidal waveform that is filtered by a bandpass. The magnitude of the output baseband waveform represents the envelope of the passband output waveform as expected.

The main consequences of the considerations in this section is that the baseband representation of a waveform should combine I- and Q-components and the carrier frequency. It seems that it is not necessary to save the phase as proposed in [7]. In case of different carrier frequencies, the operators used in baseband descriptions must define how to handle shifting of the carrier frequency. Last but not least, it should be mentioned that the strong application of the results from the describing function theory simplifies baseband modeling.

Figure 2.2. Input u(t), passband output y(t), and baseband waveform.

#### 3. Baseband Modeling Using VHDL-AMS

The connection point in the baseband description should carry the information about in-phase, quadrature component, and carrier frequency. To handle this, nature BB\_NATURE\_VECTOR is declared as follows:

```

nature BB_NATURE is

REAL through

BB_RER reference;

nature BB_NATURE_VECTOR is

array (NATURAL range <>)

of BB_NATURE;

```

A multidimensional connection point T in a baseband model can then be declared by

```

terminal T : BB_NATURE_VECTOR (1 to 2);

signal F : REAL;

```

When the dependency of transfer characteristics with respect to the carrier frequency shall is analyzed, a quantity port instead of the signal port should be

| Passband                                               | Baseband                                                                 |

|--------------------------------------------------------|--------------------------------------------------------------------------|

| $x: \mathbb{R}^+ + \to \mathbb{R} \text{ (see (2.1))}$ | $X = I + j \cdot Q$ represents $x$                                       |

| $x_1 + x_2$                                            | $X_1 + X_2$                                                              |

| $x_1 - x_2$                                            | $X_1 - X_2$                                                              |

| $h\left(x,\frac{dx}{dt}\right)$                        | $N(A,f)\cdot X$                                                          |

|                                                        | where $N: \mathbb{R} \times \mathbb{R} \to \mathbb{C}$ is the describing |

|                                                        | function associated with $h$ (see ([5])                                  |

Table 2.1. Operators for passband and baseband descriptions.

used. Furthermore, we assume that the constitutive relations of the branches in the passband description can be expressed in the following manner

$$q(i, v, s)$$

with  $q: \mathbb{R}^n \times \mathbb{R}^m \times \mathbb{R}^p \to \mathbb{R}$  (2.12)

where i, v, and s are vectors that combine branch voltages and currents and free quantities. It should be possible to express g using the operators given in Table 2.1. The same carrier frequency is used for all operands.

To assign a baseband model to a passband model the following main steps have to be carried out:

- Replace ELECTRICAL terminals by connection points as described by the code example for the multidimensional connection point T. If a terminal is connected to a voltage or current source branch the signal port is of mode out.

- Instead of real scalar free quantities in the passband description twodimensional real vectors that carry the in-phase and quadrature component are declared.

- The passband constitutive relations (2.12) should be transformed to baseband relations using Table 2.1. Arguments are mapped to complex numbers. The baseband operations are carried out in the complex area.

- If necessary a frequency shifting is carried out in the model (see equation (2.6)).

- 'DOT attributes can be replaced considering (2.7) and (2.8).

Auxiliary functions and constants that support the conversion between different types and representations can be summarized as well as the baseband nature descriptions in an additional package.

#### Example 4

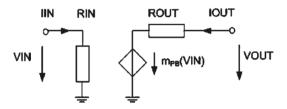

The main part of the passband model of a low noise amplifier (see Fig. 2.3) is given by

The main parts of the associated baseband model are

```

entity LNA is

architecture BASIC of LNA is

generic (

A1, A3, RIN, ROUT : REAL);

function B_OUT(

:BB_NATURE_VECTOR'THROUGH;

terminal N1:BB_NATURE_VECTOR(1 to 2);

:BB_NATURE_VECTOR'ACROSS:

signal F1:REAL;

VCTRL : BB NATURE VECTOR, ACROSS)

terminal N2:BB_NATURE_VECTOR(1 to 2);

return REAL_VECTOR is

signal F2:out REAL);

variable RESULT : COMPLEX;

end entity LNA;

begin

RESULT.

:= CMPLX(V) - ROUT*CMPLX(I)-

DF(ABS(VCTRL))*CMPLX(VCTRL);

return (RESULT.RE, RESULT.IM);

end function B_OUT;

quantity VIN across IIN through N1;

quantity VOUT across IOUT through N2;

begin

ZERO == B_IN(IIN, VIN);

ZERO == B_OUT(IOUT, VOUT, VIN);

F2 <= F1:

end architecture BASIC;

```

ZERO is a constant (0.0, 0.0) of type REAL\_VECTOR (1 to 2). The type COMPLEX is declared in the package MATH\_COMPLEX of the IEEE library. In this package, overloaded functions for + and - in the complex area and multiplication with a real constant are also declared. DF is the complex describing function associated with N(A,f) (see example 1). ABS and CMPLX are overloaded

Figure 2.3. Structure of a LNA model.

Figure 2.4. Analog PLL.

functions of complex maps. The passband model and the baseband model are compiled into different resource libraries. The structural descriptions that use these models have to be modified with respect to the different connection points.

## 4. Further Illustrative Examples

### **Analog PLL**

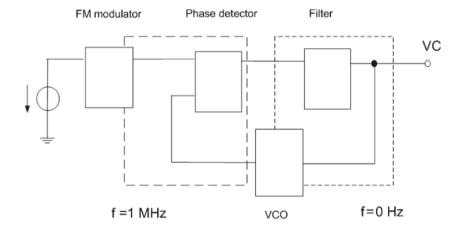

The FM modulator (see Fig. 2.4) is controlled by an electrical voltage source. The carrier frequency of the FM signal is 1 MHz. This is also the center frequency of the VCO. The phase detector is a multiplier that realizes a down-conversion to  $f=0\,\text{Hz}$ .

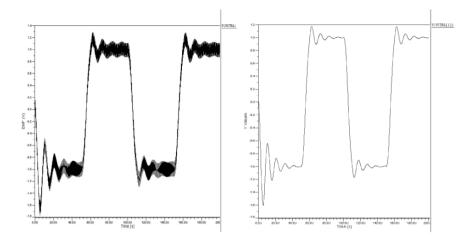

Figure 2.5 shows the demodulated waveform VC using passband and baseband models. The example demonstrates the usage of different carrier frequencies in a baseband description.

Figure 2.5. Voltages VC of passband and baseband model.

#### **Exited Duffing Oscillator**

An excited Duffing oscillator is described by

$$\frac{d^2x}{dt^2} + 2\gamma \cdot \frac{dx}{dt} + \omega_0^2 \cdot x + \beta \cdot x = k \cdot \cos(\omega t)$$

(2.13)

Then, the associated baseband description is

$$DF_{DUFF}\left(\sqrt{I^2+Q^2},\omega\right)\cdot\left(I+j\cdot Q\right)=k \tag{2.14}$$

with

$$DF_{DUFF}(A,\omega)=-\omega^2+j\cdot 2\gamma\omega+\omega_0^2+\frac{3}{4}\cdot A^2$$

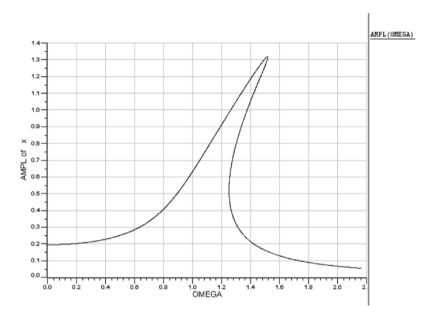

It is known that for some  $\omega$  more than one solution (I,Q) of (2.14) can be determined [2]. That means, there may exist multiple steady state solutions of (2.13). Combining (2.13) with a curve tracing algorithm these characteristics can be determined [11, 6]. Using the describing function, the basic equation (2.14) to determine the frequency response can easily be established. Figure 2.6 shows the magnitude for  $\gamma=0.05, \omega_0^2=1, \beta=1, k=0.2$ . In this example the carrier frequency is not fixed.

## 5. Summary

The verification of front ends for digital communication requires efficient modeling and simulation methods. In order to be able to compare different system architectures a high execution speed of the simulation is required. One possibility to reduce simulation time is a higher level of abstraction of the analog models. Baseband models can be used for this purpose. Other approaches are summarized in [9, 12].

Figure 2.6. Magnitude of Duffing oscillator.

Baseband models are a low-pass waveform representation of passband waveforms. The passband waveforms are characterized by a narrow frequency spectrum around a carrier frequency. With this baseband representation, in-band distortions for nonlinear blocks can be investigated, for instance.

This chapter formally defines a relation between passband and equivalent baseband models. Thus, it formally describes how to write consistent passband and baseband models. This approach can easily be implemented using behavioral description languages. It is shown how the approach works using VHDL-AMS. Some implementation details were discussed. The approach can be used with other languages and description methods as for instance Verilog-AMS or SystemC-AMS in a similar way.

The main passband functionality can be expressed using linear transfer functions and static nonlinearities. There exists a simple relation between linear transfer functions in the passband and baseband representations. Using describing functions for baseband modeling helps to establish consistent baseband and passband descriptions of the nonlinear parts. This approach makes it possible to access the former results from the describing function theory. The idea is formally described as Modeling procedure in Section 2. Example 1 shows how it works.

A special waveform representation that also considers the frequency makes it possible to switch the carrier frequency between different parts of a system. The

carrier frequency is usually constant in a part of a system. Thus in VHDL-AMS, it is represented by a time-discrete signal.

#### References

- [1] IEEE Standard VHDL Analog and Mixed-Signal Extensions. IEEE Std 1076.1-1999. Design Automation Standards Committee of the IEEE Computer Society, March 18, 1999.

- [2] Brandt, S. and Dahmen, H.D. Mechanik. Berlin: Springer, 1996.

- [3] Chen, J.E. Modeling RF Systems. March 6, 2005. Available: http://www.designers-guide.org/Modeling/

- [4] Geering, H.P. Regelungstechnik. Berlin: Springer, 2001.

- [5] Gelb, A. and Vander Velde, W.E. *Multiple-input Describing Functions and Nonlinear System Design*. New York: McGraw-Hill, 1968. Available: http://en.wikipedia.org/wiki/Describing\_function

- [6] Haase, J., Pönisch, G. and Uhle, M. Multiple DC solution determination using VHDL-AMS. Proc. BMAS 2003, October 2003, pp. 107–112. Available: http://www.bmas-conf.org/2003

- [7] Joeres, S. and Heinen, S. Mixed-mode and mixed-domain modelling and verification of radio frequency subsystems for SoC applications. Proc. BMAS 2005, September 2005, pp. 54–59. Available: http://www.bmasconf.org/2005

- [8] Kundert, K. Future directions in mixed-signal behavioral modeling. Keynote BMAS 2002, October 2002. Available: http://www.bmas-conf.org/2002

- [9] Root, D., Wood, J. and Tufillaro, N. New techniques for nonlinear behavioral modeling of microwave/RF ICs from simulation and nonlinear microwave measurement. Proc. DAC 2003. June 2003, pp. 85–90.

- [10] Tuinenga, P.W. Models rush in where simulators fear to tread: extending to the baseband-equivalent method. Proc. BMAS 2002, October 2002, pp. 31–40. Available: http://www.bmas-conf.org/2002

- [11] Ushida, A., Yamagami, Y. and Nishio, Y. Frequency response of nonlinear networks using curve tracing algorithm. Proc. ISCAS 2002, pp. 641–644.

- [12] Wambacq, P., Vandersteen, G., Rolain, Y., Dobrovolny, P., Goffioul, M and Donnay, S. Dataflow simulation of mixed-signal communication circuits using a local multirate, multicarrier signal representation. IEEE Trans. Circ. Syst I vol. 49, pp. 1554–1562, November 2003.

## Chapter 3

# VERIFICATION-ORIENTED BEHAVIORAL MODELING OF NONLINEAR ANALOG PARTS OF MIXED-SIGNAL CIRCUITS

Martin Freibothe<sup>1</sup>, Jens Döge<sup>1</sup>, Torsten Coym<sup>1</sup>, Stefan Ludwig<sup>1</sup>, Bernd Straube<sup>1</sup>, and Ernst Kock<sup>2</sup>

#### Abstract

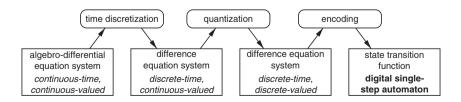

In this work, an approach to the "verification-oriented" modeling of the analog parts' behavior of mixed-signal circuits is presented. Starting from a continuous-time, continuous-valued behavioral representation of an analog part in terms of a differential-algebraic equation system, a discrete-time, discrete-valued behavioral model is derived. This kind of model both captures dynamic aspects of the analog behavior and can be implemented using the synthesizable subset of a hardware description language like VHDL. With the help of the proposed approach, the continuous-time, continuous-valued analog parts' behavioral descriptions can be replaced by digital behavioral models leading to a verification-oriented model of the underlying mixed-signal circuit. The resulting model can be formally verified using established methods and tools from formal digital verification.

**Keywords** Behavioral modeling, mixed-signal verification, semiformal methods

<sup>&</sup>lt;sup>1</sup> Fraunhofer-Institut für Integrierte Schaltungen IIS

Branch Lab Design Automation

Zeunerstr. 38, 01069 Dresden

{martin.freibothe,jens.doege,torsten.coym,stefan.ludwig,bernd.straube}@eas.iis.fraunhofer.de

<sup>&</sup>lt;sup>2</sup> Infineon Technologies AG Neubiberg ernst.kock@infineon.com

#### 1. Introduction

In today's circuit designs, the integration of analog parts on system-on-chips (SoCs) and ASICs is common practice. Usually in such designs the analog parts comprise a comparatively small fraction of the overall chip area. On the contrary, a large part of the development time of a mixed-signal circuit is spent on the analog parts.

Using well-established formal verification techniques, digital circuit designs can be formally verified in order to find design errors. In contrast to simulation-based verification, these techniques reach a 100% coverage of the functionality of a circuit design. Currently there are no tools allowing for the formal verification of analog and mixed-signal circuits. In today's verification flows the analog and digital parts are verified separately by simulation and formal verification techniques, respectively. The verification of the overall behavior of a mixed-signal circuit and, hence, the connection of the analog and digital parts is then carried out based on simulation. All simulation-based verification methods have the disadvantage of requiring a testbench and simulation stimuli. Despite the high manual effort to provide both of them, due to the complexity of today's designs only a relatively low coverage of a circuit's functionality can be achieved.

To simplify matters, those parts of a mixed-signal circuit that are represented by continuous-time, continuous-valued behavioral models are in the following referred to as 'analog components'. An approach to the verification-oriented modeling of analog components is presented. Starting from a behavioral description of an analog component in terms of nonlinear differential-algebraic equations a digital model is derived by discretizing the time and quantizing the continuous values. Based on the resulting digital behavioral model some properties of practical relevance can be proved using commercially available *bounded model checking* tools. The presented work extends the class of mixed-signal circuits that can be verified with the help of formal methods that are commonly used for the verification of digital circuits.

The remainder of the paper is organized as follows: In Section 2 related work is reviewed. Section 3 describes the proposed modeling approach and the application of formal verification techniques. An example of the application of the proposed flow is given in Section 4 and some concluding remarks are presented in Section 5.

#### 2. State of the Art

Simple mixed-signal circuits can be represented by hybrid automata [1, 10]. The verification of a circuit design is carried out by performing a reachability analysis over the state-space of the corresponding hybrid automaton. Even under strong restrictions, such as piecewise constant derivatives of the variables,

the reachability problem remains undecidable for this class of automata, for the state-space is infinite in general [11]. Recent approaches to the verification of hybrid automata utilize different techniques to approximate the reachable state sets. Standard model checking algorithms are then applied to these finite-state approximations [8, 9]. The approach proposed in [3] suggests to perform a reachability analysis on a certain class of hybrid systems that can be represented as mixed logical dynamical or piecewise affine systems to get a piecewise linear approximation of the exact solution. Drawbacks of these approaches are that they introduce an approximation error, are not sound [9], or their performance strongly depends on the shape of the reachable sets of states [3].

An approach to the verification of linear analog circuits is presented in [2]. The circuit's specification is given in terms of its transfer function. Based on the state equations, the transfer function of the implementation of the circuit is derived. Both transfer functions are transformed into the discrete-time domain using Z-transform. The continuous values denoting voltages and currents are quantized. The resulting discrete-time, discrete-valued transfer functions of both the specification and the implementation can be represented by finite deterministic automata, respectively. The verification is then carried out by an equivalence-check, an approach to property-checking is not mentioned in this work. The proposed verification flow is restricted to linear analog circuits. The problem of arithmetic overflows that might occur during verification is mentioned; however, overflows are not recognized or treated by this approach.

In [12] an approach to the semiformal verification of the static behavior of mixed-signal circuits is presented. The proposed approach is based on SAT-based property-checking. Starting point of the described verification flow is the static behavioral description of a mixed-signal circuit in VHDL. In such a circuit description, VHDL's floating point type *real* is used to characterize the analog behavior. Given such a mixed-signal circuit description, a verification-oriented model is derived for which SAT-based property-checking is carried out. In the verification-oriented model the floating point type *real* used to describe analog behavior is approximated by integer numbers of a finite interval. Such a model can be represented by a finite Mealy automaton and thus be verified using well-established formal verification methods. Possible overflows due to arithmetic operations are recognized during the verification process and cause the corresponding property to fail. The quantization error that is introduced when the verification-oriented model is derived has to be considered in the properties to be verified.

A similar approach to the verification of the static behavior of mixed-signal circuits is proposed in [6]. In this approach the rational numbers  $\mathbb Q$  are used to represent analog values. The mixed-signal circuit is given as an infinite automaton that is described in a simple XML. A validity checker that allows the usage of arithmetic expressions in the formulae is utilized to prove properties

based on the automaton. The accuracy of the internal representation of the rational numbers is only limited by the amount of memory that is available so that arithmetic overflows do not occur in practice.