# **Modern Circuit Placement** Best Practices and Results

#### Series on Integrated Circuits and Systems

| Series | Editor:  |

|--------|----------|

| Derres | L'ancor. |

Anantha Chandrakasan Massachusetts Institute of Technology Cambridge, Massachusetts

Modern Circuit Placement: Best Practices and Results Gi-Joon Nam and Jason Cong ISBN 978-0-387-36837-5

CMOS Biotechnology Hakho Lee, Donhee Ham and Robert M. Westervelt ISBN 978-0-387-36836-8

SAT-Based Scalable Formal Verification Solutions Malay Ganai and Aarti Gupta ISBN 978-0-387-69166-4, 2007

Ultra-Low Voltage Nano-Scale Memories Kiyoo Itoh, Masashi Horiguchi and Hitoshi Tanaka ISBN 978-0-387-33398-4, 2007

Routing Congestion in VLSI Circuits: Estimation and Optimization Prashant Saxena, Rupesh S. Shelar, Sachin Sapatnekar ISBN 978-0-387-30037-5, 2007

Ultra-Low Power Wireless Technologies for Sensor Networks Brian Otis and Jan Rabaey ISBN 978-0-387-30930-9, 2007

Sub-Threshold Design for Ultra Low-Power Systems Alice Wang, Benton H. Calhoun and Anantha Chandrakasan ISBN 978-0-387-33515-5, 2006

High Performance Energy Efficient Microprocessor Design Vojin Oklibdzija and Ram Krishnamurthy (Eds.) ISBN 978-0-387-28594-8, 2006

Abstraction Refinement for Large Scale Model Checking Chao Wang, Gary D. Hachtel, and Fabio Somenzi ISBN 978-0-387-28594-2, 2006

A Practical Introduction to PSL Cindy Eisner and Dana Fisman ISBN 978-0-387-35313-5, 2006

Thermal and Power Management of Integrated Systems Arman Vassighi and Manoj Sachdev ISBN 978-0-387-25762-4, 2006

Leakage in Nanometer CMOS Technologies Siva G. Narendra and Anantha Chandrakasan ISBN 978-0-387-25737-2, 2005

Statistical Analysis and Optimization for VLSI: Timing and Power Ashish Srivastava, Dennis Sylvester, and David Blaauw ISBN 978-0-387-26049-9, 2005 Gi-Joon Nam Jason Cong

# Modern Circuit Placement Best Practices and Results

*Editors:* Gi-Joon Nam IBM Austin Research Laboratory Austin, TX USA

Jason Cong University of California, Los Angeles Los Angeles, CA USA

Series Editor: Anantha Chandrakasan Department of Electrical Engineering and Computer Science Massachusetts Institute of Technology Cambridge, MA 02139 USA

Library of Congress Control Number: 2007926182

ISBN 978-0-387-36837-5 e-ISBN 978-0-387-68739-1

Printed on acid-free paper.

© 2007 Springer Science+Business Media, LLC

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now know or hereafter developed is forbidden. The use in this publication of trade names, trademarks, service marks and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

987654321

springer.com

Dedicated to VLSI circuit placement researchers and practitioners whose creative and persistent efforts made it possible for us to handle the exponential increase of circuit placement complexity in the past four decades. -Gi-Joon & Jason

# Contents

| Foreword | <br> | •••• | <br> | <br>xv   |

|----------|------|------|------|----------|

| Preface  | <br> | •••• | <br> | <br>xvii |

### Part I Benchmarks

| 1 | ISP  | D 2005/  | 2006 Placement Benchmarks                         | 3  |

|---|------|----------|---------------------------------------------------|----|

|   | 1.1  |          | uction                                            | 3  |

|   | 1.2  | ISPD 2   | 2005 Placement Contest and Benchmark              | 4  |

|   | 1.3  | ISPD 2   | 2006 Placement Contest and Benchmark              | 7  |

|   | 1.4  | ISPD ]   | Placement Contest Results                         | 8  |

|   | Refe | erences  |                                                   | 11 |

| 2 | Loc  | ality an | d Utilization in Placement Suboptimality          | 13 |

|   | 2.1  | Introd   | uction                                            | 13 |

|   | 2.2  | Peko-l   | MC Benchmark Construction                         | 15 |

|   |      | 2.2.1    | Monotone Chains                                   | 15 |

|   |      | 2.2.2    | The Peko-MC Algorithm                             | 16 |

|   | 2.3  | Peko-l   | MS Benchmark Construction                         | 17 |

|   | 2.4  | Experi   | ments                                             | 22 |

|   |      | 2.4.1    | Nonlocal Nets (Peko-MC)                           | 23 |

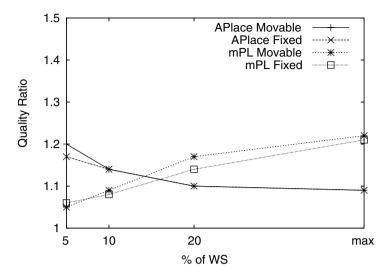

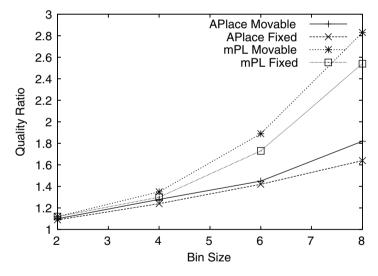

|   |      | 2.4.2    | Parametrized White Space (Peko-MS)                | 25 |

|   |      | 2.4.3    | Suboptimality Under Both Parametrized White Space |    |

|   |      |          | and Nonlocal Nets                                 | 25 |

|   |      | 2.4.4    | Suboptimality of Detailed Placement               | 27 |

|   |      | 2.4.5    | HPWL Suboptimality Comparison of Leading Academic |    |

|   |      |          | Tools on Peko-MS 2005                             | 29 |

|   |      | 2.4.6    | Suboptimality of Routability-Aware Placement      | 31 |

|   | 2.5  | Conclu   | usions                                            | 34 |

|   | 2.6  |          | wledgments                                        | 35 |

|   |      |          | -                                                 |    |

| References | 35 |

|------------|----|

|------------|----|

## Part II Flat Placement Techniques

| 3 |             |         | nchor Cell-Based Quadratic Placement with Linear    | 20       |

|---|-------------|---------|-----------------------------------------------------|----------|

|   |             |         |                                                     | 39<br>39 |

|   | 3.1<br>3.2  |         | uction                                              |          |

|   | 3.2         |         | ninaries and the Motivation                         | 41<br>41 |

|   |             | 3.2.1   | Quadratic Placement                                 |          |

|   |             | 3.2.2   | Force-Directed Quadratic Placement                  | 42       |

|   | 2.2         | 3.2.3   | The Proposed Approach                               | 44       |

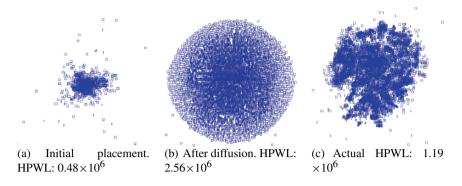

|   | 3.3         |         | l Placement in DPlace                               | 45       |

|   |             | 3.3.1   | Diffusion Preplacement                              | 45       |

|   |             | 3.3.2   | Anchor Cells                                        | 46       |

|   |             | 3.3.3   | Unconstrained Wire Length Minimization              | 48       |

|   |             | 3.3.4   | HPWL Transformation in a Quadratic System           | 50       |

|   |             | 3.3.5   | Fixed Blockages                                     | 51       |

|   |             | 3.3.6   | Wire Length Improvement Heuristics                  | 52       |

|   | 3.4         |         | ization and Detailed Placement                      | 53       |

|   | 3.5         |         | ll Algorithm                                        | 53       |

|   | 3.6         | Exper   | iments                                              | 53       |

|   |             | 3.6.1   | Advantages of our New Formulation                   | 53       |

|   |             | 3.6.2   | ISPD Placement Contest Benchmarks                   | 55       |

|   |             | 3.6.3   | PEKO-MS Benchmarks                                  | 55       |

|   | 3.7         | Concl   | usions                                              | 56       |

|   | Refe        | erences |                                                     | 57       |

| 4 | <b>V</b> no | ftwark  | : A Fast and Robust Quadratic Placer Using an Exact |          |

| 4 |             |         | Model                                               | 59       |

|   | <b>4</b> .1 |         | uction                                              | 59       |

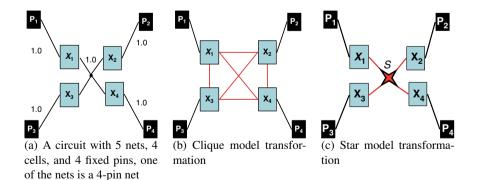

|   | 4.1         |         | Iodel                                               | 62       |

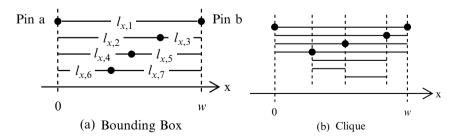

|   | 4.2         | 4.2.1   |                                                     | 63       |

|   |             |         | Clique Net Model                                    |          |

|   |             | 4.2.2   | BoundingBox Net Model.                              | 65       |

|   | 4.2         | 4.2.3   | Advantages of the BoundingBox Net Model             | 66       |

|   | 4.3         | -       | ratic Placement Methodology                         | 67       |

|   |             | 4.3.1   | Additional Forces                                   | 68       |

|   |             | 4.3.2   | Proof of Convergence                                | 71       |

|   | 4.4         |         | mentation Details                                   | 72       |

|   |             | 4.4.1   | Engineering Change Order                            | 72       |

|   |             | 4.4.2   | Quality Control                                     | 74       |

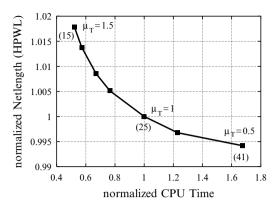

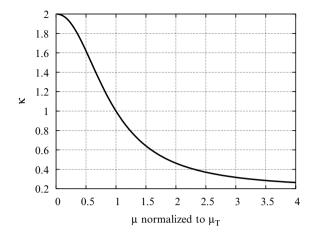

|   |             | 4.4.3   | Spring Constants of the Target Points               | 75       |

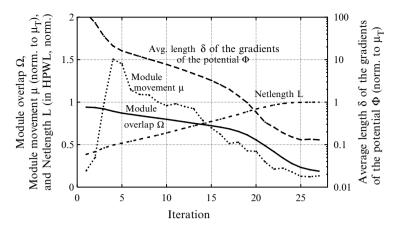

|   |             | 4.4.4   | Convergence Plot                                    | 76       |

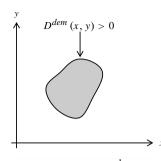

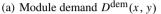

|   |             | 4.4.5   | Control of the Module Density                       | 78       |

|   | 4.5         | Exper   | imental Results                                     | 81       |

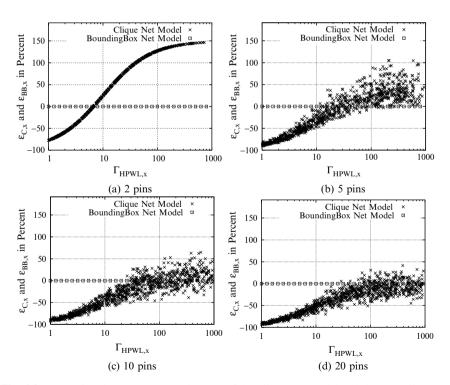

|      | 4.5.1    | Clique and BoundingBox Net Model | 82 |

|------|----------|----------------------------------|----|

|      | 4.5.2    | ISPD 2005 Contest Benchmarks     | 82 |

|      | 4.5.3    | ISPD 2006 Contest Benchmarks     | 83 |

|      | 4.5.4    | PEKO-MS ISPD 2005 Benchmarks     | 85 |

|      | 4.5.5    | PEKO-MS ISPD 2006 Benchmarks     | 88 |

|      | 4.5.6    | Computational Complexity         | 90 |

| 4.6  | Conclu   | 1sion                            | 90 |

| Refe | rences . |                                  | 91 |

|      |          |                                  |    |

## Part III Top-Down Partitioning-Based Techniques

| 5 | Cap   | o: Cong                             | gestion-Driven Placement for Standard-cell and RTL    |     |  |  |  |  |

|---|-------|-------------------------------------|-------------------------------------------------------|-----|--|--|--|--|

|   | Netli | etlists with Incremental Capability |                                                       |     |  |  |  |  |

|   | 5.1   | Introdu                             | uction                                                | 97  |  |  |  |  |

|   | 5.2   | Min-C                               | ut Placement in Capo                                  | 99  |  |  |  |  |

|   |       | 5.2.1                               | Row-Based Placement                                   | 99  |  |  |  |  |

|   |       | 5.2.2                               | Min-Cut Bisection                                     | 99  |  |  |  |  |

|   | 5.3   | Floorp                              | lacement                                              | 100 |  |  |  |  |

|   |       | 5.3.1                               | Empirical Boundary Between Placement                  |     |  |  |  |  |

|   |       |                                     | and Floorplanning                                     | 103 |  |  |  |  |

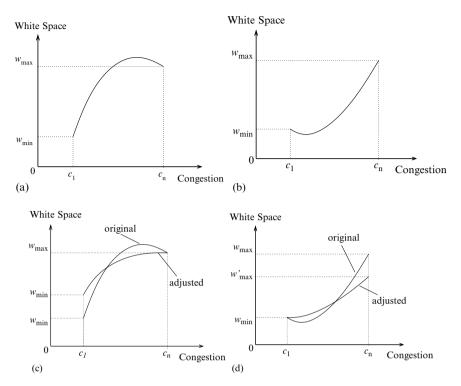

|   | 5.4   | Flexib                              | le Whitespace Allocation                              | 104 |  |  |  |  |

|   |       | 5.4.1                               | Uniform Whitespace                                    | 104 |  |  |  |  |

|   |       | 5.4.2                               | Minimum Local Whitespace                              | 105 |  |  |  |  |

|   |       | 5.4.3                               | Safe Whitespace                                       | 105 |  |  |  |  |

|   | 5.5   | Detail                              | Placement                                             | 107 |  |  |  |  |

|   |       | 5.5.1                               | RowIroning                                            | 107 |  |  |  |  |

|   |       | 5.5.2                               | Optimal Branch-and-Bound Placement                    | 107 |  |  |  |  |

|   |       | 5.5.3                               | Greedy Cell Movement                                  | 108 |  |  |  |  |

|   | 5.6   | Placen                              | nent for Routability                                  |     |  |  |  |  |

|   |       | 5.6.1                               | Optimizing Steiner Wire length                        |     |  |  |  |  |

|   |       | 5.6.2                               | Congestion-Based Cutline Shifting                     |     |  |  |  |  |

|   | 5.7   | Improv                              | ved RTL Placement                                     | 113 |  |  |  |  |

|   |       | 5.7.1                               | Selective Floorplanning for Multimillion Gate Designs |     |  |  |  |  |

|   |       | 5.7.2                               | Temporary Macro Deflation                             | 116 |  |  |  |  |

|   |       | 5.7.3                               | Whitespace Reallocation Using Linear Programming      |     |  |  |  |  |

|   |       |                                     | and Min-Cost Max-Flow                                 | 117 |  |  |  |  |

|   | 5.8   | Increm                              | nental Placement                                      | 118 |  |  |  |  |

|   |       | 5.8.1                               | General Framework                                     | 118 |  |  |  |  |

|   |       | 5.8.2                               | Fast Cutline Selection                                | 119 |  |  |  |  |

|   |       | 5.8.3                               | Scalability                                           |     |  |  |  |  |

|   |       | 5.8.4                               | Handling Macros and Obstacles                         |     |  |  |  |  |

|   |       | 5.8.5                               | Relaxing Overfullness Constraints                     |     |  |  |  |  |

|   |       | 5.8.6                               | Satisfying Density Constraints                        |     |  |  |  |  |

|   | 5.9   | Memo                                | ry Profile                                            | 124 |  |  |  |  |

|   | 5.10 | Perfor   | mance on Publicly Available Benchmarks    | 125 |

|---|------|----------|-------------------------------------------|-----|

|   |      | 5.10.1   | Routing Benchmarks                        | 125 |

|   |      | 5.10.2   | Mixed-Size Benchmarks                     | 126 |

|   |      | 5.10.3   | ISPD Contest Benchmarks                   | 129 |

|   | 5.11 | Conclu   | usions                                    | 131 |

|   | Refe | erences. |                                           | 131 |

| 6 | Con  | gestion  | Minimization in Modern Placement Circuits | 135 |

|   | 6.1  | -        | uction                                    | 135 |

|   | 6.2  | Overvi   | iew of Dragon                             | 136 |

|   |      | 6.2.1    |                                           |     |

|   | 6.3  | Mixed    | -Size Placement                           | 138 |

|   |      | 6.3.1    | Macro-Aware Partitioning                  | 139 |

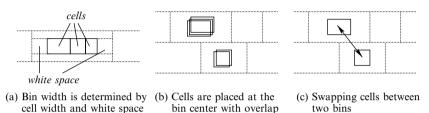

|   |      | 6.3.2    | Bin-Based Simulated Annealing             |     |

|   |      | 6.3.3    | Legalization                              | 142 |

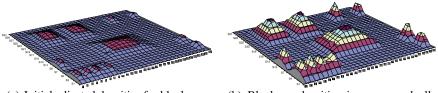

|   | 6.4  | Conge    | stion Estimation                          | 142 |

|   |      | 6.4.1    | Rent's Rule                               | 143 |

|   |      | 6.4.2    | Peak Congestion Analysis                  | 143 |

|   |      | 6.4.3    | Regional Congestion Estimation            | 146 |

|   | 6.5  | Conge    | stion Removal                             | 153 |

|   |      | 6.5.1    | Problem Formulation                       | 154 |

|   |      | 6.5.2    | Row White Space Allocation                | 155 |

|   |      | 6.5.3    | Grid White Space Allocation               | 157 |

|   |      | 6.5.4    | Placement Flow                            | 157 |

|   |      | 6.5.5    | Post-Allocation Optimization              | 157 |

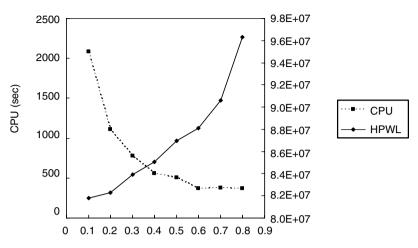

|   | 6.6  | Target   | Utilization Control                       | 158 |

|   | 6.7  | Experi   | mental Result                             | 160 |

|   | Refe | rences . |                                           | 162 |

|   |      |          |                                           |     |

## Part IV Multilevel Placement Techniques

| 7 | APla | ace: A High Quality, Large-Scale Analytical Placer               |

|---|------|------------------------------------------------------------------|

|   | 7.1  | Introduction                                                     |

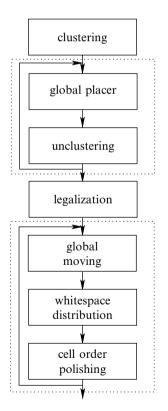

|   | 7.2  | Clustering and Unclustering 169                                  |

|   | 7.3  | Global Placement 171                                             |

|   |      | 7.3.1 Constrained Minimization Formulation 171                   |

|   |      | 7.3.2 Quadratic Penalty Method and Conjugate Gradient Solver 174 |

|   |      | 7.3.3 Multi-Level Algorithm 174                                  |

|   | 7.4  | Legalization and Detailed Placement 177                          |

|   |      | 7.4.1 Global Moving 177                                          |

|   |      | 7.4.2 Whitespace Distribution 178                                |

|   |      | 7.4.3 Cell Order Polishing 179                                   |

|   | 7.5  | ISPD'06 Contest and APlace3.0 181                                |

|   |      |                                                                  |

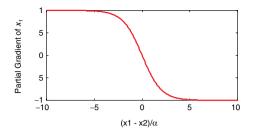

|   |      | 7.5.1    | Exploring Alternative Wirelength Functions           | 181 |

|---|------|----------|------------------------------------------------------|-----|

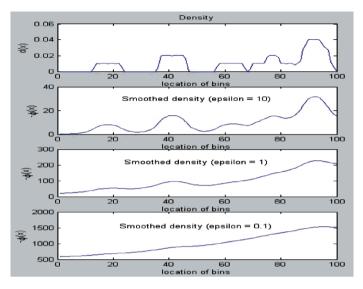

|   |      | 7.5.2    | Exploring Alternative Density Functions              | 182 |

|   | 7.6  | Experi   | mental Results                                       | 183 |

|   | Refe |          |                                                      |     |

|   |      |          |                                                      |     |

| 8 |      |          | An Efficient Multilevel Force-Directed Placement     |     |

|   | -    |          |                                                      |     |

|   | 8.1  |          | action                                               |     |

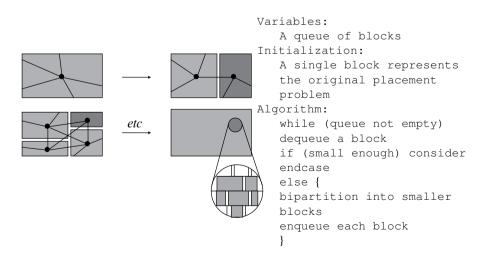

|   | 8.2  |          | ew of the Algorithm                                  |     |

|   | 8.3  |          | atic Placement Methodology                           |     |

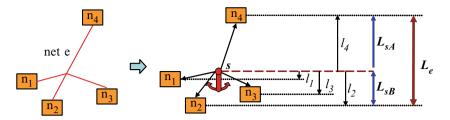

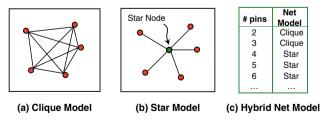

|   | 8.4  | •        | l Net Model                                          |     |

|   |      | 8.4.1    | 1                                                    |     |

|   |      | 8.4.2    | Hybrid Net Model                                     |     |

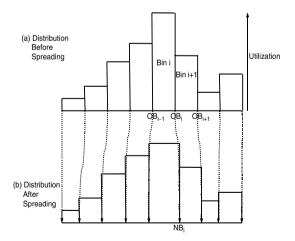

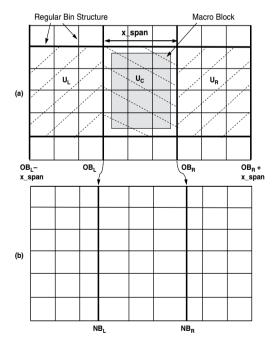

|   | 8.5  |          | nifting                                              |     |

|   |      | 8.5.1    | Shifting of Standard-cells                           |     |

|   |      | 8.5.2    | Shifting of Macro-Blocks                             |     |

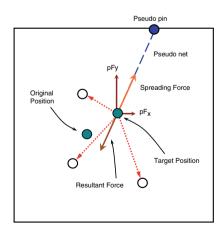

|   |      | 8.5.3    | Addition of Spreading Forces                         |     |

|   | 8.6  |          | ve Local Refinement                                  |     |

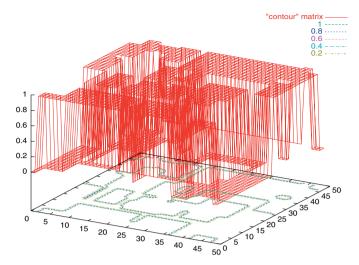

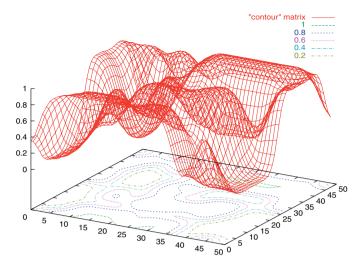

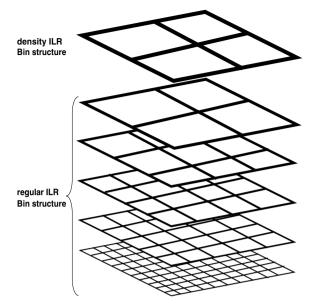

|   |      | 8.6.1    | Bin Structure for <i>r-ILR</i>                       | 206 |

|   |      | 8.6.2    | ILR for Simultaneous Spreading and Wirelength        |     |

|   |      |          | Minimization                                         |     |

|   |      | 8.6.3    | ILR for Handling Placement Blockages                 |     |

|   |      | 8.6.4    | ILR for Placement Congestion Control                 |     |

|   | 8.7  |          | ring for Placement                                   |     |

|   |      | 8.7.1    | Two-Level Clustering Scheme                          |     |

|   | 8.8  | -        | zation                                               |     |

|   |      | 8.8.1    | Legalization of Macro-Blocks                         |     |

|   |      | 8.8.2    | Legalization of Standard-Cells                       |     |

|   | 8.9  |          | P: Efficient and Effective Detailed Placement        |     |

|   |      | 8.9.1    | Global Swap                                          |     |

|   |      | 8.9.2    | Vertical Swap                                        |     |

|   |      | 8.9.3    | Local Re-Ordering                                    |     |

|   |      | 8.9.4    | Single-Segment Clustering                            |     |

|   | 8.10 | -        | mental Results and Analysis                          |     |

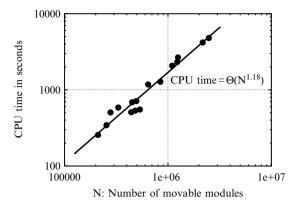

|   |      |          | Runtime Analysis of the Algorithm                    |     |

|   |      |          | ISPD-2005 Placement Contest Benchmarks               |     |

|   |      |          | ISPD-2006 Placement Contest Benchmarks               |     |

|   |      | 0.10.1   | PEKO-MS Benchmarks                                   | 225 |

|   |      |          | isions                                               |     |

|   | Refe | rences . |                                                      | 227 |

| 0 | T2 A | D. M.    | Kilowal Fired Dates & dattion Devel MI CI Discover 4 | 220 |

| 9 |      |          | Itilevel Fixed-Points Addition-Based VLSI Placement  | 229 |

|   | 9.1  |          | action                                               | 229 |

|   | 9.2  | 0        | round                                                |     |

|   | 9.3  | Fixed I  | Points                                               | 251 |

|    |      | 9.3.1 Fixed-Points and Force-Equilibrium State                                                    | 231         |

|----|------|---------------------------------------------------------------------------------------------------|-------------|

|    |      | 9.3.2 Fixed-Points Addition                                                                       |             |

|    | 9.4  | Fixed-Points Addition-Based Placement                                                             | 235         |

|    |      | 9.4.1 Fixed Points vs. Constant Forces                                                            | 235         |

|    |      | 9.4.2 Fixed Points in Global Placement                                                            | 236         |

|    |      | 9.4.3 Detailed Placement                                                                          | 240         |

|    | 9.5  | mFAR: Multilevel Fixed-Point Addition-Based Placement                                             | 240         |

|    | 9.6  | Experimental Results                                                                              | 242         |

|    |      | 9.6.1 ISPD05 Placement Contest Benchmarks                                                         | 242         |

|    |      | 9.6.2 ISPD06 Placement Contest Benchmarks                                                         | 242         |

|    |      | 9.6.3 PEKO 2005                                                                                   | 243         |

|    |      | 9.6.4 PEKO 2006                                                                                   | 243         |

|    | 9.7  | Conclusions                                                                                       | 244         |

|    | Refe | erences                                                                                           | 244         |

| 10 | DI   | C. E. Land M. Hiller J. Mins J. Char. Discourse 4 with Characteria                                |             |

| 10 |      | L6: Enhanced Multilevel Mixed-Size Placement with Congestion<br>trol                              | 247         |

|    |      | Introduction                                                                                      |             |

|    |      | Definitions and Notations                                                                         |             |

|    |      | Problem Formulation                                                                               |             |

|    |      | Multilevel Framework                                                                              |             |

|    | 10.4 | 10.4.1 Coarsening                                                                                 |             |

|    |      | 10.4.2 Relaxation                                                                                 |             |

|    |      | 10.4.3 Interpolation                                                                              |             |

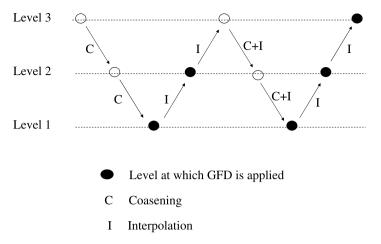

|    |      | 10.4.4 Multilevel Flow                                                                            |             |

|    | 10 5 | Generalized Force-Directed Algorithm                                                              |             |

|    | 10.5 | 10.5.1 Constrained Minimization Problem Formulation                                               |             |

|    |      | 10.5.2 Problem Solver                                                                             |             |

|    |      | 10.5.3 Analysis and Enhancements of the GFD Algorithm                                             |             |

|    | 10.6 | Legalization and Detailed Placement                                                               | 274         |

|    |      | 10.6.1 Macro Legalization                                                                         |             |

|    |      | 10.6.2 Cell Legalization                                                                          |             |

|    |      | 10.6.3 Further Wirelength Reduction                                                               |             |

|    | 10.7 | Numerical Results                                                                                 | 284         |

|    | Refe | erences                                                                                           | 285         |

| 11 | NUTT | Inlass?: An Analytical Disconford and Scale Mined Size Designs                                    | <b>1</b> 00 |

| 11 |      | Jplace3: An Analytical Placer for Large-Scale Mixed-Size Designs           Introduction         2 |             |

|    |      |                                                                                                   | 289         |

|    |      |                                                                                                   | 292         |

|    | 11.5 | *                                                                                                 | 292         |

|    |      |                                                                                                   | 297         |

|    |      | •                                                                                                 | 298         |

|    | 11.4 |                                                                                                   | 303         |

|    |      | 11.4.1 Dynamic Step-Size Control                                                                  |             |

|     | 11.4.2       | Look-Ahead Legalization   | 303 |

|-----|--------------|---------------------------|-----|

|     | 11.4.3       | HPWL and Runtime Analysis | 303 |

|     | 11.4.4       | Wire-Model Comparison     | 306 |

|     | 11.4.5       | PEKO-MS Benchmarks        | 307 |

|     | References . |                           | 308 |

| 12  | Conclusion   | and Challenges            | 311 |

| Ind | ex           |                           | 313 |

## Foreword

I have a very clear memory of the first time I ever read anything about placement algorithms. I was a graduate student, and the research community was crackling with the excitement and challenges of the early days of the "VLSI" revolution. I went to my university's library to track down a copy of the book chapter "Placement Techniques" by Maurice Hanan and Jerome M. Kurtzberg, in Mel Breuer's book on *Design Automation of Digital Systems*. This was an eye-opening experience for a young student. The seminal Hanan-Kurtzberg material was a wonderfully clear review of what was known at the time about placement problems; it was a beautiful mix of geometry, algorithms, heuristics, optimization, and real experiments on real (and by today's standards, really *small*) designs. Reading this paper was a significant "Aha!" moment in my own career in the physical design area.

The intervening decades have dramatically broadened the portfolio of successful placer strategies, beyond the simple iterative improvement and partitioning approaches of those early days. We have more powerful iterative paradigms like annealing; we have vastly improved partitioning technologies; we have large-scale analytical solutions that formulate and solve enormous numerical optimization problems; we have clustering and multi-scale methods; and we have a hierarchy of geometric models, from coarse initial placement to final legalization. In this vastly more complex landscape of challenges and solutions, where does the enterprising student of placement look to figure out what's what in the placement business today?

This book, I hope.

Based on a set of placers that competed in recent contests sponsored by the ACM International Symposium on Physical Design (ISPD), and using the tremendously important sets of common placer benchmarks associated with ISPD, this volume offers an excellent overview of what we know about placement today. We owe a great debt to its editors, Gi-Joon Nam of IBM and Jason Cong of UCLA, for organizing all this material into one accessible and coherent volume. As our problems continue to grow in size, and we layer ever more constraints like timing, power and reliability on these tools, it's clear that people are no less excited about placement problems today than when I first read about the topic as a student.

Rob A. Rutenbar Carnegie Mellon University April 2007

## Preface

Research in placement algorithms for VLSI circuits has enjoyed a renaissance in recent years. Today, there are a number of high quality academic placers that have been developed in universities. The amount of research on this topic clearly reflects the importance of the placement as the single most critical component for achieving timing/design closure in a modern physical synthesis tool. Placement algorithm itself has been researched for more than three decades. Yet, the problem is still very challenging for multiple reasons. First, the exponential increase of the circuit density according to Moore's Law has led to designs with tens of millions of placeable objects today. Although such complex designs are composed hierarchically based on the logic or function hierarchy, multiple studies (e.g. [3]) show that placement based on the logic hierarchy may lead to considerably inferior results. The preferred methodology is to place the entire design flat (with millions or tens of millions of placeable objects) to derive a good physical hierarchy and then use it to guide the subsequent physical synthesis process. Therefore, the modern placers have to handle extremely large problem sizes. Second, today's System-on-Chip (SoC) designs introduce complex constraints, such as routability and timing constraints, as well as the support of mixed size macros, area I/Os, multi-Vt and multi-Vdd islands for power optimization. Moreover, recent work on placement optimality studies ([1,2]) suggest that there exists significant room for improvement even for wire length optimization alone (details will be discussed in Chap. 2). All these reasons stimulated renewed interests in research in circuit placement problems, both in academia and industry, in the past a few years.

To help further stimulate advances in placement research, ISPD (International Symposium on Physical Design [7]) hosted two placement contests using new, large-scale benchmark suites based on real industrial designs ([5,6], see Chap.1 for more detailed discussion). The common goals of the two ISPD placement contests were:

• To provide new modern placement benchmarks to stimulate new development in placement research

- To provide a common basis for quantitative measurements of contemporary placement algorithms, and help the academic community to publicize their placement tools and results

- To provide an educational forum on a variety of state-of-art placement algorithms for future placement researchers

These two placement contests were huge success with participation from a number of academic placers and provided a common platform to evaluate various placement algorithms on the same set of realistic benchmarks. This book is the product of these academic efforts on placement contests and it can be considered as the year 2006 snapshot of state-of-the-art modern placement techniques employed in the field. The book provides in-depth description of the best practices of placement algorithms used in the research community today. Each book chapter provides detailed description of the underlying algorithm and implementation features of a placement tool that participated in the two contests, including the experimental results on ISPD placement benchmark circuits and the optimality analysis on PEKO-MS benchmarks.

This book is organized in four parts:

- Part I introduces placement benchmark suites. In Chap. 1, new industry designdriven ISPD 2005/2006 benchmark circuits are presented with contest results. Chapter 2 describes the details of PEKO-MS benchmarks that can be used for placement optimality analysis.

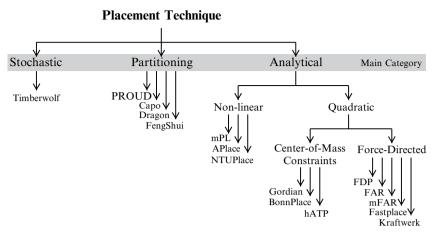

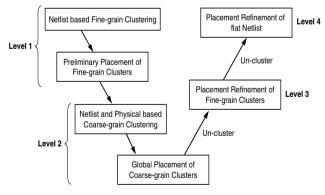

- Part II describes flat placement techniques, which formulate and solve the entire placement problem directly (although the numerical solvers used in these placers may use multilevel methods). Chapter 3 describes the most recent analytical placer DPlace that is an anchor cell-based quadratic placement engine. The Kraftwerk placement algorithm, the winner of ISPD 2006 placement contest, is presented in Chap. 4.

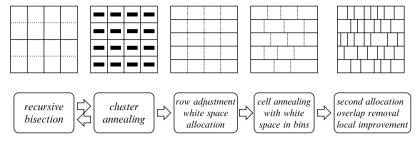

- Part III presents top-down partitioning-based placement techniques. It includes Capo, a congestion driven placer (Chap. 5) and the Dragon placer that combines simulated annealing optimization with a partitioning algorithm (Chap. 6).

- Part IV is about multilevel placement methods that have attracted significant attentions recently. It covers APlace (Chap. 7), which was the winner of the 2005 placement contest, the runtime efficient force-directed placer, FastPlace (Chap. 8), the mFAR fixed-point addition based placer (Chap.9), and the multi-level non-linear optimization placer mPL (Chap. 10) that produced the highest quality solutions in the 2006 placement contest. Also, NTUplace3 (Chap. 11), a new analytical placer for large scale mixed-size designs, is presented here.

The idea of this book emerged in April 2006, right after the ISPD 2006 placement contest, as a way of capturing a technology snapshot of dominant placement algorithms. We sent out invitations to all placement contest participants, and every team agreed to contribute to this book. By February 2007, all chapter manuscripts were submitted. In fact, some of them included the latest progress they made after the 2006 placement contest. Therefore, the results reported in some of the chapters are different (better) from the original placement contest results, which we provided at the end of Chap. 1 for reference.

The editors are well aware of the limitations of placement objectives used in the two contests. The 2005 contest uses wire length minimization as its sole objective function, while the 2006 contest uses a combination of wire length minimization, cell density control and runtime as its objective function (see Chap. 1 for more details). Real placement problems need to consider a number of other objectives, such as timing, power, and thermal optimization, as well as interaction with various physical synthesis operations, such as buffer insertion and gate sizing. A direct comparison of different placers under all these objectives and constraints may not be possible or meaningful, as each design has its own emphasis, and the final result is not determined by the placement algorithm alone. Many other steps, such as timing analysis, global and detailed routing, and various physical optimization operations can affect the final result. Therefore, we think that it is appropriate to use rather simple metrics in the two placement contests to measure the capability of the core wire length optimization engines employed in the different placers. As pointed in [4], a placer with good wire length minimization engine can be extended to handle other design objectives through weighted wire length minimization using various weighting functions.

This book is intended for graduate students, researchers, and CAD tool developers in the physical synthesis and physical design area. Each chapter is mostly selfcontained and can be read independently. We hope that the readers can benefit from this collection of modern placement algorithms and potentially contribute to the field with new perspective. Please note this book is not intended to provide a comprehensive review of all available placement techniques, but to highlight the most successful techniques and practices used in modern placers. We refer the reader to [4] for a more comprehensive survey for the existing placement techniques.

We would like to thank the ISPD organizing committee for sponsoring the two placement contests, and IBM Corporation for providing the benchmark examples. We are indebted to the time and efforts of all the chapter authors who made this book possible. Finally, we would like to thank David Papa at the University of Michigan for thorough reviews of all chapters.

Gi-Joon Nam IBM Research Austin, Texas

Jason Cong University of California Los Angeles, California

March 2007

## References

- C.-C. Chang, J. Cong and M. Xie, "Optimality and Scalability Study of Existing Placement Algorithms," Asia South Pacific Design Automation Conference, 2003, pp. 621–627

- C.-C. Chang, J. Cong, M. Romesis and M. Xie, "Optimality and Scalability Study of Existing Placement Algorithms," *IEEE Transactions on Computer-Aided Design of Inte*grated Circuits, pp. 537–549, April 2004

- J. Cong, "An Interconnect-Centric Design Flow for Nanometer Technologies", Proceedings of the IEEE, vol. 89, No. 4, pp. 505–528, April 2001

- J. Cong, T. Kong, J. Shinnerl, M. Xie and X. Yuan, "Large Scale Circuit Placement," *ACM Transaction on Design Automation of Electronic Systems*, vol. 10, no. 2, pp. 389– 430, April 2005

- Gi-Joon Nam, "ISPD 2006 placement contest: Benchmark suite and results," Proceedings of the International Symposium on Physical Design, pages 167–167, 2006

- G.-J. Nam, C.J. Alpert, P. Villarubbia, B. Winter, and M. Yildiz, "The ISPD2005 placement contest and benchmark suite," *Proceedings of the International Symposium on Physical Design*, pages 216–219, 2005

- 7. http://www.ispd.cc

Benchmarks

## ISPD 2005/2006 Placement Benchmarks

**Gi-Joon Nam<sup>1</sup>, Charles J. Alpert<sup>1</sup>, and Paul G. Villarrubia<sup>2</sup>** <sup>1</sup>IBM Austin Research Lab <sup>2</sup>IBM EDA {gnam, alpert, pgvillar}@us.ibm.com

#### 1.1 Introduction

Benchmarks can contribute significantly to algorithm development of many fields by providing a common basis for quantitative measurement and comparison. The early MCNC benchmarks and ISPD98 benchmarks [1] helped the academic community significantly to measure the advances in physical design in 1990s. While still being used extensively in placement and floorplanning research, those benchmarks can no longer be considered representative of today's physical design challenges. To further aid future advances in placement, new benchmark suites, dubbed as *ISPD 2005/2006 Placement Benchmarks*, have been released in conjunction with ISPD placement contests. There are total 16 benchmark circuits that are directly derived from modern industrial ASIC designs. These benchmarks include rather unique features to represent modern physical design challenges:

- Design size

- I/O objects

- Macros

- Floorplans

- White space

- Density target

Due to scaled technology and requirements of more complex functionality, modern designs contain more circuit elements than ever. In today's environment, several million gate designs are considered a norm and this number will increase year after year. This situation renders more scalable placement algorithm to design size preferred in the field. ISPD placement benchmarks provide five circuits with

1

more than a million placeable objects. These large circuits serve to test the scalability of placement algorithms.

In older technologies, I/O pins usually preside around the chip boundary, and they are called perimeter I/Os. Modern technologies, however, allow I/O pins to be populated within chip area to reduce signal propagation delay through I/O pins. This new technology is called the area-array I/O technology. The new ISPD benchmark suites have multiple placement instances using the area-array I/O technology.

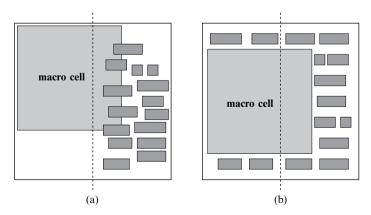

In today's design environment, hierarchical design methodology is extremely popular to reduce the turn-around-time of taping out chips. Due to this, more and more macro blocks (either fixed or movable) are introduced into modern ASIC designs. Indeed, these macro blocks can cause serious problems during placement. For example, legalization becomes extremely tricky with large movable macros. All ISPD placement benchmarks contain either movable or fixed macros or both, and serve as a good test set for mixed-size placement algorithms.

Another interesting aspect with macros is that they produce much more variety of floorplans for modern placement tools. Early decisions of where to put these macros during global placement have significant impact on the quality of placement solution. Therefore, modern placement tools have to be more reliable and robust to various floorplans. ISPD placement benchmarks provide a variety of floorplans with many macro blocks.

Modern high-performance ASIC designs have abundant white space primarily due to the needs of potential gate sizing, buffering, and other optimizations that follow the placement process. In global placement algorithm, white space management has become one of the most important considerations because it could affect the wire length of placement solution significantly. ISPD 2005/2006 benchmarks have wide range of white space to emphasize the importance of white space management.

If a placement solution is not routable, there is no point of discussing whether it is a good or bad solution. In other words, placement solution has to be routable. Unfortunately, it is extremely difficult to model the routability accurately or measure congestion during placement without actually running global/detailed router. Density target forces global/detailed placement algorithm to preserve some amounts of white space in arbitrary neighborhood of placement regions. These additional white space can serve to mitigate local congestion. All ISPD 2006 benchmarks have associated *density targets* (ranging from 50% to 90%) to represent different congestion constraints.

Next we briefly review the benchmark statistics and quality measurements of two placement contests.

#### 1.2 ISPD 2005 Placement Contest and Benchmark<sup>1</sup>

As an inaugural placement contest, the quality of placement solutions was solely measured by half-perimeter bounding box wire length (HPWL) with pin locations respected. HPWL is widely used when comparing results in placement and

<sup>&</sup>lt;sup>1</sup> Portions reprinted from the reference [11] with © [2005] ACM.

| Circuit  | #Obj    | #Mov    | #Fixed | #Net    | Density (%) | Util.(%) | # Peri.I/Os |

|----------|---------|---------|--------|---------|-------------|----------|-------------|

| adaptec1 | 211447  | 210904  | 543    | 221142  | 76          | 57       | 480         |

| adaptec2 | 255023  | 254457  | 566    | 266009  | 79          | 44       | 407         |

| adaptec3 | 451650  | 450927  | 723    | 466758  | 75          | 34       | 0           |

| adaptec4 | 496045  | 494716  | 1329   | 515951  | 63          | 27       | 0           |

| bigblue1 | 278164  | 277604  | 560    | 284479  | 54          | 45       | 528         |

| bigblue2 | 557866  | 534782  | 23084  | 577235  | 62          | 38       | 0           |

| bigblue3 | 1096812 | 1095519 | 1293   | 1123170 | 86          | 57       | 0           |

| bigblue4 | 2177353 | 2169183 | 8170   | 2229886 | 65          | 44       | 0           |

Table 1.1. ISPD 2005 benchmark characteristics.

floorplanning research. HPWL is easy to measure and still a reasonable first-order estimation for the routed wire length for small nets. For larger nets, steiner-tree wire length is necessary to accurately estimate the routed wire length.

Table 1.1 summarizes the characteristics of circuits in ISPD 2005 placement benchmark suite. The reported statistics are:

- #Obj. The total number of objects of design

- #Mov. The number of movable objects

- *#Fixed*. The number of fixed objects

- *#Net*. The number of nets

- *Density*(%). The total design density defined as the ratio of the area sum of all objects divided by placement area

- *Util.(%).* The design utilization defined as the ratio of the area sum of only movable objects divided by available free space. The available free space is defined as difference between entire placement area and the area sum of fixed objects

- *#Peri. I/Os.* The number of perimeter I/O objects. If this number is 0, a design contains only area-array I/Os

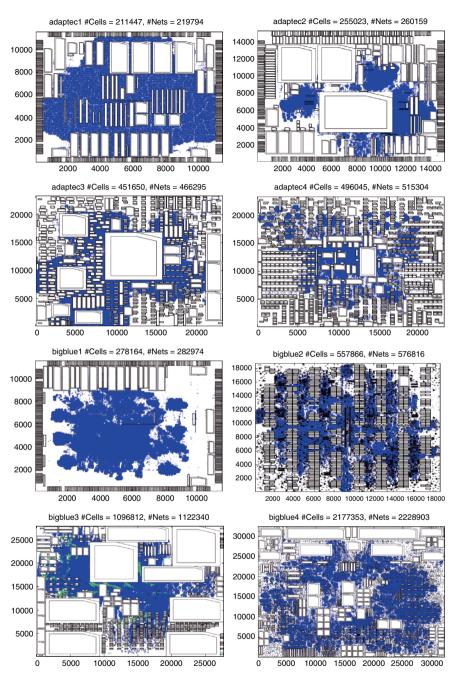

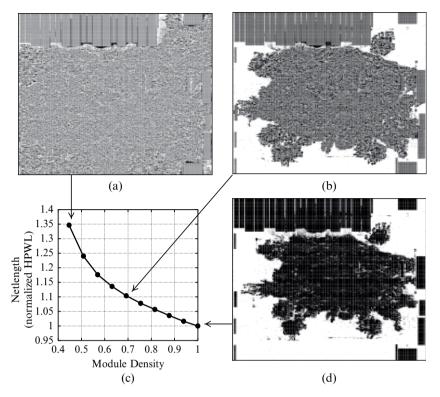

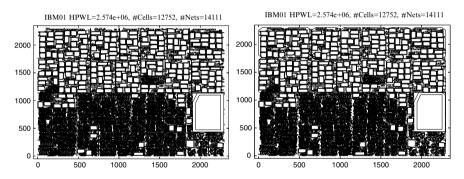

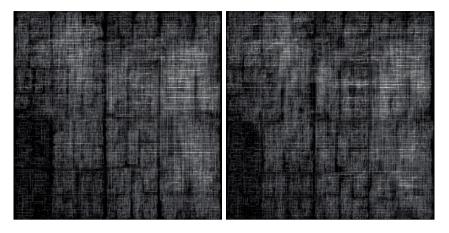

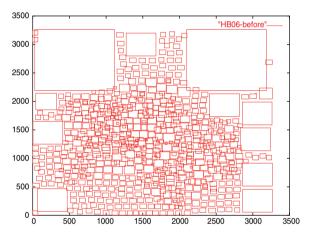

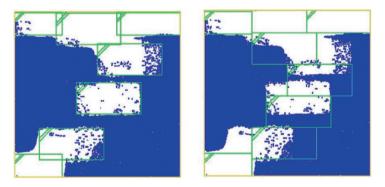

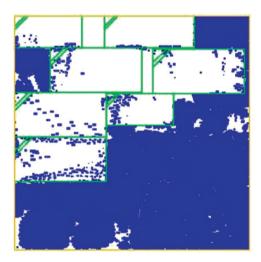

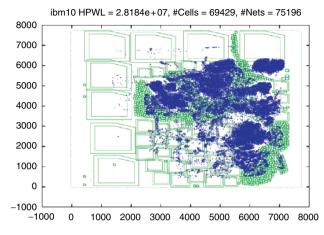

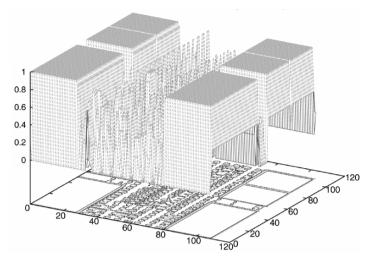

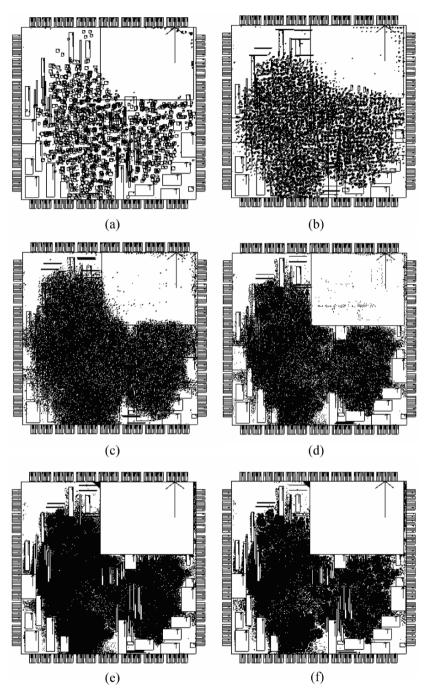

Figure 1.1 presents layout figures of benchmarks. To produce these layout figures, the Capo [14] placer's utility plotter is used that can be obtained from GSRC Bookshelf [3]. These circuits include many fixed blocks demonstrating current SoCstyle VLSI design methodology. Big fixed macro blocks basically dictate the overall placement footprints while placing movable dust logic around them becomes the main task of the placement algorithm. It is still a challenging problem because placement algorithm must be able to cope with large number of objects (scalability), satisfy timing constraints (timing closure) and produce routable solutions (routability/congestion). Each design presents slightly different styles of placement problems. For example, *adaptec2* and *adaptec3* have large fixed blocks in the center of placement region, which may cause larger variations in wire lengths depending on which sides of fixed blocks movable cells are placed. In *bigblue1*, placing movable objects at the center region in more compact manner seems to be a more critical task. The benchmark *bigblue2* have relatively large number of pins from regularly placed small fixed blocks. The design density of bigblue3 is over 85% primarily due to several large fixed blocks whereas its design utilization is around 55% with abundant free

Fig. 1.1. Layout figures of ISPD 2005 benchmark suite.

space available. Two benchmarks *bigblue3* and *bigblue4*, with more than one million placeable objects, are good test cases for testing scalability of placement algorithms.

#### 1.3 ISPD 2006 Placement Contest and Benchmark

To address the routability and congestion mitigation, ISPD 2006 placement contest benchmarks were released with associated density targets that the placer should obey. Density target is a constraint that forces a placer to reserve specified white space in any subregions of placement area. The density target is a floating number that is larger than or equal to *design density* that is defined as the total movable cell area divided by the total available area in the placement region. For example, if density target is 0.7, any local region should be less than or equal to 70% occupied. The lower the density target is, the more spreading is required. The idea behind this constraint is to improve routability and allow space for buffering, gate sizing, and clock tree that will be inserted later. In other words, this spacing helps make the placement instance more realistic to the practice in the field.

In 2006 placement contest, the quality of placement solution was measured by the adjusted HPWL function:

$$HPWL \times (1 + scaled\_overflow\_factor + cpu\_factor).$$

(1.1)

To measure *scaled\_overflow\_factor*, the placement region is divided into a set of equal-sized bins (10 circuit row heights). For each bin *b*, *bin\_overflow* is calculated as follows

$$bin\_overflow(b) = \sum_{movablev \in b} [area(v) - free\_space(b) \times density\_target] (1.2)$$

where *free\_space(b)* is the available white space, i.e., the difference between the single bin area and the sum of fixed object areas that belong to the corresponding bin. The *total\_overflow* of a design is simply the sum of *bin\_overflow(b)* over all bins. Then, *scaled\_overflow\_factor* is calculated by

$$scaled\_overflow\_factor = \frac{total\_overflow \times single\_bin\_area \times density\_target}{(\sum_{movablev \in design} area(v)) \times c}$$

(1.3)

where c is a constant. Note that the term

$$\frac{\sum_{movablev \in design} area(v)}{single\_bin\_area \times density\_target}$$

(1.4)

is the minimum number of bins that can accommodate all movable objects in a design with a given density target. This term is independent of placement region area. Rather it is a unique design related factor. Therefore, the *scaled\_overflow\_flow* gives the (scaled) average overflow over the minimum number of bins required. For ISPD 2006

| Circuit  | #Obj    | #Mov    | #Fixed | #Net    | Density (%) | Util. (%) | Density target |

|----------|---------|---------|--------|---------|-------------|-----------|----------------|

| adaptec5 | 843128  | 842482  | 646    | 867798  | 79          | 50        | 0.5            |

| newblue1 | 330474  | 330137  | 337    | 228901  | 86          | 83        | 0.8            |

| newblue2 | 441516  | 330239  | 1277   | 465219  | 86          | 62        | 0.9            |

| newblue3 | 494011  | 482833  | 11178  | 552199  | 85          | 26        | 0.8            |

| newblue4 | 646139  | 642717  | 3422   | 637051  | 66          | 46        | 0.5            |

| newblue5 | 1233058 | 1228177 | 4881   | 1284251 | 75          | 50        | 0.5            |

| newblue6 | 1255039 | 1248150 | 6889   | 1288443 | 59          | 39        | 0.8            |

| newblue7 | 2507954 | 2481372 | 26582  | 2636820 | 76          | 49        | 0.8            |

Table 1.2. ISPD 2006 benchmark characteristics.

contest, the constant c is set to 400, and to emphasize the importance of overflow factor, the squared *scaled\_overflow\_flow* term is used.

The purpose of *cpu\_factor* is designed to gently encourage CPU performance. The intention is to encourage placers to get faster but not at the cost of significant solution quality. The *cpu\_factor* is calculated as

$$cpu\_factor = 0.04 \times \ln \frac{placer\_cputime}{median\_cputime}$$

(1.5)

Therefore, if placer A is 2 times slower (faster) than a median speed placer, it gets 4% wire length penalty (advantage). If it is 4 times slower (faster), 8% wire length penalty (advantage) is imposed on placer A. However, *cpu\_factor*'s wire length penalty/advantage is limited to maximum 10%.

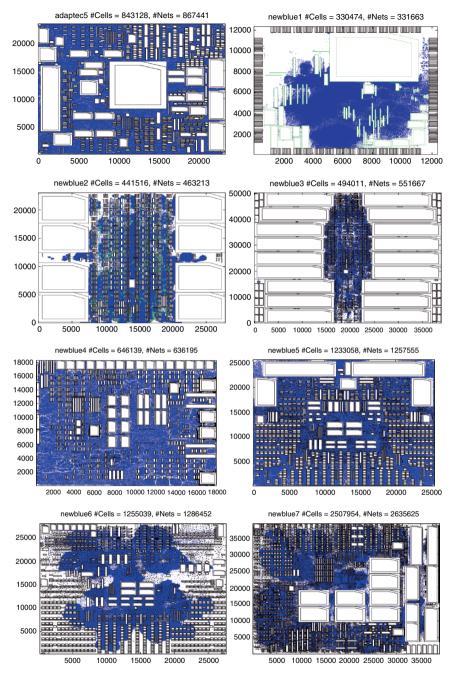

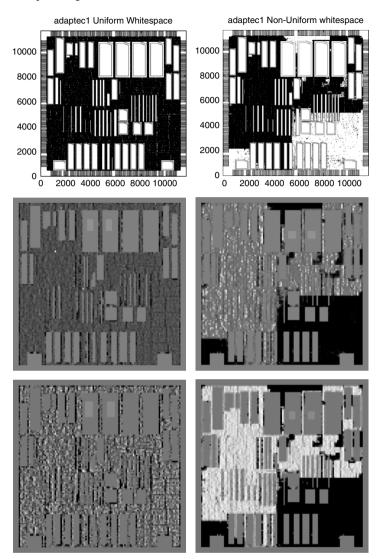

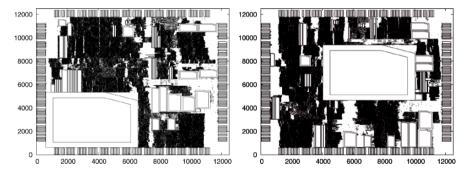

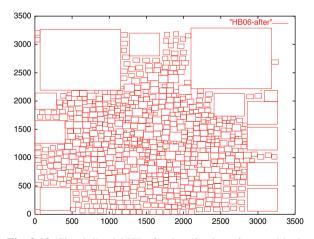

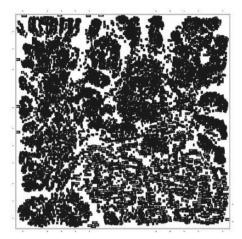

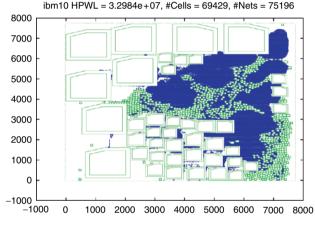

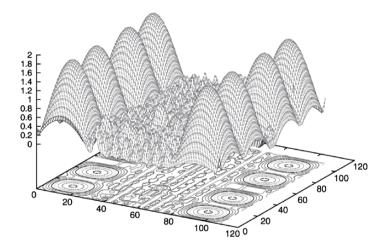

Table 1.2 summarizes the characteristics of circuits in ISPD 2006 placement benchmark suite with associated density targets, and Figure 1.2 shows the layout figures that were generated with the Capo [14] placer's utility plotter from GSRC Bookshelf [3]. Again, each circuit in ISPD 2006 benchmark suite presents different styles of placement challenges. The density target of *adaptec5* is set to 0.5 while its design utilization is a little bit below 50%. Thus, it forces a placer to spread movable objects uniformly over the entire placement area. *newblue1* has several large movable macro blocks, and test the floorplanning capability of placement algorithm. In *newblue2*, all standard cells are inflated by  $2 \times$  for congestion mitigation. Since cells are already inflated, a rather high-density target 0.9 is enforced. *newblue3* presents an unique floorplan with large fixed macros on both sides of placement region. The density targets of *newblue4* and *newblue5* are both set to 0.5, almost similar value to design utilization. Therefore, uniform spreading is required for both test cases. Also, *newblue5*, *newblue6* and *newblue7* have more than a million movable objects and the scalability of placement algorithm is important for these large circuits.

#### **1.4 ISPD Placement Contest Results**

Table 1.3 presents the results of 2005 placement contest. Columns 2–7 show the actual half-perimeter bounding box wire lengths of all placer's on each circuit and column 8 is the average ratio of a placer's wire length over the best wire length of

Fig. 1.2. Layout figures of ISPD 2006 benchmark suite.

| Placer         | adaptec2 | adaptec4 | bigblue1 | bigblue2 | bigblue3 | bigblue4 | Ratio |

|----------------|----------|----------|----------|----------|----------|----------|-------|

| Aplace [9]     | 87.31    | 187.65   | 94.64    | 143.82   | 357.89   | 833.21   | 1.00  |

| mFar [8]       | 91.53    | 190.84   | 97.70    | 168.70   | 379.95   | 876.28   | 1.06  |

| Dragon [16]    | 94.72    | 200.88   | 102.39   | 159.71   | 380.45   | 903.96   | 1.08  |

| mPL [4]        | 97.11    | 200.94   | 98.31    | 173.22   | 369.66   | 904.19   | 1.09  |

| FastPlace [18] | 107.86   | 204.48   | 101.56   | 169.89   | 458.49   | 889.87   | 1.16  |

| Capo [14]      | 99.71    | 211.25   | 108.21   | 172.30   | 382.63   | 1098.76  | 1.17  |

| NTUplace [6]   | 100.31   | 206.45   | 106.54   | 190.66   | 411.81   | 1154.15  | 1.21  |

| FengShui [2]   | 122.99   | 337.22   | 114.57   | 285.43   | 471.15   | 1040.05  | 1.50  |

| Kraftwerk [13] | 157.65   | 352.01   | 149.44   | 322.22   | 656.19   | 1403.79  | 1.84  |

Table 1.3. ISPD 2005 contest results.

| Table 1.4. ISPD 2006 contest results: Scaled HPWI |

|---------------------------------------------------|

|---------------------------------------------------|

| Placer        | ad5    | nb1    | nb2    | nb3    | nb4    | nb5    | nb6    | nb7     |

|---------------|--------|--------|--------|--------|--------|--------|--------|---------|

| Kraftwerk     | 457.92 | 78.60  | 208.41 | 280.93 | 315.53 | 569.36 | 545.94 | 1170.85 |

| mPL6 [5]      | 431.14 | 67.02  | 200.93 | 287.05 | 299.66 | 540.67 | 518.70 | 1082.92 |

| NTUplace3 [7] | 432.58 | 63.49  | 203.68 | 291.15 | 305.79 | 517.63 | 532.79 | 1181.30 |

| mFAR          | 476.28 | 77.54  | 212.90 | 303.91 | 324.40 | 601.27 | 535.96 | 1153.76 |

| Aplace3 [10]  | 520.97 | 73.31  | 198.24 | 273.64 | 384.12 | 613.86 | 522.73 | 1098.88 |

| Dragon [17]   | 500.74 | 80.77  | 260.83 | 524.58 | 341.16 | 614.23 | 572.53 | 1410.54 |

| FastPlace     | 805.64 | 84.55  | 212.30 | 362.99 | 429.79 | 962.06 | 574.18 | 1236.34 |

| DPlace        | 572.98 | 102.75 | 329.92 | 380.14 | 364.45 | 752.08 | 682.87 | 1438.99 |

| Capo [15]     | 494.64 | 98.48  | 309.53 | 361.25 | 362.40 | 659.57 | 668.66 | 1518.75 |

each circuit. Note that the sole quality metric of 2005 placement contest was the half-perimeter bounding box wire length, and no CPU time usage limit was applied.

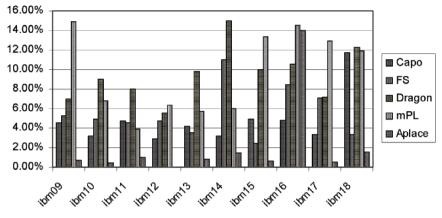

Aplace won the first contest convincingly by producing the best wire length on all circuits. Generally, analytical placers such as APlace, mFAR, mPL, and FastPlace produced better placement solutions than other algorithms. However, Kraftwerk, another analytical placement tool ended up the last place. Placeable objects in Kraftwerk solutions were spread uniformly over the entire placement regions leading to worse wire lengths. This turns out to be a critical mistake in low-utilization circuits. FengShui is a recursive partitioning-based placement tool that participated only in the first contest. Also, note that NTUplace was implemented as a partitioning-based placement tool in 2005.

The detailed data of ISPD 2006 placement contest are presented in Tables 1.4 and 1.5 [12]. Note that the scaled HPWLs in Table 1.4 include the bin overflow penalty factor in wire length calculation while CPU time factor is not included. Thus, the scaled HPWL is a representative metric for quality of solutions.

In Table 1.5, the reported statistics are:

- *Avg. HPWL Ratio.* The average ratio of a placer's HPWL over the best HPWL of each circuit. The closer to 1.0 this value is, the better a placer's HPWL is.

- Avg. OV Factor %. The average scaled bin overflow penalty factor to scaled HPWL calculation in percentage. For example, Kraftwerk got 1.68% increase in

| Placer    | Avg. HPWL Ratio | Avg. OV Factor (%) | Avg. CPU Factor (%) | Score Ratio |

|-----------|-----------------|--------------------|---------------------|-------------|

| Kraftwerk | 1.09            | 1.68               | -5.04               | 1.03        |

| mPL6      | 1.03            | 1.36               | 1.58                | 1.04        |

| NTUplace3 | 1.02            | 4.10               | 1.66                | 1.05        |

| mFAR      | 1.11            | 2.71               | -0.12               | 1.11        |

| Aplace3   | 1.10            | 3.82               | 5.31                | 1.16        |

| Dragon    | 1.33            | 0.12               | -5.90               | 1.24        |

| FastPlace | 1.18            | 22.09              | -5.62               | 1.33        |

| DPlace    | 1.34            | 9.32               | -4.54               | 1.36        |

| Capo      | 1.38            | 0.32               | 2.69                | 1.39        |

Table 1.5. ISPD 2006 contest results: HPWL, Bin overflow, and CPU time factor.

wire length due to its bin overflow penalty. FastPlace, however, was imposed over 22% wire length penalty implying that the density target was not strictly honored. Note that this penalty was already applied in the scaled HPWLs reported in Table 1.4.

- Avg. CPU Factor %. The average CPU time factor to wire length calculation in percentage. Negative value implies that a placer is faster than others and the contest scoring wire length is reduced by that amount. For example, Kraftwerk, mFAR, Dragon, FastPlace, and DPlace were rather fast placement tools and got some wire length advantage from 0.12% to 5.90%.

- *Score Ratio*. The average ratio of contest's scoring metric of a placer over the best one on individual circuit. This value represents the final ranking of the contest.

Overall, the Kraftwerk placer won the 2006 placement contest. The applied contest scoring metric with the consideration of HPWL, bin overflow, and runtime was successfully able to identify three best placers among all participants. The discrepancy between top three teams turned out to be negligible. If only HPWL and bin scaled factor (i.e., scaled HPWLs) are considered, mPL6, NTUplace3, and Kraftwerk again remain as top three teams.

### References

- C. Alpert, "The ISPD98 Circuit Benchmark Suite," in Proc. ACM/IEEE International Symposium on Physical Design, 1998, pp. 80–85

- A. Agnihotri, S. Ono and P. Madden, "Recursive Bisection Placement: Feng Shui 5.0 Implementation Details," in *Proc. ACM/IEEE International Symposium on Physical Design*, 2005, pp. 230–232

- 3. A.E. Caldwell, A.B. Kahng, I.L. Markov, VLSI cad bookshelf. http://vlsicad. eecs.umich.edu/BK/. See also Caldwell AE, Kahng AB, Markov IL (2002) Toward cad-ip reuse: the marco gsrc bookshelf of fundamental cad algorithms. IEEE Design and Test 72–81

- T.F. Chan, J. Cong, M. Romesis, J.R. Shinnerl, K. Sze and M. Xie, "mPL6: A Robust Multilevel Mixed-Size Placement Engine," in *Proc. ACM/IEEE International Symposium* on *Physical Design*, 2005, pp. 227–229

- T.F. Chan, J. Cong, J.R. Shinnerl, K. Sze and M. Xie, "mPL6: Enhanced Multilevel Mixed-Size Placement," in *Proc. ACM/IEEE International Symposium on Physical Design*, 2006, pp. 212–214

- T.-C. Chen, T.-C. Hsu, Z.-W. Jiang and Y.-W. Chang, "NTUplace: A Ratio Partitioning Based Placement Algorithm for Large-Scale Mixed-Size Designs," in *Proc. ACM/IEEE International Symposium on Physical Design*, 2005, pp. 236–238

- Z.-W. Jiang, T.-C. Chen, T.-C. Hsu, H.-C. Chen and Y.-W. Chang, "NTUplace2: A Hybrid Placer Using Partitioning and Analytical Techniques," in *Proc. ACM/IEEE International Symposium on Physical Design*, 2006, pp. 215–217

- B. Hu, Y. Zeng and M. Marek-Sadowska, "mFAR: Fixed-Points-Addion-Based VLSI Placement Algorithm," *Proc. ACM/IEEE International Symposium on Physical Design*, 2005, pp. 239–241

- A.B. Kahng, S. Reda, and Q. Wang, "APlace: A General Analytic Placement Framework," in *Proc. ACM/IEEE International Symposium on Physical Design*, 2005, pp. 233-235

- A.B. Kahng, and Q. Wang, "A Faster Implementation of APlace," in Proc. ACM/IEEE International Symposium on Physical Design, 2006, pp. 218–220

- G.-J. Nam, C.J. Alpert, P. Villarrubia, B. Winter and M. Yildiz, "The ISPD2005 Placement Contest and Benchmark Suite,", in *Proc. ACM/IEEE International Symposium on Physical Design*, 2005, pp. 216–220

- Gi-Joon Nam, "ISPD 2006 placement contest: Benchmark suite and results," Proceedings of the International Symposium on Physical Design, pages 167–167, 2006

- B. Obermeier, H. Ranke and F. M. Johannes, "Kraftwerk A Versatile Placement Approach," in *Proc. ACM/IEEE International Symposium on Physical Design*, 2005, pp. 242–244

- J.A. Roy, D.A. Papa, S.N. Adya, H.H. Chan A.N. Ng, J.F. Lu and I.L. Markov, "Capo: Robust and Scalable Open-Source Min-Cut Floorplacer," in *Proc. ACM/IEEE International Symposium on Physical Design*, 2005, pp. 224–226

- J.A. Roy, D.A. Papa, A.N. Ng and I.L. Markov, "Satisfying Whitespace Requirements in Top-down Placement," in *Proc. ACM/IEEE International Symposium on Physical Design*, 2006, pp. 206–28

- T. Taghavi, X. Yang, B.K. Choi, M. Wang and M. Sarrafzadeh, "DRAGON2005: Large-Scale Mixed-Size Placement Tool," in *Proc. ACM/IEEE International Symposium on Physical Design*, 2005, pp. 245–247

- T. Taghavi, X. Yang, B.K. Choi, M. Wang and M. Sarrafzadeh, "DRAGON2006: Blockage-Aware Congestion-Controlling Mixed-Size Placer," in *Proc. ACM/IEEE International Symposium on Physical Design*, 2006, pp. 209–211

- N. Viswanathan, M. Pan and C.C. -N. Chu, "FastPlace: An Analytical Placer for Mixed-Mode Designs," in *Proc. ACM/IEEE International Symposium on Physical Design*, 2005, pp. 221–223

## Locality and Utilization in Placement Suboptimality

Jason Cong,<sup>1</sup> Michalis Romesis<sup>2</sup>, Joseph R. Shinnerl<sup>3</sup>, Kenton Sze<sup>4</sup>, and Min Xie<sup>1</sup>

<sup>1</sup>UCLA Computer Science <sup>2</sup>Magma Design Automation, Inc. <sup>3</sup>Tabula, Inc. <sup>4</sup>UCLA Mathematics {cong,xie}@cs.ucla.edu michalis@magma-da.com jshinnerl@tabula.com nksze@math.ucla.edu

#### 2.1 Introduction

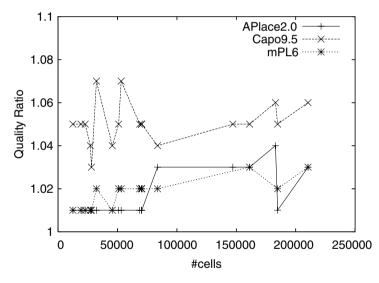

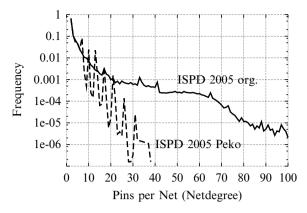

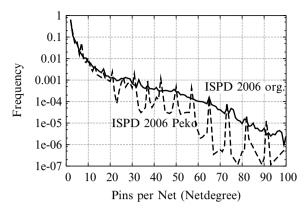

Placement is a critical step in VLSI design. Interconnect delay dominates system performance, and placement determines the interconnect more than any other step in physical design. The complexity of modern designs, however, makes estimation of suboptimality difficult [14, 16, 28]. Studies on simplified, synthetic benchmarks with known optimal-wire length placements (PEKO [7]) initially suggested that many leading tools may produce solutions with excess wire length from 60% up to 150% or more. These results have generated wide interest in both industry [13] and academia [19, 22, 28]. Recent progress in placement [1, 5, 6, 17] has reduced the wire length gap on PEKO to about 12–40%.

The PEKO benchmarks, however, have well-known limitations. Although their cell counts, net counts, and net-degree statistics match corresponding quantities in standard industrial benchmarks [2], the PEKO circuits are simplified in three key ways, in order to guarantee known optimal solutions. First, all cells are squares of the same size. Second, the known optimal placements for the PEKO circuits are packed layouts with zero white space. Third, all nets in an optimal PEKO placement are

local – the netlist of a PEKO circuit is defined over cells arranged in a regular array, with adjacent cells grouped into local nets of minimum HPWL.

Subsequent studies [9, 16] derived useful lower bounds on the HPWL suboptimality of placements of circuits with more realistic netlists. The PEKU circuits [9] add nonlocal nets to packed, uniform-grid PEKO layouts but sacrifice any assurance of optimality. Zero-change netlist transformations [16] preserve both module shapes and core utilization, but they quantify the sensitivity of a placement tool to netlist changes, not the suboptimality of a given placement on a given netlist. It is not known how close the lower bounds on suboptimality are to the true suboptimality gaps for either the PEKU circuits or the zero-change netlists.

The benchmarks described in this chapter directly address several of the shortcomings in existing suboptimality benchmarks. Two new sets of placement examples are constructed, one targeting the role of nonlocal nets in suboptimality, and another targeting the role of white space and large variations in module sizes. The first set, PEKO-MC, is a set of standard-cell circuits with nonlocal nets in known optimal placements. A given netlist is modified so as to render a given placement for it optimal for the new netlist. Cell dimensions and locations are not changed, net-degree statistics are matched exactly, and over 60% of the original netlist is left unchanged. The second set, PEKO-MS, incorporates a parametrized percentage of white space into a mixed-size placement which precisely matches given macro dimensions and locations as well as the net-degree distributions of the ISPD 2005 benchmark suite [21]. HPWL for the placements generated for the PEKO-MS circuits are proven to be less than 3% above optimal for most cases and within 8% of optimal on all cases.

The concept of a monotone path for a circuit signal has been used in performancedriven logic synthesis [23, 26], coupled timing-driven placement and logic synthesis [27], performance-driven multilevel partitioning [15], and the analysis of wire length models in timing-driven placement [24]. The concept is also employed in two of the three netlist transformations used by Kahng and Reda [16]. To our knowledge, however, the work described here is the first to employ monotone chains in the construction of netlists with known optimal-wire length placements.

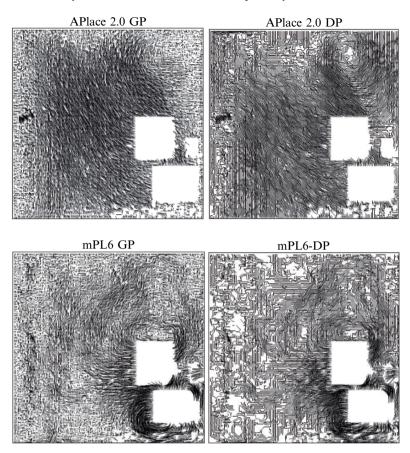

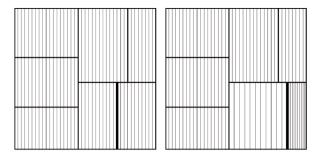

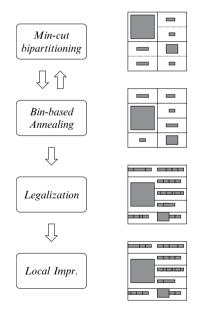

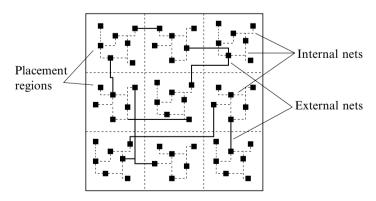

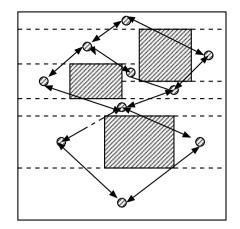

Typically, mixed size placement proceeds in three stages: global placement (GP), legalization, and detailed placement (DP). The goal of *GP* is to position each cell within some relatively small neighborhood of its final position, while eventually obtaining a sufficiently uniform distribution of cell area over the entire chip. Typically, large sets of cells are moved simultaneously under some relaxed or incremental formulation of area density control – scalable algorithms do not strictly enforce pairwise nonoverlap constraints during this stage. The goal of *legalization* is, given a sufficiently good GP  $P_g$ , determine positions of all cells so that (1) no two cells overlap and (2) a given objective, e.g., approximate total wire length or total displacement from  $P_g$ , is minimized. During *DP*, all constraints are strictly enforced. Typically, DP proceeds by a sequence of refinements made one at a time on small, contiguous subregions [4, 12] or on individual rows [18].

In practice, GP is terminated when iterations are observed to make little or no reduction in the objective and the module-area distribution is sufficiently uniform.

How much of the optimality gap left by contemporary methods should be attributed to deficiencies in global-placement algorithms, and how much to legalization and DP? On a real circuit, there is no way of knowing how far a cell is from its nearest optimal location, at any stage. On circuits with known optimal or near-optimal placements, however, it is possible to evaluate precisely the quality of any of the three engines in isolation from its counterparts. Thus, the benchmark circuits described here provide a more precise means of quantifying the relative effectiveness of the methods used in the three stages. Results estimating the separate suboptimality contributions of GP and legalization and DP are described in Sect. 2.4.

#### 2.2 Peko-MC Benchmark Construction

Each PEKO-MC example has an optimal-wirelength placement in which over 50% of the nets are non-local. Module shapes, core utilization, and net-degree statistics match corresponding quantities in a given benchmark exactly. The PEKO-MC construction is described in this section.

#### 2.2.1 Monotone Chains

The definition of a monotone chain in a netlist uses simple ideas from both graphs and hypergraphs. First, consider a path *P* in a graph *G* whose vertices lie in the plane. Let *P* consist of *n* consecutive edges  $(e_1, \ldots, e_n)$  connecting n + 1 vertices  $(v_0, \ldots, v_n)$ , vertex  $v_i$  with coordinates  $(x_i, y_i)$  and edge  $e_i$  connecting vertices  $v_{i-1}$ and  $v_i$ . Then *P* is monotone if and only if, for every  $i \in \{1, \ldots, n\}, |x_n - x_i| \le |x_n - x_{i-1}|$  and  $|y_n - y_i| \le |y_n - y_{i-1}|$ . Hence, a path in a graph embedded in the plane is monotone if and only if the Manhattan distance between its two terminal vertices equals the sum of the Manhattan lengths of its edges.

In a hypergraph, a *hyperpath* is a finite sequence of hyperedges in which each hyperedge intersects with its predecessor and successor. We say that a hypergraph lies in the plane or, equivalently, is placed in the plane, if the nodes (modules) of the hypergraph (netlist) have been assigned specific locations in the plane. In this case, the total length of a hyperpath is the sum of the HPWLs of its hyperedges (HPWL denotes minimum bounding-box half-perimeter). An edge e = (v, w) is called the *equivalent edge* of a hyperedge *h* of a hypergraph in the plane, if (1) its vertices *v* and *w* are in *h* and (2) *e*'s minimum-HPWL bounding box is the same as *h*'s minimum-HPWL bounding box. A hyperedge in the plane may have zero, one, or two equivalent edge(s).

A path P is called the *equivalent path* of a hyperpath H in a hypergraph in the plane, if there is a one-to-one correspondence between the edges of P and the hyperedges of H, such that every edge of P is the equivalent edge of its corresponding hyperedge in H. A *monotone chain* is a hyperpath which has an equivalent path that is monotone.

Assuming that no two vertices can occupy the same location, neighboring hyperedges in a monotone chain have exactly one vertex in common. These common vertices form the equivalent monotone path. The two terminal vertices of a monotone chain are the terminal vertices of its equivalent path. Hence, the length of a monotone chain equals the HPWL of the edge defined by the chain's two terminals.

**Observation 2.2.1** If the terminal vertices of a monotone chain  $P = (h_1, h_2, ..., h_n)$  of a hypergraph G are fixed in the plane, there is no other planar embedding of hypergraph G which reduces the length of P.

Given a placement of the hypergraph in the plane, a *local net* is a hyperedge the HPWL of which is the minimum possible, subject to some spacing constraints between vertices. From Observation 2.2.1, it is evident that a placement has optimal HPWL if all its nonlocal nets can be partitioned into netwise-disjoint monotone chains with fixed endpoints.

#### 2.2.2 The Peko-MC Algorithm

Starting from the placement of the real benchmark, sets of nets are identified that can be grouped together into netwise-disjoint monotone chains between well-separated fixed terminals. Initially, these chains are not complete and have gaps called intervening regions. These are later filled by other nets that are modified from the original netlist. Local nets in the given placement are not modified. The main steps of the PEKO-MC algorithm are sketched below.

*Placement generation.* The PEKO-MC generator requires a placement of the original netlist. This placement is held fixed, while the netlist is changed so that the given placement attains the optimal HPWL for the modified netlist. Starting from a random placement is possible, but experiments show that starting from a placement computed by a tool increases the final similarity of the original and the derived circuits, because a real placement has many more locally optimal nets than a random placement.

*Net categorization.* The nets of the original hypergraph are divided into three different categories depending on the placement of their pins:

- (1) Locally optimal-HPWL nets

- (2) Nets that do not have equivalent edges

- (3) Nets with equivalent edges

Nets of Type (2) cannot be members of monotone chains and are therefore modified. Nets of Type (3) are labeled according to the directions of the monotone chains of which they can be members: from lower left toward upper right, or from lower right to upper left. Some of these nets can be members of chains in either direction.

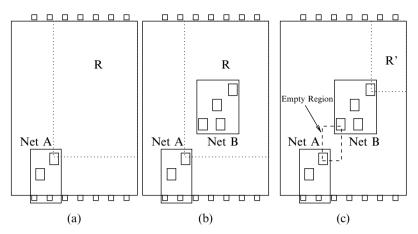

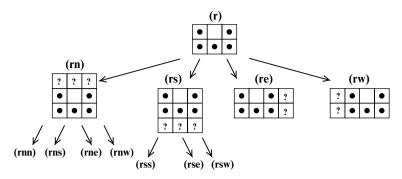

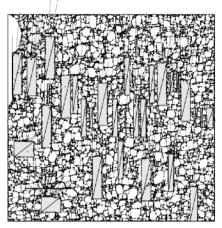

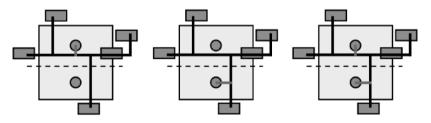

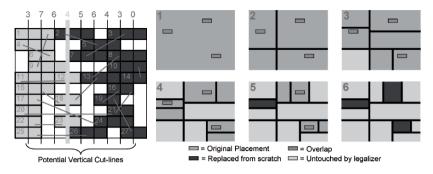

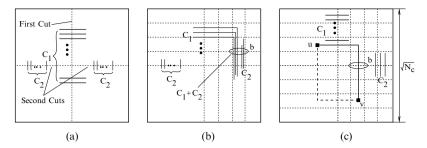

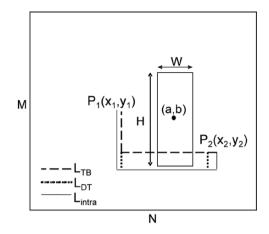

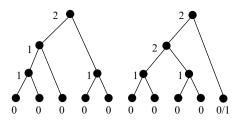

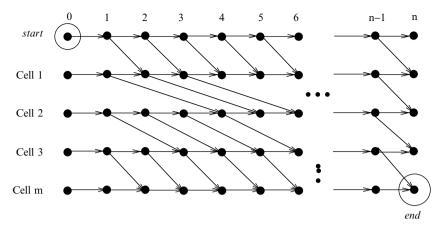

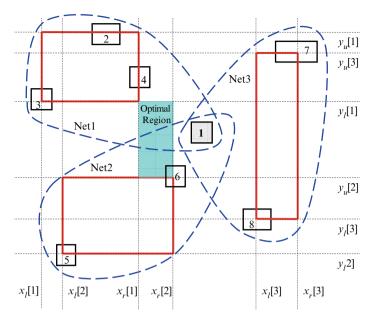

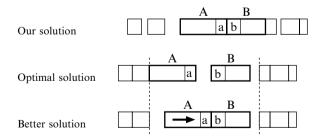

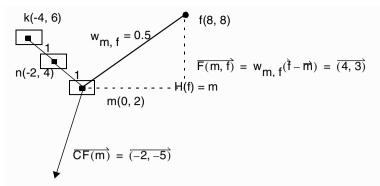

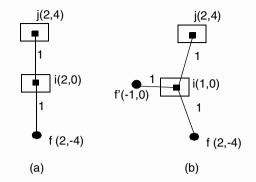

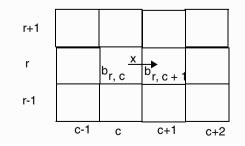

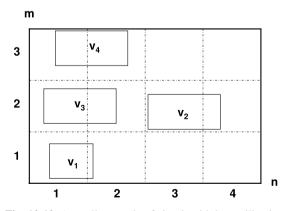

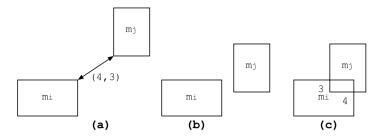

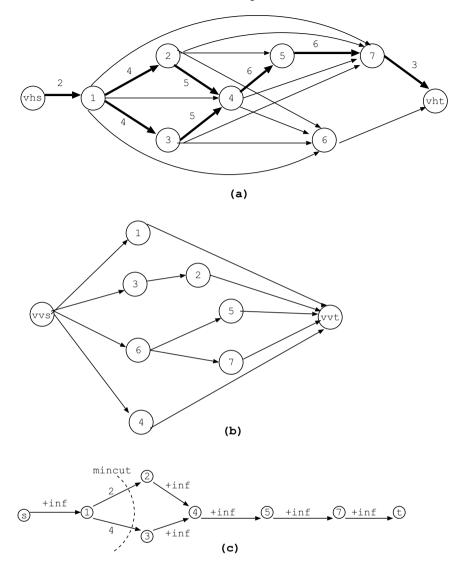

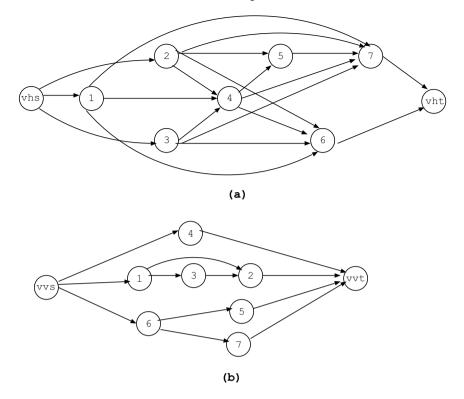

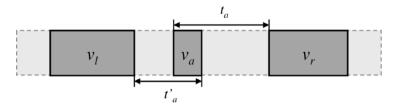

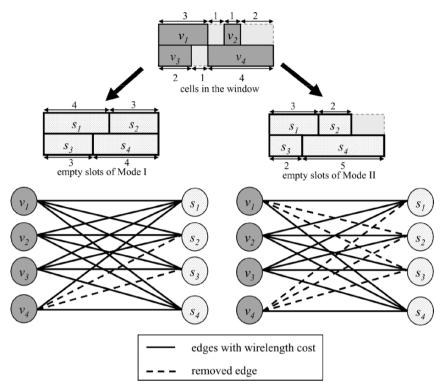

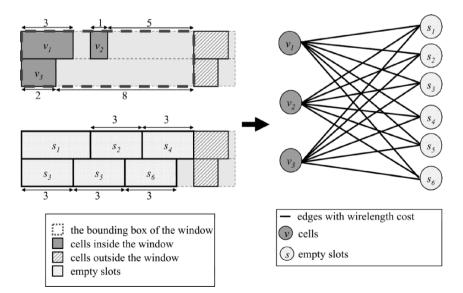

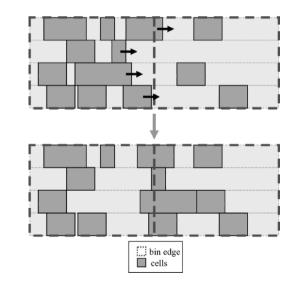

*Chain generation.* As illustrated in Figure 2.1, sets of nets that can be members of the same chain are identified along with sets of intervening regions that must later be filled by nets in order to complete the monotone chains. All nets of Type (3) are assigned to chains during this step.

*Chain removal.* In our experiments, the number of intervening regions between pairs of nets created during chain generation is higher than the number of nets of Type (2). Hence, to preserve netlist statistics, some of the chains generated are removed in order to reduce the number of such intervening regions and increase the number of

**Fig. 2.1.** Example of chain generation. (**a**) Net A, containing two cells, has already been added to the chain. A search for a new net takes place in region R. (**b**) Net B is selected to be added to the chain. (**c**) An intervening region is inserted between nets A and B that will be covered later by a new net. A new search is initiated for nets in region R'.

available nets. Chains with the highest ratios of intervening regions to contained nets are removed until the number of available nets equals or exceeds the number of gaps between terminals in chains.

*Gap covering.* In the final step, empty regions between nets in chains are filled by new nets. Each new net replaces some available net in the original netlist. The new net includes the two pins defining the equivalent edge of the bounding box of its intervening region R as well as additional pins selected from within R in order to match the degree of the replaced net. The cells whose degree in the current netlist are smallest compared to their original degree are given priority. In this way, the cell-degree distribution of the new netlist closely follows the corresponding distribution of the original circuit. Most intervening regions are covered by one net, but a few are covered by two nets, when the number of available nets exceeds the number of empty regions.

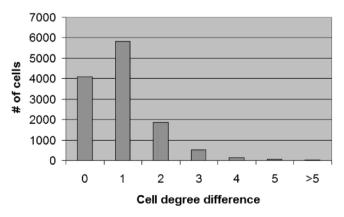

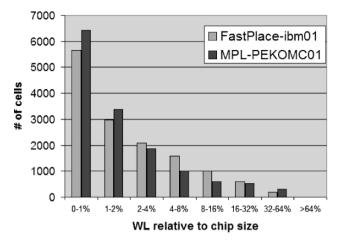

Experiments reported in Sect. 2.4 suggest that, on the 2004 FastPlace-IBM standard-cell circuits with 20% white space, nonlocal nets probably do not represent a significant source of suboptimality for these tools. In order to amplify the suboptimality observed on mixed-size cases as much as possible, the PEKO-MS benchmarks described next include only local nets by default.

#### 2.3 Peko-MS Benchmark Construction

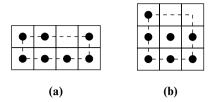

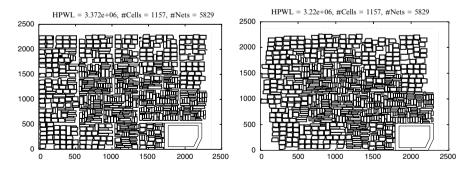

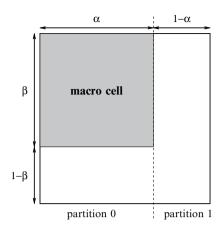

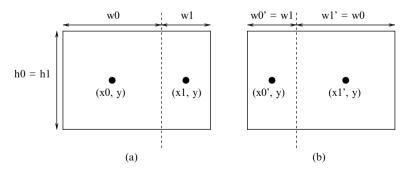

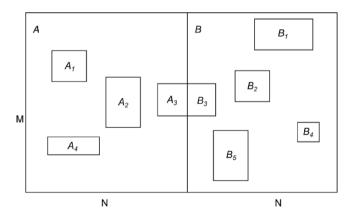

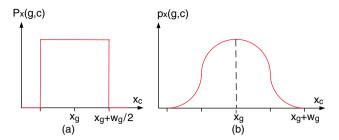

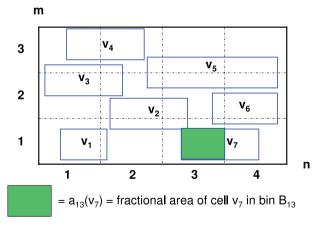

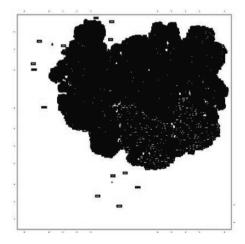

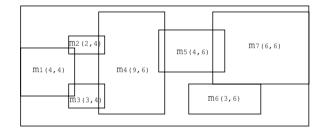

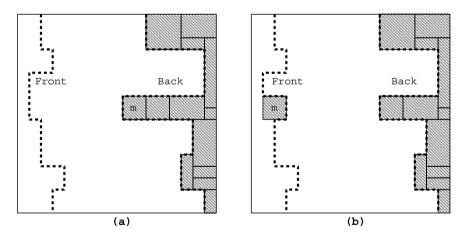

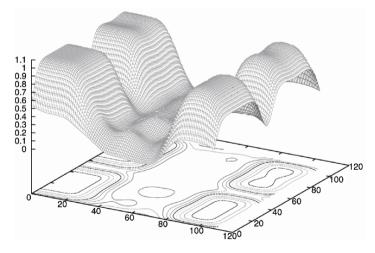

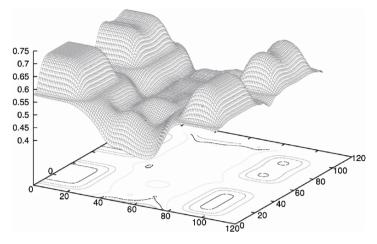

We refer to our placement suboptimality benchmarks with parametrized white space as PEKO-MS. As shown in Figure 2.2, the PEKO-MS generator produces a benchmark closely approximating the following four targets (1) net-degree histogram  $N_{\#}$ , (2) given placement  $P_{\text{mac}}$  of all macros, (3) number of standard cells  $N_{\text{sc}}$ , and (4) white

#### 18 2 Locality and Utilization in Placement Suboptimality

```

Set grid-resolution limit \overline{N_G}.

N_{\#} target net-degree histogram

P_{\rm mac} macro placement in core region \mathcal{R}

input

N_{\rm sc} target number of standard cells

\phi_{\rm ws} target white-space fraction

\phi_{\mathrm{mac}} := \left( \sum_{v_i \in P_{\mathrm{mac}}} \overline{a(v_i)} \right) / \overline{a(\mathcal{R})}.

\phi_{\rm ws} := \min\{\phi_{\rm ws}, 1 - \phi_{\rm mac} - N_{\rm sc}/\overline{N_G}\}.

\phi_{\rm sc} := 1 - \phi_{\rm mac} - \phi_{\rm ws}.

N_G := N_{\rm sc}/\phi_{\rm sc}.

if (N_G > \overline{N_G}) then

N_G := \overline{N_G}; \phi_{sc} := N_{sc}/N_G; \phi_{ws} := 1 - \phi_{mac} - \phi_{sc}.

end if

Snap P_{\text{mac}} into G, truncating macros as necessary;

mark grid cells assigned to macros.

N_{ws} := \phi_{ws} \cdot N_G.

repeat

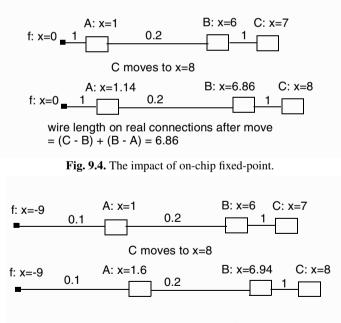

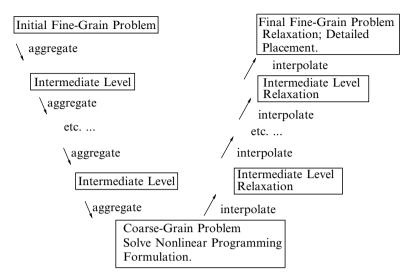

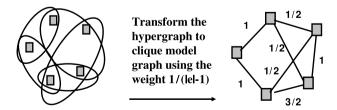

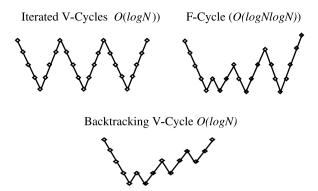

Randomly select unvisited non-macro grid cell c.