Cheng-Chi Wong · Hsie-Chia Chang

# Turbo Decoder Architecture for Beyond-4G Applications

# Turbo Decoder Architecture for Beyond-4G Applications

Cheng-Chi Wong • Hsie-Chia Chang

# Turbo Decoder Architecture for Beyond-4G Applications

Cheng-Chi Wong Department of Electronics Engineering National Chiao-Tung University Hsinchu, Taiwan Hsie-Chia Chang Department of Electronics Engineering National Chiao-Tung University Hsinchu, Taiwan

ISBN 978-1-4614-8309-0 ISBN 978-1-4614-8310-6 (eBook) DOI 10.1007/978-1-4614-8310-6 Springer New York Heidelberg Dordrecht London

Library of Congress Control Number: 2013947477

### © Springer Science+Business Media New York 2014

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

### **Preface**

Turbo code is one of the error-correcting techniques of the standards for 4G telecommunication system. From current development trend, there is a growing demand for faster data transmission; therefore, the throughput of turbo decoder should be raised to support the next-generation application. The common way to reach this objective is using parallel architecture. However, it causes increasing complexity and decreasing efficiency. These problems will limit the achievable improvement. The aim of this book is to resolve the two design issues, and our main emphasis is on the practical turbo decoders for 3GPP LTE-Advanced and IEEE 802.16m standards. Chapter 1 gives an overview of the code specifications, theoretical principles, and essential algorithms. Then Chap. 2 introduces basic functional units and main processor of a conventional turbo decoder. It further indicates the architecture with superior performance and reasonable overhead. Next, Chap. 3 illustrates the characteristics of advanced parallel architecture and explains the negative effects on complexity and efficiency. There are several implementation results supporting the introductions in Chaps. 2 and 3. All of them are derived with 90 nm technology. Chapter 4 presents how to simplify the parallel turbo decoder, while Chap. 5 shows how to get a better utilization of the component circuits. Moreover, the last two chapters highlight the conditions in which these proposed methods are suitable to use. With the materials of this book, the readers would learn about choosing the decoder architecture that can fulfill their requirements.

We wish to thank United Microelectronics Corporation for their technical support. We also wish to thank National Chiao Tung University for providing a supportive environment. In particular, we thank Professor Chen-Yi Lee for his help. Finally, we would like to express our sincere gratitude to everyone who assisted us in writing, editing, and publishing this book.

Hsinchu, Taiwan Hsinchu, Taiwan Cheng-Chi Wong Hsie-Chia Chang

### **Contents**

| 1                                                  | Intr | oductio                                   | n                                                      | 1  |  |

|----------------------------------------------------|------|-------------------------------------------|--------------------------------------------------------|----|--|

|                                                    | 1.1  | Turbo                                     | Codes: Parallel Concatenated Convolutional Codes       | 3  |  |

|                                                    |      | 1.1.1                                     | Principles of Encoding and Decoding                    | 3  |  |

|                                                    |      | 1.1.2                                     | Turbo Codes in Advanced Communication Systems          | 4  |  |

|                                                    | 1.2  | Decodi                                    | ing Procedure of Turbo Decoders                        | 8  |  |

|                                                    |      | 1.2.1                                     | MAP Algorithm for 3GPP LTE-Advanced Turbo Code         | 8  |  |

|                                                    |      | 1.2.2                                     | Iterative Flow for 3GPP LTE-Advanced Turbo Code        | 14 |  |

|                                                    |      | 1.2.3                                     | MAP Algorithm for IEEE 802.16m Turbo Code              | 19 |  |

|                                                    |      | 1.2.4                                     | Iterative Flow for IEEE 802.16m Turbo Code             | 21 |  |

|                                                    | 1.3  | Techniques for Efficient Decoding Process |                                                        |    |  |

|                                                    |      | 1.3.1                                     | Simplified MAP Algorithms                              | 24 |  |

|                                                    |      | 1.3.2                                     | Sliding Window Technique                               | 25 |  |

|                                                    |      | 1.3.3                                     | Early Stopping Criteria                                | 28 |  |

| 2                                                  | Con  | vention                                   | al Architecture of Turbo Decoder                       | 33 |  |

|                                                    | 2.1  | Practic                                   | al Turbo Decoder Architecture                          | 34 |  |

|                                                    |      | 2.1.1                                     | Circuits of Address Generators                         | 35 |  |

|                                                    |      | 2.1.2                                     | Circuits of Main Functional Units                      | 37 |  |

|                                                    | 2.2  | Design                                    | of Conventional SISO Decoders                          | 39 |  |

|                                                    |      | 2.2.1                                     | Decoder Architecture and Processing Schedule           | 39 |  |

|                                                    |      | 2.2.2                                     | Data Width and Normalization                           | 41 |  |

|                                                    | 2.3  | Design                                    | of Modified SISO Decoders                              | 46 |  |

| 3                                                  | Tur  | bo Deco                                   | der with Parallel Processing                           | 53 |  |

| 3.1 Multiple Turbo Decoders for Multiple Codewords |      | le Turbo Decoders for Multiple Codewords  | 54                                                     |    |  |

|                                                    |      |                                           | le SISO Decoders for One Codeword                      | 54 |  |

|                                                    |      | 3.2.1                                     | Important Characteristics                              | 54 |  |

|                                                    |      | 3.2.2                                     | Speedup and Performance                                | 59 |  |

|                                                    |      | 3.2.3                                     | Hardware Cost                                          | 60 |  |

|                                                    | 3.3  | Sophis                                    | ticated Functional Units for Successive Trellis Stages | 62 |  |

|                                                    | 3.4  |                                           |                                                        |    |  |

|                                                    | 3.5  | State-o                                   | of-the-Art Chip Implementation                         | 67 |  |

viii Contents

| 4  | Low-Complexity Solution for Highly Parallel Architecture |          |                                                        | 69 |

|----|----------------------------------------------------------|----------|--------------------------------------------------------|----|

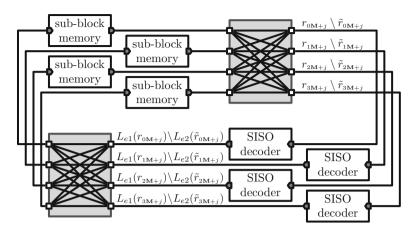

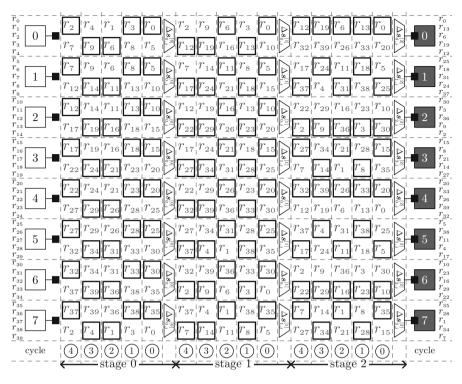

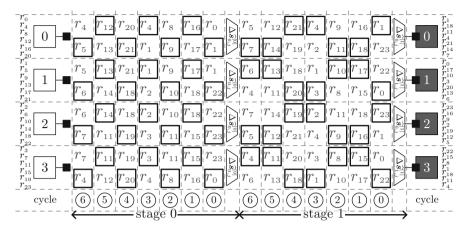

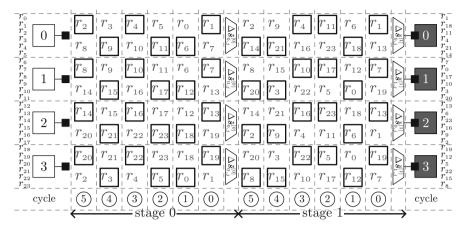

|    | 4.1                                                      | Interc   | onnection for Parallel Design with QPP Interleavers    | 70 |

|    | 4.2                                                      | Interc   | onnection for Parallel Design with ARP Interleavers    | 73 |

|    |                                                          | 4.2.1    | Parallel Architecture Using Modulo Mapping             | 73 |

|    |                                                          | 4.2.2    | Parallel Architecture Using Division Mapping           | 75 |

|    | 4.3                                                      | Perfor   | mance Compensation for Parallel Design                 | 77 |

| 5  | Higl                                                     | h-Effici | ency Solution for Highly Parallel Architecture         | 81 |

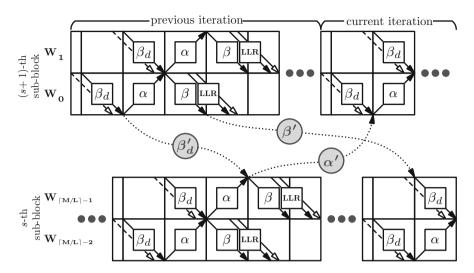

|    | 5.1                                                      | Proces   | ssing Schedule with Interlaced Decoding Rounds         | 82 |

|    | 5.2                                                      | Proces   | ssing Schedule with Overlapping Decoding Rounds        | 84 |

|    |                                                          | 5.2.1    | QPP Interleaver Design for Overlapping Decoding Rounds | 85 |

|    |                                                          | 5.2.2    | ARP Interleaver Design for Overlapping                 |    |

|    |                                                          |          | Decoding Rounds                                        | 88 |

|    |                                                          | 5.2.3    | Application of Overlapping Decoding Rounds             | 92 |

|    |                                                          | 5.2.4    | Performance of Overlapping Decoding Rounds             | 94 |

| Bi | hliog                                                    | ranhy .  |                                                        | 97 |

# Chapter 1 Introduction

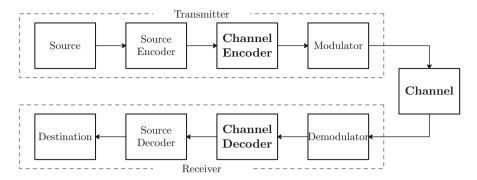

A successful transfer of information over a physical channel or a transmission medium involves a series of procedures. The model of data transmission can be depicted as Fig. 1.1. Generally, it consists of a transmitter, a channel, and a receiver. The elements inside the transmitter and receiver are utilized to guarantee reliable and efficient transmission. For less resources usage, the source encoder uses a shorter symbol sequence to replace the source information, while the source decoder performs the data decompression. When data pass through the channel, they will suffer from the channel noise and may become incorrect. To make sure the accurate information can be delivered to the destination, the channel encoder will transform its inputs into a structured sequence where parity check symbols are introduced. With these redundancies, the channel decoder is capable of recovering the messages even though the received data contain errors caused by channel impairments. In addition to the elements for signal processing, the transmitter needs a modulator to translate the data into analog forms which is suitable for transmission; and the receiver uses a demodulator to convert the channel outputs back to quantized symbols. All of the components determine the quality of data transmission. The development of the corresponding techniques will lead to the advancement of communication systems.

In a communication system, the correctness of data transmission is one of the most essential issues. This task of protecting the transmitted information against the channel noise is done by the channel encoder and channel decoder. The study about these subjects is called *forward error correction* or *channel coding*. It originated from the landmark paper by C. E. Shannon in 1948 [1,2]. Shannon's channel coding theorem indicated that arbitrary transmission can be asymptotically error-free by appropriate coding techniques if the code rate is less than the channel capacity. The theoretical limits on performance can be calculated for various signaling schemes, rates, and channels. A lot of coding techniques are developed since then, and there are two main classes of codes: *block codes* and *convolutional codes* [3, 4]. The ultimate objective is approaching the Shannon limit by a practical coding technique, and such investigation has lasted for several decades. In the 1990s, the advent of

1

Fig. 1.1 Basic elements of a communication system

turbo codes in [5] and the rediscovery of low-density parity check codes in [6] made major breakthroughs in channel coding. The two techniques both can achieve the performance close to Shannon limit at the expense of reasonable complexity [7–9]. Because of their outstanding features, they have been chosen as the forward error correction solutions in many modern communication systems [9–17].

This book focuses on the turbo codes for 3GPP LTE-Advanced standard [15] and IEEE 802.16m standard [17]. In this chapter, we begin with an overview of turbo codec structure. We will outline the relevant specifications of these up-to-date applications and mention the marked differences between these turbo codes. Then the optimal decoding algorithm toward the best performance for each standard is presented. The fundamental principles of turbo codes will be illustrated here. For avoiding complicated operations in the original algorithm, we demonstrate several suboptimal methods and examine their performance. They can make the practical implementation easier but still keep great error correction capability. Further, we discuss the order of calculation steps in every algorithm due to its dominance over the decoding latency. The technique that utilizes auxiliary calculations and rearranges the schedule to let the decoder start executions before it receives the whole data block will be introduced. It also can reduce the hardware for storing temporary calculation results. These substantial benefits let this method be applied to almost all practical designs. The last topic is about shortening the average processing time. By using well-designed criteria, the decoding flow can finish earlier than normal without causing performance loss. Our discussions will involve two of the simplest criteria, and the simulation results will prove their effectiveness.

## 1.1 Turbo Codes: Parallel Concatenated Convolutional Codes

### 1.1.1 Principles of Encoding and Decoding

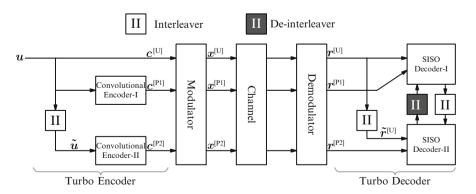

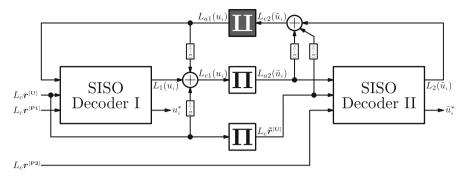

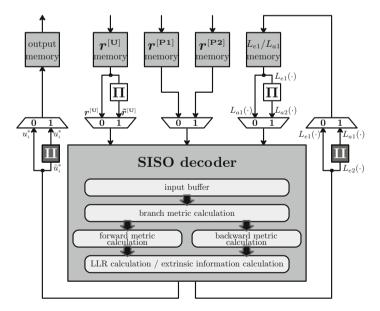

The classic turbo code is also known as the parallel concatenated convolutional code due to the special combination of two convolutional codes [5]. Figure 1.2 shows the typical framework, and its main characteristic is using interleavers in encoding and decoding procedures. The task of the interleaver is to permute its input sequence in a pseudo random way; while the de-interleaver can perform the inverse function to get the normal order back. In the turbo encoder, the interleaver is located between the two convolutional encoders. Thus, the first constituent encoder encodes the original information sequence u and get the first parity check  $c^{[P1]}$ , while the second one transforms reordered information sequence  $\tilde{\pmb{u}}$  into the second parity check  $c^{[P2]}$ . The codeword of turbo code is the concatenation of the first convolutional code (u and  $c^{[P1]}$ ) and the second convolutional code ( $\tilde{u}$  and  $c^{[P2]}$ ). Since  $\tilde{u}$  is just a permuted version of u, the turbo encoder will send only u rather than both of them to its output, and this copy of information sequence u is usually called the systematic data  $c^{[U]}$ . A complete codeword sequence of turbo code contains three parts:  $c^{[U]}$ ,  $c^{[P1]}$ , and  $c^{[P2]}$ . The modulator translates the codeword sequence into analog signals ( $x^{[U]}$ ,  $x^{[P1]}$ , and  $x^{[P2]}$ ) and then forward them to the channel. After the receiver gets these modulated signals, the demodulator produces the corresponding quantized data ( $r^{[U]}$ ,  $r^{[P1]}$ , and  $r^{[P2]}$ ) for the subsequent flows. Like encoder architecture, the turbo decoder contains two individual soft-in/soft-out (SISO) decoders, each of which deals with one constituent code. Based on the decoding algorithm for convolutional codes, the component decoder can calculate the probability of every information symbol. The first SISO decoder works with the first parity check part  $r^{[P1]}$  and the systematic part  $r^{[U]}$  to find the soft values of u, whereas the second SISO decoder processes the second parity check part  $r^{[P2]}$  and the interleaved systematic part  $\tilde{r}^{[U]}$  to derive

Fig. 1.2 Typical codec structure of the turbo code

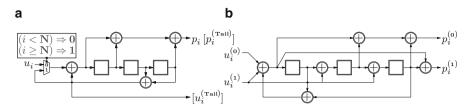

Fig. 1.3 Constituent convolutional encoders of turbo codes in advanced wireless communication systems. (a) In 3GPP LTE-Advanced standard. (b) In IEEE 802.16m standard

the soft values of  $\tilde{\boldsymbol{u}}$ . Thanks to the equivalence between  $\boldsymbol{u}$  and  $\tilde{\boldsymbol{u}}$ , the outputs of either constituent code can be treated as the *a priori* probability estimation for the other one. The interleaver and de-interleaver between the two SISO decoders can rearrange these messages in proper order. This procedure will be performed alternatively between the two constituent codes until certain criteria are satisfied. With the random-like properties of turbo code, this iterative decoding method can be very efficient.

### 1.1.2 Turbo Codes in Advanced Communication Systems

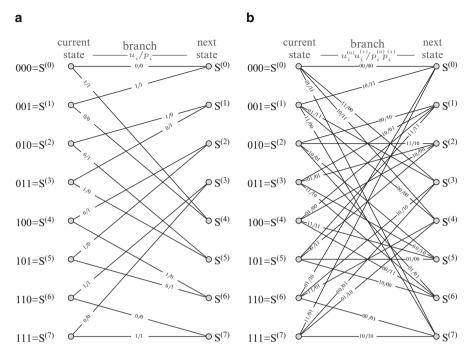

Both 3GPP LTE-Advanced standard [15] and IEEE 802.16m standard [17] adopt turbo code as one of their channel coding techniques. The constituent encoders in either standard are two identical recursive convolutional encoders, and their architecture is shown in Fig. 1.3, where each mainly constructs of three 1-bit memory cells and several XOR gates. As the information symbols  $(u_i \text{ or } u_i^{(0)} u_i^{(1)})$ are fed into the encoder, the data in the memory will be updated, and the code symbols  $(p_i \text{ or } p_i^{(0)} p_i^{(1)})$  will be produced. There are some rules of initializing and finalizing the encoding procedure by setting the memory cells. In Fig. 1.4, the state transition diagrams depict the operations of these convolutional encoders. Here the contents of the memory cells (from left to right) are regarded as the states, and either case involves eight states:  $S^{(0)} = 000$ ,  $S^{(1)} = 001$ ,  $S^{(2)} = 010$ ,  $S^{(3)} = 011$ ,  $S^{(4)} = 100, S^{(5)} = 101, S^{(6)} = 110$  and  $S^{(7)} = 111$ . These branches that indicate the possible changes in states are labeled with their respective input/output patterns  $(u_i/p_i \text{ or } u_i^{(0)}u_i^{(1)}/p_i^{(0)}p_i^{(1)})$ . By serially connecting the state diagrams of successive input symbols, we can further obtain the trellis diagram. The encoding procedure of the constituent code can correspond to a unique trellis path on this diagram. Such a graphical representation also serves as a basis for the decoding procedure. Besides the realization of encoder, the turbo code construction requires the input block size N, the code rate R, and the interleaving rules. The specifications for the two applications state these requisite data in detail.

In 3GPP LTE-Advanced standard, the constituent encoder in Fig. 1.3a deals with one information bit  $u_i$  and outputs one parity check bit  $p_i$  per unit time. The initial values of all memory cells are zeroes. After inputting the last information bit  $u_{N-1}$ , we change the selection signal of the multiplexer to force the input to the leftmost

Fig. 1.4 State transition diagrams for the encoders in Fig. 1.3. (a) State transitions for Fig. 1.3a. (b) State transitions for Fig. 1.3b

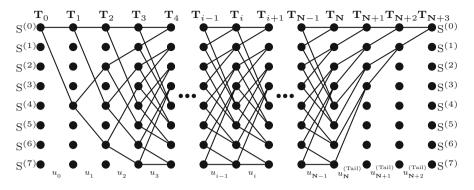

memory cell to zero. The corresponding trellis diagram is given in Fig. 1.5, where the state at the initial trellis stage  $\mathbf{T}_0$  and the state at the last trellis stage  $\mathbf{T}_{N+3}$  are both all-zero state  $S^{(0)}$ . This termination step will take three more ticks to reset these memory cells and result in six extra tail bits. Hence, for every size- $\mathbf{N}$  information block  $[u_0, u_1, \ldots, u_{N-1}]$ , the corresponding parity check sequence of one constituent code includes  $[p_0, p_1, \ldots, p_{N-1}]$  and  $[u_N^{\text{(Tail)}}, p_N^{\text{(Tail)}}, u_{N+1}^{\text{(Tail)}}, p_{N+1}^{\text{(Tail)}}, u_{N+2}^{\text{(Tail)}}]$ . Since the two constituent encoders will generate  $(2\mathbf{N}+12)$  parity check bits in total, the code rate  $\mathbf{R}$  of this turbo code is equal to  $\mathbf{N}/(3\mathbf{N}+12)$ . This specification defines 188 block sizes, ranging from 40 to 6144, and these  $\mathbf{N}$ 's can be summarized as follows:

$$\mathbf{N} = \begin{cases} 40 + \ 8 \times (\mathbb{k} - \ 0) & \text{for } \mathbb{k} = \ 0 \sim \ 58, \\ 512 + 16 \times (\mathbb{k} - \ 59) & \text{for } \mathbb{k} = \ 59 \sim \ 90, \\ 1024 + 32 \times (\mathbb{k} - \ 91) & \text{for } \mathbb{k} = \ 91 \sim 122, \\ 2048 + 64 \times (\mathbb{k} - 123) & \text{for } \mathbb{k} = 123 \sim 187. \end{cases}$$

Every information block  $[u_0, u_1, \ldots, u_{N-1}]$  will be reordered into  $[\tilde{u}_0, \tilde{u}_1, \ldots, \tilde{u}_{N-1}]$  by the quadratic permutation polynomial (QPP) interleaver [18]. The relationship between the two data blocks is  $\{\tilde{u}_i = u_{\mathcal{Q}(i)} \mid 0 \leq i, \mathcal{Q}(i) < \mathbf{N}\}$ , and their indexes  $(i \text{ and } \mathcal{Q}(i))$  satisfy

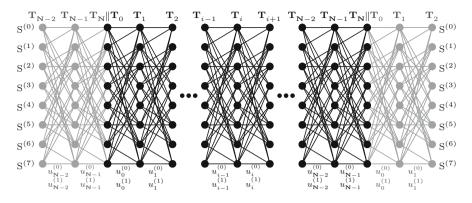

Fig. 1.5 The trellis diagram of constituent code in IEEE 802.16m standard

$$Q(i) = f_1 \times i + f_2 \times i^2 \pmod{\mathbf{N}},\tag{1.1}$$

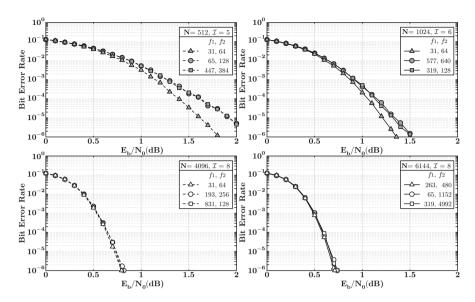

where the determination of  $f_1$  and  $f_2$  is related to **N** [18]. The turbo encoders and decoders for this standard must support 188 sets of (**N**,  $f_1$ ,  $f_2$ ). The parameters will share some characteristics. It is obvious that all **N**'s are multiples of 8. For each (**N**,  $f_1$ ,  $f_2$ ),  $f_1$  is an odd number and is relatively prime to **N**; while  $f_2$  is an even number. These common characteristics are useful for practical implementation.

In IEEE 802.16m standard, the constituent encoder in Fig. 1.3b is a double binary convolutional encoder whose every input symbol consists of two information bits  $(u_i^{(0)}, u_i^{(1)})$ . It can get two parity check bits  $(p_i^{(0)}, p_i^{(1)})$  per unit time. Note that block size N stands for the amount of input symbols, so there are 2N bits in an information block in this case. This constituent encoder utilizes the tail-biting technique to let the final contents of the memory cells agree with their initial contents [19]. The encoding procedure is divided into two steps: the pre-encoding and the actual encoding. At the first step, the memory cells are reset to zeroes, and then all information symbols are input. Based on the final contents of the memory cells at the pre-encoding step, we calculate the corresponding initial values for the succeeding step and encode the same information block again. Only the parity check bits generated at the actual encoding process are valid code symbols. This method makes the trellis diagram become a circular structure as Fig. 1.6, where the initial trellis stage  $T_0$  and the last trellis stage  $T_N$  are merged. For a size-N information block  $[(u_0^{(0)}, u_0^{(1)}), (u_1^{(0)}, u_1^{(1)}), \dots, (u_{N-1}^{(0)}, u_{N-1}^{(1)})]$ , the corresponding parity check sequence of one constituent code includes  $[(p_0^{(0)}, p_0^{(1)}), (p_1^{(0)}, p_1^{(1)}), \dots, (p_{N-1}^{(0)}, p_{N-1}^{(1)})]$ . Because the two constituent encoders will generate 4N parity check bits in total, the code rate R

Fig. 1.6 The trellis diagram of constituent code in 3GPP LTE-Advanced standard

of this turbo code is equal to 2N/6N (= 1/3). This specification defines 39 block sizes, ranging from 24 to 2400, and these N's are listed as follows:

In this turbo encoder, the interleaver first swaps the two component bits of each information symbol with odd-numbered index. This intra-symbol permutation results in  $[(u_0'^{(0)}, u_0'^{(1)}), (u_1'^{(0)}, u_1'^{(1)}), \dots, (u_{N-1}'^{(0)}, u_{N-1}'^{(1)})]$ , a permuted data block with the property:

$$\begin{cases} (u_i'^{(0)}, u_i'^{(1)}) = (u_i^{(1)}, u_i^{(0)}) & \text{if } i \mod 2 = 1, \\ (u_i'^{(0)}, u_i'^{(1)}) = (u_i^{(0)}, u_i^{(1)}) & \text{if } i \mod 2 = 0. \end{cases}$$

$$(1.2)$$

After the production of  $[(u_0'^{(0)}, u_0'^{(1)}), (u_1'^{(0)}, u_1'^{(1)}), \dots, (u_{N-1}'^{(0)}, u_{N-1}'^{(1)})]$ , there follows the almost regular permutation (ARP) interleaver [20] to further arrange this intermediate data block into  $[(\tilde{u}_0^{(0)}, \tilde{u}_0^{(1)}), (\tilde{u}_1^{(0)}, \tilde{u}_1^{(1)}), \dots, (\tilde{u}_{N-1}^{(0)}, \tilde{u}_{N-1}^{(1)})]$ . The symbols of these data blocks satisfy  $\{(\tilde{u}_i^{(0)}, \tilde{u}_i^{(1)}) = (u_{A(i)}'^{(0)}, u_{A(i)}'^{(1)}) \mid 0 \leq i, A(i) < \mathbb{N}\}$ , and the index A(i) is derived by (1.3).

$$\mathcal{A}(i) = \begin{cases} \varepsilon \times i + g_0 \pmod{\mathbf{N}} & \text{if } i \mod 4 = 0 \\ \varepsilon \times i + g_1 \pmod{\mathbf{N}} & \text{if } i \mod 4 = 1 \\ \varepsilon \times i + g_2 \pmod{\mathbf{N}} & \text{if } i \mod 4 = 2 \\ \varepsilon \times i + g_3 \pmod{\mathbf{N}} & \text{if } i \mod 4 = 3 \end{cases} \text{ and } \begin{cases} g_0 = 1 \\ g_1 = 1 + g_1' + \frac{\mathbf{N}}{2} \\ g_2 = 1 + g_2' \\ g_3 = 1 + g_3' + \frac{\mathbf{N}}{2} \end{cases}$$

(1.3)

For each **N**, there is a specific set of  $(\varepsilon, g'_1, g'_2, g'_3)$  in this standard. All of the 39 parameter sets also have some characteristics in common: every **N** is a multiple of 4;  $\varepsilon$  is an odd prime number; and the other three  $(g'_1, g'_2, g'_3)$  are even numbers.

### 1.2 Decoding Procedure of Turbo Decoders

The main idea of turbo decoding process is the message propagation between the two constituent codes. In the first paper of turbo code [5], the maximum *a posteriori* probability (MAP) algorithm [21] is applied to the SISO decoder for calculating the soft values of each component convolutional code. These outputs of one SISO decoder should undergo some modifications before being passed to the other one. For facilitating the computation, the expressions of some variables used in the decoding algorithms may vary slightly according to the codec structure. Hence, the decoding algorithms for the 3GPP LTE-Advanced turbo codes and for IEEE 802.16m turbo codes are presented separately. Our discussions in either part start with the MAP algorithm and then demonstrate the iterative decoding flow. During the derivation, we only consider the first constituent code or the sequence in original order; and it can be easily generalized to the other component by substitution of notations.

### 1.2.1 MAP Algorithm for 3GPP LTE-Advanced Turbo Code

Based on the received data and the trellis structure, the SISO decoder can use the MAP algorithm to get the probabilities of all information symbols. Every information block  $\mathbf{u} = [u_0, u_1, \ldots, u_{\mathbf{N}-1}]$  will be encoded into a parity check sequence  $\mathbf{p} = [p_0, p_1, \ldots, p_{\mathbf{N}-1}]$ . The constituent convolutional encoder will send out six more bits  $[u_{\mathbf{N}}^{(\mathrm{Tail})}, p_{\mathbf{N}}^{(\mathrm{Tail})}, u_{\mathbf{N}+1}^{(\mathrm{Tail})}, p_{\mathbf{N}+1}^{(\mathrm{Tail})}, u_{\mathbf{N}+2}^{(\mathrm{Tail})}]$  for trellis termination. These parts will make up the codeword block  $\mathbf{c} = [c_0, c_1, \ldots, c_{\mathbf{N}+2}]$ , where each symbol with the form  $c_i = (c_i^{(0)}, c_i^{(1)})$  is  $(u_i, p_i)$  for  $i = 0 \sim (\mathbf{N} - 1)$  and represents  $(u_i^{(\mathrm{Tail})}, p_i^{(\mathrm{Tail})})$  for  $i = \mathbf{N} \sim (\mathbf{N} + 2)$ . Since the binary phase shift keying (BPSK) modulation is applied, the code bits  $(c_i^{(0)}, c_i^{(1)})$  are translated into  $x_i = (x_i^{(0)}, x_i^{(1)})$ . The mapping between  $c_i^{(j)}$  and  $x_i^{(j)}$  for  $i = 0 \sim (\mathbf{N} + 2)$  and  $j = 0 \sim 1$  is given in (1.4); then we have a modulated signal sequence  $\mathbf{x} = [x_0, x_1, \ldots, x_{\mathbf{N}+2}]$ .

$$x_i^{(j)} = 1 - 2 \times c_i^{(j)} = \begin{cases} +1 & \text{if } c_i^{(j)} = 0\\ -1 & \text{if } c_i^{(j)} = 1 \end{cases}$$

(1.4)

The data received from the channel are denoted by  $\mathbf{r} = [r_0, r_1, \dots, r_{N+2}]$  with  $r_i = (r_i^{(0)}, r_i^{(1)})$ . Under the assumption of additive white Gaussian noise (AWGN) channel, each  $r_i^{(j)}$  can be viewed as the summation of the modulated signal  $x_i^{(j)}$  and the zero-mean white Gaussian noise  $n_i^{(j)}$  with variance  $\sigma^2$ .

$$r_i^{(j)} = x_i^{(j)} + n_i^{(j)} (1.5)$$

The value of  $\sigma$  is determined by the bit signal-to-noise ratio (SNR), usually termed  $E_b/N_0$ . Given a transmitted codeword block x, the probability of r can be expressed as

$$\Pr\left(r_{0}, \dots, r_{N+2} \mid x_{0}, \dots, x_{N+2}\right) \triangleq \prod_{i=0}^{N+2} \Pr\left(r_{i}^{(0)}, r_{i}^{(1)} \mid x_{i}^{(0)}, x_{i}^{(1)}\right), \tag{1.6}$$

where

$$\Pr\left(r_i^{(0)}, r_i^{(1)} \mid x_i^{(0)}, x_i^{(1)}\right) \triangleq \prod_{j=0}^{1} \Pr\left(r_i^{(j)} \mid x_i^{(j)}\right)$$

(1.7)

and

$$\Pr\left(r_i^{(j)} \mid x_i^{(j)}\right) \triangleq \frac{1}{\sqrt{2\pi}\sigma} \exp\left(-\frac{1}{2\sigma^2} \left(r_i^{(j)} - x_i^{(j)}\right)^2\right). \tag{1.8}$$

These probabilities provide the foundation for deriving the likelihood of each information bit.

The practical SISO decoder only has the knowledge about the received data sequence  $\mathbf{r}$ , so it will calculate the *a posteriori* probability (APP) of  $u_i$  as

$$\Pr(u_i \mid r_0, \dots, r_{N+2}), i = 0 \sim N - 1.$$

(1.9)

With the mapping in (1.4) and  $u_i = c_i^{(0)}$  for  $i = 0 \sim (N-1)$ , this probability is equivalent to the APP of  $x_i^{(0)}$ , and the set of possible values becomes from  $u_i \in \{0, 1\}$  to  $x_i^{(0)} \in \{+1, -1\}$ . The SISO decoder will compare the APPs relating to  $u_i = 0$  and  $u_i = 1$  to make the decision on the i-th information bit. If  $\Pr(u_i = 0 \mid r_0, \dots, r_{N+2})$  is larger than or equal to  $\Pr(u_i = 1 \mid r_0, \dots, r_{N+2})$ , the decision is 0; otherwise, the decision is 1. The log-likelihood ratio (LLR) in (1.10) is commonly used for the computation.

$$L(u_i) \stackrel{\triangle}{=} \ln \frac{\Pr(u_i = 0 \mid r_0, \dots, r_{N+2})}{\Pr(u_i = 1 \mid r_0, \dots, r_{N+2})}$$

(1.10)

The hard decision  $u_i^*$  depends on the sign of  $L(u_i)$ :

$$u_i^* = \begin{cases} 0 & \text{if } L(u_i) \ge 0, \\ 1 & \text{if } L(u_i) < 0. \end{cases}$$

(1.11)

We can derive the LLR as (1.12) by the characteristic of conditional probability.

$$L(u_{i}) = \ln \frac{\Pr(u_{i} = 0; r_{0}, \dots, r_{N+2}) / \Pr(r_{0}, \dots, r_{N+2})}{\Pr(u_{i} = 1; r_{0}, \dots, r_{N+2}) / \Pr(r_{0}, \dots, r_{N+2})}$$

$$= \ln \frac{\Pr(u_{i} = 0; r_{0}, \dots, r_{N+2})}{\Pr(u_{i} = 1; r_{0}, \dots, r_{N+2})}$$

(1.12)

Since  $u_i = 0$  and  $u_i = 1$  correspond to certain state transitions between the *i*-th trellis stage  $\mathbf{T}_i$  and the (i + 1)-th trellis stage  $\mathbf{T}_{i+1}$ , the probability of  $u_i$  can be written as

$$\Pr(u_i) = \sum_{(S_i, S_{i+1})} \Pr(u_i; S_i, S_{i+1}) = \sum_{(u_i; S_i, S_{i+1})} \Pr(S_i, S_{i+1}),$$

(1.13)

where  $S_i$  and  $S_{i+1}$  represent one of the eight states ( $S^{(0)} \sim S^{(7)}$ ) at  $\mathbf{T}_i$  and  $\mathbf{T}_{i+1}$  respectively; and ( $S_i$ ,  $S_{i+1}$ ) is the transition from  $S_i$  to  $S_{i+1}$ . The equation causes a modification to the LLR in (1.12):

$$L(u_{i}) = \ln \frac{\sum_{(S_{i}, S_{i+1})} \Pr(u_{i} = 0; S_{i}, S_{i+1}; r_{0}, \dots, r_{N+2})}{\sum_{(S_{i}, S_{i+1})} \Pr(u_{i} = 1; S_{i}, S_{i+1}; r_{0}, \dots, r_{N+2})}$$

$$= \ln \frac{\sum_{(u_{i} = 0; S_{i}, S_{i+1})} \Pr(S_{i}, S_{i+1}; r_{0}, \dots, r_{N+2})}{\sum_{(u_{i} = 1; S_{i}, S_{i+1})} \Pr(S_{i}, S_{i+1}; r_{0}, \dots, r_{N+2})}.$$

(1.14)

The LLR calculation involves the joint probability  $Pr(S_i, S_{i+1}; r_0, \dots, r_{N+2})$ . Note that this probability will be zero as there is no branch linking  $S_i$  and  $S_{i+1}$ . It can be decomposed as (1.15) with Bayes' law.

$$\Pr(S_{i}, S_{i+1}; r_{0}, \dots, r_{N+2}) = \Pr(S_{i}; r_{0}, \dots, r_{i-1}) \times \Pr(S_{i+1}; r_{i} \mid S_{i}; r_{0}, \dots, r_{i-1}) \times \Pr(r_{i+1}, \dots, r_{N+2} \mid S_{i}, S_{i+1}; r_{0}, \dots, r_{i})$$

(1.15)

We can simplify the two conditional probabilities in (1.15) by removing the redundant conditions. For  $Pr(S_{i+1}; r_i \mid S_i; r_0, \ldots, r_{i-1})$ , when  $S_i$  is given, the transition to  $S_{i+1}$  with  $r_i$  is independent of previous data  $(r_0, \ldots, r_{i-1})$ . Similarly, the event  $(r_{i+1}, \ldots, r_{N+2})$  of the last conditional probability are affected by  $S_{i+1}$  only. The removal of unnecessary conditions results in (1.16) and (1.17).

$$\Pr(S_{i+1}; r_i \mid S_i; r_0, \dots, r_{i-1}) = \Pr(S_{i+1}; r_i \mid S_i)$$

(1.16)

$$\Pr(r_{i+1}, \dots, r_{N+2} \mid S_i, S_{i+1}; r_0, \dots, r_i) = \Pr(r_{i+1}, \dots, r_{N+2} \mid S_{i+1})$$

(1.17)

Then the factorization of Pr  $(S_i, S_{i+1}; r_0, \dots, r_{N+2})$  becomes

$$\Pr(S_i; r_0, \dots, r_{i-1}) \times \Pr(S_{i+1}; r_i \mid S_i) \times \Pr(r_{i+1}, \dots, r_{N+2} \mid S_{i+1}).$$

(1.18)

Now we define the logarithmic version of the three probabilities as (1.19), (1.20), and (1.21).

$$\alpha(S_i) \triangleq \ln \Pr(S_i; r_0, \dots, r_{i-1}) \tag{1.19}$$

$$\gamma(S_i, S_{i+1}) \triangleq \ln \Pr(S_{i+1}; r_i \mid S_i)$$

(1.20)

$$\beta(S_i) \triangleq \ln \Pr(r_i, \dots, r_{N+2} \mid S_i)$$

(1.21)

Thus, (1.18) can be expressed with these notations:

$$\Pr(S_i, S_{i+1}; r_0, \dots, r_{N+2}) = \exp(\alpha(S_i)) \times \exp(\gamma(S_i, S_{i+1})) \times \exp(\beta(S_{i+1})).$$

(1.22)

By substituting (1.22) for the APPs in (1.14), the LLR will be changed into

$$L(u_{i}) = \ln \left[ \sum_{(u_{i}=0;S_{i},S_{i+1})} \exp \left( \alpha(S_{i}) + \gamma(S_{i},S_{i+1}) + \beta(S_{i+1}) \right) \right]$$

$$- \ln \left[ \sum_{(u_{i}=1;S_{i},S_{i+1})} \exp \left( \alpha(S_{i}) + \gamma(S_{i},S_{i+1}) + \beta(S_{i+1}) \right) \right]. (1.23)$$

Such a expression suggests that the SISO decoder should find out  $\alpha(S_i)$ ,  $\beta(S_{i+1})$ , and  $\gamma(S_i, S_{i+1})$  first.

In the MAP algorithm, there are efficient ways to compute (1.19)–(1.21). The  $\alpha(S_i)$  can be obtained alternatively from its original definition:

$$\exp(\alpha(S_{i})) = \Pr(S_{i}; r_{0}, \dots, r_{i-1})$$

$$= \sum_{S_{i-1}} \Pr(S_{i-1}, S_{i}; r_{0}, \dots, r_{i-1})$$

$$= \sum_{S_{i-1}} \Pr(S_{i-1}; r_{0}, \dots, r_{i-2}) \times \Pr(S_{i}; r_{i-1} \mid S_{i-1}; r_{0}, \dots, r_{i-2})$$

$$= \sum_{S_{i-1}} \Pr(S_{i-1}; r_{0}, \dots, r_{i-2}) \times \Pr(S_{i}; r_{i-1} \mid S_{i-1})$$

$$= \sum_{S_{i-1}} \exp(\alpha(S_{i-1})) \times \exp(\gamma(S_{i-1}, S_{i})). \tag{1.24}$$

The subsequent flow is taking the natural logarithm on both sides in (1.24).

$$\alpha(S_i) = \ln \sum_{S_{i-1}} \exp \left( \alpha(S_{i-1}) + \gamma(S_{i-1}, S_i) \right)$$

(1.25)

In the above equation, it just requires  $\alpha(S_{i-1})$  and  $\gamma(S_{i-1}, S_i)$  to compute  $\alpha(S_i)$ . This calculation is a recursive process from i = 0 to  $i = \mathbb{N} + 3$ ; hence,  $\alpha(S_i)$  is also named the *forward metric*. It needs an appropriate initial value  $\alpha(S_0)$ .

From Fig. 1.5, the trellis for the constituent code starts at  $S^{(0)}$ . The condition implies that  $Pr(S_0 = S^{(0)}) = 1$  and  $Pr(S_0 \neq S^{(0)}) = 0$ . Here we make use of (1.19) again and get

$$\alpha(S_0) = \begin{cases} 0 & \text{if } S_0 = S^{(0)}, \\ -\infty & \text{if } S_0 \neq S^{(0)}. \end{cases}$$

(1.26)

The derivation of  $\beta(S_i)$  is much the same as that of  $\alpha(S_i)$ . The first step is

$$\exp(\beta(S_{i})) = \Pr(r_{i}, \dots, r_{N+2} \mid S_{i})$$

$$= \sum_{S_{i+1}} \Pr(S_{i+1}; r_{i}, \dots, r_{N+2} \mid S_{i})$$

$$= \sum_{S_{i+1}} \Pr(S_{i+1}; r_{i} \mid S_{i}) \times \Pr(r_{i+1}, \dots, r_{N+2} \mid S_{i}, S_{i+1}; r_{i})$$

$$= \sum_{S_{i+1}} \Pr(S_{i+1}; r_{i} \mid S_{i}) \times \Pr(r_{i+1}, \dots, r_{N+2} \mid S_{i+1})$$

$$= \sum_{S_{i+1}} \exp(\gamma(S_{i}, S_{i+1})) \times \exp(\beta(S_{i+1})). \tag{1.27}$$

After the computation of natural logarithm, (1.27) changes to

$$\beta(S_i) = \ln \sum_{S_{i+1}} \exp \left( \gamma(S_i, S_{i+1}) + \beta(S_{i+1}) \right). \tag{1.28}$$

The calculation of  $\beta(S_i)$  needs both  $\beta(S_{i+1})$  and  $\gamma(S_i, S_{i+1})$ , and it is performed recursively in descending order; so we call  $\beta(S_i)$  the *backward metric*. The trellis diagram in Fig. 1.5 whose the last state  $S_{N+3}$  is  $S^{(0)}$  indicates the initialization:

$$\beta(S_{N+3}) = \begin{cases} 0 & \text{if } S_{N+3} = S^{(0)}, \\ -\infty & \text{if } S_{N+3} \neq S^{(0)}. \end{cases}$$

(1.29)

Furthermore, the  $\gamma(S_i, S_{i+1})$  in (1.20) can be

$$\exp(\gamma(S_{i}, S_{i+1})) = \Pr(S_{i+1}; r_{i} | S_{i})$$

$$= \frac{\Pr(S_{i}, S_{i+1}; r_{i})}{\Pr(S_{i})}$$

$$= \frac{\Pr(S_{i}, S_{i+1})}{\Pr(S_{i})} \times \frac{\Pr(S_{i}, S_{i+1}; r_{i})}{\Pr(S_{i}, S_{i+1})}$$

$$= \Pr(S_{i+1} | S_{i}) \times \Pr(r_{i} | S_{i}, S_{i+1})$$

$$= \Pr(u_{i}) \times \Pr(r_{i} | x_{i}). \tag{1.30}$$

The relationship among  $u_i$ ,  $c_i^{(0)}$ , and  $x_i^{(0)}$  promises that we can interchange  $Pr(u_i)$  with  $Pr(x_i^{(0)})$ . To find the  $Pr(u_i)$ , we need the *a priori* information with the definition as

$$L_a(u_i) \stackrel{\triangle}{=} \ln \frac{\Pr(u_i = 0)}{\Pr(u_i = 1)} = L_a(x_i^{(0)}) \stackrel{\triangle}{=} \ln \frac{\Pr(x_i^{(0)} = +1)}{\Pr(x_i^{(0)} = -1)}.$$

(1.31)

The  $L_a(x_i^{(0)})$  is utilized to calculate the *a priori* probability  $Pr(x_i^{(0)})$ :

$$\Pr\left(x_{i}^{(0)} = \pm 1\right) = \frac{\exp\left(\pm L_{a}(x_{i}^{(0)})\right)}{1 + \exp\left(\pm L_{a}(x_{i}^{(0)})\right)}$$

$$= \underbrace{\left[\frac{\exp\left(-L_{a}(x_{i}^{(0)})/2\right)}{1 + \exp\left(-L_{a}(x_{i}^{(0)})\right)}\right]}_{\vartheta_{i}} \times \exp\left(x_{i}^{(0)} \times L_{a}(x_{i}^{(0)})/2\right)$$

$$= \vartheta_{i} \times \exp\left(x_{i}^{(0)} \times L_{a}(x_{i}^{(0)})/2\right), \tag{1.32}$$

where  $\vartheta_i$  depends only on  $L_a(x_i^{(0)})$  and remains constant for either  $x_i^{(0)} = +1$  or  $x_i^{(0)} = -1$ . Based on (1.7) and (1.8), the Pr  $(r_i \mid x_i)$  can be modified to

$$\Pr(r_{i} \mid x_{i}) = \prod_{j=0}^{1} \left[ \frac{1}{\sqrt{2\pi} \sigma} \exp\left(-\frac{1}{2\sigma^{2}} (r_{i}^{(j)} - x_{i}^{(j)})^{2}\right) \right]$$

$$= \underbrace{\left(\frac{1}{\sqrt{2\pi} \sigma}\right)^{2} \times \exp\left(-\frac{1}{2\sigma^{2}} \sum_{j=0}^{1} \left[ (r_{i}^{(j)})^{2} + (x_{i}^{(j)})^{2} \right] \right)}_{\varphi_{i}}$$

$$\times \exp\left(\frac{1}{\sigma^{2}} \sum_{j=0}^{1} \left[ r_{i}^{(j)} \times x_{i}^{(j)} \right] \right)$$

$$= \varphi_{i} \times \exp\left(\frac{1}{2} L_{c} \sum_{i=0}^{1} \left[ r_{i}^{(j)} \times x_{i}^{(j)} \right] \right). \tag{1.33}$$

For all possible combinations of  $(x_i^{(0)}, x_i^{(1)})$ ,  $r_i^{(j)}$  is the same, and the square of  $x_i^{(j)}$  is 1; so  $\varphi_i$  will be a constant. In addition, the channel reliability value  $L_c$  whose value is  $2/\sigma^2$  is introduced in (1.33). It will equal to  $4\mathbf{RE_b}/\mathbf{N_0}$  in the AWGN channel [22]. With (1.32) and (1.33), we can rewritten (1.30) as

$$\gamma'(S_i, S_{i+1}) = \ln \vartheta_i + \ln \varphi_i + \frac{1}{2} x_i^{(j)} \times L_a(x_i^{(j)}) + \frac{1}{2} L_c \sum_{i=0}^{1} \left[ r_i^{(j)} \times x_i^{(j)} \right]. \quad (1.34)$$

Both  $\vartheta_i$  and  $\varphi_i$  will be canceled out in the LLR calculation in (1.23). For this reason, we drop out  $\vartheta_i$  and  $\varphi_i$  in advance and define  $\gamma(S_i, S_{i+1})$ , also known as the *branch metric*, in (1.35).

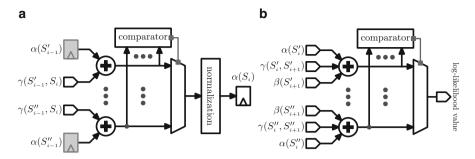

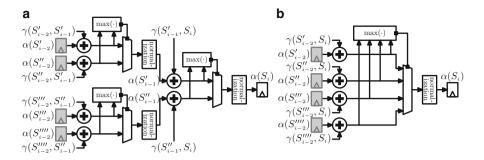

Fig. 1.7 Forward metric calculation and backward metric calculation. (a) Recursive  $\alpha(S_i)$  computation. (b) Recursive  $\beta(S_i)$  computation

$$\gamma(S_i, S_{i+1}) = \frac{1}{2} x_i^{(j)} L_a(x_i^{(j)}) + \frac{1}{2} L_c \sum_{j=0}^{1} \left[ r_i^{(j)} \times x_i^{(j)} \right]$$

(1.35)

Consequently, the SISO decoder exploits the MAP algorithm over (N+3) received codeword symbols to get the probabilities of N information bits. The initial conditions of this component convolutional code are  $\alpha(S_0)$  and  $\beta(S_{N+3})$ . After receiving  $r_i$ , the decoder can derive  $\gamma(S_i, S_{i+1})$  of each branch between trellis stages  $T_i$  and  $T_{i+1}$ . Then the decoder uses these branch metrics to calculate forward metrics and backward metrics in a recursive way. Figure 1.7 is the graphical description of these computations. In this case, every state  $S_i$  at  $T_i$  has exactly two incoming branches connecting to two different states  $(S'_{i-1}$  and  $S''_{i-1})$  at  $T_{i-1}$  and has exactly two outgoing branches connecting to two different states  $(S'_{i+1}$  and  $S''_{i+1})$  at  $T_{i+1}$ . As  $\alpha(S_i)$  and  $\beta(S_{i+1})$  are available, the  $L(u_i)$  and decision  $u_i^*$  can be further determined.

### 1.2.2 Iterative Flow for 3GPP LTE-Advanced Turbo Code

Like the MAP algorithm, the discussion about the iterative decoding flow relies heavily on the APP of the i-th information bit  $u_i$ . Instead of the definition in (1.9), we take the Pr  $(u_i; r_0, \ldots, r_{N+2})$  into account here, for both them can result in the same LLR as (1.12). By applying Bayes' law, the joint probability can be factorized into (1.36).

$$\Pr(u_{i}; \mathbf{r}) = \sum_{\mathbf{u}:u_{i}} \Pr(u_{0}, \dots, u_{N-1}; r_{0}^{(0)}, r_{0}^{(1)}, \dots, r_{N+2}^{(0)}, r_{N+2}^{(1)})$$

$$= \sum_{\mathbf{u}:u_{i}} \left[ \Pr(u_{0}, \dots, u_{N-1}) \times \Pr(r_{0}^{(0)}, \dots, r_{N+2}^{(0)} \mid u_{0}, \dots, u_{N-1}) \times \Pr(r_{0}^{(1)}, \dots, r_{N+2}^{(1)} \mid u_{0}, \dots, u_{N-1}; r_{0}^{(0)}, \dots, r_{N+2}^{(0)}) \right]$$

$$\times \Pr(r_{0}^{(1)}, \dots, r_{N+2}^{(1)} \mid u_{0}, \dots, u_{N-1}; r_{0}^{(0)}, \dots, r_{N+2}^{(0)})$$

$$(1.36)$$

Since the constituent encoder generates an unique modulated codeword sequence  $[x_0^{(0)}, x_0^{(1)}, \dots, x_{N+2}^{(0)}, x_{N+2}^{(1)}]$  from every information block  $[u_0, \dots, u_{N-1}]$ , this one-to-one mapping allows for the interchangeability in (1.37)–(1.39).

$$\Pr(u_0, \dots, u_{N-1}) = \Pr(x_0^{(0)}, \dots, x_{N-1}^{(0)})$$

(1.37)

=

$$\Pr\left(x_0^{(0)}, \dots, x_{N-1}^{(0)}, x_N^{(0)}, x_{N+1}^{(0)}, x_{N+2}^{(0)}\right)$$

(1.38)

=

$$\Pr\left(x_0^{(0)}, \dots, x_{N+2}^{(0)}; x_0^{(1)}, \dots, x_{N+2}^{(1)}\right)$$

(1.39)

With the relations of equality, we can modify the  $Pr(u_i; r)$  from (1.36) to

$$\Pr(u_{i}; r) = \sum_{u:u_{i}} \left[ \Pr(x_{0}^{(0)}, \dots, x_{N+2}^{(0)}) \times \Pr(r_{0}^{(0)}, \dots, r_{N+2}^{(0)} \mid x_{0}^{(0)}, \dots, x_{N+2}^{(0)}) \right]$$

$$\times \Pr(r_{0}^{(1)}, \dots, r_{N+2}^{(1)} \mid x_{0}^{(0)}, \dots, x_{N+2}^{(0)}; x_{0}^{(1)}, \dots, x_{N+2}^{(1)}; r_{0}^{(0)}, \dots, r_{N+2}^{(0)}) \right]$$

$$= \sum_{u:u_{i}} \left[ \Pr(x_{0}^{(0)}, \dots, x_{N+2}^{(0)}) \times \Pr(r_{0}^{(0)}, \dots, r_{N+2}^{(0)} \mid x_{0}^{(0)}, \dots, x_{N+2}^{(0)}) \right]$$

$$\times \Pr(r_{0}^{(1)}, \dots, r_{N+2}^{(1)} \mid x_{0}^{(1)}, \dots, x_{N+2}^{(1)}) \right],$$

$$(1.40)$$

where the probability about  $[r_0^{(1)},\ldots,r_{N+2}^{(1)}]$  ignores the conditions  $[x_0^{(0)},\ldots,x_{N+2}^{(0)}]$  and  $[r_0^{(0)},\ldots,r_{N+2}^{(0)}]$  while  $[x_0^{(1)},\ldots,x_{N+2}^{(1)}]$  is given. For the discrete memoryless channel, (1.41) is another expression of  $\Pr(u_i;r)$ . In (1.42), the probabilities directly relating to  $u_i,x_i^{(0)}$ , and  $r_i^{(0)}$  bit are taken out; and the rest excludes the i-th systematic data.

$$\Pr(u_{i}; \mathbf{r}) = \sum_{u:u_{i}} \left[ \prod_{j=0}^{N+2} \Pr(x_{j}^{(0)}) \times \Pr(r_{j}^{(0)} \mid x_{j}^{(0)}) \times \Pr(r_{j}^{(1)} \mid x_{j}^{(1)}) \right]$$

$$= \Pr(x_{i}^{(0)}) \times \Pr(r_{i}^{(0)} \mid x_{i}^{(0)})$$

$$\times \sum_{u:u_{i}} \left[ \prod_{\substack{j=0\\j\neq i}}^{N+2} \Pr(x_{j}^{(0)}) \times \Pr(r_{j}^{(0)} \mid x_{j}^{(0)}) \times \prod_{l=0}^{N+2} \Pr(r_{l}^{(1)} \mid x_{l}^{(1)}) \right]$$

$$(1.41)$$

Now we substitute (1.42) for the probabilities in (1.12) and then derive the LLR of i-th information bit as (1.43), where the last term is called the extrinsic information  $L_e(u_i)$ .

$$L(u_{i}) = \ln \frac{\Pr(u_{i} = 0; \mathbf{r})}{\Pr(u_{i} = 1; \mathbf{r})}$$

$$= \ln \frac{\Pr(x_{i}^{(0)} = +1)}{\Pr(x_{i}^{(0)} = -1)} + \ln \frac{\Pr(r_{i}^{(0)} \mid x_{i}^{(0)} = +1)}{\Pr(r_{i}^{(0)} \mid x_{i}^{(0)} = -1)}$$

$$= \frac{\sum_{\substack{u:u_{i}=0}} \left[ \prod_{\substack{j=0\\j\neq i}}^{N+2} \Pr(x_{j}^{(0)}) \times \Pr(r_{j}^{(0)} \mid x_{j}^{(0)}) \times \prod_{l=0}^{N+2} \Pr(r_{l}^{(1)} \mid x_{l}^{(1)}) \right]}{\prod_{\substack{u:u_{i}=1}} \left[ \prod_{\substack{j=0\\j\neq i}}^{N+2} \Pr(x_{j}^{(0)}) \times \Pr(r_{j}^{(0)} \mid x_{j}^{(0)}) \times \prod_{l=0}^{N+2} \Pr(r_{l}^{(1)} \mid x_{l}^{(1)}) \right]}$$

$$= \frac{\sum_{\substack{u:u_{i}=1}} \left[ \prod_{\substack{j=0\\j\neq i}}^{N+2} \Pr(x_{j}^{(0)}) \times \Pr(r_{j}^{(0)} \mid x_{j}^{(0)}) \times \prod_{l=0}^{N+2} \Pr(r_{l}^{(1)} \mid x_{l}^{(1)}) \right]}{\sum_{\substack{u:u_{i}=1}} \left[ \prod_{\substack{j=0\\j\neq i}}^{N+2} \Pr(x_{j}^{(0)}) \times \Pr(r_{j}^{(0)} \mid x_{j}^{(0)}) \times \prod_{l=0}^{N+2} \Pr(r_{l}^{(1)} \mid x_{l}^{(1)}) \right]}$$

$$= \frac{\sum_{\substack{u:u_{i}=1}} \left[ \prod_{\substack{j=0\\j\neq i}}^{N+2} \Pr(x_{j}^{(0)}) \times \Pr(r_{j}^{(0)} \mid x_{j}^{(0)}) \times \prod_{l=0}^{N+2} \Pr(r_{l}^{(1)} \mid x_{l}^{(1)}) \right]}{\sum_{\substack{u:u_{i}=1}} \left[ \prod_{\substack{j=0\\j\neq i}}^{N+2} \Pr(x_{j}^{(0)}) \times \Pr(r_{j}^{(0)} \mid x_{j}^{(0)}) \times \prod_{l=0}^{N+2} \Pr(r_{l}^{(1)} \mid x_{l}^{(1)}) \right]} \right]}$$

$$= \frac{1}{\sum_{\substack{u:u_{i}=1}} \left[ \prod_{\substack{j=0\\j\neq i}}^{N+2} \Pr(x_{j}^{(0)}) \times \Pr(r_{j}^{(0)} \mid x_{j}^{(0)}) \times \prod_{l=0}^{N+2} \Pr(r_{l}^{(1)} \mid x_{l}^{(1)}) \right]} \right]}$$

The first term in (1.43) is  $L_a(u_i)$  in (1.31); the second term can also be written as (1.44) by the definition in (1.8) and  $L_c = 2/\sigma^2$ .

$$\ln \frac{\Pr\left(r_{i}^{(0)} \mid x_{i}^{(0)} = +1\right)}{\Pr\left(r_{i}^{(0)} \mid x_{i}^{(0)} = -1\right)} = \ln \frac{\frac{1}{\sqrt{2\pi}\sigma} \times \exp\left(-\frac{1}{2\sigma^{2}}(r_{i}^{(0)} - 1)^{2}\right)}{\frac{1}{\sqrt{2\pi}\sigma} \times \exp\left(-\frac{1}{2\sigma^{2}}(r_{i}^{(0)} + 1)^{2}\right)}$$

$$= \frac{1}{2\sigma^{2}} \times \left[(r_{i}^{(0)} + 1)^{2} - (r_{i}^{(0)} - 1)^{2}\right]$$

$$= \frac{2}{\sigma^{2}} \times r_{i}^{(0)} = L_{c} \times r_{i}^{(0)}$$

(1.44)

As a result,  $L(u_i)$  is regarded as the summation of *a priori* probability, the weighted received data, and the extrinsic information:

$$L(u_i) = L_a(u_i) + L_c \times r_i^{(0)} + L_e(u_i). \tag{1.45}$$

Figure 1.8 shows the detailed decoding procedure for passing soft values from one SISO decoder to the other. The SISO decoders can update useful estimation about every information bit  $u_i$  with the applications of (1.23) and (1.45). In general, the first SISO decoder performs the MAP algorithm on the systematic part and first parity check part to compute all necessary metrics. We assume that  $\Pr(u_i = 0)$  and  $\Pr(u_i = 1)$  are both 1/2; thus, the *a priori* value  $L_{a1}(u_i)$  which is involved in the  $\gamma(S_i, S_{i+1})$  calculation is initialized with 0. This SISO decoder will output  $L_1(u_i)$ , the LLR of the *i*-th information bit. From (1.45), the corresponding extrinsic information  $L_{e1}(u_i)$  can be obtained by

$$L_{e1}(u_i) = L_1(u_i) - L_c \times r_i^{(0)} - L_{a1}(u_i). \tag{1.46}$$

Since  $L_{e1}(u_i)$  is derived from the whole codeword except the i-th systematic data, it can provide newer information than the probabilities calculated from  $r_i^{(0)}$  and  $L_{a1}(u_i)$  directly. We use  $L_{e1}(u_i)$  as an estimate for the *a priori* value of the other constituent code. The second SISO decoder also does the trellis-based decoding

Fig. 1.8 The propagation of soft values in the iterative decoding flow

procedure with  $\tilde{r}^{[U]}$ ,  $r^{[P2]}$ , and  $L_{a2}(\tilde{u}_i)$ . Then it evaluates  $L_2(\tilde{u}_i)$ , the LLR for the permuted information sequence, and it further gets the extrinsic information  $L_{e2}(\tilde{u}_i)$  of the second constituent code by

$$L_{e2}(\tilde{u}_i) = L_2(\tilde{u}_i) - L_c \times \tilde{r}_i^{(0)} - L_{a2}(\tilde{u}_i). \tag{1.47}$$

The  $L_{e2}(\tilde{u}_i)$  is passed back to the first SISO decoder. A de-interleaver rearranges the sequence order so that  $L_{e2}(\tilde{u}_i)$  can be the a priori value  $L_{a1}(u_{\phi(i)})$  for the first constituent code. After updating the  $L_{a1}(u_i)$  for  $i=0 \sim (N-1)$ , the first SISO decoder performs the MAP algorithm again. Such soft value calculation of each constituent code is named as a half-iteration, and two successive processes form one complete iteration. Usually, we will set a maximum iteration number  $\mathcal{I}$  as the conventional stopping criterion. At the last half-iteration, the decoder makes hard decisions from the LLRs by (1.11). Note that the tail bits of both constituent codes are excluded in the message propagation; their probabilities remain the same throughout the iterative flow, and we only need to calculate the corresponding metrics once. Because the correlation between APP estimations and received data will become stronger after every half-iteration, the benefit of extrinsic information diminishes gradually. This phenomenon leads to very small enhancement in performance when the decoding flow has proceeded repeatedly for certain iterations. Hence, the determination of  $\mathcal{I}$  depends on the trade-off between performance requirement and processing time.

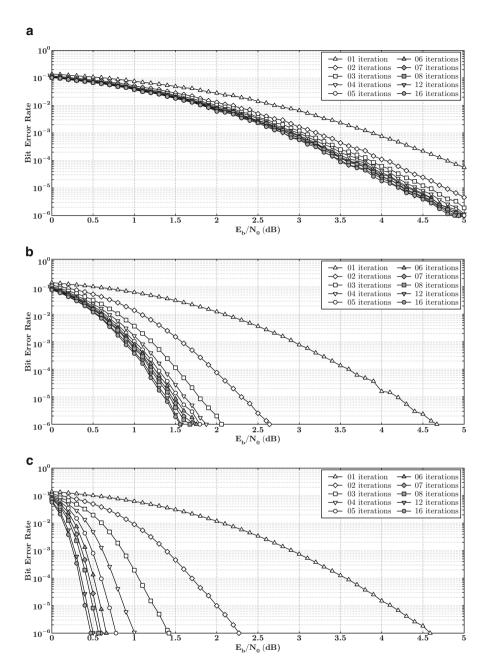

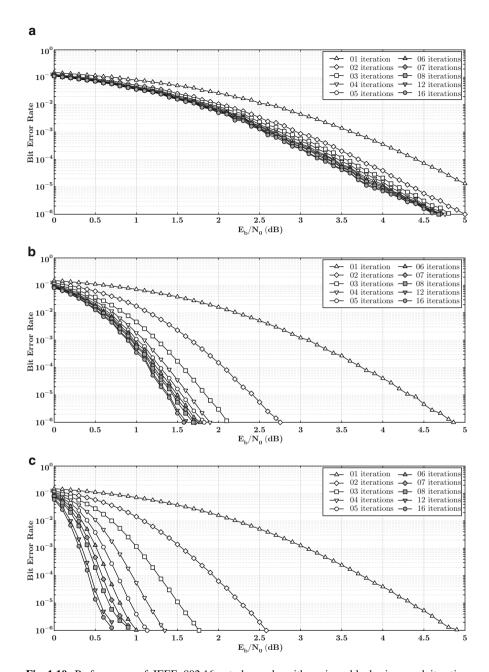

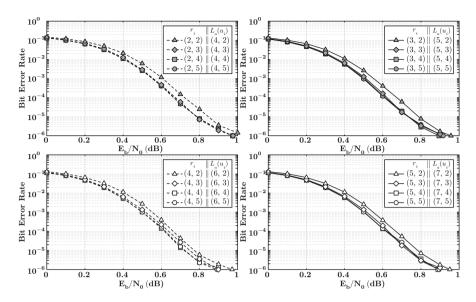

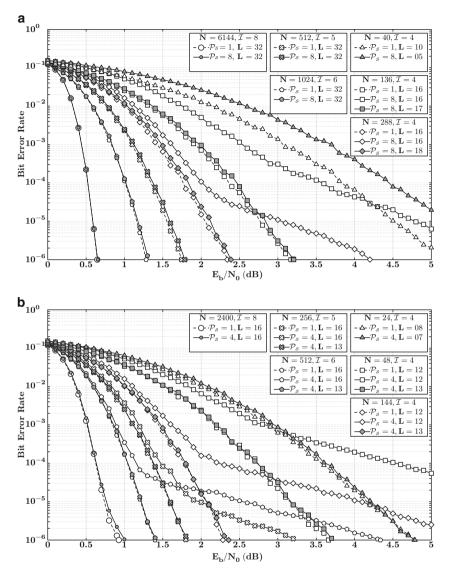

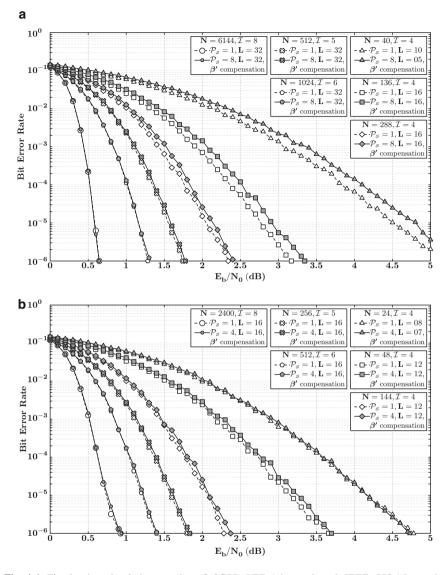

The bit error rate (BER) versus SNR diagrams in Fig. 1.9 present how the performance of 3GPP LTE-Advanced turbo code with  $N = \{40, 512, 6144\}$  varies as the iteration increases from 1 to 16. The simulation results show that the iterative message propagation can provide greater error correction capability in larger blocks than in small blocks. Moreover, it is easy to notice that there is slighter performance gain at higher iterations, especially when N is small. In spite of the excellent performance at  $\mathcal{I}=16$ , the decoding latency is too long. Considering the improvement, it is inefficient to use so many iterations for all blocks. From Fig. 1.9c, the result at  $\mathcal{I}=16$  is merely 0.1 dB better than at  $\mathcal{I}=8$ , but its process

**Fig. 1.9** Performance of 3GPP LTE-Advanced turbo code with various block sizes and iteration numbers. (a) 3GPP LTE-Advanced turbo code: N=40 and  $\mathcal{I}=\{1,2,3,4,5,6,7,8,12,16\}$ . (b) 3GPP LTE-Advanced turbo code: N=512 and  $\mathcal{I}=\{1,2,3,4,5,6,7,8,12,16\}$ . (c) 3GPP LTE-Advanced turbo code: N=6144 and  $\mathcal{I}=\{1,2,3,4,5,6,7,8,12,16\}$

takes double time. Thus, choosing  $\mathcal{I}=8$  is more suitable for  $\mathbf{N}=6144$  in this application. Similarly, based on Figs. 1.9a and 1.9b, we can use  $\mathcal{I}=4$  for  $\mathbf{N}=40$  and  $\mathcal{I}=5$  for  $\mathbf{N}=512$ . In summary, the 3GPP LTE-Advanced turbo decoder generally needs four to eight iterations for all  $\mathbf{N}$ 's in the standard.

### 1.2.3 MAP Algorithm for IEEE 802.16m Turbo Code

To support the double binary codec structure and tail-biting technique of this turbo code, we must make some modifications to the MAP algorithm. The first step is redefinition of notations. The encoder will transform a size-**N** information block  $\mathbf{u} = [u_0, u_1, \ldots, u_{\mathbf{N}-1}]$  with  $u_i = (u_i^{(0)}, u_i^{(1)})$  into **N** pairs of parity check bits:  $\mathbf{p} = [(p_0^{(0)}, p_0^{(1)}), (p_1^{(0)}, p_1^{(1)}), \ldots, (p_{\mathbf{N}-1}^{(0)}, p_{\mathbf{N}-1}^{(1)})]$ . The two parts form the constituent codeword  $\mathbf{c} = [c_0, c_1, \ldots, c_{\mathbf{N}-1}]$ , of which every symbol  $c_i = (c_i^{(0)}, c_i^{(1)}, c_i^{(2)}, c_i^{(3)})$  represents  $(u_i^{(0)}, u_i^{(1)}, p_i^{(0)}, p_i^{(1)})$ . According to (1.4), the code bit  $c_i^{(j)}$  is mapped into a BPSK signal  $x_i^{(j)}$  for  $i = 0 \sim (\mathbf{N} - 1)$  and  $j = 0 \sim 3$ . The modulated signal sequence  $\mathbf{x} = [x_0, x_1, \ldots, x_{\mathbf{N}-1}]$  with  $x_i = (x_i^{(0)}, x_i^{(1)}, x_i^{(2)}, x_i^{(3)})$  will be passed into the channel, and each signal  $x_i^{(j)}$  may suffer from noise  $n_i^{(j)}$  as (1.5) during the transmission. Then the SISO decoder will receive  $\mathbf{r} = [r_0, r_1, \ldots, r_{\mathbf{N}-1}]$  with  $r_i = (r_i^{(0)}, r_i^{(1)}, r_i^{(2)}, r_i^{(3)})$  from the channel. Therefore, the probability of  $\mathbf{r}$  can be derived as (1.48) by changing the upper bounds of i and j in (1.6) and (1.7).

$$\Pr(r_{0}, \dots, r_{N-1} \mid x_{0}, \dots, x_{N-1}) \triangleq \prod_{i=0}^{N-1} \Pr(r_{i}^{(0)}, r_{i}^{(1)}, r_{i}^{(2)}, r_{i}^{(3)} \mid x_{i}^{(0)}, x_{i}^{(1)}, x_{i}^{(2)}, x_{i}^{(3)})$$

$$= \prod_{i=0}^{N-1} \left[ \prod_{i=0}^{3} \Pr(r_{i}^{(j)} \mid x_{i}^{(j)}) \right]$$

(1.48)

The APP becomes (1.49) as well.

$$\Pr(u_i \mid r_0, \dots, r_{N-1}) = \Pr(u_i^{(0)}, u_i^{(1)} \mid r_0, \dots, r_{N-1}), \quad i = 0 \sim N - 1. \quad (1.49)$$

The combination of  $u_i = (u_i^{(0)}, u_i^{(1)})$  with the largest possibility will be selected as the decisions. We often use LLRs rather than APPs to make this comparison. For simplicity, we define the following 2-tuple representations:

$$\{\mathcal{U}(\ell) = (\ell^{(0)}, \ell^{(1)}) \mid \mathcal{U}(0) = (0, 0), \, \mathcal{U}(1) = (0, 1), \, \mathcal{U}(2) = (1, 0), \, \mathcal{U}(3) = (1, 1)\}.$$

Thus, the LLR for the double binary scheme will be (1.50) with  $\ell = 0 \sim 3$ . The APP of  $u_i = (0,0)$  in the denominator is served as the reference value.

$$L^{[\ell]}(u_i) \triangleq \ln \frac{\Pr(u_i = \mathcal{U}(\ell) \mid r_0, \dots, r_{N-1})}{\Pr(u_i = \mathcal{U}(0) \mid r_0, \dots, r_{N-1})}$$

$$= \ln \frac{\Pr(u_i = \mathcal{U}(\ell); r_0, \dots, r_{N-1})}{\Pr(u_i = \mathcal{U}(0); r_0, \dots, r_{N-1})}$$

(1.50)

With these LLRs, we can get the hard decisions  $u_i^*$  by

$$u_i^* = \mathcal{U}(\ell'), \quad \text{if } L^{[\ell']}(u_i) = \max\left(L^{[0]}(u_i), L^{[1]}(u_i), L^{[2]}(u_i), L^{[3]}(u_i)\right).$$

(1.51)

Since the same principle can apply here, the LLR can be also modified into the equation in (1.23) while changing the number of received symbols to N. The definitions of  $\alpha(S_i)$  and  $\beta(S_i)$  are still (1.25) and (1.28) respectively; but it needs distinct initial values for the trellis path with undetermined beginning state and ending state. To solve this problem, we assume that each  $Pr(S_0 = S^{(m)}) = 1/8$ and Pr  $(S_N = S^{(m)}) = 1/8$  for  $m = 0 \sim 7$ ; and we introduces an auxiliary forward metric  $\alpha'(S_i)$  with  $\alpha'(S_0 = S^{(m)}) = 0$  and an auxiliary backward metric  $\beta'(S_i)$ with  $\beta'(S_N = S^{(m)}) = 0$ . Then we compute  $\alpha'(S_i)$  in a forward recursive behavior until we get  $\alpha'(S_N)$ . The property  $S_0 = S_N$  allows us to treat  $\alpha'(S_N)$  as  $\alpha(S_0)$  in the circular trellis structure. For backward metric, the initial  $\beta(S_N)$  can be updated with  $\beta'(S_0)$ , the final results of auxiliary computation. In addition to the initialization, there is a small change in the branch metric calculation. The basic calculation of  $\gamma(S_i, S_{i+1})$  is identical to (1.30). However, the  $Pr(u_i)$  and  $Pr(r_i \mid x_i)$  must be redefined to match the current version of constituent codeword. The new expressions will cover all four cases of the i-th symbol. We first give the *a priori* value as (1.52)whose format agrees with that of LLR.

$$L_a^{[\ell]}(u_i) \stackrel{\triangle}{=} \ln \frac{\Pr(u_i = \mathcal{U}(\ell))}{\Pr(u_i = \mathcal{U}(0))}, \quad \ell = 0 \sim 3$$

(1.52)

Then the probability of  $u_i = \mathcal{U}(\ell)$  is determined by

$$\Pr(u_{i} = \mathcal{U}(\ell)) = \underbrace{\left[\sum_{j=0}^{3} \exp\left(L_{a}^{[j]}(u_{i})\right)\right]^{-1}}_{\boldsymbol{\vartheta}_{i}'} \times \exp\left(L_{a}^{[\ell]}(u_{i})\right)$$

$$= \boldsymbol{\vartheta}_{i}' \times \exp\left(L_{a}^{[\ell]}(u_{i})\right), \tag{1.53}$$

where  $\vartheta_i'$  is fixed for any  $\ell$ . We also renew the index of  $\Pr(r_i \mid x_i)$  as

$$\Pr(r_{i} \mid x_{i}) = \underbrace{\left(\frac{1}{\sqrt{2\pi}\sigma}\right)^{4} \times \exp\left(-\frac{1}{2\sigma^{2}} \sum_{j=0}^{3} \left[(r_{i}^{(j)})^{2} + (x_{i}^{(j)})^{2}\right]\right)}_{\varphi_{i}'} \times \exp\left(\frac{1}{\sigma^{2}} \sum_{j=0}^{3} \left[r_{i}^{(j)} \times x_{i}^{(j)}\right]\right)$$

$$= \varphi_{i}' \times \exp\left(\frac{1}{2} L_{c} \sum_{j=0}^{3} \left[r_{i}^{(j)} \times x_{i}^{(j)}\right]\right). \tag{1.54}$$

This equation involves another constant number  $\varphi'_i$ . By replacing the probabilities in (1.30) and removing the constant part, we have the branch metric for this constituent code:

$$\gamma(S_i, S_{i+1}) = L_a(u_i = \mathcal{U}(\ell)) + \frac{1}{2}L_c \sum_{j=0}^{3} \left[ r_i^{(j)} \times x_i^{(j)} \right]. \tag{1.55}$$

### 1.2.4 Iterative Flow for IEEE 802.16m Turbo Code

When we consider the iterative decoding flow on the basis of this constituent code, the derivation of useful soft values should be revised for the compatibility with the LLR definition in (1.50). The first step is factorizing  $\Pr(u_i; r)$  in the same way as (1.42). The equivalence  $\Pr(u_i^{(0)}, u_i^{(1)}) = \Pr(x_i^{(0)}, x_i^{(1)})$  let this joint probability be factorized to

$$\Pr(u_{i}; r_{0}, \dots, r_{N-1}) = \Pr(x_{i}^{(0)}, x_{i}^{(1)}) \times \Pr(r_{i}^{(0)}, r_{i}^{(1)} \mid x_{i}^{(0)}, x_{i}^{(1)}) \\

\times \sum_{u:u_{i}} \left[ \prod_{\substack{j=0\\j\neq i}}^{N-1} \Pr(x_{j}^{(0)}, x_{j}^{(1)}) \Pr(r_{j}^{(0)}, r_{j}^{(1)} \mid x_{j}^{(0)}, x_{j}^{(1)}) \prod_{l=0}^{N-1} \Pr(r_{l}^{(2)}, r_{l}^{(3)} \mid x_{l}^{(2)}, x_{l}^{(3)}) \right].$$

Therefore, the LLR in (1.50) can be rewritten as

$$L^{[\ell]}(u_i) = \ln \frac{\Pr(u_i = \mathcal{U}(\ell))}{\Pr(u_i = \mathcal{U}(0))} + \ln \frac{\Pr(r_i^{(0)}, r_i^{(1)} \mid u_i = \mathcal{U}(\ell))}{\Pr(r_i^{(0)}, r_i^{(1)} \mid u_i = \mathcal{U}(0))} + L_e^{[\ell]}(u_i), \quad (1.56)$$

where the last term  $L_e^{[\ell]}(u_i)$  is

$$\ln \frac{\sum\limits_{\boldsymbol{u}:u_{i}} \left[ \prod\limits_{\substack{j=0\\j\neq i}}^{N-1} \Pr \left( u_{j} = \mathcal{U}(\ell) \right) \Pr \left( r_{j}^{(0)}, r_{j}^{(1)} \mid u_{j} = \mathcal{U}(\ell) \right) \prod\limits_{l=0}^{N-1} \Pr \left( r_{l}^{(2)}, r_{l}^{(3)} \mid x_{l}^{(2)}, x_{l}^{(3)} \right) \right]}{\sum\limits_{\boldsymbol{u}:u_{i}} \left[ \prod\limits_{\substack{j=0\\j\neq i}}^{N-1} \Pr \left( u_{j} = \mathcal{U}(0) \right) \Pr \left( r_{j}^{(0)}, r_{j}^{(1)} \mid u_{j} = \mathcal{U}(0) \right) \prod\limits_{l=0}^{N-1} \Pr \left( r_{l}^{(2)}, r_{l}^{(3)} \mid x_{l}^{(2)}, x_{l}^{(3)} \right) \right]}.$$

The second term in (1.56) can be simplified into (1.57) by the following properties:  $\mathcal{U}(\ell) = (\ell^{(0)}, \ell^{(1)}), (u^{(0)}, u^{(1)}) = (c^{(0)}, c^{(1)}), (1.4), \text{ and } (1.8).$

$$\ln \frac{\Pr\left(\left(r_i^{(0)}, r_i^{(1)}\right) \mid \left(u_i^{(0)}, u_i^{(1)}\right) = \mathcal{U}(\ell)\right)}{\Pr\left(\left(r_i^{(0)}, r_i^{(1)}\right) \mid \left(u_i^{(0)}, u_i^{(1)}\right) = \mathcal{U}(0)\right)} = -L_c \times \left[r_i^{(0)} \times \ell^{(0)} + r_i^{(1)} \times \ell^{(1)}\right]$$

(1.57)

Moreover, we can use  $L_a^{[\ell]}(u_i)$  in (1.52) to take the place of the first term. These substitutions lead to a proper LLR representation for the double binary scheme as (1.58) with  $\ell = 0 \sim 3$ .

$$L^{[\ell]}(u_i) = L_a^{[\ell]}(u_i) - L_c \times [r_i^{(0)} \times \ell^{(0)} + r_i^{(1)} \times \ell^{(1)}] + L_e^{[\ell]}(u_i). \tag{1.58}$$

Notice that the definition of  $L^{[\ell]}(u_i)$  in (1.50) will have identical numerator and denominator when  $\ell$  is 0. It implies  $L^{[0]}(u_i) = 0$  for  $i = 0 \sim (N-1)$ . For the same reason,  $L_a^{[0]}(u_i)$  and  $L_e^{[0]}(u_i)$  always keep zero. The calculations of these three likelihood ratios can be skipped.

The message propagation between the two constituent codes are also affected by the double binary code structure. Initially, we set the *a priori* value  $L_{a1}^{[\ell]}(u_i)$  for the first constituent code to zero and utilize the MAP algorithm to calculate the *a posteriori* information  $L_{1}^{[\ell]}(u_i) = 0$  for all *i*'s and  $\ell$ 's. From (1.58), the extrinsic information  $L_{a1}^{[\ell]}(u_i)$  will be

$$L_{e1}^{[\ell]}(u_i) = L_1^{[\ell]}(u_i) - L_{e1}^{[\ell]}(u_i) + L_c \times [r_i^{(0)} \times \ell^{(0)} + r_i^{(1)} \times \ell^{(1)}]. \tag{1.59}$$

The  $L_{e1}^{[\ell]}(u_i)$  is regarded as the *a priori* value of the second constituent code. Due to the periodical intra-symbol permutation in (1.2), we must exchange the results about  $\mathcal{U}(\ell) = (\ell^{(1)}, \ell^{(0)})$  for those about  $\mathcal{U}(\ell) = (\ell^{(0)}, \ell^{(1)})$  as long as the symbol index satisfy the condition. If the  $\tilde{u}_i$  has an even index, its *a priori* value estimation is updated according to (1.60); otherwise, the  $L_{a2}^{[\ell]}(\tilde{u}_i)$  comes directly from  $L_{e1}^{[\ell]}(\tilde{u}_i)$  for each  $\ell$ .

$$\begin{cases}

\ell^{(0)} \neq \ell^{(1)} : L_{a2}^{[1]}(\tilde{u}_i) \leftarrow L_{e1}^{[2]}(u_{\mathcal{A}(i)}), & L_{a2}^{[2]}(\tilde{u}_i) \leftarrow L_{e1}^{[1]}(u_{\mathcal{A}(i)}) \\

\ell^{(0)} = \ell^{(1)} : L_{a2}^{[0]}(\tilde{u}_i) \leftarrow L_{e1}^{[0]}(u_{\mathcal{A}(i)}), & L_{a2}^{[3]}(\tilde{u}_i) \leftarrow L_{e1}^{[3]}(u_{\mathcal{A}(i)})

\end{cases} (1.60)$$

When the second SISO decoder collects all requisite inputs, it will get the LLR  $L_2^{[\ell]}(\tilde{u}_i)$  by the MAP algorithm and derive the extrinsic information  $L_{e2}^{[\ell]}(\tilde{u}_i)$  by

$$L_{e2}^{[\ell]}(\tilde{u}_i) = L_2^{[\ell]}(\tilde{u}_i) - L_{a2}^{[\ell]}(\tilde{u}_i) + L_c \times [\tilde{r}_i^{(0)} \times \ell^{(0)} + \tilde{r}_i^{(1)} \times \ell^{(1)}].$$

(1.61)

This result will be the *a priori* information  $L_{al}^{[\ell]}(u_{\mathcal{A}(i)})$  of the other constituent code. Those cases relating to the  $\mathcal{U}(\ell)$  with  $\ell^{(0)} \neq \ell^{(1)}$  for an even-indexed  $\tilde{u}_i$  must be swapped, too. After all *a priori* values are ready, a new half-iteration for the first constituent code can start. The turbo decoding runs iteratively until the iteration number reaches  $\mathcal{I}$ , and then the hard decisions that are determined by (1.51) are outputted.

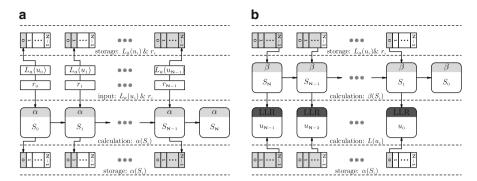

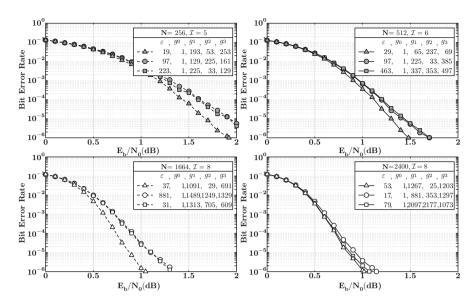

Figure 1.10 shows the BER performance of IEEE 802.16m turbo code with  $N = \{24, 256, 2400\}$  at various iterations. Compared to Fig. 1.9, the results of the examples with similar number of information bits are alike. In any example, the curve of  $\mathcal{I} = 16$  can approximately be viewed as the ultimate performance bound. Actually, when  $\mathcal{I}$  exceeds a certain threshold, the improvement caused by further iterations will be limited to 0.2 dB. Due to the insignificant difference in

**Fig. 1.10** Performance of IEEE 802.16m turbo code with various block sizes and iteration numbers. (a) IEEE 802.16m turbo code: N = 24 and  $\mathcal{I} = \{1, 2, 3, 4, 5, 6, 7, 8, 12, 16\}$ . (b) IEEE 802.16m turbo code: N = 256 and  $\mathcal{I} = \{1, 2, 3, 4, 5, 6, 7, 8, 12, 16\}$ . (c) IEEE 802.16m turbo code: N = 2400 and  $\mathcal{I} = \{1, 2, 3, 4, 5, 6, 7, 8, 12, 16\}$

performance and considerable saving in latency, we prefer that threshold to 16 while determining the necessary iteration number. According to the simulation results, the common value of  $\mathcal{I}$  can be set to 4 for  $\mathbf{N}=24$ , 5 for  $\mathbf{N}=256$ , and 8 for  $\mathbf{N}=2400$ . It is easy to infer that the suitable  $\mathcal{I}$  for any other  $\mathbf{N}$  in this standard is in the range of four to eight, and we will adopt these choices in later discussions.

### 1.3 Techniques for Efficient Decoding Process

### 1.3.1 Simplified MAP Algorithms

Although the turbo code can achieve the impressive performance, the complex algorithm will be an obstacle to implement the decoders. The main operations of the MAP algorithm are exponentiation and logarithm. Both of them take more hardware resources than most basic arithmetic operations. To reduce the complexity, the works in [23–25] proposed simpler algorithms that chiefly use addition and subtraction to calculate the metrics and LLRs. These alternative methods are developed with the following Jacobian function

$$\ln(e^{y_1} + e^{y_2}) \stackrel{\triangle}{=} \max^*(y_1, y_2) = \max(y_1, y_2) + \ln(1 + e^{-|y_1 - y_2|}), \quad (1.62)$$

and its extension form

$$\ln(e^{y_1} + e^{y_2} + e^{y_3}) = \max^*(y_1, y_2, y_3) = \max^*(\max^*(y_1, y_2), y_3).$$

(1.63)

Note that the logarithmic function is equivalent to the summation of the normal  $\max(\cdot)$  function and a correction term  $\ln(1+e^{-|y_1-y_2|})$ . The normal  $\max(\cdot)$  function is just the comparison and selection among all inputs. In addition, the  $\ln(1+e^{-|y_1-y_2|})$ , whose value depends on  $|y_1-y_2|$ , can be calculated beforehand and stored in a lookup table. Thus, the  $\max^*(\cdot)$  function can be realized easily. After replacing the original computations in (1.23), (1.25), and (1.28) with the  $\max^*(\cdot)$  functions, we can write the forward metric, backward metric, and LLR as (1.64)–(1.66) respectively.

$$\alpha(S_i) = \max_{S_{i-1}}^* \left[ \gamma(S_{i-1}, S_i) + \alpha(S_{i-1}) \right]$$

(1.64)

$$\beta(S_i) = \max_{S_{i+1}}^* \left[ \gamma(S_i, S_{i+1}) + \beta(S_{i+1}) \right]$$

(1.65)

(1.66)

$$L(u_i) = \max_{(S_i, S_{i+1}): u_i = 0}^* \left[ \alpha(S_i) + \gamma(S_i, S_{i+1}) + \beta(S_{i+1}) \right]$$

$$- \max_{(S_i, S_{i+1}): u_i = 1}^* \left[ \alpha(S_i) + \gamma(S_i, S_{i+1}) + \beta(S_{i+1}) \right].$$

The decoding algorithm based on the above three equations is named the Log-MAP algorithm. For the Log-MAP algorithm, a lookup table with high accuracy can lead to the same performance as the MAP algorithm, but it also means the requirement of larger memory.

A further simplification can be achieved by completely discarding the lookup table. The correction term will be omitted from the  $\max^*(\cdot)$  function:

$$\max^*(y_1, y_2) \approx \max(y_1, y_2). \tag{1.67}$$

This approximation leads to the Max-Log-MAP algorithm that involves only the additions and the  $\max(\cdot)$  functions. However, the lack of the correction term would make the LLR calculation too optimistic and then cause performance degradation. From [26, 27], the problem can be solve by scaling the extrinsic information. While the SISO decoder get the extrinsic information through the Max-Log-MAP algorithm, it will multiply  $L_e(u_i)$  by a scaling factor  $\zeta$ . Afterward, the scaled  $L'_e(u_i)$  in (1.68) is send to the other SISO decoder as more reliable *a priori* value.

$$L'_e(u_i) = \zeta \times L_e(u_i) \tag{1.68}$$

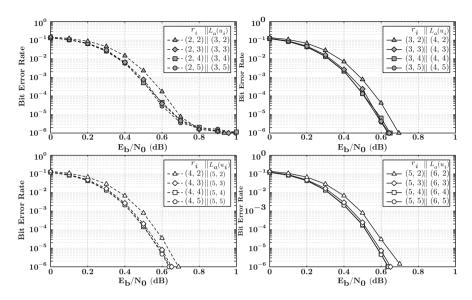

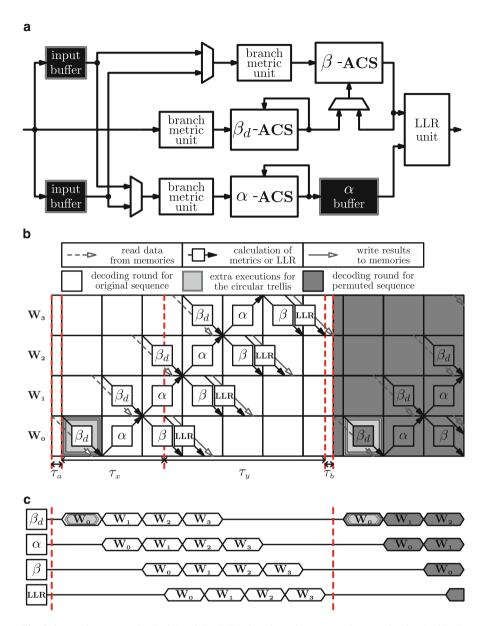

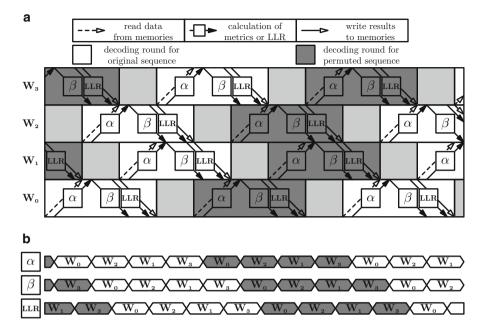

The effect of  $\zeta$  depends on the code structure and channel condition. With the aid of simulation, we can determine if the scaling factor is beneficial. Figure 1.11 shows the variations in performance after using the simplified MAP algorithms. For these 3GPP LTE-Advanced turbo codes, choosing  $\zeta=0.75$  achieves better improvement than the other cases with respect to Max-Log-MAP algorithms; but  $\zeta=0.5$  would be an unwise choice for its inferior performance as  $E_b/N_0$  exceeds 0.8 dB. The results of IEEE 802.16m turbo codes indicates that both  $\zeta=0.875$  and  $\zeta=0.75$  successfully compensate the information loss in (1.67), while  $\zeta=0.625$  and  $\zeta=0.5$  worsen the performance. In our applications, the Max-Log-MAP algorithm with  $\zeta=0.75$  would be an effective solution that provides a compromise between complexity and performance.

### 1.3.2 Sliding Window Technique

The processing schedule also has a great influence on the overhead of a practical SISO decoder. Here we consider a general case of a size-N data block and assume that initial state  $S_0$  and the last state  $S_N$  of the corresponding trellis path are known. The inputs includes received data and *a priori* values, and they are usually sent to the SISO decoder in ascending order. With the initial condition  $\alpha(S_0)$ , the forward metric can be derived immediately after the reception of  $r_i$  and  $L_a(u_i)$ ; but all backward metrics, which are initialized with  $\beta(S_N)$ , cannot be computed until the last input data  $(r_{N-1}$  and  $L_a(u_{N-1}))$  are ready. According to the decoding algorithm, the calculation of  $L(u_i)$  involves  $\alpha(S_i)$  and  $\beta(S_{i+1})$ , so it needs to wait the completion of the two types of metrics. The dependencies force the SISO decoder

Bit Error Rate  $10^{-3}$  $10^{-4}$ - MAP - Log-MAP Max-Log-MAP Max-Log-MAP with  $\zeta$ = 0.875 Max-Log-MAP with  $\zeta$ = 0.750  $10^{-5}$ Max-Log-MAP with  $\zeta = 0.625$ Max-Log-MAP with  $\zeta = 0.500$  $10^{-6}$ 0.7 0.1 0.2 0.3 0.5 0.6 0.8 0.4 $E_b/N_0 (dB)$

Fig. 1.11 Performance of turbo codes with various decoding algorithms. (a) 3GPP LTE-Advanced turbo code: N=6144 and  $\mathcal{I}=8$ . (b) IEEE 802.16m turbo code: N=2400 and  $\mathcal{I}=8$

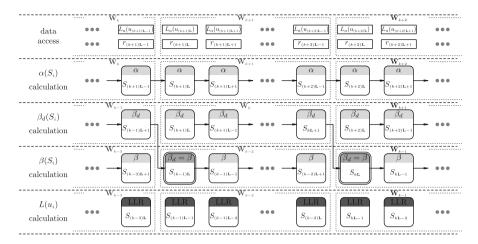

Fig. 1.12 Basic processing schedule of the SISO decoder. (a) Data access and execution of  $\alpha(S_i)$ . (b) Execution of  $\beta(S_i)$  and  $L(u_i)$

keeping the input data and forward metrics in memories before it starts computing the backward metrics and LLRs. Figure 1.12 demonstrates the conventional order of main executions. The execution of  $L(u_i)$  follows the generations of  $\beta(S_{i+1})$ ; and all LLRs are outputted in descending order. The period between the first input and the first output is directly proportional to the block size, and so is the requirement of extra memories. As N is large, the SISO decoder will have long processing latency and use many storage elements; it would be impractical to implement such a design.

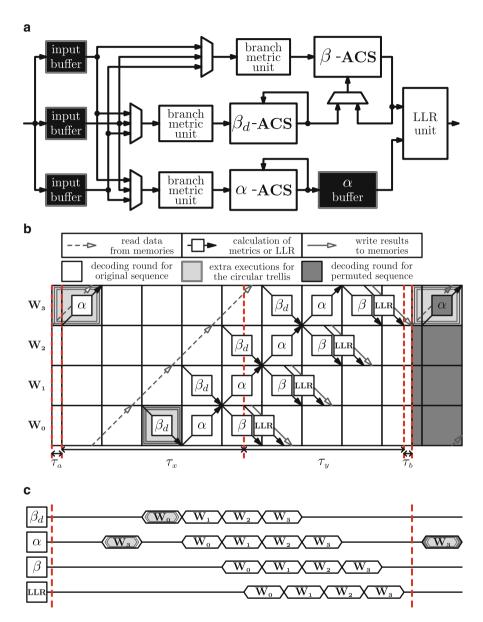

The sliding window technique introduced in [28, 29] can avoid considerable overhead of the SISO decoder with large  $\mathbf{N}$ . It exploits a dummy backward metric calculation, symbolized as  $\beta_d(S_i)$  for the states at i-th trellis stage, to establish the initial conditions for the true backward metric. With this technique, the data block is divided into  $\lceil \mathbf{N}/\mathbf{L} \rceil$  windows. Here we let  $\mathbf{W}_k$  stand for the k-th window, and the length of  $\mathbf{W}_k$  obeys

$$\left\{ \begin{array}{ll} \mathbf{L} & \text{if } k \in \{0, \cdots, \left\lceil \frac{\mathbf{N}}{\mathbf{L}} \right\rceil - 2\}; \\ \mathbf{N} - \mathbf{L} \times (\left\lceil \frac{\mathbf{N}}{\mathbf{L}} \right\rceil - 1) & \text{if } k = \left\lceil \frac{\mathbf{N}}{\mathbf{L}} \right\rceil - 1. \end{array} \right.$$

(1.69)

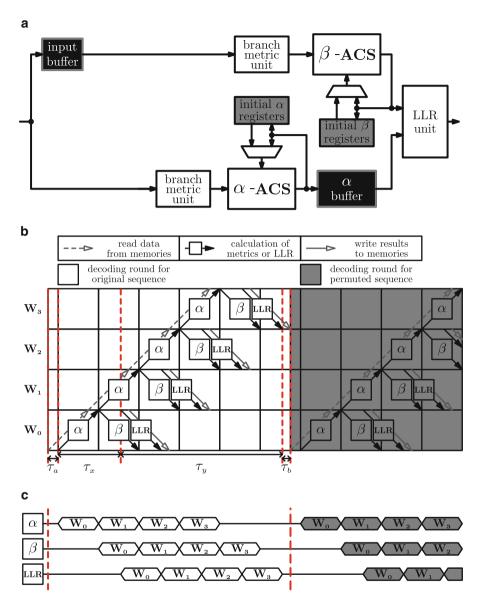

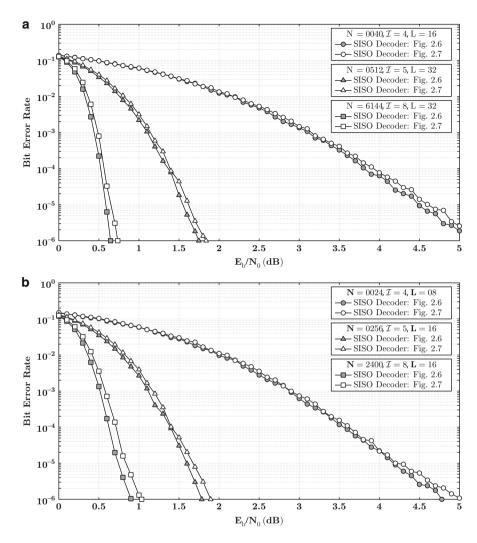

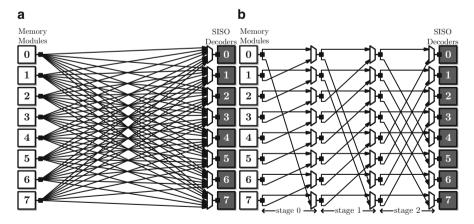

Except for the last window, the SISO decoder performs the dummy backward metric calculation over each  $\mathbf{W}_k$  with the initial value  $\beta_d(S_{(k+1)L} = \mathbf{S}^{(m)}) = 0$  for  $m = 0 \sim 7$  when all necessary inputs are ready; and it can get  $\beta_d(S_{kL})$  after  $\mathbf{L}$  recursion steps. This result will be assigned to the true backward metric at the  $(k\mathbf{L})$ -th trellis stage:  $\beta(S_{kL}) = \beta_d(S_{kL})$ ; then there is an initialization for calculating  $\beta(S_i)$  for  $i \leq k\mathbf{L}$ . Notice that the process of calculating the initial backward metric of the last window is exactly like the conventional way, but the  $\beta(S_N)$  in a circular trellis structure will be derived from the dummy backward calculation of  $\mathbf{W}_0$ . The executions can be scheduled as Fig. 1.13, where the data access and forward metric calculation remain unchanged. The SISO decoder is allowed to calculate the  $\beta_d(S_i)$ 's of  $\mathbf{W}_k$  whenever it collects the data of  $\mathbf{W}_k$ . At the same time, the executions of  $\beta(S_i)$  and  $L(u_i)$

28 1 Introduction

Fig. 1.13 Decoding process with the sliding window technique

relating to  $\mathbf{W}_{k-2}$  can start with  $\beta(S_{(k-1)\mathbf{L}}) = \beta_d(S_{(k-1)\mathbf{L}})$ . Now the processing latency and storage requirement depend on window length  $\mathbf{L}$  rather than block size  $\mathbf{N}$ . As a consequence, the LLRs can be generated earlier than those in the conventional process; besides, the memory usage for  $r_i$ ,  $L_a(u_i)$ , and  $\alpha(S_i)$  will decrease.

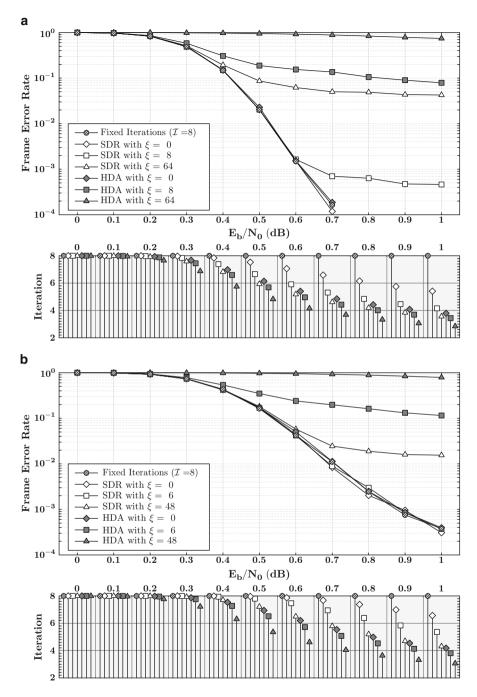

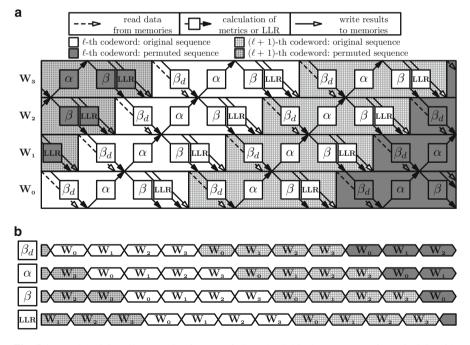

The overhead and performance must be considered together when the sliding window technique is employed. Although this method with short  ${\bf L}$  can favor the cost reduction of one SISO decoder, the dummy backward metric calculation might fail to provide robust initialization for true backward metrics; that is, too short  ${\bf L}$  might cause performance loss. The suitable  ${\bf L}$  will vary with the turbo code specifications such as  ${\bf N}$  and  ${\bf R}$ . Figure 1.14 presents the performance of turbo codes with different combinations of  ${\bf N}$  and  ${\bf L}$  in each standard. For those 3GPP LTE-Advanced turbo codes, choosing  ${\bf L}=8$  degrades the performance significantly, especially for  ${\bf N}=6144$  and  ${\bf N}=512$ ; whereas choosing  ${\bf L}>16$  can make the performance very close to the ideal results. For IEEE 802.16m application, the schemes with  ${\bf L}\geq 16$  work as successfully as the conventional cases ( ${\bf L}={\bf N}$ ) for both  ${\bf N}=2400$  and  ${\bf N}=256$ ; and the choices of  ${\bf L}\geq 8$  are preferable for  ${\bf N}=24$ . As a result, the practical turbo decoders should support the maximum  ${\bf L}$  of 32 and of 16 for all  ${\bf N}$ 's in 3GPP LTE-Advanced and IEEE 802.16m standards respectively so that it can approximate the optimal BER at reasonable cost.

# 1.3.3 Early Stopping Criteria

The iteration number is another dominant factor in the overall decoding time. In the previous discussion, the value of  $\mathcal{I}$  is typically determined based on the worst case. Actually, from Figs. 1.9 and 1.10, the decoder can correct some received

**Fig. 1.14** Performance of turbo codes with various block sizes and window lengths. (a) 3GPP LTE-Advanced turbo code:  $\zeta = 0.75$ , and  $N = \{40, 512, 6144\}$ . (b) IEEE 802.16m turbo code:  $\zeta = 0.75$ , and  $N = \{24, 256, 2400\}$

data blocks before the maximum iteration. It is unnecessary to spend the same  $\mathcal{I}$  iterations in decoding every received data block [22]. During the turbo decoding of most erroneous data blocks, the corresponding soft values will converge after certain iterations; so the performance gain in the subsequent process is very insignificant. If the data suffer from slighter noise, there is a high possibility that the iteration bound about the convergence is smaller than preset  $\mathcal{I}$ . The process from the lower bound to  $\mathcal{I}$  is viewed as a waste of computation and time. To avoid too much redundant process, we will terminate the decoding flow dynamically by early stopping criteria. Most criteria are the statistics for difference between the temporary results at different half-iterations. Among all criteria, the hard-decision-aided (HDA) criterion

30 1 Introduction