Kazuo Kondo · Morihiro Kada Kenji Takahashi *Editors*

Three-Dimensional Integration of Semiconductors

Processing, Materials, and Applications

Three-Dimensional Integration of Semiconductors

Kazuo Kondo • Morihiro Kada • Kenji Takahashi Editors

# Three-Dimensional Integration of Semiconductors

Processing, Materials, and Applications

*Editors* Kazuo Kondo Department of Chemical Engineering Osaka Prefecture University Osaka Japan

Morihiro Kada Osaka Prefecture University Osaka Japan Kenji Takahashi Toshiba Corporation Oita Japan

ISBN 978-3-319-18674-0 ISBN 978-3-319-18675-7 (eBook) DOI 10.1007/978-3-319-18675-7

Library of Congress Control Number: 2015943688

Springer Cham Heidelberg New York Dordrecht London © Springer International Publishing Switzerland 2015

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors, and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

Springer International Publishing AG Switzerland is part of Springer Science+Business Media (www.springer.com)

# Preface

The concept of three-dimensional integration of semiconductors originated with the US patent by IBM in 1969. The patent is titled "Hourglass-shaped conductive connection through semiconductor structures" (http://www.google.com.mx/patents/US3648131). The original interconnect looks like an hourglass. Since 1969, the three-dimensional integration concept has spread out to semiconductor industries all over the world and more than 40 consortia and companies have been involved in this development. Forty-five years after its invention, three-dimensional integration of semiconductors is becoming very popular, and is about to be industrialized in advanced electronics in the very near future.

This book reviews the state of the art of three-dimensional semiconductor integration. Chapter 1 gives an overview of three-dimensional integration research and development history. Chapter 2 summarizes recent three-dimensional integration research and development activities and applications. Chapter 3 gives an explanation of through-silicon via (TSV) formation processes. Chapters 4 and 5 cover wafer handling, wafer thinning, and bonding of wafers and dies. Chapter 6 explains metrology and inspection. Chapter 7 discusses reliability and characterization issues. Chapter 8 covers trends in technology development of three-dimensional integration circuits testing. Finally, Chapter 9 summarizes research and development project results conducted by New Energy and Industrial Technology Development Organization (NEDO)/Association of Super-Advanced Electronics Technologies (ASET): Japan in 2008 to 2012.

We really hope that this book will help not only beginners in three-dimensional integration technology of semiconductors but also engineers who are already involved in this field, both in industry and academia. I was very much astonished when, in 2000, ASET members visited my university and asked for support to fill an interconnect via that was huge compared to the contact via created by the damascene process of copper electrodeposition. This introduction gave me the initial motivation to start my research on three-dimensional integration. Two editors, Morihiro Kada and Kenji Takahasi, are former ASET leaders. The opportunity given by K. Howell of Springer to publish this book is very much appreciated.

Kazuo Kondo Morihiro Kada Kenji Takahasi Osaka Osaka Oita

| 1 | Res  | earch a  | nd Devel  | opment History of Three-Dimensional             |    |

|---|------|----------|-----------|-------------------------------------------------|----|

|   |      | 0        |           | ogy                                             | 1  |

|   | -    | ihiro K  |           |                                                 |    |

|   | 1.1  | Introd   |           |                                                 | 1  |

|   |      | 1.1.1    |           | rnational Technology Roadmap for Semiconductors | 1  |

|   |      | 1.1.2    |           | gration Technology                              | 3  |

|   | 1.2  |          |           | 3D Integration Technology                       | 4  |

|   | 1.3  | Resear   | rch and D | evelopment History of 3D Integration Technology | 5  |

|   |      | 1.3.1    | 3D Pack   | aging Technology                                | 5  |

|   |      | 1.3.2    | Origin o  | of the TSV Concept                              | 6  |

|   |      | 1.3.3    | Researc   | h and Development History of 3D                 |    |

|   |      |          | Technol   | ogy in Organizations                            | 8  |

|   |      |          | 1.3.3.1   | Japan                                           | 9  |

|   |      |          | 1.3.3.2   | Japanese 3D Integration Technology              |    |

|   |      |          |           | Research and Development Project                |    |

|   |      |          |           | (Dream Chip)                                    | 10 |

|   |      |          | 1.3.3.3   | The USA                                         | 11 |

|   |      |          | 1.3.3.4   | Europe                                          | 13 |

|   |      |          | 1.3.3.5   | Asia                                            | 14 |

|   |      |          | 1.3.3.6   | International                                   | 15 |

|   | 1.4  | Resear   | rch and D | evelopment History of 3D Integration            |    |

|   |      |          |           | Applications                                    | 15 |

|   |      | 1.4.1    |           | Image Sensor and MEMS                           | 15 |

|   |      | 1.4.2    | DRAM      | -                                               | 16 |

|   |      | 1.4.3    | 2.5D wi   | th Interposer                                   | 17 |

|   |      | 1.4.4    | Others    | -                                               | 17 |

|   | Refe | erences. |           |                                                 | 19 |

|   |      |          |           |                                                 |    |

| 2 | Rec  | ent Res  | earch an  | d Development Activities of                     |    |

|   | Thr  | ee-Dim   | ensional  | Integration Technology                          | 25 |

|   | Mor  | ihiro Ka |           |                                                 |    |

|   | 2.1  | Recen    | t Announ  | cement of Research and Development Activities   | 25 |

|   | 2.2  |          |           | om-Access Memory                                | 30 |

|   |      | -        |           | -                                               |    |

|   |      | 2.2.1   | Through-Silicon Via Technology for Dynamic           |      |

|---|------|---------|------------------------------------------------------|------|

|   |      |         | Random-Access Memory                                 | 30   |

|   |      | 2.2.2   | Wide I/O and Wide I/O2 Mobile Dynamic Random-        |      |

|   |      |         | Access Memory                                        | . 31 |

|   | 2.3  | Hybrid  | d Memory Cube and High Bandwidth Memory              |      |

|   |      |         | nic Random-Access Memory                             | 33   |

|   |      | 2.3.1   | Hybrid Memory Cube                                   |      |

|   |      | 2.3.2   |                                                      | . 55 |

|   |      | 2.3.2   | Memory                                               | 34   |

|   | 2.4  | EDCA    | A and 2.5D                                           |      |

|   | 2.4  |         |                                                      |      |

|   | 2.5  |         | S                                                    | 36   |

|   | 2.6  |         | Energy and Industrial Technology Development         |      |

|   |      | -       | ization Japan                                        |      |

|   |      | 2.6.1   |                                                      | 37   |

|   |      | 2.6.2   | Background, Purpose, and Target of                   |      |

|   |      |         | "Smart Device" Project                               | 37   |

|   | Refe | rences. |                                                      | 38   |

|   |      |         |                                                      |      |

| 3 | TSV  | Proce   | sses                                                 | 43   |

|   | Mas  | ahiko T | Fanaka, Makoto Sekine, Itsuko Sakai, Yutaka Kusuda,  |      |

|   | Tom  | oyuki N | Nonaka, Osamu Tsuji, Kazuo Kondo                     |      |

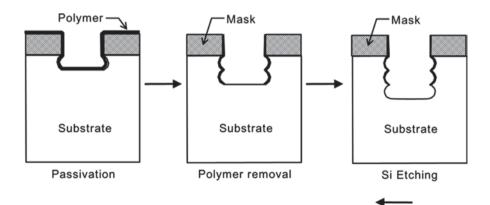

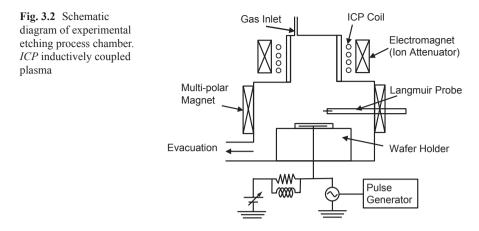

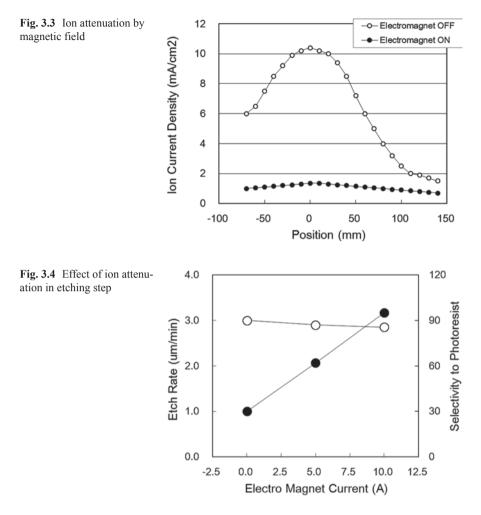

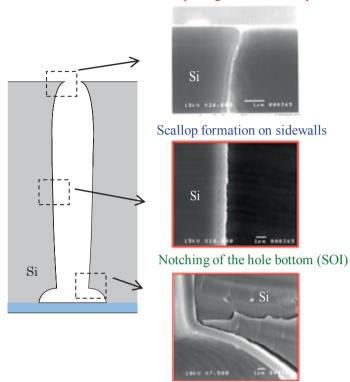

|   | 3.1  |         | Silicon Etching by Bosch Process                     | 43   |

|   |      | 3.1.1   | •••                                                  |      |

|   |      | 3.1.2   |                                                      |      |

|   |      | 3.1.3   |                                                      |      |

|   |      | 3.1.4   |                                                      |      |

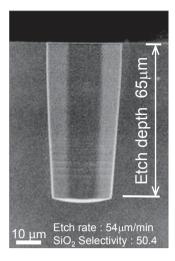

|   | 3.2  | High-   | Rate Silicon Via Etching and Basics of Sidewall Etch |      |

|   | 5.2  |         | ion by Steady-State Etch Process                     | 52   |

|   |      | 3.2.1   |                                                      |      |

|   |      | 3.2.2   |                                                      |      |

|   |      | 5.2.2   | 3.2.2.1 Effect of RF                                 |      |

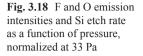

|   |      |         | 3.2.2.2 Effect of Pressure                           |      |

|   |      |         |                                                      |      |

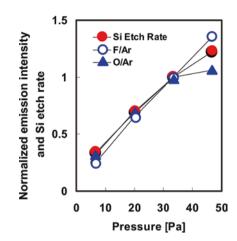

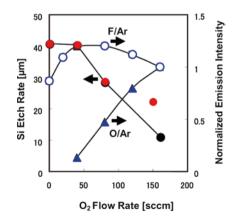

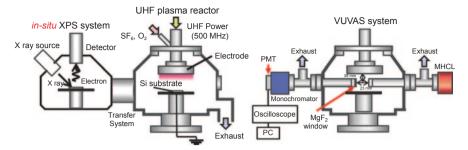

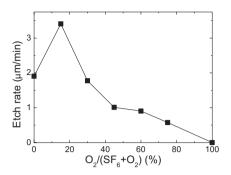

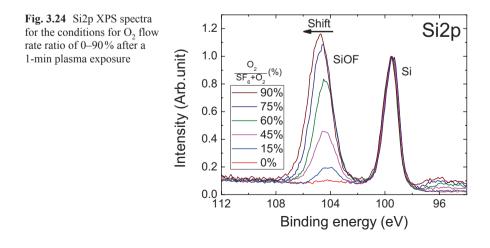

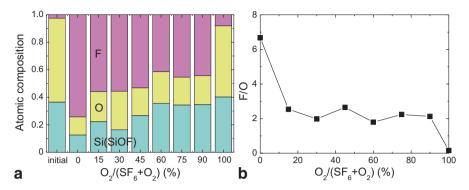

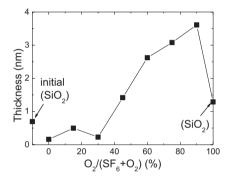

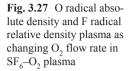

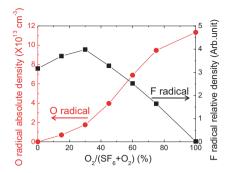

|   |      | 2 2 2   | 3.2.2.3 Effect of Oxygen Addition                    | 56   |

|   |      | 3.2.3   |                                                      | 50   |

|   |      |         | by $SF_6 - O_2$ Plasma                               |      |

|   |      |         | 3.2.3.1 Effect of Oxygen Addition                    |      |

|   |      |         | 3.2.3.2 Effect of Substrate Temperature              |      |

|   |      |         | 3.2.3.3 Effect of SiF <sub>4</sub> Addition          |      |

|   |      | 3.2.4   | Conclusion                                           |      |

|   | 3.3  |         | Temperature CVD Technology                           |      |

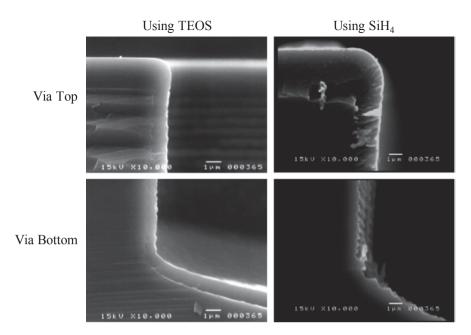

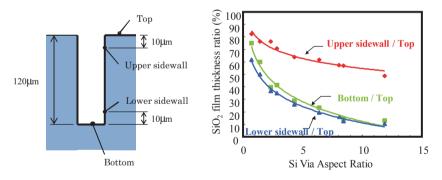

|   |      | 3.3.1   | Introduction                                         |      |

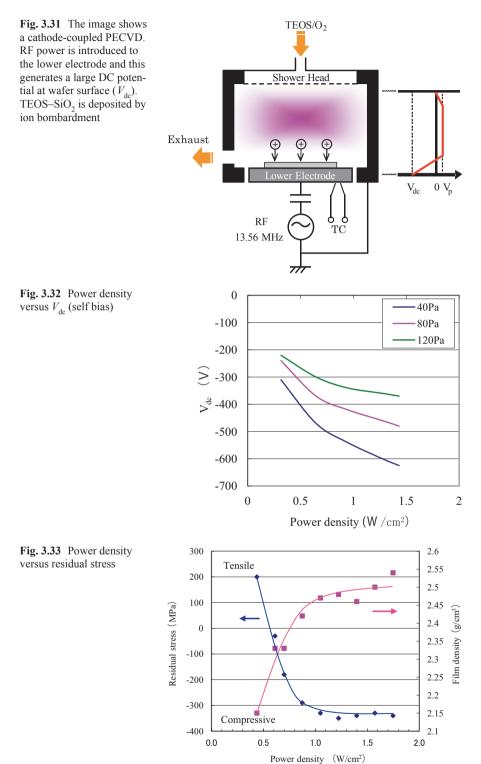

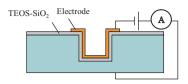

|   |      | 3.3.2   | Cathode-Coupled Plasma-Enhanced CVD (LS-CVD)         | 66   |

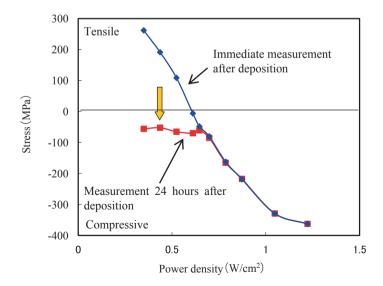

|   |      | 3.3.3   | Low-Temperature SiO, Deposition                      | 69   |

|   |      |         | 3.3.3.1 Wafer Temperature During Low-                |      |

|   |      |         | Temperature Deposition                               | 69   |

|   |      |         |                                                      |      |

|   |      |           | 3.3.3.2   | Step Coverage in Si-Via Holes                          | 70  |

|---|------|-----------|-----------|--------------------------------------------------------|-----|

|   |      |           | 3.3.3.3   |                                                        |     |

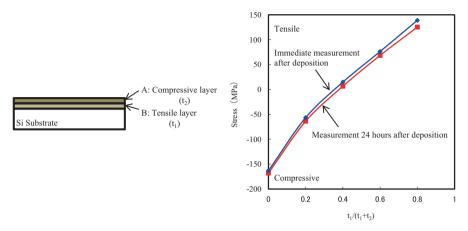

|   |      |           |           | Deposited at Low Temperature                           | 72  |

|   |      |           | 3.3.3.4   | Stress Control of SiO <sub>2</sub> Film Deposited      |     |

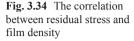

|   |      |           |           | Using LS-CVD.                                          | 73  |

|   |      | 3.3.4     | Conclus   | sion                                                   | 74  |

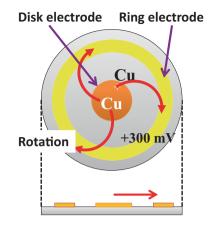

|   | 3.4  | Electr    |           | on for Via Filling                                     | 74  |

|   |      | 3.4.1     |           | as an Accelerant Additive of Copper                    |     |

|   |      |           |           | leposition                                             | 74  |

|   |      | 3.4.2     |           | Between Via Filling and Cu <sup>+</sup> Ion by         |     |

|   |      |           |           | cal Reverse Current Waveform                           | 79  |

|   |      | 3.4.3     | Simulat   | ion of Cu <sup>+</sup> Ion Distribution Inside the Via | 82  |

|   |      | 3.4.4     | High-St   | beed Via Filling Electrodeposition by Other            |     |

|   |      |           |           | ations                                                 | 87  |

|   |      | 3.4.5     |           | on of Thermal Expansion Coefficient of                 |     |

|   |      |           |           | leposited Copper for TSV by Additive                   | 90  |

|   | Refe | erences   |           | 1 11 7                                                 | 94  |

|   |      |           |           |                                                        |     |

| 4 | Waf  | er Han    | dling and | d Thinning Processes                                   | 97  |

|   | Taka | ashi Hai  | imoto, Ei | ichi Yamamoto, Takahiko Mitsui,                        |     |

|   | Tosł | nihiro It | o, Tsuyos | shi Yoshida, Tsubasa Bandoh,                           |     |

|   |      |           |           | sahiro Yamamoto                                        |     |

|   | 4.1  | Wafer     | Thinning  | Solution for TSV Devices                               | 97  |

|   |      | 4.1.1     |           | ction                                                  | 97  |

|   |      | 4.1.2     |           | Thinning                                               | 98  |

|   |      | 4.1.3     |           | hinning for TSV Devices                                | 99  |

|   |      | 4.1.4     |           | ontrol                                                 | 99  |

|   |      | 4.1.5     |           | ry                                                     | 102 |

|   | 4.2  | A Nov     |           | fiddle TSV Thinning Technology by Si/Cu                |     |

|   |      |           |           | MP                                                     | 103 |

|   |      | 4.2.1     | -         | ction                                                  | 103 |

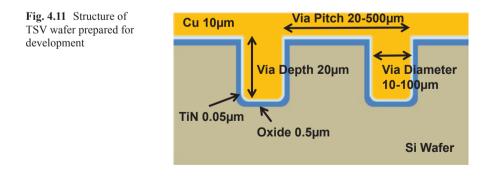

|   |      | 4.2.2     | Experin   | nental Method                                          | 105 |

|   |      | 4.2.3     | Results   | and Discussion                                         | 106 |

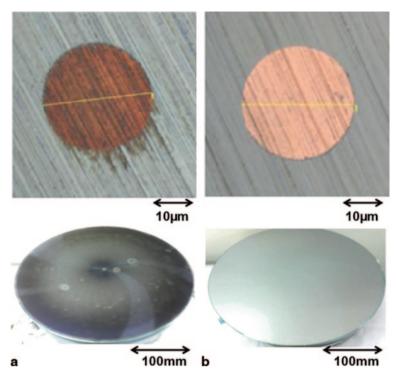

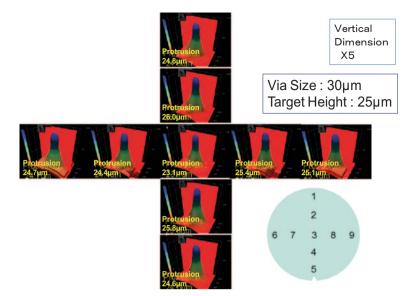

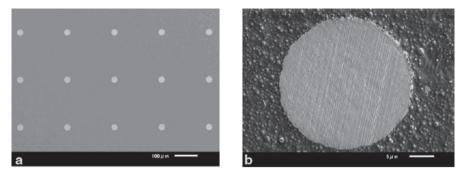

|   |      |           | 4.2.3.1   | Si/Cu Simultaneous Grinding Using                      |     |

|   |      |           |           | Low-Density TSV Wafers                                 | 106 |

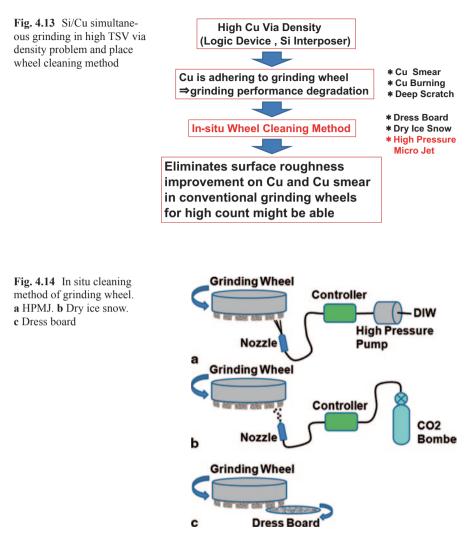

|   |      |           | 4.2.3.2   | Si/Cu Simultaneous Grinding Using                      |     |

|   |      |           |           | High-Density TSV Wafers                                | 107 |

|   |      |           | 4.2.3.3   | Si/Cu Same Removal Rate CMP (First                     |     |

|   |      |           |           | CMP): Non-Selective CMP Between Cu and Si              | 112 |

|   |      |           | 4.2.3.4   | TSV Protrusion CMP (Second CMP):                       |     |

|   |      |           |           | Selective CMP Between Cu and Si                        | 114 |

|   |      |           | 4.2.3.5   | Post Second CMP Cleaning                               | 115 |

|   |      | 4.2.4     |           | sion                                                   | 117 |

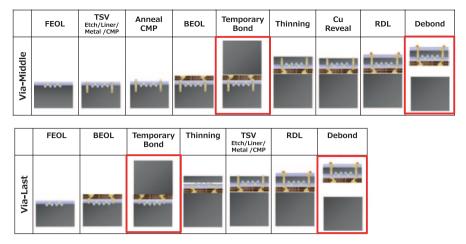

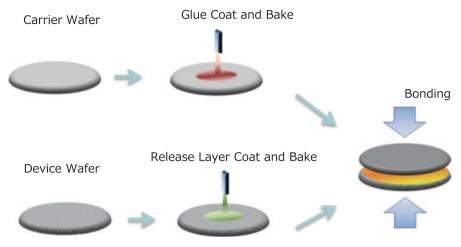

|   | 4.3  | Tempo     |           | ıding                                                  | 118 |

|   |      | 4.3.1     |           | ound                                                   | 118 |

|   |      |           | 0         |                                                        |     |

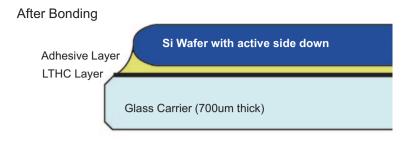

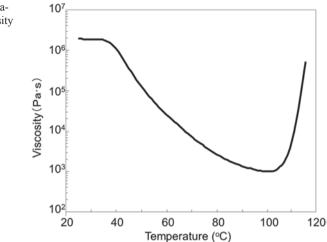

|   |      | 4.3.2  | The 3M    | <sup>TM</sup> Temporary Bonding Materials  | 119 |

|---|------|--------|-----------|--------------------------------------------|-----|

|   |      | 4.3.3  |           | <sup>TM</sup> Temporary Adhesive           | 120 |

|   |      | 4.3.4  |           | bsorbing Layer                             | 124 |

|   |      | 4.3.5  |           | t Steps                                    | 128 |

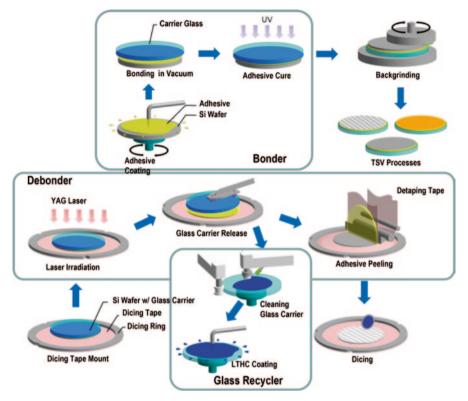

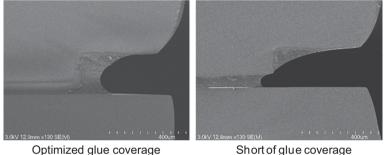

|   | 4.4  | Tempo  | orary Bon | ding and Debonding for TSV Processing      | 128 |

|   |      | 4.4.1  |           | tion                                       | 128 |

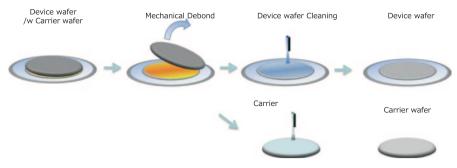

|   |      | 4.4.2  |           | ary Bonding and Debonding Process          | 129 |

|   |      | 4.4.3  |           | ing Method.                                | 131 |

|   |      | 4.4.4  |           | and Performance Requirements for           | 101 |

|   |      |        |           | ary Bonding Device                         | 132 |

|   |      | 4.4.5  |           | and Performance Requirements for           | 10- |

|   |      |        |           | ing Devices                                | 135 |

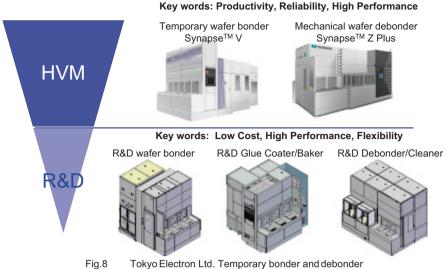

|   |      | 4.4.6  |           | Electron's Temporary Bonder and Debonder   |     |

|   |      |        |           | Concept and Lineup                         | 137 |

|   |      | 4.4.7  |           | Dutlook                                    | 137 |

|   | Refe |        |           |                                            | 138 |

|   |      |        |           |                                            | 100 |

| 5 | Waf  | er and | Die Bond  | ling Processes                             | 139 |

| - |      |        |           | nihito Inaba and Toshihisa Nonaka          |     |

|   | 5.1  |        |           | er Bonding                                 | 139 |

|   |      |        |           |                                            | 139 |

|   |      | 5.1.2  |           | mperature or Room Temperature Wafer        |     |

|   |      | 0.11.2 |           | Bonding Method and Application             | 140 |

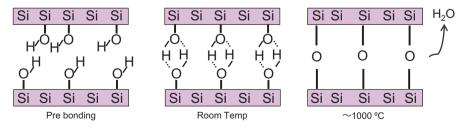

|   |      |        | 5.1.2.1   | • • • • • • • • • • • • • • • • • • • •    | 140 |

|   |      |        | 5.1.2.2   | •                                          | 140 |

|   |      |        | 5.1.2.3   | Anodic Bonding                             | 141 |

|   |      |        | 5.1.2.4   | Cu <sub>2</sub> Cu/Oxide Hybrid Bonding    | 142 |

|   |      |        | 5.1.2.5   | Conclusion of Low-Temperature or Room      | 112 |

|   |      |        | 0.1.2.0   | Temperature Wafer Direct Bonding           |     |

|   |      |        |           | Methods and Their Applications             | 142 |

|   |      |        | 5.1.2.6   | Future Outlook for Bonding Application     | 112 |

|   |      |        | 0.1.2.0   | Using Low-Temperature or Room              |     |

|   |      |        |           | Temperature Wafer Direct Bonding Methods   | 142 |

|   |      | 5.1.3  | Request   | s Made to Equipment Makers and Initiatives | 172 |

|   |      | 5.1.5  | -         | ng Low-Temperature or Room Temperature     |     |

|   |      |        |           | virect Bonding Methods                     | 143 |

|   |      |        |           | Post BAA                                   | 144 |

|   |      |        |           | Scaling                                    | 144 |

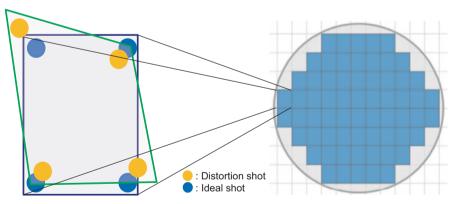

|   |      |        | 5.1.3.3   | Distortion                                 | 145 |

|   |      |        | 5.1.3.4   | Bonding Strength                           | 145 |

|   |      |        | 5.1.3.4   | Void                                       | 140 |

|   |      | 5.1.4  |           | Void                                       | 140 |

|   |      | 5.1.4  |           | ion                                        | 147 |

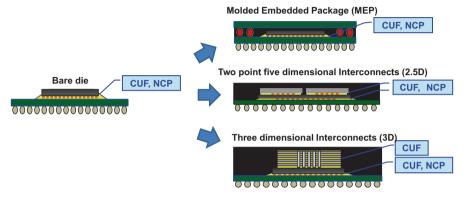

|   | 5.2  |        |           | ials                                       | 148 |

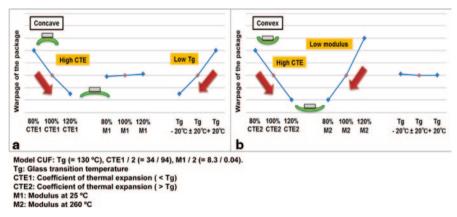

|   | 5.4  | 5.2.1  |           | al Trend for Three-Dimensional Integration | 140 |

|   |      | 3.4.1  |           | s and Underfill Materials                  | 148 |

|   |      |        | rackage   |                                            | 140 |

|   |      | 5.2.2  | Requirements for Underfill Materials                | 150 |

|---|------|--------|-----------------------------------------------------|-----|

|   |      |        | 5.2.2.1 Requirements for CUF and Material           |     |

|   |      |        | Technology Trend                                    | 150 |

|   |      |        | 5.2.2.2 Requirements for NCP and Material           |     |

|   |      |        | Technology Trend                                    | 152 |

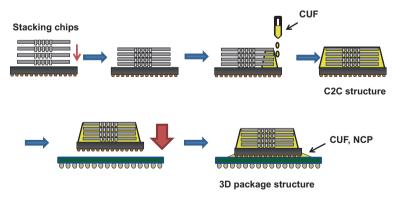

|   |      | 5.2.3  | Application to CUF Between the Stacked Chips        | 154 |

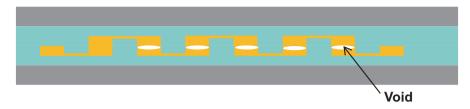

|   | 5.3  | Nonco  | onductive Films                                     | 155 |

|   |      | 5.3.1  | Introduction                                        | 155 |

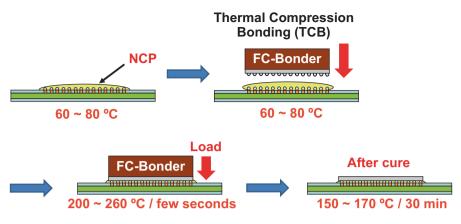

|   |      | 5.3.2  | Required Material Feature from Bonding Process      | 156 |

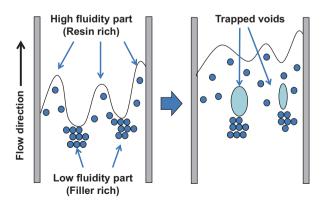

|   |      | 5.3.3  | Void Issue in NCF                                   | 160 |

|   |      | 5.3.4  | High Throughput NCF-TCB                             | 163 |

|   | Refe | rences |                                                     | 165 |

|   |      |        |                                                     |     |

| 6 |      | 0.     | and Inspection                                      | 167 |

|   |      |        | squet, Jean-Philippe Piel, Sylvain Perrot, Hideo    |     |

|   |      |        | Osamu Sato, Allen Gu, Michael Feser, Bruce Johnson, |     |

|   | Rale | 0      | rada and Yoshitaka Tatsumoto                        |     |

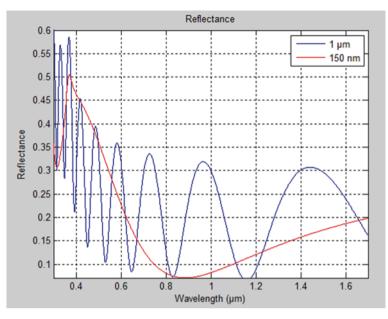

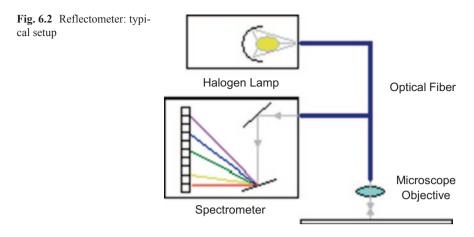

|   | 6.1  | Princi | ples of Spectroscopic Reflectometry                 |     |

|   |      | 6.1.1  | Introduction                                        |     |

|   |      | 6.1.2  | Measurement                                         |     |

|   |      | 6.1.3  | Setup                                               |     |

|   |      | 6.1.4  | Analysis                                            |     |

|   |      | 6.1.5  | Conclusion                                          | 171 |

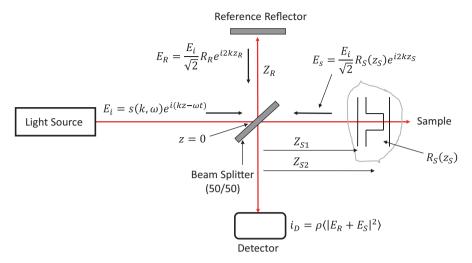

|   | 6.2  |        | Coherence Interferometry for Three-Dimensional      |     |

|   |      | -      | ated Circuit Through-Silicon Via                    |     |

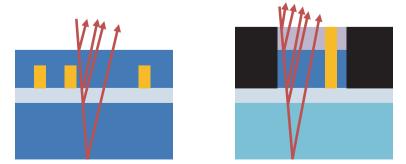

|   |      | 6.2.1  | Optical Measurement of Topographies and Thicknesse  |     |

|   |      |        | 6.2.1.1 3D IC TSV Needs Tomography                  | 171 |

|   |      |        | 6.2.1.2 Tomography with Low-Coherence               |     |

|   |      |        | Interferometry                                      |     |

|   |      | 6.2.2  | Theory of Optical Coherence Tomography              |     |

|   |      |        | 6.2.2.1 Basic Principle                             |     |

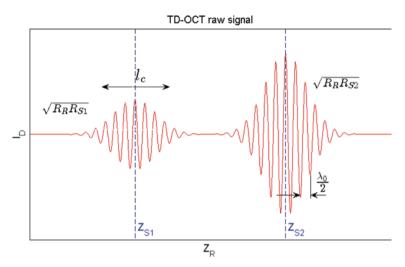

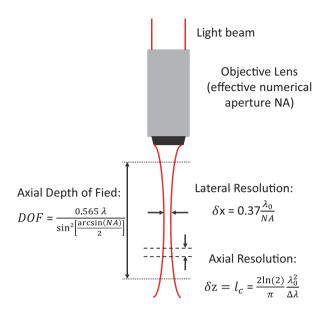

|   |      |        | 6.2.2.2 Time-Domain OCT                             |     |

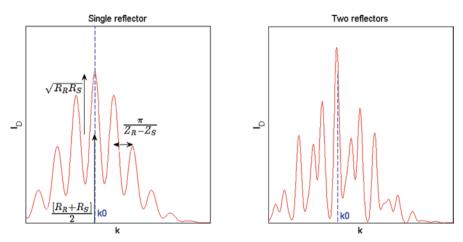

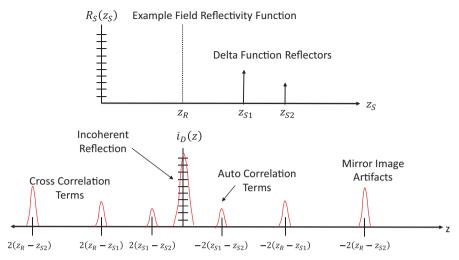

|   |      |        | 6.2.2.3 Fourier-Domain OCT                          |     |

|   |      | (      | 6.2.2.4 Practical Considerations                    |     |

|   |      | 6.2.3  | Conclusion.                                         |     |

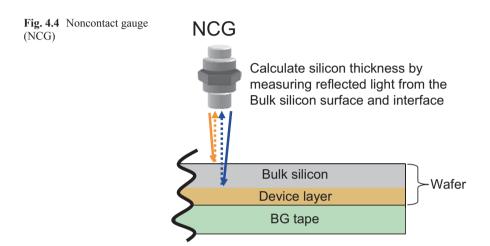

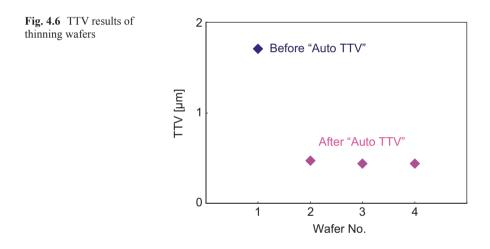

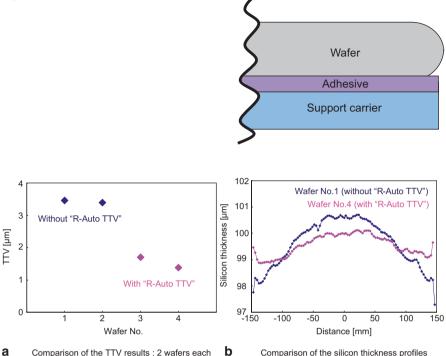

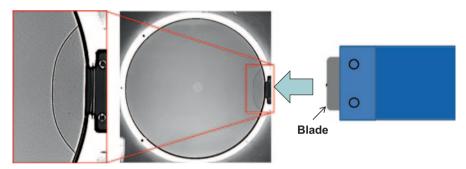

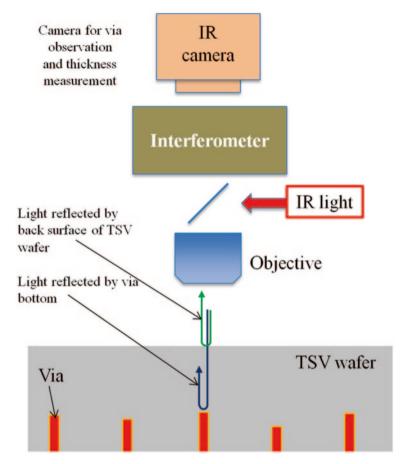

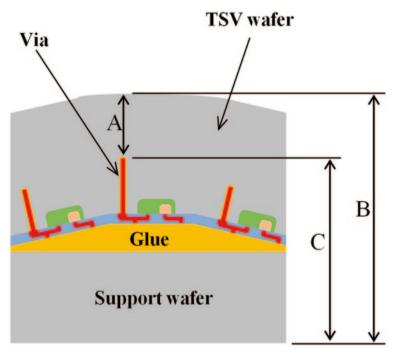

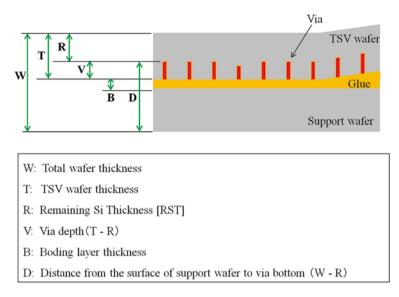

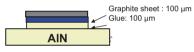

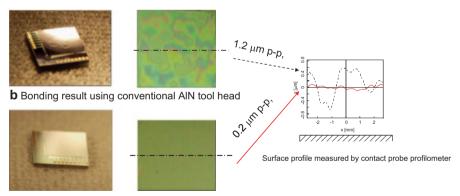

|   | 6.3  |        | n and Glue Thickness Measurement for Grinding       |     |

|   |      | 6.3.1  | Introduction                                        | 182 |

|   |      | 6.3.2  | 8 8                                                 | 102 |

|   |      | ( 2 2  | of Grinding                                         |     |

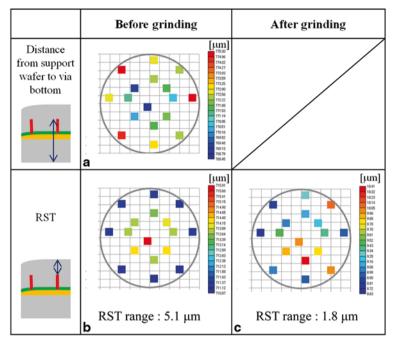

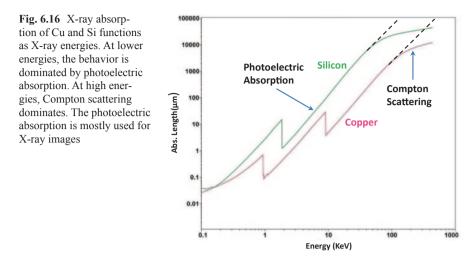

|   |      | 6.3.3  | Features of BGM300                                  |     |

|   |      | 6.3.4  | Verifying BGM300 Measurement Results                |     |

|   |      | 6.3.5  | Measurement After Grinding                          |     |

|   |      | 6.3.6  | Optimized Wafer Grinding Based on Via               | 107 |

|   |      | ()7    | Height Information from BGM300                      |     |

|   |      | 6.3.7  | Conclusion                                          | 189 |

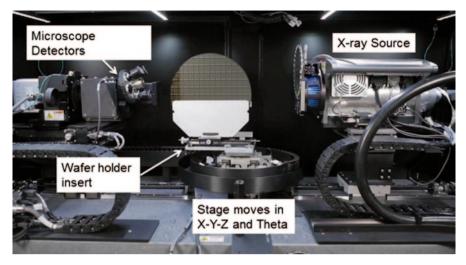

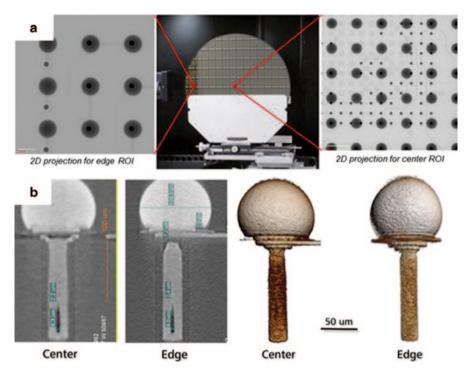

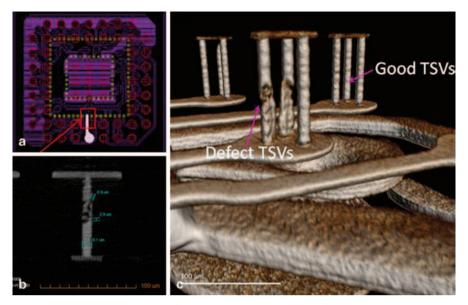

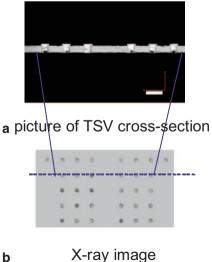

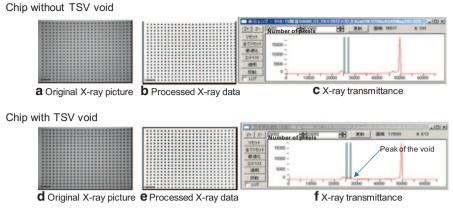

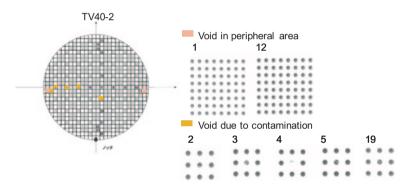

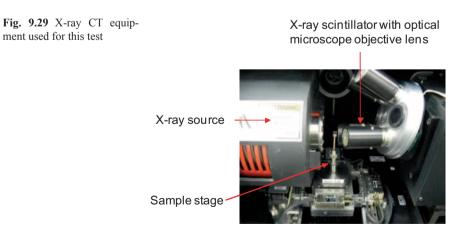

|   | 6.4                                                       |                                  | ray Microscopy Technology for Nondestructive           |  |  |  |  |  |  |  |

|---|-----------------------------------------------------------|----------------------------------|--------------------------------------------------------|--|--|--|--|--|--|--|

|   |                                                           | Analy                            | sis of TSV                                             |  |  |  |  |  |  |  |

|   |                                                           | 6.4.1                            |                                                        |  |  |  |  |  |  |  |

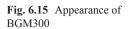

|   |                                                           | 6.4.2                            | Fundamentals of X-ray Microscopy                       |  |  |  |  |  |  |  |

|   |                                                           |                                  | 6.4.2.1 Physics of X-ray Imaging                       |  |  |  |  |  |  |  |

|   |                                                           |                                  | 6.4.2.2 3D X-ray Microscopy                            |  |  |  |  |  |  |  |

|   |                                                           | 6.4.3                            | Applications for TSV Process Development               |  |  |  |  |  |  |  |

|   |                                                           | 6.4.4                            | Applications for TSV Failure Analysis                  |  |  |  |  |  |  |  |

|   |                                                           | 6.4.5                            | Summary                                                |  |  |  |  |  |  |  |

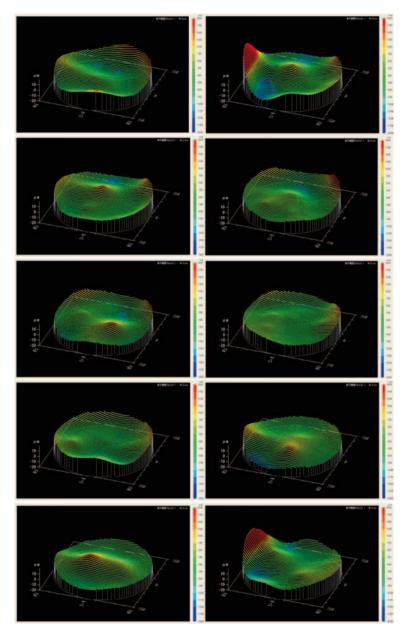

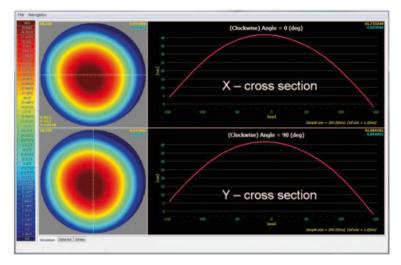

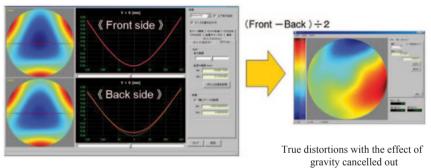

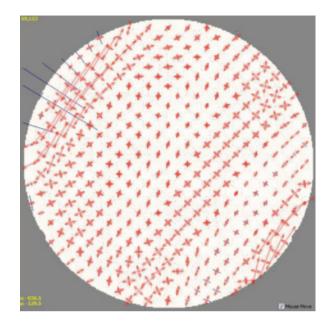

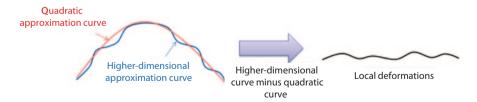

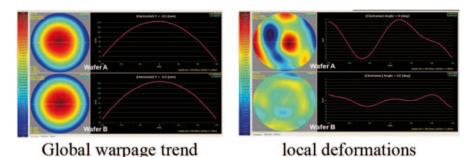

|   | 6.5                                                       | Wafer                            | Warpage and Local Distortion Measurement               |  |  |  |  |  |  |  |

|   |                                                           | 6.5.1                            | Introduction                                           |  |  |  |  |  |  |  |

|   |                                                           | 6.5.2                            | Basic Functions of WDM300                              |  |  |  |  |  |  |  |

|   |                                                           | 6.5.3                            | Measurement and Analysis of Local Deformations         |  |  |  |  |  |  |  |

|   |                                                           | 6.5.4                            | Application                                            |  |  |  |  |  |  |  |

|   |                                                           | 6.5.5                            | Summary                                                |  |  |  |  |  |  |  |

|   | Refe                                                      | rences                           |                                                        |  |  |  |  |  |  |  |

|   |                                                           |                                  |                                                        |  |  |  |  |  |  |  |

| 7 |                                                           |                                  | acteristics and Reliability: Impact of 3D              |  |  |  |  |  |  |  |

|   |                                                           |                                  | 1 Processes on Device Reliability                      |  |  |  |  |  |  |  |

|   |                                                           | angwook Lee and Mitsuma Koyanagi |                                                        |  |  |  |  |  |  |  |

|   | 7.1                                                       |                                  |                                                        |  |  |  |  |  |  |  |

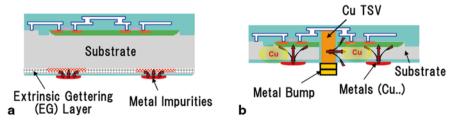

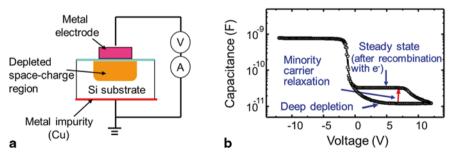

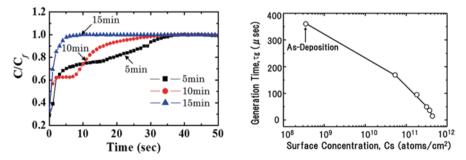

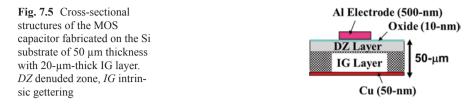

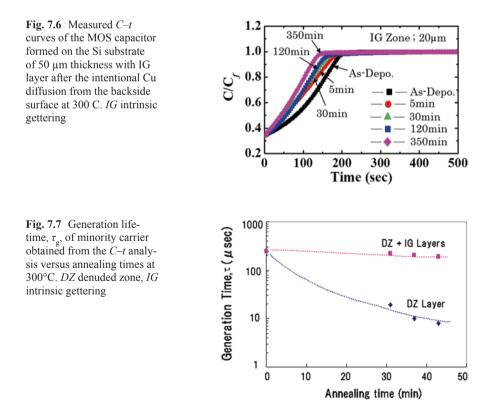

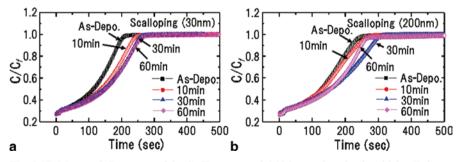

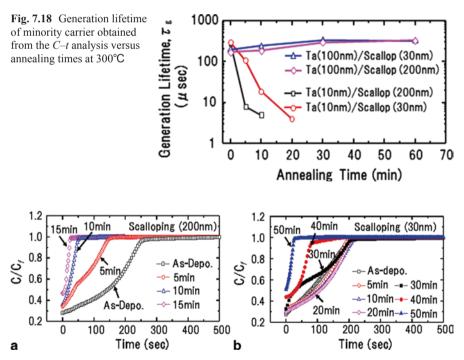

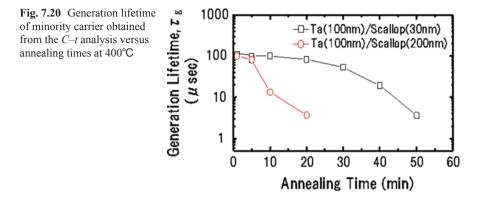

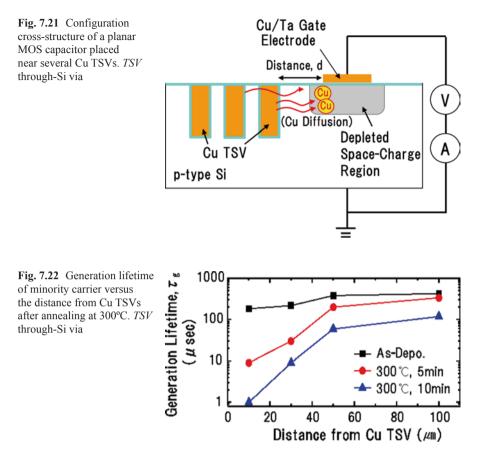

|   | 7.2 Impact of Cu Contamination on Device Reliabilities in |                                  |                                                        |  |  |  |  |  |  |  |

|   |                                                           | Thinned 3D-IC Chip               |                                                        |  |  |  |  |  |  |  |

|   |                                                           | 7.2.1                            | Impact of Cu Diffusion at Backside Surface in          |  |  |  |  |  |  |  |

|   |                                                           |                                  | Thinned 3D-IC Chip                                     |  |  |  |  |  |  |  |

|   |                                                           |                                  | 7.2.1.1 Effect of Intrinsic Gettering Layer            |  |  |  |  |  |  |  |

|   |                                                           |                                  | 7.2.1.2 Effect of EG Layer                             |  |  |  |  |  |  |  |

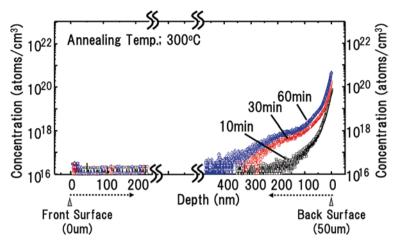

|   |                                                           | 7.2.2                            | Impact of Cu Diffusion from Cu Via                     |  |  |  |  |  |  |  |

|   |                                                           |                                  | 7.2.2.1 Effect of the Barrier Thickness and the        |  |  |  |  |  |  |  |

|   |                                                           |                                  | Scallop Roughness                                      |  |  |  |  |  |  |  |

|   |                                                           |                                  | 7.2.2.2 Effect of the Annealing Temperature            |  |  |  |  |  |  |  |

|   |                                                           |                                  | 7.2.2.3 Keep-Out-Zone Characterization by Cu           |  |  |  |  |  |  |  |

|   |                                                           |                                  | Diffusion from Cu Via                                  |  |  |  |  |  |  |  |

|   | 7.3                                                       |                                  | t of Mechanical Stress/Strain on Device Reliability in |  |  |  |  |  |  |  |

|   |                                                           |                                  | ed IC                                                  |  |  |  |  |  |  |  |

|   |                                                           | 7.3.1                            |                                                        |  |  |  |  |  |  |  |

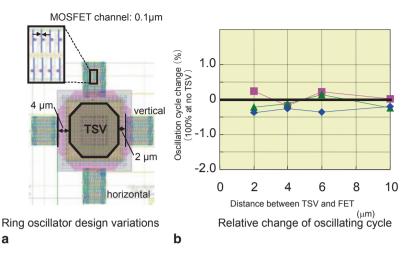

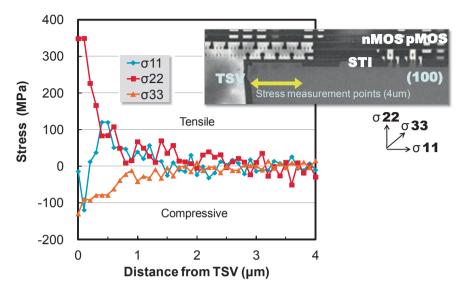

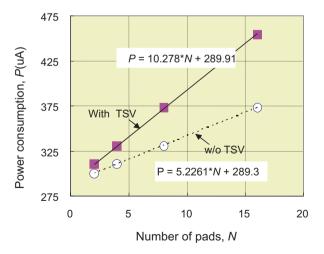

|   |                                                           | 7.3.2                            | 0 5 0                                                  |  |  |  |  |  |  |  |

|   | 7.4                                                       |                                  | t of 3D Integration Process on DRAM Retention          |  |  |  |  |  |  |  |

|   |                                                           |                                  | cteristics                                             |  |  |  |  |  |  |  |

|   |                                                           | 7.4.1                            | Impact of Mechanical Strength on Retention             |  |  |  |  |  |  |  |

|   |                                                           |                                  | Characteristics in Thin DRAM Chip                      |  |  |  |  |  |  |  |

|   |                                                           | 7.4.2                            | Impact of Cu Contamination on Memory Retention         |  |  |  |  |  |  |  |

|   |                                                           |                                  | Characteristics in DRAM Chip                           |  |  |  |  |  |  |  |

|   | Refe                                                      | rences                           |                                                        |  |  |  |  |  |  |  |

| 8 | Trei                                                                                          | nds in 3 | D Integr    | ated Circuit (3D-IC) Testing Technology         | 235      |  |  |  |  |  |  |  |

|---|-----------------------------------------------------------------------------------------------|----------|-------------|-------------------------------------------------|----------|--|--|--|--|--|--|--|

|   | Hirc                                                                                          | shi Tak  | ahashi, Se  | enling Wang, Shuichi Kameyama,                  |          |  |  |  |  |  |  |  |

|   | Yosl                                                                                          | hinobu 1 | Higami, F   | Iiroyuki Yotsuyanagi, Masaki Hashizume,         |          |  |  |  |  |  |  |  |

|   | Shy                                                                                           | ue-Kung  | g Lu and 2  | Zvi Roth                                        |          |  |  |  |  |  |  |  |

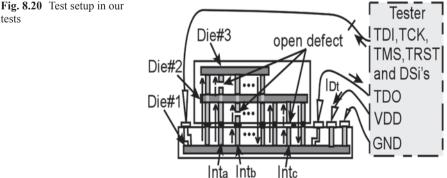

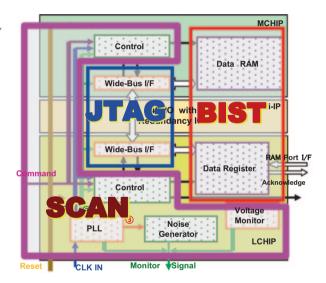

|   | 8.1                                                                                           | Crucia   | al Issues a | nd Key Technologies for 3D-IC Testing           | 230      |  |  |  |  |  |  |  |

|   | 8.2                                                                                           |          |             |                                                 |          |  |  |  |  |  |  |  |

|   | 8.3                                                                                           |          |             |                                                 |          |  |  |  |  |  |  |  |

|   | 8.4                                                                                           | Resear   | rch Trend   | s in Automatic Test Pattern Generator and       |          |  |  |  |  |  |  |  |

|   |                                                                                               |          |             | for TSVs in 3D-IC                               | 24       |  |  |  |  |  |  |  |

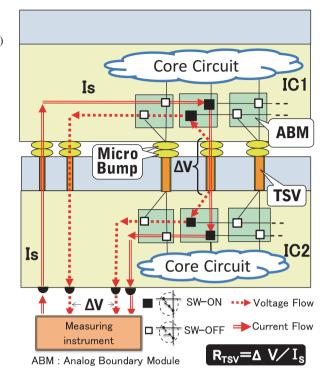

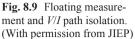

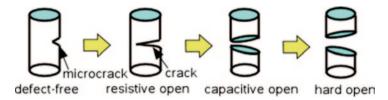

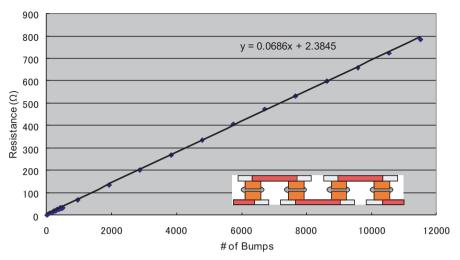

|   | 8.5                                                                                           |          |             | sistance Measuring Method for TSVs in 3D-IC     | 24       |  |  |  |  |  |  |  |

|   |                                                                                               | 8.5.1    |             | ound of Our Study                               | 24       |  |  |  |  |  |  |  |

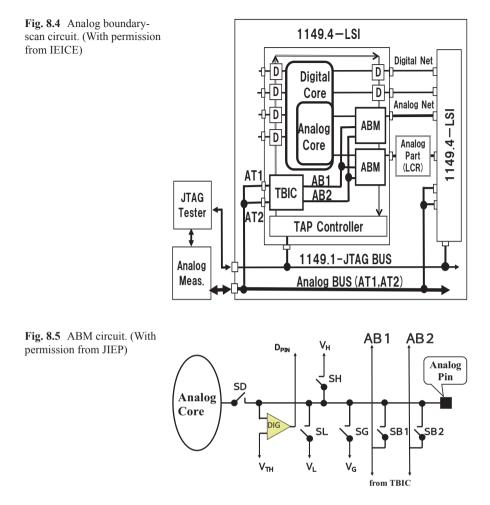

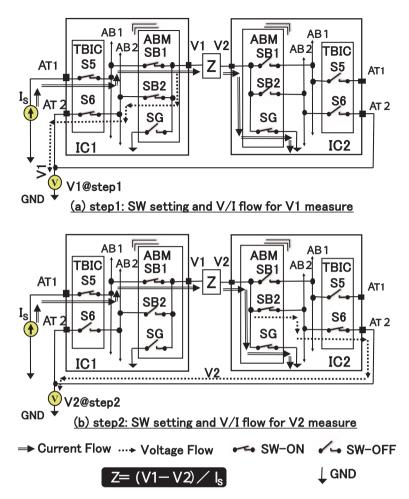

|   |                                                                                               | 8.5.2    |             | s of Conventional Analog Boundary Scan          |          |  |  |  |  |  |  |  |

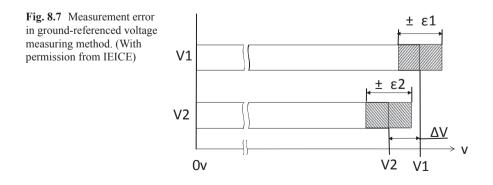

|   |                                                                                               |          |             | Resistance Measurement                          | 24       |  |  |  |  |  |  |  |

|   |                                                                                               |          | 8.5.2.1     |                                                 | 24       |  |  |  |  |  |  |  |

|   |                                                                                               |          | 8.5.2.2     | Standard Resistance Measuring Method            |          |  |  |  |  |  |  |  |

|   |                                                                                               |          | 0.0.2.2     | by 1149.4                                       | 24       |  |  |  |  |  |  |  |

|   |                                                                                               |          | 8.5.2.3     | Problems of Conventional Analog Bound-          | 21       |  |  |  |  |  |  |  |

|   |                                                                                               |          | 0.0.2.5     | ary Scan for TSV Resistance Measuring           | 24       |  |  |  |  |  |  |  |

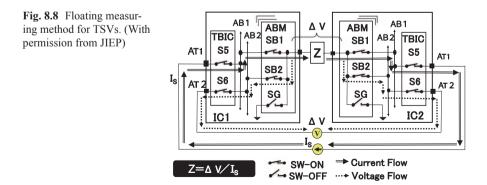

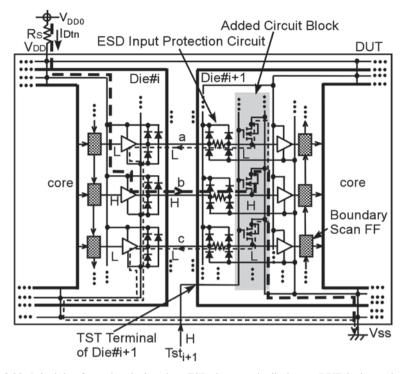

|   |                                                                                               | 8.5.3    | Propose     | d Measuring Method                              | 24       |  |  |  |  |  |  |  |

|   |                                                                                               | 8.5.4    |             | ۲                                               | 25       |  |  |  |  |  |  |  |

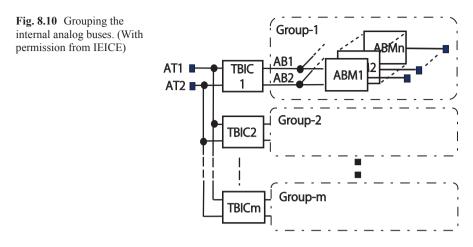

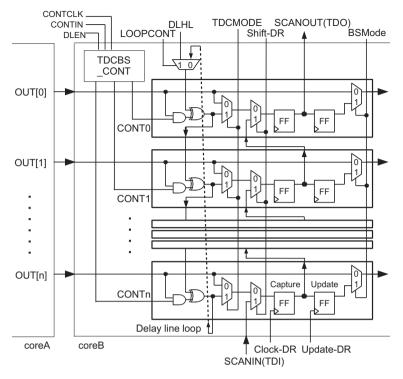

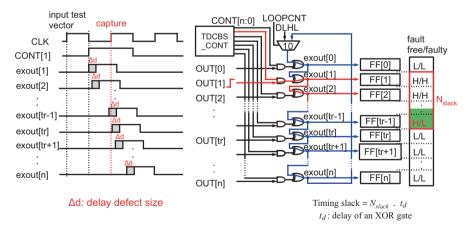

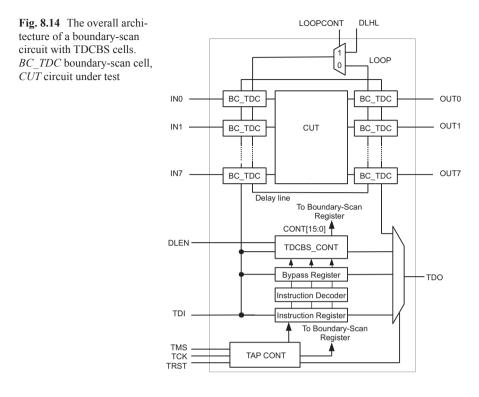

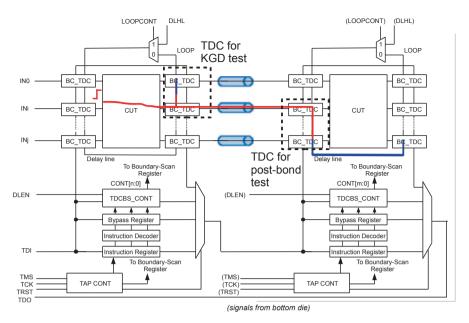

|   | 8.6                                                                                           |          |             | nent Circuits for Detecting TSV Delay Faults    | 25       |  |  |  |  |  |  |  |

|   | 8.6.1 Application of Time-to-Digital Converter                                                |          |             |                                                 |          |  |  |  |  |  |  |  |

|   | 8.6.1 Application of Time-to-Digital Converter<br>Embedded in Boundary Scan for 3D-IC Testing |          |             |                                                 |          |  |  |  |  |  |  |  |

|   |                                                                                               | 8.6.2    |             | leasurement Circuit Using the                   | 25       |  |  |  |  |  |  |  |

|   |                                                                                               | 8.0.2    | •           | Delay Line                                      | 25       |  |  |  |  |  |  |  |

|   |                                                                                               | 8.6.3    |             | on of Defect Size Detectable by the Test Method | 25       |  |  |  |  |  |  |  |

|   |                                                                                               | 8.6.4    |             | 5                                               | 23<br>25 |  |  |  |  |  |  |  |

|   | 07                                                                                            |          |             | y                                               | 25       |  |  |  |  |  |  |  |

|   | 8.7                                                                                           |          |             | connect Tests of Open Defects in a              | 25       |  |  |  |  |  |  |  |

|   |                                                                                               |          |             | uilt-In Supply Current Test Circuit             | 25       |  |  |  |  |  |  |  |

|   |                                                                                               | 8.7.1    |             | al Tests with a Built-In Supply                 | 25       |  |  |  |  |  |  |  |

|   |                                                                                               | 070      |             | Test Circuit                                    | 25       |  |  |  |  |  |  |  |

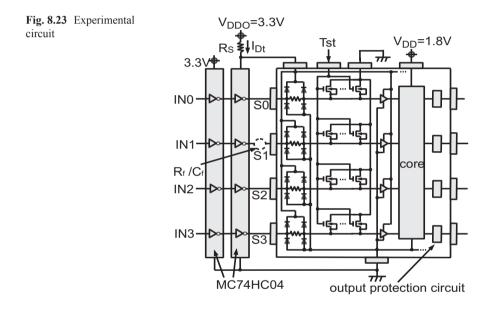

|   |                                                                                               | 8.7.2    | -           | nental Evaluation of Our Electrical Test Method | 26       |  |  |  |  |  |  |  |

|   | <b>D</b> 0                                                                                    | 8.7.3    |             | у                                               | 26<br>26 |  |  |  |  |  |  |  |

|   | References                                                                                    |          |             |                                                 |          |  |  |  |  |  |  |  |

| • |                                                                                               |          |             |                                                 |          |  |  |  |  |  |  |  |

| 9 |                                                                                               |          |             | t at ASET                                       | 26       |  |  |  |  |  |  |  |

|   |                                                                                               |          |             | ufumi Kobayashi, Fumiaki Yamada, Haruo          |          |  |  |  |  |  |  |  |

|   |                                                                                               |          |             | Jchiyama, Kenichi Takeda, Kenichi Osada,        |          |  |  |  |  |  |  |  |

|   |                                                                                               |          |             | Fumihiko Nakazawa                               |          |  |  |  |  |  |  |  |

|   | 9.1                                                                                           |          |             | panese 3D Integration Technology Research       |          |  |  |  |  |  |  |  |

|   |                                                                                               |          | evelopme    | nt Project (Dream Chip)                         | 27       |  |  |  |  |  |  |  |

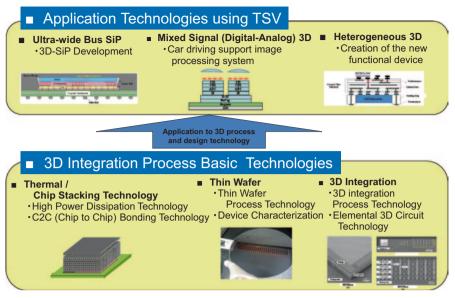

|   |                                                                                               | 9.1.1    |             | gration Process Basic Technologies              | 27       |  |  |  |  |  |  |  |

|   |                                                                                               |          | 9.1.1.1     | Thermal Management and Chip-Stacking            | -        |  |  |  |  |  |  |  |

|   |                                                                                               |          |             | Technology                                      | 27       |  |  |  |  |  |  |  |

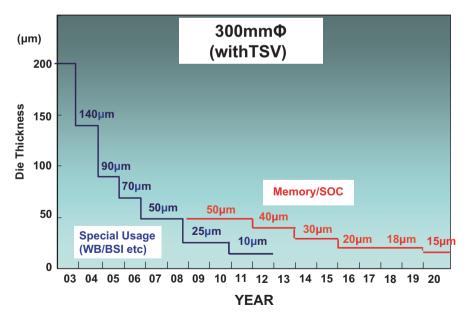

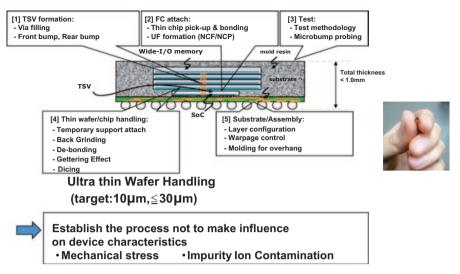

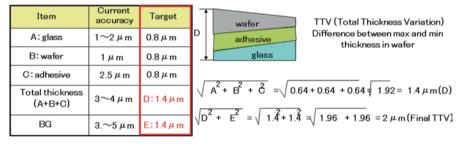

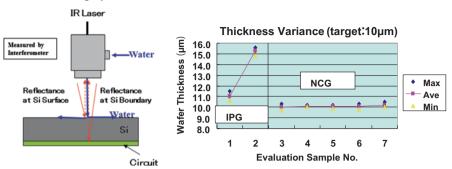

|   |                                                                                               |          | 9.1.1.2     | Thin-Wafer Technology                           | 27       |  |  |  |  |  |  |  |

|             |       | 9.1.1.3  | 3D Integration Technology                   | 271   |

|-------------|-------|----------|---------------------------------------------|-------|

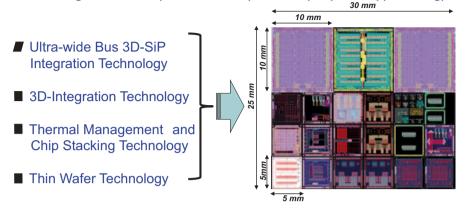

|             | 9.1.2 | Applicat | tion Technologies                           | 272   |

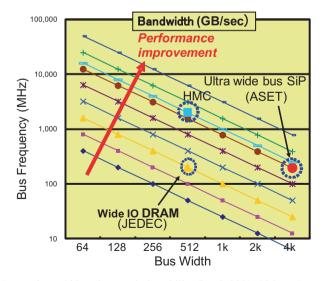

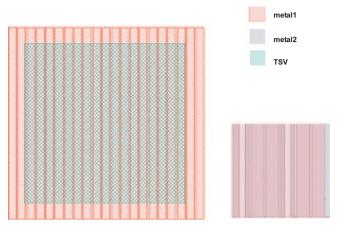

|             |       | 9.1.2.1  | Ultrawide Bus 3D-SiP Integration Technology | 272   |

|             |       | 9.1.2.2  |                                             |       |

|             |       |          | Integration Technology for Automotive       |       |

|             |       |          | Application                                 | 272   |

|             |       | 9.1.2.3  | Heterogeneous 3D Integration Technology     |       |

|             |       |          | for Radio Frequency Microelectromechan-     |       |

|             |       |          | ical Systems                                | 272   |

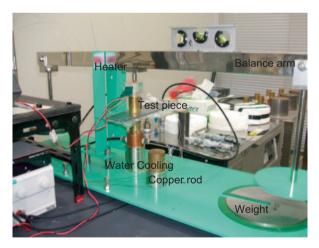

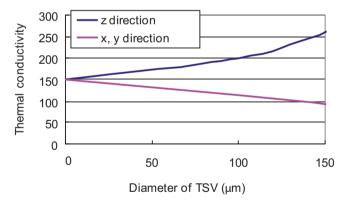

| 9.2         | Therm | al Manag | gement and Chip-Stacking Technology         | 273   |

| ·. <u>-</u> | 9.2.1 |          | ound                                        | 273   |

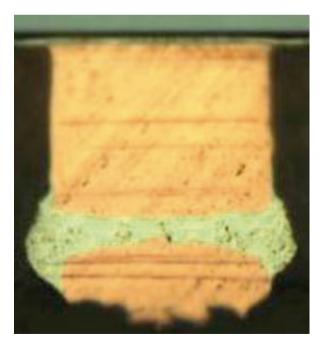

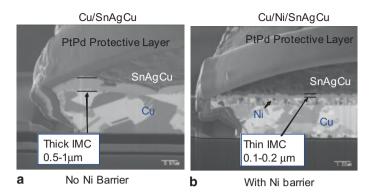

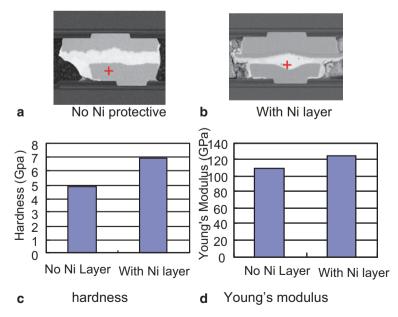

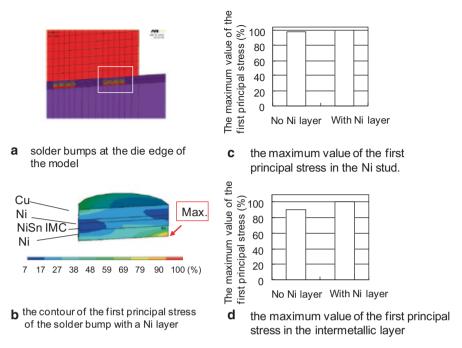

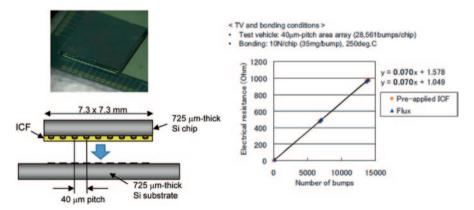

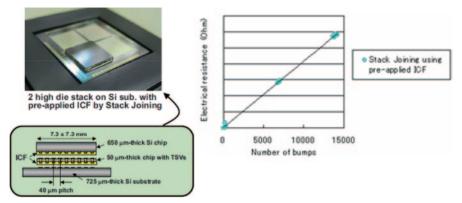

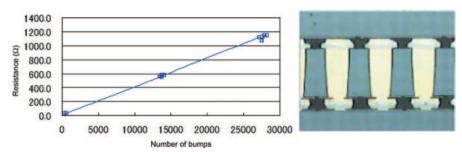

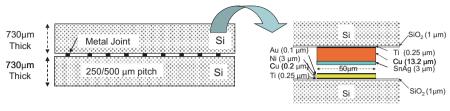

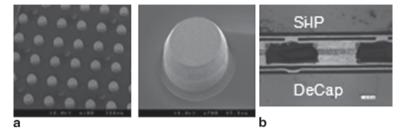

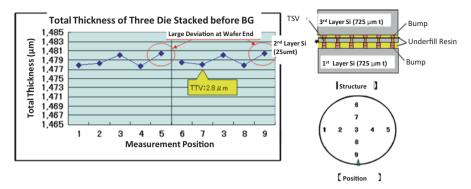

|             | 9.2.2 |          | acking/Joining Technology                   | 273   |

|             | 9.2.2 | 9.2.2.1  |                                             |       |

|             |       | 9.2.2.1  | 1                                           |       |

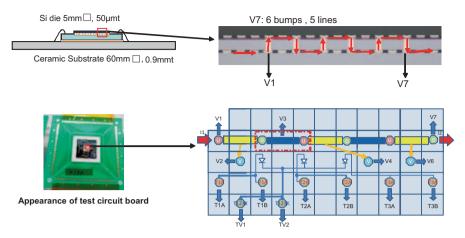

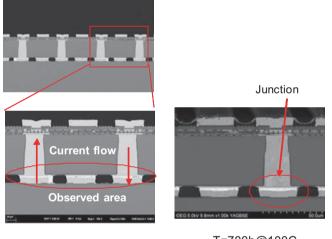

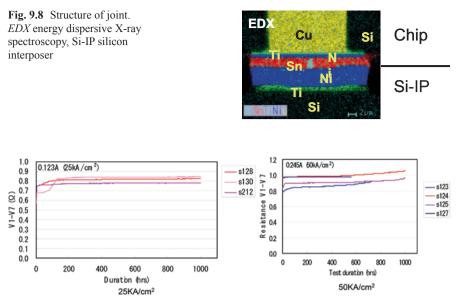

|             |       | 9.2.2.2  | Electromigration Test to Understand the     | 277   |

|             |       | 9.2.2.5  | Current Density of Micro-bump Joint         | 276   |

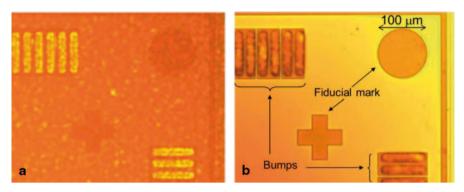

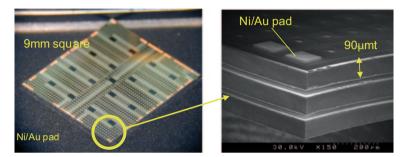

|             |       | 9.2.2.4  | Flip Chip Bonding Density Towards           | 270   |

|             |       | 9.2.2.4  | 10-μm Connection Bump Pitch                 | 277   |

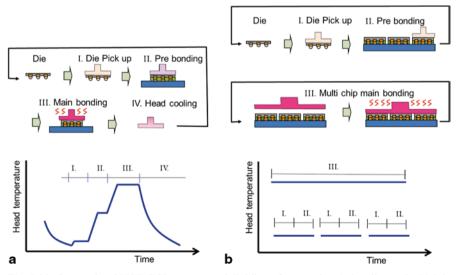

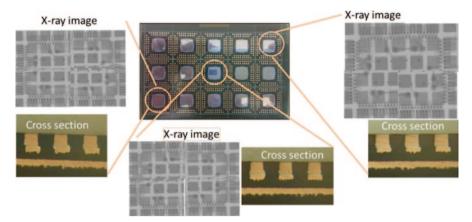

|             |       | 9.2.2.5  | Stack and Gang Bonding                      | 285   |

|             |       | 9.2.2.3  |                                             | 283   |

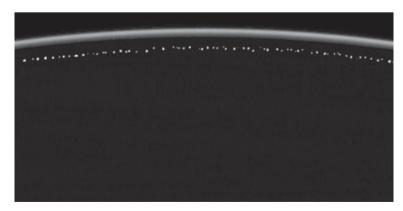

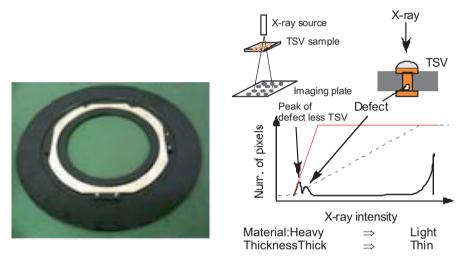

|             |       | 9.2.2.0  | Nondestructive Inspection Technologies of   | 207   |

|             | 0.2.2 | These    | Micro-joint                                 | 287   |

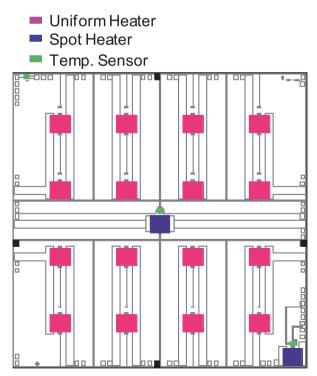

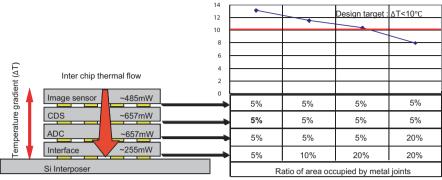

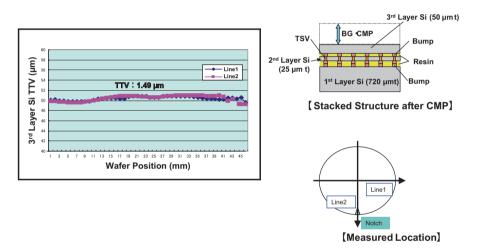

|             | 9.2.3 | 9.2.3.1  | Management Study                            | 292   |

|             |       | 9.2.3.1  | 6, 6                                        | 202   |

|             |       | 0 2 2 2  | Chip Stack                                  | 292   |

|             |       | 9.2.3.2  | TV200 Measurement Result and Correla-       | 20.4  |

|             |       |          | tion with Simulation                        | 294   |

|             |       | 9.2.3.3  | Thermal Conductivity Anisotropy Induced     | • • • |

|             |       |          | by Cu TSV                                   | 295   |

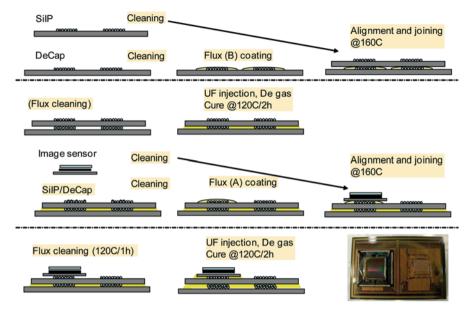

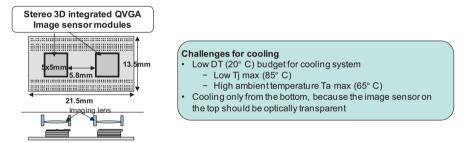

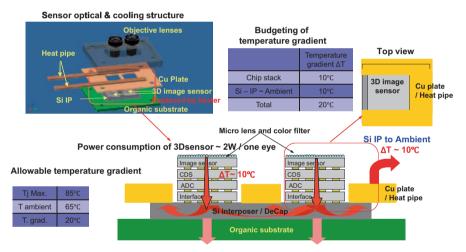

|             | 9.2.4 |          | ment of Automobile Drive Assistance Camera  | 295   |

|             |       |          | Development of Integration Process          | 295   |

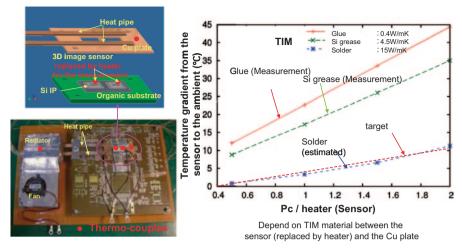

|             |       | 9.2.4.2  | Development of Cooling System for           |       |

|             |       |          | Automobile Drive Assistance Camera          | 297   |

|             | 9.2.5 |          | ry                                          | 300   |

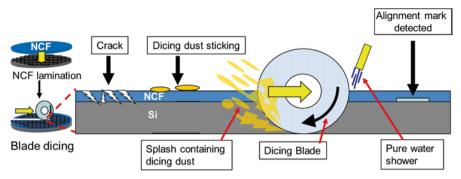

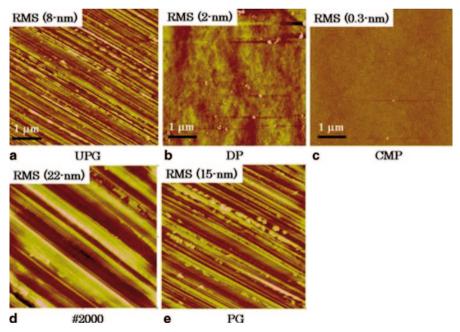

| 9.3         |       |          | hnology                                     | 302   |

|             | 9.3.1 | Backgro  | ound of Wafer Thinning Technology           | 302   |

|             | 9.3.2 | Issues o | f Wafer Thinning                            | 303   |

|             | 9.3.3 |          | n Wafer Thinning Process                    |       |

|             |       |          | Wafer Support System                        | 303   |

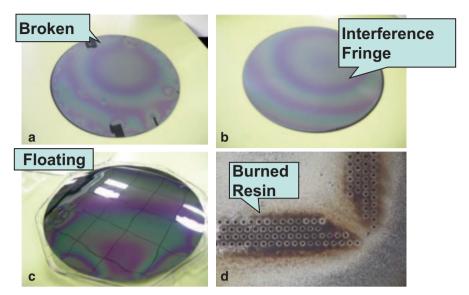

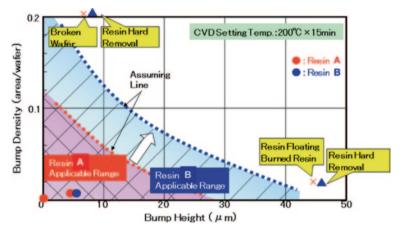

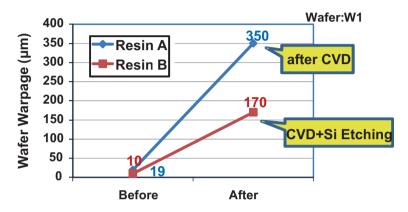

|             |       | 9.3.3.2  | Heat Resistance of the Resin Used for       |       |

|             |       |          | WSS Temporary Bonding                       | 307   |

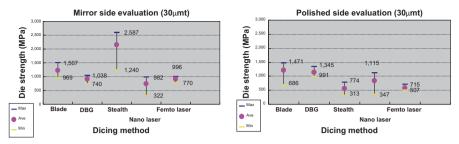

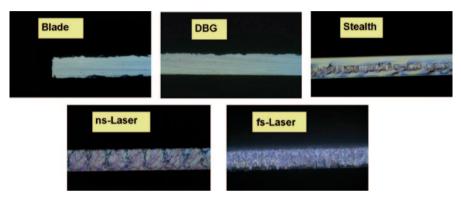

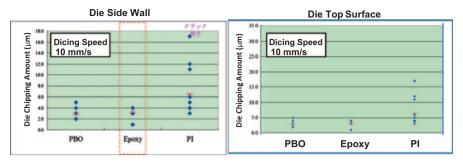

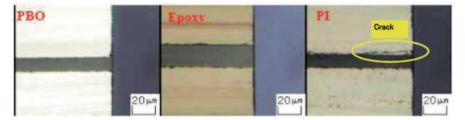

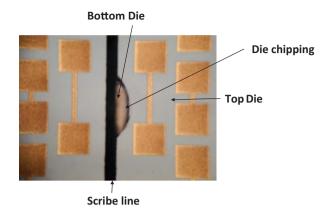

|             |       | 9.3.3.3  | Dicing Technology of Thin Chips             | 310   |

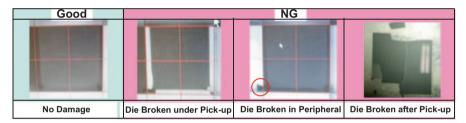

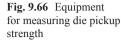

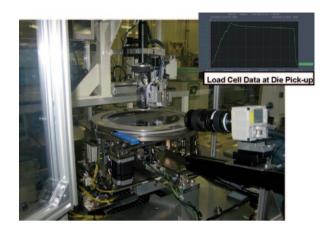

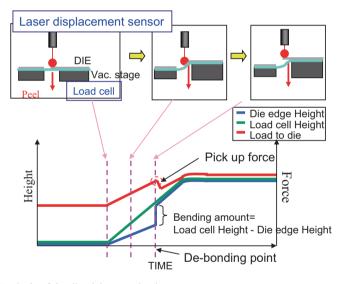

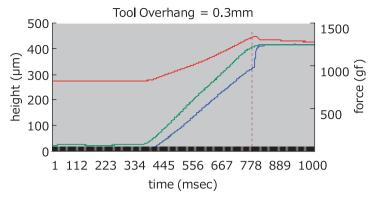

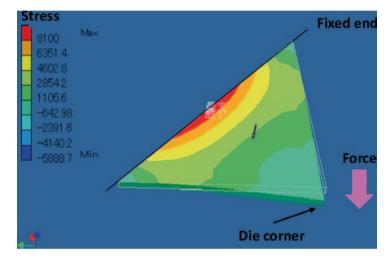

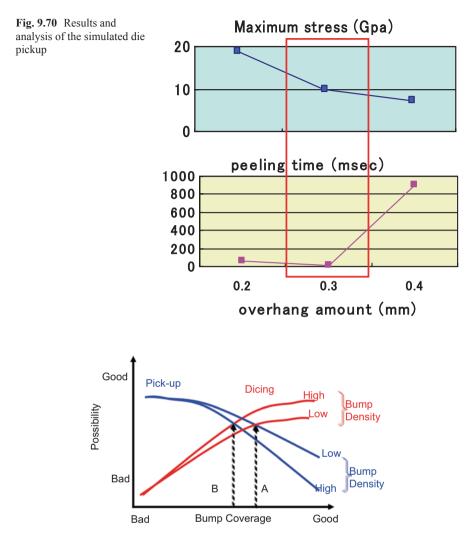

|             |       | 9.3.3.4  | Die Pickup Technology of Thin Chips         | 311   |

|             |       | 9.3.3.5  | Thin Wafer Processing Technique in the      |       |

|             |       |          | Wafer-Stacking Process                      | 317   |

|             |       |          |                                             |       |

|     | 9.3.4         | Issues i        | n the Prevention of Device Characteristic        |     |

|-----|---------------|-----------------|--------------------------------------------------|-----|

|     |               | Change          | s and Metal Contamination During Wafer Thinning. | 321 |

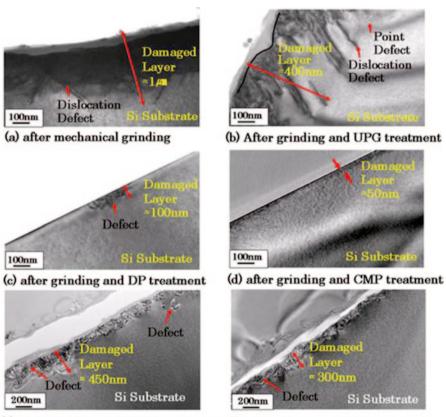

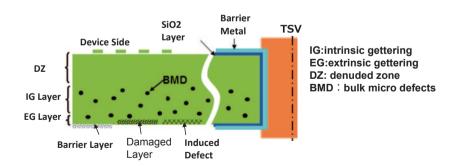

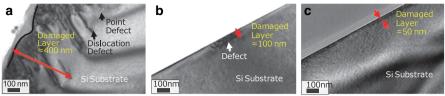

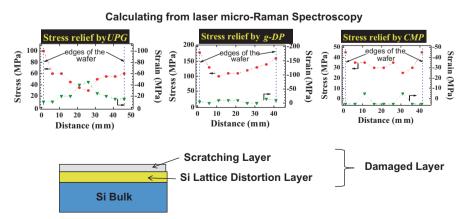

|     |               | 9.3.4.1         | Evaluation of Crystal Defects and Metal          |     |

|     |               |                 | Pollution in the Thin Wafer                      | 322 |

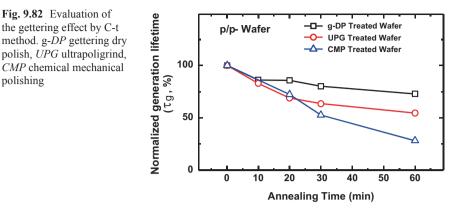

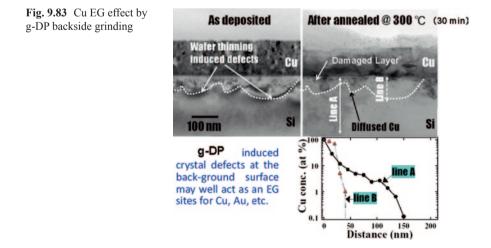

|     |               | 9.3.4.2         | Backside Grinding Methods and                    |     |

|     |               |                 | Their EG Effect                                  | 322 |

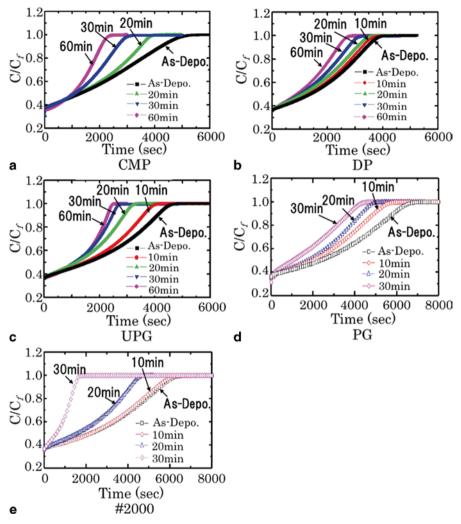

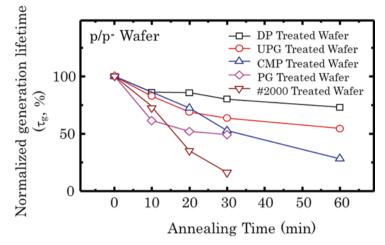

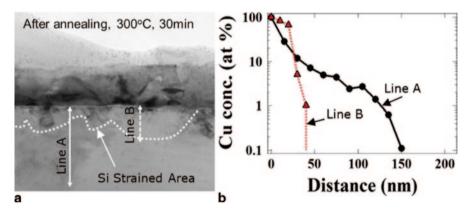

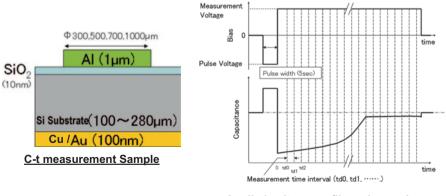

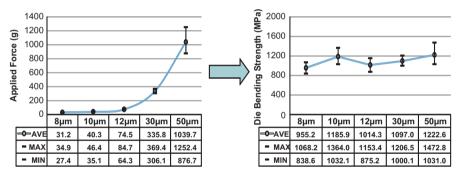

|     |               | 9.3.4.3         | Variation of Electrical Characteristics          |     |

|     |               |                 | with Mechanical Stress                           | 325 |

|     | 9.3.5         | Standar         | dization                                         | 329 |

|     | 9.3.6         |                 | ry                                               | 330 |

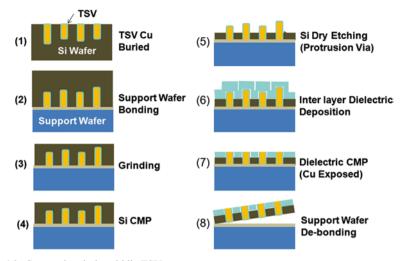

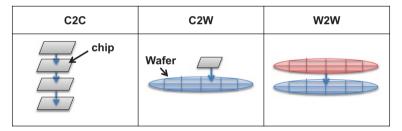

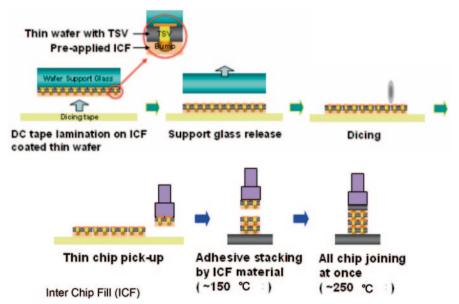

| 9.4 | 3D Int        |                 | Technology                                       | 331 |

|     | 9.4.1         |                 | bund and Scope                                   | 331 |

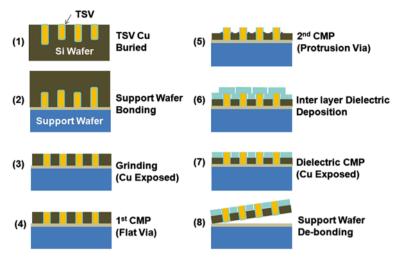

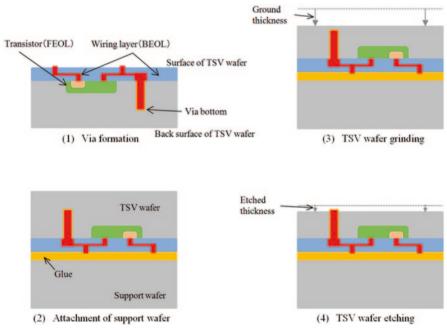

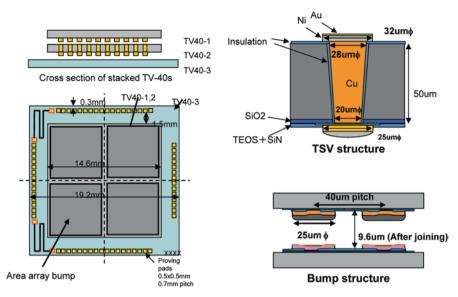

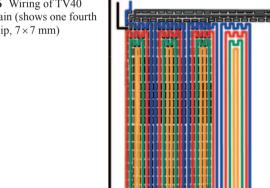

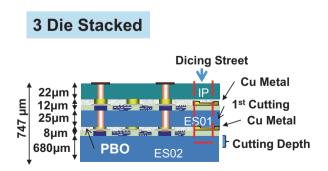

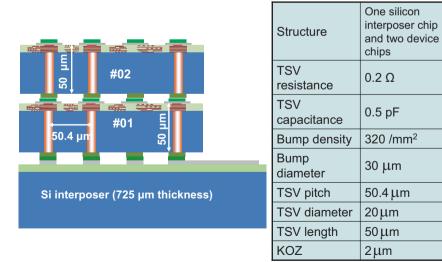

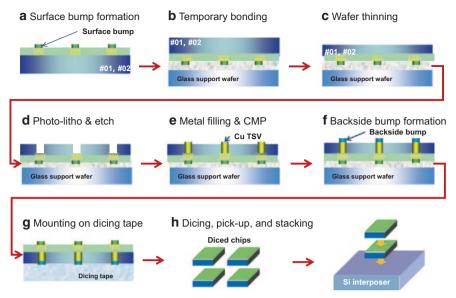

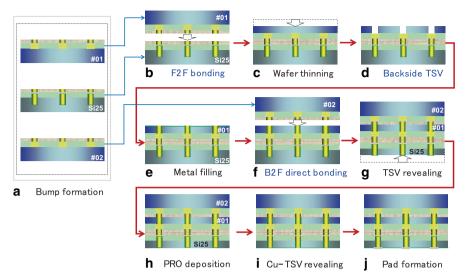

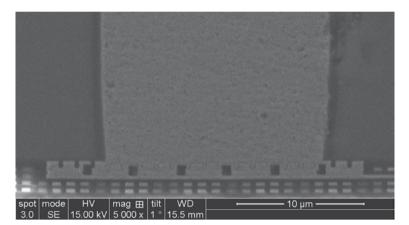

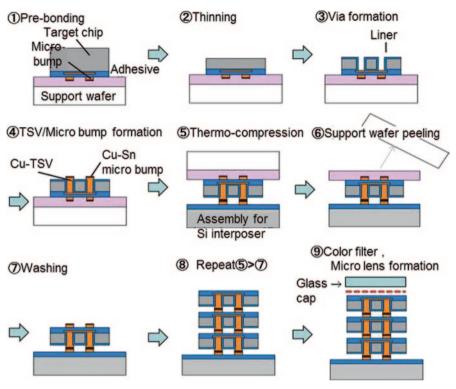

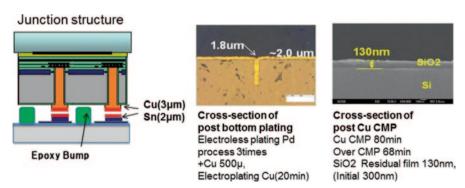

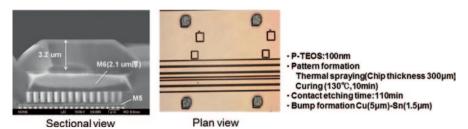

|     | 9.4.2         |                 | Docess                                           | 332 |

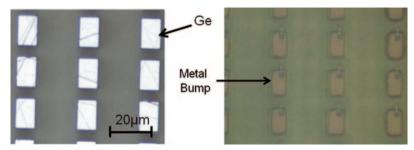

|     |               | 9.4.2.1         |                                                  | 332 |

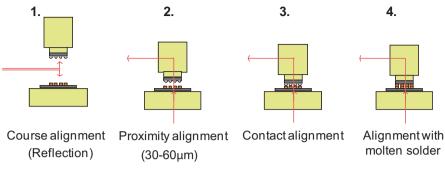

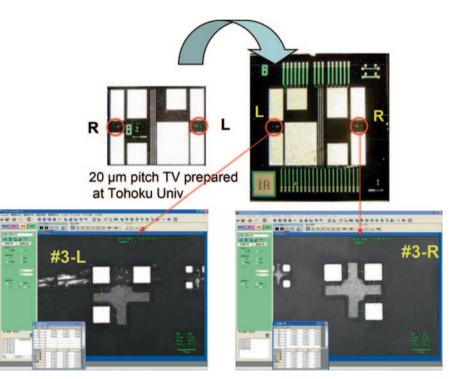

|     |               | 9.4.2.2         | •                                                | 334 |

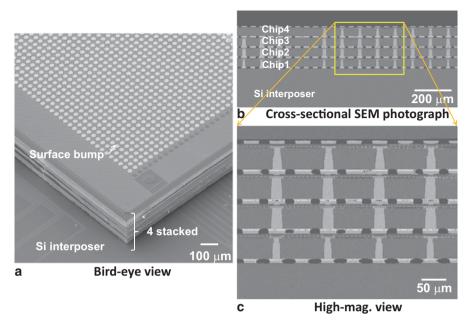

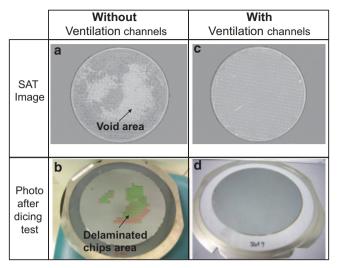

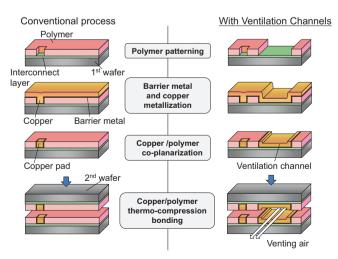

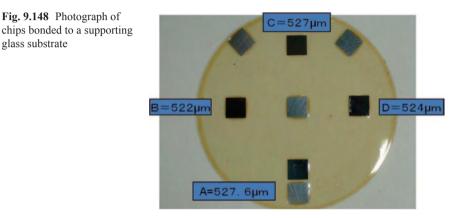

|     | 9.4.3         | W2W P           | rocess                                           | 338 |

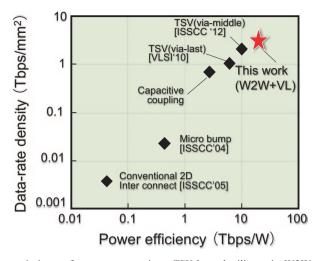

|     |               |                 | W2W Integration Overview                         | 338 |

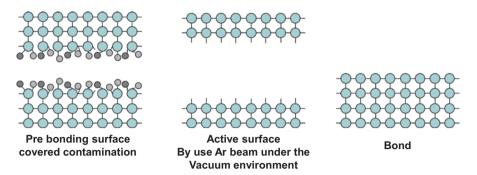

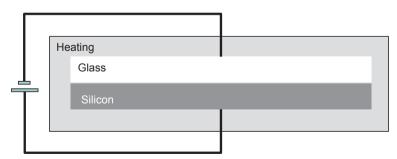

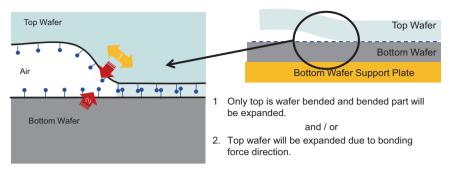

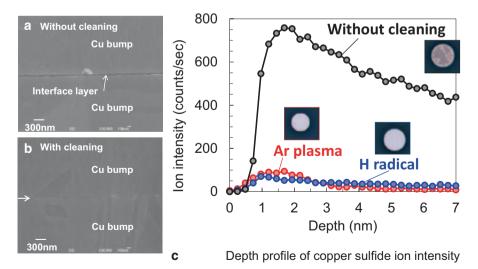

|     |               |                 | Wafer Bonding Technology                         | 342 |

|     |               |                 | W2W Integration Results                          | 345 |

|     | 9.4.4         |                 | dization                                         | 350 |

|     |               | 9.4.4.1         |                                                  |     |

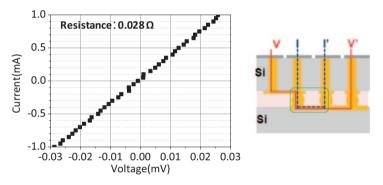

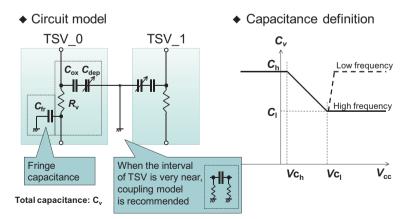

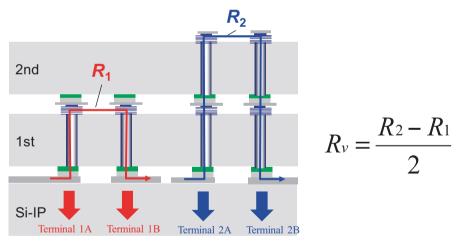

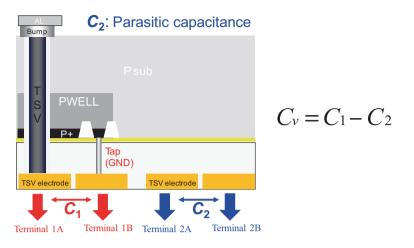

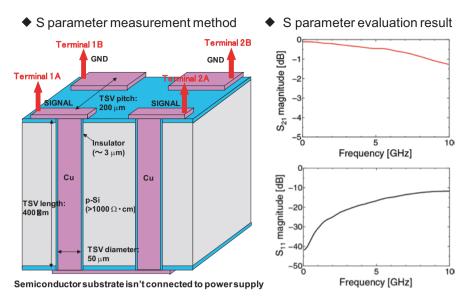

|     |               |                 | acteristics and Guideline of Test Conditions     | 350 |

|     | 9.4.5         | Summa           | ry                                               | 355 |

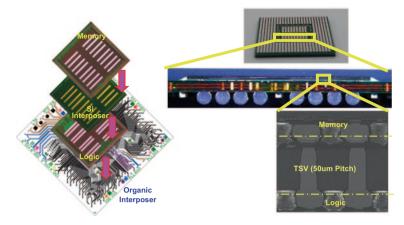

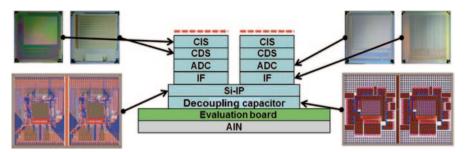

| 9.5 |               |                 | 3D System in Package Technology                  | 356 |

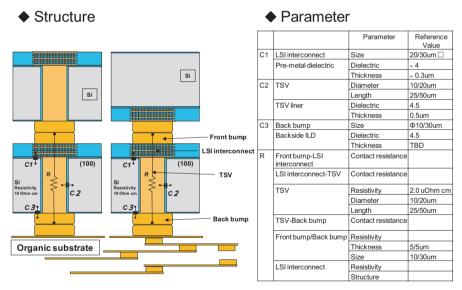

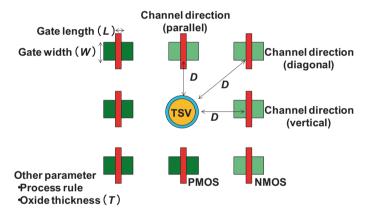

|     | 9.5.1         |                 | ound                                             | 356 |

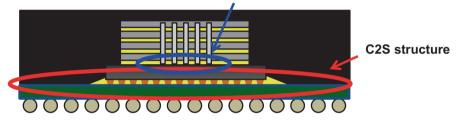

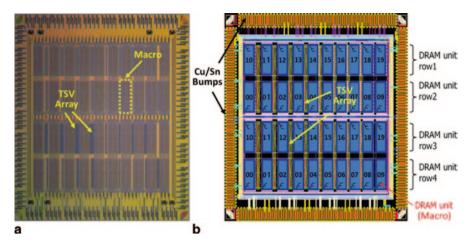

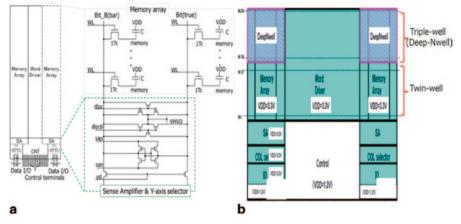

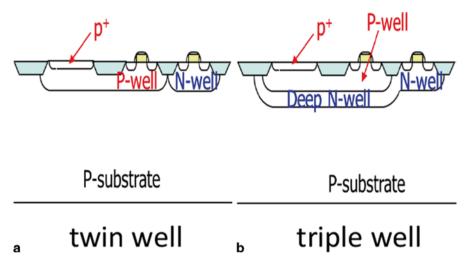

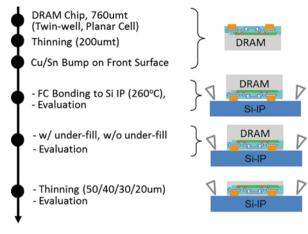

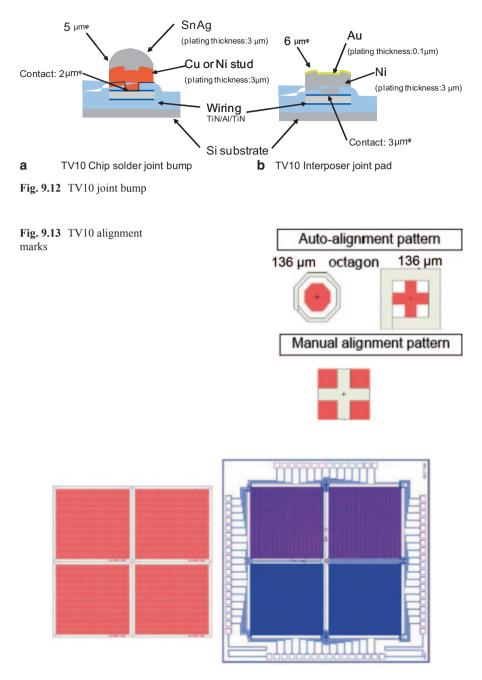

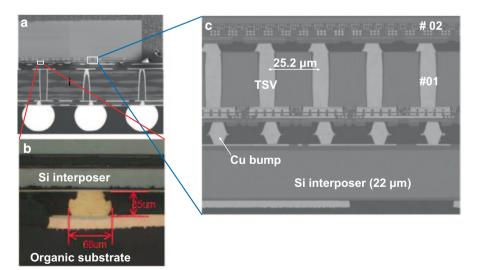

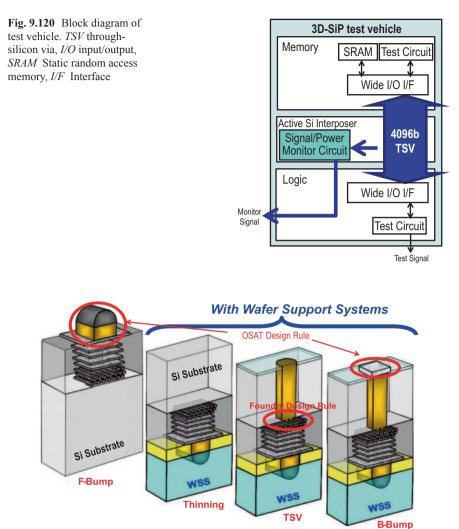

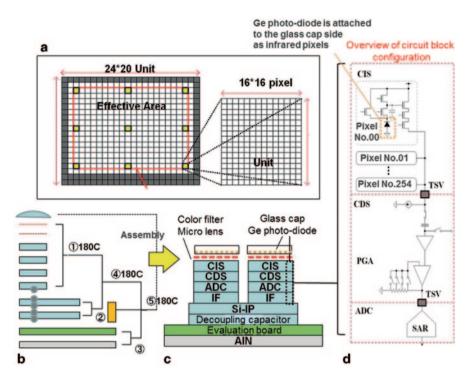

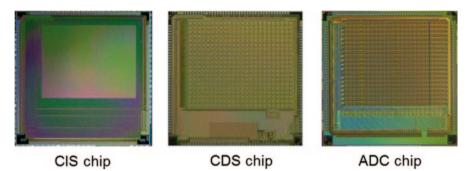

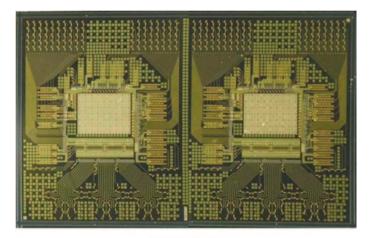

|     | 9.5.2         | 0               | t Vehicle Fabrication                            | 357 |

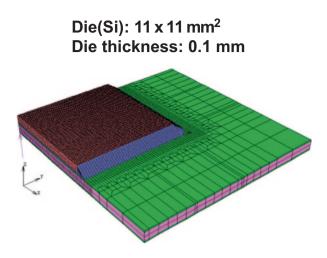

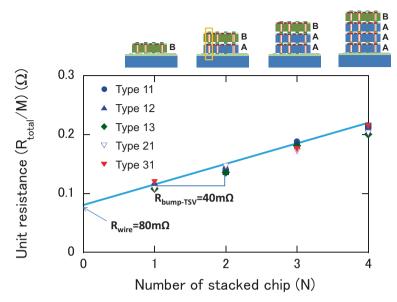

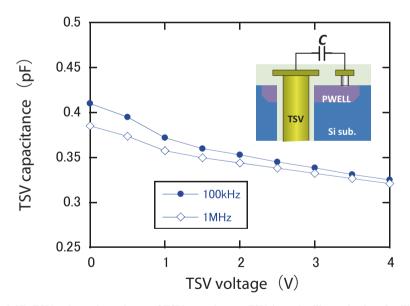

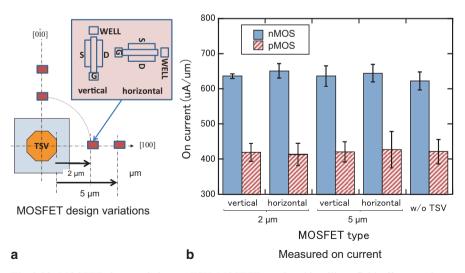

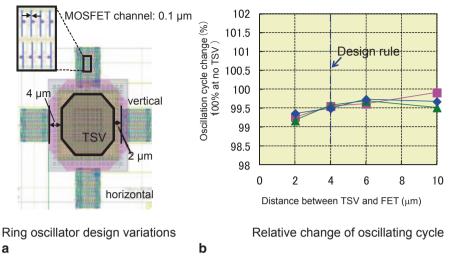

|     | 9.5.3         |                 | ion                                              | 360 |

|     | 9.5.4         |                 | ry                                               | 369 |

| 9.6 |               |                 | Digital and Analog) 3D Integration               |     |

|     |               |                 | Automotive Applications                          | 369 |

|     | 9.6.1         |                 | ction                                            | 369 |

|     | 9.6.2         |                 | ges                                              | 370 |

|     | 9.6.3         |                 | of Development of Mixed-Signal 3D Inte-          |     |

|     | ,             |                 | Technology                                       | 371 |

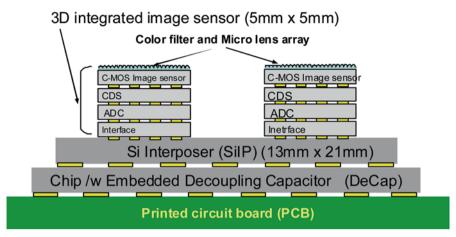

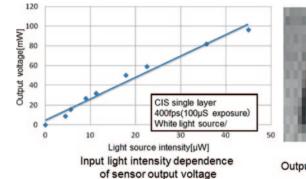

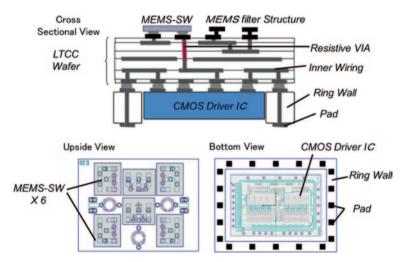

|     |               | 9.6.3.1         |                                                  | 57. |

|     |               | 2.0.0.1         | Integrated Imaging Sensor Module for             |     |

|     |               |                 | In-Vehicle Support Systems                       | 371 |

|     |               | 9.6.3.2         | 11 9                                             | 571 |

|     |               | 9.0.3. <b>2</b> | Integrated Structure with TSV Connection         | 373 |

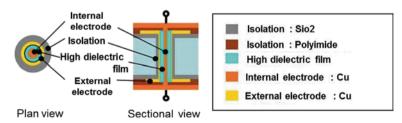

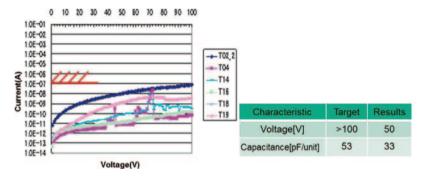

|     |               | 9.6.3.3         | Development of an Si Interposer with             | 512 |

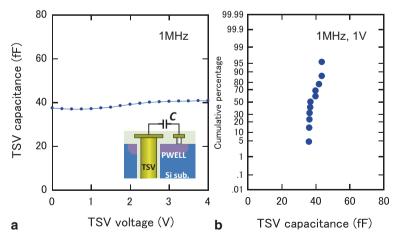

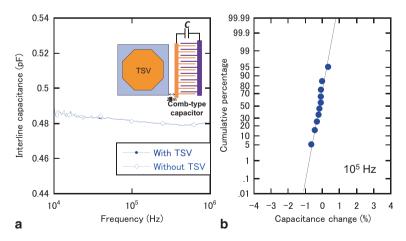

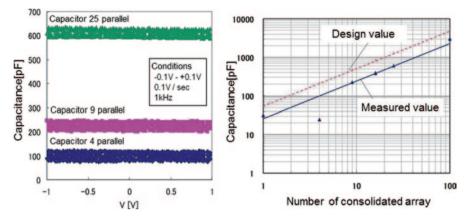

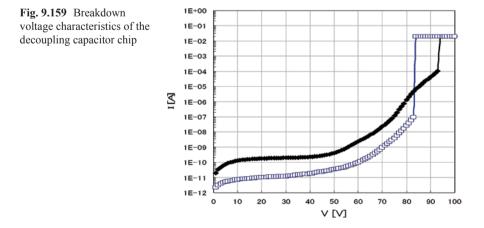

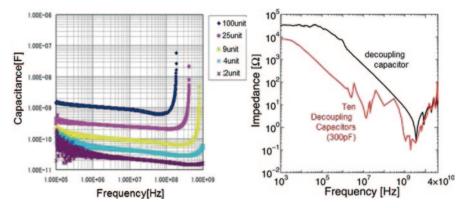

|     |               | 9.0.5.5         | TSV-Type Decoupling Capacitor                    | 379 |

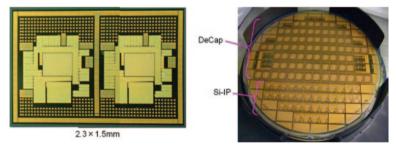

|     |               | 9.6.3.4         | A Trial Production and Evaluation of the         | 515 |

|     |               | 7.0.J. <b>⊤</b> | Driving-Assistance Image-Processing Sys-         |     |

|     |               |                 | tem for Automobiles                              | 383 |

|     | 9.6.4         | Conclus         | sion                                             | 384 |

|     | <i>у</i> .0.т | Concius         | 1011                                             | 504 |

| 9.7.1      | Backgro | ound and Issues                         |

|------------|---------|-----------------------------------------|

| 9.7.2      | Develop | oment Result                            |

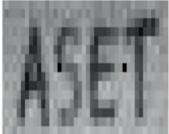

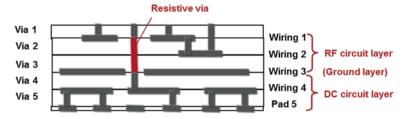

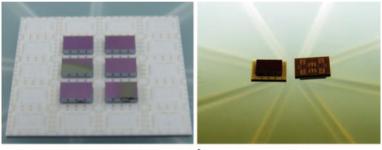

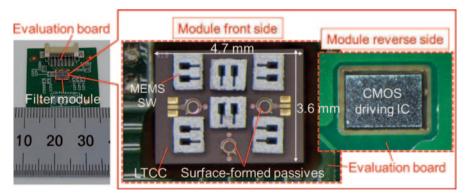

|            | 9.7.2.1 | Structure of 3D Integration RF Module   |

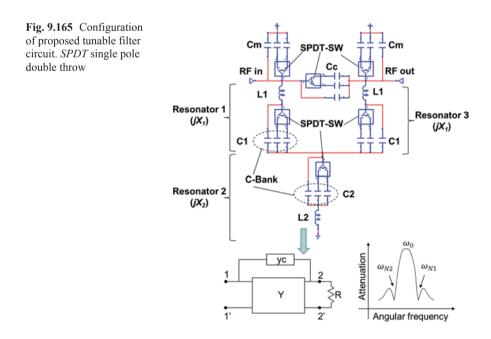

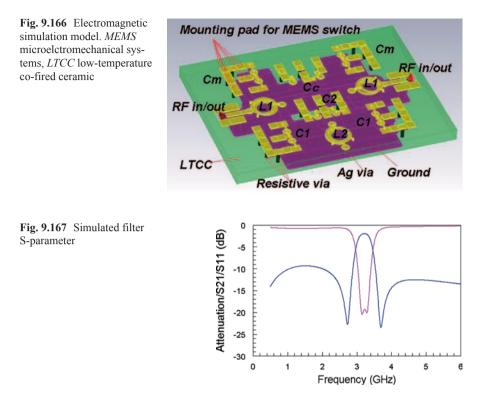

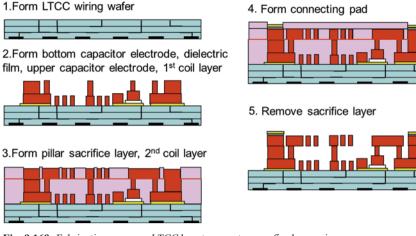

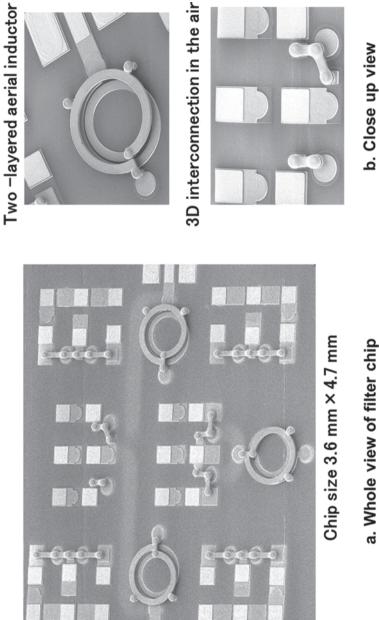

|            | 9.7.2.2 | MEMS Tunable Filter                     |

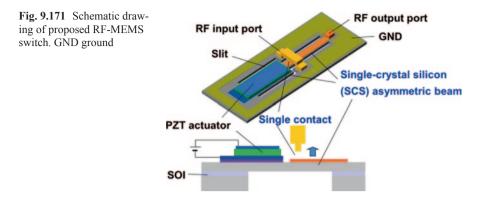

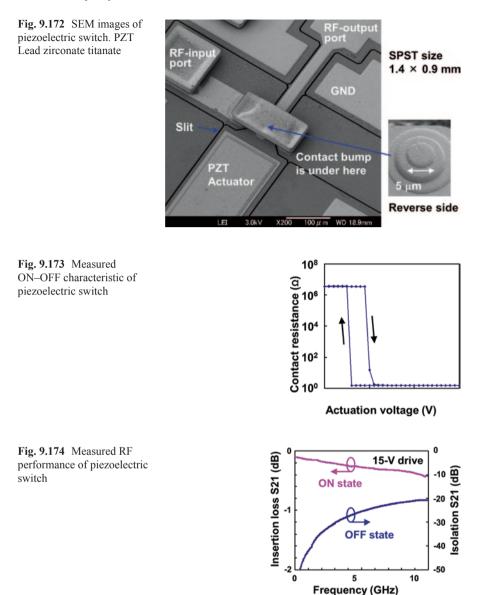

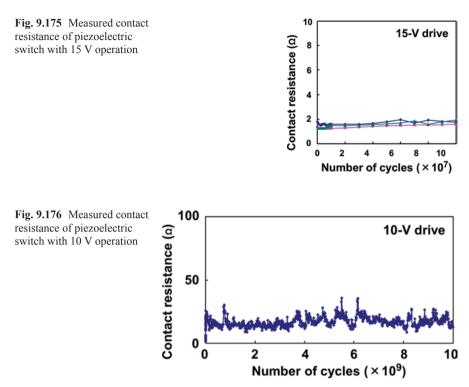

|            | 9.7.2.3 | MEMS Switch                             |

|            | 9.7.2.4 | CMOS Driving IC                         |

|            | 9.7.2.5 | 3D Integration of Tunable Filter Module |

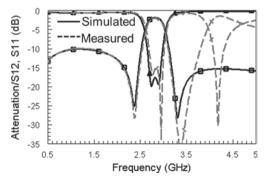

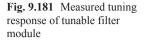

|            | 9.7.2.6 | RF and Tuning Performances of the       |

|            |         | Fabricated 3D Tunable Filter Module     |

| 9.7.3      | Summa   | ſy                                      |

| References |         | -                                       |

# Contributors

Tsubasa Bandoh Okamoto Machine Tool Works, Ltd., Annaka, Gunma, Japan Raleigh Estrada Carl Zeiss X-ray Microscopy Inc., Pleasanton, CA, USA Michael Feser Carl Zeiss X-ray Microscopy Inc., Pleasanton, CA, USA Gilles Fresquet FOGALE nanotech, NÎMES, France Hiroaki Fusano 3DI Dept. ATS BU, Tokyo Electron Ltd., Tokyo, Japan Allen Gu Carl Zeiss X-ray Microscopy Inc., Pleasanton, CA, USA Takashi Haimoto Dicer Grinder Marketing Team, Marketing Group, Sales Engineering Division, DISCO Corporation, Ota-ku, Tokyo, Japan Masaki Hashizume The University of Tokushima, Tokushima, Japan Yoshinobu Higami Ehime University, Ehime, Japan Yoshihito Inaba Hitachi Chemical Co., Ltd., Ibaraki, Japan Toshihiro Ito Okamoto Machine Tool Works, Ltd., Annaka, Gunma, Japan Bruce Johnson Carl Zeiss X-ray Microscopy Inc., Pleasanton, CA, USA Morihiro Kada Osaka Prefecture University, Osaka, Japan The National Institution of Advanced Industrial Science and Technology (AIST), Ibaraki, Japan Tadashi Kamada DENSO Corp., Aichi, Japan Shuichi Kameyama Fujitsu Limited, Kanagawa, Japan Harufumi Kobayashi Lapis Semiconductor, Kanagawa, Japan Kazuo Kondo Osaka Prefecture University, Osaka, Japan Mitsuma Koyanagi NICHe, Tohoku University, Miyagi, Japan Yutaka Kusuda R&D Division, SAMCO Inc., Kyoto, Japan

Contributors

Kangwook Lee NICHe, Tohoku University, Miyagi, Japan

**Shyue-Kung Lu** National Taiwan University of Science and Technology, Taipei, Taiwan (R.O.C.)

Takahiko Mitsui Okamoto Machine Tool Works, Ltd., Annaka, Gunma, Japan

Fumihiko Nakazawa FUJITSU LABORATORIES LTD., Kanagawa, Japan

Tomoyuki Nonaka R&D Division, SAMCO Inc., Kyoto, Japan

Toshihisa Nonaka Toray Research Center, Inc. (TRC), Shiga, Japan

Kenichi Osada Hitachi Ltd., Tokyo, Japan

Sylvain Perrot FOGALE nanotech, NÎMES, France

Jean-Philippe Piel FOGALE nanotech, NÎMES, France

Zvi Roth Florida Atlantic University, Boca Raton, FL, USA

Kazuta Saito 53M Japan Limited, Sagamihara-shi, Kanagawa, Japan

Itsuko Sakai Graduate School of Engineering, Nagoya University, Nagoya, Japan

Osamu Sato Lasertec Corporation, Yokohama, Japan

Makoto Sekine Graduate School of Engineering, Nagoya University, Nagoya, Japan

Haruo Shimamoto Advanced Industrial Science and Technology (AIST), Ibaraki, Japan

Hiroshi Takahashi Computer Science, Graduate School of Science and Engineering, Ehime University, Ehime, Japan

Kenichi Takeda Hitachi Ltd., Tokyo, Japan

Hideo Takizawa Lasertec Corporation, Yokohama, Japan

Masahiko Tanaka SPP Technologies Co., Ltd., Amagasaki, Hyogo, Japan

Yoshitaka Tatsumoto Lasertec Corporation, Yokohama, Japan

Osamu Tsuji R&D Division, SAMCO Inc., Kyoto, Japan

Shiro Uchiyama Micron Memory Japan, Kanagawa, Japan

Senling Wang Ehime University, Ehime, Japan

Fumiaki Yamada IBM Research, Tokyo, Japan

Eiichi Yamamoto Okamoto Machine Tool Works, Ltd., Annaka, Gunma, Japan

Masahiro Yamamoto 3DI Dept. ATS BU, Tokyo Electron Ltd., Minato-ku, Tokyo, Japan

Tsuyoshi Yoshida Okamoto Machine Tool Works, Ltd., Annaka, Gunma, Japan

Hiroyuki Yotsuyanagi The University of Tokushima, Tokushima, Japan

# **About the Editors**

**Dr. Kazuo Kondo** is a professor in the Department of Chemical Engineering, Osaka Prefecture University. He received his Ph.D. in chemical engineering from the University of Illinois in 1981. He has worked for Sumitomo Metal Industries, Hokkaido University, and Okayama University. He has 200 research publications and 100 patents. His major research is Copper Electrodeposition for TSV. His research extends to various fields, not only in electrodeposition but also in battery science and CVD. He is a member of the Electrochemical Society, IEEE, the Society of Chemical Engineering, Japan, the Japanese Institute of Electronics Packaging, the Surface Finishing Society of Japan, Material Japan, Electrochemistry Japan and the Japanese Society of Applied Physics.

**Morihiro Kada** is an invited researcher of the National Institute of Advanced Industrial Science and Technology (AIST) and a part-time researcher at Osaka Prefecture University. Prior to joining AIST and the university, he headed the Japanese national research and development project on semiconductor 3D-Integration technology in the Association of Super-Advanced Electronics Technologies (ASET). He has also been the general manager of the Advanced Packaging Development Department in Sharp Corporation. He received his B.E. in applied physics from Fukui University, Japan in 1970. He has more than 40 years of experience in semiconductor packaging engineering, with major emphasis on developing chip scale, chip stack package, and three-dimensional-system-in-package (3D-SiP), and is the global pioneer of 3D-Integration technology in the world.

**Dr. Kenji Takahashi** is a chief specialist at Memory Packaging Development Department, Memory Division, Semiconductor and Storage Company, Toshiba Corporation. He received an M.E. in chemical engineering from the University of Tokyo in 1984 and a Ph.D. in information science and electrical engineering from Kyushu University in 2010. His major research and development focuses on semiconductor packaging and chip package interaction, especially through-silicon via technology. He was the research manager of the Electronic System Integration Technologies (ASET). He is a senior member of IEEE, and a member of the Society for Chemical Engineers, Japan; the Institute of Electronics, Information and Communication Engineers; and the Japanese Institute of Electronics Packaging.

# Chapter 1 Research and Development History of Three-Dimensional Integration Technology

Morihiro Kada

# 1.1 Introduction

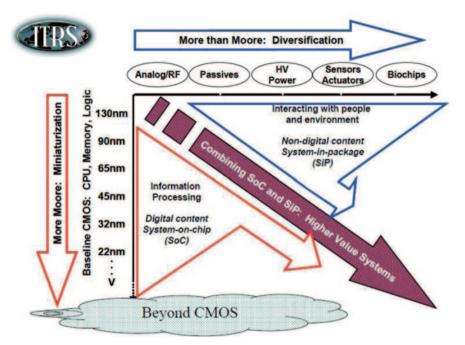

Semiconductor integrated circuits have been developed according to Moore's law; the conjecture made in 1965 was that the number of transistors in a dense integrated circuit (IC) will double every 2 years, and the industry has developed according to this trend [1]. Two different concepts have been proposed for future advancements. One is "More Moore," which suggests that technological progress will continue to follow scaling theory, and the other is termed "More than Moore," which emphasizes the evolution and diversification of function [2].

# 1.1.1 The International Technology Roadmap for Semiconductors

The international semiconductor research community gathered in 2005, at the abovementioned meeting (the International Technology Roadmap for Semiconductors, ITRS), which led to the concept of "More than Moore." Two years later, at ITRS 2007, a number of such ideas were formally defined. We elaborate on two of these: scaling and functional diversification with reference to Fig. 1.1.

- 1. Scaling: Fig. 1.1, vertical axis of "More Moore"

- a. *Geometrical scaling:* Also referred to as constant field scaling, this design methodology involves reducing the horizontal and vertical dimensions of physical features of the on-chip logic and memory storage components to

M. Kada (🖂)

Osaka Prefecture University, Osaka, Japan e-mail: cmk26222@osakafu-u.ac.jp

The National Institution of Advanced Industrial Science and Technology (AIST), Ibaraki, Japan e-mail: m-kada@aist.go.jp

<sup>©</sup> Springer International Publishing Switzerland 2015 K. Kondo et al. (eds.), *Three-Dimensional Integration of Semiconductors*, DOI 10.1007/978-3-319-18675-7\_1

**Fig. 1.1** A diagrammatic representation of the concepts of "Moore's law" and "More than Moore". (Reproduced with permission from Ref. [3], Fig. 4). *RF* radio frequency, *CPU* central processing unit, *CMOS* complementary metal–oxide–semiconductor

improve density (cost per function reduction), performance (speed, power), and reliability (Fig. 1.1).

- b. *Equivalent scaling:* This approach refers to (a) three-dimensional (3D) device structure ("design factor") improvements as well as other nongeometric processing techniques and the use of new materials that affect the performance of the chip; (b) novel design techniques and technologies, such as multi-core design. Equivalent scaling occurs in conjunction with geometric scaling and aims for the continuation of "Moore's law."

- 2. Functional Diversification: Fig. 1.1, horizontal axis of "More than Moore."

Moore's law is not the only way to provide additional value to the end user. A complementary approach is that of functional diversification, which refers to the incorporation of new functionalities into devices that are not necessarily scalings of existing hardware or software. Typical of this "More than Moore" approach is the migration of non-digital functionalities (e.g., radio frequency (RF) communication, power control, passive components, sensors, and actuators) from the system board level into a particular chip-level (system on a chip; SoC) or package-level (system in package; SiP) implementation. As the need increases for evermore complex software to be embedded into SoCs and SiPs, the role of the software itself in performance scaling may also need to be considered. The objective of the "More than Moore" design methodology is to incorporate digital and non-digital functionalities into compact systems.

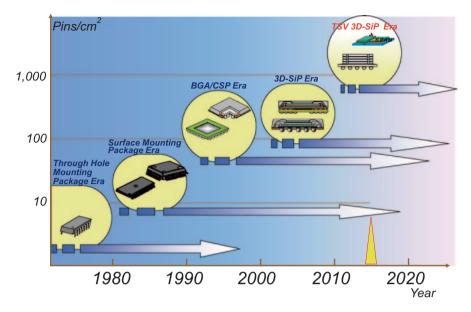

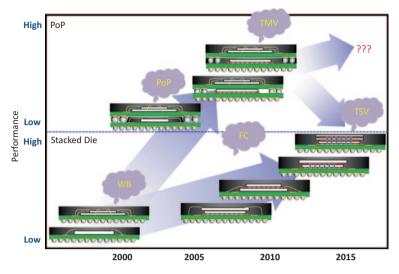

Fig. 1.2 Toward the new TSV 3D-SiP Era. *3D-SiP* three-dimensional system in package, *TSV* through-Si via, *BGA/CSP* ball grid array/chip-scale package

## 1.1.2 3D Integration Technology

Although 3D integration technology is not explicit in the definition of "More than Moore," it is generally considered to be one of the most important technology development strategies. The transistor scaling that has continued for more than 40 years is approaching the atomic level of silicon, and this physical limit will likely be reached in 10–15 years.

Entirely new device structures, such as carbon nanotubes, spintronics, and molecular switches are being developed to replace transistor technology. However, they will not be ready for 10–15 years. In the interim, 3D integration technology offers a viable solution for continued performance and economic advancement [4].

"More than Moore" is not just a solution to the limitation of "More Moore," it also recognizes the evolution and potential for improvements of packaging technology. Figure 1.2 illustrates the history of IC packaging technology. Every 10 years since the 1970s, packaging technology has undergone a technological revolution. The first decade of this century is the era of the 3D system in package (3D-SiP), and work has begun to develop new 3D technology termed through-Si via (TSV) that will define the present decade [5]. In TSV, the electrode passes completely through the silicon wafer (or chip). It represents the fusion of silicon wafer process technology (front end of line, FEOL) and semiconductor packaging technology (assembly/packaging).

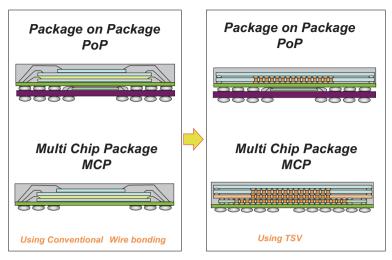

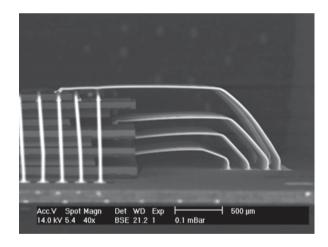

3D integration using conventional technologies, such as with the wire bonding (WB) as shown in Fig. 1.3 (left), is referred to as 3D integration packaging technologies. In this book, we focus our attention on systems in which semiconductor chips are stacked and connected by TSV, as shown in Fig. 1.3 (right), which

Fig. 1.3 3D integration packaging technology and 3D integration technology [6]

define 3D integration technology [6]. We do not discuss 3D integrated circuits (3D-IC) that use FEOL, such as 3D NAND in which transistors are stacked, nor the Intel tri-gate transistors that were introduced in the 22-nm generation ivy bridge CPU.

# 1.2 Motivation for 3D Integration Technology

The development impetus is accounted for in the following two points.

- 1. If semiconductor integrated circuit chips are connected using TSV, the interconnected distance is approximately 1/1000 of that using conventional WB (micrometers compared with millimeters). This results in dramatic reductions in electric resistance and capacitance, making possible high-speed operation and low power consumption.

- 2. It is difficult to make (wire) connections between the conventional packages on the mounting board on the order of thousands, but this task is straightforward, and on even grander scales, between Si chips using TSV. Thus, TSV-based systems that have several 1000 input/output (I/O) circuits are realizable, which also benefit from being lower power consumption devices with higher data transmission speeds.

3D integration need not be confined to like technologies. By combining semiconductor integrated circuits with, for example, micro-electro-mechanical systems (MEMS) devices, unique functionalities can be developed in what is termed heterogeneous 3D integration technology.

# **1.3 Research and Development History of 3D Integration** Technology

# 1.3.1 3D Packaging Technology

Even as of 2015, the use of 3D-IC (TSV) is uncommon, with the exception of complementary metal–oxide–semiconductor imaging sensors (CIS). However, high-volume manufacturing of 3D integration packaging technology using WB continues.

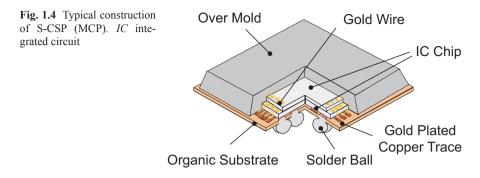

In 1998, Sharp Corporation developed the world's first stacked two-chip chipscale package (CSP) using WB [7]. Before that time, there was no notion of chip stacking in CSP. This led to its development for use in mobile phones, mostly by Japanese chip makers, such as Sharp, Mitsubishi, Hitachi, NEC, Toshiba, and Fujitsu. This technology was called stacked chip-scale (size) package (S-CSP) or multichip package (MCP). Figure 1.4 shows the typical construction of S-CSP (MCP).

S-CSP/MCP was first used to make combinations of NOR flash memory and of static random-access memory (SRAM), which are at the heart of all mobile phones. Consumer demand fuelled the development of smaller sizes and higher performance [8]. When Sharp developed the world's first stacked CSP, the combination memory development race was called the "East versus West War" over standardization by the Joint Electron Device Engineering Council. It became a demonstration of the strength of Japanese packaging technology.

Although, in the beginning, the interconnect technology was only WB, CSP stacking has given rise to the package on package (PoP) model, which also uses flip chip (FC) technology. Today, this approach is integral to modern smart phones and tablets; dynamic random access memory (DRAM) and application and/or baseband processors are stacked together using this technology. Upon these foundations, newer technologies continue to drive advances in telecommunications, such as through mold via (TMV) [9, 10]; see Fig. 1.5.

In the present-day flash memory, there are more than eight chips stacked into a single package [11]; see, for example, Fig. 1.6. This technology will likely continue being a mainstay of 3D integration packaging technology for some time yet. On the horizon are wireless interconnect technologies, such as capacitive and inductive 3D coupling [12].

**Fig. 1.5** 3D integration packaging technology transition [10]. (With permission from Amkor Technology, Inc., Chandler AZ). *WB* wire bonding, *PoP* package on package, *FC* flip chip, *TMV* through-mold via, *TSV* through-Si via

**Fig. 1.6** World's first ninechip stacked memory. (With permission from Toshiba Corporation)

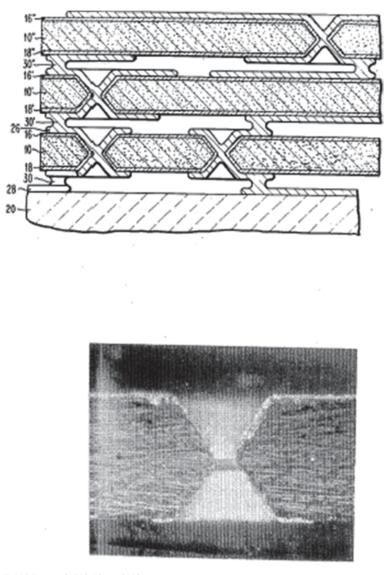

# 1.3.2 Origin of the TSV Concept

The underlying concept of TSV technology is not new. International Business Machines Corporation filed the patent USP3,648,131 entitled, "Hourglass-shaped conductive connection through semiconductor structures" in November 1969, with the following abstract [13]: 1 Research and Development History of Three-Dimensional ...

Fig. 1.7 US Patent 3,648,131 A [13]

"An integrated semiconductor structure including the fabrication thereof, and more particularly, an improved means for interconnecting the two planar surfaces of a semiconductor wafer. To provide the electrically conductive interconnections through the wafer, a hole is etched, insulated, and metallized. Active or passive devices may be formed on either or both sides of the wafer and connected to a substrate by solder pads without the use of beam leads or flying lead bonding." The drawings are shown in Fig. 1.7.

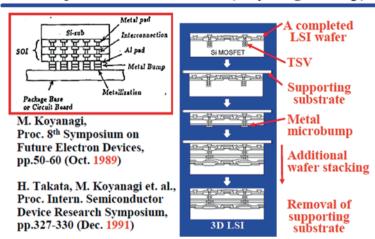

3D Projects in Tohoku Univ. (Koyanagi Group)

**Fig. 1.8** Extracts from presentations by Tohoku University researchers in 1989 [14] and 1991 [15]. (With permission from Tohoku University, Japan). *TSV* through-Si via, *LSI wafer* large-scale integration wafer

Later on, patents JP (S59)1984-22954 (June 1, 1983) and patent JP (S61)1986–88546 (October 5, 1984) were filed by Hitachi Ltd. and Fujitsu Ltd, respectively. The patent JP (S63)1988–156348 (December 19, 1986), by Fujitsu, describes a stacked chip structure. Figure 1.8 shows key schematics of chip stacking techniques sourced from 1989 and 1991 conference presentations by Tohoku University, Japan [14, 15].

# 1.3.3 Research and Development History of 3D Technology in Organizations

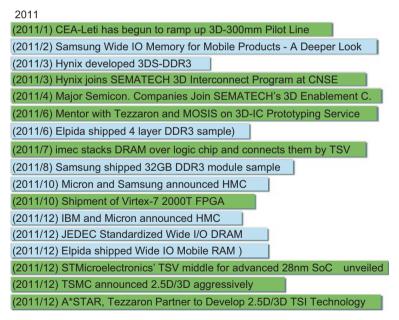

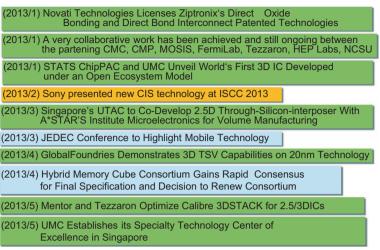

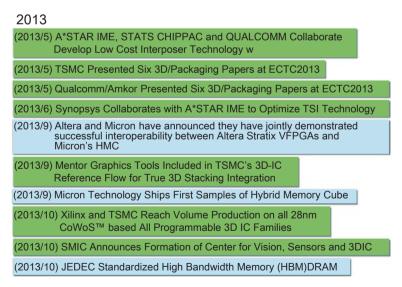

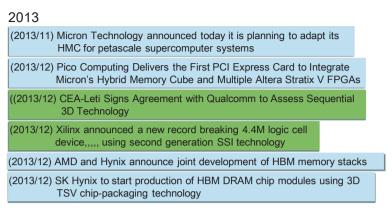

Research and development of 3D integration technologies has been carried out through global efforts [16]. Some of the major contributions by region are summarized in Fig. 1.9 [17].

# History of WW R&D on 3D Integration/Interconnect Technology

|       |                                     | 1999  | 2000                | 2001 | 2002                | 2003  | 2004                     | 2005 | 2006                                                                                                                         | 2007                   | 2008 | 2009           | 2010                        | 2011                                                                                                                                     | 2012                                                  | 2013                             | 2014                     |

|-------|-------------------------------------|-------|---------------------|------|---------------------|-------|--------------------------|------|------------------------------------------------------------------------------------------------------------------------------|------------------------|------|----------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------|--------------------------|

|       | kD in<br>Ipan                       |       |                     |      | Super H<br>technolo | ign 🔪 | NEDO: R<br>memory<br>tec |      |                                                                                                                              | Preparator<br>Research |      | 0:Drea         | am Chi                      | p Proje                                                                                                                                  | ect                                                   |                                  | :Smart<br>Project        |

|       | kD in<br>ISA                        | DARPA |                     |      |                     |       |                          |      | A: VISA Proj. DAGA: 3DL1, 3DM2, 3DM3 3D Circuit Design etc<br>Sematech (Private) Program (2007–) 3D IC Manufacturing Process |                        |      |                |                             |                                                                                                                                          |                                                       |                                  |                          |

|       | LBT Pj.<br>D in<br>rope             | Ger   | German BMBF Project |      |                     |       |                          |      | Europe (FP6): e-CUBES Proj.<br>3D-Integrated Wireless<br>Sensor Systems<br>IMEC 3D-SiC Program(2                             |                        |      |                |                             | Best Reliable Ambient Intelligent<br>Nanosensor Systems<br>Europe (FP7): e-BRAINS<br>interconnects at the global o<br>intermediate level |                                                       |                                  |                          |

| R&D   | in Asia                             |       |                     |      |                     |       |                          |      |                                                                                                                              |                        | A    | industr<br>IME | y-acade<br>3DTSV<br>allianc | emia-go<br>Conso<br>e of ind                                                                                                             | anizing t<br>vernmei<br>rtium (2<br>ustry &<br>amsung | nt-institu<br>009 ~ S<br>governr | utes<br>ingapore<br>nent |

| inter | t R&D for<br>mational<br>rcializati |       |                     |      |                     |       |                          |      |                                                                                                                              |                        | 3D E | MC(200         | D ASSM                      |                                                                                                                                          | ia Tec (L<br>AIST (K                                  |                                  | 1                        |

Source: M. Kada (ASET)Sep. 2009, Mate Feb.2010, Modified 2014

Fig. 1.9 History of global research and development on 3D integration technology. (Adapted from Ref. [16]). *NEDO* New Energy and Industrial Technology Development Organization, *DARPA* Defense Advanced Research Projects Agency, VISA vertically interconnected sensor arrays, *AD-STAC* Advanced Stacked-System Technology and Application Consortium, *TSV* through-silicon via, *ASSM* All Silicon System Module, *EMC* Equipment and Materials Consortium, *SiC* stacked integrated circuit, *German BMFT* German Ministry of Research, *BMBF* Federal Ministry of Education and Research, *FP7* Seventh Framework Programme

#### 1.3.3.1 Japan

In Japan, research and development of the "Three-Dimensional Circuit Element R&D Project" by the Research and Development Association for Future (New) Electron Devices was conducted from 1981 to 1990, and the technology developed was termed "Cumulatively Bonded IC" (CUBIC): (in Japanese); TSV was not integral to the design. A thin film (approximately 2-µm thick) of electron channel metal–oxide–semiconductor field-effect transistor (nMOSFET) was laminated onto the bulk silicon device. The electrical interconnection of 1600 wiring contact arrays was checked, and the contact volume resistance of  $5 \times 10^{-6} \Omega \cdot cm^2$  did not adversely affect the operation [18].

In Japan, the Association of Super-Advanced Electronics Technologies (ASET) carried out a research and development project of 3D integration technology using TSV during the 5-year period 1999–2003. The project was entitled, "R&D on High Density Electronic System Integration Technology" (in Japanese). Its execution was entrusted to the New Energy and Industrial Technology Development Organization (NEDO) organization of the Japanese government's Ministry of Economy, Trade, and Industry (METI) [19]. Following on were the "Stacked Memory Chip

Technology Development Project" (in Japanese), 2004–2006 [20] and the "Development on Functionally Innovative 3D-Integrated Circuit (Dream Chip) Technology Project" (in Japanese), 2008–2012. In 2010, research was conducted with a focus on "Design Environmental Technology, Interposer Technology, Chip-Testing Technology, Three-dimensional Integration Basic Technology, Flex chip (FPGA) Technology, and RF MEMS."

The majority of the semiconductor-related businesses in Japan were involved in these projects. These included semiconductor companies Elpida, Toshiba, Renesas, and Rohm; electronic companies NEC, Sharp, Nac Image Tech., IBM, Panasonic, Hitachi, and Fujitsu; and material/equipment companies Advantest, DNP, Ibiden, Shinko, TEL, Toppan, Yamaichi, and Zycube. Furthermore, The University of Tokyo, Tohoku University, and the National Institute of Advanced Industrial Science and Technology represented the academic participation [21–23].

In 2010, an interim assessment led to a focus shift to thermal management/chip stacking technology, thin wafer technology, 3D integration technology, ultra-wide bus 3D-SiP, mixed signal (digital–analog) 3D integration technology, and heterogeneous 3D integration technology. The research outcomes are described in later sections of this book [24, 25].

However, despite the sizeable investment by the Japanese government over these long periods of time, the national semiconductor industry is presently in decline and future research and development remains uncertain.

The WOW alliance based at the Tokyo Institute of Technology (based at The University of Tokyo until 2014) was founded in 2008 [26], and the "Three-Dimensional Semiconductor Investigation Center" (translated from the Japanese) in Kyushu commenced operations in 2011 [27].

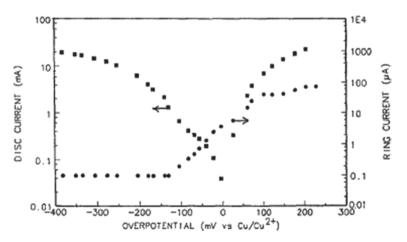

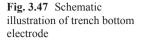

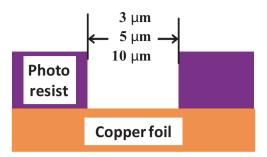

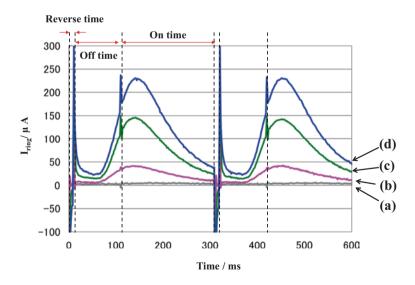

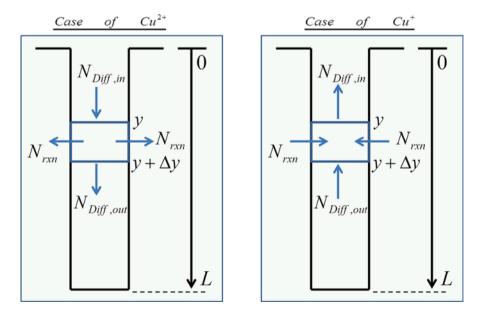

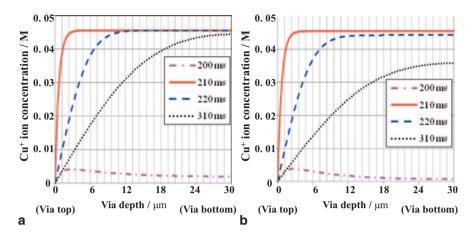

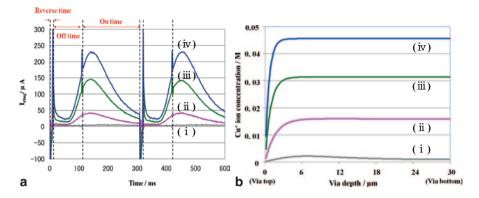

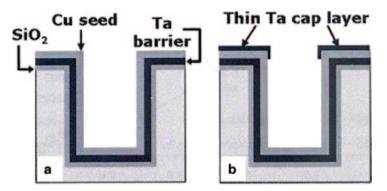

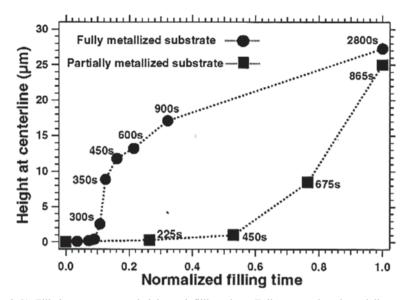

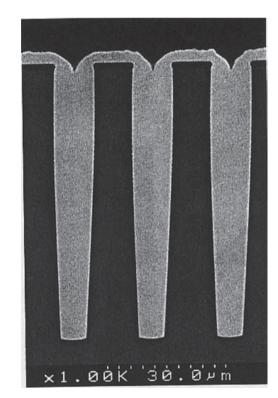

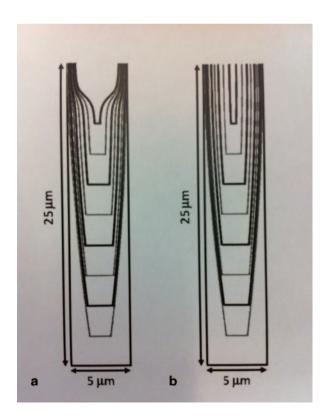

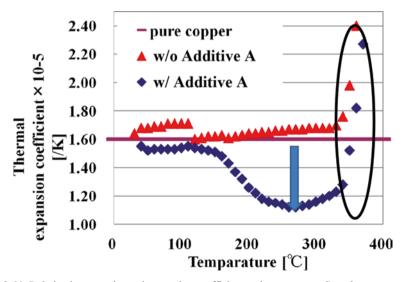

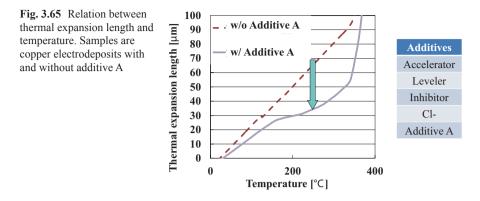

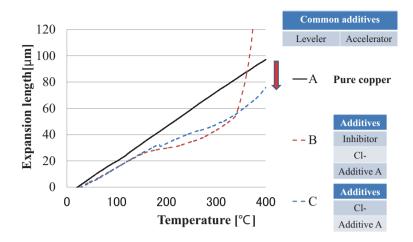

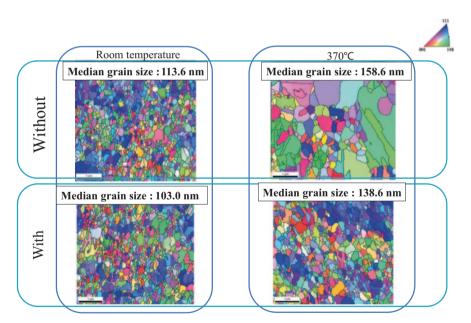

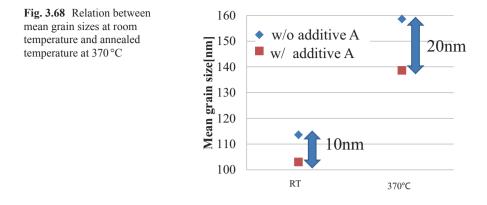

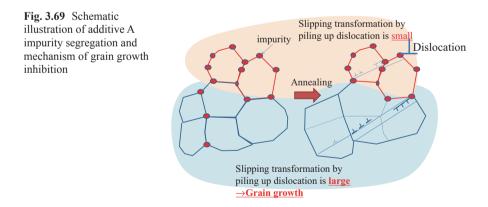

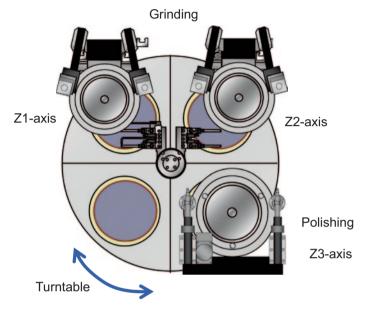

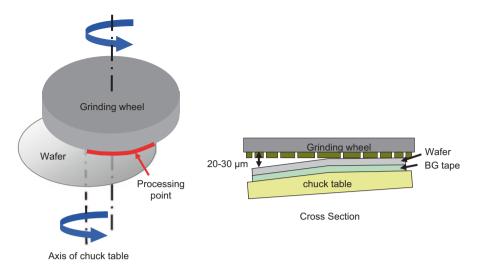

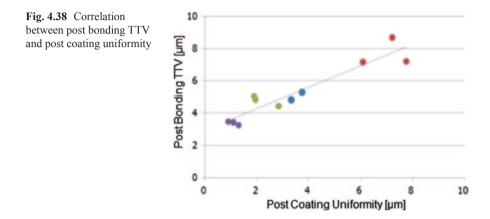

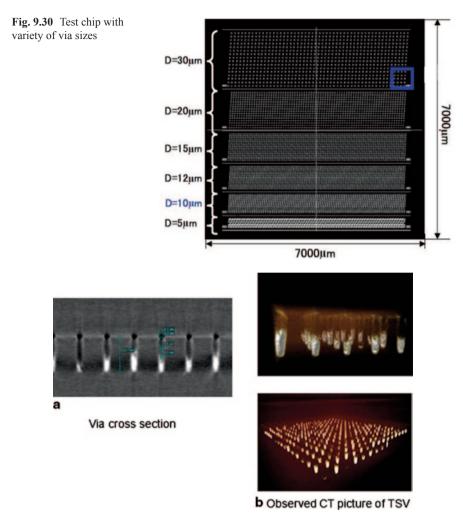

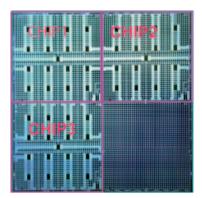

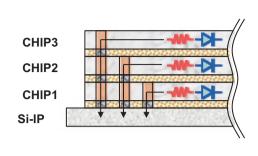

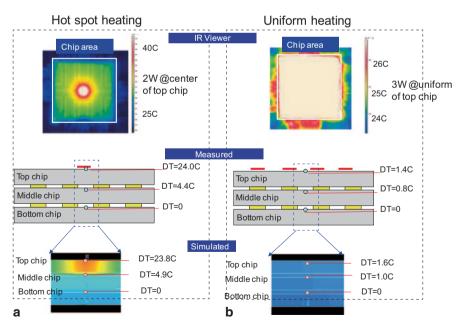

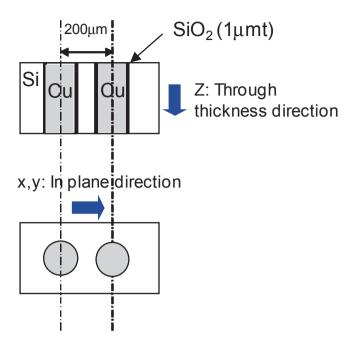

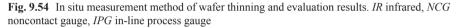

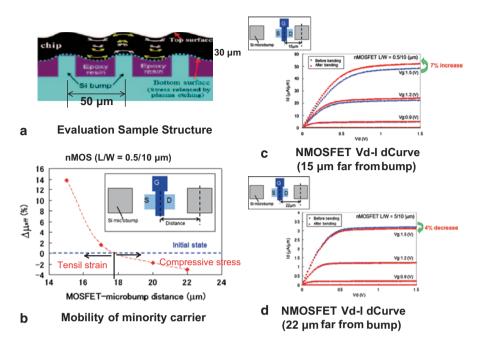

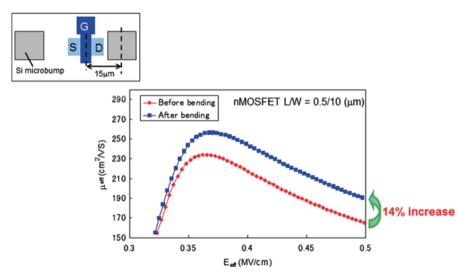

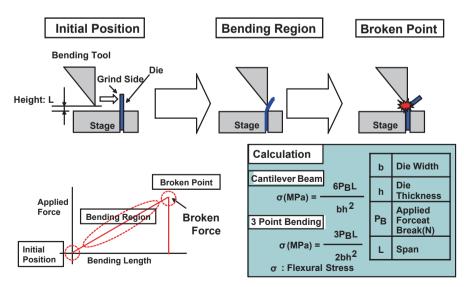

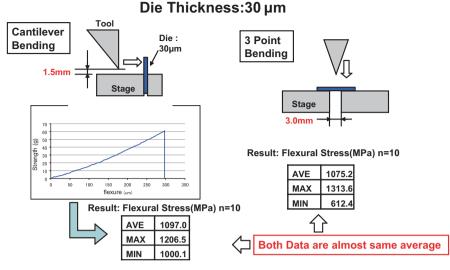

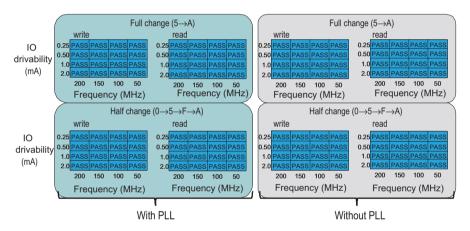

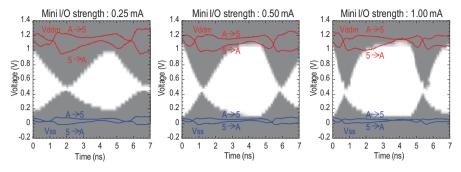

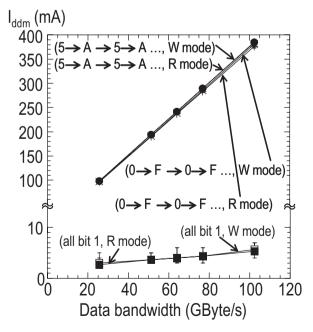

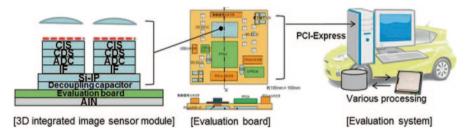

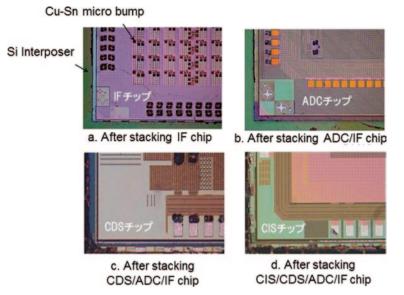

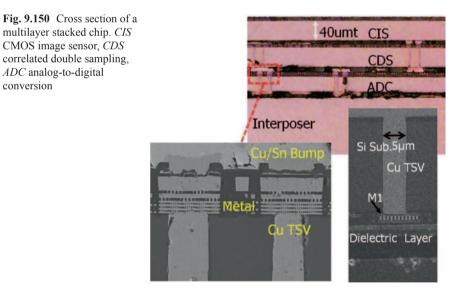

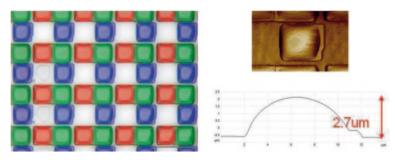

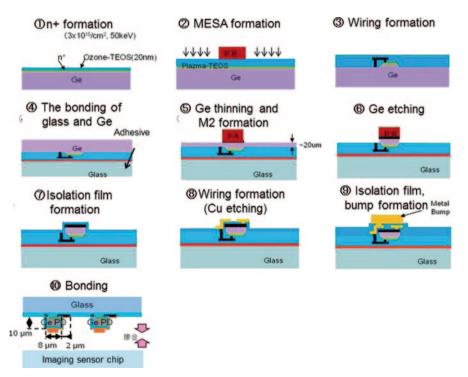

## 1.3.3.2 Japanese 3D Integration Technology Research and Development Project (Dream Chip)