## Cheol Seong Hwang Editor

# Atomic Layer Deposition for Semiconductors

## Atomic Layer Deposition for Semiconductors

Cheol Seong Hwang Editor

## Atomic Layer Deposition for Semiconductors

Editor

Cheol Seong Hwang

Department of Materials Science

and Engineering and Inter-university

Semiconductor Research Center

Seoul National University

Seoul

Korea

ISBN 978-1-4614-8053-2 ISBN 978-1-4614-8054-9 (eBook) DOI 10.1007/978-1-4614-8054-9 Springer New York Heidelberg Dordrecht London

Library of Congress Control Number: 2013951501

#### © Springer Science+Business Media New York 2014

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law. The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

#### **Foreword**

Atomic Layer Deposition (ALD) is not a new technique, since the first experiments were carried out over 40 years ago. Industrial use began in 1983 with the production of thin film electroluminescent displays. In these displays, the dielectric-luminescent layer-dielectric thin films stack is made in a continuous process. Interestingly, this stack is 1–1.5 micron thick. Other industrial applications of ALD remained limited for 20 years, but during the past 10–15 years microelectronics has been the major driver for ALD technology.

In the late 1990s, it became obvious that the continuation of Moore's law would require introduction of new materials into microelectronics. Additionally, new deposition methods were needed in IC technology since materials had to be deposited with atomic level accuracy as very thin films uniformly over the increasing wafer sizes and conformally over the increasingly demanding three-dimensional (3D) device structures. New interest was paid to ALD and enormous research activities went into the development of processes to manufacture high-*k* dielectric materials, metals, and materials for barrier layers.

High-*k* dielectric materials for both gate oxides in metal–oxide–semiconductor field effect transistors (MOSFET) and capacitor dielectrics in Dynamic Random Access Memories (DRAM) have been the most important topics in ALD research during last 10–15 years. Especially, DRAMs require complex 3D capacitor structures and no other thin film technology than ALD can be employed in their production. ALD has been used in these high-*k* applications already for some time. Furthermore, at the moment the dielectrics used in DRAMs are ZrO<sub>2</sub>–Al<sub>2</sub>O<sub>3</sub>–ZrO<sub>2</sub> nanolaminates the preparation of which on a 3D structure is even more challenging. The DRAMs contain electrodes which also need to be conformal. ALD TiN is the material of choice for this application.

About 6 years ago, it was announced that the first microprocessors using MOSFETs containing high-k dielectrics were coming to the market. These revolutionary new devices contained ALD-made hafnium-based oxides as dielectrics and metals as gate electrodes. The current MOSFETs are still planar devices and as such not so much dependent on ALD as the 3D DRAMs. On the other hand, the replacement gate approach and the future 3D transistor structures will also make MOSFET processing a 3D task and thereby involve ALD.

vi Foreword

A third semiconductor application area where ALD has been extensively studied is interconnects. Apparently, the first real application was tungsten seed layers for tungsten chemical vapor deposition (CVD) contact plug fill using a process based on reduction of WF<sub>6</sub> with either diborane or silanes. For copper interconnects ALD has been explored for years but its implementation has been delayed. Copper appears to be a challenging material to find good ALD chemistry and the problem has not been solved yet. Development of ALD processes for platinum group metals has been successful and they may be employed in semiconductor applications as electrodes or barriers. There are also many other application areas in microelectronics for which ALD have been explored and where it could be used. These include non-volatile memories such as ferroelectric RAM (FeRAM), flash, and phase change memories.

This book *Atomic Layer Deposition for Modern Semiconductor Devices* focuses on its topic ALD in semiconductor industry, but presents also fundamentals of ALD technology and ALD reactors. This book consists of chapters written by prominent scientists and engineers in the field. It is timely since there are enough research and results on the use of ALD in microelectronics for reviewing. This book nicely covers the existing application areas of ALD in microelectronics and presents the emerging areas such as phase change memories. This book is useful for scientists, students, and engineers to achieve an overview of the present situation, as well as the future and challenges in ALD for microelectronic materials and device fabrication.

Helsinki, Finland, April 30, 2012

Markku Leskelä

### **Preface**

How will our world and society look in 100 years? This may be a question that no one can answer clearly. Perhaps, it is even difficult to say how our world and society will look in 10 years. There can be, however, many plausible answers to the question about our future even at this moment. "It will be a world that uses better information technology than now" without a doubt. The basic hardware for the information technology will be certainly take the form of a computer, no matter which level they are at; from supercomputer to small hand-held electronic appliances. Better computers, however, do not simply mean calculation machines with higher speed processors and higher density memories. They must be environmentally benign and sustainable. In addition, the main stream semiconductor technology based on Si-chips will most likely not be radically changed within 10-20 years although there are several potential technology contenders such as carbon-based electronics. On the other hand, it is forecast that pursuit of the present technology trend in computer and semiconductor chips will necessitate too much energy consumption in 10 years. Therefore, computers with better performance but low energy consumption are necessary. Lighter weight and longer battery life time are the key market requirements for portable appliances. These impose a significant challenge to all scientists, engineers, and designers in the information technology field and semiconductor industry.

Two basic strategies could be adopted to accomplish such a demanding goal; one is following Moore's law, and the other is surpassing it (or pursuing goals beyond-Moore's law). The enormous improvement in computing technology over the last  $\sim\!50$  years has been accomplished according to Moore's law. This has been achieved by appropriate collaborations among and competitions between people working in the fields of design technology (such as recent multi-core architecture of microprocessors), material innovations, and chip fabrication technology. As the dimensions of modern semiconductor chips have shrunk to  $\sim\!20$  nm, further miniaturization became extremely challenging due to the complexities of related processes and resultant costs. Therefore, alternatives to blind miniaturization are indispensable; those would include new functional materials, new device structures, and new thin film processes including deposition, etching, and cleaning.

There have been innovative approaches differing from the conventional computing technologies based on the binary digits which have been so successfully implemented on complementary metal oxide semiconductor field effect transistors.

viii Preface

The so-called quantum computing is one of these new directions although it faces critical challenges due to the uncertainty principle. These approaches are usually called more-Moore or beyond-Moore technology. No matter which research trend becomes the main stream in 10–20 years in the field of microelectronics or nanoelectronics, new functional materials processed by an innovative process technology for new innovative devices must be pursued.

Confining the scope of discussion to the field of semiconductor processing. Atomic Layer Deposition (ALD) naturally comes to our attention due to its unique properties in fabricating various nanometer scale thin films. ALD was originally designed for depositing uniform passivation layers over a very large area specifically for display devices in late 1970s and early 1980s when other thin film deposition techniques could not offer this capability. However, it has not been highlighted until the end of the twentieth century; it only became very popular at the dawn of the twenty-first century. This is probably due to the adoption of this technique in highly integrated semiconductor memory devices. ALD started being applied to Dynamic Random Access Memories (DRAM) early in this century, while earlier DRAMs were mostly constructed by chemical vapor deposition. Nowadays, many other types of memory chips also employ ALD processes for various purposes. Another milestone in microelectronics in ALD history was the mass production of microprocessors which was initiated with the production of Penryn in 2007 by Intel, where the replacement gate process with high-k/metal gate stack was adopted. Since then ALD has evolved into a standard process in semiconductor industry.

According to these new trends, a book entitled "Atomic Layer Deposition of Nanostructured Materials" edited by N. Pinna and M. Knez was published by VCH-Wiley in 2011. The editor of this monograph contributed a chapter, entitled "Atomic Layer Deposition for Microelectronic Applications" to that book. The book was intended to cover the general aspects of ALD and contained almost all possible applications in nano-research related fields as the title implies. This is a timely and useful guide book for ALD, but may not be detailed enough for the microelectronics or nanoelectronics field despite the huge potential importance of this technique. Inspired by this idea, an initial suggestion on this monograph was made by a senior editor of the publisher Springer, Dr. Kenneth Howell, in the middle of 2010 when I was serving as the general chair of 10th international conference on the ALD held in Seoul, which was a special conference series of American Vacuum Society. After several discussions with colleagues in the field, this monograph took shape. I appreciate all the contributions to this great work, thank all the contributors, and hope that it can be a useful guideline for all engineers and designers in this field as well as for all application-oriented physicists and chemists.

kwanak-ku, seoul

Cheol Seong Hwang

## **Contents**

| Pä | irt 1 Introduction                        |     |

|----|-------------------------------------------|-----|

| 1  | Introduction                              | 3   |

| Pa | art II Fundamentals                       |     |

| 2  | ALD Precursors and Reaction Mechanisms    | 15  |

| 3  | ALD Simulations                           | 47  |

| Pa | art III ALD for Memory Devices            |     |

| 4  | Mass-Production Memories (DRAM and Flash) | 73  |

| 5  | PCRAM                                     | 123 |

| 6  | FeRAM                                     | 149 |

| Pa | art IV ALD for Logic Devices              |     |

| 7  | Front End of the Line Process             | 175 |

x Contents

| 8 Back End of the Line                                 | 209 |

|--------------------------------------------------------|-----|

| Part V ALD Machines                                    |     |

| 9 ALD Machines                                         | 241 |

| Erratum to: Atomic Layer Deposition for Semiconductors | E1  |

| Index                                                  | 257 |

## Part I Introduction

### Chapter 1 Introduction

Cheol Seong Hwang and Cha Young Yoo

The enormous improvement in information technology, accomplished mostly by the better computers, has been one of the most important impetuses that have driven the development of modern civilization over the last  $\sim 50$  years. Better computers are based on better semiconductor chips for logic processors and solid state memories, such as dynamic random access memory (DRAM), as well as disk-type storage devices. The paradigm for the chip fabrication can be well represented by the famous Moore's law, which has been accomplished through strict scaling technology in both memory and logic chips. Although the scaling has been achieved mainly by the improved photolithography and dry etching processes, advanced thin film growth processes can also greatly contribute to the development of the devices.

As the scaling of semiconductor devices proceeds, the demands for a thin film deposition with low thermal budget, higher accuracy in thickness control, and better conformality over three-dimensional (3D) structures are increased. This is mainly due to the highly scaled metal-oxide-semiconductor field effect transistors (MOSFET), high-k gate dielectric/metal gate technology, and capacitors for DRAMs. The extremely small gate length (<20 nm) of most advanced MOSFETs generally leads to the instability in the threshold voltage control due to various reasons (called short channel effect). Among the several methods to overcome this issue, adopting the low thermal budget for chip fabrication is one of the options which generally results in the better diffusion profile control and shallow junction formation. The atomic layer deposition (ALD) often adopts a lower process temperature compared to the chemical vapor deposition (CVD), making it a more desirable method for the low thermal budget. Another key technology for

Department of Materials Science and Engineering and Inter-university Semiconductor Research Center, Seoul National University, Seoul 151-744, Korea e-mail: cheolsh@snu.ac.kr

C. Y. Yoo

Semiconductor R&D center, Samsung Electronics Co. Ltd, Yongin, Korea

C. S. Hwang (⊠)

addressing the issues related with the MOSFET is the high-k gate dielectric/metal gate, which greatly decreases the gate leakage current as well as the threshold voltage instability. The thickness level of high-k gate dielectrics in modern logic chips is only 2-3 nm, meaning that the thickness variation by 0.2-0.3 nm already corresponds to 10 % of the total thickness. It must be noted that 0.2-0.3 nm corresponds to only one mono-layer thickness of most oxides, indicating that selflimiting or self-terminating thin film deposition techniques should be used to fulfill such a tough requirement. In addition, the extremely shrunk dimensions of modern semiconductor devices naturally require physically very thin films. A typical example is the stack capacitor of DRAMs, which requires at least three layers (two capacitor dielectric and one top electrode layers) between two storage nodes meaning that the thickness of each layer must be <7 nm for devices with the 20 nm design rule (more precisely 40 nm pitch device). Regardless of the electrical performances, the materials cannot be placed into the narrow gap if they are thicker than  $\sim 7$  nm. This consequently imposes significant challenges to many materials. For example, the effective dielectric constant of a very high-k material (e.g., (Ba,Sr)TiO<sub>3</sub>) degrades very rapidly with decreasing film thickness [1], which could make the adoption of such a process-wise demanding material less advantageous considering the less severe thickness-dependent properties of the relatively lower (bulk) k material, such as TiO<sub>2</sub> [2-4]. Such intrinsic behavior of thin dielectric film is almost independent of the film growth and the interface controlling methods. This means that the material choice for such extremely scaled devices cannot be determined solely based on the intrinsic or bulk properties. Furthermore, the extreme 3D geometry also requires a thin film deposition process with better step coverage than CVD. The very thin films (<10 nm) usually have different structural and electrical properties compared with bulk materials, particularly for the case with the vapor-phase grown materials. This is a natural consequence of the growth process considering that the very thin layers are deposited on a certain type of substrate which is usually different from the depositing material itself. Once the substrate is coated with the growing materials, the film growth enters into the steady state and more bulk-like films can be obtained. For many cases, the initial growth on the heterogeneous substrates is retarded by the inherent nucleation barriers which usually render an island-like growth and non-uniform film. These factors severely affect the material properties of the very thin films. This is, however, one type of extrinsic effects that could be improved by an appropriate growth control process.

Therefore, ALD appears to be a very timely and indispensable process for microelectronics, even though it was originally expected to achieve film deposition with uniform thickness ( $\sim \mu m$ ) over a very large area for other applications [5]. In addition to its unprecedented conformality over the 3D structures when precursor molecules are well saturated on the surface, ALD is suitable for the extremely thin film growth due to the following two reasons. The first is its self-saturating or self-regulating nature, making the thickness control at atomic level feasible. Secondly, in principle, once the substrate surface is covered with the first mono-layer of the growing film, the growth should be in the steady-state, suggesting that the film

1 Introduction 5

recovers the bulk-like properties from thicknesses as thin as  $< \sim 1$  nm. However, these two are valid only for several exceptional cases, and in most cases they deviate from these ideal behaviors, making all the engineering efforts in ALD field indispensable.

ALD usually suffers from the low growth rate (thickness increase per process time) except for several exceptional cases with an extremely high growth rates [6]. Typical ALD materials, such as HfO<sub>2</sub>, benefit from an improved growth rate by the recent development of novel precursors based on the heteroleptic ligand structures [7]. However, it is noteworthy that the generally low growth rate becomes less problematic in microelectronics because the required film thickness decreases gradually as mentioned above. This subsequently makes the adoption of ALD into the future microelectronics and nanoelectronics highly desirable.

During the past  $\sim 10$  years, these general features of ALD progressively became known to the thin film and microelectronics society and also attracted much of their interest. Although the ALD industry is not fully matured yet, it has already been applied to sizable material and deposition tool industries as well as huge semiconductor chip fabrication lines. Due to the layer-by-layer growth mechanism of ALD, it fits very well to the scientific interests on the surface reaction so that many surface chemists and material scientists have devoted a considerable amount of effort to this field. ALD actually serves as a viable methodology to understand the gas—solid interactions in somewhat complicated material systems. Several in situ, such as Fourier transformed infrared spectroscopy or spectroscopic ellipsometry, and ex-situ, such as X-ray photoelectron spectroscopy, and surface sensitive investigation techniques have been employed.

However, a considerable gap in understanding and application of ALD appeared between surface scientists and semiconductor process/device engineers. This monograph is hence intended to serve as a link between the two groups. The diverse structures and operational principles of semiconductor devices might be difficult to understand for surface scientists, while the engineers and designers in the solid-state device field may have problems in understanding the chemistryoriented ALD reactions and materials properties. This monograph, therefore, is composed of chapters describing the device structure, operation principle, and material processing issues related with ALD in various types of memory and logic devices. Due to the extreme diversity of the ALD processes in various semiconductor devices, the book was written on a rather arbitrary classification of semiconductor devices into mass-production memory/emerging memory and logic devices. Mass-production level memories include the DRAM and Flash memories, whereas the phase change random access memory (PcRAM) and ferroelectric RAM (FeRAM) belong to emerging memories. There are also other memories such as static RAM (SRAM), magnetic RAM (MRAM, or spin transfer torque RAM (STTRAM)), and resistance switching RAM (ReRAM). However, SRAM is comprised of six transistors forming the cross-coupled latches, which is the same as logic devices from the fabrication point of view. The key component of MRAM and STTRAM is magnetic tunnel junction (MTJ), where an extremely thin dielectric layer (~1-2 nm), typically MgO or Al<sub>2</sub>O<sub>3</sub>, is sandwiched between two magnetic conductors. Depending on the relative magnetization directions of the two magnetic layers, the electrical conduction which occur via the tunneling mechanism through the thin dielectric layer modulates, which is the basic principle of the MRAM or STTRAM. Due to the extremely high sensitivity of the tunneling current on the dielectric layer thickness, very tight control (<0.1 nm) over the dielectric layer thickness throughout the large area wafer is crucial. ALD can be a viable solution for the tough target, but presently plasma oxidation of sputter-deposited metal (Mg or Al) layer is used as the industry standard. Several trials of the ALD process were adapted to this area but little noteworthy success has been reported. ReRAM is an interesting area where numerous materials show electrically induced non-volatile resistance switching based on various mechanisms [8]. However, there are several problems in ReRAM from the ALD point of view. One of them is the non-determined resistance switching material. The device structure is not well defined yet either. Therefore, SRAM, MRAM (STTRAM) and ReRAM are excluded from this monograph.

Certainly, there are very diverse logic devices ranging from the state-of-the-art multi-core main processors to fairly simple microprocessors. However, all those logic chips are combinations of high performance transistors without special capacitors or junction devices involved. Therefore, from the ALD point of view, the logic can be treated as a device composed of the front-end and back-end of the line (the sequence of fabrication procedure is called 'line' here) steps. This monograph has two separate chapters on the front-end and back-end of the line processes for Si chips, accordingly. On the other hand, great attention has been paid recently in the adoption of new substrates with high-mobility, such as Ge, compound semiconductors (GaAs and InP-based materials), or even carbon-based materials. These substrates have very distinctive physical and chemical interactions with the growing high-k films. Therefore, this must be treated separately but was not included in this monograph.

In addition to the above mentioned main bodies, there are three more important chapters. Two of them are on the fundamental sides of ALD—one chapter for the precursors and the other for the simulations. The final chapter is for ALD hardware/tools. These three chapters can be regarded as the general background for all types of ALD but are more focused on the microelectronic applications.

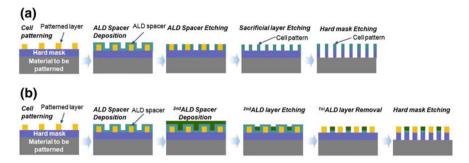

In this application field, the ALD layers work not only as the functional materials in the final products but also as the sacrificial layers that enhance several process capabilities. ALD layers discussed above are the functional materials. As a process capability enhancing factor, the double patterning process is a typical example of sacrificial ALD, which largely improves the photolithographic capability without astronomical cost. This kind of application is also discussed in detail in the main text. These two applications require very different film properties and process conditions. The active applications need supreme quality films that are generally accompanied by high process temperatures and low growth rates, whereas the sacrificial applications require low temperatures but rather thick ALD films. These conditions are generally incompatible with each other.

1 Introduction 7

In this introductory chapter, the general aspects of memory and logic devices are shortly covered too, which we believe particularly helpful for more process-and/or chemistry-oriented readers. More detailed operational principles of each device are described in each chapter. Presently, digital binary data stored in memory devices are in the form of either charge (DRAM, Flash, FeRAM, and SRAM) or resistance (PcRAM, MRAM, and ReRAM). Logic operations, which process the stored date according to the Boolean logic functions, proceed by combinatorial operations of complementary MOSFETs (CMOSFET). The most common logic elements are NAND, NOR, and NOT gates. Shannon already revealed that all the necessary Boolean logic operations can be accomplished using the (complicated) combinations of the three basic logic gates [9].

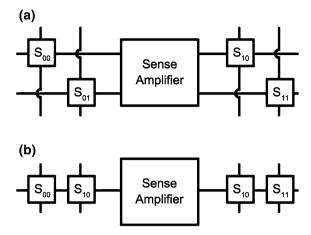

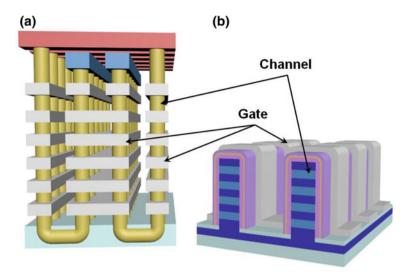

First, let us consider the principles of memory. Since a large amount of digital data must be stored, the memory cells are arranged in a type of array structures. As widely recognized, the most efficient array structure is the so-called "matrix" type, where the two crossing lines, bit- and word-lines, define a memory cell. The 3D cell structure is constructed by extending the two-dimensional memory arrays into the third dimension either by layer stacking or vertical integration.

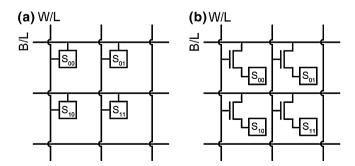

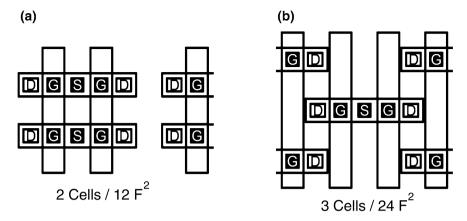

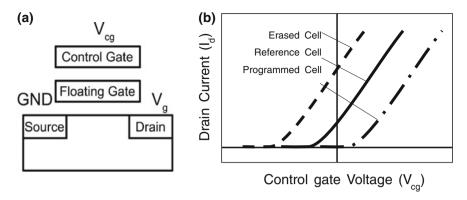

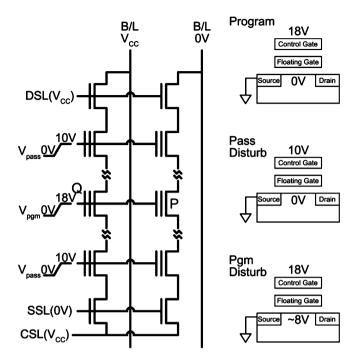

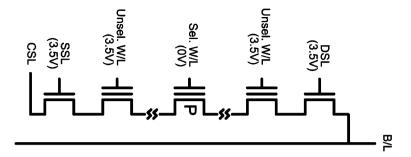

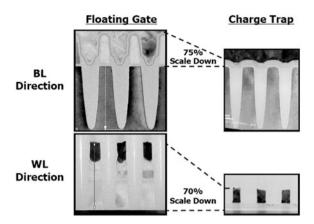

On a very fundamental level, two types of arrays, passive and active are shown in Fig. 1.1 a and b, respectively. In the passive array, the simultaneous activations of both bit- and word-lines are required to "write" a data bit into a certain cell. In this writing process, a certain threshold level of stimulus intensity must be overcome, which must be greater than the signal intensity of the bit- or word-line. This means that only the cell where both lines accessed becomes active, which makes a "random access" possible. The random access here means the "write" and "read" of a certain memory cell without involving "write" and "read" of other memory cells. Needless to mention, the random access is a more efficient way to operate the memory compared to non-random access methods as in the NAND flash. In this case, a memory cell adopts an orthodox chain-like geometry making random access very complicated. One example of the passive array type memory cell can be found from the NOR type flash memory. Flash memories, both NAND and NOR type, use double gate MOSFETs where the floating gate serves as the charge storage and the control gate drives charge transports between the channel region

Fig. 1.1 Schematic diagrams of (a) the passive matrix array and (b) the active matrix array

and floating gate by applying a high voltage between semiconductor channel and itself. When a high control gate voltage ( $\sim 10 \text{ V}$ ) is applied to a certain word-line, all cells connected to this word-line are just about to inject electrons from the inverted channel to the floating gate via the tunneling oxide. Then, the bit-line connected to the target cell is activated, and a current starts to flow between the source and drain in the target cell because the transistor would be already turned on due to the sufficiently high control gate voltage. The flowing carriers heat up the channel region by scattering and the carriers are thermally excited (hot carriers) to be injected into the floating gate particularly near the drain edge with the help of the high control gate voltage. Therefore, only the target cell can be programmed leaving other cells with common word-line unaffected because the current between source and drain does not flow, and, thus, the thermal effect would not be induced. Cells with the common bit-line would not be influenced because there is no control gate voltage and no source-drain current flow due to the off state of the MOSFET. Another type of passive memory cell can be found from the selection diode integrated PcRAM cell. This is explained again in conjunction with the active matrix array below.

On the other hand, the active matrix array utilizes an electrically operating switch between the bit-line and each of storage cell. This array has been extensively used in DRAM where the switch and storage cell are cell MOSFET (mostly n-type) and capacitor, respectively. The n-type MOSFET switches are driven by the word-line voltage. In this case, all the cells connected to a common bit-line are ready to be written when the bit-line is activated. When the word-line connected to the target cell is activated, the MOSFET is turned on and charges flow into the storage capacitor from the bit-line and the memory cell is thus written. Then, the word-line voltage decreased and the written data is kept within the cell. It can be easily understood that other cells sharing the same bit-line are not written because their switches were remained off (the word-line voltage remained low). In addition, other cells sharing the activated word-line with the target cell are not written either because the bit-line connected is not activated. This is a typical operation of DRAM. Overall, the active type memory cell is conceptually simple and easier to design compared to the passive type memory cell, which relies upon certain nonlinearity and threshold effect of the transistor and other functional material. However, with an extreme shrinkage of cell size, imperfect operation of MOS-FETs as a switch (i. e., incomplete turning on when the gate (word-line) bias was turned on and incomplete turning off when the gate bias was turned off) makes the passive type memory gain renewed interest. While the logic MOSFETs are designed to gain high on-current for higher operation speed, which is generally achieved by the low threshold voltage (~0.3 V), memory cell MOSFETs have a higher threshold voltage ( $\sim 0.7-0.8 \text{ V}$ ) to keep the stored charge stably. The low and high threshold voltages inevitably suffer from high off-state leakage current and low on-state current problems, respectively. Despite huge amount of engineering work, this is a sort of unsolved inherent problem of present MOSFET, the operation of which is based on the thermal distribution of electrons. These are charge-based memory because the digital data is stored as a form of charge in cell 1 Introduction 9

capacitor of DRAM and in floating gate of Flash memory (or charge trap layer in charge trap flash cell). Storing and saving charges in memory cells generally require two contradicting functions of MOSFET, i.e., to be completely on during writing and to be completely off during saving, which cannot be satisfied simultaneously even with practical criteria in highly scaled memory cells. Therefore, alternatives can be found in resistance-based memories.

Figure 1.2 a and b shows (overly) simplified internal read out scheme of a charge-based memory (DRAM) and a resistance-based memory cell (typically PcRAM) when the stored data is read out. For the case of DRAM, the potential  $(V_{bit})$  of bit-line, which is connected to the sense amplifier, is set to be half of the operation voltage  $(V_{dd}/2)$  initially. Then, the word-line voltage  $(V_{word})$  is pulled up to turn on the MOSFET of the reading cell.  $V_{bit}$  either increases or decreases depending on the charge state of the cell capacitor, which triggers the sense amplifier, which is a destructive readout. Right after the destructive read process, the original data is recovered by the self-refreshing function of the read operation. If the stored charge is overly small resulting from insufficient capacitance of the cell capacitor, small write current, and/or large leakage current of the capacitor dielectric and MOSFET, the sense amplifier may not detect the variation of  $V_{bit}$ . It can be easily anticipated that this problem becomes increasingly serious as the

Fig. 1.2 Simplified internal read out scheme of (a) a charge-based memory and (b) a resistance-based memory cell

device scaling proceeds. On the other hand, the situation is different in the resistance-based memory cell. In this case,  $V_{\rm bit}$  was also initially set to a certain value. Then, the cell MOSFET turns on, and  $V_{\rm bit}$  decreases depending on the resistance of the resistor (MTJ or phase-change/resistance-change material). The sense amplifier detects the difference and therefore the digital data stored as either high or low voltage, can be read out. It can be understood that the necessary functionality of cell MOSFET in this case is much less strict because there is no need to keep the stored charge. This is therefore a fundamental advantage of these memories compared to the charge-based memory. However, the electrically switchable resistors, which are as reliable, low power consuming, fast operating, and repeatable as DRAM capacitor, are not available yet. MTJ is probably close to these targets but both the extreme difficulty in fabricating such a thin tunneling dielectric layer and the overly high operational current inhibit its widespread use.

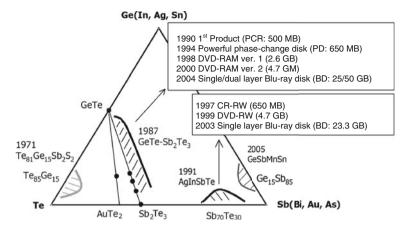

There is another problem related with the cell MOSFET. The resistance switching in promising materials including Ge<sub>x</sub>Sb<sub>y</sub>Te<sub>z</sub> alloys for PcRAM and metal oxides for ReRAM, requires very high current to change its resistance state. For example, the PcRAM requires a short (<50 ns) peak current (order of 0.1 mA) to reset (i.e., switch from on-state (crystalline state) to off-state (amorphous state)) the phase change cell, which must flow through the cell MOSFET. However, MOSFET generally has a maximum allowable current of <0.1 mA when the gate width is <100 nm. Therefore, scaling of PcRAM with the cell MOSFET has been hindered by the limited current supply, meaning that the active array configuration may not fit well to the PcRAM. Recent PcRAM, therefore, adopts the passive array type cross-bar structure, where the bit- and word-lines cross in a matrix-like shape and the phase-change materials are intervened between the two lines. The voltages of bit- and word-lines can be controlled to induce the desired phase change only at the junction of interest where both lines are activated. Since there is no MOSFET used in this structure, the problem of "limited current" is hence eliminated. However, a so-called read disturbance issue arises with this type of passive array. When an off-state cell is surrounded by on-state cells, the off-state cell can be misread as on-state since the surrounding on-cells provide a fluent current path. A common solution to this problem is placing diodes in series with each of the memory cell [10]. In the present PcRAM, p-n junction type Si-based diodes are employed instead of MOSFETs and each diode is connected with each memory cell [11]. The cross-sectional microscopy image of PcRAM may look like an active array but it is actually a passive array. Old paradigm comes back and revives in a new emerging memory!

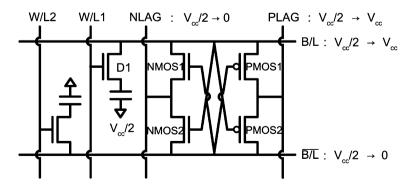

As for logic devices, basic functions of the NAND gate are explained and characteristic features of CMOSFET circuit are briefly mentioned below. Other gates can be understood in the same manner. Figure 1.3 shows a simplified diagram of a NAND gate which is composed of two n-MOSFETs and two p-MOSFETs. The truth table of NAND logic is also included in Fig. 1.3. In electric circuit, the "1" and "0" logic states correspond to the high and low levels of voltages, respectively. Although the detailed operations of n- and p-MOSFETs are rather complicated and non-linear in response to the external voltage input, they

1 Introduction 11

**Fig. 1.3** Simplified diagram of a NAND gate and the truth table of NAND logic

can be simply approximated as follows. In n-MOSFET, the high and low (or equal) gate voltage (Vg) relative to the source region (Vs) corresponds to the on- and offstates of the n-MOSFET, respectively. In p-MOSFET, the opposite is the case, where low (or equal) and high V<sub>g</sub> relative to V<sub>s</sub> correspond to the on- and offstates, respectively. The source voltage or ground potential connected to one of the n- and p-MOSFETs is transferred to the output depending on the combinations of two input voltages, which are applied to the gates of the four MOSFETs. Readers thus can easily understand that the output voltage is determined by the two inputs according to the truth table when the operation (on or off) of each MOSFET in the figure is traced according to the input voltages on each gate. One notable finding from such a circuit element is that there is no steady-state current flow; once the transient current flew to charge up the node capacitances, the source voltage and ground are never connected directly while the output node is connected to either the voltage source (logic state 1) or ground (logic state 0). The output is connected to the gates of following/neighboring logic circuits (inputs of them) so that there is no steady-state current flow from the output node to the following circuitry. They are separated by n- or p-MOSFET at the off-state and gate insulator, so that there is no steady-state power consumption. This is the most notable feature of the circuits composed of CMOSFETs compared to other circuits, and was one of the reasons why the CMOSFETs have dominated the logic chips. However, this will be the case only in the ideal case where there is no leakage through the gate dielectric and source-drain junctions, which is certainly not the case in reality. Particularly when the gate length is shortened to a very small value ( $\ll 100 \text{ nm}$ ) for a high on-current, the short channel effect, i.e., increase in the off current even at the  $V_{\rm g}$  < threshold voltage, becomes very serious. It has been widely recognized that one of the most promising ways to suppress the short channel effect is to increase the gate capacitance, either by decreasing the SiO<sub>2</sub> gate dielectric thickness or adopting high-k dielectrics. Decreasing the gate dielectric thickness to  $< \sim 1$  nm results in a significant gate leakage current whereby the power consumption cannot be tolerated. Even the logic state can be influenced erroneously with the overly high gate leakage (input can be directly transferred to output). Therefore, the high-k gate dielectric technology is indispensable and the metal gate technology is being pursued along with the high-k gate dielectric technology in an effort to eliminate the gate poly-Si depletion effect.

Another key asset of the CMOSFET in logic circuit is its ability to amplify signal levels due to the non-linear response of FET to the input signals. The input signal variation, which is generally induced by various noises and parasitic circuit components, can be successfully filtered once it passes through the MOSFET. Every future switching device, whether based on Si or other materials (ca. carbon), they must have this functionality in order to be used in the high performance logic circuits. Further details on this can be found in the recent book by Waser [12].

#### Reference

- 1. Hwang CS (2002) J Appl Phys 92:432

- 2. Kim SK, Kim KM, Kim WD, Hwang CS, Jeong J (2004) Appl Phys Lett 85:4112

- 3. Kim SK, Choi G-J, Lee SY, Seo M, Lee SW, Han JH, Ahn H-S, Han S, Hwang CS (2008) Adv Mater 20:1429

- 4. Kim SK, Lee SW, Han JH, Lee B, Han S, Hwang CS (2010) Adv Func Mater 20:2989

- 5. Ahonen M, Pessa M, Suntola T (1980) Thin Solid Films 65:301

- 6. Hausmann D, Becker J, Wang S, Gordon RG (2002) Sci 298:402

- 7. Seo M, Kim SK, Min Y-S, Hwang CS (2011) J Mater Chem Adv Art 21:18497

- 8. Waser R, Dittmann R, Staikov G, Szot K (2009) Adv Mater 21:2632

- 9. Shannon CE (1949) Bell Syst Tech J 28:59

- Lee M-J, Park Y, Suh D-S, Lee E-H, Seo S, Kim D-C, Jung R, Kang B-S, Ahn S-E, Lee CB, Seo DH, Cha Y-K, Yoo I-K, Kim J-S, Park BH (2007) Adv Mater 19:3919

- 11. Oh JH, Park JH, Lim YS, Lee HS, Oh YT, Kim JS, Shin JM, Park JH, Song YJ, Ryoo KC, Lim DW, Park SS, Kim JI, Kim JH, Yu J, Yeung F, Jeong CW, Kong JH, Kang DH, Koh GH, Jeong GT, Jeong HS, Kim K (2006) IEEE Int Electron Devices Meet (IEDM) Tech Dig 1

- Waser R (2003) Nanoelectronics and information technology. Introduction to part3, Wiley-VCH, 323

## Part II Fundamentals

## Chapter 2 ALD Precursors and Reaction Mechanisms

Roy G. Gordon

#### 2.1 Introduction

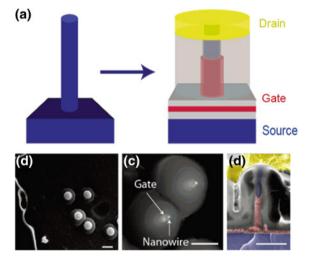

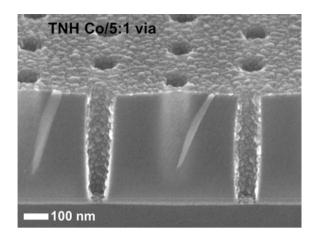

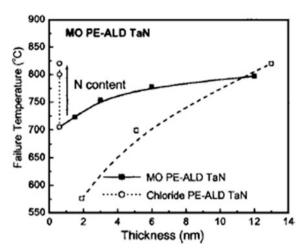

ALD has become accepted as a reliable tool for production of thin films in the microelectronics industry. Dielectrics and metal electrodes for DRAM capacitors are now routinely produced by ALD, which is the only technique capable of uniformly coating inside the narrow structures required by current technology. Transistors will soon be produced as 3D structures, with requirements for conformal coatings over their increasingly complex surfaces. Metal circuits between transistors are also pushing toward narrower and deeper structures, such as through-silicon vias. In order to extend the use of ALD into these new areas, a greater variety of materials will need to be deposited.

Successful use of ALD requires suitable chemical precursors used under reaction conditions that are appropriate for them. There are many requirements for ALD precursors: sufficient volatility, thermal stability, and self-limited reactivity with substrates and with the films being deposited. The precursor vapor should not etch or corrode the substrate or deposited film. In addition, it is easier to produce the required vapors if the precursor is liquid at room temperature, or if it is a solid with a melting point below its vaporization temperature, or if it is soluble in an inert solvent with vapor pressure similar to that of the precursor. Ideally, the precursors should be non-flammable, non-corrosive, non-toxic, non-hazardous, and simple and inexpensive to make. In applications of ALD to microelectronics, precursors with high purity may be required.

It is not easy to find ideal precursors that satisfy all of these requirements. When the properties of precursors are inadequate, satisfactory ALD results cannot be achieved.

R. G. Gordon (\subseteq)

Department of Chemistry and Chemical Biology, Harvard University, Cambridge, MA 02138, USA

e-mail: gordon@chemistry.harvard.edu

16 R. G. Gordon

If the precursor does not have sufficient vapor pressure at a temperature at which it is thermally stable, then the surface reactions cannot be saturated within a practical cycle time. Uniform step coverage will be limited to features with low aspect ratios. Impurities may also be incorporated into the films because some ligands are not removed during an exposure (defined as vapor pressure multiplied by the time of vapor contact) that is too low to complete the surface reactions.

If the thermal stability of a precursor is too low, then decomposition takes place during the surface reactions, and the reactions are usually not self-limited. Step coverage will be non-uniform, and impurities from the ligand decomposition products may remain in the films.

Self-limited surface reactions may not exist because of a number of non-ideal behaviors. The surface reactions may be reversible, so they do not remain saturated when the supply of reactant vapor is removed. If a precursor etches the film, a stable saturated condition will not be reached. If a precursor is not reactive enough with a substrate, nucleation of film is delayed many cycles, and growth happens only sporadically and non-reproducibly on defects on the substrate.

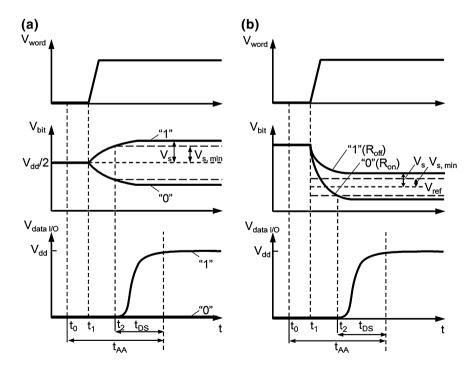

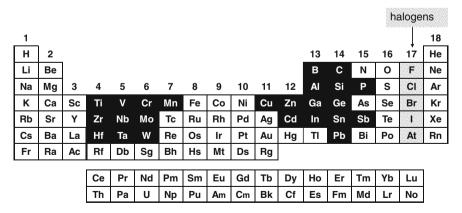

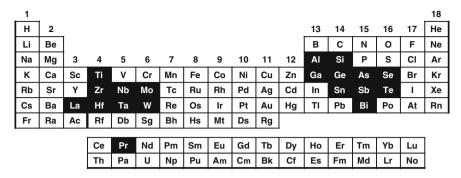

Because of the ingenuity and hard work of many scientists, useful, if not ideal, precursors have been found for most of the non-radioactive elements. Figure 2.1 shows this wide range of elements that have been incorporated into films deposited by ALD. Still missing from this repertoire are the heavier alkali metals sodium, potassium, rubidium, and cesium, for which few volatile compounds are known. The heavier halogens (chlorine, bromine, and iodine) and hydrogen are usually considered deleterious impurities to be avoided in ALD films. Non-reactive elements, such as the noble gases, are not included in ALD films. The highly toxic element, thallium, has also been neglected.

Fig. 2.1 Elements in ALD films

ALD of pure elements has been achieved for the 19 elements that are underlined in Fig. 2.2. Many different types of compounds have been made successfully by ALD. These compounds are shown in Fig. 2.2 as combinations of the element whose symbol is at the center of each box with one or more of the elements whose symbols lie on the periphery of the box. ALD materials are organized by the type or properties of the compound in Fig. 2.3. An impressive breadth of applicability for ALD has been achieved by researchers from around the world. As a result, the

| _1 | 2  |    | _  |    |   |    |    |   |     |            |      |           |     |               |             |      |      | 1    | 13   | 14    |     | 15    |

|----|----|----|----|----|---|----|----|---|-----|------------|------|-----------|-----|---------------|-------------|------|------|------|------|-------|-----|-------|

| 0  | 0  |    |    |    |   |    |    |   |     |            |      |           |     |               |             |      |      |      | 0    |       |     |       |

| Li | Be |    |    |    |   |    |    |   |     |            |      |           |     |               |             |      | ļ,   | PΙ   | В    | С     |     | N     |

|    |    |    |    |    |   |    |    |   |     |            |      |           |     |               |             |      | L    |      |      |       |     |       |

|    | 0  | F  |    |    |   |    |    |   |     |            |      |           |     |               |             |      | - 1  |      |      | N O   |     | во    |

| Na | Mg |    |    |    |   |    |    |   |     |            |      |           |     |               |             |      | ļ!   | P A  | ΔI   | P Si  |     | Si P  |

|    |    | Те |    | 3  |   |    | 4  |   | 5   | 6          | 7    | 8         | 9   | 10            | 11          | 12   | 1    | As   |      | С     |     |       |

|    | 0  | F  | N  | 0  |   | N  | 0  |   | 0   | 0          | N O  | N O       | N O | N O           | N O         | NO I | F    | N (  | 0    | 0     |     |       |

| K  | Ca | s  |    | Sc |   | Zr | Τi | s | ٧   | Cr         | Mn S | <u>Fe</u> | Co  | C <u>Ni</u> S | <u>Cu</u> S | Zn S | s  ı | P    | Ga   | Ge    | 2   | As    |

|    |    |    |    |    |   |    | ΑI | С |     | Al         | Те   |           |     |               |             | Te S | Se / | As   |      | Sb Te | :   |       |

|    | 0  | F  | N  | 0  |   | N  | 0  |   | N O | N          |      | 0         | 0   |               |             |      | ļ.   | N (  | 0    | 0     |     | 0     |

| Rb | Sr | s  |    | Υ  | s | Si | Zr |   | Nb  | Mo         | Tc   | Ru        | Rh  | Pd            | Ag          | Cd S | s  ı | PΙ   | In S | Sr    | ı S | Sb    |

|    | Ti |    |    |    |   | Ti | ΑI |   |     |            |      |           |     |               |             | Te S | Se / | As S | Sb   |       |     | Te    |

|    | 0  |    | N  | 0  | F | Ν  | 0  |   | N O | N O        |      |           | 0   |               |             |      | П    |      |      | 0     |     | 0     |

| Cs | Ba | S  | Si | La | s | Si | Hf |   | Ta  | <u>w</u> s | Re   | Os        | lr  | <u>Pt</u>     | Au          | Hg   |      |      | TI   | Pt    | S   | Si Bi |

|    | Ti |    |    | ΑI |   | ΤĹ | ΑI |   | С   | Si C       |      |           |     |               |             | 1    | Ге   |      |      | Ti    |     | Ti    |

|    |    |    | _  |    | _ |    |    |   |     |            |      |           |     |               |             |      | _    |      |      |       |     |       |

|    | 0  |    |    | 0  |   |    | 0  |   |     | 0          | 0    | 0         | 0   | 0             | 0           | 0    |      | (    | 0    | 0     |     | N O   |

|    | Ce |    |    | Pr |   |    | Nd |   | Pm  | Sm         | Eu   | Gd        | Tb  | Dy            | Ho          | Er   |      | 1    | Tm   | Yt    | )   | Lu    |

|    |    |    | L  |    |   |    |    |   |     |            |      |           |     |               |             |      |      |      |      |       |     |       |

**Fig. 2.2** Combinations of elements in ALD films. ALD films have been made with combinations of 2 or more elements within a box. Underlined elements have been deposited as pure, single elements. Updated from R. Puurunen, J. Appl. Phys. 97, 121301 (2005)

| Oxide dielectrics      | Al <sub>2</sub> O <sub>3</sub> , TiO <sub>2</sub> , ZrO <sub>2</sub> , HfO <sub>2</sub> , Ta <sub>2</sub> O <sub>5</sub> , Nb <sub>2</sub> O <sub>5</sub> , Sc <sub>2</sub> O <sub>3</sub> , Y <sub>2</sub> O <sub>3</sub> , BeO, MgO, B <sub>2</sub> O <sub>3</sub> , |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | SiO <sub>2</sub> , GeO <sub>2</sub> , La <sub>2</sub> O <sub>3</sub> , CeO <sub>2</sub> , PrO <sub>x</sub> , Nd <sub>2</sub> O <sub>3</sub> , Sm <sub>2</sub> O <sub>3</sub> , EuO <sub>x</sub> , Gd <sub>2</sub> O <sub>3</sub> , Dy <sub>2</sub> O <sub>3</sub> ,    |

|                        | Ho <sub>2</sub> O <sub>3</sub> , Er <sub>2</sub> O <sub>3</sub> , Tm <sub>2</sub> O <sub>3</sub> , Yb <sub>2</sub> O <sub>3</sub> , Lu <sub>2</sub> O <sub>3</sub> , SrTiO <sub>3</sub> , BaTiO <sub>3</sub> , PbTiO <sub>3</sub> , PbZrO <sub>3</sub> ,               |

|                        | Bi <sub>x</sub> Ti <sub>y</sub> O, Bi <sub>x</sub> Si <sub>y</sub> O, SrTa <sub>2</sub> O <sub>6</sub> , SrBi <sub>2</sub> Ta <sub>2</sub> O <sub>9</sub> , YScO <sub>3</sub> , LaAlO <sub>3</sub> , NdAlO <sub>3</sub> ,                                              |

|                        | GdScO <sub>3</sub> , LaScO <sub>3</sub> , LaLuO <sub>3</sub> , LaYbO <sub>3</sub> , Er <sub>3</sub> Ga <sub>5</sub> O <sub>13</sub>                                                                                                                                    |

| Oxide conductors or    | In <sub>2</sub> O <sub>3</sub> , In <sub>2</sub> O <sub>3</sub> :Sn, In <sub>2</sub> O <sub>3</sub> :F, In <sub>2</sub> O <sub>3</sub> :Zr, SnO <sub>2</sub> , SnO <sub>2</sub> :Sb, SnO <sub>2</sub> :Al, SnO <sub>2</sub> :N,                                        |

| semiconductors         | Sb <sub>2</sub> O <sub>3</sub> , ZnO, ZnO:Al, ZnO:B, ZnO:Ga, RuO <sub>2</sub> , RhO <sub>2</sub> , IrO <sub>2</sub> , Ga <sub>2</sub> O <sub>3</sub> , VO <sub>2</sub> ,                                                                                               |

|                        | V <sub>2</sub> O <sub>5</sub> , WO <sub>3</sub> , W <sub>2</sub> O <sub>3</sub> , NiO, CuO <sub>x</sub> , FeO <sub>x</sub> , CrO <sub>x</sub> , CoO <sub>x</sub> , MnO <sub>x</sub>                                                                                    |

| Other ternary oxides   | LaCoO <sub>3</sub> , LaNiO <sub>3</sub> , LaMnO <sub>3</sub> , La <sub>1-x</sub> Ca <sub>x</sub> MnO <sub>3</sub>                                                                                                                                                      |

| Nitride dielectrics or | BN, AIN, GaN, InN, Si <sub>3</sub> N <sub>4</sub> , Ta <sub>3</sub> N <sub>5</sub> , Cu <sub>3</sub> N, Zr <sub>3</sub> N <sub>4</sub> , Hf <sub>3</sub> N <sub>4</sub> , LaN, LuN                                                                                     |

| semiconductors         |                                                                                                                                                                                                                                                                        |

| Metallic nitrides      | TiN, Ti-Si-N, Ti-Al-N, TaN, NbN, MoN, WN <sub>x</sub> , WN <sub>x</sub> C <sub>y</sub> , Co <sub>x</sub> N, Sn <sub>x</sub> N                                                                                                                                          |

| II-VI semiconductors   | ZnS, ZnSe, ZnTe, CaS, SrS, BaS, CdS, CdTe, MnTe, HgTe                                                                                                                                                                                                                  |

| II-VI based phosphors  | ZnS:M (M=Mn,Tb,Tm); CaS:M (M=Eu, Ce, Tb, Pb); SrS:M(M=Ce,Tb, Pb)                                                                                                                                                                                                       |

| III-V semiconductors   | GaAs, AIAs, AIP, InP, GaP, InAs                                                                                                                                                                                                                                        |

| Fluorides              | CaF <sub>2</sub> , SrF <sub>2</sub> , MgF <sub>2</sub> , LaF <sub>3</sub> , ZnF <sub>2</sub>                                                                                                                                                                           |

| Elements               | Ru, Pt, Ir, Pd, Rh, Ag, Cu, Ni, Co, Fe, Mn, Ta, W, Mo, Ti, Al, Si, Ge, Sb                                                                                                                                                                                              |

| Other semiconductors   | PbS, SnS, In <sub>2</sub> S <sub>3</sub> , Sb <sub>2</sub> S <sub>3</sub> , Cu <sub>x</sub> S, CuGaS <sub>2</sub> , WS <sub>2</sub> , SiC, Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub>                                                                             |

| Others                 | La <sub>2</sub> S <sub>3</sub> , Y <sub>2</sub> O <sub>2</sub> S, TiC <sub>x</sub> , TiS <sub>2</sub> , TaC <sub>x</sub> , WC <sub>x</sub> , Ca <sub>3</sub> (PO <sub>4</sub> ) <sub>2</sub> , CaCO <sub>3</sub> , organics                                            |

|                        |                                                                                                                                                                                                                                                                        |

Fig. 2.3 ALD materials by type. Updated from M. Ritala and J. Niinisto, in Chemical vapor deposition (Royal Society of Chemistry, 2009)

18 R. G. Gordon

number of papers applying known ALD processes now greatly outnumbers those reporting new ones. Nevertheless, considerable challenges remain for finding precursors with more nearly ideal properties for use in ALD. Recently, many reviews of ALD and its applications have been published [1–18].

This review will first summarize the various types of chemicals that have been used successfully as precursors for ALD processes. Then the kinds of surface reactions that they undergo will be classified. Despite the wide variety of chemical types involved, it will become clear that only a few kinds of surface reactions account for the many ALD processes that have been discovered.

### 2.2 Types of ALD Precursors for Metals

In a few cases, the elements themselves, rather than compounds, can serve as ALD precursors. The metals zinc, cadmium, and mercury are the most common examples. Most other metals have vapor pressure that is too low, unless they are evaporated from high-temperature effusion sources in high vacuum, as in molecular beam epitaxy (MBE) systems. While MBE can be an excellent tool for laboratory investigations, it is not as easily scaled to large-area production of films as are the conventional ALD processes based on more volatile precursors.

Halide compounds, including fluorides, chlorides, and iodides, have been used as precursors for ALD for those elements shown with a dark background in Fig. 2.4. Halides generally display excellent thermal stability. Widespread industrial use is made of titanium tetrachloride, TiCl<sub>4</sub>, to make titanium nitride, TiN, electrodes for DRAM, and hafnium tetrachloride, HfCl<sub>4</sub>, to make HfO<sub>2</sub> gate dielectric for transistors. Vapor pressures of halides vary widely. Tungsten hexafluoride, WF<sub>6</sub>, is a gas at room temperature. Copper(I) chloride, CuCl, requires

Fig. 2.4 Elements with halide ALD precursors. Halides are compounds  $MX_n$ , n = 1, 2, 3, 4, 5 or 6, of an element M and a halogen X = F, Cl, Br or I

high temperature (340 °C) to produce a useful amount of vapor [19]. The main disadvantage of metal halides is the corrosive nature of the precursors and their reaction byproducts. They can etch or corrode substrates, the deposited films, ALD equipment, and vacuum pumps. For example, a NbCl $_5$  precursor partly etches away Nb $_2$ O $_5$  film as it is formed, so non-uniform thicknesses are observed [20]. Halide impurities can also be retained in the films, with deleterious consequences to their properties.

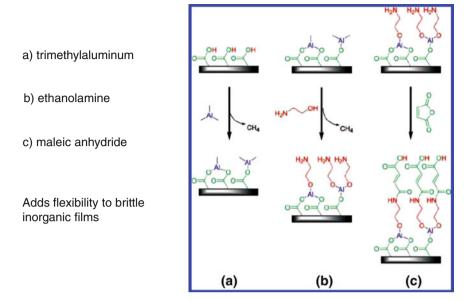

Metal alkyls, which have metal-carbon bonds, are another popular class of precursor for ALD. Trimethylaluminum, (CH<sub>3</sub>)<sub>3</sub>Al, is probably the precursor most often used for depositing aluminum oxide because it displays nearly ideal properties.[1] Diethylzinc, (C<sub>2</sub>H<sub>5</sub>)<sub>2</sub>Zn [21] and dimethylzinc, (CH<sub>3</sub>)<sub>2</sub>Zn [22], are usually used for depositing zinc oxide. These metal alkyls need to be handled carefully because they ignite spontaneously if exposed to air (pyrophoric behavior), and can explode if contacted by water. Safer non-pyrophoric aluminum alkylalkoxides, such as dimethylaluminum isopropoxide [23], are also effective for ALD of aluminum oxide. Non-pyrophoric complexes of dimethylzinc with Lewis bases, such as dimethylsulfide, are also known [24–26]. Figure 2.5 shows those elements with metal alkyl precursors suitable for ALD. Other metal alkyls lack sufficient volatility or thermal stability for use in ALD.

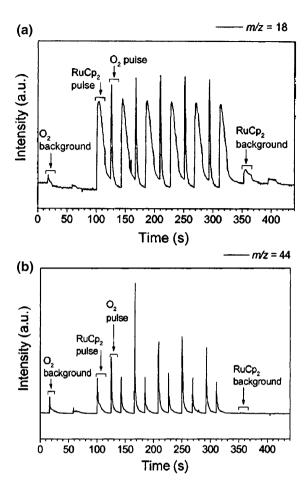

Cyclopentadienyl ligands (Fig. 2.6) tend to form more stable metal compounds because they form 5 carbon-metal bonds for each ligand [27–30]. In comparison, each metal atom is bonded to only one carbon atom in each ligand of a metal alkyl. Small metal atoms, such as magnesium, are bound to cyclopentadiene rings with just small hydrogen atoms attached. For large atoms, such as lanthanum, bulky isopropyl groups are attached to the cyclopentadienyl ring so that the resulting compound remains monomeric and is thus slightly volatile. Examples of metal cyclopentadienyl compounds are listed in Fig. 2.7. A wide variety of metal cyclopentadienyls, shown in Fig. 2.8, have been used in ALD. Because of the strong metal-carbon bonding, cyclopentadienyl ligands can be difficult to remove completely, sometimes contaminating ALD films with carbon impurity.

| 1  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 18 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Н  | 2  |    |    |    |    |    |    |    |    |    |    | 13 | 14 | 15 | 16 | 17 | Не |

| Li | Ве |    |    |    |    |    |    |    |    |    |    | В  | С  | N  | 0  | F  | Ne |

| Na | Mg | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | Al | Si | Р  | S  | CI | Ar |

| K  | Ca | Sc | Ti | ٧  | Cr | Mn | Fe | Со | Ni | Cu | Zn | Ga | Ge | As | Se | Br | Kr |

| Rb | Sr | Υ  | Zr | Nb | Мо | Тс | Ru | Rh | Pd | Ag | Cd | In | Sn | Sb | Те | ı  | Хe |

| Cs | Ва | La | Hf | Та | W  | Re | Os | lr | Pt | Au | Hg | TI | Pb | Bi | Ро | At | Rn |

| Fr | Ra | Ac | Rf | Db | Sg | Bh | Hs | Mt | Ds | Rg |    |    |    |    |    |    |    |

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|    |    |    | Се | Pr | Nd | Pm | Sm | Eu | Gd | Tb | Dy | Но | Er | Tm | Yb | Lu |    |

|    |    |    | Th | Pa | U  | Np | Pu | Am | Cm | Bk | Cf | Es | Fm | Md | Lr | No |    |

Fig. 2.5 Elements with alkyl ALD precursors

20 R. G. Gordon

$$Cp = cyclopentadienyl \\ HC \\ \Theta \\ CH \\ HC \\ CH \\ CH_3 \\ CH_4 \\ CH_3 \\ CH_5 \\ CH_$$

Fig. 2.6 Cyclopentadienyl ligands

Cyclopentadienyl ligands can also be mixed with alkyl groups attached to the same metal atom. A popular example of such heteroleptic precursors is (methylcyclopentadienyl)(trimethyl)platinum: [31, 32].

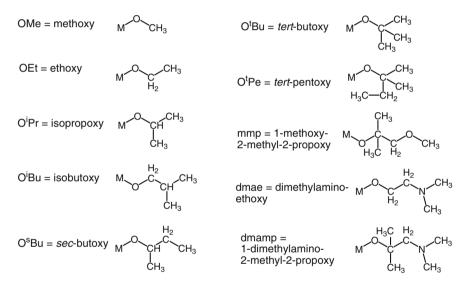

Alkoxide compounds have a metal bonded to oxygen, which is then attached to carbon, as illustrated in Fig. 2.9. Alkoxides are known for most of the metals in the periodic table, but only a few of them, identified in Fig. 2.10, have all the properties needed for ALD. Other alkoxides lack sufficient thermal stability and/or volatility [33]. Some alkoxide precursors are listed in Fig. 2.11. A popular alkoxide precursor is titanium isopropoxide [34, 35]:

Cp<sub>2</sub>Ni = bis(cyclopentadienyl)nickel(II)

(EtCp)<sub>2</sub>Ru = bis(ethylcyclopentadienyl)ruthenium(II)

(Me<sub>5</sub>Cp)<sub>2</sub>Sr = bis(pentamethylcyclopentadienyl)strontium

(PrCp)3La = tris(isopropylcyclopentadienyl)lanthanum

$Cp_2Me_2Zr = (dicyclopentadienyl)(dimethyl)zirconium$

(MeCp)(Me)<sub>3</sub>Pt = (methylcyclopentadienyl)(trimethyl)platinum(IV)

Fig. 2.7 Examples of cyclopentadienyl precursors

One way to make alkoxides more thermally stable is to attach a dialkylamine group at the end of an alkyl chain of the alkoxide, as in the 1-dimethylamino-2-methyl-2-propanolate (dmamp) ligand:

$$Ni(dmamp)_2 \xrightarrow{H_3C} \xrightarrow{CH_3} \xrightarrow{CH_3} \xrightarrow{CH_3}$$

$$H_2C \xrightarrow{Ni} \xrightarrow{CH_2} \xrightarrow{CH_2} \xrightarrow{CH_3}$$

| 1  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 18 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Н  | 2  |    |    |    |    |    |    |    |    |    |    | 13 | 14 | 15 | 16 | 17 | He |

| Li | Ве |    |    |    |    |    |    |    |    |    |    | В  | С  | N  | 0  | F  | Ne |

| Na | Mg | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | AI | Si | Р  | S  | CI | Ar |

| K  | Ca | Sc | Ti | ٧  | Cr | Mn | Fe | Со | Ni | Cu | Zn | Ga | Ge | As | Se | Br | Kr |

| Rb | Sr | Υ  | Zr | Nb | Мо | Тс | Ru | Rh | Pd | Ag | Cd | In | Sn | Sb | Те | 1  | Хе |

| Cs | Ва | La | Hf | Та | w  | Re | Os | lr | Pt | Au | Hg | TI | Pb | Bi | Ро | At | Rn |

| Fr | Ra | Ac | Rf | Db | Sg | Bh | Hs | Mt | Ds | Rg |    |    |    |    |    |    |    |

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|    |    |    | Се | Pr | Nd | Pm | Sm | Eu | Gd | Tb | Dy | Но | Er | Tm | Yb | Lu |    |

|    |    |    | Th | Pa | U  | Np | Pu | Am | Cm | Bk | Cf | Es | Fm | Md | Lr | No |    |

Fig. 2.8 Cyclopentadienyl ALD precursors

Fig. 2.9 Alkoxide Compounds

The attachment of the metal to each ligand by two bonds stabilizes the molecule by what is called the "chelate effect". It is, however, more difficult to remove these chelated ligands using reducing agents such as hydrogen or ammonia, so impurities of carbon, oxygen, and nitrogen from the ligands are found to contaminate the nickel metal films. Water vapor does cleanly cleave the ligands to deposit pure nickel oxide [36].

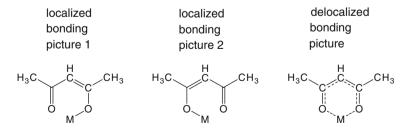

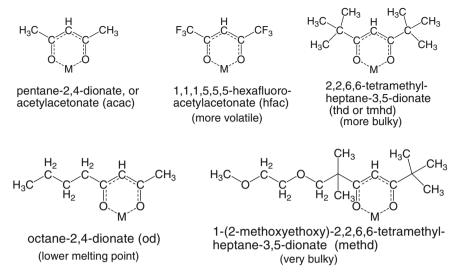

Metal  $\beta$ -diketonates have 2 metal-oxygen bonds for each ligand, as pictured in Fig. 2.12. The chelate effect makes metal  $\beta$ -diketonates more thermally stable than metal alkoxides. By varying the atoms or atom groups attached to the 3 carbon atoms, the properties of metal  $\beta$ -diketonates can be adjusted. Small groups, such as methyl, are suitable for small metals, while bulky groups are needed to maintain a

| . 1 |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 18 |

|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Н   | 2  |    |    |    |    |    |    |    |    |    |    | 13 | 14 | 15 | 16 | 17 | He |

| Li  | Ве |    |    |    |    |    |    |    |    |    |    | В  | С  | N  | 0  | F  | Ne |

| Na  | Mg | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | ΑI | Si | Р  | s  | CI | Ar |

| K   | Ca | Sc | Ti | ٧  | Cr | Mn | Fe | Со | Ni | Cu | Zn | Ga | Ge | As | Se | Br | Kr |

| Rb  | Sr | Υ  | Zr | Nb | Мо | Тс | Ru | Rh | Pd | Ag | Cd | In | Sn | Sb | Те | ı  | Xe |

| Cs  | Ва | La | Hf | Та | W  | Re | Os | lr | Pt | Au | Hg | TI | Pb | Bi | Ро | At | Rn |

| Fr  | Ra | Ac | Rf | Db | Sg | Bh | Hs | Mt | Ds | Rg |    |    |    |    |    |    |    |

|     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|     |    |    | Се | Pr | Nd | Pm | Sm | Eu | Gd | Tb | Dy | Но | Er | Tm | Yb | Lu |    |

|     |    |    | Th | Pa | U  | Np | Pu | Am | Cm | Bk | Cf | Es | Fm | Md | Lr | No |    |

Fig. 2.10 Elements with alkoxide ALD precursors

Al(OEt)<sub>3</sub> = tris(ethoxy)aluminum = aluminum ethoxide AIMe<sub>2</sub>(O<sup>i</sup>Pr) = isopropoxydimethylaluminum B(OMe)<sub>3</sub> = tris(methoxy)boron = trimethylborate  $Hf(O^{t}Bu)_{4} = tetra(tert-butoxy)hafnium = hafnium tert-butoxide$  $Hf(mmp)_{4} = tetra(1-methoxy-2-methyl-2-propoxy)hafnium$ Nb(OEt)<sub>5</sub> = penta(ethoxy)niobium = niobium ethoxide Ni(dmamp)<sub>2</sub> = bis (1-dimethylamino-2-methyl-2-propoxy)nickel(II)  $Pb(O^tBu)_2 = bis(tert-butoxy)lead(II) = lead(II) tert-butoxide$  $Si(OEt)_4 = tetra(ethoxy)silane = tetraethylorthosilicate = TEOS$ Si(OtBu)3OH = tris(tert-butoxy)silanol = TBOS Si(O<sup>t</sup>Pe)<sub>3</sub>OH = tris(tert-pentoxy)silanol = TPSOL Ta(OEt)<sub>5</sub> = penta(ethoxy)tantalum = tantalum ethoxide Ti(OMe)<sub>4</sub> = tetra(methoxy)titanium = titanium methoxide Ti(OEt)₄ = tetra(ethoxy)titanium = titanium ethoxide Ti(O<sup>i</sup>Pr)<sub>4</sub> = tetra(isopropoxy)titanium = titanium isopropoxide VO(O<sup>i</sup>Pr)<sub>3</sub>=tris(isopropoxy)oxovanadium=vanadyl isopropoxide

Fig. 2.11 Alkoxide compounds used in ALD

Fig. 2.12 Three ways to represent a metal acetylacetonate (acac)

24 R. G. Gordon

Fig. 2.13 Beta-diketonate compounds

| . 1 |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 18 |

|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Н   | 2  |    |    |    |    |    |    |    |    |    |    | 13 | 14 | 15 | 16 | 17 | He |

| Li  | Ве |    |    |    |    |    |    |    |    |    |    | В  | С  | N  | 0  | F  | Ne |

| Na  | Mg | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | AI | Si | Р  | s  | CI | Ar |

| Κ   | Ca | Sc | Ti | ٧  | Cr | Mn | Fe | Со | Ni | Cu | Zn | Ga | Ge | As | Se | Br | Kr |

| Rb  | Sr | Υ  | Zr | Nb | Мо | Тс | Ru | Rh | Pd | Ag | Cd | In | Sn | Sb | Те | 1  | Хе |

| Cs  | Ва | La | Hf | Та | W  | Re | Os | lr | Pt | Au | Hg | TI | Pb | Bi | Ро | At | Rn |

| Fr  | Ra | Ac | Rf | Db | Sg | Bh | Hs | Mt | Ds | Rg |    |    |    |    |    |    | _  |

|     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|     |    |    | Се | Pr | Nd | Pm | Sm | Eu | Gd | Tb | Dy | Но | Er | Tm | Yb | Lu |    |

|     |    |    | Th | Pa | U  | Np | Pu | Am | Cm | Bk | Cf | Es | Fm | Md | Lr | No |    |

Fig. 2.14 Elements with beta-diketonate ALD precursors

monomeric molecular structure for large metals, as diagrammed in Fig. 2.13. Fluorine substitution increases the vapor pressure. The melting point can be decreased by substitution of longer hydrocarbon chains. By these adjustments, metal  $\beta$ -diketonate precursors have been demonstrated for many metals (Fig. 2.14) [37–40]. Typical metal  $\beta$ -diketonate precursors are listed in Fig. 2.15.

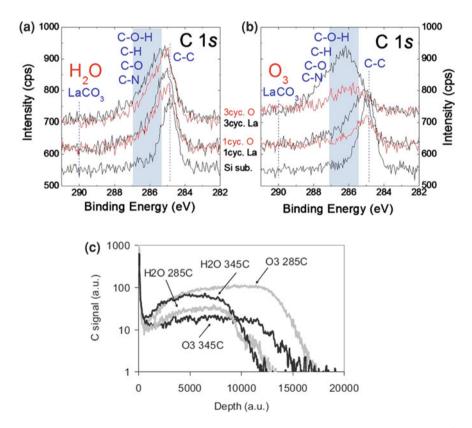

Because metal  $\beta$ -diketonates are so stable, very reactive sources must often be used as the co-reactants. For example, strong oxidants, such as ozone, are typically required to deposit metal oxides from metal  $\beta$ -diketonates, and these strong oxidants can attack substrates. Byproducts of these oxidation reactions include carbon dioxide, which can cause carbonate contamination of oxides of large metals, such

**Fig. 2.15** Beta-diketonate ALD precursors

| Ba(thd) <sub>2</sub>  | $Mg(thd)_2$            |

|-----------------------|------------------------|

| Ce(thd) <sub>4</sub>  | $Mn(thd)_3$            |

| Co(acac) <sub>2</sub> | $Nd(thd)_3$            |

| Co(acac) <sub>3</sub> | Ni(acac) <sub>2</sub>  |

| Co(thd) <sub>3</sub>  | $Ni(thd)_2$            |

| Cr(acac) <sub>3</sub> | Pb(thd) <sub>2</sub>   |

| Cu(hfac) <sub>2</sub> | Pd(hfac) <sub>2</sub>  |

| Cu(thd) <sub>2</sub>  | Pd(thd) <sub>2</sub>   |

| Dy(thd) <sub>3</sub>  | Pt(acac) <sub>2</sub>  |

| Er(thd) <sub>3</sub>  | $Ru(thd)_3$            |

| Eu(thd) <sub>3</sub>  | $Ru(od)_3$             |

| Fe(acac) <sub>3</sub> | Sc(thd) <sub>3</sub>   |

| Fe(thd) <sub>3</sub>  | Sm(thd) <sub>3</sub>   |

| Gd(thd) <sub>3</sub>  | $Sr(thd)_2$            |

| Ho(thd) <sub>3</sub>  | Sr(methd) <sub>2</sub> |

| Ir(acac) <sub>3</sub> | $Tm(thd)_3$            |

| La(thd) <sub>3</sub>  | $Y(thd)_3$             |

|                       |                        |

as strontium and lanthanum. Metal nitrides can be difficult to make from metal  $\beta$ -diketonates because the strong metal-oxygen bonds are hard to disrupt with nitrogen sources.

Nitrogen is bonded to metals in metal amides (a single chemical bond between nitrogen and a metal) and metal imides (a double bond between nitrogen and a metal). Some typical amides and imides are illustrated in Fig. 2.16. Precursors of these types have been developed for some metals highlighted in Fig. 2.17, and

$$NMe_2 = dimethylamino = dimethylamido \\ M = M_2C = CH_3 \\ NEtMe = ethylmethylamino = ethylmethylamido \\ NEt_2 = diethylamino = diethylamido \\ M = M_2C = CH_3 \\ M = M_2C = C$$

Fig. 2.16 Amide and imide ligands

26 R. G. Gordon

Fig. 2.17 Elements with amide and imide precursors for ALD

$Al(NMe_2)_3 = tris(dimethylamido)aluminum$ = Al<sub>2</sub>(NMe<sub>2</sub>)<sub>6</sub> = hexakis(dimethylamido)dialuminum  $Bi[N(SiMe_3)_2]_3 = tris(bis(trimethylsilyl)amido)bismuth$  $Hf(NMe_2)_4 = tetrakis(dimethylamido)hafnium$ Hf(NEtMe)₄ = tetra(ethylmethylamido)hafnium = TEMAH  $Hf(NEt_2)_4 = tetrakis(diethylamido)hafnium = TDEAH$  $La[N(SiMe_3)_2]_3 = tris(bis(trimethylsilyl)amido)lanthanum$  $Pr[N(SiMe_3)_2]_3 = tris(bis(trimethylsilyl)amido)praseodymium$  $Ta(NMe_2)_5 = pentakis(dimethylamido)tantalum$  $Ta(NEt_2)_5 = pentakis(diethylamido)tantalum$  $Ta(NtBu)(NEt_2)_3 = (tert-butylimido)tris(diethylamido)tantalum$ Ti(NMe<sub>2</sub>)<sub>4</sub> = tetrakis(dimethylamido)titanium  $Ti(NEtMe)_{4} = tetra(ethylmethylamido)titanium = TEMAT$  $W(NtBu)_2(NMe_2)_2 = bis(tert-butylimido)bis(dimethylamido)tungsten$  $Zn[N(SiMe_3)_2]_2 = bis(bis(trimethylsilyl)amido)zinc$ Zr(NMe2)<sub>4</sub> = tetrakis(dimethylamido)zirconium Zr(NEtMe)<sub>4</sub> = tetra(ethylmethylamido)zirconium = TEMAZ  $Zr(NEt_2)_4$  = tetrakis(diethylamido)zirconium = TDEAZ

Fig. 2.18 Amide and imide precursors for ALD

particular examples are listed in Fig. 2.18. Dialkylamide precursors are popular for making zirconium and hafnium oxides and nitrides. The reactivity of metal dialkylamides is quite high, so deposition is possible at very low substrate temperatures, even down to room temperature. This low temperature capability can be used for coating plastics and biological specimens, or for patterning by lift-off of photoresist [41]. The thermal stability of dialkylamides is generally limited, so substrate temperatures must be kept below their decomposition temperatures. A widely used metal amide precursor is tetrakis(ethylmethylamido)hafnium (TE-MAH) [42, 43]:

Metal amides may also be stabilized by the chelate effect. An example is a cyclic amide of tin(II) ("CAT"),

which is an effective ALD precursor for SnS and SnO<sub>2</sub> [44-46].

An example of a precursor with both imide bonds and amide bonds is provided by the useful precursor bis(*tert*-butylimido)bis(dimethylamido)tungsten(VI):

$$(H_3C)_3CN \\ W \\ NC(CH_3)_3 \\ (H_3C)_2N \\ N(CH_3)_2$$

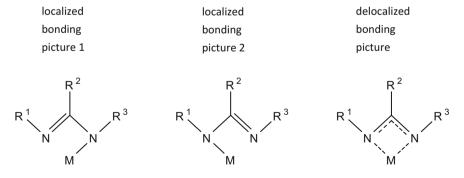

Metal amidinates have two metal-nitrogen bonds, as diagrammed in Fig. 2.19 [16]. Amidinates relate to amides analogously to how  $\beta$ -diketonates relate to alkoxides. The chelate effect results in metal amidinates being more thermally stable than metal amides, which have only one metal-nitrogen bond. By making

Fig. 2.19 Three ways to represent metal amidinate compounds.  $R^1$ ,  $R^2$  and  $R^3$  are non-metals, usually alkyl groups  $C_xH_{2x+1}$ ; other non-metals, such as silicon or nitrogen may be included

28 R. G. Gordon

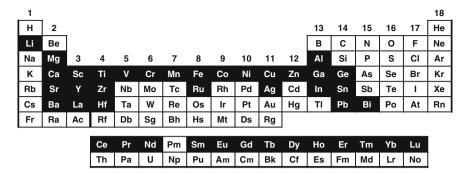

Fig. 2.20 Elements with amidinate ALD precursors

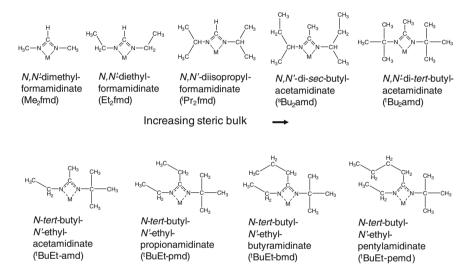

Increasing flexibility leads to decreasing melting points and liquids -

Fig. 2.21 Some amidinate ligands

appropriate choices of the amidinate ligands, volatile and reactive ALD precursors have been constructed for many metals, as shown in Fig. 2.20 [47–51].

The physical and chemical properties of metal amidinates can be adjusted by choice of the alkyl groups attached to the two nitrogens in an amidinate ligand (Fig. 2.21). The required size of the alkyl groups depends both on the size of the metal atom and the number of amidinate ligands attached to it (normally equal to the oxidation state of the metal, for a neutral compound).

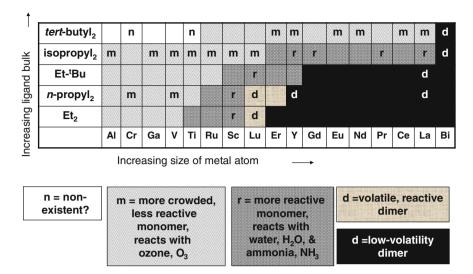

To make the most volatile amidinates, the alkyl groups should be just large enough to prevent oligomerization of the compound. This trend is illustrated for metal acetamidinates with two ligands in Fig. 2.22, which display monomeric, dimeric, or polymeric structures, depending on the ligand size. Small metals and

| Increasing ligand bulk→ | tert-butyl <sub>2</sub>       | m  | m  | m  | m  | m  | m  | d  | d  | d  |

|-------------------------|-------------------------------|----|----|----|----|----|----|----|----|----|

|                         | isopropyl <sub>2</sub>        | m  | m  | m  | d  | d  | d  | d  | р  | р  |

|                         | <sup>t</sup> Bu-Et            | m  | d  | d  | d  |    |    |    | р  | р  |

|                         | <i>n</i> -propyl <sub>2</sub> |    | d  |    |    |    |    |    |    |    |

|                         |                               | Ni | Со | Cr | Fe | Mg | Mn | Ca | Sr | Ва |

Increasing size of metal atom ----

m = volatile monomer d = volatile dimer p = non-volatile polymer

Fig. 2.22 Structures of metal(II) acetamidinates

bulky ligands form volatile monomers, as indicated in the upper left part of Fig. 2.22. The most volatile compound for each metal is the lowest monomeric one. The dimers below them are a little less volatile, and become monomeric in the vapor phase. Compounds with ligands that are too small for their large metals result in non-volatile polymers, as seen in the lower right part of Fig. 2.22. Bis(*N*,*N*'-di-*tert*-butylacetamidinato)nickel(II) is a widely used precursor for nickel nitride and nickel oxide films:

$$Ni(^{t}Bu_{2}amd)_{2} \qquad \qquad H_{3}C - C - CH_{3}$$

$$Ni(^{t}Bu_{2}amd)_{2} \qquad \qquad Ni - C - CH_{3}$$

$$Ni(^{t}Bu_{2}amd)_{3} - C(CH_{3})_{3} - C(CH_{3})_{3}$$

Because its surface reactions are slow, this same precursor is very useful in CVD, where it produces highly conformal coatings much more quickly than is possible by ALD [52, 53].

Copper(I) amidinates are always dimers, such as (N,N'-di-sec-butylami-do)copper(I) dimer [47, 54, 55]:

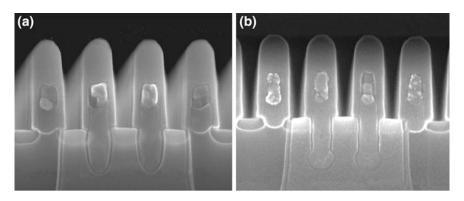

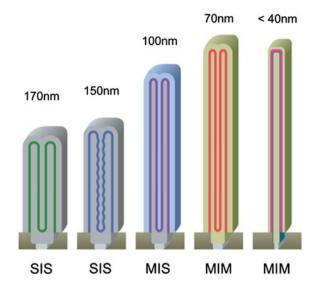

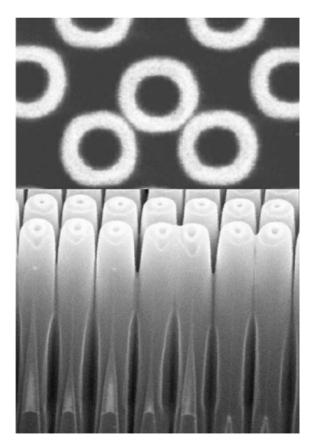

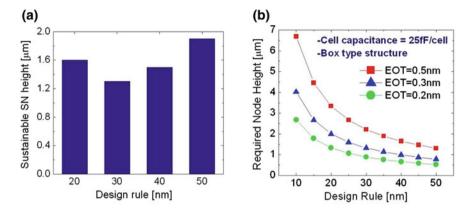

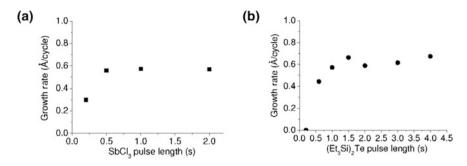

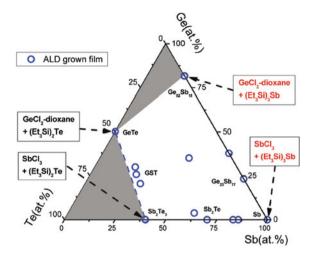

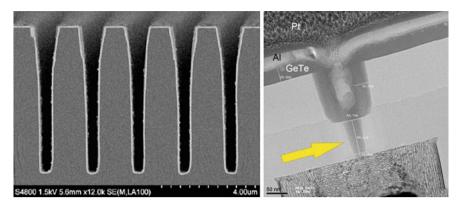

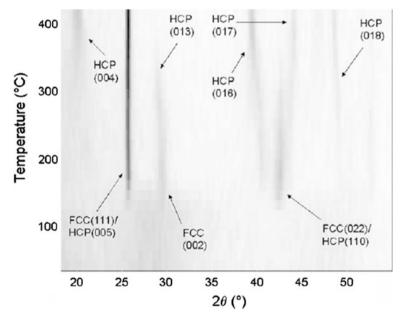

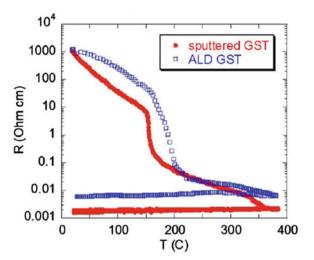

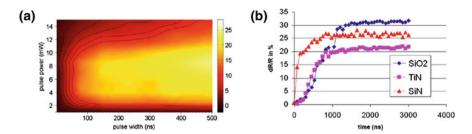

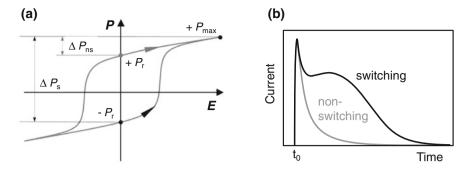

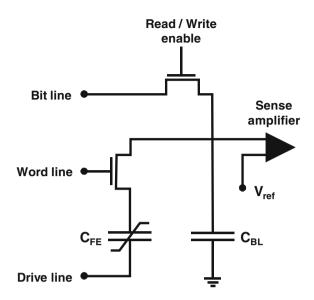

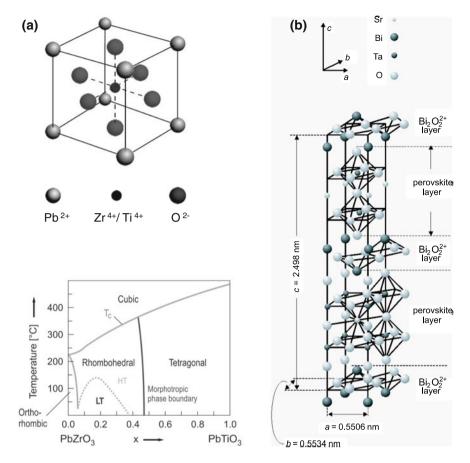

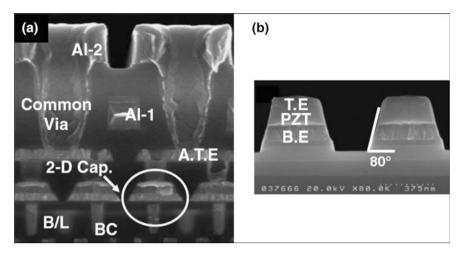

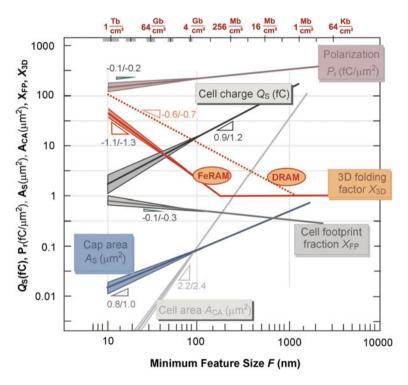

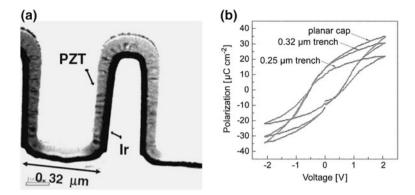

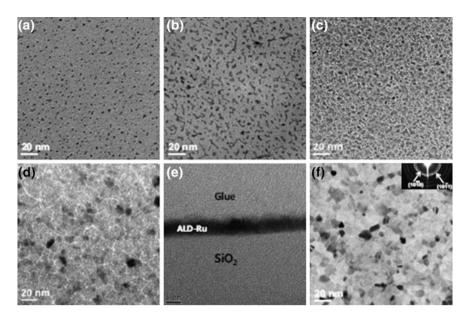

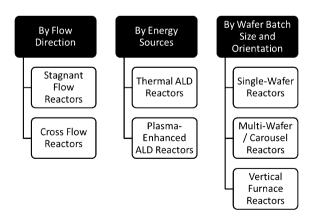

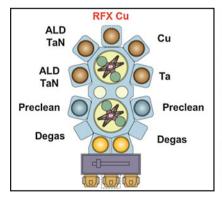

Fig. 2.23 Structures of metal(III) acetamidinates