## Eugenio Villar *Editor*

# Embedded Systems Specification and Design Languages

Selected Contributions from FDL'07

# Embedded Systems Specification and Design Languages

Selected contributions from FDL'07

#### Lecture Notes in Electrical Engineering

Embedded Systems Specification and Design Languages Villar, Eugenio (Ed.) 2008, Approx. 400 p., Hardcover ISBN: 978-1-4020-8296-2, Vol. 10

Content Delivery Networks Buyya, Rajkumar; Pathan, Mukaddim; Vakali, Athena (Eds.) 2008, Approx. 400 p., Hardcover ISBN: 978-3-540-77886-8, Vol. 9

Unifying Perspectives in Computational and Robot Vision Kragic, Danica; Kyrki, Ville (Eds.) 2008, 28 illus., Hardcover ISBN: 978-0-387-75521-2, Vol. 8

Sensor and Ad-Hoc Networks Makki, S.K.; Li, X.-Y.; Pissinou, N.; Makki, S.; Karimi, M.; Makki, K. (Eds.) 2008, Approx. 350 p. 20 illus., Hardcover ISBN: 978-0-387-77319-3, Vol. 7

Trends in Intelligent Systems and Computer Engineering Castillo, Oscar; Xu, Li; Ao, Sio-Iong (Eds.) 2008, Approx. 750 p., Hardcover ISBN: 978-0-387-74934-1, Vol. 6

Advances in Industrial Engineering and Operations Research Chan, Alan H.S.; Ao, Sio-Iong (Eds.) 2008, XXVIII, 500 p., Hardcover ISBN: 978-0-387-74903-7, Vol. 5

Advances in Communication Systems and Electrical Engineering Huang, Xu; Chen, Yuh-Shyan; Ao, Sio-Iong (Eds.) 2008, V, 615 p., Hardcover ISBN: 978-0-387-74937-2, Vol. 4

Digital Noise Monitoring of Defect Origin Aliev T. 2007, XIV, 223 p. 15 illus., Hardcover ISBN: 978-0-387-71753-1, Vol. 2

Multi-Carrier Spread Spectrum 2007 Plass, S.; Dammann, A.; Kaiser, S.; Fazel, K. (Eds.) 2007, X, 106 p., Hardcover ISBN: 978-1-4020-6128-8, Vol. 1 Eugenio Villar Editor

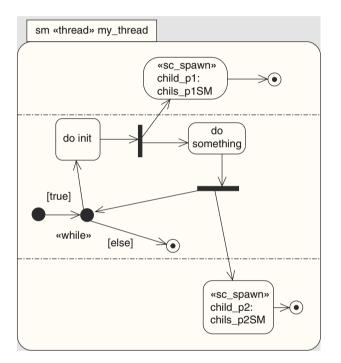

# Embedded Systems Specification and Design Languages

Selected contributions from FDL'07

*Editor* Prof. Eugenio Villar University of Cantabria Spain

Series Editors Sio-Iong Ao IAENG Secretariat 37–39 Hung To Road Unit 1, 1/F Hong Kong People's Republic of China

Li Xu Zhejiang University College of Electrical Engineering Department of Systems Science & Engineering Yu-Quan Campus 310027 Hangzhou People's Republic of China

ISBN 978-1-4020-8296-2 e-ISBN 978-1-4020-8297-9

Library of Congress Control Number: 2008921989

© 2008 Springer Science + Business Media, B.V.

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Printed on acid-free paper

9 8 7 6 5 4 3 2 1

springer.com

#### Preface

FDL is the premier European forum to present research results, to exchange experiences, and to learn about new trends in the application of specification and design languages as well as of associated design and modeling methods and tools for complex, heterogeneous HW/SW embedded systems. Modeling and specification concepts push the development of new methodologies for design and verification to system level; thus providing the means for model driven design of complex information processing systems in a variety of application domains. The aim of FDL is to cover several related thematic areas and to give an opportunity to gain up-to-date knowledge in this fast evolving, essential area in system design and verification.

FDL'07 was the tenth of a series of successful events that were held in Lausanne, Lyon, Tübingen, Marseille, Frankfurt am Main, Lille and Darmstad. FDL'07 was held between September 18 and 20, 2007 at the 'Casa de Convalescència', the main Congress facilities of the 'Universitat Autònoma de Barcelona' in the city center of Barcelona, the capital city of Catalonia, Spain.

The high number of submissions to the conference this year allowed the Program Committee to prepare a high quality conference program.

The book includes a selection of the most relevant contributions based on the review made by the program committee members and the quality of the contents of the presentation at the conference. The original content of each paper has been revised and improved by the authors following the comments made by the reviewers.

FDL'07 was organized again around four thematic areas (TA) that cover essential aspects of system-level design methods and tools. The book follows the same structure:

Part I, C/C++ Based System Design, contains seven chapters covering a comparison between Esterel and SystemC, modeling of asynchronous circuits, TLM bus models, SystemC debugging, quality analysis of SystemC test benches and SystemC simulation of a custom configurable architecture.

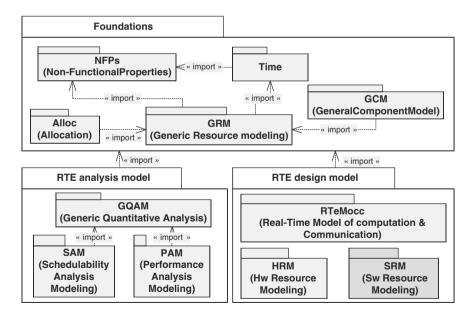

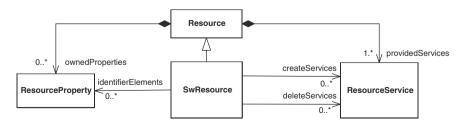

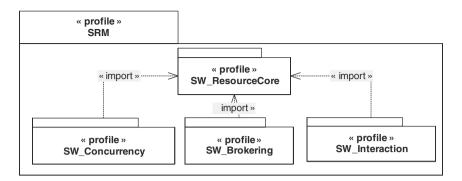

Part II, Analog, Mixed-Signal, and Heterogeneous System Design, includes three chapters addressing heterogeneous, mixed-signal modeling, extensions to VHDL-AMS for partial differential equations and modeling of configurable CMOS transistors. Part III, UML-Based System Specification and Design, presents six contributions comparing AADL with MARTE, modeling real-time resources, proposing model transformations to synchronous languages, mapping UML to SystemC, defining a SystemC UML profile with dynamic features and generating SystemC from StateCharts.

Part IV, Formalisms for Property-Driven Design, is composed of three chapters presenting methods for monitoring logical and temporal assertions, for transactorbased formal verification and a case study in property-based synthesis.

The collection of contributions to the book provides an excellent overview of the latest research contributions to the application of languages to the specification, design and verification of complex Embedded Systems. The papers cover the most important aspects in this essential area in Embedded Systems design.

I would like to take this opportunity to thank the member of the program committee who made a tremendous effort in revising and selecting the best papers for the conference and the most outstanding among them for this book. Specially, the four Topic Chairs, Frank Oppenheimer from OFFIS, responsible of C/C++ Based System Design, Sorin Huss from TU Darmstad, responsible of Analog, Mixed-Signal, and Heterogeneous System Design, Pierre Boulet from Lille University, responsible of UML-Based System Specification and Design and Dominique Borrione from TIMA, responsible of Formalisms for Property-Driven Design. I would like to thank also all the authors for the extra work made in revising and improving their contributions to the book.

The objective of the book is to serve as a reference text for researchers and designers interested in the extension and improvement of the application of design and verification languages in the area of Embedded Systems.

Eugenio Villar FDL'07 General Chair University of Cantabria

#### Contents

#### Part I C/C++ Based System Design

| 1  | How Different Are Esterel and SystemC                                                                                                                   | 3  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2  | Timed Asynchronous Circuits Modeling and Validation         Using SystemC.         Cédric Koch-Hofer and Marc Renaudin                                  | 15 |

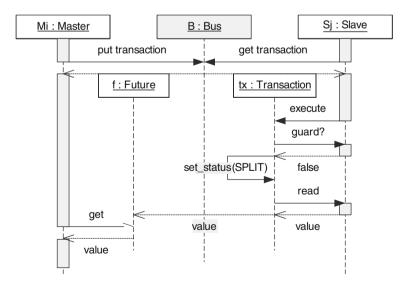

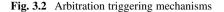

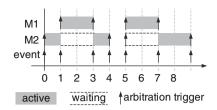

| 3  | <b>On Construction of Cycle Approximate Bus TLMs</b>                                                                                                    | 31 |

| 4  | <b>Combinatorial Dependencies in Transaction Level Models</b><br>Robert Guenzel, Wolfgang Klingauf, and James Aldis                                     | 45 |

| 5  | An Integrated SystemC Debugging Environment<br>Frank Rogin, Christian Genz, Rolf Drechsler, and Steffen Rülke                                           | 59 |

| 6  | Measuring the Quality of a SystemC Testbench<br>by Using Code Coverage Techniques<br>Daniel Große, Hernan Peraza, Wolfgang Klingauf, and Rolf Drechsler | 73 |

| 7  | SystemC-Based Simulation of the MICAS Architecture<br>Dragos Truscan, Kim Sandström, Johan Lilius, and Ivan Porres                                      | 87 |

| Pa | rt II Analog, Mixed-Signal, and Heterogeneous System Design                                                                                             |    |

| 8  | Heterogeneous Specification with HetSC and SystemC-AMS:                                                                                                 |    |

| 8 | Heterogeneous Specification with HetSC and SystemC-AMS: |     |

|---|---------------------------------------------------------|-----|

|   | Widening the Support of MoCs in SystemC                 | 107 |

|   | F. Herrera, E. Villar, C. Grimm, M. Damm, and J. Haase  |     |

| Contents |

|----------|

|----------|

| 9   | An Extension to VHDL-AMS for AMS Systems with Partial<br>Differential Equations                                                                            | 123 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | Leran Wang, Chenxu Zhao, and Tom J. Kazmierski                                                                                                             |     |

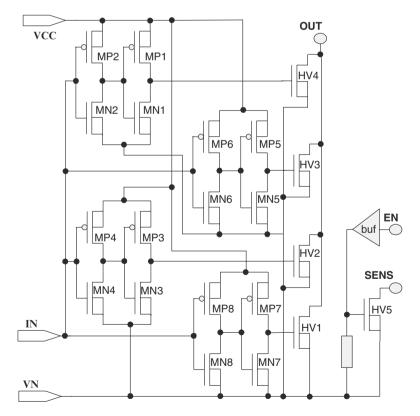

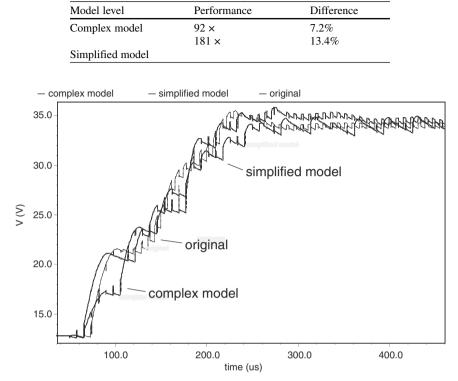

| 10  | Mixed-Level Modeling Using Configurable MOS<br>Transistor Models                                                                                           | 137 |

| Par | t III UML-Based System Specification and Design                                                                                                            |     |

| 11  | Modeling AADL Data Communications with UML MARTE<br>Charles André, Frédéric Mallet, and Robert de Simone                                                   | 155 |

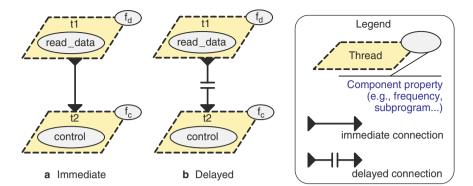

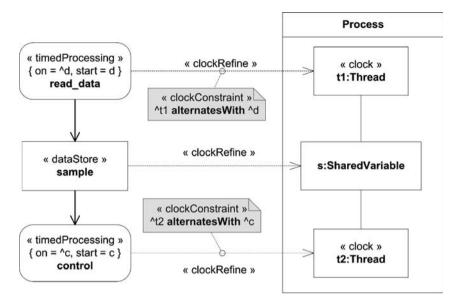

| 12  | <b>Software Real-Time Resource Modeling</b><br>Frédéric Thomas, Sébastien Gérard, Jérôme Delatour,<br>and François Terrier                                 | 169 |

| 13  | Model Transformations from a Data Parallel Formalism<br>Towards Synchronous Languages<br>Huafeng Yu, Abdoulaye Gamatié, Eric Rutten, and Jean-Luc Dekeyser | 183 |

| 14  | UML and SystemC – A Comparison and Mapping Rules<br>for Automatic Code Generation<br>Per Andersson and Martin Höst                                         | 199 |

| 15  | An Enhanced SystemC UML Profile for Modeling<br>at Transaction-LevelS. Bocchio, E. Riccobene, A. Rosti, and P. Scandurra                                   | 211 |

| 16  | SC <sup>2</sup> StateCharts to SystemC: Automatic Executable<br>Models Generation<br>Marcello Mura and Marco Paolieri                                      | 227 |

| Par | t IV Formalisms for Property-Driven Design                                                                                                                 |     |

| 17  | Asynchronous On-Line Monitoring of Logical<br>and Temporal Assertions<br>K. Morin-Allory, L. Fesquet, B. Roustan, and D. Borrione                          | 243 |

Contents

| 18 | Transactor-Based Formal Verification of Real-Time                                               |     |

|----|-------------------------------------------------------------------------------------------------|-----|

|    | Embedded Systems                                                                                | 255 |

|    | D. Karlsson, P. Eles, and Z. Peng                                                               |     |

| 19 | A Case-Study in Property-Based Synthesis: Generating                                            |     |

|    |                                                                                                 |     |

|    | a Cache Controller from a Property-Set                                                          | 271 |

|    | a Cache Controller from a Property-Set<br>Martin Schickel, Martin Oberkönig, Martin Schweikert, | 271 |

### Part I C/C++ Based System Design

#### Chapter 1 How Different Are Esterel and SystemC

Jens Brandt<sup>1</sup> and Klaus Schneider<sup>2</sup>

**Abstract** In this paper, we compare the underlying models of computation of the system description languages SystemC and Esterel. Although these languages have a rather different origin, we show that the execution/simulation of programs written in these languages consists of many corresponding computation steps. As a consequence, we identify different classes of Esterel programs that can be easily translated to SystemC processes and vice versa. Moreover, we identify concepts like preemption in Esterel that are difficult to implement in a structured way in SystemC.

Keywords Synchronous Languages, SystemC, Models of Computation

#### 1.1 Introduction

System description languages like SystemC [11, 13] and synchronous languages [1, 8] like Esterel [2, 4, 5, 12] are becoming more and more popular for the efficient development of modern hardware-software systems. The common goal of these languages is to establish a model-based design flow, where different design tasks like simulation, verification and code generation (for both hardware and software) can be performed on the basis of a single system description.

While the overall goal of SystemC and Esterel is therefore the same, there are many differences between these languages. In particular, these languages have different underlying models of computation.

As a synchronous language, the execution of an Esterel program is divided into macro steps that correspond with single reactions that are triggered by a common clock of a hardware circuit. Each macro step is divided into finitely many microsteps that are all executed in zero time and within the same variable environment.

<sup>&</sup>lt;sup>1</sup>Embedded Systems Group, University of Kaiserslautern, Email: brandt@informatik.uni-kl.de

<sup>&</sup>lt;sup>2</sup>Embedded Systems Group, University of Kaiserslautern, Email: klaus.schneider@informatik.uni-kl.de

E. Villar (ed.) Embedded Systems Specification and Design Languages,

<sup>©</sup> Springer Science + Business Media B.V. 2008

Hence, the execution of Esterel programs are driven in a cycle-based fashion. Due to the instantaneous reaction of microsteps, causality problems may occur if actions modify variables whose values are responsible for triggering the action. In order to analyze the causality of programs, a fixpoint iteration may be performed to compute the reaction of a macrostep. It is well-known that this fixpoint iteration is the ternary simulation [6] of the corresponding hardware circuits. However, it has to be remarked that Esterel compilers usually perform this fixpoint analysis at compile time, so that (1) more efficient code is generated and (2) it is known at compile time that the iteration finally terminates with known values.

SystemC follows the discrete-event semantics that are well-known from hardware description languages like VHDL [9] and Verilog [10]. A SystemC program consists of a set of processes that run in parallel. SystemC distinguishes thereby between three classes of processes, namely 'methods', asynchronous processes and synchronous processes. Methods are special cases of asynchronous processes that do not have **wait** statements. Asynchronous processes are triggered by events, i.e., by changes of the variables on which the process depends, and they are executed as long as variable changes are seen. For this reason, the execution of the asynchronous processes is also a fixpoint computation that terminates as soon as a fixpoint of the variables' values is found. After this, the synchronous processes are executed once to complete the simulation cycle.

As can already be seen from the above coarse description, the execution of synchronous languages like Esterel and SystemC have more in common as may have been expected if only their main paradigms were considered. Clearly, there are also many differences between these languages:

- The semantics of Esterel is given in form of a very concise structural operational semantics that can be directly used as specification of a simulator. In contrast, the semantics of SystemC is only given in terms of natural language (except for some attempts like [14, 15, 22]).

- In Esterel, most statements are reduced to a small core language for which hardware and software generation is available. No significant blow-up is obtained by this reduction (this is due to the so-called write-things-once-principle). In contrast, SystemC is an extension of C++ by constructs required to describe hardware systems like built-in concurrency, wait/interrupt mechanisms, and special data types like bitvectors. As a consequence, hardware synthesis is only available for a rather small subset of SystemC.

- Esterel offers comfortable preemption statements for aborting or suspending other statements. A first attempt towards preemption statements will be obtained by SystemC's **watching** statement, that does however not yet reach the power of Esterel's abortions.

- Esterel has special variables that model events. These variables take a default value unless they are assigned another value in the current macrostep.

- Esterel has a fully orthogonal set of statements. In particular, concurrency is an ordinary statement that can be combined with all other statements, while in SystemC programs consist of a set of processes that implement sequential code.

• SystemC offers different kinds of abstraction levels like 'untimed functional', 'timed functional', 'bus cycle-accurate', and 'cycle-accurate' modeling to support refinements from transaction levels down to register-transfer level descriptions.

Hence, there are also many differences between these languages. Some of theses difference may, however, only exist in the current versions of these languages and may disappear in later versions.

In this paper, we outline the differences and similarities of synchronous languages like Esterel and SystemC. In particular, we define classes of systems that can be easily described in both languages in a way that allows one to structurally translate these descriptions into each other. This is the result of the similarities that we have identified between the two languages. On the other hand, the differences we will outline in the following may be interesting for those who work on later versions of both languages. With this paper, we therefore hope to stimulate the discussion between the communities of SystemC and synchronous languages.

The rest of the paper is organized as follows: In the next section, we describe the languages SystemC and Esterel in more detail. In Section 1.3, we compare the execution of Esterel and SystemC programs in more detail and show that there are some correspondences. These correspondences give rise to define simple classes of programs that can be easily translated between both languages. In addition to this, we list differences between the two languages that lead to problems for the translation between the languages in Section 1.4. Finally, we conclude with a short summary in Section 1.5.

#### **1.2 Esterel and SystemC**

In this section, we give a rough overview of the main concepts and paradigms of Esterel and SystemC. Section 1.3 outlines then some similarities between the languages, while Section 1.4 outlines some major differences.

#### 1.2.1 Esterel

Esterel [2, 4, 5, 12] is a synchronous language [1, 8] that can be used both for hardware and software synthesis. As usual for synchronous languages, the computation of an Esterel program is divided into single reactions. Within each reaction, new inputs are read and new outputs are generated for these inputs with respect to the current state of the program. Moreover, the reaction determines the next state of the program that is used in the next reaction step.

The state of the program is determined by the current values of the variables and the current set of active control flow locations of the program. Control flow locations are statements like the **pause** statement where the control flow may rest for one unit of time.

Since Esterel statements include the parallel statement  $S_1 \parallel S_2$ , it may be the case that the control flow may rest at several control points at the same point of time.

Besides the usual statements like assignments, conditionals, sequences and loops, Esterel provides also many statements to implement complex concurrent behaviours. In particular, there are four kinds of abortion statements that run some Esterel code while observing an abortion condition in each macro step. If the condition holds, then the code is aborted and the abortion statement terminates. Other preemptive statement are suspension statements that suspend the execution of an Esterel statement if a given condition holds in a macro step.

It is very important that variables do not change during the macro step, i.e., all microsteps are viewed to be executed in zero time. Therefore, all microsteps are executed at the same point of time with the same variable environment. As a consequence, the values of the variables are uniquely defined in each macro step.

Due to the instantaneous reaction, synchronous programs may suffer from causality conflicts [3, 18, 19]. These causality conflicts occur if an assignment modifies the value of a variable that is responsible for the execution of the assignment. Compilers check the causality of a program at compile time with algorithms that are essentially the same as those used for checking the speed independence of asynchronous circuits via ternary simulation [6]. These algorithms essentially consist of a fixpoint computation that starts with unknown values for the output variables, and successively replaces these unknown values by known ones. While this analysis is usually done at compile time, we consider this fixpoint iteration in the following as being part of the execution that is performed within a macro step. This is done to outline similarities to the execution of SystemC programs.

Several generations of compilation techniques [7, 20, 24] have been developed for Esterel that can be used to generate hardware circuits at the gate level as well as software in sequential programming languages from the same Esterel program. Moreover, some of these compilation techniques have already been formally verified [16, 17].

#### 1.2.2 SystemC

SystemC is a language used for the simulation of complex hardware software systems. SystemC simulations may run up to 1,000 times faster than corresponding descriptions given in hardware description languages like VHDL and Verilog due to the higher level of abstraction that is used in SystemC. SystemC supports several levels of abstractions, which allows one to describe completely untimed systems down to cycle-accurate descriptions of hardware circuits at the gate level.

SystemC is not a self-contained language; instead, it is a class library for the wellknown C++ programming language [23]. SystemC extends C++ by typical data types used for hardware circuits like bitvectors and arithmetic on binary numbers with a specified bit-width. Moreover, SystemC offers concurrency in a similar way as hardware description languages, i.e., SystemC programs consist of a set of concurrent processes. To this end, SystemC features three different kinds of process types:

- Methods are triggered by signal events. Methods are entirely executed in a single simulation cycle and correspond to combinatorial circuits, i.e., their execution does not take time.

- Asynchronous processes are also triggered by signal events, but they may not be entirely executed within one simulation cycle. Instead, the control may stop at wait statements and may rest there until it is triggered by a new event.

- Synchronous processes are triggered by clocks. Like asynchronous processes, synchronous processes may not be entirely executed within one simulation cycle, and the control may stop at wait statements of the process. In contrast to asynchronous processes, the execution of synchronous processes is only triggered by the next clock event.

Although SystemC shares with VHDL the discrete-event based semantics, it does not have the possibility to assign signal assignments with delay. Hence, progress of time is only driven by clocks. Between these simulation steps, the output signal updates that are due to assignments of synchronous processes are not committed immediately. Instead, they are deferred to the beginning of the next simulation step. In contrast to this, local variables can always be modified, and the effect becomes visible without delay.

#### 1.3 Similarities Between SystemC and Esterel

From a general point of view, SystemC and synchronous languages are based on different models of computation: While SystemC has a discrete-event based semantics, synchronous languages rely on a global clock triggering the overall execution, i.e., a cycle-based semantics. However, a closer look to the features of each language reveals that there are similarities that allow us to define a common core of both languages. In particular, the integration of synchronous processes in SystemC provides some hooks to establish links between both worlds.

First of all, consider when variables change. In Esterel, there are immediate and delayed assignments that change the value of a variable immediately or only at the next macrostep. Similarly, the asynchronous processes of SystemC immediately update variable values, while the assignments of synchronous processes are committed only before the next simulation cycle.

However, synchronous languages follow the paradigm of perfect synchrony, i.e. all variable assignments are made simultaneously in a macrostep. This has the consequence that all variables can only have one value per clock cycle.

The perfect synchrony also has another consequence. Programs may not be executed in the order given by the programmer. Data dependencies of the program may require to execute the statements in a completely different order than specified by the programmer. Thus, the simulator does not simply execute the code of a synchronous program once, but it reiterates the execution and deduces from iteration to iteration the value of more signals until no further values can be deduced. As an example, consider a sequence in which the following operations are performed: assign a a value depending on b and c, then assign b a value depending on c and finally assign c some constant value. Without reordering (which is generally not applicable), the simulator needs three iterations to compute all outputs.

Figure 1.1 compares the execution of a SystemC and an Esterel program. There are apparent similarities in the execution of both types of programs: Both of them start with the determination of the time of the next step. In SystemC, this is determined by the next changing clock signal, whereas the logical time of Esterel just requires to wait for the next clock tick. Then, both simulators enter an iteration. In SystemC, the methods and asynchronous processes are executed as long as some signals change. In Esterel, there is a similar condition. The outputs are computed in a fixpoint operation that incrementally computes all signals of the current step. Subsequently, actions with immediate effects are executed, which are followed by the updates caused by delayed actions. Both in SystemC and Esterel, these updates stem from the previous clock cycle. If the iterative part of a step is finished, the SystemC simulator executes the synchronous processes that have been scheduled in the previous step. Similarly, the Esterel compiler executes the code at the currently active control flow locations with the determined signal values. Both programs now schedule processes and produce delayed actions for the next clock cycle.

This comparison shows that Esterel and the synchronous part of SystemC basically follow the same overall execution scheme. However, as already mentioned above, the execution of the individual processes is generally different. SystemC processes are sequential and thus, they are executed as specified by the programmer, while Esterel is inherently parallel, and its execution follows the data dependencies. Hence, a synchronous program cannot be directly translated to SystemC, since causility problems must be considered.

| function SystemCStep()                                    |

|-----------------------------------------------------------|

| <pre>// determine next changing clock signal</pre>        |

| do                                                        |

| <pre>// execute activated sc_methods and sc_threads</pre> |

| <pre>// update outputs of sc_methods and sc_threads</pre> |

| <pre>// update outputs of previous sc_threads</pre>       |

| while (signals change);                                   |

| <pre>// execute scheduled sc_threads</pre>                |

| function EsterelStep()                                    |

| 1.0                                                       |

| // proceed to next macrostep                              |

| do                                                        |

| // execution: determining current signals                 |

| // update immediate outputs;                              |

| // update delayed outputs of previous step                |

| while (fixpoint not reached);                             |

| // execution: prepare next macrostep                      |

Fig. 1.1 Comparing the execution of SystemC and Esterel programs

Nevertheless, for most programs that appear in real-world applications, the problems are not as difficult as outlined before. With restricting to a subclass of synchronous programs that covers most important applications, a direct structural mapping is possible. Basically, the following classes can be distinguished.

- *Programs that contain only delayed action*: No problems occur if programs that solely contain delayed actions are translated. For this class of programs, the iterative part is almost redundant: Only the outputs from the previous step must be committed once. The fixpoint iteration can be completely omitted, since no actions manipulate them in the course of the current step and thus, they are all known in advance. The actual execution of the program code is done after the loop, which is equivalent to SystemC synchronous processes.

- *Programs requiring only one fixpoint iteration*: In principle, the condition for the input set of programs does not have to be as strict as described above: The only thing that must be guaranteed is that a single iteration of is enough to determine the output values. In this case, the execution scheme is again analogous and a directly translated program shows the same behavior. Hence, programs may contain immediate actions which must be however set before their usage in the step. In particular, the individual threads of a program have to be executed in the right order that respects inter-thread data dependencies.

- All other programs: The set of programs for a translation does not need to be restricted at all. The causality analysis of synchronous programs can be simulated in SystemC with the help of asynchronous processes. Each program fragment (i.e. either equations or the result of the compilation method presented in the next section) is wrapped in an asynchronous process that contains all used variables in its sensitivity list. Like this, its execution is triggered each time a value changes. Note that Esterel program that are not causally correct, may result in SystemC programs that have a nonterminating simulation cycle: Asynchronous processes may infinitely often trigger each other and thus, simulate an oscillating wire in the circuit design they represent.

#### **1.4 Differences Between SystemC and Esterel**

The previous section showed that synchronous processes in SystemC and Esterel programs share a common core, which can comprehend many practical systems. While most elements of SystemC can be mapped more or less directly to Esterel, some problems arise for the other way around due to the rich set of control flow statements Esterel provides.

First, problems occur due to the Esterel's orthogonal use of parallelism. Since parallel and sequential code can be arbitrarily mixed in Esterel but not in SystemC, threads in synchronous programs must be reorganized. Second, there are many preemption constructs in Esterel, which are all based on some primitive abortion and suspension statements. As SystemC does not provide preemption, this part must be also removed before a translation to SystemC code.

Recently, we developed a new compilation scheme for our Esterel-variant Quartz, which compiles programs to an intermediate code, which represents a small synchronous programming languages without complicated control flow statements [20, 21]. The basic building block of this format is a job. Such a job  $J = (x, S_x)$  is a pair, where x is a label and  $S_x$  a code fragment. These jobs resemble synchronous processes in SystemC. The overall idea of compilation is as follows: In a first step, for each control flow location  $\ell$  of the program, a job ( $\ell$ ,  $S_\ell$ ) is computed that has to be executed if the control flow resumes the execution from location  $\ell$ .

**Definition 1.** [Job Code Statements] The following list contains the job code statements. *S*, *S*<sub>1</sub>, and *S*<sub>2</sub> are also job code statements,  $\ell$  is a location variable, *x* is an event variable, *y* is a state variable,  $\sigma$  is a Boolean expression, and  $\lambda$  is a lock variable:

- *nothing* (empty statement)

- $y = \tau$  and  $next(y) = \tau$  (assignments)

- *init*(*x*) (initialize local variable)

- *schedule*(*l*) (resumption at next reaction)

- $reset(\lambda)$  (reset a barrier variable)

- $fork(\lambda)$  (immediately fork job  $\lambda$ )

- *barrier*( $\lambda$ ,*c*) (try to pass barrier  $\lambda$ )

- $if(\sigma) S_1$  else  $S_2$  (conditional)

- $S_1; S_2$  (sequence)

The atomic statements *nothing*,  $y = \tau$ , and  $next(y) = \tau$  have the same meaning as in ordinary synchronous programs. The meaning of conditionals and sequences is also the same. The statement init(x) replaces a local variable declaration. The *schedule(l)* statement inserts the job corresponding to control flow location l to the schedule of the next step. The statements  $reset(\lambda)$ ,  $fork(\lambda)$ , and  $barrier(\lambda, c)$ are used to implement concurrency based on *barrier synchronization*. The statement *barrier(\lambda,c)* first increments the integer variable  $\lambda$  and then compares it with the constant *c*. If  $\lambda \ge c$  holds, it immediately terminates, so that a further statement *S* can be executed in a sequence *barrier(\lambda,c)*; *S*. If  $\lambda < c$  holds, the execution fails, so that the code behind the barrier is not yet executed. Executing *reset(\lambda)* simply resets  $\lambda = 0$ . The statement  $fork(\lambda)$  immediately executes the job  $\mathcal{G}_{\lambda}$ that is associated with  $\lambda$ .

As explained in detail in [20], the compilation of preemption statements first computes the normal execution that is performed when no abortion takes place. Then, as a post-processing, the potential preemption behavior is added to all jobs. To this end, each location ℓ inside the abort statement's body the corresponding job  $S_{\ell}$  is protected by the abortion and suspension guards so that the statements are not executed if a preemption condition hols.

Figure 1.2 contains a small example that illustrates how **Quartz** code can be translated to SystemC. The lower left part of the figure lists the job code of the module and the right hand-side shows how it can be used for the translation to

```

module Wait(event a, b, r, &o)

void Wait :: \ell_0(){

r.write(false);\ell_{a}.write(true);\ell_{b}.write(true);

loop{

\ell_a: await(a); \parallel \ell_b: await(b);

}

emit next(o);

void Wait :: \ell_{-}()

while(true){

\ell : await(r);

wait_until(\ell_a.delayed());

}

wait until(a.delayed());

\ell.write(false);

\ell_{0} : reset(\lambda_{1});

}}

schedule(\ell_{a});

void Wait :: \ell_{h}(){

schedule(\ell_{\mu});

while(true){

\ell_{a}: if(\nega) schedule(\ell_{a}) else fork(\lambda_{1});

wait_until(\ell_{b}.delayed());

\ell_b^{a}: if (\neg b) schedule (\ell_b^{a}) else fork (\lambda_{a});

wait_until(b.delayed());

\ell_{r}: if(r){

\ell_{b}.write(false);

}}

reset(\lambda_1);

schedule(\ell_{a});

schedule(\ell_{\rm h});

void Wait :: \ell_{()}

} else

wait_until(r.delayed());

schedule(\ell_{.});

\ell_a.write(true);\ell_b.write(true);

}

\lambda_1: barrier(\lambda_1, 2);

emit next(o);

void Wait ::\lambda_{1}(){

schedule(\ell_{i});

wait_until(!\ell_a.delayed()&&!\ell_b.delayed());

r.write(true):

wait();

r.write(false);

ℓ ();

}

```

Fig. 1.2 Module Wait in Quartz, Job Code (left) and SystemC (right)

SystemC. The fine-grained parallelism used by the threads of  $\ell_a$  and  $\ell_b$  is mapped to coarse-grained parallelism of SystemC.

Figure 1.3 shows another example, which extends the previous one. It illustrates how preemption statements are removed by the compilation into JobCode. The translation to SystemC is not affected by this part, as only additional conditional statement are inserted, which do not pose significant problems.

Obviously, the various kinds of preemption statements in Esterel are powerful and convenient components used to program complex concurrent behaviors. The translation as performed by the Job code compilation is a solution, but it would be better if SystemC could benefit from the same programming possibilities as imperative synchronous languages. While the watching statement provides rudimentary abortion functionality, a complete support of all abortion and suspension variants would be desirable.

Moreover, fine-grained parallelism would be a second important extension of SystemC, from which a translation of imperative synchronous programs would benefit.

```

\ell_0 : reset(\lambda_1)

module ABRO(event a,b,r,&o)

schedule(\ell_{-});

loop{

schedule(\ell_{h});

abort{

ℓ.: if(¬r){

\ell_a: await(a); \parallel \ell_b: await(b);

reset(\lambda_i);

schedule(\ell_{a});

emit next(o);

} when(r);

schedule(\ell_{h});

\ell_{r}: await(r);

} else

}

schedule(\ell);

\lambda_1: barrier(\lambda_1,2);

emit next(o);

schedule(\ell);

ℓ<sub>2</sub>: if(r){

reset(\ell_1);

schedule(\ell_{a});

schedule(\ell_{\bar{b}});

} else

if(\neg a) schedule(\ell_1) else fork(\ell_1);

\ell_{h}: if(r){

reset(\ell_1);

schedule(\ell_{a});

schedule(\ell_{b});

} else

if(\neg b) schedule(\ell_b) else fork(\ell_1);

```

Fig. 1.3 Module ABRO in Quartz and Job Code

#### 1.5 Summary

In this paper, we identified similarities of the execution of SystemC and Esterel programs. Despite their different paradigms, we identified a class of programs that can be easily translated from one language to the other. Furthermore, we investigated language features that cause problems in a transformation process: In particular, preemption and fine-grained parallelism as in Esterel programs were identified as major differences, which might be interesting extensions of SystemC.

#### References

- A. Benveniste, P. Caspi, S. Edwards, N. Halbwachs, P. Le Guernic, and R. de Simone. The synchronous languages twelve years later. *Proceedings of the IEEE*, 91(1):64–83, 2003.

- G. Berry. The foundations of Esterel. In G. Plotkin, C. Stirling, and M. Tofte, editors, *Proof, Language and Interaction: Essays in Honour of Robin Milner*. MIT Press, Cambridge, USA 1998.

- 3. G. Berry. The constructive semantics of pure Esterel. http://www-sop.inria.fr/esterel.org/, July 1999.

- 4. G. Berry and L. Cosserat. The synchronous programming language Esterel and its mathematical semantics. In S.D. Brookes, A.W. Roscoe, and G. Winskel, editors, *Seminar on Concurrency*, volume 197 of *LNCS*, pages 389–448, Springer Pittsburgh, PA 1984.

- 5. G. Berry and R. de Simone. The Esterel language. *Proceedings of the IEEE*, 79:1293–1304, 1991.

- 6. J.A. Brzozowski and C.-J.H. Seger. Asynchronous Circuits. Springer, New York 1995.

- S. Edwards. Compiling concurrent languages for sequential processors. ACM Transactions on Design Automation of Electronic Systems (TODAES), 8(2):141–187, 2003.

- 8. N. Halbwachs. Synchronous Programming of Reactive Systems. Kluwer Dordrecht, 1993.

- 9. IEEE Computer Society. *IEEE Standard VHDL Language Reference Manual*. New York, 2000. IEEE Std. 1076–2000.

- 10. IEEE Computer Society. *IEEE Standard Hardware Description Language Based on the Verilog Hardware Description Language*. New York, 2001. IEEE Std. 1394–2001.

- 11. IEEE Computer Society. *IEEE Standard SystemC Language Reference Manual*. New York, USA, December 2005. IEEE Std. 1666–2005.

- 12. IEEE Computer Society. *IEEE Standard Esterel Language Reference Manual*. New York, USA, to appear 2007. IEEE Std. 1778.

- 13. Open SystemC Initiative. SystemC Version 2.1 User's Guide, 2005.

- W. Müller, J. Ruf, D. Hoffmann, J. Gerlach, T. Kropf, and W. Rosenstiel. The simulation semantics of SystemC. In *Design, Automation and Test in Europe (DATE)*, pages 64–70, IEEE Computer Society Munich, Germany, 2001.

- W. Müller, J. Ruf, and W. Rosenstiel. An ASM based SystemC simulation semantics. In W. Müller, J. Ruf, and W. Rosenstiel, editors, *SystemC – Methodologies and Applications*, pages 97–126, Kluwer Dordrecht, 2003.

- K. Schneider. Proving the equivalence of microstep and macrostep semantics. In V. Carreño, C. Muñoz, and S. Tahar, editors, *Theorem Proving in Higher Order Logic (TPHOL)*, volume 2410 of *LNCS*, pages 314–331, Springer Hampton, VA, 2002.

- K. Schneider, J. Brandt, and T. Schuele. A verified compiler for synchronous programs with local declarations. *Electronic Notes in Theoretical Computer Science (ENTCS)*, 153(4):71–97, 2006.

- K. Schneider, J. Brandt, T. Schuele, and T. Tuerk. Improving constructiveness in code generators. In Synchronous Languages, Applications, and Programming (SLAP), Edinburgh, 2005.

- K. Schneider, J. Brandt, T. Schuele, and T. Tuerk. Maximal causality analysis. In *Application of Concurrency to System Design (ACSD)*, pages 106–115, IEEE Computer Society St. Malo, France, 2005.

- K. Schneider, J. Brandt, and E. Vecchié. Efficient code generation from synchronous programs. In F. Brewer and J.C. Hoe editors, *Formal Methods and Models for Codesign (MEMOCODE)*, pages 165–174, IEEE Computer Society Napa Valley, CA, 2006.

- K. Schneider, J. Brandt, and E. Vecchié. Modular compilation of synchronous programs. In IFIP Conference on Distributed and Parallel Embedded Systems (DIPES), Springer Braga, Portugal, 2006.

- 22. R.K. Shyamasundar, F. Doucet, R. Gupta, and I.H. Krüger. Compositional reactive semantics of SystemC and verification in RuleBase. In *Workshop on Next Generation Design and Verification Methodologies for Distributed Embedded Control Systems*, 2007.

- 23. B. Stroustrup. *The C++ Programming Language*. Series in Computer Science. Addison-Wesley, Reading, MA, 1986.

- 24. J. Zeng, C. Soviani, and S.A. Edwards. Generating fast code from concurrent program dependence graphs. In *Languages, Compilers, and Tools for Embedded Systems (LCTES)*, pages 175–181, ACM Washington, DC, 2004.

#### Chapter 2 Timed Asynchronous Circuits Modeling and Validation Using SystemC

Cédric Koch-Hofer and Marc Renaudin

**Abstract** ASC is a SystemC library designed for modeling asynchronous circuits. In order to respect the semantic of asynchronous circuits, the synchronization primitives of ASC rely on SystemC immediate notification. In this paper we present a time model which allows us to properly trace ASC processes activity. This time model is not restricted to ASC and could be used to model asynchronous circuits using a CSP based modeling language. Moreover, this time model can be used for validating timed models of circuits mixing synchronous and asynchronous parts. This time model is therefore used for designing the tracing facilities of ASC. This paper also presents a patch of the OSCI SystemC simulator allowing to properly validate ASC models. As relevant examples, two versions of the Octagon interconnect are modeled and verified using the ASC library.

Keywords Asynchronous Circuits, SystemC, Time Model, Simulation and Validation

#### 2.1 Introduction

With advances in digital VLSI technologies, asynchronous design styles are becoming more and more popular. The intrinsic properties of asynchronous circuits are well adapted to new interconnects paradigms like "Network on Chip" [1] (NoC). An Asynchronous circuit [2] use a local handshaking protocol to synchronize data transfers between its components. Therefore, there are no longer any problems with NoC clock management, and the integration of cores with different clock frequencies is properly managed [3]. Moreover, asynchronous NoCs take advantage of the benefits of asynchronous circuits such as low power consumption, communication robustness...

TIMA laboratory, 46 Av. Félix Viallet, 38031 Grenoble, France Email: {cedric.koch-hofer, marc.renaudin}@imag.fr

E. Villar (ed.) *Embedded Systems Specification and Design Languages*, © Springer Science+Business Media B.V. 2008

Today, the lack of tools for the design of asynchronous circuits are the principal inhibitors for their adoption [4]. Two families of tools are available. The first family of tools uses graphical description as input. Examples of such tools are: Petrify [5], minimalist [6], 3D [7]. These kinds of tools allow the production of very efficient small circuits; nevertheless they can not be used for designing complex systems like NoC. The second family of tools uses programming languages as input. Examples of such languages are: CHP [8], Balsa [9] and Tangram [10]. These modeling languages do not support standard CAD tools and are not adequate to model synchronous circuits. However, these facilities are required for the design of an Asynchronous Locally Synchronous" [11] (GALS) "System on Chip" (SoC). Moreover, the design frameworks associated with these modeling languages do not allow us to properly codesign the hardware and software part of a SoC.

In order to leverage these problems, we have developed ASC [12], an extension of the SystemC [13] language for modeling asynchronous circuits. The semantic of ASC is based on CSP [14]. Indeed, an ASC model is composed of a set of concurrent processes communicating via synchronous point-to-point channel. This SystemC library also includes a set of operators and statements for accurately modeling the basic components of an Asynchronous Network on Chip.

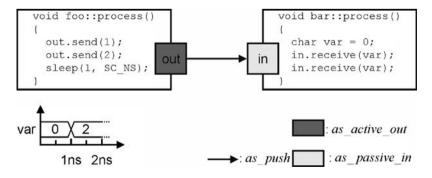

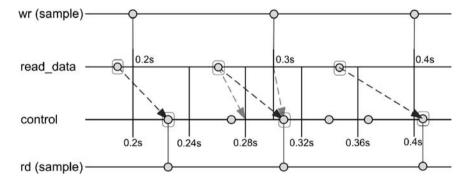

The standard tracing facilities defined by SystemC are based on changes of variable values between different simulation times or between two different deltacycles [13]. By this way, it is not possible to trace several communications occurring over an ASC channel if they happen in the same delta-cycle. For example, Fig. 2.1 illustrates what happens if standard tracing facilities of SystemC are used for tracing the variable *var*. In this example the *foo::process* sends two chars to the *bar::process*. Nevertheless, only the last change of value can be recorded by the standard tracing facilities of SystemC. Indeed, the ASC channels use immediate notification to synchronize their connected processes and therefore multiple communications can be executed during a delta-cycle over the same channel. Thus, standard SystemC tracing facilities only display the last change of value and can not be used for validating ASC models.

Fig. 2.1 Trace with SystemC tracing facilities

An obvious solution resolving this problem could be adding latencies in ASC channels. However, this solution adds extra dependencies on the order of execution of the processes, not allowing proper ASC processes delay insensitivity checking In fact, tracing activities of such a distributed system requires using a time model not based on a single common clock.

The "Lamport clocks" [15] is a time model commonly used for synchronizing activities of distributed systems. In this time model each process has its own local clock. The messages exchanged by the processes are used for synchronizing their local clocks. In this paper we present a time model, called AST (Asynchronous SystemC Time), based on "Lamport clocks" allowing proper tracing of ASC processes activity. More generally, this time model can be used for tracing activities of any models of asynchronous circuits specified with a modeling language based on CSP.

Previous works [16–18] on timing models for asynchronous circuits use models at the gate level. They are used to perform static analysis of latencies of the circuit components. For example, they use min-max algorithm, Monte-Carlo simulation... for checking that the delay limits are respected. Thus, these models manipulate very low level abstraction entities like signals. These models of time are therefore not suited to handle high level language constructs like processes, channels...

A SystemC framework based on "Lamport clocks" time model is presented in [19]. However, they do not use it for tracing activities of channels but for improving simulation speed. Indeed, the "Lamport clocks" time model is used in this framework to efficiently manage the execution of the SystemC processes on a distributed simulation platform. The execution of these processes is synchronized according to the time stamp of the packets received by the processes.

The ASC library enables us to model any class of asynchronous circuits (QDI [20], micro-pipeline [21]...). Thus, we want to be able to validate any kind of asynchronous circuits modeled using ASC. For properly checking the delay insensitivity of an ASC model of a Delay Insensitive (DI) asynchronous circuit, all the valid scheduling of the processes should be tested. Hopefully, the specification of the SystemC scheduler [13] is non-deterministic. However, the system has to be simulated with a particular implementation of the scheduler. For example, the SystemC reference simulator [22] is deterministic. In order to leverage this problem, we have developed a patch for this simulator allowing a non-deterministic scheduling of the processes.

This paper also presents how the AST time model was used to define the tracing facilities of ASC. To demonstrate the relevance of this approach, this paper finally presents how ASC is used to model and validate two versions of an asynchronous Octagon interconnect [23].

The organization of the paper is as follows. Section 2.2 presents the AST time model. The ASC library is introduced in Section 2.3. As illustrative examples, Section 2.4 describes the two ASC versions of Octagon interconnect. Finally, conclusions and future works on the ASC library are presented in Section 2.5.

#### 2.2 **Time Model**

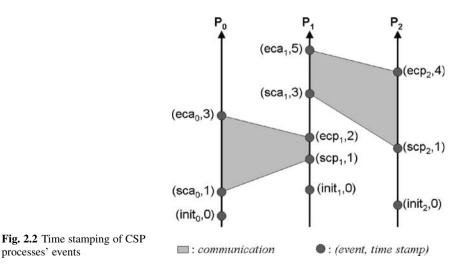

A model of asynchronous circuits based on CSP is a set of processes which communicate with one another by exchanging messages via synchronous point-to-point channels. In this kind of distributed system, all processes are running concurrently and it is therefore difficult (even impossible) to say that one of two events occurred first. As in [15], our goal is to adapt and extend the relation "happened before" in order to define a partial ordering of the events happening in such a system. At the end, we want to be able to assign a coherent time stamp to each event occurring in this kind of system. For example, Fig. 2.2 shows different events occurring when executing a CSP model of an asynchronous circuit composed of three processes (P<sub>0</sub>, P<sub>1</sub> and P<sub>2</sub>). Figure 2.2 also illustrates the time stamps associated to these events. The different kind of events and their relationship are described formally in Sub-section 2.2.1. The rules for computing the time stamp of these events are presented in Subsection 2.2.2.

A nice property of this time model is that it can be easily extended. For example in Sub-section 2.2.3 we present an extension of this time model allowing interfacing these asynchronous clocks with the clock of a synchronous circuit.

#### 2.2.1 **Partial Ordering**

processes' events

In the AST time model, the execution of a CSP model of an asynchronous circuit is represented by a set of processes  $P = \{p_0, p_1...\}$  and a set of channels  $CH = \{ch_0, p_1...\}$  $ch_1...$ }. A process  $p_i$  is defined by the sequence of events  $p_i = (e_0, e_1...)$  occurring in this process during its execution. The first event of a process  $p_i$  is its "initialization"

*init<sub>i</sub>*. When a process  $p_i$  terminates, its last event is its "termination" *end<sub>i</sub>*. A channel  $ch_k$  is specified by a couple  $ch_k = (p_i, p_j)$  where  $p_i$  and  $p_j$  are the processes using  $ch_k$ .  $p_i$  and  $p_j$  are connected to  $ch_k$  by an active port and by a passive port, respectively. It can be noticed that in this time model the direction of the data communicated through the channel is not relevant. A communication  $c = \{sca_i, scp_j, ecp_j, eca_i\}$  between two processes  $p_i$  and  $p_j$  over a channel  $ch_k = (p_i, p_j)$  is defined by the following four events:

- $sca_i$  and  $eca_i$ : beginning and termination of the communication *c* for the process  $p_i$

- $scp_j$  and  $ecp_j$ : beginning and termination of the communication *c* for the process  $p_j$

A process  $p_j$  connected to a channel  $ch_k = (p_i, p_j)$  can probe it. The probing action is atomic and generates one, and only one, of the two following events:

- *pp<sub>j</sub>*: this event, called a "positive probe", happens if the process *p<sub>i</sub>* has initiated a communication on the channel *ch<sub>i</sub>*.

- np<sub>j</sub>: this event, called a "negative probe", occurs if the process p<sub>i</sub> does not initiated a communication on the channel ch<sub>i</sub>.

In our formalism a task  $t_{i,l}$  is a sequence of instructions of a process  $p_i$ . In standard CSP, it is not possible to perform a set of tasks in parallel in the same process. In order to leverage this restriction most of the modeling language for asynchronous circuits based on CSP defines a parallel composition operator. This operator enables concurrently execution of a set of tasks  $T_i = \{t_{i,0}, t_{i,1}...\}$  in the same process  $p_i$ . Each task  $t_{i,l}$  is concurrently executed by a sub-process  $p_m$ . The main process  $p_i$  is blocked until the termination of all these sub-processes. Execution of this composition operator is characterized by the following two events:

- cti<sub>i</sub>: this event, called "concurrent tasks initialization", occurs when a set of concurrent tasks are triggered by process p<sub>i</sub>.

- *ctt<sub>i</sub>*: this event, called "concurrent tasks termination", happens when all the subprocesses triggered by process *p<sub>i</sub>* for executing a set of concurrent tasks have terminated.

The sequence of events  $(e_i, e_i'...)$  defining a process  $p_i$  respects the order of occurrences of its events. We are assuming that two events in the same process can not happen at the same time, and therefore the sequence of events  $(e_i, e_i'...)$  respects a total ordering. However, our goal is to define an ordering relation on the set  $E = \{e, e'...\}$  of all the events. For this purpose, we define the "happened before" relation  $< : E \rightarrow E$ . This relation is defined by the following conditions:

- (C0) If  $e_i$  and  $e'_i$  are events in the same process, and  $e_i$  occurs before  $e'_i$ , then  $e'_i < e'_i$

- (C1)  $\forall e, e', e'' \in E, (e < e' \land e' < e'') \Rightarrow e < e''$

- (C2) If  $\{sca_i, scp_j, ecp_j, eca_i\}$  is a communication between processes  $p_i$  and  $p_j$ , then  $sca_i < ecp_i$ ,  $scp_i < ecp_i$  and  $ecp_i < eca_i$

- (C3) If  $c = \{sca_i, scp_j, ecp_j, eca_i\}$  is a communication between processes  $p_i$ and  $p_j$ , and  $pp_j$  is a "positive probe" by the process  $p_j$  of the communication c, then  $sca_i < pp_i$  and  $pp_i < scp_i$

- (C4) If  $np_j$  is a "negative probe" done by the process  $p_j$  on the channel  $ch_k = (p_i, p_j)$ , and  $\{sca_i, scp_j, ecp_j, eca_i\}$  is a communication between processes  $p_i$  and  $p_i$  via the channel  $ch_k$ , then  $ecp_j < np_j$  or  $np_j < sca_i$

- (C5) If *init<sub>m</sub>* is the initialization event of a sub-process  $p_m$  created for performing a concurrent task  $t_{i,p}$  and  $cti_i$  is the "concurrent task initialization" generated by the composition operator which triggered the process  $p_m$ , then  $cti_i < init_m$

- (C6) If  $end_m$  is the termination event of a sub-process  $p_m$  created for performing a concurrent task  $t_{i,l}$ , and  $ctt_i$  is the "concurrent task termination" generated by the composition operator which triggered the process  $p_m$ , then  $end_m < ctt_i$

Obviously, in this kind of system an event can not occur before itself  $\forall e \in E, \neg(e < e)$ . Moreover, the asymmetric property of the relation < can be easily demonstrated. Thus, the relation < defines a strict partial ordering of *E*.

#### 2.2.2 Computing Time of Events

The AST time model associates a time stamp to each event. The value of this time stamp is defined by a function clk :  $E \to \mathbb{N}$  respecting the strict partial ordering <. This last function represents the logical time of the system and it is defined according to the logical local time of each process. The logical time of a process  $p_p$  is defined by a function clk<sub>p</sub> :  $E_p \to \mathbb{N}$  where  $E_p \subseteq E$  is the set of all the events occurring in  $p_p$ . The time stamp clk( $e_p$ ) = clk<sub>p</sub>( $e_p$ ) of an event  $e_p \in E_p$  occurring in a process  $p_p$  is computed with the help of the following computation rules:

- (R0) If  $e_p = \emptyset$  is an event which has never happened, then  $clk(\emptyset) = 0$

- (R1) If  $e_p = init_i$  is the initialization of the process  $p_i$  and this process is not a sub-process, then  $clk_i(init_i) = 0$

- (R2) If  $e_p = init_m$  is the initialization of the process  $p_m$ , and this process is a sub-process triggered by the event  $cti_i$  of the process  $p_i$ , then  $clk_m(init_m) = clk_i(cti_i) + 1$

- (R3) If  $e_p = end_i$  is the last event of the process  $p_i$ , and  $le_i$  is the last event occurring in  $p_i$  before  $end_i$ , then  $clk_i(end_i) = clk_i(le_i) + 1$

- (R4) If  $e_p = sca_i$  is the beginning of a communication performed by a process  $p_i$  over a channel  $ch_k = (p_i, p_j)$ , and  $np_j$  is the last negative probe of the process  $p_j$  of the channel  $ch_k$ , and  $le_i$  is the last event occurring in  $p_i$ before  $sca_i$ , then  $clk_i(sca_i) = max(clk_i(le_i), clk_i(np_i)) + 1$

- (R5) If  $e_p = scp_j$  is the beginning of a communication performed by a process  $p_j$  over a channel  $(p_i, p_j)$ , and  $le_j$  is the last event occurring in  $p_j$ before  $scp_j$ , then  $clk_i(scp_j) = clk_i(le_j) + 1$

- (R6) If  $e_p = ecp_j$  is the end of a communication  $\{sca_i, scp_j, ecp_j, eca_i\}$  performed by a process  $p_j$  over a channel  $(p_i, p_j)$ , then  $clk_j(ecp_j) = max(clk_i(sca_i), clk_i(scp_j)) + 1$

- (R7) If  $e_p = eca_i$  is the end of a communication { $sca_i, scp_j, ecp_j, eca_i$ } performed by a process  $p_i$  over a channel  $(p_i, p_i)$ , then  $clk_i(eca_i) = clk_i(ecp_i) + 1$

- (R8) If  $e_p = pp_j$  is a positive probe of the communication {*sca*, *scp*, *ecp*, *eca*<sub>i</sub>} performed by a process  $p_j$ , and  $le_j$  is the last event occurring in  $p_j$ before  $pp_j$ , then clk<sub>i</sub>( $pp_j$ ) = max(clk<sub>i</sub>( $le_i$ ), clk<sub>i</sub>(*sca*<sub>i</sub>)) + 1

- (R9) If  $e_p = np_j$  is a negative probe performed by a process  $p_j$  of a channel  $ch_k = (p_i, p_j)$ , and  $\{sca_i, scp_j, ecp_j, eca_i\}$  is the last communication on the channel  $ch_k$ , and  $le_j$  is the last event occurring in  $p_j$  before  $np_j$ , then  $clk_i(np_i) = max(clk_i(le_i), clk_i(ecp_i)) + 1$

- (R10) If  $e_p = cti_i$  is the initialization of a composition operator, and  $le_i$  is the last event occurring in  $p_i$  before  $cti_i$ , then  $clk_i(cti_i) = clk_i(le_i) + 1$

- (R11) If  $e_p = ctt_i$  is the termination of a composition operator, and  $p_m, p_{m+1} \dots$ are the sub-processes created by this composition operator, and  $end_m$ ,  $end_{m+1} \dots$  are the last events occurring in these sub-processes, then  $clk_i(ctt_i) = max(clk_m(end_m), clk_{m+1}(end_{m+1})...) + 1$

As explained in [15], the function clk :  $E \rightarrow \mathbb{N}$  respects the strict partial ordering < if the following condition is respected:

Clock Condition.  $\forall e, e' \in E, (e < e' \Rightarrow \text{clk}(e) < \text{clk}(e'))$

The lack of space does not allow us to give details of the proof of the *clock condition*. Briefly, this proof consists of proving that all the conditions defining the relation < are respected by the previous computation rules defining the function clk :  $E \rightarrow \mathbb{N}$ .

#### 2.2.3 Interfacing with Synchronous World

One of the goals on ASC is to model circuits composed of asynchronous and synchronous components. For being able to trace activities of such system, our time model must be able to take into account its synchronous time. In order to leverage this problem, we extend the set of processes P of the AST time model with a new process  $p_{\Delta} \in P$ . This process represents the system's global clock of the synchronous parts. Indeed, at the end of each global clock cycle, an event  $ge_{\Delta}$  occurs in the process  $p_{\Delta}$ .

To preserve the coherency of the < relation we extend it with the following condition:

- (C7) If  $e_i$  is an event occurring in  $p_i$  and  $ge_{\Delta}$  is an event occurring in  $p_{\Delta}$  before  $e_i$ , then  $ge_{\Delta} < e_i$

- (C8) If  $ge_{\Delta}$  is an event occurring in  $p_{\Delta}$  and  $e_i$  is an event occurring in  $p_i$  before  $ge_{\Delta}$ , then  $e_i < ge_{\Delta}$

The computation rules of the time stamp also have to be updated. Firstly, we add the following computation rule:

(R12) If  $e_p = ge_{\Delta}$  is the end of a clock cycle happening in the process  $p_{\Delta}$ , and  $le_{\Delta}$ ,  $le_0$ ,  $le_1$  ... are the last event happening in processes  $p_{\Delta}$ ,  $p_0$ ,  $p_1$  ... of  $P = \{p_{\Delta}, p_0, p_1, ...\}$  before  $ge_{\Delta}$ , then  $clk_{\Delta}(ge_{\Delta}) = max(clk_{\Delta}(le_{\Delta}), clk_0(le_0), clk_1(le_1)...) + 1$

Secondly, we update the rules (R2) to (R11) for taking into account the local time of the process  $p_{\Delta}$ . For example, for the rule (R2), if we take the same hypothesis and if  $le_{\Delta}$  is the last event occurring in  $p_{\Delta}$  before  $init_m$ , then  $clk_m(init_m) = max(clk_i(cti_i), clk_{\Delta}(le_{\Delta})) + 1$ . The other rules (R3) to (R11) are updated in the same way.

#### 2.3 ASC Library

An ASC model is composed of a set of ASC **modules** interconnected via predefined ASC **ports** and ASC **channels**. New methods and operators are also defined by ASC enabling **parallel communication** and **non-deterministic choice**.

The ASC tracing facilities are composed of several functions. These functions are used to trace communications and events happening in the ASC channels. The generated output trace file can not be directly used by the standard CAD tools, but it can be converted in standard VCD trace file [24] with the *ast2vcd* tool we have developed.

For being able to properly validate an ASC model, we have developed a patch of the OSCI SystemC simulator. The resulting simulator allows us testing different interleaving of the processes execution.

#### 2.3.1 ASC Modeling Language

ASC defines two different kinds of module. The *container modules* are used to define the hierarchical structure of the system. They can contain other modules, channels and ports. The ASC *process modules* specify the behavior and the concurrent aspects of an asynchronous circuit. The behavior of a process module is defined by its *process* method.

The ports are the communication interfaces of ASC processes. An ASC port is unidirectional (*input* or *output*) and can be connected to at most one ASC channel. The emission of data through an output port is done with its *send* method. The *receive* method of the input port connected to an output port allows to get the data sent by an output port. A handshaking protocol is used to synchronize the communication between two ASC ports. They are two different kinds of port: active and passive. An *active port* initiates the handshaking protocol and a *passive port* acknowledges it. A passive port has a special method called *probe* allowing it to check if its connected active port has initiated a communication or not.

The channels are the mediums used by the ASC processes to communicate and synchronize their executions. A *pull* and a *push* channel interconnects an active input port to a passive output port and an active output port to a passive input port, respectively. These channels implement the communication and synchronization primitives offered by the ASC ports. Indeed, the previous methods of these ports (*send*, *receive* and *probe*) just forward their procedure call to the methods of their connected channels.

To synchronize its execution, an ASC process can use its *idle* methods. A first version of this method is used to wait until at least one of its passive ports is ready to communicate. A second version is used to wait that a set of parallel communications have been completed. A parallel communication is triggered with the *par\_receive* or *par\_send* methods of the ASC ports, and a set of parallel communications is constructed with the overloaded operator *//*.

The two new statements *as\_choice\_nd* and *as\_guard* are provided by the ASC library. The *as\_choice\_nd* defines a non-deterministic choice over a set of guarded commands. A guard of a non-deterministic choice is specified with the statement *as\_guard*.

#### 2.3.2 Tracing Facilities

A trace file respecting the AST time model is created with the function *as\_create\_ast\_trace\_file*. This function takes as a parameter the name of the output trace file and returns a pointer on this trace file. This pointer can be used by the *as\_trace* function to define the ASC channels to trace. This pointer can also be used with the *as\_set\_time\_unit* function to set the time resolution used for performing the simulation. Finally, a trace file shall be closed by calling the function *as\_close\_ast\_trace\_file*.

An ASC channel has a template parameter defining the DATA carried out by this channel. Any kind of channel can be traced with the *as\_trace* function. Currently, the value of a data transferred over a traced channel will be reported only if its type belongs to one of the following C++ types: *bool, char, short, int, long, long long, unsigned char, unsigned short, unsigned int, unsigned long, unsigned long long, float, double.* However, ASC tracing facilities can be easily extended to handle specific user data types. Indeed, the *as\_trace* function can be overloaded in order to handle any kind of data.

The *ast2vcd* takes as input an ASC trace file and produces a VCD output trace file. For each traced ASC channel *ch* is defined the following VCD signals:

- *Data*: represents the data transferred during a communication.

- *sca*, *scp*, *eca*, *ecp*: represent the events defining a communication.

- *p*: the call to the probe method of the channel. The value of the channel is equal to the result of the probe.

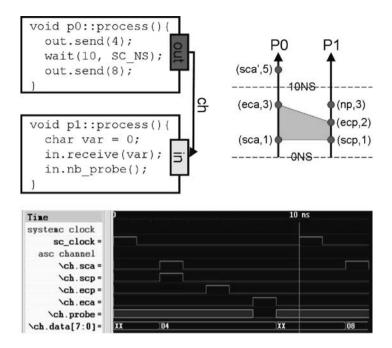

Fig. 2.3 Traces with ASC tracing facilities

Figure 2.3 shows the VCD and the AST traces generated by the simulation of the two ASC processes p0 and p1. These two processes are connected via an ASC channel *ch*. All the events represented in this figure, except *sca*', happen at the simulation time 0 nanosecond (NS). However, in the resulting VCD, these events do not happen at 0 NS. Indeed, to represent the AST time stamp and make the trace readable, the events occurring at the same SystemC simulation time, but at different AST times, are separated by  $\varepsilon$  time steps. In order to know at which SystemC simulation time an AST event occurs, the SystemC simulation clock is represented by the *sc\_clock* signal. The  $\varepsilon$  value is automatically computed by ast2vcd. It takes care that each AST event occurs after its SystemC simulation time and before the next *sc\_clock* signal.

#### 2.3.3 ASC Simulator

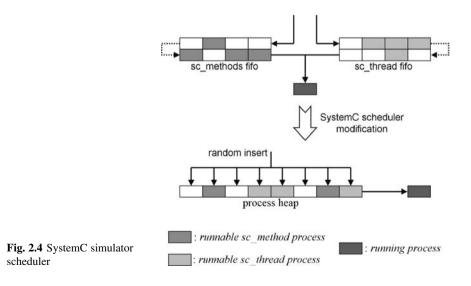

Because DI asynchronous circuits are not sensitive to delays, the execution order of the processes modeling such circuits should not have any impact on the correctness. For checking this fundamental property of a DI asynchronous circuit, the selection of a process to execute among the set of runnable processes should be non-deterministic. The current implementation of the SystemC kernel simulator [22] uses two pseudo-fifo lists for managing the set of runnable processes. The first one contains the runnable *sc\_method* and the second one the runnable *sc\_thread*. These pseudo-fifo are divided into two lists: *get\_list* and *push\_list*. The *get\_list* is used by the scheduler for selecting the new process to execute. The *push\_list* is used for inserting a new runnable process into the pseudo-fifo. During an evaluation phase, all the processes which are in the *get\_list* of the *sc\_method* pseudo-fifo are firstly executed. Secondly, all the processes which are in the *get\_list* are not empty, they are swapped with their corresponding *get\_list*. These three steps are repeated until the two *get\_list* are empty at the beginning of the first step. Thus, we can see that this scheduling algorithm is deterministic and do not allow us to test different interleaving of processes execution.

As illustrated in Fig. 2.4, the patch that we have defined merges the two pseudofifos into one priority queue. We have also defined a new common class for the  $sc_{thread}$  and the  $sc_{method}$  defining their priority of execution. When a process is becoming runnable, a new priority is affected to this process and then it is inserted into the priority queue. The priority value is computed by a pseudo random generator. In order to be able to replay a simulation, the seed of this pseudo random generator can easily be determined. When the active process execution finished, the scheduler chooses the process in the priority queue with the lowest priority. By this way, we are able to test different interleaving of processes execution.

Another promising solution for this problem is presented in [25]. It presents a method and tools enabling to efficiently generating the different scheduling allowed by the scheduler specification. They use dynamic partial-order reduction techniques to avoid the generation of two schedulings that have the same effect on the system's behavior.

#### 2.4 Octagon NoC with ASC

The Octagon [23] interconnect was developed by STMicroelectronics to efficiently interconnect eight CPUs on a single chip. This interconnect is composed of 8 nodes and 20 bidirectional links. However, in our version of the Octagon, each bidirectional link is replaced by two unidirectional links. The resulting configuration of the system is illustrated in Fig. 2.5. In this figure, the integer associated to each node is the address used by a CPU for sending a packet to another CPU. Each node uses an algorithm based on the Octagon topology and on arithmetic properties to route its incoming packets to the right output.

The first ASC version of the Octagon operates in packet switching mode. Figure 2.6 exhibits the ASC code of the nodes used in this version of the Octagon. These nodes wait for a new packet on one of the four input ports. When at least one packet is available, the nodes perform a non-deterministic choice over the set of input ports ready to transmit a new packet. A packet is then received on the selected input port. Finally, this packet is forwarded to an output port according to the routing Octagon algorithm.

The second ASC version of the Octagon operates in circuit switching mode. In this version there are two different kinds of packet: *request packet* and *response packet*. The request packets are sent by a CPU which is willing to access a resource of another CPU. When a request packet is received by a CPU, it sends a response packet to the CPU which sent this request packet.

Fig. 2.5 Octagon NoC confguration

Fig. 2.6 Packet switching router

```

void node::process() {

idle(in ip | in clk | in cclk | in frt);

as choice nd(

as guard(in ip.nb probe(), IP),

as guard(in clk.nb probe(), CLK),

as guard(in cclk.nb probe(), CCLK),

as guard(in frt.nb probe(), FRT)))

case IP: in ip.receive(pkt);

case CLK: in clk.receive(pkt);

case CCLK: in cclk.receive(pkt);

case FRT: in frt.receive(pkt);

switch( (pkt.adr - this->adr) mod 8 ) {

case 0: out ip.send(pkt); break;

case 1:

case 2: out clk.send(pkt); break;

case 6:

case 7: out cclk.send(pkt); break;

default: out frt.send(pkt); break;

```

```

void node::process() {

receive_req(l_pkt_req, l_in_dir);

l_out_dir = route(l_pkt_req.adr_dest);

forward_req(l_pkt_req, l_out_dir);

receive_rsp(l_pkt_rsp, l_out_dir);

forward_rsp(l_pkt_rsp, l_in_dir);

```

Fig. 2.7 Circuit switching router

The ASC code of the routers used in this version of the Octagon is summed up in Fig. 2.7. When one of these nodes receives a new request packet, it stores which input port ( $l_in_dir$ ) transmitted the packet. As for the previous version, the packet is then transmitted through the right output port. However, this time the node does not restart to wait for a packet on all its input ports, but it waits on the input port associated to the output port ( $l_out_dir$ ) which was used to send the packet. In this way the next packet received by this node can only be the response packet of the previous request packet. When this last response packet is received, it is forwarded through the output port corresponding to the input port which received the request packet. Thus, in this mode, the entire path between the CPU which sends the request and the CPU which receives it is reserved for the response packet.

In a first step, the ASC tracing facilities enabled us to validate the functional behavior of the two versions of the Octagon. For example, they helped us to check the behavior of the routers and to understand how dead-locks were happening in such a NoC. To this end, we have replaced the CPUs with traffic generator processes and traffic consumer processes. In a second step, we added latencies to the different components (consumers, producers and routers) and to the ASC channels. By this way, we were able to analyze the congestions and latencies of the NoC under different pattern of traffic (uniform, hot-spot and random).

#### 2.5 Conclusion

This paper presented a time model which can be used to validate asynchronous circuit models using a language based on CSP. This time model was used to define the tracing facilities of the ASC library. These tracing facilities produce traces of the ASC process activities over their connected channels, which can then be used to generate standard VCD. However, the VCD format is not really adapted to asynchronous circuits. Thus, we are currently investigating other trace formats like SCV. We are also evaluated the time model on complex multiple clock systems.

Finally, modeling and validating asynchronous logic with the ASC library is the first step towards the synthesis. Our final goal is to be able to synthesize these models with the TAST framework [26]. We are currently formally defining the synthesis process of ASC based models to efficiently generate gate level asynchronous circuits.

**Acknowledgments** The authors thank Y. Remond for initiating the research on this time model, and K. Morin-Allory for reviewing initial versions of the document, and R. Solari for reviewing final versions of the document. This work is partially supported by the French government in the MEDEA + framework, through the 2A703 NEVA project (Networks on Chips Design Driven by Video and Distributed Applications).

#### References

- 1. Jantsch A, Tenhunen H (2003) Networks on chip. Kluwer, Boston, MA

- 2. Sparsø J, Furber S (2001) Principles of asynchronous circuit design. Kluwer, Boston, MA

- Nielsen SF, Sparsø J (2001) Analysis of low-power SoC interconnection networks. In: 19th Norchip, pp 77–86

- Edwards DA, Toms WB (2004) Design, Automation and Test for Asynchronous Circuits and Systems. Technical Report IST-1999-29119, 3rd edn. Working Group on Asynchronous Circuit Design (ACiD-WG). http://www.scism.sbu.ac.uk/ccsv/ACID-WG

- Cortadella J, Kishinevsky M, Kondratyev A, Lavagno L, Yakovlev A (1997) Petrify: a tool for manipulating concurrent specifications and synthesis of asynchronous controllers. In: IEICE Trans Inf. and Syst, pp 315–325

- 6. Fuhrer RM, Nowick SM, Theobald M, Jha NK, Lin B, Plana L (1999) Minimalist: An Environment for the Synthesis, Verification and Testability of Burst-Mode Asynchronous Machines. Technical Report CUCS-020-9. Columbia University, Computer Science Department

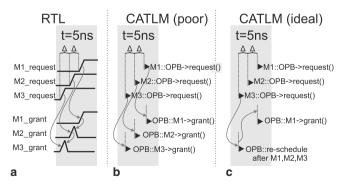

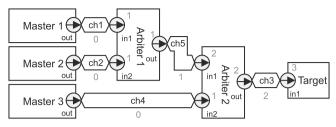

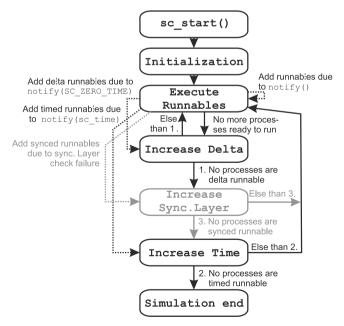

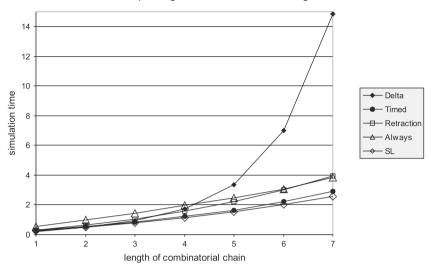

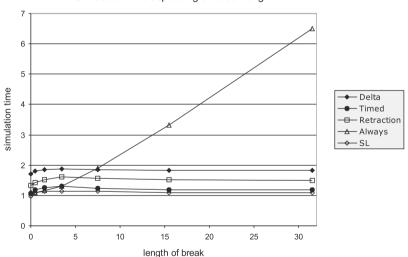

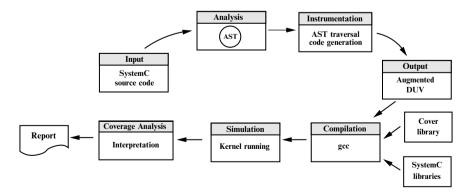

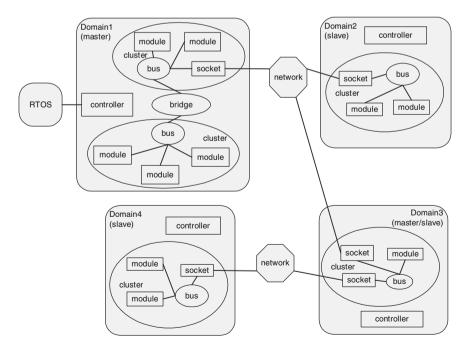

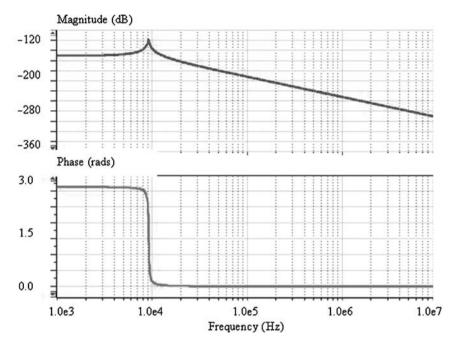

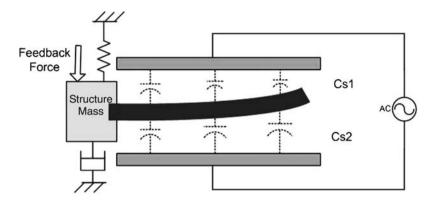

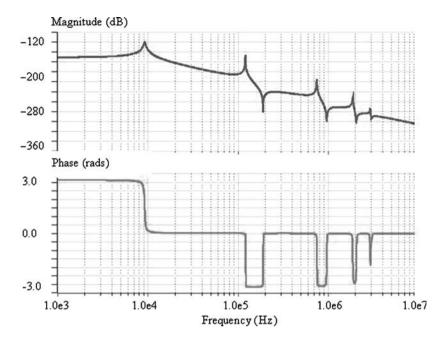

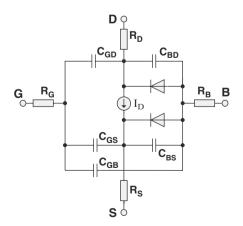

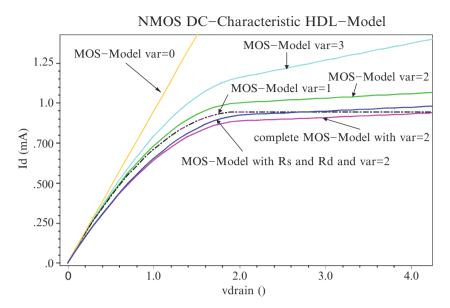

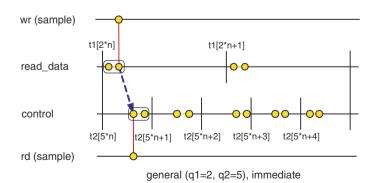

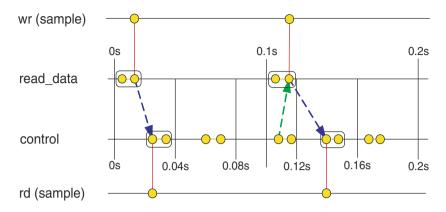

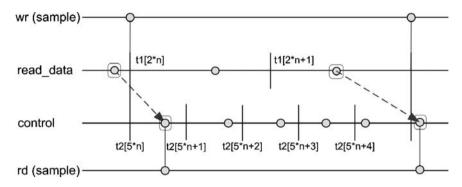

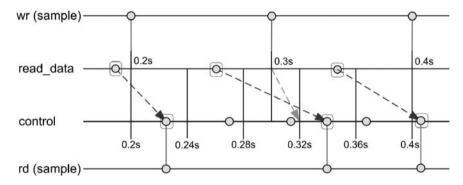

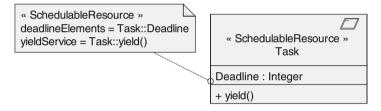

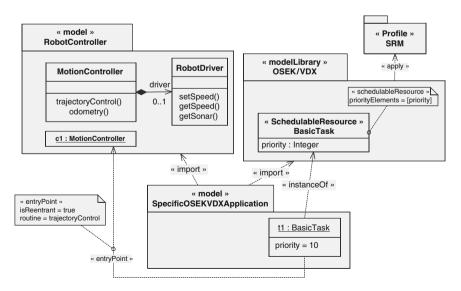

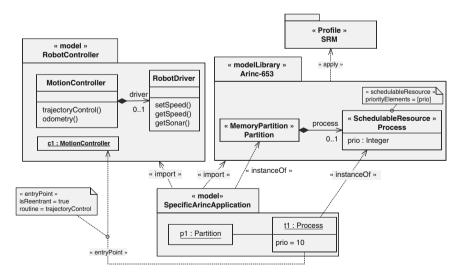

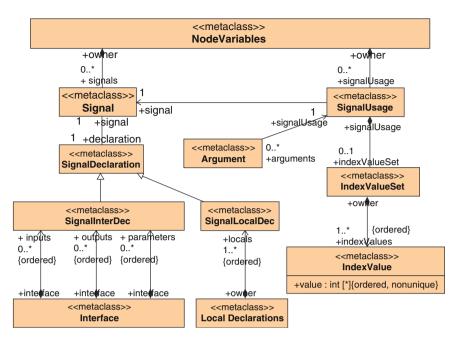

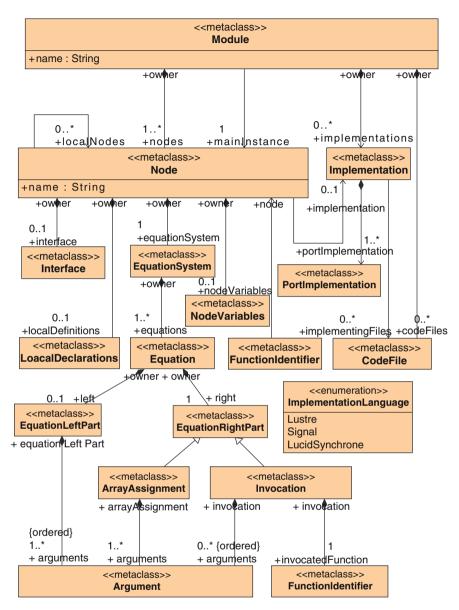

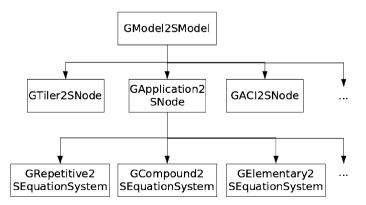

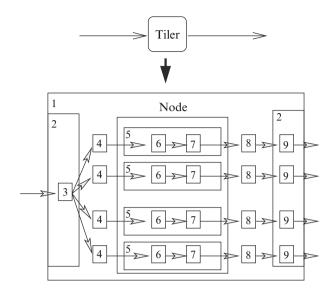

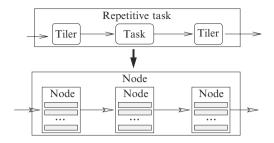

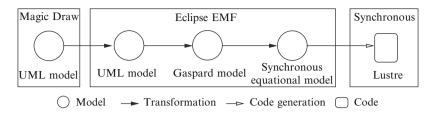

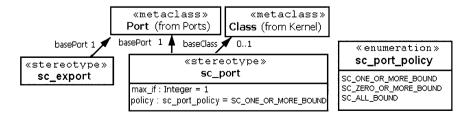

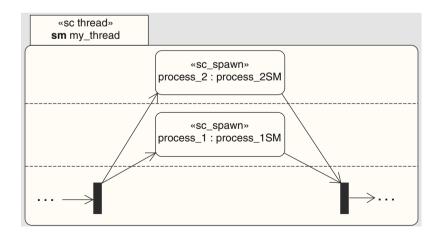

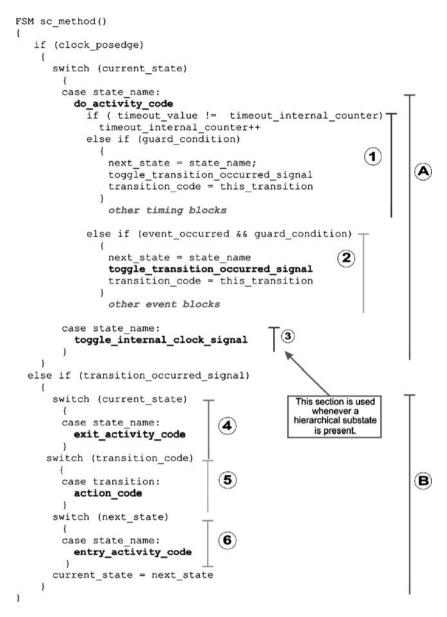

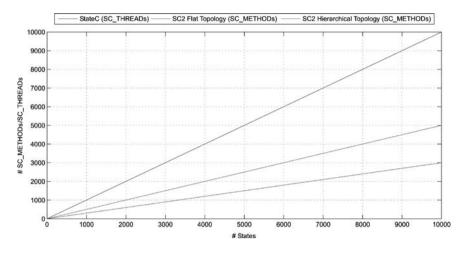

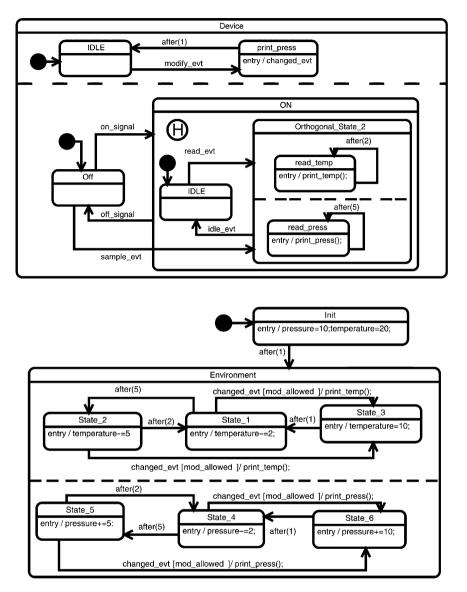

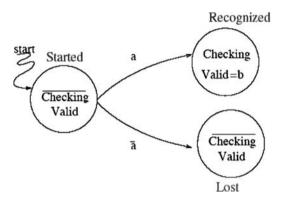

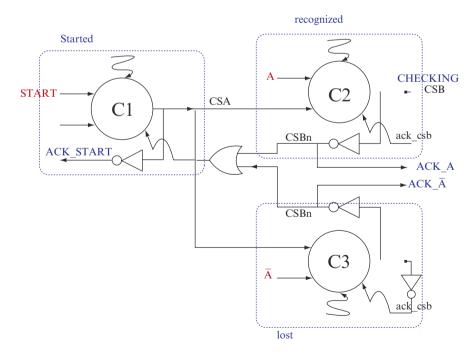

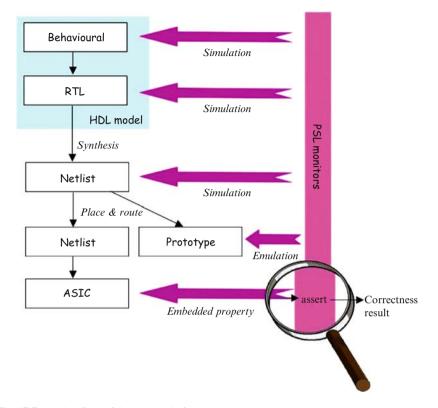

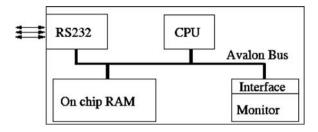

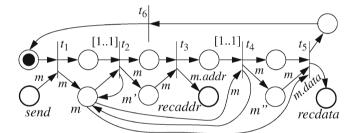

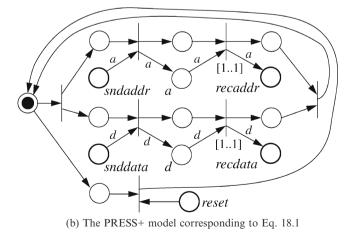

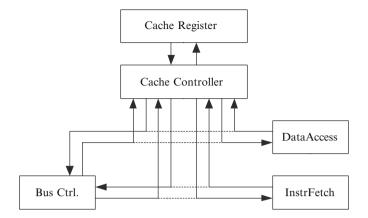

- 7. Yun KY, Dill DL (1992) Automatic synthesis of 3D asynchronous state machines. In: ICCAD92, pp 576–580. Santa Clara, CA