Oliver Schliebusch Heinrich Meyr Rainer Leupers

# Optimized ASIP Synthesis from Architecture Description Language Models

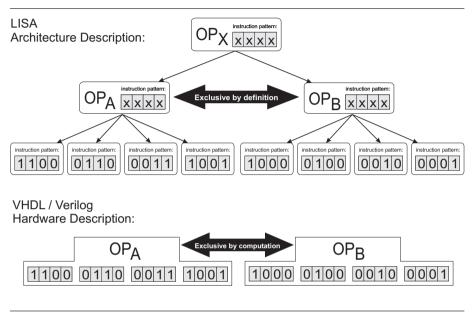

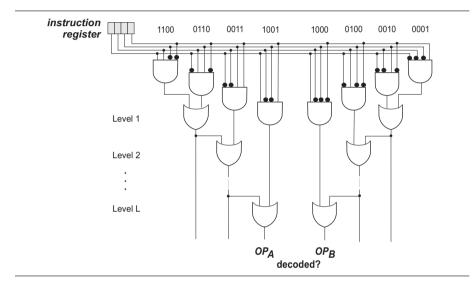

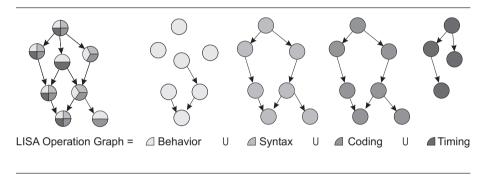

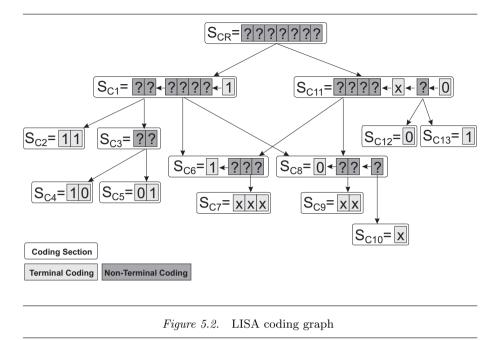

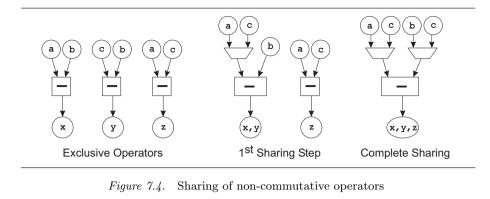

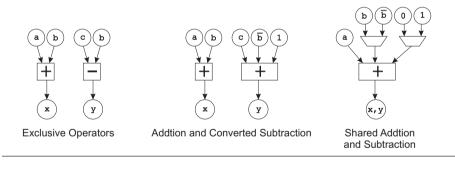

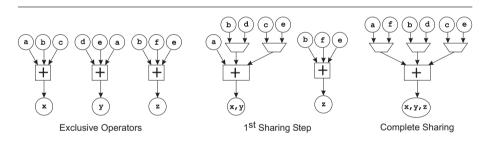

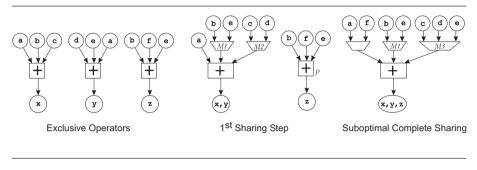

# OPTIMIZED ASIP SYNTHESIS FROM ARCHITECTURE DESCRIPTION LANGUAGE MODELS

# Optimized ASIP Synthesis from Architecture Description Language Models

by

OLIVER SCHLIEBUSCH

CoWare Inc, Aachen, Germany

HEINRICH MEYR RWTH Aachen University, Germany

and

RAINER LEUPERS RWTH Aachen University, Germany

A C.I.P. Catalogue record for this book is available from the Library of Congress.

ISBN-10 1-4020-5685-0 (HB) ISBN-13 978-1-4020-5685-7 (HB) ISBN-10 1-4020-5686-9 (e-book) ISBN-13 978-1-4020-5686-4 (e-book)

Published by Springer, P.O. Box 17, 3300 AA Dordrecht, The Netherlands.

www.springer.com

Printed on acid-free paper

All Rights Reserved © 2007 Springer No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Dedicated to my wife Frauke and my daughter Svenja.

# Contents

| De       | edicat                                                          | tion                                                                      | V    |

|----------|-----------------------------------------------------------------|---------------------------------------------------------------------------|------|

| Foreword |                                                                 |                                                                           | xi   |

| Preface  |                                                                 |                                                                           | xiii |

| 1.       | INT                                                             | 1                                                                         |      |

|          | 1.1                                                             | From ASIC to ASIP                                                         | 1    |

|          | 1.2                                                             | Heterogeneous Architectures:<br>Computational Performance vs. Flexibility | 4    |

|          | 1.3                                                             | Challenges of ASIP Design                                                 | 7    |

|          | 1.4                                                             | Organization of This Book                                                 | 9    |

| 2.       | ASIP DESIGN METHODOLOGIES                                       |                                                                           |      |

|          | 2.1                                                             | ADL based ASIP Design                                                     | 12   |

|          | 2.2                                                             | (Re)Configurable Architectures                                            | 17   |

|          | 2.3                                                             | Hardware Description Languages<br>and Logic Representation                | 19   |

|          | 2.4                                                             | Motivation of This Work                                                   | 20   |

| 3.       | ASIP DESIGN BASED ON LISA                                       |                                                                           | 23   |

|          | 3.1                                                             | Design Space Exploration                                                  | 23   |

|          | 3.2                                                             | Software Tools Generation                                                 | 25   |

|          | 3.3                                                             | System Simulation and Integration                                         | 28   |

| 4.       | A NEW ENTRY POINT<br>FOR ASIP IMPLEMENTATION                    |                                                                           |      |

|          | 4.1 Acceptance Criteria for an<br>Automatic ASIP Implementation |                                                                           |      |

|          | 4.2                                                             | From Architecture to Hardware Description                                 | 32   |

| 5. | LIS                                                          | A FRONTEND                                                         | 41  |  |

|----|--------------------------------------------------------------|--------------------------------------------------------------------|-----|--|

|    | 5.1                                                          | Resource Section                                                   | 42  |  |

|    | 5.2                                                          | LISA Operations                                                    | 44  |  |

|    | 5.3                                                          | LISA Operation Graph                                               | 45  |  |

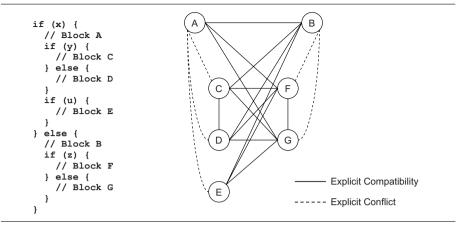

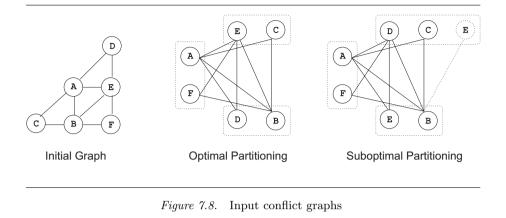

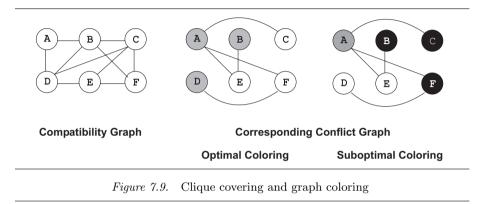

|    | 5.4                                                          | Representing Exclusiveness in<br>Conflict and Compatibility Graphs | 55  |  |

|    | 5.5                                                          | Exclusiveness Information<br>on the Level of LISA Operations       | 59  |  |

|    | 5.6                                                          | 5.6 Exclusiveness Information on the Behavioral Level              |     |  |

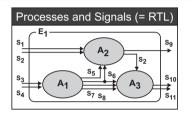

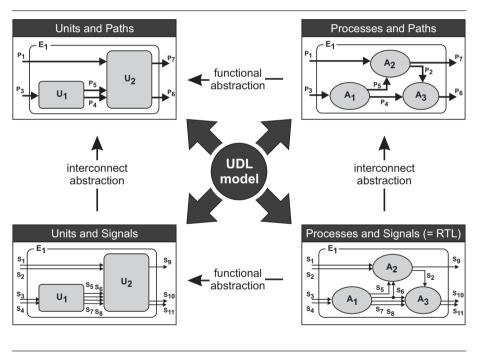

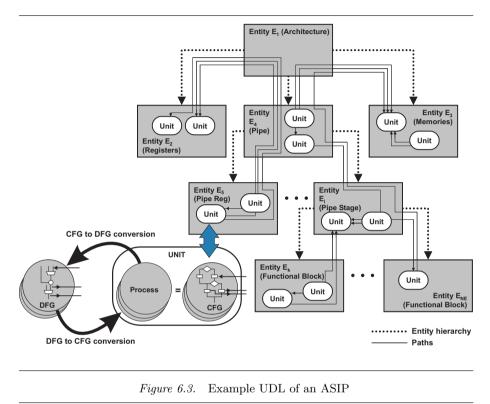

| 6. | INTERMEDIATE REPRESENTATION                                  |                                                                    |     |  |

|    | 6.1                                                          | Unified Description Layer                                          | 67  |  |

|    | 6.2                                                          | Optimization Framework                                             | 73  |  |

|    | 6.3                                                          | VHDL, Verilog and SystemC Backend                                  | 74  |  |

| 7. | OPTIMIZATIONS BASED ON EXPLICIT<br>ARCHITECTURAL INFORMATION |                                                                    |     |  |

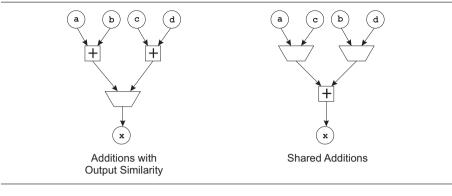

|    | 7.1                                                          | Basic DFG based Optimizations                                      | 78  |  |

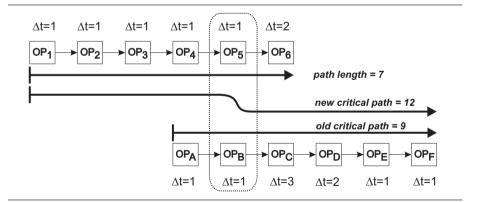

|    | 7.2                                                          | Resource Sharing                                                   | 84  |  |

|    | 7.3                                                          | Dependency Minimization                                            | 96  |  |

|    | 7.4                                                          | Decision Minimization                                              | 98  |  |

| 8. | CONFIGURABLE<br>PROCESSOR FEATURES                           |                                                                    |     |  |

|    | 8.1                                                          | Processor Features                                                 | 101 |  |

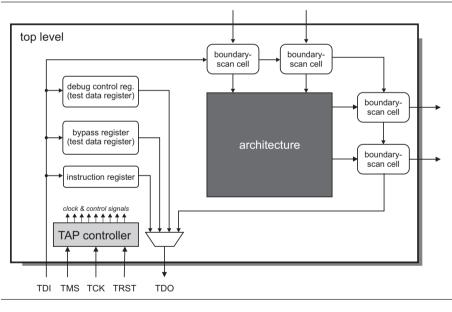

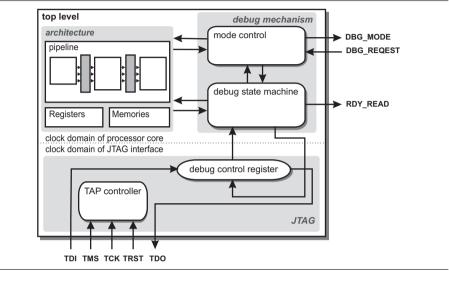

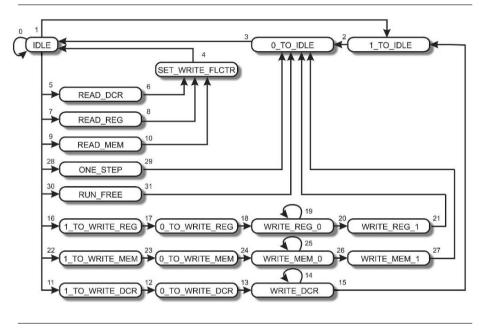

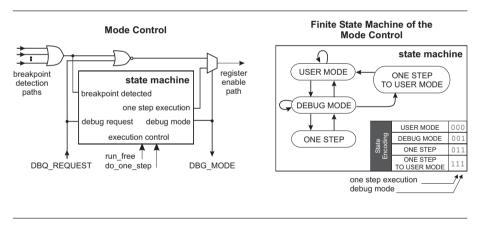

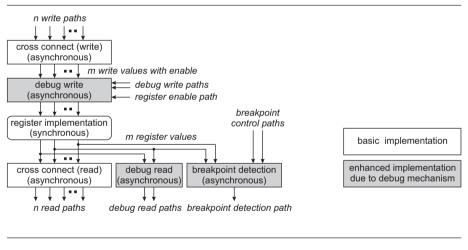

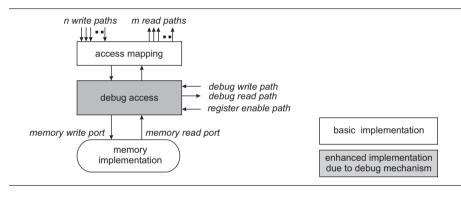

|    | 8.2                                                          | JTAG Interface and Debug Mechanism Generation                      | 103 |  |

|    | 8.3                                                          | Adaptability of Synthesis Framework                                | 114 |  |

| 9. | CASE STUDY:<br>AN ASIP FOR TURBO DECODING 117                |                                                                    |     |  |

|    | 9.1                                                          | Turbo Decoding based on Programmable Solutions                     | 117 |  |

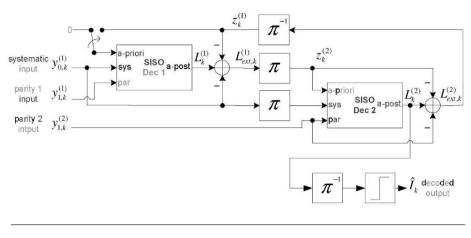

|    | 9.2                                                          | The Turbo Decoding Principle                                       | 120 |  |

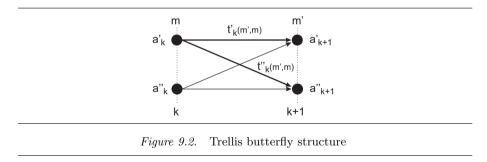

|    | 9.3                                                          | The Max-LOGMAP Algorithm                                           | 120 |  |

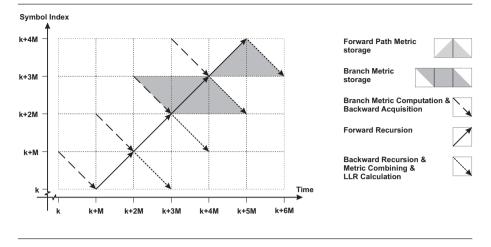

|    | 9.4                                                          | Memory Organization and Address Generation                         | 123 |  |

|    | 9.5                                                          | Instruction-Set and Data-Path Implementation                       | 128 |  |

|    | 9.6                                                          | Instruction Schedule                                               | 128 |  |

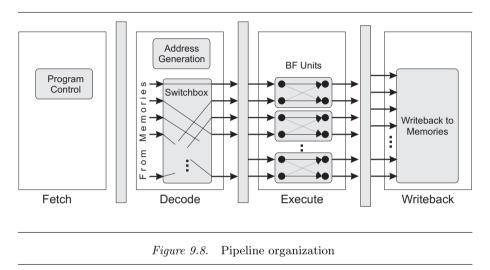

|    | 9.7                                                          | Pipeline Structure                                                 | 131 |  |

|    | 9.8                                                          | Results                                                            | 132 |  |

|    | 9.9                                                          | Concluding Remarks                                                 | 133 |  |

| Contents                                  | ix  |  |

|-------------------------------------------|-----|--|

| 10. CASE STUDIES: LEGACY CODE REUSE       | 135 |  |

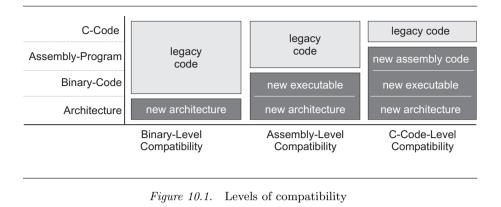

| 10.1 Levels of Compatibility              | 135 |  |

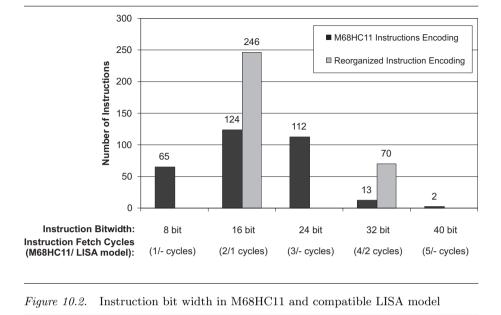

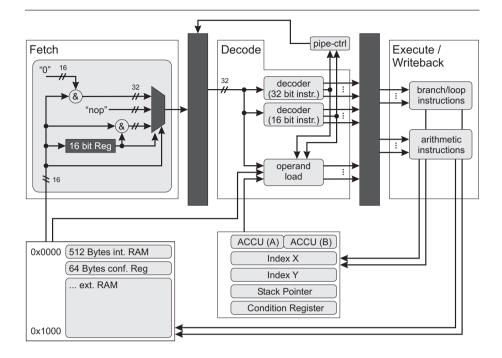

| 10.2 The Motorola 68HC11 Architecture     | 137 |  |

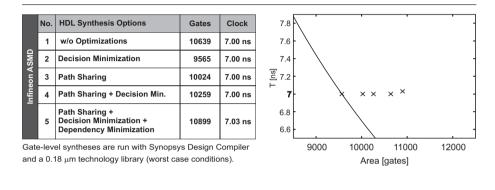

| 10.3 The Infineon Technologies ASMD       | 144 |  |

| 11. SUMMARY                               | 149 |  |

| Appendices                                | 153 |  |

| A Case Studies                            | 153 |  |

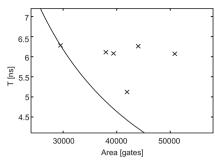

| A.1 ICORE                                 | 154 |  |

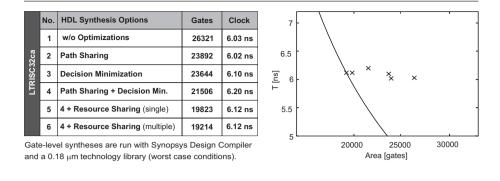

| A.2 LT Architecture Family                | 156 |  |

| B CFG and DFG Conversions                 | 161 |  |

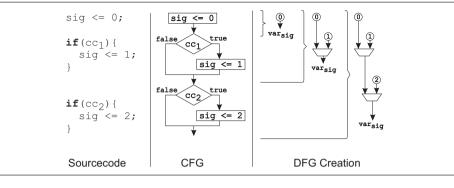

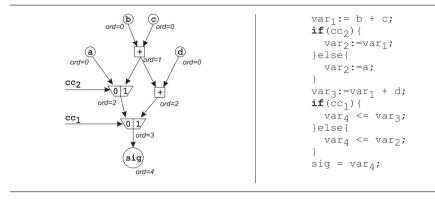

| B.1 CFG to DFG Conversion                 | 161 |  |

| B.2 DFG to CFG Conversion                 | 164 |  |

| C Debug Mechanism                         | 167 |  |

| C.1 Advanced Features of Debug Mechanisms | 167 |  |

| List of Figures                           | 171 |  |

| List of Tables                            | 175 |  |

| References                                | 177 |  |

| About the Authors                         |     |  |

| Index                                     | 191 |  |

## Foreword

We are presently observing a paradigm change in designing complex SoC as it occurs roughly every twelve years due to the exponentially increasing number of transistors on a chip. The present design discontinuity, as all previous ones, is characterized by a move to a higher level of abstraction. This is required to cope with the rapidly increasing design costs. While the present paradigm change shares the move to a higher level of abstraction with all previous ones, there exists also a key difference.

For the first time advances in semiconductor manufacturing do not lead to a corresponding increase in performance. At 65 nm and below it is predicted that only a small portion of performance increase will be attributed to shrinking geometries while the lion share is due to innovative processor architectures. To substantiate this assertion it is instructive to look at major drivers of the semiconductor industry: wireless communications and multimedia. Both areas are characterized by an exponentially increasing demand of computational power to process the sophisticated algorithms necessary to optimally utilize the limited resource bandwidth. The computational power cannot be provided in an energy-efficient manner by traditional processor architectures, but only by a massively parallel, heterogeneous architecture.

The promise of parallelism has fascinated researchers for a long time; however, in the end the uniprocessor has prevailed. What is different this time? In the past few years computing industry changed course when it announced that its high performance processors would henceforth rely on multiple cores. However, switching from sequential to modestly parallel computing will make programming much more difficult without rewarding this effort with dramatic improvements.

A valid question is: Why should massive parallel computing work when modestly parallel computing is not the solution? The answer is: It will work only if one restricts the application of the multiprocessor to a class of applications. In wireless communications the signal processing task can be naturally partitioned and is (almost) periodic. The first property allows to employ the powerful technique of task level parallel processing on different computational elements. The second property allows to temporally assign the task by an (almost) periodic scheduler, thus avoiding the fundamental problems associated with multithreading. The key building elements of the massively parallel SoC will be clusters of application specific processors (ASIP) which make use of instructionlevel parallelism, data-level parallelism and instruction fusion.

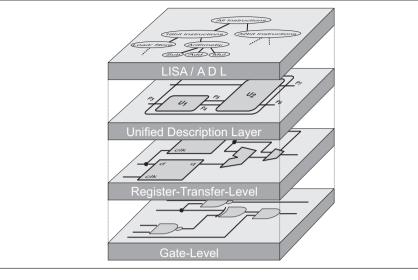

This book describes the automatic ASIP implementation from the architecture description language LISA employing the tool suite "Processor Designer" of CoWare. The single most important feature of the approach presented in this book is the efficient ASIP implementation while preserving the full architectural design space at the same time. This is achieved by introducing an intermediate representation between the architectural description in LISA and the Register Transfer Level commonly accepted as entry point for hardware implementation. The LISA description allows to explicitly describing architectural properties which can be exploited to perform powerful architectural optimizations. The implementation efficiency has been demonstrated by numerous industrial designs.

We hope that this book will be useful to the engineer and engineering manager in industry who wants to learn about the implementation efficiency of ASIPs by performing architectural optimizations. We also hope that this book will be useful to academia actively engaged in this fascinating research area.

Heinrich Meyr, September 2006

## Preface

The work presented in this book reflects my PhD thesis accomplished at the Institute for Integrated Signal Processing Systems (ISS) at RWTH Aachen University. The core topic of RTL hardware model generation is only one out of many complex aspects in the field of design automation for Application Specific Instruction-Set Processor (ASIP) development. While several approaches focus on single aspects only, a few methodologies target the whole design flow and have gained acceptance in industry. One of these bases on the architecture description language LISA, which was initially defined to enable the generation of fast instruction-set simulators. Although not foreseen in the beginning, LISA was nevertheless the starting point for a research project that consequently aimed at the needs posed by commercial ASIP design. The development began with simulator generation, then moved on to software tools generation and system integration and has now arrived at C-Compiler generation and RTL model generation. As the RTL model generation was one of the latest aspects targeted, it was a huge challenge to bridge the discrepancy between already commercialized parts of the LISA tool suite and the latest research results. Therefore, the distance between initial research and the final product was extremely short, providing challenge and motivation simultaneously.

I would like to thank Prof. Heinrich Meyr for his support and the numerous inspiring discussions. It was really motivating working in an open and interdisciplinary atmosphere. Also, I would like to express my thanks to Prof. Tobias Noll for his great interest in my work and for his commitment as secondary advisor.

The concepts of a synthesis environment as described in this book can hardly be implemented by a single person. At show-time, shortly before product release, 11+ full time PhD and undergraduate students were working on the project with enthusiasm. Each one of them made it become a huge success. In particular, I must thank Anupam Chattopadhyay, David Kammler and Martin Witte for their outstanding contribution.

Further, I would like to thank my wife Frauke for her support and understanding during the whole project and especially while writing this book. Last but not least, I would like to give special thanks to my parents Udo and Monika for making my academic profession possible.

This book provides a snapshot not only from a technical point of view, but also a snapshot in time. There are many challenging questions in the emerging field of ESL design. Academic readers might be interested in visiting the web pages of the ISS at RWTH Aachen University (www.iss.rwth-aachen.de), while readers from industry might consider visiting CoWare's web pages (www.coware.com) for latest product information.

OLIVER SCHLIEBUSCH, SEPTEMBER 2006

#### Chapter 1

# INTRODUCTION

The increasing utilization and steadily enhancing functionality of digital devices is noticeable in everyday life. This development is enabled by Systems-on-Chips (SoCs) that comprise various computational building blocks, memories and on-chip communication. However, a crisis in SoC design is posed by the conflicting demands for performance, energy efficiency and flexibility. Thus, hardware designers and the Electronic Design Automation (EDA) industry face extreme pressure to find advanced architectures and appropriate design approaches. The importance of shifting away from architectures with fixed functionality, namely Application-Specific Integrated Circuits (ASICs), to more flexible solutions is discussed in this chapter.

#### 1.1 From ASIC to ASIP

There are four major reasons for today's ASIC design challenges [1]. First, so-called deep-submicron effects are not considered on the abstraction level used for architectural specification. With regard to the interconnect, for example, both an increased influence of the signal propagation delay and a compromised signal integrity due to crosstalk are not considered adequately by traditional design methodologies. An architecture implementation below Register Transfer Level (RTL) is required to take these effects into account and to achieve an accurate estimation of the physical behavior of the architecture. This implies the necessity for several costly design iterations. Second, larger chips can be implemented due to the advances in semiconductor manufacturing. The ITRS [2] expects a growth from 697 million transistors per chip today up to 7,022 million transistors per chip in 2015. As early as 2003, it was predicted that up to 250 million gates per chip will become feasible in 2005, although it was expected that only 50 million will be used [3]. Third, not only the amount of gates, but also the complexity of the designs is increasing. Analog as well as digital parts are integrated on a single chip and, moreover, different functionalities are combined. Last but not least, the shrinking time-to-market as well as the shortened time-inmarket augment the challenges in ASIP design.

Due to the above-mentioned reasons, SoC building blocks need to be designed for reuse and adaption. Contrary to this requirement, ASICs provide only a fixed function and not the required flexibility. However, ASICsASIC are required in SoC designs due to their high performance as well as energy efficiency.

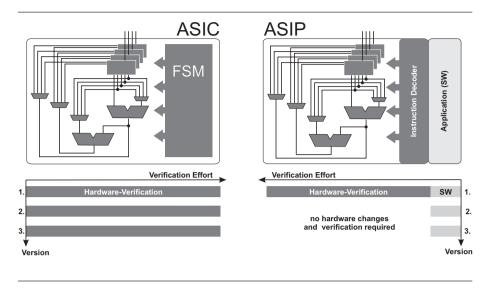

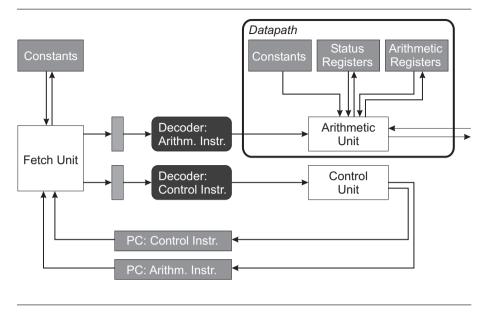

As shown in figure 1.1, an ASIC can be divided into two components data-path and control-path. The data-path covers computational units. storage elements and multiplexers to route the data. The control-path basically consists of a Finite State Machine (FSM) that controls the datapath. Thus, the FSM represents the application dependent schedule of operations. Due to its complexity and irregularity, design errors are more likely to appear in the control-path than in the data-path of the architecture [4]. Although the separation between data-path and control-path is theoretically existent, unfortunately, traditional ASIC design combines these components without a clear interface. This certainly affects the initial specification, but even more the reuse and adaption of the ASIC. Every variation of the ASIC has to be completely verified even if only the control-path is changed, as shown on the left of figure 1.1. Moreover, the commonly used design entry point is a hardware description on RTL, which already covers numerous hardware details unnecessary for a *functional* verification. However, these hardware details cause a slow simulation performance and render verification extremely costly.

Concluding from the previous paragraphs, a separation of concerns must be achieved. Hot spots of the application must be accelerated by an application-specific and optimized data-path while its control must be flexible and easy to verify. Processors partially address this requirement by being programmable and thus flexible with regard to the schedule of operations. This also implies a separation between fixed data-path and flexible control. Here, errors which ensue from the complex application dependent control can be easily eliminated by software updates. Furthermore, since application software can be executed by more abstract and therefore faster simulators compared to RTL hardware simulators, the time for functional verification is reduced. However, due to their generality, off-the-shelf General Purpose Processors (GPPs), Digital Signal

Figure 1.1. Comparison of ASIC and ASIP verification effort

Processors (DSPs) or Microcontrollers ( $\mu$ Cs) can neither achieve the performance nor the energy efficiency of ASICs.

The inevitable consequence is the use of *Application-Specific Instruction-Set Processors* (ASIPs) which incorporate the flexibility of processors and high performance and energy efficiency of ASICs [5][6][7]. The software, more precisely the sequence of instructions, represents the state transitions of the finite state machine mentioned above. Furthermore, the software can be written and verified independently from the ASIP implementation, which enables an efficient reuse of the ASIP. The orthogonal structure of an ASIP is illustrated on the right of figure 1.1, emphasizing the aspect of verification for the first instantiation and the subsequent reuse (bottom right corner of figure 1.1).

Obviously, not only the hardware implementation of an ASIP but also software development tools are required. As long as they have to be developed manually, the gain with regard to the verification time is neutralized. Therefore, a new ASIP design methodology is indispensable, to preserve the architectural advantages of ASIPs and to reduce the overall design effort.

The complexity of ASIP design results from the fundamental different design tasks and the optimization of the processor concerning a given application. This topic is discussed in detail in section 1.3.

Within the scope of this book the focus is set on application-specific computational elements in SoCs. However, various other aspects of SoC design are also crucially related to the design complexity, such as the on-chip communication. Numerous publications describe the SoC design crisis, e.g. [3], [4], [8], [9], [10] and [11].

This crisis in SoC design currently motivates new heterogeneous architectures, which represent alternatives to ASIPs. A brief overview of the different solutions is given in the following section.

#### 1.2 Heterogeneous Architectures: Computational Performance vs. Flexibility

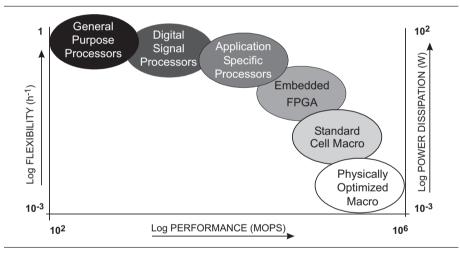

Heterogeneous architectures combine existing architecture types to satisfy the demands of SoC design. The available architecture types differ regarding performance, energy efficiency and flexibility [12][13], as depicted in figure 1.2.

Figure 1.2. Computational building blocks in SoCs. Source: T. Noll, EECS [14]

Off-the-shelf processors provide the most flexibility at the expense of performance and energy efficiency. The processors have fixed instruction-sets, data-paths and interfaces. Software development tools, such as C-compiler, assembler, linker, simulator and debugger are used for application software development. In contrast to this, ASICs provide the best performance at the expense of flexibility. ASIC development, usually started on RTL, requires gate-level synthesis tools, hardware simulators, place and route tools, etc. ASIPs as well as Field Programmable Gate Arrays (FPGAs) enable a trade-off between flexibility and performance. FPGAs provide flexibility by being reconfigurable to new hardware specifications. Due to the regular structure of FPGA building blocks, logic blocks with an regular structure can be mapped more efficiently to FPGAs than logic with an irregular structure. Therefore, the efficiency of the implementation strongly depends on the architecture.

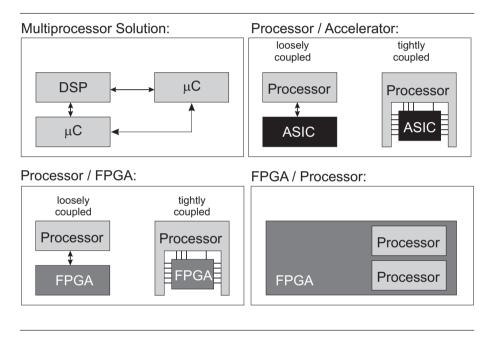

The architectures types mentioned above are combined to trade off design characteristics in heterogenous SoC design. Architectures currently discussed in academia and industry are presented in the following and summarized in figure 1.3.

Figure 1.3. Heterogeneous architecture types as SoC building blocks

MultiProcessor (MP) solutions receive significant impetus from the requirement for flexible solutions in embedded systems. They benefit from the high availability of off-the-shelf processors, such as GPPs,  $\mu$ Cs and DSPs. The required design tools are software development tools, such as C-compiler, assembler, linker and simulator. A challenging task is to consider the data and control dependencies while developing multitasking/multi-threading applications<sup>1</sup>.

However, one of the drawbacks of this approach is that the system performance does not scale linearly with the number of processors, as the on-chip communication has a substantial impact on the overall system performance [16]. Therefore, the design challenges are moved from the computational building blocks to the on-chip communication. Moreover, the potential for application-specific optimization of the computational blocks is completely neglected, which leads to suboptimal solutions.

A Processor with a loosely/tightly coupled accelerator addresses the need to speed up certain computational tasks. The data traffic between processor and accelerator is dependent on the given application. A *loosely coupled* accelerator may be used by multiple units in the SoC and accessed, for example, via a bus. This interface is suitable if data transfer rates are low and the computational tasks are independent of other computations executed in the meantime. The *tightly coupled* accelerator is preferable if a computational task depends on the overall control-flow of the application or a heavy data transfer between processor core and accelerator exists. These accelerators are embedded into the processor structure and directly linked to the temporal behavior of the processor. Often the accelerators are triggered by special purpose instructions. The major drawbacks of utilizing accelerators are the generality of the processor, the fixed interface between processor and accelerator and the fixed function of the accelerator. The above-mentioned drawbacks of ASIC design are valid for the accelerator design as well.

A Processor with loosely/tightly coupled FPGA partially eliminates the drawbacks of the processor-accelerator coupling. The fixed ASIC accelerator is replaced by an FPGA. The reconfigurable device may be either loosely or tightly coupled. Here, both components provide post-fabrication flexibility. However, the fixed interface between processor and reconfigurable device clearly restricts the architectural design space and prohibits possible optimization of the architecture with regard to a given application.

**FPGAs with integrated processors** are offered and promoted by FPGA vendors. Here, a particular number of GPPs and peripherals are integrated into the FPGA. Contemporary approaches also integrate

<sup>&</sup>lt;sup>1</sup>Multi-Tasking/Multi-Threading describes the ability to simultaneously execute several tasks/threads on MP-systems or pseudo-simultaneously by sharing the processing power of a single processor. The different terms can be distinguished by the definition given in [15]: A *task* is a semi-independent portion of the application that carries out a specific duty. A *process* is a completely independent program that has its own address space, while a *thread* is a semi-independent program segment that executes within a process.

special hardware as, for example, DSP engines into the FPGA chip. However, even though a high flexibility is provided, off-the-shelf solutions are hardly application-specific and potentially lead to suboptimal solutions.

The heterogeneous solutions mentioned above compete with ASIPs with regard to flexibility, performance, power dissipation and design efficiency. The particular characteristics of ASIPs are explained in the following.

Application-Specific Instruction-Set Processors incorporate the flexibility of programmable solutions and the high performance and energy efficiency of ASICs. The separation between processor and accelerator is completely removed, thus eliminating the drawbacks introduced by interfaces. However, eliminating the interface leads to a more complex design process, since the previously separated application software development and accelerator implementation are now merged into one design process. Furthermore, ASIP-specific application software development tools are required. Thus, the design of ASIPs requires a new design methodology reducing the overall design complexity, as discussed in the following section.

#### 1.3 Challenges of ASIP Design

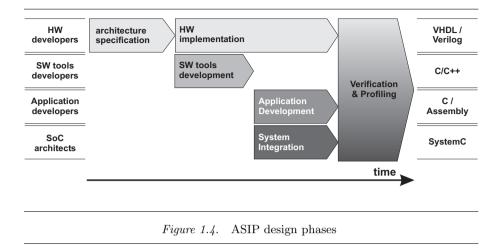

The development of a processor is a complex task, involving several development phases, multiple design teams and different development languages, as depicted in figure 1.4. The key phase in processor design is the architecture specification since it servers as the basis for all remaining design phases. Although Hardware Description Languages (HDLs) are designed for architecture implementation, in a traditional design flow, these languages are also often used for the initial specification of the processor. In this design phase tasks, such as hardware/software partitioning, instruction-set and micro-architecture definition is performed [17][18]. Based on the architecture specification, both the hardware implementation and the development of software tools is triggered. Both tasks are basically independent and therefore performed by different experts and design methodologies. Hardware designers use HDLs such as VHDL or Verilog, while software designers mostly utilize the C/C++programming language. In addition, the target processor needs to be integrated into the SoC and the application software needs to be implemented. Communication between the design teams is obviously difficult because of the heterogenous methodologies and languages. Nevertheless, as soon as the above-mentioned phases of processor design are completed, the verification of the hardware, application software and software development tools can be triggered.

Considering the traditional processor design flow, the strong dependencies between design phases imply a unidirectional design flow and prevent even minor optimizations. For example, an optimization of the instruction-set due to the application software development requires changes to the software tools and the hardware implementation as well. Due to the different development languages, changes to the architecture are difficult to communicate and inconsistencies are very likely to appear.

The complexity of processor design even increases in ASIP design, since optimizations targeted to a particular application are mandatory. Mapping an architecture to a given application means moving through a design space spanned by axes such as flexibility, power consumption, clock speed, area and more. Every design decision in one dimension constrains other decisions, for example

| architectural features   | vs. | design time,              |

|--------------------------|-----|---------------------------|

| design time              | vs. | physical characteristics, |

| physical characteristics | vs. | flexibility,              |

| flexibility              | vs. | verification effort,      |

| verification effort      | vs. | architectural features.   |

It is obviously not possible to move through this design space by applying the traditional processor design methodology. A unified design methodology is required, which provides a common basis for all design phases. It must be suitable for all design engineers involved and naturally consider the dependencies of the design phases.

Today's dilemma in SoC design stems from the requirement of flexible high performance computational building blocks under the constraint of a low design complexity. Most approaches today utilize heterogeneous solutions, which combine already known architecture types and well established design methodologies. Thus, the requirements can only partially be addressed. Contrary to these approaches, this book proposes a new ASIP implementation methodology, which is based on Architecture Description Languages (ADLs) in general and the Language for Instruction-Set Architectures (LISA) in particular. Along with the work performed in the fields of design space exploration, software tools development and system integration based on LISA (cf. chapter 3), this leads to a novel ASIP design methodology. This book addresses the automatic ASIP implementation starting from a given LISA description. which surpasses the traditional processor design flow regarding design efficiency and architectural efficiency. Therefore, a paradigm shift in ASIP implementation is advocated.

#### 1.4 Organization of This Book

This book is organized as follows. In chapter 2 the related work in the field of ASIP design methodologies, RTL hardware implementation and heterogeneous architectures is discussed. In chapter 3, the LISA design environment is described focusing on design space exploration capabilities, software development tools generation and system integration. In chapter 4 impetus is provided regarding the new entry point for ASIP design and implementation. After this, the architecture description language LISA is discussed with regard to automatic hardware implementation (chapter 5). In chapter 6 the intermediate representation used for automatic ASIP implementation is presented. The intermediate representation forms the basis for high level optimizations, described in chapter 7, and for the automatic integration of processor features, described in chapter 8. Three case studies are presented in detail in chapter 9 and 10 to demonstrate the feasibility of the proposed synthesis methodology. The first case study deals with an ASIP for turbo decoding. The second and third case studies discuss architectures derived from existing processors while maintaining application software compatibility. The ISS-68HC11 was devised to achieve a higher instruction throughput compared to the original Motorola architecture. Infineon's ASMD was devised to support new instructions while offering backwards compatibility to existing applications. Finally, the proposed automatic ASIP implementation is summarized in chapter 11.

## Chapter 2

# ASIP DESIGN METHODOLOGIES

The challenges in ASIP design, as described in the previous chapter, are addressed differently by today's design methodologies. Several approaches are based on Architecture Description Languages (ADLs), which can be grouped according to the following three categories:

**Instruction-set centric languages** focus on the *instruction-set* and thus represent the programmer's view of the architecture. They are mainly used to describe the instruction encoding, assembly syntax and behavior. The languages nML [19] and ISDL [20] are examples for this category.

Architecture centric languages focus on the *structural aspects* of the architecture. The architecture's behavior is described by functional building blocks and their interconnections, often in an hierarchical description style. Therefore, these languages represent the hardware designer's view of the architecture. An example for this type of ADLs is the MIMOLA [21] language.

Mixed instruction-set and architecture oriented languages combine the description of the instruction-set and the structural aspects in one ADL. Therefore, ASIP design approaches based on mixed-level languages mostly are able to target all domains of ASIP design: architecture exploration, architecture implementation, software development tools generation and system integration. Representatives of this category are e.g. EXPRESSION [22] and LISA [23]. Furthermore, ADLs can be distinguished whether or not a library of predefined building blocks is used (also referred to as *module library approach* [24]). In general, such a set of predefined building blocks enables a high quality of the generated software tools as well as an efficient implementation of the final architecture. However, these advantages are accompanied by a moderate flexibility and therefore possibly suboptimal solutions. This drawback can be eliminated by ADLs which are not limited to a set of predefined components, but allow the semantic and/or behavioral description of architectural building blocks. Due to the enormous flexibility provided by the ADLs, software development tools generation, automatic hardware implementation and system integration become challenging tasks.

In section 2.1 several ADL based approaches, which address all domains of ASIP design, are discussed. Approaches which only target a subset of the complete ASIP design tasks are omitted.

Beside ADL based ASIP design, various approaches are based on (re)configurable architectures. These are presented in section 2.2.

The currently accepted entry point for hardware implementation is an architecture description in an HDL on RTL. The synthesis down to gatelevel and logic optimizations are performed by already established tools. Therefore, the RTL hardware model is the interface between the proposed automatic ASIP implementation and the existing implementation flow. HDLs and logic representations are briefly covered in section 2.3.

#### 2.1 ADL based ASIP Design

In contrast to traditional processor design and ASIP design based on (re)configurable architectures, the ADL based design addresses a huge architectural design space while providing a high design efficiency. The different approaches are presented in the following.

**EXPRESSION.** The EXPRESSION ADL [22][25], developed at the U.C. Irvine, captures the structure and the instruction-set of a processor as well as their mapping. The structural description comprises components and communication between them. Four different types of components exist: units (e.g. ALUs), storage elements (e.g. register files), ports and connections (e.g. buses). Each component is configurable by a list of attributes. The instruction-set is specified by operations that consist of opcode, operands, behavior and instruction format definition. Mapping functions are used to map the structure defined by the components to the operation's behavior specification.

This defines, for each component, the component's set of supported operations (and vice versa).

EXPRESSION originally targeted the software tools generation, such as C-compiler, assembler, linker and simulator. The generation of an RTL hardware model came into focus only in recent years.

The language EXPRESSION provides a set of predefined (sub-)functions to describe the behavior and the instruction-set of the processor. Base on a, so called, *functional abstraction* [26], the functions represent coarse-grained operations (e.g. a program memory access) and sub-functions fine-grained operations (e.g. an addition).

Multiple functions can be nested to describe a behavior which is not represented by the set of functions initially. Considering the hardware generation from an EXPRESSION model, the utilization of predefined (sub-)functions enables a hardware generation based on predefined but configurable RTL building blocks. The major drawback here is given by the reduced flexibility with regard to the behavioral description.

EXPRESSION maps the given architecture description directly to a hardware description [26][27], without applying optimizations. Even if optimized RTL building blocks are instantiated, the hardware generation results in an suboptimal architectural efficiency as a cross template optimization is missing. Also, this framework does currently not support commonly required processor features, such as a debug mechanism or power save modes. Therefore, the generated RTL hardware model only addresses an estimation of the physical characteristics of the architecture during design space exploration.

FlexWare. FlexWare [28] from SGS Thomson/Bell Northern Research consists of the code generator CodeSyn, an assembler generator, a linker generator and the Insulin Simulator. The Simulator is based on a parameterizable VHDL model. Additionally, FlexWare supports the generation of an RTL hardware model, which is not possible in the FlexWare2 environment developed by STMicroelectronics. The FlexWare2 environment [29][30] is capable of generating assembler, linker, simulator (FlexSim) and debugger (FlexGdb) from the, so called, Instruction Description Language (IDL).

**ISDL.** The Massachusetts Institute of Technology (MIT) developed the language ISDL [20] to target VLIW architecture modeling, simulator generation (GENSIM) and hardware model generation (HGEN).

The published hardware generation approach [31][32] generates a Verilog description from a given ISDL model. The developed hardware generation only targets the design phase of architecture exploration rather than a final architecture implementation, which therefore must still be manually implemented.

Although resource sharing optimizations are identified as major challenge in automatic hardware implementation from ADLs, their implementation in HGEN only addresses a minimization of computational resources by using a maximum clique search. This abstract view to the resource sharing problem neglects an optimization of the interconnect as well as the timing effects of resource sharing optimizations. Overall, the presented optimizations neither achieve a sufficient architectural efficiency nor trade off different physical characteristics.

ISDL contains only very little structural information about the architecture. The architecture is mainly described from the programmer's point of view, and therefore important information required for an implementation of the architecture is missing or only implicitly available. For example, the information about timing and schedule of instructions is specified in ISDL by annotating the latency. Information about the pipeline structure is not specified but must be derived from the information about the instructions' latencies. Considering the automatic hardware implementation, incomplete or implicit information can only be compensated by assumptions. These certainly lead to a suboptimal architecture implementation if optimizations are not applied adequately.

LISA. The LISA language and the corresponding processor design environment has been developed at the Institute for Integrated Signal Processing Systems (ISS) at the RWTH Aachen University [33] and is commercially available form CoWare Inc. [34]. The LISA design environment is described in chapter 3 regarding architecture exploration, software tools generation and system integration. The information about the underlying hardware which is inherent in the LISA model is described in chapter 5. The optimizations performed during hardware synthesis and the integration of processor features are described in chapter 7 and chapter 8.

**MetaCore.** The MetaCore system from the Korea Advanced Institute of Science and Technology (KAIST) [35][36] targets the ASIP development for DSP applications. MetaCore divides ASIP design in two phases, first a design exploration and second the design generation. On the basis of a set of benchmark programs and a formal specification of the processor, an estimation of the hardware costs and performance estimation is provided. The formal specification is provided by the so called MetaCore Structural Language (MSL) and the MetaCore Behavioral Language (MBL). Once the architecture specification is fixed the processor is automatically implemented in an HDL and software tools comprising C-compiler, assembler and instruction-set simulator are generated. The MetaCore system selects and customizes macro-blocks from a library to generate the target architecture. Therefore, the architectural design space is limited to the available macro-blocks.

**MIMOLA.** The language MIMOLA [21], developed at the Universität Dortmund, describes processors by a hierarchical net-list close to the RTL. Software tools such as C-compiler (MSSQ compiler [37] and RECORD compiler [38]) and instruction-set simulator can be generated. Moreover, MIMOLA supports code-generation, test-generation and the automatic hardware implementation. However, the low abstraction level goes along with numerous architectural details which hinder an efficient design space exploration. The quality of the generated software tools is therefore not sufficient for application software development.

**nML.** The language nML [19][39] originates from the Technische Universität Berlin and targets the instruction-set description. Several projects utilize nML for software tools generation as well as for hardware generation. Research activities at the TU Berlin led to the generation of the instruction-set simulator SIGH/SIM and the code generator CBC.

Based on nML, a retargetable C-compiler (Chess) and instruction-set simulator generator (Checkers) were developed by IMEC [40] in Leuven, Belgium, and commercialized by Target Compiler Technologies [41]. In addition the commercial software development tool suite comprises a retargetable assembler and disassembler (Darts), linker (Bridge) and a retargetable test-program generator (Risk). The generation of an RTL hardware model is supported by a tool called Go. According to [42], the hardware model is only partially generated and the designer has to plug in the implementation of functional units and memories himself. Due to this semi-automatic approach inconsistencies between the nML model and the RTL hardware model are very likely. In addition, it is hardly possible to evaluate continuously the effects of high level architectural decisions on the physical characteristics of the architecture.

The nML language was also adopted by Cadence in cooperation with the Indian Institute of Technology. The project, called sim-nML [43], targets the software tools generation, while SIM-HS [44] targets the generation of behavioral Verilog models and the generation of structural synthesisable Verilog processor models. Sim-nML descriptions provide temporal information by the specification of the latency instead of the temporal execution order. Therefore, the synthesis process has to perform scheduling and resource allocation commonly known from behavioral synthesis. The complexity of these techniques is reduced by adopting templates. For example, a four stage pipelined architecture is always assumed. All transformations, which can be performed during synthesis, are either operating on a very coarse-grained level (e.g. pipeline stages) or on a very fine-grained (e.g. single arithmetic operations) level of abstraction. Overall, this approach is lacking flexibility in ASIP implementation by utilizing fixed structural and temporal templates.

**PEAS.** The PEAS (Practical Environment for ASIP Development) project started in 1989 targeting the configuration of an parameterizable core regarding the instruction-set and architectural parameters [45], such as bit widths or register file size. In the second version of the PEAS system the support for VLIW architectures was added. In the third version of the PEAS environment [24][46], called PEAS-III, also simple pipelined architectures are addressed. The development of the PEAS environment was the basis for ASIP Meister [47], available as beta version first in 2002. The PEAS environment is based on a graphical user interface (GUI), capturing the architecture's specification. According to the architecture specification a hardware model for simulation and synthesis is generated. Even if the gate-level synthesis results are comparable to handwritten implementations, the PEAS approach covers only a small area of the available ASIP design space.

Tipi (Mescal Architecture Development System). The Tipi ASIP design framework has been developed within the scope of the Mescal project at the U.C. Berkeley [48][49][50]. The Tipi framework focuses on the specification of the data-path, which is described in a structural manner close to RTL. The control-path is considered to be overhead in the ASIP design process and thus strongly abstracted or omitted. An assembler, a cycle and bit true simulator and a synthesisable RTL Verilog model are generated from the architecture description. For hardware implementation a one-to-one mapping from the Tipi framework to the hardware model is proposed. High level optimizations and the generation of commonly required processor features are not included in the framework. Details about hardware implementation and their gate-level synthesis results, especially about the control-path, are not available.

The current trends in ASIP design clearly indicate that the design entry point is raised above the RTL. In contrast to this, the Tipi design framework concentrates on an abstraction level close to RTL, which is not suited to perform an efficient design space exploration. Moreover, possible optimizations to the implementation of the complete architecture are highly limited by focusing only on the data-path specification.

#### 2.2 (Re)Configurable Architectures

Although the proposed LISA processor design methodology is completely different from utilizing (re)configurable designer extensible architectures both approaches strongly compete. Compared to ADL based ASIP design, (re)configurable architectures cover a limited architectural design space only but enable a high design efficiency. Configurable architectures can be customized before fabrication, while reconfigurable architecture provide the same architectural flexibility even after fabrication. In the following, three examples are discussed.

**ARC.** ARC International [51] is an independent company since 1998 and provides configurable microprocessor cores. Also, peripherals, software (such as Real Time Operating Systems and Codecs) and development tools are included in the company's portfolio.

ARC offers several architectures, currently the ARCtangent-A4, ARCtangent-A5, ARC 600 and ARC 700. The RISC cores support the ARCompact instruction-set, which provides 16 bit instructions for the most frequently used operations and covers all other operations by 32 bit instructions. These two types of instructions can be arbitrarily used within one application. The architecture may be configured with regard to DSP extensions, cache and memory structure, bus interfaces or peripherals. A designer can select from a range of processor configuration options or add custom Intellectual Property (IP) to alter the architecture. For this purpose, ARC provides a Java-based configuration tool, namely ARChitect 2. It enables designers to vary configuration options and to incorporate new instructions. The design environment generates the source code (Verilog or VHDL), synthesis scripts, test files, HDL-simulator support files and HTML-formatted documentation for the design.

**Tensilica.** Tensilica Inc. [52] provides configurable microprocessor cores, in 2005 the Xtensa LX and Xtensa V. The latter one, for example, is a 32 bit RISC microprocessor architecture made up of five pipeline stages and supports a 16 bit or 24 bit instruction-set. The

instruction-set is not switchable during runtime. The microprocessor is made up of fixed, optional, configurable and designer defined building blocks. The base architecture comprises processor control unit, instruction fetch unit, decode unit and data laod/store unit. The memory management unit, all memory blocks and i/o blocks are optional and/or configurable. Other processor features, such as Trace Port, JTAG Tap Control, on-chip debug mechanisms, multiply-accumulate units, multiply units, floating point unit and also a DSP engine are optional. Registers and, so called, hardware execution units can be defined by the designer.

Designer defined building blocks are specified in the Tensilica Instruction Extension (TIE) language [53]. This Verilog-like specification language enables the designer to cover the hardware aspect, such as computational units and additional registers, and the software aspect, for example instruction mnemonics and operand utilization. The TIE description and the selection/configuration of building blocks are the input to the, so called, processor generator. This tool generates on the one hand the synthesisable RTL VHDL or Verilog description and on the other hand the software tools for application development. Further information can be found in [9].

This approach enables a high performance hardware implementation as well as high quality application software development tools. Tensilica's latest development is the Xtensa Processor Extension Synthesis (XPRES) Compiler. This tool identifies hot spots in a given Capplication and customizes the Xtensa architecture to accelerate the application execution.

The limited architectural flexibility is the major drawback of this approach. The fixed structure of the on-chip communication as well as the given microprocessor core cause an upper bound to the performance increase.

**Stretch.** Stretch Inc. [54] offers the reconfigurable processor core family S5000. This architecture family consists of a programmable RISC processor core with a tightly coupled reconfigurable device, so called Instruction-Set Extension Fabric (ISEF). The ISEF is used to implement custom instructions, which extend the original instruction-set of the architecture. Up to three 128 bit operand registers and two 128 bit result registers can be utilized to establish the communication between the fixed RISC architecture and the reconfigurable portion of the architecture. The RISC core of the S5000 family is based on the Tensilica Xtensa RISC processor core, described above.

Available tools are C-compiler, assembler, linker, debugger and profiler, which are combined in an integrated design environment. Moreover, the C-source code of the application can be profiled automatically and hot spots are identified with regard to the application execution time. These portions of the application are mapped to the ISEF. With this approach a simulated speed up of a factor of 191 is achieved for the EEMBC Telemark Score [55], by comparing the S5610 RISC core with and without customized instructions.

The S5000 architecture family provides post-fabrication flexibility with regard to the control by software and with regard to the datapath implementation by an reconfigurable building block. However, application-specific optimizations are limited to this reconfigurable building block. Thus, numerous optimizations in ASIP design are omitted. For example, the pipeline organization cannot be changed in accordance to the targeted application. The memory as well as register organization is fixed and the interface between processor core and the reconfigurable building block is predefined.

#### 2.3 Hardware Description Languages and Logic Representation

A hardware description on RTL is the commonly accepted entry point for architecture implementation. Within this book a new synthesis approach from an ADL to a hardware description language is proposed. Currently, VHDL, Verilog and SystemC are supported. The synthesis framework can easily be enhanced to support future languages, for example SystemVerilog.

#### 2.3.1 VHDL, Verilog, SystemVerilog and SystemC

In the scope of this book the languages VHDL, Verilog, SystemVerilog and SystemC are considered as hardware description languages on RTL, although these languages can be used to describe the target architecture on multiple abstraction levels. Common to all languages is the ability to describe hardware on RTL by providing elements such as concurrency, clocks and sensitivity.

The development of **VHDL** has been started in 1980 by IBM, Texas Instruments, and Intermetrics and became the IEEE 1076 standard in 1987 [56][57]. The initial version (VHDL '87) was continuously discussed and adopted to new requirements (VHDL '93 and VHDL '00). VHDL is mostly used in Europe. In 1985 Verilog originated from Automated Integrated Design Systems, in the meanwhile acquired by Cadence Design Systems [58]. This HDL is mostly used in the USA and Asia. It became IEEE Standard 1364 [56][59] in 1995. The latest revision is Verilog 2001.

**SystemVerilog** is the latest approach, initiated by Accelera, to establish a language combining aspects of a hardware description and hardware verification [60]. Currently, this language is only supported by few existing tools, thus real-world experience about the efficiency is missing.

**SystemC** has been invented to close the gap between algorithm specification, often described using the C-programming language, and system simulation [61]. Its current development is driven by the Open SystemC Initiative (OSCI) which is steered by major EDA companies and IP-providers. However, while the SystemC language became famous in the area of system level design, the support for gate-level synthesis in Synopsys' Design Compiler was discontinued in 2003.

#### 2.3.2 Logic Representation and Binary Decision Diagrams (BDDs)

In order to perform gate-level synthesis, the RTL hardware description needs to be transformed into a low level representation made up of building blocks of a technology library. Therefore, gate-level synthesis consists of several steps: logic synthesis, logic optimizations and technology mapping. These steps are based on boolean function representations, such as truth tables or Karnaugh Maps. However, these data structures are insufficient to handle the computational complexity of real world problems. Two-level boolean representation or Multi-Level boolean networks became favored to apply advanced optimization techniques.

An alternative representation are Binary Decision Diagrams (BDDs), which have been discussed since 1959 [62][63]. However, BDDs gained importance in 1986 when Bryant [64] proposed restrictions on BDDs enabling new algorithms.

In order to reduce the computational complexity, the synthesis framework and the optimizations proposed in this book operate on an abstraction level above RTL. Therefore, the concepts commonly known from logic optimizations are not reused.

#### 2.4 Motivation of This Work

As described above, various approaches cover hardware generation from ADLs. However, most approaches map the architectural information of the ADL model directly to a hardware description on RTL. The achieved physical characteristics, in terms of area, timing and power consumption, are not sufficient for a final architecture implementation. Optimizations are basically not considered for the ADL to HDL synthesis process. Moreover, essential processor features, such as debug mechanism or power save modes, are not covered by these automatic approaches. Therefore, in these approaches hardware generation is only suited for a rough estimation of the physical characteristics during architecture exploration.

Some approaches base on coarse granular building blocks provided in a library or by predefined architecture templates. In these cases, an efficient implementation can be derived from the architecture model. However, the architecture model cannot be optimally tailored to the application, as only a limited architectural flexibility is provided by these approaches.

The contribution of this work is an automatic ASIP implementation from LISA, which fulfills the demands of a final hardware implementation while preserving the desired architectural flexibility. Based on an intermediate representation between the level of ADLs and HDLs and explicit architectural information given in the LISA model, optimizations are performed and processor features are automatically integrated. The achieved architecture implementations are comparable to implementations handwritten by experienced designers. Therefore, the entry point for ASIP implementation is shifted from the currently accepted RTL to a LISA based implementation.

#### Chapter 3

# ASIP DESIGN BASED ON LISA

The LISA Processor Design Platform (LPDP) has been developed at the Institute for Integrated Signal Processing Systems (ISS), RWTH Aachen University [33]. The LISA design methodology [23][65] has become one of the most comprehensive and powerful ADL based design environments and is internationally recognized by academia and industry. The design environment based on LISA, including the automatic ASIP implementation proposed in this book, is commercially available from CoWare Inc. [34].

In order to tailor the architecture to the special requirements of a given application, ASIP design requires an efficient design space exploration phase. The instruction-set, micro-architecture, register configuration, memory configuration, etc. are subject to optimizations. The LISA based design space exploration, software tools generation and system integration are described in the following sections.

#### **3.1** Design Space Exploration

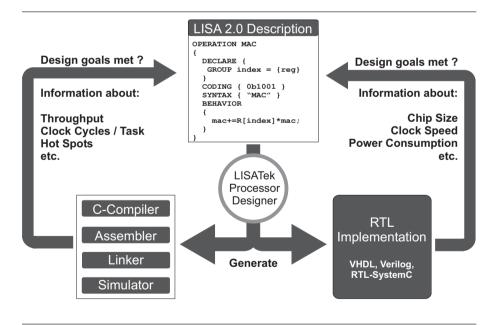

In ASIP design the key is an efficient exploration of the architectural design space. The LISA language allows to implement changes to the architecture model quickly, as the level of abstraction is higher than RTL. As shown in figure 3.1, the LISA model of the target architecture is used to automatically generate software tools such as C-compiler, assembler, linker, simulator and profiler. These software tools are used to identify

hot spots and to jointly profile the architecture and the application. Both are optimized according to the profiling results, e.g. throughput, clock cycles or execution count of instructions. This exploration loop can be repeated until the design goals are met. With LISA a highly efficient design space exploration is ensured, as the ASIP model can be modified easily and the software tools are re-generated within a negligible amount of time. Moreover, the LPDP provides additional tools that accelerate the design space exploration, such as, for example, an instruction encoding generator [66].

The knowledge about the physical characteristics of the architecture is important at an early design stage already. For example, the information about clock speed substantially influences the number of pipeline stages or even the pipeline organization in general. Ignoring physical parameters in the design space exploration phase leads to suboptimal solutions or long redesign cycles. The automatic ASIP implementation from LISA, also shown in figure 3.1, provides important feedback about the physical characteristics of the architecture. The hardware generation from LISA is discussed in the following chapters.

Figure 3.1. Exploration and implementation based on LISA

#### **3.2** Software Tools Generation

The software tools generated from the LISA description are able to cope with the requirements of complex application development. Ccompiler, assembler, linker, simulator and profiler are generated from a LISA model.

#### 3.2.1 C-Compiler Generation

The shift from assembly code to the C-programming language is ongoing for software application development for embedded systems. This is basically motivated by the increasing complexity of the embedded software. Considering the number of different versions of an ASIP during design space exploration and the complexity of C-compiler design Complexity, C-Compiler design, the automatic generation of a C-compiler is highly desired [67]. For this reason, the automatic generation of a C-compiler in ASIP design strongly came into focus recently [68].

To retarget a C-compiler, in particular the architecture-specific backend of a C-compiler must be adjusted or rewritten, while the architecture independent frontend and most of the optimizations are kept unchanged. The C-compiler platform CoSy from ACE [69] is used to retarget the C-Compiler based on the information extracted from the LISA model. While some information is explicitly given in the LISA model (e.g. via resource declarations), other information (e.g. resource allocation) is only implicitly given and needs to be extracted by special algorithms. Some further, highly compiler-specific information is not present in the LISA model at all, e.g. data-type bit widths. Thus, compiler information is automatically extracted from LISA whenever possible, while GUI-based user interaction is required for other compiler components. For details about C-compiler generation from LISA the reader is referred to [70][71] [72].

#### 3.2.2 Assembler and Linker Generation

The generated assembler [73] processes the assembly application and produces object code (LISA Object File, LOF) for the target architecture. An automatically generated assembler is required, as the modelled architecture has a specialized instruction-set. A comfortable *macro assembler* exists to provide more flexibility to the designer.

The automatically generated linker combines several pieces of object code to a single executable in ELF format [74]. The linker is architecturespecific since the modelled memory organization needs to be taken into account. Various configuration possibilities are provided to steer the linking process. Further information about assembler, macro-assembler and linker can be found in [75].

#### 3.2.3 Simulator Generation

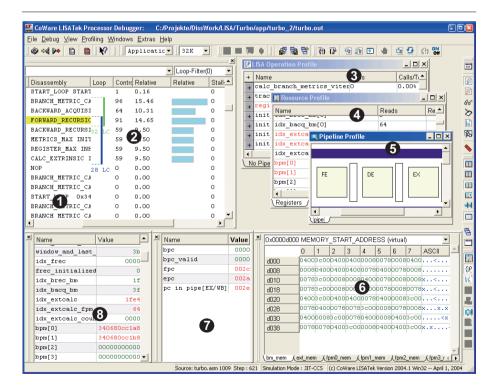

Generation, Simulator The generated simulator is separated into backend and frontend. The frontend is shown in figure 3.2. It supports application debugging, architecture profiling and application profiling capabilities. The screenshot shows some features such as disassembly view (1) including loop and execution profiling (2), LISA operation execution profiling (3), resource profiling (4) and pipeline utilization profiling (5). The content of memories (6), resources in general (7) and registers in particular (8) can be viewed and modified. Thus, the designer is able to debug both ASIP and application easily. Additionally, the necessary profiling information for design space exploration is provided, such as pipeline and instruction utilization.

Figure 3.2. The LISA simulator and debugger frontend

The performance of the simulator strongly depends on both the abstraction level of the underlying LISA model and the accuracy of the memory model [76]. Furthermore, various simulation techniques, e.g. compiled simulation [77], interpretive simulation and Just-In-Time Cache Compiled Simulation (JIT-CCS) [78][79] are supported. These techniques are briefly described below.

#### Interpretive simulation

The interpretive simulation techniquesimulation technique, interpretive is based on a software implementation of the underlying decoder of the architecture. For this reason, the interpretive simulation is considered to be a virtual machine performing the same operations as the hardware does, namely fetching, decoding and executing instructions. All simulation steps are performed at simulation runtime. In contrast to a hardware decoder, the control portions of an instruction execution requires a significant amount of time in software.

#### **Compiled** simulation

Compiled simulation [80][81] uses the locality of code in order to speed up the execution time of the simulation compared to the interpretive simulation technique. The task of fetching and decoding is performed once for an instruction before simulation run. Thus, the simulation runtime is reduced when instructions are executed multiple times. However, compiled simulation requires the program memory content to be known before simulation runtime and to be static during simulation. Various scenarios are not supported by the compiled simulation technique, such as system simulations with external and thus unknown memory content or operating systems with changing program memory content. Additionally, large applications require a large amount of memory on the target host.

#### Just-in-time cache compiled simulation (JIT-CCS)

The objective of the JIT-CCS is to provide both a general applicability and a high simulation speed. Techniques from interpretive simulation and compiled simulation are combined in the JIT-CCS [79]. The basic technique is to perform the decoding process *just-in-time* at simulation runtime and to store the results in a cache for later use. In every subsequent simulation step the cache is searched for already existing and valid decoding results. Because of that, the full flexibility of interpretive simulation is provided. Due to the locality of code in typical applications the simulation speed can be significantly improved using JIT-CCS. Numerous case studies show that with an increasing cache size JIT-CCS performance converges to the performance of compiled simulation. According to the case studies a reasonable maximum of cache lines is 32768, where a line corresponds to one decoded instruction. The maximum amount of cache lines corresponds to a memory consumption of less than 16 MB on the simulator host. Compared to the traditional compiled simulation technique, where the complete application is translated before simulation, this memory consumption is negligible.

# 3.3 System Simulation and Integration

Today, typical SoCs combine a mixture of several computational elements, such as DSPs,  $\mu$ Cs, ASIPs, ASICs, etc. Certainly, system level simulation is necessary for both performance evaluation and verification in the system context. The automatically generated LISA processor simulators can easily be integrated into various system simulation environments, such as CoWare ConvergenSC [34] or Synopsys' System Studio [82].

The communication between an ASIP and its system environment can be modelled on different levels of abstraction. First, LISA pin resources can be connected directly to the SoC environment for pin accurate cosimulation. Second, the LISA bus interface allows to use commonly accepted SoC communication primitives and to model the communication on a higher abstraction level, for example the level of TLM [83]. Third, a generic C-programming language interface provides adaptability to arbitrary interfaces.

The system simulation debugger offers all observability and controllability features for multiprocessor simulation as known from standalone processor simulation. Thus, a software centric view to an arbitrary number of ASIPs as well as the system context is provided to the designer [84].

# Chapter 4

# A NEW ENTRY POINT FOR ASIP IMPLEMENTATION

Due to the high efficiency of design space exploration, the automatic generation of software development tools and the possibility of an early system integration, ASIP *design* nowadays starts with an architecture model in an ADL. The ASIP design phases and their corresponding software tools are presented in the previous chapter. ADLs do not provide a link to the ASIP *implementation* naturally, and thus essential information about the physical characteristics of the architecture is unknown.

Currently, the design phase of hardware implementation is entered on the RTL. Gate-level synthesis tools, such as Synopsys' Design Compiler [85] or Cadence's First Encounter [86], are used to proceed from RTL to gate-level regarding a particular technology library. On this abstraction level, accurate estimates about the physical characteristics, including clock speed, area or power consumption, can be obtained for the first time<sup>1</sup>.

A manual implementation of the ASIP on RTL certainly provides information about physical characteristics. However, modifications to the ADL model of the ASIP are often necessary because of either violated physical constraints or possible optimizations. Obviously, in these cases the design efficiency becomes unacceptably low, as two models for software tools generation and implementation have to be written and maintained throughout the entire design process. In particular, adapting an RTL hardware model is a tedious and error-prone task, which

<sup>&</sup>lt;sup>1</sup>Research and development in the field of already established design methodologies below RTL is still ongoing. In particular an accurate estimation of physical characteristics for shrinking technology sizes is targeted.

typically leads to significant inconsistencies between the two models of the same ASIP.

Various approaches target the generation of an RTL hardware model from an ADL model, as described in chapter 2. The generated RTL hardware models are inferior to models that are handwritten by experienced designers [26][87][88][89]. They neither achieve equal physical characteristics nor support well-known processor features, such as builtin debug mechanisms or automatic power save control. Thus, these RTL hardware models are only used during architecture exploration for a rough estimation of the physical characteristics. Manual optimizations are required if these models are used for the final architecture implementation. However, this potentially causes inconsistencies between the final implementation and the automatically generated software development tools.

Obviously, there is a pressing need for an advanced automatic ASIP implementation which closes the currently existing gap between ADL models and RTL hardware models. To gain the acceptance of ASIP designers an automatic approach must fulfill particular criteria, which are discussed in the following.

# 4.1 Acceptance Criteria for an Automatic ASIP Implementation

Considering several academic and industrial case studies [26][87][88], the following criteria must be fulfilled in order to establish an automatic ADL based ASIP implementation. First of all, the *architectural efficiency* and *implementation flexibility* must be close to the results achieved by manual implementations on RTL. Second, the *processor features*, which are supported by an automatic implementation, must be comparable to the those of handwritten implementations. Third, the goals must be met without compromising architectural flexibility and design efficiency. These three criteria are elaborated in the following sections.

# 4.1.1 Architectural Efficiency and Implementation Flexibility

In VLSI design, *architectural efficiency* is used to quantitatively compare different architectural alternatives. The physical characteristics, such as timing, area and energy, are used to evaluate an architecture. The valid ranges of the physical characteristics are defined by *boundary constraints*, whereas *precise constraints* must be accurately fulfilled to avoid device failure.

Derived from [90] and [91], physical characteristics<sup>2</sup>  $P_i$  and corresponding weights  $w_i$  define the architectural efficiency  $\eta_{arch}$  by

$$\eta_{arch} = \prod_{i=1}^{n} \frac{1}{P_i^{w_i}} \,. \tag{4.1}$$

In VLSI design the architectural efficiency is commonly defined by  $\eta_{arch} = \frac{1}{AT}$  (or  $\eta_{arch} = \frac{1}{ATE}$ ), which uses equally weighted Area (A), Timing (T) (and Energy (E)).

According to equation 4.1, the same architectural efficiency can be achieved by various implementations each balancing the physical characteristics differently. The ability to trade off the physical characteristics during architecture implementation is called *implementation flexibil-ity* in the following.

In order to optimally tailor the architecture to the application, the architectural efficiency and the implementation flexibility are equally important in ASIP design. In both fields, an automatic approach must achieve results which are close to handwritten implementations by experienced designers.

# 4.1.2 **Processor Features**

The recent developments of GPPs,  $\mu$ C and DSPs have produced sophisticated auxiliary **processor features**, such as built-in debug mechanisms or automatic power save control. Although these features do not influence the core functionality of the architecture, they are nevertheless important for the usability of the ASIP and can considerably influence the implementation. HDLs naturally support their description, while ADLs do not in order to accelerate the design space exploration. Certainly, this negatively affects the acceptance of ADL based ASIP design. Therefore, an automatic ASIP implementation has to cover these processor features in an appropriate way.

# 4.1.3 Design Efficiency

The **design efficiency** is of major importance in SoC and ASIP design to satisfy today's time-to-market requirements. The architectural efficiency  $\eta_{arch}$  and the overall design effort  $T_{design}$  (in man months and weighted by  $w_{design}$ ) can be used to compare the efficiency of different design methodologies [90][91], as given in equation 4.2.

<sup>&</sup>lt;sup>2</sup>In [91]  $P_i$  is referred to as architectural parameter.

$$\eta_{design} = \left(\frac{1}{T_{design}}\right)^{w_{design}} \eta_{arch} \tag{4.2}$$

The main goal of an ADL-based ASIP design is a high design efficiency, which has been demonstrated by various case studies, as presented in [23], [87], [92], [93], [94] and [95].

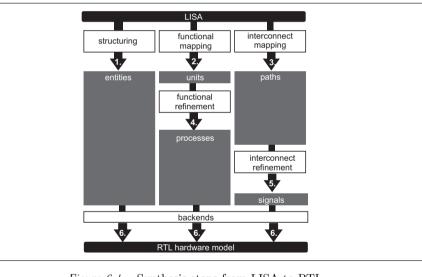

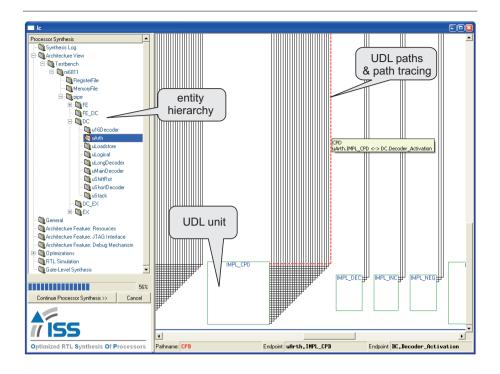

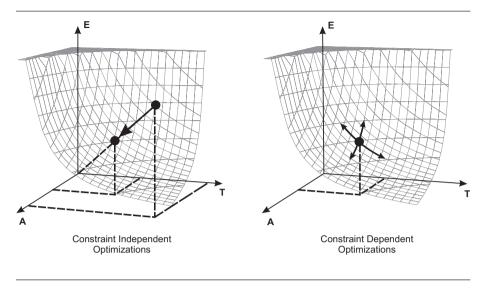

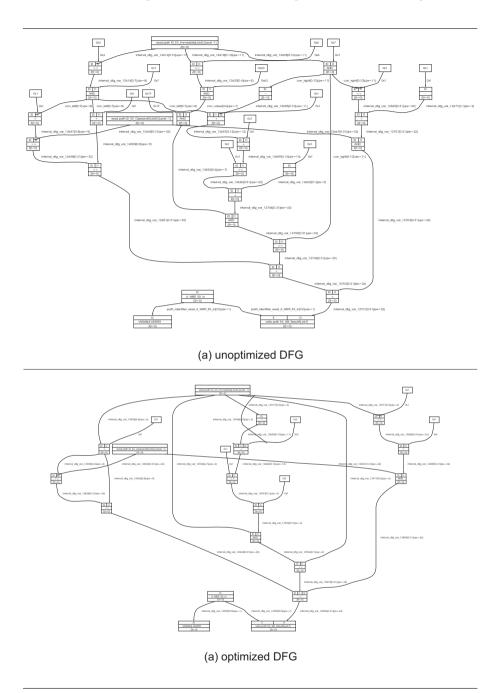

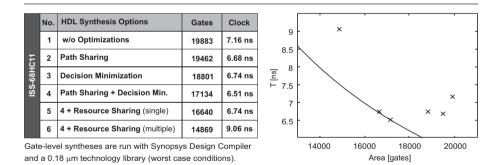

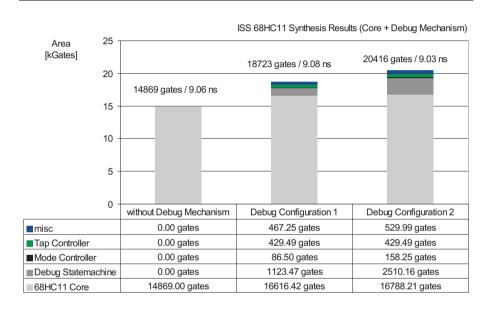

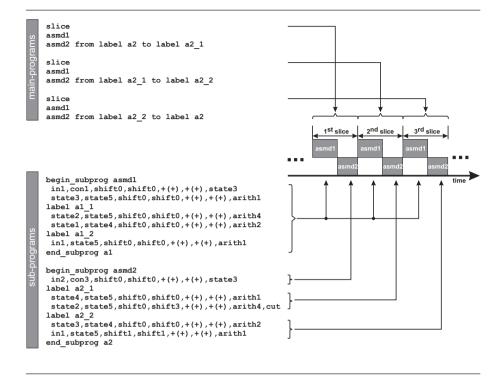

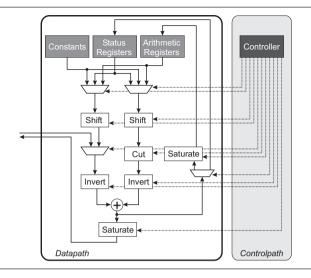

# 4.2 From Architecture to Hardware Description