Alex Doboli · Edward H. Currie

# Introduction to Mixed-Signal, Embedded Design

# Introduction to Mixed-Signal, Embedded Design

### Introduction to Mixed-Signal, Embedded Design

### **Alex Doboli**

State University of New York Stony Brook, NY, USA

### **Edward H. Currie**

Hofstra University Hempstead, NY, USA

Alex Doboli Department of Electrical Engineering State University of New York Stony Brook, NY 11794, USA adoboli@ece.sunysb.edu Edward H. Currie Department of Computer Science Hofstra University Hempstead, NY 11549, USA edward.currie@hofstra.edu

A previous version of this book was published by The Cypress University Alliance in 2007

ISBN 978-1-4419-7445-7 e-ISBN 978-1-4419-7446-4 DOI 10.1007/978-1-4419-7446-4 Springer New York Dordrecht Heidelberg London

Library of Congress Control Number: 2010937588

Mathematics Subject Classification (2011): 94CXX, 94-04

©Springer Science+Business Media, LLC 2011

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media(www.springer.com)

# Contents

| $\mathbf{P}_{1}$ | refac | e                                                              | kix  |

|------------------|-------|----------------------------------------------------------------|------|

| Α                | ckno  | wledgment xx                                                   | ciii |

| 1                | An    | Overview of Mixed-Signal, Embedded System Design               | 1    |

|                  | 1.1   | Embedded Applications                                          | 2    |

|                  | 1.2   | Embedded Architectures                                         | 12   |

|                  | 1.3   | Top-Down Design Flow                                           | 19   |

|                  | 1.4   | Embedded Systems Market                                        | 23   |

|                  | 1.5   | Embedded Design Example: Fan Control System                    | 23   |

|                  |       | 1.5.1 Description of the Fan Controller System                 | 24   |

|                  |       | 1.5.2 Design of the Fan Controller System                      | 29   |

|                  | 1.6   | Conclusions                                                    | 42   |

|                  | 1.7   | Further Readings                                               | 43   |

|                  | 1.8   | Recommended Exercises                                          | 45   |

| <b>2</b>         | Mic   | crocontroller Architecture                                     | 51   |

|                  | 2.1   | Microcontroller Architecture                                   | 51   |

|                  |       | 2.1.1 Microcontroller Addressing Modes                         | 53   |

|                  |       | 2.1.2 Instruction Set                                          | 56   |

|                  | 2.2   | Memory Space                                                   | 91   |

|                  | 2.3   | Conclusions                                                    | 96   |

|                  | 2.4   | Recommended Exercises                                          | 98   |

| 3                | Har   | rdware and Software Subsystems of Mixed-Signal Architectures 1 | 03   |

|                  | 3.1   | Subsystems of the PSoC Mixed-Signal Architecture               | 04   |

|                  |       | 3.1.1 PSoC Hardware Components                                 | 106  |

|                  |       | 3.1.2 PSoC Software Components                                 | 10   |

|                  | 3.2   | The PSoC Interrupt Subsystem                                   | 114  |

|                  |       | 3.2.1 Case Study: Tachometer Interrupt Service Routines        | 117  |

|                  | 3.3   | Global I/O Ports                                               | 124  |

|                  | 3.4   | System Buses                                                   |      |

|                  | 3.5   | System Clocks                                                  | 43   |

|                  | 3.6   | Conclusions                                                    | 46   |

|                  | 3.7   | Recommended Exercises                                          | 49   |

| 4        | Per        | formance Improvement by Customization 151                                                                                              |

|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------|

|          | 4.1        | Introduction to Application-Specific Customization                                                                                     |

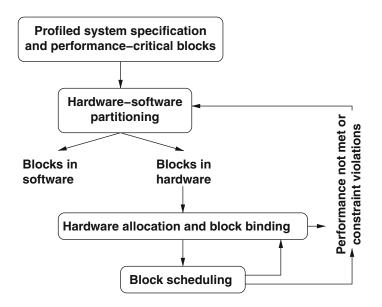

|          | 4.2        | Design Methodology for Architecture Customization                                                                                      |

|          |            | 4.2.1 System Specification and Profiling                                                                                               |

|          |            | 4.2.2 System Partitioning and Implementation                                                                                           |

|          | 4.3        | Programmable Digital Blocks                                                                                                            |

|          |            | 4.3.1 Timer Block                                                                                                                      |

|          |            | 4.3.2 Counter Block                                                                                                                    |

|          |            | 4.3.3 Deadband Block                                                                                                                   |

|          | 4.4        | Customized PSoC Digital Blocks                                                                                                         |

|          |            | 4.4.1 Pulse Width Modulator Blocks                                                                                                     |

|          |            | 4.4.2 Multiply ACcumulate                                                                                                              |

|          |            | 4.4.3 Decimator Blocks                                                                                                                 |

|          | 4.5        | Conclusions                                                                                                                            |

|          | 4.6        | Recommended Exercises                                                                                                                  |

|          |            |                                                                                                                                        |

| <b>5</b> | Pro        | grammable Data Communication Blocks 207                                                                                                |

|          | 5.1        | Abstract Communication Channels                                                                                                        |

|          | 5.2        | Channel Implementation Units                                                                                                           |

|          | 5.3        | Hardware–Software Implementation of Channels                                                                                           |

|          | 5.4        | Channel Implementation Unit: SPI Block                                                                                                 |

|          |            | 5.4.1 Hardware Circuit                                                                                                                 |

|          |            | 5.4.2 Software Routines                                                                                                                |

|          | 5.5        | Channel Implementation Unit: <b>UART</b> Block                                                                                         |

|          |            | 5.5.1 <b>UART</b> Hardware Circuit                                                                                                     |

|          |            | 5.5.2 Software Routines $\ldots \ldots 234$ |

|          | 5.6        | Conclusions                                                                                                                            |

|          | 5.7        | Recommended Exercises                                                                                                                  |

| 6        | Cor        | tinuous-Time, Analog Building Blocks 243                                                                                               |

| U        | 6.1        | Introduction to Operational Amplifiers                                                                                                 |

|          | 0.1        | 6.1.1 Ideal OpAmps                                                                                                                     |

|          |            | 6.1.2 Real OpAmps                                                                                                                      |

|          |            | 6.1.2    Real OpAmps    244      6.1.3    OpAmp Macromodeling    254                                                                   |

|          | 6.2        | Continuous-Time Analog Building Blocks                                                                                                 |

|          | 0.2        | 6.2.1 Inverting Amplifiers                                                                                                             |

|          |            | 6.2.1       Inverting Amplifier       203         6.2.2       Non-Inverting Amplifier       270                                        |

|          |            | 6.2.2       Non-Inverting Amplifier       270         6.2.3       Summing Amplifier       271                                          |

|          |            |                                                                                                                                        |

|          |            | 6.2.4 Difference Amplifier                                                                                                             |

|          |            | 6.2.5 Integrator                                                                                                                       |

|          | <i>c</i> 9 | $6.2.6  \text{Comparator}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                            |

|          | 6.3        | Reconfigurable Continuous-Time Analog Blocks                                                                                           |

|          | 6.4        | Conclusions                                                                                                                            |

|          | 6.5        | Recommended Exercises                                                                                                                  |

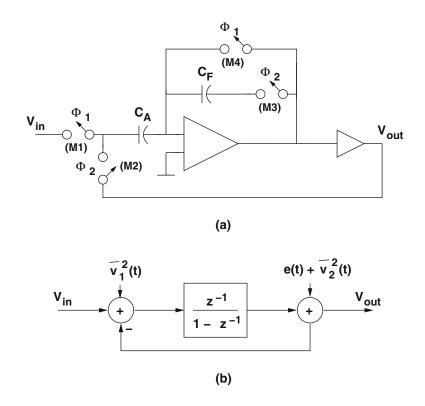

| 7        | Swi        | tched-Capacitor Blocks 289                                                                                                             |

|          | 7.1        | Introduction To Switched Capacitor Techniques                                                                                          |

|          |            | 7.1.1 Nonidealities in Switched Capacitor Circuits                                                                                     |

|          | 7.2        | Active Switched Capacitor Circuits                                                                                                     |

|          |            | 7.2.1   Fixed Gain Amplifier   295                                                                                                     |

|          |            | · · · · · · · · · · · · · · · · · · ·                                                                                                  |

|   |                | 7.2.2             | Comparators                                                                                                          |

|---|----------------|-------------------|----------------------------------------------------------------------------------------------------------------------|

|   |                | 7.2.3             | Switched Capacitor Integrator                                                                                        |

|   |                | 7.2.4             | Switched Capacitor Differentiator                                                                                    |

|   |                | 7.2.5             | Reference Selection                                                                                                  |

|   |                | 7.2.6             | Analog-to-Digital Conversion                                                                                         |

|   | 7.3            | Switch            | ed Capacitor PSoC Blocks                                                                                             |

|   |                | 7.3.1             | Type C Switched Capacitor Blocks                                                                                     |

|   |                | 7.3.2             | Type D Switched Capacitor Blocks                                                                                     |

|   | 7.4            | Conclu            | sions                                                                                                                |

|   | 7.5            | Recom             | mended Exercises                                                                                                     |

|   |                |                   |                                                                                                                      |

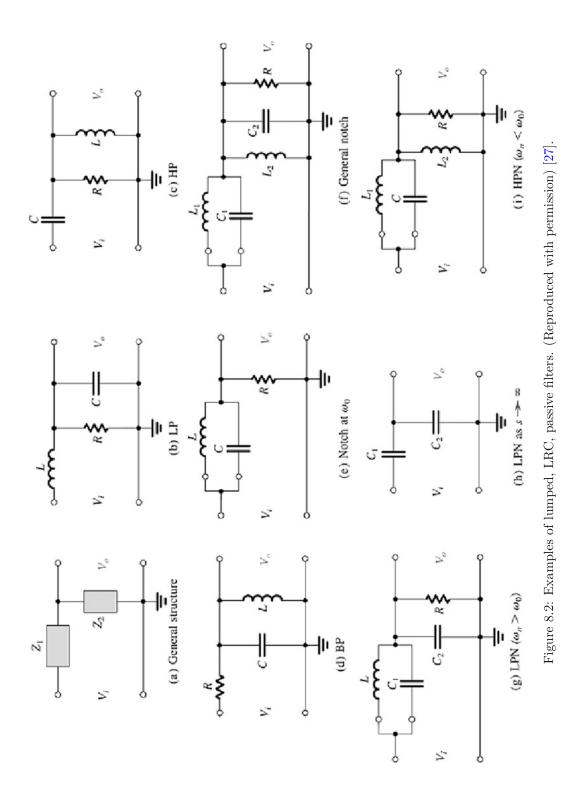

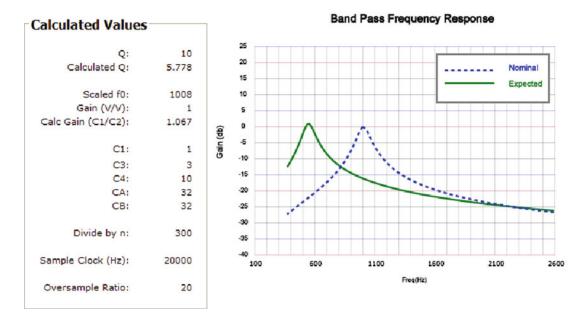

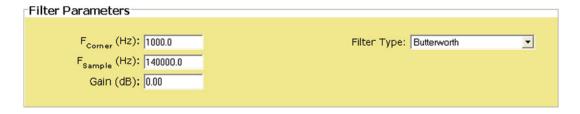

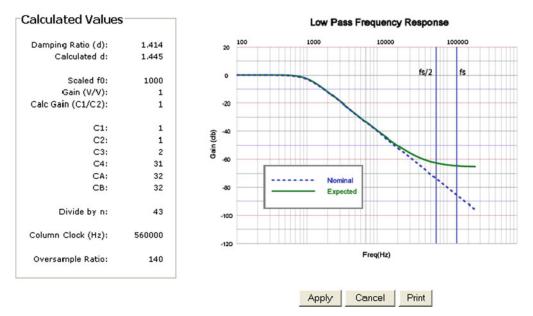

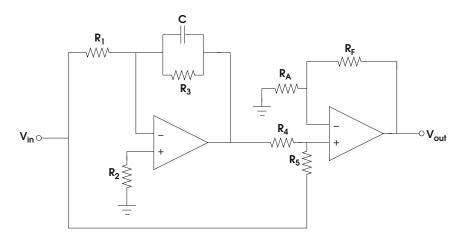

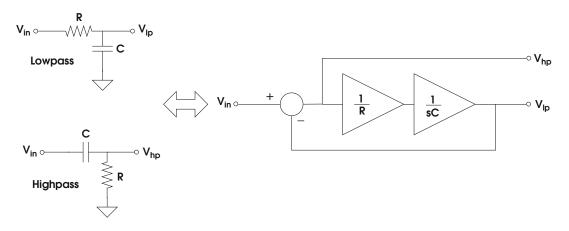

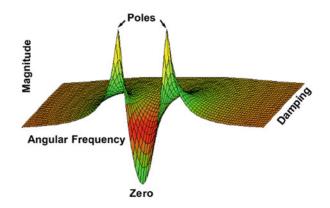

| 8 | Ana            | -                 | d Digital Filters 325                                                                                                |

|   | 8.1            | Filter I          | Fundamentals $\ldots \ldots 326$ |

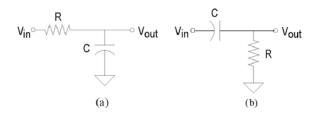

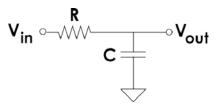

|   |                | 8.1.1             | Passive Filters                                                                                                      |

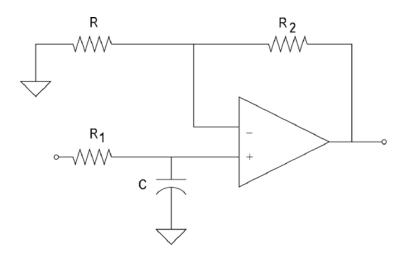

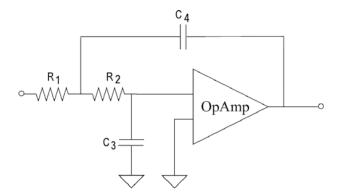

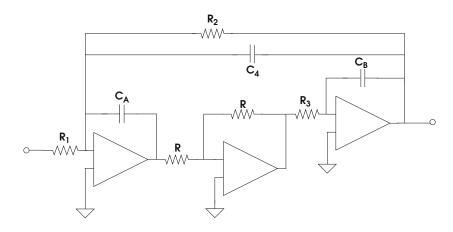

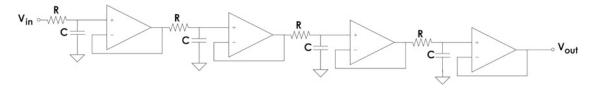

|   |                | 8.1.2             | Linear Active Filters                                                                                                |

|   |                | 8.1.3             | Digital Filters                                                                                                      |

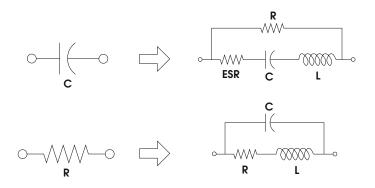

|   |                | 8.1.4             | Filter Components                                                                                                    |

|   | 8.2            | Filter I          | Design $\ldots$ $\ldots$ $\ldots$ $\ldots$ $332$                                                                     |

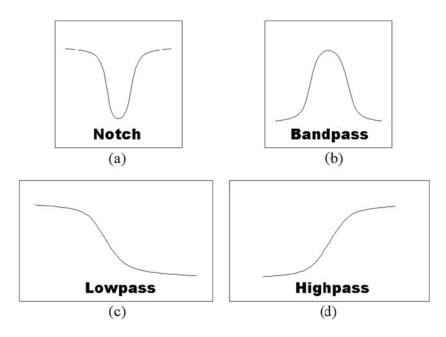

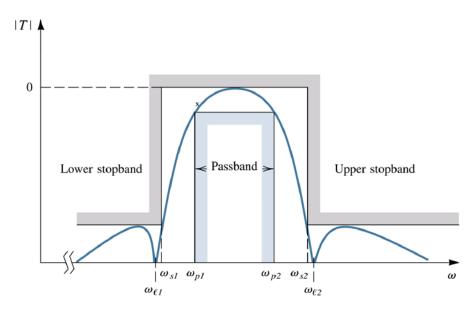

|   |                | 8.2.1             | Specific Filter Types                                                                                                |

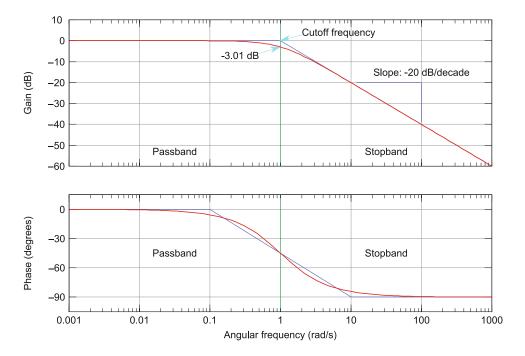

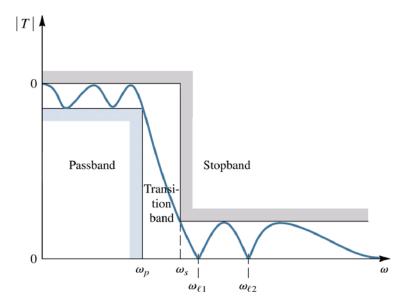

|   |                | 8.2.2             | Filter Parameters                                                                                                    |

|   |                | 8.2.3             | Scaling and Normalization                                                                                            |

|   |                | 8.2.4             | Cascading Analog Filters                                                                                             |

|   | 8.3            | Analog            | ; Filters                                                                                                            |

|   |                | 8.3.1             | Time-Continuous Integrators as Filters                                                                               |

|   |                | 8.3.2             | The Passive Lowpass Filter                                                                                           |

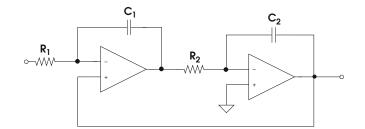

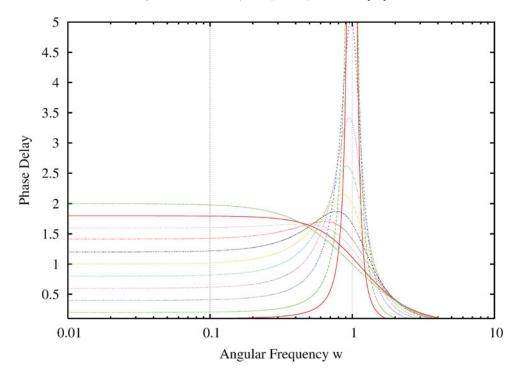

|   |                | 8.3.3             | The Sallen–Key Lowpass Active Filter                                                                                 |

|   |                | 8.3.4             | The Switched-Capacitance Filter                                                                                      |

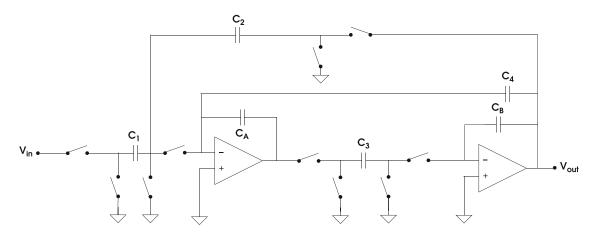

|   |                | 8.3.5             | Biquad Switched Capacitor Filter                                                                                     |

|   |                | 8.3.6             | An Allpass Filter                                                                                                    |

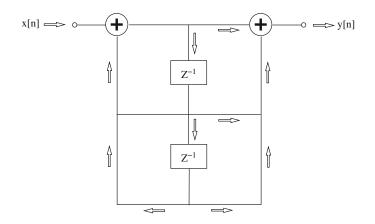

|   | 8.4            | Digital           | Filters                                                                                                              |

|   |                | 8.4.1             | Digital FIR Filter                                                                                                   |

|   |                | 8.4.2             | Infinite Impulse Response Filter                                                                                     |

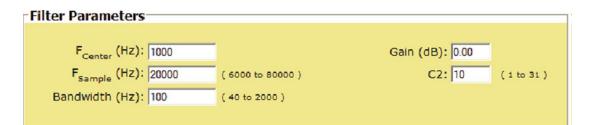

|   | 8.5            | Filter 1          | Design Software Tools                                                                                                |

|   | 8.6            | Conclu            | sion                                                                                                                 |

|   | 8.7            | Recom             | mended Exercises                                                                                                     |

|   |                |                   |                                                                                                                      |

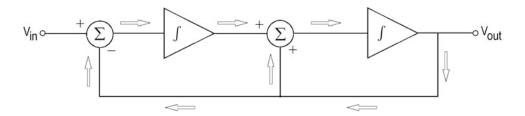

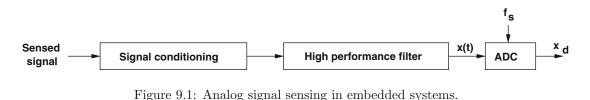

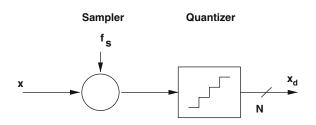

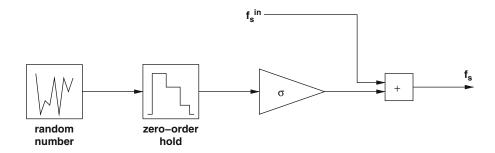

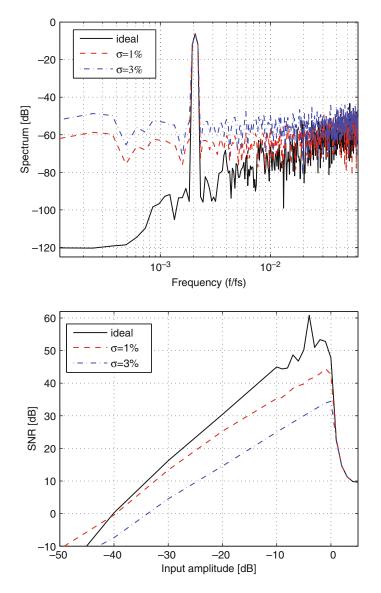

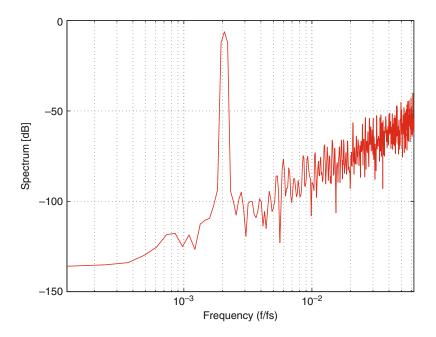

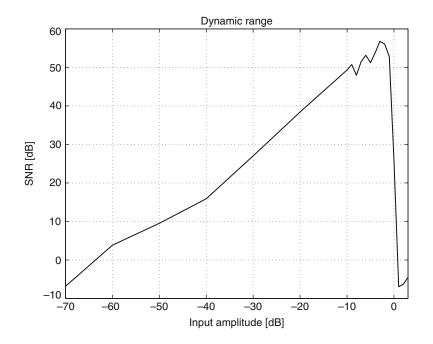

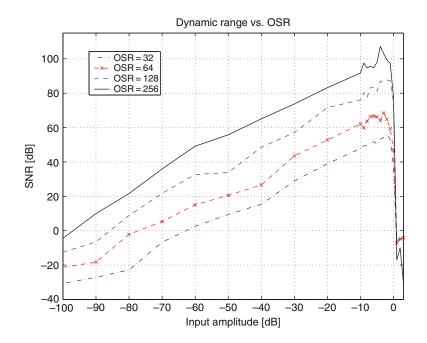

| 9 | $\Delta\Sigma$ |                   | g-to-Digital Converters 373                                                                                          |

|   | 9.1            | Nyquis            | t ADCs-A Short Introduction                                                                                          |

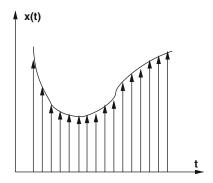

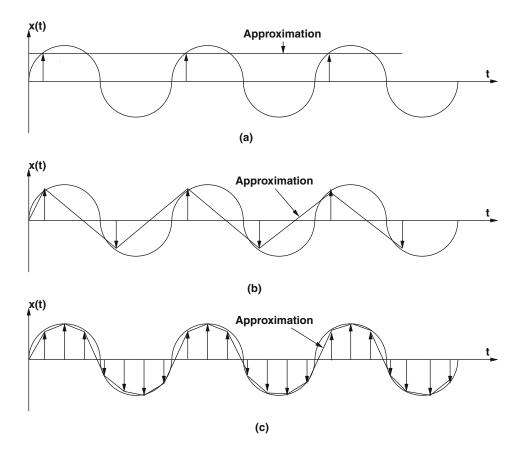

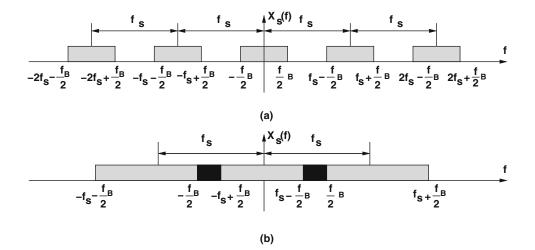

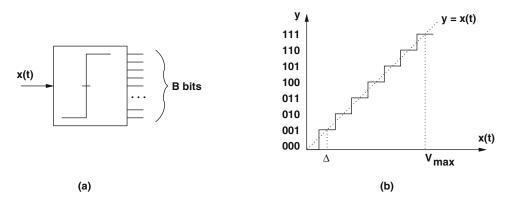

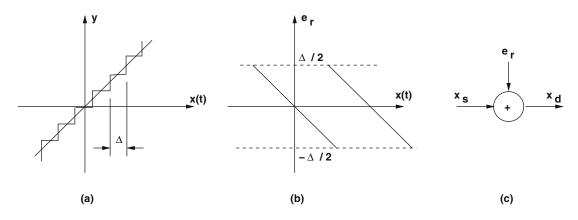

|   |                | 9.1.1             | Sampling and Quantization                                                                                            |

|   |                | 9.1.2             | Sampling                                                                                                             |

|   |                | 9.1.3             | Quantization                                                                                                         |

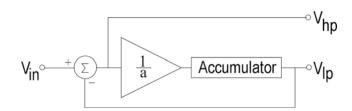

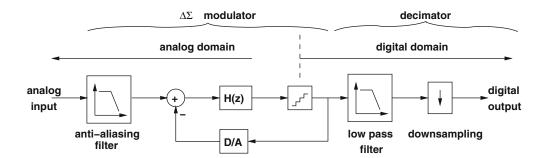

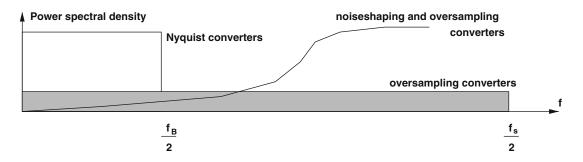

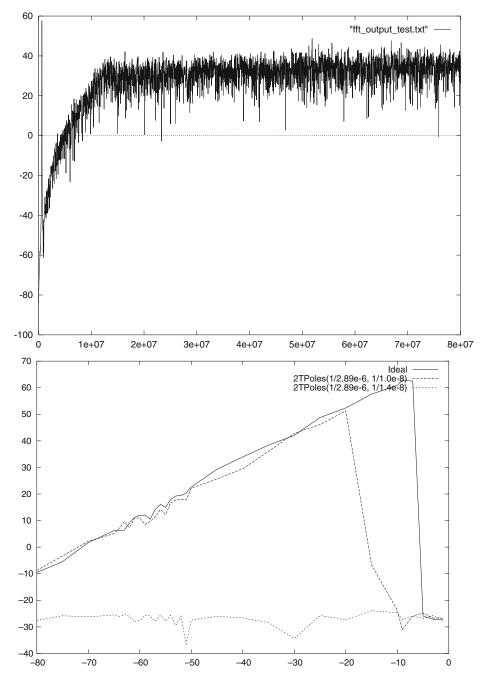

|   | 9.2            | $\Delta\Sigma AI$ | DCs                                                                                                                  |

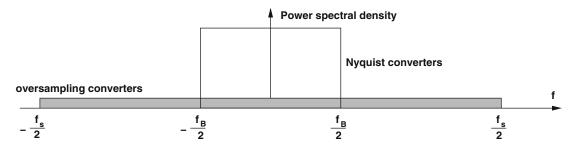

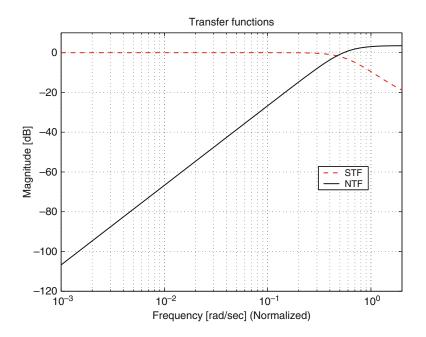

|   |                | 9.2.1             | Oversampling and Noise-Shaping                                                                                       |

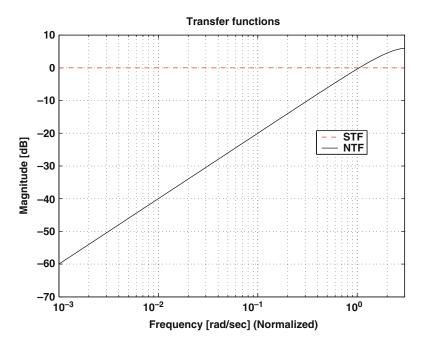

|   |                | 9.2.2             | $\Delta\Sigma$ ADC Performance                                                                                       |

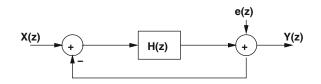

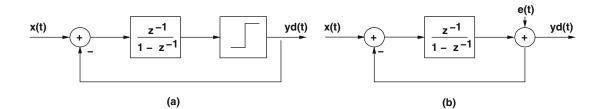

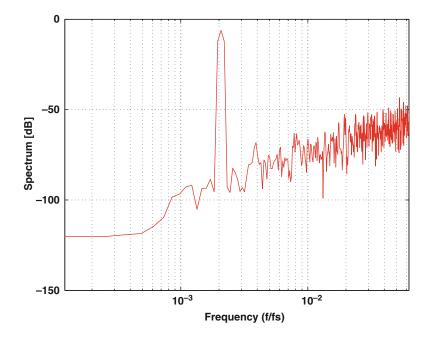

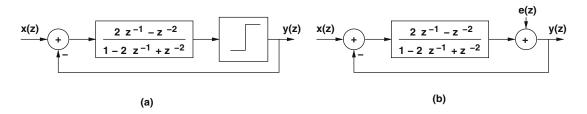

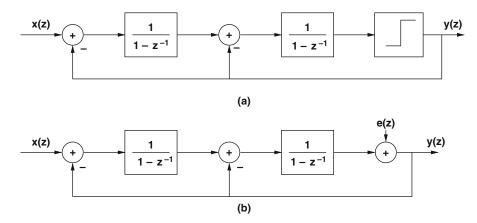

|   |                | 9.2.3             | First-Order $\Delta\Sigma$ Modulator                                                                                 |

|   |                | 9.2.4             | PSoC Implementation of First-Order $\Delta\Sigma$ Modulators                                                         |

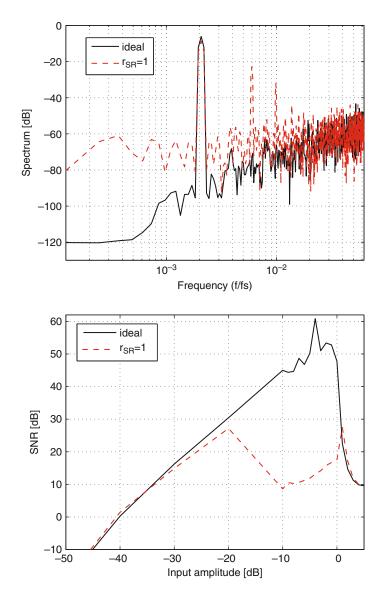

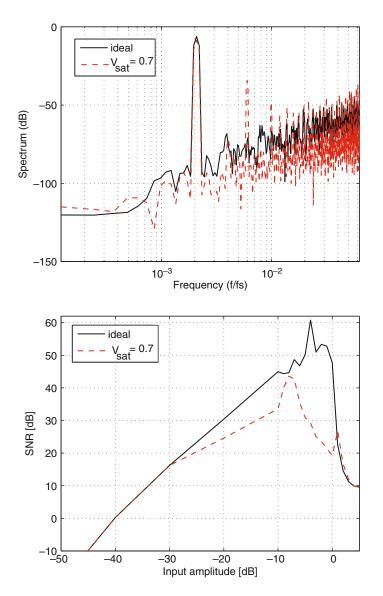

|   |                | 9.2.5             | Impact of Circuit Non-Idealities on $\Delta\Sigma$ Modulator Performance 394                                         |

|   |                | 9.2.6             | Second-Order $\Delta\Sigma$ Modulator                                                                                |

|   | 9.3            | Conclu            | sions                                                                                                                |

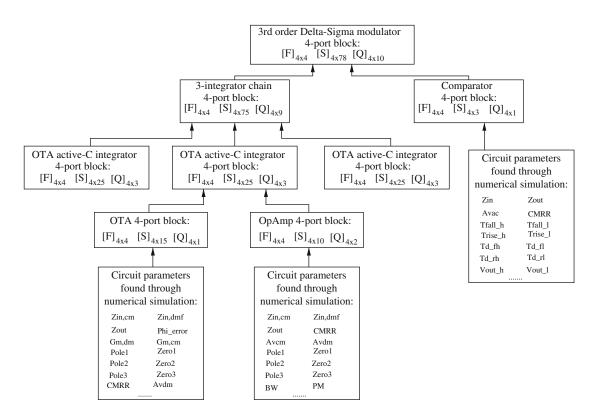

| 10 Future Directions in Mixed-Signal Design Automation 4             | 13 |

|----------------------------------------------------------------------|----|

| 10.1 Top-Down Design and Design Activities                           | 13 |

| 10.2 Two Examples of Architecture Customization                      | 15 |

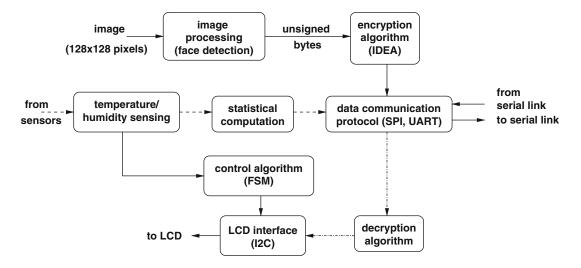

| 10.2.1 IDEA Algorithm for Data Encryption                            | 15 |

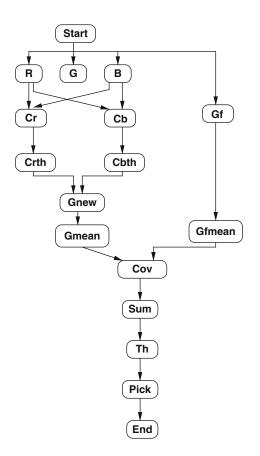

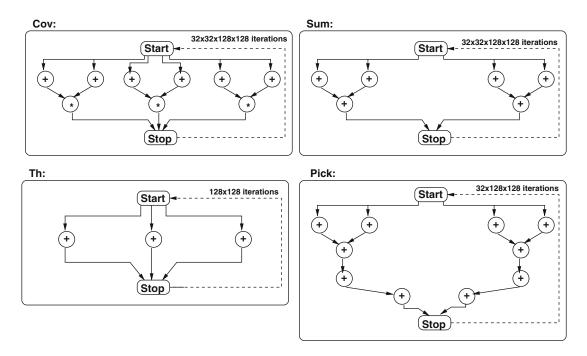

| 10.2.2 Face Detection for Image Processing                           | 17 |

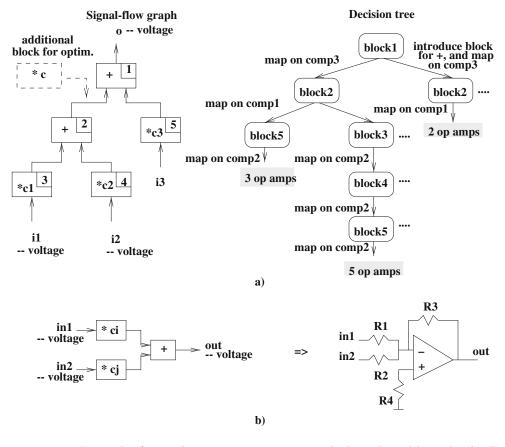

| 10.3 Challenges in Mixed-Signal Design Automation                    | 21 |

| 10.3.1 High-Level Specification of Analog and Mixed-Signal Systems 4 | 22 |

| 10.3.2 Fast Performance Estimation by Customized Simulation Code 4   | 24 |

| 10.3.3 High-Level Synthesis of Analog Subsystems                     | 35 |

| Index 4                                                              | 43 |

# List of Figures

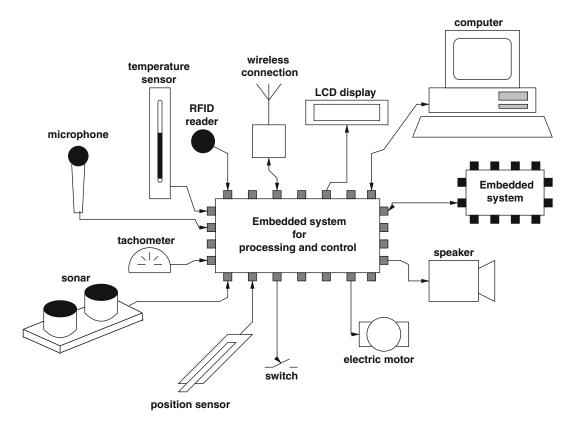

| Popular sensing and actuation devices in embedded applications                   | 3                                                              |

|----------------------------------------------------------------------------------|----------------------------------------------------------------|

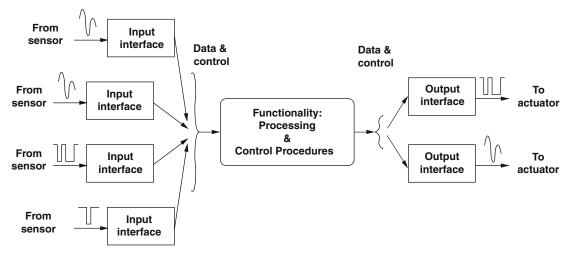

| Dataflow and structure of embedded systems.                                      | 4                                                              |

| Analog input interfaces in embedded systems.                                     | 4                                                              |

| Digital input interfaces in embedded systems.                                    | 5                                                              |

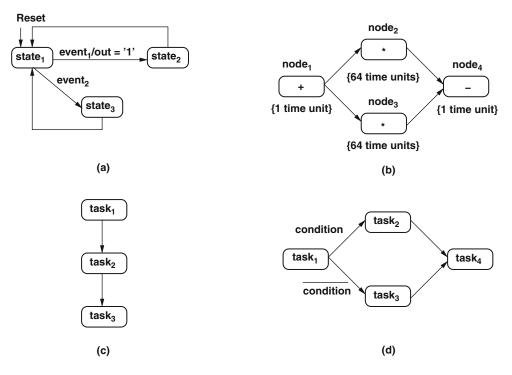

| Functionality types for embedded systems.                                        | 7                                                              |

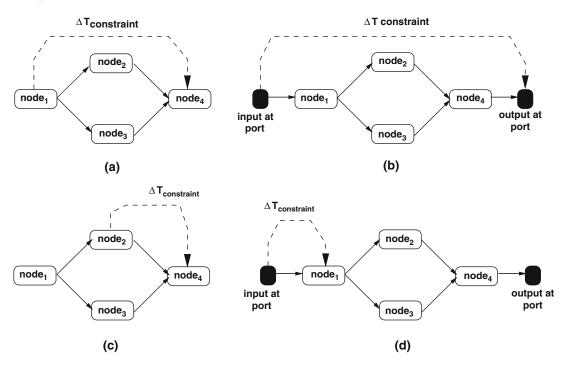

| Real-time constraints in embedded systems.                                       | 9                                                              |

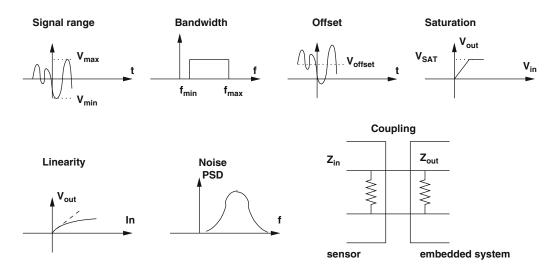

| Signal properties and nonidealities in analog circuits.                          | 10                                                             |

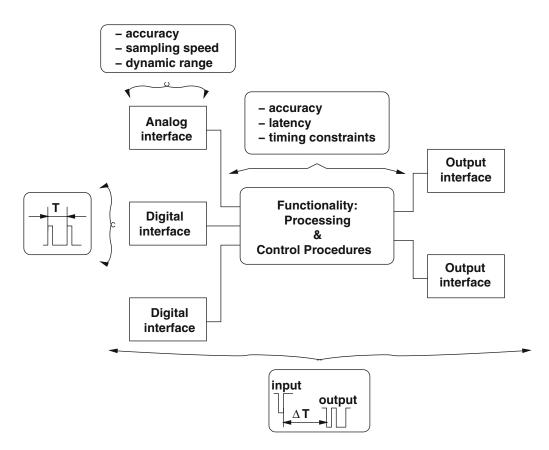

| Embedded systems design and performance requirements                             | 11                                                             |

|                                                                                  | 13                                                             |

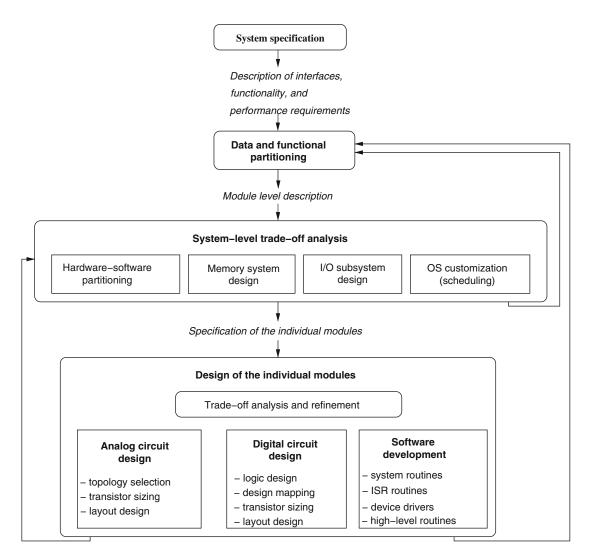

| Top-down embedded system design flow.                                            | 20                                                             |

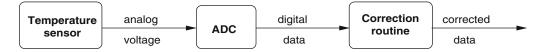

| Linear signal-processing flow.                                                   | 24                                                             |

|                                                                                  | 25                                                             |

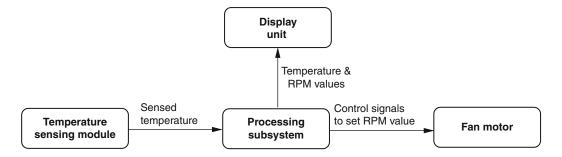

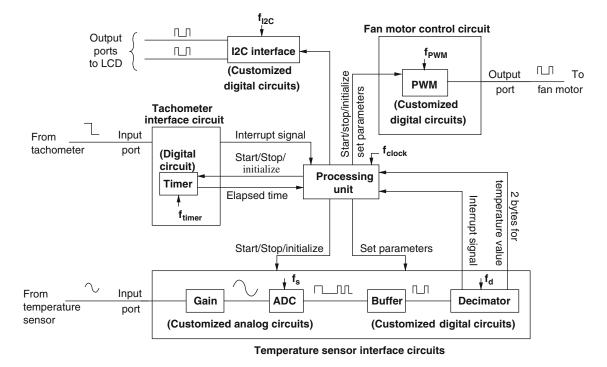

| Block structure for the embedded fan control system (concept-level description). | 25                                                             |

| Temperature reading procedure.                                                   | 26                                                             |

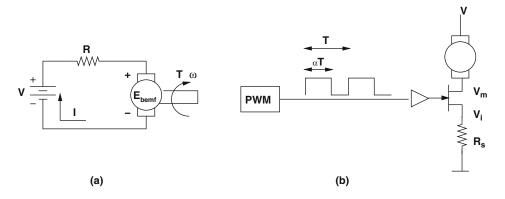

| DC motor model and operation.                                                    | 27                                                             |

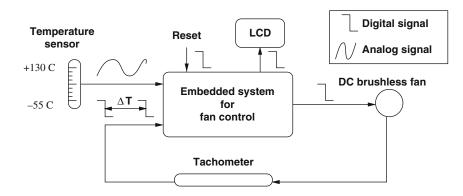

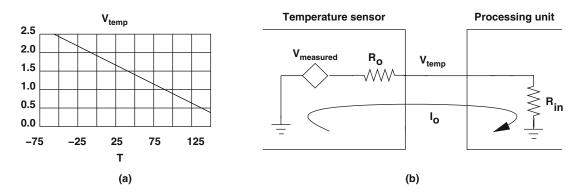

| Temperature sensor                                                               | 28                                                             |

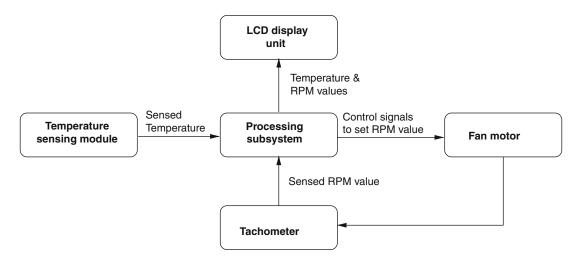

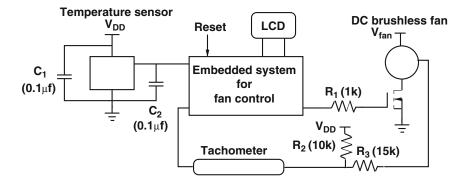

| Interfaced fan controller system (concept-level description)                     | 29                                                             |

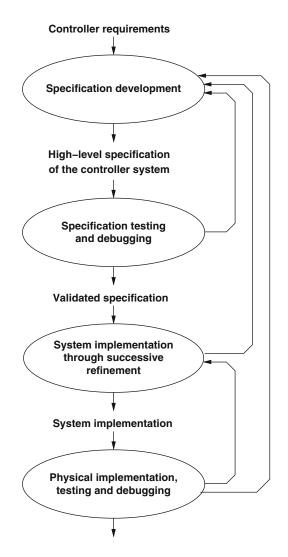

| Design flow for the embedded fan controller.                                     | 31                                                             |

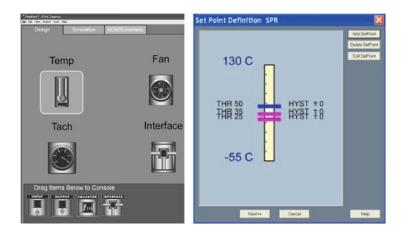

| Fan controller I/O specification (PSoC Express)                                  | 32                                                             |

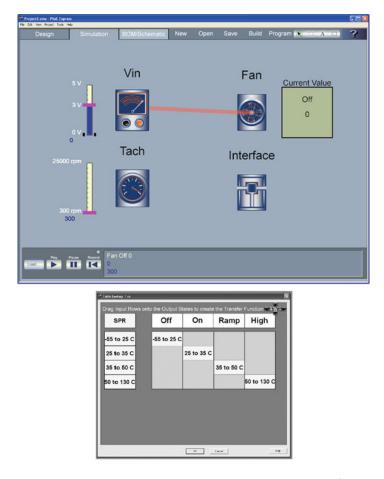

| System structure and table lookup transfer function (PSoC Express)               | 33                                                             |

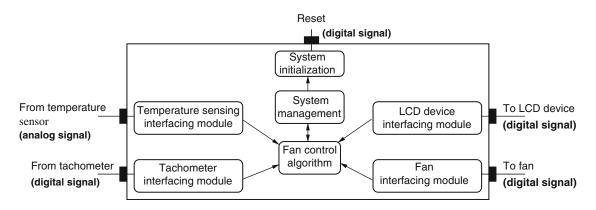

| Block-level design after functional partitioning.                                | 35                                                             |

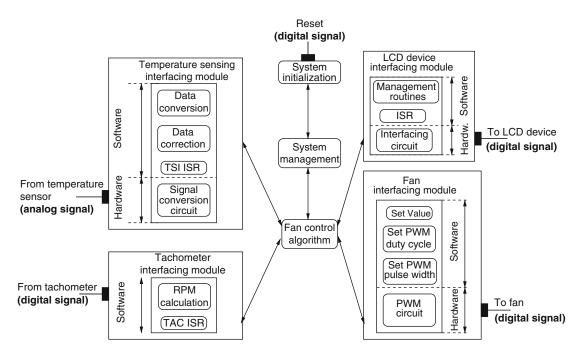

| Refined block-level design after domain selection.                               | 36                                                             |

| Circuit level implementation after domain selection.                             | 38                                                             |

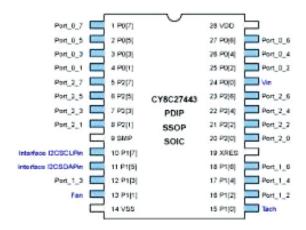

| PSoC implementation (after circuit implementation and software development).     | 39                                                             |

| Implementation I/O pins                                                          | 40                                                             |

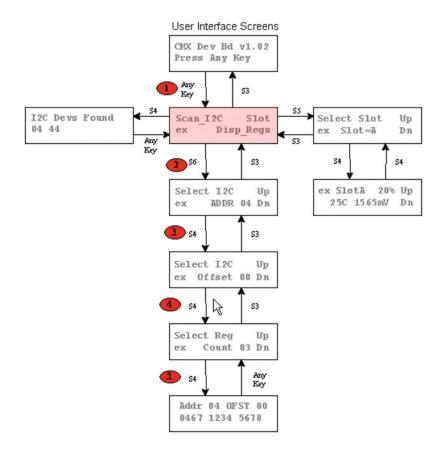

| LCD device operation for monitoring and debugging.                               | 41                                                             |

| Fan controller monitoring using HyperTerminal                                    | 41                                                             |

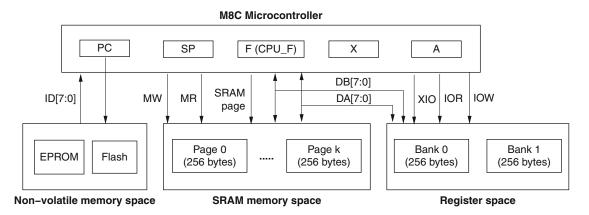

| The M8C microcontroller structure.                                               | 52                                                             |

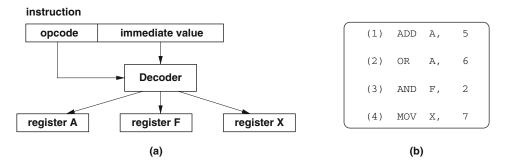

| Source-immediate addressing mode.                                                | 53                                                             |

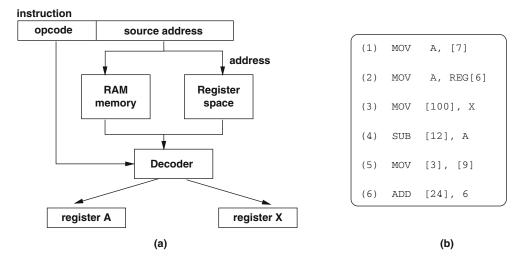

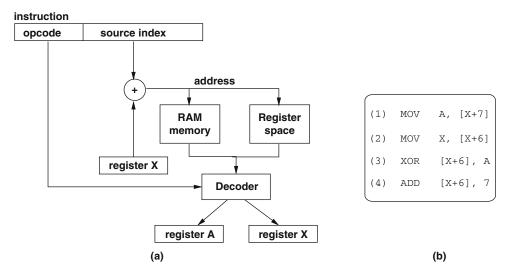

| Source-direct and destination-direct addressing modes.                           | 54                                                             |

|                                                                                  |                                                                |

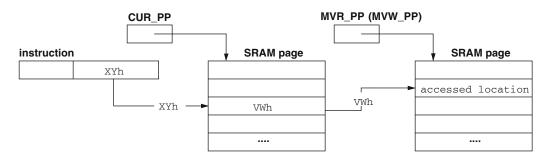

| MVI instructions.                                                                | 59                                                             |

|                                                                                  |                                                                |

|                                                                                  |                                                                |

|                                                                                  |                                                                |

|                                                                                  |                                                                |

|                                                                                  |                                                                |

|                                                                                  | Popular sensing and actuation devices in embedded applications |

| 2.11         | Assembly code for multiplication.                                            |     |

|--------------|------------------------------------------------------------------------------|-----|

| 2.12         | Bit manipulations.                                                           |     |

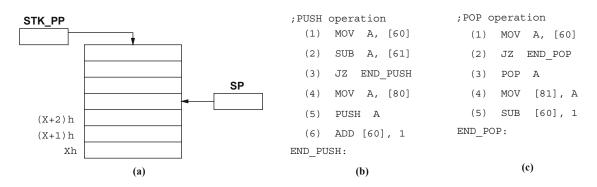

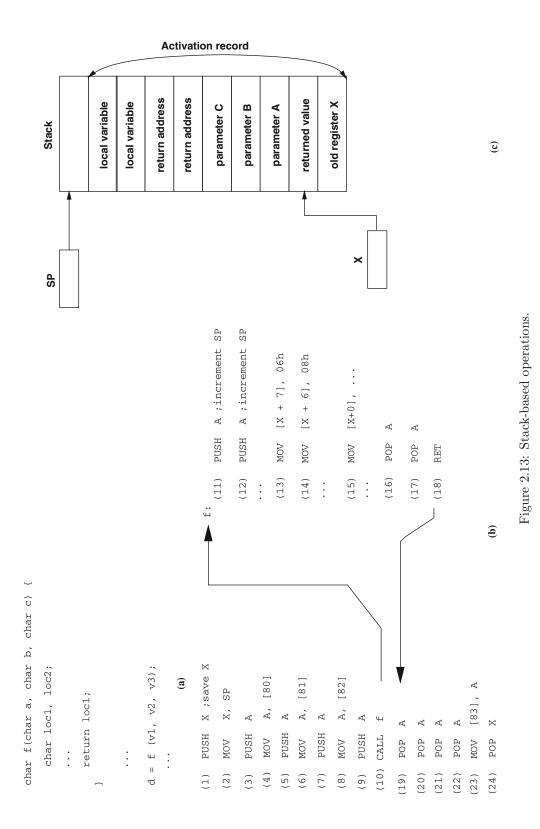

| 2.13         | Stack-based operations.                                                      | 84  |

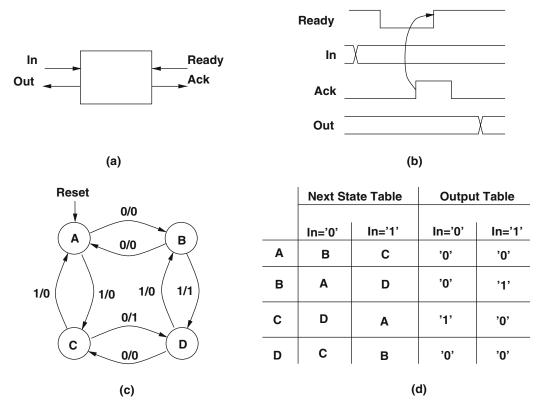

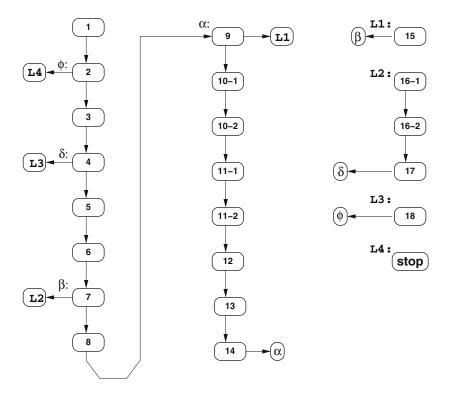

| 2.14         | Sequence detector.                                                           | 86  |

| 2.15         | Sequence detector design.                                                    | 87  |

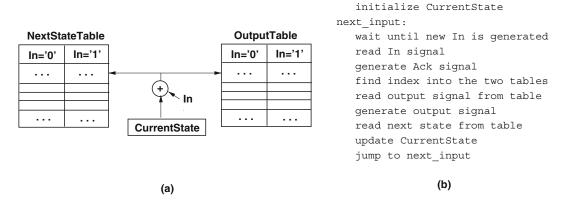

| 2.16         | Sequence detector implementation using INDEX instructions                    |     |

| 2.17         | RAM-based sequence detector implementation                                   |     |

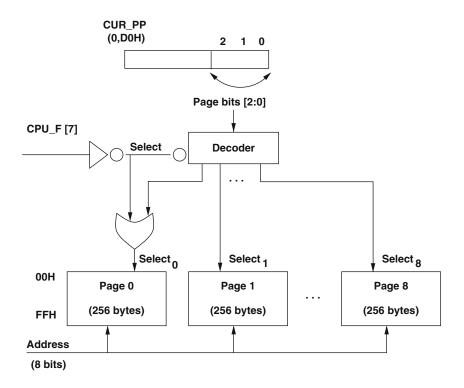

| 2.18         | Paged SRAM space.                                                            |     |

| 2.19         | ReadBlock and WriteBlock SROM functions                                      |     |

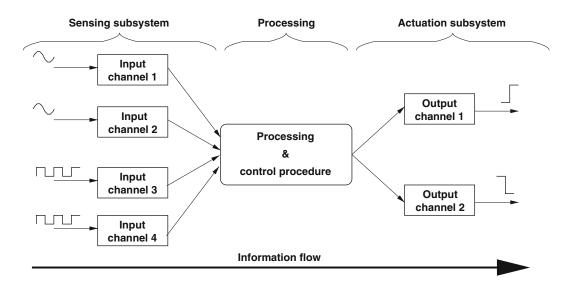

| 3.1          | Sense-process and control-actuate flow in embedded applications              | 104 |

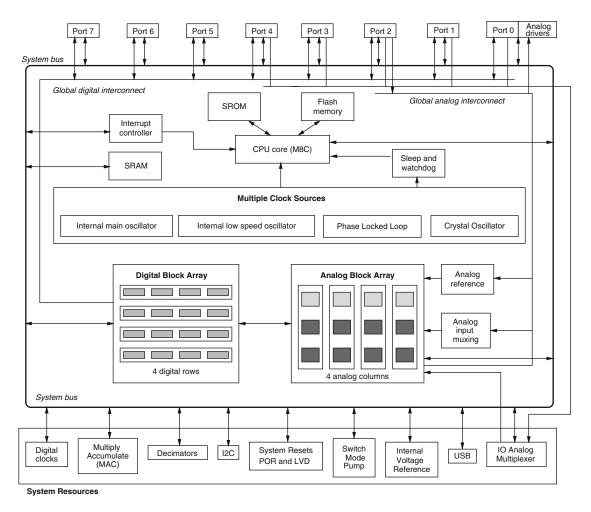

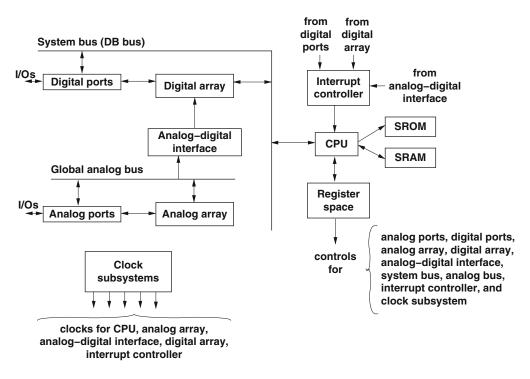

| 3.1<br>3.2   | Subsystems of the PSoC architecture                                          | 104 |

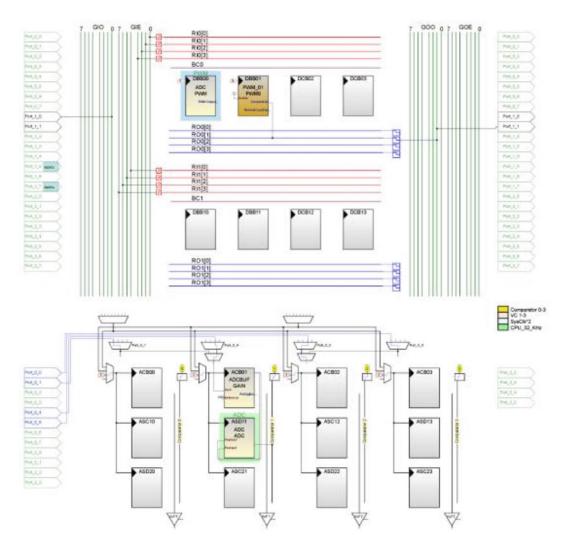

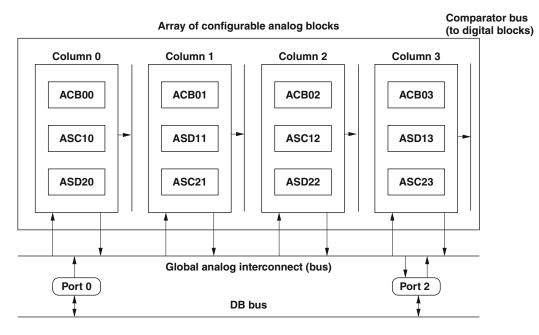

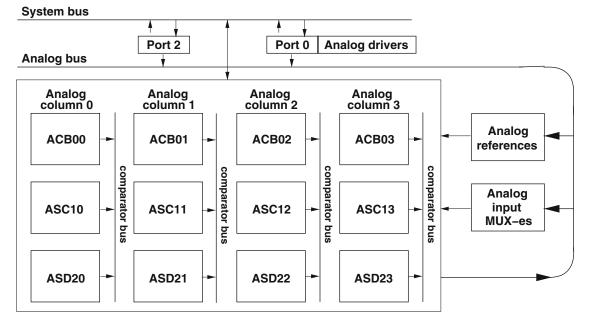

| 3.2<br>3.3   | Matrix of programmable analog blocks.                                        |     |

|              |                                                                              |     |

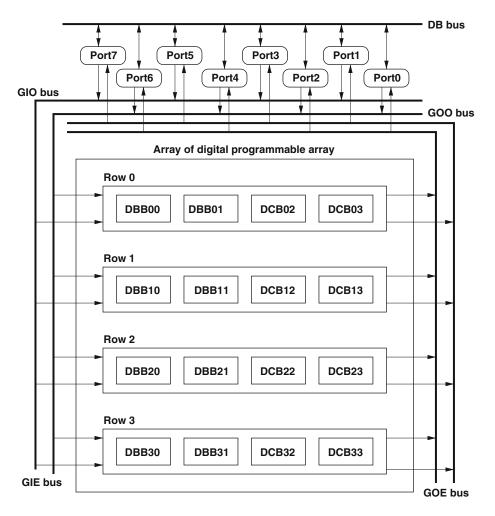

| 3.4          | Matrix of programmable digital blocks.                                       |     |

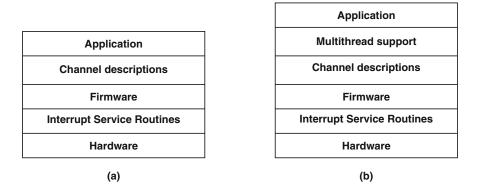

| 3.5          | (a) Boot program and (b) application routine.                                |     |

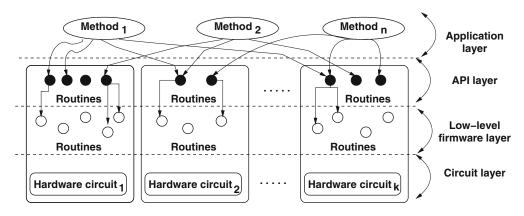

| 3.6          | Hierarchy of abstraction levels in a mixed-signal architecture.              |     |

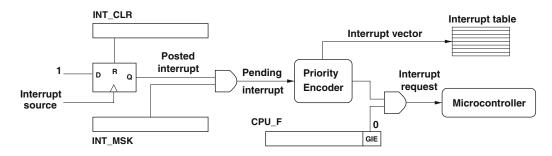

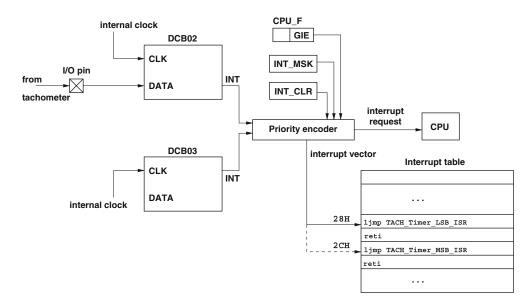

| 3.7          | Interrupt system.                                                            |     |

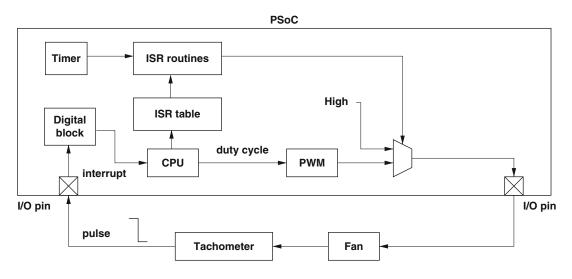

| 3.8          | Tachometer interfacing to PSoC                                               |     |

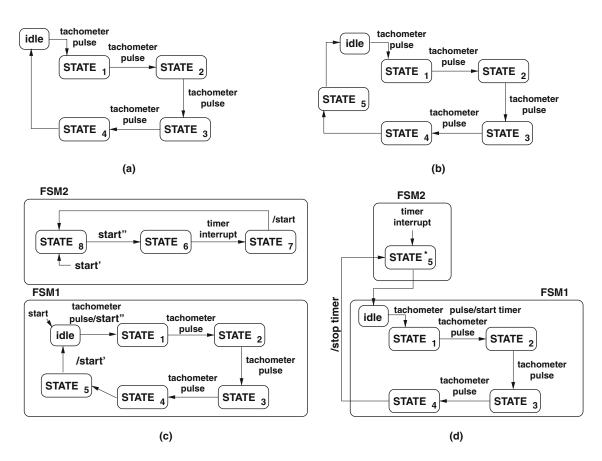

| 3.9          | Specification of the tachometer ISR.                                         |     |

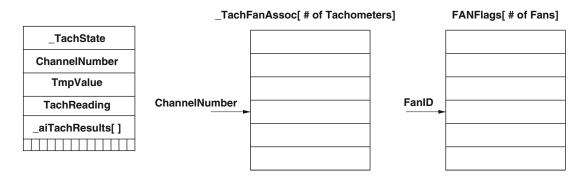

| 3.10         | Data structure for handling multiple tachometers.                            |     |

| 3.11         | Pseudocode of the FSM1 ISR.                                                  |     |

| 3.12         | Pseudocode of the FSM2 ISR.                                                  |     |

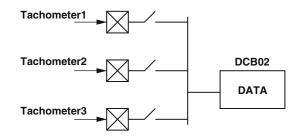

| 3.13         | Connecting multiple tachometers to PSoC.                                     |     |

| 3.14         | Hardware and software components implementing the tachometer ISR             |     |

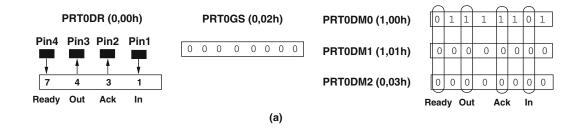

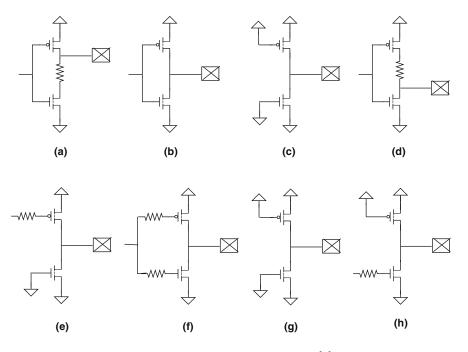

| 3.15         | Port driving modes                                                           |     |

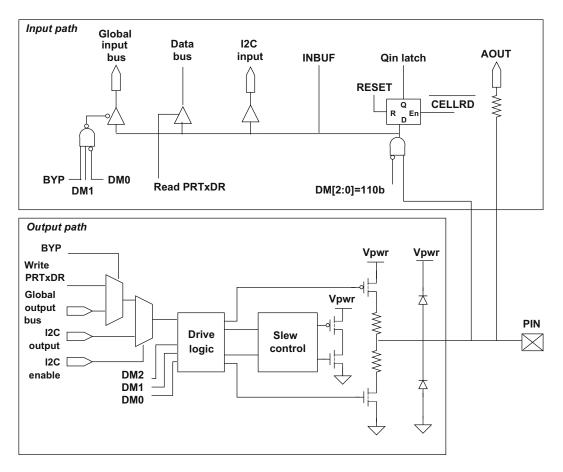

| 3.16         | GPIO block structure.                                                        |     |

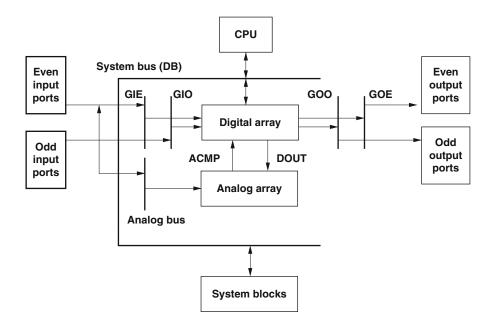

| 3.17         | PSoC system buses                                                            |     |

| 3.18         | Bus connections to the I/O ports                                             |     |

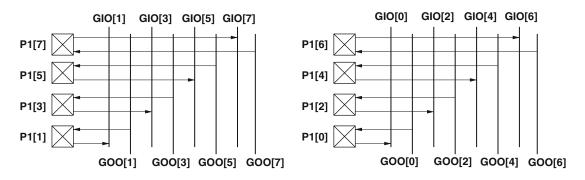

| 3.19         | Bus connections to the I/O ports                                             |     |

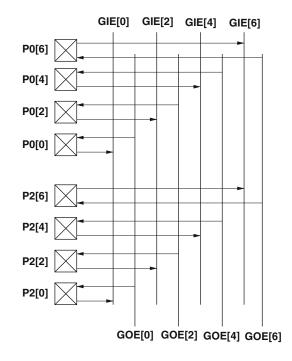

| 3.20         | Direct connection of buses GIx and buses GOx.                                |     |

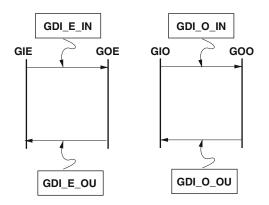

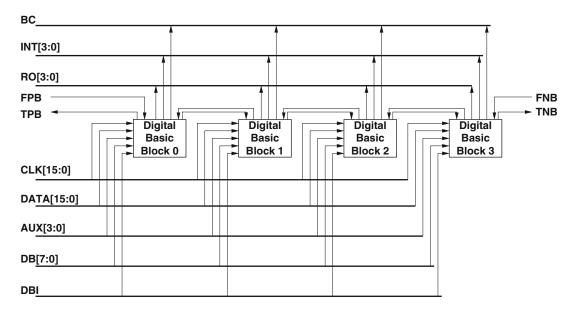

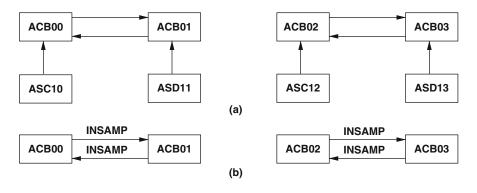

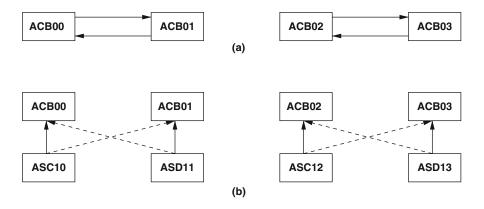

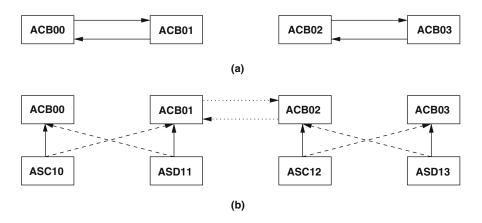

| 3.21         | Array digital interconnect.                                                  |     |

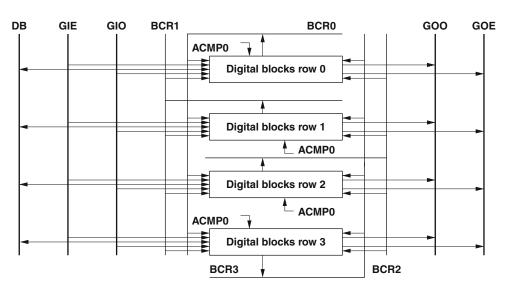

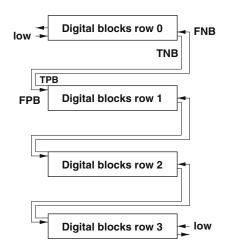

| 3.22         | Structure of the row digital interconnect.                                   |     |

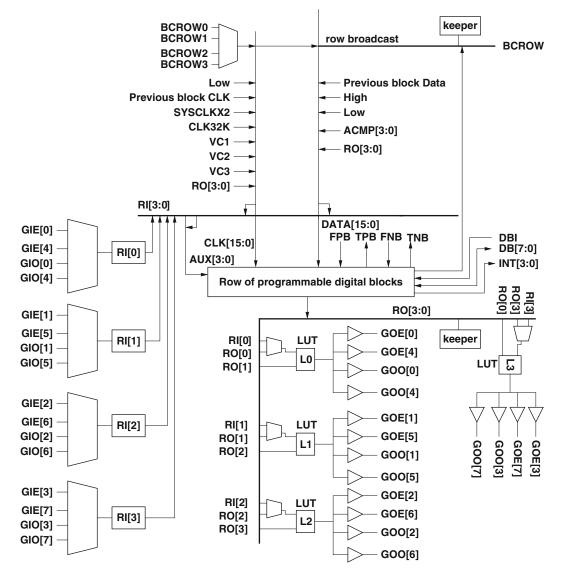

| 3.23         | Row digital interconnect.                                                    |     |

| 3.24         | Chaining of the programmable digital blocks.                                 | 135 |

| 3.25         | Control registers for programming row digital interconnect                   |     |

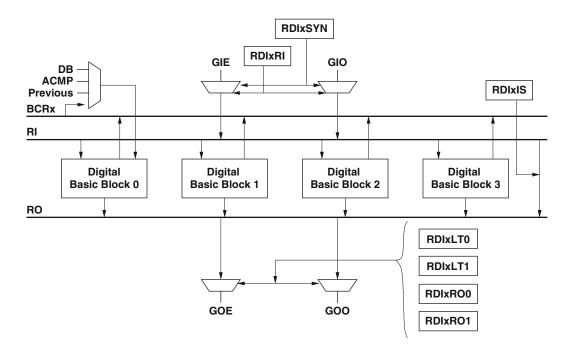

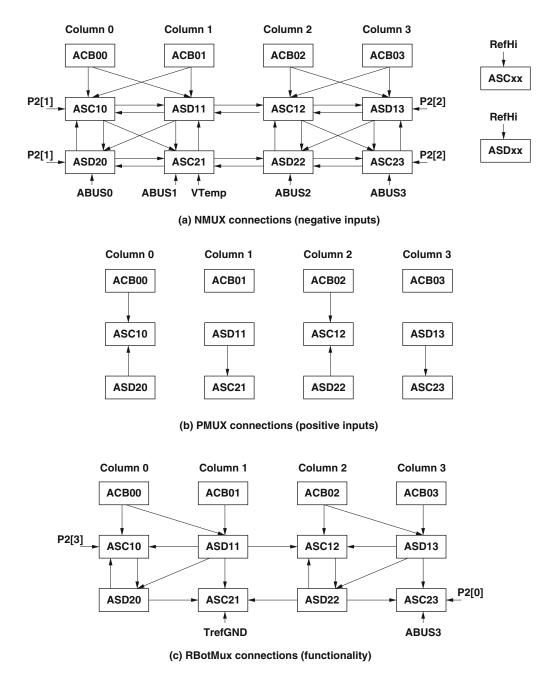

| 3.26         | Local programmable interconnect for the continuous-time analog blocks        | 139 |

| 3.27         | Local programmable interconnect for the switched capacitor analog blocks     |     |

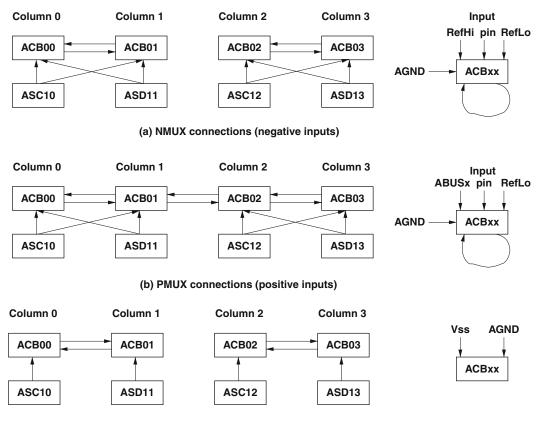

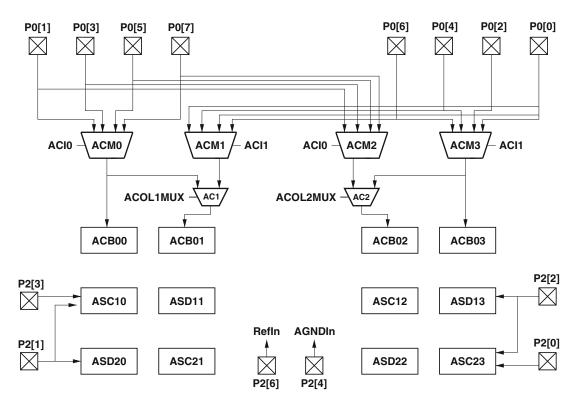

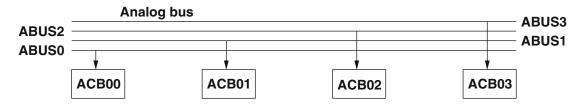

| 3.28         | Input port connections for the programmable analog blocks                    | 141 |

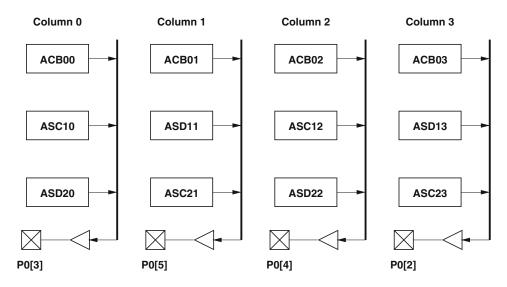

| 3.29         | Output port connections for the programmable analog blocks                   | 142 |

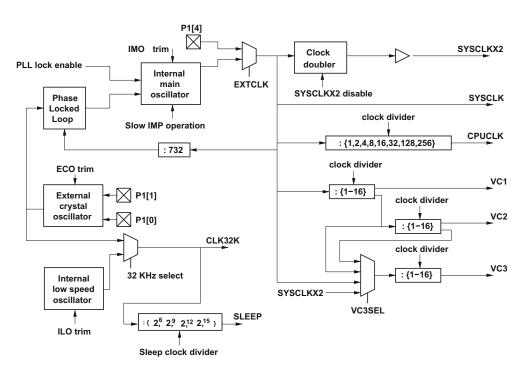

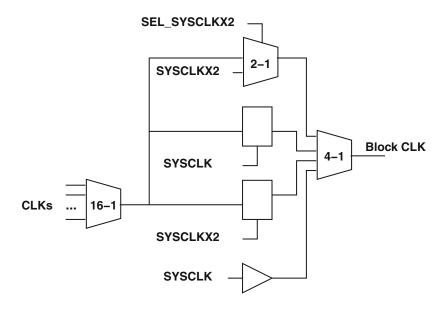

| 3.30         | PSoC system clocks                                                           | 143 |

| 4.1          | Hardware module implementation for reusability.                              | 153 |

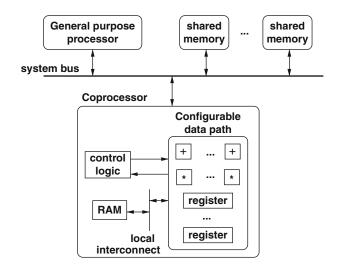

| 4.2          | Design flow for architectures with single processor and shared coprocessors. |     |

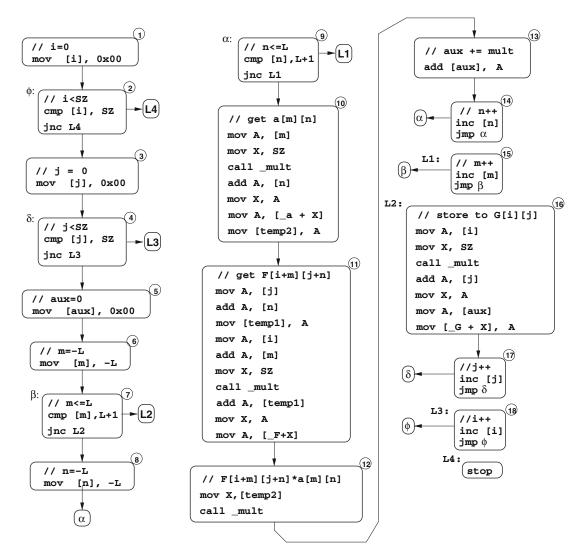

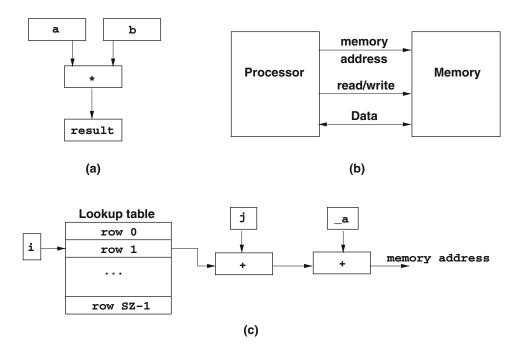

| 4.2          | Example of a data processing intensive application.                          |     |

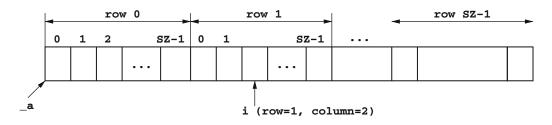

| 4.3<br>4.4   | Organization of arrays in the memory.                                        |     |

| $4.4 \\ 4.5$ | Block structure of the system specification.                                 |     |

| 4.5<br>4.6   |                                                                              |     |

|              | Refined block structure of the system specification                          |     |

| 4.7          | Generic architecture consisting of processor and shared coprocessor          |     |

| 4.8          | Customized hardware circuits for the performance-critical blocks             |     |

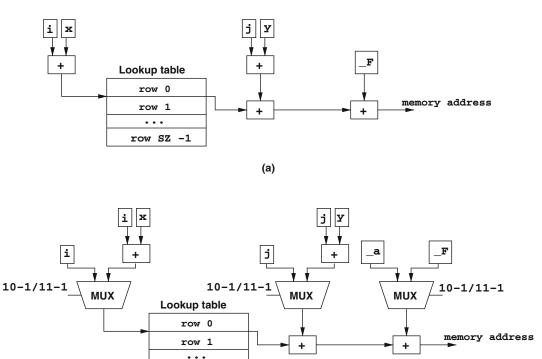

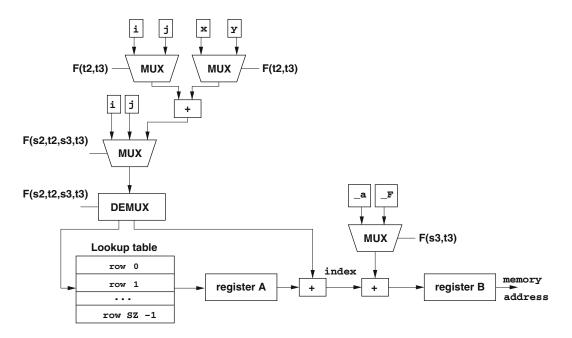

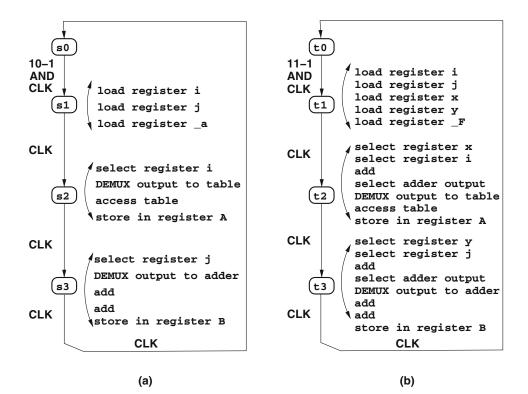

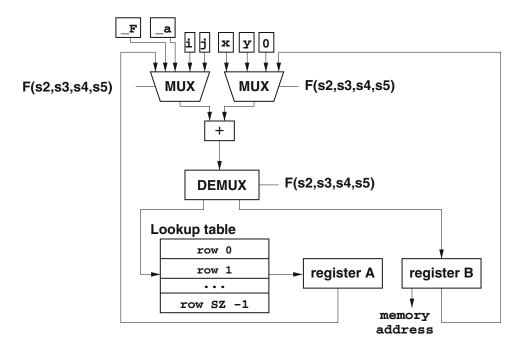

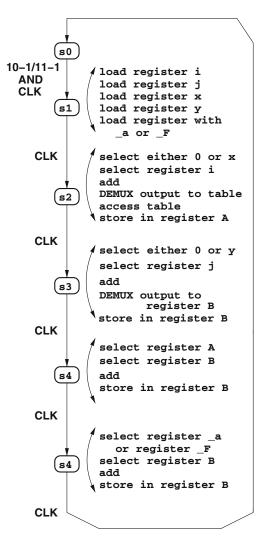

| 4.9          | Customized hardware circuits for Blocks 10-1 and 11-1                        | 105 |

| 4.10         | Data path for Blocks 10-1 and 11-1.                            | . 166 |

|--------------|----------------------------------------------------------------|-------|

| 4.11         | Controller circuits for Blocks 10-1 and 11-1.                  | . 166 |

| 4.12         | Data path for Blocks 10-1 and 11-1.                            | . 167 |

| 4.13         | Controller for Blocks 10-1 and 11-1.                           | . 169 |

| 4.14         | Modified data processing algorithm.                            | . 169 |

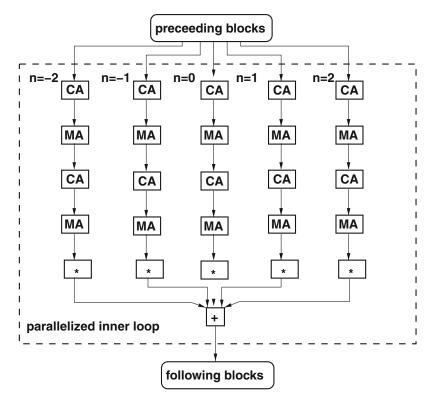

| 4.15         | Inner loop parallelization for the modified algorithm.         |       |

| 4.16         | Operation scheduling for different hardware resource sets      |       |

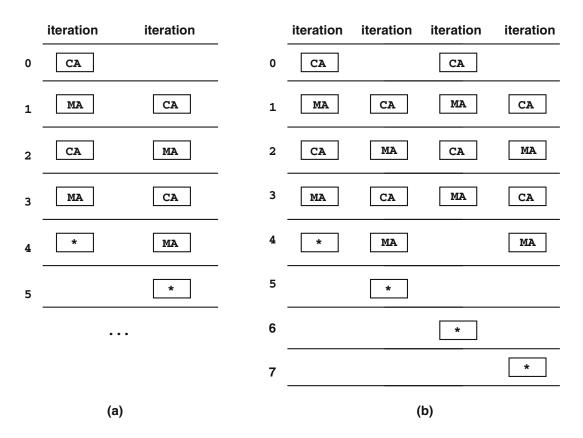

| 4.17         | PSoC's array of programmable digital blocks PSoC.              |       |

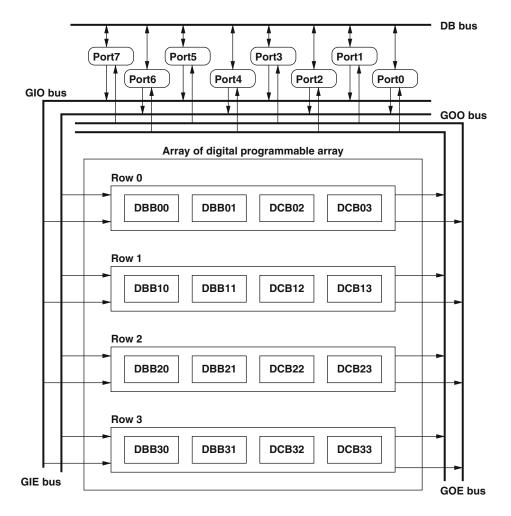

| 4.18         | Programmable digital block.                                    |       |

| 4.19         | Programmable clocks of the digital blocks.                     |       |

| 4.20         | Input and output configuration.                                |       |

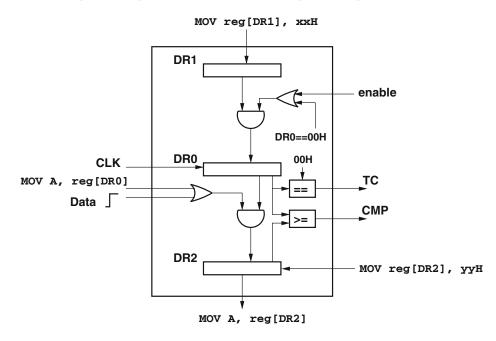

| 4.21         | Dataflow of the timer block.                                   |       |

| 4.22         | Main timer function and the corresponding control registers    |       |

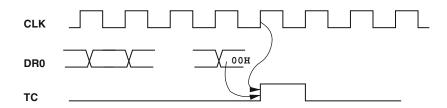

| 4.23         | Timing diagram for the PSoC timer circuit.                     |       |

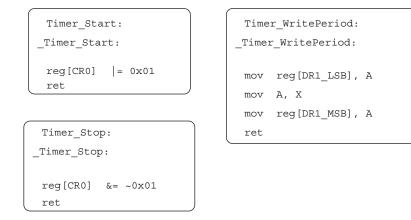

| 4.24         | Terminal count firmware routines                               |       |

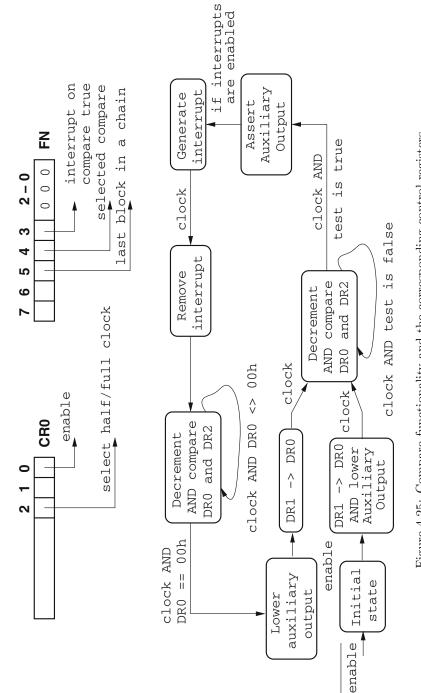

| 4.25         | Compare functionality and the corresponding control registers  |       |

| 4.26         | Capture function related firmware routines.                    |       |

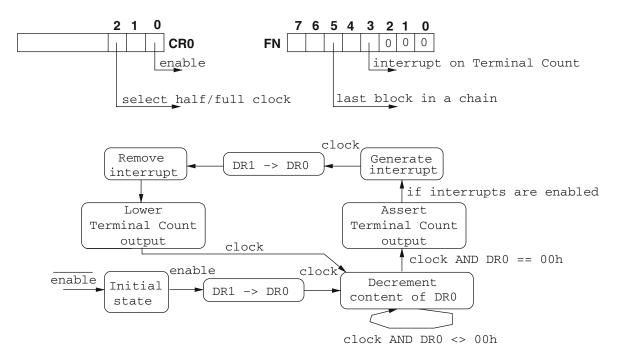

| 4.27         | The counter functionality and the related control registers    |       |

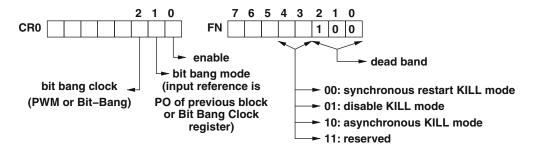

| 4.28         | Configuration and function registers for the deadband circuit. |       |

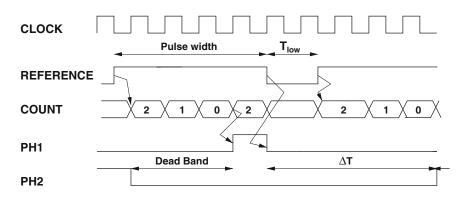

| 4.29         | Deadband circuit timing diagram.                               |       |

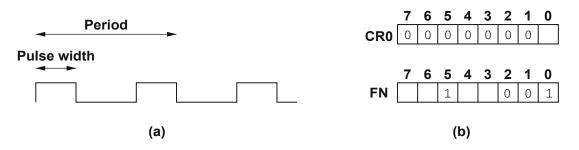

| 4.30         | Pulse width modulator.                                         |       |

| 4.31         | PWM firmware level routines.                                   |       |

| 4.32         | PWM firmware routines (continued).                             |       |

| 4.33         | PWM firmware routines (continued).                             |       |

| 4.34         | PWM firmware routines (continued).                             |       |

| 4.35         | PWM implementation as assembly code routines                   |       |

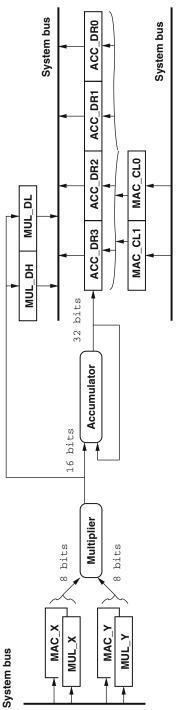

| 4.36         | Multiply accumulate (MAC) circuit.                             | 190   |

| 4.37         | C code for scalar product algorithm.                           |       |

| 4.38         | Assembly code generated by a C compiler.                       |       |

| 4.39         | Assembly code generated by a C compiler (continued).           |       |

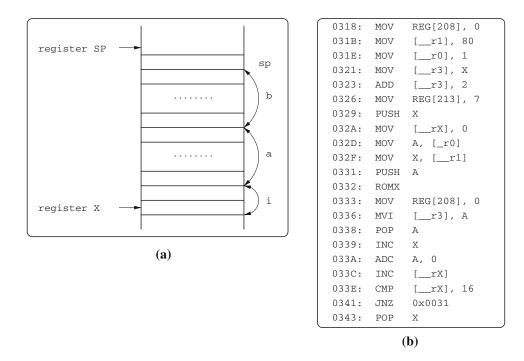

| 4.40         | Assembly code for scalar product without using MAC.            |       |

| 4.41         | Assembly code for scalar product using MAC.                    |       |

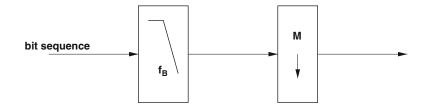

| 4.42         | Dataflow of the decimation operation.                          |       |

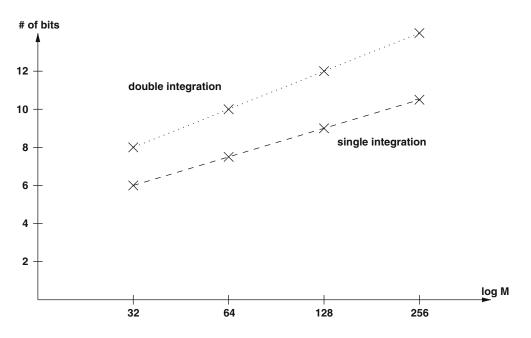

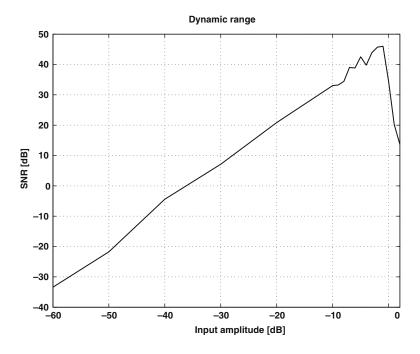

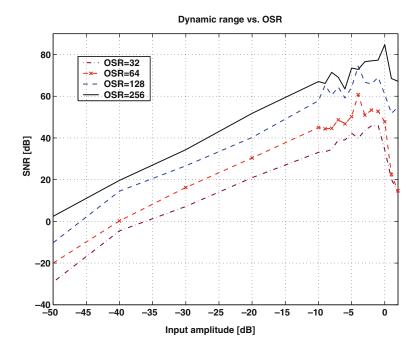

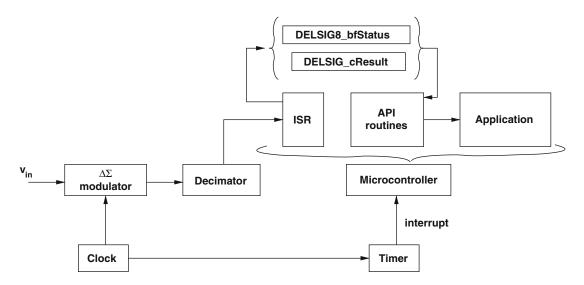

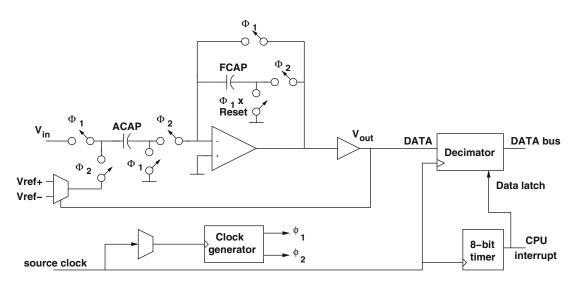

| 4.43         | ADC performance as a function of the decimation factor M.      |       |

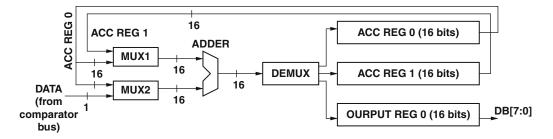

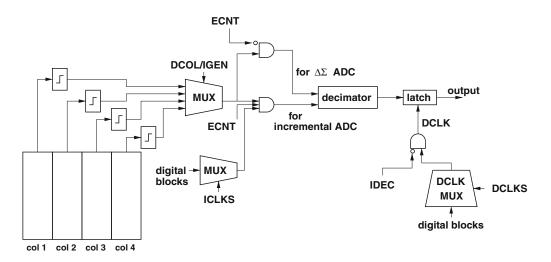

| 4.44         | Structure of the PSoC type 1 decimator circuit.                |       |

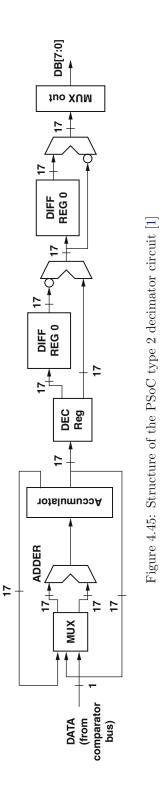

| 4.45         | Structure of the PSoC type 2 decimator circuit                 |       |

| 4.46         | Programming of the decimator circuit.                          |       |

| 1.10         |                                                                |       |

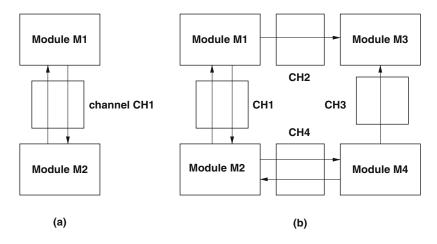

| 5.1          | Data communication between modules.                            | . 208 |

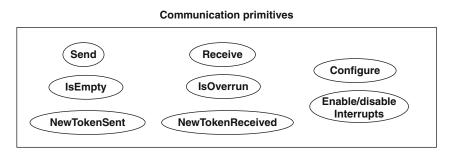

| 5.2          | High-level data communication primitives.                      |       |

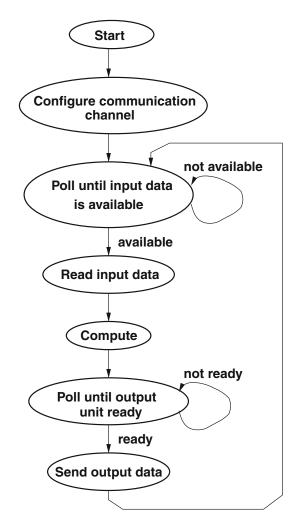

| 5.3          | Pseudocode of a communicating module.                          |       |

| 5.4          | Successive refinement steps for communication design.          |       |

| 5.5          | Handling abstract channels and channel implementation units    |       |

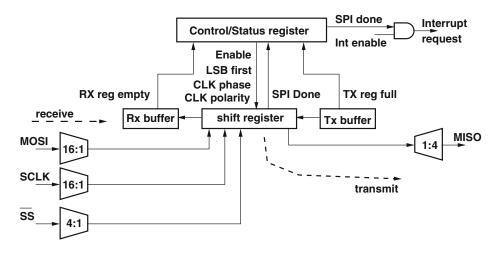

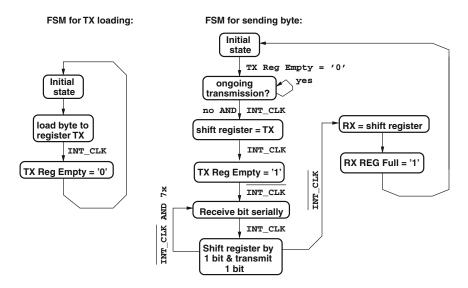

| 5.6          | PSoC SPI blocks.                                               |       |

| 5.7          | PSoC SPIM dataflow.                                            |       |

| 5.8          | PSoC SPIS dataflow.                                            |       |

| 5.9          | SPI circuit operation.                                         |       |

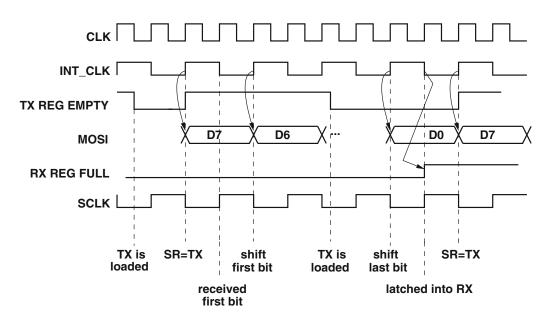

| 5.10         | Timing diagrams of the <i>SPIM</i> circuit.                    |       |

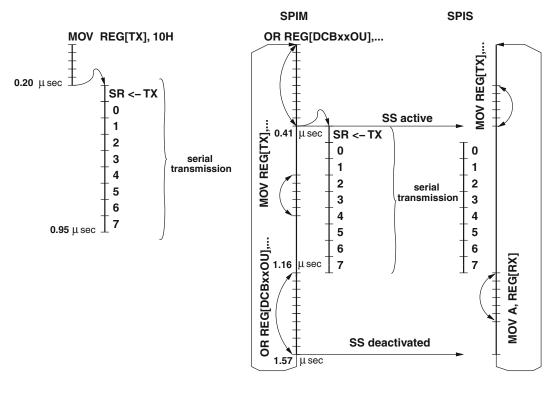

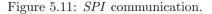

| 5.10<br>5.11 | SPI communication.                                             |       |

| 5.12         | Improved SPI communication.                                    |       |

| 0.14         |                                                                | . 220 |

| 5.13           | SPIM start and stop routines.                                                                                                         | . 226 |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------|-------|

| 5.14           | SPIM send and receive routines                                                                                                        | . 227 |

| 5.15           | SPIM read status function                                                                                                             | . 227 |

| 5.16           | Program using the <i>SPIM</i> -related routines                                                                                       | . 228 |

| 5.17           | Program using the SPIS related routines                                                                                               |       |

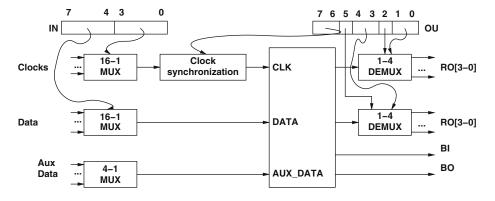

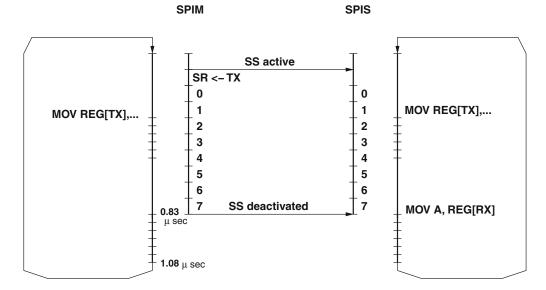

| 5.18           | Block structure of the block UART                                                                                                     |       |

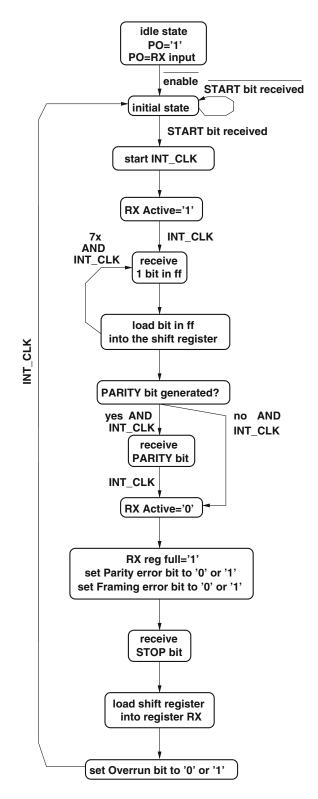

| 5.19           | UART receiver operation                                                                                                               | . 231 |

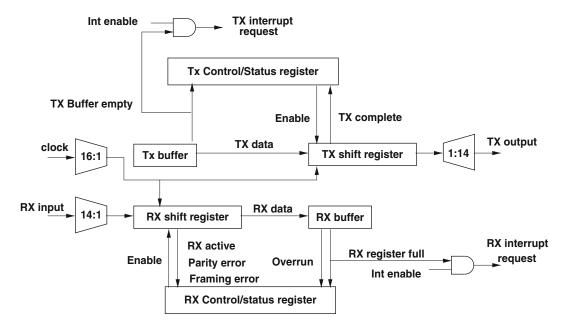

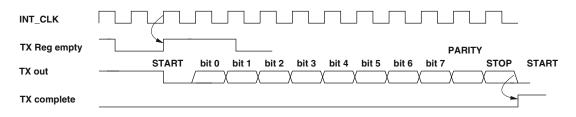

| 5.20           | Waveforms for the UART transmit operation.                                                                                            |       |

| 5.21           | UART receiver operation                                                                                                               | . 233 |

| 5.22           | Waveforms for the UART receiver operation                                                                                             |       |

| 5.23           | UART related functions.                                                                                                               | . 235 |

| 5.24           | Finding the status of the Rx and Tx subblocks.                                                                                        | . 236 |

| 5.25           | Receiving and sending data using the UART block.                                                                                      | . 237 |

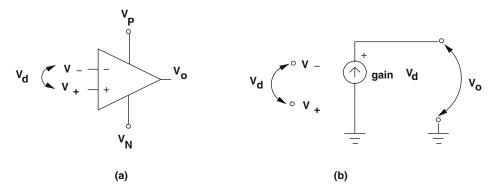

| 6.1            | Ideal OpAmp symbol and macromodel.                                                                                                    | . 244 |

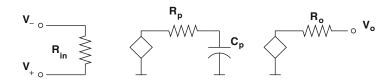

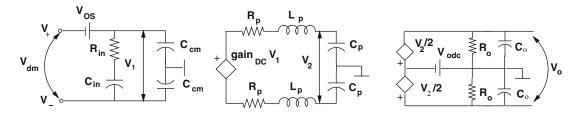

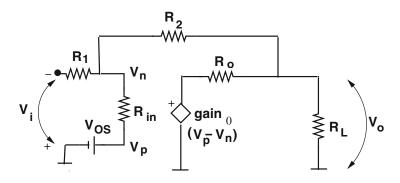

| 6.2            | OpAmp macromodel.                                                                                                                     |       |

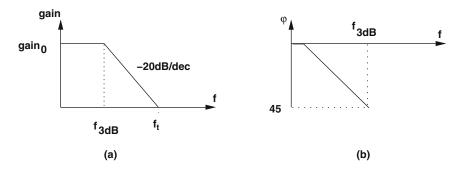

| 6.3            | Magnitude and phase response for the single-pole OpAmp model                                                                          |       |

| 6.4            | Magnitude and phase response for the three OpAmp model                                                                                |       |

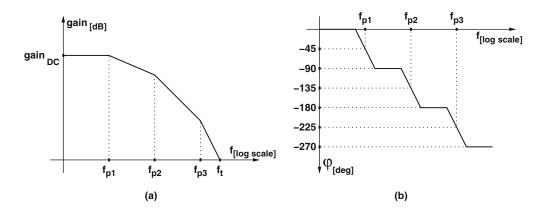

| 6.5            | Definition of circuit distortion.                                                                                                     |       |

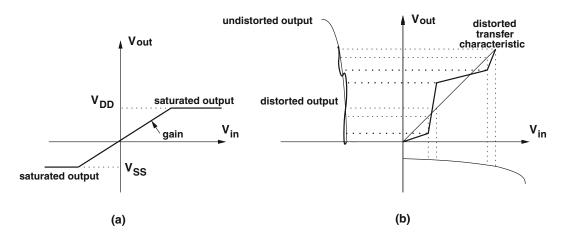

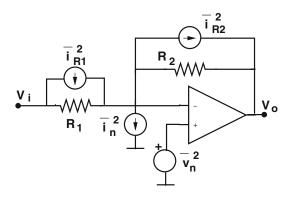

| 6.6            | Noise modeling.                                                                                                                       |       |

| 6.7            | Detailed OpAmp macromodel                                                                                                             |       |

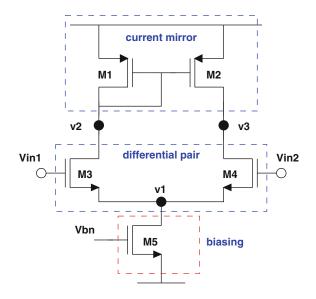

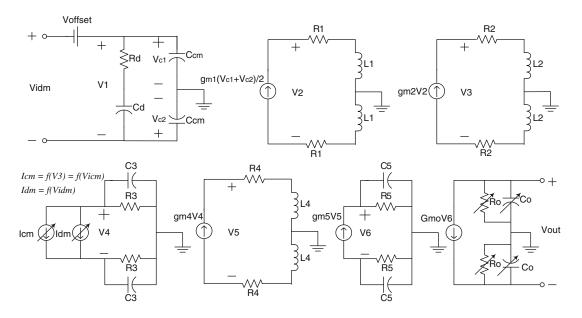

| 6.8            | Single-stage OpAmp.                                                                                                                   |       |

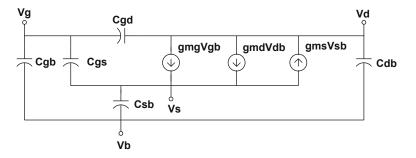

| 6.9            | Linear <i>hybrid</i> - $\pi$ MOSFET model                                                                                             | . 255 |

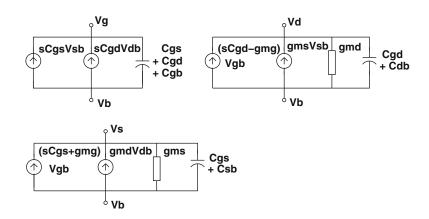

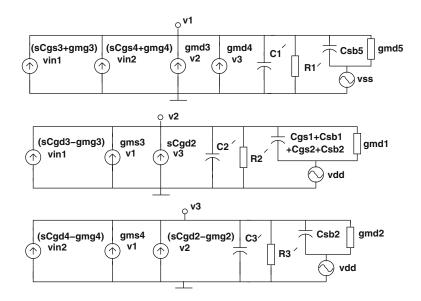

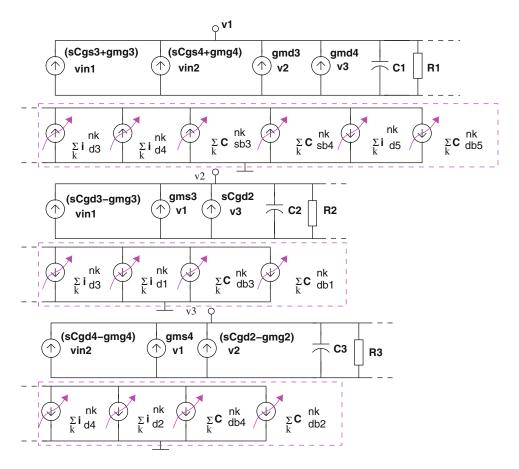

| 6.10           | Transformed linear <i>hybrid-</i> $\pi$ MOSFET model                                                                                  | . 256 |

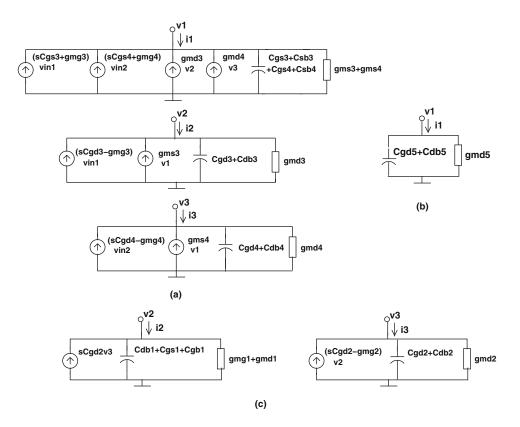

| 6.11           | Macromodels of the single-stage OpAmp basic building blocks: (a) differential                                                         |       |

|                | input, (b) biasing circuit, and (c) current mirror                                                                                    | . 257 |

| 6.12           | Coupled macromodel of the single-stage OpAmp.                                                                                         | . 258 |

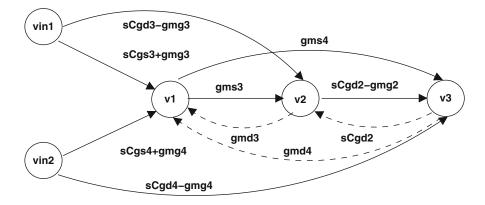

| 6.13           | Signal path of the single-stage OpAmp                                                                                                 |       |

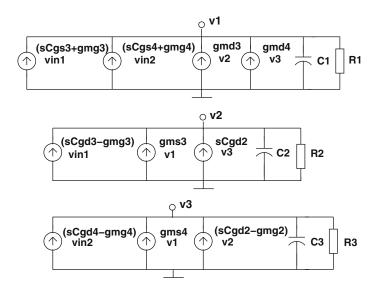

| 6.14           | Uncoupled macromodel for single-stage OpAmp                                                                                           | . 260 |

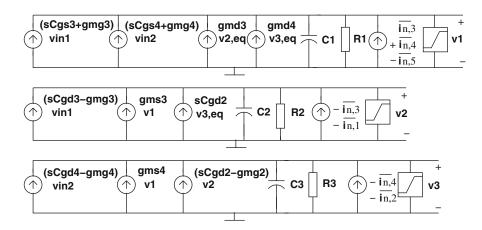

| 6.15           | Macromodel for single-stage OpAmp with power-supply variation                                                                         |       |

| 6.16           | Nonlinear macromodel for single stage OpAmp.                                                                                          | . 262 |

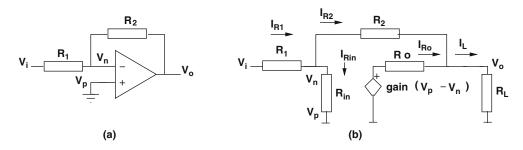

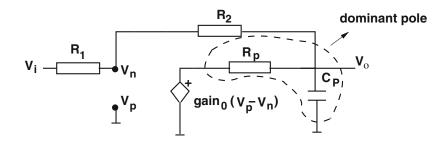

| 6.17           | Inverting amplifier.                                                                                                                  | . 263 |

| 6.18           | Impact of the OpAmp pole on the amplifier behavior.                                                                                   | . 266 |

| 6.19           | Noise analysis for inverting amplifier                                                                                                | . 267 |

| 6.20           | Impact of offset voltage on inverting amplifier output                                                                                | . 268 |

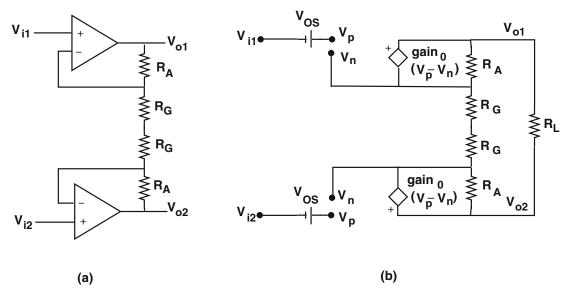

| 6.21           | Instrumentation amplifier.                                                                                                            | . 269 |

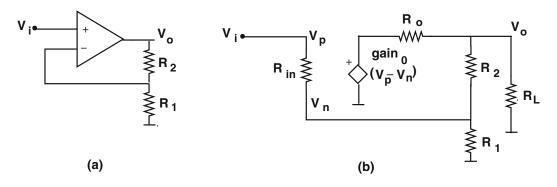

| 6.22           | Non-inverting amplifier circuit.                                                                                                      | . 270 |

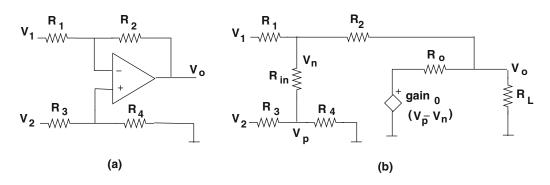

| 6.23           | Summing amplifier circuit.                                                                                                            | . 271 |

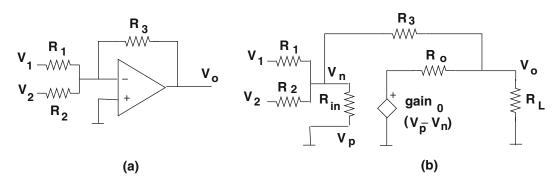

| 6.24           | Difference amplifier circuit.                                                                                                         | . 272 |

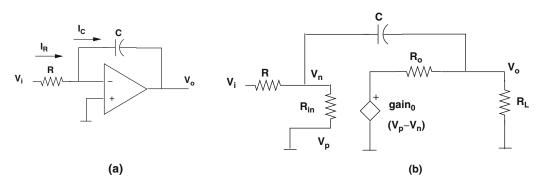

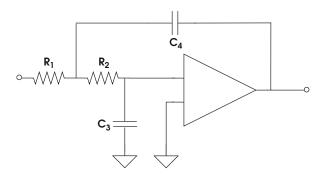

| 6.25           | Integrator circuit.                                                                                                                   | . 273 |

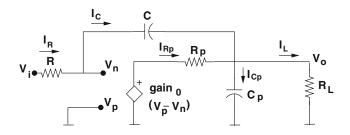

| 6.26           | Integrator circuit with a single-pole OpAmp                                                                                           | . 274 |

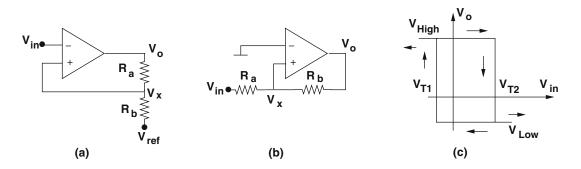

| 6.27           | Schmitt trigger: (a) inverting circuit, (b) noninverting circuit, and (c) transfer                                                    |       |

|                | characteristics                                                                                                                       | . 275 |

| 6.28           | Analog section of the PSoC architecture.                                                                                              | . 276 |

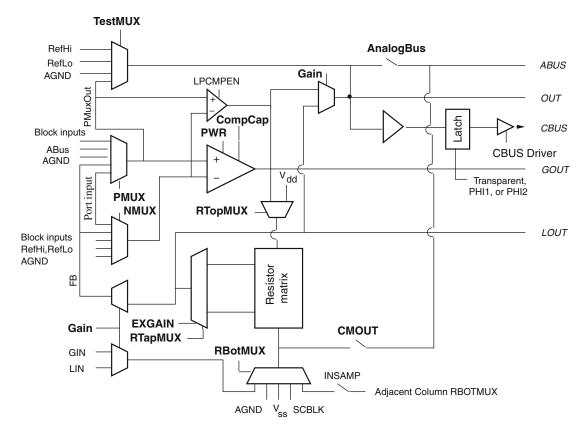

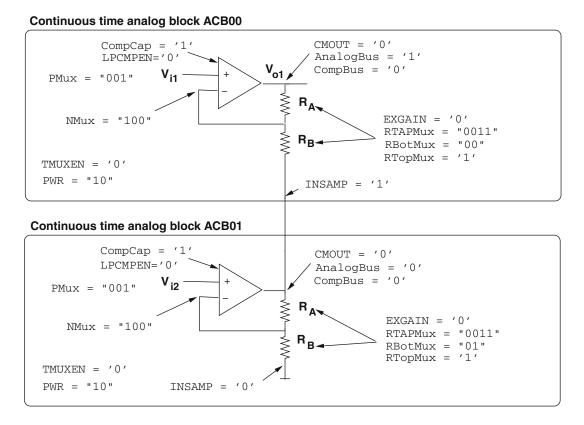

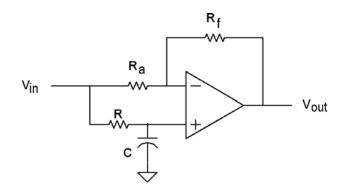

| 6.29           | Reconfigurable continuous-time analog block                                                                                           | . 277 |

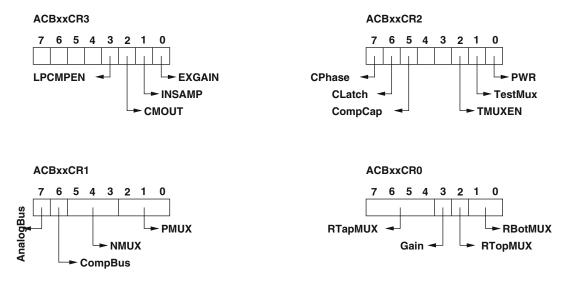

| 6.30           | Control registers for PSoC continuous-time analog block.                                                                              |       |

| 6.31           | Possible connections to the resistor matrix bottom node in CT blocks                                                                  |       |

| 6.32           |                                                                                                                                       |       |

|                | Types of links between continuous-time and switched capacitor analog blocks.                                                          | . 280 |

| 6.33           | Types of links between continuous-time and switched capacitor analog blocks.<br>Types of links between continuous-time analog blocks. |       |

| $6.33 \\ 6.34$ |                                                                                                                                       | . 281 |

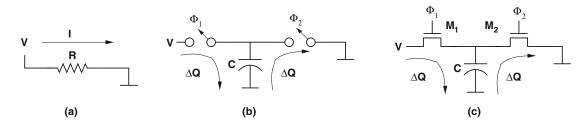

| 7.1                                                                                                                                                                   | Moving charge with current stimulus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 290                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.2                                                                                                                                                                   | Time behavior of switched capacitor circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 292                                                                                                                                                                                            |

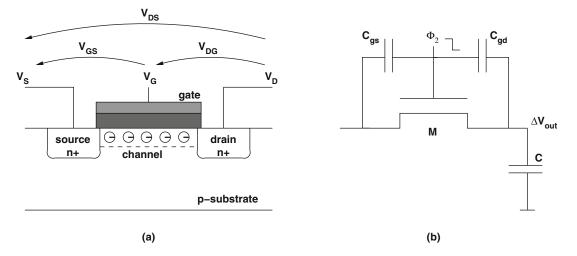

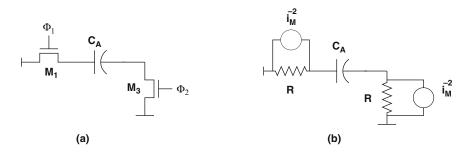

| 7.3                                                                                                                                                                   | (a) Channel charge injection and (b) clock feedthrough                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 294                                                                                                                                                                                            |

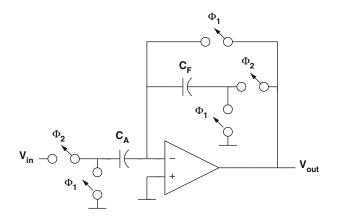

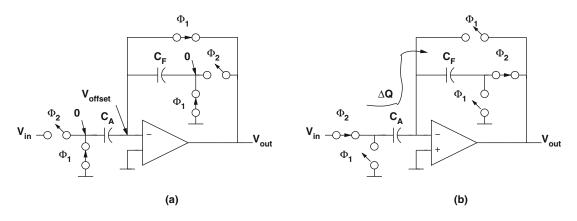

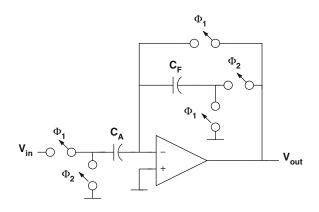

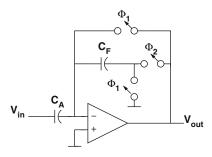

| 7.4                                                                                                                                                                   | Switched capacitor fixed gain amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                  |

| 7.5                                                                                                                                                                   | Set for (a) signal acquisition $(\phi_1)$ phase and (b) charge transfer $(\phi_2)$ phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 296                                                                                                                                                                                            |

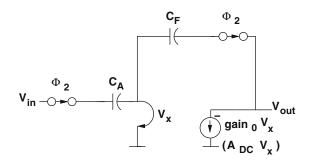

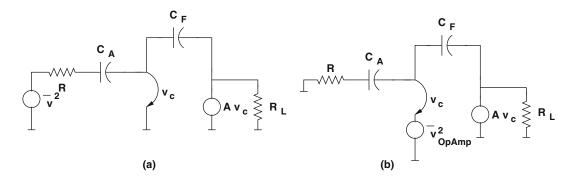

| 7.6                                                                                                                                                                   | Impact of finite OpAmp gain of the SC amplifier performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 298                                                                                                                                                                                            |

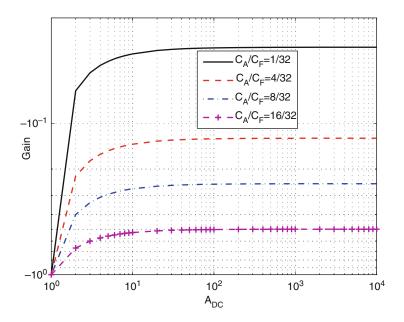

| 7.7                                                                                                                                                                   | Dependency of the amplifier gain on the OpAmp's finite gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 298                                                                                                                                                                                            |

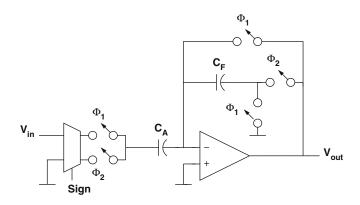

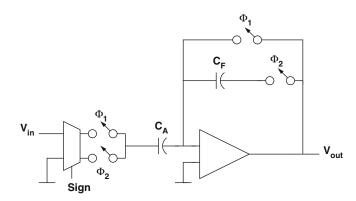

| 7.8                                                                                                                                                                   | Amplifier with input switches swapped                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 299                                                                                                                                                                                            |

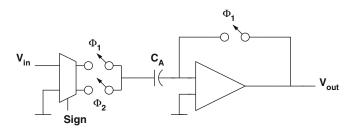

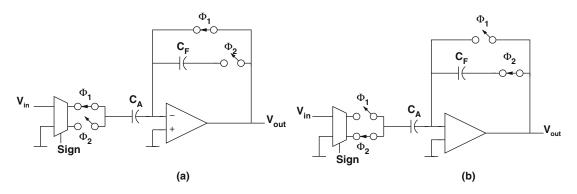

| 7.9                                                                                                                                                                   | Selectable gain polarity amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 300                                                                                                                                                                                            |

| 7.10                                                                                                                                                                  | Switched capacitor comparator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 300                                                                                                                                                                                            |

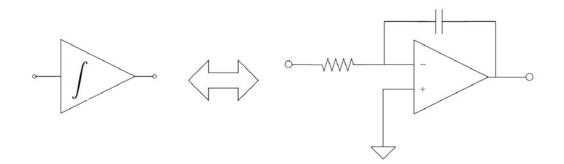

| 7.11                                                                                                                                                                  | Switched capacitor integrator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 301                                                                                                                                                                                            |

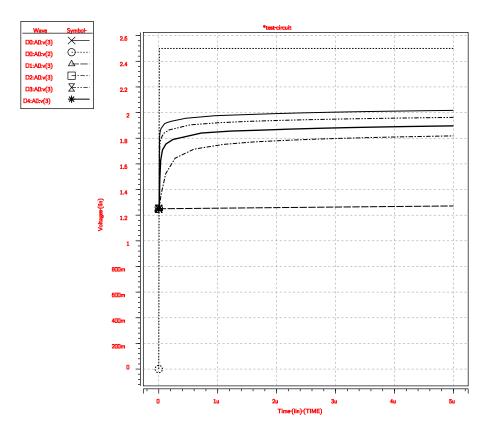

| 7.12                                                                                                                                                                  | Integrator operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                  |

| 7.13                                                                                                                                                                  | Switched capacitor differentiator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                  |

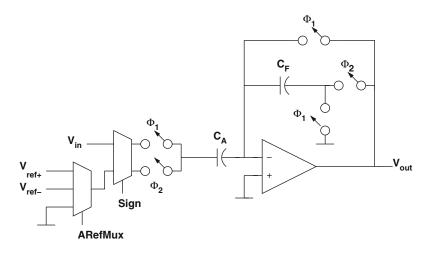

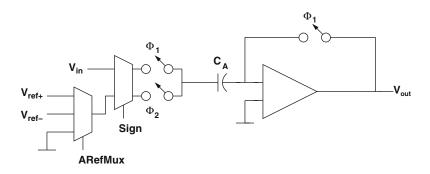

| 7.14                                                                                                                                                                  | Improved reference selection for noninverting amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                  |

| 7.15                                                                                                                                                                  | Simple two bit analog-to-digital converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                  |

| 7.16                                                                                                                                                                  | Simple two bit analog-to-digital converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                  |

| 7.17                                                                                                                                                                  | Analog to digital modulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                  |

| 7.18                                                                                                                                                                  | The analog section of the PSoC architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                  |

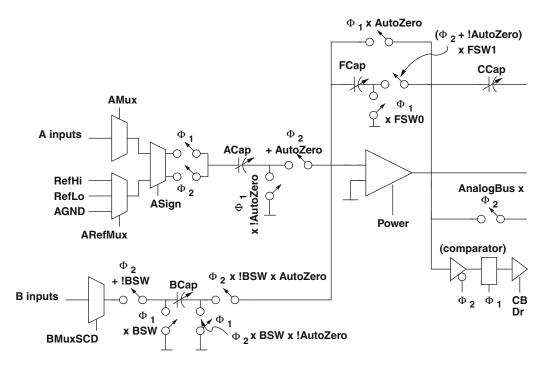

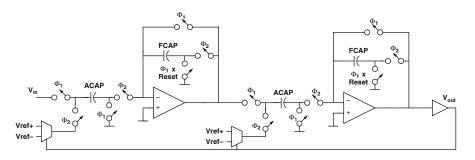

| 7.19                                                                                                                                                                  | Type C Switched capacitor block.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                  |

| 7.20                                                                                                                                                                  | Type D switched capacitor block.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                  |

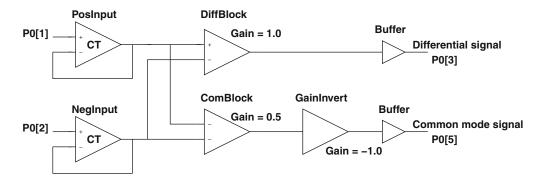

| 7.21                                                                                                                                                                  | Differential amplifier with common mode output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                  |

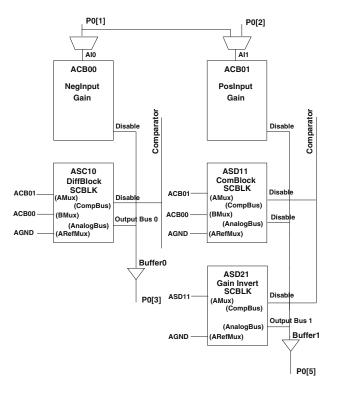

| 7.22                                                                                                                                                                  | PSoC block placement for the differential amplifier with common mode output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                  |

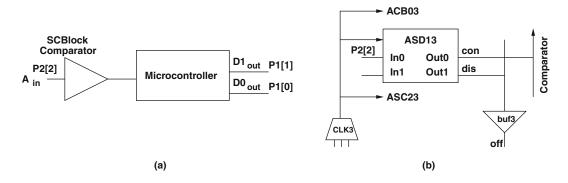

| 7.23                                                                                                                                                                  | PSoC implementation of a four state ADC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                  |

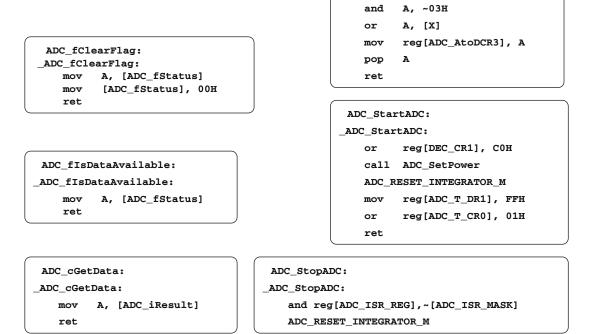

| 7.24                                                                                                                                                                  | Assembly code for two bit ADC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                  |

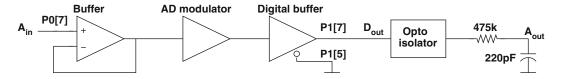

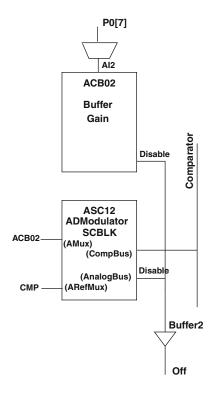

|                                                                                                                                                                       | Isolated analog driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                  |

| 7.25                                                                                                                                                                  | ISOLATED ALLALOG ULLVEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                  |

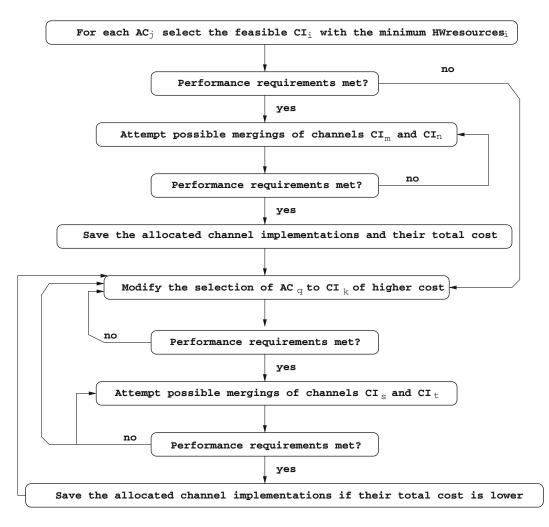

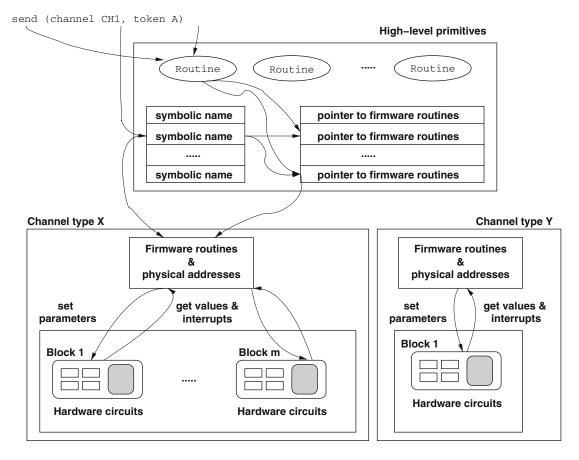

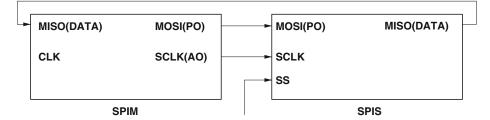

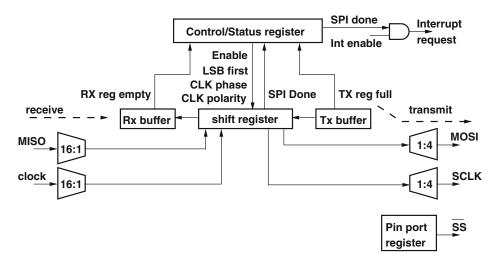

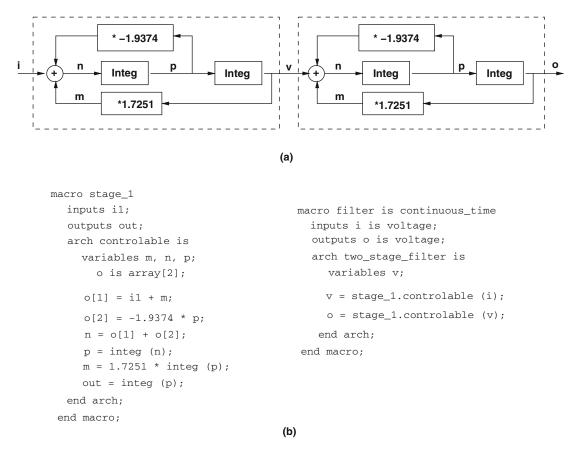

| $7.25 \\ 7.26$                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                  |