### lan A. Grout

# Integrated Circuit Test Engineering Modern Techniques

## Integrated Circuit Test Engineering

#### **Modern Techniques**

With 149 Figures

Ian A. Grout, PhD Department of Electronic and Computer Engineering University of Limerick Limerick Ireland

British Library Cataloguing in Publication Data Grout, Ian Integrated circuit test engineering: modern techniques 1. Integrated circuits - Verification I. Title 621.3'81548 ISBN-10: 1846280230

Library of Congress Control Number: 2005929631

ISBN-10: 1-84628-023-0 e-ISBN: 1-84628-173-3 Printed on acid-free paper ISBN-13: 978-1-84628-023-8 Printed on acid-free paper

© Springer-Verlag London Limited 2006

HSPICE® is the registered trademark of Synopsys, Inc., 700 East Middlefield Road, Mountain View, CA 94043, U.S.A. http://www.synopsys.com/home.html

MATLAB® is the registered trademark of The MathWorks, Inc., 3 Apple Hill Drive Natick, MA 01760-2098, U.S.A. http://www.mathworks.com

Verifault-XL®, Verilog® and PSpice® are registered trademarks of Cadence Design Systems, Inc., 2655 Seely Avenue, San Jose, CA 95134, U.S.A. http://www.cadence.com/index.aspx

T-Spice™ is the trademark of Tanner Research, Inc., 2650 East Foothill Blvd. Pasadena, CA 91107, U.S.A. http://www.tanner.com/

Apart from any fair dealing for the purposes of research or private study, or criticism or review, as permitted under the Copyright, Designs and Patents Act 1988, this publication may only be reproduced, stored or transmitted, in any form or by any means, with the prior permission in writing of the publishers, or in the case of reprographic reproduction in accordance with the terms of licences issued by the Copyright Licensing Agency. Enquiries concerning reproduction outside those terms should be sent to the publishers.

The use of registered names, trademarks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant laws and regulations and therefore free for general use.

The publisher makes no representation, express or implied, with regard to the accuracy of the information contained in this book and cannot accept any legal responsibility or liability for any errors or omissions that may be made.

Typesetting: Camera ready by author Production: LE-T<u>F</u>X Jelonek, Schmidt & Vöckler GbR, Leipzig, Germany Printed in Germany

$9\,8\,7\,6\,5\,4\,3\,2\,1$

Springer Science+Business Media springeronline.com

This book is dedicated to Jane.

Test

A procedure intended to establish the quality, performance or reliability of something, especially before it is taken into widespread use.

New Oxford English Dictionary

#### **About the Author**

Ian Grout is a lecturer within the Department of Electronic and Computer Engineering at the University of Limerick, Ireland. He was born in London, UK in 1967, and earned his PhD from Lancaster University in 1994. He has worked within the microelectronics field for several years, in particular Integrated Circuit test research and education. He has been a lecturer at Limerick since 1998.

#### Preface

The extensive use of electronic products in everyday life has only been made possible with the advent of, and substantial advances in, the field of microelectronic circuit engineering. The types of microelectronic circuits that can be developed today provide for a complex circuit behaviour within a physically small package. The advent of high-value, high-functionality portable electronic systems such as the laptop computer, mobile phone and Personal Digital Assistant (PDA), are testament to this. Since the successful demonstration of the transistor back in 1947 by Bardeen, Brattain, and Shockley at Bell Laboratories (USA), in just over half a century the ability to create microelectronic circuits containing tens of millions of transistors is a remarkable statement of achievement. The trend towards increases in design complexity and speed of operation, coupled with the need for improvements in the engineering processes utilised in order further to reduce product costs, is leading to improvements in all aspects of device design, fabrication and test. It is the field of test engineering that this book aims to identify and discuss.

With the increased demands placed on test engineering activities within the electronic, and in particular microelectronic, circuit and system development and production (manufacturing) environments, the need to consider the importance of developing the right circuit/system test procedure is critical to the commercial success of a developed product. Test and evaluation activities provide an essential input to the product development at a range of stages within a product development cycle in that they:

- Provide insight into a design development activity from concept through to implementation in order to ensure that the design can be adequately tested once it has been manufactured/fabricated.

- Ensure devices that contain circuit faults due to problems with either the design or fabrication are not perceived as "good devices".

- Provide the means to evaluate the operation of the design over a range of operating conditions that may be encountered in a final application.

- Determine and guarantee the operating specifications that will be required by the end-user.

- Allow for failures to be identified and the causes of the failures to be fedback to design and fabrication for appropriate corrective action to be undertaken in order to eliminate the sources of the identified failures, and reduce the risk of faulty devices being passed onto the customer.

The important role of test engineering is now widely acknowledged, such that the test procedure (program) development process is now considered of equal importance to that of design. Test requirements, once seen in many cases as an afterthought and considered only once a design had been generated, are now in many cases a prerequisite to the design activity, and test is now an active process from design concept identification and specification through to high-volume fabrication of the final product. This is due to a number of factors including the:

- Rapid increase in design complexity, particularly for digital systems (more functionality per mm<sup>2</sup> of silicon area).

- Utilisation of new fabrication processes (reduced geometries allowing for the creation of smaller devices but which may suffer from fabrication process variation problems leading to new device failure modes and an increase in the fabricated device parameter variability).

- Increase in design performance (higher operating frequencies, greater demands on design specifications).

- Need for more competitive products (the customer receiving devices with superior performance at lower cost, given the availability of a greater number of suppliers of the necessary technology).

- Need to test the operation of the fabricated device in a cost-effective manner with the available test equipment, without the requirement to acquire and utilise prohibitively high-cost test equipment.

- Need to enable the device to run self-test algorithms once in the final application using additional circuitry built into the design (BIST: Built-In Self-Test), and for this type of self-test to be independent of external circuitry.

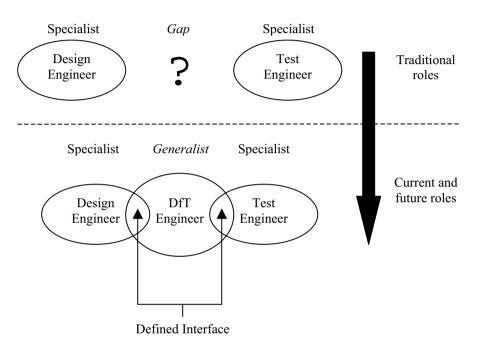

Over the last few years, the evolution of test has brought it closer to design, bridging the "*traditional*" gap between design and test. Here, where once the design and test activities were separate and distant in many aspects ranging from the ultimate "*end product*" to the terminology used, the gap has been bridged with

a unified "*Design for Testability*" (*DfT*) – sometimes referred to as "*Design for Test*" - approach. Specialist engineers in design and test are supported with a more generalist DfT engineer providing the ability to bridge the gap, but not necessarily required to be a specialist in either field – the need for specialists is based on the need for in-depth knowledge of specific design and test issues, roles which a single person could not realistically be expected to undertake. The gap between design and test expertise, leading to potential problems in a product development process, is being replaced with this "*Design for Testability*" (DfT) link, providing the bridge between the experts. This is coupled with the traditional boundary between digital and analogue electronic circuits, a nice and neat separation of behaviour into logic and voltage/current for design and analysis purposes, being eroded by the requirements for true mixed-signal device operation. Digital, analogue and mixed-signal DfT for devices ranging from a single operational amplifier through to the latest generation microprocessor is a complex task requiring substantial knowledge of design, test and the implications of both aspects on the other.

The purpose of this book is to discuss the range of requirements placed on the test engineering activities and the test engineer within the rapidly changing microelectronic circuit engineering environment, and to identify the methods available to solving a range of test problem scenarios.

The book is presented as follows:

**Chapter 1** provides an introduction to the role of test within the electronic/microelectronic engineering environment and highlights a number of key trends. The trends in test are highlighted, along with an overview of key actions.

**Chapter 2** provides an overview of the key fabrication processes. Whilst not aimed at being an exhaustive review of the field, it is aimed at identifying key aspects relating to test program development, in particular those relating to process induced circuit failure modes and test program development following a defect oriented approach.

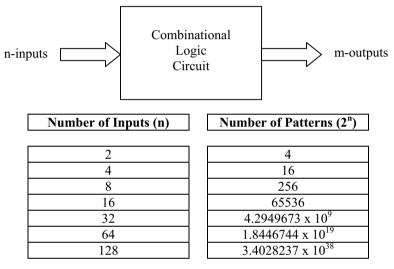

**Chapter 3** overviews test program development for digital logic, both combinational logic and sequential logic. The principles identified here are relevant for later discussions into System on a Chip (SoC) test program development.

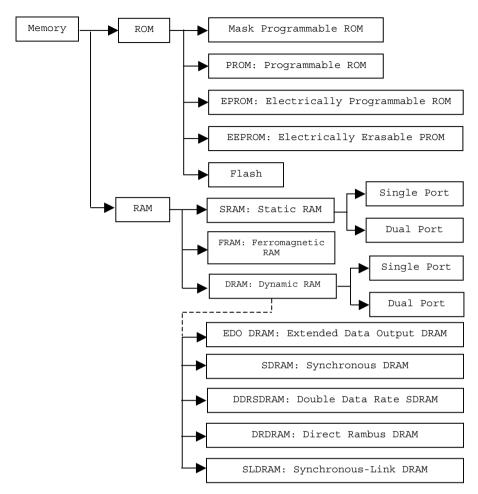

**Chapter 4** introduces semiconductor memory structures and test procedures. Traditionally, memories have been discrete packaged devices which, when utilised with a suitable processor, develop the basic operation of a computer system. Increasingly, the move towards higher levels of integration is leading to memories being provided as macro cells for placement alongside other circuitry on the same silicon die, leading towards *System on a Chip* (SoC) and *System in Package* (SiP) solutions that require extensive use of memory.

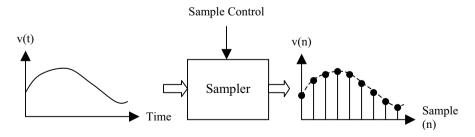

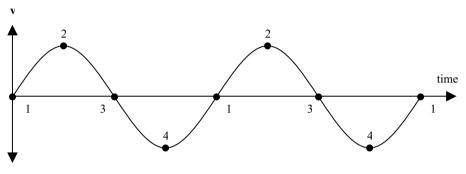

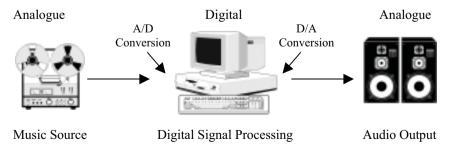

**Chapter 5** introduces analogue test. The key differences between digital and analogue test are presented, along with the challenges that exist in the need to develop suitable analogue circuit stimulus, to capture signals and to analyse results.

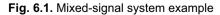

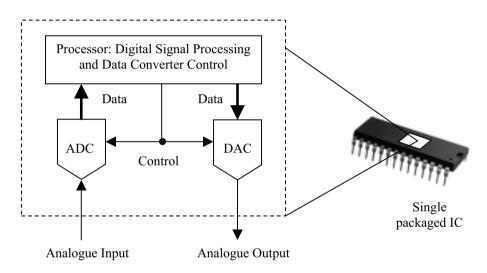

**Chapter 6** provides a discussion into the combining of digital and analogue test methods to provide the ability to test mixed-signal designs. In particular, data converter test requirements and solutions are considered.

**Chapter 7** discusses test procedures for digital and analogue Input/Output cells which interface the core of the silicon die to the package. Such cells have particular test requirements.

**Chapter 8** further develops digital test concepts and introduces structured approaches to test program development and linkages to design with the "*Design for Testability*" (*DfT*) approach.

**Chapter 9** discusses the problem with, and need for solutions to, the testing of System on a Chip (SoC) devices. Essentially, the previous concepts are revisited, limitations identified and the need to adopt structured DfT approaches in product development identified.

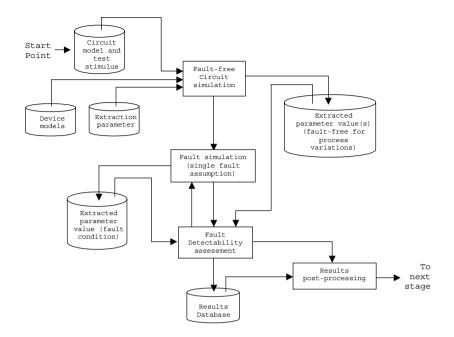

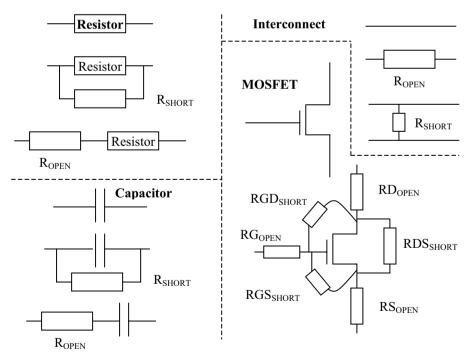

**Chapter 10** introduces test pattern generation and fault simulation techniques. These activities are required as an input to the development of structural test programs. Fault simulation provides an important input to the development of structural test programs that aim to detect circuit faults rather than confirm the circuit functionality. Digital fault simulation is well established for specific fault models, whereas analogue and mixed-signal test still require more refinement.

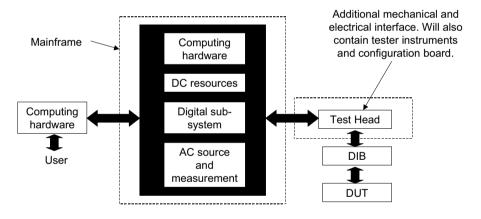

**Chapter 11** discusses the need for, and issues relating to, the use of Automatic Test Equipment (ATE) for semiconductor devices. The need to understand the structure of the ATE, along with the limitations, are key to the success of test program application in a production environment, are identified.

**Chapter 12** highlights the role of Test Economics as an aid to the development of effective and cost efficient test programs.

The text is supported with examples of how the concepts may be demonstrated on modest sized designs suitable for laboratory exercises. The text is aimed at providing an insight into the area of modern test engineering for those who would like to learn more of the subject area as well as those who are entering the area for the first time. Electronic material for use with this text can be downloaded from *springer.com*

#### Acknowledgements

Thanks must be expressed to the following people. First, to JJ O'Riordan (Analog Devices Inc., Limerick, Ireland) for his work within the test engineering community nationally and his continued support for the test engineering teaching and research within the University of Limerick. Second, thanks to the following postgraduates within the DfT Group: Joseph Walsh, Thomas O'Shea, Michael Canavan, Jeffrey Ryan and Jason Murphy, for their enthusiasm and interesting discussions.

#### Contents

| A | bbrevi | ations                                                     | xxv |

|---|--------|------------------------------------------------------------|-----|

| 1 | Intro  | duction to Integrated Circuit Test Engineering             | 1   |

| - | 1.1    | Introduction                                               |     |

|   | 1.2    | The Rule of Ten                                            |     |

|   | 1.3    | The Evolution of Test Engineering                          |     |

|   | 1.4    | Test Engineer Activities                                   |     |

|   | 1.5    | Device Testing                                             |     |

|   | 1.6    | Production Test: ATE Systems                               |     |

|   | 1.7    | Technology Trends                                          |     |

|   | 1.8    | International Technology Roadmap for Semiconductors (ITRS) |     |

|   | 1.9    | Computer Aided Test                                        |     |

|   | 1.10   | Virtual Test                                               |     |

|   | 1.11   | Moore's Law                                                |     |

|   | 1.12   | Rent's Rule                                                |     |

|   | 1.13   | Benchmark Circuits                                         |     |

|   | 1.14   | DfX                                                        |     |

|   | 1.15   | Summary                                                    | 14  |

|   | 1.16   | References                                                 |     |

| 2 | Fahr   | ication Processes for Integrated Circuits                  | 17  |

| - | 2.1    | Introduction                                               |     |

|   | 2.2    | Technology Nodes                                           |     |

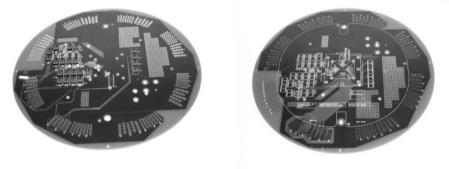

|   | 2.3    | Wafer Size                                                 |     |

|   | 2.4    | Bipolar Technology                                         |     |

|   | 2.5    | Complementary Metal Oxide Semiconductor (CMOS) Technology  |     |

|   | 2.6    | BiCMOS Technology                                          |     |

|   | 2.7    | SiGe BiCMOS Technology                                     |     |

|   | 2.8    | Gallium Arsenide (GaAs) Technology                         |     |

|   | 2.9    | Memory Processes                                           |     |

|   | 2.10   | Packaging                                                  |     |

|   | 2.11   | Die Bonding                                                |     |

|   | 2.12     | Multi-Chip Modules                                     | 32  |

|---|----------|--------------------------------------------------------|-----|

|   | 2.13     | Foundry Services                                       | 34  |

|   | 2.14     | Process Variations                                     |     |

|   | 2.15     | Electromigration                                       |     |

|   | 2.16     | Future Directions                                      |     |

|   | 2.17     | Summary                                                |     |

|   | 2.18     | References                                             |     |

|   |          | cises                                                  |     |

| • | <b>D</b> |                                                        | 4.1 |

| 3 | 0        | al Logic Test                                          |     |

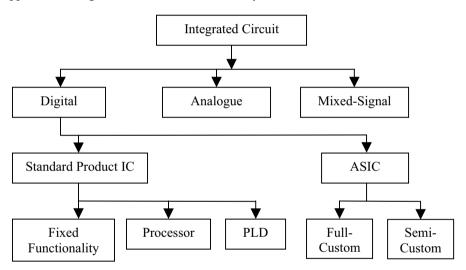

|   | 3.1      | Introduction                                           |     |

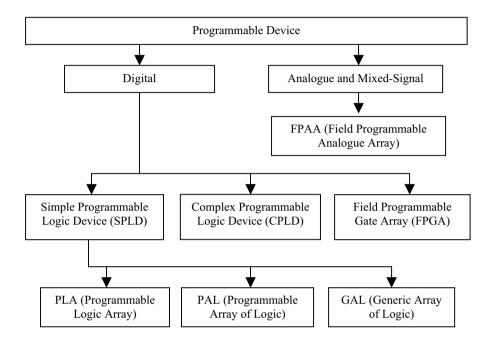

|   | 3.2      | Logic Families                                         |     |

|   | 3.3      | Digital Logic ICs                                      |     |

|   | 3.4      | Programmable Logic                                     |     |

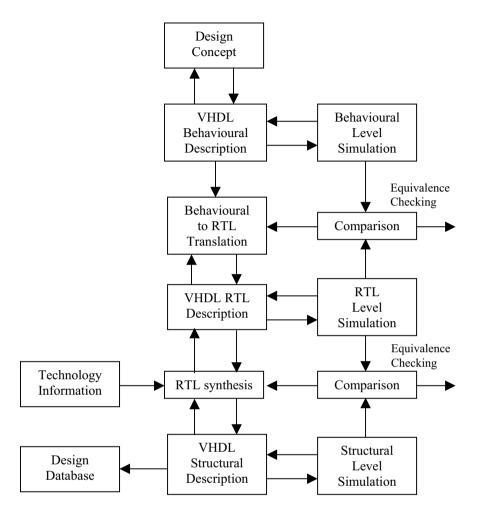

|   | 3.5      | Basic Logic Gates                                      |     |

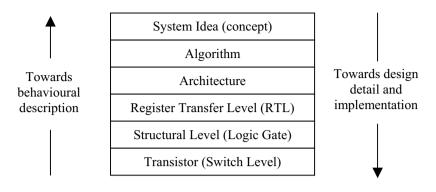

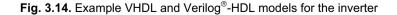

|   | 3.6      | Hardware Description Languages                         |     |

|   | 3.7      | Digital Circuit and System Design Flow                 |     |

|   | 3.8      | Number Systems                                         |     |

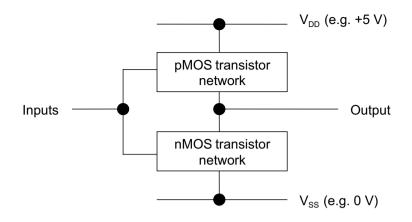

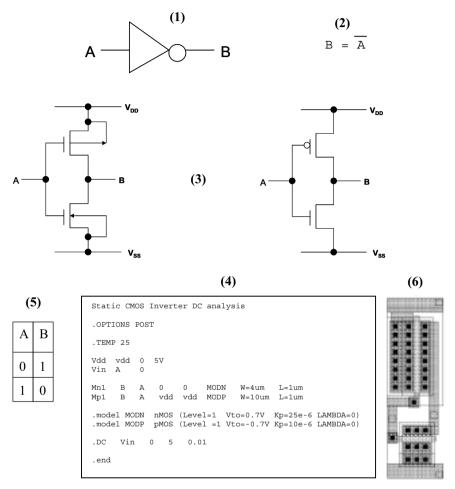

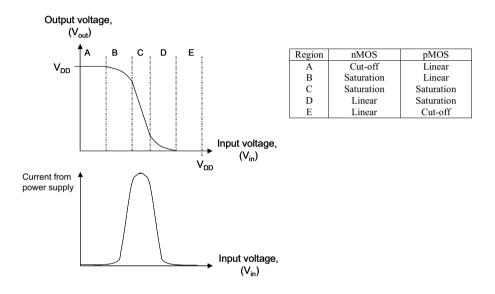

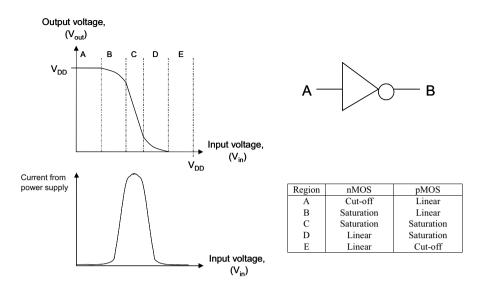

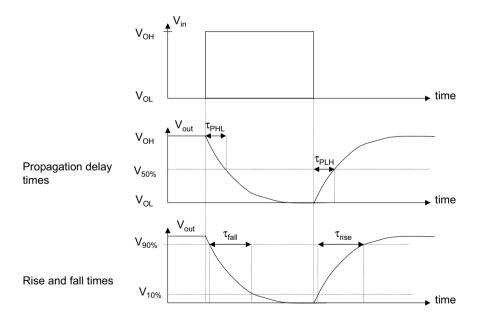

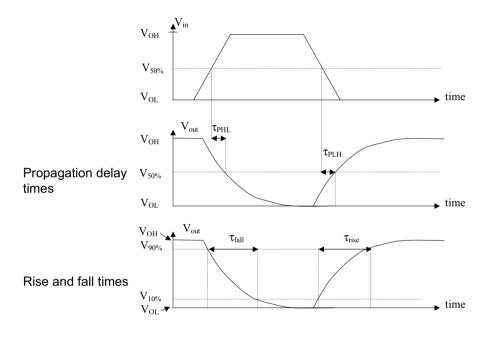

|   | 3.9      | CMOS Inverter                                          |     |

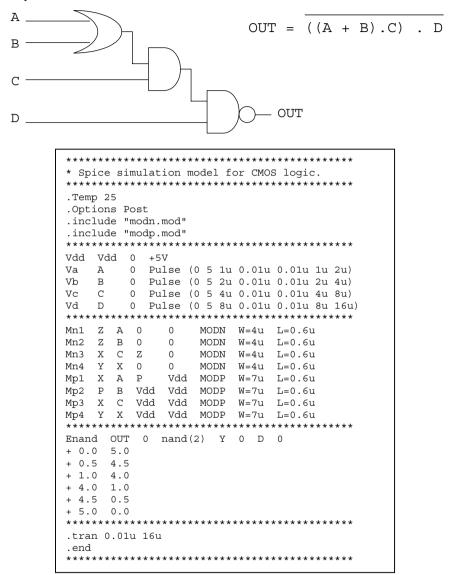

|   | 3.10     | Latch-Up                                               |     |

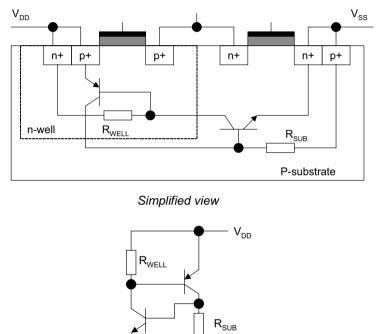

|   | 3.11     | Introduction to Digital Logic Test                     |     |

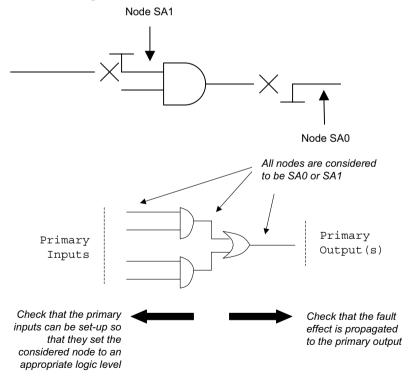

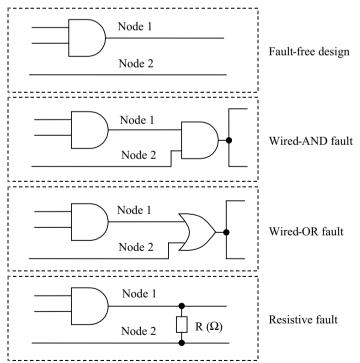

|   | 3.12     | Fault Models                                           |     |

|   |          | 3.12.1 Stuck-At-Fault                                  |     |

|   |          | 3.12.2 Bridging Fault                                  |     |

|   |          | 3.12.3 Delay Fault                                     |     |

|   |          | 3.12.4 Memory Fault                                    | 69  |

|   |          | 3.12.5 Stuck-Open and Stuck Short Faults               | 70  |

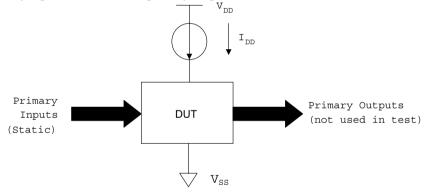

|   |          | 3.12.6 I <sub>DDO</sub> Fault                          | 70  |

|   | 3.13     | Combinational Logic Test                               | 74  |

|   |          | 3.13.1 Introduction                                    | 74  |

|   |          | 3.13.2 Test Pattern Generation                         | 74  |

|   |          | 3.13.3 Non-Detectable Faults Due to Circuit Redundancy |     |

|   |          | 3.13.4 Fan-out and Reconvergence                       | 76  |

|   |          | 3.13.5 Local and Global Feedback                       |     |

|   |          | 3.13.6 Multiple Faults and Fault Masking               |     |

|   |          | 3.13.7 Limitations of Fault Models                     |     |

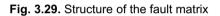

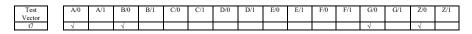

|   |          | 3.13.8 The Fault Matrix                                |     |

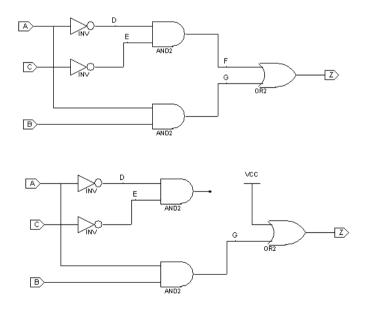

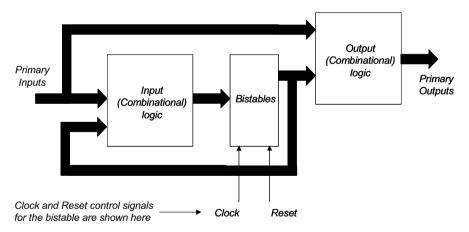

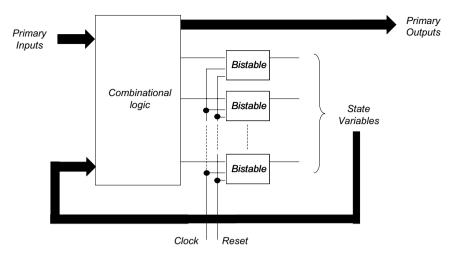

|   | 3.14     | Sequential Logic Test                                  |     |

|   |          | 3.14.1 Introduction                                    |     |

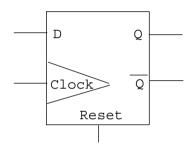

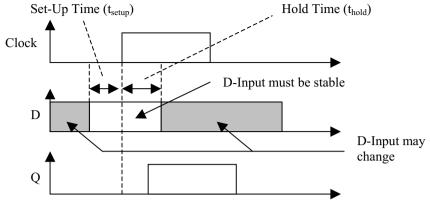

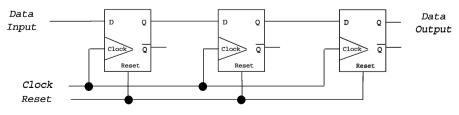

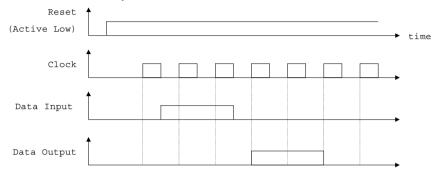

|   |          | 3.14.2 D-Type Bistable                                 |     |

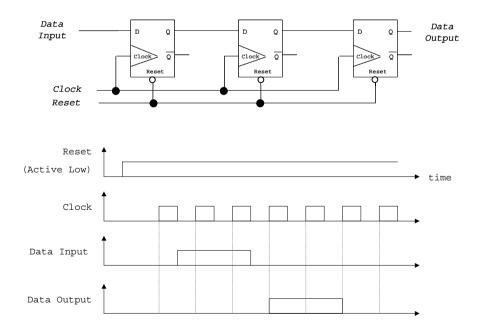

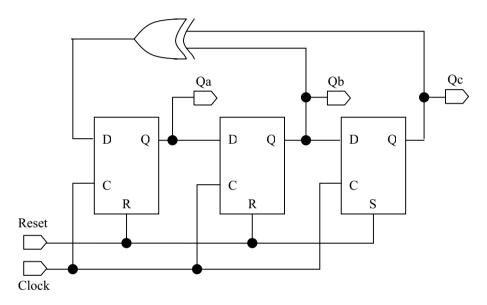

|   |          | 3.14.3 Example Circuits                                |     |

|   | 3.15     | DfT and BIST Overview                                  |     |

|   | 3.16     | Future Directions                                      |     |

|   | 3.17     | Summary                                                |     |

|   | 3.18     | References                                             |     |

|   |          | cises                                                  |     |

|   | LAUR     |                                                        |     |

| 4 | Mem   | nory Test                                | 95  |

|---|-------|------------------------------------------|-----|

|   | 4.1   | Introduction                             | 95  |

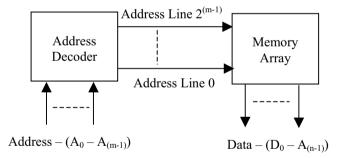

|   |       | 4.1.1 Memory Overview                    | 95  |

|   |       | 4.1.2 Read Only Memory (ROM)             | 98  |

|   |       | 4.1.3 Random Access Memory (RAM)         |     |

|   | 4.2   | SRAM Structure                           |     |

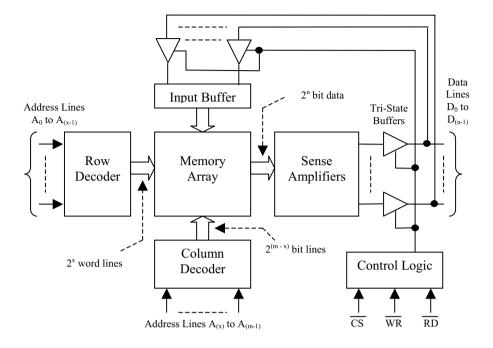

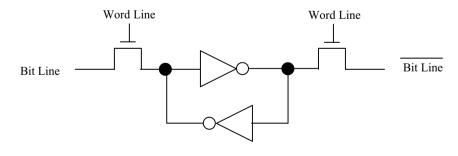

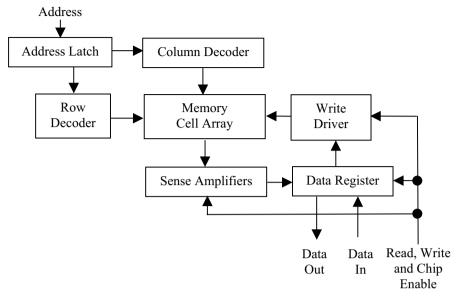

|   | 4.3   | DRAM Structure                           |     |

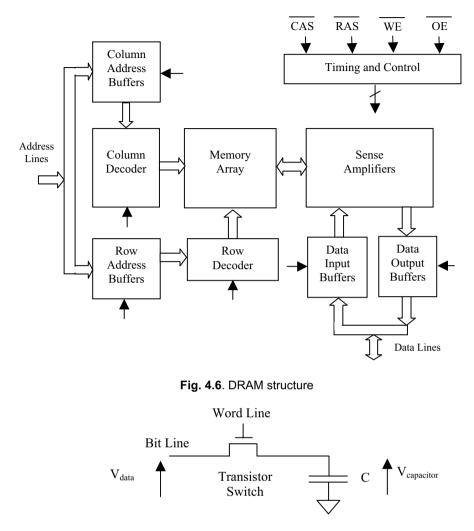

|   | 4.4   | ROM structure                            |     |

|   | 4.5   | Fault Modelling in Memory                |     |

|   | 4.6   | RAM Test Algorithms                      |     |

|   |       | 4.6.1 Introduction                       |     |

|   |       | 4.6.2 Notation                           |     |

|   |       | 4.6.3 RAM Test Algorithms                |     |

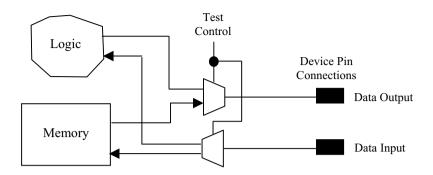

|   | 4.7   | Memory Access for Test                   |     |

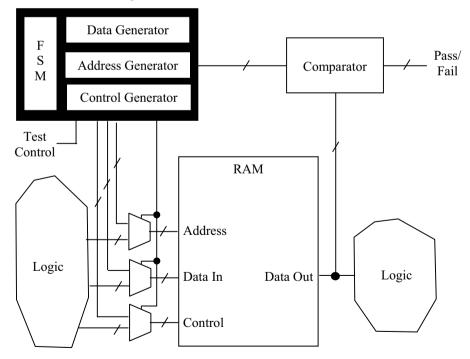

|   | 4.8   | Memory BIST                              |     |

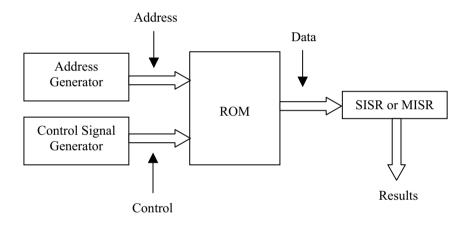

|   | 4.9   | ROM Test                                 |     |

|   | 4.10  | Future Directions                        |     |

|   | 4.11  | Summary                                  |     |

|   | 4.12  | References                               |     |

|   | Exerc | cises                                    |     |

|   |       |                                          |     |

| 5 | Anal  | logue Test                               |     |

|   | 5.1   | Introduction                             | 123 |

|   | 5.2   | Analogue Circuit Overview                |     |

|   | 5.3   | Measuring Analogue Parameters            |     |

|   | 5.4   | Coherent Sampling                        |     |

|   | 5.5   | Functional vs Structural Test            |     |

|   | 5.6   | Fault Modelling in Analogue              | 136 |

|   | 5.7   | Future Directions                        |     |

|   | 5.8   | Summary                                  |     |

|   | 5.9   | References                               | 139 |

|   | Exerc | cises                                    | 141 |

|   |       |                                          |     |

| 6 | Mixe  | ed-Signal Test                           | 143 |

|   | 6.1   | Introduction                             | 143 |

|   | 6.2   | Mixed-Signal Circuit Test Overview       | 145 |

|   | 6.3   | Fault Modelling in Mixed-Signal Circuits | 147 |

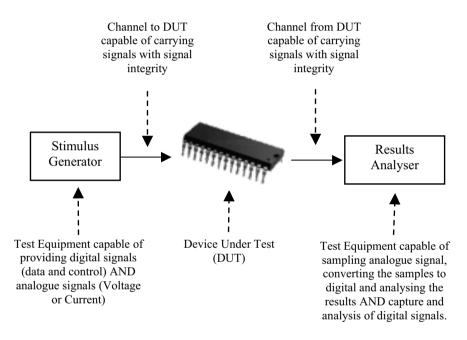

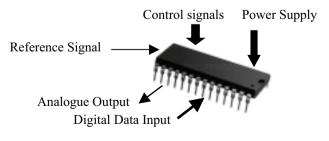

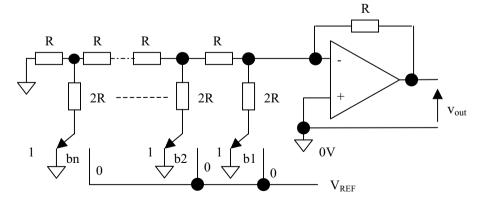

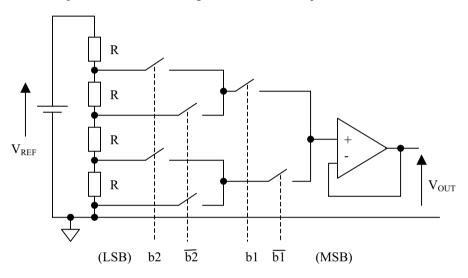

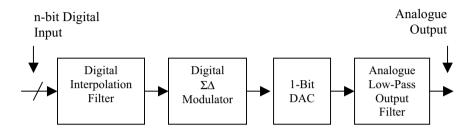

|   | 6.4   | DAC Architectures                        | 148 |

|   |       | 6.4.1 Introduction                       |     |

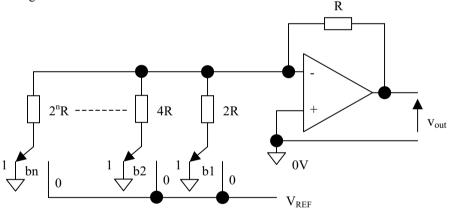

|   |       | 6.4.2 Binary-Weighted Resistor DAC       | 151 |

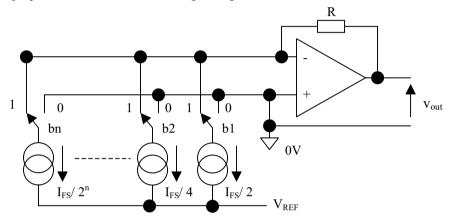

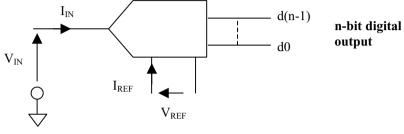

|   |       | 6.4.3 Binary-Weighted Current DAC        |     |

|   |       | 6.4.4 R-2R Ladder DAC                    |     |

|   |       | 6.4.5 Resistor String DAC                | 153 |

|   |       | 6.4.6 Segmented Resistor String DAC      |     |

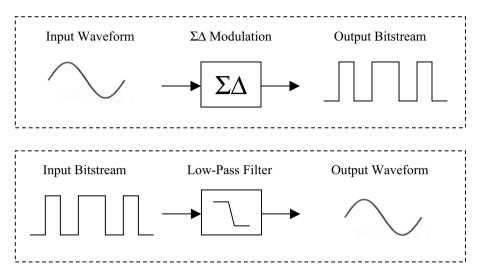

|   |       | 6.4.7 Sigma-Delta ( $\Sigma\Delta$ ) DAC |     |

|   |       | 6.4.8 Hybrid DAC                         |     |

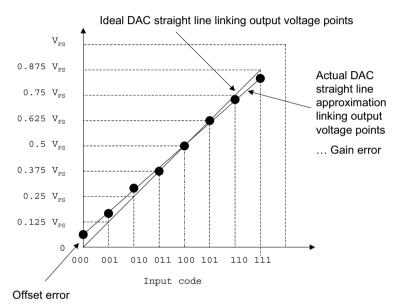

|   | 6.5   | DAC Test                                 |     |

|   |       |                                          |     |

|   |                          | 6.5.1 Introduction                                                                                                                                                                                                                       |                          | 5                                    |

|---|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------|

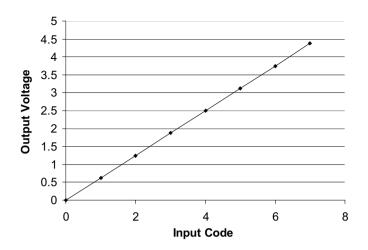

|   |                          | 6.5.2 Static (DC) Tests                                                                                                                                                                                                                  |                          | 5                                    |

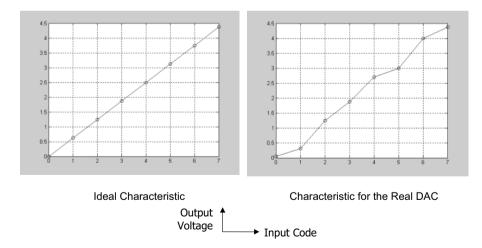

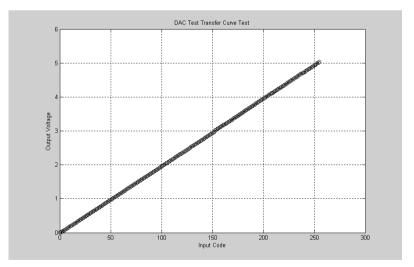

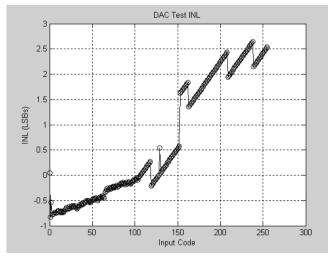

|   |                          | 6.5.3 Transfer Curve Tests                                                                                                                                                                                                               |                          | 6                                    |

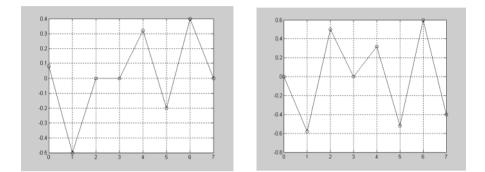

|   |                          | 6.5.4 Dynamic Tests                                                                                                                                                                                                                      |                          | 8                                    |

|   |                          | 6.5.5 FFT, SNR, SFDR and THD                                                                                                                                                                                                             |                          | 9                                    |

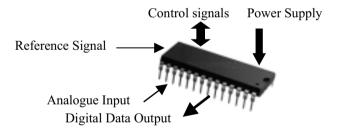

|   | 6.6                      | ADC Architectures                                                                                                                                                                                                                        |                          |                                      |

|   |                          | 6.6.1 Introduction                                                                                                                                                                                                                       |                          | 9                                    |

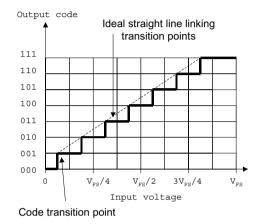

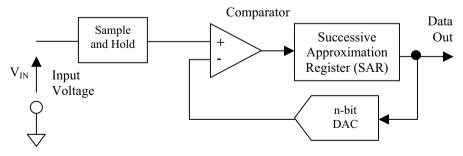

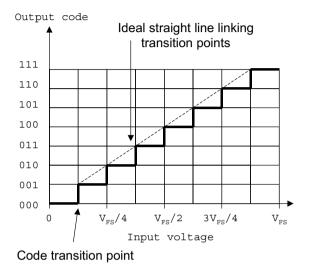

|   |                          | 6.6.2 Successive Approximation AD                                                                                                                                                                                                        | C161                     | 1                                    |

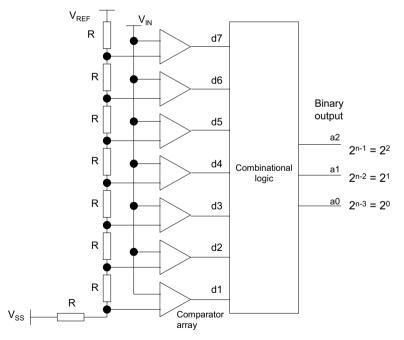

|   |                          |                                                                                                                                                                                                                                          | ope) ADC162              |                                      |

|   |                          |                                                                                                                                                                                                                                          |                          |                                      |

|   |                          | 6.6.5 Sigma-Delta ( $\Sigma\Delta$ ) ADC                                                                                                                                                                                                 |                          | 3                                    |

|   | 6.7                      | ADC test                                                                                                                                                                                                                                 |                          |                                      |

|   |                          |                                                                                                                                                                                                                                          |                          |                                      |

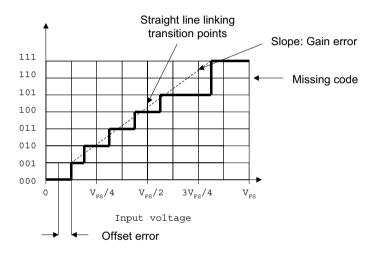

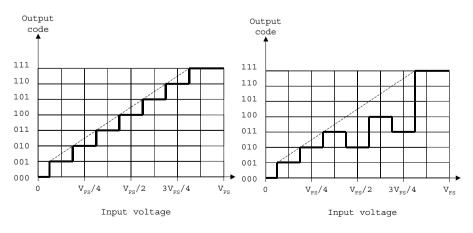

|   |                          |                                                                                                                                                                                                                                          | e Tests164               |                                      |

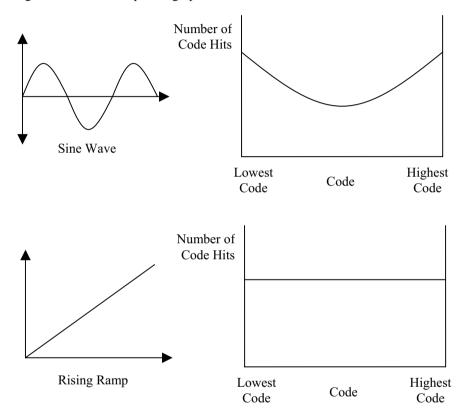

|   |                          |                                                                                                                                                                                                                                          |                          |                                      |

|   |                          |                                                                                                                                                                                                                                          |                          |                                      |

|   |                          |                                                                                                                                                                                                                                          |                          |                                      |

|   | 6.8                      | Future Directions                                                                                                                                                                                                                        |                          |                                      |

|   | 6.9                      | Summary                                                                                                                                                                                                                                  |                          | 9                                    |

|   | 6.10                     | References                                                                                                                                                                                                                               |                          |                                      |

|   | Exerc                    | cises                                                                                                                                                                                                                                    |                          | 1                                    |

|   |                          |                                                                                                                                                                                                                                          |                          |                                      |

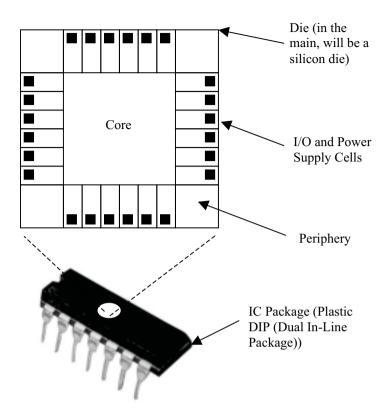

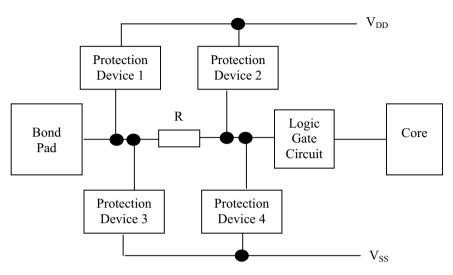

| 7 | Inpu                     | t-Output Test                                                                                                                                                                                                                            |                          | 5                                    |

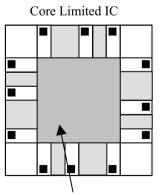

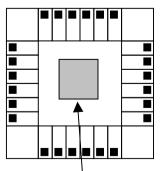

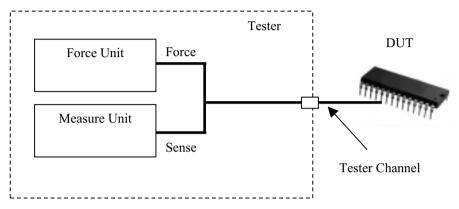

|   | $7.1^{-1}$               | Introduction                                                                                                                                                                                                                             |                          | 5                                    |

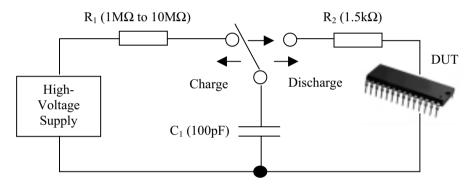

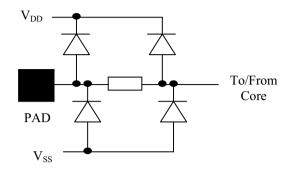

|   | 7.2                      | Electrical Overstress and Electrostatic I                                                                                                                                                                                                | Discharge178             | 8                                    |

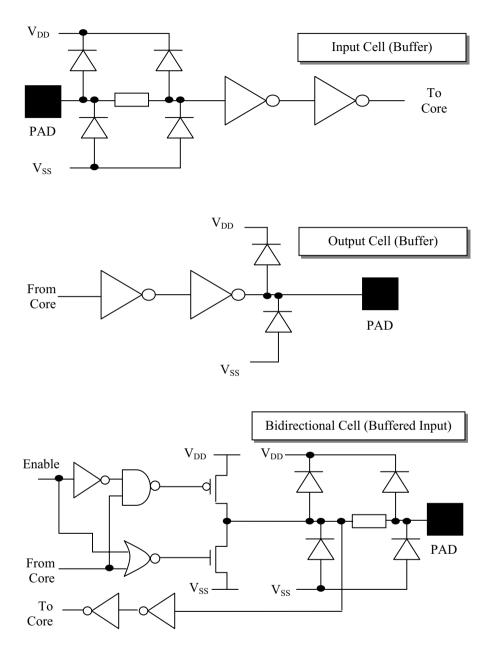

|   | 7.3                      | Digital I/O Structures                                                                                                                                                                                                                   |                          | 9                                    |

|   |                          | 7.3.1 Introduction                                                                                                                                                                                                                       |                          | 9                                    |

|   |                          | 7.3.2 CMOS Inverter                                                                                                                                                                                                                      |                          | 2                                    |

|   |                          | 7.3.3 Logic Design Variants                                                                                                                                                                                                              |                          | 6                                    |

|   |                          | 7.3.4 TTL Family Variants                                                                                                                                                                                                                |                          | 6                                    |

|   |                          | 7.3.5 CMOS Family Variants                                                                                                                                                                                                               |                          | 7                                    |

|   |                          |                                                                                                                                                                                                                                          |                          |                                      |

|   | 7.4                      | Digital I/O Test                                                                                                                                                                                                                         |                          | 8                                    |

|   |                          | 7.4.1 Introduction                                                                                                                                                                                                                       |                          | 8                                    |

|   |                          | 7.4.2 Measuring Input Cell Voltage a                                                                                                                                                                                                     | and Current19            | 1                                    |

|   |                          | 7.4.3 Measuring Output Cell Voltage                                                                                                                                                                                                      |                          |                                      |

|   |                          | , the mitubuling surplus som some                                                                                                                                                                                                        | e and Current191         | I                                    |

|   |                          |                                                                                                                                                                                                                                          | e and Current19<br>ls192 |                                      |

|   |                          | 7.4.4 Dealing with Bidirectional Cell                                                                                                                                                                                                    |                          | 2                                    |

|   | 7.5                      | 7.4.4 Dealing with Bidirectional Cell                                                                                                                                                                                                    | ls                       | 2<br>2                               |

|   | 7.5<br>7.6               | 7.4.4Dealing with Bidirectional Cell7.4.5Dealing with Internal Pull-UpsAnalogue I/O StructuresAnalogue I/O Test                                                                                                                          | ls                       | 2<br>2<br>3                          |

|   |                          | <ul> <li>7.4.4 Dealing with Bidirectional Cell</li> <li>7.4.5 Dealing with Internal Pull-Ups</li> <li>Analogue I/O Structures</li> <li>Analogue I/O Test</li> <li>Future Directions</li> </ul>                                           | ls                       | 2<br>2<br>3<br>3                     |

|   | 7.6<br>7.7<br>7.8        | 7.4.4Dealing with Bidirectional Cell7.4.5Dealing with Internal Pull-UpsAnalogue I/O Structures.Analogue I/O Test.Future Directions.Summary                                                                                               | ls                       | 2<br>2<br>3<br>3<br>4                |

|   | 7.6<br>7.7               | <ul> <li>7.4.4 Dealing with Bidirectional Cell</li> <li>7.4.5 Dealing with Internal Pull-Ups</li> <li>Analogue I/O Structures</li> <li>Analogue I/O Test</li> <li>Future Directions</li> </ul>                                           | ls                       | 2<br>2<br>3<br>3<br>4                |

|   | 7.6<br>7.7<br>7.8<br>7.9 | 7.4.4Dealing with Bidirectional Cell7.4.5Dealing with Internal Pull-UpsAnalogue I/O Structures.Analogue I/O TestFuture Directions.SummaryReferences.                                                                                     | ls                       | 2<br>2<br>2<br>3<br>3<br>4<br>5      |

| 8 | 7.6<br>7.7<br>7.8<br>7.9 | <ul> <li>7.4.4 Dealing with Bidirectional Cell</li> <li>7.4.5 Dealing with Internal Pull-Ups</li> <li>Analogue I/O Structures.</li> <li>Analogue I/O Test.</li> <li>Future Directions.</li> <li>Summary.</li> <li>References.</li> </ul> | ls                       | 2<br>2<br>2<br>3<br>3<br>4<br>5<br>7 |

| 8 | 7.6<br>7.7<br>7.8<br>7.9 | 7.4.4Dealing with Bidirectional Cell7.4.5Dealing with Internal Pull-UpsAnalogue I/O Structures.Analogue I/O TestFuture Directions.SummaryReferences.                                                                                     | ls                       | 2<br>2<br>3<br>3<br>4<br>5<br>7<br>7 |

|     | 8.3          | Digital DfT                                    | 199 |

|-----|--------------|------------------------------------------------|-----|

|     |              | 8.3.1 Design Partitioning                      |     |

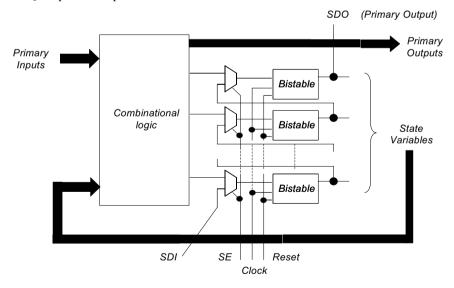

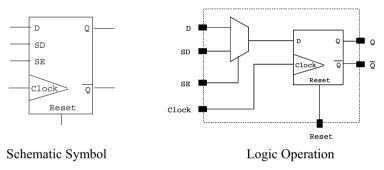

|     |              | 8.3.2 Scan Path Test                           |     |

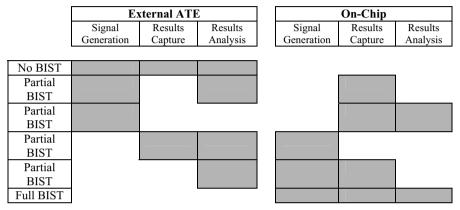

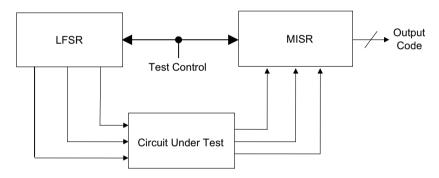

|     |              | 8.3.3 Built-In Self-Test (BIST)                |     |

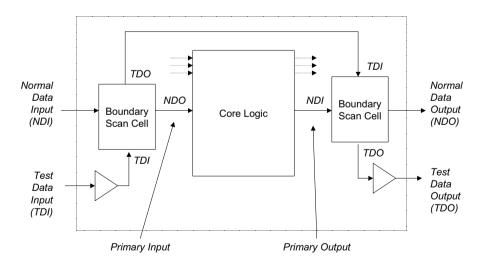

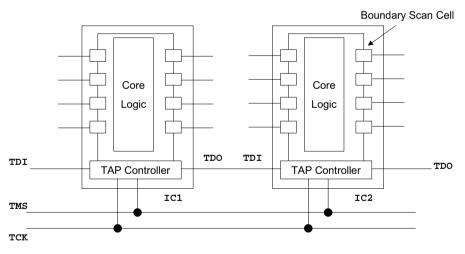

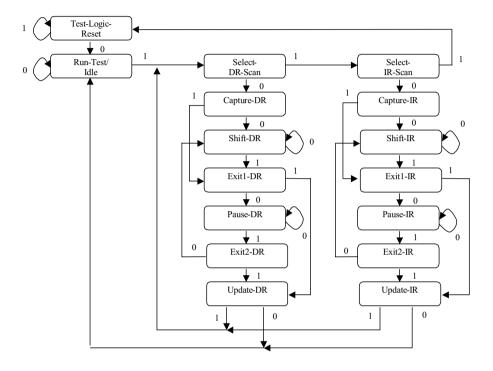

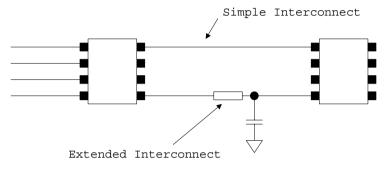

|     |              | 8.3.4 1149.1 Boundary Scan                     |     |

|     |              | 8.3.5 P1500 Core Test Standard Development     |     |

|     | 8.4          | Analogue and Mixed-Signal DfT                  |     |

|     |              | 8.4.1 Overview                                 |     |

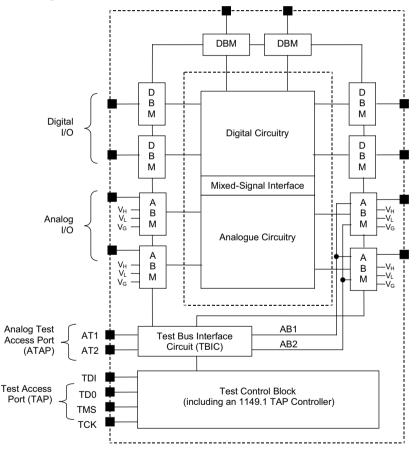

|     |              | 8.4.2 1149.4 Mixed-Signal Test Bus             |     |

|     | 8.5          | Future Directions for DfT and BIST             |     |

|     | 8.6          | Summary                                        |     |

|     | 8.7          | References                                     |     |

|     | Exerc        | cises                                          | 221 |

|     |              |                                                |     |

| 9   | Syste        | em on a Chip (SoC) Test                        |     |

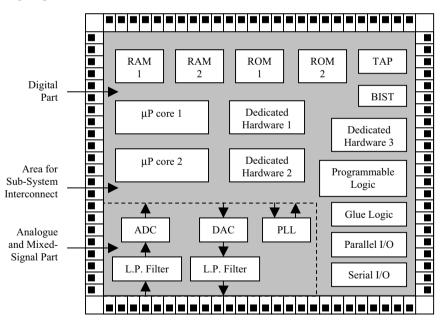

|     | 9.1          | Introduction                                   |     |

|     | 9.2          | Examples of SoC Devices                        |     |

|     | 9.3          | Test Complexity and Additional Problems        |     |

|     | 9.4          | P1500 Core Test Standard Development           |     |

|     | 9.5          | Future Directions for SoC Test                 |     |

|     | 9.6          | Summary                                        |     |

|     | 9.7          | References                                     | 232 |

| 4.0 | -            |                                                |     |

| 10  |              | Pattern Generation and Fault Simulation        |     |

|     | 10.1         | Introduction                                   |     |

|     | 10.2         | Test Pattern Generation                        |     |

|     | 10.3         | Digital Fault Simulation                       |     |

|     | 10.4         | Analogue Fault Simulation                      |     |

|     |              | Mixed-Signal Fault Simulation                  |     |

|     |              | Issues with Fault Simulation                   |     |

|     |              | Circuit vs Behavioural Level Fault Simulation  |     |

|     |              | Future Directions                              |     |

|     |              | Summary                                        |     |

|     |              | ) References                                   |     |

|     | Exerc        | cises                                          | 253 |

| 11  | Anto         | matic Test Equipment (ATE) and Production Test | 257 |

| 11  | Auto<br>11.1 | Introduction                                   |     |

|     |              | Production Test Flow                           |     |

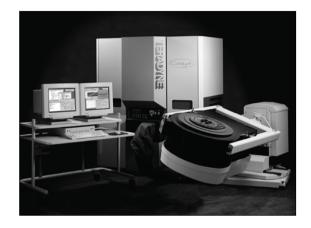

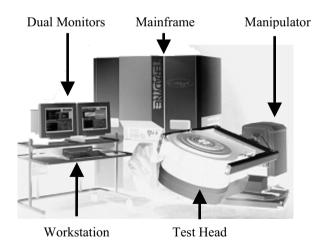

|     | 11.2         | ATE Systems                                    |     |

|     | 11.5         | Future Directions for ATE Systems              |     |

|     | 11.4         | Summary                                        |     |

|     | 11.5         | References                                     |     |

|     | 11.0         |                                                | 203 |

| 12  | Test         | Economics                                      |     |

| _   | 12.1         | Introduction                                   |     |

|     | 12.2         | Purpose of a Test Economics Model              |     |

|     |              | -                                              |     |

| 12.3 | Test Economics Model Development |     |

|------|----------------------------------|-----|

|      | Summary                          |     |

| 12.5 | References                       | 274 |

#### Appendices

| A | Intro | duction to VHDL                           |

|---|-------|-------------------------------------------|

|   | A.1   | Introduction                              |

|   | A.2   | Entities and Architectures                |

|   | A.3   | Libraries, Packages and Configurations    |

|   | A.4   | VHDL Testbench                            |

|   | A.5   | References                                |

| В | Intro | duction to Verilog <sup>®</sup> -HDL      |

|   | B.1   | Introduction                              |

|   | B.2   | Verilog <sup>®</sup> -HDL Modules         |

|   | B.3   | Verilog <sup>®</sup> -HDL Testfixture     |

|   | B.4   | Data Types                                |

|   | B.5   | Lexical Conventions                       |

|   | B.6   | Example                                   |

|   | В.7   | References                                |

|   | _     |                                           |

| С |       | duction to Spice                          |

|   | C.1   | Introduction                              |

|   | C.2   | Scope of Discussions                      |

|   | C.3   | Input File Format                         |

|   | C.4   | Commenting the Input File                 |

|   | C.5   | Analyses                                  |

|   | C.6   | Input Stimuli                             |

|   | C.7   | Defining Components in Spice              |

|   | C.8   | Scale Factors in Spice                    |

|   | C.9   | Dealing with Design Hierarchy290          |

|   | C.10  | References                                |

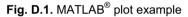

| D | Intro | duction to MATLAB <sup>®</sup>            |

| - | D.1   | Introduction                              |

|   | D.2   | Interactive and Batch Modes               |

|   | D.3   | Scalar Variables and Arithmetic Operators |

|   | D.4   | Useful Commands                           |

|   | D.5   | Matrix Variables and Arithmetic Operators |

|   | D.6   | Signals and Results Plotting              |

|   | D.7   | References                                |

| - |       |                                           |

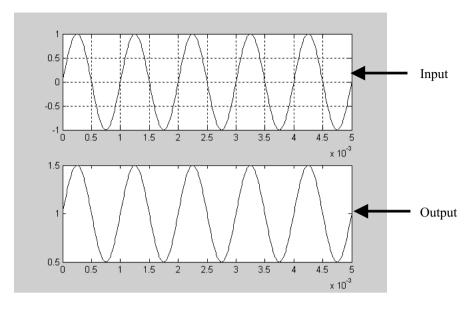

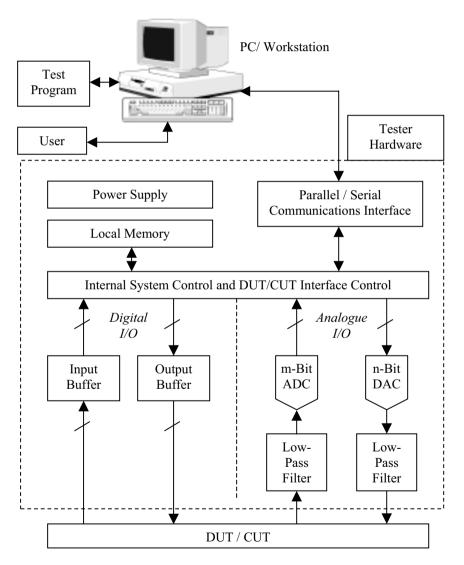

| E |       | ware Experimentation                      |

|   | E.1   | Introduction                              |

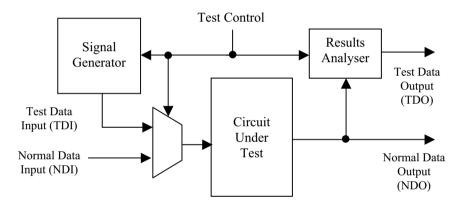

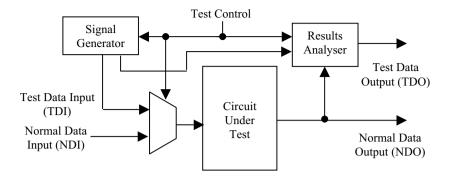

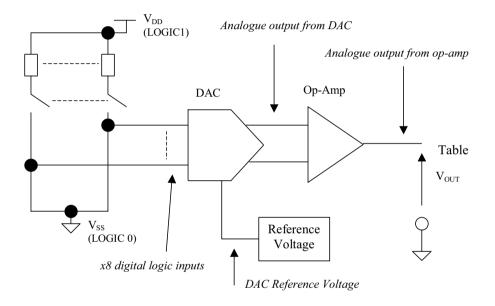

|   | E.2   | Generic Tester Arrangement                |

|   | E.3   | CPLD Based Logic and Memory Tester        |

|    | E.4     | References                                  | 302 |

|----|---------|---------------------------------------------|-----|

| F  |         | L Simulation Examples                       |     |

|    | F.1     | Introduction                                | 303 |

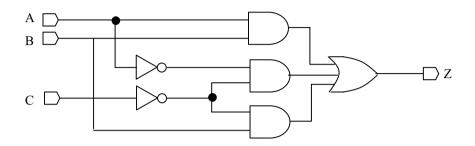

|    | F.2     | 2-Input Combinational Logic Circuit         | 305 |

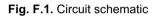

|    | F.3     | 8-Input Priority Encoder                    | 308 |

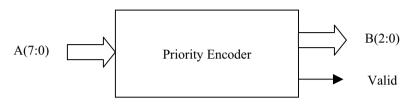

|    | F.4     | 3-Bit Binary Counter                        | 311 |

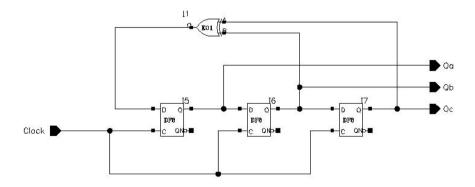

|    | F.5     | 3-Bit Linear Feedback Shift Register (LFSR) | 314 |

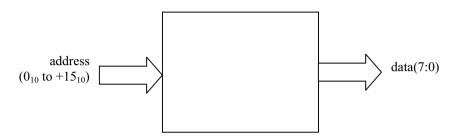

|    | F.6     | Simple 4 x 8-Bit ROM                        |     |

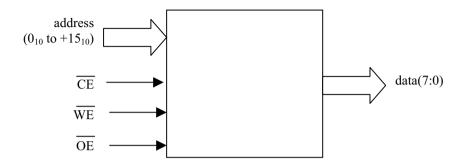

|    | F.7     | Simple 4 x 8-Bit RAM                        |     |

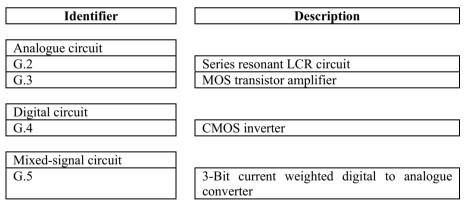

| G  | HSPI    | ICE <sup>®</sup> Simulation Examples        | 323 |

|    | G.1     | Introduction                                |     |

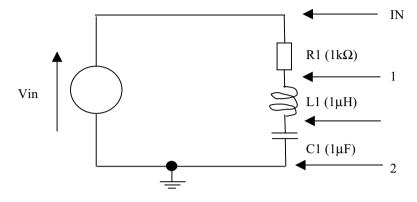

|    | G.2     | Series Resonant LCR Circuit                 | 324 |

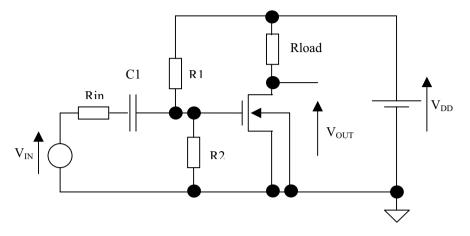

|    | G.3     | MOS Transistor Amplifier                    |     |

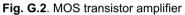

|    | G.4     | CMOS Inverter.                              |     |

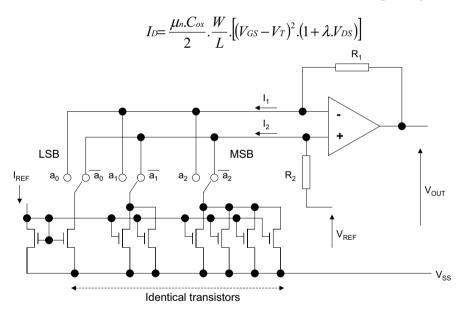

|    | G.5     | 3-Bit DAC                                   |     |

| н  | МАТ     | <b>TLAB<sup>®</sup> Simulation Examples</b> |     |

|    | H.1     | Introduction                                |     |

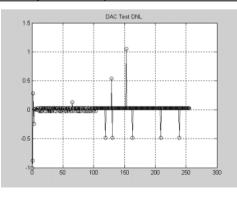

|    | H.2     | DAC example                                 |     |

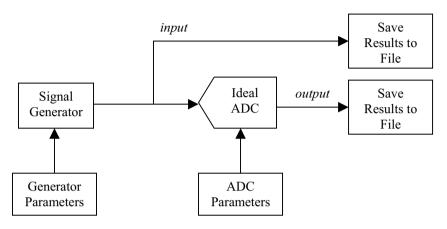

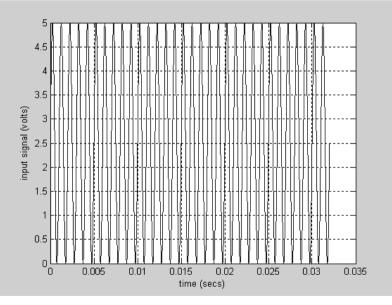

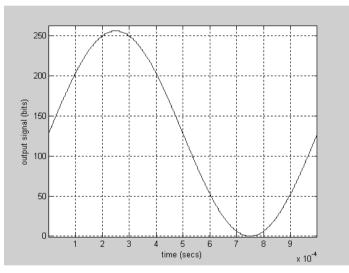

|    | H.3     | ADC example                                 |     |

| I  | Jour    | nals, Conferences and Organisations         | 341 |

| Bi | bliogra | aphy                                        | 345 |

| In | dex     |                                             | 359 |

#### Abbreviations

| ABM    | Analog Boundary Module                  |

|--------|-----------------------------------------|

| AC     | Alternating Current                     |

| ADC    | Analog(ue) to Digital Converter         |

| ALU    | Arithmetic and Logic Unit               |

| AMS    | Analog(ue) and Mixed-Signal /           |

|        | Austria Mikro Systems                   |

| ANSI   | American National Standards Institute   |

| ARM    | Advanced RISC Machines                  |

| ASIC   | Application Specific Integrated Circuit |

| ASSP   | Application Specific Standard Product   |

| ATE    | Automatic Test Equipment                |

| ATPG   | Automatic Test Program Generation       |

| AWG    | Arbitrary Waveform Generator            |

|        |                                         |

| BiCMOS | Bipolar and CMOS                        |

| BICS   | Built-In Current Sensor                 |

| BILBO  | Built-In Logic Block Observer           |

| BISR   | Built-In Self-Repair                    |

| BIST   | Built-In Self-Test                      |

| BSDL   | Boundary Scan Description Language      |

| BST    | Boundary Scan Test                      |

|        |                                         |

| CAD    | Computer Aided Design                   |

| CAT    | Computer Aided Test                     |

| CDM    | Charged Device Model                    |

| CF     | Coupling Fault                          |

| CIF    | Caltech Intermediate Format             |

| CISC   | Complex Instruction Set Computer        |

| CMOS   | Complementary MOS                       |

| COTS   | Commercial Off The Shelf                |

| CPLD   | Complex PLD                             |

| CPU    | Central Processing Unit                 |

|        |                                         |

| CTFT      | Continuous Time Fourier Transform                    |

|-----------|------------------------------------------------------|

| CTL       | Core Test Language                                   |

| CUT       | Circuit Under Test                                   |

| DAC       | Digital to Analog(ue) Converter                      |

| DBM       | Digital Boundary Module                              |

| DC        | Direct Current                                       |

| DDR SDRAM | Double Data Rate SDRAM                               |

| DfD       | Design for Debug                                     |

| DFF       | D-Type Flip-Flop                                     |

| DfA       | Design for Assembly                                  |

| DfM       | Design for Manufacture                               |

| DfR       | Design for Reliability                               |

| DfT       | Design for Testability / Design for Test             |

| DFT       | Discrete Fourier Transform                           |

| DfY       | Design for Yield                                     |

| DIB       | Device Interface Board                               |

| DIL       | Dual In-Line                                         |

| DIP       | DIL Package                                          |

| DL        | Defect Level                                         |

| DNL       | Differential Non-Linearity                           |

| DPM       | Defects Per Million                                  |

| DR        | Data Register                                        |

| DRAM      | Dynamic RAM                                          |

| DRC       | Design Rules Checking                                |

| DRDRAM    | Direct Rambus DRAM                                   |

| DSM       | Deep Sub-Micron                                      |

| DSP       | Digital Signal Processor / Digital Signal Processing |

| DUT       | Device Under Test                                    |

| ECL       | Emitter Coupled Logic                                |

| EDA       | Electronic Design Automation                         |

| EDIF      | Electronic Design Interchange Format                 |

| EEPROM    | Electrically Erasable PROM                           |

| EMC       | Electromagnetic Compatibility                        |

| EMI       | Electromagnetic Interference                         |

| EOS       | Electrical Overstress                                |

| EPROM     | Erasable PROM                                        |

| ESD       | Electrostatic Discharge                              |

| ESIA      | European Semiconductor Industry Association          |

| FA        | Failure Analysis                                     |

| FET       | Field Effect Transistor                              |

| FFM       | Functional Fault Model                               |

| FFT       | Fast Fourier Transform                               |

| FMC       | Fault Model Coverage                                 |

| FPGA      | Field Programmable Gate Array                        |

| FRAM                                     | Ferromagnetic RAM                                                                                                                                                                                                                            |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FSM                                      | Finite State Machine                                                                                                                                                                                                                         |

| GaAs                                     | Gallium Arsenide                                                                                                                                                                                                                             |

| GAL                                      | Generic Array of Logic                                                                                                                                                                                                                       |

| GALPAT                                   | Galloping Patterns                                                                                                                                                                                                                           |

| GDSII                                    | GDSII Stream File Format                                                                                                                                                                                                                     |

| HBM                                      | Human Body Model                                                                                                                                                                                                                             |

| HBT                                      | Hetrojunction Bipolar Transistor                                                                                                                                                                                                             |

| HDL                                      | Hardware Description Language                                                                                                                                                                                                                |

| IC                                       | Integrated Circuit                                                                                                                                                                                                                           |

| $I_{CC}$                                 | Power supply current (into $V_{CC}$ pin for Bipolar circuits)                                                                                                                                                                                |

| ICT                                      | In-Circuit Test                                                                                                                                                                                                                              |

| $I_{DD}$                                 | Power supply current (into $V_{DD}$ pin for CMOS circuits)                                                                                                                                                                                   |

| $I_{DDQ}$                                | Quiescent power supply current ( $I_{DD}$ )                                                                                                                                                                                                  |

| $I_{EE}$                                 | Power supply current (out of $V_{EE}$ pin for Bipolar circuits)                                                                                                                                                                              |

| IEE                                      | The Institution of Electrical Engineers                                                                                                                                                                                                      |

| IEEE                                     | Institute of Electrical and Electronics Engineers                                                                                                                                                                                            |

| IFA                                      | Inductive Fault Analysis                                                                                                                                                                                                                     |

| IIC ( $I^2C$ )                           | Inter-IC Bus                                                                                                                                                                                                                                 |

| IMAPS                                    | International Microelectronics and Packaging Society                                                                                                                                                                                         |

| INL                                      | Integral Non-Linearity                                                                                                                                                                                                                       |

| I/O                                      | Input/Output                                                                                                                                                                                                                                 |

| IP                                       | Intellectual Property                                                                                                                                                                                                                        |

| IR                                       | Instruction Register                                                                                                                                                                                                                         |

| $I_{SS}$                                 | Power supply current (out of $V_{SS}$ pin for CMOS circuits)                                                                                                                                                                                 |

| $I_{SSQ}$                                | Quiescent power supply current ( $I_{SS}$ )                                                                                                                                                                                                  |

| ITRS                                     | International Technology Roadmap for Semiconductors                                                                                                                                                                                          |

| JEDEC<br>JEITA<br>JETAG<br>JETTA<br>JTAG | Joint Electron Device Engineering Council<br>Japan Electronics and Information Technology Industries<br>Association<br>Joint European Test Action Group<br>Journal of Electronic Testing, Theory and Applications<br>Joint Test Action Group |

| KGD                                      | Known Good Die                                                                                                                                                                                                                               |

| KSIA                                     | Korean Semiconductor Industry Association                                                                                                                                                                                                    |

| LFSR                                     | Linear Feedback Shift Register                                                                                                                                                                                                               |

| LSB                                      | Least Significant Bit                                                                                                                                                                                                                        |

| LSI                                      | Large Scale Integration                                                                                                                                                                                                                      |

| LSSD                                     | Level Sensitive Scan Design                                                                                                                                                                                                                  |

| LVS                                      | Layout vs Schematic                                                                                                                                                                                                                          |

| Matlab  | Matrix Laboratory (from The Mathworks Inc.)       |

|---------|---------------------------------------------------|

| MATS    | Modified Algorithmic Test Sequence                |

| MBIST   | Memory BIST                                       |

| MCM     | Multi-Chip Module                                 |

| MEMs    | Micro Electro-Mechanical Systems                  |

| MISR    | Multiple Input Signature Register                 |

| MM      | Machine Model                                     |

| MOS     | Machine Model<br>Metal Oxide Semiconductor        |

| MOSFET  | Metal Oxide Semiconductor Field Effect Transistor |

| MPU     | Microprocessor Unit                               |

| MPW     | Multi-Project Wafer                               |

| MS-BIST | Mixed-Signal BIST                                 |

| MSAF    | Multiple Stuck-At-Fault                           |

| MSAF    | Multiple Stack-At-Fault<br>Most Significant Bit   |

| MSCAN   | Most Significant Bit<br>Memory Scan               |

| MSCAN   | Medium Scale Integration                          |

| MUX     | Multiplexer                                       |

| MUX     | Multiplexer                                       |

| NDI     | Normal Data Input                                 |

| NDO     | Normal Data Output                                |

| nMOS    | n-channel MOS                                     |

| NRE     | Non-Recurring Engineering                         |

| NVM     | Non-Volatile Memory                               |

|         |                                                   |

| OEM     | Original Equipment Manufacturer                   |

| 00      | Object Oriented                                   |

| Op-Amp  | Operational Amplifier                             |

| ORA     | Output Response Analyser                          |

| OS      | Operating System                                  |

| OVI     | Open Verilog International                        |

| PAL     | Programmable Array of Logic                       |

| PC      | Personal Computer                                 |

| PCB     | Printed Circuit Board                             |

| PDA     | Personal Digital Assistant                        |

| PDF     | Portable Document Format                          |

| PGA     | Pin Grid Array                                    |

| PI      | Primary Input                                     |

| PIPO    | Parallel In Parallel Out                          |

| PLA     | Programmable Logic Array                          |

| PLD     | Programmable Logic Device                         |

| PLL     | Phase-Locked Loop                                 |

| pMOS    | p-channel MOS                                     |

| PMU     | Precision Measurement Unit                        |

| РО      | Primary Output                                    |

| PODEM   | Path Oriented Decision Making                     |

| PPM     | Parts Per Million                                 |

|         |                                                   |

| PROM        | Programmable ROM                                           |

|-------------|------------------------------------------------------------|

| PRPG<br>PSF | Pseudo-Random Pattern Generator<br>Pattern Sensitive Fault |

| QTAG        | Quality Test Action Group                                  |

| RAM         | Random Access Memory                                       |

| RF          | Radio Frequency                                            |

| RISC        | Reduced Instruction Set Computer                           |

| RMS         | Root Mean Squared                                          |

| ROM         | Read Only Memory                                           |

| RTD         | Round Trip Delay                                           |

| RTL         | Register Transfer Level                                    |

| RWM         | Read Write Memory (also referred to as RAM)                |

| Rx          | Receiver                                                   |

| SA0         | Stuck-At-0                                                 |

| SA1         | Stuck-At-1                                                 |

| SAF         | Stuck-At-Fault                                             |

| SDRAM       | Synchronous DRAM                                           |

| SFDR        | Spurious Free Dynamic Range                                |

| SIA         | Semiconductor Industries Association                       |

| SiGe        | Silicon Germanium                                          |

| SiP         | System in Package                                          |

| SIPO        | Serial In Parallel Out                                     |

| SISO        | Serial In Serial Out                                       |

| SISR        | Serial Input Signature Register                            |

| SLDRAM      | Synchronous-Link DRAM                                      |

| S/(N + THD) | Signal to Noise Ratio plus Total Harmonic Distortion       |

| SNR         | Signal to Noise Ratio                                      |

| SoB         | System on Board                                            |

| SoC         | System on a Chip                                           |

| SOF         | Stuck Open Fault                                           |

| SOI         | Silicon on Insulator                                       |

| SPI         | Serial Peripheral Interface                                |

| SPICE       | Simulation Program with Integrated Circuit Emphasis        |

| SPLD        | Simple PLD                                                 |

| SRAM        | Static RAM                                                 |

| SSAF        | Single Stuck-At-Fault                                      |

| SSI         | Small Scale Integration                                    |

| STC         | Semiconductor Test Consortium                              |

| STIL        | Standard Test Interface Language                           |

| TAB         | Tape Automated Bonding                                     |

| TAP         | Test Access Port                                           |

| TCE         | Thermal Coefficient of Expansion                           |

| TCK         | Test Clock                                                 |

|             |                                                            |

| TDI             | Test Data Input                                        |

|-----------------|--------------------------------------------------------|

| TDO             | Test Data Output                                       |

| TF              | Transition Fault                                       |

| TMS             | Test Mode Select                                       |

| TPG             | Test Program Generation                                |

| TRST            | Test Reset                                             |

| TSIA            | Taiwan Semiconductor Industry Association              |

| TSMC            | Taiwan Semiconductor Manufacturing Company             |

| TTL             | Transistor-Transistor Logic                            |

| Tx              | Transmitter                                            |

| UART            | Universal Asynchronous Receiver Transmitter            |

| ULSI            | Ultra Large Scale Integration                          |

| UTP             | Unit Test Period                                       |

| UUT             | Unit Under Test                                        |

| UV              | Ultraviolet                                            |

| V <sub>CC</sub> | Power Supply Voltage (positive - for Bipolar circuits) |

| V <sub>DD</sub> | Power Supply Voltage (positive - for CMOS circuits)    |

| V <sub>EE</sub> | Power Supply Voltage (negative - for Bipolar circuits) |

| VDSM            | Very deep sub-micron                                   |

| VHDL            | VHSIC Hardware Description Language                    |

| VHSIC           | Very High Speed Integrated Circuit                     |

| VLSI            | Very Large Scale Integration                           |

| V <sub>SS</sub> | Power Supply Voltage (negative - for CMOS circuits)    |

| WALKPAT         | Walking Pattern                                        |

| WSI             | Wafer Scale Integration                                |

|                 |                                                        |

#### Chapter 1

### Introduction to Integrated Circuit Test Engineering

Acknowledgement of the important role that test engineering related activities undertake within an electronic/microelectronic circuit development process is leading to the evolution of the role of test engineering and the skills set required by the test engineer within a product development team. This chapter will introduce the role of the test engineer and the need to consider the test issues throughout a design development process from design concept through to high-volume production. A seamless integration of the design, fabrication and test activities is the only realistic way forward in order to ensure that a design concept is brought through to a successful production and delivery to the end-user (customer).

#### **1.1 Introduction**

Whenever an Integrated Circuit (IC) product is developed and manufactured, the three key engineering disciplines required are:

- Design

- Fabrication

- Test

Each discipline is primarily concerned with solving a particular problem and traditionally, these have been considered in the main as separate activities with a limited interface boundary:

• The *design* [1] activity is primarily concerned with taking an IC specification (high-level, word based description of the IC operation) and translating this into a working circuit that meets a set of performance targets. The completion of this is a fully developed design that has been

2 Integrated Circuit Test Engineering: Modern Techniques

evaluated in simulation, and is in a design database format that the fabrication activity can utilise.

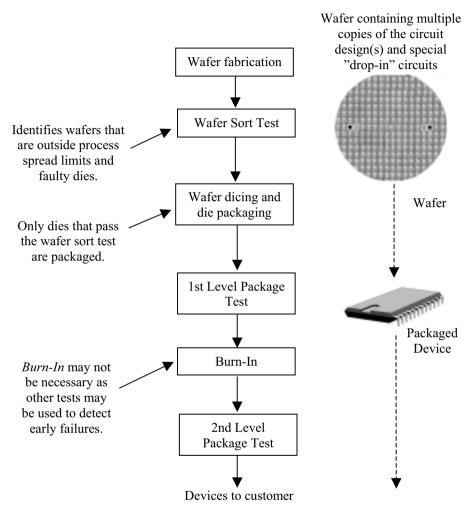

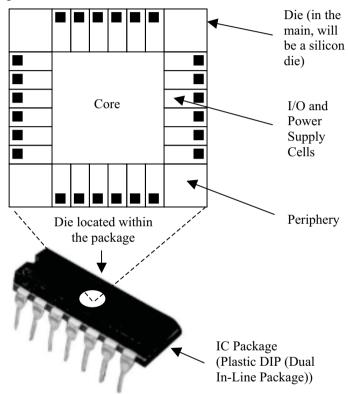

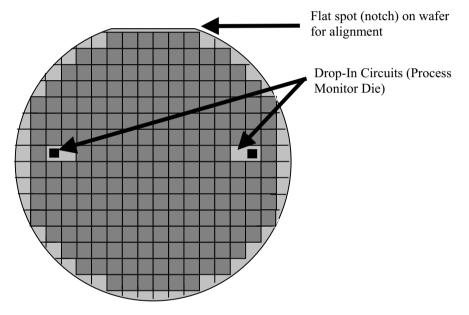

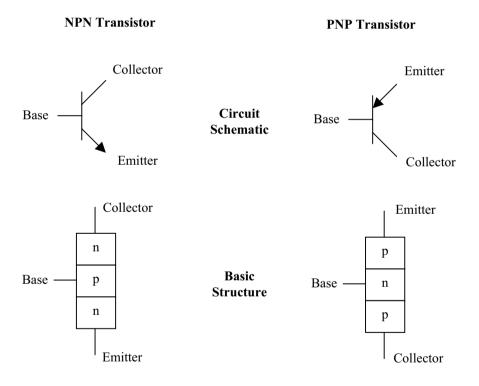

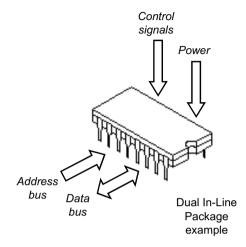

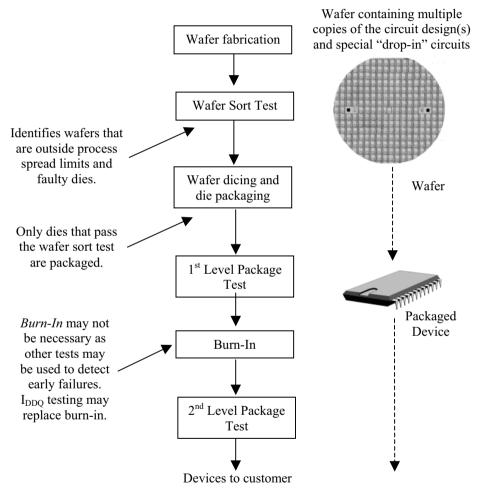

- The *fabrication* activity is primarily concerned with taking a completed design and translating this into the physical IC using the available fabrication process. The completion of this is a fabricated circuit, to be provided at the wafer level, bare die (for Multi-Chip Module (MCM) or System in Package (SiP) products), or a fully packaged device.

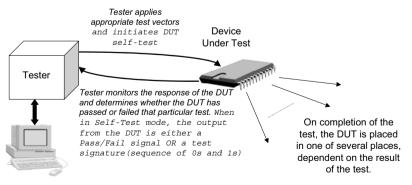

- The *test* [2-6] activity is primarily concerned in ensuring that the fabricated circuit actually meets the required set of performance targets, and that it has been fabricated without fault and within the defined fabrication process tolerances.

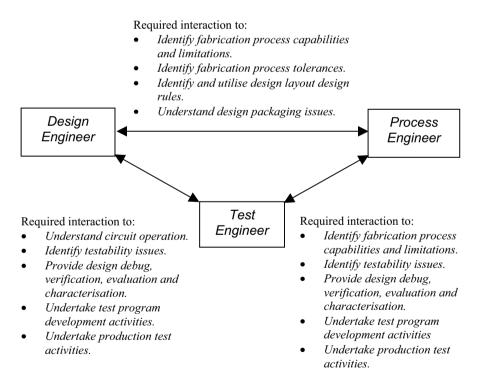

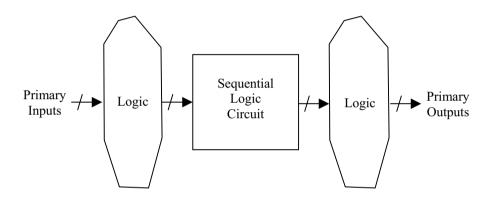

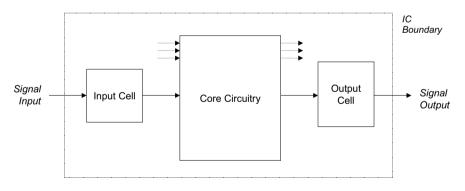

This *traditional* separation of these tasks has led to a number of barriers developing between the disciplines that have the effect of enforcing limitations in the capabilities of the interactions that must however be undertaken. These basic interactions between the disciplines are shown in Fig. 1.1.

Fig. 1.1. Design, test and fabrication interaction

The barriers that have developed between the disciplines over the years has led to a non-optimal situation, since each activity is actually interdependent on the other, and the introduction of barriers between the disciplines has limited the ability for the disciplines to communicate effectively. For example, the fact that the disciplines have been placed within different departments within organisations, have been structured with their own sets of priorities, and have evolved their own methods and terminology (the terminology may differ between disciplines even though they may describe the same thing), has been accepted in previous years. Now however, with the ever-increasing design complexities, the newer fabrication processes, the ever increasing problems for test and the need for lower product costs, this has required a major rethink and reorganisation of activities. Fortunately, over the last few years, there has been a concerted effort on behalf of the semiconductor community to remove the barriers and ensure that better approaches to product development are undertaken. This is especially so in the closer linkages between design and test. The move towards adopting a Design for Testability (DfT) approach, whereby testability issues are identified at an early stage in the design development and special test circuitry may be added to address specific test access problems, has led to the fusing of design and test disciplines into a DfT discipline.

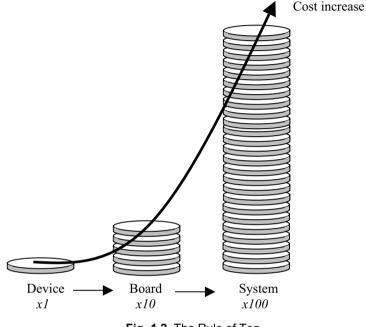

#### 1.2 The Rule of Ten

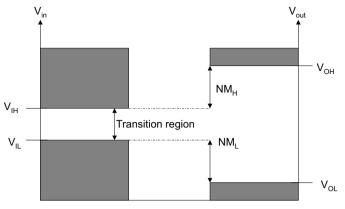

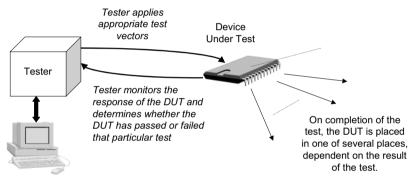

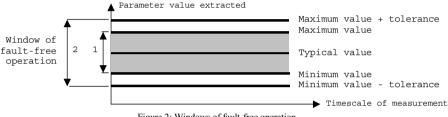

A useful indicator that is quoted in order to demonstrate the importance of test and discovering faults in an electronic circuit once it has been fabricated and before it is used, is referred to as the "*Rule of Ten*" [2], see Fig. 1.2. In this, the cost multiplies by ten every time a faulty item is not detected but is used to form a large electronic circuit or system. Whilst this is a generalisation, it identifies the cost escalation of failing to detect faults whenever an electronic circuit/system is manufactured/fabricated. Here, if the cost of detecting a faulty device (IC) when it is produced is one unit, the cost to detect that faulty device when used at the board level (PCB) is ten times that. The cost to detect that faulty board when inserted in its system is ten times the cost of detecting the faulty board at production, and so on. Hence, there is a cost escalation that must be avoided.

#### 1.3 The Evolution of Test Engineering

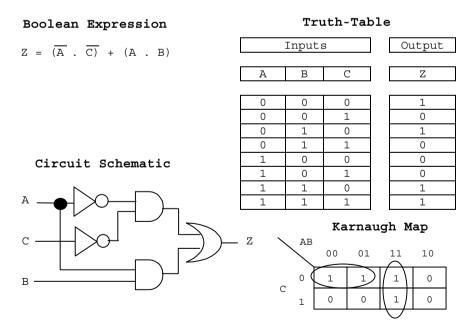

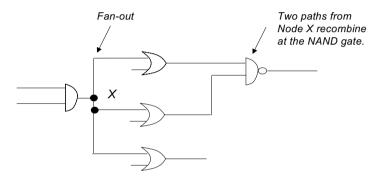

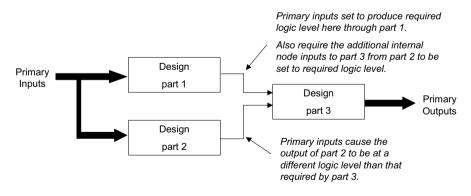

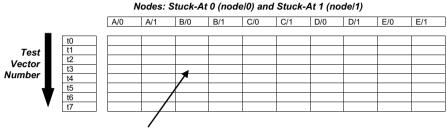

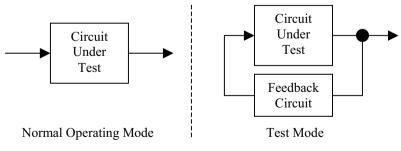

Over the last few years, the evolution of test engineering has brought it closer to design, bridging the "traditional" gap between design and test. Here, where once the design and test activities were separate and distant, the gap has been bridged by developing and adopting the "*Design for Testability*" (DfT) – or sometimes referred to as "*Design for Test*" - approach, see Fig. 1.3. Here, test is now closer to design and may influence specific details on how a design is created in order to