ACSP · Analog Circuits And Signal Processing

# Khaled Salah Mohamed

# IP Cores Design from Specifications to Production

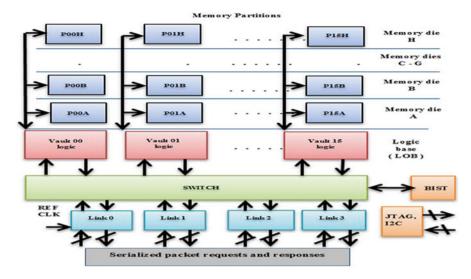

Modeling, Verification, Optimization, and Protection

# Analog Circuits and Signal Processing

Series editors Mohammed Ismail Mohamad Sawan

More information about this series at http://www.springer.com/series/7381

Khaled Salah Mohamed

# IP Cores Design from Specifications to Production

Modeling, Verification, Optimization, and Protection

Khaled Salah Mohamed Emulation Mentor Graphics Heliopolis, Egypt

ISSN 1872-082X ISSN 2197-1854 (electronic) Analog Circuits and Signal Processing ISBN 978-3-319-22034-5 ISBN 978-3-319-22035-2 (eBook) DOI 10.1007/978-3-319-22035-2

Library of Congress Control Number: 2015947256

Springer Cham Heidelberg New York Dordrecht London © Springer International Publishing Switzerland 2016

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

Springer International Publishing AG Switzerland is part of Springer Science+Business Media (www.springer.com)

### Preface

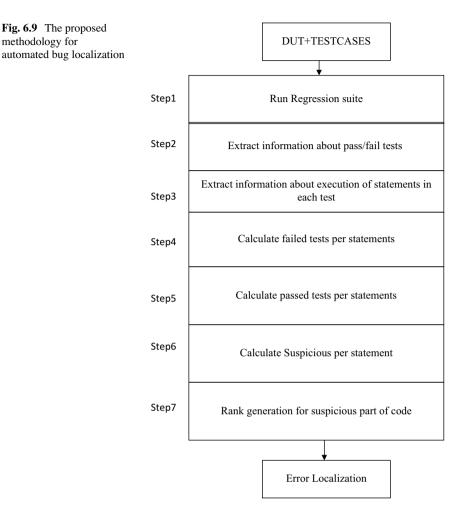

This book discusses the life cycle process of IP cores from specification to production which includes four major steps: (1) IP modeling, (2) IP verification, (3) IP optimization, and (4) IP protection. Moreover, the book presents most of the famous memory cores and controller IPs and analyzes the trade-off between them. In this book, we give an in-depth introduction to SoC buses and peripheral IPs. We explain their features and architectures in detail. Moreover, we provide a deep introduction to Verilog from both implementation and verification points of view. The book presents a simple methodology in building a reusable RTL verification environment using UVM. UVM is a culmination of well-known ideas and best practices. Moreover, it presents simple steps to verify an IP and build an efficient and smart verification environment. A SoC case study is presented to compare traditional verification with a UVM-based verification. Bug localization is a process of identifying specific locations or regions of source code that is buggy and needs to be modified to repair the defect. Bug localization can significantly reduce human effort and design cost. In this book, a novel automated coverage-based functional bug localization method for complex HDL designs is proposed, which significantly reduces debugging time. The proposed bug localization methodology takes information from regression suite as an input and produces a ranked list of suspicious parts of the code. We present an online RTL-level scan-chain methodology to reduce debugging time and effort for emulation. Run-time modifications of the values of any of the internal signals of the DUT during execution can be easily performed through the proposed online scan-chain methodology. A utility tool has been developed to help ease this process.

Heliopolis, Egypt

Khaled Salah Mohamed

# Contents

| 1 | Introduction |          |                                                    |    |  |

|---|--------------|----------|----------------------------------------------------|----|--|

| 2 | IP C         | Cores D  | esign from Specifications to Production: Modeling, |    |  |

|   |              |          | n, Optimization, and Protection                    | 13 |  |

|   | 2.1          | Introd   | uction                                             | 13 |  |

|   | 2.2          | IP Mo    | deling                                             | 13 |  |

|   |              | 2.2.1    | FPGA                                               | 15 |  |

|   |              | 2.2.2    | Processor                                          | 23 |  |

|   |              | 2.2.3    | ASIC                                               | 25 |  |

|   |              | 2.2.4    | PCB                                                | 27 |  |

|   | 2.3          | IP Ver   | ification                                          | 27 |  |

|   |              | 2.3.1    | FPGA-Based/Processor-Based IP Verification         | 28 |  |

|   |              | 2.3.2    | ASIC-Based IP Verification                         | 36 |  |

|   |              | 2.3.3    | PCB-Based IP Verification                          | 37 |  |

|   | 2.4          | IP Opt   | timization                                         | 37 |  |

|   |              | 2.4.1    | FPGA-Based IP Optimization                         | 37 |  |

|   |              | 2.4.2    | Processor-Based IP Optimization                    | 44 |  |

|   |              | 2.4.3    | ASIC-Based IP Optimization                         | 45 |  |

|   |              | 2.4.4    | PCB-Based IP Optimization                          | 46 |  |

|   | 2.5          | IP Pro   | tection                                            | 47 |  |

|   |              | 2.5.1    | FPGA-Based/Processor-Based IP Protection           | 47 |  |

|   |              | 2.5.2    | ASIC-Based IP Protection                           | 47 |  |

|   |              | 2.5.3    | PCB-Based IP Protection                            | 48 |  |

|   | 2.6          | Summ     | nary                                               | 48 |  |

|   | Refe         | rences.  |                                                    | 49 |  |

| 3 | Ana          | lyzing ( | the Trade-off Between Different Memory Cores       |    |  |

|   | and          | Contro   | ollers                                             | 51 |  |

|   | 3.1          | Introd   | uction                                             | 51 |  |

|   | 3.2          | Memo     | bry Cores                                          | 52 |  |

|   | 3.3          | Why S    | Standards?                                         | 57 |  |

|   | 3.4  | Memo    | ry Controllers                                   | 58  |

|---|------|---------|--------------------------------------------------|-----|

|   | 3.5  | Compa   | arison Between Different Memory Controllers      | 64  |

|   | 3.6  | New T   | rends in SoC Memories                            | 73  |

|   | 3.7  | Summ    | ary                                              | 73  |

|   | Refe | erences |                                                  | 76  |

| 4 | SoC  | Buses a | and Peripherals: Features and Architectures      | 77  |

|   | 4.1  |         | uction                                           | 77  |

|   | 4.2  | SoC B   | uses and Peripherals Background                  | 78  |

|   | 4.3  |         | uses: Features and Architectures                 | 80  |

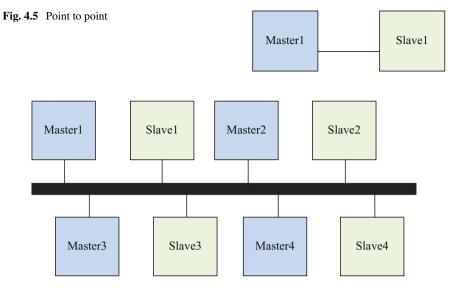

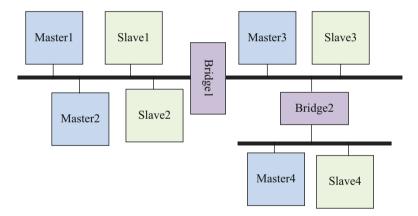

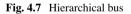

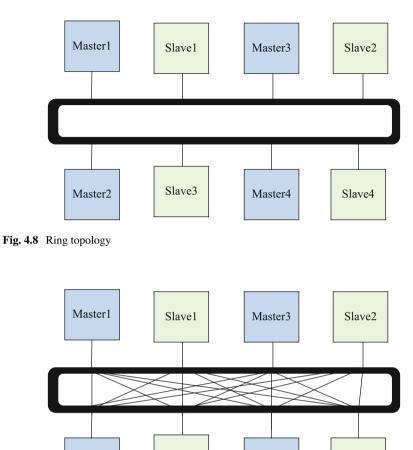

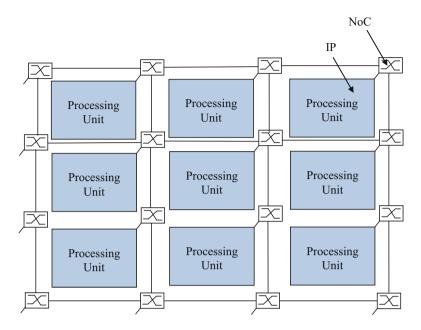

|   |      | 4.3.1   | SoC Bus Topology                                 | 80  |

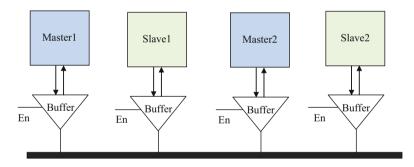

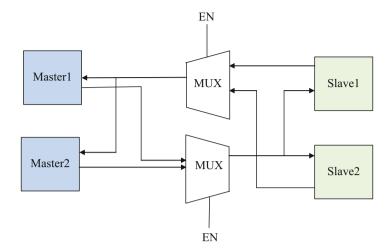

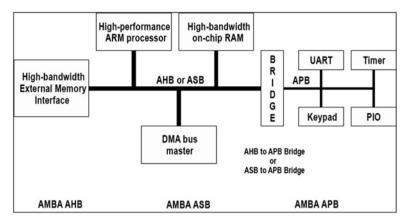

|   |      | 4.3.2   | Arbitration (Mux/Tri-State-Based)                | 83  |

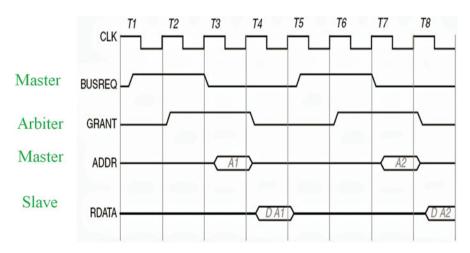

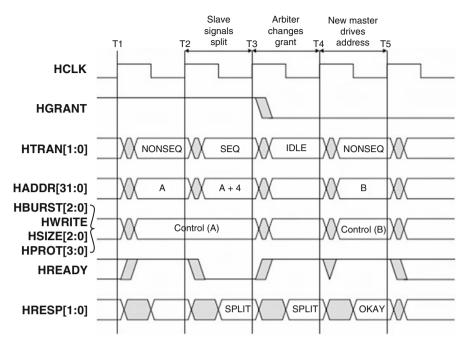

|   |      | 4.3.3   | Transfers                                        | 86  |

|   |      | 4.3.4   | Timing                                           | 89  |

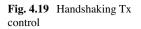

|   |      | 4.3.5   | Tx Control                                       | 90  |

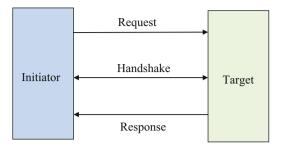

|   |      | 4.3.6   | Тх Туре                                          | 90  |

|   | 4.4  | Bus A   | rchitecture Examples                             | 91  |

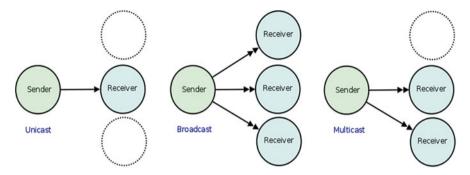

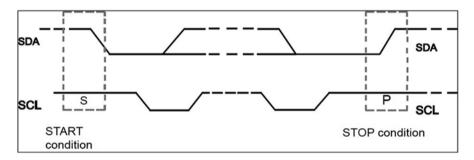

|   |      | 4.4.1   | I2C Bus                                          | 91  |

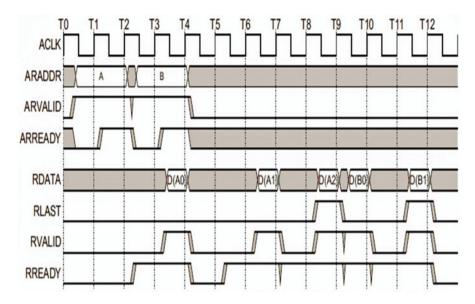

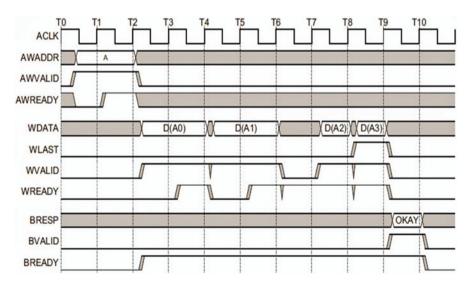

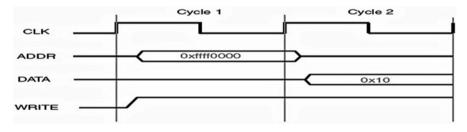

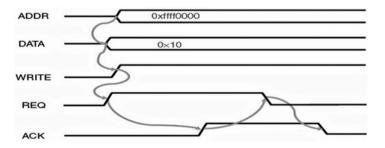

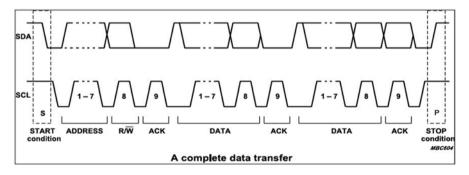

|   |      | 4.4.2   | Advanced Microcontroller Bus Architecture (AMBA) | 93  |

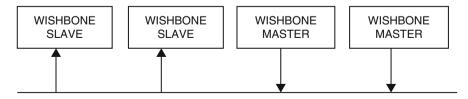

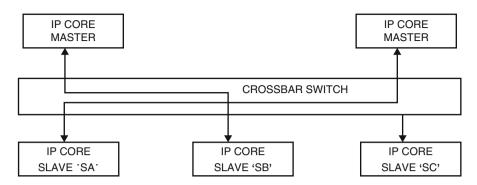

|   |      | 4.4.3   | Wishbone                                         | 95  |

|   | 4.5  | Summ    | ary                                              | 95  |

|   | Refe | erences |                                                  | 96  |

| 5 | Veri | log for | Implementation and Verification                  | 97  |

|   | 5.1  | -       | uction                                           | 97  |

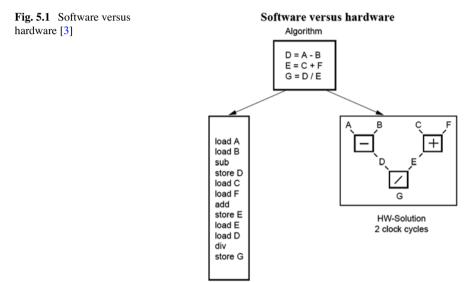

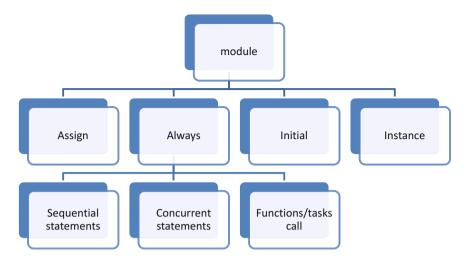

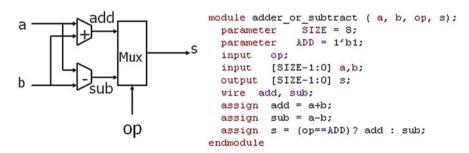

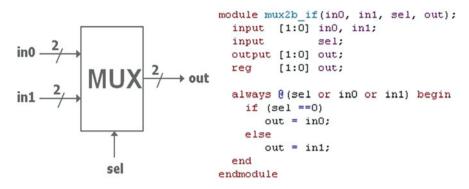

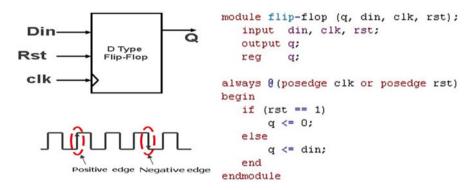

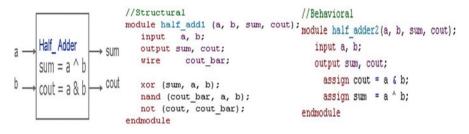

|   | 5.2  | Verilog | g for Implementation                             | 98  |

|   |      | 5.2.1   | Introduction                                     | 98  |

|   |      | 5.2.2   | Data Representation                              | 101 |

|   |      | 5.2.3   | Verilog Coding Style                             | 102 |

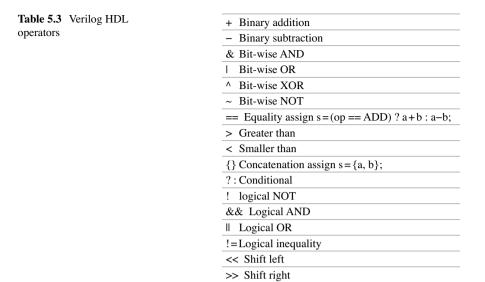

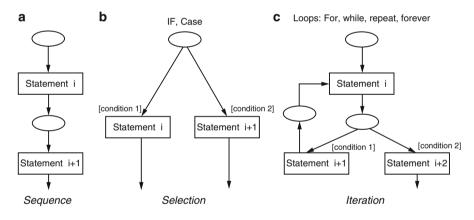

|   |      | 5.2.4   | Verilog Operators and Control Constructs         |     |

|   |      | 5.2.5   | Verilog Design Issues                            | 106 |

|   |      | 5.2.6   | Verilog Template and Reusable Code Tips          |     |

|   |      | 5.2.7   | Main Digital System Building Blocks              | 108 |

|   | 5.3  | Verilog | g for Verification                               | 108 |

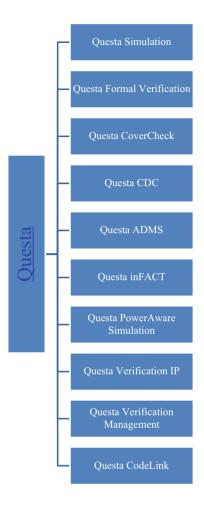

|   | 5.4  | Logic   | Simulators                                       | 111 |

|   |      | 5.4.1   | Questa Simulation                                | 112 |

|   |      | 5.4.2   | Questa Formal Verification                       | 114 |

|   |      | 5.4.3   | Questa CoverCheck                                |     |

|   |      | 5.4.4   | Questa CDC                                       | 115 |

|   |      | 5.4.5   | Questa ADMS                                      | 115 |

|   |      | 5.4.6   | Questa inFACT                                    | 116 |

|   |      | 5.4.7   | Questa Power Aware Simulation                    |     |

|   |      | 5.4.8   | Questa Verification IP                           |     |

|   |      | 5.4.9   | Questa Verification Management                   |     |

|   |      | 5.4.10  | Questa CodeLink                                  | 118 |

|   | 5.5  |         | ary                                              | 118 |

|   | Refe | erences |                                                  | 118 |

| 6 | New  | v Trend  | s in SoC Verification: UVM, Bug Localization,            |      |

|---|------|----------|----------------------------------------------------------|------|

|   | Sca  | n-C006   | 8ain-Based Methodology, GA-Based Test Generation         | 121  |

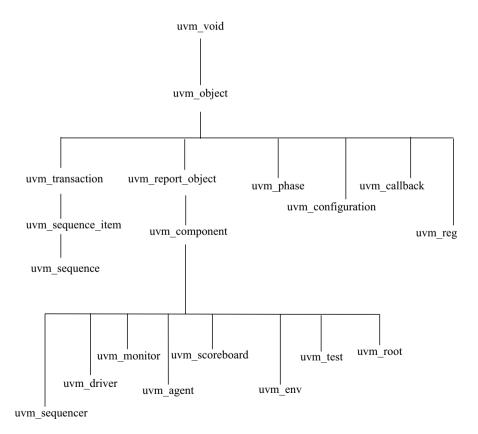

|   | 6.1  | Part I:  | UVM                                                      | 121  |

|   |      | 6.1.1    | Introduction                                             | 121  |

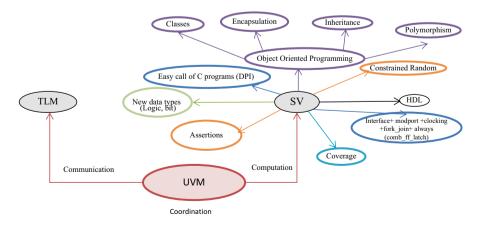

|   |      | 6.1.2    | SystemVerilog                                            | 123  |

|   |      | 6.1.3    | TLM                                                      | 126  |

|   |      | 6.1.4    | UVM                                                      | 127  |

|   |      | 6.1.5    | Summary                                                  | 133  |

|   | 6.2  | Part II  | RTL Bug Localization                                     | 133  |

|   |      | 6.2.1    | Introduction                                             | 133  |

|   |      | 6.2.2    | RTL Bug Localization                                     | 135  |

|   |      | 6.2.3    | Summary                                                  | 138  |

|   | 6.3  | Part II  | I: RTL Scan-Chain                                        | 141  |

|   |      | 6.3.1    | Introduction                                             | 141  |

|   |      | 6.3.2    | The Proposed RTL-Level Scan-Chain Methodology            | 141  |

|   |      | 6.3.3    | Summary                                                  | 143  |

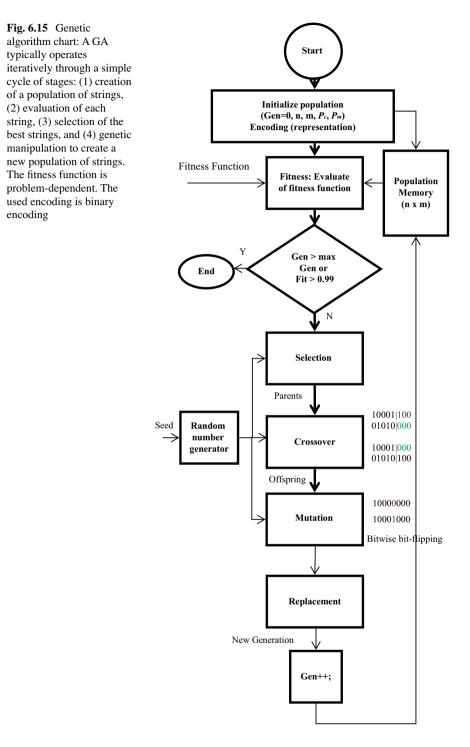

|   | 6.4  | Part I   | V: Automatic Test Generation Based on Genetic Algorithms | 144  |

|   |      | 6.4.1    | Introduction                                             | 144  |

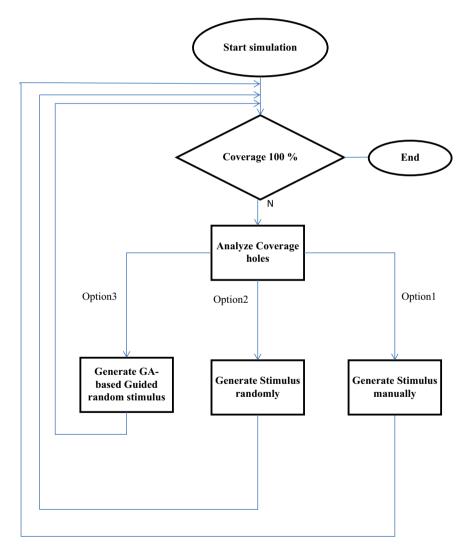

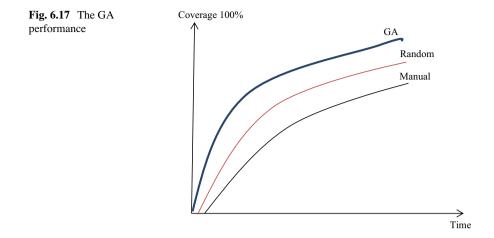

|   |      | 6.4.2    | Proposed Methodology                                     | 146  |

|   |      | 6.4.3    | Summary                                                  | 150  |

|   | Refe | erences. | •                                                        | 150  |

| _ | C    |          |                                                          | 1.50 |

| 7 | Con  | clusion  | IS                                                       | 153  |

## Chapter 1 Introduction

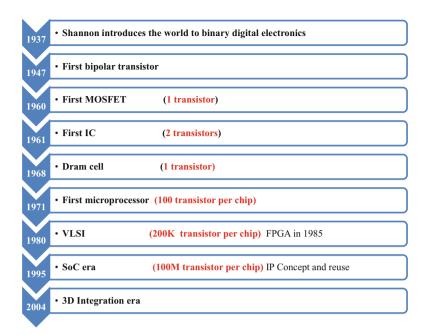

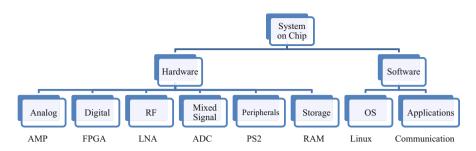

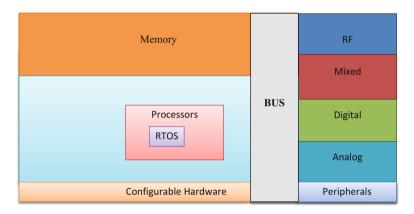

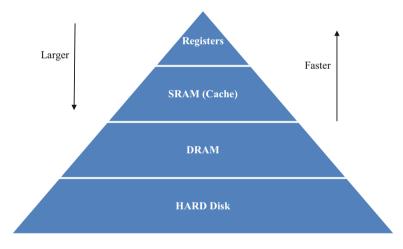

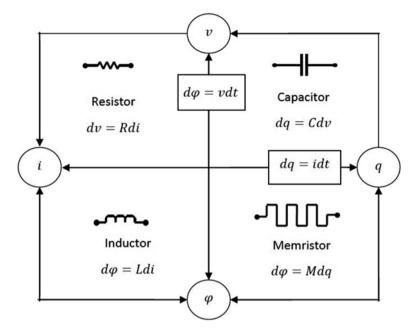

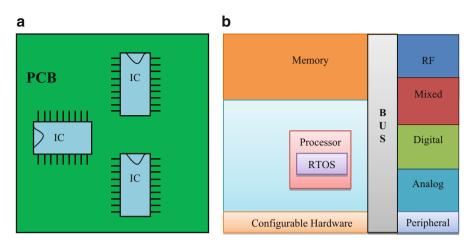

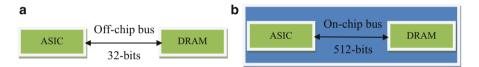

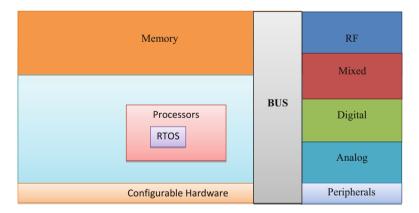

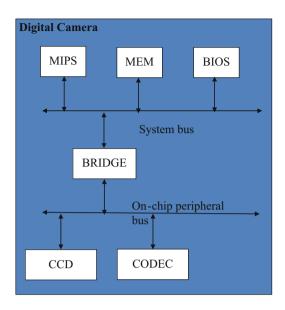

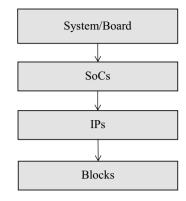

Technological progress enables more and more functionality to be integrated on a single chip. Figure 1.1 shows the most important milestones in Very-large-scale integration (VLSI), it is all about integration. In 1937, Shannon introduces the world to binary digital electronics. The first bipolar transistor was fabricated at Bell Labs in 1947 [1]. In 1960, the first MOSFET which contains one transistor was fabricated followed by the first integrated circuit (IC) which contains two transistors in 1961. The first DRAM cell was fabricated in 1968. One of the most important VLSI milestones was the fabrication of the first microprocessor which contains 100 transistors per chip in 1971. VLSI era started in 1980 by fabricating more than 200 K transistor per chip. FPGA was invented in 1985. System-on-chip (SoC) and intellectual property (IP) era started in 1995 by integration of more than 100 M transistor per chip. Recently in 2004, 3D integration era started. Table 1.1 summarizes the most important terms in VLSI. A SoC design is a "product creation process" which starts at identifying the end-user need and ends at delivering a product with enough functional satisfaction from the end user. A typical SoC contains hardware and software as depicted in Fig. 1.2. An example for the SoC architecture is shown in Fig. 1.3. Benefits of using SoC are reducing overall system cost, increasing performance, lowering power consumption, and reducing size. The advantages and disadvantages of SoC are summarized in Table 1.2 [2].

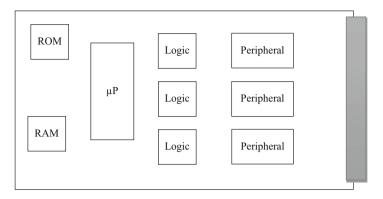

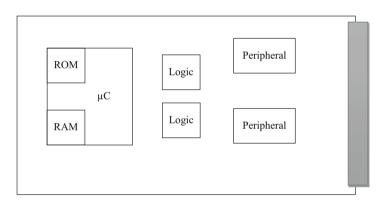

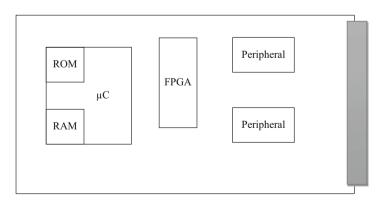

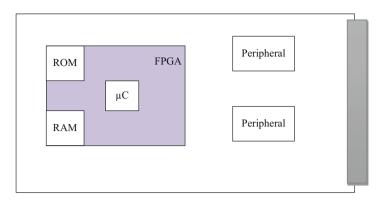

The early predecessor of a SoC was the Single Board Computer (SBC). All required logic was integrated on a single board (Fig. 1.4). When it became possible to integrate more logic into ICs, memory, and some peripherals were integrated into the microprocessor chip. The result is called "microcontroller." A single board computer with microcontrollers contains fewer chips and becomes cheaper. However, still additional logic and peripherals are necessary, since a microcontroller does not contain all required peripherals for most applications (Fig. 1.5). With the availability of programmable logic, the discrete logic ICs (costly and require board space and several extra wires) could disappear (Fig. 1.6). The FPGAs of today include microprocessor core, memories, and enough logic to include all kinds of peripherals (Fig. 1.7) [3].

Fig. 1.1 The most important milestones in VLSI: it is all about integration

| What is VLSI?      | Integration improves the performance and reduces the cost                                                      |

|--------------------|----------------------------------------------------------------------------------------------------------------|

| What is IC ?       | The VLSI final product                                                                                         |

| What is SoC ?      | It is a VLSI design style. Idea: combine several large blocks into one.                                        |

| What is IP?        | Predesigned component can be reused in different SoC. Protected through patents or copyrights                  |

| What is EDA tools? | Tools provide the design software used to create all of the world's electronic systems (VLSI, IC, IP, and SoC) |

Table 1.1 Important terms in VLSI

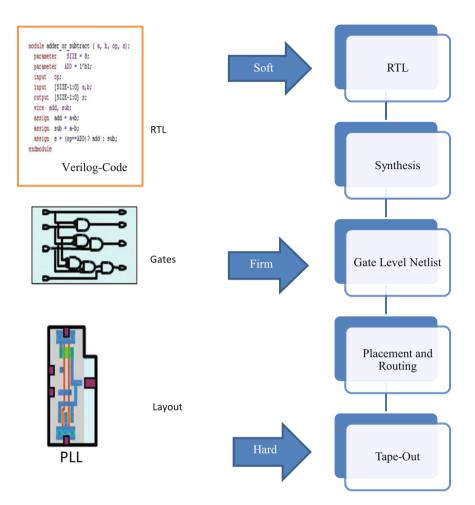

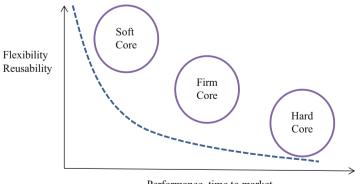

To conquer the complexity of SoC, predesigned components are used (IP reuse) [4]. Hardware IP cores have emerged as an integral part of modern SoC designs. IP cores are predesigned and preverified complex functional blocks. Based on their properties, IP cores can be distinguished into three types of cores: hard, firm, and soft as depicted in Table 1.3 [5, 6], where Soft-cores are architectural modules which are synthesizable and offer the highest degree of modification flexibility, Firm-cores are delivered as a mixture of RTL code and a technology-dependent netlist [7], and are synthesized with the rest of ASIC logic, and Hard-cores are mask and technology-dependent modules. Mapping of IP cores on VLSI design flow is shown in Fig. 1.8. IP core categories tradeoffs are summarized in Fig. 1.9.

Fig. 1.2 SoC components: it contains hardware and software. Not all software fits on hardware, we have to check the compatibility

**Fig. 1.3** An example of SoC architecture. Different components in single chip (same piece of Si). Many of the components have become standard IP

| Advantages                                       | Disadvantages                                           |

|--------------------------------------------------|---------------------------------------------------------|

| <ul> <li>Lower cost per gate</li> </ul>          | <ul> <li>Increased system complexity</li> </ul>         |

| <ul> <li>Lower power consumption</li> </ul>      | <ul> <li>Increased verification requirements</li> </ul> |

| <ul> <li>Faster circuit operation</li> </ul>     | <ul> <li>HW/SW co-design</li> </ul>                     |

| <ul> <li>More reliable implementation</li> </ul> | <ul> <li>Integration of analog &amp; RF IPs</li> </ul>  |

| <ul> <li>Smaller physical size/area</li> </ul>   |                                                         |

| <ul> <li>Greater design security</li> </ul>      |                                                         |

Table 1.2 Advantages and disadvantages of SOC

Fig. 1.4 Single board computer

Fig. 1.5 Single board computer with microcontroller

Fig. 1.6 Single board computer with microcontroller and programmable logic

Fig. 1.7 Towards SoC structure

| Table 1.3 | Classification | of hardware IP |

|-----------|----------------|----------------|

|-----------|----------------|----------------|

| IP   | Representation     | Technology                     | Optimization | Reuse     | Changes                    |

|------|--------------------|--------------------------------|--------------|-----------|----------------------------|

| Soft | RTL (HDL)          | Independent<br>(Fabless level) | Low          | Very high | Many                       |

| Firm | Gate level netlist | Independent                    | Medium       | High      | Some placement and routing |

| Hard | GDSII (layout)     | Dependent<br>(Fab level)       | Very high    | low       | No                         |

The main differences in design between IC and IP are that, in IC number of input/output (I/O), pins are limited, but in IP it is unlimited. Moreover, in IP we can parameterize IP Design, i.e., design all the functionality in hardware description language (HDL) code, but implement desired parts in the silicon (reusability). These differences are summarized in Table 1.4.

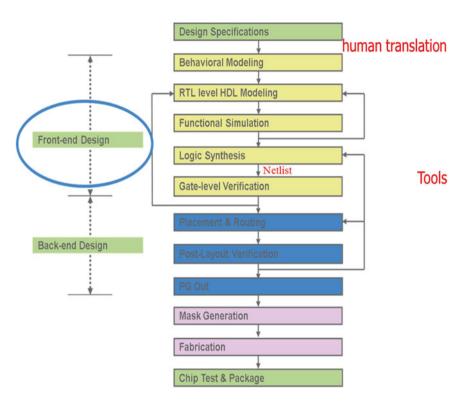

The IC design flow is shown in Fig. 1.10. The first step in IC design is design specification (what customer wants) then we convert the specification to behavioral description. The behavioral description is then converted to RTL description. Then we perform functional verification and if there are any bugs we fix it in the RTL and then do the verification again. If the functional verification is ok, we start synthesizing the RTL code and do the gate level verification. By this, the front-end design is done. The back-end design starts by placement and routing then post-layout verification, we may repeat it if there are any errors until we generate the mask and send it to the fab. After fabrication, chip testing is done.

There is a lot of SoC applications and corresponding IPs as shown in Table 1.5, where industry segments: including mobile communication, automotive, imaging, medical, and networking [8].

Fig. 1.8 IP cores in a typical VLSI design flow

Performance, time to market

Fig. 1.9 IP cores categories tradeoffs [5]

| Table 1.4   Differences |                              | IP        | IC      |

|-------------------------|------------------------------|-----------|---------|

| between IP and IC       | I/O                          | Unlimited | Limited |

|                         | Reusability/parameterization | 1         | X       |

Fig. 1.10 A simplified high-level overview of IC design flow. PG stands for pattern generation

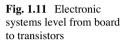

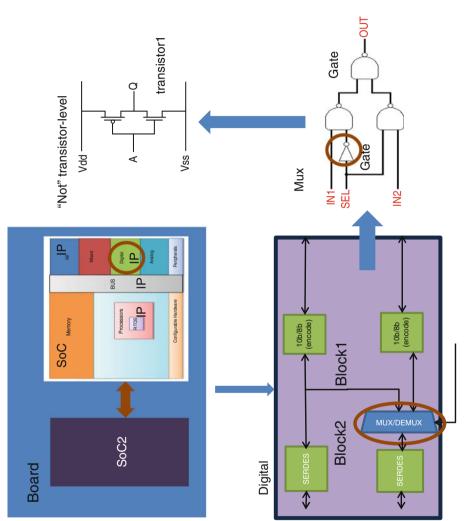

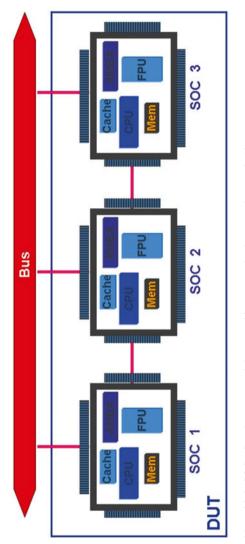

The complete picture for electronic systems is described in Figs. 1.11 and 1.12. For System with multiple SoCs, globally asynchronous locally synchronous (GALS) interconnect concept is used to simplify its design (Fig. 1.13). GALS aims at filling the gap between the purely synchronous and asynchronous domains [9].

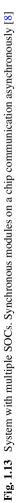

IP cores life cycle process from specification to production includes four major steps: (1) IP Modeling, (2) IP verification, (3) IP optimization, (4) IP protection. These steps are elaborated in Fig. 1.14 [11].

IP life cycle is completed with the help of computer aided design (CAD)/ electronic design automation (EDA) tools. EDA tools provide software to be used to create all of the world's electronic systems (VLSI, IC, IP, and SoC). The EDA tools play a vital rule in converting an IP specification to an IP product [10].

**Table 1.5**SOC applicationsand IPS examples

| Category      | IP                            |  |

|---------------|-------------------------------|--|

| Processors    | ARM                           |  |

| DSP           | MPEG4, Viterbi                |  |

| I/Os          | PCI, USB                      |  |

| Mixed signal  | ADC, DAC, PLL                 |  |

| Multimedia    | HDMI                          |  |

| Memories      | DRAM controller, flash memory |  |

| SoC Buses     | AHB                           |  |

| Miscellaneous | UART, Ethernet MAC            |  |

Anatomy of EDA Tools: CAD+TCAD. TCAD tools are used for fabrication process, where it simulates the electrical characteristics of semiconductor devices. The EDA tools can be categorized according to the functionality:

- 1. Design entry (capture tools)

- 2. Synthesis tools

- 3. Simulation tools

- 4. IC physical design & layout tools

- 5. IC verification tools

- 6. PCB design & analysis tools

The most famous EDA companies are SYNOPOSYS, MENTOR GRAPHICS, and CADENCE.

Fig. 1.12 Detailed electronic systems level, where a single board contains number of SoCs and each SoC consists of a number of IPs, these IPs consist of a number of blocks which consist of a number of gates. Gates consist of a number of transistors [8]

#### References

- 1. Lojek B (2007) History of semiconductor engineering. Springer, Heidelberg

- 2. Rajsuman R (2009) System-on-a-chip. Artech House, London

- 3. http://ce.sharif.edu/courses/88-89/1/ce757-1/resources/root/Slides/lec11.pdf. Accessed 2014

- 4. dic.csie.ncku.edu.tw/vlsi.../Introduction\_to\_SOC.pdf. Accessed 2014

- 5. Hoon Choi, Myung-Kyoon Yim, Jae-Young Lee, Byeong-Whee Yun, and Yun-Tae Lee (2006) Formal verification of a system-on-a-chip. ICCD 2000, Austin. pp 453–458

- Xu J (2005) Obstacle-avoiding rectilinear minimum-delay Steiner tree construction towards IP-block-based SOC design. ISQED

- 7. Kong Weio Susanto (2003) A verification platform for a system on chip. University of Glasgow, Glasgow

- Wolf M (2013) Computer as components: principles of embedded computing system design, 3rd edn. Morgan Kaufman, Burlington. ISBN 978-0-12-388436-7

- 9. Teehan P, Greenstreet M, Lemieux G (2007) A survey and taxonomy of GALS design styles. IEEE Des Test Comput 24(5):418–428

- 10. Mathaikutty DA, Shukla S (2009) Metamodeling-driven IP reuse for SoC integration and microprocessor design. Artech House, Norwood

- 11. Salah K, AbdElSalam M (2013) IP cores design from specifications to production. 25th International Conference on Microelectronics (ICM). IEEE, Beirut

## Chapter 2 IP Cores Design from Specifications to Production: Modeling, Verification, Optimization, and Protection

#### 2.1 Introduction

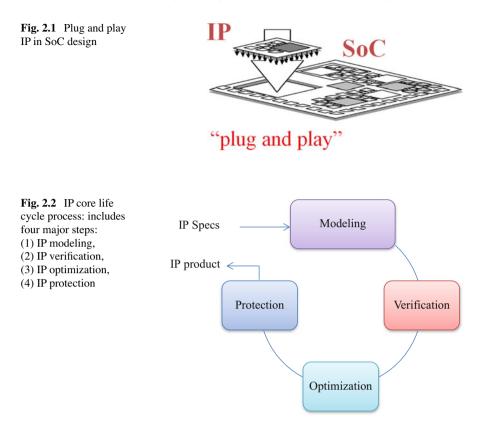

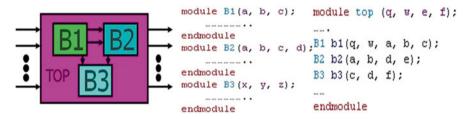

As stated earlier in the previous chapter, plug and play IP in SoC design is the recent trend in VLSI design (Fig. 2.1). IP cores life cycle process from specification to production includes four major steps: (1) IP modeling, (2) IP verification, (3) IP optimization, (4) IP protection. These steps are elaborated in Fig. 2.2. In the next sections, we will discuss each step in detail.

#### 2.2 IP Modeling

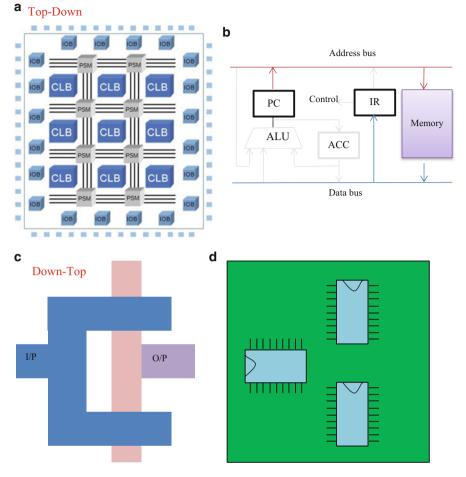

To model an IP, we have four design modeling methodologies as depicted in Fig. 2.3 [1-6]:

- 1. FPGA-based Modeling: defined by fixed functionality and connectivity of hardware elements.

- 2. Processor-based Modeling: Processor running programs written using a predefined fixed set of instructions (ISA).

- 3. ASIC-based Modeling: Silicon-level Layout.

- 4. PCB-based Modeling: it uses standard ICs such as 74xx (TTL), 40xx (CMOS), it is not VLSI, it is just discrete components.

The comparison between theses typical hardware options is shown in Table 2.1. Choice of any option depends on application and requirements.

Table 2.1

Comparison between different types of hardware

|                    | Processor    |              |                   |                         |                   |

|--------------------|--------------|--------------|-------------------|-------------------------|-------------------|

|                    | GPP          | DSP          | ASIC              | FPGA                    | PCB               |

| Examples           | μΡ, μC       | MAC, FFT     | -                 | -                       | -                 |

| Software/hardware  | Software     | Software     | Hardware          | Hardware                | Hardware          |

| Spatial/temporal   | Temporal     | Temporal     | Spatial           | Spatial                 | Spatial           |

| Functionality      | Programmable | Programmable | Fixed             | Programmable            | Fixed             |

| Time-to-market     | High         | High         | Low               | High                    | Medium            |

| Performance        | Low          | Medium       | High              | Med-high                | Low               |

| Cost               | Low          | Medium       | High              | Low                     | Low               |

| Power              | High         | Medium       | Low               | Low-med                 | High              |

| Memory bandwidth   | Low          | Low          | High              | High                    | Low               |

| Companies          | Intel-ARM    | TI           | TSMC              | Xilinx-<br>Altera-Actel | Valor             |

| Design alternative | Digital      | Digital      | Digital<br>analog | Digital                 | Digital<br>analog |

|                    |              |              | RF mixed          |                         | RF mixed          |

| Languages          | С            | С            | -                 | Verilog                 | -                 |

|                    | Assembly     |              |                   | VHDL                    |                   |

Fig. 2.3 (a) FPGA-based modeling, (b) processor-based modeling, (c) ASIC-based modeling, (d) PCB-based modeling

#### 2.2.1 FPGA

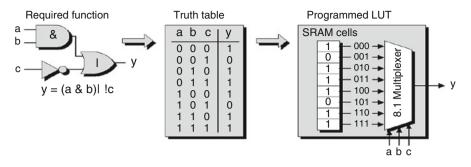

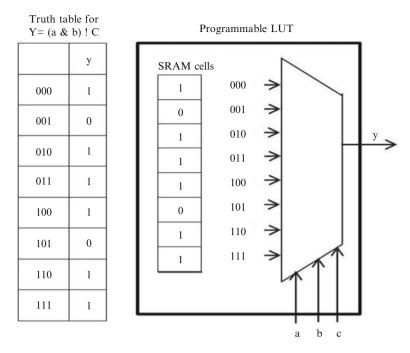

FPGAs are programmable chips, compared to hard-wired chips, FPGAs can be customized as per needs of the user by programming. This convenience, coupled with the option of reprogramming in case of problems, makes the programmable chips very vital choice. Other benefits include instant turnaround, low starting cost, and low risk. FPGA means "The chip that flip-flops." An FPGA is like an electronic breadboard that is wired together by an automated synthesis tool. An example of a programmable function using FPGA is shown in Fig. 2.4. A 3-input lookup table (LUT) can implement any function of three inputs.

Fig. 2.4 Programmable function using LUT-based FPGA [7]

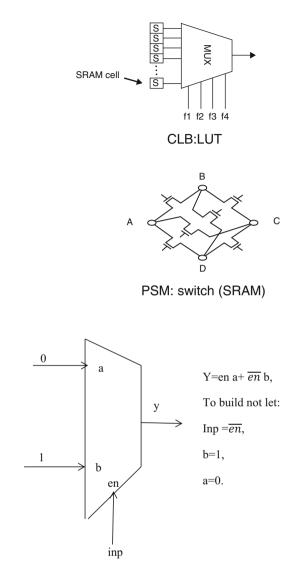

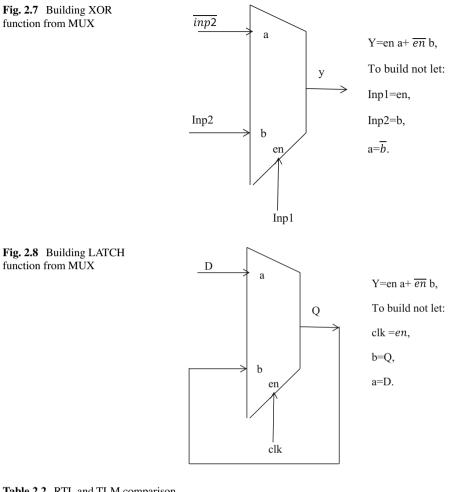

Referring to Fig. 2.3a, the general architecture of FPGA is shown where, CLB: Configurable Logic Block, IOB: Input/Output Block, and PSM: Programmable Switch Matrix. CLBs provide the functional elements for implementing the user's logic. IOBs provide the interface between the package pins and internal signal lines. Routing channels provide paths to interconnect the inputs and outputs of the CLBs and IOBs. An example for CLB and PSM architecture is shown in Fig. 2.5 [7–9]. The configurable block can be MUX not only LUT. MUX can implement any function, an example for implementing NOT and XOR function is shown in Figs. 2.6 and 2.7 respectively. Also an example for building a latch is shown in Fig. 2.8. FPGAs can be also classified according to their routing structure. The three most common structures are island-style, hierarchical, and row-based [10]. FPGAs are one-size fits all architectures.

FPGA is considered a top-down methodology (RTL to layout), this methodology makes design of complex systems more simpler as it focuses on functionality, reduce time-to-market as it shortens the design verification loop, and makes exploring different design options easier and cheaper for example (latency versus throughput).

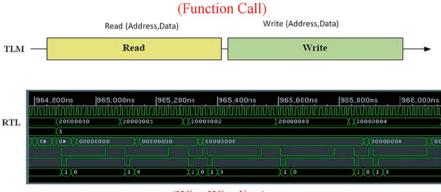

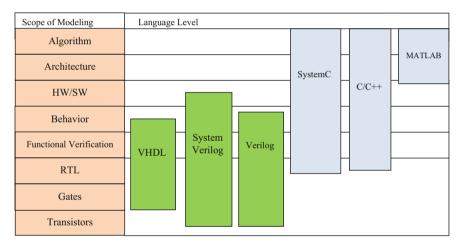

As for modeling languages and the scope of using FPGA-based design, two levels for IP modeling are highlighted register-transfer level (RTL) and transaction level modeling (TLM) (Table 2.2).

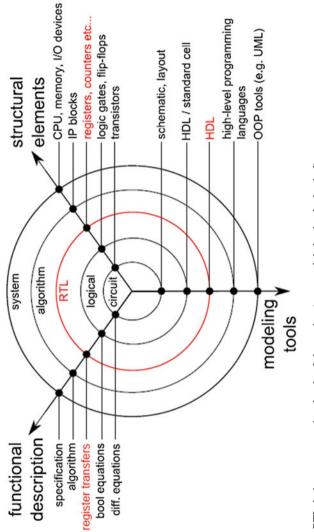

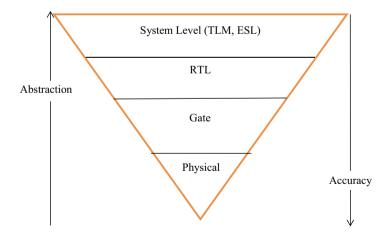

RTL is the abstraction level between algorithm and logic gates. In RTL description, circuit is described in terms of registers (flip-flops or latches) and the data is transferred between them using logical operations (combinational logic, if needed). That is why the nomenclature: Register-Transfer Level (RTL). Y-chart is shown in Fig. 2.9.

TLM is a technique for describing a system by using function calls that define a set of transactions over a set of channels. TLM descriptions can be more abstract, and therefore simulate more quickly than the RTL. TLM separates computation from communication as depicted in Fig. 2.10.

Modeling at the transactional level has several advantages, not only for the IP provider (designers and verification engineers), but also for the users, which can evaluate the performances and the behavior of the IP very early in the design flow.

**Fig. 2.5** CLB and PSM architecture example [7]

**Fig. 2.6** Building NOT function from MUX

The different levels of abstraction and the different modeling languages are shown in Fig. 2.11 and Table 2.3.

System level modeling is widely employed at early stages of system development for simplifying design verification and architectural exploration. Raising the abstraction level results in a faster development of prototypes and the reduction of implementation details in system level design can increase the simulation speed and allow a more global view of the system. During the phase of RTL development, the system level design can serve as a reference model for RTL design and verification.

Table 2.2 RTL and TLM comparison

|                   | RTL           | TLM                    |

|-------------------|---------------|------------------------|

| Simulation speed  |               |                        |

| Abstraction level |               |                        |

| RTL synthesizable | Yes           | No                     |

| Languages         | Verilog, VHDL | Systemverilog, SystemC |

| Accuracy          |               |                        |

There are several high-level modeling languages like Systemverilog [11] and SystemC [12]. TLM does not contain a clock signal. TLMs use function calls for communication between different modules and events to trigger communication actions. It allows designers to implement high-level communication protocols for simulations up to faster than at register-transfer level (RTL). Thus encouraging the use of virtual platforms for fast simulation prior to the availability of the RTL code.

Fig. 2.9 Y-chart for RTL design representation: levels of abstraction (structural, behavioral, physical)

(Wire Wiggling)

**Fig. 2.10** TLM and RTL example, where TLM does not take into consideration the details, i.e., higher abstraction level. TLM replaces all pin-level events with a single function call. TLM speeds up verification

Fig. 2.11 Comparison between different modeling languages [4]

|                         | MATLAB | SystemC | Systemverilog | Verilog | VHDL |

|-------------------------|--------|---------|---------------|---------|------|

| Requirements            | Yes    | YES     | No            | No      | No   |

| Architecture            | Yes    | Yes     | No            | No      | No   |

| HW/SW                   | No     | Yes     | No            | No      | No   |

| Behavior                | No     | Yes     | Yes           | No      | Yes  |

| Functional verification | No     | Yes     | Yes           | No      | No   |

| Testbench               | No     | Yes     | Yes           | Yes     | Yes  |

| RTL                     | No     | Yes     | Yes           | Yes     | Yes  |

| Gates                   | No     | No      | Yes           | Yes     | Yes  |

| Transistors             | No     | No      | Yes           | Yes     | No   |

Table 2.3

The modeling languages comparison

#### 2.2 IP Modeling

Systemverilog suffers from [13]:

- 1. It is closed source.

- 2. It is not software domain, i.e., does not support HW/SW co-verification.

- 3. Single core, no multi-core support.

- 4. Incomplete support for OOP, for example there is no const class method.

- 5. It does not support function overloading.

- 6. No automatic garbage collector.

- 7. DPI has a long runtime overhead.

SystemC suffers from:

- 1. Single core, no multi-core support.

- 2. No coverage support.

- 3. Transaction randomization is limited.

There is another family of languages called **scripting** languages like PERL [14], TCL [15], and Python [16]. Scripting languages are programming languages designed to make programming tasks easier, for example to run all the test cases automatically after every RTL change to make sure that it does not affect other test cases. Scripting languages are dynamic high-level languages with extensive standard library which enables rapid prototyping and experimentation.

There are advances in design methods such as using IP-XACT. IP-XACT is a standard written in an XML file format to describe hardware designs at a higher level [17, 18]. Also, it provides a standard for component design description exchange among heterogeneous platforms or among different designers working on different components or in other words, it helps in IP reuse.

The XML document is written using XML editors and it contains set of tags which represent a synthesizable hardware component such as registers and FIFO. IP-XACT documents the attributes of an IP component such as Interfaces, signals, parameters, memory, ports, and registers. An XML parser interprets the document and generates RTL code as XML is just plain text. The parsing process of an XML is relatively fast. Python is one of the languages used for parsing [19].

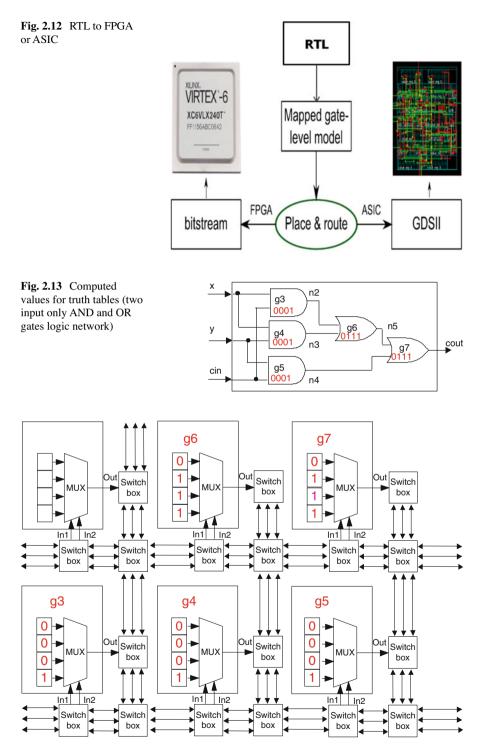

FPGA design flow comprises the following steps:

- 1. Convert specification to RTL code.

- 2. Synthesis the code which means converts the RTL code into generic Boolean netlist (gates, wires, registers).

- 3. Do mapping: map the generic Boolean gates into target technology (LUT or MUX CLB). The RTL can be mapped into FPGA or ASIC as depicted in Fig. 2.12.

- 4. Placement and routing.

- 5. Downloading: the file which is generated and downloaded to the FPGA is called bitstream file.

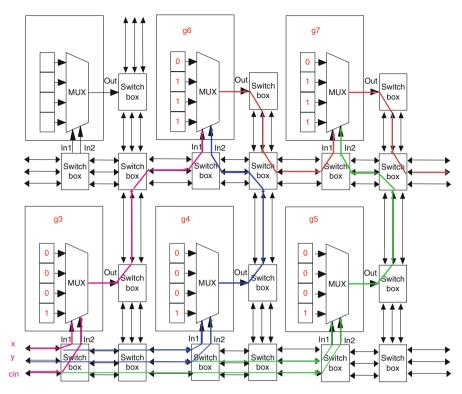

An example for a logic block is shown in Fig. 2.13. The placement process is described in Fig. 2.14 and the routing process is described in Fig. 2.15.

Fig. 2.14 FPGA placing

Fig. 2.15 FPGA routing

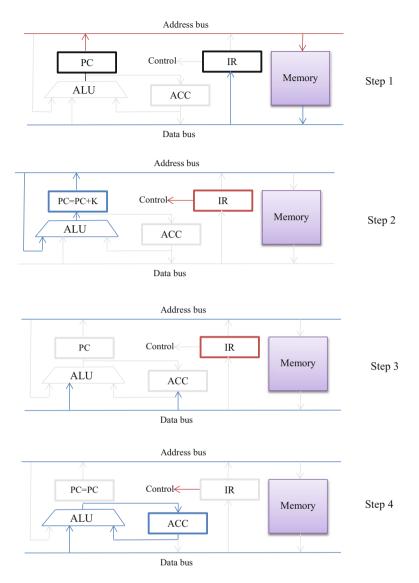

#### 2.2.2 Processor

Referring to Fig. 2.3b, the general architecture for a very simple processor is shown, where PC: program counter, ACC: accumulator, ALU: arithmetic logic unit, IR: instruction register. The PC holds the address of next instruction to be executed, ACC holds the data to be processed, ALU performs operation on data, IR holds the current instruction code being executed. The operation can be summarized in the following steps (Fig. 2.16):

- 1. Instruction fetch: The value of PC is outputted on address bus, memory puts the corresponding instruction on data bus, where it is stored in the IR.

- 2. Instruction decode: The stored instruction is decoded to send control signals to ALU which increment the value of PC after pushing its value to the address bus.

- 3. Operand fetch: The IR provides the address of data where the memory outputs it to ACC or ALU.

- 4. Execute instruction: ALU is performing the processing and store the results in the ACC. The instruction types include: data transfer, data operation (arithmetic, logical), and program control such as interrupts.

Fig. 2.16 A simple processor operation

Theses cycles are continuous and called fetch–decode–execute cycle. The processors can be programmed using high-level language such as C or mid-level language such as assembly [20]. Assembly is used for example in nuclear application because it is more accurate. At the end the compiler translates this language to the machine language which contains only ones and zeroes.

Instruction Set Architecture (ISA) describes a processor from the user's point of view and gives enough information to write correct programs. Examples of ISA are Intel ISA (8086, Pentium).

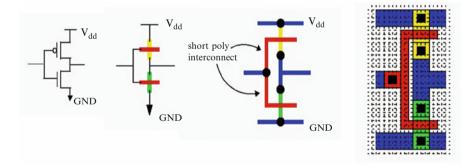

#### 2.2.3 ASIC

Physical design converts a circuit description into a geometric description. This description is used to manufacture a chip. Geometric shapes which correspond to the patterns of metal, oxide, or semiconductor layers that make up the components of the integrated circuit. It is top view of the cross-sectional device [21].

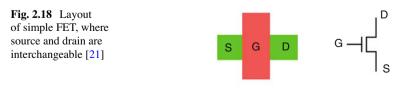

Using ASIC design methodology, it is very hard to fix bugs and it needs long time through the fabrication process (Design, Layout, Prototype, Fabrication, and Testing). It requires expensive tools and requires a very expensive Fab. But, it provides superior performance [22]. In ASIC, the schematics is converted to stick diagram to find Euler path which determines the best way to put the devices in the substrate and then the stick diagram is converted to layout (Fig. 2.17). The layout can be analog, digital, or mixed signal. An example for a layout of a simple FET transistor is shown in Fig. 2.18. The layout has some design rules called design rule check (DRC) [23].

Since there are different semiconductor processes (with different set of rules and properties), the designer has to know the specifications for the one that is to be used. This information is stored in a set of files called Technology Files. The technology files contain information about:

- Layer definitions: Conductors, contacts, transistors.

- Design rules: minimum size, distance to objects.

- Display: Colors and patterns to use on the screen.

- Electrical properties: resistance, capacitance.

**Fig. 2.17** Schematics to stick diagram to layout. A stick diagram is a symbolic layout: contains the basic topology of the circuit. It is always much faster to design layout on paper using stick diagram first before using the layout CAD tool [21]

Poly crossed over Diffusion → Field effect transistor (FET)

Fig. 2.19 Typical PCB: computer motherboard

The process features example:

- *p*-Type substrate

- *n*-Well

- n + and p + diffusion implants

- One layer of poly (gate material)

- Two layers of metal for interconnection (metal 1 and metal 2)

- Contact (metal 1 to poly or metal 1 to diffusion)

- Via (metal 1 to metal 2)

After finishing the layout, GDS-II file is sent to the fab to be fabricated. This stage is called "Tape out."

#### 2.2.4 PCB

Standard logic ICs provides fixed function devices which can be connected together on PCB to implement a system. Standard logic ICs has limited speed and limited number of pins. Standard ICs such as 74xx (TTL), 40xx (CMOS). Typical PCB is the computer motherboard as depicted in Fig. 2.19. PCBs are made of copper and dielectric. Copper is an excellent electrical conductor and it is inexpensive material. PCBs can be single-sided, double-sided, or multilayer boards [24].

For single-sided PCB, components are on one side and conductor pattern on the other side. Routing is very difficult.

For double-sided PCB, conductor patterns are on both sides of the board and we connect between the two layers through vias. Via is a hole in the PCB, filled or plated with metal and touches the conductor pattern on both sides. Since routing is on both sides, double-sided boards are more suitable for complex circuits than single-sided ones. It is always better to minimize the number of vias.

For multilayer PCB, these boards have one or more conductor patterns inside the board. Several double-sided boards are glued together with insulating layers in between. For interlayer connections, there is blind via to connects an inner layer to an outer layer and buried via to connects two inner layers. The layers are classified as: Signal layers, Ground plane, and Power plane. Power planes may have special restrictions such as wider track widths

#### 2.3 IP Verification

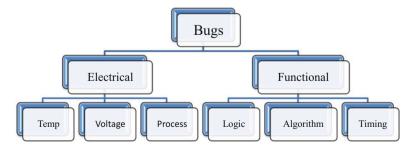

Verification is a process used to demonstrate the functional correctness of a design (no bugs). The types of bugs are summarized in Fig. 2.20. It is called bugs because in 1942 using the computer to perform calculations, it gave the wrong results. To find out what was going wrong, they opened the computer and looked inside (remember, this was in the "good old days," and an electromechanical computer was in use). And there they found a moth stuck inside the computer, which had caused the malfunction. The design/verification matrix is shown in Fig. 2.21.

Fig. 2.20 Types of bugs

| Fig. 2.21 Design/                                |             | Bad Verification                                                          | Good Verification                                            |

|--------------------------------------------------|-------------|---------------------------------------------------------------------------|--------------------------------------------------------------|

| verification matrix: the cost<br>of verification | Bad Design  | Many Bugs Exists<br>Bugs Not discovered<br>Bad Reputation at<br>customers | Many Bugs Exists<br>Bugs discovered<br>Time-to-market loss   |

|                                                  | Good Design | Few Bugs Exists<br>Bugs Not discovered<br>Bad Reputation at<br>customers  | Few Bugs Exists<br>All bugs are discovered<br>Customer Happy |

## 2.3.1 FPGA-Based/Processor-Based IP Verification

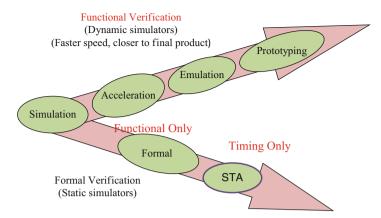

To verify an IP, we have two options as depicted in Figs. 2.22 and 2.23:

- 1. Function-based verification

- (a) Simulation-based

- (b) Accelerator-based

- (c) Emulation-based

- (d) FPGA prototyping

- 2. Formal-based verification

- (a) Assertion-based

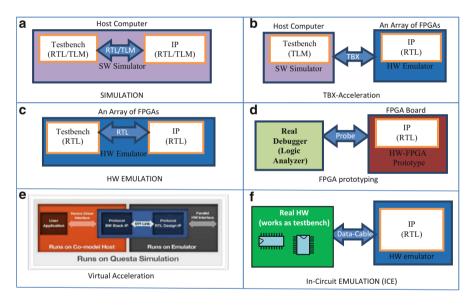

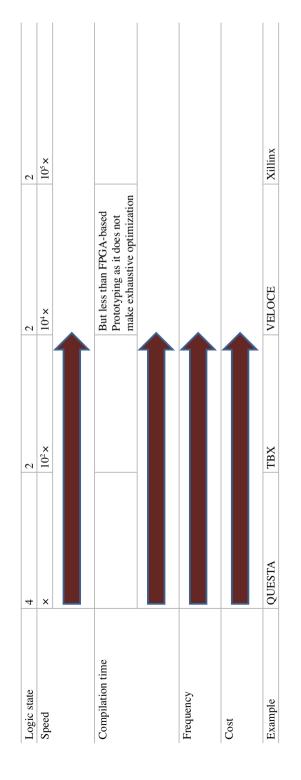

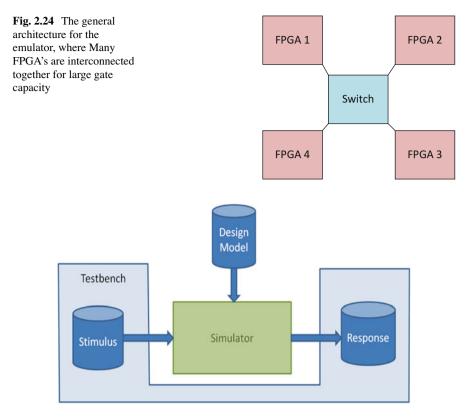

IPs functional verification is a key to reduce development cost and time-tomarket. Simulation speed is a relevant issue for complex systems with multiple operational modes and configurations since in such cases a slow simulator may prevent the coverage of a sufficient number of test cases in the verification phase [25]. To boost the performance of simulation, a number of platforms have recently attracted interest as alternatives to software-based simulation: acceleration, emulation, and prototyping platforms. Advantages and disadvantages of each type is summarized in Table 2.4, where **simulation** is easy and low cost, but not fast enough for large IP designs. **FPGA prototyping** are fast, but has little debugging capability. **Accelerators** can improve the performance to an extent where, the DUT is mapped into hardware and the testbench is run on the workstation, if we use real host application SW and real OS SW to access the device is called **virtual accelerators**.

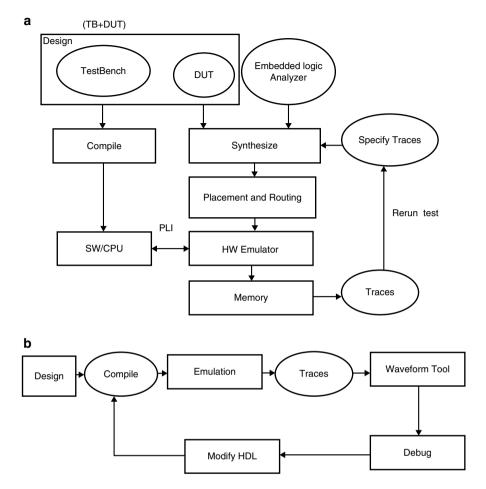

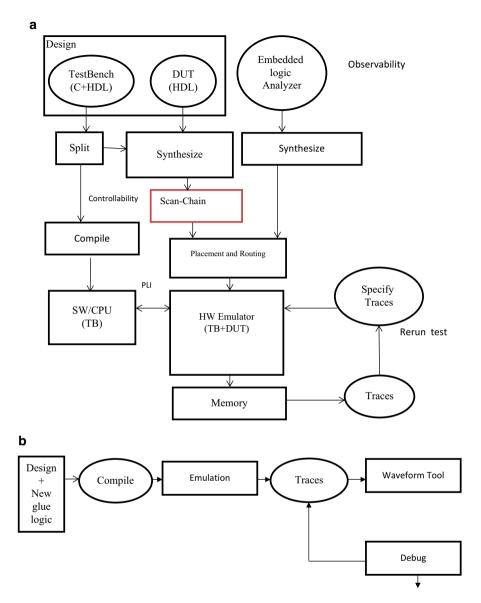

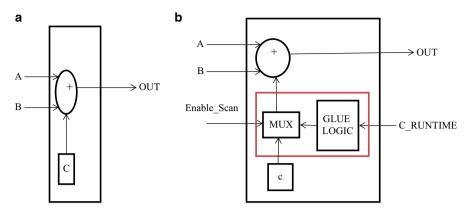

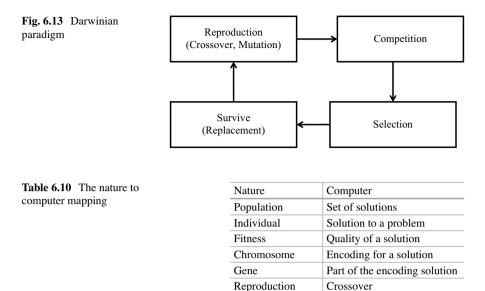

**Emulation improves** the accelerators performance, where the testbench and DUT are mapped into hardware; it also provides efficient debugging capabilities over the FPGA prototyping. The general architecture for the emulator is shown in Fig. 2.24, where many FPGAs are interconnected together for large gate capacity.

There is another mode of operation for the emulator called (in-circuit emulator) ICE, the difference between them can be interpreted by Fig. 2.23f, where in ICE part of the model is a real hardware.

Fig. 2.22 IP cores verification options (platforms)

**Fig. 2.23** Simulation, accelerators, emulation, FPGA prototyping platform comparison, the IP can be a host or peripheral. (a) Simulation, (b) TBX-acceleration, (c) HW emulation, (d) FPGA prototyping, (e) virtual acceleration, (f) in-circuit emulation (ICE)

The **formal verification** complements simulation-based RTL design verification by analyzing all possible behaviors of the design to detect any reachable error states using assertion-based verification (ABV) methodology and languages like SVA. This exhaustive analysis ensures that critical control blocks work correctly in all cases and locates design errors that may be missed in simulation. Moreover, it is a static simulator, that is why it takes less time in simulation than dynamic ones.

| Table 2.4 Sim       | ulation, accele | Table 2.4 Simulation, accelerators, emulation, FPGA prototyping comparison | otyping comparison                            |                                               |                                                      |

|---------------------|-----------------|----------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------|------------------------------------------------------|

|                     |                 | Simulation                                                                 | Accelerators                                  | Emulation                                     | FPGA prototyping                                     |

| Figure              |                 | Fig. 2.23a                                                                 | Fig. 2.23b, e                                 | Fig. 2.23c, f                                 | Fig. 2.23d                                           |

| Technology          | Software        | >                                                                          | >                                             | ×                                             | ×                                                    |

|                     |                 | Workstation                                                                | Workstation                                   |                                               |                                                      |

|                     | Hardware        | X                                                                          | >                                             | >                                             | >                                                    |

|                     |                 |                                                                            | An array of FPGA's                            | An array of FPGA's                            | FPGA                                                 |

| Execution           | DUT             | Serially                                                                   | In parallel                                   | In parallel                                   | In parallel                                          |

|                     | Testbench       | Serially                                                                   | Serially                                      | In parallel                                   | 1                                                    |

| Synthesizable       |                 | ×                                                                          | ×                                             | >                                             | 1                                                    |

| Supported languages | guages          | Verilog                                                                    | Verilog                                       | Verilog                                       | Verilog                                              |

|                     |                 | VHDL                                                                       | VHDL                                          | VHDL                                          | VHDL                                                 |

|                     |                 | SystemC                                                                    | SystemC                                       |                                               |                                                      |

|                     |                 | Systemverilog                                                              | Systemverilog                                 |                                               |                                                      |

|                     |                 |                                                                            | C++                                           |                                               |                                                      |

| Debugging           |                 | <ul> <li>Full RTL-level visibility</li> </ul>                              | <ul> <li>Full RTL-level visibility</li> </ul> | <ul> <li>Full RTL-level visibility</li> </ul> | <ul> <li>Limited visibility (limited O/P)</li> </ul> |

|                     |                 | - Workstation                                                              | <ul> <li>Workstation</li> </ul>               | - Workstation                                 | <ul> <li>Logic analyzer</li> </ul>                   |

|                     |                 |                                                                            |                                               | - Visibility for past time is                 |                                                      |

|                     |                 |                                                                            |                                               | emulator's trace memory                       |                                                      |

| g comparise     |

|-----------------|

| prototyping     |

| FPGA            |

| emulation,      |

| accelerators, e |

| Simulation,     |

| Table 2.4       |

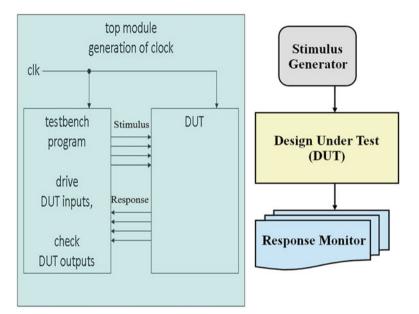

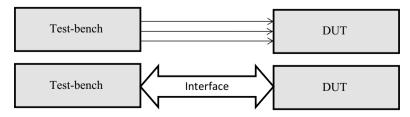

Fig. 2.25 Directed testing. Instantiates design under test (DUT), applies data to DUT, monitors the output

The verification methodologies can be classified into:

#### 1. Directed testing (traditional verification):

To ensure that the IP core is 100 % correct in its functionality and timing. Verification engineer sets goals and writes/generates directed tests for each item in Test Plan (Fig. 2.25). If the design is complex enough, it is impossible to cover all features with directed testbenches.

2. UVM:

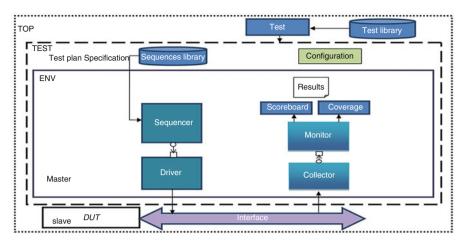

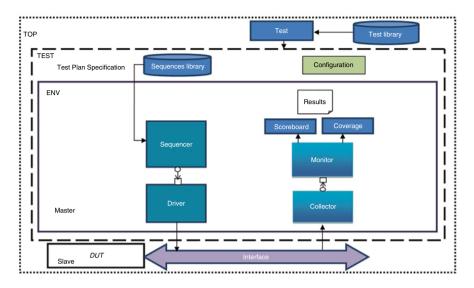

Reduce testbench development and testing as it supports all the building blocks required to build a test environment as depicted in Fig. 2.26, and it makes multimaster multi-slave testing easier. High-level verification languages and environments such as Systemverilog and e, as used in UVM, may be the state-of-the-art for writing test bench IP, but they are useless for developing models, transactors, and testbenches to run in FPGAs for emulation and prototyping. None of these languages are synthesizable. The component functionalities are as follows:

- **Sequencer**: Transaction is an instruction from the sequence to the driver (through the sequencer) to exercise the DUT.

- **Driver**: UVM component that converts a stream of transactions into pin wiggles.

Fig. 2.26 UVM environment

- **Scoreboard**: Gets a copy of the transaction in the monitor through the Analysis port and use that transaction for analysis purposes.

- Monitor: UVM component that monitors the pins of the DUT.

# 3. Checkers (assertions):

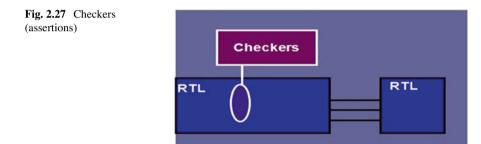

An assertion is a statement about a specific functional characteristic or property that is expected to hold for a design. The assertion-based methodology is used to ensure the functionality of the IP, where it monitors the transactions on an interface and check for any invalid operation and outputs error and/or warning messing of bus protocol. Self-checking ensures proper DUT response (Fig. 2.27). Assertions enhance observability coverage, making it easier to spot the source of an error [26].

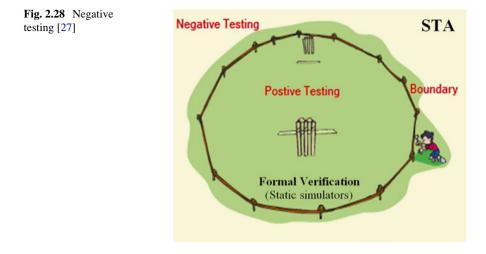

# 4. Negative testing (error injection):

Negative testing means "verify that the IP will produce an error report if it sees illegal traffic." The theory on which negative testing is based depending on the "Assertion-based" methodology [27]. The negative testbenches generate illegal traffic; the IP is supposed to recognize this traffic as illegal, and issues the trace error messages (Fig. 2.28).

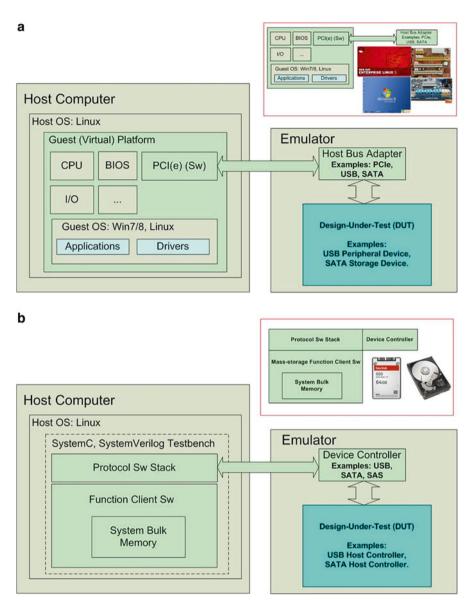

#### 5. Software-driven testing:

Software-driven testing adds a range of capabilities that promise to redraw the functional verification landscape. These include virtual host and peripheral models (called "virtual devices") and software debug technologies enabled by transaction-based, co-model channel technology. Virtual devices are an emerging technology, with products beginning to offer the same functionality as traditional In-Circuit (ICE) solutions, but without the need for additional cables and additional hardware units. Generally the function of virtual device architecture is to package a software stack running on the co-model host workstation with communication protocol IP running on Veloce using a TBX co-model link. This creates protocol solutions so customers can verify their IP at the device driver level and verify the DUT with realistic software, which is the device driver itself as depicted in Fig. 2.29.

#### 6. Coverage:

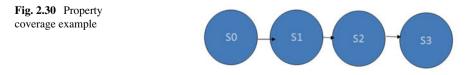

The main purpose of coverage is to check whether the given property (functional coverage) or statement (code coverage) is covered during simulation/ emulation. For example, is the sequence shown in (Fig. 2.30) ever followed by my FSM?

#### 7. Formal:

Input: HDL, post-synthesis gate-level netlist. It checks if the RTL description and the post-synthesis gate-level netlist have the same functionality. It is a static verification [28].

### 8. STA: static timing analysis

*Motivation*: How can I ensure my design will work at the target frequency under all circumstances?

How: By ensuring any timing path meets the timing requirements.

Why: always fastest than a simulation!

Fig. 2.29 A virtual device packages a software stack running on co-model workstation with communication protocol IP running on Veloce using a TBX co-model link, (a) host bus is running on emulator, (b) device controller is running on emulator

35

*Concept*: Check the data are available at the right time around the clock edge signal through static timing calculation.

*Technique*: Delay Calculation **R**, **C**=**f**(**Area**).

Hierarchical analysis is based on timing models for blocks *Notes*: STA does not check functionality.

### 9. Linting tools

Linting tools are widely used to check the HDL syntax before synthesizing it. The input to the linting tool is HDL source and the output is warning and error messages. Linting tools do not detect functional bugs. And they do not need stimulus [29]. They targets:

- Unsynthesizable constructs.

- Unintentional latches.

- Unused declarations.

- Driven and undriven signals.

- Race conditions.

- Incorrect usage of blocking and non-blocking assignments.

- Incomplete assignments in subroutines.

- Case statement style issues.

- Out-of-range indexing.

# 2.3.2 ASIC-Based IP Verification

It is called physical verification and it includes [30]:

1. Design rule checking (DRC):

DRC checks for if layout complies with foundry rules that is if the layout will be manufacturable. Typically this will have width check, density check, spacing checks, overlap checks, extension checks, etc.

2. Electrical rule check (ERC):

Checks for no short contacts, no floating points, etc.

3. Layout vs. Schematics (LVS):

LVS checks if the layout matches with the reference. In case of full-custom, the reference is spice netlist which is verified for functionality before getting into layout.

4. Post-layout simulation:

Add the parasitics extracted to the model and resimulate it to make sure that its functionality is still ok.

# 2.3.3 PCB-Based IP Verification

After drawing the schematic of your circuit and verifying its functionality using any circuit simulator like spice, and after implementing it on PCB, you can verify it using these tips:

- To perform the PCB verification test, compare the PCB with the layout. During this stage, you might also want to test the connectivity of each traces to ensure no broken traces by using the diode function in the multimeter especially those with buzzer sound. This will ease the verification process as once we hear the buzzer sound, you will know that the trace is connected from one end to another.

- 2. To check for shorts, look at any suspicious traces that are too close and test using diode function in the multimeter as well. This time, if your buzzer sounds, then you know there is an unwanted shorts [31].

# 2.4 IP Optimization

The optimization objective is to reduce area, delay, latency, and power and to increase performance and speed to meet the requirement.

# 2.4.1 FPGA-Based IP Optimization

To optimize an FPGA-based IP, we have three directions [5]:

- 1. Compilation time optimization.

- 2. Maximum frequency optimization.

- 3. Following some RTL design tips.

# 2.4.1.1 Compilation Time Optimization

#### Best practice design methodology

- Do not use long loops.

- Store large data in memory not in a register.

- Reduce the use of power "\*\*" and the division "\", instead use log and shift right.

- Do not write long ternary statement "()? : () ? : () ? ...." This very Verilog-based designs.

- Use 2D memory instead of 1D memory as 2-D memory reduce the compile as it is mapped directly to the memory blocks not to the logic.

#### Use of the latest computer technology

• Parallel (distributed) compilation, use dual or more core feature.

#### Place-and-route algorithm improvements

• Improve the place-and-route algorithms in the CAD tool development.

### 2.4.1.2 Maximum Frequency Optimization

#### Best practice design methodology

- 1. Make long "Assign" in a clock statement (Pipelining). This is for Verilog-based designs. Note that removing clk cycle to improve latency is easier than inserting one to improve pipelining.

- 2. Initialization of all uninitialized registers.

- 3. Using of linting tools such as 0-IN from Mentor Graphics.

- 4. Make the design under test (DUT) works with posedge clock or negedge clock only, not a mix of them to avoid the half-cycle path. half-cycle path is a path where the data is launched by a flip-flop (FF) on posedge of a clock and captured by a FF on negedge, hence the time available is only half a cycle instead of full cycle where both FF are working on posedge.

### 2.4.1.3 Follow Some RTL Design Tips

#### 1. Partition a large memory into several small blocks

For example, Questa/Modelsim maximum limit is 2G addresses per memory, so you need to divide the memory if it is higher than 2G as depicted in Fig. 2.31.

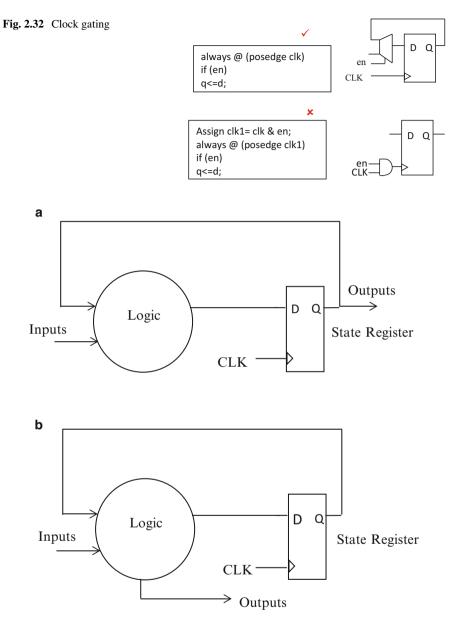

2. Clock gating

The concept of clock gating is shown in Fig. 2.32.

3. Resetting

For proper operation we must reset all the registers into the reset process.

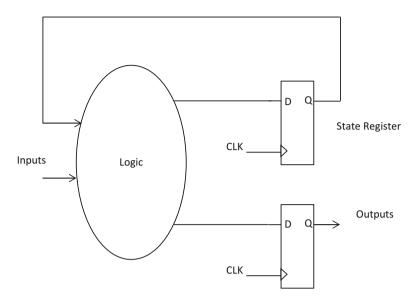

### 4. FSM coding style

The explicit, naive style FSM is better than Mealy or Moore machines as these machines have two distinct disadvantages (Fig. 2.33): (1) they may end with long combinational paths as they don't have output registers. (2) Even worse, if the coding is not done properly latches could be introduced and there will be mismatches between simulation and emulation. So, we strongly recommend a state machine to use a naive style (Fig. 2.34). This way we will have registers for the states and the outputs. For granted this ends up with more

Fig. 2.31 Partition a large memory into several small blocks

Fig. 2.33 Structures of (a) Moore type FSMs and (b) Mealy type FSMs

registers but it is much, much safer design and it makes it also run at higher frequency as the paths between registers are shorter [2].

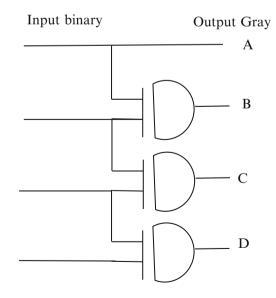

Encoding of FSMs including different encoding styles, the most famous one is binary encoding. There is also gray encoding and one-hot encoding. Binary encoding implements very less logic. Also it used minimum number of FFs.

Fig. 2.34 Explicit naive style FSM

Possible state values for a 4 state binary state machine (00, 01, 10, 11). Gray encoding is especially useful when the outputs of the state bits are used asynchronously. This kind of state coding avoids intermediate logics. For example if a state wants to change its state from "01" to "10." In Gray coding between state transitions only one bit will change. Possible state values for a 4 state gray state machine (00, 01, 11, 10).

One-hot encoding uses one flip-flop for each state. For example if there are 10 states in logic then it will use 10 flip-flops. This type of encoding is fast because only one bit needed to check for each state. It implies complex logic and more area inside the chip due to more number of flip-flops. FPGAs are "Flip-flop rich," therefore one-hot state machine encoding is often a good approach. It also reduces hardware's logic switching rate. Possible state values for a 4 state one-hot state machine (0001, 0010, 0100, 1000), also an example of how to write the one-hot encoding FSM is shown in Table 2.5.

Choice of an encoding style is depending of the requirements and performance goals (Table 2.6). Here, one-hot Finite State Machine (FSM) encoding scheme is being adopted for HDL model. One-hot state machines are typically faster, where the logic complexity associated to each state gets decreased. For comparison between binary, gray, and one-hot encoding scheme, one sample state machine was taken with *n* states. Verilog code was developed using binary and one-hot encoding scheme and then was synthesized to evaluate performance and area. One-hot encoding is a preferred approach if the timing in the output path is critical. Conversion from Binary Encoding to Gray Encoding is shown in Fig. 2.35 [32].

#### 5. Parameterizing

Use parameters as much as possible instead of hard-coded values, as it makes verification easier. Parameterization means design all features in HDL code and choose what you want to fabricate. Fixed IP versus parameterized IP is shown

```

case (1'b1)

state [S0]:

if (in == 1)

next_state [S1] = 1'b1;

else

next_state [S2]=1'b1;

state [S1]:

if (in == 1)

next_state [S0]=1'b1;

else begin

next_state [S2]=1'b1;

state [S2]:

next_state [S0]=1'b1;

```

Table 2.5

One-hot encoding verilog example

| Feature                 | Binary                                              | Gray                                                                  | One-hot                               |

|-------------------------|-----------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------|

| Number<br>of flip-flops | #(flip flops)=log <sub>2</sub> (#states)<br>Fewer   | #(flip flops)=log <sub>2</sub> (#states)<br>Fewer                     | #(flip flops)=<br>#(states)           |

| Speed                   | Slower                                              | Slower, only one bit is changed in state transition                   | Faster                                |

| Critical path searching | Need more tracking to find critical path during STA | Need more tracking to find critical path during STA                   | Easy to find critical path during STA |

| Debug easiness          | Tedious to debug                                    | Tedious to debug                                                      | Easy to debug                         |

| Low power               | Higher power                                        | Suitable for low-power<br>design because of low<br>signal transitions | Higher power                          |

-

Fig. 2.35 Conversion from binary encoding to gray encoding

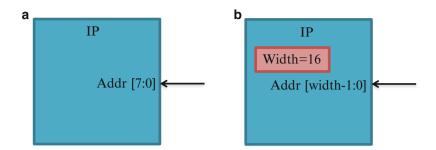

Fig. 2.36 (a) Fixed IP versus (b) parameterized IP

in Fig. 2.36. The advantage of parameterization mechanisms over the use of constants/packages is that parameterization allows the same component to be used multiple times in a single design with different sets of parameters [33].

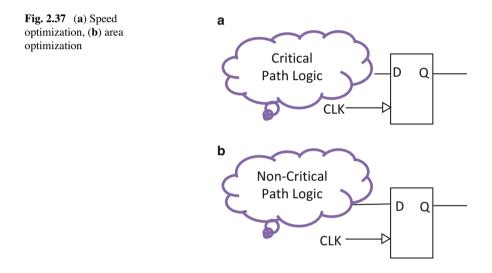

#### 6. Speed and area optimization

Keep critical path logic in a separate module, optimize the critical path logic for speed, and optimize the noncritical path logic for area (Fig. 2.37).

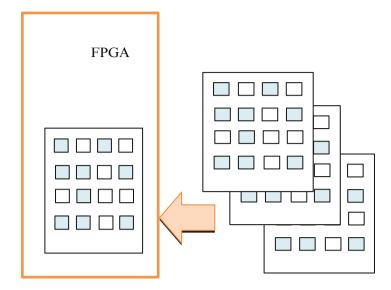

Dynamic Partial Reconfiguration (DPR) is also used to optimize area usage. With DPR, it is possible to implement different circuits that are not needed at the same time, and that do not operate simultaneously, on the same FPGA area, resulting in considerable area savings as depicted in Fig. 2.38. This area is generally called the reconfigurable region (RR). Whenever the designer wants to change the implemented circuit, an amount of time is needed to rewrite the configuration memory at runtime and this is called the reconfiguration time [34–36]. The subsystem that performs the reconfiguration is called the reconfiguration manager and is generally implemented in software.

Fig. 2.38 DPR concept, implement different circuits that are not needed at the same time, and that do not operate simultaneously, on the same FPGA area, resulting in considerable area savings

The configuration memory of the reconfiguration region (RR) consists of SRAM memory cells that control the content of the lookup tables and the state of the routing switches. To implement a circuit in the RR, a configuration needs to be generated that contains the binary values that need to be written in the RR's memory cells. Figure 2.39 gives an example that describes the role of configuration memory [37–40].

In conventional DPR systems, a configuration bitstream is generated for every mode by implementing it separately in the RR, where every RR memory cell corresponds to a collection of binary values, one value for each mode. When these binary values are the same, this collection is called a static bit. If they are not the same, this collection is called a dynamic bit. Memory cells containing a static bit do not need to be rewritten during runtime.

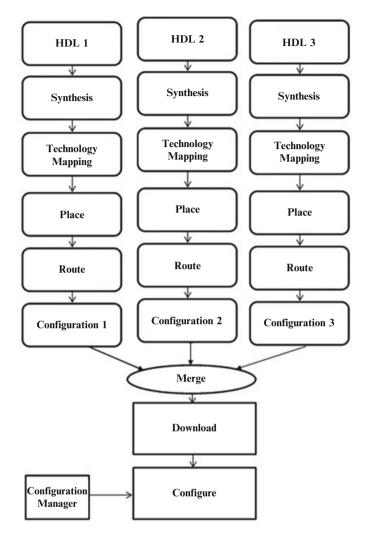

The DPR design flow methodology framework comprises a set of steps, which are necessary to implement the proposed multi-mode memory controller's applications using DPR as described in Fig. 2.40.

- (a) During the initial phase, the static modules and the partial reconfiguration modules (PRM) are described in HDL language.

- (b) The PRMs are synthesized to generate the corresponding netlist for each module.

- (c) Perform placement and routing and generation of the full and partial reconfiguration bitstream.

- (d) Merges the full bitstream to generate a final downloadable bitstream.

- (e) The final downloadable bitstream is copied onto the compact flash card and the card is plugged into the FPGA to bring up the design on the next power cycle.

- (f) To switch between the different circuits, the reconfiguration manager writes the reconfigurable region with the appropriate bitstream configuration.

Fig. 2.39 An example describes the role of configuration memory [37]

- 7. Power optimization

- Use gray-coding FSM.

- Use line coding to reduce transitions (8b/10b encoder): reduce  $\alpha$  (switching activity factor).

- Increase data bus width to reduce transfer cycles: reduce α.

# 2.4.2 Processor-Based IP Optimization

#### A. Best practice design methodology

- 1. Do not use long loops.

- 2. Split logic circuits to shorten the critical path.

- 3. Choose faster logic circuit architectures.

#### B. Use of the latest computer technology

1. Parallel (distributed) compilation, use dual or more core feature.

Fig. 2.40 DPR design flow methodology framework. It comprises a set of steps, which are necessary to implement the proposed multi-mode memory controller's applications using DPR

# 2.4.3 ASIC-Based IP Optimization

- 1. Keep *n*-devices near *n*-devices and *p*-devices near *p*-devices [1].

- 2. Keep *n*MOS near ground and *p*MOS near  $V_{dd}$ .

- 3. Layout of large transistor: large transistors can be viewed as number of parallel small transistors because as the gate width increases beyond certain limit, the efficiency of the transistors decreases as poly resistance increases.

- 4. Metal line bending: use 45° bending not 90° as the effective area of the current flow through 90° bending is reduced to 50 %.

- 5. Put guard rings around differential pairs, *n*-well, and *p*-well.

- 6. If we leave the differential pairs on the edges without dummies, they will see different surroundings and mechanical stress than the middle ones; with dummies we can avoid this.

- 7. Use interleaving between transistors so that if a fabrication error happened in a die, it does not affect the remaining transistors and the chip can remain working correctly.

- 8. Global signals should be routed on the top and bottom of layout blocks. Local signals should be routed through the center of layout blocks.

# 2.4.4 PCB-Based IP Optimization

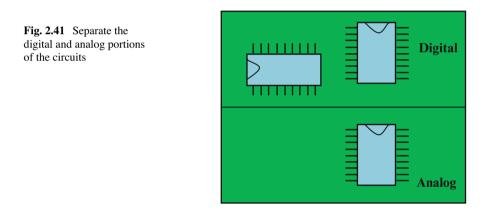

- 1. Separate the digital and analog portions of the circuits (Fig. 2.41).

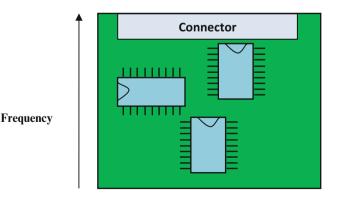

- 2. High frequency components should be placed near the connectors (Fig. 2.42).

Fig. 2.42 High-frequency components should be placed near the connectors

# 2.5 IP Protection

Without IP protection, companies can lose revenue and market share.

# 2.5.1 FPGA-Based/Processor-Based IP Protection

IP vendors are facing major challenges to protect hardware IPs from IP-piracy as, unfortunately, recent trends in IP-piracy and reverse engineering efforts to produce counterfeit ICs have raised serious concerns in the IC design community. IP-piracy can take several forms, as illustrated by the following scenarios:

- 1. A chip design house buys an IP core from an IP vendor and makes an illegal copy or "clone" of the IP. The IC design house then sells it to another chip design house (after minor modifications) claiming the IP to be its own.

- 2. An untrusted fabrication house makes an illegal copy of the GDS-II database supplied by a chip design house and then illegally sells them as hard IP.

- 3. An untrusted foundry manufactures and sells counterfeit copies of the IC under a different brand name.

- 4. An adversary performs post-silicon reverse engineering on an IC to manufacture its illegal clone.

These scenarios demonstrate that all parties involved in the IC design flow are vulnerable to different forms of IP infringement which can result in loss of revenue and market share. Hence, there is a critical need of a piracy-proof design flow that equally benefits the IP vendor, the chip designer, as well as the system designer. A desirable characteristic of such a secure design flow is that it should be transparent to the end-user, i.e., it should not impose any constraint on the end-user with regard to its usage, cost, or performance.

To secure an IP, we need to obfuscate it then encrypt the contents before sending it to the customer. **Obfuscation** is a technique that transforms an application or a design into one that is functionally equivalent to the original but is significantly more difficult to reverse engineer. So, Obfuscation changes the name of all signals to numbers and characters combination. The second level is to encrypt the whole files [41, 42]. Although encryption is effective, code obfuscation is an effective enhancement that further deters code understanding for attackers [43]. Moreover, **Watermarking** can be used to protect Soft-IPs [44]. It includes modules duplication or module splitting.

# 2.5.2 ASIC-Based IP Protection

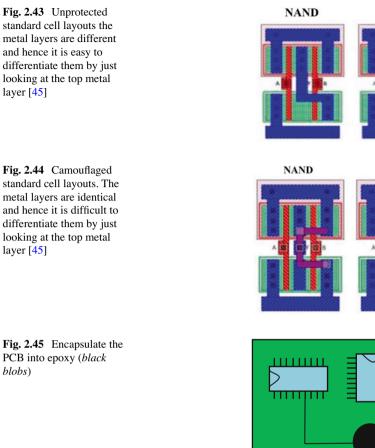

1. **Circuit camouflage**: let individual logic cells appear identical at each mask layer, when in fact subtle changes are present to differentiate logic functions. Changes are designed so that the reverse engineer is unable to automate cell recognition [45]. Figure 2.43 Shows an example of unprotected layout and Fig. 2.44 shows a protected one.

NOR

NOR

#### Fig. 2.45 Encapsulate the PCB into epoxy (black blobs)

# 2.5.3 PCB-Based IP Protection

- 1. Remove the markings from all the major ICs and mark them with in-house part numbers.

- 2. Encapsulate the PCB into epoxy (black blobs) as depicted in Fig. 2.45 [46].

- 3. Add a few fake layers for complexity.

#### 2.6 Summary

This chapter discusses the IP cores life cycle process from specification to production which includes four major steps: (1) IP Modeling, (2) IP verification, (3) IP optimization, (4) IP protection. For IP modeling, four major methodologies are

layer [45]

layer [45]

introduced which includes: FPGA-based modeling, processor-based modeling, ASIC-based modeling, and PCB-based modeling. For IP verification, different platforms are presented and analyzed such as simulation, acceleration, emulation, and prototyping. Moreover, different verification methodologies are introduced such as: UVM, direct testing, negative testing, software-driven testing, and formal testing. We presented different methods for IP optimization for the main design methodologies to improve area, speed, and power. For IP protection, we analyzed different strategies to perform protection not to make companies lose revenue and market share.

# References

- 1. www.cs.clemson.edu/~mark/464/fab.pdf

- Rafla NI, Davis, Brett LaVoy (2006) A study of finite state machine coding styles for implementation in FPGAs. 49th IEEE International Midwest Symposium on Circuits and Systems, San Juan

- 3. Roudier T, Moussa I, di Crescenzo P (2003) IP modelling and reuse for system level design. Published for DATE

- 4. http://www.esa.int/TEC/Microelectronics/SEM6Z0AMT7G\_0.html

- 5. Simpson P, Jagtiani A (2007) How to achieve faster compile times in high-density FPGA. EE Times

- Ricardo R, Marcelo L, Jochen J (2010) Design of systems on chip: design and test. Springer, Dordrecht

- 7. Clive M (ed) (2007) FPGAs: world class design. Newness, Burlington

- 8. Hauck S, DeHon A (2008) Reconfigurable computing: the theory and practice of FPGA-based computation. Morgan Kaufmann, Burlington

- 9. Maxfield CM (2004) The design warrior's guide to FPGAs. Newnes, Burlington

- 10. Betz V, Rose J, Marquardt A (1999) Architecture and CAD for deep-submicron FPGAs. Kluwer, Boston

- 11. Sutherland S, Davidmann S, Flake P (2003) Systemverilog for design: a guide to using systemverilog for hardware design and modeling. Kluwer, Norwell

- Black D, Donovan J, Bunton B, Keist A (2010) SystemC: from the ground up, 2nd edn. Springer, New York. ISBN 978-0-387-69957-8

- 13. Goel P, Adhikari S (2014) Introduction to next generation verification language—Vlang. DVCON Conference and Exhibition, Munich

- 14. Schwartz RL, Phoenix T (2008) Learning PERL. O'Reilly Media, Sebastopol

- 15. www.ActiveState.com

- 16. Ucoluk G, Kalkan S (2007) Introduction to programming concepts with case studies in python. Springer, London

- 17. http://www.accellera.org/activities/committees/ip-xact

- 18. IEEE 1685-2009 IPXACT. Accessed 18 Feb 2010

- 19. Kulkarni R (2013) Automated RTL generator. M.Sc. Thesis, San Jose State University

- 20. Axelson J (1997) The microcontroller idea book. Lakeview Research, Madison

- 21. Sherwani NA (1999) Algorithms for VLSI physical design automation, 3rd edn. Kluwer, Boston

- 22. Sung Kyu L (2008) Practical problems in VLSI physical design automation. Springer, New York

- Clein D (2000) CMOS IC layout concepts, methodologies, and tools. Butterworth–Heinemann, Newton

- 24. Coombs CF Jr (2001) Printed circuits handbook. McGraw-Hill, New York

2 IP Cores Design from Specifications to Production: Modeling, Verification...

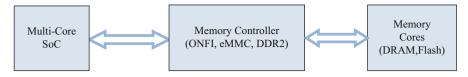

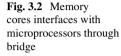

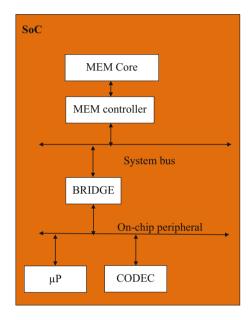

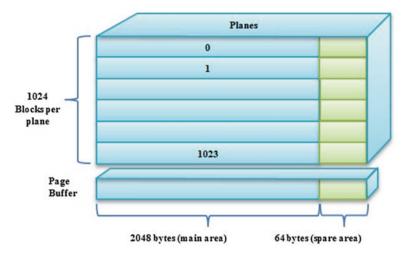

- 25. Masahiro F, Indradeep G, Mukul P (2008) Verification techniques for system-level design. Morgan Kaufmann, San Francisco