# Carlos Manuel Ferreira Carvalho Nuno Filipe Silva Veríssimo Paulino

# CMOS Indoor Light Energy Harvesting System for Wireless Sensing Applications

CMOS Indoor Light Energy Harvesting System for Wireless Sensing Applications Carlos Manuel Ferreira Carvalho Nuno Filipe Silva Veríssimo Paulino

# CMOS Indoor Light Energy Harvesting System for Wireless Sensing Applications

Carlos Manuel Ferreira Carvalho Instituto Politécnico de Lisboa (IPL) Instituto Superior de Engenharia de Lisboa (ISEL-ADEETC) Lisboa Portugal Nuno Filipe Silva Veríssimo Paulino Faculdade de Ciências e Tecnologia da Universidade Nova de Lisboa Caparica Portugal

ISBN 978-3-319-21616-4 DOI 10.1007/978-3-319-21617-1

ISBN 978-3-319-21617-1 (eBook)

Library of Congress Control Number: 2015944734

Springer Cham Heidelberg New York Dordrecht London

© Springer International Publishing Switzerland 2016

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

Springer International Publishing AG Switzerland is part of Springer Science+Business Media (www.springer.com)

## Preface

This book presents a micro-power light energy harvesting system for indoor environments. Light energy is collected by amorphous silicon photovoltaic (a-Si:H PV) cells, processed by a switched-capacitor (SC) voltage doubler circuit with maximum power point tracking (MPPT), and finally stored in a large capacitor. The MPPT fractional open-circuit voltage ( $V_{OC}$ ) technique is implemented by an asynchronous state machine (ASM) that creates and, dynamically, adjusts the clock frequency of the step-up SC circuit, matching the input impedance of the SC circuit to the maximum power point (MPP) condition of the PV cells. The ASM has a separate local power supply to make it robust against load variations. In order to reduce the area occupied by the SC circuit, while maintaining an acceptable efficiency value, the SC circuit uses MOSFET capacitors with a charge reusing scheme for the bottom-plate parasitic capacitors. The circuit occupies an area of 0.31 mm<sup>2</sup> in a 130-nm CMOS technology. The system was designed in order to work under realistic indoor light intensities. Experimental results show that the proposed system, using PV cells with an area of  $14 \text{ cm}^2$ , is capable of starting up from a 0 V condition, with an irradiance of only  $0.32 \text{ W/m}^2$ . After starting up, the system requires an irradiance of only  $0.18 \text{ W/m}^2$  (18  $\mu$ W/cm<sup>2</sup>) to remain in operation. The ASM circuit can operate correctly using a local power supply voltage of 453 mV, dissipating only  $0.085 \mu$ W. These values are, to the best of the authors' knowledge, the lowest reported in the literature. The maximum efficiency of the SC converter is 70.3 % for an input power of 48  $\mu$ W, which is comparable with the reported values from circuits operating at similar power levels.

### Acknowledgments

The authors would like to express their gratitude to all of those that made possible the completion of this book, as well as the work contained in it.

In particular, we would like to thank Charles B. Glaser, executive editor, Applied Sciences USA, for the publication of the present book, as well as to all the persons involved in this task, namely Brian Halm and Jessica Lauffer, among others.

We would like to thank to Dr. Guilherme Lavareda, for his cooperation regarding the subject of photovoltaic cells and for having manufactured the cells that were used to test the prototype system, as well as to all the persons involved in this manufacturing.

We would also like to thank to Edinei Santin, Taimur Gibran, Michael Figueiredo, and António Couto Pinto, for having helped us during the integrated circuit layout process, and to Tiago Oliveira and João Casaleiro for their help about how to use the PCB layout software.

# Contents

| 1 | Intr | oductio                                                    | )n                                                  | 1  |

|---|------|------------------------------------------------------------|-----------------------------------------------------|----|

|   | 1.1  | Motiv                                                      | ation and Context                                   | 1  |

|   | 1.2  | Book                                                       | Organization                                        | 4  |

|   | Refe | erences                                                    |                                                     | 5  |

| 2 | Ene  | røv Ha                                                     | rvesting Electronic Systems                         | 7  |

| - | 2.1  |                                                            | able Energy Sources                                 | 7  |

|   | 2.1  | 2.1.1                                                      | Mechanical Energy                                   | 8  |

|   |      | 2.1.2                                                      | Thermal Gradients                                   | 11 |

|   |      | 2.1.3                                                      | Radio Frequency Electromagnetic Energy              | 14 |

|   |      | 2.1.4                                                      | Human Generation.                                   | 17 |

|   |      | 2.1.5                                                      | Microbial Fuel Cells                                | 20 |

|   |      | 2.1.6                                                      | Light                                               | 23 |

|   | 2.2  |                                                            | parison of Harvestable Energy Sources               | 29 |

|   | 2.3  | -                                                          | y Harvesting-Based Sensor Networks                  | 30 |

|   |      | 2.3.1                                                      |                                                     | 30 |

|   |      | 2.3.2                                                      | Energy Neutrality                                   | 30 |

|   |      | 2.3.3                                                      | Examples of WSN Powered by Harvested Energy         | 31 |

|   | 2.4  |                                                            | usions                                              | 36 |

|   | Refe |                                                            |                                                     | 37 |

| _ |      | _                                                          |                                                     |    |

| 3 |      |                                                            | ic Cell Technologies                                | 43 |

|   | 3.1  |                                                            | uction                                              | 43 |

|   | 3.2  |                                                            | epts and Parameters Regarding PV Cells              | 44 |

|   |      | 3.2.1                                                      |                                                     | 44 |

|   |      | 3.2.2                                                      | Fill Factor                                         | 45 |

|   |      | 3.2.3                                                      | Efficiency                                          | 46 |

|   |      | 3.2.4                                                      | Peak Watt                                           | 46 |

|   | 3.3  | 3.3 Generation of Electric Power in Semiconductor PV Cells |                                                     |    |

|   |      | 3.3.1                                                      | Efficiency Limit According to Shockley and Queisser | 49 |

|   | 3.4  | Types                                              | of PV Cells                                         | 50  |

|---|------|----------------------------------------------------|-----------------------------------------------------|-----|

|   |      | 3.4.1                                              | First-Generation PV Cells                           | 50  |

|   |      | 3.4.2                                              | Second Generation PV Cells                          | 53  |

|   |      | 3.4.3                                              | Third-Generation PV Cells                           | 55  |

|   |      | 3.4.4                                              | Comparison of the Different PV Technologies         | 58  |

|   | 3.5  | Integra                                            | ated CMOS PV Cell Prototype                         | 58  |

|   |      | 3.5.1                                              | Electrical Model of a CMOS PV Cell                  | 60  |

|   |      | 3.5.2                                              | Development and Layout of an Integrated             |     |

|   |      |                                                    | CMOS PV Cell.                                       | 61  |

|   |      | 3.5.3                                              | Experimental Results of the Prototyped Integrated   |     |

|   |      |                                                    | PV Cell                                             | 64  |

|   |      | 3.5.4                                              | Conclusions About the Integrated PV Cell            | 65  |

|   | 3.6  | Indoor                                             | r Light Energy Availability Study                   | 66  |

|   |      | 3.6.1                                              | Light Power Intensity Measurements                  | 66  |

|   |      | 3.6.2                                              | Conclusions                                         | 69  |

|   | Refe | rences                                             |                                                     | 70  |

|   |      |                                                    |                                                     |     |

| 4 | Volt | age Ste                                            | p-up Circuits                                       | 73  |

|   | 4.1  | Types                                              | of Voltage Converters                               | 73  |

|   |      | 4.1.1                                              | Linear Converters                                   | 73  |

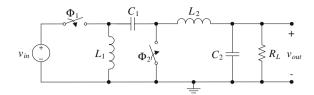

|   |      | 4.1.2                                              | Switched Converters                                 | 75  |

|   | 4.2  | Induct                                             | or-Based Converters                                 | 75  |

|   |      | 4.2.1                                              | Voltage Step-up Circuits.                           | 78  |

|   |      | 4.2.2                                              | Voltage Step-down Circuits                          | 81  |

|   |      | 4.2.3                                              | Voltage Step-up/Step-down Circuits                  | 82  |

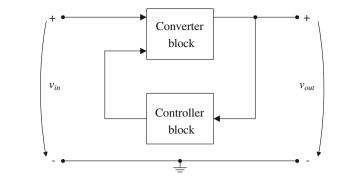

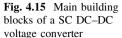

|   | 4.3  | Switched-Capacitor (SC) DC–DC Voltage Converters 8 |                                                     | 86  |

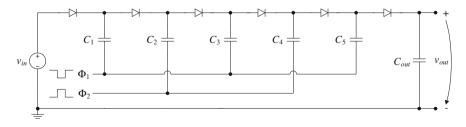

|   |      | 4.3.1                                              | Voltage Step-up Converter Using the Ladder          |     |

|   |      |                                                    | Topology                                            | 89  |

|   |      | 4.3.2                                              | Voltage Step-up Converter Using the                 |     |

|   |      |                                                    | Cockcroft–Walton Topology                           | 91  |

|   |      | 4.3.3                                              | Voltage Step-up Converter Using the Dickson         |     |

|   |      |                                                    | Charge Pump Topology                                | 92  |

|   |      | 4.3.4                                              | Voltage Step-up Converter Using the Fibonacci       |     |

|   |      |                                                    | Topology                                            | 94  |

|   |      | 4.3.5                                              | Voltage Step-up Converter Using the Parallel-Series |     |

|   |      |                                                    | Topology                                            | 94  |

|   |      | 4.3.6                                              | Voltage Step-up Converter Using the Voltage         |     |

|   |      |                                                    | Doubler Topology                                    | 95  |

|   | 4.4  |                                                    | y Storing Devices                                   | 97  |

|   |      | 4.4.1                                              | Batteries                                           | 98  |

|   |      | 4.4.2                                              | Supercapacitors                                     | 100 |

|   | 4.5  |                                                    | num Power Point Tracking (MPPT) Techniques          | 103 |

|   |      | 4.5.1                                              | Introduction                                        | 103 |

|   |      | 4.5.2                                              | Quasi-MPPT Techniques                               | 105 |

|   |      | 4.5.3    | True MPPT Techniques                              | 107 |

|---|------|----------|---------------------------------------------------|-----|

|   |      | 4.5.4    | Critical Analysis                                 | 108 |

|   | 4.6  | Concl    | usions                                            | 110 |

|   | Refe | erences  |                                                   | 111 |

|   |      |          |                                                   |     |

| 5 | Proj |          | Energy Harvesting System                          | 117 |

|   | 5.1  |          | uction                                            | 117 |

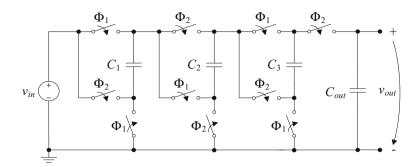

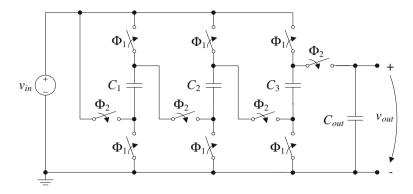

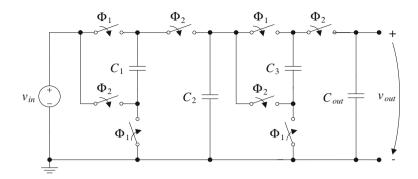

|   | 5.2  | SC Vo    | oltage Doubler                                    | 118 |

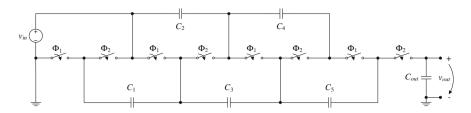

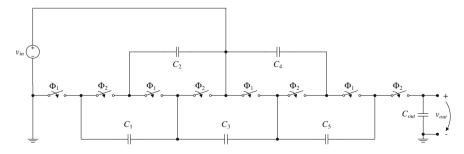

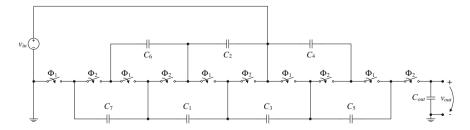

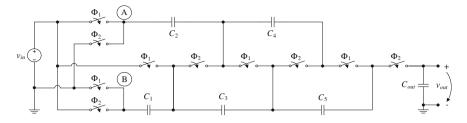

|   |      | 5.2.1    | SC Voltage Doubler with Charge Reusing            | 124 |

|   | 5.3  |          | Controller                                        | 131 |

|   |      | 5.3.1    | MPPT Regulation Using the Fractional Open-Circuit |     |

|   |      |          | Voltage                                           | 131 |

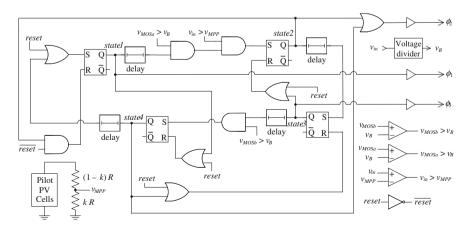

|   |      | 5.3.2    | Asynchronous State Machine (ASM) Circuit          | 132 |

|   | 5.4  | Local    | Supply                                            | 142 |

|   | 5.5  | Start-ı  | ир                                                | 143 |

|   |      | 5.5.1    | Electrical Structure and Operating Principle      | 143 |

|   | 5.6  | Voltag   | ge Limiter Circuit.                               | 144 |

|   |      | 5.6.1    | Motivation and Background                         | 144 |

|   |      | 5.6.2    | Voltage Limiter Circuit Architecture              | 147 |

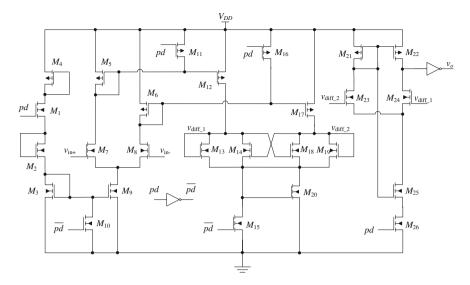

|   |      | 5.6.3    | Voltage Reference Circuit.                        | 147 |

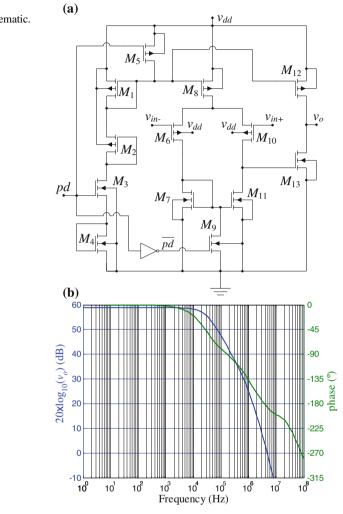

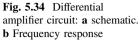

|   |      | 5.6.4    | Differential Voltage Amplifier.                   | 148 |

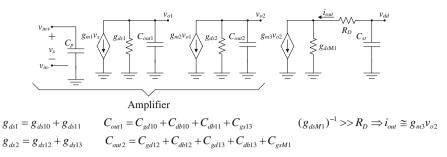

|   |      | 5.6.5    | Stability Analysis                                | 149 |

|   |      | 5.6.6    | Simulated Performance of the Voltage Limiter      | 151 |

|   | 5.7  | Concl    | usions                                            | 153 |

|   | Refe | erences  |                                                   | 154 |

|   |      |          |                                                   |     |

| 6 | Lay  | out of t | the System                                        | 157 |

|   | 6.1  | Introd   | uction                                            | 157 |

|   | 6.2  | SC Vo    | oltage Doubler                                    | 158 |

|   |      | 6.2.1    | Switches                                          | 158 |

|   |      | 6.2.2    | MOSFET Capacitors                                 | 159 |

|   | 6.3  | Phase    | Controller                                        | 161 |

|   |      | 6.3.1    | Logic Gates                                       | 161 |

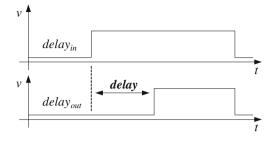

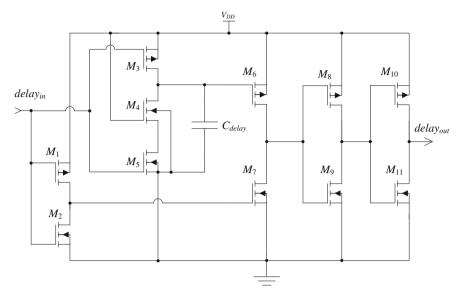

|   |      | 6.3.2    | Delay Circuits                                    | 162 |

|   |      | 6.3.3    | Voltage Divider and Its Respective Decoupling     | 164 |

|   |      | 6.3.4    | Comparator Circuits                               | 165 |

|   | 6.4  | Local    | Supply                                            | 166 |

|   | 6.5  | Start-u  | ıp Circuit                                        | 168 |

|   | 6.6  | Voltag   | ge Limiter Circuit.                               | 168 |

|   |      | 6.6.1    | Voltage Reference Circuit.                        | 168 |

|   |      | 6.6.2    | Differential Voltage Amplifier                    | 169 |

|   |      | 6.6.3    | Complete Layout of the Voltage Limiter Circuit    | 170 |

|                                                                            | 6.7  | Overall Circuit and Pin Assignment                    | 170 |

|----------------------------------------------------------------------------|------|-------------------------------------------------------|-----|

|                                                                            | 6.8  | Extracted Layout Simulation                           | 175 |

|                                                                            | 6.9  | Conclusions                                           | 177 |

|                                                                            | Refe | rences                                                | 177 |

| 7                                                                          | Exp  | erimental Evaluation of the Prototype                 | 179 |

|                                                                            | 7.1  | Experimental Prototype                                | 179 |

|                                                                            | 7.2  | Experimental Results                                  | 181 |

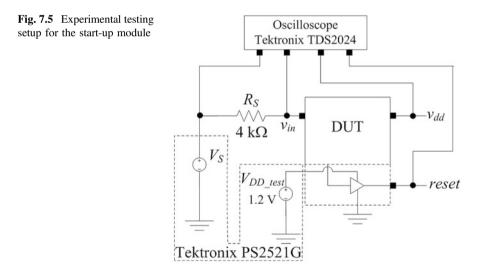

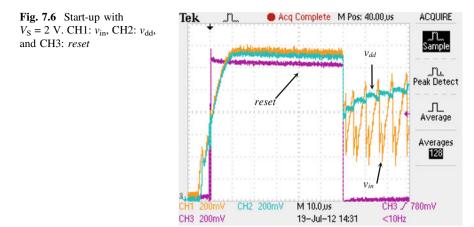

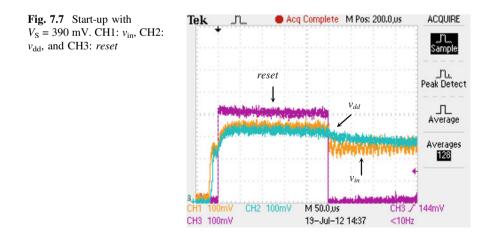

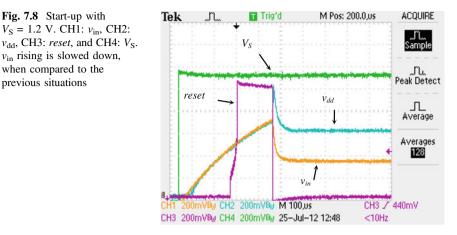

|                                                                            |      | 7.2.1 Experimental Evaluation of the Start-up Circuit | 181 |

|                                                                            |      | 7.2.2 Experimental Evaluation of the DC–DC Converter  | 184 |

|                                                                            |      | 7.2.3 Experimental Evaluation of the MPPT Controller  | 190 |

|                                                                            |      | 7.2.4 Experimental Results Using the PV Cells         | 192 |

|                                                                            | Refe | rence                                                 | 195 |

| 8                                                                          | Con  | clusions and Future Perspectives                      | 197 |

|                                                                            | 8.1  | Summary and Achievements                              | 197 |

|                                                                            | 8.2  | Future Perspectives                                   | 199 |

|                                                                            | Refe | rences                                                | 201 |

| Ap                                                                         | pend | ix A: Light Power Measuring Device                    | 203 |

| Ap                                                                         | pend | ix B: Description of the Manufactured PV Cell         | 207 |

| Appendix C: Computation of Power in a Circuit<br>with a Switched-Capacitor |      |                                                       | 213 |

# Acronyms

| AC               | Alternating current                               |

|------------------|---------------------------------------------------|

| a-Si:H           | Hydrogenated amorphous silicon                    |

| ASM              | Asynchronous state machine                        |

| BEEM             | Building energy and environment monitoring        |

| CCM              | Continuous conduction mode                        |

| CMOS             | Complementary metal-oxide-semiconductor           |

| CPU              | Central processing unit                           |

| c-Si             | Crystalline silicon                               |

| DC               | Direct current                                    |

| DC-DC            | Direct current to direct current                  |

| DLC              | Double-layer capacitor                            |

| DUT              | Device under test                                 |

| ESD              | Electrostatic discharge                           |

| EWT              | Emitter wrap through                              |

| FF               | Fill factor                                       |

| I <sup>2</sup> C | Inter-integrated circuit                          |

| IC               | Integrated circuit                                |

| IoT              | Internet of Things                                |

| LDO              | Low dropout                                       |

| MEMS             | Micro-electromechanical system                    |

| MFC              | Microbial fuel cell                               |

| MOSFET           | Metal-oxide-semiconductor field-effect transistor |

| MPP              | Maximum power point                               |

| MPPT             | Maximum power point tracking                      |

| OTEC             | Ocean thermal energy conversion                   |

| PCB              | Printed circuit board                             |

| PEC              | Photosynthetic electrochemical cell               |

| PSD              | Power spectral density                            |

| PV               | Photovoltaic                                      |

| RF               | Radio frequency                                   |

| RFID             | Radio frequency identification                    |

|                  |                                                   |

| SC    | Switched-capacitor                        |

|-------|-------------------------------------------|

| SEPIC | Single-ended primary inductance converter |

| SHM   | Structural health monitoring              |

| SLA   | Sealed lead acid                          |

| SOI   | Silicon on insulator                      |

| STC   | Standard test conditions                  |

| TEG   | Thermoelectric generator                  |

| UWB   | Ultra-wide band                           |

| VCR   | Voltage conversion ratio                  |

| VRC   | Voltage reference circuit                 |

| WBAN  | Wireless body area network                |

| WMSN  | Wireless multimedia sensor network        |

| WSN   | Wireless sensor network                   |

| WWTP  | Wastewater treatment plant                |

# Chapter 1 Introduction

**Abstract** The aim of this chapter is to give the reader a general overview about the subject that will be addressed in this book. Firstly, a contextualization is carried out, in order to show where the whole subject fits in and what are the main purposes and challenges. Secondly, the organization of this book is presented, so as to give the reader the road map of what can be found in it.

#### **1.1 Motivation and Context**

The capability of electronic circuits to obtain energy from the surrounding environment, for self-powering, is an interesting feature that has gained increased attention [1], either for sensor networks [2, 3] or for embedded systems [4]. This capability allows for electronic devices to operate without the need to be connected to the power grid, nor the replacement of batteries on a regular basis [1, 3, 5, 6]. This feature is especially important for sensor networks, because the remote sensor nodes can be deployed to any place where a sufficient amount of energy can be obtained from the environment. These networks can be used in a wide range of applications [3], and therefore, the design of low-cost energy harvesting devices and networks is attracting more attention [2]. This philosophy is promising to take over the powering paradigm, in opposition to traditional powering methods, involving batteries or a cord connection to the power grid. Moreover, if there is the intent of deploying a wireless sensor network (WSN) where the extension of the power grid is infeasible, or the replacement of batteries has a large cost, the use of self-powered nodes is the only option. Sensor networks that solely rely on grid connections are limited by having the sensors located close to a power outlet or from the power grid. Thus, if one wants ubiquity and pervasive operation, relying on the power grid is an evident limiting factor.

One step forward toward unlimited sensor location could be the use of batteries. This allows for complete freedom in the location of the sensors. However, one last obstacle remains, which is the batteries themselves, because as their stored energy

C.M. Ferreira Carvalho and N.F.S.V. Paulino, *CMOS Indoor Light Energy Harvesting System for Wireless Sensing Applications*, DOI 10.1007/978-3-319-21617-1\_1

gets depleted, they need to be replaced. Eventually, this can be a problem if a large number of sensors are deployed and if they reside in places that are difficult to reach. As such, the trivial operation of battery replacement can become expensive and burdensome.

To achieve indefinite operation in inhospitable locations, the sensors must be powered in such a way that they can obtain their power directly from the surrounding environment. This kind of procedure is commonly known as energy harvesting, or energy scavenging. Besides its ubiquitous facet, energy harvesting also reveals to be interesting both in ecological and in economical terms. Avoiding the need of batteries, for system main powering purposes, the sensor system will not be responsible for contributing to chemical pollution caused by disposing of batteries, or even their manufacturing, in the first place. In economical terms, not using batteries represents cost reduction both in devices and in replacement procedures.

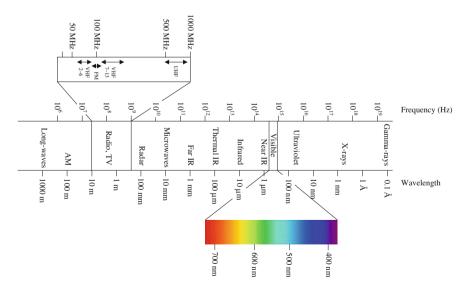

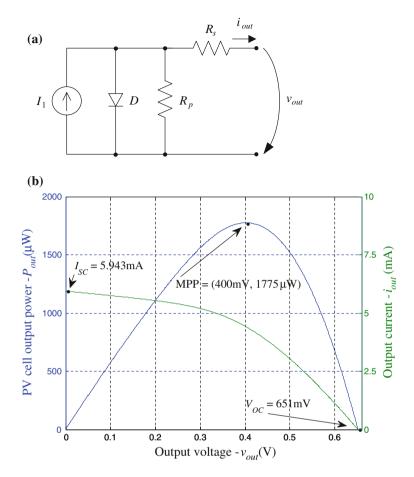

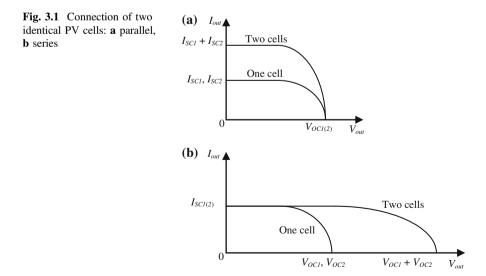

Energy harvesting systems can obtain energy from different sources: light (solar [5] or artificial [7]), electromagnetic emissions [8], mechanical movements (e.g., vibrations) [9], thermal gradients [10], etc. All of these sources share a common limitation: low energy density. This means that the electronic circuits inside the sensor node must operate using extremely low energy levels and must have efficiencies as high as possible. This poses significant design challenges. Furthermore, in many applications, the very limited available energy forces the circuits to remain in a power-down state for most of the time, until enough energy has been harvested and stored. Among all energy sources, light is the one with the highest density by volume unit, for low-power systems [5]. Moreover, photovoltaic (PV) cells are more compact devices than those that harvest energy from other sources and can be compatible with some CMOS processes [11].

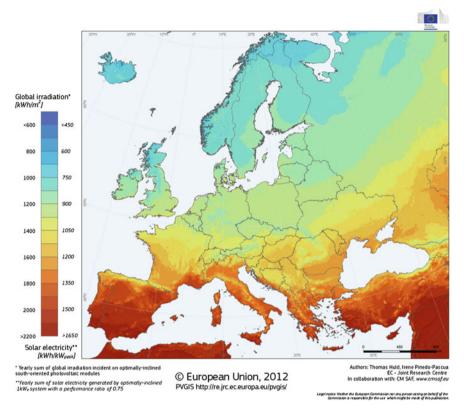

In indoor environments, it can be preferable to have a sensor, or network of sensors, self-supplied, in order to avoid the use of any cord connection. Using harvested energy, the costs of material such as cable duct, the tangling of wires, or any other inconvenient can be avoided, in addition to having the freedom to put the nodes where exactly required. Energy can also be obtained from the light existing indoors; however, using indoor light to power an electronic application represents an increased challenge. The levels of available light energy inside buildings are much lower than those that can be obtained outside, and the available light energy in indoor environments can vary significantly, since the light from the Sun is attenuated and can be mixed with artificial light.

This book describes an indoor light energy harvesting system intended to power a sensor node, enabling a network similar to the one described in [12]. Although designed to cope with indoor light levels, the system is also able to work with higher levels, making it an all-round light energy harvesting system.

A powered sensor circuit can work in an ON–OFF regime, with a low duty cycle. When the voltage in a storage capacitor becomes larger than a certain value, the sensor circuit can be turned on, drawing current from the storage capacitor, thus reducing its voltage. This will control the maximum output voltage produced by the harvesting system.

The system described in this book can be fully integrated in CMOS (except for the PV cells and the energy storing large value capacitor), to minimize size and cost.

The harvested energy can be stored, either in a supercapacitor [13, 14] or in a rechargeable battery [15]. The use of any of these devices enables the node to work when there is no energy available from the environment. In order to maximize the harvested power from a PV cell, it is necessary to use a DC–DC converter that can track the MPP of the PV panel. In this book, it is proposed to develop a MPPT DC–DC converter based on switched-capacitor (SC) networks instead of inductors [15], to reduce both the cost and volume of the system. The MPPT algorithm will be implemented in the analog domain to save power, putting aside any implementation based on a microcontroller.

Given that some amount of harvested energy is needed to power the control circuits, it is expectable that the efficiency, at this power level, will yield a lower value than that of a larger power application, using the same principles and algorithms. The maximum efficiencies are between 60 and 70 % [13, 15]. One thing to keep in mind is that the total harvested energy must be such that it can be made useful for powering the desired application or circuit and also to self-power the control circuitry that manages the harvester. This demand is formally stated in the literature, as the *Energy Neutrality* [4, 16]. Generally speaking, the system will be able to work whenever it has the available energy to do it. If the system has the ability to permanently harvest enough energy from the environment, then it can permanently operate, although occasional interruptions may eventually exist. This means that interruptions will have to be tolerable, or even they can be a strategy of operation. There are a number of strategies that can be adopted, according to the type of system usage [16].

The objective of the system presented in this book is to show that it is possible to manufacture the harvesting section, such that it can work with the available energy from its surroundings, proving that this concept can be viable. It is expected that the developed system can be adapted to work with different types of sensors such as temperature, pressure, and light. If the purpose of the system is to transmit the light intensity received by the PV cells, then this information will be available from the operating frequency of the DC–DC converter. Such a node could prove its usefulness by monitoring the light conditions inside a room and, using this information, adjust the illumination to an optimal level, optimizing the electrical energy usage. This is why the system must be robust enough to operate in indoor environments, where the available light is substantially less than in outdoor scenarios [16].

Another strong motivation deals with economy and with environmental sustainability. As the overall system is intended to operate without the need of common batteries to get powered, it will pay off in the long term, since there is no need to buy additional powering components. Moreover, the power received from the surrounding environment is zero cost.

In addition to the economic benefit, not using batteries also means that it will not be necessary to use any process for recycling drained devices. This environmental aspect is particularly important, even though the most recent generation of batteries is progressively making use of less polluting materials. Yet a more primary consequence of avoiding battery powering is the fact that batteries do not even need to be manufactured, in the first place.

According to the present trends, and thinking about a broader application, the node supplied by the proposed system could be a part of the Internet of Things (IoT).

#### **1.2 Book Organization**

This book is organized as follows: Chap. 2 presents an overview about energy harvesting electronic systems, namely regarding energy harvestable sources and a comparison between them. Chapter 3 shows a study about PV cell technologies, an integrated CMOS PV cell that was actually implemented and a light energy availability assessment in indoor environments, in order to check the realistic conditions of the design. Chapter 4 shows the issues related to DC–DC converters, MPPT techniques, and energy storing devices. Chapter 5 presents the design of the proposed system. The step-up converter architecture, the design of the ASM that controls the switching, and the MPPT technique than is jointly used are described. Chapter 6 presents the physical implementation of the system, i.e., its layout in integrated circuit, using a CMOS technology. Chapter 7 presents the experimental test bed, its details, and the results that were obtained from the complete manufactured prototype, composed by the integrated system and the PV cells. Finally, Chap. 8 presents the conclusions about this work, discussing the issues and the results that were shown, and future perspectives are also suggested. In the References block, the complete list of the literature references is given, which served to aid in the making of all of this work.

Additionally, there are three appendixes. In Appendix A, the light measuring device, used for the light availability study performed in Chap. 3, as well as its accessories, is presented so as to have an overview about it. Appendix B presents the manufacturing, characterization, and analysis process of an amorphous silicon PV cell that has been specifically designed and manufactured for this work. The results about a prototype cell are presented, consisting of the parameters that can be used to model the cell for different ambient light intensities. Finally, Appendix C presents a short study about how to use the waveform results given by the simulations in Spectre, so that the correct measurements about power can be computed, when dealing with SC circuits.

#### References

- 1. Paradiso, J. A., & Starner, T. (2005). Energy scavenging for mobile and wireless electronics. *IEEE Pervasive Computing*, 4(1), 18–27.

- Kansal, A., & Srivastava, M. B. (2003). An environmental energy harvesting framework for sensor networks. In *Proceedings of the International Symposium on Low Power Electronics* and Design (ISLPED'03), 25–27 August 2003, pp. 481–486.

- Chou, P. H., & Park, C. (2005). Energy-efficient platform designs for real-world wireless sensing applications. In *Proceedings of the IEEE ACM International Conference on Computer-Aided Design (ICCAD-2005)*, 6–10 November 2005, pp. 913–920.

- Raghunathan, V., & Chou, P. H. (2006). Design and power management of energy harvesting embedded Systems. In *Proceedings of the International Symposium on Low Power Electronics and Design (ISLPED'06)*, 4–6 October 2006, pp. 369–374.

- Chalasani, S., & Conrad, J. M. (2008). A survey of energy harvesting sources for embedded systems. In *Proceedings of IEEE Southeastcon 2008*, 3–6 April 2008, pp. 442–447.

- Jiang, X., Polastre, J., & Culler, D. (2005). Perpetual environmentally powered sensor networks. In *Fourth International Symposium on Information Processing in Sensor Networks* (*IPSN 2005*), 15 April 2005, pp. 463–468.

- Hande, A., Polk, T., Walker, W., & Bhatia, D. (2007). Indoor solar energy harvesting for sensor network router nodes. *Microprocessors and Microsystems*, 31(6), 420–432.

- 8. Dallago, E., Danioni, A., Marchesi, M., Nucita, V., & Venchi, G. (2011). A self-powered electronic interface for electromagnetic energy harvester. *IEEE Transactions on Power Electronics*, 26(11), 3174–3182.

- Kong, N., & Ha, D. S. (2012). Low-power design of a self-powered piezoelectric energy harvesting system with maximum power point tracking. *IEEE Transactions on Power Electronics*, 27(5), 2298–2308.

- Lhermet, H., Condemine, C., Plissonnier, M., Salot, R., Audebert, P., & Rosset, M. (2008). Efficient power management circuit: thermal energy harvesting to above-IC microbattery energy storage. *IEEE Journal of Solid-State Circuits*, 43(1), 246–255.

- Guilar, N. J., Kleeburg, T. J., Chen, A., Yankelevich, D. R., & Amirtharajah, R. (2009). Integrated solar energy harvesting and storage. *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, 17(5), 627–637.

- Wang, W., Wang, N., Jafer, E., Hayes, M., O'Flynn, B., & O'Mathuna, C. (2010). Autonomous wireless sensor network based building energy and environment monitoring system design. In *Proceedings of the 2nd Conference on Environmental Science and Information Application Technology (ESIAT)*, 17–18 July 2010, pp. 367–372.

- 13. Brunelli, D., Moser, C., Thiele, L., & Benini, L. (2009). Design of a solar-harvesting circuit for batteryless embedded systems. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 56(11), November 2009, pp. 2519–2528.

- Simjee, F., & Chou, P. H. (2006). Everlast: Long-life, super-capacitor-operated wireless sensor node. In *Proceedings of the 2006 International Symposium on Low Power Electronics and Design (ISLPED'06)*, 4–6 October 2006, pp. 197–202.

- 15. Shao, H, Tsui, C.-Y., & Ki, W.-H. (2009). The design of a micro power management system for applications using photovoltaic cells with the maximum output power control. *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, *17*(8), 1138–1142.

- Pimentel, D., & Musilek, P. (2010). Power management with energy harvesting devices. In Proceedings of the 23rd Canadian Conference on Electrical and Computer Engineering (CCECE), 2–5 May 2010, pp. 1–4.

## Chapter 2 Energy Harvesting Electronic Systems

**Abstract** This chapter presents a literature review about the various ambient energy sources that can be harvested and the description of some related systems. As such, this chapter will provide a brief overview about each source and describe some systems that use that same energy source. This will be extended on to the domain of the wireless sensor networks and the aspects related to it, being presented some examples of energy harvesting powered WSN in different environments. A brief description of what is expected from each network and how it succeeds in harvesting the energy that enables it to work will receive a particular focus. Since light is the energy source being harvested, in order to power the system described in this book, some more attention will be dedicated to the analysis of this source. Proceeding with this purpose, a more detailed overview about PV technologies will be given in Chap. 3. In addition, a more focused insight covering DC–DC converters, energy storing devices, and MPPT techniques will be given in Chap. 4, so as to complete the literature review opened up in the present chapter.

#### 2.1 Available Energy Sources

In the surrounding environment, there are a number of possible energy sources that can be conveniently harvested, in order to power electronic applications [1]. Depending on whether a certain energy source is more abundant, that could be the preferred one.

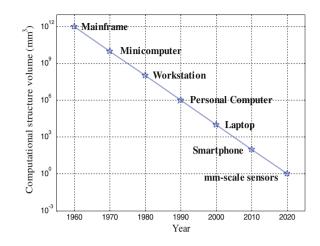

However, another possible configuration that performs ambient energy scavenging relies on the conjunction of multiple energy sources, like in [1–7]. The latter is a highly miniaturized system, designed to have modularity, in the sense that one can add or remove IC layers, which communicate among themselves using the  $I^2C$ protocol. This system occupies a volume of only 1 mm<sup>3</sup>, entering in the category of smart dust, which are wireless sensor nodes with perpetual energy harvesting. Next, Fig. 2.1 shows the evolution in terms of volume reduction that occurred over the past decades, in conformity with Bell's law, as stated in [7]. This law is somewhat related to the well-known Moore's law [8], although the latter may probably be reaching its limit [9].

The scavenged energy sources more commonly used are presented in this chapter and very briefly described and characterized in the following subsections, as a more detailed overview is outside the scope of this book. However, relevant references will be given, in order to aid in getting a broader insight about each source and related systems that are specifically designed to work with it.

#### 2.1.1 Mechanical Energy

Mechanical energy can be harvested from various natural sources, such as wind [10], wave motion [11], vehicle motion, or in general, any kind of vibrations or movement, namely by resonance. There is an important issue specific to mechanical energy harvesting systems, which is the need to have rectifying circuits. As one is dealing with alternating signals, an AC to DC conversion must be carried out. The rectifiers can be passive or active. The former ones are based on diode topologies, namely rectifier bridges, while the latter ones employ some means of switching power conversion, as in [12].

There are several ways of converting mechanical energy into electrical energy, from which one can choose. This conversion can be done by using electromagnetic [1, 13], piezoelectric [14], or electrostatic means [15]. According to [13], the most suitable materials to harvest mechanical energy are those that exploit the electromagnetic and the piezoelectric principles, possessing the highest power density, when compared to the electrostatic ones. Each of these materials has a different electrical behavior, and thus, when using any of them, a different electric interface must be used. Harvesters exploiting vibrations presently have an efficiency ranging from 25 to 50 % [16].

#### 2.1.1.1 Electromagnetic Conversion

In order to have the possibility to perform simulations, destinated to check any proof of concept, it is necessary to have a model of the harvester device. In the mechanical context, when dealing with electromagnetic conversion devices, it is usual to have finite element method (FEM) models, so as to have a suitable representation of the harvester. This model can be used in conjunction with electric circuits, in order to enable a simulation. For example, in [13], an electromagnetic energy harvester is studied using this approach. From the FEM model, one can extrapolate a block diagram model at the numerical level and this one can then be translated to Spectre, for example, allowing for electric simulation. In the block diagram model, one will have the kinematic variables playing their role.

Electromagnetic transducers generate a voltage offering a low impedance output, and typically, electromagnetic conversion is used for larger power levels than the ones aimed by this book, and, therefore, it will not be addressed further. Moreover, the cost of this type of converters is higher than that for other types.

#### 2.1.1.2 Piezoelectric Conversion

There is a material, Lead Zirconium Titanate (PZT), widely used for this conversion, which is considered as the silicon counterpart of piezoelectric materials, when dealing with engineering applications, as it can be found in [6, 17, 18].

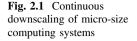

A piezoelectric energy harvester is typically a cantilevered beam with one or two piezoceramic layers, which can vibrate in various vibration modes. The induced strain is converted into electrical charge, originating a voltage. The generated voltage is proportional to the force and thus to the vibration magnitude applied to the harvester. However, piezoelectric energy transducers are characterized by a high impedance output, unlike conventional voltage sources. This results in the need to use appropriate electric circuits that correctly interface with this type of transducer. The voltage generation mechanism is illustrated in Fig. 2.2.

This kind of mechanism is bidirectional, such that by applying a voltage will result in a deformation, meaning that these materials can be used both as sensors and as actuators.

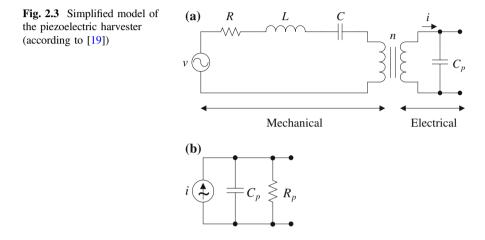

The simplified electric model of a unimodal piezoelectric harvester is represented in Fig. 2.3a.

At the left-hand side of Fig. 2.3a, the mechanical part of the model is represented, where R, L, and C represent the mechanical parameter loss, mass, and stiffness, respectively. The transition from the mechanical to the electrical domain is modeled by a transformer with a ratio of n, where the conversion from stiffness to the current i is performed, instead of using the generated voltage directly. At the right-hand side, i.e., in the electrical domain,  $C_p$  represents the plate capacitance of the piezoelectric material. When at resonance, the whole circuit can be simplified to a current source in parallel with a capacitor and a resistor, in which the latter represents the losses. This model is depicted in Fig. 2.3b. With this circuit, the MPP

Fig. 2.2 Voltage generation mechanism in a piezoelectric harvester

condition can be achieved if the load connected at the output is the conjugate of the impedance represented by  $C_p$  and  $R_p$ , i.e., the load must have an inductive component.

#### 2.1.1.3 Electrostatic Conversion

Micro-electrical mechanical systems (MEMS) are well suited to collect mechanical energy. Devices using this kind of technology can be built so as to be compatible with CMOS integration, in order to lay out both the harvester and the energy processing system in the same die.

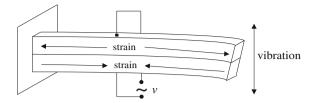

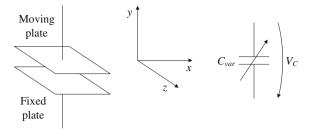

Basically, the harvester can consist of a simple variable plate-distance capacitor. The energy conversion can be achieved in two ways, either by varying the gap between the plates or by varying their overlap. A simple way to illustrate this principle is by looking at Fig. 2.4, representing a rest position, from where the moving plate can suffer a translation along any of the axis, as a consequence of vibrations or any other motion.

If this translation occurs along the *y*-axis, the distance between plates will vary, and the capacitance will vary accordingly, in an inversely proportional way. On the other hand, if the translation occurs along the *x*- or the *z*-axis, the plate overlap will

Fig. 2.4 Symbolic representation of the conversion mechanism using MEMS

decrease and so will the resulting capacitance. If the capacitor is precharged and then kept open-circuited with a constant charge, the capacitance variation will change the voltage of the capacitor ( $V_C$ ) and, consequently, the stored energy [20].

The variation of capacitance is given by the parallel plate capacitor equation,

$$C_{\rm var} = \varepsilon_0 \varepsilon_r \frac{A}{d}, \qquad (2.1)$$

and relies on modifying either the superposition area of the plates of the capacitor (*A*), the distance between plates (*d*), or even the dielectric constant of the insulation material between plates ( $\varepsilon_r$ ), if a different material is inserted in between.  $\varepsilon_0$  is the dielectric constant of vacuum.

By having established the value for the variable capacitance, the voltage that appears at the terminals of the capacitor is

$$V_{\rm C} = \frac{Q}{C_{\rm var}},\tag{2.2}$$

and the energy that can be used thanks to this generation process, if the capacitor is discharged over a resistor *R* during an interval  $t_{on}$ , is

$$E(t) = \int_{0}^{t_{on}} \frac{V_{\rm C}^2}{R} e^{-\frac{2t}{RC_{\rm var}}} dt.$$

(2.3)

MEMS are also compatible with both the piezoelectric and electromagnetic processes.

#### 2.1.2 Thermal Gradients

Obtaining energy from temperature sources may be an option in certain contexts, for instance, where there are high temperatures, such as furnaces or exhaust pipes.

These can be conveniently scavenged as a thermal source, providing a consistent amount of power [1, 3, 17, 18].

Thermoelectric generators (TEG) have the advantageous characteristics of requiring little or none amount of human intervention during their useful lifetime. Moreover, these devices are reliable and quiet, as there are no moving parts.

Current thermoelectric materials can only convert a maximum of 5–6 % of the useful heat into electricity. However, significant research is being carried out, in order to develop new materials and module constructions which can eventually reach a harvesting efficiency higher than 10 % [21].

A thermoelectric element converts thermal energy, in the form of temperature differences, into electrical energy and vice versa. Devices using  $Bi_2Te_3$  have already proven their usefulness [18] and showed to possess the highest figure of merit [22], defined as

$$Z \cdot T = \frac{\alpha^2 \sigma}{\lambda} \cdot T, \qquad (2.4)$$

in which, *T* is the temperature,  $\alpha$  is the Seebeck coefficient,  $\sigma$  is the electrical resistivity, and  $\lambda$  is thermal conductivity. Using this material, for temperatures between -50 and 80 °C, the figure of merit in (2.4) can reach values up to unity.

The drawback behind this kind of source comes from the hostile environment to be scavenged, having to take particular care with the electronic circuits being powered. Thermopiles are among the other types of devices to achieve harvesting from this kind of source, but there are also some novel devices and systems under research [17, 23].

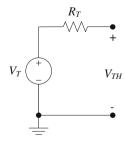

The model of a thermoelectric energy harvester is a simple Thévenin equivalent circuit, like the one shown in Fig. 2.5.

The voltage  $V_{\rm T}$  is an open-circuit voltage proportional to the temperature difference between both sides of the TEG, and to the Seebeck coefficient. The latter depends on the material being used and represents a measure of the magnitude of an induced thermoelectric voltage, in response to a temperature difference across that same material. In the model of Fig. 2.5, resistance  $R_{\rm T}$  represents the loss of the model of the TEG and  $V_{\rm TH}$  is the output voltage of the harvester. According to the maximum power transfer theorem, the maximum power point can be achieved by matching a load resistance to the source resistance,  $R_{\rm T}$ .

**Fig. 2.5** Electrical equivalent of the thermoelectric generator

The Seebeck effect is the generation of an electromotive force within two different metals, when their junctions are maintained at different temperatures. A common application of this principle is the use of thermocouples to measure temperature. However, when a thermocouple is used in temperature measurements, the electromotive force being generated is countered by an applied voltage, resulting in no current flowing. The main difference, between using the thermoelectric effect for temperature measurement or for power generation, is the use of semiconductor materials, instead of metals, when the purpose is the latter. This use enables the flow of current in the generator, allowing it to produce power.

The Seebeck coefficient is defined as the obtained voltage variation in response to each degree of temperature gradient. Thus, the thermoelectrically generated voltage in the model of Fig. 2.5 ( $V_{\rm T}$ ) is given by (2.5), where S is the Seebeck coefficient (expressed in V/K), which is material-dependent, and  $\Delta T$  is the temperature difference between the hot and the cold sides of the harvester device.

$$V_{\rm T} = S\Delta T. \tag{2.5}$$

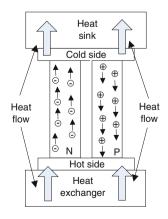

Semiconductor materials have a significantly higher Seebeck coefficient, when compared to metals, and so they are more suited to manufacture power generator devices. The Seebeck effect in the n-type material creates a flow of excess electrons from the hot junction to the cold one. In the p-type material, holes migrate toward the cold side creating a net current flow which is in the same direction as the one in the n-type material. In Fig. 2.6, the simplified schematic structure of a typical semiconductor thermoelectric device is shown.

MEMS structures are also used for building TEG, and, in [24], a new MEMS fabrication method is presented.

For example, a WSN able to monitor the health of the structure of an aircraft can be established [22]. One of the main advantages of a WSN is to avoid complex wiring, saving material, and consequently weight and cost. The temperature difference obtained between the aircraft cabin and the aircraft body shell, at high altitudes, can be such to obtain a high potential.

**Fig. 2.6** Typical structure of a semiconductor thermoelectric harvester

At a bigger scale, thinking about renewable energy sources and environmental issues, [25] proposes using ocean thermal energy conversion (OTEC), by taking advantage of the difference of about 20 °C existing in subzero regions. Since the water is almost at freezing level, and the outside temperature can be at about -20 °C, this permanent temperature gradient is suitable for thermal energy harvesting. At a smaller scale, this factor could be interesting to deploy a WSN in these geographical zones of the ocean, with the nodes being supplied by this harvestable source.

There are also environments at a much smaller scale, such as wireless body area networks (WBAN), which can also make use of thermal gradients, by using human warmth. This topic will be further explored in Sect. 2.1.4.

More recently, new technologies have been developed by using an innovative concept of mixing mechanical and thermal energy to harvest energy. This is done by firstly using heat to provoke a deformation in a material, such as a bimetallic. Secondly, that deformation, by electrostatic conversion (see Sect. 2.1.1.3), is used to produce energy. Such developments can be found in [26, 27].

#### 2.1.3 Radio Frequency Electromagnetic Energy

In environments mostly located in urban areas, one source that becomes appealing to be harvested is the radio frequency (RF) energy. This energy exists around every place and is generated by sources such as radio and television broadcasting, mobile phone cellular network, Wi-Fi networks, and other sources alike.

One important factor that makes this source very appealing to harvest is the fact that ambient RF energy, as a power source for outdoor sensor nodes, is typically available all the time, either day or night.

As the harvested signals are AC, in order to provide at the end of the chain a stable DC supply, it is necessary to use rectifiers to perform such a conditioning, like it can be found in [3, 6, 28]. Harvesters exploiting the RF sources presently have an efficiency that can go up to 50 % [16].

The low magnitude of the voltages resulting from the RF energy harvesting process is at such reduced level that the design of rectifiers is very challenging, since many half-wave or full-wave diode rectifiers require nonzero turn-on voltages to operate.

Typical rectifier circuits are based on the well-known diode bridge. These can make use of NMOS or PMOS transistors and can implement half- or full-wave rectifiers. According to design parameters and required performance, some trade-offs must be adopted.

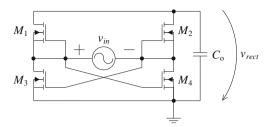

In Fig. 2.7, a way of implementing a MOSFET rectifier circuit using NMOS devices is shown [6]. Voltage  $v_{in}$  represents the RF source being harvested.

The rectifying process is as follows: When  $v_{in}$  is in its positive half cycle,  $M_1$  and  $M_4$  are conducting current, while  $M_2$  and  $M_3$  are in open circuit. During the negative half cycle of  $v_{in}$ , the roles of the transistors are exchanged. At the end, the rectified

Fig. 2.7 NMOS full-wave rectifier

voltage  $v_{\text{rect}}$  will ideally be a DC voltage, appearing at the terminals of the filtering capacitor  $C_{0}$ .

With circuits like the one shown, a low voltage drop ( $v_{ds}$ ) in the transistors implies using wide channels and low frequencies. On the opposite, narrow channels imply a higher voltage drop and the operation at higher frequencies. If, instead of just one transistor, several transistors are connected in parallel, the performance of the rectifier can be improved in terms of working frequency and voltage drop. This technique divides the total current by each one of the transistors in the parallel, thus reducing the voltage drop of each individual device. In addition, frequency can also be improved, because the size of each transistor is smaller, as compared to having just one big transistor. In [6], the implementation of full-wave rectifiers allowed to obtain voltage drops as low as 0.2 V and operating frequencies of 16 MHz, by using a parallel structure of transistors with  $W = 10 \ \mu m$  and  $L = 0.28 \ \mu m$ .

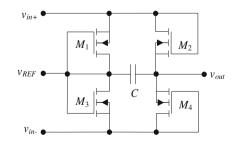

In [28], a different type of rectifier is used, by making a field-to-voltage conversion, which is not grounded. This structure is depicted in Fig. 2.8, where  $v_{in-}$  and  $v_{in+}$  connect to an antenna or similar device.

The  $v_{\text{REF}}$  terminal allows for offsetting the output voltage  $v_{\text{out}}$ . Using this structure, it is possible to stack several of these modules, in which the lower one can have  $v_{\text{REF}}$  grounded, while its output terminal connects to the  $v_{\text{REF}}$  terminal of the next structure, and so on. By doing so, the contribution of each rectifier helps to effectively increase the overall output voltage, so as to have, at the output of the upper structure, a suitable value to power an electronic application. A more detailed

Fig. 2.8 Full-wave rectifier, acting as a field-to-voltage converter

study of MOSFET rectifiers is done in [29], where the transistors are working in the weak inversion region, having all of the terminals being exploited.

This RF energy source appears typically in a very limited amount, representing a very low power density [17]. In order to assess the real availability of energy that could be made useful by using RF sources, by performing power density measurements, [30] surveys the expected power density levels from GSM 900 and GSM 1800 base stations at a certain distance and also in a WLAN environment. According to it, for distances ranging from 25 to 100 m from a GSM base station, power density levels range from 0.1 to 3.0 mW/m<sup>2</sup>. Measurements in a WLAN environment indicated even lower power density values, thus making GSM and WLAN unlikely to produce enough ambient RF energy for wirelessly powering miniature sensors. Also according to [30], a single GSM telephone has proven to deliver enough energy for wirelessly powering small applications at moderate distances.

In general, the levels of power density are much dependent on the frequency of operation and on the distance between the transmitter base station and the receiving harvester.

At a bigger scale, thinking about grid power transfer, [31] presents some results about wireless power transfer, although at reduced distances, as electromagnetic energy has a strong decay over distance and with the frequency being used.

An essential part of this kind of system is the antenna, in order to capture the radio signals. There is a system that agglutinates the functionality of antenna and rectifier, which is called a rectenna. These devices, and antennas in general, have a relatively low conversion efficiency, but this parameter is dependent on the frequency of operation. As such, the key parameters to have into consideration are bandwidth, polarization, directivity, and size. In order to be sensitive to a wider range of frequencies, the antenna must tend to be bigger, in order to capture the lower frequencies. The work in [32] presents an architecture for a RF energy harvesting system, where the system components such as the antenna and the ultra-wideband (UWB) input matching LC network are designed and studied in depth, as well as the optimum rectenna load. Also, a study about the availability of RF ambient energy, coming from digital television broadcasting in a given geographical area and its surroundings, is carried out in [32].

The work developed in [33], besides making use of television broadcasting, also uses the energy radiated by the base transceiver stations of the mobile telephone networks. The collected energy is sufficient to power a sensing application, whose objective is to transmit information about temperature and light. The duty cycle being used is very small, and the firmware is implemented with particular care about reducing computationally consuming operations.

The applications described in [3, 6] make use of radio frequency (RF) power as a resource to be harvested in conjunction with other sources. However, in [28, 32, 33], this is the only source being scavenged.

Another important set of applications that make use of RF energy harvesting is the radio frequency identification (RFID) tags, widely disseminated in commercially available consumer products. When queried by a reader device, the tag is momentarily powered by a RF signal close to it and responds by sending a coded identification number. The same type of device can also be used to identify live-stock or pets, in which the tag is implanted beneath the skin.

To harvest the electromagnetic energy in RFID systems, an antenna or an inductor coil must be used. However, as with other sources, this RF energy may present itself unpredictable and much dependent on the distance at which the reader is put from the tag. In [34], a system is presented in order to enhance range operation. Due to the dependence on the distance between the reader and the tag, voltage limiter circuits must be used to prevent any damage to the tag being read. Examples of limiter architectures with such a purpose are presented in [35, 36].

#### 2.1.4 Human Generation

The idea behind using applications powered by a human source is very interesting and has captivated the interest of researchers since some years ago [37]. The human body provides multiple sources of energy that can be harvested. According to [38], it has been shown that, ideally, 2.4–4.8 W of power is available in body heat, 0.4 W in exhalation, 0.37 W in blood pressure, 0.76–2.1 mW in finger motion, 60 W in arm motion, 67 W in heel strike, 69.8 W in ankle motion, 49.5 W in knee motion, 39.2 W in hip motion, 2.1 W in elbow motion, and 2.2 W in shoulder motion.

The necessity of providing energy to wearable computing devices made the conversion of human motion into useful electrical energy, a topic of extensive study. For instance, in gyms, there is some equipment, such as exercising bicycles that have their instrument panel powered by the user who is exercising. However, in such a situation, the user must strive forcefully into the production of the required energy. More broadly, in energy harvesting generated by human motion, the preferable situation is to have the user oblivious of such an action, while providing the necessary energy to power an electronic application. For example, the kinetic energy from human motion is already used to power electronic wrist watches [39]. In the medical domain, electronic medical implants can be powered by using the human heat as a power source.

In fact, the energy generated by human means is coming from a particular environment where there coexist some of the sources already described, namely the thermal gradients and the mechanical energy sources, but that are not restricted to these. Energy harvesting of electromagnetic radiations is also possible with the human body, as it will be shown ahead.

A very important class of applications, in a human energy harvesting environment, is the implantable biosensor. There are some requirements for these sensor systems, which are the reduced size, the complete absence of user intervention, once the applications have been deployed into the body, and the possibility of these applications to be hermetically sealed. All of these requirements come from the fact that the applications are to be deployed inside the human organism. An increased challenge exists, when using the human-originated energy sources, because of the limited power densities that these provide. When compared to sources originated in an industrial or outdoor environment, a single human body provides a reduced amount of power.

With respect to the mechanical generation, the movements of the body occur at a very low frequency, and concerning the thermal gradients, the difference of temperature between the human body and the outside environment is not very high, except perhaps, in extreme cold conditions. Moreover, if the body is immobile, a great deal of potentially available mechanical energy is not available. The best place to put a sensor powered by mechanical means would be in a limb, because this zone is prone to have a greater mechanical activity.

The limit values of the power generated from a linearly excited motion-driven generator with linear proof-mass motion, mounted on a walking person, when using a conventional MEMS-compatible and inertial micro-generator strapped to the human body are presented in [40]. These values are between 1 and 4  $\mu$ W for a device occupying around 0.25 mm<sup>3</sup>, rising to between 0.5 and 1.5 mW for a generator occupying 8 cm<sup>3</sup>.

In addition, the upper limit of the power generated from a vibration-driven device in a human worn application is presented, which is

$$P_{\max} = 2 \frac{Z_l Y_0 \omega^3 m}{\pi}.$$

(2.6)

In (2.6),  $Z_l$  is the amplitude of the inertial mass motion,  $Y_0$  is the amplitude of the driving motion, *m* is the value of the proof mass, and  $\omega$  is the angular frequency of the driving motion. Also in [40], it is assumed that when a person is running at 12 km/h,  $Y_0$  is 0.25 m and the excitation frequency is around 2 Hz.

The light energy source has some drawbacks when used in the human context. These drawbacks are the inexistence of light availability for devices implanted beneath the skin, or the shortage of light for devices worn under clothing. Although light is a very important source of power, it has been shown that thermoelectric devices, also a reliable solid-state technology, are superior to PV cells in the WBAN domain.

For human implantable devices, the thermoelectric generators are receiving increased attention. In order to maximize the amount of power that can be harvested, it is important to match the output impedance of the harvester with the load being supplied, both at the electrical and at the thermal domain. According to [40], the maximum of electric power that can be extracted from a thermoelectric generator is

$$P_{\rm max} = \frac{\left(n \, S \, \Delta T_{\rm TEG}\right)^2}{4R_{\rm T}}.\tag{2.7}$$

In this expression, *n* is the number of *P* and *N* elements like those in Fig. 2.6, *S* is the Seebeck coefficient,  $\Delta T_{\text{TEG}}$  is the thermal difference, and  $R_{\text{T}}$  is the electric resistance of the model of the thermoelectric generator, like the one in Fig. 2.5.

The human body has an almost constant temperature. This temperature is due to the metabolism, which has a power 58.15  $W/m^2$  over the body surface. A normal adult, with an average surface area of 1.7 m<sup>2</sup>, in thermal comfort and regular metabolism, has a heat loss of approximately 100 W. However, the metabolism can provide a value as low as 46  $W/m^2$ , while sleeping, or as high as 550  $W/m^2$ , when running at 15 km/h. During a common workday, sitting at an office, this value can be 70  $W/m^2$ , corresponding to a power dissipation of 119 W and a burn of about 10.3 MJ during a day [41]. The thermal gradient is established between the body temperature and air around the body. Even if the generated energy is not enough to supply a sensor node on a permanent basis, the usual strategy is to accumulate the harvested energy, so that a transmission is enabled from time to time, powering the transmitter with the energy that has been harvested and stored, in the mean time.

In general, as documented in [40], one has power densities of about 300 and  $20 \,\mu\text{W/cm}^3$ , representing the limits for kinetic and thermal devices, respectively, while the user is running. The values of 30 and  $10 \,\mu\text{W/cm}^3$  are the power density limits if the user is walking. The present challenge, which is still under active research, is the means to obtain the correct adaptability for the harvester, in order to match the electric and the thermal impedances, if the body of the user is undergoing a running or a walking regime.

Some specific applications have also been documented, like in [42], where an electromagnetic generator is used both as a harvester and as a sensor, in a situation where the respiratory effort mechanical motion is the energy source. The harvested energy has been shown to be enough to continuously power a low-power micro-controller working with a low data rate wireless link, while monitoring the respiratory rate, and depth, of the user, with good accuracy.

A heel impact absorber harvester has also been developed, to store energy by using human locomotion [17], but in [38], a different approach is taken. Instead of heel impact, the human horizontal foot motion is used. This system uses this energy to charge a rechargeable battery. An interesting feature about this application is the introduction of a MPPT perturb and observe algorithm (which will be addressed in Sect. 4.5.3), optimized for low-frequency human horizontal foot motion, in order to extract as much power as possible. The information provided by the MPPT controller is delivered to a PI controller, in order to establish the optimal switching rate of both a boost and a buck converter. The power density that can be achieved with this application is 8.5 mW/cm<sup>3</sup>.

Another way of harvesting energy from human motion has been used in the Sustainable Dance Club [43], where the energy released by dancing people is used to power the light effects in the dance floor zone. The harvesting is performed by using dance floor modules, in the form of tiles. A dancing person can, in average, generate a power of about 2–8 W. In order not to be intrusive to the dancer and to his/her dancing experience, the floor tile is only allowed to displace vertically by a few millimeters, thanks to using a high-stiffness spring. Because of the nature of the involved movement, the working frequency is in the range of 1–2.5 Hz. To match the harvester as best as possible with the load, it is considered that the combination of a single user plus platform weights about 70–100 kg. An additional advantage in this system is the fact that the energy is being locally generated, avoiding the losses

occurred when energy is being transported over the power grid. The measured efficiency for this system was 48 %, including the losses due to the diode rectifier.

The concern about obtaining the intended energy without interfering with the user, so that the harvesting process can be as seamless and unconscious as possible, is also present in [44], where a framework to harvest vibration energy from the human gait is presented. This framework is for calculating the optimal power output for both piezoelectric and electromagnetic vibration harvesters, covering energy harvesting for both walking and running gait of a wide variety of healthy subjects ranging from recreational to elite athletes. The generator is mounted on the lower leg because this is a zone that, because of the foot strike, shows a great acceleration and, simultaneously, allows for conveniently wearing the harvester.

On the other hand, instead of using the sensor in the lower leg, in [45], a miniaturized electromechanical generator, integrated into a human knee prosthesis, is used to power a sensor system inside the prosthesis, enabling it to transmit information about the load on the surfaces of the articulation.

The development of new piezoelectric materials is an active research field. In [46], the fabrication of piezoelectric rubber films and their applications in heartbeat sensing and human energy harvesting is shown. It was demonstrated that the use of the piezoelectric rubber films can function as both sensing and powering elements and potentially realize the integration of human physiological monitoring and energy harvesting.

The human body can even be used to harvest energy from electromagnetic radiations. According to a study performed in [47], it has been shown that the properties of the human tissues, which have a high dielectric constant, especially at low frequencies, are much suitable to receive the electromagnetic radiations of low frequency, emitted by the power lines in an indoor environment. Moreover, using an antenna would be very difficult to capture the same radiation because of the low frequency band and the narrow bandwidth. The harvested energy can be delivered to an application by simply making contact with the human body.

In [47], measurements were made in order to determine the effective length of the human body. The effective lengths had maximum values (about 5 cm) at about 40 MHz, which is large, considering the poor conductivity of body tissues. With higher and lower frequencies, the length decreases. In addition, measurements also included the estimated voltages received by the human body, which varies from place to place, according to the frequency predominance in the environment.

Another work that also studies the theme of electromagnetic energy harvesting using the human body can be found in [48].

#### 2.1.5 Microbial Fuel Cells

The microbial fuel cell (MFC) principle is based on the electrochemical reactions that bacteria produce when in activity. The energy generated by these reactions can be harvested, similarly as with the other sources already addressed.

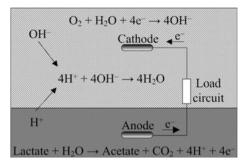

#### 2.1 Available Energy Sources

Fig. 2.9 MFC structure and electrochemical reactions

At environments where it is very difficult to reach, in electronic applications that have been deployed, like in underwater monitoring systems, there have been successfully tried several ways to power such applications by using the bacteria that live in the water. In [49], the MFC consists of two electrodes (one anode and one cathode), in which the anode is buried in the seafloor and the cathode is left suspended in the water. On the anode side, there is a type of bacteria, the *Shewanella oneidensis*, which breaks down the lactate in the water and makes it to release electrons and react with water. The basic structure of the setup and the chemical reactions that occur are schematically shown in Fig. 2.9, and the reaction just mentioned appears at the bottom of it.

The electrons produced in the seafloor  $(4e^-)$  travel to the anode and then to the cathode, through the load of the MFC. On the other hand, the protons produced by this reaction  $(4H^+)$  travel to the cathode side, through the water.

On the cathode side, the electrons from the anode react with water and with the oxygen in the water, to produce  $4OH^-$ , as shown by the chemical equation at the top of Fig. 2.9. Ultimately, the reaction of  $OH^-$  produced at the cathode, with  $H^+$ , coming from the anode, ends up forming water ( $4H_2O$ ). Neither of the electrodes gets corroded, because the chemical reactions just described do not include any other material than those that were mentioned. Moreover, the net product of the chemical reaction is not some polluting compound. One topic that must be carefully addressed is the surface area of the electrodes, because this factor has a key role in the power density that can be achieved.

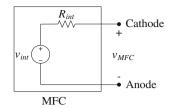

Generally, the voltage and the current that can be generated are weak, requiring an adequate power management system to interface the MFC with the load and having to encompass a storage device. Thus, the load can only work intermittently, in order to correctly meet the demand of power and for short periods of time. However, an application like the one described is self-contained, renewable, maintenance-free, and operational (on an intermittent basis), in a water environment.

Another environment, where there is an abundant quantity of bacteria, is in wastewater. This environment is very hostile to humans, so the use of a WSN that requires no human interventions after deployment is unarguably preferable. Another place, with similar problems, is the water tanks of nuclear plants. As such, under the subject of monitoring and control of wastewater treatment plants

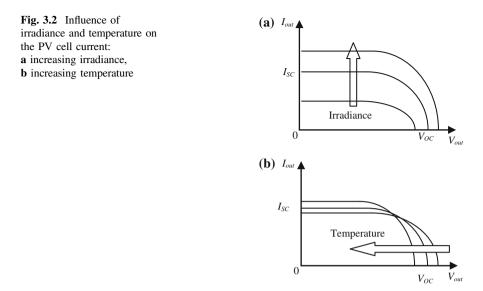

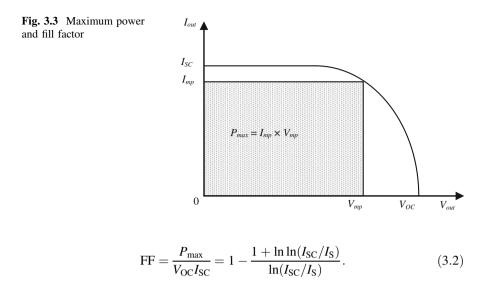

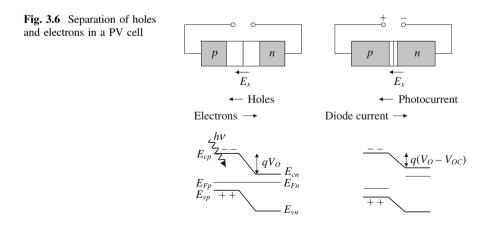

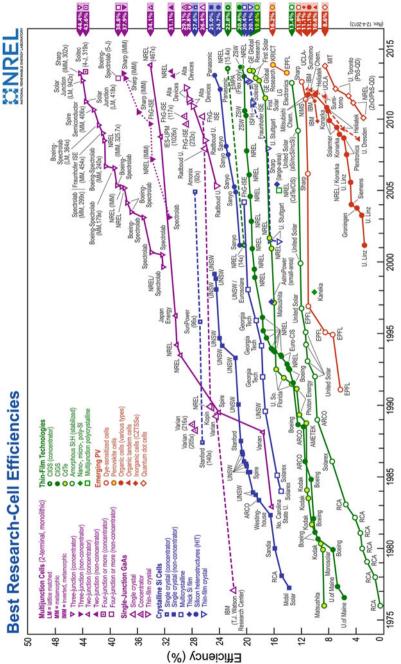

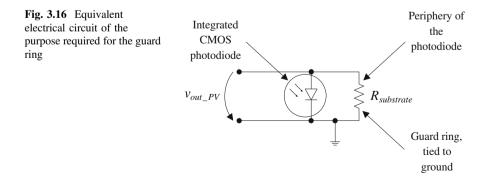

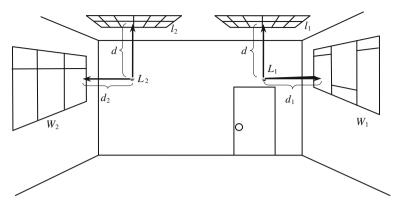

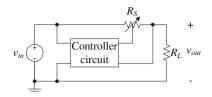

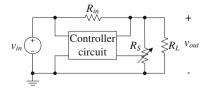

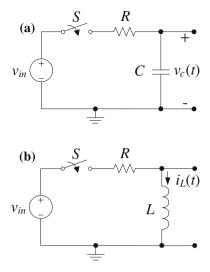

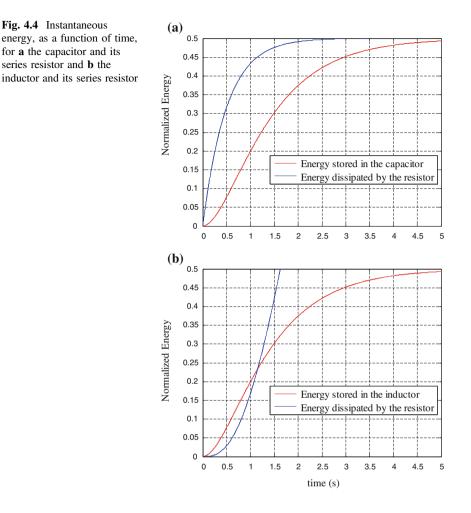

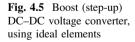

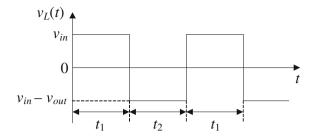

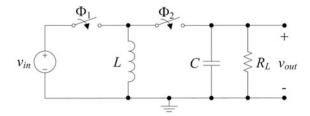

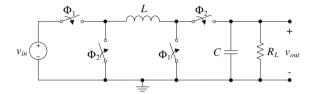

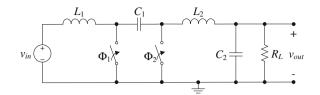

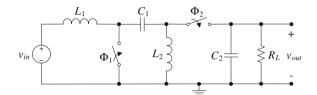

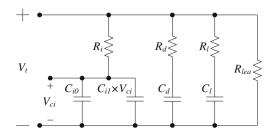

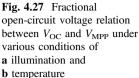

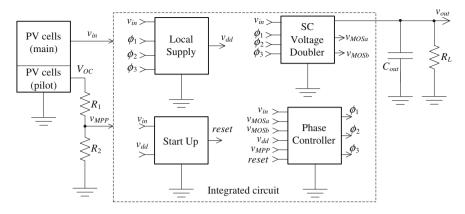

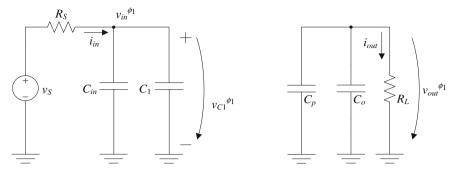

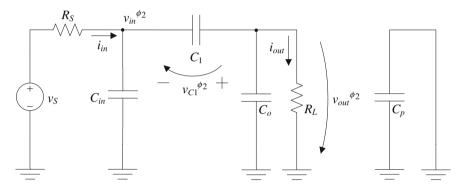

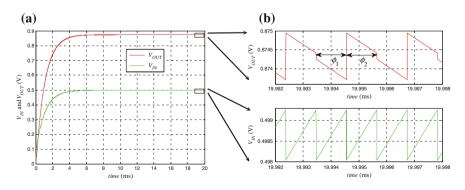

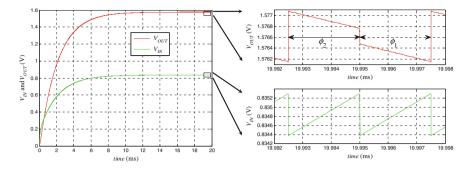

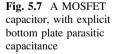

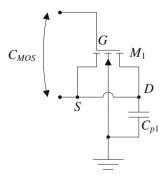

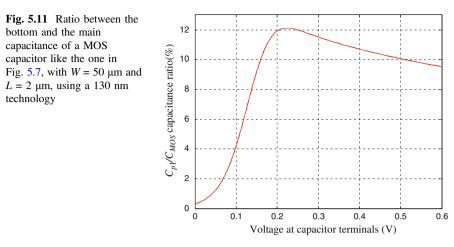

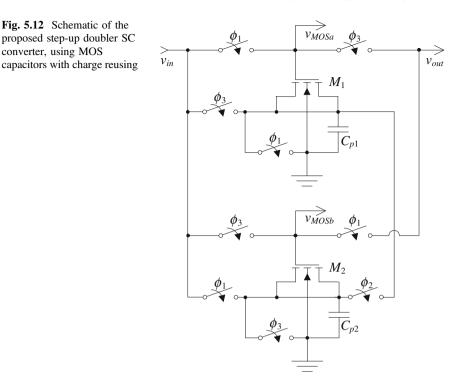

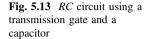

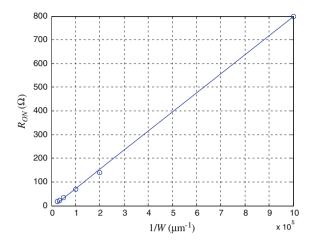

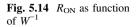

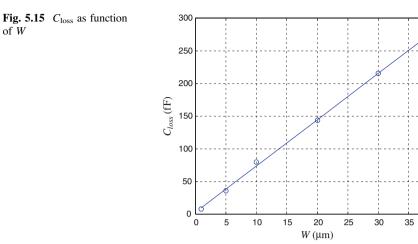

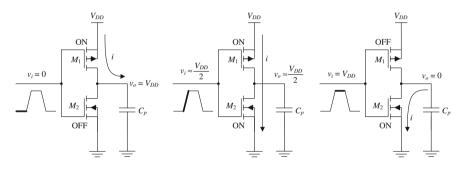

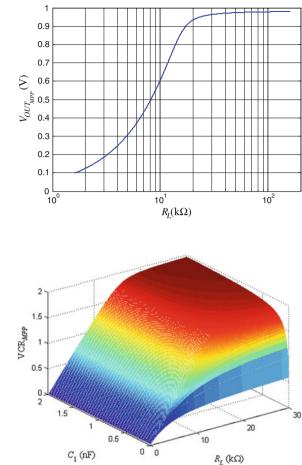

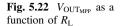

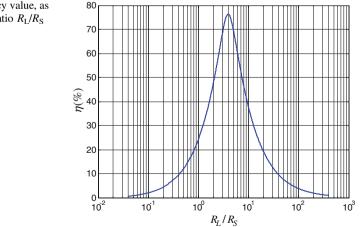

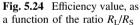

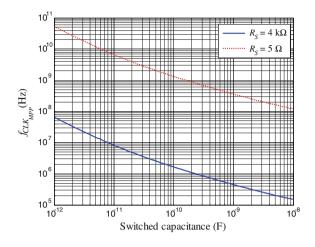

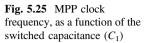

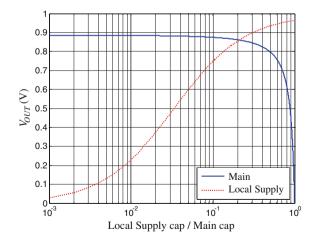

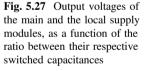

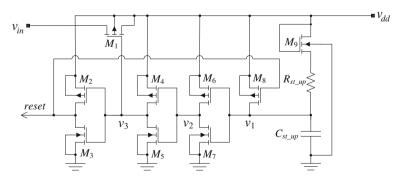

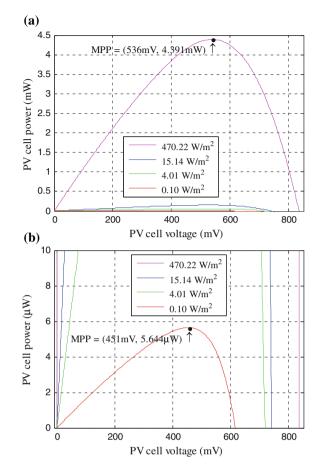

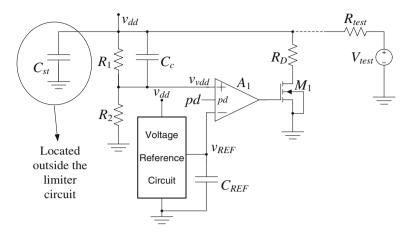

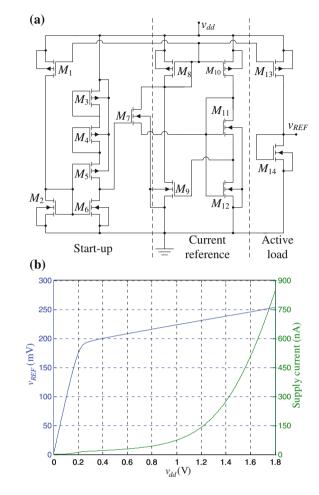

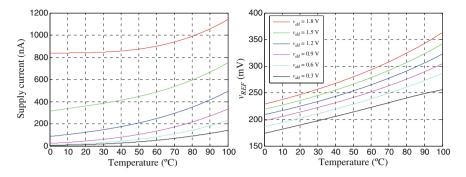

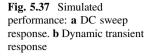

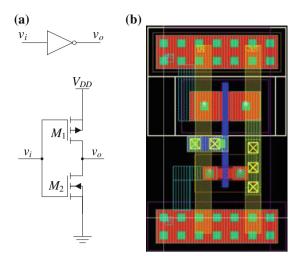

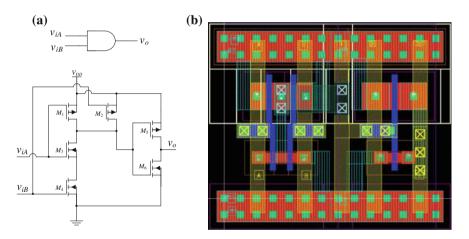

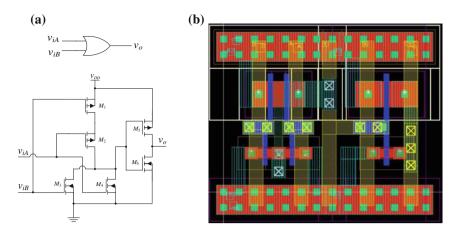

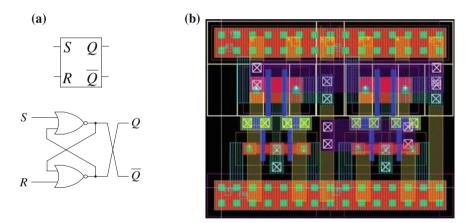

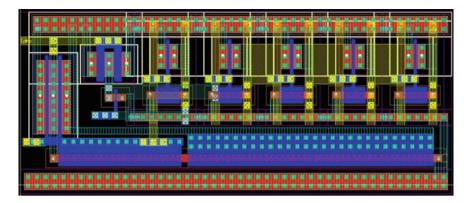

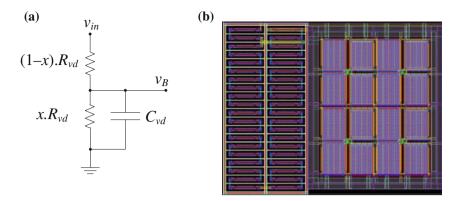

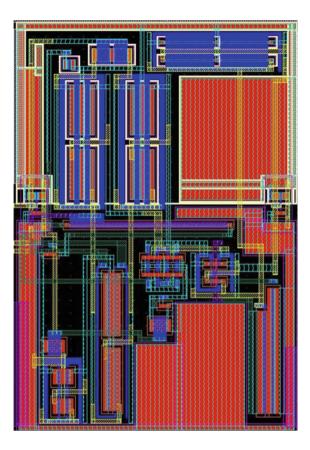

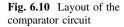

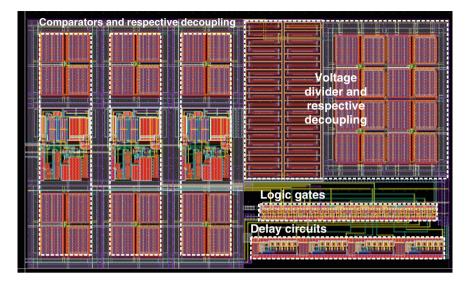

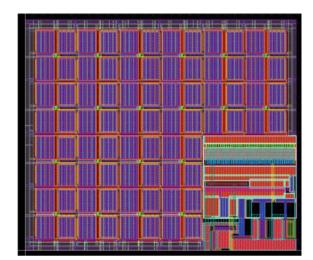

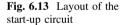

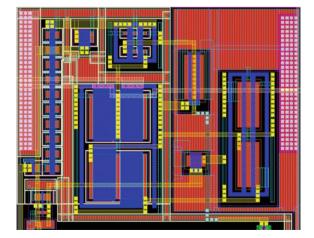

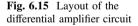

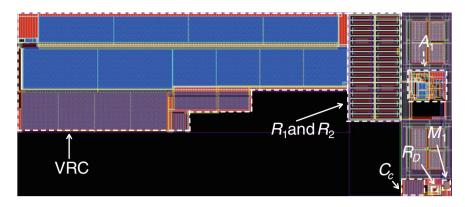

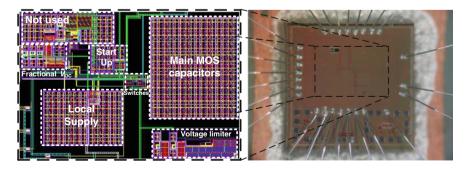

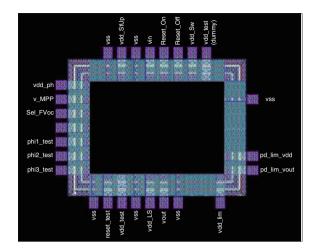

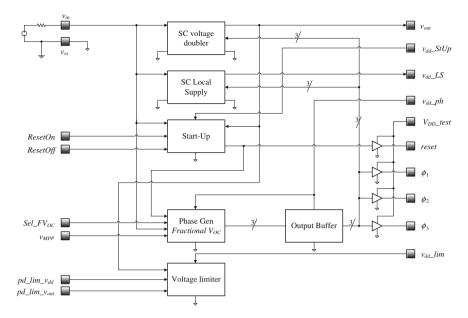

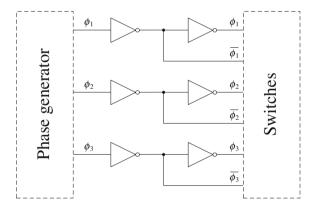

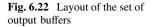

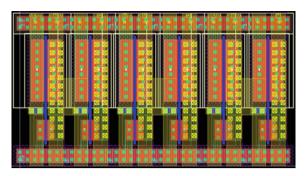

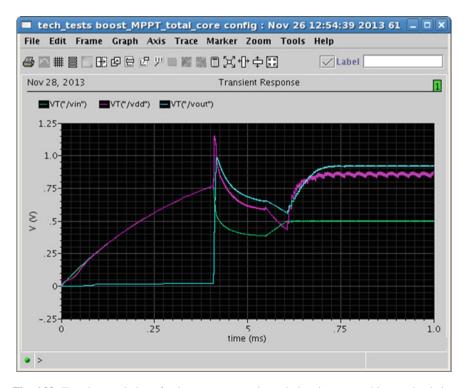

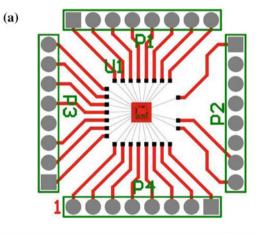

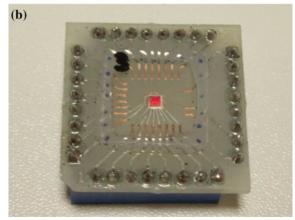

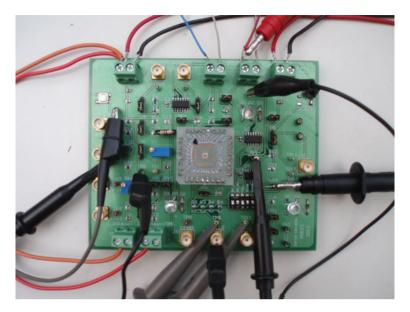

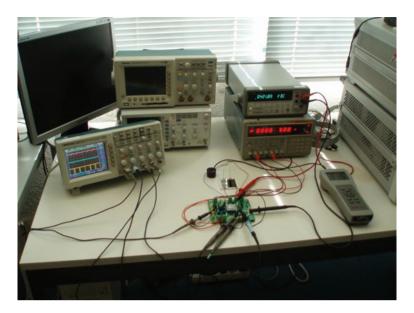

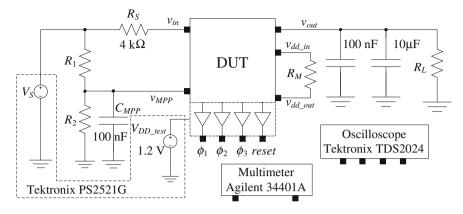

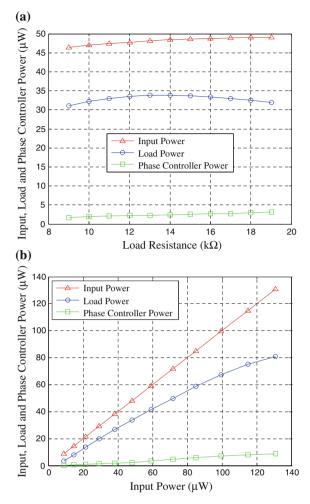

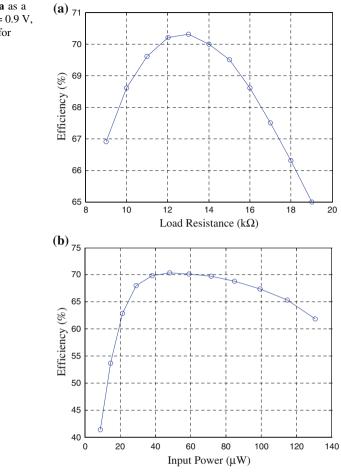

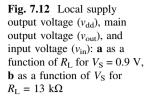

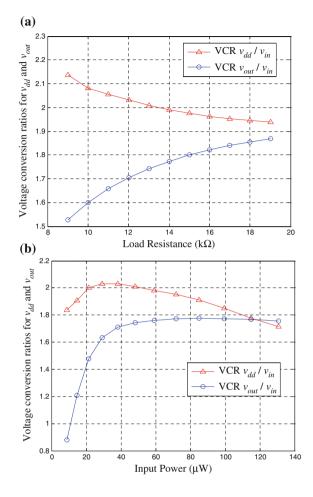

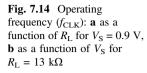

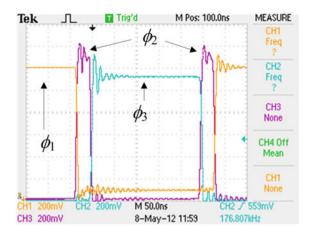

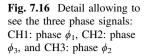

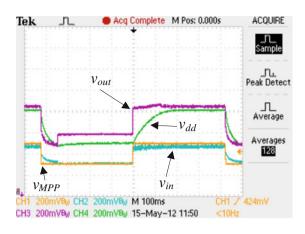

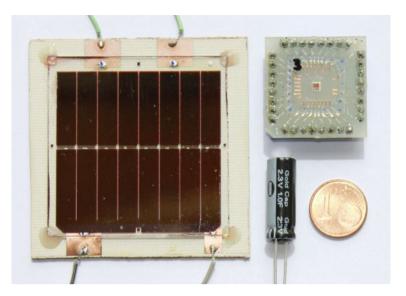

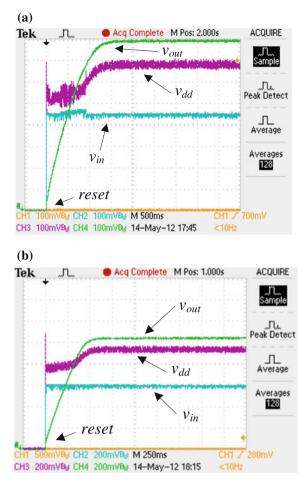

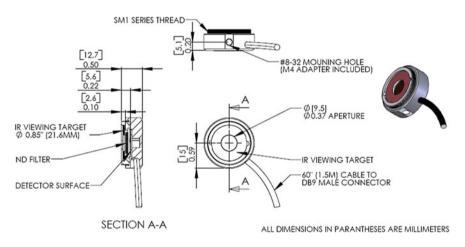

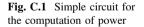

Fig. 2.10 Electrical model for a MFC