Marko Bertogna · Luís Miguel Pinho Eduardo Quiñones (Eds.)

# Reliable Software Technologies – Ada-Europe 2016

21st Ada-Europe International Conference on Reliable Software Technologies Pisa, Italy, June 13–17, 2016, Proceedings

#### Lecture Notes in Computer Science

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### Editorial Board

David Hutchison Lancaster University, Lancaster, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Friedemann Mattern ETH Zurich, Zürich, Switzerland John C. Mitchell Stanford University, Stanford, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen TU Dortmund University, Dortmund, Germany Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Gerhard Weikum Max Planck Institute for Informatics, Saarbrücken, Germany More information about this series at http://www.springer.com/series/7408

Marko Bertogna · Luís Miguel Pinho Eduardo Quiñones (Eds.)

# Reliable Software Technologies – Ada-Europe 2016

21st Ada-Europe International Conference on Reliable Software Technologies Pisa, Italy, June 13–17, 2016 Proceedings

*Editors* Marko Bertogna Università di Modena e Reggio Emilia Modena Italy

Luís Miguel Pinho CISTER/INESC-TEC, ISEP Porto Portugal Eduardo Quiñones Barcelona Supercomputing Center Barcelona Spain

ISSN 0302-9743 ISSN 1611-3349 (electronic) Lecture Notes in Computer Science ISBN 978-3-319-39082-6 ISBN 978-3-319-39083-3 (eBook) DOI 10.1007/978-3-319-39083-3

Library of Congress Control Number: 2016939061

LNCS Sublibrary: SL2 - Programming and Software Engineering

#### © Springer International Publishing Switzerland 2016

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

This Springer imprint is published by Springer Nature The registered company is Springer International Publishing AG Switzerland

#### Preface

The 21<sup>st</sup> edition of the International Conference on Reliable Software Technologies (Ada-Europe 2016) took place in the city of Pisa, hosted by Scuola Superiore Sant'Anna, an internationally renowned university school. This was the return of the conference to Italy, after Venice in 2008. Previous editions of the conference were held in Spain (Santander, 1999, Palma de Mallorca, 2004, Valencia, 2010, and Madrid, 2015), France (Toulouse, 2003, Brest, 2009, and Paris, 2014), the UK (London, 1997, York, 2005, and Edinburgh, 2011), Switzerland (Montreux, 1996, and Geneva, 2007), Sweden (Uppsala, 1998, and Stockholm 2012), Germany (Potsdam, 2000, and Berlin, 2013), Belgium (Leuven, 2001), Austria (Vienna, 2002), and Portugal (Porto, 2006). The conference series is run and sponsored by Ada-Europe, in collaboration with local organizations. This year Scuola Superiore Sant'Anna led the organization, with the support of a truly international team.

The conference took place during June 13–17, 2016, with a rich program on both the technical and social sides. The scientific part of the conference program featured 12 presentations selected among 28 peer-reviewed papers, which were grouped into four regular sessions spread out on the central days of the conference, on topics ranging from concurrency and parallelism to real-time systems via testing and verification and program correctness and robustness. The program also included eight industrial presentations, split across two industrial sessions. A session featuring presentations from students of the ITS EASY post-graduate school, which co-located its meeting with the conference, a poster session, and one vendor session with an accompanying vendor exhibition completed the core program. In addition to this rich set of contents, eight tutorials for the equivalent of 10 half-day sessions were scheduled on Monday and Friday. Also on Friday, the week featured the third edition of the Challenges and New Approaches for Dependable and Cyber-Physical Systems Engineering Workshop.

The submissions to scientific and industrial tracks of the conference program came from 25 countries and 96 distinct authors, from Europe, Asia, North and South America, and Africa. The final result was a truly international program with contributions from Australia, Austria, Canada, France, Germany, Italy, Portugal, Spain, Sweden, Tunisia, UK, and USA.

Each day of the core conference program opened with a keynote talk centered on topics of high interest within conference focus:

- "Why the Expressive Power of Languages Such as Ada Is Needed for Future Cyber Physical Systems." Alan Burns, from the University of York, UK, presented the challenges put forward to the developer of cyber physical systems to fully exploit the wealth of real-time systems theory, and how these are addressed with the highlevel programming abstractions of Ada.

- "Challenges for the Automotive Platform of the Future." Valerio Giorgetta, from Magneti Marelli, Italy, presented how the concept of a car will be impacted by the

challenges put forward such as autonomous vehicles and functional safety and reliability.

"The HiPEAC Vision." Marc Duranton, from CEA, France, presented an overview of the HiPEAC vision, a bi-annual document produced by the HiPEAC network of excellence, with the upcoming challenges in computing systems.

The proceedings contained in this volume cover the opening keynote talk and the full set of peer-reviewed papers. The remainder of the conference contributions are published, in successive instalments, in the *Ada User Journal*, the quarterly magazine of Ada-Europe.

The tutorial program covered a wide range of topics in the scope of the central themes of the conference, as follows:

- "A Semi-formal Approach to Software Development," William Bail, The MITRE Corporation, USA

- "Software Test and Verification Techniques for Dependable Systems," William Bail, The MITRE Corporation, USA

- "Embedded ARM Programming with Ada 2012," Patrick Rogers, AdaCore, USA

- "Ada 2012 (Sub)types and Subprogram Contracts in Practice," Jacob Sparre Andersen, JSA Research & Innovation, Denmark

- "Towards Energy Awareness and Predictability in the Linux Kernel," J. Lelli, ARM Ltd., Italy

- "Access Types and Memory Management in Ada 2012," J.P. Rosen, Adalog, France

- "Using Gnoga for Desktop/Mobile GUI and Web Development in Ada," J.P. Rosen, Adalog, France

- "Parallelism in Ada, C, Java and C#, Today and Tomorrow," Brad Moore, General Dynamics Canada, and Stephen Michell, Maurya Software, Canada

The industrial sessions featured eight presentations centered on various aspects of reliable software development:

- "What Has the ARG Been up to? Recent and Future Changes to Ada 2012," Jeff Cousins, ARG Rapporteur, UK

- "Using Ada's Visibility Rules and Static Analysis to Enforce Segregation of Safety Critical Components," Jean-Pierre Rosen and Jean-Christophe Van-Den-Hende, Adalog and Alstom-Transport, France

- "Automated Testing of SPARK Ada Contracts (AUTOSAC)," Christopher Bryan, Rapita Systems, UK

- "Ada Usage in HMI for Onboard Safety Critical Applications," Clara Maria Arcones-Gabriel, Enrique Chicharro-Lopez and Ismael Lafoz-Pastor, Airbus Defence and Space, Spain

- "An Update on Programming Language Vulnerabilities," Stephen Michell, WG23 Convenor, Canada

- "Middleware for Distributed and Redundant Software," Vincent Monfort, Systerel, France

- "Model-Based Design and Schedulability Analysis for Avionic Applications on Multicore Platforms," Wenceslas Godard and Geoffrey Nelissen, Airbus Group SAS, France and CISTER/ISEP, Portugal

- "Fitting the CONCERTO Component Model Approach to AUTOSAR Development Flow," Andrea Russino, Stefano Puri and Alessandro Zovi, Intecs and Università di Padova, Italy

This edition of the conference featured a focused topic on "Safe and Predictable Parallel Software Technologies." Ada has been a language that has always excelled with its advanced high-level concurrency support. In the last 20 years, Ada has steadily extended its wealth of concurrency features and capabilities to a considerable extent, yet within the bounds of a sequential task reasoning. With the advances in processor architectures, and in particular the move into a parallel world, it is time to discuss how Ada should be evolved into supporting in the language the notion of fine-grained parallelism. The program included a special session on "Ada and Parallelism," which discussed the design choices and evolutions of the language to support fine-grained parallel programs. The session included both presentations from experts in the following topics as well as an open discussion to the floor:

- "Paraffin: A Parallelism Library for Ada," Brad Moore, Gran Dynamics, Canada

- "Ada Container Iterators for Parallelism and Map/Reduce," S. Tucker Taft, Ada-Core, USA

We would like to acknowledge the work of all the people who contributed, with various responsibilities and official functions, to the making of the conference program. First of all, the authors of the contributions, who were largely responsible for the success of the conference. Then the members of the Program and Industrial Committees, who worked hard to review and select a high-quality set of papers, both for the Springer LNCS volume in the case of peer-reviewed papers and the *Ada User Journal* in the case of the industrial presentations, the special session papers, and the workshop.

Finally, the group of organizers who made the conference program a reality: Giorgio Buttazzo (Conference Chair); Ettore Ricciardi (Local Chair); Marco Di Natale and Tullio Vardanega (Industrial Co-chairs); Jorge Real (Tutorial and Workshop Chair); Geoffrey Nelissen (Publication Chair); Mauro Marinoni and Dirk Craeynest (Publicity Co-chairs); Paolo Gai and Ahlan Marriott (Exhibition Chair). They all deserve our gratitude for their effort.

We hope that the attendees enjoyed the conference, both its technical and social program, as much as we did in organizing it.

June 2016

Marko Bertogna Luís Miguel Pinho Eduardo Quiñones

#### Organization

The 21st International Conference on Reliable Software Technologies, Ada-Europe 2016, was organized by Ada-Europe, in cooperation with ACM SIGAda, ACM SIGBED, ACM SIGPLAN, and Ada Resource Association.

#### **Conference Chair**

| Giorgio Buttazzo                    | Scuola Superiore Sant'Anna, Italy                                              |  |

|-------------------------------------|--------------------------------------------------------------------------------|--|

| Program Co-chairs                   |                                                                                |  |

| Marko Bertogna<br>Luís Miguel Pinho | University of Modena and Reggio Emilia, Italy CISTER/INESC-TEC, ISEP, Portugal |  |

| Special Session Chair               |                                                                                |  |

| Eduardo Quiñones                    | Barcelona Supercomputing Center, Spain                                         |  |

| Tutorial and Workshop               | Chair                                                                          |  |

| Jorge Real                          | Universitat Politecnica de Valencia, Spain                                     |  |

| Industrial Co-chairs                |                                                                                |  |

| Marco Di Natale<br>Tullio Vardanega | Scuola Superiore Sant'Anna, Italy<br>Università di Padova, Italy               |  |

| Publication Chair                   |                                                                                |  |

| Geoffrey Nelissen                   | CISTER/INESC-TEC, ISEP, Portugal                                               |  |

| Exhibition Co-chairs                |                                                                                |  |

| Paolo Gai<br>Ahlan Marriott         | Evidence Srl, Italy<br>White Elephant GmbH, Switzerland                        |  |

| Publicity Co-chairs                 |                                                                                |  |

| Mauro Marinoni<br>Dirk Craeynest    | Scuola Superiore Sant'Anna, Italy<br>Ada-Belgium and KU Leuven, Belgium        |  |

#### Local Chair

Ettore Ricciardi

ISTI-CNR, Pisa, Italy

#### **Sponsoring Institutions**

AdaCore Esterel Technologies Ellidiss Software, TNI Europe Ltd. Vector Software Rapita Systems Ltd. PTC

#### **Program Committee**

Mario Aldea University of Cantabria, Spain Ted Baker National Science Foundation, USA Marko Bertogna Università di Modena e Reggio Emilia, Italy Johann Blieberger TU Wien, Austria Bernd Burgstaller Yonsei University, Korea Albert Cohen Inria. France Juan A. de La Puente Universidad Politécnica de Madrid, Spain Michael Gonzalez Harbour Universidad de Cantabria, Spain J. Javier Gutierrez Universidad de Cantabria, Spain ISAE, France Jerome Hugues University of Hertfordshire, UK Raimund Kirner Albert Llemosi Universitat de les Illes Balears, Spain Franco Mazzanti **ISTI-CNR**, Italy Maurya Software Inc., Canada Stephen Michell Jurgen Mottok Regensburg University of Applied Sciences, Germany Telecom ParisTech, France Laurent Pautet Luís Miguel Pinho CISTER/INESC-TEC, ISEP, Portugal Erhard Plodereder University of Stuttgart, Germany Eduardo Quinones Barcelona Supercomputing Center, Spain Universitat Politècnica de València, Spain Jorge Real Christine Rochange IRIT - Université de Toulouse, France Jose Ruiz AdaCore, France Sergio Saez Universidad Politècnica de València, Spain Martin Schoeberl Technical University of Denmark, Denmark Tucker Taft AdaCore, USA Theodor Tempelmeier University of Applied Sciences Rosenheim, Germany Elena Troubitsyna Aabo Akademi University, Finland Santiago Uruena GMV, Spain Tullio Vardanega Università di Padua, Italy

#### **Industrial Committee**

| Ian Broster           | Rapita Systems, UK                     |

|-----------------------|----------------------------------------|

| Jorgen Bundgaard      | Ramboll, Denmark                       |

| Dirk Craeynest        | Ada-Belgium and KU Leuven, Belgium     |

| Arne Hamann           | Bosch, Germany                         |

| Ismael Lafoz          | Airbus Defence & Space, Spain          |

| Ahlan Marriott        | White Elephant, Switzerland            |

| Paolo Panaroni        | Intecs, Italy                          |

| Paul Parkinson        | Wind River, UK                         |

| Eric Perlade          | AdaCore, France                        |

| Jean-Pierre Rosen     | Adalog, France                         |

| Jacob Sparre Andersen | JSA Consulting, Denmark                |

| Claus Stellwag        | Elektrobit AG, Germany                 |

| Jean-Loup Terraillon  | European Space Agency, The Netherlands |

| Sergey Tverdyshev     | SysGO, Germany                         |

| Rod White             | MBDA, UK                               |

|                       |                                        |

#### **Additional Reviewers**

| Etienne Borde          | Erjola Lalo          | Erna Oklapi   |

|------------------------|----------------------|---------------|

| Hugues Cassé           | Tobias Langer        | Lukas Osinski |

| Jorge Garrido Balaguer | Simon Maurer         | Hector Perez  |

| Hamza Hamza            | Manel Medina         | Pascal Sotin  |

| Saverio Iacovelli      | Patrick Meumeu Yomsi |               |

|                        |                      |               |

#### Contents

#### **Invited Paper**

| Why the Expressive Power of Programming Languages Such as Ada Is<br>Needed for Future Cyber Physical Systems                                             | 3  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Concurrency and Parallelism                                                                                                                              |    |

| Modeling and Analysis of Data Flow Graphs Using the Digraph Real-Time<br>Task Model                                                                      | 15 |

| Morteza Mohaqeqi, Jakaria Abdullah, and Wang Yi                                                                                                          |    |

| Eliminating Data Race Warnings Using CSP                                                                                                                 | 30 |

| Real-Time Stream Processing in Java                                                                                                                      | 44 |

| Testing and Verification                                                                                                                                 |    |

| Addressing the Regression Test Problem with Change Impact Analysis         for Ada       Andrew V. Jones                                                 | 61 |

| Test Case Prioritization Using Online Fault Detection Information<br>Mohsen Laali, Huai Liu, Margaret Hamilton, Maria Spichkova,<br>and Heinz W. Schmidt | 78 |

| An Experience in Ada Multicore Programming: Parallelisation of a Model<br>Checking Engine                                                                | 94 |

#### **Program Correctness and Robustness**

| Lessons Learned in a Journey Toward Correct-by-Construction               |     |

|---------------------------------------------------------------------------|-----|

| Model-Based Development.                                                  | 113 |

| Laura Baracchi, Silvia Mazzini, Stefano Puri, and Tullio Vardanega        |     |

| Extension of the Ocarina Tool Suite to Support Reliable Replication-Based |     |

| Fault-Tolerance.                                                          | 129 |

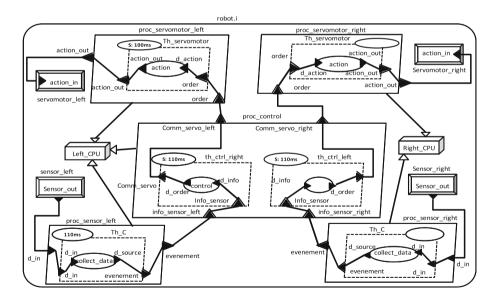

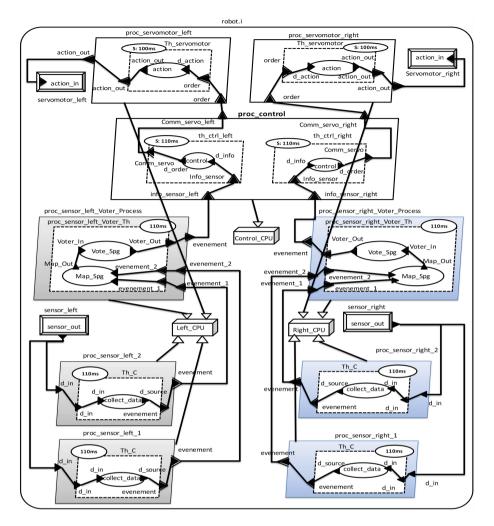

| Wafa Gabsi, Bechir Zalila, and Mohamed Jmaiel                             |     |

#### XIV Contents

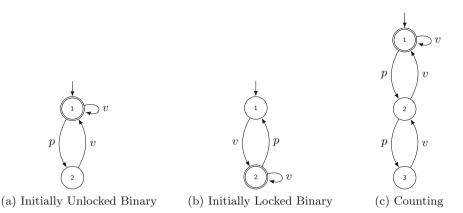

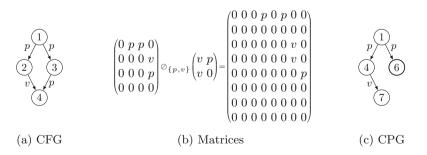

| Kronecker Algebra for Static Analysis of Barriers in Ada | 145 |

|----------------------------------------------------------|-----|

| Robert Mittermayr and Johann Blieberger                  |     |

#### **Real-Time Systems**

| An Empirical Investigation of Eager and Lazy Preemption Approaches                                                                                                  |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| in Global Limited Preemptive Scheduling.                                                                                                                            | 163 |

| Abhilash Thekkilakattil, Kaiqian Zhu, Yonggao Nie, Radu Dobrin,<br>and Sasikumar Punnekkat                                                                          |     |

| ana Sasikumar Punnekkai                                                                                                                                             |     |

| The Polling Effect on the Schedulability of Distributed Real-Time Systems<br>Héctor Pérez, J. Javier Gutiérrez, Michael González Harbour,<br>and J. Carlos Palencia | 179 |

| Combining Time-Triggered Plans with Priority Scheduled Task Sets Jorge Real, Sergio Sáez, and Alfons Crespo                                                         | 195 |

| Author Index                                                                                                                                                        | 213 |

### **Invited Paper**

#### Why the Expressive Power of Programming Languages Such as Ada Is Needed for Future Cyber Physical Systems

Alan Burns<sup>( $\boxtimes$ )</sup>

Department of Computer Science, University of York, York, UK alan.burns@york.ac.uk

**Abstract.** If Cyber Physical Systems (CPS) are to be built with efficient resource utilisation it is imperative that they exploit the wealth of scheduling theory available. Many forms of real-time scheduling, and its associated analysis, are applicable to CPS, but it is not clear how the system developer/programmer can gain access to this theory when real CPS are being constructed. This short paper gives the background to the associated presentation where the facilities available in the Ada programming language are highlighted and reviewed. The aim of the presentation is to show that Ada provides most of the programming abstractions needed to deliver future CPS.

#### 1 Introduction

The design and implementation of reliable and cost-effective Cyber-Physical Systems (CPS) incorporates many issues in both the hardware and software aspects of the system. For reliability (and for many CPS, safety), timing constraints such as deadlines must be satisfied, and in many applications evidence for such compliance must be provided (perhaps in a safety-case to be used during certification). For cost-effectiveness, resources must be used effectively and sparingly. Resources in this context being platform hardware and run-time energy consumption.

The branch of Computer Science that deals with resource usage in this context is real-time scheduling. Scheduling protocols promote efficient (and at times optimal) resource utilisation. And scheduling analysis provides the means of verifying that, even in the worst-case, deadlines will be met.

Over the last 50 years a considerable body of knowledge and volume of results in the field of real-time scheduling have been produced. These results can, potentially, have a significant impact on how further CPS are developed. But to realise this potential it must be possible for software developers to exploit this theory; they must be able to apply the scheduling protocols and to subject their software to the relevant forms of scheduling analysis.

The means of exploiting scheduling theory is via the programming languages (PLs) and operating systems (OSs) available to the developer. PLs provide abstractions, such as tasks with priorities and priority based processor scheduling, whilst OSs provide interfaces that can support, for example, threads, priorities and priority-based dispatching.

© Springer International Publishing Switzerland 2016 M. Bertogna et al. (Eds.): Ada-Europe 2016, LNCS 9695, pp. 3–11, 2016. DOI: 10.1007/978-3-319-39083-3\_1 In this paper and talk I want to give a somewhat high level, and necessarily brief, review of the many scheduling results that may be of utility to CPS development. I then want to see to what extent these results are available to developers via OSs and programming languages. I shall argue that for all but the most basic level of support, OSs (and certainly OS Standards) lack the expressive power required. However, programming language abstractions do exist that give access to many (but of course not all) forms of scheduling protocols and analysis. And the programming language that implements/supports most of these abstractions is Ada. Therefore the expressive power of the Ada programming language will form the main focus of this keynote.

#### 2 Scheduling Results

Here some of the major results from scheduling theory, which could be employed in CPS development are outlined. Requirements are linked to applicable scheduling protocols. Of course not all requirements are needed for all CPS, but each one has the potential to be useful. We looks at this work under four headings, uniprocessor systems, multiprocessor systems, mixed criticality systems and then a *catch all* section.

#### 2.1 Uniprocessor Theories

We start with some very basic requirements

- Interactions with the parallel world requires concurrency (tasks, threads, processes etc.).

- Safe Sharing between distinct software components synchronisation controls (semaphores, mutexes, monitors etc.).

- Synchronisation with external real-time clock abstractions and delay primitives.

- Synchronisation with external events interrupt handling.

Concurrency allows tasks to execute non-deterministically. Basic scheduling allows this freedom to be constrained so that the possibility of meeting timing requirements is optimised (and verified if the appropriate analysis is applied):

- Predicable task ordering (static) priority attributes for tasks, priority ceilings for monitors.

- *Deadline aware task execution* deadline attributes for tasks, protocols for effective sharing.

- *Deterministic execution order* Non-preemptive scheduling (with static priorities).

Building upon these basic schemes there are a wealth of protocols that aim to improve resource utilisation, for example:

- Deferred preemption [18].

- Dual priorities [13].

- Dynamic priorities (which can be used to program a wide variety of protocols).

or support more general computational models:

- Logical Execution Time (LET) [20,21,27].

- Anytime or imprecise algorithms (where following the production of an adequate result, further processing will improve the result up to the point when the result must be output).

- Dynamic periods and deadlines (elastic task model) [16].

- N in M constraints (only N out of every M jobs need meet their deadlines) [6].

- Multiframe Tasks (tasks execute through a series of frames with different resource requirements) [28].

- Generalised Task Model (where tasks are related by DAG models) [5].

- Open Systems with admission control (dynamic task creation) [12,24].

Many CPS have to demonstrate resilience as well as functional correctness; for this, fault tolerance behaviour needs to be supported. This takes the form of error recognition, firewall protection and various forms of adaptive resource management. For example,

- Deadline miss detection

- Budget monitoring

- Budget overrun detection

- Budget enforcement

- Watchdog timers

- Aborting rogue computation

- Budget management per task

- Budget management per group of tasks

- Early task termination identification

Aborting rogue computation is needed at the task/thread level and at the functional code level. It must be possible to undertake this abandonment without leaving shared data in an undefined state.

#### 2.2 Multiprocessor Theories

Once the execution platform changes from uniprocessor to one with multiple processors (or cores) then other requirements have to be addressed by the scheduling theory. The basic features that must be supported are:

- Partitioned scheduling managing the static assignment of tasks/threads to processors/cores.

- Global scheduling managing the run-time migration of tasks/threads to follow the rules of the scheduling protocol.

- Semi-partitioned scheduling managing the controlled migration of individual tasks/threads at run-time [9,10,22].

#### 6 A. Burns

- Sharing - controlling the sharing of resources between potentially parallel executing tasks/threads (this is a major open problem, in that effective general purpose protocols are not yet available).

On top of these basic protocols there are more advanced schemes that again deliver more efficient execution or support more general models of computation:

- TkC, and DkC (global schemes with priority-based scheduling then non-preemptive) [2,19].

- tasklets to model parallelism within a task/thread [25].

- barriers to efficiently synchronise tasks/threads on multiprocessor platforms.

Finally there is the need to support heterogeneous as well as homogeneous hardware platforms.

#### 2.3 Mixed Criticality Theories

Mixed criticality system introduce new scheduling protocols that aim to increase the resilience of such systems but keep their resource usage as low as possible. Most of the proposed protocols involve forms of change management. For example:

- task/thread parameter modification (extend period and deadlines),

- suspending tasks/threads,

- modifying scheduling attributes: priorities and deadlines,

- resume tasks/threads.

Also important is the means of supporting partitioning; in particular the allocation of processor time – the overrun of one subsystem must not impact on the resources available to another subsystem. This is especially true if the subsystems are of different levels of criticality. However, the complete separation of subsystems can lead to the over provisioning of resources as the certification of safety-critical software requires very conservative resource-usage estimates. Mixed criticality research has focused on scheduling protocols that provide managed sharing as well as adequate separation [8].

#### 2.4 Others Requirements and Scheduling Features

Here we note some other issues:

- Control of when tasks/threads that preform I/O execute (e.g. minimising input and output jitter).

- Control of memory used by tasks/threads.

- Control of power used by tasks/threads.

- Control over the speed of variable rate processors.

- Control over placement on FPGA type hardware

#### **3** Required Abstractions and/or Interfaces

To satisfy the above extensive list of requirements and protocols, one can either provide a (large) set of high-level abstractions/models, or aim to support primitives from which these abstractions can be programmed. For example, the notion of a periodic task could be provided in a model-based development scheme. Such a concept would have a defined period and deadline; but to give an elastic task it will be necessary to allow period and deadline to change – will the abstraction allow this? Also when executed by a priority based dispatcher how are the priority changes managed? Alternatively, the more general notion of a task or event handler, supported by clocks, a delay statement and a dynamic priority routine will allow any form of time-triggered computation to be programmed. In general a high-level abstraction is easier to use if it is exactly what is required; but lacks the expressive power to allow variants to be derived. Lower-level abstractions, however, present the programmer with more challenges.

Another problem with high level abstractions come from composition. (e.g. how to obtain a periodic tasks with deadline overrun protection, budget enforcement and an N in M execution requirement). Will the three or four high level models work together? Yes programming the required behaviour from lower level abstractions is more effort (and hence is potentially more error prone). But it does allow the actual necessary semantics to be delivered as long as the low-level abstractions are adequate and themselves provide the necessary expressive power.

The interfaces provided by a modern Real-Time operating system, such as one based on POSIX or Linux, give a good level of support for the protocols defined above. Threads have priorities, there are mutexes and priority ceiling protocols, priorities can by modified, budgets can be monitored, signals sent from one thread to another, and mappings to processors can be managed at run-time via affinities. But not all the requirements can be satisfied by OS standards. And composition via library APIs is error-prone and lacks the usability one would hope to have in a programming environment. Programming languages can however embed the protocols within the syntax as well as provide standard library routines, and this allows programmers to directly address the needs of CPS. But of course the programming language must be up to this challenge. In the following section I will look at what Ada provides and argue that it does indeed have (mostly) the required expressive power. Ada is chosen as it provides more low-level abstractions than any other programming language.

#### 4 Ada's Provisions

For those very familiar with Ada they will find nothing new in this brief overview, but for others I hope to at least remind you of what is now supported in the full Ada language. The Ravenscar profile is an important technology for simple real-time scheduling. But for the schemes likely to be needed in future CPS the expressive power of the full language is required. Again I will do this in the form of lists. So first basic concurrency, Ada supports

#### 8 A. Burns

- Calendar and real-time clocks.

- Static and dynamic creation of tasks.

- Delay mechanisms.

- Priority assignment.

- Protected objects with requeue to give controlled sharing.

- Dynamic task priorities and dynamic priority ceilings.

The requeue facility allows the full expressive power of a monitor to be provided without the need for very low level condition variables.

By supporting dynamic priorities and flexible delay mechanisms many different forms of behaviour can be programmed (such as an elastic task that changes its period).

To support scheduling protocols directly Ada supports:

- Priority based dispatching with priority ceiling protocol.

- EDF scheduling with the Stack Resource Protool (SRP) [3,4] (and possibly in the future the Deadline Floor Protocol, DFP [1,11]).

- Round Robin and non-preemptive dispatching.

- Hierarchical scheduling (for example, combined priority-based and EDF).

- Primitives to allow tasks to suspend themselves and other tasks.

- Timing events code that executes at a specified time (can be used to control input and output jitter).

- Group budget monitoring and control that allows standard execution time servers such as the Periodic Server, Sporadic Server and Deferrable Server to be constructed [7,14,15,17,26].

To support more resilient software Ada supports:

- Budget clocks that monitor task execution time, and can signal when specified levels of usage have been reached.

- Task aborting, and the ability to abandon computation at the sub-task level (ATC – select then abort))

- Timing events that are only execute in error conditions, i.e. programmed watchdog timers.

- Signaling when a task terminates (useful when the task should not!).

The ATC (Asynchronous Task Control) facility is not only of use in error handling for it also allows anytime algorithms to be easily programmed – set the ATC at a deadline, loop through some code to improve quality of computation, storing result in a protected object, abandon when deadline is reacted.

Timing events are another language feature with multiple usages. They can be used positively to control when I/O operations occur, but they can be 'not used' for watchdog timers. Here the 'alarm' is programmed to occur at some future event. The 'I'm alive' signal simple pushes the alarm time further into the future.

To support multiprocessor execution, Ada provides:

- Affinities that can control where a task executes; a task can be restricted to just one CPU, a groups of CPUs or be allowed to execute on any CPU.

- Dynamic affinities to allow semi-partitioned schemes to be programmed.

Other features that are potential important in CPS:

- Use of memory pools to control this important resource.

Having introduced a wide range of important features currently supported by Ada it is only fair to consider some that are missing:

- Support for parallel execution within a task a plan for including the notion of tasklet into the language is currently under consideration [23].

- Support for energy aware programming API to whatever is supported by the underlying hardware/run-time is the only current approach available – I would like to execute a loop within a bound determined by energy available.

- Support for an effective synchronisation scheme for multiprocessor execution many schemes have been proposed in the literature but there is not yet consensus on which Ada can build.

To illustrate the expressive power of Ada a couple of illustrative examples will be included in the presentation.

#### 5 Conclusions

A brief introduction to the scheduling requirements for future Cyber Physical Systems has been given. The list of requirements has been mapped against the provisions of the Ada programming language. In general, Ada provides a rich set of facilities from which higher level abstractions can be built.

The alternative to the use of a facilitating programming language is to rely upon the provisions of the operating systems upon which the software executes. Unfortunately the APIs provided by real-time operating systems (RTOSs) are not flexible enough to deal with the emerging approaches to scheduling resources that are being considered for cost-effective future systems.

Clearly Ada is not a static finished language, it has proved itself to be adaptable and to be able to embrace new ideas and programming styles. New challenges will continue to emerge, such as support for fine grain parallelism, and Ada must be as adaptable going forward as it has been in the past.

#### References

- Aldea, M., Burns, A., Gutirrez, M., Harbour, M.G.: Incorporating the deadline floor protocol in Ada. ACM SIGAda Ada Lett. Proc. IRTAW 16 XXXIII(2), 49–58 (2013)

- 2. Andersson, B., Jonsson, J.: Fixed-priority preemptive multiprocessor scheduling: to partition or not to partition. In: Proceedings of the International Conference on Real-Time Computing Systems and Applications (2000)

- Baker, T.P.: A stack-based resource allocation policy for realtime processes. In: Proceedings of IEEE Real-Time Systems Symposium (RTSS), pp. 191–200 (1990)

- Baker, T.P.: Stack-based scheduling of realtime processes. J. Real-Time Syst. 3(1), 37–99 (1991)

- Baruah, S.K.: A general model for recurring real-time tasks. In: rtss, p. 114. IEEE (1998)

- Bernat, G., Burns, A.: Combining (n m)-hard deadlines with dual priority scheduling. In: Proceedings of 18th IEEE Real-Time Systems Symposium, pp. 46–57 (1997)

- Bernat, G., Burns, A.: New results on fixed priority aperiodic servers. In: Proceedings of 20th IEEE Real-Time Systems Symposium, pp. 68–78 (1999)

- Burns, A., Davis, R.I.: Mixed criticality systems: a review. Technical report MCC-1(e). Department of Computer Science, University of York (2015). http:// www-users.cs.york.ac.uk/burns/review.pdf

- Burns, A., Davis, R.I., Wang, P., Zhang, F.: Partitioned EDF scheduling for multiprocessors using a C=D scheme. In: Proceedings of 18th International Conference on Real-Time and Network Systems (RTNS), pp. 169–178 (2010)

- Burns, A., Davis, R.I., Wang, P., Zhang, F.: Partitioned EDF scheduling for multiprocessors using a C=D task splitting scheme. Real-Time Syst. J. 48(1), 3–33 (2012)

- Burns, A., Gutierrez, M., Aldea, M., González Harbour, M.: A deadline-floor inheritance protocol for EDF scheduled embedded real-time systems with resource sharing. IEEE Trans. Comput. 64(5), 1241–1253 (2015)

- Burns, A., Prasad, D., Bondavalli, A., Di Giandomenico, F., Ramamritham, K., Stankovic, J., Stringini, L.: The meaning and role of value in scheduling flexible real-time systems. J. Syst. Archit. 46, 305–325 (2000)

- Burns, A., Wellings, A.J.: Dual priority scheduling in Ada 95 and real-time POSIX. In: Proceedings of the 21st IFAC/IFIP Workshop on Real-Time Programming, WRTP 1996, pp. 45–50 (1996)

- Burns, A., Wellings, A.J.: Programming execution-time servers in Ada 2005. In: Proceedings of IEEE Real-Time Systems Symposium (RTSS), pp. 47–56 (2006)

- Burns, A., Wellings, A.J.: Programming execution-time servers in Ada 2005. In: Proceedings of the 27th IEEE Real-Time Systems Symposium, pp. 47–56 (2006)

- Buttazzo, G., Lipari, G., Abeni, L.: Elastic task model for adaptive rate control. In: IEEE Real-Time Systems Symposium, pp. 286–295 (1998)

- 17. Caccamo, M., Sha, L.: Aperiodic servers with resource constraints. In: Proceedings of the IEEE Real-Time Systems Symposium, December 2001

- Davis, R.I., Bertogna, M.: Optimal fixed priority scheduling with deferred preemption. In: Proceedings of IEEE Real-Time Systems Symposium, pp. 39–50 (2012)

- Davis, R.I., Burns, A.: Priority assignment for global fixed priority pre-emptive scheduling in multiprocessor real-time systems. In: Proceedings of IEEE Real-Time Systems Symposium (RTSS), pp. 398–409 (2009)

- Hagenauer, H., Martinek, N., Pohlmann, W.: Ada meets Giotto. In: Llamosí, A., Strohmeier, A. (eds.) Ada-Europe 2004. LNCS, vol. 3063, pp. 237–248. Springer, Heidelberg (2004)

- Henzinger, T.A., Horowitz, B., Kirsch, C.M.: Giotto: a time-triggered language for embedded programming. In: Henzinger, T.A., Kirsch, C.M. (eds.) EMSOFT 2001. LNCS, vol. 2211, p. 166. Springer, Heidelberg (2001)

- Kato, S., Yamasaki, N.: Semi-partitioned fixed-priority scheduling on multiprocessors. In: IEEE Real-Time and Embedded Technology and Applications Symposium, pp. 23–32 (2009)

- Michell, S., Moore, B., Pinho, L.M.: Tasklettes a fine grained parallelism for Ada on multicores. In: Keller, H.B., Plödereder, E., Dencker, P., Klenk, H. (eds.) Ada-Europe 2013. LNCS, vol. 7896, pp. 17–34. Springer, Heidelberg (2013)

- Prasad, D., Burns, A., Atkin, M.: The measurement and usage of utility in adaptive real-time systems. J. Real-Time Syst. 25(2/3), 277–296 (2003)

- Saifullah, A., Li, J., Agrawal, K., Lu, C., Gill, C.: Multi-core real-time scheduling for generalized parallel task models. Real-Time Syst. 49(4), 404–435 (2013)

- Sprunt, B., Sha, L., Lehoczky, J.P.: Aperiodic task scheduling for hard real-time systems. J. Real-Time Syst. 1, 27–69 (1989)

- Wellings, A., Burns, A.: The evolution of real-time programming revisited: programming the Giotto model in Ada 2005. In: Real, J., Vardanega, T. (eds.) Ada-Europe 2010. LNCS, vol. 6106, pp. 196–207. Springer, Heidelberg (2010)

- Zuhily, A., Burns, A.: Exact scheduling analysis of non-accumulatively monotonic multiframe tasks. Real-Time Syst. J. 43, 119–146 (2009)

## **Concurrency and Parallelism**

#### Modeling and Analysis of Data Flow Graphs Using the Digraph Real-Time Task Model

Morteza Mohaqeqi<sup>(⊠)</sup>, Jakaria Abdullah, and Wang Yi

Uppsala University, Uppsala, Sweden morteza.mohaqeqi@it.uu.se

**Abstract.** Data flow graphs are widely used for modeling and analysis of real-time streaming applications in which having a predictable and reliable implementation is an essential requirement. In this paper, we consider scheduling a set of data flow graphs such that liveness and boundedness properties are guaranteed, which leads to a predictable and correct behavior of the application. A formal translation method is proposed to map a given set of data flow graphs to a set of graph-based real-time tasks. Additionally, sufficient conditions are derived under which the obtained task set provides a semantically correct implementation of the given data flow graphs. It is shown that the proposed approach provides a higher level of design flexibility compared to the existing methods which use a simpler, i.e. periodic, task model.

Keywords: Data flow graphs  $\cdot$  Real-time task models  $\cdot$  Buffer boundedness  $\cdot$  Schedulability analysis

#### 1 Introduction

During the past decades, data flow graphs [1,2] have been extensively used for modeling and analysis of real-time streaming and signal processing applications. A number of prominent measures of these applications, including throughput, timeliness, liveness, and processing latency have been analyzed based on this formalism. Such analyses help the designers to have a predictable and reliable implementation of the mentioned applications.

Recently, increasing attention has been paid to study data flow graphs from a real-time scheduling point of view [3-8]. A popular approach is mapping each actor in a given data flow graph to an independent real-time task. Then, the problem is to specify the real-time tasks parameters such that the timing behavior of the data flow is correctly reflected by the task set. The advantage of this approach is that it makes it possible to *reuse* the existing analysis frameworks developed for real-time systems in the scheduling of a set of data flow graphs. For instance, using this approach, the interfering effect of different data flow applications on each other can be analyzed based on the existing theory of real-time task models.

In spite of the relatively extensive studies in this context, only a limited number of real-time task models have been explored by the researchers. In particular,

<sup>©</sup> Springer International Publishing Switzerland 2016

M. Bertogna et al. (Eds.): Ada-Europe 2016, LNCS 9695, pp. 15–29, 2016. DOI: 10.1007/978-3-319-39083-3.2

the work has been mainly focused on the periodic task model. Nonetheless, more expressive models can provide more flexibility to the designers which can lead to better solutions.

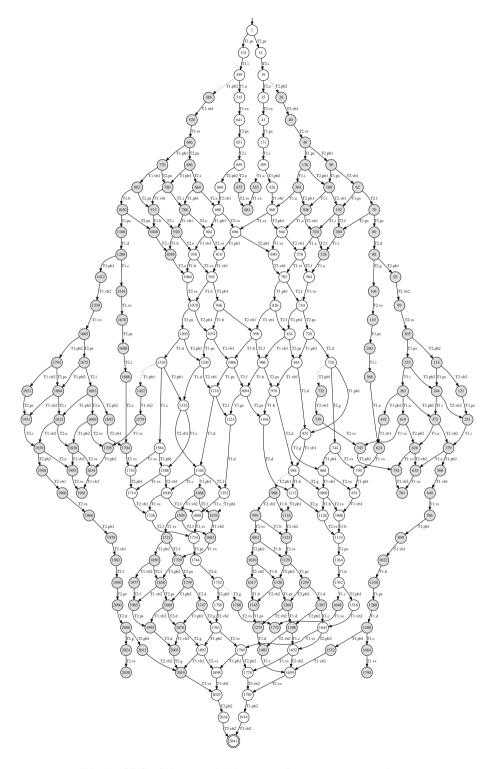

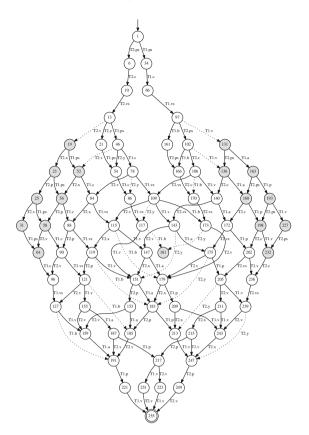

In this paper, we propose to use one of the most expressive yet efficiently analyzable real-time task models, namely the Digraph Real-Time (DRT) model [9], to specify data flow graphs. We present a translation method and discuss the potential benefits and the restrictions of this approach. The proposed method guarantees both boundedness and liveness properties of a data flow graph.

The rest of this paper is organized as follows: Sect. 2 describes the system model by presenting a brief review on the syntax and semantics of a data flow graph. The Digraph Real-Time task model is reviewed in Sect. 3. We present our translation method in Sect. 4. The proposed method is evaluated through the model of an MP3 playback application in Sect. 5. The work related to the current study is reviewed in Sect. 6. The paper is concluded in Sect. 7.

#### 2 System and Application Model

In this paper, we consider a uniprocessor system which runs a number of applications modeled as a set of static data flow graphs. Formally, a static data flow is a directed graph (V, E), where V and E represent the set of vertices and edges, respectively. Each vertex represents an *actor*. Each edge denotes a FIFO channel (also called a buffer), connecting the input port and the output port of two (not necessarily different) actors. A channel c may contain an initial number of tokens, denoted by  $\bar{c}$ , at the system start time. Further, each channel c has a maximum capacity of  $\tilde{c}$ . This means that the number of tokens existing in c should never exceed  $\tilde{c}$ .

Any release of one instance (job) of an actor is called a firing. An actor can be fired only when the required number of tokens are available on its input ports. During its execution, an actor consumes the required tokens from the input ports, and generates some tokens to its output ports. The number of tokens which are produced (consumed) at each firing of an actor is called the production (consumption) rate. Static data flows are classified according to the variability of an actor behavior and its production/consumption rate in different firings. In the following, three major classes, namely synchronous, homogeneous, and cyclo-static data flows [2], are reviewed.

- Synchronous Data Flow (SDF): In an SDF, the execution time as well as the production/consumption rate of each actor is fixed.

- Homogeneous Synchronous Data Flow (HSDF): An SDF is homogeneous if all production/consumption rates are equal to one.

- Cyclo-Static Data Flow (CSDF): The cyclo-static data flow (CSDF) model is a generalization of SDF, in which each actor a has a sequence of different behaviors, affecting its execution time and the production/consumption rates, which repeats cyclically [3]. Let  $n_a$  be the length of this sequence.

Then,  $[f_a(1), f_a(2), \ldots, f_a(n_a)]$  represents the execution sequence of an actor  $a \in V$ . This means that in its *i*th firing, the actor execution time is given by

$$f_a \left( \left( (i-1) \mod n_a \right) + 1 \right).$$

(1)

Similarly, the production and consumption rates are specified by sequences of length  $n_a$ . More specifically, for an actor a, and considering a specific buffer,

- $[g_a(1), g_a(2), \ldots, g_a(n_a)]$  denotes the sequence of production rates;

- $[h_a(1), h_a(2), \dots, h_a(n_a)]$  denotes the sequence of consumption rates.

In the current work, our focus is on the CSDF model.

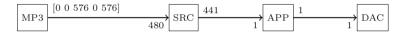

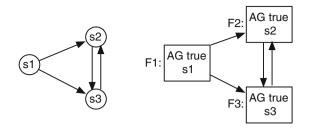

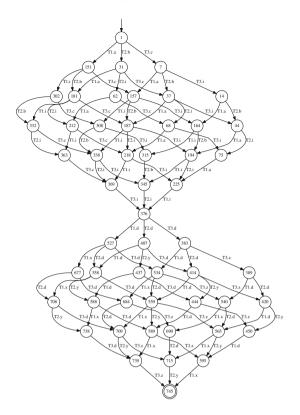

*Example 1.* Figure 1 shows the CSDF graph of an MP3 playback application [10]. This application consists of four tasks, including MP3, Sample Rate Converter (SRC), Audio Post-Processing (APP), and Digital to Analogue Converter (DAC).

Fig. 1. A CSDF graph for the MP3 playback application [10]. Production and consumption rates are shown on the edges.

An implementation of a data flow graph is supposed to provide *liveness* and *boundedness* properties. Intuitively, liveness means that each actor will be executed infinitely many times. In contrast, boundedness necessitates the existence of a bound on the maximum size of each buffer which is never exceeded by the writing actors during the system execution.

#### 3 Digraph Real-Time Task Model

In this section, we review the digraph real-time (DRT) task model [9]. This task model will be used in the next section for modeling CSDF graphs.

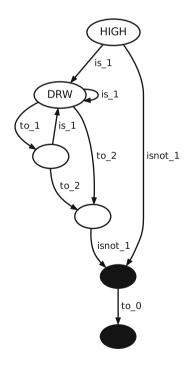

A DRT task T is specified by a directed graph G(T) = (V(T), E(T)), where V(T) and E(T) denote the graph vertices and edges, respectively. Each vertex of the graph represents a *job type*. A vertex  $v \in V(T)$  is labeled by a pair  $\langle e(v), d(v) \rangle$ , where e(v) and d(v) denote the worst-case execution time (WCET) and relative deadline of the corresponding job, respectively. Further, each edge  $(u, v) \in E(T)$  is labeled with a positive number, p(u, v), denoting the interrelease time between the two jobs u and  $v^1$ .

Each path in the graph denotes a possible sequence of jobs which may be generated by the respective task. If the outgoing degree of each vertex in a

<sup>&</sup>lt;sup>1</sup> In the original definition of DRT, an edge label determines the *minimum* inter-release time. Nonetheless, the DRT schedulability analyses [9,11] are valid for the modified version which we use here.

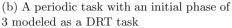

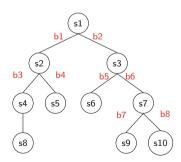

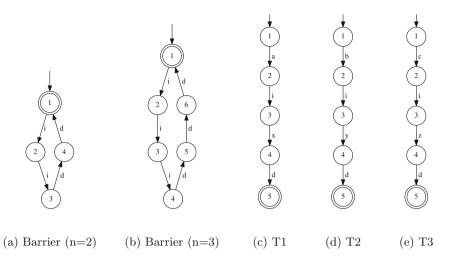

(a) A DRT task with two job types (b)

Fig. 2. Two sample DRT tasks.

task graph is restricted by one, that is, no branching is allowed, then the model reduces to the Generalized Multiframe task model [12].

The focus of this paper is on the *constrained* deadline DRT tasks. Hence, given a DRT task T, it is assumed that for each  $u \in V(T)$ , we have  $d(u) \leq p(u, v)$  for all  $(u, v) \in E(T)$ .

*Example 2.* A sample DRT task with two job types with inter-release times of 5 and 4 is shown in Fig. 2a. Further, Fig. 2b depicts a DRT task which models a periodic task with an initial phase.

The inherent capability of the DRT model to represent non-fixed and nonperiodic behavior of a component makes it suitable for modeling CSDF graphs. In the next section, we present our method for representing CSDF graphs using set of DRT tasks.

#### 4 Translation Method

In this section, we describe our translation method for transforming a given data flow graph to a set of DRT tasks. The method maps each actor to a real-time task. In the following, the details of the translation method and the criteria for determining the real-time task set parameters are provided.

Consider two actors a and b in a given CSDF graph. In addition, let c be a FIFO channel between them with an initial number of tokens of  $\bar{c}$  and a maximum capacity of  $\tilde{c}$ . Let  $n_a$  be the size of the sequence which specifies the cyclically variable behavior of the actor a (as defined in the previous section). We associate a DRT task with  $n_a + 1$  vertices,  $v_0, \ldots, v_{n_a}$ , to a. The starting vertex denotes a job type with the WCET of zero, which is used to enforce a phase (an initial phase before the release time of the first job) in the task. Additionally, for each i,  $0 \le i < n_a$ , an edge is added from  $v_i$  to  $v_{i+1}$ . Also, we consider an edge from  $v_{n_a}$  to  $v_1$ . This set of edges enforce the cyclically repeating pattern of the given actor's behavior. The WCET associated with each vertex  $v_i$ ,  $0 < i \le n_a$ , is set to be the WCET of the *i*th firing of the actor, which is specified by  $f_a(i)$ .

As described, the DRT task corresponding to an actor a contains  $n_a + 1$  vertices and  $n_a + 1$  edges. Edge  $(v_0, v_1)$ , which represents the phase of the task, is labeled by  $\phi_a$ . Further, let the label of the other edges  $(v_i, v_{i+1})$ ,  $1 \le i < n_a$ ,

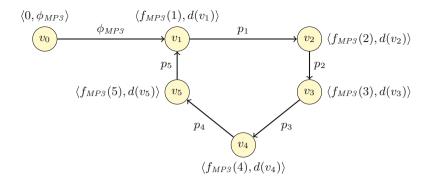

Fig. 3. DRT task for the actor MP3 of the CSDF graph presented in Fig. 1.

be denoted by  $p_i^2$  (also, the edge  $(v_{n_a}, v_1)$  is labeled by  $p_{n_a}$ ). The edge labels are parameters which should be determined such that the liveness and boundedness properties are achieved.

Example 3. Consider the data flow graph of the MP3 player application shown in Fig. 1. According to the specified translation method, the first actor (MP3) will be modeled as a DRT task with six vertices, as shown in Fig. 3. Given a sequence of execution times  $[f_{MP3}(1), \ldots, f_{MP3}(5)]$  for this actor, we can assign the WCET of the job types of the DRT task as  $e(v_i) = f_{MP3}(i)$ , for  $1 \le i \le 5$ . Additionally, the other actors will be represented by a DRT task expressing a periodic behavior, in a similar way as shown in Fig. 2b.

For a complete translation, we need to determine the timing parameters of the DRT tasks. These parameters include the relative deadline of each job type, and the edge labels which represent the inter-release time between the jobs. The timing parameters should be assigned in such a way that the correctness conditions of the implementation are satisfied.

We use the correctness criteria in terms of the Kahn semantics [13] for a Kahn process network. As shown in [10], these criteria imply a *live* and *bounded* behavior of the system specified by a data flow graph. For this purpose, it must be guaranteed that the system never leads to a buffer overflow or buffer underflow. An overflow happens when writing to a buffer exceeds its maximum capacity. In turn, an underflow occurs whenever an actor tries to read from an empty buffer. In the following, we formalize these correctness requirements. To this end, we first need to determine the number of released and finished instances of each job (actor) up to each time instant.

19

<sup>&</sup>lt;sup>2</sup> Please notice that,  $p_i$  is an actor-specific parameter. However, for brevity reasons, it is not explicitly indicated in the notation.

#### 4.1 Number of Released/Finished Jobs

For an actor a, define  $Rel_a(v,t)$  and  $Fin_a(v,t)$  as follows:

$Rel_a(v, t) \equiv$  the number of instances of job type v released up to and including time t,

$Fin_a(v,t) \equiv$  the number of instances of job type v finished up to and including time t.

According to the translation model, the release and completion of a job corresponding to an actor firing are governed by the associated DRT tasks. As a result,  $Rel_a(v,t)$  and  $Fin_a(v,t)$  depend on the timing parameters of the derived DRT tasks. Here, we formally specify the relation between function  $Rel_a(v,t)$ (also  $Fin_a(v,t)$ ) and these parameters. First, it is noted that, for  $t < \phi$ , we have  $Rel_a(v,t) = 0$  and  $Fin_a(v,t) = 0$ . Thus, in the following, we assume that  $t \ge \phi$ .

According to the defined notations, we can specify  $Rel_a(v,t)$  as

$$Rel_{a}(v_{i},t) = 1 + \left\lfloor \frac{t - \phi_{a} - \sum_{j=1}^{i-1} p_{j}}{\pi_{a}} \right\rfloor.$$

(2)

where  $\pi_a = \sum_{j=1}^{n_a} p_j$  is the super-period of the DRT task. In words,  $\pi_a$  denotes the amount of time that it takes for the DRT to have a complete cycle, through which, each job (except the first job which represents the initial phase) is released exactly once. Also, a lower bound for  $Fin_a(v, t)$  can be obtained by

$$Fin_a(v_i, t) \ge 1 + \left\lfloor \frac{t - \phi_a - \sum_{j=1}^{i-1} p_j - d(v_i)}{\pi_a} \right\rfloor.$$

(3)

It is worth noting that the equality does not necessarily hold. This is because that, depending on the scheduling approach, a job may be completed before its deadline, leading to a possibly higher number of finished jobs up to time tcompared to the case in which the job finishes exactly at its deadline.

#### 4.2 Underflow Analysis

Based on the semantics of a data flow graph, an actor may produce (consume) the output (input) tokens at any time during its execution. As a result, for the underflow analysis, we employ a pessimistic approach [10], in which, we consider the minimum possible number of tokens that may be buffered at each instant. Based on this approach, it is assumed that each actor writes to the output buffer(s) as late as possible. In other words, the tokens are assumed to be written to the buffer when the actor completes its execution. On the other hand, we suppose that each actor reads from its input buffer(s) as soon as possible, namely at its release instant.

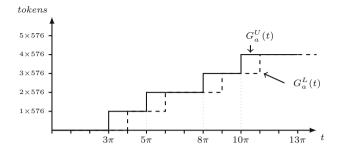

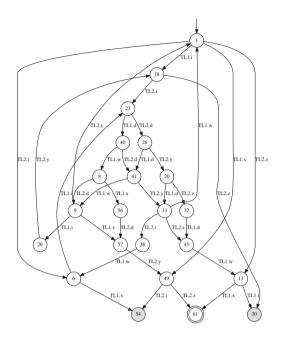

Fig. 4. Upper and lower bound on the number of produced tokens for the MP3 actor.

Regarding the abovementioned pessimistic assumptions, a lower bound for the total number of tokens written to the channel c by an actor a up to (and including) time t can be calculated as

$$G_a^L(t) = \sum_{i=1}^{n_a} g_a(i) \times Fin_a(v_i, t).$$

$$\tag{4}$$

As an example, the dashed line in Fig. 4 depicts the function  $G_a^L(t)$  for the MP3 actor of the CSDF graph specified in Example 1. In this example, it is assumed that any two successive firings are identically separated by a time interval of length  $\pi$ . Further, an implicit deadline has been considered (i.e.  $d(v_i) = \pi$ ).

In addition, an upper bound for the total number of tokens read from a channel c by an other actor b up to and including time t is given by

$$H_{b}^{U}(t) = \sum_{i=1}^{n_{b}} h_{b}(i) \times Rel_{b}(v_{i}, t).$$

(5)

According to these relations, a sufficient condition for the underflow avoidance of channel c is formulated by

$$\forall t \ge 0 : \bar{c} + G_a^L(t) - H_b^U(t) \ge 0,$$

(6)

where  $\bar{c}$  denotes the initial number of tokens of c.

#### 4.3 Overflow Analysis

Based on an approach similar to the one presented for the underflow, we can specify a sufficient condition for overflow avoidance. In this case, the pessimistic assumptions are stated as follows:

- Each actor writes to the output buffer(s) as soon as possible (namely at its release time);

- Each actor reads from its input buffer(s) as late as possible (namely at its finish time).

Consequently, the maximum number of tokens written to a buffer c by an actor a up to time t can be specified as

$$G_a^U(t) = \sum_{i=1}^{n_a} g_a(i) \times Rel_a(v_i, t).$$

(7)

Figure 4 partly shows the variation of  $G_a^U(t)$  for the MP3 CSDF graph, under the previously mentioned assumptions.

Additionally, the minimum number of tokens read from a buffer c by an actor b up to time t is given by

$$H_b^L(t) = \sum_{i=1}^{n_b} h_b(i) \times Fin_b(v_i, t).$$

(8)

Regarding the defined notations, no overflow happens if the following condition holds (recall that  $\tilde{c}$  denotes the maximum buffer capacity)

$$\forall t \ge 0 : \bar{c} + G_a^U(t) - H_b^L(t) \le \tilde{c}.$$

(9)

#### 4.4 Design Space Exploration

Relations (6) and (9) provide sufficient conditions for the correctness of an implementation of a data flow graph. Then, the problem is to assign suitable values to the DRT tasks parameters, namely their inter-release times,  $p_i$ , and relative deadlines,  $d(v_i)$ , such that, while the mentioned conditions are satisfied, some design objective, e.g. the application throughput, is optimized. Furthermore, from a schedulability point of view, these values must be selected such that the obtained task set is schedulable, i.e., each job can complete its execution no later than its deadline. This can be checked using efficient methods proposed in [9,11] for static-priority and dynamic-priority schedulability analysis of DRT task sets.

Here, we discuss a simplifying technique for improving the efficiency of the state-space exploration. First, it is observed that the correctness criteria derived in the previous sections are independent of the worst-case execution time of the actors. In other words, they deal only with the release times and completion times. As a result, the problem of finding an appropriate value assignment to the timing parameters can be first solved irrespective of the schedulability concerns. Afterwards, we have to consider the schedulability of the system. If the system with the derived value assignments is not schedulable, one can easily scale up the timing parameters such that the obtained task set becomes schedulable.

It is worth noting that scaling up all the parameters by the same amount does not affect the correctness of the system, i.e. the validity of (6) and (9). This is because that, in this situation, the numerator and denominator of the respective fractions in (2) and (3) are scaled with the same factor, and the value of the fraction remains unchanged. It should be noted that a similar approach, called abstraction-refinement, has been previously used for the periodic task model [6] to overcome the complexity of the problem. In addition to this technique, another simplification can be made by a linear approximation, which is specified in the following.

**Linear Approximation:** Based on Relations (2) and (3), it is observed that the functions  $Rel_a(v_i, t)$  and  $Fin_a(v_i, t)$ , respectively, can be over-approximated and under-approximated by some linear functions. These approximations are constructed on the basis of the inequality  $x < 1 + \lfloor x \rfloor \leq 1 + x$ , which holds for any real number x [14]. Using this, we specify an overapproximation for the function  $Rel_a(v_i, t)$  as

$$Rel_{a}^{UApp}(v_{i},t) = 1 + \frac{t - \phi_{a} - \sum_{j=1}^{i-1} p_{j}}{\pi_{a}}.$$

(10)

In fact, for any  $t \ge 0$ , we have  $Rel_a(v_i, t) \le Rel_a^{UApp}(v_i, t)$ . In addition, we can obtain an under-approximation for the function  $Fin_a(v_i, t)$  as

$$Fin_{a}^{LApp}(v_{i},t) = \frac{t - \phi_{a} - \sum_{j=1}^{i-1} p_{j} - d(v_{i})}{\pi_{a}}.$$

(11)

These approximate functions can be used in calculating  $G_a^L(t)$ ,  $H_b^U(t)$ ,  $G_a^U(t)$ , and  $H_b^L(t)$ , defined in Eqs. (4), (5), (7), and (8). Then, we can rewrite the underflow and overflow avoidance conditions, presented in (6) and (9), based on these approximations. In the following, we elaborate the underflow condition; the procedure for the overflow condition can be done in a similar manner.

Using the provided approximations, we can rewrite the underflow avoidance condition as

$$\forall t \ge 0 : \bar{c} + \sum_{i=1}^{n_a} g_a(i) \times Fin_a^{LApp}(v_i, t) - \sum_{i=1}^{n_b} h_b(i) \times Rel_b^{UApp}(v_i, t) \ge 0.$$

Moreover, by replacing  $Fin_a^{LApp}(v_i, t)$  and  $Rel_a^{UApp}(v_i, t)$  from (11) and (10), we will get

$$\forall t \ge 0:$$

$$\bar{c} + \sum_{i=1}^{n_a} g_a(i) \left( \frac{t - \phi_a - \sum_{j=1}^{i-1} p_j - d(v_i)}{\pi_a} \right) - \sum_{i=1}^{n_b} h_b(i) \left( 1 + \frac{t - \phi_b - \sum_{j=1}^{i-1} p_j}{\pi_b} \right) \ge 0$$

$$(12)$$

From [10], it is known that, as a necessary condition for overflow and underflow avoidance, the average production rate for any buffer must be equal to its average consumption rate, namely

$$\frac{\sum_{i=1}^{n_a} g_a(i)}{\pi_a} = \frac{\sum_{i=1}^{n_b} h_b(i)}{\pi_b}.$$

(13)

Based on this fact, we can simplify the inequality specified in (12) as

$$\forall t \ge 0:$$

$$\bar{c} + \sum_{i=1}^{n_a} g_a(i) \left( \frac{-\phi_a - \sum_{j=1}^{i-1} p_j - d(v_i)}{\pi_a} \right) - \sum_{i=1}^{n_b} h_b(i) \left( 1 + \frac{-\phi_b - \sum_{j=1}^{i-1} p_j}{\pi_b} \right) \ge 0.$$

Also, from (13), we can write  $\pi_b$  as a linear function of  $\pi_a$ , that is,  $\pi_b = \gamma \pi_a$  for some constant  $\gamma$ . Hence, we have

$$\forall t \ge 0:$$

$$\bar{c}\pi_a + \sum_{i=1}^{n_a} g_a(i) \left( -\phi_a - \sum_{j=1}^{i-1} p_j - d(v_i) \right) - \sum_{i=1}^{n_b} h_b(i) \left( \pi_a + \frac{-\phi_b - \sum_{j=1}^{i-1} p_j}{\gamma} \right) \ge 0.$$

As seen, the obtained relation specifies a *linear* constraint on the problem parameters, which significantly reduces the complexity of the problem.

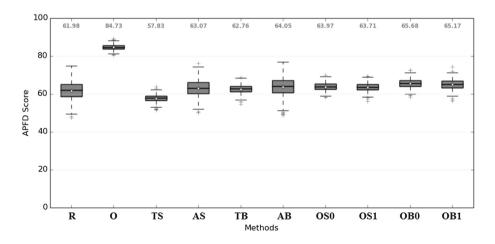

#### 5 Evaluation

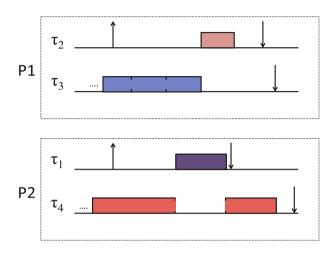

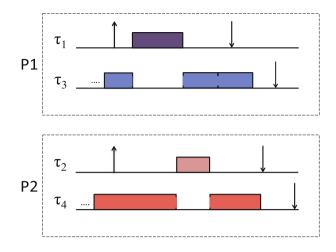

In this section, we evaluate the effectiveness of the proposed approach compared to a previously proposed method which employs a periodic task model for the analysis of CSDF graphs [6, 10]. We compare the two methods in terms of the throughput [15] and the buffer size requirements [16]. The throughput of a dataflow graph measures how often the application is executed in a unit of time. We assume the preemptive EDF algorithm for scheduling the obtained real-time tasks.

For the evaluation purpose, we apply the mentioned methods to the MP3 playback application shown in Fig. 1. According to [10], the execution time of the MP3 actor is specified as the sequence  $f_{MP3}(.) = [670, 2700, 720, 2700, 720] \,\mu$ s. Further, the execution time of SRC, APP, and DAC are specified as 2500  $\mu$ s, 22  $\mu$ s, and 22  $\mu$ s, respectively.

The primary objective is to specify the timing parameters of the task set so as to minimize the total required buffer sizes, while the correctness criteria specified in (6) and (9) are respected and the task set is EDF-schedulable. As well, it is desired to increase the application throughput. In the following, we first present the obtained task sets for each approach. Then, the buffer requirement and the throughput achieved by each method are reported and discussed.

#### 5.1 Obtained Task Sets

In this section, we first specify the periodic task set obtained in [10] for the MP3 playback application. Next, the corresponding DRT task set is described.

**Periodic Task Model:** According to the approach utilized in [10], a periodic task is considered for each actor. In order to have a safe analysis, one needs to consider the maximum execution time of each actor as the WCET of the corresponding periodic task. As a result, a WCET of max{670, 2700, 720, 2700, 720} = 2700  $\mu$ s is considered for the task associated to the MP3 actor. As the other actors have a fixed execution time, WCET of the respective tasks are simply set to those fixed values. The periods and phases assigned to the tasks according to this method are shown in Table 1 [10]. This parameter assignment leads to the system utilization of 99.96 %, which reveals the schedulability of the task set.

**DRT Task Model:** As pointed out before, the MP3 application can be modeled by four DRT tasks. When constructing the tasks, in order to decrease the number

|     | Period ( $\mu s)$ | Phase ( $\mu s)$ |

|-----|-------------------|------------------|

| MP3 | 13219.416         | 0                |

| SRC | 27540.45          | 66647.889        |

| APP | 62.45             | 121760.014       |

| DAC | 62.45             | 121916.139       |

Table 1. Task set parameters obtained for the periodic tasks [10]

of design parameters, we assume that the relative deadline of each job type is set to be equal to the inter-release time between that job and the next one. As noted in Example 3, for the actors SRC, APP, and DAC we can use the DRT task structure which models a periodic task with a specific phase. This is because these actors have a periodically repeating behavior. On the other hand, the MP3 actor is modeled by a DRT task with six different job types, as shown in Fig. 3. It is worth noting that, here, as opposed to the periodic task model, we can consider the actual pattern of the execution times for the MP3 actor, instead of using one conservative maximum value. The goal is to assign the relative deadline of each job such that the problem objective is optimized.

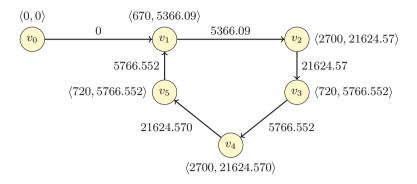

Initially, we use the same values reported in Table 1 for the DRT tasks associated to SRC, APP, and DAC. Additionally, for the DRT task related to MP3, we assume that the inter-release times, in the average, are equal to the period specified for the corresponding periodic task. As a result, the super-period of this task is  $\pi_{MP3} = 5 \times 13219.416$ . Now, we attempt to determine the concrete value of the inter-release times for each pair of job types of this task. In order to decrease the utilization of the task (and hence, increase the schedulability of the task set), we assign the relative deadline of each job (or equivalently, the interrelease time between that job and the next one) in proportion to its execution time. Since in the DRT task, we can consider the actual pattern of execution times instead of a fixed and pessimistic value (which is done in the periodic task model), the total utilization is lower than that of the periodic task. As a result, we can scale down the timing parameters, namely the phases and inter-release times, so as to increase the application throughput, while the task set is still schedulable. The results of this approach are shown in Table 2 and Fig. 5.

**Table 2.** Task set parameters for the DRT tasks ( $\mu$ s)

|     | Period    | Phase      |

|-----|-----------|------------|

| SRC | 25061.809 | 60649.578  |

| APP | 56.829    | 110801.612 |

| DAC | 56.829    | 110943.686 |

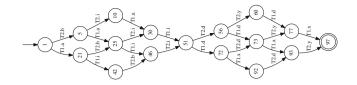

Fig. 5. Parameters for the DRT task which models the MP3 actor  $(\mu s)$ .

#### 5.2 Evaluation Results

The total buffer requirement and the throughput which is achieved by the two approaches are reported in Table 3. As seen, the DRT-based method outperforms the other one in terms of both the buffer requirement and the application throughput.

Table 3. Total buffer requirement and throughput for each method

|                   | Buffer requirement | Throughput $(s^{-1})$ |

|-------------------|--------------------|-----------------------|

| Periodic task set | 2273               | 16013                 |

| DRT task set      | 2155               | 17596                 |

| Improvement       | 5%                 | 9.8%                  |

As a conclusion, it is seen that the DRT-based approach provides a higher degree of flexibility in the design of data flow graphs which can lead to better solutions. Of course, this advantage is achieved at the cost of treating more parameters, which means a larger state-space which must be explored.

#### 6 Related Work

Synchronous Data Flow (SDF) [1] and Cyclo-Static Data Flow (CSDF) [2] are two very basic data flow models. In the past, several variants of these models have been proposed to provide more expressiveness and flexibility in the design of streaming applications. For instance, the *parametric* extensions of the SDF have been developed [17–19] which allow the data flow graph properties, such as the production and consumption rates, to be changed at runtime. In particular, Boolean Parametric Data Flow (BPDF) [18] is a parametric model in which the graph topology can be changed as well as the production and consumption rates of the actors. In this model, an edge can be labeled with a boolean expression which is modified by some actor. At runtime, according to the actual value of the boolean expression, an edge may be enabled or disabled, determining whether the edge should be considered in the firing of the actors at that moment. An assumption made in the related stuies, such as [18–20], is that each actor runs in a dedicated core. Hence, when analyzing the data flow graph, one does not need to take into account the interference of the actors (caused by resource contention) on each other. While this approach provides a high degree of predictability for a single data flow, it is not easily extendible to incorporate the impact of multiple data flows on each other when they are running on the same processing platform with possible resource contention.

Meanwhile, due to the increasing use of real-time operating systems in complex embedded systems which work in dynamic environments, using dynamic scheduling policies, such as rate-monotonic and earliest-deadline first (EDF), for SDFs has been considered recent studies. The advantage of this approach is that the already existing analyses for different scheduling algorithms can be used in this context. This provides the possibility of running multiple applications on the same processing resource, while the interfering effects is considered. One approach to utilize this facility is to use a set of independent real-time tasks to reflect the timing behavior of data flow graphs. One of the basic studies which use periodic realtime task model for data flow graphs is presented by Bmakhra and Stefanov [3]. They explore that how the execution of actors can be parallelized to achieve a maximum throughput. In the same realm, Ali et al. [8] consider the problem of assigning parameters of periodic tasks modeling an HSDF. They suppose a given set of applications each one modeled as an HSDF graph. Each application exhibits two kinds of requirements: a minimum throughput, which is the minimum output data rate (or iteration rate of the whole graph); and one or multiple *latency* constraints put on a number of pairs of actors. A latency constraint is a timing constraint between firing of two actors located on a path. While they consider more constraints compared to the model considered in this paper, their work is specific to HSDF, which is less expressive compared to the CSDF.

Moreover, Bouakaz et al. considered a more general category of data flow graphs. They extended the CSDF model by introducing ultimately periodic CSDF [10] in which the system behavior becomes repetitive after a finite interval, but it is not needed to be periodic from the beginning. They define the affine firing relation which specifies the condition under which a data flow implementation can satisfy the correctness criteria. They investigate the correctness of the implementation based on the periodic task model. In their work, the correctness conditions of an implementation, including boundedness, completeness, and soundness, are obtained based on the Kahn process network semantics [13].

The work presented in [6] can be regarded as one of the most related work to the current study. They consider a CSDF model with a set of buffer size constraints. The goal is to construct a set of periodic tasks reflecting the execution of the given SDFs. The main difference of that work compared to our approach is that we use a more expressive real-time task model, which suggests more flexibility, and thus, a higher degree of schedulability. This, in turn, allows to look for more efficient solutions.

## 7 Conclusion

In this paper, we proposed a formal translation method for converting a given set of data flow graphs to a graph-based real-time task model. We focused on cyclo-static data flow graphs in which an actor behavior, including its worst-case execution time, consumption rate, and production rate, is not necessarily fixed in different firings. We presented sufficient conditions for a correct translation in terms of liveness and boundedness of data flow graphs. The proposed method provides the opportunity of exploring a larger state-space for finding optimal or near optimal solutions for the design of corresponding applications. Based on the translated task model, one can easily perform analyses such as schedulability tests, while taking into account the interfering of the applications running on the same processing core.

The proposed approach can be extended by employing efficient optimization methods for finding task set parameters such that, while the design constraints are met, design objectives like the total buffer size or the application throughput are optimized. In addition, when the DRT tasks exhibit a restricted structure in which only a single cycle is contained, they can be modeled as a set of Generalized Multiframe (GMF) Tasks [12]. In this case, one may employ more efficient analysis methods specific to this task model for schedulability test of the translated tasks.

## References

- Lee, E.A., Messerschmitt, D.G.: Synchronous data flow. Proc. IEEE **75**(9), 1235– 1245 (1987)

- Bilsen, G., Engels, M., Lauwereins, R., Peperstraete, J.: Cycle-static dataflow. IEEE Trans. Sig. Process. 44(2), 397–408 (1981)

- Bamakhrama, M., Stefanov, T.: Hard-real-time scheduling of data-dependent tasks in embedded streaming applications. In: International Conference on Embedded Software, pp. 195–204 (2011)

- Dkhil, A., Do, X.K., Dubrulle, P., Louise, S., Rochange, C.: Self-timed periodic scheduling for a cyclo-static dataflow model. In: International Conference on Computational Science, pp. 1134–1145 (2014)