Patrick Reynaert Michiel Steyaert

> ACSP Analog Circuits And Signal Processing

# RF Power Amplifiers for Mobile Communications

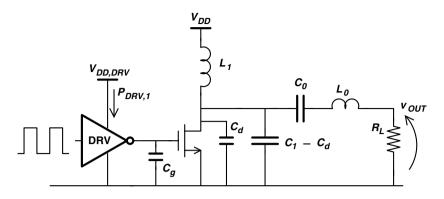

# RF POWER AMPLIFIERS FOR MOBILE COMMUNICATIONS

#### ANALOG CIRCUITS AND SIGNAL PROCESSING SERIES

Consulting Editor: Mohammed Ismail. Ohio State University **Related** Titles: IQ CALIBRATION TECHNIQUES FOR CMOS RADIO TRANCEIVERS Chen, Sao-Jie, Hsieh, Yong-Hsiang ISBN: 1-4020-5082-8 CMOS CURRENT-MODE CIRCUITS FOR DATA COMMUNICATIONS Yuan, Fei ISBN: 0-387-29758-8 ADVANCED DESIGN TECHNIQUES FOR RF POWER AMPLIFIERS Rudiakova, A.N., Krizhanovski, V. ISBN 1-4020-4638-3 CMOS CASCADE SIGMA-DELTA MODULATORS FOR SENSORS AND TELECOM del Río, R., Medeiro, F., Pérez-Verdú, B., de la Rosa, J.M., Rodríguez-Vázquez, A. ISBN 1-4020-4775-4 Titles in former series International Series in Engineering and Computer Science: SIGMA DELTA A/D CONVERSION FOR SIGNAL CONDITIONING Philips, K., van Roermund, A.H.M. Vol. 874, ISBN 1-4020-4679-0 CALIBRATION TECHNIQUES IN NYQUIST A/D CONVERTERS van der Ploeg, H., Nauta, B. Vol. 873, ISBN 1-4020-4634-0 ADAPTIVE TECHNIQUES FOR MIXED SIGNAL SYSTEM ON CHIP Faved, A., Ismail, M. Vol. 872, ISBN 0-387-32154-3 WIDE-BANDWIDTH HIGH-DYNAMIC RANGE D/A CONVERTERS Doris, Konstantinos, van Roermund, Arthur, Leenaerts, Domine Vol. 871 ISBN: 0-387-30415-0 METHODOLOGY FOR THE DIGITAL CALIBRATION OF ANALOG CIRCUITS AND SYSTEMS: WITH CASE STUDIES Pastre, Marc, Kayal, Maher Vol. 870, ISBN: 1-4020-4252-3 HIGH-SPEED PHOTODIODES IN STANDARD CMOS TECHNOLOGY Radovanovic, Sasa, Annema, Anne-Johan, Nauta, Bram Vol. 869, ISBN: 0-387-28591-1 LOW-POWER LOW-VOLTAGE SIGMA-DELTA MODULATORS IN NANOMETER CMOS Yao, Libin, Steyaert, Michiel, Sansen, Willy Vol. 868, ISBN: 1-4020-4139-X DESIGN OF VERY HIGH-FREQUENCY MULTIRATE SWITCHED-CAPACITOR CIRCUITS U, Seng Pan, Martins, Rui Paulo, Epifânio da Franca, José Vol. 867, ISBN: 0-387-26121-4 DYNAMIC CHARACTERISATION OF ANALOGUE-TO-DIGITAL CONVERTERS Dallet, Dominique; Machado da Silva, José (Eds.) Vol. 860, ISBN: 0-387-25902-3 ANALOG DESIGN ESSENTIALS Sansen, Willy Vol. 859, ISBN: 0-387-25746-2 DESIGN OF WIRELESS AUTONOMOUS DATALOGGER IC'S Claes and Sansen Vol. 854, ISBN: 1-4020-3208-0 MATCHING PROPERTIES OF DEEP SUB-MICRON MOS TRANSISTORS Croon, Sansen, Maes Vol. 851, ISBN: 0-387-24314-3 LNA-ESD CO-DESIGN FOR FULLY INTEGRATED CMOS WIRELESS RECEIVERS Leroux and Stevaert Vol. 843, ISBN: 1-4020-3190-4 SYSTEMATIC MODELING AND ANALYSIS OF TELECOM FRONTENDS AND THEIR BUILDING BLOCKS Vanassche, Gielen, Sansen Vol. 842, ISBN: 1-4020-3173-4 LOW-POWER DEEP SUB-MICRON CMOS LOGIC SUB-THRESHOLD CURRENT REDUCTION van der Meer, van Staveren, van Roermund Vol. 841, ISBN: 1-4020-2848-2 WIDEBAND LOW NOISE AMPLIFIERS EXPLOITING THERMAL NOISE CANCELLATION Bruccoleri, Klumperink, Nauta Vol. 840, ISBN: 1-4020-3187-4

# RF POWER AMPLIFIERS FOR MOBILE COMMUNICATIONS

by

# Patrick Reynaert

Katholieke Universiteit Leuven, Belgium

and

Michiel Steyaert

Katholieke Universiteit Leuven, Belgium

A C.I.P. Catalogue record for this book is available from the Library of Congress.

ISBN-10 1-4020-5116-6 (HB) ISBN-13 978-1-4020-5116-6 (HB) ISBN-10 1-4020-5117-4 (e-book) ISBN-13 978-1-4020-5117-3 (e-book)

> Published by Springer, P.O. Box 17, 3300 AA Dordrecht, The Netherlands.

> > www.springer.com

Printed on acid-free paper

All Rights Reserved © 2006 Springer

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Printed in the Netherlands.

# Contents

| Pre | eface                        |        |                                                     | ix |

|-----|------------------------------|--------|-----------------------------------------------------|----|

| 1.  | INT                          | RODU   | CTION                                               | 1  |

|     | 1.1                          | Wirele | ess Communication                                   | 1  |

|     | 1.2                          | CMOS   | S Technology and Scaling                            | 2  |

|     |                              | 1.2.1  | Moore's Law                                         | 2  |

|     |                              | 1.2.2  | RF-CMOS: Moore meets Marconi                        | 3  |

|     | 1.3                          | The R  | esearch Work                                        | 4  |

|     | 1.4                          | Outlin | e of the Work                                       | 6  |

| 2.  | MOBILE COMMUNICATION SYSTEMS |        |                                                     |    |

|     | AND                          | ) POWI | ER AMPLIFICATION                                    | 9  |

|     | 2.1                          | Introd | uction                                              | 9  |

|     | 2.2                          | Mobil  | e Communication Systems                             | 9  |

|     |                              | 2.2.1  | Modulated Bandpass Signals                          | 10 |

|     |                              | 2.2.2  | Digital Modulation                                  | 13 |

|     |                              | 2.2.3  | Probability Density Function of the Envelope Signal | 15 |

|     | 2.3                          | Some   | Aspects of Power Amplification                      | 16 |

|     |                              | 2.3.1  | Output Power                                        | 16 |

|     |                              | 2.3.2  | Peak Output Power and Crest Factor                  | 18 |

|     |                              | 2.3.3  | Input Power and Power Gain                          | 20 |

|     |                              | 2.3.4  | Efficiency                                          | 20 |

|     |                              |        | Efficiency and Modulated Signals                    | 23 |

|     |                              | 2.3.6  | Power Control                                       | 24 |

|     |                              | 2.3.7  | Linearity                                           | 26 |

|     |                              | 2.3.8  | Inductors, Capacitors and Quality Factor            | 27 |

|     | 2.4                          | Power  | Amplifier Classification                            | 30 |

|     |                              | 2.4.1  | Class A                                             | 30 |

|    |     | 2.4.2   | Reduced Conduction Angle: Class AB, B and C        | 33  |

|----|-----|---------|----------------------------------------------------|-----|

|    |     | 2.4.3   | Saturated Class A                                  | 40  |

|    |     | 2.4.4   | Harmonic Tuning for Improved Efficiency: Class F   | 44  |

|    |     | 2.4.5   | Switching Amplifiers                               | 48  |

|    |     | 2.4.6   | Class D                                            | 49  |

|    |     | 2.4.7   | Class E                                            | 51  |

|    |     | 2.4.8   | Reliability                                        | 55  |

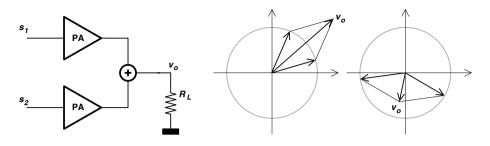

|    | 2.5 | Efficie | ency and Linearity                                 | 58  |

|    |     | 2.5.1   | Efficiency Improvement of Linear Amplifiers        | 60  |

|    |     | 2.5.2   | Linearization of Nonlinear Amplifiers              | 62  |

|    | 2.6 | Conclu  | usion                                              | 64  |

| 3. | ANA | ALYSIS  | AND DESIGN OF THE                                  |     |

|    | CLA | SS E P  | OWER AMPLIFIER IN CMOS                             | 65  |

|    | 3.1 | Introdu | uction                                             | 65  |

|    | 3.2 | A The   | oretical Study of the Class E Amplifier            | 65  |

|    |     | 3.2.1   | The Class E Requirements                           | 65  |

|    |     | 3.2.2   | Existing Methods to Solve the Class E Equations    | 68  |

|    |     | 3.2.3   | A State-Space Model of the Class E Power Amplifier | 69  |

|    |     | 3.2.4   | Limitations of the State-Space Approach            | 74  |

|    | 3.3 | Desigr  | n of the Class E Amplifier in CMOS                 | 75  |

|    |     | 3.3.1   | Design of the Load Resistor                        | 75  |

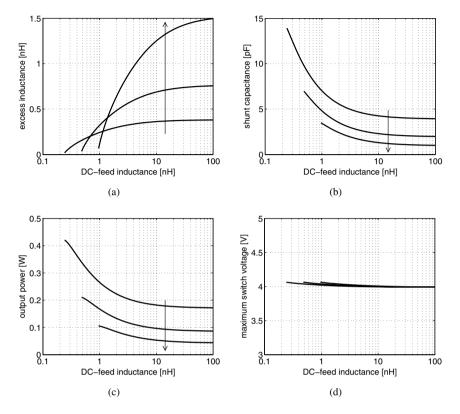

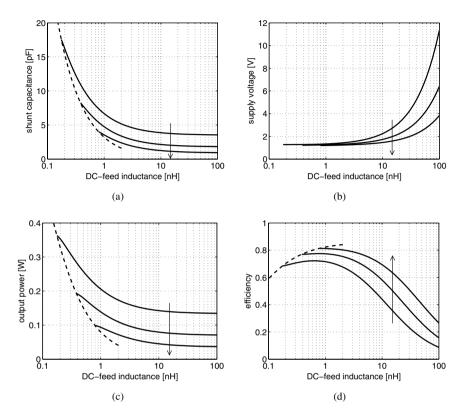

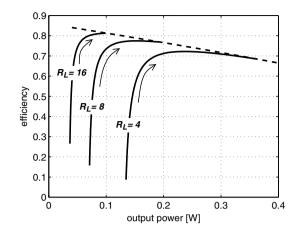

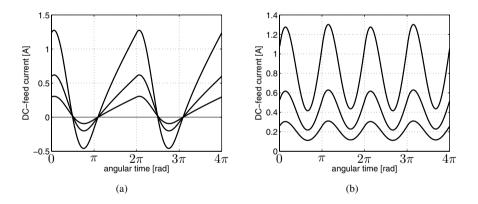

|    |     | 3.3.2   | Design of the DC-feed Inductance                   | 76  |

|    |     | 3.3.3   | Design of the nMOS switch                          | 80  |

|    |     | 3.3.4   | Technology Scaling                                 | 84  |

|    |     | 3.3.5   | Device Stacking                                    | 87  |

|    |     | 3.3.6   | Increasing the Operating Frequency                 | 92  |

|    |     | 3.3.7   | Deviation from Class E: Class BE                   | 93  |

|    | 3.4 | CMOS    | S Layout Aspects                                   | 97  |

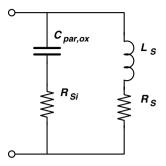

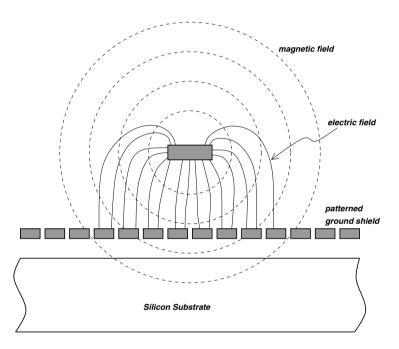

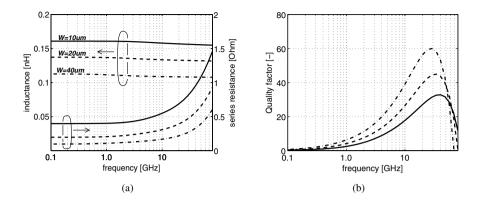

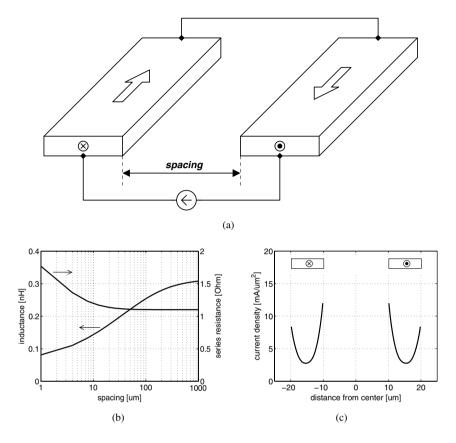

|    |     | 3.4.1   | Integrated Inductors                               | 97  |

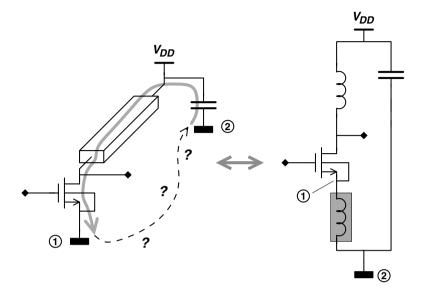

|    |     | 3.4.2   | Decoupling and Bondwires                           | 103 |

|    | 3.5 | Conclu  | usion                                              | 109 |

| 4. | IMP | EDAN    | CE TRANSFORMATION                                  |     |

|    |     |         | ER COMBINATION                                     | 111 |

|    | 4.1 | Introdu | uction                                             | 111 |

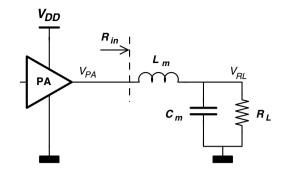

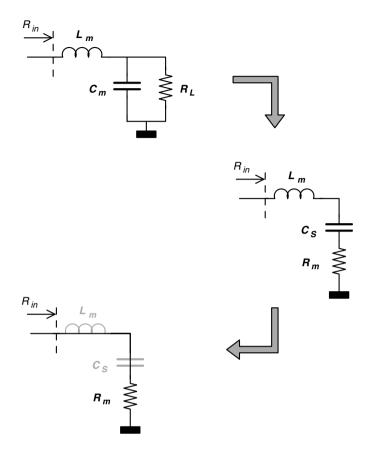

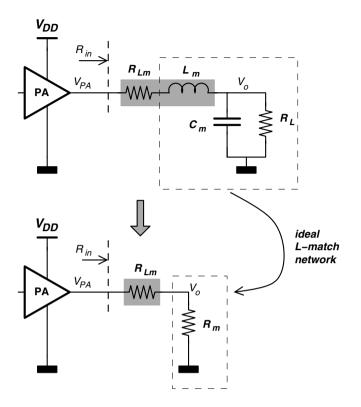

|    | 4.2 | L-mate  | ch Impedance Transformation                        | 111 |

|    |     | 4.2.1   | Basic Equations                                    | 112 |

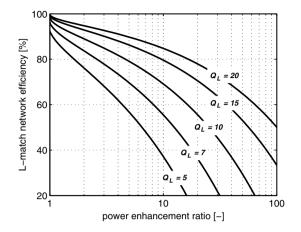

|    |     | 4.2.2   | Inductor Loss and Efficiency                       | 114 |

|    |     |         |                                                    |     |

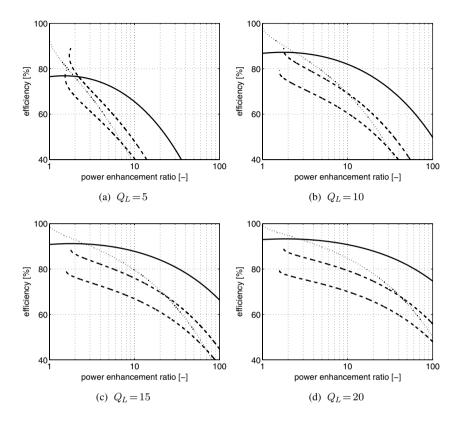

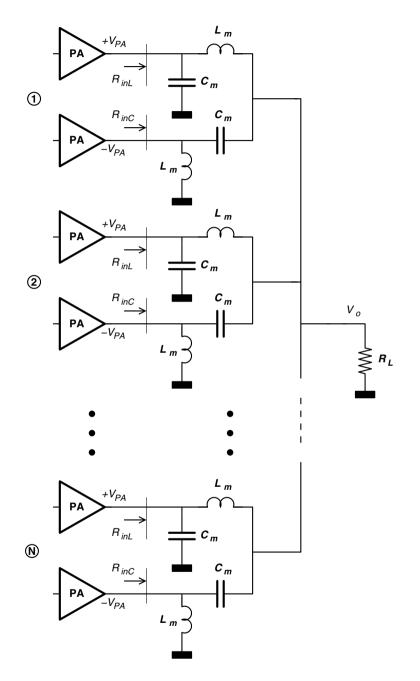

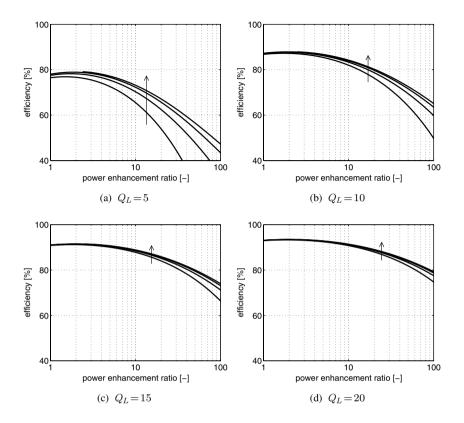

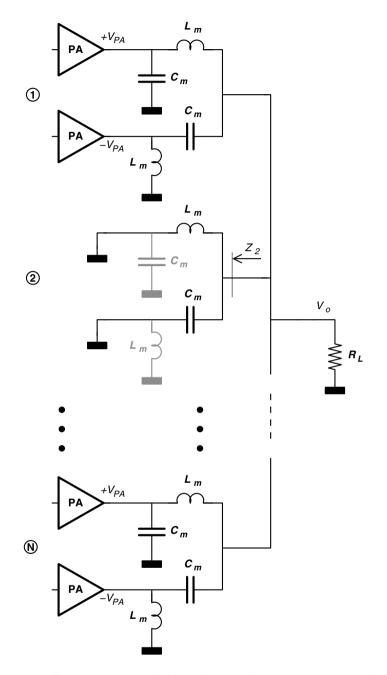

|    | 4.3 | Power  | Combination                                              | 118 |

|----|-----|--------|----------------------------------------------------------|-----|

|    |     | 4.3.1  | Basic Equations                                          | 119 |

|    |     | 4.3.2  | Inductor Loss and Efficiency                             | 122 |

|    |     | 4.3.3  | Multi Section Lattice-Type LC Balun                      | 126 |

|    |     | 4.3.4  | Power Control                                            | 128 |

|    |     | 4.3.5  | Multi Section LC Balun with Non-Identical Sections       | 131 |

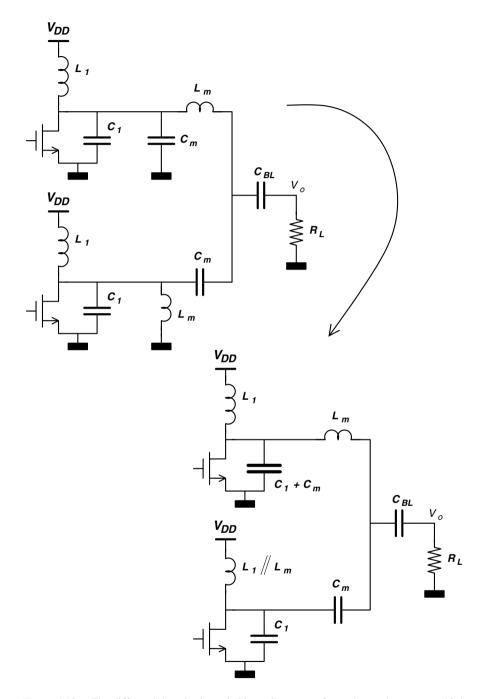

|    |     | 4.3.6  | Merging the Class E Amplifier and the LC Balun           | 132 |

|    | 4.4 | Conclu | usion                                                    | 132 |

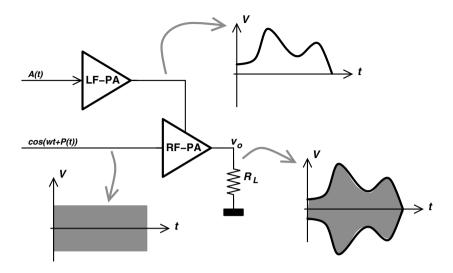

| 5. | POL | AR MO  | DDULATION                                                | 135 |

|    | 5.1 | Introd | uction                                                   | 135 |

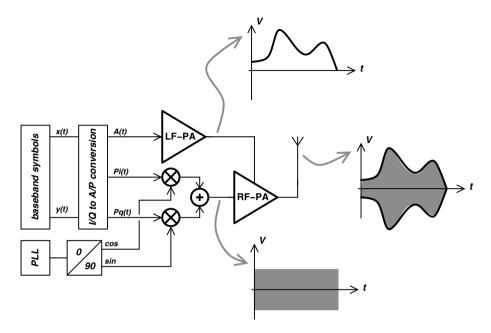

|    | 5.2 | The Po | olar Modulation Architecture                             | 135 |

|    |     | 5.2.1  | Basic Equations                                          | 135 |

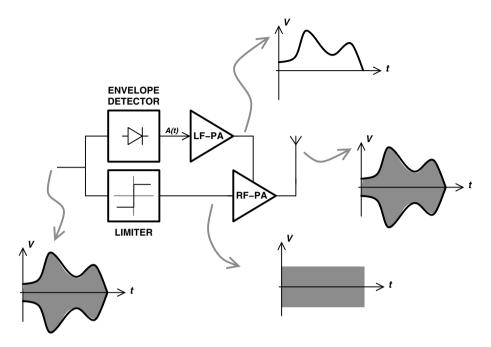

|    |     | 5.2.2  | Envelope Elimination and Restoration                     | 137 |

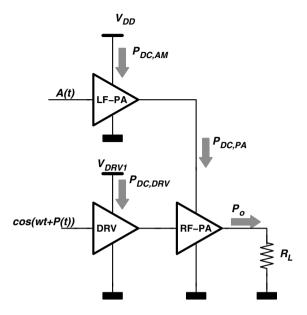

|    |     | 5.2.3  | Influence of the Driver Stages on the Overall Efficiency | 139 |

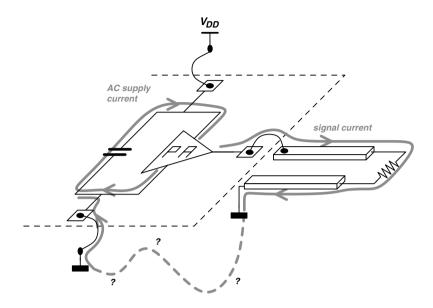

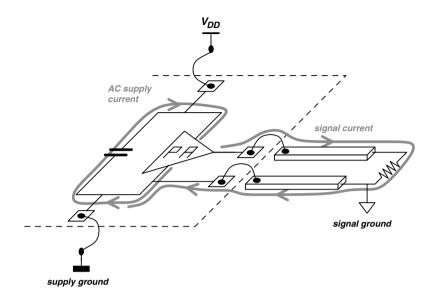

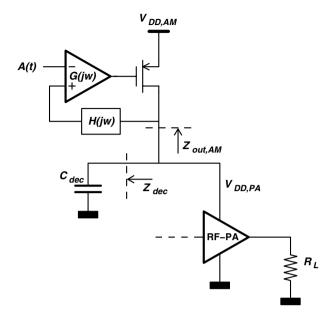

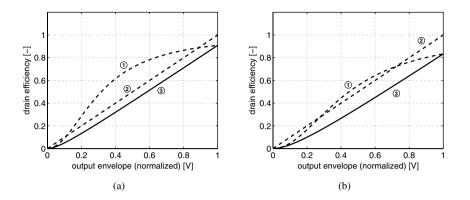

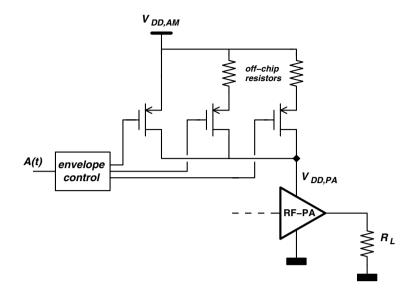

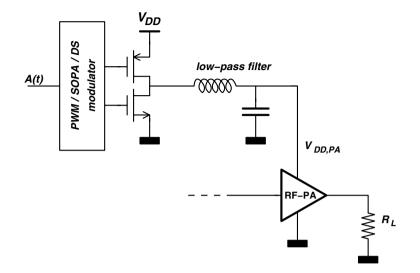

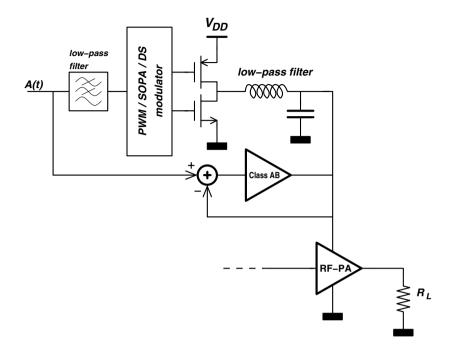

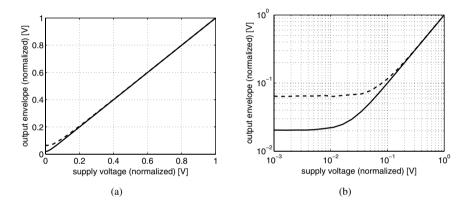

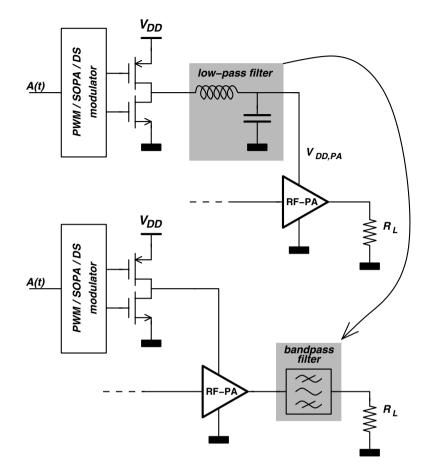

|    |     | 5.2.4  | Implementation of the Amplitude Modulator                | 140 |

|    | 5.3 | Distor | tion in a Polar Modulated Power Amplifier                | 149 |

|    |     | 5.3.1  | Nonlinear Polar Modulated Power Amplifier Models         | 149 |

|    |     | 5.3.2  | Feedforward                                              | 151 |

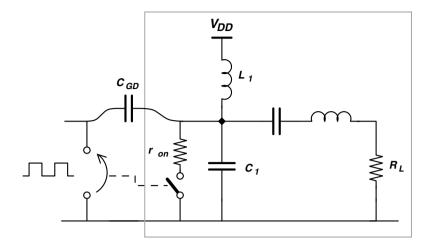

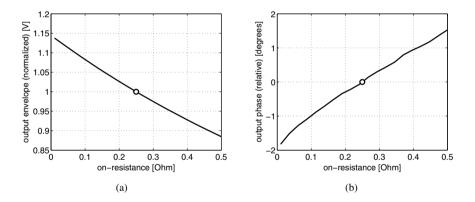

|    |     | 5.3.3  | Nonlinear on-resistance                                  | 155 |

|    |     | 5.3.4  | Nonlinear drain-bulk junction capacitance                | 157 |

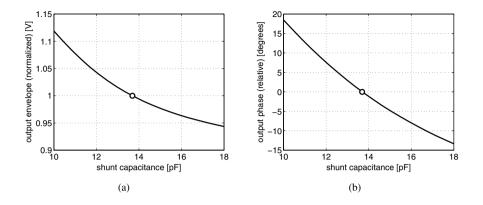

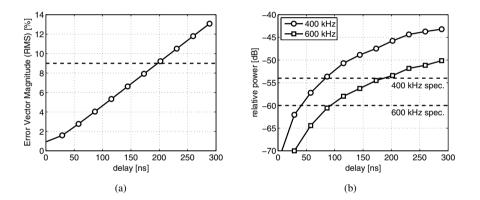

|    |     | 5.3.5  | Differential Delay                                       | 158 |

|    |     | 5.3.6  | Envelope Filtering                                       | 159 |

|    |     | 5.3.7  | 5                                                        | 166 |

|    |     | 5.3.8  | Linearity Improvement Techniques                         | 166 |

|    | 5.4 | Power  | Combination and Polar Modulation                         | 167 |

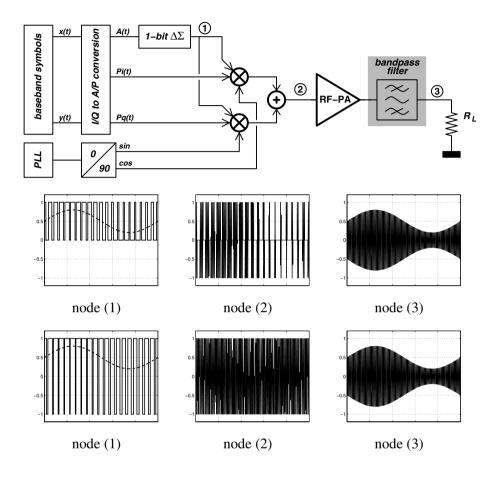

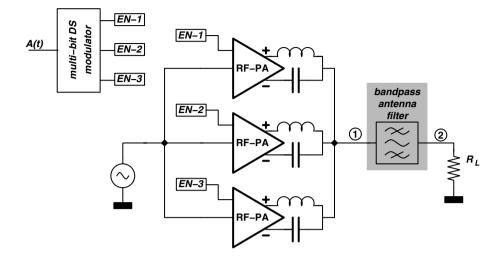

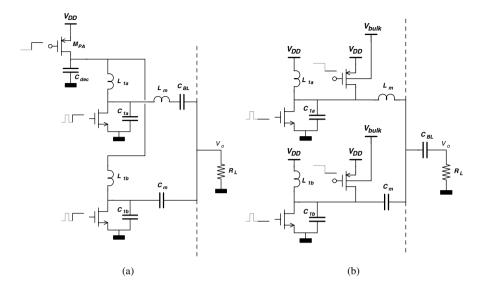

|    | 5.5 | Full D | igital Linearization                                     | 170 |

|    |     | 5.5.1  | A single-bit RF D-to-A                                   | 170 |

|    |     | 5.5.2  | The Lattice-type LC balun as a multi-bit RF D-to-A       | 172 |

|    | 5.6 | Conclu | usion                                                    | 174 |

| 6. | A C | MOS P  | OWER AMPLIFIER FOR GSM-EDGE                              | 177 |

|    | 6.1 | Introd | uction                                                   | 177 |

|    | 6.2 | The E  | DGE System                                               | 178 |

|    |     | 6.2.1  | Enhanced Datarates for GSM Evolution                     | 178 |

|    |     | 6.2.2  | Generation of the EDGE Signal                            | 179 |

|    |     | 6.2.3  | EDGE Transmitter Linearity Requirements                  | 183 |

|    |     | 6.2.4  | EDGE Transmitter Output Power Requirements               | 185 |

|    | 6.3 | A Pola | ar Modulated Power Amplifier for EDGE                    | 185 |

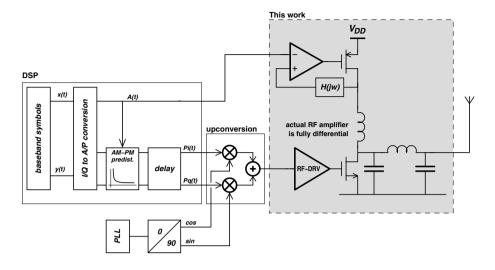

|     |         | 6.3.1    | Architecture                             | 186 |

|-----|---------|----------|------------------------------------------|-----|

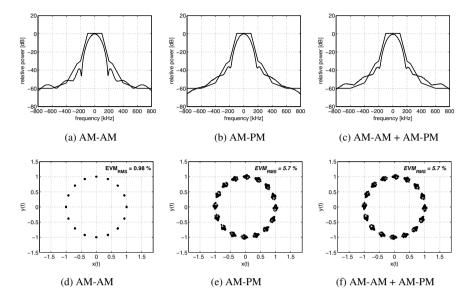

|     |         | 6.3.2    | Distortion                               | 187 |

|     | 6.4     | Circuit  | Implementation                           | 192 |

|     |         | 6.4.1    | Design of the RF amplifier               | 192 |

|     |         | 6.4.2    | Design of the Linear Amplitude Modulator | 196 |

|     |         | 6.4.3    | Layout Aspects                           | 199 |

|     | 6.5     | Measu    | rements                                  | 199 |

|     |         | 6.5.1    | Measurement Setup                        | 199 |

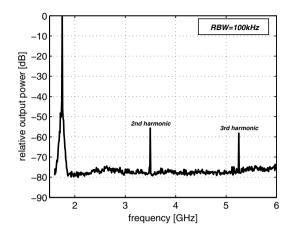

|     |         |          | Constant Envelope Measurements           | 201 |

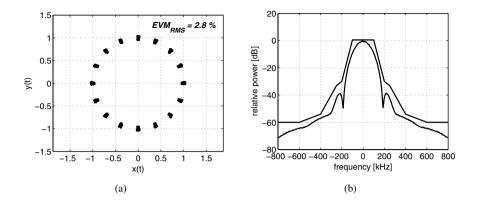

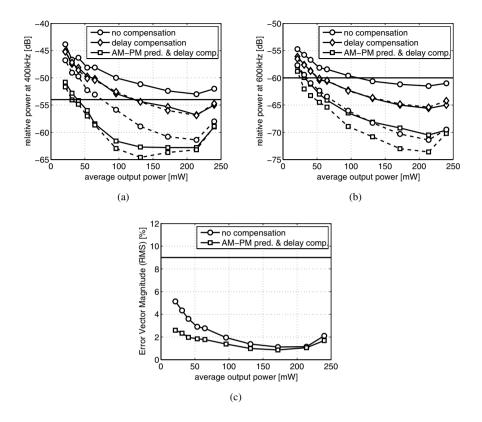

|     |         | 6.5.3    |                                          | 202 |

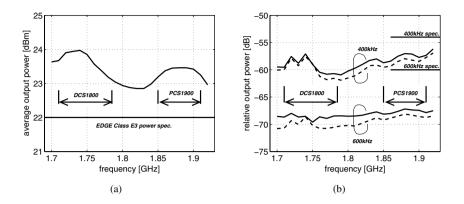

|     |         |          | EDGE Measurements                        | 204 |

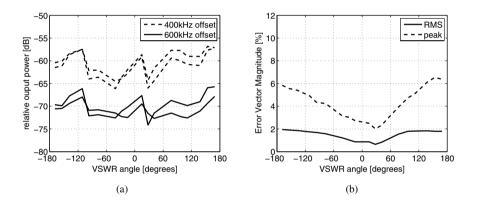

|     |         |          | 16-QAM Modulation and Two-Tone Test      | 209 |

|     | 6.6     | Archite  | ectural Improvements                     | 210 |

|     | 6.7     | Compa    | arison with Other EDGE Solutions         | 212 |

|     | 6.8     | Conclu   | ision                                    | 213 |

| 7.  | AC      | MOS PC   | OWER AMPLIFIER FOR BLUETOOTH             | 215 |

|     | 7.1     | Introdu  | action                                   | 215 |

|     | 7.2     | The Bl   | uetooth System                           | 215 |

|     |         | 7.2.1    | Modulation                               | 216 |

|     |         | 7.2.2    | Power Amplifier Requirements             | 217 |

|     |         | 7.2.3    | Spectral Purity and Spurious Emissions   | 217 |

|     | 7.3     | Circuit  | Implementation                           | 218 |

|     | 7.4     | Layout   | tAspects                                 | 220 |

|     | 7.5     | Measu    | rements                                  | 222 |

|     |         | 7.5.1    | Output Power and Efficiency              | 222 |

|     |         | 7.5.2    | Bluetooth Measurements                   | 224 |

|     | 7.6     | Compa    | arison with Other Work                   | 225 |

|     | 7.7     | Conclu   | ision                                    | 227 |

| 8.  | CON     | ICLUSI   | ONS                                      | 231 |

|     | 8.1     | Main C   | Contributions and Achievements           | 231 |

|     | 8.2     | Epilog   | ue                                       | 233 |

| Lis | st of A | Abbrevia | tions and Symbols                        | 235 |

| Re  | feren   | ces      |                                          | 239 |

| Inc | Index   |          |                                          | 249 |

|     |         |          |                                          |     |

# Preface

Since the early nineties, mobile communication systems have entered our daily life. The main reason for this unprecedented wireless revolution, is the high integration level that can be achieved with CMOS. This allowed the integration of enormous amounts of digital functionality on one single chip. As such, it became feasible to introduce digital coding and digital signal processing in wireless communication systems which resulted in the powerful mobile networks of today. Another reason for the successful wireless development, is the low cost of the user equipment which in turn is due to the low cost of CMOS.

The evolution of mobile communication systems continues and today, telephony, television, internet, e-mail, radio broadcast, . . . are all being merged together. They have become services, rather than stand-alone systems, that users can access through one single mobile device. Putting all this functionality into one small mobile device, at a reasonable cost, requires a higher integration level. For the comfort of the user, it also requires an increased battery lifetime and thus a low power consumption.

Mobile phones and wireless network equipment both require a power amplifier to amplify the radio signal before it can be transmitted through the antenna. The power amplifier should amplify the radio signal to the desired output level, as accurately as possible, but without consuming too much power itself as this would reduce the battery lifetime. In other words, besides the required output power, the power amplifier should have sufficient linearity and a high efficiency.

The overall goal of this work is to provide circuit design techniques that allow the reader to design a power amplifier that (1) meets the output power and linearity requirements of a mobile communication system, (2) has a high efficiency and gain, (3) is integrated in CMOS and (4) requires no expensive off-chip components. To achieve this goal, a theoretical foundation is developed first. It investigates the consequences of CMOS integration with respect to power amplification. Impedance transformation and power combining are crucial to achieve sufficient output power in a low-voltage CMOS technology and is subsequently covered. Combining efficiency and linearity leads to the development of a polar modulation architecture.

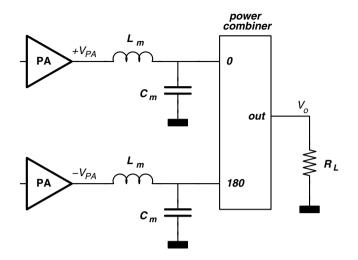

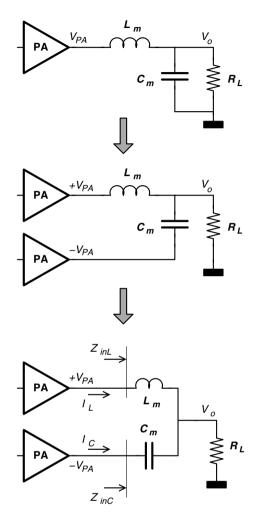

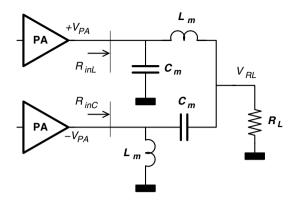

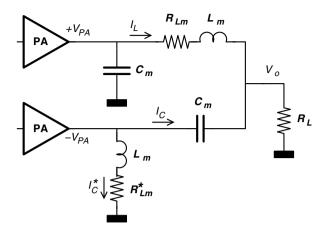

To validate the developed theory, two amplifiers were successfully designed, fabricated and measured. The first amplifier is designed for GSM-EDGE in a 0.18  $\mu$ m CMOS technology and operates at 1.75 GHz. To efficiently amplify the non-constant envelope EDGE signal, a polar modulation architecture was developed. The amplifier achieves a peak output power of 27 dBm with an overall efficiency of 34 %. When transmitting EDGE signals, the amplifier achieves an overall efficiency of 22 % at an output power of 23.8 dBm or 240 mW. The second amplifier is integrated in a 0.13  $\mu$ m CMOS technology, operates at 2.45 GHz, is fully differential and has a single-ended output. To achieve sufficient output power in the 0.13  $\mu$ m technology, a lattice-type LC power combining network is integrated on the CMOS chip, that allows the parallel connection of four amplifiers. The amplifier achieves an output power of 23 dBm with an overall efficiency of 29 %. The power combining network allows for both a discrete power control and an efficiency improvement.

# Chapter 1

# **INTRODUCTION**

# 1.1 Wireless Communication

Wireless and mobile communication systems have become ubiquitous in our daily life and it has changed our society and our way of living in a tremendous way. For sure, the desire for mobility and communication are natural human properties and society is always changing. But it is only recently that the possibilities have taken a steep flight upwards, it is only recently that people are able to *see and hear* things that are not nearby. Thanks to the invention of wireless (radio-)communication in the nineteenth century and television in the twentieth century, humanity has extended its own sensorial capabilities; an unprecedented change.

It is generally accepted that mobile communication was born in 1897, when Guglielmo Marconi gained a patent for his wireless telegraph<sup>1</sup>. In those days, radio-communication was merely transmitting the dots and dashes of the Morse code. Slowly, communication equipment enhanced and radio-communication was used for navigation and to keep contact with ships and airplanes. But still, there was as strong need for new technologies that could manipulate, amplify and decode the weak electronic radio signals.

The invention of the vacuum tube in 1906 by Lee De Forest made it possible to amplify and process the received radio signals. Armstrong was the first to develop radio receivers and is well-known for his invention of the regenerative receiver in 1913, the invention of the super-heterodyne receiver during World War I and his successful demonstration of frequency modulation in 1933. Although a brilliant radio amateur, Armstrong eventually lost all his patents.

<sup>&</sup>lt;sup>1</sup>Nikola Tesla is now credited with having inventing modern radio; the Supreme Court overturned Marconi's patent in 1943 in favor of Tesla.

The invention of the transistor in 1947 by John Bardeen, Walter Brattain and William Shockley resulted in a tremendous size and weight reduction of most electronic equipment and increased the reliability; the *transistor radio* is a nice example of this. Another important technological step was made in 1958, when Jack Kilby invented the integrated circuit. He conceived and built the first electronic circuit in which all of the components, both active and passive, were fabricated in a single piece of semiconductor material half the size of a paper clip. The successful laboratory demonstration of that first simple microchip on September 12, 1958, made history.

Apart from the wireless evolution, the invention of the integrated circuit also enabled engineers to design large digital systems at a relative low cost. This in turn gave rise to a rapid growth of the number of personal computers and a shift from the old telephone systems to digital networks. The Internet, invented in 1973 and laid out in 1983 and the World Wide Web, developed in 1989, were the logical consequences.

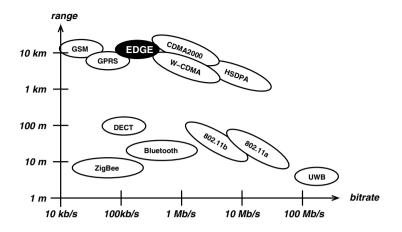

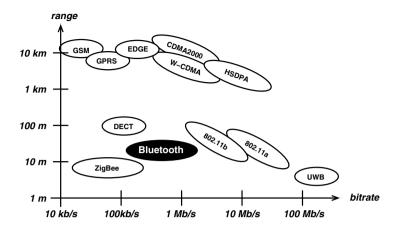

Since the introduction of GSM in Europe in 1991, the mobile telephony market is growing rapidly. In 2003, the number of global mobile subscribers exceeded the number of fixed lines for the first time and it is expected that by 2010, there will be over 23 billion individual wireless subscribers worldwide [Deut04]. Besides the mobile phone networks, the development of wireless data networks, like W-LAN and Bluetooth, followed quickly and they became very popular to make a wireless link between all kinds of devices and for wireless internet access.

Today, telephony, television, internet, e-mail, radio broadcast, ... are all being merged together. They have become services, rather than stand-alone systems, that users can access through one single mobile device. The design of such a single mobile device requires a high level of integration and miniaturization, a low power consumption and a low production cost. This is the point were CMOS pops up.

# 1.2 CMOS Technology and Scaling

### 1.2.1 Moore's Law

Device scaling aims to integrate more transistors per unit area. This requires less silicon area for the same functionality and a lower production cost. Gordon Moore has predicted this trend already in 1965 [Moor65]. He observed that the number of transistors on a single chip doubles every year. In 1975, he updated his prediction to once every two years. While originally intended as a rule of thumb in 1965, it has become the guiding principle for the industry to deliver ever-more-powerful semiconductor chips at proportionate decreases in cost. To achieve such high integration levels, the size of each individual transistor has to shrink, and to reduce the cost, the yield has to go up.

#### Introduction

In 1962, Steven Hofstein and Fredric Heiman at the RCA research laboratory in Princeton, New Jersey, invented a new family of devices called metal-oxide semiconductor field-effect transistors, or MOSFET. CMOS circuits were invented in 1963 by Frank Wanlass at Fairchild Semiconductor. The first CMOS integrated circuits were made by RCA in 1968 by a group led by Albert Medwin. Since the eighties, CMOS is pre-eminently *the* digital technology of choice. The success of CMOS in the digital semiconductor market has resulted in huge technological investments to shrink the transistors and to increase the production yield. CMOS scaling has followed *Moore's Law* for over 40 years and nowadays, several billions of transistors can be integrated on a single chip. As such, CMOS has also become the cheapest technology available today. Roughly, the cost of a SiGe technology is two to three times the cost of CMOS and GaAs is about five to ten times the cost of CMOS [Jaco].

The influence of Moore's Law on our every day life can not be overestimated. The semiconductor industry is the only industry that achieves a cost reduction every two years. In the 2005 annual report of the Semiconductor Industry Association [SIA05], it is formulated as follows: "... in 1978, a commercial flight between New York and Paris cost 900 USD and took seven hours. If the principles of Moore's Law were applied to the airline industry, that flight would now cost about a penny and take less than one second ... " an impressive thought.

# 1.2.2 **RF-CMOS:** Moore meets Marconi

The main trigger for the tremendous growth of the mobile phone market, was the introduction of digital coding and signal processing in wireless communications [Reyn03b]. The development and scaling of CMOS allowed the integration of enormous amounts of digital functionality on one single chip. This *digital power* enabled the use of sophisticated modulation schemes, complex demodulation algorithms, high quality error detection and correction, and allowed to obtain high data rate communications.

For a consumer, performance is only one aspect, he or she also wants a low cost mobile device with a high battery lifetime. In other words: low cost and low power consumption. The digital circuitry, typically integrated on one or two CMOS chips, already fulfills this requirement to a great extend. It is only recently that the radio frontend, i.e. the analog interface between the antenna and the digital baseband circuitry, is being integrated in CMOS [Abid04]. For this, it took the persistence of some academic institutions [Stey98] and some

pioneering firms [Silb] to prove the feasibility of CMOS design at radio frequencies<sup>2</sup> (RF).

CMOS is a digital technology and was originally not developed for highfrequency or microwave design. It is thanks to the scaling, dictated by Moore's Law, that CMOS became able to operate at GHz frequencies and this triggered researchers to investigate the possibilities to do analog RF design in CMOS. Surely, better RF performance can be achieved with a dedicated RF technology like GaAs, SiGe or InP. However, the real strength of RF-CMOS is the low cost and the possibility to use digital signal processing to improve the performance of the RF frontend. Furthermore, in a highly integrated solution, the signals stay on-chip. Driving off-chip RF components requires more power and makes the system prone to noise pick-up. A highly integrated RF frontend in a CMOS technology thus results in a low power consumption, a better noise immunity and a low cost solution.

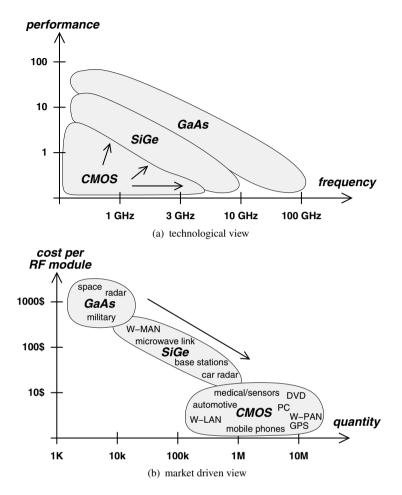

A lot of controversy still exists around RF design in CMOS. After all, CMOS can operate at high frequencies, but it is not a dedicated RF or microwave technology. Yet, the cost reduction and high integration level are the main motivations. If extreme high performance is needed, like in military or space applications, no doubt that other technologies are preferable. However, for medium performance applications and especially if low cost and high production volumes are an issue, CMOS is unbeatable. To illustrate this view, figure 1.1 shows a traditional technological view and a market driven view of CMOS, compared to SiGe and GaAs [Jaco]. The operating frequency and performance of CMOS has improved over the last decades; this is the technological view. Today, an entire mobile phone at 1.8 GHz can be integrated in CMOS [Silb] and research is done to integrated circuits at 24 GHz and even 60 GHz in CMOS [Komi04, Doan04]. The market-driven view on the other hand shows for which applications CMOS is of importance. If it has to be cheap and large quantities are required, CMOS is the only viable solution. But of course, the performance has to be met and no doubt that for some applications, CMOS will never be good enough.

#### **1.3** The Research Work

The RF power amplifier is a vital part of any wireless transmitter as it has to amplify the electric radio signal before it can be transmitted through the antenna. Wireless communication systems are of course very broad, submarine communications at 18 kHz are wireless, a microwave link at 60 GHz is also wireless. ... and yet they both require a power amplifier. However, this

<sup>&</sup>lt;sup>2</sup>RF stands for Radio Frequencies and is rather general term since radio waves can have frequencies from a few hertz up to several hundreds of gigahertz. However, RF has become a synonym for frequencies roughly above 1 GHz.

Figure 1.1. Position of RF-CMOS compared to SiGe and GaAs.

research is focussed on the design of RF power amplifiers in mobile user devices, like mobile phones.

Four keywords characterize the electrical performance of a power amplifier: *output power, efficiency, gain* and *linearity*. Output power and linearity are performance figures that are set by the requirements of the wireless system. If these specifications are not met, the power amplifier is useless. This is different for efficiency and gain. A high efficiency and a large gain results in a power amplifier that consumes little power from the battery while amplifying and transmitting radio signals. In other words, these figures are related to the battery lifetime. A higher efficiency gives a longer battery lifetime and thus a longer talk time of the mobile device. The product cost, maybe the most important figure for many customers, is related to the technology in which the amplifier is integrated and the number of external components that are needed to have a functional power amplifier. As said before, CMOS in large volumes undoubtedly has a production cost advantage over competing technologies like SiGe and GaAs.

Several research institutes have already demonstrated the CMOS integration of RF transceivers for mobile telephony, Bluetooth and WLAN. Nowadays, these research efforts become visible in the many commercially available products [Ath, Silb, STM, Axi, Bro, RFMa] and the research focus on RF transceivers in CMOS has shifted to higher frequencies [Komi04, Doan04] and to low power consumption [Otis05].

The integration of power amplifiers in CMOS seems to follow a slightly different story. Although CMOS RF power amplifiers become commercially available [Sila, Axi], many research institutes and companies continue to investigate the possibilities to combine linearity, efficiency and output power in one single CMOS RF power amplifier. Many alternative architectures and approaches exist in literature and, in contrast to integrated receiver architectures, a clear road or solution has not arisen yet.

# **1.4 Outline of the Work**

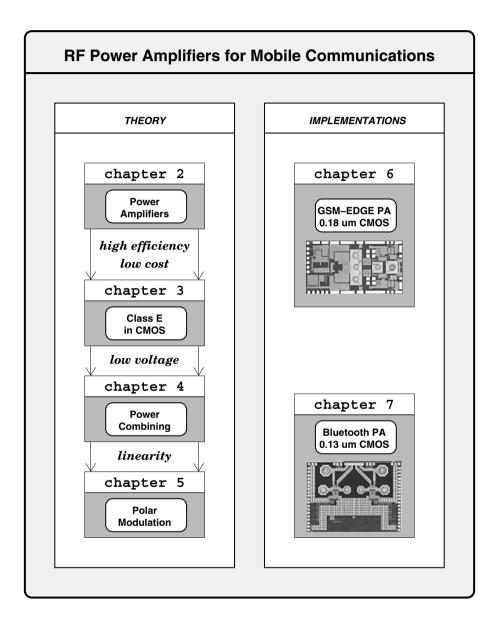

Combining the previous thoughts, the aim of this work is to develop design techniques for an integrated CMOS RF power amplifier. These techniques should allow the design a CMOS RF power amplifier that meets the output power and linearity requirements of a mobile communication system, that has a high efficiency and gain, that is integrated in CMOS and that requires no expensive off-chip components. The outline of this work is shown in figure 1.2. It is divided in two major parts: *theory* and *implementations*.

- Chapter 2 aims to welcome the reader in the world of power amplification. It gives a general overview of digital modulation and it will introduce some important definitions and figures that characterize a power amplifier. Next, a classification of RF power amplifiers is given together with a discussion on how to combine efficiency and linearity in one power amplifier.

- The aim to achieve both a high efficiency and a high integration level in a low cost CMOS technology is the basic idea that will lead us to chapter 3. It first presents a tool to analyze and design the Class E amplifier with the inclusion of all power losses. The influence of the parasitic capacitances on the transistor sizing is demonstrated with the design tool. Next, the impact of technology scaling, device stacking and the shift towards a higher frequency are investigated. The chapter concludes with some CMOS layout aspects.

#### Introduction

- The next problem to tackle is the low supply voltage of current CMOS technologies, and this is covered in chapter 4. First the L-match network is discussed, followed by the lattice-type LC balun network. The latter network allows to achieve a higher output power, can easily be integrated in CMOS and can be merged with the Class E amplifier. The LC balun also allows to implement a discrete form of power control.

- Modern communication systems, like W-LAN and CDMA, allow both amplitude and phase modulation of the RF carrier to increase the datarate of a wireless link. Hence, the amplifier must have sufficient amplitude linearity. Polar modulation of the Class E amplifier allows to combine a high efficiency and a high integration level together with the required linearity and output power specifications. Chapter 5 presents a thorough discussion on polar modulation. The architectural issues and the distortion mechanisms of polar modulation are covered in this chapter and are expanded towards full digital linearization.

The theoretical aspects of this research were also put into practice and resulted in the design, fabrication and measurement of two integrated CMOS RF power amplifiers.

- Chapter 6 will discuss the design, the implementation and the measurement results of a polar modulated power amplifier for the GSM-EDGE mobile phone system. The amplifier is integrated in a 0.18  $\mu$ m CMOS technology and requires no expensive RF components. First, the system level aspects of EDGE are covered, which leads to the design requirements of the integrated amplifier. The circuit implementation of the RF amplifier and the amplitude modulator are covered and followed by an extensive discussion on the measurement results.

- Chapter 7 will discuss the design, implementation and measurement results of an integrated power amplifier for Bluetooth. The differential amplifier is fully integrated in a 0.13  $\mu$ m CMOS technology, has a single-ended output and is capable to efficiently control its output power. First, a brief discussion of the Bluetooth system is given and followed by the circuit level implementation issues. The measurement results clearly demonstrate the efficiency improvement of the amplifier.

Figure 1.2. Outline of the Work.

# Chapter 2

# MOBILE COMMUNICATION SYSTEMS AND POWER AMPLIFICATION

# 2.1 Introduction

Amplifying an electrical signal is the sole purpose of a power amplifier. Though trivial at first sight, several conditions will impede the design and the implementation. For a power amplifier that is designed for a mobile or wireless communication system, *output power*, *efficiency*, *gain* and *linearity* are the most important properties, and they can easily be quantified. On the other hand *cost* and *reliability* are not as easy to quantify but their importance should not be underestimated.

To gain better insight in the different tradeoffs, this chapter will first discuss some system level aspects of mobile communication systems and the properties of the signals that need to be amplified. Next, some key parameters of an RF power amplifier are defined, as they will frequently be used throughout this text. In section 2.4, a classification of power amplifiers is given based on the classical theory of conduction angle, overdrive level and harmonic termination at the output. The classification is focussed on the difficulties regarding CMOS implementation and integration. Finally, in section 2.5 the tradeoff between efficiency and linearity is clarified and some efficiency improvement and linearization techniques are discussed.

# 2.2 Mobile Communication Systems

The very first step in designing a power amplifier for wireless or mobile communication is a good knowledge of the communication system itself and the signals that needs to be amplified. Therefore, this first section will review some important concepts of digital modulation and some signal properties that are important for power amplifier are defined.

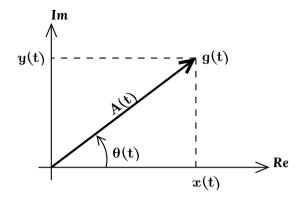

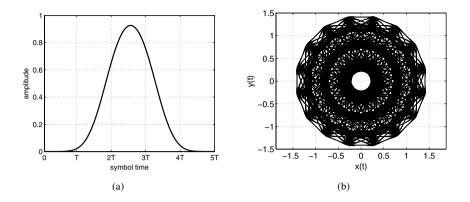

Figure 2.1. Representation of the complex envelope in the complex plane.

# 2.2.1 Modulated Bandpass Signals

A modulated bandpass signal can be represented as [Couc97]

$$v(t) = \operatorname{Re}\left\{g(t)e^{j\omega_{c}t}\right\}$$

(2.1)

with  $f_c = \omega_c/2\pi$  the carrier frequency and g(t) the *complex envelope* of v(t). The complex function g(t) thus modulates the phasor  $e^{j\omega_c t}$ . Since g(t) is a complex function, its instantaneous value can be represented in the complex plane, see figure 2.1.

A single point in the complex plane can also be represented by Cartesian and polar coordinates.

$$g(t) = x(t) + jy(t) = A(t)e^{j\theta(t)}$$

(2.2)

Using the Cartesian and polar representation of g(t), the modulated signal v(t) can now be expressed as

$$v(t) = x(t)\cos(\omega_c t) - y(t)\sin(\omega_c t)$$

(2.3)

$$v(t) = A(t)\cos(\omega_c t + \theta(t))$$

(2.4)

Looking at above equation, A(t) carries the amplitude modulation and  $\theta(t)$  contains the phase information. In short, A(t) is called the *envelope signal* or *amplitude signal* and  $\theta(t)$  is called the *phase signal*. For similar reasons, x(t) is the *in-phase* or I(t) signal and y(t) is the *quadrature* or Q(t) signal. All these signals are baseband signals with a relatively low bandwidth, at least compared to  $\omega_c$ . The conversion between the two equivalent representations is as follows

$$A(t) = \sqrt{x(t)^2 + y(t)^2}$$

(2.5)

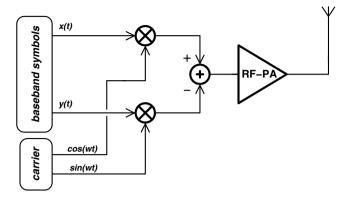

Figure 2.2. Transmitter architecture based on a Cartesian representation of a modulated signal.

$$\theta(t) = \arctan\left(\frac{y(t)}{x(t)}\right)$$

(2.6)

. . .

$$x(t) = A(t)\cos(\theta(t))$$

(2.7)

$$y(t) = A(t)\sin(\theta(t))$$

(2.8)

In most wireless transmitter architectures, the Cartesian representation of the signal is directly converted in a circuit diagram, as shown in figure 2.2.

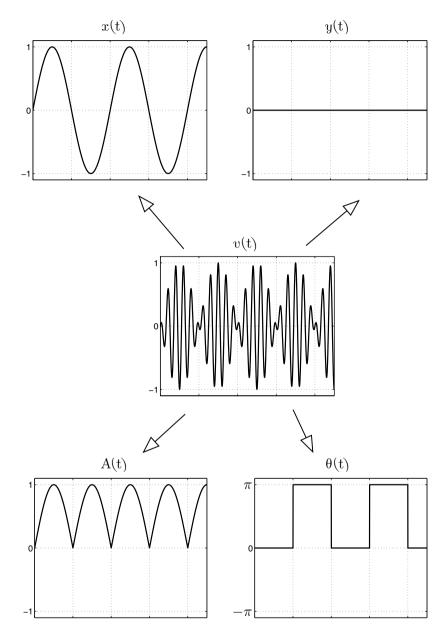

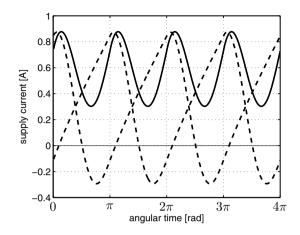

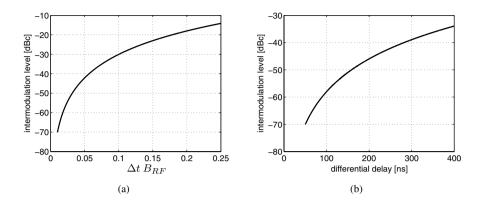

In figure 2.3, the example of a two-tone signal is given. From this signal, the envelope and phase signal can be calculated as

$$v(t) = \sin(\omega_{LF}t)\cos(\omega_{c}t)$$

(2.9)

$$= |\sin(\omega_{LF}t)| \cdot sign [\sin(\omega_{LF}t)] \cdot \cos(\omega_{c}t)$$

(2.10)

$$= |\sin(\omega_{LF}t)| \cos\left(\omega_{c}t + \pi/2 - \pi/2 \cdot s(\omega_{LF}t)\right)$$

(2.11)

$$= A(t)\cos\left(\omega_c t + \theta(t)\right) \tag{2.12}$$

It can easily be seen that

$$A(t) = |\sin(\omega_{LF}t)| \tag{2.13}$$

$$\theta(t) = \pi/2 - \pi/2 \cdot s(\omega_{LF}t) \tag{2.14}$$

$$x(t) = \sin(\omega_{LF}t) \tag{2.15}$$

$$y(t) = 0 \tag{2.16}$$

with  $s(\omega_{LF}t) = sign [\sin(\omega_{LF}t)]$  being a ±1 switching function having the same sign as  $\sin(\omega_{LF}t)$ . To conclude, the envelope signal is a rectified sine wave and the phase signal is a square wave between 0 and  $\pi$ , as indicated by figure 2.3. Therefore, a two-tone signal exhibits both amplitude and phase modulation.

Figure 2.3. Two-tone signal and the corresponding envelope and phase signals.

To summarize, table 2.1 gives an overview of the different signals and their symbols as used throughout this text.

| symbol                           | name                                             |

|----------------------------------|--------------------------------------------------|

| $\overline{v(t)}$                | modulated RF signal                              |

| g(t)                             | complex envelope signal, complex baseband signal |

| A(t)                             | envelope signal, amplitude signal                |

| $\theta(t), P(t)$                | phase signal                                     |

| $e^{j\theta(t)}, e^{jP(t)}$      | complex phase signal                             |

| $v_P(t) = \cos(\omega t + P(t))$ | RF phase signal                                  |

| x(t), I(t)                       | in-phase signal                                  |

| y(t), Q(t)                       | quadrature signal                                |

Table 2.1. nomenclature of modulated signals

# 2.2.2 Digital Modulation

In digital modulation systems, a digital signal, i.e. a time discrete signal with a finite set of amplitudes, is mapped on a finite number of points in the complex plane, and these points are called *constellation points*. The corresponding graph showing all possible constellation points is named a *constellation diagram*.

One should realize that a constellation diagram is only half the story. How the complex envelope moves from one constellation point to another will determine the bandwidth of the transmitted RF signal. The complex envelope will not move instantaneously to another constellation point, as this would require an infinite bandwidth. Rather, the transition from one point to another constellation point is smoothed by applying a baseband filter on both the in-phase signal x(t) and the quadrature signal y(t).

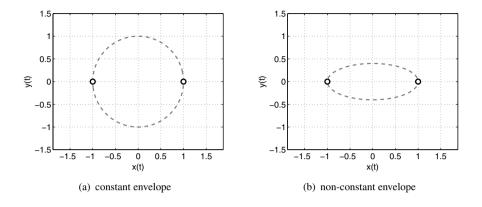

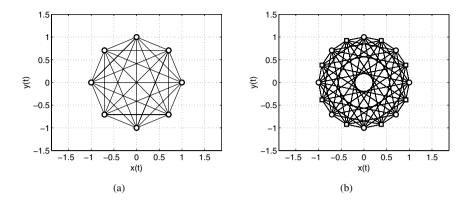

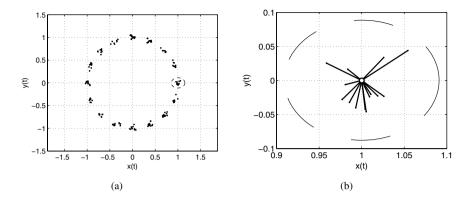

The trajectory from one constellation point to another will also determine the envelope variations of the output RF signal. It will be shown later that these variations have a large impact on the design of the power amplifier. As a first example, consider the case of a Binary Phase Shift Keying (BPSK) constellation diagram, consisting of 2 constellation points. If the trajectory between the two points follows a circle, the amplitude of the complex envelope signal, i.e. the magnitude of the complex vector g(t) and thus the amplitude signal A(t), will not change and the RF output signal that needs to be transmitted has a *constant envelope*. In other words, A(t) does not change in time. This is depicted in figure 2.4(a).

However, the path between the two constellation points of the previous example can be shortened by using an ellipse or a straight line between the two points. If a straight line is chosen, the trajectory would then go through the origin of the complex plane. The length of the complex vector will continuously change and this can be seen as a variation of the amplitude of the RF output

Figure 2.4. BPSK modulation.

signal. The RF signal at the output will have a changing envelope, which is denoted as a *non-constant envelope signal*. In short, A(t) will change in time. This is demonstrated in figure 2.4(b).

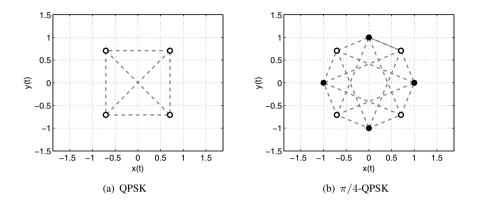

The same holds for Quadrature Phase Shift Keying (QPSK) modulation, depicted in figure 2.5(a). A common technique to reduce the variation of the envelope signal is to use two constellation schemes that are rotated to each other. The trajectory is continuously switching between the two constellation diagrams. As an example, consider the  $\pi/4$ -QPSK of figure 2.5(b). The two QPSK constellation diagrams are rotated 45 degrees to each other. As such, the origin is avoided and the amplitude variations of the complex envelope signal are less severe compared to the QPSK example. Therefore, the amplitude variations of the RF signal that needs to be transmitted will also be less. In other words, the modulation depth of the amplitude modulation is reduced.

It can be concluded that envelope variations of the RF output signal are not only caused by the fact that constellation points are not lying on a circle. The transitions between the constellation points are as important to determine the envelope variations of the RF output signal. Even if the constellation points are lying on a circle, the output RF signal can still have envelope variations.

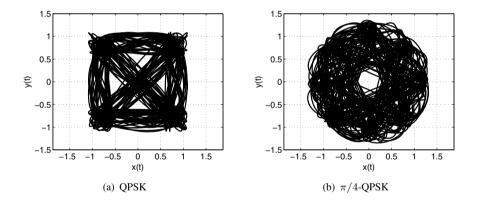

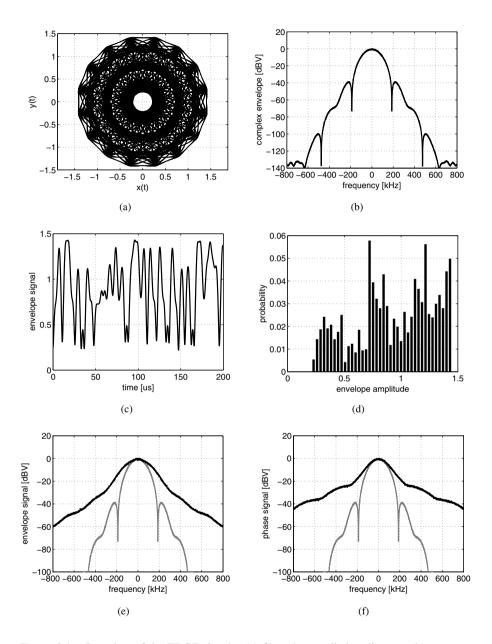

Furthermore, the transitions between the constellation points are filtered by a baseband filter, to limit the bandwidth of the transmitted signal, and this filtering operation will also effect the variation of the envelope signal. As an example, the QPSK and  $\pi/4$ -QPSK modulation schemes of figure 2.5 is filtered by a commonly used root-raised cosine filter with a roll-off of 0.35. Figure 2.6 shows the resulting filtered constellation diagram. Depending on the sequence of the transmitted symbols, the overshoot and undershoot of the

*Figure 2.5.* Unfiltered complex envelope signal for (a) QPSK and (b)  $\pi/4$ -QPSK modulation. The trajectory avoids the origin in  $\pi/4$ -QPSK modulation.

*Figure 2.6.* Filtered complex envelope signal for (a) QPSK and (b)  $\pi/4$ -QPSK modulation. A root-raised cosine baseband filter (r=0.35) has been applied.

baseband filter will add or subtract and thus the dynamic range of the complex signal is increased. Also, the *eye* or opening of the  $\pi/4$ -QPSK modulation around the origin, becomes smaller due to the baseband filtering.

# 2.2.3 Probability Density Function of the Envelope Signal

The location of the constellation points and the transitions or trajectories between these points, will both determine how the transmitted RF signal will look like. Nevertheless, even for the most complex (multi-carrier) modulation scheme, one can still think of it as a carrier that is modulated both in amplitude and phase.

The design of the power amplifier will be constrained by (1) the bandwidth of the phase signal, (2) the bandwidth of the amplitude signal and (3) the variation of the envelope or amplitude signal. If no amplitude modulation is present, one denotes this as a constant envelope signal or system and amplitude linearity is of no concern. As such, the design of the power amplifier is facilitated.

A more complete description of the amplitude modulation of the carrier is given by the *probability density function of the envelope signal (PDF*). It gives the relative amount of time the envelope spends at a certain value. Besides the probability density function, one can also define the *cumulative density function (CDF*). It describes the probability that A(t) is lower than a certain value.

Signals that only use phase or frequency modulation, do not have a varying envelope signal. Therefore, as the envelope is at a constant value, the corresponding probability density function will be a Dirac impulse. It should be stressed that, for RF communication, it is more common to look at the envelope *PDF*. In baseband amplifiers and line drivers, it is more common to look at the *PDF* of the actual output signal.

The envelope PDF is important for the optimization of the amplifier. After all, the PDF tells the designer what signal the amplifier will have to transmit, most of the time. As such, one could optimize the power amplifier in the region where the PDF is high.

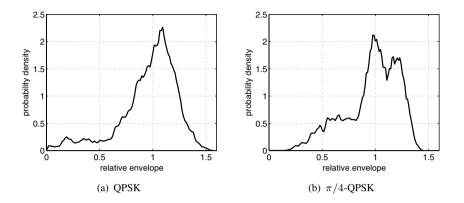

As an example, the QPSK and  $\pi/4$ -QPSK modulation schemes can be used again. The envelope waveform can be obtained from figure 2.6 and the corresponding envelope probability density function is shown in figure 2.7. For QPSK, the envelope has a peak value of 1.58, an average value of 0.96 and an rms value of 1. The crest factor is 3.97 dB. Notice that the envelope for which the probability density is maximum, does not correspond to either the average or rms value of the envelope. For  $\pi/4$ -QPSK, the envelope has a peak value of 1.5, an average value of 0.97 and an rms value of 1. The crest factor is 3.28 dB. As said before, the  $\pi/4$ -QPSK modulation scheme avoids the origin, and this can clearly be seen in the corresponding PDF.

## 2.3 Some Aspects of Power Amplification

# 2.3.1 Output Power

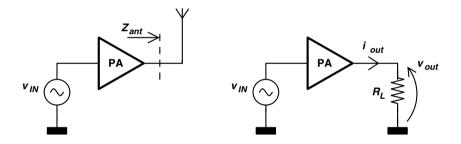

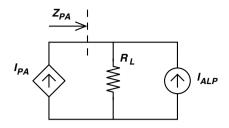

Consider the basic circuit of figure 2.8, which shows a power amplifier connected to an antenna. The output power is defined as the active power, delivered by the power amplifier and flowing into the antenna. Inside the antenna, the power is *dissipated* under the form of a radiated electromagnetic wave. In most cases, the antenna impedance  $Z_{ant}$  is designed to be purely resistive at

*Figure 2.7.* Probability density function of the envelope signal after applying a root-raised cosine baseband filter (r=0.35).

Figure 2.8. Definition of output power.

the frequencies of interest. Therefore, at these frequencies, the antenna can be represented by a single load resistor  $R_L$ . The power dissipated in  $R_L$  (under the form of heat) is, by definition, equal to the power in the electromagnetic wave, transmitted by the antenna.

In RF and Microwave, it is common to *design towards* 50  $\Omega$ . Antennas, antenna filters and other microwave components typically have single-ended input and output impedances of 50  $\Omega$ . However, it will be shown in chapter 4 that it is possible to convert the 50  $\Omega$  antenna impedance to a lower or higher value. Therefore, it is assumed for now that  $R_L$  can virtually have any desired value.

The instantaneous output power is defined as

$$p_o(t) = v_{out}(t) \cdot i_{out}(t) \tag{2.17}$$

The *total* or *average* output power  $P_{o,tot}$  is defined as

$$P_{o,tot} = \langle p_o(t) \rangle = \lim_{T \to \infty} \frac{1}{T} \int_{-T/2}^{T/2} p_o(t) dt$$

(2.18)

with  $\langle \cdot \rangle$  the time average operator. If the output voltage is a sine wave with frequency  $f_c$  en period  $T_c$ , previous equation simplifies to

$$P_{o,tot} = \langle p_o(t) \rangle = \frac{1}{T_c} \int_{-T_c/2}^{T_c/2} p_o(t) dt$$

(2.19)

Under the assumption of a resistive load,

$$P_{o,tot} = \langle v_{out}(t) \cdot i_{out}(t) \rangle = \frac{\langle v_{out}^2(t) \rangle}{R_L}$$

(2.20)

$$= \frac{V_{o,rms}^2}{R_L} \tag{2.21}$$

with

$$V_{o,rms} = \sqrt{\langle v_{out}^2(t) \rangle}$$

(2.22)

the well known RMS value of the output voltage.

Although trivial at first sight, these basic textbook definitions are not always as useful for a power amplifier. The amplifier will not only generate power at the frequency of interest, but also at integer multiples of the fundamental frequency  $f_c$ . In most cases, only the power at the fundamental frequency is wanted and the harmonic power has to be filtered or suppressed at the output. Therefore, it is more useful to define a *fundamental average output power*,  $P_{o,f_c}$ , equal to the output power at the fundamental frequency only

$$P_{o,f_c} = \frac{V_o^2}{2R_L}$$

(2.23)

with  $V_o$  the amplitude or peak value of the sinusoidal output voltage at frequency  $f_c$ . This value can be obtained from a Fourier Series expansion of  $v_{out}(t)$ .

Throughout this text, the general term *output power*, denoted as  $P_o$ , will be used to indicate the average output power at the fundamental frequency. Thus,

$$P_o = P_{o,f_c} \tag{2.24}$$

# 2.3.2 Peak Output Power and Crest Factor

For modulated signals, the profile of the envelope or amplitude signal A(t) becomes important. One can proof that the average output power of a bandpass

modulated signal is given by [Couc97]

$$P_{o} = \frac{\left\langle |g(t)|^{2} \right\rangle}{2R_{L}} = \frac{\left\langle A^{2}(t) \right\rangle}{2R_{L}} = \frac{\left(A_{rms}\right)^{2}}{2R_{L}}$$

(2.25)

If the output RF signal is only phase modulated, the output power is the same as if the signal was not modulated at all. Hence, for constant envelope systems, the presence of the modulation will not change the output power.

Clearly, the average output power will be dependent on the behavior of the envelope signal. One could define a *fixed envelope output power*  $P_o(A)$  as the average output power, dissipated in the load, if the envelope or amplitude signal is kept constant at a specific value A

$$P_o(A) = \frac{A^2}{2R_L} \tag{2.26}$$

which is basically the same as definition 2.23.

One can also define the *peak envelope output power*, *PEP*. It is the power, dissipated in the load, if the envelope or amplitude signal is kept at its maximum value [Couc97].

$$PEP = \max\left\{P_o(A(t))\right\} = \frac{\left(\max\left\{A(t)\right\}\right)^2}{2R_L} = \frac{A_{max}^2}{2R_L}$$

(2.27)

The peak output power value is of great importance in PA design since the amplifier must be designed to transmit these high peaks. However, the average output power can be much lower than the peak output power.

In this regard, an important parameter is the *Peak to Average Power Ratio*, *PAPR*, defined as

$$PAPR = \frac{PEP}{P_o} \tag{2.28}$$

The peak to average ratio can also be calculated based on voltages. This is expressed by the *Crest Factor* (CF), defined as the ratio of the peak value to the rms value of the RF output voltage.

$$CF = \frac{V_{o,max}}{V_{o,rms}} = \frac{A_{max}}{A_{rms}}$$

(2.29)

Note that

$$PAPR = CF^2 \tag{2.30}$$

A signal with a high *PAPR*, will require a lot of headroom for the power amplifier. Most of the time, the amplifier will operate at a relatively low output power level, but from time to time, the power amplifier has to be able to transmit relatively large power peaks. This time-domain behavior of the power

amplifier is determined by the characteristics of the RF signal that needs to be transmitted. One such characteristic is the probability density function of the envelope signal, as already discussed in section 2.2.3. For systems with only phase modulation, the peak output power will be the same as the average output power, since the envelope signal A(t) is a constant and equal to  $V_{o,max}$ . Therefore, the *PAPR* and *CF* will both be equal to 1 and thus 0 dB.

In the general case where multiple tones or carriers are present, the average output power of the combined signal will be [Krau80]

$$P_o = P_{o,1} + P_{o,2} + \ldots + P_{o,k}$$

(2.31)

$$= \frac{1}{2R_L} \left( A_1^2 + A_2^2 + \ldots + A_k^2 \right)$$

(2.32)

with  $P_{o,i}$  the average output power of the *i*-th carrier and  $A_i$  the amplitude of the *i*-th carrier. If it is assumed that all carriers are independent from each other, they will at some point in time simultaneously reach their positive maximum values, resulting in a peak envelope output power of

$$PEP = \frac{1}{2R_L} \left( A_1 + A_2 + \ldots + A_k \right)^2$$

(2.33)

Furthermore, if all carriers have the same amplitude A

$$P_o = \frac{kA^2}{2R_L} \tag{2.34}$$

$$PEP = \frac{(kA)^2}{2R_L} \tag{2.35}$$

and thus

$$PAPR = \frac{PEP}{P_o} = k \tag{2.36}$$

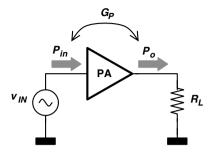

### 2.3.3 Input Power and Power Gain

In order to drive the power amplifier, a certain amount of RF input power is required. An oscillator can be regarded as an exception to this, since it only requires DC input power.

The power gain, usually expressed in dB, is defined as

$$G_{P,dB} = 10\log_{10}\left(\frac{P_o}{P_{in}}\right) \tag{2.37}$$

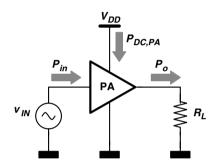

#### 2.3.4 Efficiency

An *efficient* power amplifier aims to deliver a certain amount of power to the load, without consuming too much power itself. The DC power consumption,

Figure 2.9. Definition of input power and power gain.

Figure 2.10. Definition of DC power consumption.

$P_{DC,PA}$  in figure 2.10, will always be larger than  $P_o$ . The *drain* or *collector* efficiency  $\eta_d$  is defined as

$$\eta_d = \frac{P_o}{P_{DC,PA}} \tag{2.38}$$

Equation 2.38 can also be regarded as a *fundamental* efficiency, since it only takes into account the output power at the fundamental frequency.

One can also define a *conversion* efficiency  $\eta_{conv}$  which is the ratio of the total RF output power to the DC power consumption of the amplifier.

$$\eta_{conv} = \frac{P_{o,tot}}{P_{DC,PA}} \tag{2.39}$$

$P_{o,tot}$  includes the fundamental output power  $P_o$  as well as the (unwanted) output power at the higher harmonics. Therefore,  $\eta_{conv}$  can be regarded as an indication how well DC power is converted to RF power, hence the name conversion efficiency.

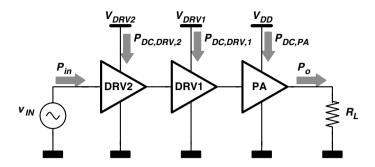

In almost any transmitter chain, several driver stages are required between the signal source or upconversion mixer and the last amplifier stage. These driver stages will also consume DC power, but it is not as easy to define input and output power, since the impedance levels at the input and output of each stage will be different and will normally be composed of both a real and complex part. Taking the DC power consumption of the driver stages into account, the *overall efficiency* of the power amplifier can be defined as [Raab02]

$$\eta_{oa} = \frac{P_o}{P_{DC,PA} + \sum_{i=0}^{n} P_{DC,DRV,i}}$$

(2.40)

The more driver stages are added, the higher the power gain of the entire amplifier, but the lower the overall efficiency  $\eta_{oa}$ .

The Power Added Efficiency (PAE ) takes into account the RF input power  $P_{in}$  and it is defined as

$$PAE = \frac{P_o - P_{in}}{P_{DC,PA} + \sum_{i=0}^{n} P_{DC,DRV,i}}$$

(2.41)

By using equation 2.37, the PAE can be rewritten as

$$PAE = \eta_{oa} \left( 1 - \frac{P_{in}}{P_o} \right) = \eta_{oa} \left( 1 - \frac{1}{G_P} \right)$$

(2.42)

However, some authors define the PAE as

$$PAE = \frac{P_o - P_{in}}{P_{DC,PA}} = \eta_d \left( 1 - \frac{1}{G_P} \right)$$

(2.43)

which clearly results in a better performance. Anyhow, if the gain is sufficiently high, the *PAE* defined in equation 2.41 becomes equal to the overall efficiency.

The drain efficiency of an amplifier can, at least in theory, reach 100%. However, the overall efficiency will always be smaller than 100%, even in the ideal case. The reason is clear; the power that is consumed by the driver stages will not flow to the output but is dissipated at the input of the next stage in line. As such, even if the power amplifier and the driver stages operate at a drain efficiency of 100%, the overall efficiency will not be 100%, simply because of the definition of overall efficiency.

The question remains which definition of efficiency to use. From a circuit level point of view, drain efficiency and *PAE* seems the best, especially if for a stand-alone power amplifier with an input matched to  $50 \Omega$ . From a system point of view and for a system designer, the PA is *everything after the up-converter*. Therefore, the overall efficiency  $\eta_{oa}$  is a better indication of how

Figure 2.11. Definition of DC power consumption, including driver stages.

much power is needed to amplify the signal, relatively to the output power itself. Of course, one could argue if the power consumption of the DSP and other digital and analog block shouldn't be included as well. After all, these blocks, just like the driver stages, are also required to modulate and transmit a signal. This, however, would lead us to definitions that have little to do with *conversion* of DC power to an electromagnetic wave, but rather with *consumption* of energy to transmit information.

# 2.3.5 Efficiency and Modulated Signals

Regardless of what type of modulation is used, the definition of drain efficiency is still equal to the average output power divided by the average DC power consumption.

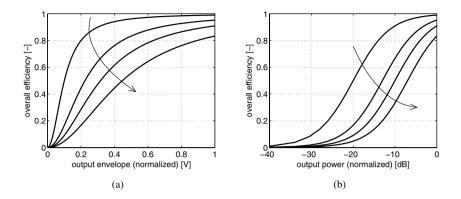

However, in almost any power amplifier, drain efficiency and output power are closely related to each other. In section 2.3.2, the fixed envelope output power was defined as the average output power, if the envelope signal is kept constant at a specific value A.

$$P_o(A) = \frac{A^2}{2R_L} \tag{2.44}$$

With this envelope output power, one can define a drain efficiency for a specific constant envelope signal. In other words, the drain efficiency is made dependent on the envelope signal and one can define a *fixed envelope drain efficiency* as.

$$\eta_d(A) = \frac{P_o(A)}{P_{DC,PA}(A)} \tag{2.45}$$

If the envelope signal changes in time, the fixed envelope efficiency will also change. The average efficiency can now be interpreted as the time average of the fixed envelope efficiency.

$$\eta_d = \langle \eta_d(A(t)) \rangle = \lim_{T \to \infty} \frac{1}{T} \int_{-T/2}^{T/2} \eta_d(A(t)) dt$$

(2.46)

The calculation of the average efficiency can also be done, based on the envelope probability density function. This does not require knowledge of the the time behavior of the envelope signal. Only the probability density function is required.

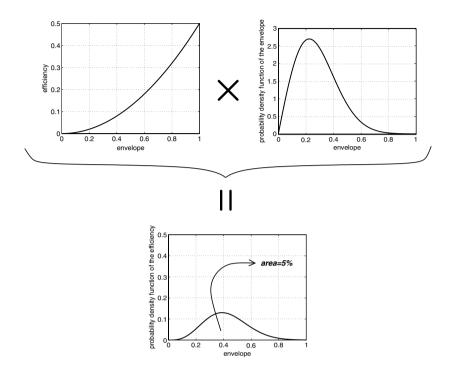

$$\eta_d = \int_0^{A_{max}} \eta_d(A) \cdot p(A) \cdot dA \tag{2.47}$$

The product  $\eta_d(A) \cdot p(A)$  can be seen as the *probability density function of the drain efficiency*.

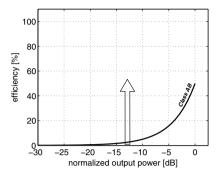

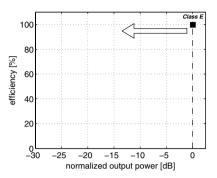

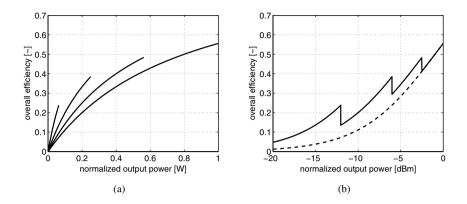

For the Class A power amplifier (see section 2.4.1), the relationship between efficiency and envelope signal is given by

$$\eta_d = \frac{P_o}{P_{DC,PA}} = \frac{1}{2} \cdot \left(\frac{A}{V_{DD}}\right)^2 \qquad A = [0 \dots V_{DD}] \tag{2.48}$$

If the supply voltage  $V_{DD}$  is normalized ( $V_{DD} = 1 \text{ V}$ ), the relationship becomes

$$\eta_d = \frac{A^2}{2} \qquad A = [0\dots 1]$$

(2.49)

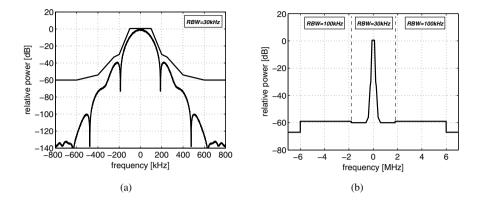

which reveals a quadratic dependency of  $\eta_d$  on the amplitude of the output signal A. Figure 2.12 shows the calculation of the efficiency, based on equation 2.47. The efficiency versus envelope curve is first multiplied with the envelope probability density function. The resulting graph is then integrated to obtain the average efficiency of the amplifier.

#### 2.3.6 **Power Control**

Most wireless systems utilize some form of power control to either avoid interference with other users or to conserve battery power. After all, it is of no use to transmit more power than actually needed to preserve a communication link. Normally the highest output power levels are only needed in a worst-case scenario. In the case of wireless telephony, this may occur when the mobile station is distant from the nearest base station. Other factors are: attenuation by buildings, multi path fading and orientation of the mobile antenna. In modern systems, the average output power is constantly adopted to the lowest possible level in order to increase the battery lifetime. This variation of the average output power can also be interpreted as an amplitude modulation and thus as a variation of the envelope signal A(t).

It should be stressed that power control is also strongly related to the actual system. In CDMA systems [Sahu04], all users transmit at the same time, at the same frequency. This may cause a so called near-far problem if no

*Figure 2.12.* Calculation of the efficiency, based on the probability density profile of the envelope and the efficiency versus envelope curve of the amplifier.

precautions are taken. At the base station, the signal of a distant user will arrive at a much lower power level compared to nearby users. As such, nearby users may *overpower* the weak signal of a distant user, since both signals occur at the same time and at the same frequency. For a maximum capacity in a CDMA system, power control is crucial and the system will try to make the received level of each user equal at the base station. Consequently, the power control in each mobile terminal needs to be accurate and adjusted frequently. In systems that employ TDMA or FDMA, each user either transmits in another time slot or on another frequency. For these systems, power control is not crucial for maximum capacity and it is mainly used to increase the battery lifetime of the mobile terminal.

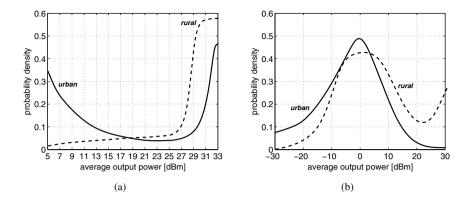

Based on actual measurements, a probability density function of the average output power can be obtained. Such a function will heavily depend on both the environment and the system in use. For a TDMA and FDMA system in a rural environment, the average output power will be fairly constant and only dependent on the distance to the base station. Base station density is rather low in rural areas, and therefore, the mobile terminal will operate at higher output

*Figure 2.13.* Examples of a probability density function of the average output power for (a) TDMA/FDMA and (b) CDMA.

power levels. In an urban environment, the attenuation can raise to very high peaks, as buildings may create a strong shading of the antenna. Such strong attenuation peaks will raise the output power towards its peak levels. On the other hand, the base station density is much higher in urban environment than in a rural environment. This will enable the mobile terminal to operate at lower power levels from time to time. For CDMA, similar observations can be made. From these qualitative descriptions, the probability density function of the average output power could have a profile as illustrated in figures 2.13(a) and 2.13(b) [Hani99], [Raab02] and [Sahu04].

The time-variant behavior of the envelope signal will thus have two causes, (1) amplitude modulation of the carrier and (2) the variation of the output power due to power control. From this point of view, a *long-term average efficiency* could be defined that takes into account the variation of A(t) due to power control. However, calculating such a long-term average efficiency requires accurate knowledge of the environment and the behavior of the user, which will be difficult to predict.

#### 2.3.7 Linearity

Linearity of a power amplifier can be defined in two ways: phase linearity and amplitude linearity. Phase linearity is easy to achieve as long as the bandwidth of the modulated signal is small compared to the carrier frequency. Phase nonlinearity or phase distortion is denoted as PM-PM distortion. Amplitude linearity is harder to achieve, and in general results in a lower efficiency as will become clear in section 2.4. Amplitude nonlinearity or amplitude distortion is denoted as AM-AM distortion. In this regard, constant envelope systems, like GSM and Bluetooth, have an efficiency advantage. The amplifier only needs to have phase linearity and amplitude linearity is of no concern. Recent years have shown that most new communication systems (EDGE, W-CDMA, W-LAN) have varying envelope signals. To amplify these signals correctly, the power amplifier must thus have sufficient amplitude linearity.

The varying envelope of the RF signal may also induce phase errors, indicated as AM-PM. Likewise, PM-AM are amplitude or envelope errors caused by the phase or frequency modulation of the carrier. AM-AM, AM-PM, ... are in fact a DC approximation of the power amplifier nonlinearity. In reality, the distortion curves are not fixed but can change slowly due to temperature changes or other environmental effects. This is denoted as memory-effects.

Different means exist to quantify the linearity of a power amplifier. The third order intercept point (IP3) is a well known characteristic of low noise amplifiers and mixers [Crip99]. It is based on a two-tone signal test and gives the (virtual) output power for which the third order intermodulation term becomes as large as the actual output power. Modern communication systems create highly complex signals and the relative simple IP3 measurement is often not suited as a good indicator for the required linearity. Furthermore, communication standards do not specify the required IP3 of the transmitter but rather, terms like *spectral mask*, *error vector* and *adjacent channel power* are used.

The distortion of RF power amplifiers and the linearity requirements will be further discussed in chapters 5, 6 and 7.

### 2.3.8 Inductors, Capacitors and Quality Factor

As inductors and capacitors play a crucial role in RF amplification, some basic metrics are briefly reviewed in this section.

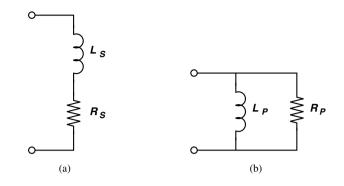

#### 2.3.8.1 Un-tuned Network

In reality, inductors and capacitors are never ideal. They always exhibit some loss, which can be modeled by adding a resistance either in series or parallel.

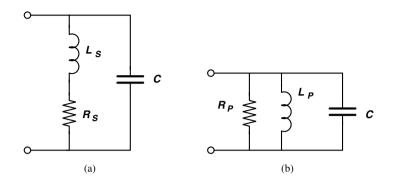

Figure 2.14(a) shows the very basic circuit of an inductor with a series resistance. One can define a quality factor of this little circuit as being the ratio of the average reactive power to the average power dissipated in the resistor. For the circuit of figure 2.14(a), this becomes

$$Q = \frac{X_S}{R_S} = \frac{\omega L_S}{R_S} \tag{2.50}$$

For a capacitor with a series resistance, the formula becomes

$$Q = \frac{X_S}{R_S} = \frac{1}{\omega C_S R_S} \tag{2.51}$$

Figure 2.14. Inductor with loss. (a) Series model and (b) parallel model.

This little circuit can be converted in a parallel network, as given by figure 2.14(b). The quality factor of the parallel network can be calculated as

$$Q = \frac{R_P}{X_P} = \frac{R_P}{\omega L_P} \tag{2.52}$$

For a capacitor with a parallel resistance, the formula becomes

$$Q = \frac{R_P}{X_P} = R_P \,\omega C_P \tag{2.53}$$

The series and parallel representation are equivalent to each other. A relationship between  $L_S$ ,  $L_P$ ,  $R_S$  and  $R_P$  can easily be obtained by calculating the impedance of both networks and equalizing the real and imaginary part. This results in following equivalences:

$$L_P = L_S \left( 1 + \frac{1}{Q^2} \right) \approx L_S \tag{2.54}$$

$$R_P = R_S \left( 1 + Q^2 \right) \tag{2.55}$$

Equivalent formulas can be obtained for a capacitance

$$C_P = C_S \left(\frac{1}{1+1/Q^2}\right) \approx C_S \tag{2.56}$$

$$R_P = R_S \left( 1 + Q^2 \right) \tag{2.57}$$

#### 2.3.8.2 Tuned Network

Figure 2.15 depicts a tuned RLC network with losses. In most cases, the quality factor of a capacitor will be much higher than the quality factor of an

Figure 2.15. RLC network with inductor loss.

inductor. Therefore the quality factor of the entire network will mainly be determined by the quality factor of the inductor alone.

For figure 2.15(b), the resonance frequency will be equal to

$$\omega_0 = \frac{1}{\sqrt{L_P C}} \tag{2.58}$$

and the quality factor of that circuit becomes

$$Q(\omega_0) = R_P \sqrt{\frac{C}{L_P}}$$

(2.59)

The circuit of figure 2.15(a) has the same resonance frequency since both circuits are electrically equivalent. After some calculations, one can find that

$$\omega_0 = \frac{1}{\sqrt{L_P C}} = \sqrt{\frac{1}{L_S C} - \frac{R_S^2}{L_S^2}} \approx \frac{1}{\sqrt{L_S C}}$$

(2.60)

and therefore

$$Q(\omega_0) \approx \frac{1}{R_S} \sqrt{\frac{L_S}{C}}$$

(2.61)

If, in a first order approximation and at a fixed frequency, the series resistance is assumed to be proportional to the value of the series inductance, i.e.

$$R_S = \alpha L_S \tag{2.62}$$

then, the impedance of the tuned network at the resonance frequency  $\omega_0$  will become purely resistive and equal to  $R_P$

$$R_P = R_S(1+Q^2) \approx R_S Q^2 \approx \frac{1}{\alpha C}$$

(2.63)

From previous equation it can be seen that, although the capacitor is *tuned* by the inductor, the higher the capacitance, the lower the equivalent resistance seen at the (same) resonant frequency.

## 2.4 Power Amplifier Classification

Power Amplifiers are traditionally divided in several classes, depending on how the transistor is driven and the harmonic content or time behavior of the drain voltage [Crip99]. This classification dates back from the early days of electronics, during the glory days of triode and pentode tubes. Although most real-world solid-state amplifiers are situated in between the different classes, a strict classification allows to obtain a better view on the tradeoff between output power, gain, efficiency and linearity.

For wireless communication, the most important distinction is that between linear and nonlinear amplifiers. The latter refers to a power amplifier that only has phase linearity but no amplitude linearity. The main motivation for using a nonlinear amplifier, is the higher efficiency that can be achieved. The nonlinear behavior doesn't necessarily has to be a drawback. A lot of wireless systems and standards use only phase modulation and the corresponding RF waveforms do not have amplitude variations. As a consequence, the power amplifier only needs to have phase linearity and the amplitude linearity is of no concern.

As this work is focused on CMOS, MOS transistors and their formulas will be used. But of course, the classification is independent of technology.

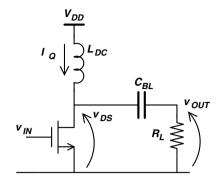

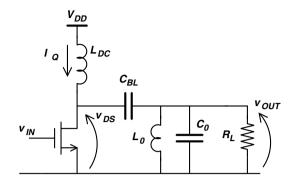

### 2.4.1 Class A

Figure 2.16 show the simplest circuit that can operate as a Class A amplifier, using an nMOS transistor. At the gate, a DC bias voltage ensures that a quiescent current  $I_Q$  is flowing through the transistor and inductor  $L_{DC}$ . A DC-blocking capacitor  $C_{BL}$  ensures that no DC current is flowing through the load resistor  $R_L$ .

The main requirement for Class A operation, is that the transistor conducts current all the time. The maximal output voltage, equal to  $V_{DD}$ , occurs when the transistor drain current almost goes to zero. The minimal output voltage is equal to  $V_{DD} - I_Q R_L$ . The output swing is thus maximized if the quiescent current through the transistor is chosen equal to  $V_{DD}/R_L$ .

If the AC input signal is a sine wave, the output voltage will also be a sine wave. and the output power will be equal to

$$P_o = \frac{V_o^2}{2R_L} \tag{2.64}$$

with  $V_o$  the amplitude or peak value of the sinusoidal output voltage  $v_o(t)$ . The maximum amplitude of the output voltage is equal to  $V_{DD}$ . The power

Figure 2.16. Simplified circuit of a Class A power amplifier.

delivered by the DC voltage source is equal to

$$P_{DC} = I_Q \cdot V_{DD} = \frac{V_{DD}^2}{R_L} \tag{2.65}$$

where it is assumed that the quiescent current  $I_Q$  is chosen equal to  $V_{DD}/R_L$ From these equations, the well known formula for the efficiency of the Class A power amplifier can be obtained.

$$\eta = \frac{P_o}{P_{DC}} = \frac{1}{2} \cdot \left(\frac{V_o}{V_{DD}}\right)^2 \tag{2.66}$$

Above equation reveals the quadratic dependency of the efficiency on the output voltage amplitude  $V_o$  and the maximum sinusoidal efficiency of 50 %.

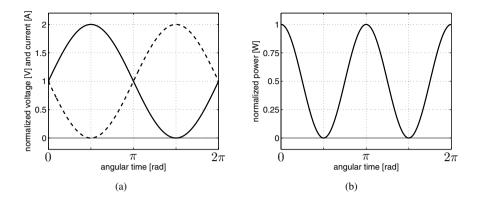

If the Class A power amplifier is *normalized*, i.e.  $V_{DD} = 1$  V and  $R_L = 1 \Omega$ , the maximum normalized output power is equal to 0.5 W, the maximum drain-source voltage becomes 2 V and the maximum drain-source current is 2 A. Although trivial, the normalized voltage and current waveforms and the normalized power dissipation in the transistor are shown in figure 2.17 for completeness.

Some authors also define an output power capability as

$$C_P = \frac{P_o}{v_{DS,max} \cdot i_{DS,max}} \tag{2.67}$$

It originates from the fact that discrete power transistors are one of the most expensive components of a transmitter. This means that the devices have to be used as close as possible to their maximum voltage and current ratings. For CMOS, the main restriction is the breakdown voltage of the transistor, rather than the current limits of the technology. In this regard, one can define a

*Figure 2.17.* (a) Normalized drain voltage and drain current (dashed line) and (b) normalized power dissipation for a Class A power amplifier.

maximum output power, related to the maximum drain-source voltage as

$$P_{o,max} = \frac{1}{8} \cdot \frac{v_{DS,max}^2}{R_L} = 0.125 \cdot \frac{v_{DS,max}^2}{R_L}$$

(2.68)

The fact that the nMOS transistor of a Class A amplifier will continuously conduct current, has a large influence on the reliability and this will be discussed in section 2.4.8.

It should be stressed that the 50 % efficiency of the Class A amplifier only occurs at the maximum (idealized) output swing. If an amplitude modulated signal is applied, the amplitude of the RF sinewave at the output  $V_o$  will change according to the envelope signal A(t). Depending on the probability density function of A(t), the average efficiency will be much lower (see section 2.3.5).

Furthermore, the assumption of a maximal amplitude of  $V_{DD}$  will no longer hold if the *knee*-region<sup>1</sup> of the transistor is taken into account. For an nMOST, the drain-source voltage should remain higher than  $V_{GS} - V_{th}$  as the transistor would otherwise be over-driven and no longer behave as a current source<sup>2</sup>. As an example, consider a  $0.18 \,\mu\text{m}$  CMOS technology. The supply voltage is chosen to be 0.9 V, which makes the maximal drain voltage equal to 1.8 V. If a  $V_{GS} - V_{th}$  of 200 mV is chosen, the output voltage will have a maximum amplitude of 700 mV and the maximum efficiency will only be 30 %, not taking into account the power loss of the inductor. Thus, it is necessary to reduce

<sup>&</sup>lt;sup>1</sup>which is the linear region for a MOST and the saturated region for a BJT.

<sup>&</sup>lt;sup>2</sup>in section 2.4.3, the Class A amplifier is revisited under overdrive conditions.

Figure 2.18. Simplified circuit for reduced conduction angle operation.

the value of  $V_{GS} - V_{th}$ . In a (very) first order approximation,

$$I_{DS} = K \frac{W_g}{L_g} \left( V_{GS} - V_{th} \right)^2$$

(2.69)

and thus for a given current,

$$(V_{GS} - V_{th}) \sim \frac{1}{\sqrt{W_g}} \tag{2.70}$$

$$g_m \sim \sqrt{W_g}$$

(2.71)

$$C_{gs} \sim W_g$$

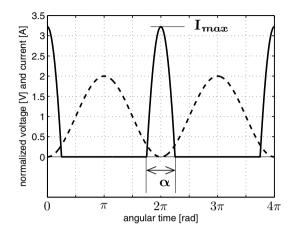

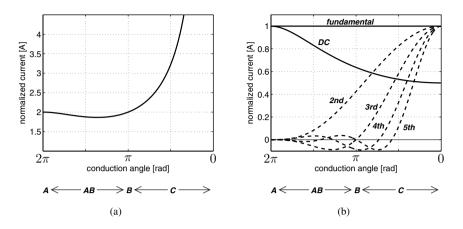

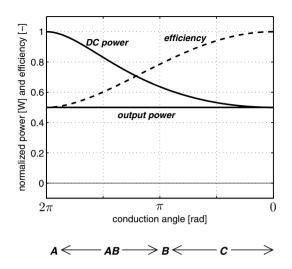

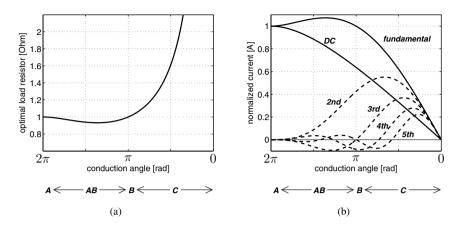

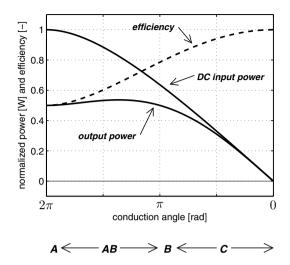

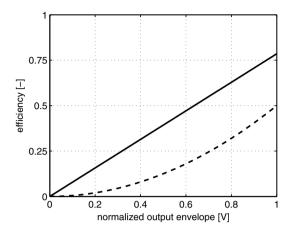

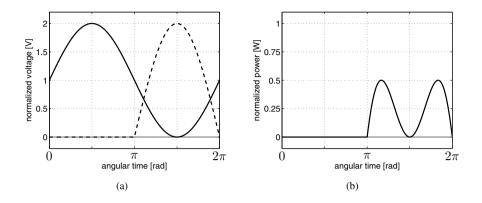

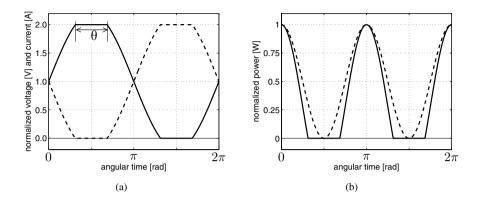

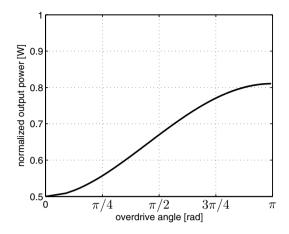

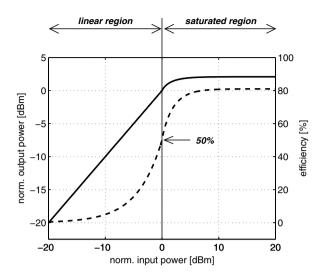

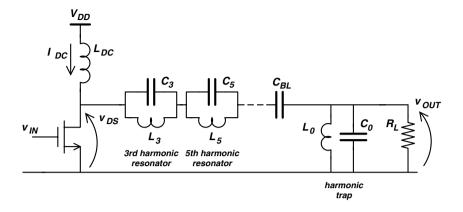

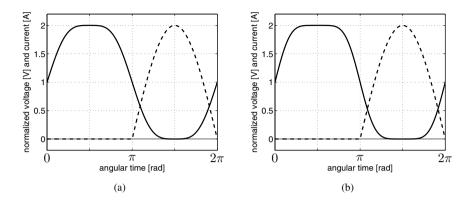

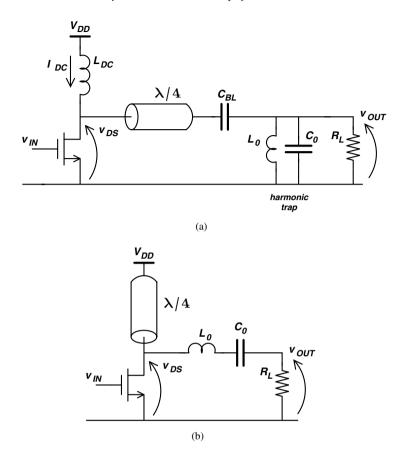

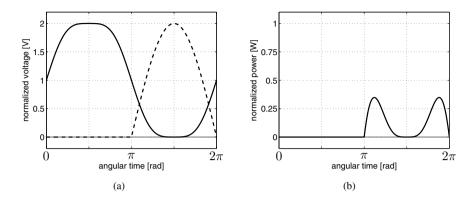

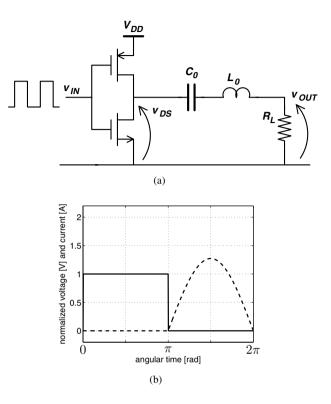

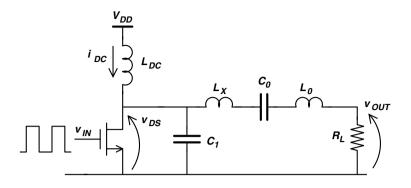

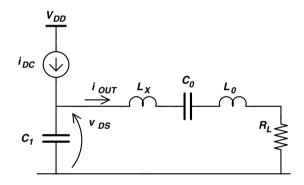

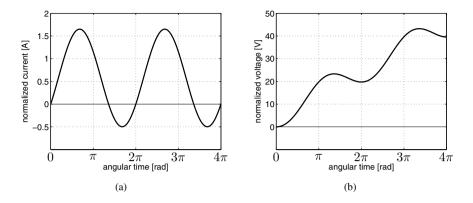

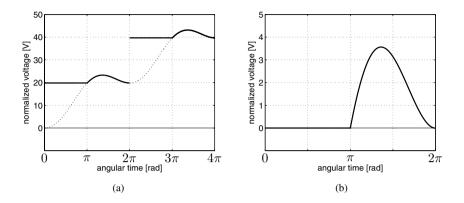

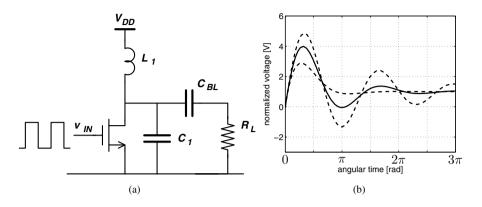

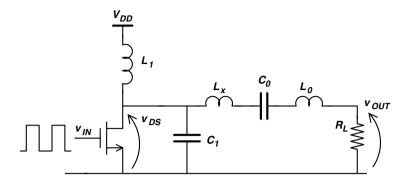

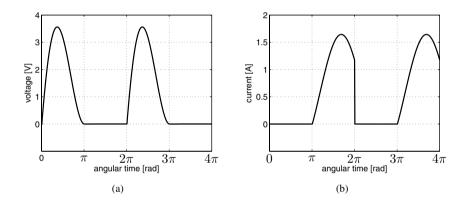

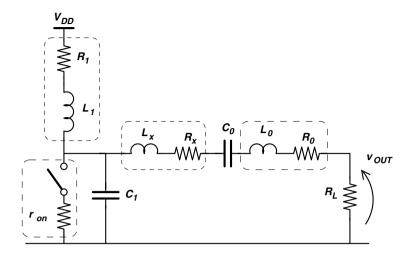

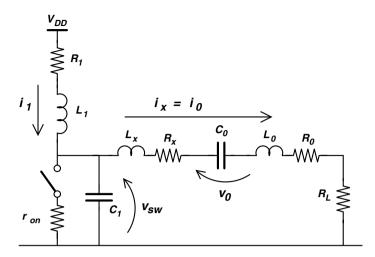

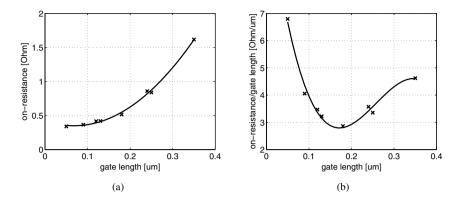

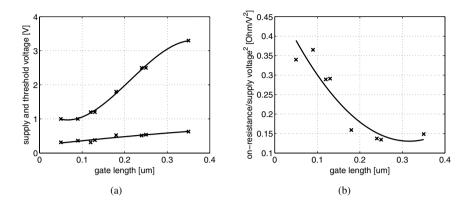

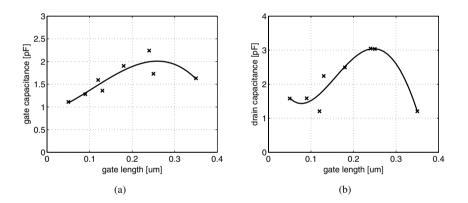

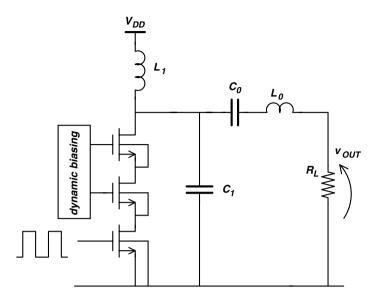

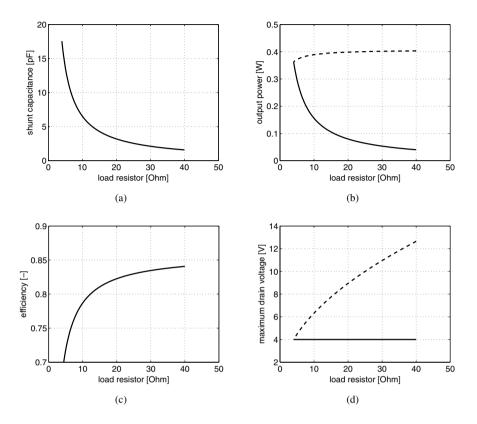

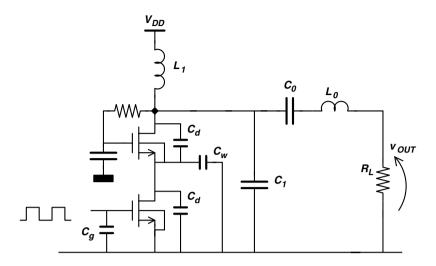

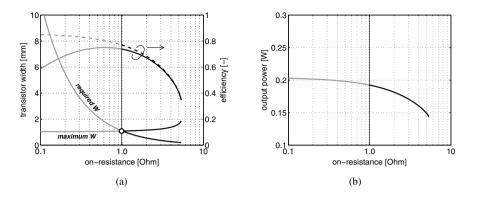

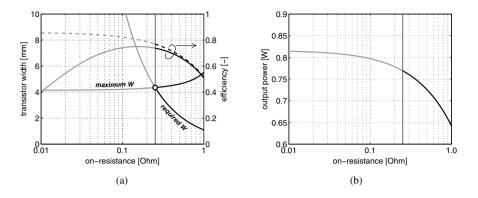

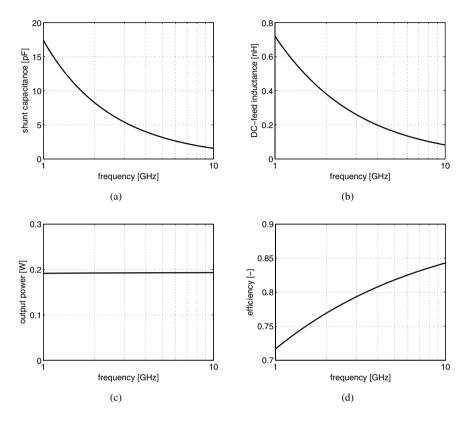

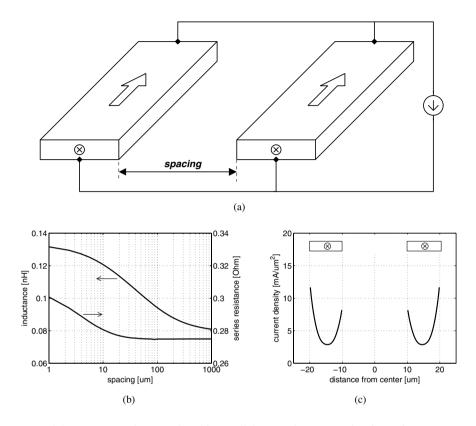

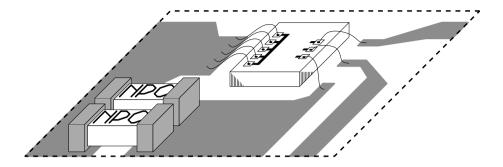

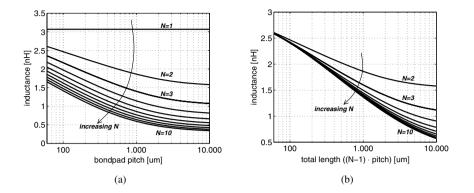

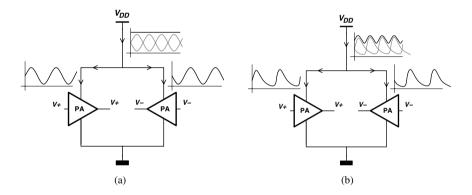

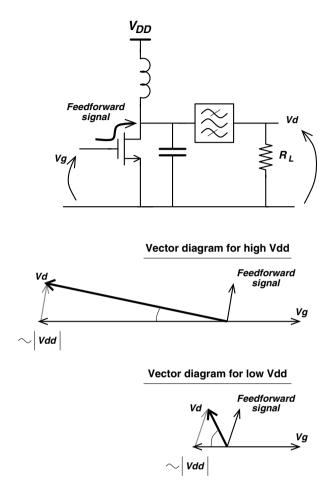

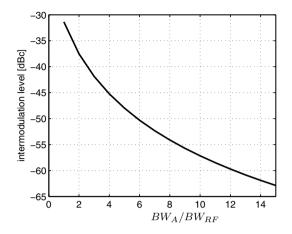

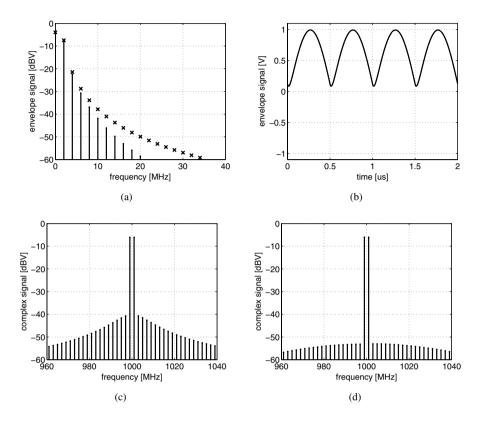

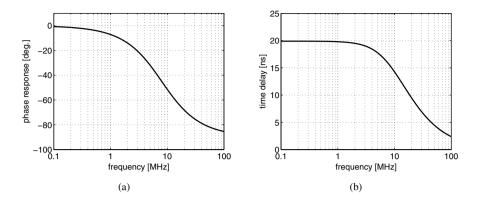

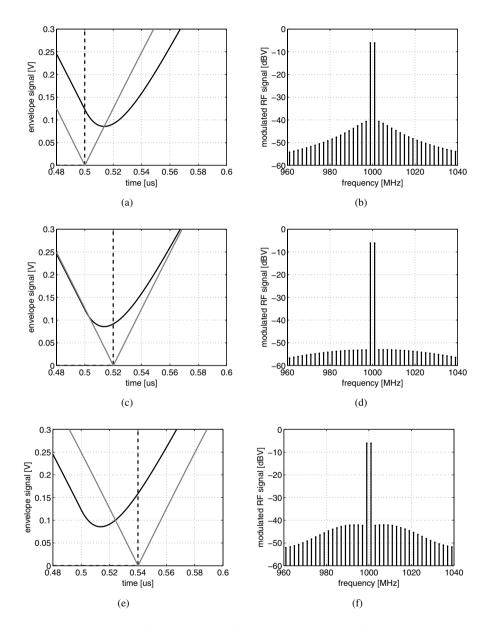

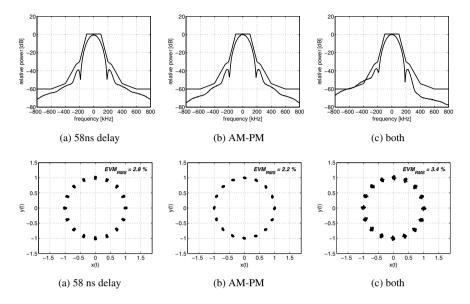

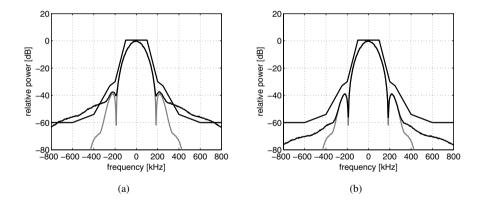

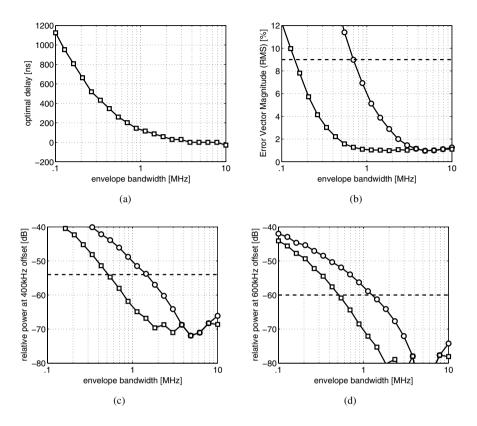

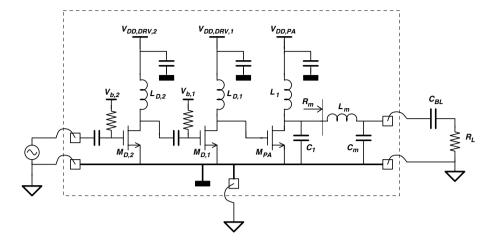

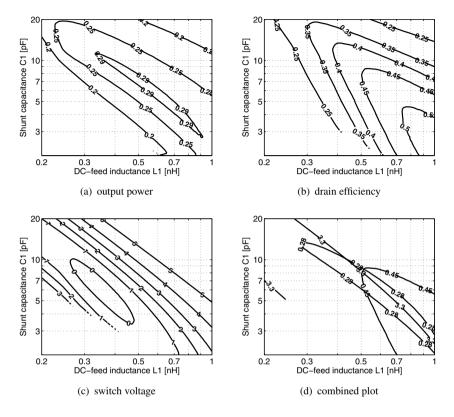

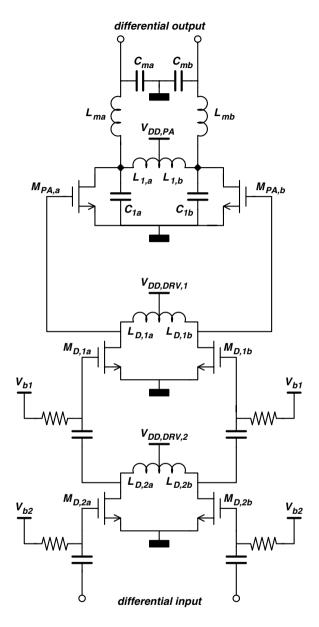

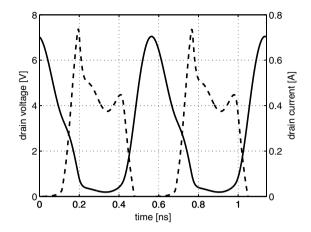

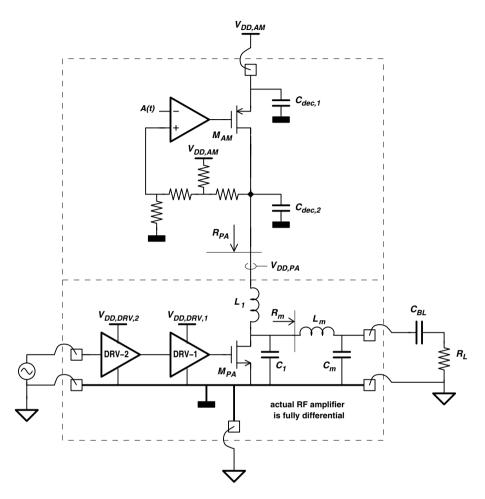

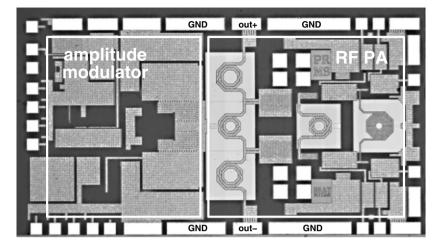

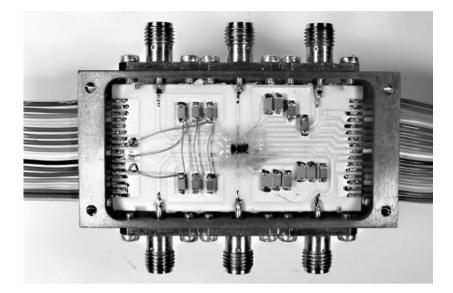

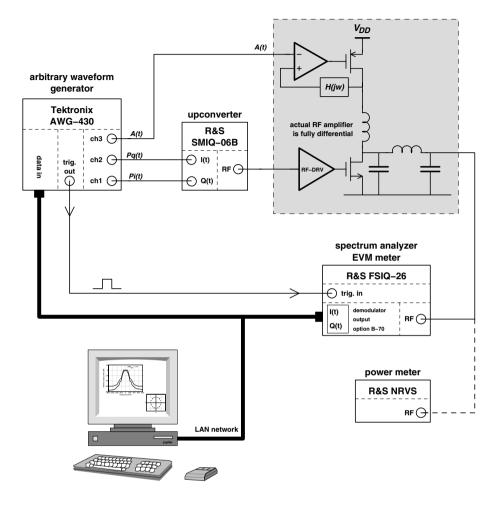

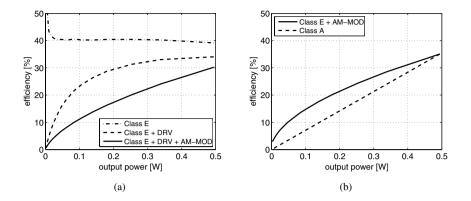

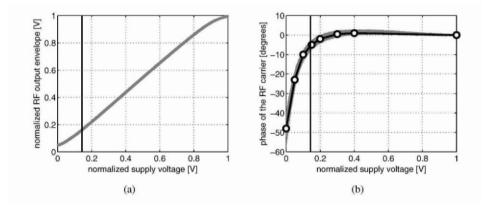

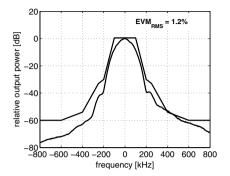

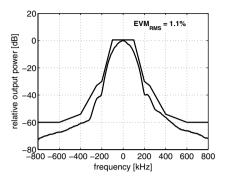

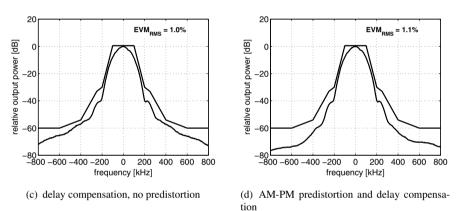

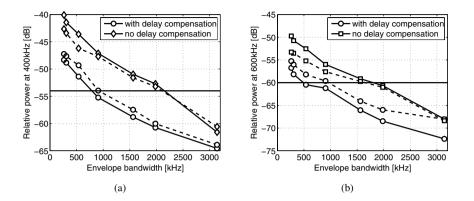

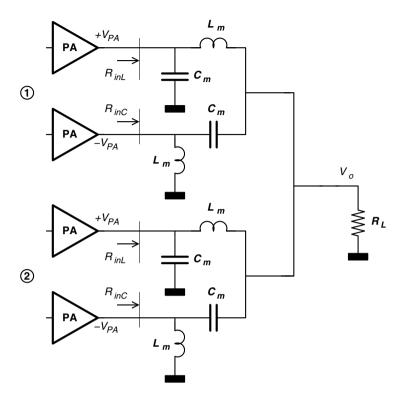

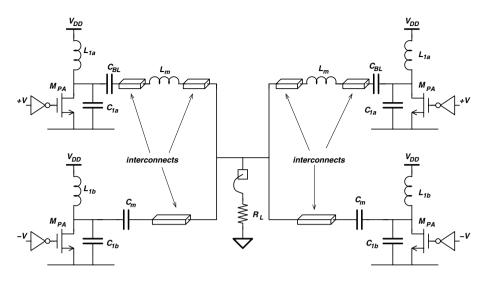

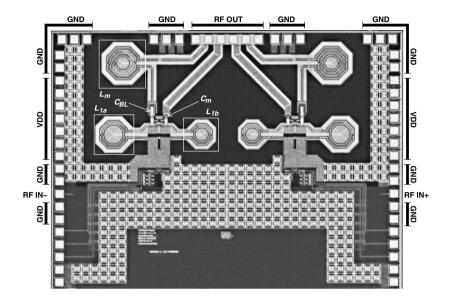

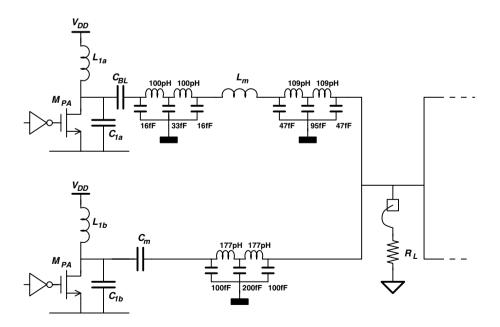

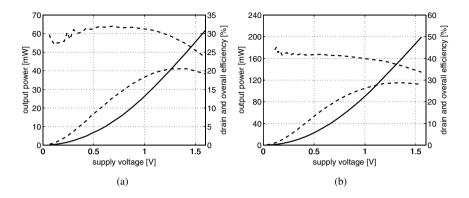

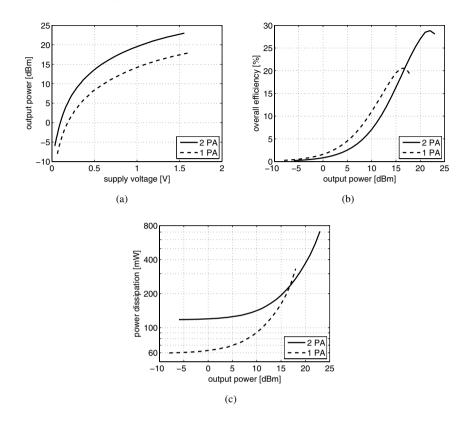

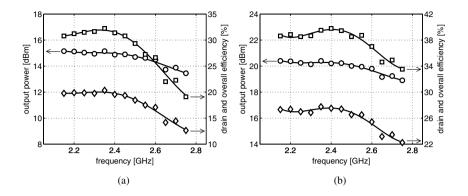

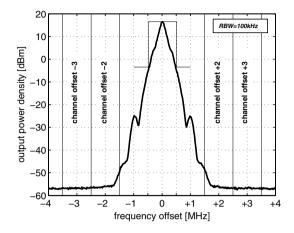

(2.72)