# Mohammed Ismail Delia Rodríguez de Llera González *Editors*

# Radio Design in Nanometer Technologies

#### RADIO DESIGN IN NANOMETER TECHNOLOGIES

# Radio Design in Nanometer Technologies

Edited by

MOHAMMED ISMAIL

The Ohio State University, Columbus, OH, U.S.A.

and

DELIA RODRÍGUEZ DE LLERA GONZÁLEZ

The Royal Institute of Technology, Stockholm, Sweden

A C.I.P. Catalogue record for this book is available from the Library of Congress.

ISBN-10 1-4020-4823-8 (HB) ISBN-13 978-1-4020-4823-4 (HB) ISBN-10 1-4020-4824-6 (e-book) ISBN-13 978-1-4020-4824-1 (e-book)

Published by Springer, P.O. Box 17, 3300 AA Dordrecht, The Netherlands.

www.springer.com

Printed on acid-free paper

All Rights Reserved © 2006 Springer No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Ismail would like to dedicate this work to his family. Para todos los que han hecho de mí una persona mejor. Con todo mi cariño. Delia

## Contents

| xi    |

|-------|

| xxi   |

| xxiii |

| xxvii |

|       |

| Part I Current and Future Trends |

|----------------------------------|

|                                  |

| 1. |      | AND THE WIRELESS WORLD 2015 - CHALLENGES<br>YSTEM ARCHITECTURES AND COMMUNICATION |    |

|----|------|-----------------------------------------------------------------------------------|----|

|    |      | ADIGMS                                                                            | 3  |

|    | 1    | Introduction                                                                      | 3  |

|    | 2    | From the "Swiss Army Knife"                                                       | 4  |

|    | 3    | to Navigating the "Wireless Chaos"                                                | 5  |

|    | 4    | Six "Grand Challenges" in Wireless Systems                                        | 7  |

|    | 5    | Challenges in Radio Design - Flexible or Software Defined Radios                  | 9  |

|    | 6    | Conclusions                                                                       | 9  |

|    | Refe | rences                                                                            | 10 |

| 2. | CEL  | LULAR RF REQUIREMENTS AND INTEGRATION TRENDS                                      | 11 |

|    | 1    | Handset Technology Drivers                                                        | 11 |

|    | 2    | RF Transceiver Design Challenges                                                  | 16 |

|    | 3    | Architectures                                                                     | 23 |

|    | 4    | Technology Scaling                                                                | 28 |

|    | 5    | Handset Implementation Trends                                                     | 31 |

|    | Refe | rences                                                                            | 33 |

| 3. |       | TWARE DEFINED RADIO — VISIONS,<br>ALLENGES AND SOLUTIONS             | 35  |

|----|-------|----------------------------------------------------------------------|-----|

|    | 1     | Introduction                                                         | 35  |

|    | 2     | Technical Visions                                                    | 36  |

|    | 3     | Some Comments on Frequency Planning                                  | 38  |

|    | 4     | The Radio Challenge                                                  | 40  |

|    | 5     | Power Consumption of the Analog to Digital Converter                 | 44  |

|    | 6     | Other Key Components                                                 | 48  |

|    | 7     | Example of a 160MHz Carrier SDR Front-End                            | 49  |

|    | 8     | Example of a 2.4GHz Carrier Front-End                                | 50  |

|    | 9     | Conclusion                                                           | 53  |

|    | Refe  | erences                                                              | 55  |

| Pa | rt II | Digital SOC Design                                                   |     |

| 4. | TRI   | ENDS IN SOC ARCHITECTURES                                            | 59  |

|    | 1     | Introduction                                                         | 59  |

|    | 2     | VLSI Design Space                                                    | 62  |

|    | 3     | Conclusion                                                           | 79  |

|    | 4     | Acknowledgement                                                      | 80  |

|    | Refe  | erences                                                              | 80  |

| 5. | PRO   | OGRAMMABLE BASEBAND PROCESSORS                                       | 83  |

|    | 1     | Introduction                                                         | 83  |

|    | 2     | Baseband Processing Challenges                                       | 84  |

|    | 3     | Programmable Baseband Processors                                     | 86  |

|    | 4     | OFDM and WCDMA Example                                               | 88  |

|    | 5     | Multi-Standard Processor Design                                      | 94  |

|    | 6     | Conclusion                                                           | 99  |

|    | Refe  | erences                                                              | 99  |

| 6. |       | ALOG-TO-DIGITAL CONVERSION TECHNOLOGIES<br>& SOFTWARE DEFINED RADIOS | 101 |

|    | 1     | Introduction                                                         | 101 |

|    | 2     | Why Software Defined Radios?                                         | 102 |

|    | 3     | Commercial SDRs and SRs                                              | 103 |

|    | 4     | Current and Future Radio Architectures                               | 104 |

|    | 5    | Analog-To-Digital Conversion Challenges  | 108 |

|----|------|------------------------------------------|-----|

|    | 6    | Reconfigurable ADCs for SDR/SR           | 112 |

|    | 7    | Conclusions                              | 119 |

|    | Refe | erences                                  | 120 |

| 7. | REC  | CONFIGURABLE A/D CONVERTERS FOR FLEXIBLE |     |

|    | WIF  | RELESS TRANSCEIVERS IN 4G RADIOS         | 123 |

|    | 1    | Introduction                             | 123 |

|    | 2    | Towards 4G Radios                        | 124 |

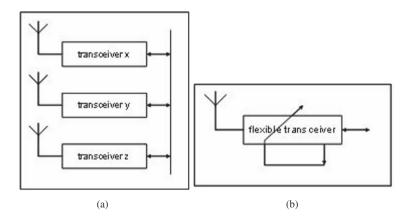

|    | 3    | Flexible Receiver Architectures          | 126 |

|    | 4    | Multi-standard A/D Converters            | 127 |

|    | Refe | erences                                  | 140 |

#### Part III Radio Design

| 8. |        | EIVER DESIGN FOR INTEGRATED MULTI-STANDARD<br>ELESS RADIOS     | 145 |

|----|--------|----------------------------------------------------------------|-----|

|    | 1      | Introduction                                                   | 145 |

|    | 2      | Multi-standard Receiver Design Considerations                  | 148 |

|    | 3      | From Standard to Receiver Specs                                | 149 |

|    | 4      | Frequency Planning                                             | 156 |

|    | 5      | Receiver Budget                                                | 160 |

|    | 6      | Case Study:WCDMA/WLAN Receiver Budget                          | 165 |

|    | 7      | Conclusions                                                    | 169 |

|    | Refe   | rences                                                         | 170 |

| 9. | ON-    | CHIP ESD PROTECTION FOR RFICS                                  | 173 |

|    | 1      | Introduction                                                   | 173 |

|    | 2      | Full-chip Protection Topology                                  | 173 |

|    | 3      | ESD Protection Circuits for RF I/Os                            | 175 |

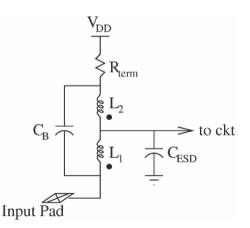

|    | 4      | Inductor-based Protection Circuits                             | 181 |

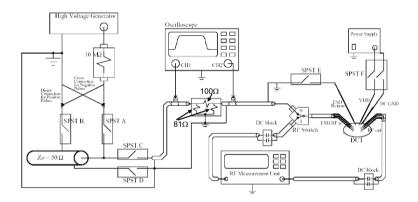

|    | 5      | ESD Testing of RFICs                                           | 189 |

|    | Refe   | rences                                                         | 190 |

| 10 | . SILI | CON-BASED MILLIMETER-WAVE POWER AMPLIFIERS                     | 193 |

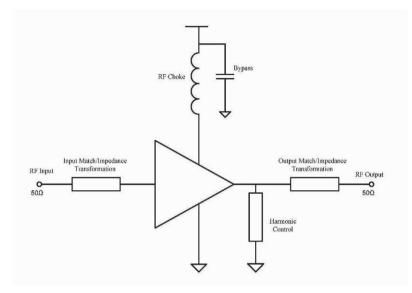

|    | 1      | Introduction                                                   | 193 |

|    | 2      | Challenges in Microwave/Millimeter-Wave Power Amplifier Design | 194 |

ix

|     | 3       | Power Amplifier Design Approaches                                                        | 196 |

|-----|---------|------------------------------------------------------------------------------------------|-----|

|     | 4       | Power Combining Techniques                                                               | 202 |

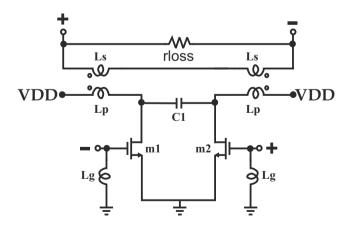

|     | 5       | Case Study: Design of a 24GHz Power Amplifier Based<br>on Distributed Active Transformer | 205 |

|     | 6       | Summary and Conclusions                                                                  | 212 |

|     | Refer   | rences                                                                                   | 214 |

| 11. |         | OLITHIC INDUCTOR MODELING<br>OPTIMIZATION                                                | 217 |

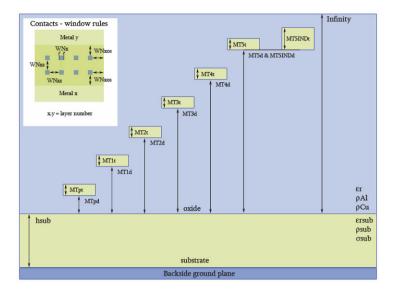

|     | 1       | Monolithic Inductor Modeling                                                             | 218 |

|     | 2       | The Inductor CAD-Tool Indentro                                                           | 230 |

|     | 3       | Verification of the Capacitance Model                                                    | 233 |

|     | Refer   | rences                                                                                   | 238 |

| 12. |         | LLENGES IN THE DESIGN OF PLLS IN DEEP-SUBMICRON<br>INOLOGY                               | 241 |

|     | 1       | Introduction                                                                             | 241 |

|     | 2       | Technology Trends                                                                        | 241 |

|     | 3       | PLL Performance Metrics                                                                  | 247 |

|     | 4       | Impact of Technology Scaling                                                             | 261 |

|     | 5       | Architecture Landscape                                                                   | 272 |

|     | Refer   | rences                                                                                   | 284 |

| 13. | RFIC    | DESIGN FOR FIRST-PASS SILICON SUCCESS                                                    | 287 |

|     | 1       | Introduction                                                                             | 287 |

|     | 2       | SoC Integration                                                                          | 295 |

|     | 3       | Self Awareness                                                                           | 305 |

|     | 4       | Self Calibration                                                                         | 308 |

|     | 5       | Self Configuration                                                                       | 312 |

|     | 6       | Leveraging Self Configuration for System Parameters                                      | 312 |

|     | 7       | Conclusion                                                                               | 314 |

|     | Refer   | rences                                                                                   | 314 |

| Ab  | out the | e Authors                                                                                | 315 |

| Ind | ex      |                                                                                          | 321 |

# List of Figures

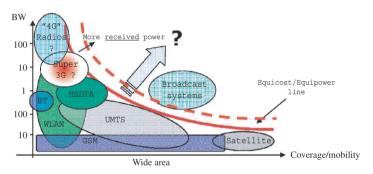

| 1.1  | Range/Coverage/Mobility - Bandwidth relationship.                                                               | 4  |

|------|-----------------------------------------------------------------------------------------------------------------|----|

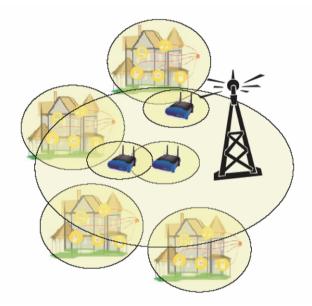

| 1.2  | Heterogeneous wireless infrastructure with a multitude of access with varying properties (range, data rate, mo- |    |

|      | bility etc.)                                                                                                    | 6  |

| 2.1  | GH197 (1992).                                                                                                   | 12 |

| 2.2  | T28 (1999).                                                                                                     | 12 |

| 2.2  | T39 (2000).                                                                                                     | 13 |

|      |                                                                                                                 |    |

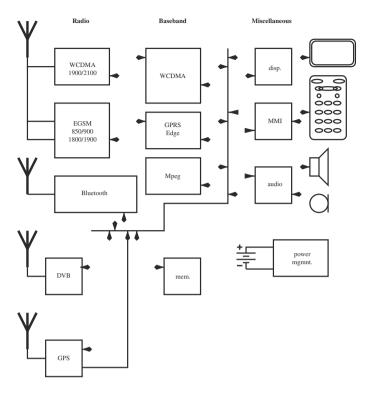

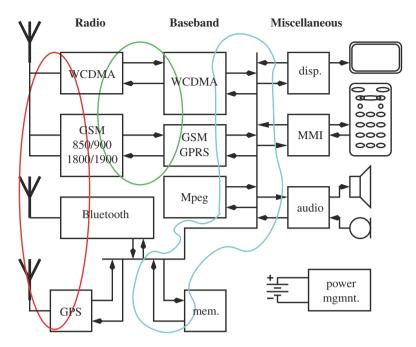

| 2.4  | Tentative handset block diagram.                                                                                | 15 |

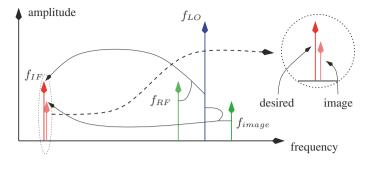

| 2.5  | Image response.                                                                                                 | 16 |

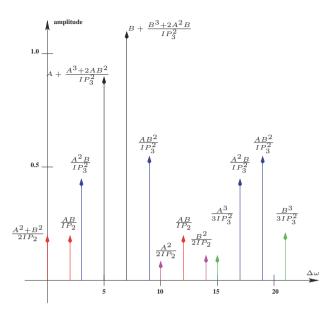

| 2.6  | Intermodulation products resulting from $0.9\cos(5\Delta\omega t)+$                                             |    |

|      | $1.1\cos(7\Delta\omega t)$ applied to a cubic nonlinearity with $IP_2 =$                                        |    |

|      | 5 and $IP_3 = \sqrt{2}$ .                                                                                       | 18 |

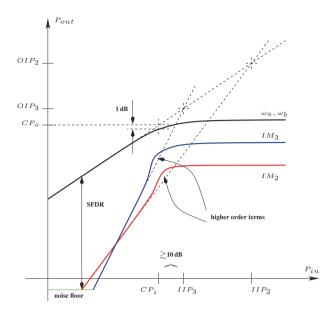

| 2.7  | Linearity definitions; intercept points, compression point                                                      |    |

|      | and spurious-free dynamic range.                                                                                | 19 |

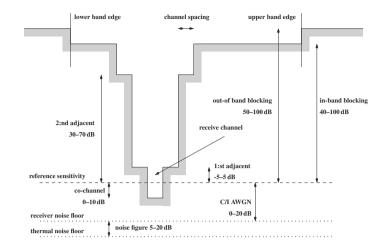

| 2.8  | Selectivity and blocking dynamic range requirements.                                                            | 20 |

| 2.9  | Receiver domain partitioning.                                                                                   | 21 |

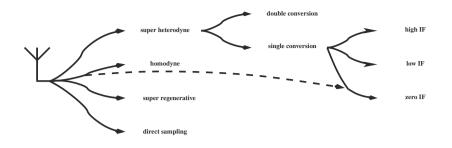

| 2.10 | Receiver architecture genealogy.                                                                                | 23 |

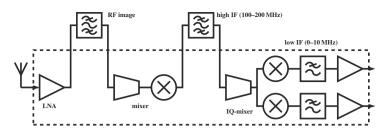

| 2.11 | Double super heterodyne receiver (less antenna filters).                                                        | 24 |

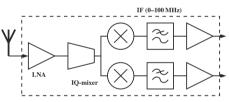

| 2.12 | Single conversion zero-IF receiver.                                                                             | 24 |

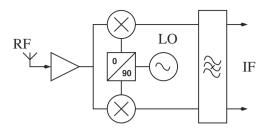

| 2.13 | Single-conversion low-IF receiver with poly-phase IF filter.                                                    | 25 |

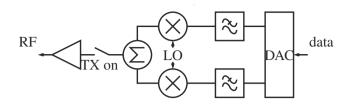

| 2.14 | Direct up-conversion transmitter.                                                                               | 26 |

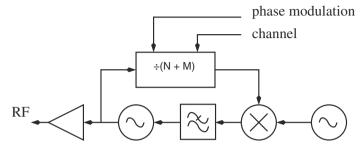

| 2.15 | Direct phase-modulation transmitter.                                                                            | 27 |

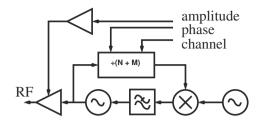

| 2.16 | Polar modulation transmitter.                                                                                   | 28 |

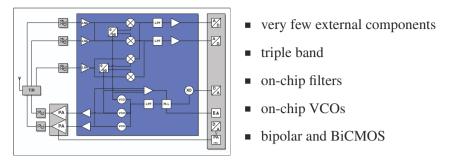

| 2.17 | Single-chip Bluetooth modem.                                                                                    | 29 |

| 2.18 | Single-chip Bluetooth transceiver.                                                                              | 30 |

| 2.19 | Single-chip GPRS transceiver.                                                                                                                                                            | 31 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.20 | Handset internal interfaces.                                                                                                                                                             | 32 |

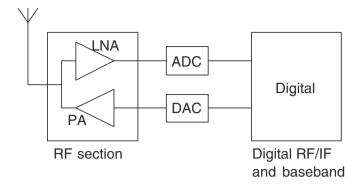

| 3.1  | "Ideal" software defined radio.                                                                                                                                                          | 37 |

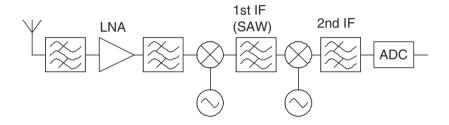

| 3.2  | Double superheterodyne receiver.                                                                                                                                                         | 37 |

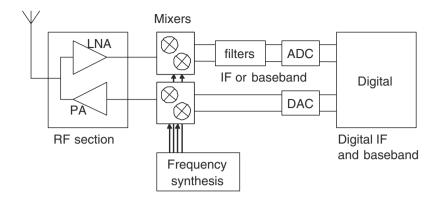

| 3.3  | Homodyne transceiver.                                                                                                                                                                    | 38 |

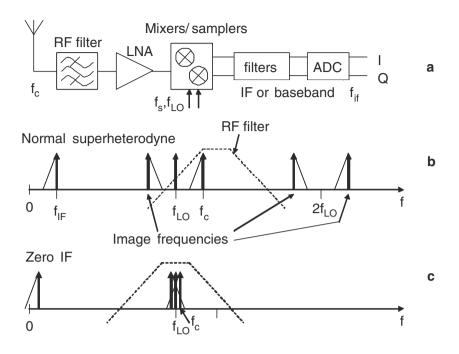

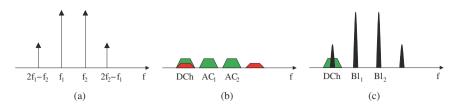

| 3.4  | Frequency planning for a superheterodyne (b) and a ho-<br>modyne (c).                                                                                                                    | 39 |

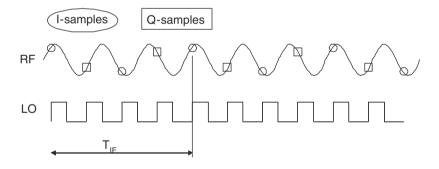

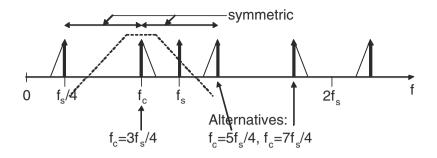

| 3.5  | I/Q-sampling utilizing $f_s=4f_c/3$ .                                                                                                                                                    | 39 |

| 3.6  | Frequency planning for I/Q sampling with various $f_c/f_s$ ratios.                                                                                                                       | 40 |

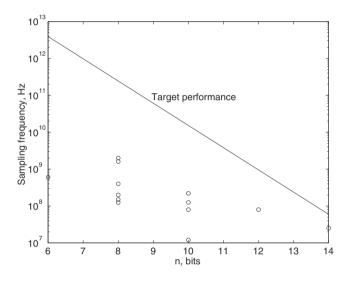

| 3.7  | Performance of various published ADCs plotted as sam-<br>pling frequency versus resolution. We also show our<br>target performance $f_s 2^{2n} = 1.6 \cdot 10^{16}$ Hz. Data from [5–7]. | 43 |

| 3.8  | Power consumption versus $f_s 2^{2n}$ for various published ADCs. We also show lines representing $P_S=12kTf_s 2^{2n}$ and $10^4$ times higher. Data from [5–7].                         | 44 |

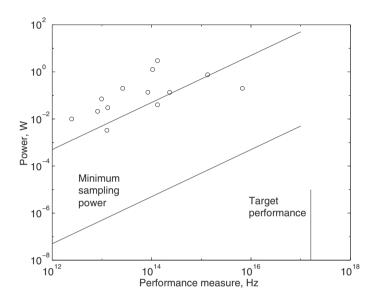

| 3.9  | Sampling circuit.                                                                                                                                                                        | 45 |

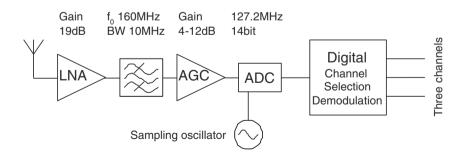

| 3.10 | SDR implementation of a three channel radio for AIS band.                                                                                                                                | 49 |

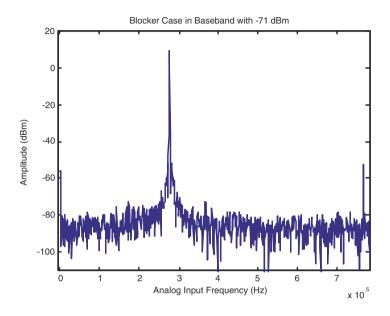

| 3.11 | Unfiltered digital signal including a signal at zero and a large blocker at 290kHz.                                                                                                      | 51 |

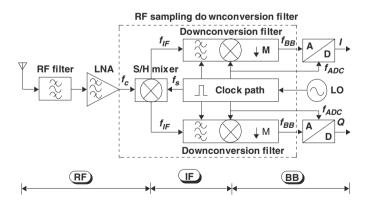

| 3.12 | Block diagram of an RF front-end based on a sampling downconversion filter.                                                                                                              | 51 |

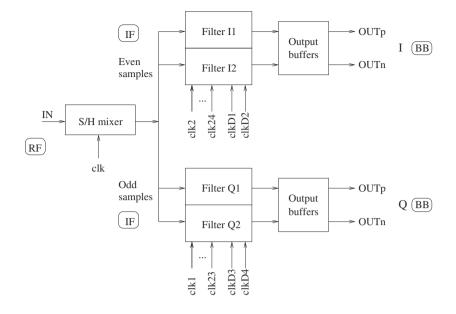

| 3.13 | Implementation of the filter in the sampling downcon-<br>version unit.                                                                                                                   | 52 |

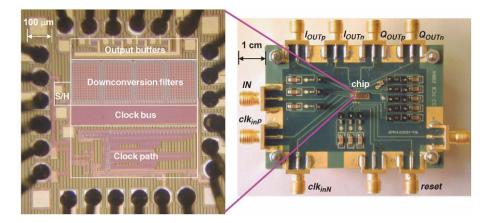

| 3.14 | Chip photo of the sampling downconversion filter (a) and test board (b).                                                                                                                 | 53 |

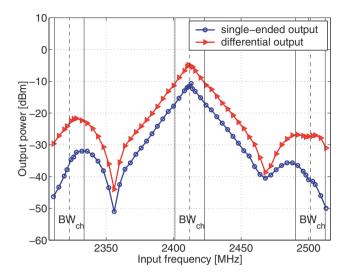

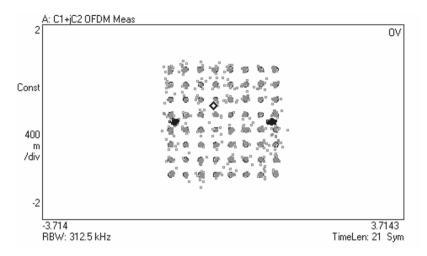

| 3.15 | Measured filter response, single-ended output and differential output. $BW_{ch}$ is the anticipated channel width.                                                                       | 54 |

| 3.16 | Measured constellation diagram when receiving a 64QAM modulated signal.                                                                                                                  | 55 |

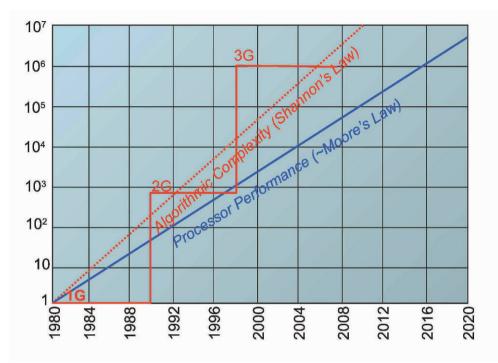

| 4.1  | Shannon beats Moore. Source Rabaey [1].                                                                                                                                                  | 60 |

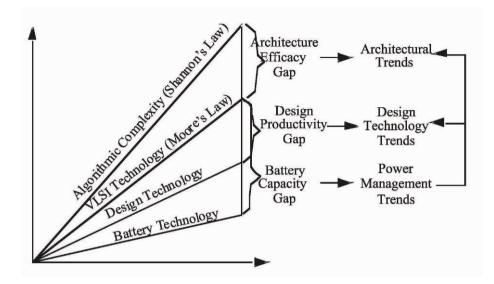

| 4.2  | Growth in Algorithmic Complexity vs Progress in VLSI,<br>Design and Battery Technologies.                                                                                                | 61 |

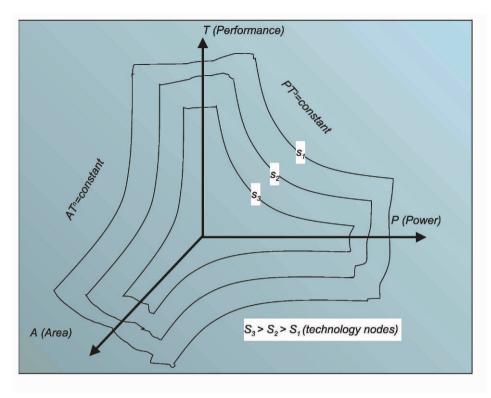

| 4.3  | VLSI Design Space (Source Flynn et. al. [5]).                                                                                                                                            | 63 |

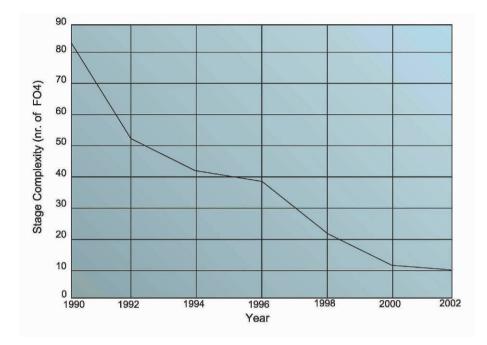

| 4.4  | The decreasing stage size.                                                                                                                                                               | 64 |

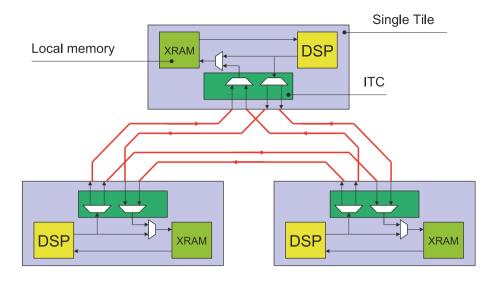

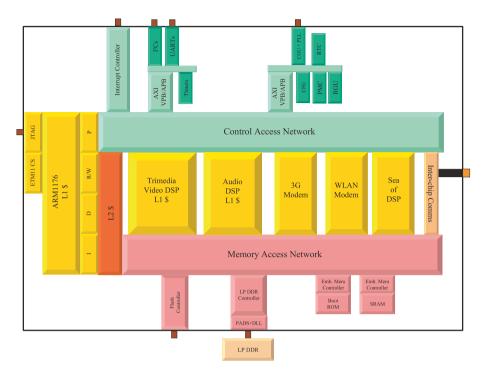

| 4.5  | Sea of DSP message passing platform from Philips Semi-<br>conductors.                                                                                                                    | 67 |

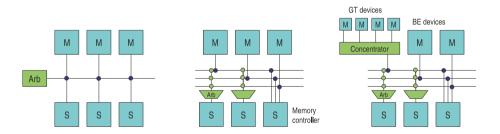

| 4.6  | Multi-processor architecture shared memory architec-<br>ture from Philips Semiconductors.                                                                                                | 68 |

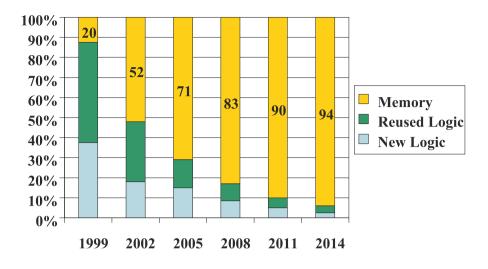

| 4.7  | Embedded memory content in SOC is increasing rapidly.                                                                | 70    |

|------|----------------------------------------------------------------------------------------------------------------------|-------|

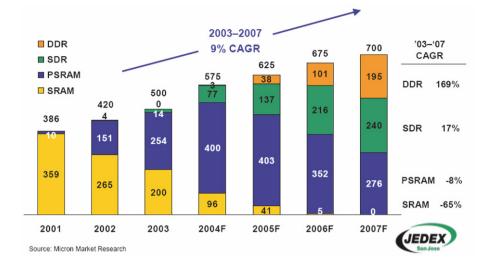

| 4.8  | Volatile Memory is shifting from static to dynamic mem-<br>ories. (Source [12]).                                     | 71    |

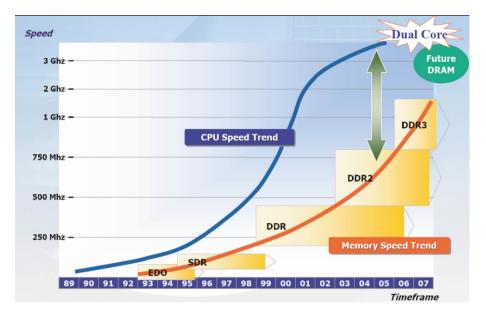

| 4.9  | CPU vs Memory Speed Trends. Source: Hynix (Source [13]                                                               | ). 72 |

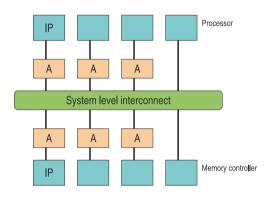

| 4.10 | Evolution of Interconnect Schemes.                                                                                   | 72    |

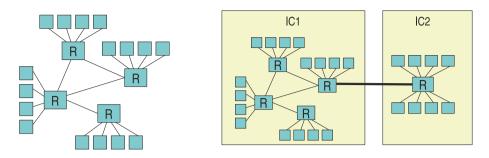

| 4.11 | Evolution of NOC as intra-chip interconnect as well as                                                               |       |

|      | an interchip interconect.                                                                                            | 73    |

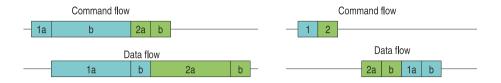

| 4.12 | Evolution of Interconnect Protocols.                                                                                 | 74    |

| 4.13 | Abstracting IP Functions from System.                                                                                | 74    |

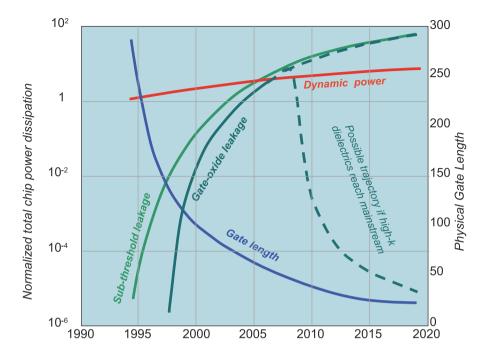

| 4.14 | Trends in power consumption components. Source Nam Sung Kim et. al. [16].                                            | 75    |

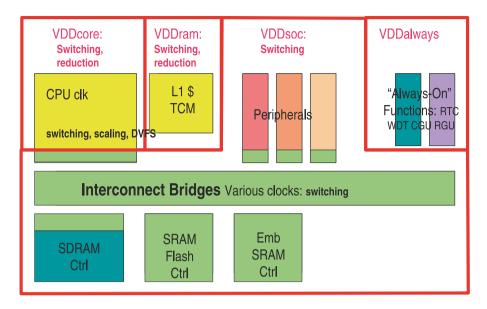

| 4.15 | Multiple Voltage Domains.                                                                                            | 77    |

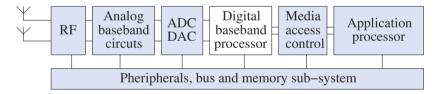

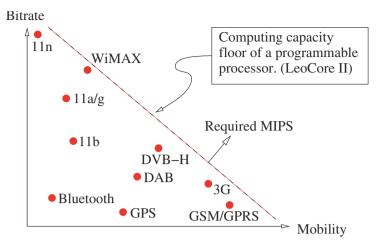

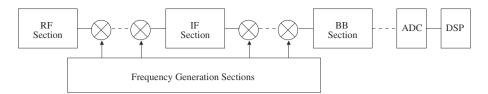

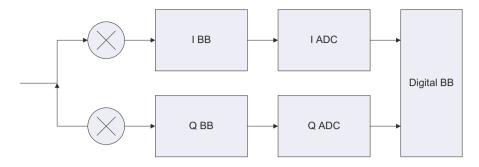

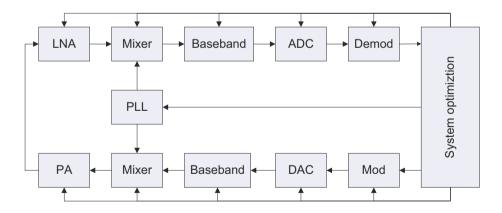

| 5.1  | Radio system overview.                                                                                               | 83    |

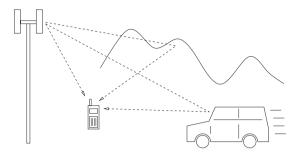

| 5.2  | Multi-path propagation.                                                                                              | 85    |

| 5.3  | Dynamic MIPS usage.                                                                                                  | 88    |

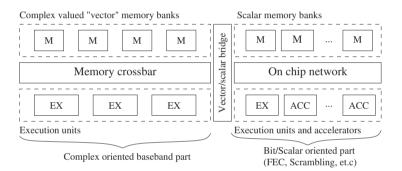

| 5.4  | Hardware multiplexing on LeoCore DSPs.                                                                               | 88    |

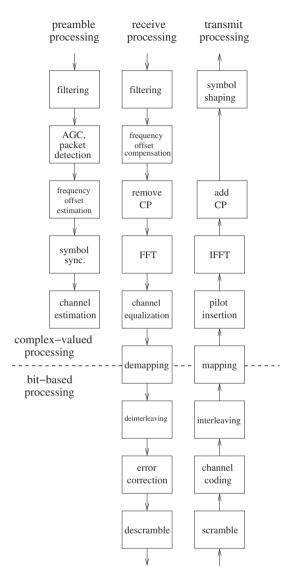

| 5.5  | OFDM processing flow.                                                                                                | 92    |

| 5.6  | LeoCore basic architecture.                                                                                          | 96    |

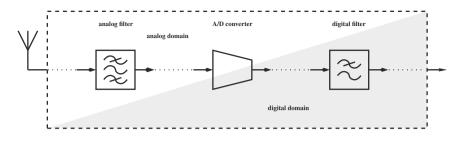

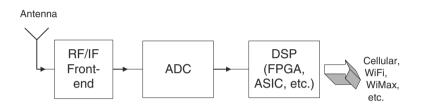

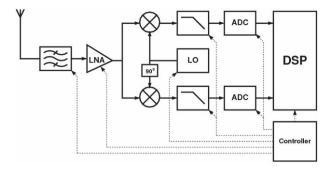

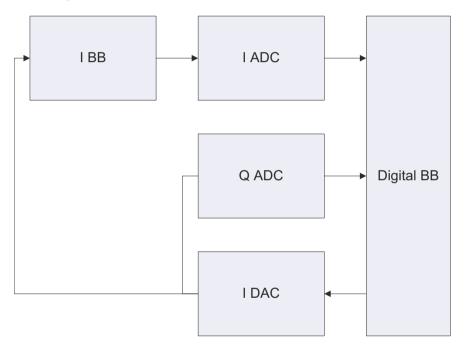

| 6.1  | Conceptual Block Diagram of a Radio Receiver.                                                                        | 104   |

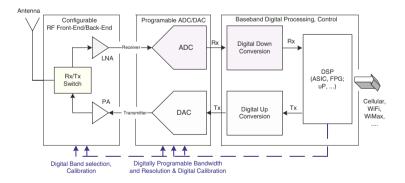

| 6.2  | Software Radio Architecture.                                                                                         | 104   |

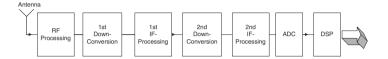

| 6.3  | Superheterodyne Receiver Architecture.                                                                               | 106   |

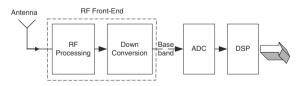

| 6.4  | Zero-IF Receiver Architecture.                                                                                       | 106   |

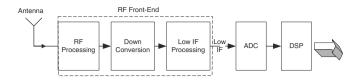

| 6.5  | Low-IF (near zero) Receiver Architecture.                                                                            | 107   |

| 6.6  | High-IF (could be near RF) Receiver Architecture.                                                                    | 107   |

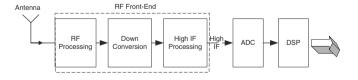

| 6.7  | Figure-Of-Merit and Resolution vs. Bandwidth.                                                                        | 110   |

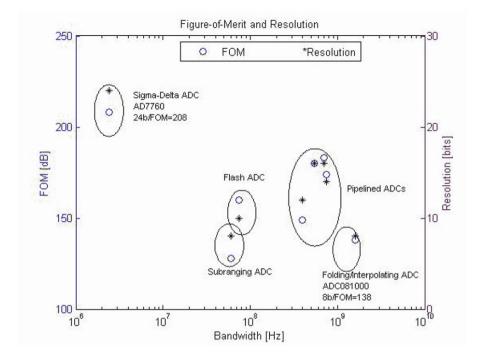

| 6.8  | Required ADC Resolution vs. Bandwidth.                                                                               | 111   |

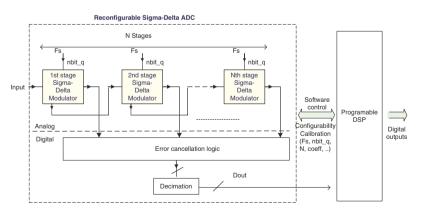

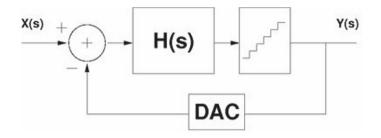

| 6.9  | Generic Reconfigurable $\Sigma \Delta$ ADC.                                                                          | 113   |

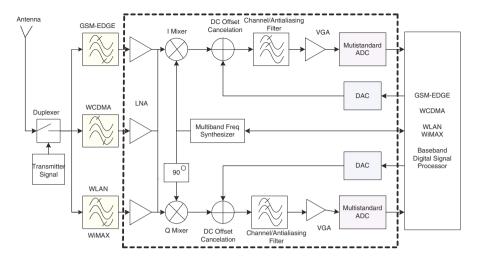

| 6.10 | Multi-standard Receiver.                                                                                             | 114   |

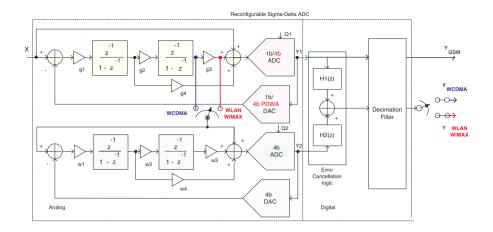

| 6.11 | Reconfigurable SC Modified Cascaded $\Sigma\Delta$ ADC.                                                              | 115   |

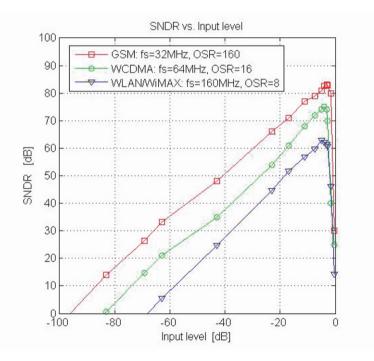

| 6.12 | SNDR vs. Input Signal.                                                                                               | 115   |

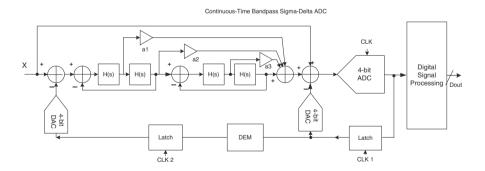

| 6.13 | 4th order Continuous-Time Bandpass Sigma-Delta ADC.                                                                  | 117   |

| 6.14 | Sigma-Delta Pipelined ADCs Array.                                                                                    | 118   |

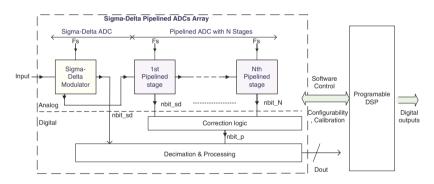

| 6.15 | CT Sigma-Delta Pipelined ADCs array.                                                                                 | 119   |

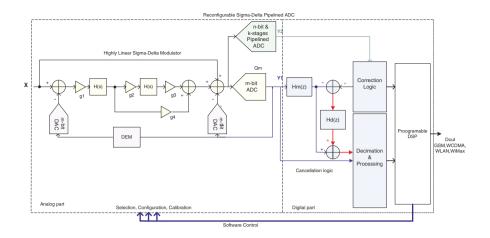

| 7.1  | (a) Multiple parallel transceivers for each standard, ver-                                                           |       |

|      | sus (b) one flexible transceiver for multiple standards.                                                             | 125   |

| 7.2  | Simplified block diagram of a flexible software-defined receiver with digital control of a reconfigurable front-end. | 127   |

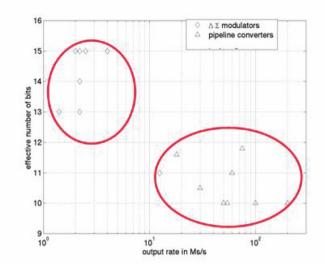

| 7.3  | Comparison of performance of $\Delta\Sigma$ and pipelined A/D converters.                                                             | 128 |

|------|---------------------------------------------------------------------------------------------------------------------------------------|-----|

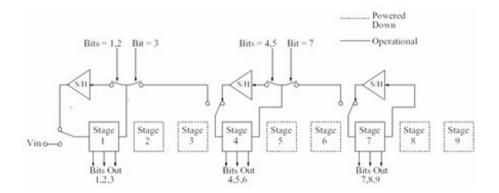

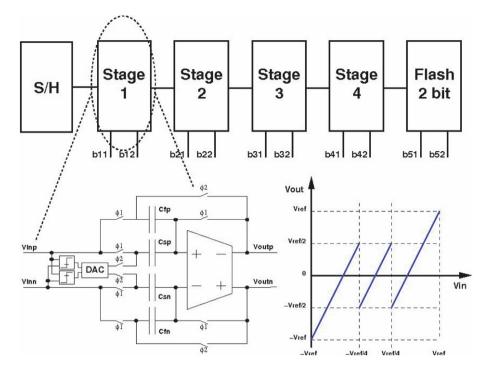

| 7.4  | Changing the resolution and bandwidth of a pipelined A/D converter by switching in/out stages and by chang-<br>ing the sampling rate. | 129 |

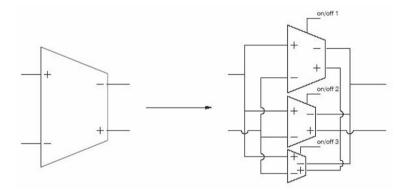

| 7.5  | Reconfiguring an OTA by switching in/out different                                                                                    |     |

|      | substages (different sizes, currents or capacitors.                                                                                   | 129 |

| 7.6  | Basic Block Diagram of a $\Delta\Sigma$ modulator.                                                                                    | 130 |

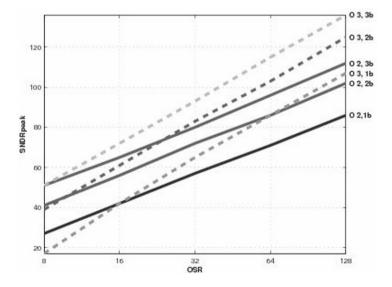

| 7.7  | SNDR vs. OSR for different $\Delta\Sigma$ A/D converter topologies.                                                                   | 131 |

| 7.8  | The Leslie-Singh architecture with discrete-time loop                                                                                 |     |

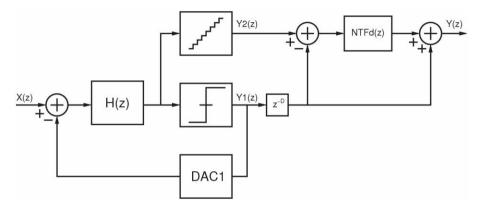

|      | filter and digital reconstruction filter.                                                                                             | 132 |

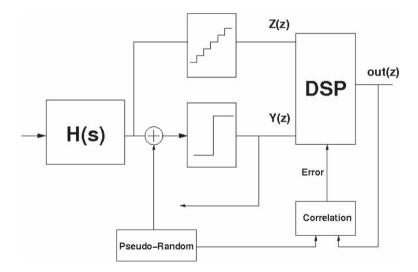

| 7.9  | Principle schematic of the tuning of the digital filter (implemented in the DSP block).                                               | 133 |

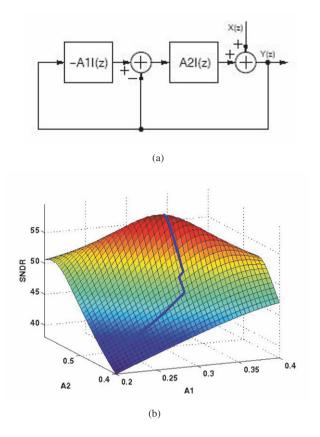

| 7.10 | (a) Structure of the digital IIR tuning filter, and (b) impact on the SFDR by tuning the digital filter coefficients.                 | 134 |

| 7.11 | Circuit schematic of the pipelined quantizer used in the A/D converter.                                                               | 135 |

| 7.12 | Circuit schematic of the loop filter used in the reconfig-<br>urable A/D converter.                                                   | 136 |

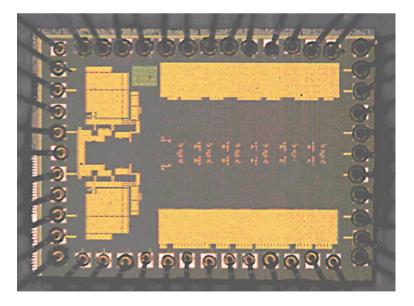

| 7.13 | Chip photograph of a prototype multi-standard over-<br>sampling A/D converter in 0.18 $\mu$ m CMOS technology.                        | 137 |

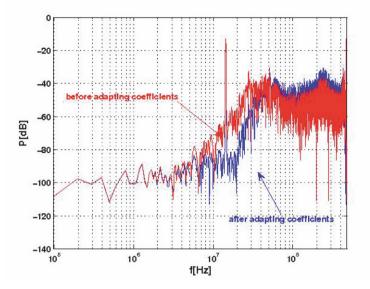

| 7.14 | Simulated spectrum of the A/D converter before and after adapting the digital filter's tuning coefficients.                           | 138 |

| 8.1  | Different wireless scenarios and the connectivity op-<br>tions they provide.                                                          | 146 |

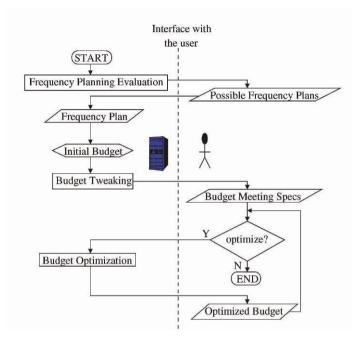

| 8.2  | Simulation flow and interaction with the user of the fre-<br>quency planning and budget tools.                                        | 150 |

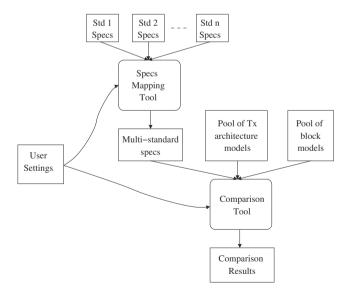

| 8.3  | TACT components.                                                                                                                      | 150 |

| 8.4  | Third order intermodulation in a non-linear system.                                                                                   | 153 |

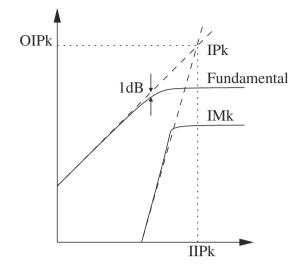

| 8.5  | Calculation of the $k^{th}$ order intercept point (IPk).                                                                              | 154 |

| 8.6  | Abstract model of a generic receiver architecture.                                                                                    | 156 |

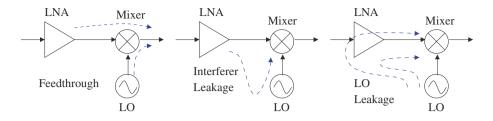

| 8.7  | Signal feedthrough and self-mixing.                                                                                                   | 157 |

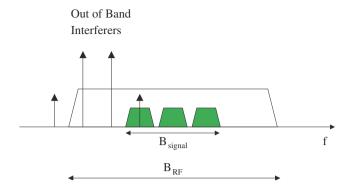

| 8.8  | Effect of out-of-band interferers after going through a non-linear stage.                                                             | 160 |

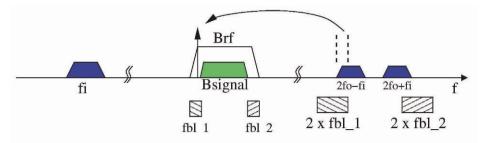

| 8.9  | Calculation of the most detrimental out-of-band inter-<br>fering frequency bands.                                                     | 161 |

| 8.10 | Algorithm to find a budget meeting specs.                                                                                             | 164 |

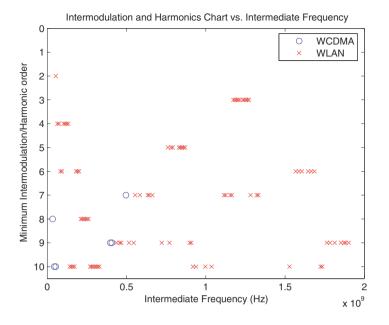

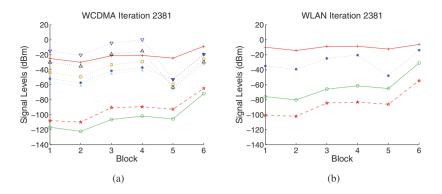

| 8.11 | Minimum order of distortion components vs. the inter-<br>mediate frequency band within which they fall.                               | 167 |

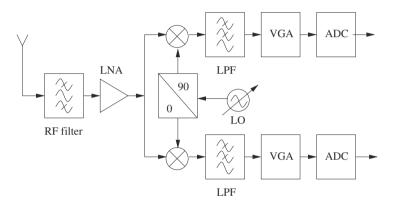

| 8.12            | Zero IF receiver architecture.                                                                                                                                                                                                                                 | 168 |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 8.13            | Signal levels along the blocks for WCDMA and WLAN for a typical TACT run.                                                                                                                                                                                      | 169 |

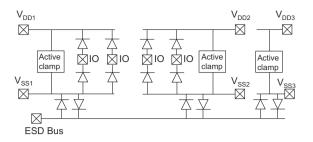

| 9.1             | Full-chip ESD protection network.                                                                                                                                                                                                                              | 174 |

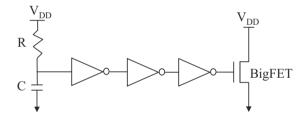

| 9.2             | Schematic of an active clamp.                                                                                                                                                                                                                                  | 174 |

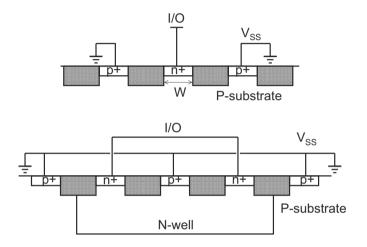

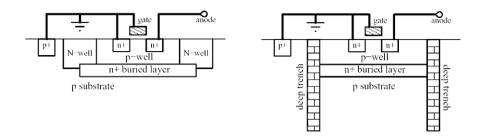

| 9.2<br>9.3      | Cross-sections of substrate and N-well bottom diodes.                                                                                                                                                                                                          | 174 |

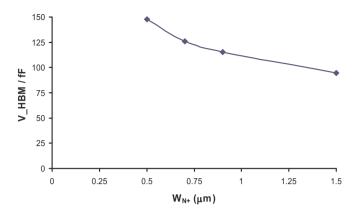

| 9.3<br>9.4      | ESD protection level vs. PN junction width.                                                                                                                                                                                                                    | 170 |

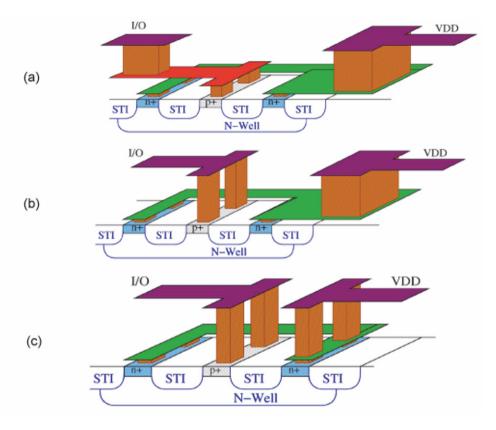

| 9. <del>4</del> | Interconnect routing configurations for an N-well top diode.                                                                                                                                                                                                   | 177 |

| 9.6             | Schematics of wide-band common-emitter and common-                                                                                                                                                                                                             | 170 |

| 9.0             | base amplifiers.                                                                                                                                                                                                                                               | 179 |

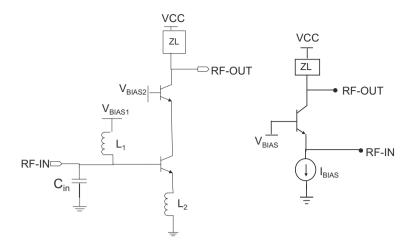

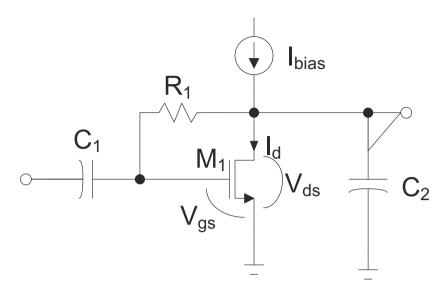

| 9.7             | Schematic of a common-source narrowband LNA.                                                                                                                                                                                                                   | 180 |

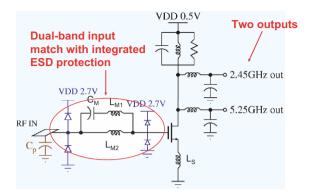

| 9.8             | Schematic of a dual-band LNA.                                                                                                                                                                                                                                  | 181 |

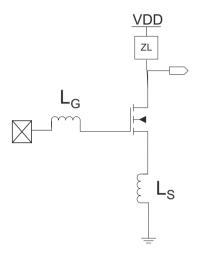

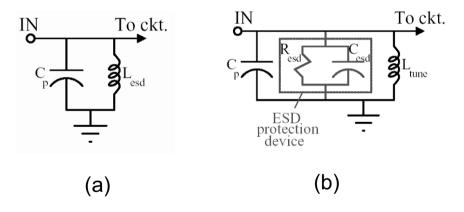

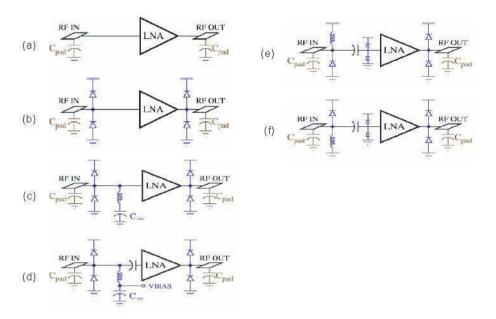

| 9.9             | Tuned ESD protection circuits.                                                                                                                                                                                                                                 | 182 |

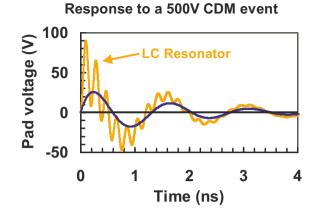

| 9.10            | Protection circuits' response to a 500 V CDM discharge.                                                                                                                                                                                                        | 183 |

| 9.11            | Cross-sections of floating-body, grounded-gate NFETs.                                                                                                                                                                                                          | 184 |

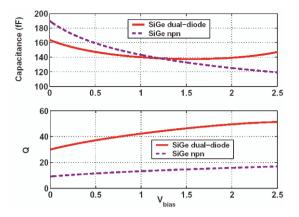

| 9.12            | Off-state impedance of SiGe HBT and dual-diode pro-                                                                                                                                                                                                            |     |

|                 | tection circuits.                                                                                                                                                                                                                                              | 185 |

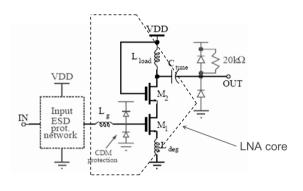

| 9.13            | LNA test circuit.                                                                                                                                                                                                                                              | 185 |

| 9.14            | Six ESD protection strategies.                                                                                                                                                                                                                                 | 186 |

| 9.15            | T-coil based ESD protection circuit.                                                                                                                                                                                                                           | 188 |

| 9.16            | Combined TLP/RF measurement system.                                                                                                                                                                                                                            | 189 |

| 10.1            | Typical power amplifier schematic.                                                                                                                                                                                                                             | 195 |

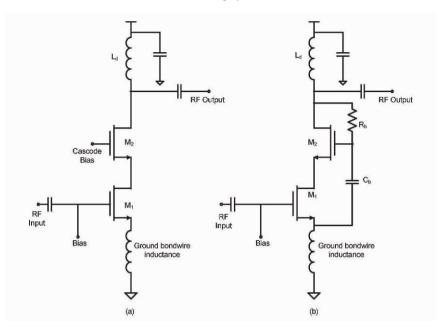

| 10.2            | (a) Conventional cascode amplifier. (b) Self-biased cas-<br>code amplifier [14].                                                                                                                                                                               | 197 |

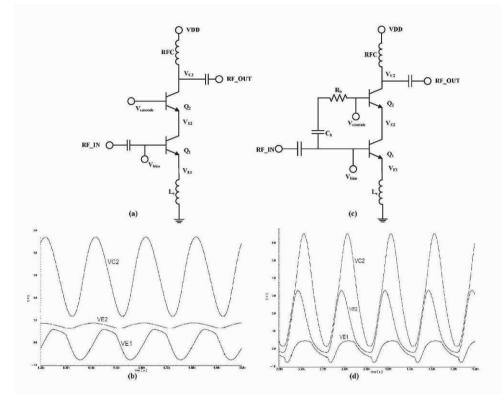

| 10.3            | <ul> <li>(a) Fixed-bias cascode amplifier. (b) Collector and emitter voltage waveforms for fixed-bias cascode amplifier.</li> <li>(c) RF-driven cascode amplifier. (d) Collector and emitter voltage waveforms for the RF-driven cascode amplifier.</li> </ul> | 198 |

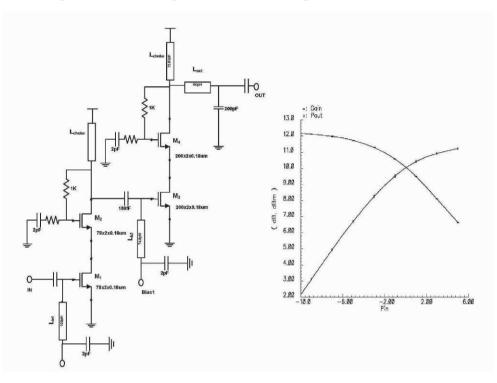

| 10.4            | (a) Schematic of a two stages single-ended CMOS power<br>amplifier. (b) Simulated output power and power gain<br>of the amplifier at 24GHz.                                                                                                                    | 199 |

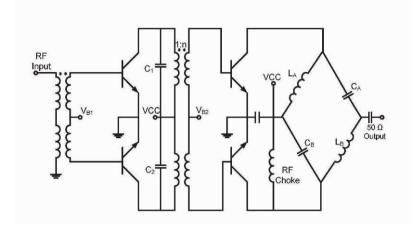

| 10.5            | A fully integrated differential SiGe PA with transformer-<br>based matching network and on-chip balun [19].                                                                                                                                                    | 201 |

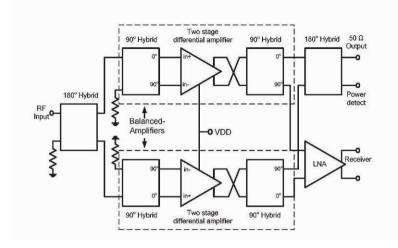

| 10.6            | Doubly-balanced transceiver front-end topology based on $90^{\circ}$ and $180^{\circ}$ couplers [23].                                                                                                                                                          | 203 |

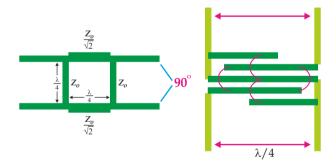

| 10.7            | (a) Branch-line coupler. (b) Lange coupler.                                                                                                                                                                                                                    | 203 |

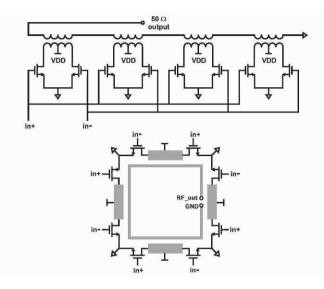

| 10.8            | Conceptual schematic and layout of a 4-stage PA coupled through a distributed active transformer [26].                                                                                                                                                         | 205 |

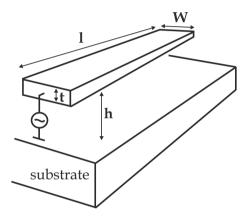

| 10.9  | A generic slab inductor structure.                                                                                                                            | 206 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 10.10 | EM Simulations showing the quality factor for different inductance values.                                                                                    | 209 |

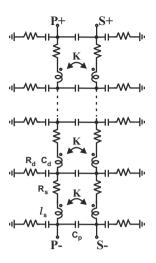

| 10.11 | E6-segement equivalent circuit for modeling the distrib-                                                                                                      |     |

|       | uted transformer.                                                                                                                                             | 210 |

| 10.12 | Basic Differential Stage.                                                                                                                                     | 210 |

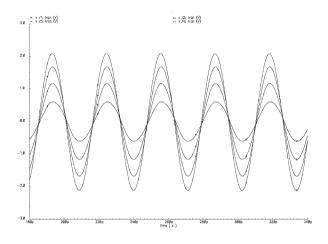

| 10.13 | Power combining in time domain.                                                                                                                               | 212 |

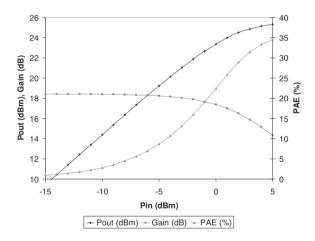

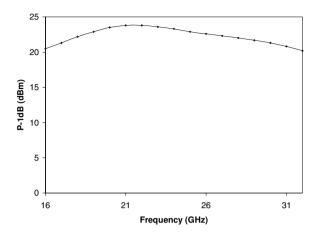

| 10.14 | Pout, Gain and PAE v.s. Pin.                                                                                                                                  | 212 |

| 10.15 | Simulated 1-dB compression point versus frequency.                                                                                                            | 213 |

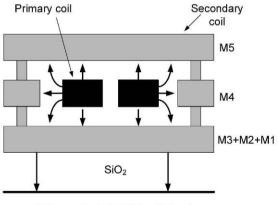

| 10.16 | Self-shielded monolithic transformer used in the distributed-<br>active-transformer DAT-based power amplifier reported                                        | 010 |

| 111   | in [11].                                                                                                                                                      | 213 |

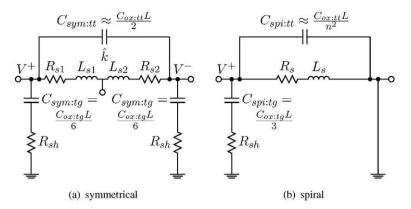

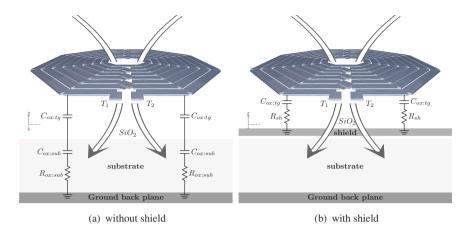

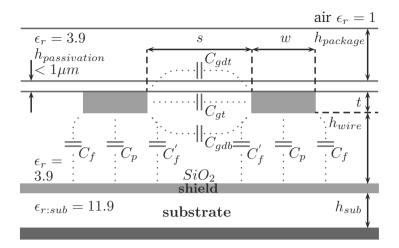

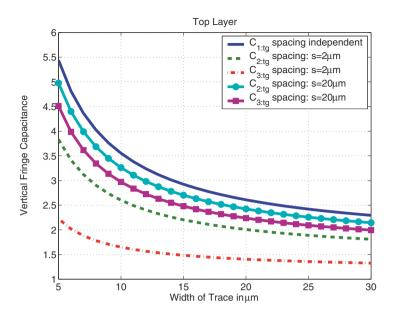

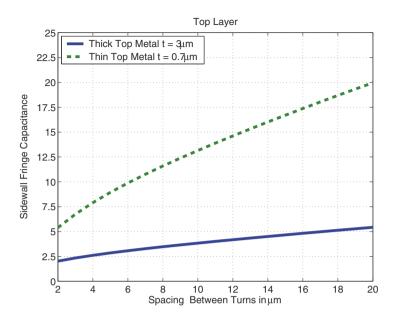

| 11.1  | Inductor $\pi$ -model. $C_{ox:tg}L$ is the total capacitance from<br>the inductor trace to ground and $C_{ox:tt}L$ is the total turn-<br>to-turn capacitance. | 218 |

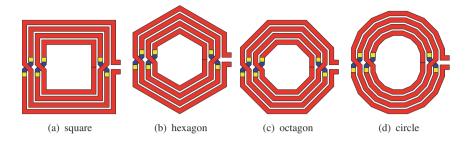

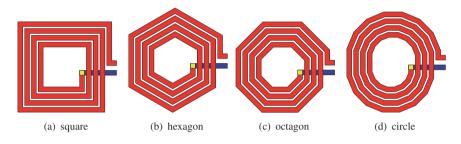

| 11.2  | Layout of symmetrical inductors.                                                                                                                              | 219 |

| 11.3  | Layout of spiral inductors.                                                                                                                                   | 219 |

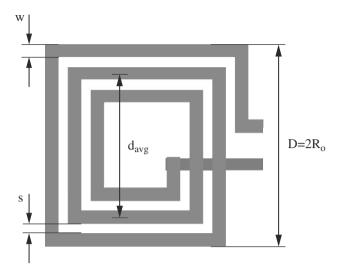

| 11.4  | Layout of spiral inductors, showing design parameters.                                                                                                        | 220 |

| 11.5  | (a) Electric and magnetic substrate losses without shield.                                                                                                    | 220 |

| 11.0  | (b) Magnetic (eddy) substrate losses with shield.                                                                                                             | 224 |

| 11.6  | Cross-section of microstrips on-chip and their capacitances.                                                                                                  | 225 |

| 11.7  | Capacitance ratios versus width, w. $(t = 3\mu m, h = 6\mu m.)$                                                                                               | 228 |

| 11.8  | Capacitance ratio of $C'_{qt}$ versus spacing between wires,                                                                                                  |     |

|       | s. $(h = 6\mu \text{m}, \text{ and } w = 10\mu \text{m}.)$                                                                                                    | 229 |

| 11.9  | Main window of Indentro.                                                                                                                                      | 231 |

| 11.10 | Graphic view of technology file.                                                                                                                              | 232 |

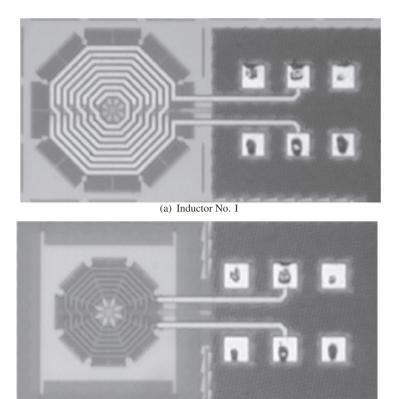

| 11.11 | A photograph of two of the inductors. The skating marks from the probes are clearly visible.                                                                  | 235 |

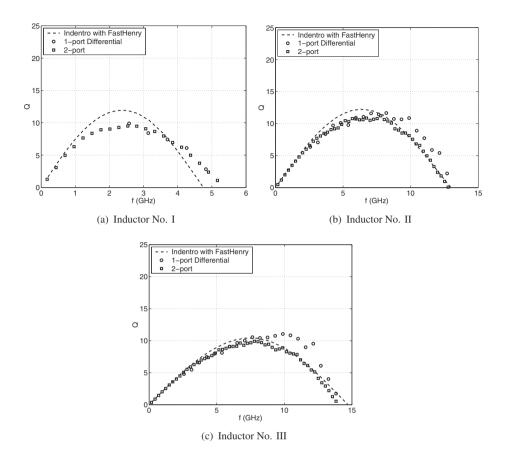

| 11.12 | Comparison between Indentro with FastHenry, and 1-<br>port and 2-port measurements.                                                                           | 236 |

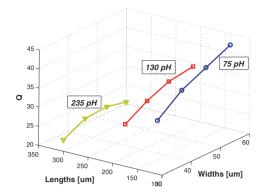

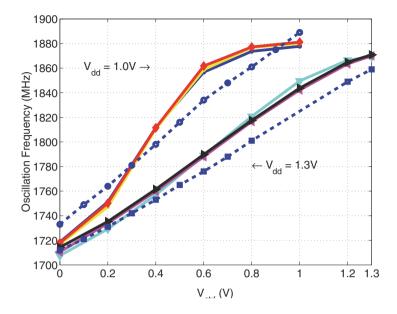

| 11.13 | Tuning characteristic for three measured chips at 1.0V and 1.3V supply. Dashed lines is the simulated tuning                                                  | 007 |

| 11 14 | characteristic.                                                                                                                                               | 237 |

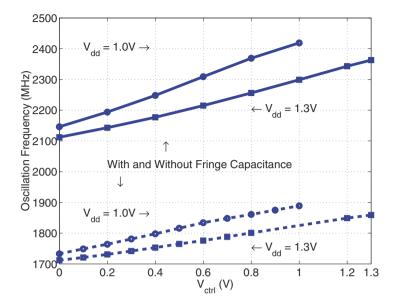

| 11.14 | Simulated tuning characteristic at 1.0V and 1.3V supply with and without the fringe capacitances.                                                             | 238 |

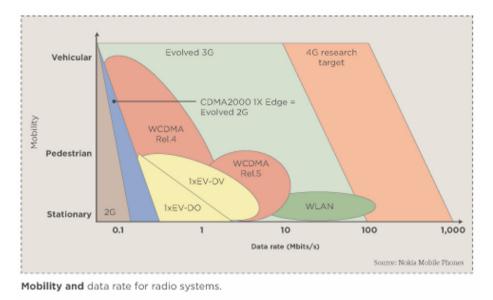

| 12.1  | Data rates for current and future radios.                                                                                                                     | 242 |

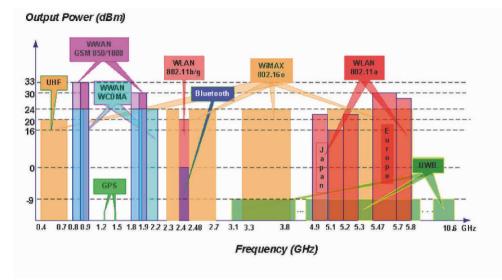

| 12.2  | Mobile frequency spectrum.                                                                                                                                    | 244 |

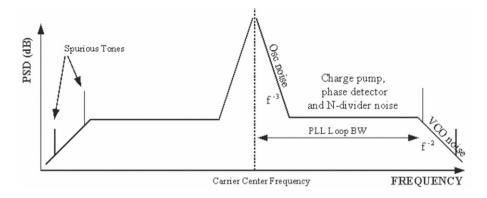

| 12.3  | Power spectral density of a PLL output signal.                                                                                                                | 247 |

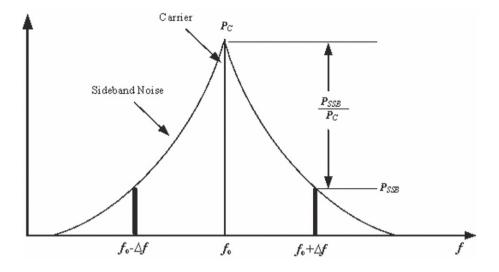

| 12.4  | Spectrum analyzer output displaying the carrier phase noise.                                                                           | 250 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------|-----|

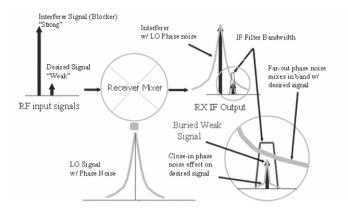

| 12.5  | Impact of LO close-in and far-out phase noise on the receiver.                                                                         | 253 |

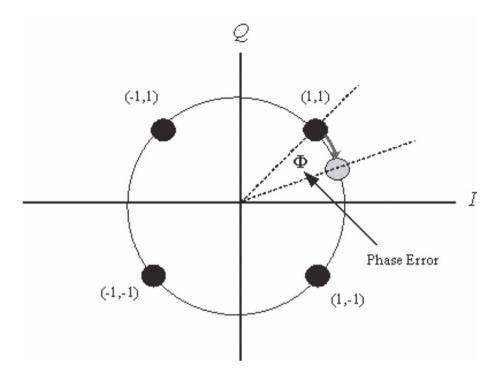

| 12.6  | Effect of phase noise on QPSK signal.                                                                                                  | 254 |

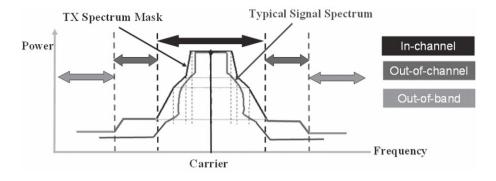

| 12.7  | Typical transmitter frequency mask.                                                                                                    | 255 |

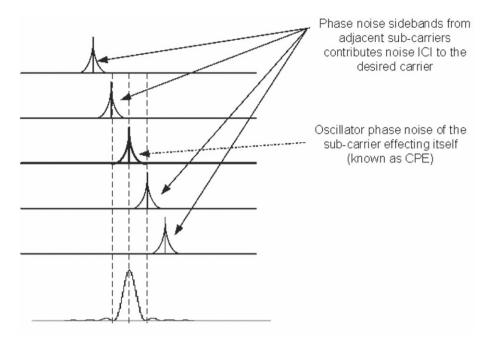

| 12.8  | The effect of oscillator phase noise sidebands on the modulated sub-carrier in OFDM systems.                                           | 257 |

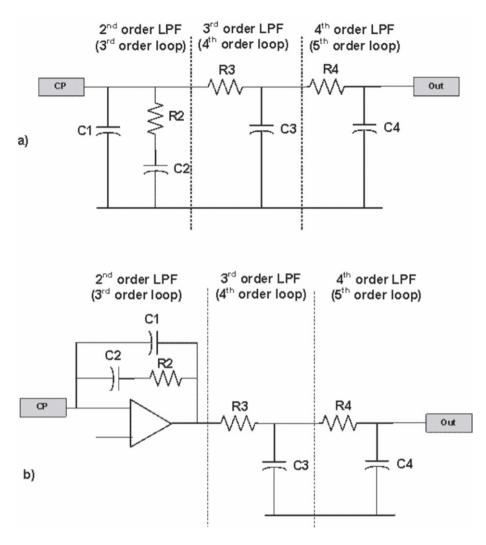

| 12.9  | LPF types: a) Passive LPF, b) Active LPF.                                                                                              | 259 |

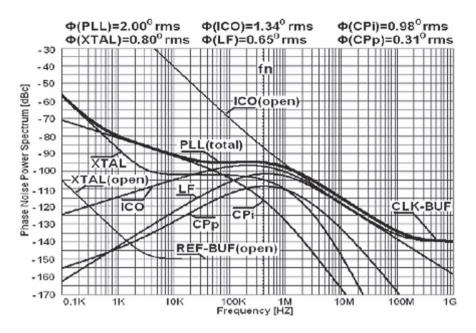

| 12.10 | PLL phase noise example showing contribution of dif-<br>ferent PLL sub-circuits. (A. Maxim, Silicon Labs Inc.)                         | 261 |

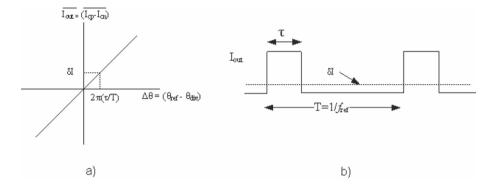

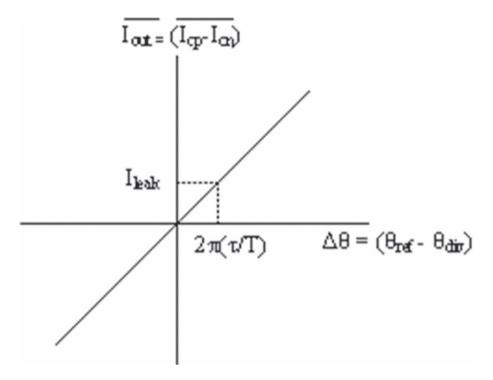

| 12.11 | a) Average charge pump current vs. input phase error<br>at the phase detector. b) Time domain representation of<br>charge pump output. | 262 |

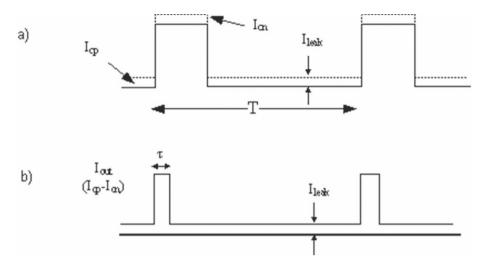

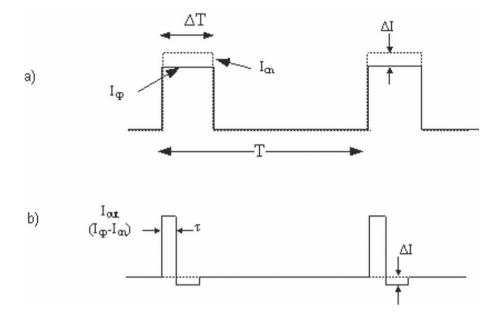

| 12.12 | a) Charge pump up and down current at arbitrary phase offset showing the leakage effect. b) Charge pump output under lock condition.   | 263 |

| 12.13 | Charge pump linear phase analysis showing locking under leakage condition.                                                             | 264 |

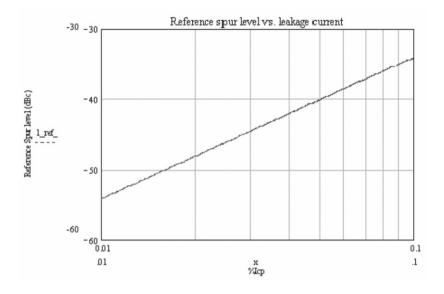

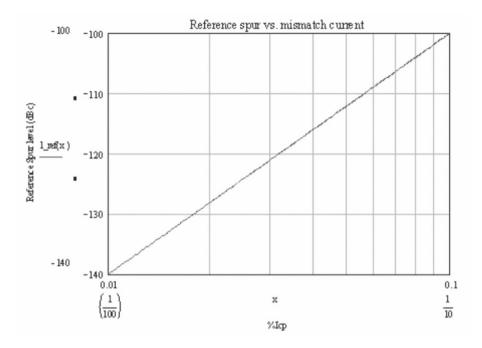

| 12.14 | Reference spur level as a function of leakage current.                                                                                 | 265 |

| 12.15 | <ul><li>a) PLL up and down currents under mismatch condition.</li><li>b) PLL output current in lock condition.</li></ul>               | 266 |

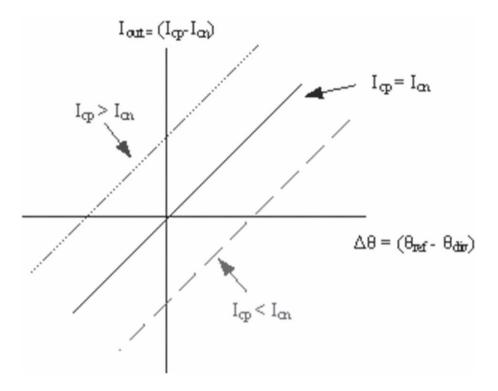

| 12.16 | PLL linear phase plot under different current mismatch conditions.                                                                     | 268 |

| 12.17 | Reference spur level as a function of % mismatch in charge pump current.                                                               | 269 |

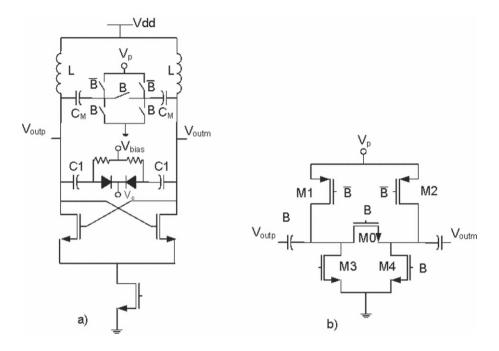

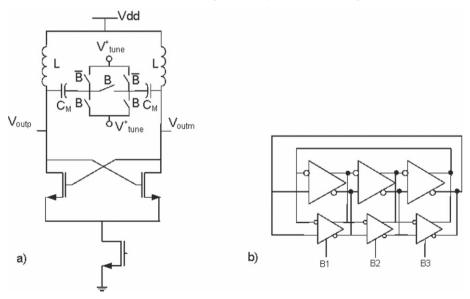

| 12.18 | (a) A digitally calibrated VCO to mitigate reduced tun-<br>ing range due to limited voltage headroom (b) Unit<br>coarse tuning cell.   | 270 |

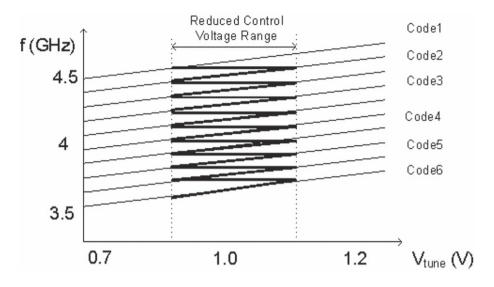

| 12.19 | Reduced effective tuning voltage range of a digitally calibrated VCO.                                                                  | 271 |

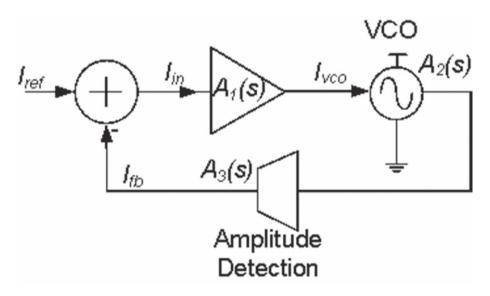

| 12.20 | Block diagram of an analog amplitude controlled VCO.                                                                                   | 271 |

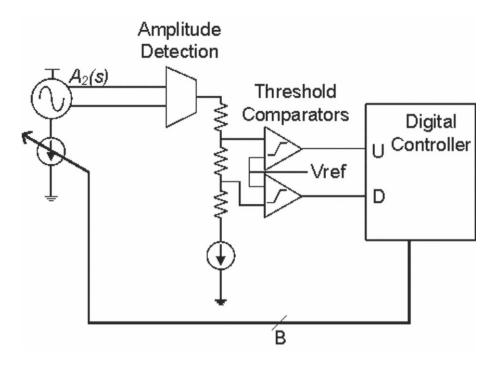

| 12.21 | Block diagram of a digital amplitude controlled VCO.                                                                                   | 272 |

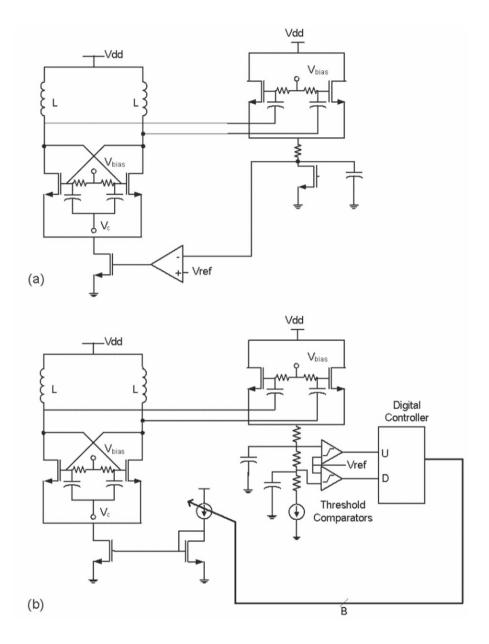

| 12.22 | Circuit level implementation of (a) analog and (b) digital amplitude controlled deep-submicron VCOs.                                   | 273 |

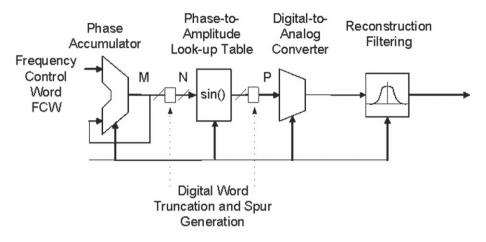

| 12.23 | Typical DDFS with associated word truncation points and spur sources.                                                                  | 274 |

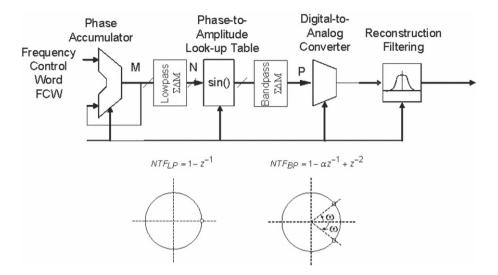

| 12.24 | A $\Sigma\Delta$ DDFS with a lowpass noise shaper before the amplitude LUT and a bandpass noise shaper before the |     |

|-------|-------------------------------------------------------------------------------------------------------------------|-----|

|       | DAC. Associated noise shaping functions and NTF zeros are shown below the DDFS.                                   | 276 |

| 12.25 | a) Basic architecture of fractional-N PLL, b) Fractional                                                          | 278 |

| 12.26 | division example, N=4.25.                                                                                         |     |

| 12.26 | $\Sigma\Delta$ fractional-N synthesizer.                                                                          | 279 |

| 12.27 | Third-order $\Sigma\Delta$ modulator block diagram.                                                               | 280 |

| 12.28 | Noise Spectrum for $3^{rd}$ order $\Sigma \Delta$ MASH modulator.                                                 | 281 |

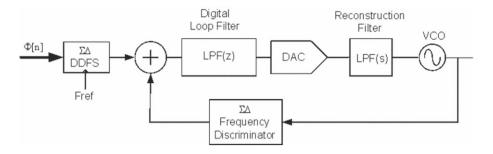

| 12.29 | Block diagram of a frequency discriminator controlled ADPLL.                                                      | 282 |

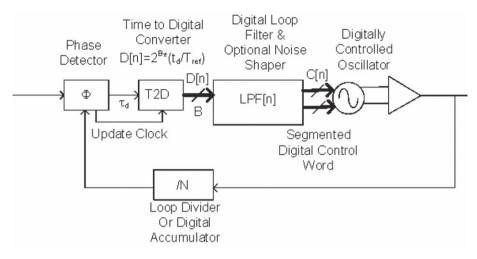

| 12.30 | Block diagram of an ADPLL utilizing a DCO.                                                                        | 283 |

| 12.31 | Typical DCO architectures utilizing a) programmable LC tank circuit b) programmable delay line via unit           |     |

|       | delay cells.                                                                                                      | 283 |

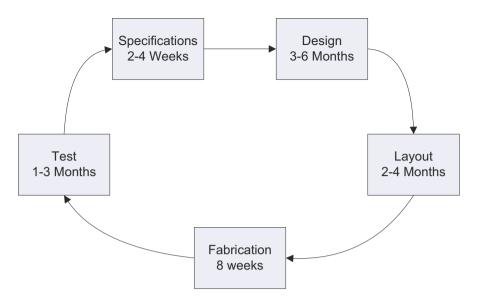

| 13.1  | A typical design cycle can take from 6 to 9 months.                                                               | 289 |

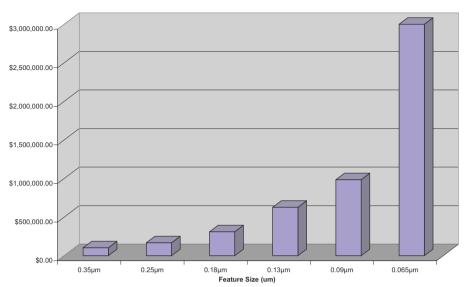

| 13.2  | The price of mask sets are increasing exponentially with every new process generation[1].                         | 290 |

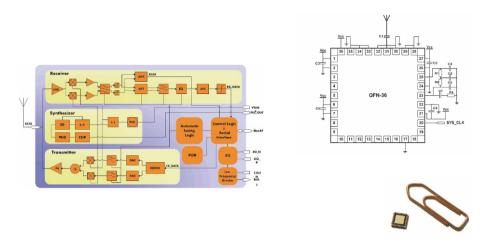

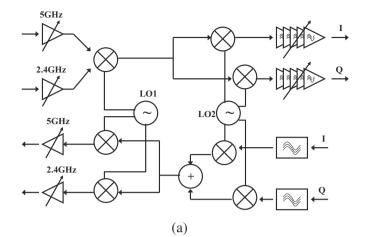

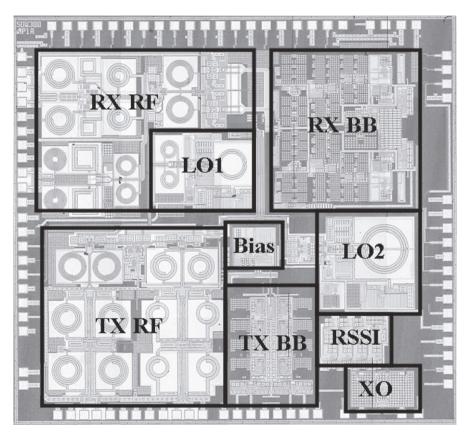

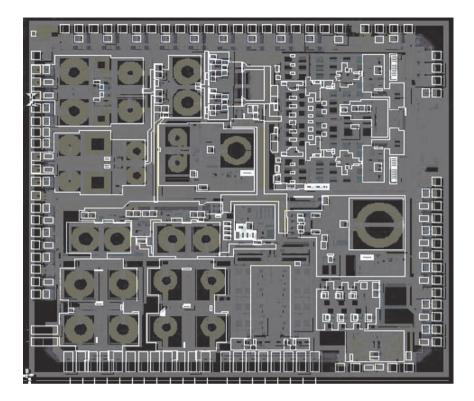

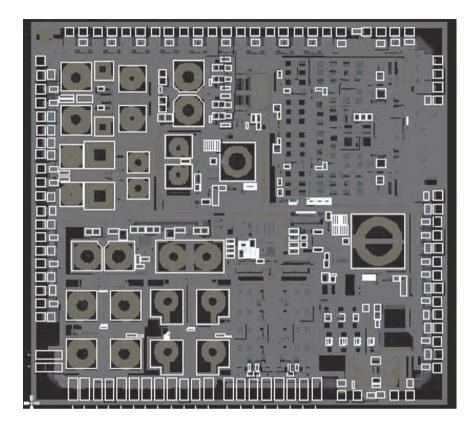

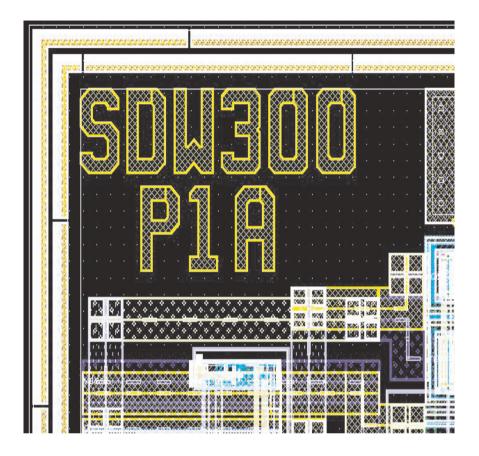

| 13.3  | An 802.11a/b/g WLAN radio transceiver. (a) transciver architecture, (b) chip photo.                               | 291 |

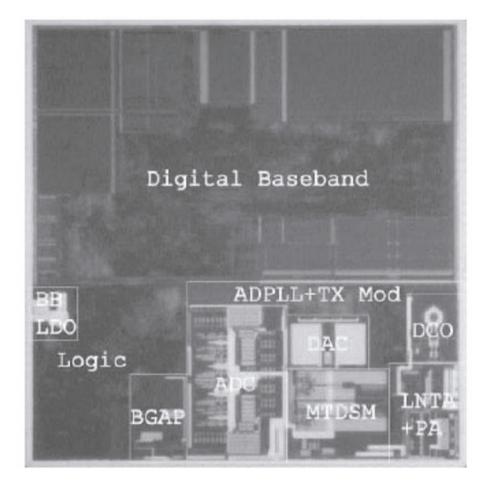

| 13.4  | Texas Instruments Bluetooth transceiver [3].                                                                      | 294 |

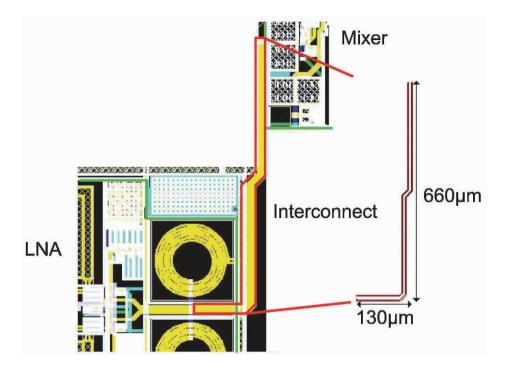

| 13.5  | The routing between the LNA and mixer form part of the LNA resonant tank                                          | 296 |

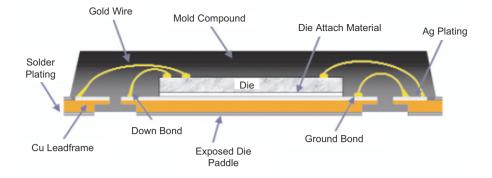

| 13.6  | Example of a QFN package [4].                                                                                     | 298 |

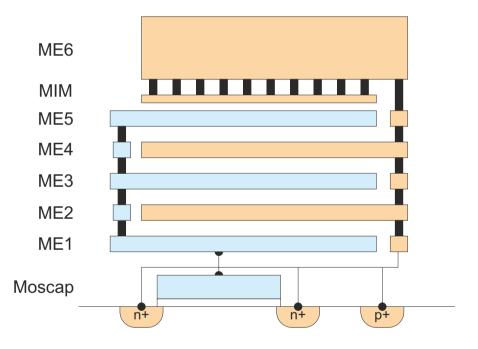

| 13.7  | Unit cell that provides a large capacitance per $\mu$ m <sup>2</sup> and metal density fill.                      | 298 |

| 13.8  | The dummy blocking layers are used to prevent dummy patterns from being added to special areas.                   | 301 |

| 13.9  | The p-implant blocking layer is used to create high re-<br>sistivity substrate regions.                           | 302 |

| 13.10 | The die seal used is a staggered die seal, designed to minimize the noise coupling in the chip.                   | 303 |

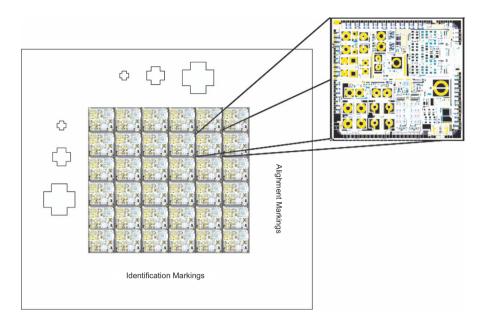

| 13.11 | The reticle is used to provide the stepper with an image large enough to allow for accurate steps.                | 304 |

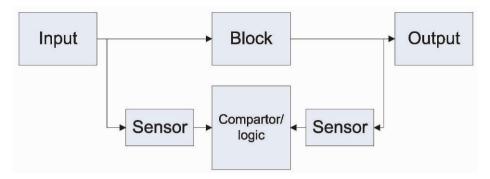

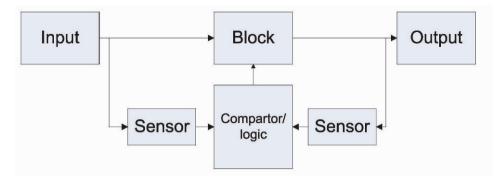

| 13.12 | Being self aware means that the block knows how well<br>it is performing, by measuring its input and output       | 306 |

| 13.13 | Schematic of an RF detector.                                                                                      | 307 |

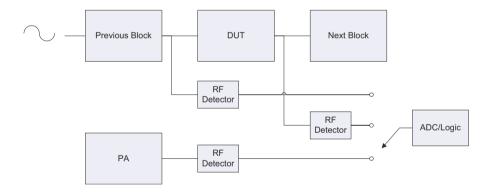

| 13.14 | The RF detector can be calibrated against the PA to get accurate amplitude measurements.                          | 307 |

| 13.15  | To measure the compression point of the DUT, sweep<br>the output power of the PA.                                               | 308 |

|--------|---------------------------------------------------------------------------------------------------------------------------------|-----|

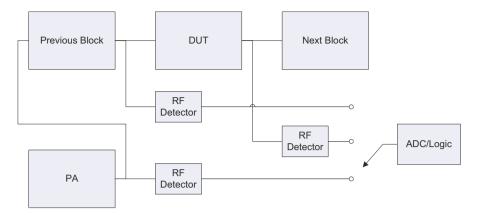

| 13.16a | To measure the IQ imbalance, use both receiver base-<br>bands.                                                                  | 309 |

| 13.16b | To measure one baseband, use both ADCs and DDS from the transmitter.                                                            | 309 |

| 13.17  | Once the cause of the impairments are found, circuit techniques can be used to close the calibration loop.                      | 310 |

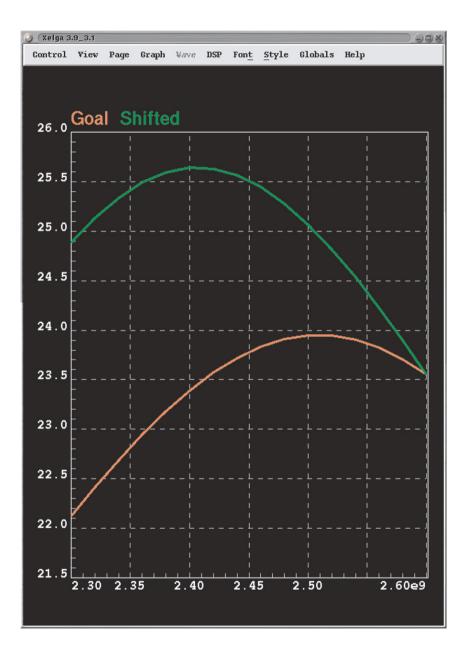

| 13.18  | Through self awareness, the LNA knows that the gain<br>has shifted down by 100MHz, and can retune its tanks<br>to move it back. | 311 |

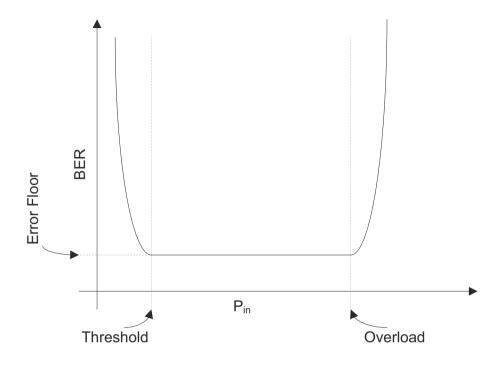

| 13.19  | The threshold and overload points are directly related<br>to the input sensitivity and maximum input power.                     | 313 |

| 13.20  | A system employing self calibration in each block to<br>maximize performance while minimizing power con-                        |     |

|        | sumption.                                                                                                                       | 313 |

|        |                                                                                                                                 |     |

## **List of Tables**

| 3.1 | N, $f_s$ pairs fulfilling our requirement criterion.                                                             | 43  |

|-----|------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Requirements of ISM receiver.                                                                                    | 49  |

| 3.3 | Non-zero coefficient multiplication and summation (S) sequence for the filter implementation shown in Fig. 3.13. | 52  |

| 3.4 | Measured data of the sampling downconversion filter for two different sampling frequencies.                      | 54  |

| 5.1 | FFT computation complexity for different OFDM standards                                                          | 90  |

| 5.2 | OFDM algorithm profiling                                                                                         | 91  |

| 5.3 | Computation complexity for WCDMA-FDD and HSDPA                                                                   | 94  |

| 5.4 | WCDMA algorithm profiling                                                                                        | 95  |

| 5.5 | FEC algorithms usage in common standards                                                                         | 99  |

| 6.1 | Current and Future Radio Architectures                                                                           | 105 |

| 6.2 | ADCs with Outstanding Performance                                                                                | 109 |

| 6.3 | Enabling Technologies and ADC Architectures for SDR/SR                                                           | 112 |

| 6.4 | Performance Summary of the Reconfigurable $\Sigma\Delta$ Modulator 116                                           |     |

| 7.1 | Different wire standards and some basic ADC requirements.                                                        | 124 |

| 7.2 | Topology of the reconfigurable converter in the different modes.                                                 | 137 |

| 7.3 | Summary of results for the different modes of the pro-<br>totype chip design.                                    | 138 |

| 7.4 | Distribution of power consumption over the different blocks in the wideband mode.                                | 139 |

| 8.1 | Execution time results.                                                                                          | 165 |

| 8.2 | Summary of the WCDMA (TDD) and WLAN(802.11b)                                                                     |     |

|     | RF specifications.                                                                                               | 166 |

| 8.3  | Summary of the receiver specs for WCDMA (TDD) and WLAN (802.11b).                                        | 168 |

|------|----------------------------------------------------------------------------------------------------------|-----|

| 8.4  | Parameter distribution for the proposed WCDMA/WLAN multi-standard receiver.                              | 169 |

| 8.5  | Specifications and performance of a typical run for a WCDMA/WLAN multi-standard receiver.                | 170 |

| 9.1  | Measurement results for 3 UWB LNAs.                                                                      | 179 |

| 9.2  | Measurement results for the dual-band LNA.                                                               | 182 |

| 9.3  | Measurement results for the six LNA test circuits.                                                       | 187 |

| 9.4  | Failure current values obtained from TLP testing of the six LNAs.                                        | 188 |

| 10.1 | Example of inductance values and corresponding dimensions                                                | 208 |

| 10.2 | Equivalent circuit component values.                                                                     | 210 |

| 10.3 | Final Design Parameters.                                                                                 | 211 |

| 11.1 | Constants: Modified Wheeler.                                                                             | 221 |

| 11.2 | Constants: Geometric mean distance (GMD).                                                                | 221 |

| 11.3 | Constants: Data-fitted monomial expression.                                                              | 222 |

| 11.4 | Octagonal Inductor Geometries Under Measurement.                                                         | 234 |

| 12.1 | Multi-radio PLL frequencies and bandwidth Standard RX Frequency Range (MHz) TX Frequency Range.          | 245 |

| 12.2 | CMOS technology scaling trends (C. Sodini, RFIC2005).<br>246                                             |     |

| 12.3 | Relation between integrated phase noise and rms phase error. RMS Phase Error.                            | 257 |

| 12.4 | Relative spur attenuation level (dB) for $3^{rd}$ and $4^{th}$ order LPF relative to $2^{nd}$ order LPF. | 260 |

| 13.1 | Parameters to be measured for self awareness                                                             | 306 |

## Preface

As we move beyond third generation (3G) wireless, future handheld wireless devices will be able to access different wireless infrastructures, e.g. cellular, WLAN, WiMaX for a multitude of wireless services including voice, data and multimedia applications. As a result, the radio part of a chipset for such a device will be increasingly complex and challenging. Currently, commercial radio chips are designed in 0.18 and 0.13 micron CMOS technologies. Single chip solutions (radio plus digital baseband) are recently becoming available commercially for Bluetooth, WLAN and GSM. Soon, radio chips will be designed in nanometer (<100 nanometer) technologies. This poses another significant challenge particularly that mask set costs increase exponentially with smaller feature size, market windows are getting narrower and product life cycles are becoming shorter. All this requires that fully integrated radio design achieve first-pass-silicon success.

This book addresses these challenges and discusses key aspects of integrated radio design for future handheld wireless devices. Recognizing the fact that a successful radio design must be done in the context of an end-to-end system solution, the book discusses trends at the wireless network and system levels as well as trends in programmable system-on-chip (SoC) digital baseband solutions and in programmable RF CMOS radio transceivers. To our knowledge, this is the first text on the subject of integrated nanometer radio design and the first to address the radio design problem in the context of a complete end-to-end wireless solution.

By looking at the requirements of super 3G (aka UTRAN/LTE or long Term Evolution), one can see that integrated radio systems of tomorrow will be very complex. Current and future trends call for pushing system integration to the highest levels in order to achieve low cost and low power for large volume products in the consumer and telecom markets ,such as feature-rich handheld battery-operated devices. While CMOS technology scaling to nanometer levels, coupled with innovations in platform based systems and Network-on-Chip

(SoC and NoC) have resulted in great strides with the digital part of a system, the analog, radio or mixed signal part of the total solution remains a major bottleneck. Random process variations do not scale with feature size leading to over design and increased power consumption. Lack of accurate process, package models and RF design kits presents another challenge. Therefore, in today's analog RF design environment, a fully integrated CMOS radio may require several silicon spins before it meets all product specifications and often with relatively low yields. This, results in significant increase in NRE costs, especially when mask set costs increase exponentially as feature size scales down. Furthermore, this could lead to missing important market windows, particularly with the decreasing life cycles of semiconductor products. The choice of topics covered in the book is motivated by the need to minimize integrated RF design risks and to reduce silicon spins.

The book is divided into three main parts. Part I has three chapters and deals with current and future trends in wireless communications and the evolution of wireless chipset development. Part II has four chapters devoted to digital baseband cores and their mixed signal interface to the radio. Part III has 6 chapters devoted to key aspects of fully integrated radio design.

Chapter 1 presents a futuristic view of next generation wireless networks and discusses challenges in system architectures and communication paradigms. Chapter 2 discusses cellular RF requirements and gives an overview of the evolution of cellular chip sets and of the integration trends. Chapter 3 focuses on challenges and design solutions for software defined radios.

Chapters 4 and 5 are devoted to system-on-chip (SoC) design and implementation of programmable digital baseband process cores while Chapters 6 and 7 are focusing on mixed signal and data converters to interface with the digital baseband.

Chapter 8 launches the radio design part of the book and discusses a methodology for the systematic design and optimization of integrated radio receivers. Chapters 9 and 10 discuss key RFIC design aspects of receivers and transmitters respectively while Chapter 11 discusses modeling and computer aided design of on-chip inductors. Chapter 12 deals with design challenges of frequency synthesizers in nanometer technologies. Chapter 13 concludes the book with RF design techniques that minimize design risks, avoids over design and achieves first-pass silicon success.

The book is intended for use by graduate students in electrical and computer engineering as well as system, analog/RF and digital design engineers in the semiconductor and telecom industries. It will also be useful for design managers, project leaders and individuals in marketing and business development.

This book has its roots in lectures by leading experts in the field from both industry and academia given as part of the RaMSiS (Radio and Mixed Signal Integrated Systems) Summer School on Radio Design in Nanometer Technologies held in Visby, Gotland, Sweden in the summer of 2005. We would like to thank all those who assisted us at different phases of this work specially our colleagues of the RaMSiS Group, the Swedish Royal Institute of Technology and of the Analog VLSI Lab at Ohio State. Special Thanks go to all authors for their very valuable and timely contributions, see a complete list of their names and affiliations in the acknowledgements section. We would also like to thank the Springer crew, especially Cindy Zitter for all her help.

Finally, but not least, we would like to thank our families for their understanding and support during the development of this work.

Mohammed Ismail and Delia Rodríguez de Llera González Stockholm, Sweden July 2006

## Acknowledgment

We would like to acknowledge all contributors to this book. We list them below in an alphabetical order:

Stefan Andersson Linköping University, Linköping, Sweden.

Bertan Bakkaloglu Department of Electrical Engineering, Arizona State University, USA.

Burak Çatli Rensselaer Polytechnic Institute, Troy, NY, USA.

Georges Gielen Katholieke Universiteit Leuven, Leuven, Belgium.

Erwin Goris Katholieke Universiteit Leuven, Leuven, Belgium.

Mona Mostafa Hella Rensselaer Polytechnic Institute, Troy, NY, USA.

Ahmed Hemani Royal Institute of Technology, Kista, Sweden.

Sami Hyvonen University of Illinois, Urbana, IL, USA.

Mohammed Ismail Analog VLSI Lab, The Ohio State University, Columbus, USA. RaMSiS Group, Royal Institute of Technology, Stockholm, Sweden.

Yi Ke Katholieke Universiteit Leuven, Leuven, Belgium. Waleed Khalil Intel Corporation, Phoenix, Arizona, USA.

Peter Klapproth Philips Semiconductors BV, Eindhoven, The Netherlands.

Dake Liu Linköping University, Linköping, Sweden.

Sven Mattison Ericsson Mobile Platforms, Lund, Sweden. Anders Nilsson Linköping University, Linköping, Sweden.

Delia Rodríguez de Llera González Royal Institute of Technology, Stockholm, Sweden.

Elyse Rosenbaum University of Illinois, Urbana, IL, USA.

Ana Rusu Royal Institute of Technology (KTH) Stockholm, Sweden. Technical University of Cluj-Napoca, Romania.

Henrik Sjöland Lund University, Lund, Sweden.

Christer Svensson Linköping University, Linköping, Sweden.

Eric Tell Linköping University, Linköping, Sweden.

Niklas Troedsson Lund University, Lund, Sweden.

James Wilson Firstpass Technologies, Inc., Dublin, Ohio, USA.

Jens Zander Wireless@KTH, Royal Institute of Technology, Stockholm, Sweden. PART I

## CURRENT AND FUTURE TRENDS

#### Chapter 1

## "4G" AND THE WIRELESS WORLD 2015 - CHALLENGES IN SYSTEM ARCHITECTURES AND COMMUNICATION PARADIGMS

Jens Zander

#### 1. Introduction

Wireless applications and services are in the next decade likely to become a pervasive, with a widely spread use of wireless devices everywhere. The technology will undergo a transformation, from an expensive, highly visible, "hi-tech" technology as in early cellular phones, over the current state were (almost) everyone owns a mobile phone, to a "disappearing technology" that is present everywhere and taken for granted. Since the current cellular mobile approach, with its excellent mobility management and coverage properties, does to not scale in an economical fashion into large bandwidths, it is more likely that a highly heterogeneous infrastructure will emerge with a large variety of wireless access options. Such a vision challenges many of the current paradigms in mobile communication. In this paper we will discuss these challenges in more detail and give an outlook on some possible directions for research and developments.

Computation and wireless communication capabilities are radically integrated in a great variety of different everyday things, from simple sensors and interactive appliances (cards, rings, eyeglasses...), via pocket and lap-sized devices to wall or table screen working areas. The technology will undergo a transformation, from an expensive, highly visible, "hi-tech" technology as in early cellular phones, over the current state were (almost) everyone owns a mobile phone, to a "disappearing technology" that is present everywhere and taken for granted. The consequence of this vision is that not only wireless terminals but also infrastructure components (similar to electric appliances) need to be no-maintenance/disposable and self-configuring, local access networks that can be deployed in minutes without requiring highly skilled and trained personnel. This will radically lower the entry thresholds for new actors in the infrastructure field which creates new business opportunities and competition. Facility, shop and restaurant owners and even private persons will provide both wireless access to global services as well as "value-added" localized services. The infrastructure components can form integrated parts of a "wireless grid" and be accessible to the public. The large diversity and efficient competition between providers of network & services elements or combinations thereof will provide seamless service according to user preferences. The user priorities tend to change from good coverage to low cost when networks have been deployed in large scale and getting mature.

Two of the key design challenges of the next decade will therefore be

Figure 1.1. Range/Coverage/Mobility - Bandwidth relationship

- How to provide efficient services on a heterogeneous wireless access infrastructure with many network components owned by various business players providing a plethora diverse service offerings,

- How to deploy local high bandwidth access infrastructure in an highly efficient and economical way.

In the following sections we will see how these challenges can be met and what critical research issues still remain open.

#### 2. From the "swiss army knife" ....

As wireless infrastructure system approach higher and higher data rates, the ranges of the individual radios becomes less and less as is illustrated by Figure  $1.1^1$ . This graph in a coarse manner illustrates the range/bandwidth relations of various wireless access systems. All systems are confined to the lower left region, bounded by the solid line, which is basically the "Shannon bound" of communication theory. This limit is due to the fact that a minimum amount of

energy is required to reliably transfer every bit of information. The higher the data rate, the less energy is available for every bit (at constant transmit power) at the transmitter, the less is the range. If we want to push this limit upwards to the right we need either increase the transmitter power<sup>2</sup> or to increase the number of access points. The former path seems closed due to high expectations on battery life and to limit potential health hazards. The latter path on the other hand involves larger investments. It has been shown [1] that the number of access points required grows linearly with the bandwidth provided. Besides high bandwidth, important cost drivers are reliable wide area coverage, high-speed mobility and real-time requirements. In fact, it seems impossible to provide all these four properties simultaneously for reasonable costs. It is for instance reasonably cheap to provide high data rates for internet access (non-realtime) to pedestrians (low mobility) in city centers (small coverage), whereas providing a real-time high rate service to fast mobile terminals all over a sparsely populated country is vastly more expensive.

From a business point of view, the problem is quite clear. An operator needs a sufficiently large number of users for every access point he deploys to eventually recover his investments without claiming un-acceptable prices for his access service. This means that in areas where the user density is low, only a low density of access points can be supported with a corresponding low to moderate data rate. On the other hand, in locations where the user density is high, high data rates is not a problem.

The traditional solution to this problem is to provide access systems with flexible air interfaces that can provide both high rate, short range as well as low rate long range communication. A leading paradigm behind such a solution is that the user terminal can handle only one (albeit very complex) air interface and that a single, world-wide standard is necessary for commercial success. The key drawback of such a "Swiss army knife" system (one system reasonably suited for all purposes) is its complexity and it inherent lack of flexibility. The system will be capable of reliable wide area coverage and high speed handover everywhere, but pedestrian (lap-top) users in city center will only very rarely need those capabilities. In addition there is a risk that the built-in flexibility in the system is not sufficient to meet future needs. Wide-area infrastructure deployment is a matter of decades, whereas user needs may change more rapidly. The large investments required to provide single system coverage everywhere is also a significant barrier against new entrants on the market and effective competition.

#### 3. ... to Navigating the "Wireless Chaos"

A much more attractive scenario would be triggered by the appearance of a flexible multimode terminal. In this scenario, a plethora of specialized access systems would co-exist, each optimized to provide cost effective access for its "niche" market (geographical, mobility, Quality-of-Service etc) without any requirement (on each and every system) for coverage and service everywhere. This would indeed challenge that a single world wide wireless standard is necessary, that a single public operator is needed to provide cost effective physical access. On the contrary one could claim that for broadband local access systems, very high data rates are not that difficult to achieve in a cost-efficient manner provided that high speed mobility may not be the prime interest of the users. In local wireless access the boundaries between fixed and wireless become blurred and local access provisioning will become more and more the business of facilities owners. In rural areas and for vehicular mobility on the other hand, the traditional cellular solutions are the most cost effective ones and are likely to keep their dominating position.

*Figure 1.2.* Heterogeneous wireless infrastructure with a multitude of access with varying properties (range, data rate, mobility etc.)

In this mixed environment, infrastructure deployment can be incremental and the entry thresholds for new niche actors are significantly lower than today. Infrastructure components (access points, routers etc) have to become low cost, user deployable, i.e. self-configuring and low maintenance [3]. In this scenario it is not the individual access schemes, but instead the collection of systems that will provide the universal coverage that we aspire. Terminals are consumer products with a life-cycle of 2-3 years and they are perceived by the buyer to be intimately connected with the applications of choice. Choosing the proper set of air interfaces for a particular terminal is thus not a problem and when each he buys a new terminal it is likely to contain a different set. Still the user wants access to his services in a transparent way and he is likely to be ignorant regarding which air interface his terminal is currently using. The economic advantages of this scenario are significant to all actors - operators do not need to provide coverage everywhere and customers will benefit from effective access competition.

The strict compatibility at the physical layer of the current systems will thus be replaced by interoperability at the network layer. Creating this interoperability in future access is addressed in the IST/FP6 project WWI Ambient Networks [3] which proposes a modular "generalized" internetworking approach, where the provisioning of connections can be achieve across technology and business barriers. The latter is imperative if a competitive environment is to be achieved in the wireless access domain to the benefit of the consumer.

Whereas a key paradigm in traditional cellular system was the spectrum is scarce resource, this no longer holds in our scenario. An important consequence of relaxing the physical layer compatibility, is that different access systems can use different parts of the spectrum. Further, as we go to higher data rates (shorter ranges), spectrum reuse become more effective and international spectrum coordination becomes less of a problem as (short range) signals are less likely to cross national borders. More capable radios also open the possibility of a more effective use of the spectrum - not even the access system of a single provider needs to use the same part of the spectrum in every geographical area and the system may "scavenge" for free spectrum, so called Dynamic Spectrum Access (DSA) [6].

#### 4. Six "Grand Challenges" in Wireless Systems

To make a scenario as outlined above possible we believe that the following six research challenges have to be adequately met. These challenges are based on the work in [9]:

#### I. Scalability and affordability - Creating a wireless communication infrastructure for affordable, mass-market services

As the cost of providing advanced wireless devices continues to decrease, designing cost effective infrastructure solutions capable of providing affordable wireless broadband access (almost) everywhere is one of the key success factors for future wireless systems. This research challenge includes devising novel radio technologies, new system architectural concepts, and new and cost-efficient ways to provide attractive services to end-users.

# **II.** Seamlessness and Transparency - Providing services independently of system technology

One of the success factors of IP networks is the end-to-end principle, which separates services and applications from bit transport. The same service can be provided on a variety of devices (using higher level protocols) without any change in the infrastructure. A key challenge is to preserve such architecture in order to enable easy and dynamic composition of disparate networks amid an ever-increasing heterogeneity of technologies and infrastructures. An additional difficulty is to provide access and services across networks operated by different business actors from various sectors, such as telecommunications, automotive, transportation, medical, industrial control systems etc.

III. Mastering complexity of interaction - Providing high quality services on the edge of technology and artefacts that are easy to use for everyone

A great challenge is how to provide an easy to use, natural, stable, and convenient interface to the user in each situation, in spite of the great complexity of the underlying system. This involves personalized human interfaces, understanding a complex interplay of behaviors, as well as adaptivity and context sensitivity of services and applications.

#### IV. Zero-configuration and reliability through massive redundancy and network robustness - Lowering entry thresholds for new actors in the wireless system market by low cost, simple-to-deploy, and low-maintenance systems and networking components

Future wireless devices and infrastructure components have to be deployed and maintained by owners or users without specific skills and special training. This means that the devices need to be adaptive and self-configuring, sensing their physical and logical environment. The key challenge is to exploit massive redundancy and adaptivity to build secure, robust and highly reliable networks and systems from large number of consumer grade devices.

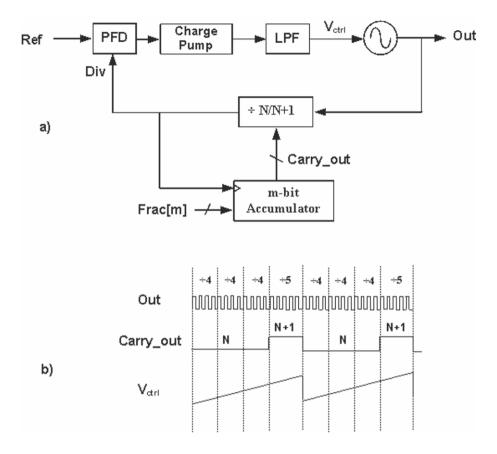

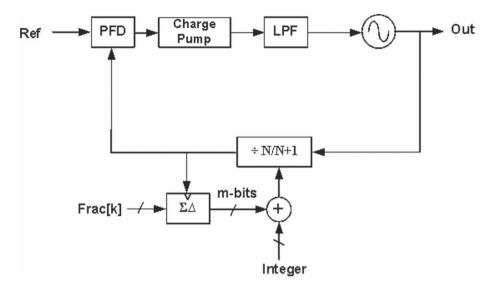

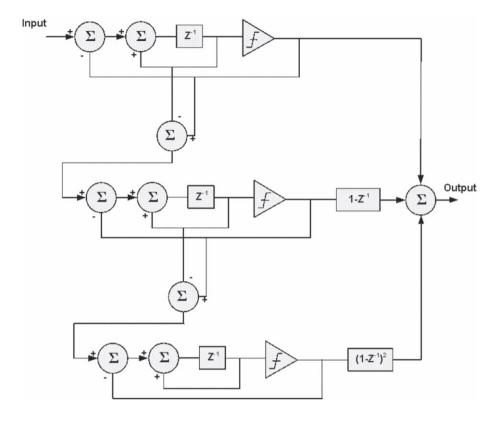

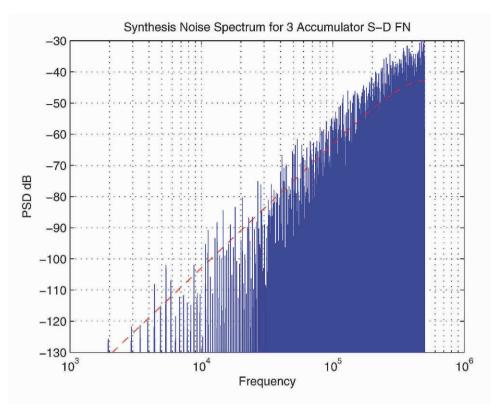

# V. Regulative environment - Lowering regulatory entry barriers for new actors to stimulate the innovation process