Manish Verma Peter Marwedel

# Advanced Memory Optimization Techniques for Low-Power Embedded Processors

Advanced Memory Optimization Techniques for Low-Power Embedded Processors

# Advanced Memory Optimization Techniques for Low-Power Embedded Processors

By

Manish Verma Altera European Technology Center, High Wycombe, UK

and

Peter Marwedel University of Dortmund, Germany

A C.I.P. Catalogue record for this book is available from the Library of Congress.

ISBN-13 978-1-4020-5896-7 (HB) ISBN-13 978-1-4020-5897-4 (e-book)

Published by Springer, P.O. Box 17, 3300 AA Dordrecht, The Netherlands.

www.springer.com

Printed on acid-free paper

All Rights Reserved

© 2007 Springer

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Dedicated to my father

Manish Verma

# Acknowledgments

This work is the accomplishment of the efforts of several people without whom this work would not have been possible. Numerous technical discussions with our colleagues, *viz.* Heiko Falk, Robert Pyka, Jens Wagner and Lars Wehmeyer, at Department of Computer Science XII, University of Dortmund have been a greatly helpfull in bringing the book in its current shape. Special thanks goes to Mrs. Bauer for so effortlessly managing our administrative requests.

Finally, we are deeply indebted to our families for their unflagging support, unconditional love and countless sacrifices.

Dortmund, November 2006

Manish Verma Peter Marwedel

# Contents

| 1 | Intr                                                      | oductio                                                                                                | n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                        |

|---|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|   | 1.1                                                       | Design                                                                                                 | n of Consumer Oriented Embedded Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2                                                        |

|   |                                                           | 1.1.1                                                                                                  | Memory Wall Problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2                                                        |

|   |                                                           | 1.1.2                                                                                                  | Memory Hierarchies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3                                                        |

|   |                                                           | 1.1.3                                                                                                  | Software Optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4                                                        |

|   | 1.2                                                       | Contri                                                                                                 | butions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5                                                        |

|   | 1.3                                                       | Outlin                                                                                                 | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6                                                        |

| 2 | Rela                                                      | nted Wo                                                                                                | rk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9                                                        |

|   | 2.1                                                       | Power                                                                                                  | and Energy Relationship                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9                                                        |

|   |                                                           | 2.1.1                                                                                                  | Power Dissipation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9                                                        |

|   |                                                           | 2.1.2                                                                                                  | Energy Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11                                                       |

|   | 2.2                                                       | Survey                                                                                                 | on Power and Energy Optimization Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11                                                       |

|   |                                                           | 2.2.1                                                                                                  | Power vs. Energy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12                                                       |

|   |                                                           | 2.2.2                                                                                                  | Processor Energy Optimization Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12                                                       |

|   |                                                           | 2.2.3                                                                                                  | Memory Energy Optimization Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 14                                                       |

|   |                                                           |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

| 3 | Mer                                                       | nory Av                                                                                                | vare Compilation and Simulation Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17                                                       |

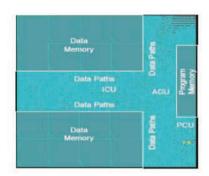

| 3 | <b>Mer</b><br>3.1                                         |                                                                                                        | vare Compilation and Simulation Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17<br>19                                                 |

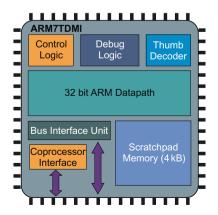

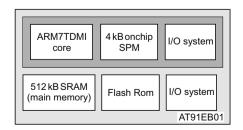

| 3 |                                                           |                                                                                                        | rocessor ARM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                          |

| 3 |                                                           | Uni-Pı                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19                                                       |

| 3 |                                                           | Uni-Pı<br>3.1.1                                                                                        | ocessor ARM<br>Energy Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19<br>20                                                 |

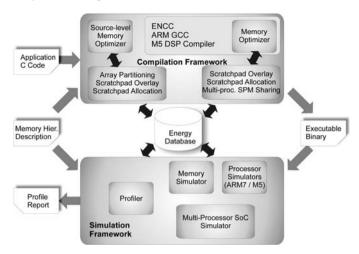

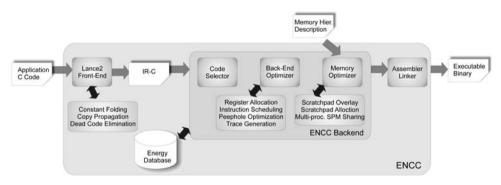

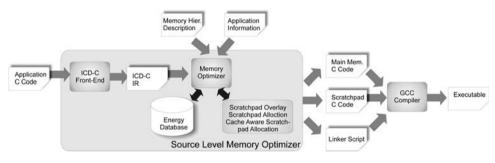

| 3 |                                                           | Uni-Pi<br>3.1.1<br>3.1.2                                                                               | cocessor ARM          Energy Model          Compilation Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 19<br>20<br>22                                           |

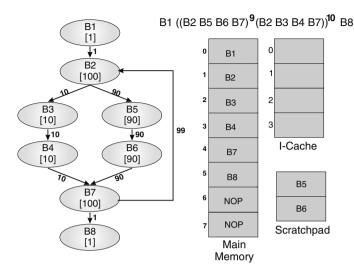

| 3 |                                                           | Uni-Pr<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4                                                             | cocessor ARM         Energy Model         Compilation Framework         Instruction Cache Optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 19<br>20<br>22<br>23                                     |

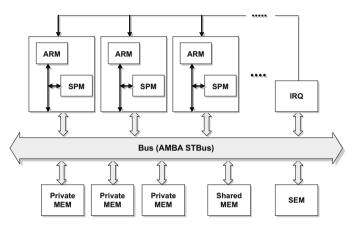

| 3 | 3.1                                                       | Uni-Pr<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4                                                             | Processor ARM         Energy Model         Compilation Framework         Instruction Cache Optimization         Simulation and Evaluation Framework         Processor ARM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19<br>20<br>22<br>23<br>24                               |

| 3 | 3.1                                                       | Uni-Pr<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>Multi-                                                   | cocessor ARM         Energy Model         Compilation Framework         Instruction Cache Optimization         Simulation and Evaluation Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19<br>20<br>22<br>23<br>24<br>26<br>27                   |

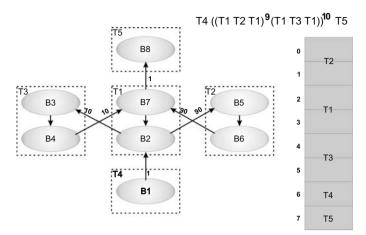

| 3 | 3.1                                                       | Uni-Pr<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>Multi-<br>3.2.1<br>3.2.2                                 | Processor ARM         Energy Model         Compilation Framework         Instruction Cache Optimization         Simulation and Evaluation Framework         Processor ARM         Energy Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 19<br>20<br>22<br>23<br>24<br>26<br>27<br>27             |

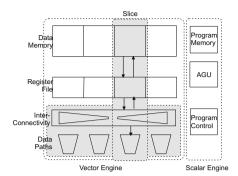

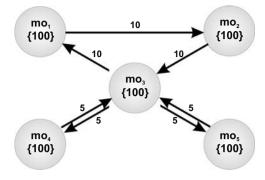

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul>             | Uni-Pn<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>Multi-<br>3.2.1<br>3.2.2<br>M5 DS                        | Processor ARM         Energy Model         Compilation Framework         Instruction Cache Optimization         Simulation and Evaluation Framework         Processor ARM         Energy Model         Compilation Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 19<br>20<br>22<br>23<br>24<br>26<br>27<br>27             |

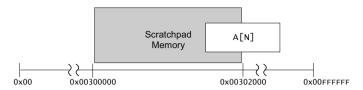

|   | <ul><li>3.1</li><li>3.2</li><li>3.3</li><li>Non</li></ul> | Uni-Pr<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>Multi-<br>3.2.1<br>3.2.2<br>M5 DS<br>-Overla             | Processor ARM         Energy Model         Compilation Framework         Instruction Cache Optimization         Simulation and Evaluation Framework         Processor ARM         Energy Model         Compilation Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 19<br>20<br>22<br>23<br>24<br>26<br>27<br>27<br>29       |

|   | <ul><li>3.1</li><li>3.2</li><li>3.3</li><li>Non</li></ul> | Uni-Pr<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>Multi-<br>3.2.1<br>3.2.2<br>M5 DS<br>-Overla<br>Main / S | with a state of the state | 19<br>20<br>22<br>23<br>24<br>26<br>27<br>27<br>29<br>31 |

| х | Contents |

|---|----------|

| х | Contents |

|   | 4.3  | Related Work                                       | 35 |

|---|------|----------------------------------------------------|----|

|   | 4.4  | Problem Formulation and Analysis                   | 36 |

|   |      | 4.4.1 Memory Objects                               | 36 |

|   |      | 4.4.2 Energy Model                                 | 37 |

|   |      | 4.4.3 Problem Formulation                          | 38 |

|   | 4.5  | Non-Overlayed Scratchpad Allocation                | 39 |

|   |      | 4.5.1 Optimal Non-Overlayed Scratchpad Allocation  | 39 |

|   |      |                                                    | 40 |

|   | 4.6  |                                                    | 41 |

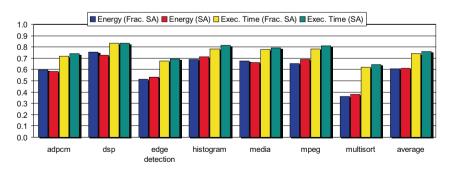

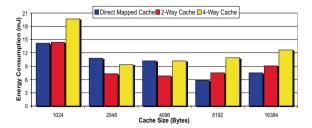

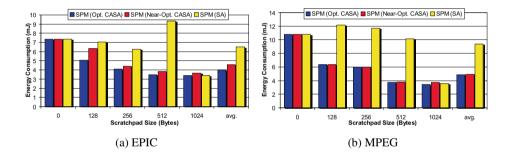

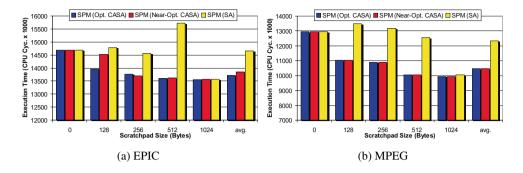

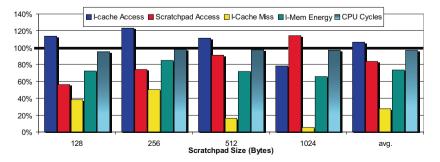

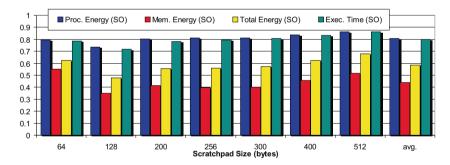

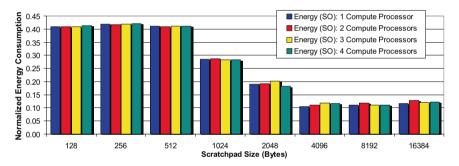

|   |      | 4.6.1 Uni-Processor ARM                            | 41 |

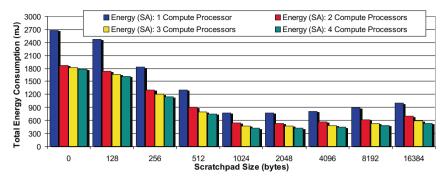

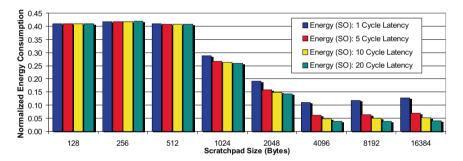

|   |      | 4.6.2 Multi-Processor ARM                          | 44 |

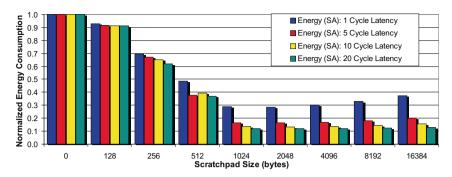

|   |      | 4.6.3 M5 DSP                                       | 46 |

|   | 4.7  | Summary                                            | 47 |

|   |      | •                                                  |    |

| 5 |      | -Overlayed Scratchpad Allocation Approaches for    |    |

|   |      |                                                    | 49 |

|   | 5.1  | Introduction                                       | 49 |

|   | 5.2  |                                                    | 51 |

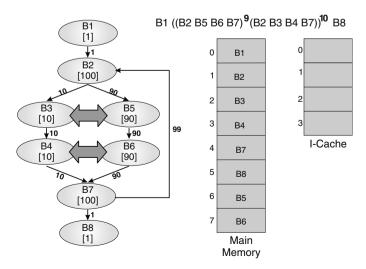

|   | 5.3  | Motivating Example                                 | 54 |

|   |      | 5.3.1 Base Configuration                           | 54 |

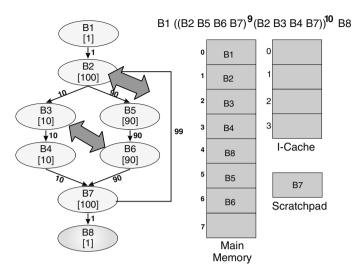

|   |      | 5.3.2 Non-Overlayed Scratchpad Allocation Approach | 55 |

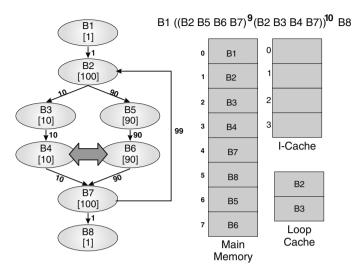

|   |      | 5.3.3 Loop Cache Approach                          | 56 |

|   |      | 5.3.4 Cache Aware Scratchpad Allocation Approach   | 57 |

|   | 5.4  | Problem Formulation and Analysis                   | 58 |

|   |      | 5.4.1 Architecture                                 | 59 |

|   |      | 5.4.2 Memory Objects                               | 59 |

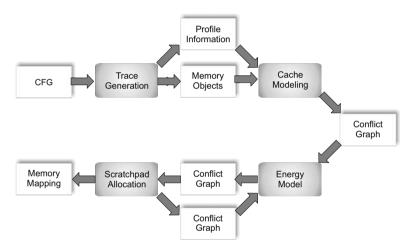

|   |      | 5.4.3 Cache Model (Conflict Graph)                 | 60 |

|   |      | 5.4.4 Energy Model                                 | 61 |

|   |      | 5.4.5 Problem Formulation                          | 63 |

|   | 5.5  | Cache Aware Scratchpad Allocation                  | 64 |

|   |      |                                                    | 65 |

|   |      |                                                    | 67 |

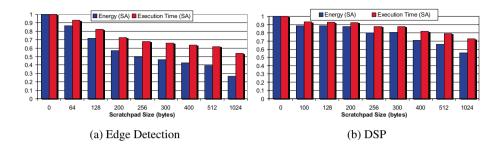

|   | 5.6  |                                                    | 68 |

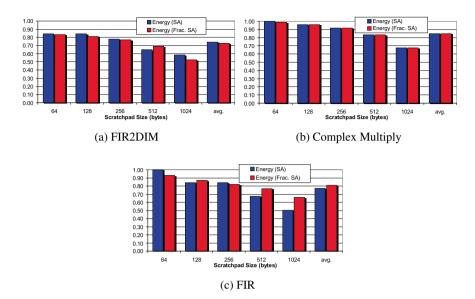

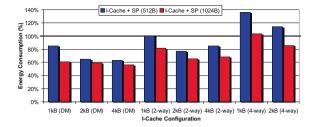

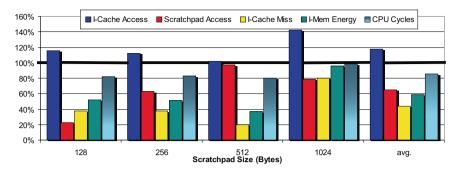

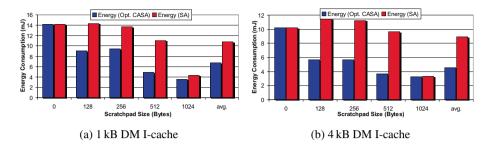

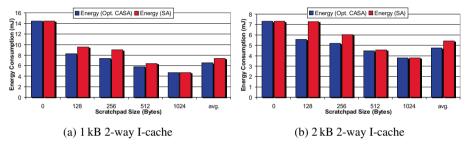

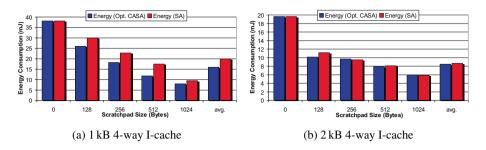

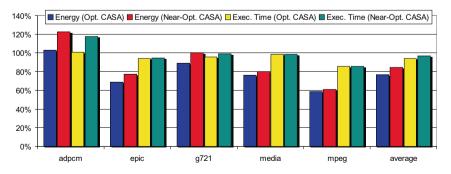

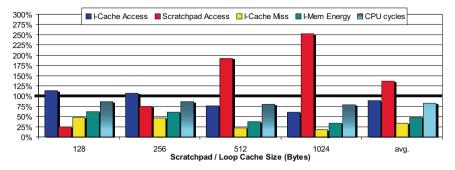

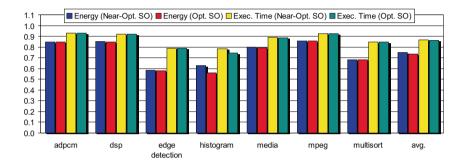

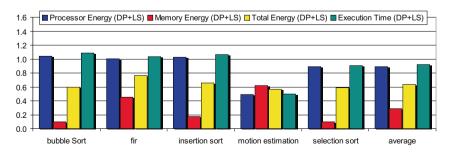

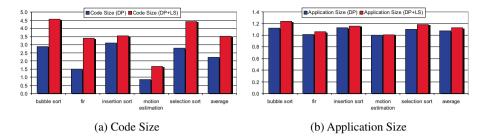

|   |      | 1                                                  | 68 |

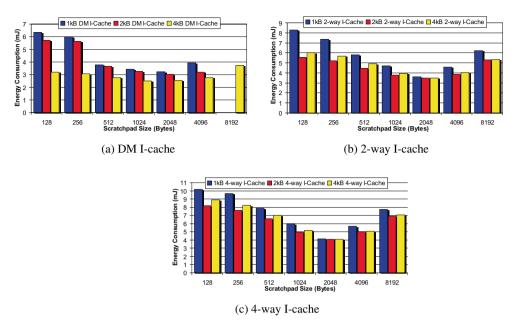

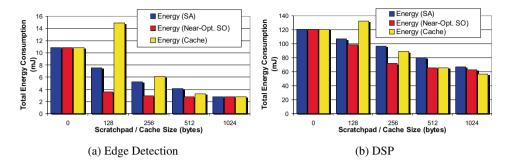

|   |      |                                                    | 78 |

|   |      |                                                    | 80 |

|   | 5.7  |                                                    | 81 |

|   |      |                                                    |    |

| 6 | Scra | atchpad Overlay Approaches for Main / Scratchpad   |    |

|   | Mer  | nory Hierarchy                                     | 83 |

|   | 6.1  | Introduction                                       | 83 |

|   | 6.2  |                                                    | 85 |

|   | 6.3  |                                                    | 86 |

|   | 6.4  |                                                    | 88 |

|   |      | •                                                  | 89 |

|   |      |                                                    | 90 |

|   |      |                                                    |    |

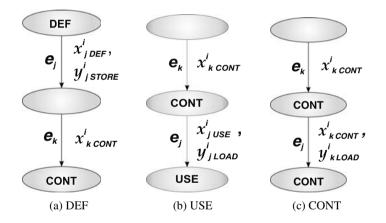

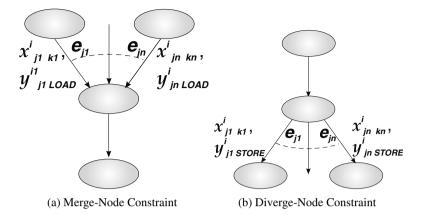

|   |      | 6.4.3 Livene   | ess Analysis                                           | 90  |

|---|------|----------------|--------------------------------------------------------|-----|

|   |      | 6.4.4 Energy   | y Model                                                | 95  |

|   |      | 6.4.5 Proble   | m Formulation                                          | 97  |

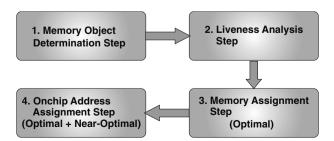

|   | 6.5  | Scratchpad Ov  | verlay Approaches                                      | 98  |

|   |      | 6.5.1 Optima   | al Memory Assignment                                   | 98  |

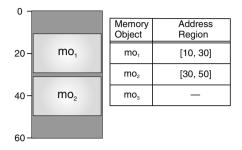

|   |      | 6.5.2 Optima   | al Address Assignment                                  | 105 |

|   |      | 6.5.3 Near-O   | Optimal Address Assignment                             | 108 |

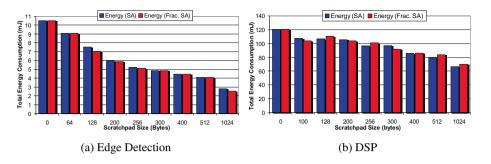

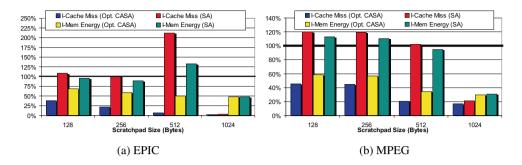

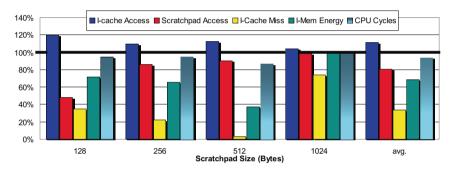

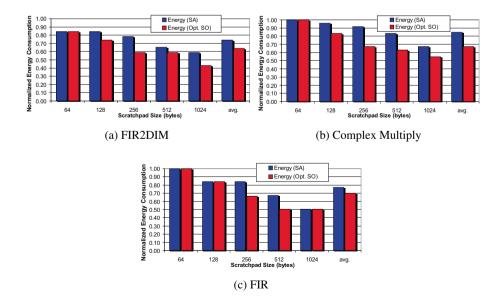

|   | 6.6  | Experimental   | Results                                                | 109 |

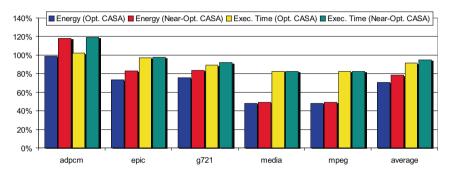

|   |      | 6.6.1 Uni-Pr   | rocessor ARM                                           | 109 |

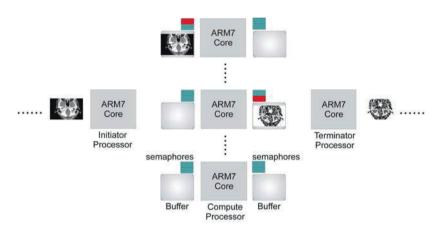

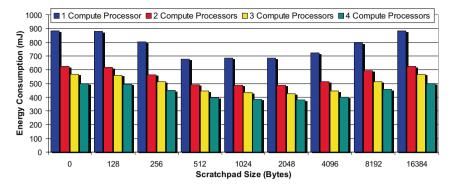

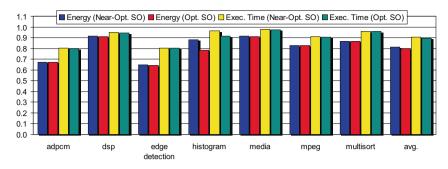

|   |      | 6.6.2 Multi-   | Processor ARM                                          | 116 |

|   |      | 6.6.3 M5 DS    | SP                                                     | 118 |

|   | 6.7  | Summary        |                                                        | 119 |

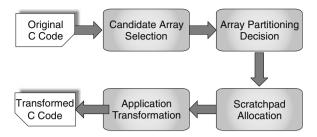

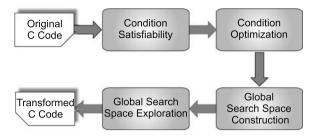

| 7 | Data | Partitioning a | and Loop Nest Splitting                                | 121 |

|   | 7.1  |                |                                                        |     |

|   | 7.2  |                |                                                        |     |

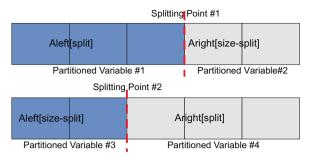

|   | 7.3  |                | ulation and Analysis                                   |     |

|   |      |                | oning Candidate Array                                  |     |

|   |      |                | ng Point                                               |     |

|   |      | 7.3.3 Memo     | ry Objects                                             | 127 |

|   |      |                | y Model                                                |     |

|   |      | 0.             | m Formulation                                          |     |

|   | 7.4  |                | ing                                                    |     |

|   |      |                | r Linear Programming Formulation                       |     |

|   | 7.5  |                | litting                                                |     |

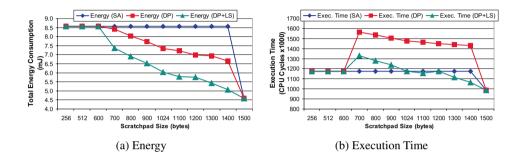

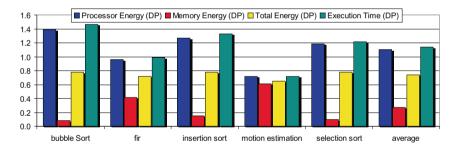

|   | 7.6  |                | Results                                                |     |

|   | 7.7  | Summary        |                                                        | 139 |

| 8 | Scra | tchpad Sharin  | g Strategies for Multiprocess Applications             | 141 |

|   | 8.1  | -              |                                                        |     |

|   | 8.2  |                | ample                                                  |     |

|   | 8.3  | -              | r                                                      |     |

|   | 8.4  |                | for Problem Formulation                                |     |

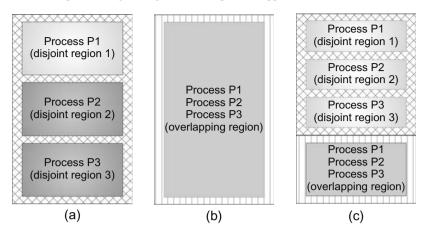

|   |      |                | on                                                     |     |

|   |      |                | n Variables                                            |     |

|   |      | •              | ry Objects                                             |     |

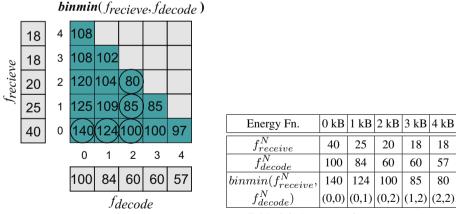

|   |      |                | y Model                                                |     |

|   | 8.5  |                | on-Saving/Restoring Context Switch (Non-Saving)        |     |

|   |      | -              |                                                        | 148 |

|   |      |                | m Formulation                                          |     |

|   |      |                | thm for Non-Saving Approach                            |     |

|   | 8.6  |                | wing/Restoring Context Switch (Saving) Approach        |     |

|   |      |                | m Formulation                                          |     |

|   |      |                | thm for Saving Approach                                |     |

|   | 8.7  | 0              | hpad Saving/Restoring Context Switch (Hybrid) Approach |     |

|   |      |                | m Formulation                                          |     |

|      |                       | 8.7.2 Algorithm for Hybrid Approach                 | <br>158                   |

|------|-----------------------|-----------------------------------------------------|---------------------------|

|      | 8.8                   | Experimental Setup                                  | <br>160                   |

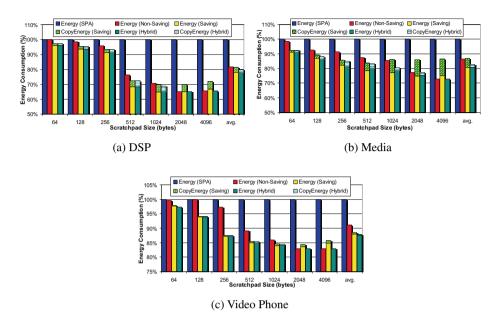

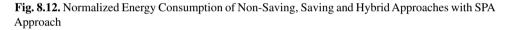

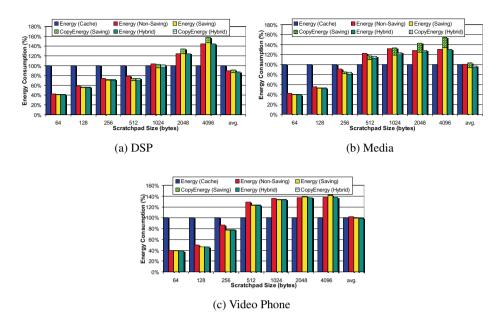

|      | 8.9                   | Experimental Results                                |                           |

|      | 8.10                  | Summary                                             |                           |

| 9    | Cone                  | clusions and Future Directions                      | <br>167                   |

|      | 9.1                   | Research Contributions                              | <br>167                   |

|      | 9.2                   | Future Directions                                   | <br>170                   |

|      |                       |                                                     |                           |

| Α    | Theo                  | oretical Analysis for Scratchpad Sharing Strategies | <br>171                   |

| A    |                       |                                                     |                           |

| A    | A.1                   | Formal Definitions       Correctness Proof          | <br>171                   |

|      | A.1<br>A.2            | Formal Definitions                                  | <br>171<br>171            |

| List | A.1<br>A.2<br>t of Fi | Formal Definitions                                  | <br><br>171<br>171<br>175 |

xii

Contents

# Introduction

In a relatively short span of time, computers have evolved from huge mainframes to small and elegant desktop computers, and now to low-power, ultra-portable handheld devices. With each passing generation, computers consisting of processors, memories and peripherals became smaller and faster. For example, the first commercial computer UNIVAC I costed \$1 million dollars, occupied 943 cubic feet space and could perform 1,905 operations per second [94]. Now, a processor present in an electric shaver easily outperforms the early mainframe computers.

The miniaturization is largely due to the efforts of engineers and scientists that made the expeditious progress in the microelectronic technologies possible. According to Moore's Law [90], the advances in technology allow us to double the number of transistors on a single silicon chip every 18 months. This has lead to an exponential increase in the number of transistors on a chip, from 2,300 in an Intel 4004 to 42 millions in Intel Itanium processor [55]. Moore's Law has withstood for 40 years and is predicted to remain valid for at least another decade [91].

Not only the miniaturization and dramatic performance improvement but also the significant drop in the price of processors, has lead to situation where they are being integrated into products, such as cars, televisions and phones which are not usually associated with computers. This new trend has also been called the *disappearing computer*, where the computer does not actually disappear but it is everywhere [85].

Digital devices containing processors now constitute a major part of our daily lives. A small list of such devices includes microwave ovens, television sets, mobile phones, digital cameras, MP3 players and cars. Whenever a system comprises of information processing digital devices to control or to augment its functionality, such a system is termed *an embedded system*. Therefore, all the above listed devices can be also classified as *embedded systems*. In fact, it should be no surprise to us that the number of operational embedded systems has already surpassed the human population on this planet [1].

Although the number and the diversity of embedded systems is huge, they share a set of common and important characteristics which are enumerated below:

(a) Most of the embedded systems perform a fixed and *dedicated* set of functions. For example, the microprocessor which controls the fuel injection system in a car will perform the same functions for its entire life-time.

- 2 1 Introduction