## Seetharaman Ramachandran

# Digital VLSI Systems Design

A Design Manual for Implementation of Projects on FPGAs and ASICs using Verilog

DIGITAL VLSI SYSTEMS DESIGN

# Digital VLSI Systems Design

## A Design Manual for Implementation of Projects on FPGAs and ASICs Using Verilog

By

#### Dr. S. Ramachandran

Indian Institute of Technology Madras, India

A C.I.P. Catalogue record for this book is available from the Library of Congress.

ISBN 978-1-4020-5828-8 (HB) ISBN 978-1-4020-5829-5 (e-book)

Published by Springer, P.O. Box 17, 3300 AA Dordrecht, The Netherlands.

www.springer.com

#### Printed on acid-free paper

"Figures/Materials based on or adapted from figures and text owned by and are courtesy of Xilinx, Inc. © Xilinx, Inc. 1994-2007. All rights reserved."

"Figures/Materials based on or adapted from figures and text owned by and are courtesy of Mentor graphics, Corp. © Mentor graphics, Corp. All rights reserved."

"Figures/Materials based on or adapted from figures and text owned by and are courtesy of Synplicity Inc. © Synplicity Inc. 2007. All rights reserved."

"Figures/Materials based on or adapted from figures and text owned by and are courtesy of XESS, Corp. © XESS, Corp. 1998-2006. All rights reserved."

The rights of the editors and the author of the works herein have been asserted by them in accordance with the Copyright, Designs and Patents Act.

Verilog/Matlab codes presented in the book, CD or solution manual shall not be used directly/indirectly for any commercial production, be it for manufacture of integrated circuit chips or for IP cores.

All Rights Reserved © 2007 Springer No part of this work may be reproduced, stored in a retrieval system, or transmitted

in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

### Contents

| Preface   |                                                             | • xiii |

|-----------|-------------------------------------------------------------|--------|

| Chapter 1 | Introduction to Digital VLSI Systems Design                 | 3      |

| 1.1       | Evolution of VLSI Systems                                   | 4      |

| 1.2       | Applications of VLSI Systems                                | 5      |

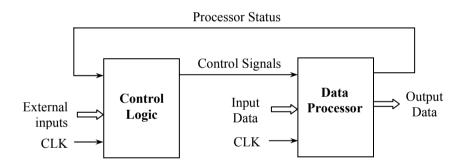

| 1.3       | Processor Based Systems                                     | 7      |

| 1.4       | Embedded Systems                                            |        |

| 1.5       | FPGA Based Systems                                          |        |

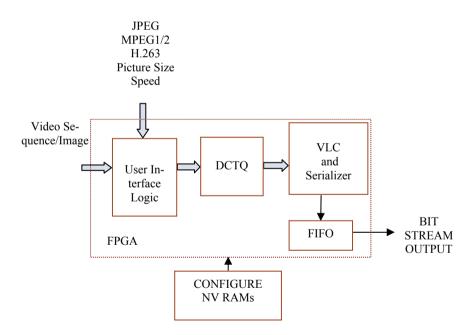

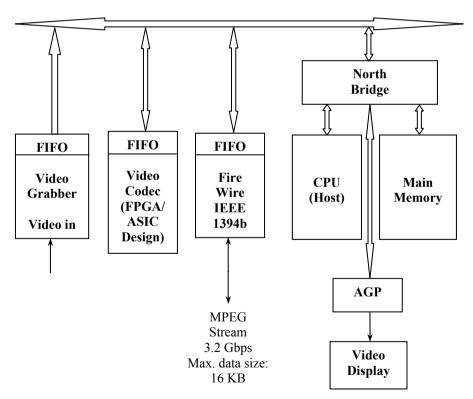

|           | 1.5.1 FPGA Based Design: Video Compression<br>as an Example |        |

| 1.6       | Digital System Design Using FPGAs                           |        |

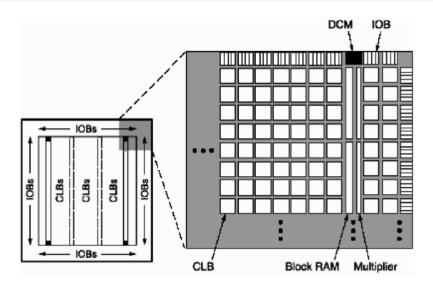

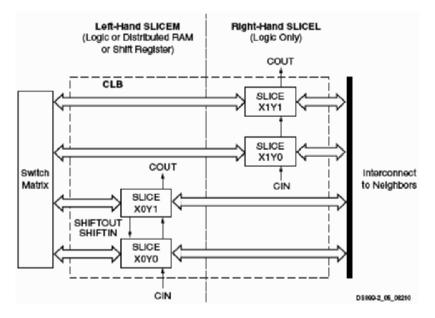

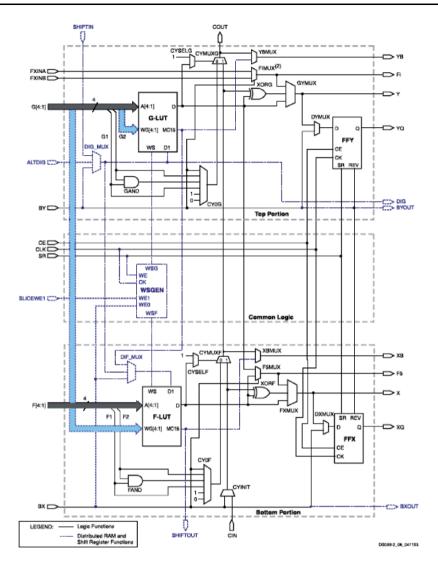

|           | 1.6.1 Spartan-3 FPGAs                                       |        |

| 1.7       | Reconfigurable Systems Using FPGAs                          |        |

| 1.8       | Scope of the Book                                           |        |

|           | 1.8.1 Approach                                              |        |

| Chapter 2 | Review of Digital Systems Design                            | 33     |

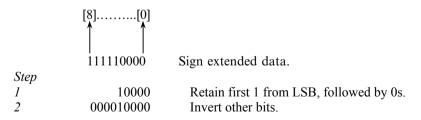

| 2.1       | Numbering Systems                                           | 33     |

| 2.2       | Twos Complement Addition/Subtraction                        |        |

| 2.3       | Codes                                                       |        |

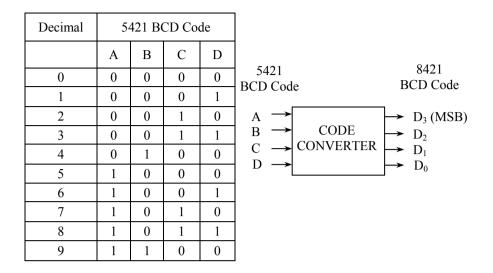

|           | 2.3.1 Binary and BCD Codes                                  |        |

|           | 2.3.2 Gray Code                                             |        |

|           | 2.3.3 ASCII Code                                            |        |

|           | 2.3.4 Error Detection Code                                  |        |

| 2.4       | Boolean Algebra                                             |        |

| 2.5       | Boolean Functions Using Minterms and Maxterms               |        |

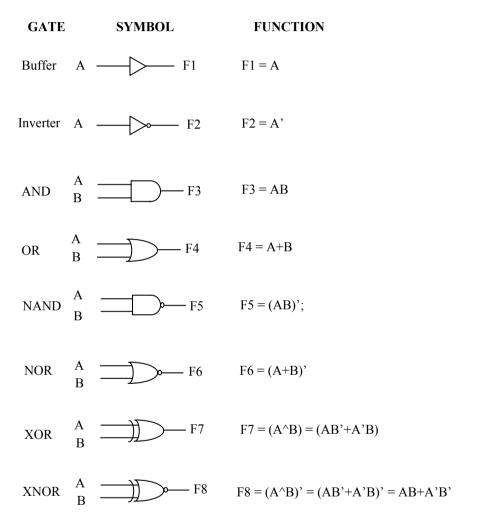

| 2.6       | Logic Gates                                                 |        |

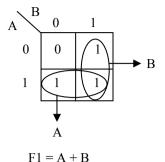

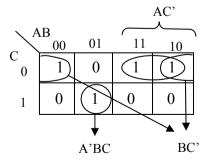

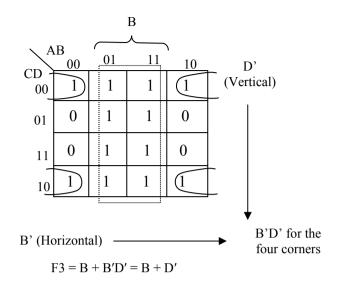

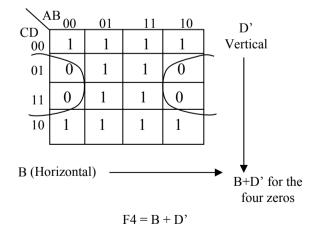

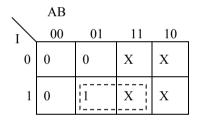

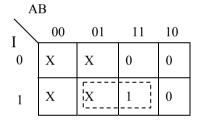

| 2.7       | The Karnaugh MAP Method of Optimization                     |        |

|           | of Logic Circuits                                           | 47     |

| 2.8       | Combination Circuits                                        |        |

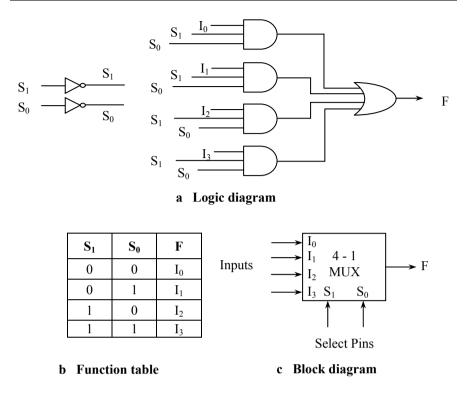

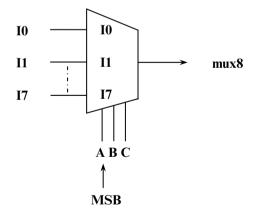

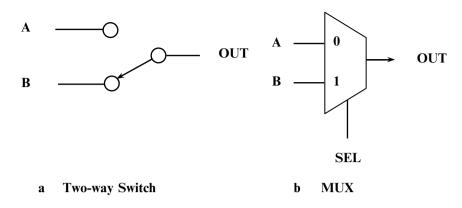

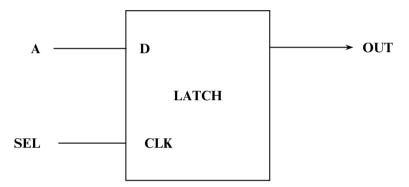

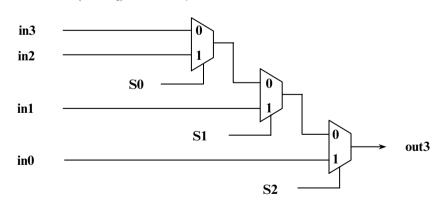

|           | 2.8.1 Multiplexers.                                         |        |

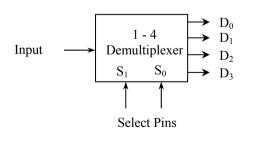

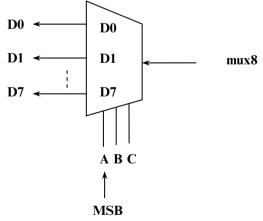

|           | 2.8.2 Demultiplexers.                                       |        |

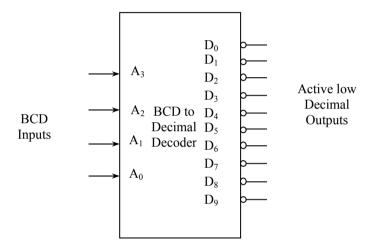

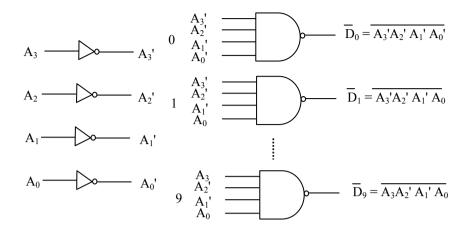

|           | 2.8.3 Decoders                                    | 52  |

|-----------|---------------------------------------------------|-----|

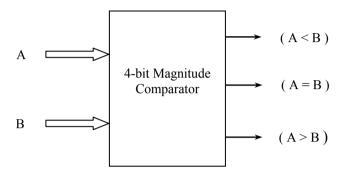

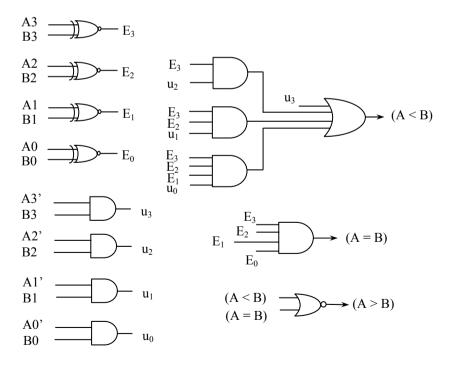

|           | 2.8.4 Magnitude Comparator                        | 53  |

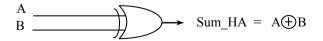

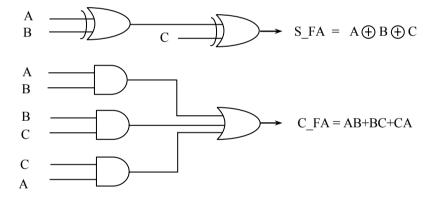

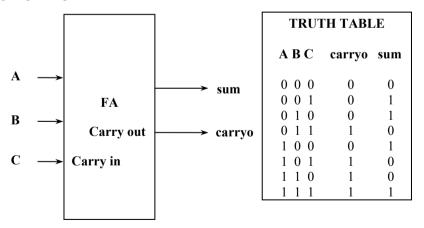

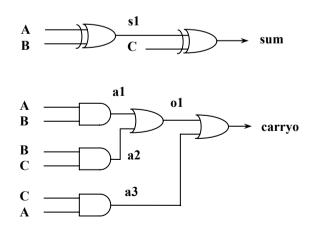

|           | 2.8.5 Adder/Subtractor Circuits                   |     |

|           | 2.8.6 SSI and MSI Components                      |     |

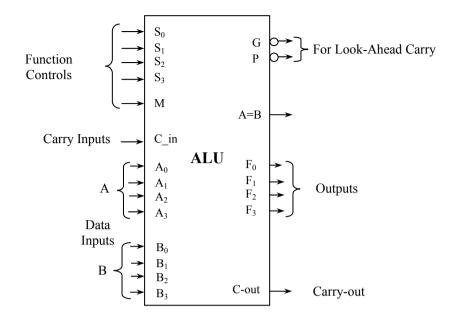

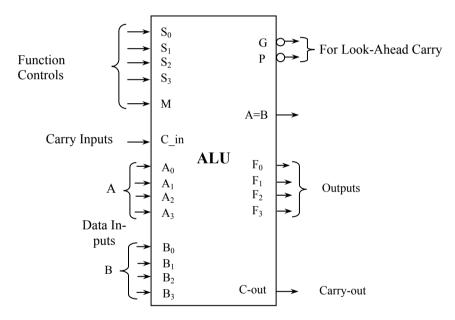

| 2.9       | Arithmetic Logic Unit                             | 58  |

| 2.10      | Programmable Logic Devices                        | 59  |

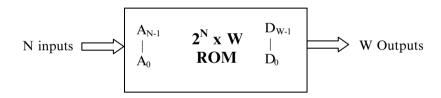

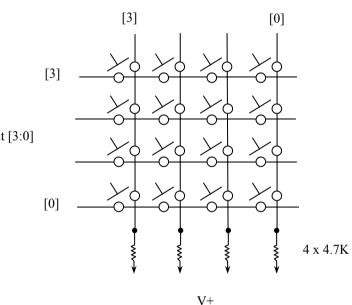

|           | 2.10.1 Read-Only Memory                           | 61  |

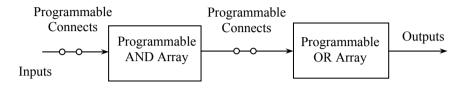

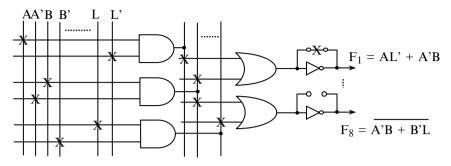

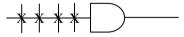

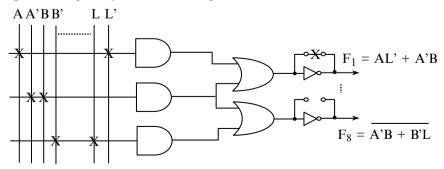

|           | 2.10.2 Programmable Logic Array (PLA)             | 62  |

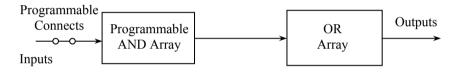

|           | 2.10.3 Programmable Array Logic (PAL)             | 63  |

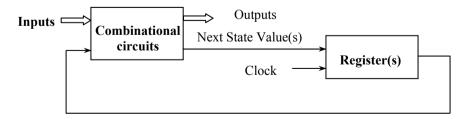

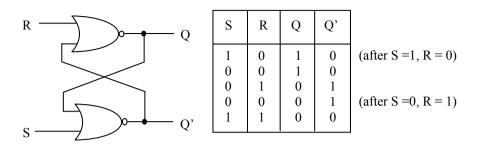

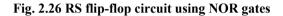

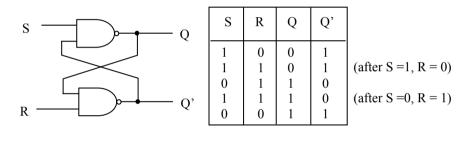

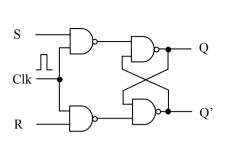

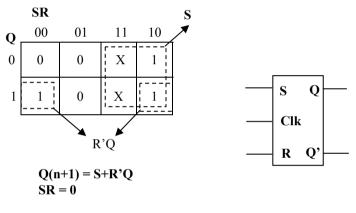

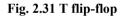

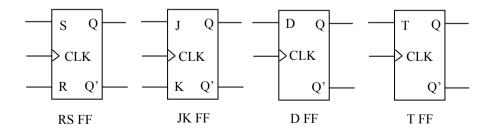

| 2.11      | Sequential Circuits                               |     |

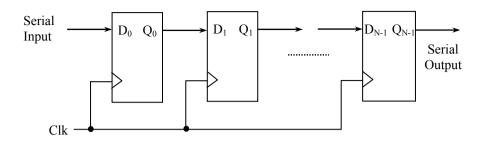

| 2.12      | Random Access Memory (RAM)                        | 72  |

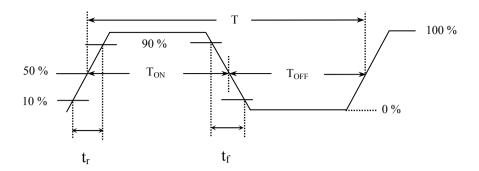

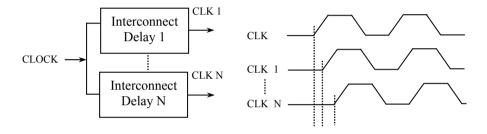

| 2.13      | Clock Parameters and Skew                         | 73  |

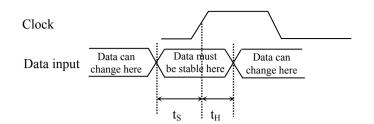

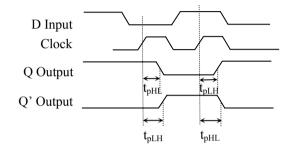

| 2.14      | Setup, Hold, and Propagation Delay Times          |     |

|           | in a Register                                     | 74  |

|           | 2.14.1 Estimation of Maximum Clock Frequency      |     |

|           | for a Sequential Circuit                          |     |

|           | 2.14.2 Metastability of Flip-flops                | 76  |

| 2.15      | Digital System Design Using SSI/MSI Components    | 77  |

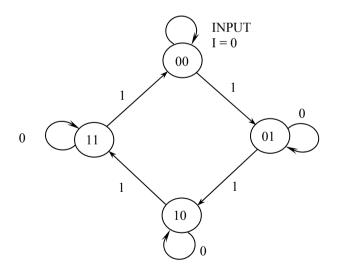

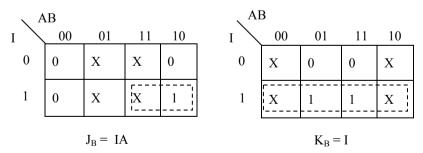

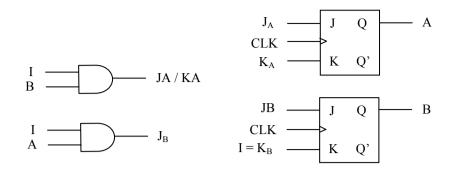

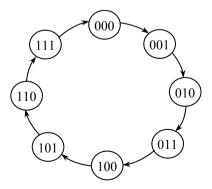

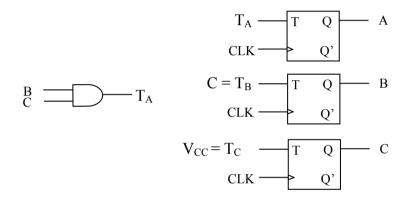

|           | 2.15.1 Two-bit Binary Counter Using JK Flip-flops |     |

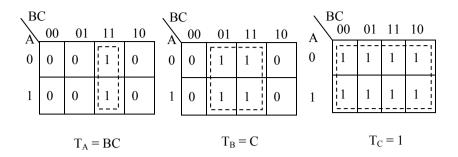

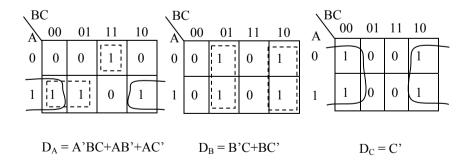

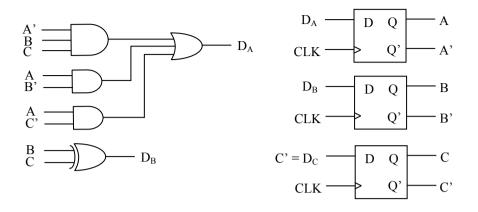

|           | 2.15.2 Design of a Three-bit Counter Using        |     |

|           | T and D Flip-flops                                | 80  |

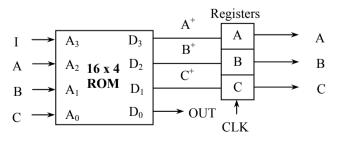

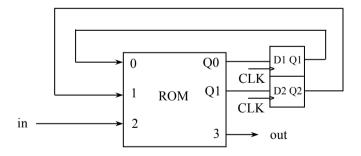

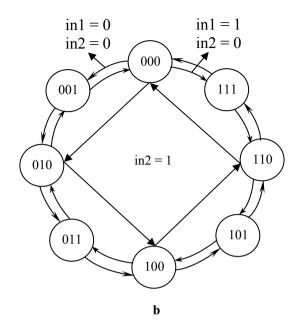

|           | 2.15.3 Controlled Three-bit Binary Counter Using  |     |

|           | ROM and Registers                                 |     |

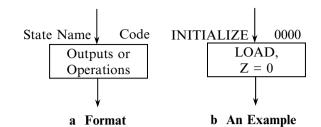

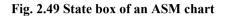

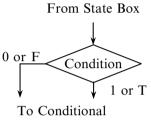

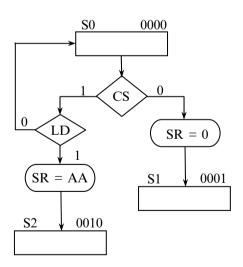

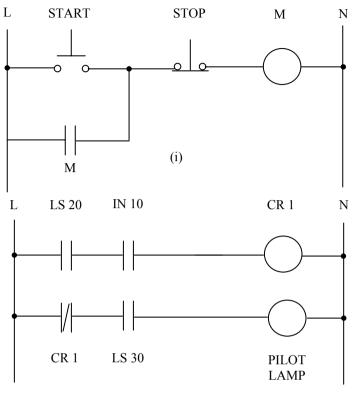

| 2.16      | Algorithmic State Machine                         |     |

| 2.17      | Digital System Design Using ASM Chart and PAL     |     |

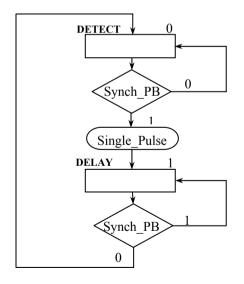

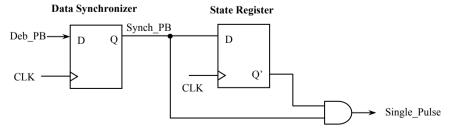

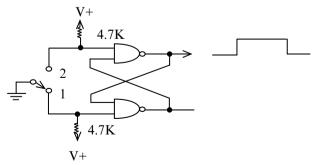

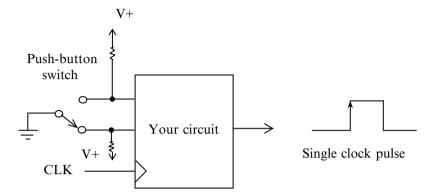

|           | 2.17.1 Single Pulser Using ASM Chart              |     |

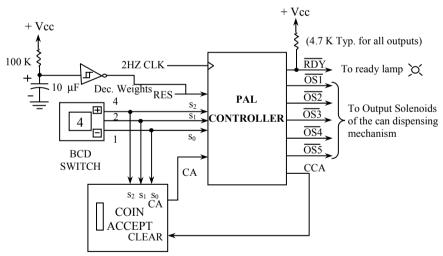

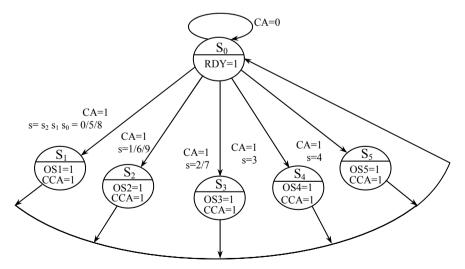

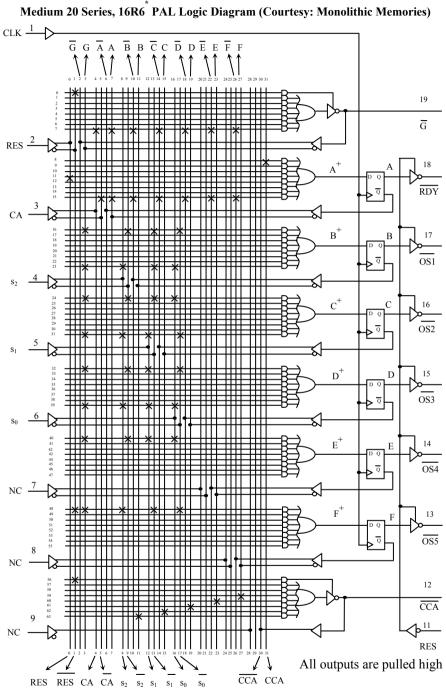

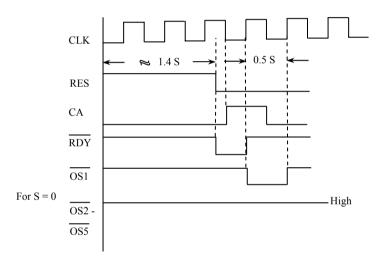

|           | 2.17.2 Design of a Vending Machine Using PAL      | 90  |

| Chapter 3 | Design of Combinational and Sequential Circuits   |     |

| Chapter 5 | Using Verilog                                     | 07  |

|           |                                                   |     |

| 3.1       | Introduction to Hardware Design Language 1        | 07  |

| 3.2       | Design of Combinational Circuits 1                |     |

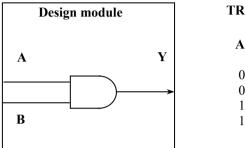

|           | 3.2.1 Realization of Basic Gates 1                | 10  |

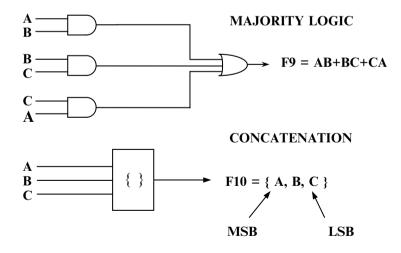

|           | 3.2.2 Realization of Majority Logic               |     |

|           | and Concatenation.                                | 111 |

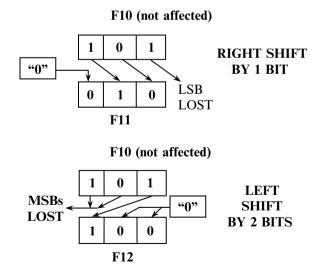

|           | 3.2.3 Shift Operations 1                          | 12  |

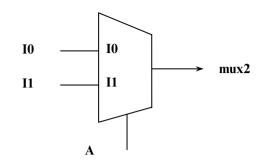

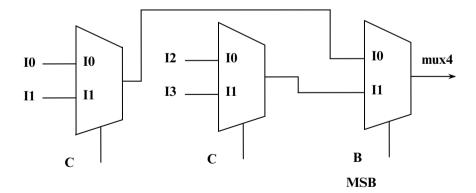

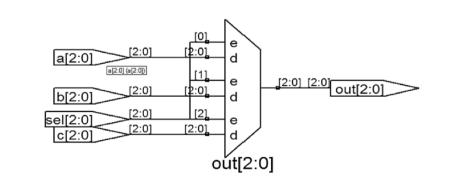

|           | 3.2.4 Realization of Multiplexers 1               | 13  |

|           | 3.2.5 Realization of a Demultiplexer              | 116 |

|           | 3.2.6 Verilog Modeling of a Full Adder 1          |     |

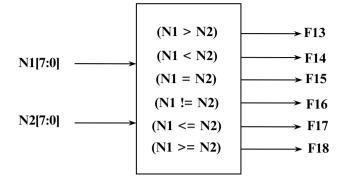

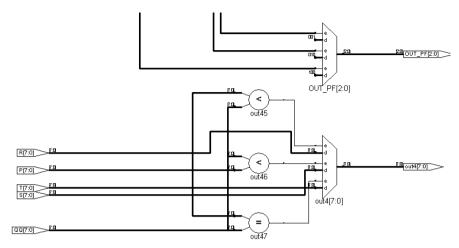

|           | 3.2.7 Realization of a Magnitude Comparator       |     |

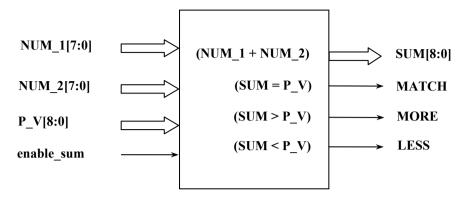

|           | 3.2.8 A Design Example Using an Adder             |     |

|           | and a Magnitude Comparator                        | 121 |

| 3.3       | Verilog Modeling of Sequential Circuits                                                   |       |

|-----------|-------------------------------------------------------------------------------------------|-------|

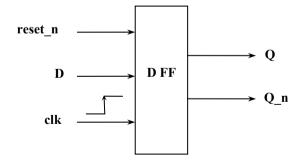

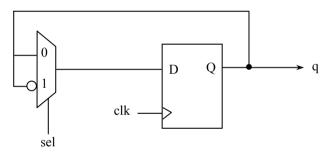

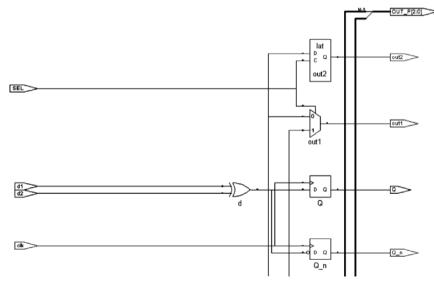

|           | 3.3.1 Realization of a D Flip-flop                                                        |       |

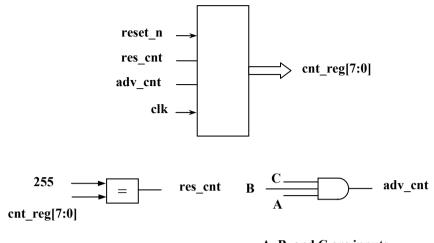

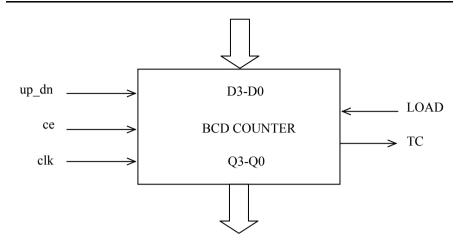

|           | <ul><li>3.3.2 Realization of Registers.</li><li>3.3.3 Realization of a Counter.</li></ul> |       |

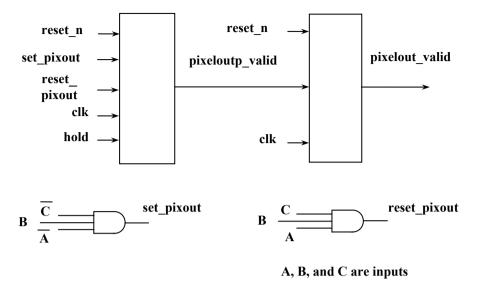

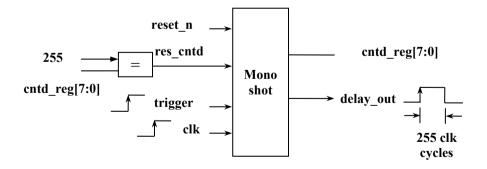

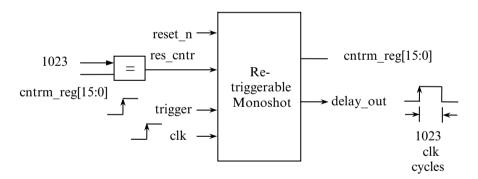

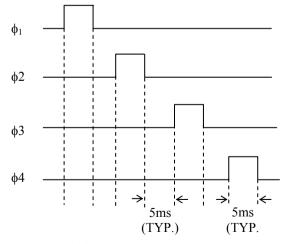

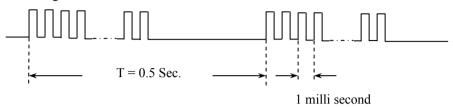

|           | 3.3.4 Realization of a Non-retriggerable Monoshot                                         |       |

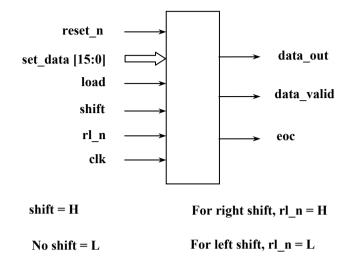

|           | 3.3.5 Verilog Coding of a Shift Register                                                  |       |

|           | 3.3.6 Realization of a Parallel to Serial Converter                                       |       |

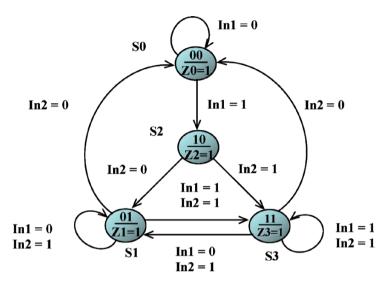

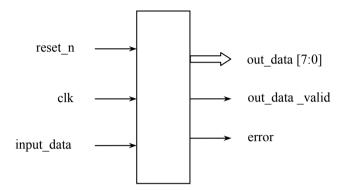

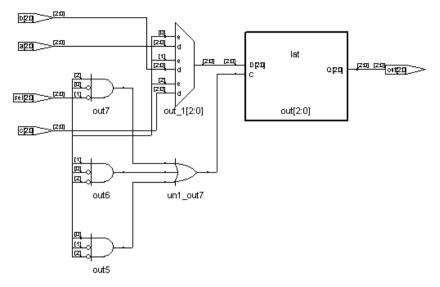

|           | 3.3.7 Realization of a Model State Machine                                                |       |

|           | 3.3.8 Pattern Sequence Detector                                                           |       |

| 3.4       | Coding Organization.                                                                      |       |

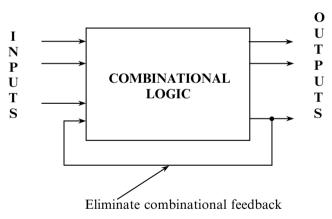

| 5.4       | 3.4.1 Combinational Circuit Design                                                        |       |

|           | 3.4.2 Sequential Circuit Design                                                           |       |

|           | 5.4.2 Sequential Chedit Design                                                            | 14/   |

| Chapter 4 | Writing a Test Bench for the Design                                                       | 165   |

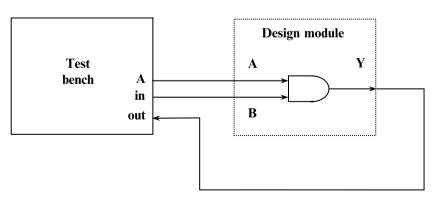

| 4.1       | Modeling a Test Bench                                                                     | 165   |

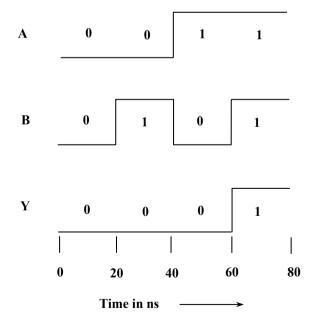

| 4.2       | Test Bench for Combinational Circuits                                                     | 169   |

| 4.3       | Test Bench for Sequential Circuits                                                        |       |

| Chapter 5 | RTL Coding Guidelines                                                                     | 187   |

| •         | 8                                                                                         |       |

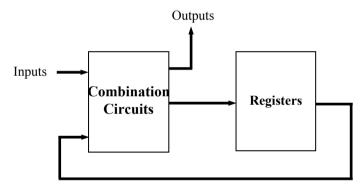

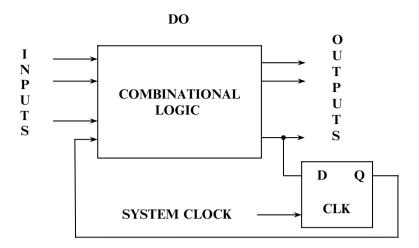

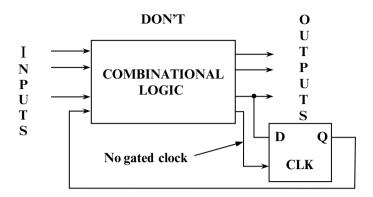

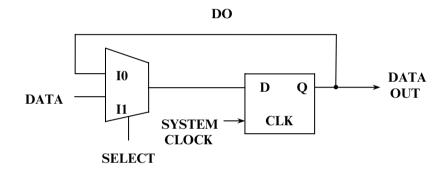

| 5.1       | Separation of Combinational and Sequential                                                |       |

|           | Circuits                                                                                  |       |

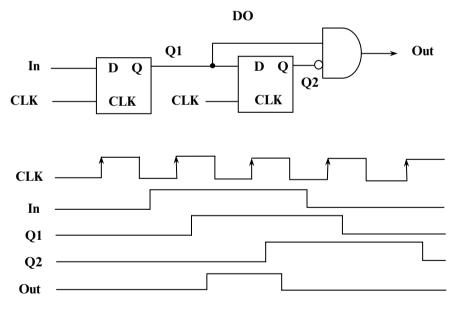

| 5.2       | Synchronous Logic                                                                         |       |

| 5.3       | Synchronous Flip-flop                                                                     |       |

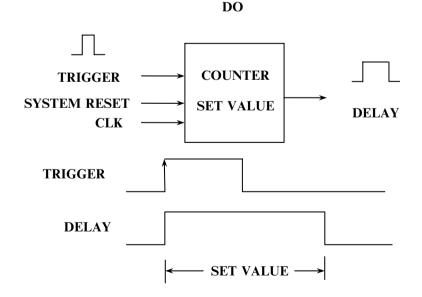

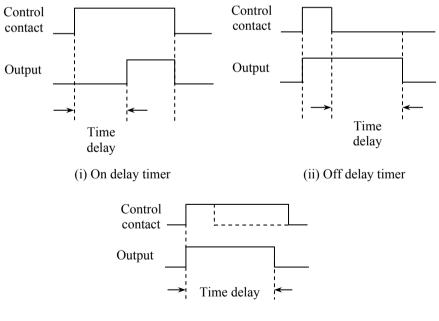

| 5.4       | Realization of Time Delays                                                                |       |

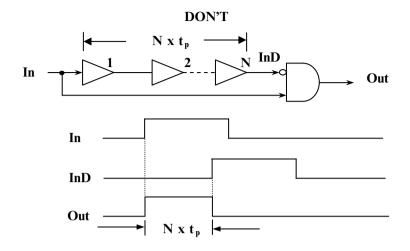

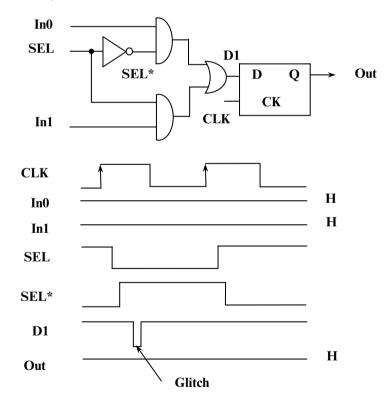

| 5.5       | Elimination of Glitches Using Synchronous Circuits.                                       |       |

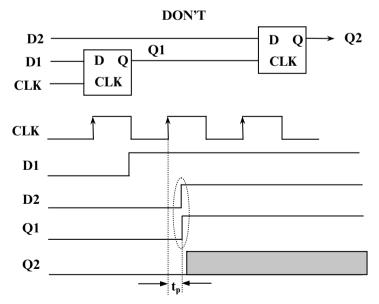

| 5.6       | Hold Time Violation in Asynchronous Circuits                                              |       |

| 5.7       | RTL Coding Style                                                                          | 195   |

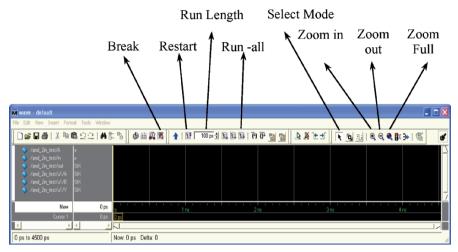

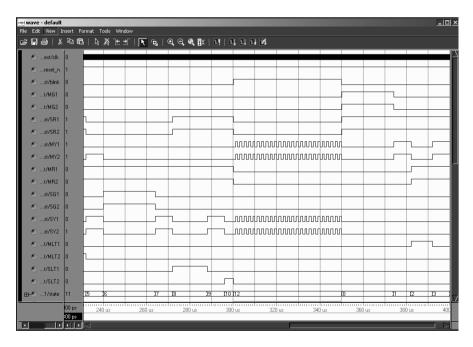

| Chapter 6 | Simulation of Designs – Modelsim Tool                                                     | . 217 |

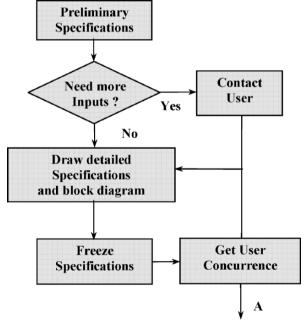

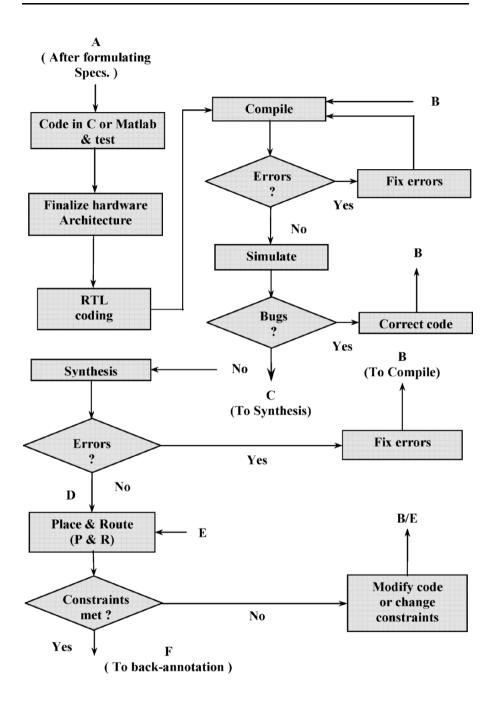

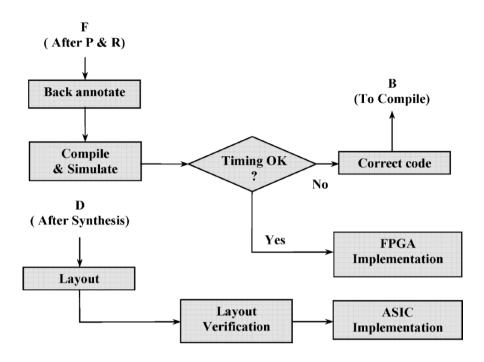

| 6.1       | VLSI Design Flow                                                                          | . 217 |

| 6.2       | Design Methodology                                                                        |       |

| 6.3       | Simulation Using Modelsim                                                                 |       |

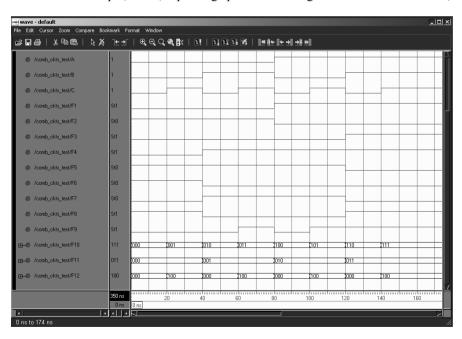

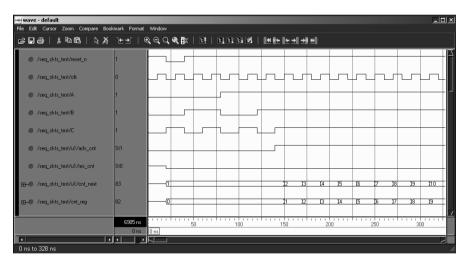

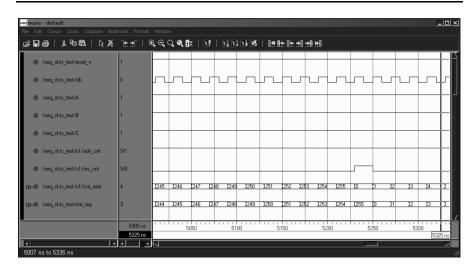

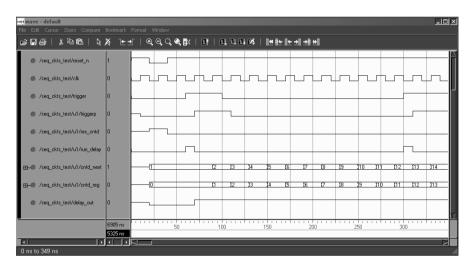

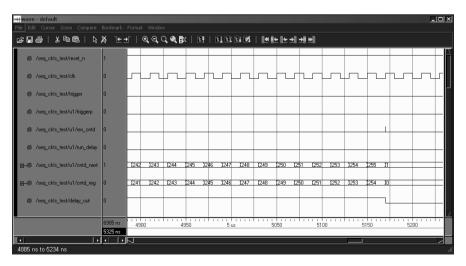

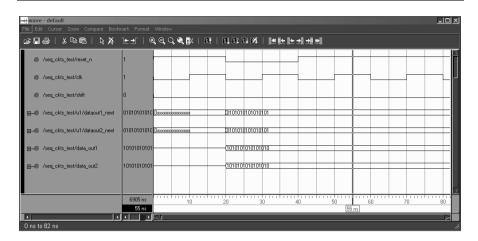

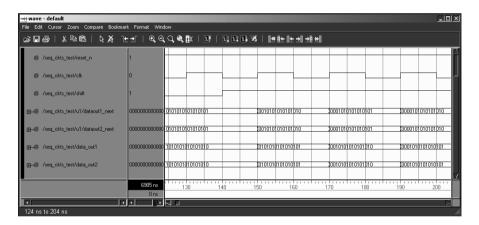

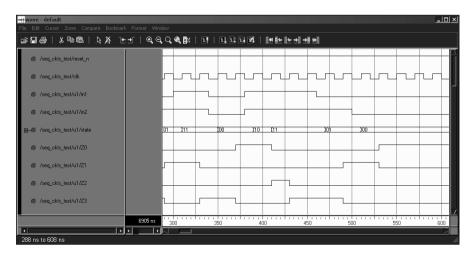

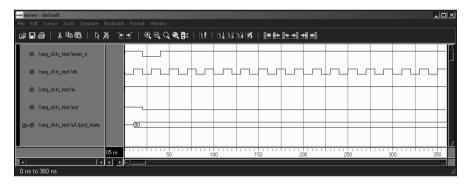

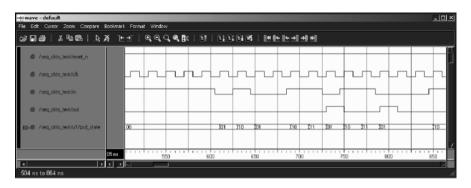

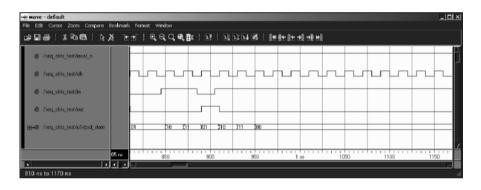

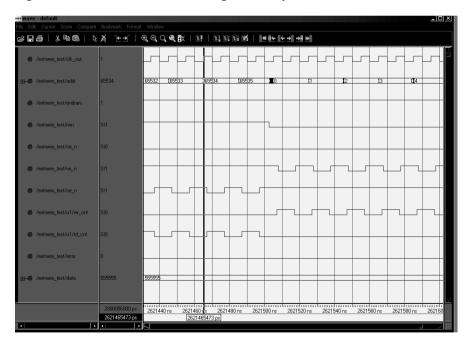

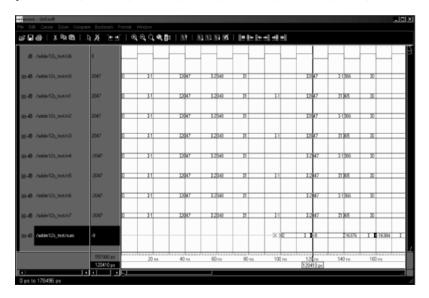

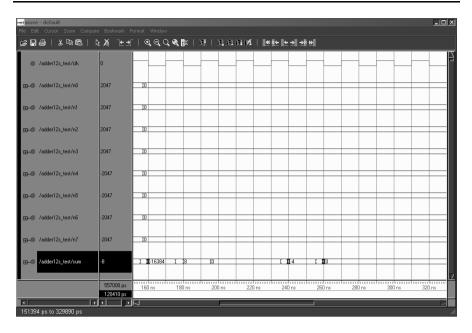

|           | 6.3.1 Simulation Results of Combinational Circuits                                        | 230   |

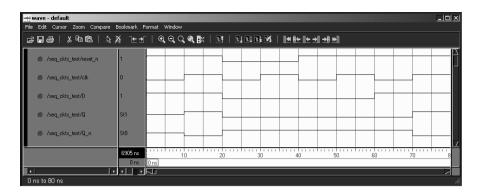

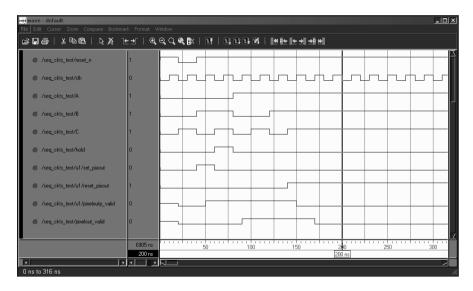

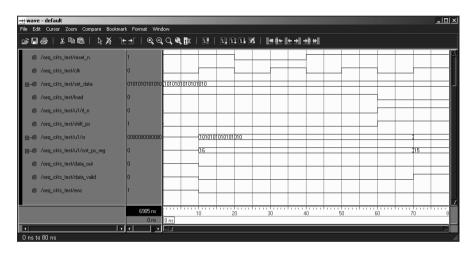

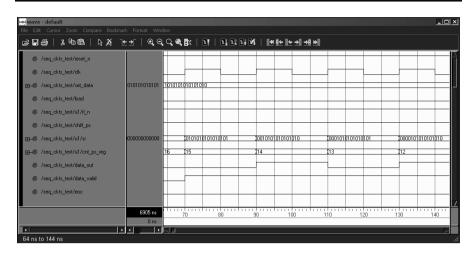

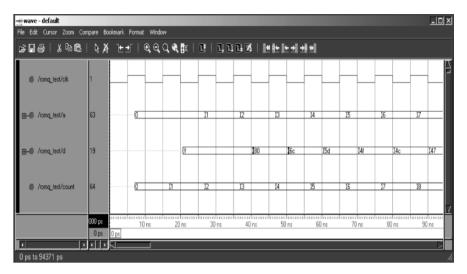

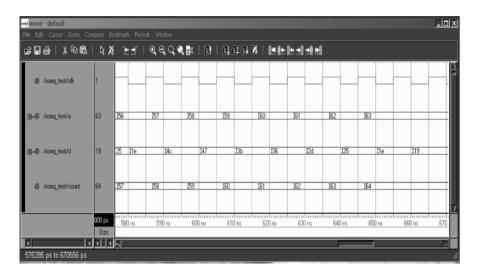

|           | 6.3.2 Simulation Results of Sequential Circuits                                           |       |

|           | 6.3.3 Modelsim Command Summary                                                            |       |

| Chapter 7 | Synthesis of Designs – Synplify Tool                                                      | . 255 |

| 7.1       | Synthesis                                                                                 | 255   |

|           | 7.1.1 Features of Synthesis Tool                                                          |       |

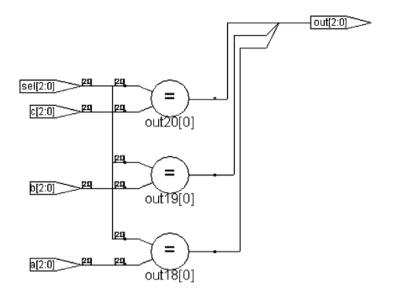

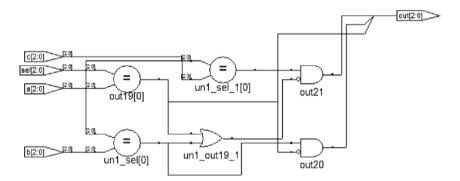

| 7.2       | Analysis of Design Examples Using Synplify Tool                 | . 256 |

|-----------|-----------------------------------------------------------------|-------|

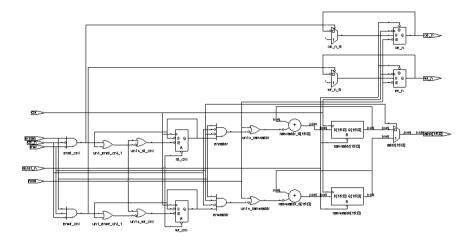

| 7.3       | Viewing Verilog Code as RTL Schematic Circuit                   | 2(0   |

| 7.4       | Diagrams<br>Optimization Effected in Synopsys Full and Parallel | . 260 |

| 7.7       | Cases                                                           | 274   |

| 7.5       | Performance Comparison of FPGAs of Two Vendors                  |       |

|           | for a Design                                                    | . 278 |

| 7.6       | Fixing Compilation Errors in Modelsim and Synplify              |       |

|           | Tools                                                           |       |

| 7.7       | Synplify Command Summary                                        | 283   |

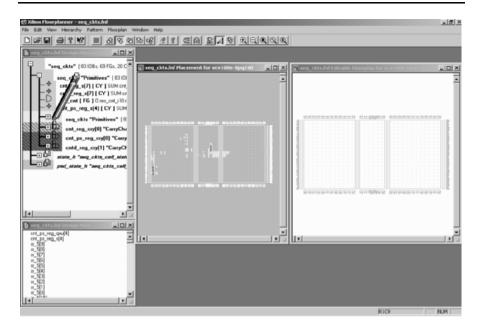

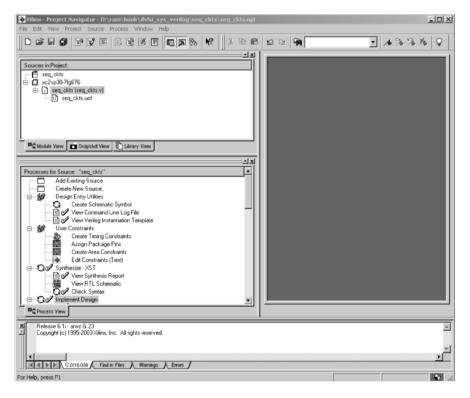

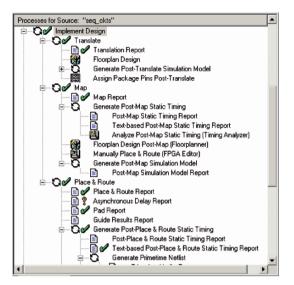

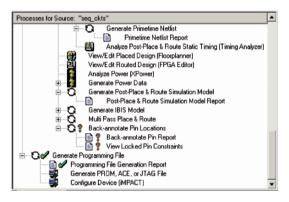

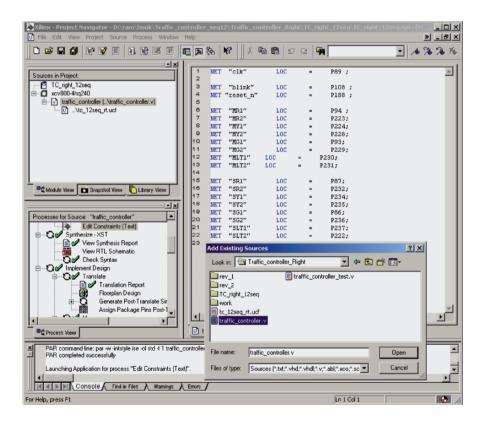

| Chapter 8 | Place and Route                                                 | . 295 |

| 8.1       | Xilinx Place and Route                                          | . 295 |

| 8.2       | Xilinx Place and Route Tool Command Summary                     | . 300 |

| 8.3       | Place and Route and Back Annotation Using Xilinx                |       |

|           | Project Navigator                                               | . 301 |

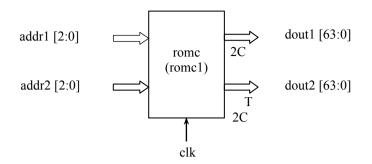

| Chapter 9 | Design of Memories                                              | 319   |

| 9.1       | On-chip Dual Address ROM Design                                 | 319   |

|           | 9.1.1 Verilog Code for Dual Address ROM Design                  |       |

|           | 9.1.2 Test Bench for Dual Address ROM Design                    | . 323 |

|           | 9.1.3 Simulation Results of Dual Address ROM                    |       |

|           | Design                                                          | 325   |

|           | 9.1.4 Synthesis Results for Dual Address ROM                    |       |

|           | Design                                                          | 327   |

|           | 9.1.5 Xilinx P&R Results for Dual Address ROM                   | 220   |

| 0.2       | Design.                                                         |       |

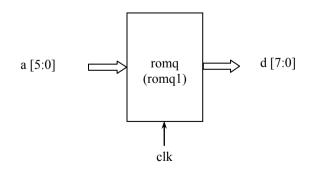

| 9.2       | Single Address ROM Design                                       | 329   |

|           | 9.2.1 Verilog Code for Single Address ROM<br>Design             | 220   |

|           | 9.2.2 Test Bench for Single Address ROM Design                  |       |

|           | 9.2.3 Simulation Results of Single Address ROM                  | 551   |

|           | Design                                                          | 332   |

|           | 9.2.4 Synthesis Results for Single Address ROM                  | 552   |

|           | Design                                                          | 334   |

|           | 9.2.5 Xilinx P&R Results for Single Address ROM                 | 554   |

|           | Design                                                          | 335   |

|           |                                                                 |       |

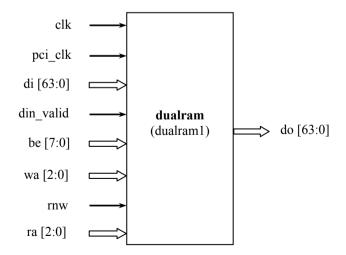

| 9.3                                        | On-Chip Dual RAM Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 335                                                                              |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|                                            | 9.3.1 Verilog Code for Dual RAM Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

|                                            | 9.3.2 Test Bench for the Dual RAM Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 342                                                                              |

|                                            | 9.3.3 Simulation Results of Dual RAM Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 345                                                                              |

|                                            | 9.3.4 Synthesis Results for the Dual RAM Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 348                                                                              |

|                                            | 9.3.5 Xilinx P&R Results for the Dual RAM Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 350                                                                              |

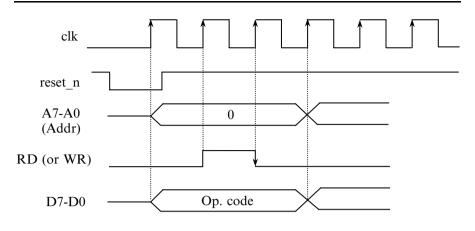

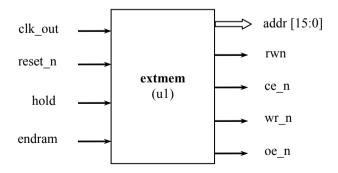

| 9.4                                        | External Memory Controller Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 351                                                                              |

|                                            | 9.4.1 Design of an External RAM Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |

|                                            | for Video Scalar Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 351                                                                              |

|                                            | 9.4.2 Verilog Code for External RAM Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

|                                            | Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 352                                                                              |

|                                            | 9.4.3 Test Bench for External RAM Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

|                                            | Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

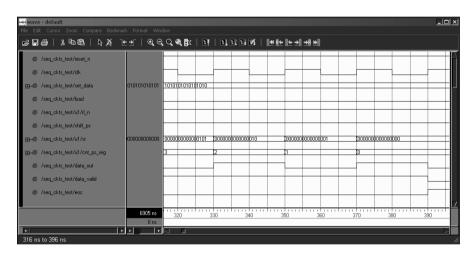

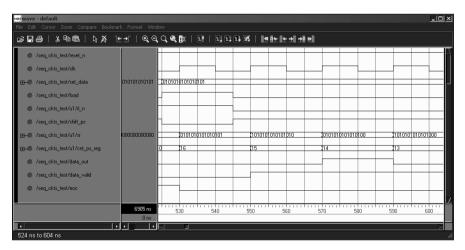

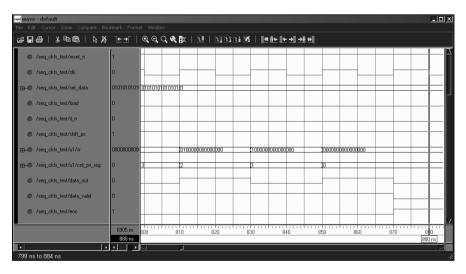

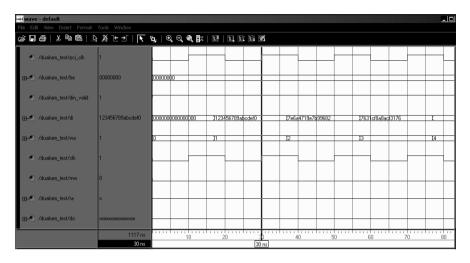

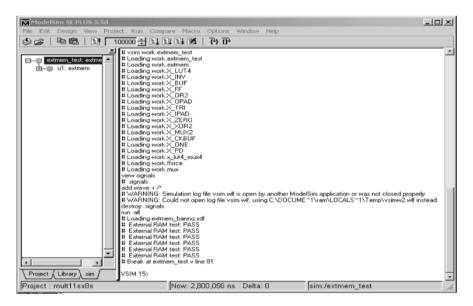

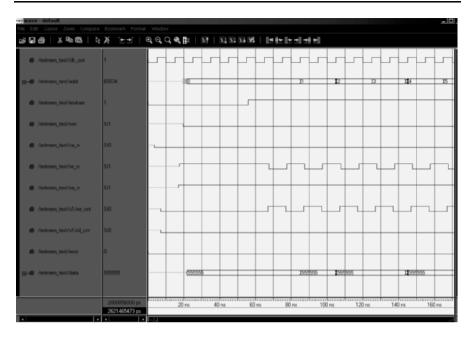

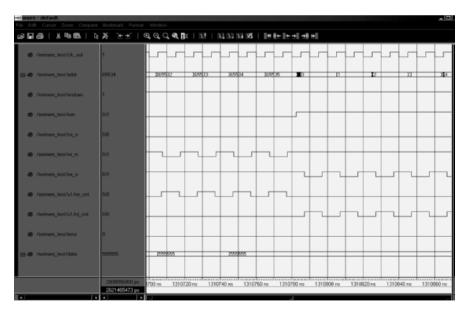

|                                            | 9.4.4 Simulation Results for External RAM Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

|                                            | Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 359                                                                              |

|                                            | 9.4.5 Synthesis Results for External RAM Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

|                                            | Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 362                                                                              |

|                                            | 9.4.6 Xilinx P&R Results for the External RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

|                                            | Controller Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 364                                                                              |

|                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

| Chapter 10                                 | Arithmetic Circuit Designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 371                                                                              |

| Chapter 10                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

| -                                          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 371                                                                              |

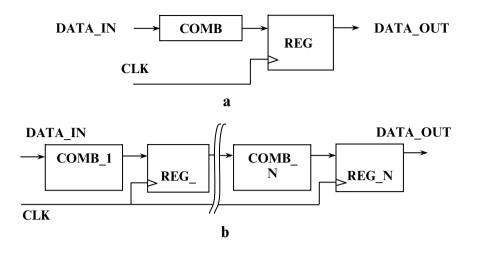

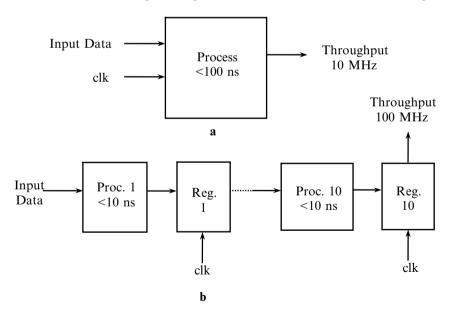

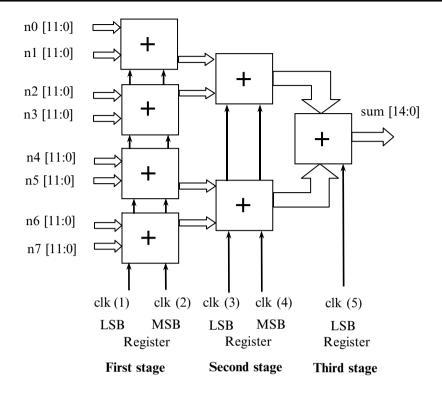

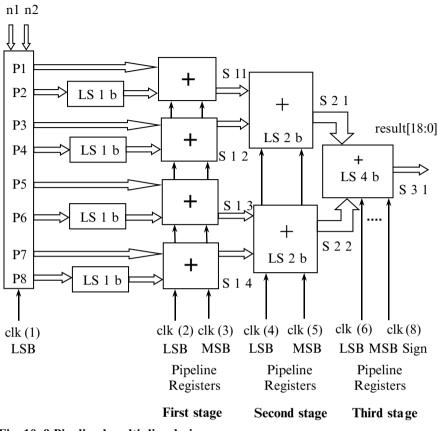

| 10.1                                       | Digital Pipelining                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

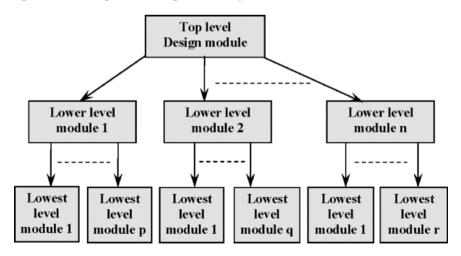

| -                                          | Digital Pipelining<br>Partitioning of a Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 374                                                                              |

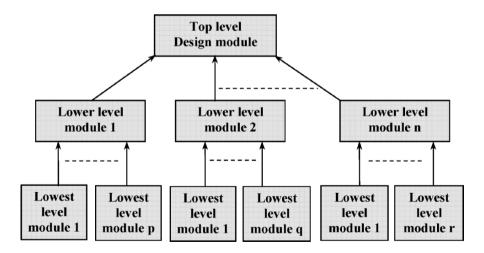

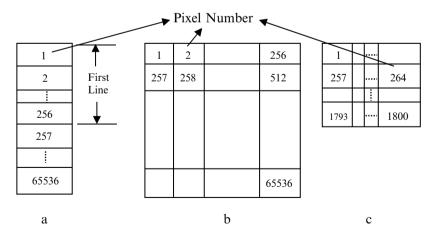

| 10.1                                       | Digital Pipelining<br>Partitioning of a Design<br>10.2.1 Partition of Data Width                                                                                                                                                                                                                                                                                                                                                                                                                                | 374<br>374                                                                       |

| 10.1                                       | Digital Pipelining<br>Partitioning of a Design<br>10.2.1 Partition of Data Width<br>10.2.2 Partition of Functionality                                                                                                                                                                                                                                                                                                                                                                                           | 374<br>374<br>374                                                                |

| 10.1<br>10.2                               | Digital Pipelining<br>Partitioning of a Design<br>10.2.1 Partition of Data Width<br>10.2.2 Partition of Functionality<br>Signed Adder Design.                                                                                                                                                                                                                                                                                                                                                                   | 374<br>374<br>374<br>375                                                         |

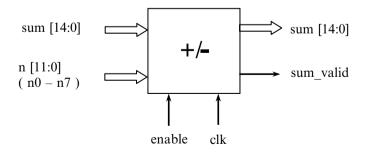

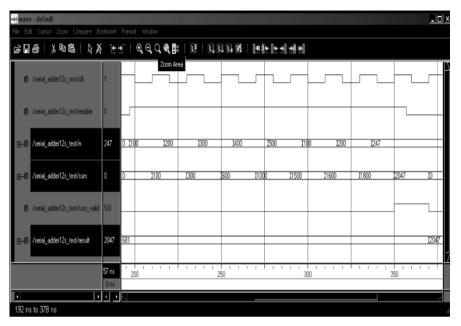

| 10.1<br>10.2                               | Digital Pipelining<br>Partitioning of a Design<br>10.2.1 Partition of Data Width<br>10.2.2 Partition of Functionality<br>Signed Adder Design<br>10.3.1 Signed Serial Adder                                                                                                                                                                                                                                                                                                                                      | 374<br>374<br>374<br>375<br>375                                                  |

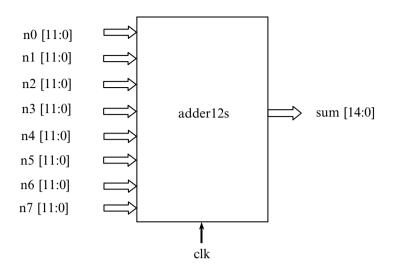

| 10.1<br>10.2                               | Digital Pipelining.<br>Partitioning of a Design.<br>10.2.1 Partition of Data Width.<br>10.2.2 Partition of Functionality.<br>Signed Adder Design.<br>10.3.1 Signed Serial Adder<br>10.3.2 Parallel Signed Adder Design.                                                                                                                                                                                                                                                                                         | 374<br>374<br>374<br>375<br>375<br>381                                           |

| 10.1<br>10.2<br>10.3                       | Digital Pipelining<br>Partitioning of a Design<br>10.2.1 Partition of Data Width<br>10.2.2 Partition of Functionality<br>Signed Adder Design<br>10.3.1 Signed Serial Adder                                                                                                                                                                                                                                                                                                                                      | 374<br>374<br>374<br>375<br>375<br>381<br>395                                    |

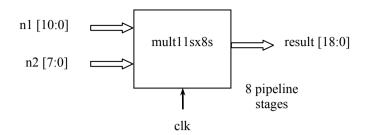

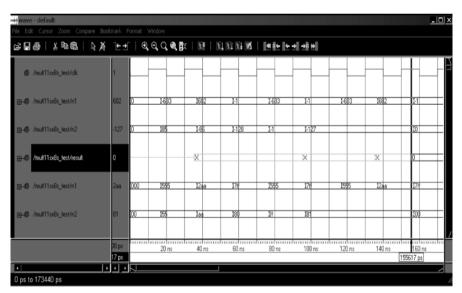

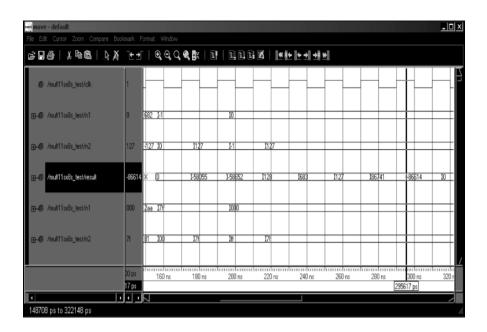

| 10.1<br>10.2<br>10.3<br>10.4               | Digital Pipelining<br>Partitioning of a Design<br>10.2.1 Partition of Data Width<br>10.2.2 Partition of Functionality.<br>Signed Adder Design<br>10.3.1 Signed Serial Adder<br>10.3.2 Parallel Signed Adder Design<br>Multiplier Design<br>10.4.1 Verilog Code for Multiplier Design                                                                                                                                                                                                                            | 374<br>374<br>374<br>375<br>375<br>381<br>395                                    |

| 10.1<br>10.2<br>10.3                       | Digital Pipelining<br>Partitioning of a Design<br>10.2.1 Partition of Data Width<br>10.2.2 Partition of Functionality<br>Signed Adder Design<br>10.3.1 Signed Serial Adder<br>10.3.2 Parallel Signed Adder Design<br>Multiplier Design<br>10.4.1 Verilog Code for Multiplier Design<br><b>Development of Algorithms and Verification</b>                                                                                                                                                                        | 374<br>374<br>375<br>375<br>381<br>395<br>398                                    |

| 10.1<br>10.2<br>10.3<br>10.4               | Digital Pipelining<br>Partitioning of a Design<br>10.2.1 Partition of Data Width<br>10.2.2 Partition of Functionality.<br>Signed Adder Design<br>10.3.1 Signed Serial Adder<br>10.3.2 Parallel Signed Adder Design<br>Multiplier Design<br>10.4.1 Verilog Code for Multiplier Design                                                                                                                                                                                                                            | 374<br>374<br>375<br>375<br>381<br>395<br>398                                    |

| 10.1<br>10.2<br>10.3<br>10.4<br>Chapter 11 | Digital Pipelining.<br>Partitioning of a Design.<br>10.2.1 Partition of Data Width.<br>10.2.2 Partition of Functionality.<br>Signed Adder Design.<br>10.3.1 Signed Serial Adder.<br>10.3.2 Parallel Signed Adder Design.<br>Multiplier Design.<br>10.4.1 Verilog Code for Multiplier Design.<br><b>Development of Algorithms and Verification<br/>Using High Level Languages.</b>                                                                                                                               | 374<br>374<br>375<br>375<br>381<br>395<br>398<br><b>417</b>                      |

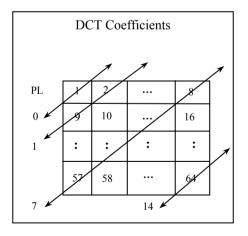

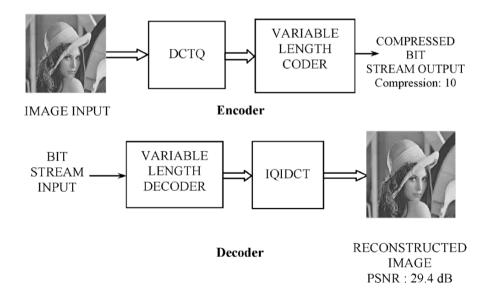

| 10.1<br>10.2<br>10.3<br>10.4               | Digital Pipelining.Partitioning of a Design.10.2.1 Partition of Data Width.10.2.2 Partition of Functionality.Signed Adder Design.10.3.1 Signed Serial Adder.10.3.2 Parallel Signed Adder Design.Multiplier Design.10.4.1 Verilog Code for Multiplier Design.Development of Algorithms and VerificationUsing High Level Languages.2D-Discrete Cosine Transform and Quantization.                                                                                                                                 | 374<br>374<br>375<br>375<br>381<br>395<br>398<br><b>417</b>                      |

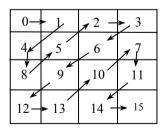

| 10.1<br>10.2<br>10.3<br>10.4<br>Chapter 11 | Digital Pipelining.Partitioning of a Design.10.2.1 Partition of Data Width.10.2.2 Partition of Functionality.Signed Adder Design.10.3.1 Signed Serial Adder.10.3.2 Parallel Signed Adder Design.Multiplier Design.10.4.1 Verilog Code for Multiplier Design.Development of Algorithms and VerificationUsing High Level Languages.2D-Discrete Cosine Transform and Quantization.11.1.1 Algorithm for Parallel Matrix Multiplication                                                                              | 374<br>374<br>375<br>375<br>381<br>395<br>398<br><b>417</b><br>418               |

| 10.1<br>10.2<br>10.3<br>10.4<br>Chapter 11 | <ul> <li>Digital Pipelining.</li> <li>Partitioning of a Design.</li> <li>10.2.1 Partition of Data Width.</li> <li>10.2.2 Partition of Functionality.</li> <li>Signed Adder Design.</li> <li>10.3.1 Signed Serial Adder.</li> <li>10.3.2 Parallel Signed Adder Design.</li> <li>Multiplier Design.</li> <li>10.4.1 Verilog Code for Multiplier Design.</li> <li>Development of Algorithms and Verification</li> <li>Using High Level Languages.</li> <li>2D-Discrete Cosine Transform and Quantization</li></ul> | 374<br>374<br>374<br>375<br>375<br>381<br>395<br>398<br><b>417</b><br>418<br>419 |

| 10.1<br>10.2<br>10.3<br>10.4<br>Chapter 11 | Digital Pipelining.Partitioning of a Design.10.2.1 Partition of Data Width.10.2.2 Partition of Functionality.Signed Adder Design.10.3.1 Signed Serial Adder.10.3.2 Parallel Signed Adder Design.Multiplier Design.10.4.1 Verilog Code for Multiplier Design.Development of Algorithms and VerificationUsing High Level Languages.2D-Discrete Cosine Transform and Quantization.11.1.1 Algorithm for Parallel Matrix Multiplication                                                                              | 374<br>374<br>374<br>375<br>375<br>381<br>395<br>398<br><b>417</b><br>418        |

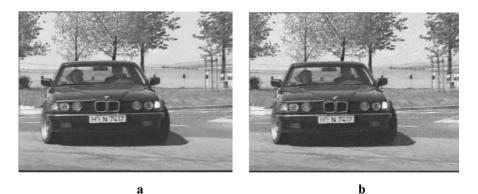

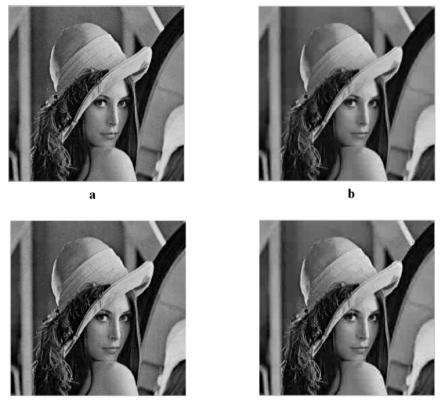

| 11.2       | Automatic Quality Control Scheme for Image<br>Compression                                    | 431        |

|------------|----------------------------------------------------------------------------------------------|------------|

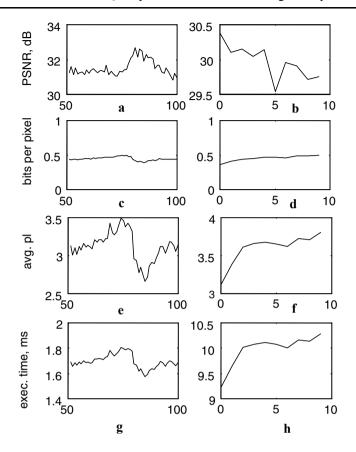

|            | 11.2.1 Algorithm for Assessing Image Quality<br>Dynamically                                  | 133        |

|            | 11.2.2 Verification of DCTQ–IQIDCT Processes with                                            | . 433      |

|            | Automatic Pruning Level Control Incorporated                                                 |            |

|            | Using Matlab                                                                                 |            |

|            | 11.2.3 Results and Discussions for the Fixed                                                 |            |

|            | and Automatic Pruning Level Controls                                                         | . 447      |

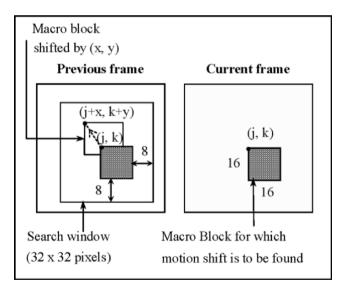

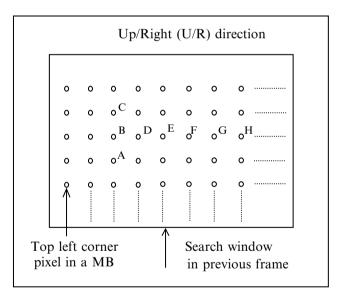

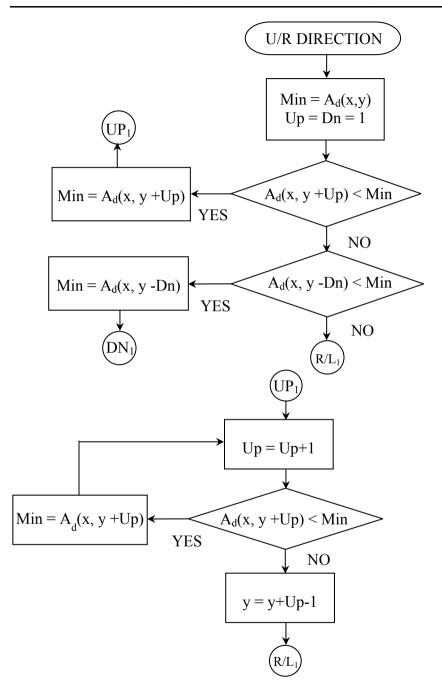

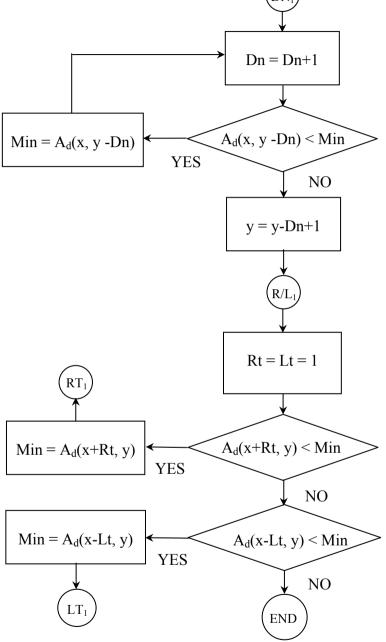

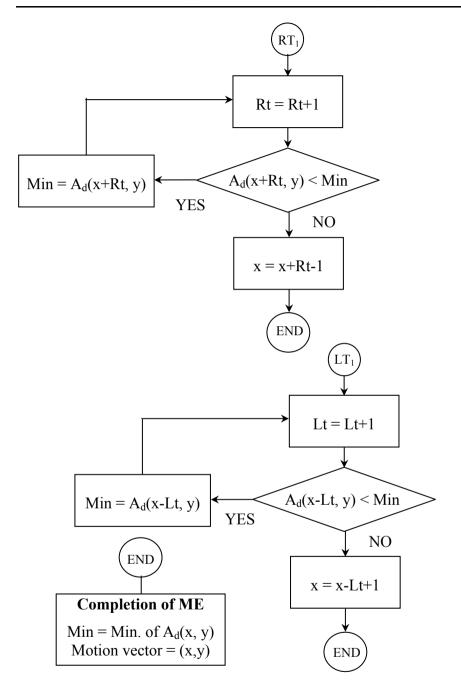

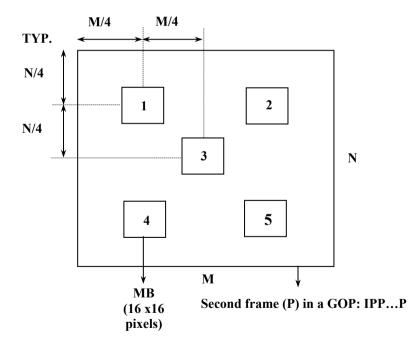

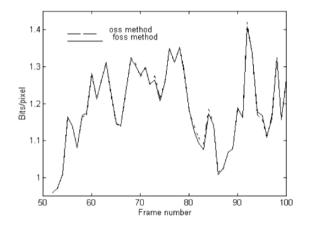

| 11.3       | Fast Motion Estimation Algorithm for Real-Time                                               |            |

|            | Video Compression                                                                            |            |

|            | 11.3.1 Introduction.                                                                         | 452        |

|            | 11.3.2 The Fast One-at-a-time Step Search                                                    | 151        |

|            | Algorithm                                                                                    | . 434      |

|            | Blocks                                                                                       | 459        |

|            | 11.3.4 Detection of Scene Change                                                             |            |

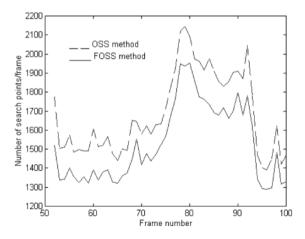

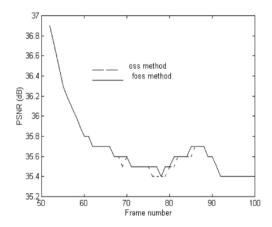

|            | 11.3.5 Results and Discussions of FOSS Motion                                                | 157        |

|            | Estimation Algorithm                                                                         | . 461      |

|            |                                                                                              |            |

| Chapter 12 | Architectural Design                                                                         | 473        |

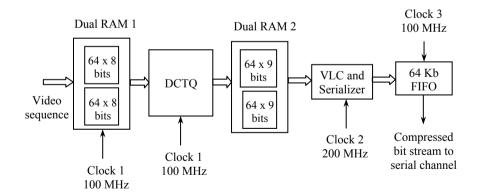

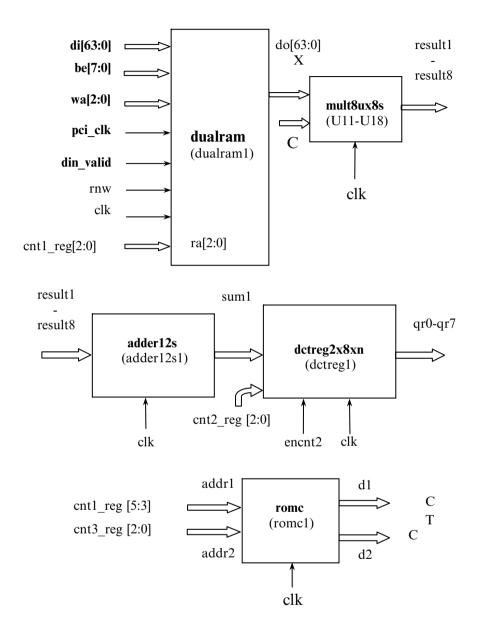

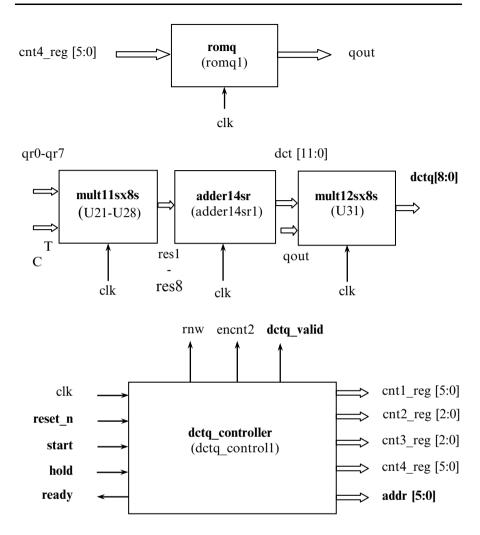

| 12.1       | Architecture of Discrete Cosine Transform                                                    |            |

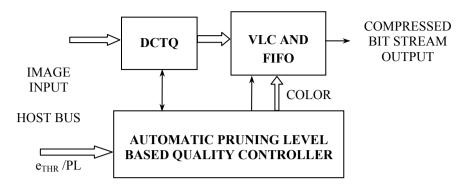

|            | and Quantization Processor                                                                   | 473        |

| 12.2       | Architecture of a Video Encoder Using Automatic                                              |            |

|            | Quality Control Scheme and DCTQ Processor                                                    |            |

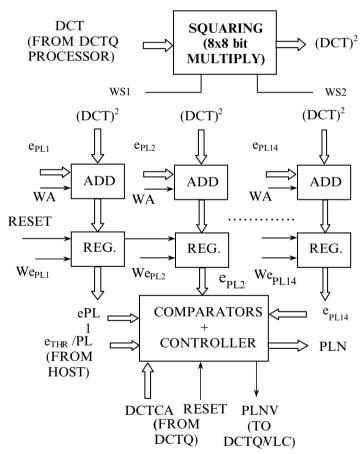

| 10.0       | 12.2.1 The Automatic Quality Controller                                                      | 477        |

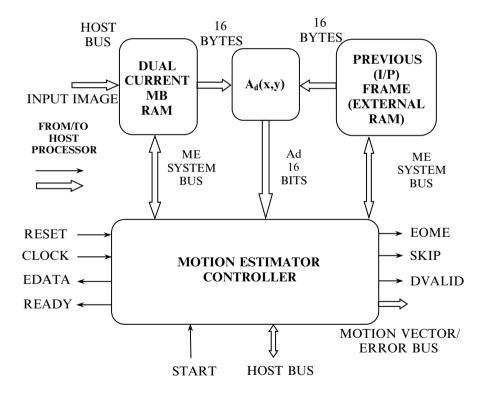

| 12.3       | Architecture for the FOSS Motion Estimation                                                  | 470        |

|            | Processor                                                                                    | 4/9        |

| Chapter 13 | Project Design                                                                               | . 487      |

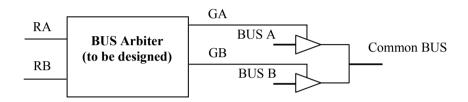

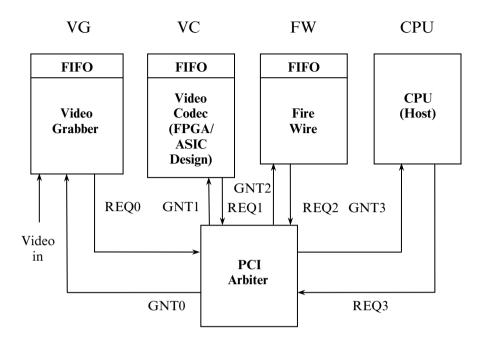

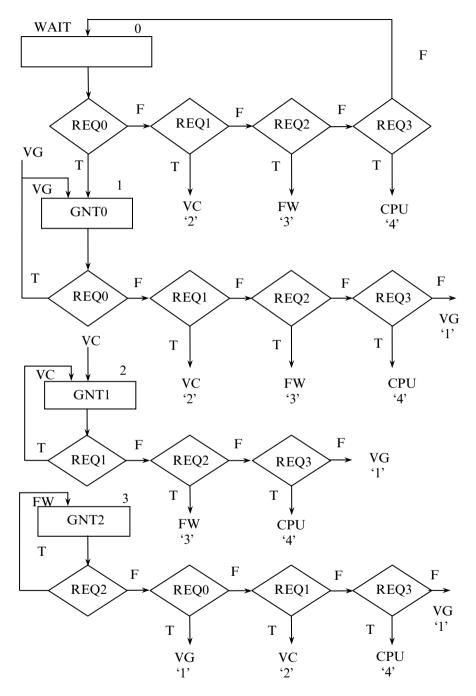

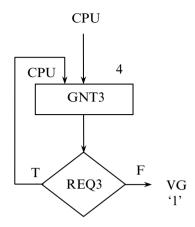

| 13.1       | PCI Bus Arbiter                                                                              | 487        |

| 10.11      | 13.1.1 Design of PCI Arbiter                                                                 |            |

|            | 13.1.2 Verilog Code for PCI Arbiter Design                                                   |            |

|            | 13.1.3 Test Bench for the Functional Testing                                                 |            |

|            |                                                                                              | 100        |

|            | of PCI Arbiter                                                                               |            |

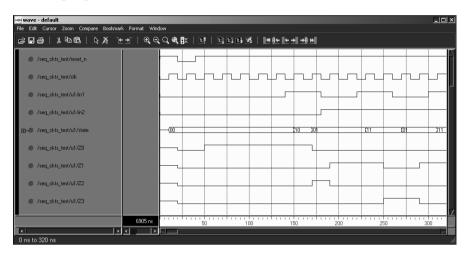

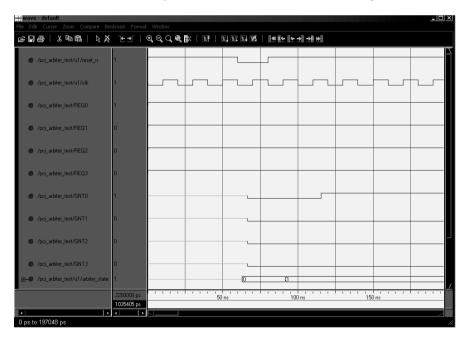

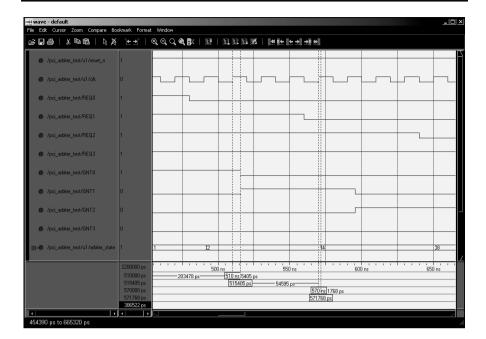

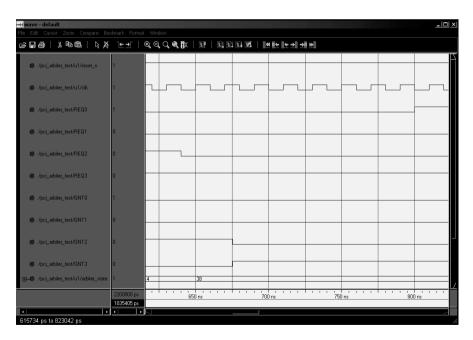

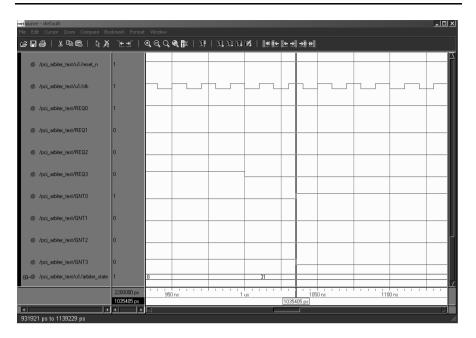

|            | 13.1.4 Simulation Results                                                                    | 498        |

|            | <ul><li>13.1.4 Simulation Results</li><li>13.1.5 Synthesis Results for PCI Arbiter</li></ul> | 498        |

|            | 13.1.4 Simulation Results                                                                    | 498<br>500 |

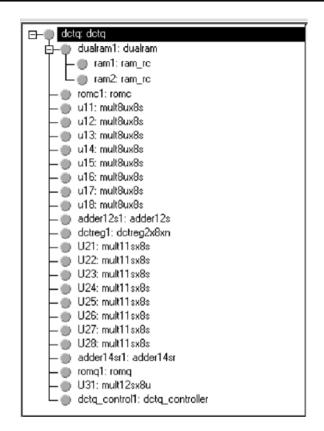

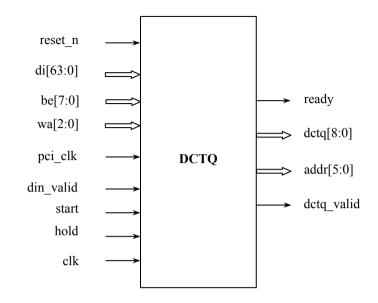

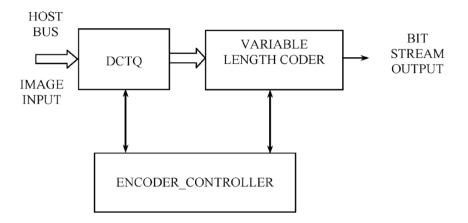

| 13.2                 | Design of the DCTQ Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 502                                                                                                                                                                                 |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | 13.2.1 Specification of DCTQ Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 503                                                                                                                                                                                 |

|                      | 13.2.2 Sequence of Operations of the Host                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                     |

|                      | and the DCTQ Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 504                                                                                                                                                                                 |

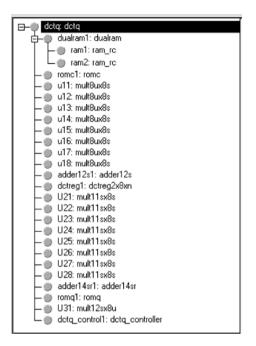

|                      | 13.2.3 Verilog Code for the DCTQ Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                     |

|                      | 13.2.4 Test Bench for the DCTQ Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 526                                                                                                                                                                                 |

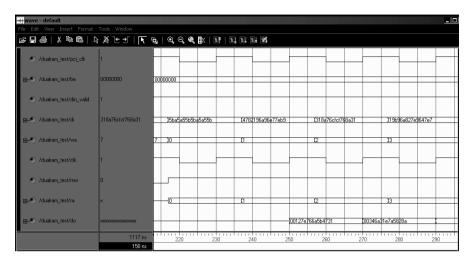

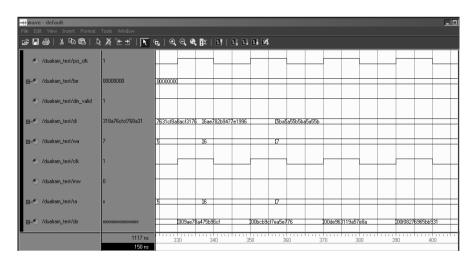

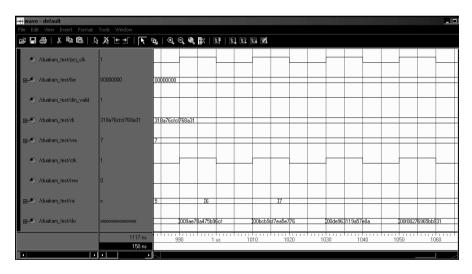

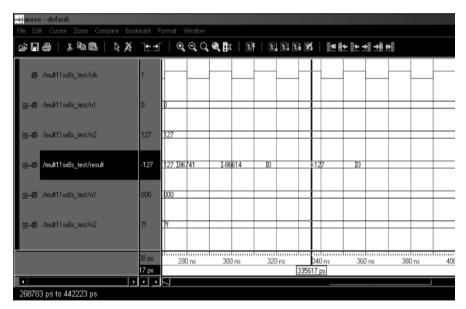

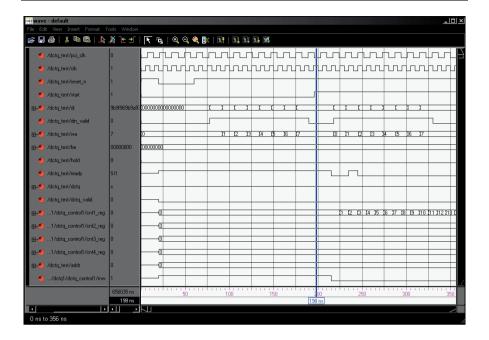

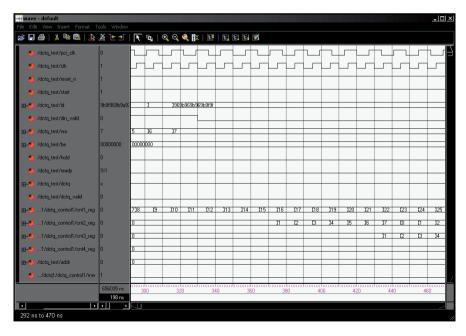

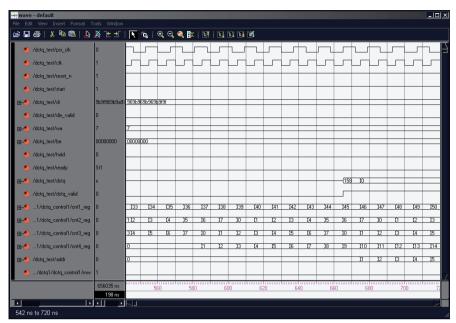

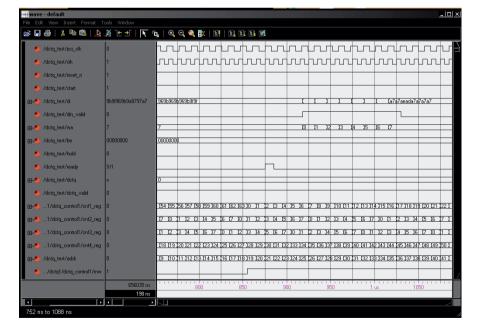

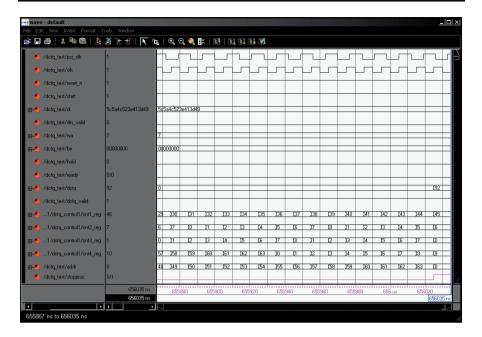

|                      | 13.2.5 Simulation Results for DCTQ Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 531                                                                                                                                                                                 |

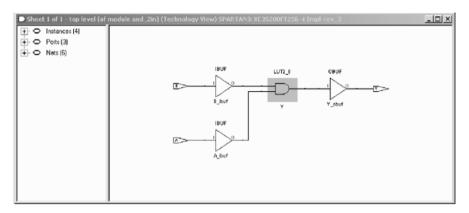

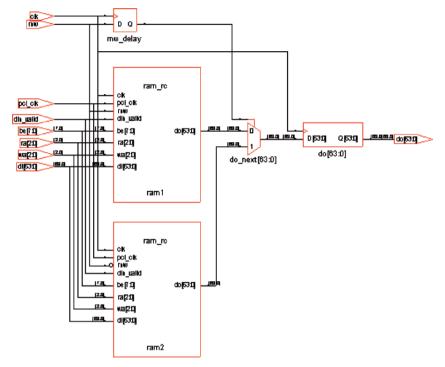

|                      | 13.2.6 Synthesis Results for DCTQ Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                     |

|                      | 13.2.7 Place and Route Results for DCTQ Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 537                                                                                                                                                                                 |

|                      | 13.2.8 Matlab Codes for Pre-processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                     |

|                      | and Post-processing an Image                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 538                                                                                                                                                                                 |

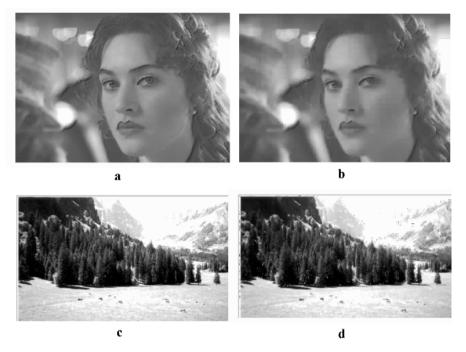

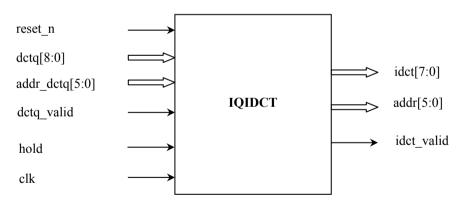

|                      | 13.2.9 Verification of Verilog DCTQ-IQIDCT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                     |

|                      | Cores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 544                                                                                                                                                                                 |

|                      | 13.2.10 Simulation Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 545                                                                                                                                                                                 |

|                      | 13.2.11 Implementation of DCTQ/IQIDCT IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                     |

|                      | Cores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                     |

|                      | 13.2.12 Capabilities of the IP Cores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 548                                                                                                                                                                                 |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                     |

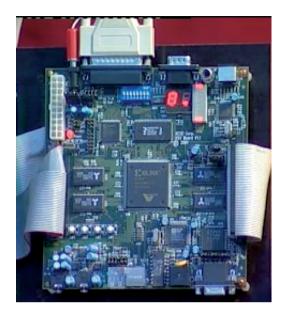

| Chapter 14           | Hardware Implementations Using FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                     |

|                      | and I/O Boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 555                                                                                                                                                                                 |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                     |

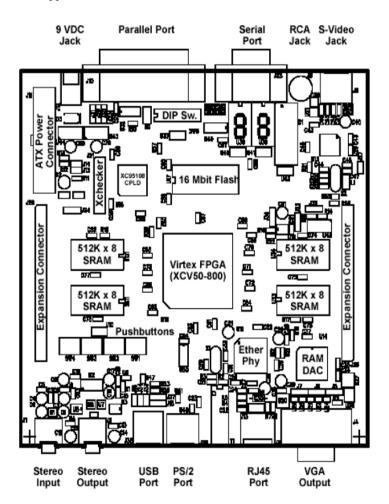

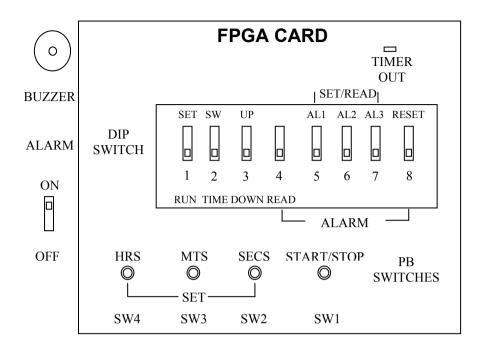

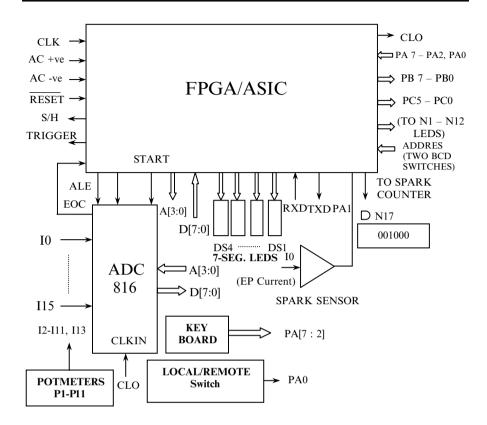

| 14.1                 | FPGA Board Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 556                                                                                                                                                                                 |

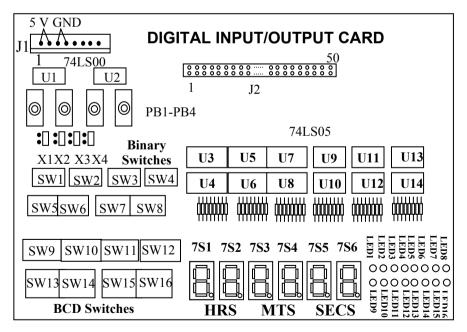

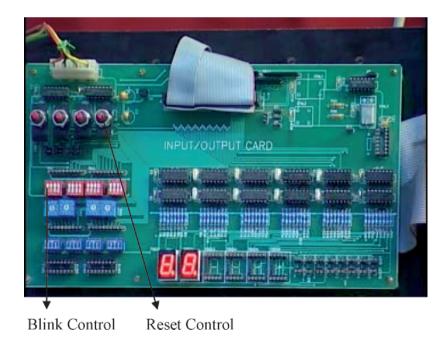

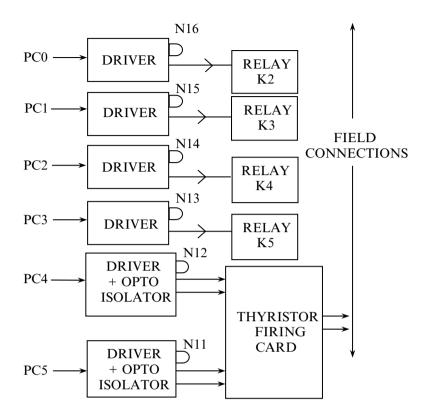

| 14.1<br>14.2         | FPGA Board Features<br>Features of Digital Input/Output Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                     |

|                      | FPGA Board Features<br>Features of Digital Input/Output Board<br>Problem on Some FPGA Boards and Its Solution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 558                                                                                                                                                                                 |

| 14.2                 | Features of Digital Input/Output Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 558                                                                                                                                                                                 |

| 14.2                 | Features of Digital Input/Output Board<br>Problem on Some FPGA Boards and Its Solution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 558<br>560                                                                                                                                                                          |

| 14.2                 | Features of Digital Input/Output Board<br>Problem on Some FPGA Boards and Its Solution<br>14.3.1 Verilog Code to Solve the Malfunctioning of<br>System Using XC4000 Series FPGA Boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 558<br>560<br>561                                                                                                                                                                   |

| 14.2<br>14.3         | Features of Digital Input/Output Board<br>Problem on Some FPGA Boards and Its Solution<br>14.3.1 Verilog Code to Solve the Malfunctioning of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 558<br>560<br>561                                                                                                                                                                   |

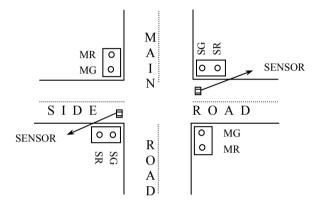

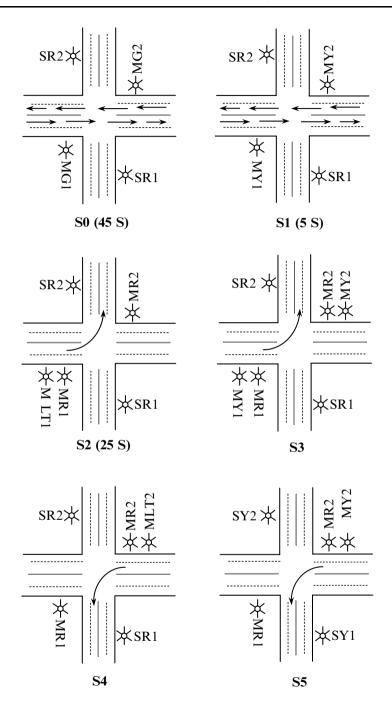

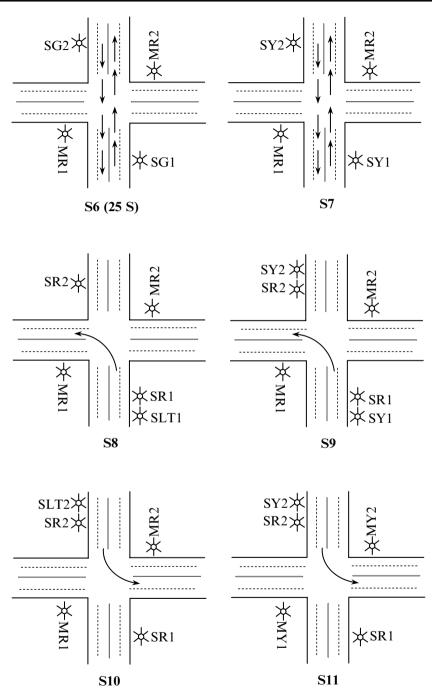

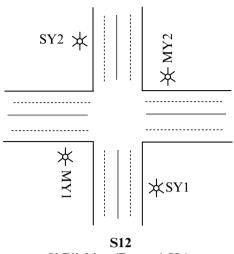

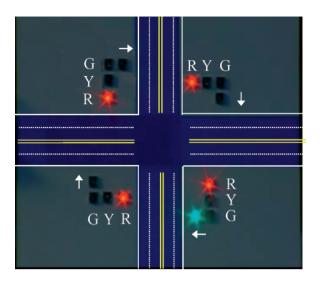

| 14.2<br>14.3         | <ul> <li>Features of Digital Input/Output Board</li> <li>Problem on Some FPGA Boards and Its Solution</li> <li>14.3.1 Verilog Code to Solve the Malfunctioning of<br/>System Using XC4000 Series FPGA Boards</li> <li>Traffic Light Controller Design</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 558<br>560<br>561<br>562                                                                                                                                                            |

| 14.2<br>14.3         | <ul> <li>Features of Digital Input/Output Board</li> <li>Problem on Some FPGA Boards and Its Solution</li> <li>14.3.1 Verilog Code to Solve the Malfunctioning of<br/>System Using XC4000 Series FPGA Boards</li> <li>Traffic Light Controller Design</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 558<br>560<br>561<br>562<br>565                                                                                                                                                     |

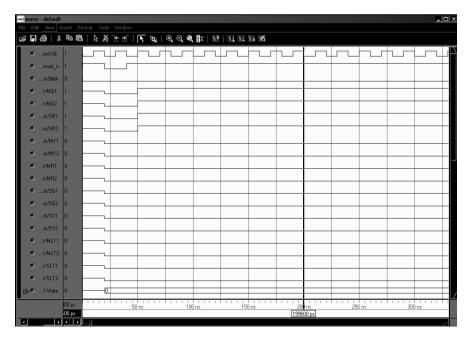

| 14.2<br>14.3         | <ul> <li>Features of Digital Input/Output Board.</li> <li>Problem on Some FPGA Boards and Its Solution.</li> <li>14.3.1 Verilog Code to Solve the Malfunctioning of<br/>System Using XC4000 Series FPGA Boards</li> <li>Traffic Light Controller Design.</li> <li>14.4.1 Verilog RTL Code for Traffic Light<br/>Controller.</li> <li>14.4.2 Test Bench for the Traffic Light Controller.</li> <li>14.4.3 Simulation of Traffic Light Controller.</li> </ul>                                                                                                                                                                                                                                                      | <ul> <li>558</li> <li>560</li> <li>561</li> <li>562</li> <li>565</li> <li>582</li> <li>584</li> </ul>                                                                               |

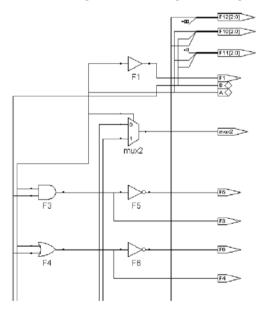

| 14.2<br>14.3         | <ul> <li>Features of Digital Input/Output Board</li> <li>Problem on Some FPGA Boards and Its Solution</li> <li>14.3.1 Verilog Code to Solve the Malfunctioning of<br/>System Using XC4000 Series FPGA Boards</li> <li>Traffic Light Controller Design</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <ul> <li>558</li> <li>560</li> <li>561</li> <li>562</li> <li>565</li> <li>582</li> <li>584</li> <li>586</li> </ul>                                                                  |

| 14.2<br>14.3         | <ul> <li>Features of Digital Input/Output Board</li> <li>Problem on Some FPGA Boards and Its Solution</li> <li>14.3.1 Verilog Code to Solve the Malfunctioning of<br/>System Using XC4000 Series FPGA Boards</li> <li>Traffic Light Controller Design</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <ul> <li>558</li> <li>560</li> <li>561</li> <li>562</li> <li>565</li> <li>582</li> <li>584</li> <li>586</li> <li>587</li> </ul>                                                     |

| 14.2<br>14.3         | <ul> <li>Features of Digital Input/Output Board</li> <li>Problem on Some FPGA Boards and Its Solution</li> <li>14.3.1 Verilog Code to Solve the Malfunctioning of<br/>System Using XC4000 Series FPGA Boards</li> <li>Traffic Light Controller Design</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <ul> <li>558</li> <li>560</li> <li>561</li> <li>562</li> <li>565</li> <li>582</li> <li>584</li> <li>586</li> <li>587</li> </ul>                                                     |

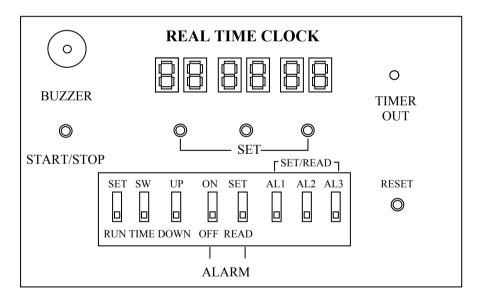

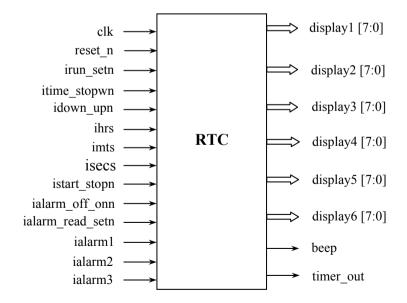

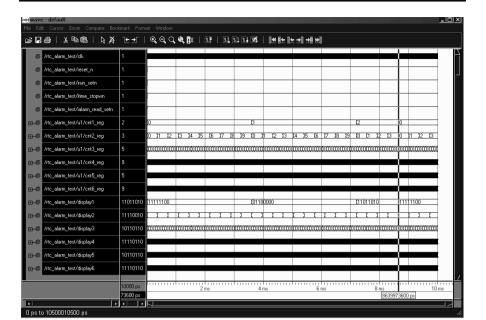

| 14.2<br>14.3         | <ul> <li>Features of Digital Input/Output Board.</li> <li>Problem on Some FPGA Boards and Its Solution.</li> <li>14.3.1 Verilog Code to Solve the Malfunctioning of<br/>System Using XC4000 Series FPGA Boards</li> <li>Traffic Light Controller Design.</li> <li>14.4.1 Verilog RTL Code for Traffic Light<br/>Controller.</li> <li>14.4.2 Test Bench for the Traffic Light Controller.</li> <li>14.4.3 Simulation of Traffic Light Controller.</li> <li>14.4.5 Place and Route Results of Traffic Controller</li> <li>14.4.6 Hardware Setup of Traffic Light Controller.</li> <li>Real Time Clock Design.</li> </ul>                                                                                           | 558<br>560<br>561<br>562<br>565<br>582<br>584<br>586<br>587<br>589<br>592                                                                                                           |

| 14.2<br>14.3<br>14.4 | <ul> <li>Features of Digital Input/Output Board.</li> <li>Problem on Some FPGA Boards and Its Solution.</li> <li>14.3.1 Verilog Code to Solve the Malfunctioning of<br/>System Using XC4000 Series FPGA Boards</li> <li>Traffic Light Controller Design.</li> <li>14.4.1 Verilog RTL Code for Traffic Light<br/>Controller.</li> <li>14.4.2 Test Bench for the Traffic Light Controller.</li> <li>14.4.3 Simulation of Traffic Light Controller.</li> <li>14.4.4 Synthesis Results of Traffic Light Controller</li> <li>14.4.5 Place and Route Results of Traffic Light Controller.</li> <li>14.4.6 Hardware Setup of Traffic Light Controller.</li> <li>14.5.1 Applications.</li> </ul>                         | <ul> <li>558</li> <li>560</li> <li>561</li> <li>562</li> <li>565</li> <li>582</li> <li>584</li> <li>586</li> <li>587</li> <li>589</li> <li>592</li> <li>592</li> <li>592</li> </ul> |