NEW ALGORITHMIS, ARCHITECTURES AND APPLICATIONS FOR RECONFIGURABLE COMPUTING

> Edited by Patrick Lysaght and Wolfgang Rosenstiel

New Algorithms, Architectures and Applications for Reconfigurable Computing

# New Algorithms, Architectures and Applications for Reconfigurable Computing

Edited by

Patrick Lysaght Xilinx, San Jose, USA

and

Wolfgang Rosenstiel University of Tübingen, Germany

#### A C.I.P. Catalogue record for this book is available from the Library of Congress.

ISBN-10 1-4020-3127-0 (HB) Springer Dordrecht, Berlin, Heidelberg, New York ISBN-10 1-4020-3128-9 (e-book) Springer Dordrecht, Berlin, Heidelberg, New York ISBN-13 978-1-4020-3127-4 (HB) Springer Dordrecht, Berlin, Heidelberg, New York ISBN-13 978-1-4020-3128-1 (e-book) Springer Dordrecht, Berlin, Heidelberg, New York

Published by Springer, P.O. Box 17, 3300 AA Dordrecht, The Netherlands.

Sold and distributed in North, Central and South America by Springer, 101 Philip Drive, Norwell, MA 02061, U.S.A.

In all other countries, sold and distributed by Springer, P.O. Box 322, 3300 AH Dordrecht, The Netherlands.

Printed on acid-free paper

All Rights Reserved

© 2005 Springer

No part of this work may be reproduced, stored in a retrieval system, or transmitted or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Printed in the Netherlands.

# Contents

| Introduction                                                                          | ix   |

|---------------------------------------------------------------------------------------|------|

| About the Editors                                                                     | XV   |

| Acknowledgements                                                                      | xvii |

| Architectures                                                                         |      |

| Chapter 1                                                                             |      |

| Extra-dimensional Island-Style FPGAs<br>Herman Schmit                                 | 1    |

| Chapter 2                                                                             |      |

| A Tightly Coupled VLIW/Reconfigurable Matrix and its Modulo<br>Scheduling Technique   | 15   |

| Bingfeng Mei, Serge Vernalde, Diederik Verkest, and Rudy Lauwereins                   |      |

| Chapter 3                                                                             |      |

| Stream-based XPP Architectures in Adaptive<br>System-on-Chip Integration              | 29   |

| Jürgen Becker, Martin Vorbach                                                         |      |

| Chapter 4                                                                             |      |

| Core-Based Architecture for Data Transfer Control in SoC Design                       | 43   |

| Unai Bidarte, Armando Astarloa, Aitzol Zuloaga, José Luis Martín<br>and Jaime Jiménez |      |

| Chapter 5                                                                             |      |

| Customizable and Reduced Hardware Motion Estimation Processors                        | 55   |

| Nuno Roma, Tiago Dias, Leonel Sousa                                                   |      |

## vi

## Methodologies and Tools

| Chapter 6                                                                                                                                                          |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Enabling Run-time Task Relocation on Reconfigurable Systems<br>J-Y. Mignolet, V. Nollet, P. Coene, D. Verkest, S. Vernalde,<br>R. Lauwereins                       | 69  |

| Chapter 7                                                                                                                                                          | 0.1 |

| A Unified Codesign Environment<br>Theerayod Wiangtong, Peter Y.K Cheung, Wayne Luk                                                                                 | 81  |

| Chapter 8                                                                                                                                                          |     |

| Mapping Applications to a Coarse Grain Reconfigurable System<br>Yuanqing Guo, Gerard J.M. Smit, Michèl A.J. Rosien,<br>Paul M. Heysters, Thijs Krol, Hajo Broersma | 93  |

| Chapter 9                                                                                                                                                          |     |

| Compilation and Temporal Partitioning for a Coarse-grain<br>Reconfigurable Architecture                                                                            | 105 |

| João M.P. Cardoso, Markus Weinhardt                                                                                                                                |     |

| Chapter 10                                                                                                                                                         |     |

| Run-time Defragmentation for Dynamically Reconfigurable Hardware<br>Manuel G. Gericota, Gustavo R. Alves, Miguel L. Silva, and<br>José M. Ferreira                 | 117 |

| Chapter 11                                                                                                                                                         |     |

| Virtual Hardware Byte Code as a Design Platform for Reconfigurable<br>Embedded Systems                                                                             | 131 |

| S. Lange, U. Kebschull                                                                                                                                             |     |

| Chapter 12                                                                                                                                                         |     |

| A Low Energy Data Management for Multi-Context Reconfigurable<br>Architectures                                                                                     | 145 |

| M. Sanchez-Elez, M. Fernandez, R. Hermida, N. Bagherzadeh                                                                                                          |     |

| Chapter 13                                                                                                                                                         |     |

| Dynamic and Partial Reconfiguration in FPGA SoCs: Requirements<br>Tools and a Case Study                                                                           | 157 |

| Fernando Moraes, Ney Calazans, Leandro Möller, Eduardo Brião,<br>Ewerson Carvalho                                                                                  |     |

#### Contents

## Applications

| Chapter 14<br>Design Flow for a Reconfigurable Processor<br>Alberto La Rosa, Luciano Lavagno, and Claudio Passerone                                                                       | 171 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Chapter 15<br>IPsec-Protected Transport of HDTV over IP<br>Peter Bellows, Jaroslav Flidr, Ladan Gharai,<br>Colin Perkins, Pawel Chodowiec, and Kris Gaj                                   | 183 |

| Chapter 16                                                                                                                                                                                |     |

| Fast, Large-scale String Match for a 10 Gbps<br>FPGA-based NIDS<br>Ioannis Sourdis and Dionisios Pnevmatikatos                                                                            | 195 |

| Chapter 17                                                                                                                                                                                |     |

| Architecture and FPGA Implementation of a Digit-serial<br>RSA Processor<br>Alessandro Cilardo, Antonino Mazzeo, Luigi Romano,<br>Giacinto Paolo Saggese                                   | 209 |

| Chapter 18                                                                                                                                                                                |     |

| Division in <i>GF(p)</i> for Application in Elliptic Curve<br>Cryptosystems on Field Programmable Logic<br>Alan Daly, William Marnane, Tim Kerins, and Emanuel Popovici                   | 219 |

| Chapter 19                                                                                                                                                                                |     |

| A New Arithmetic Unit in <i>GF</i> (2 <sup><i>M</i></sup> ) for Reconfigurable<br>Hardware Implementation<br><i>Chang Hoon Kim, Chun Pyo Hong, Soonhak Kwon and</i><br><i>Yun Ki Kwon</i> | 231 |

| Chapter 20                                                                                                                                                                                |     |

| Performance Analysis of SHACAL-1 Encryption<br>Hardware Architectures<br>Máire McLoone, J.V. McCanny                                                                                      | 251 |

| Chapter 21                                                                                                                                                                                |     |

| Security Aspects of FPGAs in Cryptographic Applications<br>Thomas Wollinger and Christof Paar                                                                                             | 265 |

viii

| Chapter 22                                                       |     |  |  |  |  |

|------------------------------------------------------------------|-----|--|--|--|--|

| Bioinspired Stimulus Encoder for Cortical Visual Neuroprostheses |     |  |  |  |  |

| Leonel Sousa, Pedro Tomás, Francisco Pelayo, Antonio Martinez,   |     |  |  |  |  |

| Christian A. Morillas and Samuel Romero                          |     |  |  |  |  |

| Chapter 23                                                       |     |  |  |  |  |

| A Smith-Waterman Systolic Cell                                   | 291 |  |  |  |  |

| C.W. Yu, K.H. Kwong, K.H. Lee and P.H.W. Leong                   |     |  |  |  |  |

| Chapter 24                                                       |     |  |  |  |  |

| The Effects of Polynomial Degrees                                | 301 |  |  |  |  |

| Dong-U Lee and Wayne Luk, John D. Villasenor, Peter Y.K. Cheung  |     |  |  |  |  |

|                                                                  |     |  |  |  |  |

## Introduction

In describing the progression of the semiconductor industry over the last several decades, Dr. Tsugio Makimoto proposed a model that has subsequently come to be known as Makimoto's Wave. The model consists of cycles that alternate between product standardization and customization. According to the model, we are now firmly in the middle of a field programmable cycle that is characterized by *standardization in manufacturing and customization in application*. Field programmable gate arrays (FPGAs) are the standard bearers of this new age. At a time when only the largest companies can afford to fully exploit state-of-the-art silicon, FPGAs bring the benefits of deep submicron and nano-scale integration to even the smallest teams. It is fitting then that we are witnessing a huge surge in the amount of research being conducted worldwide into field programmable logic and its related technologies. This book was inspired by the desire to compile a selection of the best of the current research efforts and present it in an accessible way to a wide audience.

The book consists of a collection of invited contributions from the authors of some of the best papers from the Design, Automation, and Test conference in Europe (DATE'03) and the Field Programmable Logic conference (FPL'03). The contributions are organized into twenty-four chapters. In all, eighty-five authors have described their latest research, making this volume a unique record of the state-of-the-art in FPGA-related research.

The twenty-four chapters are organized into three main categories. The first five chapters address hard and soft architectures. Chapters 6 to 13 are concerned with design methodology and tools. The final eleven chapters are devoted to applications, of which chapters 14 to 21 focus on networking, encryption and security. Some of the research reported here defies simple classification so there is more than one example of work that could appear in more than one category. Nonetheless, the classification scheme does impose a useful order on the work.

#### Architectures

In the opening chapter, Schmit presents an insightful analysis of the challenges facing architects of island-style FPGAs in scaling interconnect to match increasing netlist complexity. His approach is based on the introduction of additional wiring in the *logical* third and fourth dimensions and then mapping these additional routes into the two-dimensional silicon. The benefits the author claims for this strategy include longer tile life, better evolution of CAD tools and a unification of the analysis of time-multiplexed FPGAs.

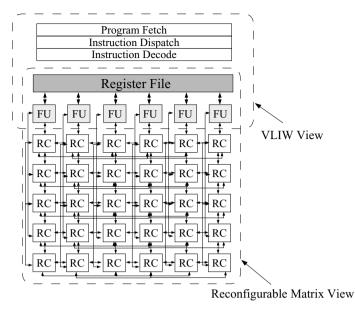

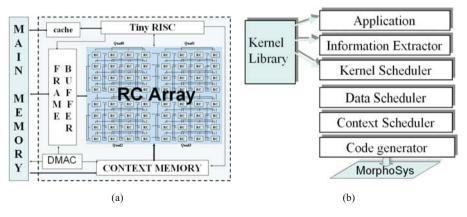

The next two chapters introduce two new coarse-grained architectures. The motivation for coarse-grained architectures includes better computational and power efficiency, and improved opportunities for the automatic compilation of designs from higher-level design representations. Mei and colleagues propose ADRES (Architecture for Dynamically Reconfigurable Embedded System) which is a novel integration of a VLIW processor and a coarse-grained reconfigurable matrix that combine to form a single architecture with two virtual, functional views. They also present a novel modulo scheduling technique which they claim can map kernel loops on to the matrix efficiently by simultaneously solving the placement, routing and scheduling problems.

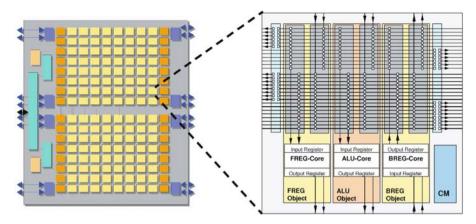

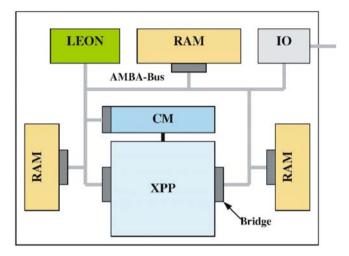

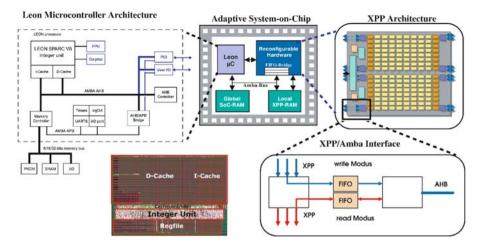

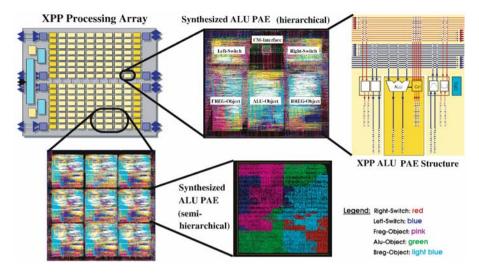

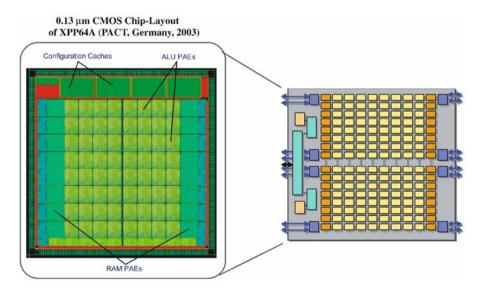

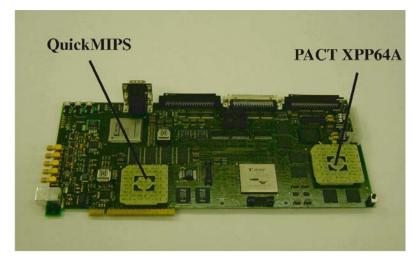

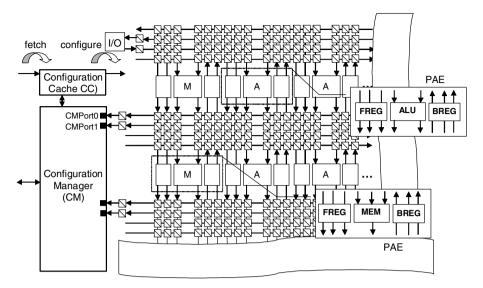

Chapter 3 describes the structures and principles of the stream-based, reconfigurable PACT/XPP architectures. The status of an adaptive System-on-Chip (SoC) integration is given, consisting of a SPARC-compatible LEON processorcore, a coarse-grain XPParray, and an Amba-based communication interfaces.

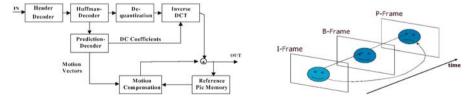

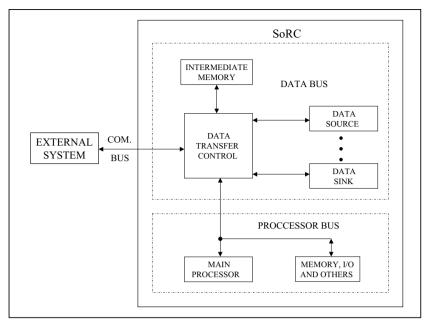

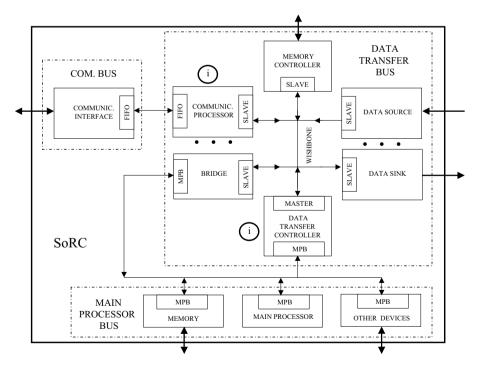

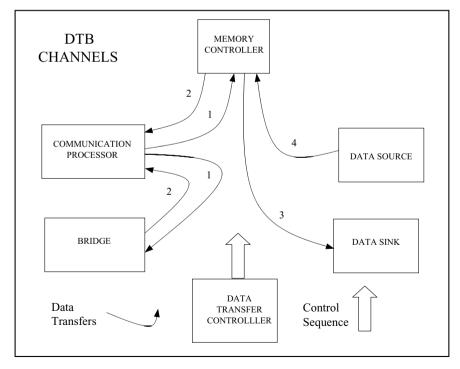

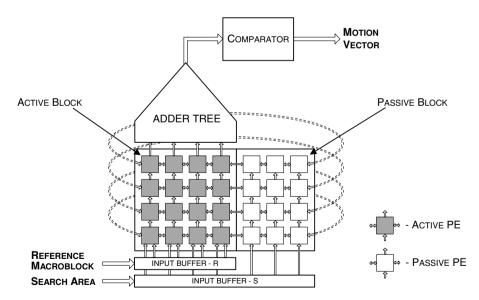

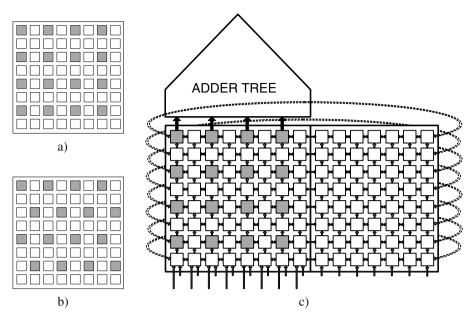

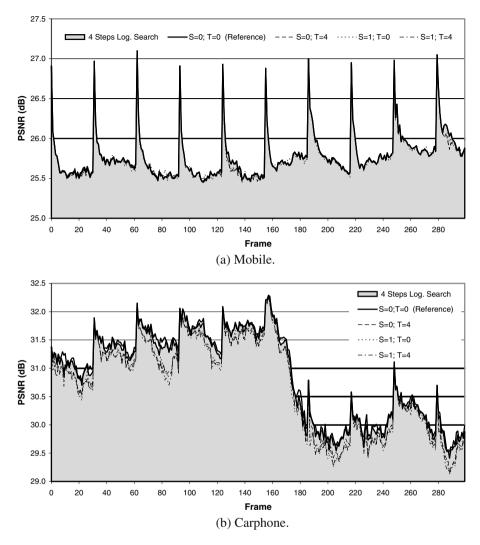

In chapters 4 and 5 two soft architectures are proposed. Bidarte et al describe their *system on reconfigurable chip* (SORC). This is a core based system-onchip architecture that they have verified with two industrial control type applications. They considered a number of interconnection networks before selecting the Wishbone interconnection architecture for portable IP cores that is available from OpenCores.org. The second core-based architecture, proposed by Roma et al, is specialized for motion estimation applications. The authors describe a customizable core-based architecture for real-time motion estimation in FP-GAs using a two-dimensional array processor with extensive parallelism and pipelining. By applying sub-sampling and truncation techniques, the complexity of the architecture can be tailored to provide fast and low cost real-time motion estimation.

#### **Methodology and Tools**

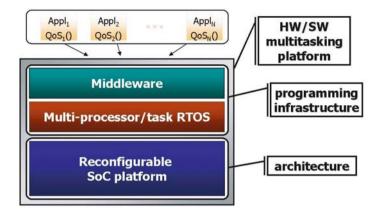

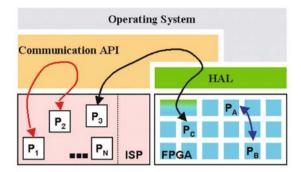

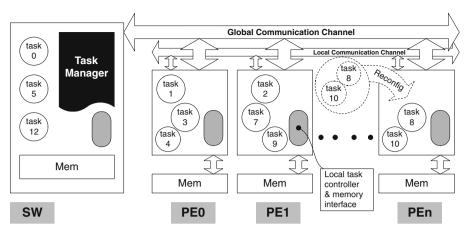

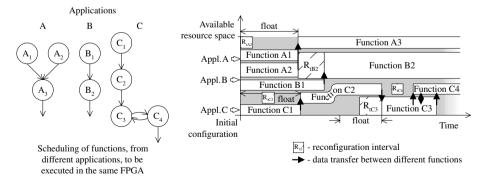

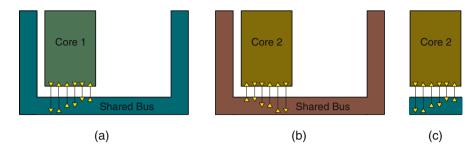

The ability to (re)schedule a task either in hardware or software will be an important asset in a reconfigurable systems-on-chip. To support this feature Mignolet et al. have developed an infrastructure that, combined with a suitable design environment permits the implementation and management of hardware/software relocatable tasks. The authors present a strategy for heterogeneous context switching together with a description of the communication scheme and the design environment.

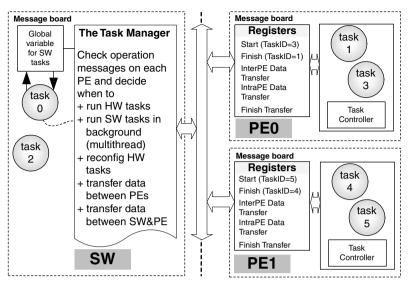

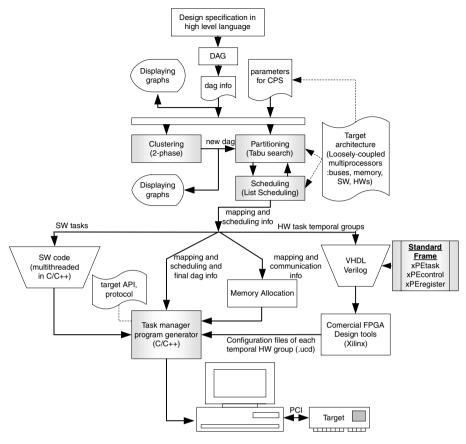

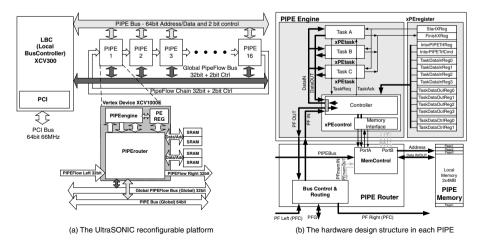

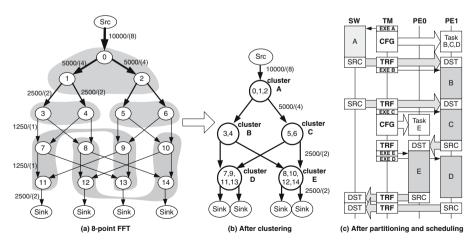

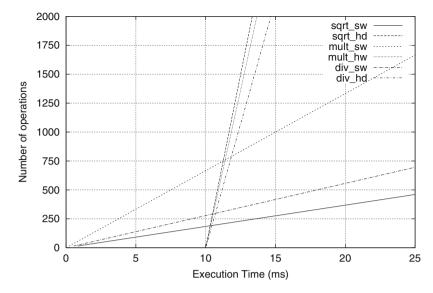

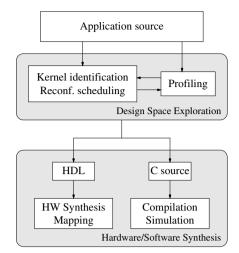

In Chapter 7, Wiangtong et al describe a semi-automatic co-design environment for the *UltraSONIC* reconfigurable computer. *UltraSONIC* is targeted at

#### Introduction

real-time video applications and consists of a single multitasking host processor augmented with multiple reconfigurable coprocessors. Tasks are assumed to be dataflow intensive with few control flow constructs. By treating hardware and software tasks uniformly, the authors are able to engineer a common run-time task manager with support for automatic partitioning and scheduling. They validate their flow by implementing an 8-point FFT algorithm.

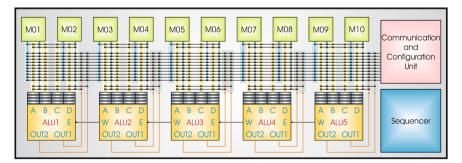

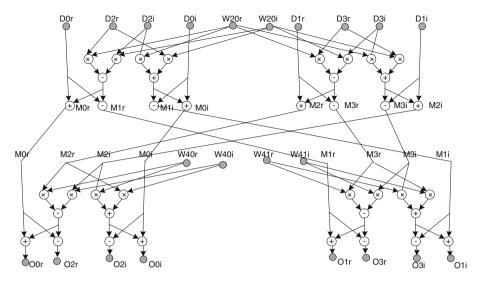

In Chapter 8, Guo et al describe a design method to map applications written in a high level source language program, like C, to a coarse grain reconfigurable architecture, called MONTIUM. The source code is first translated into a control dataflow graph (CDFG). Then after applying graph clustering, scheduling and allocation on this CDFG, it can be mapped onto the target architecture. High performance and low power consumption are achieved by exploiting maximum parallelism and locality of reference respectively. Using a special mapping method, the flexibility of the MONTIUM architecture can be exploited.

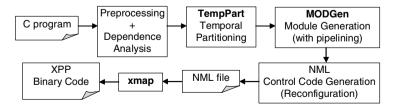

The eXtreme Processing Platform (XPP) is a coarse-grained dynamically reconfigurable architecture which was already introduced in Chapter 3. Chapter 9 presents a compiler aiming to program the XPP using a subset of the C language. The compiler, apart from mapping the computational structures onto the available resources on the device, splits the program in temporal sections when it needs more resources than the physically available. In addition a scheme to split the program such that the reconfiguration overheads are minimized, taking advantage of the overlapping of the execution stages on different configurations is presented.

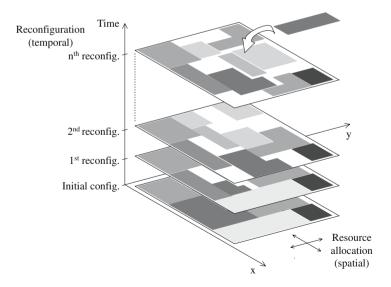

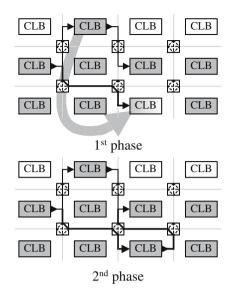

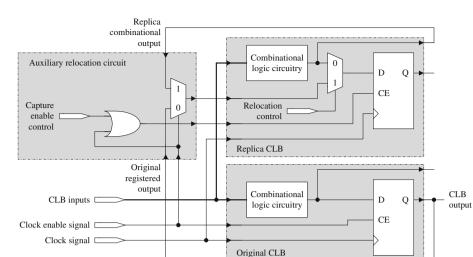

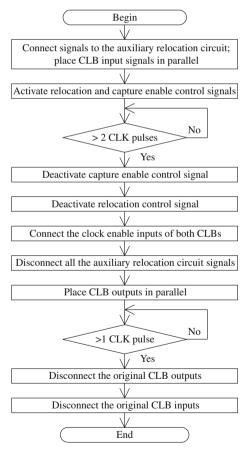

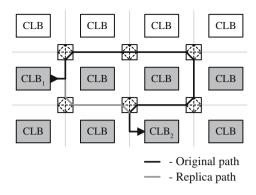

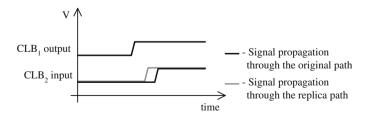

A rearrangement of the currently running functions is presented in Chapter 10 to obtain enough contiguous space to implement incoming functions, avoiding the spreading of their components and the resulting degradation of system performance. A novel active relocation procedure for Configurable Logic Blocks (CLBs) is presented, able to carry out online rearrangements and defragmenting the available FPGA resources without disturbing functions currently running.

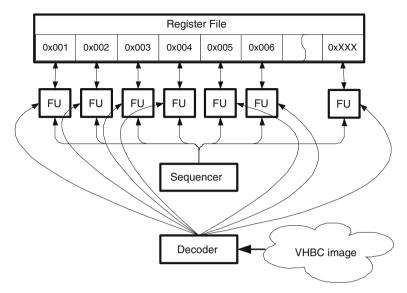

Chapter 11 shows how the hardware parts of an embedded system can be implemented in a hardware byte code, which can be interpreted using a virtual hardware machine running on an arbitrary FPGA. The authors describe how this approach leads to fast, portable and reconfigurable designs, which run on any programmable target architecture.

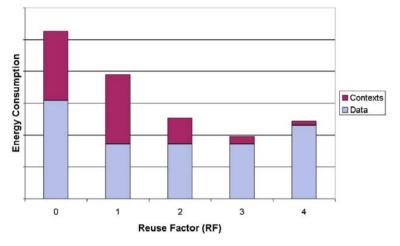

Chapter 12 presents a new technique to improve the efficiency of data scheduling for multi-context reconfigurable architectures targeting multimedia and DSP applications. The main goal of this technique is to diminish application energy consumption. Two levels of on-chip data storage are assumed in the reconfigurable architecture. The authors show that a suitable data scheduling could decrease the energy required to implement the dynamic reconfiguration of the system.

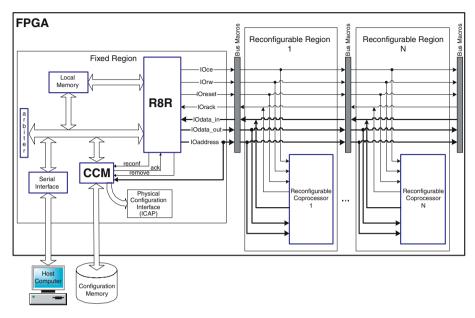

Chapter 13 focuses on design methods for dynamic reconfiguration targeted to SoCs implemented on FPGAs. The main distinction between conventional digital systems design and the methods addressed here is the possibility of dynamically replacing hardware modules (i.e. IP cores) while the rest of the system is still working.

#### Applications

Chapter 14 describes an approach to hardware/software design space exploration for reconfigurable processors. The existing compiler tool-chain, because of the user-definable instructions, needs to be extended in order to offer developers an easy way to explore the design space. Such extension often is not easy to use for developers who have only a software background, and are not familiar with reconfigurable architecture details or hardware design. The authors illustrate their approach by using a real case study, a software implementation of a UMTS turbo-decoder that achieves a good speed-up of the whole application by exploiting user-defined instructions on the dynamically reconfigurable portion of the data path.

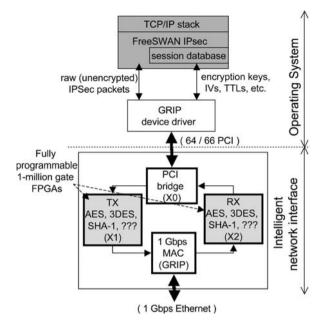

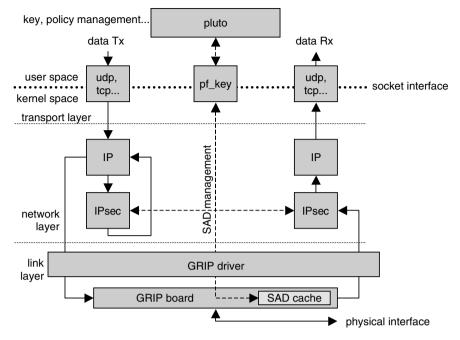

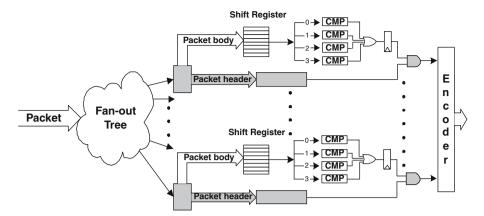

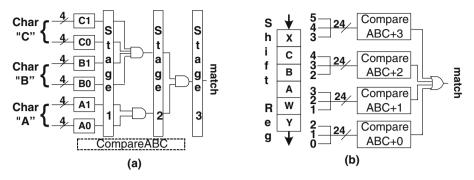

The work of Bellows et al. is motivated by the fact that network performance is doubling every eight months while the processing power of modern CPUs is failing to keep pace. Faced with handling higher network data rates and more complex encryption algorithms, the authors describe how they have developed an accelerator based on FPGAs called GRIP (gigabit-rate IPsec). GRIP is a network-processing accelerator that uses Xilinx FPGAs and integrates into a standard Linux-TCP/IP host equipped with IPsec, a set of protocols developed to support secure exchange of packets at the layer. The accelerator can handle full end-to-end, AES encrypted HDTV at 1 Gbps line rates on commodity networks. Meanwhile, Sourdis and Pnevmatikatos describe in Chapter 16 a network intrusion detection system (NIDS) designed to operate at the 10 Gbps OC192 line speeds. Using extensive parallelism and fine-grained pipelining, they have achieved throughput in excess of 11 Gbps with 50 rules from the open source Snort system.

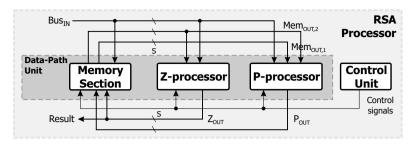

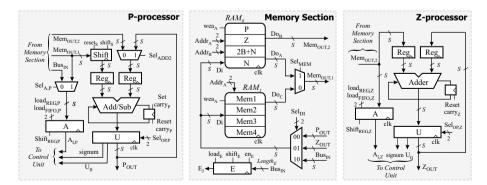

In Chapter 17 Cilardo et al. present a modification of the popular Montgomery algorithm for modular multiplication through the addition of carrysave number representation. They evaluate their approach by implementing the Rivest-Shamir-Adleman (RSA) public-key cryptography algorithm. Their algorithm results in a highly modular, bit-sliced architecture that maps efficiently on to FPGAs and yields a 32% speed advantage over previously reported implementations.

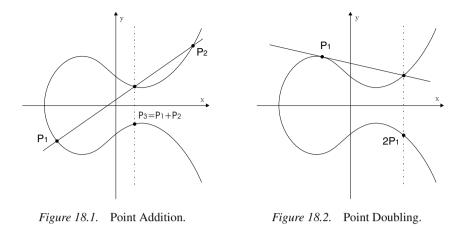

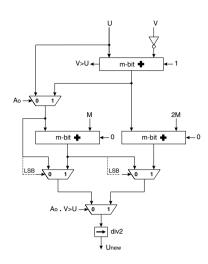

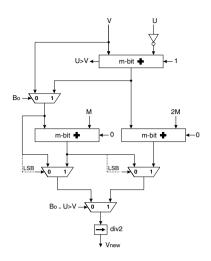

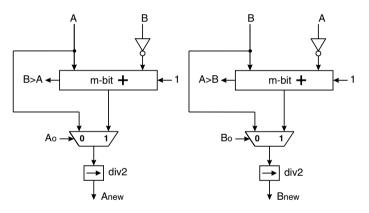

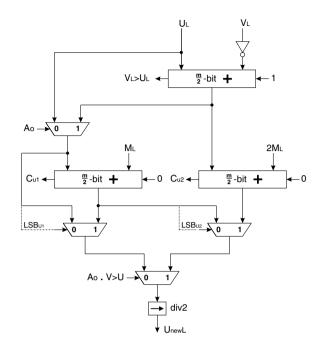

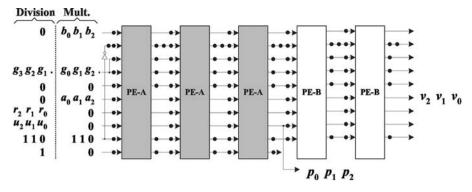

The relative complexity of the discrete log problem in elliptic curve cryptography (ECC) can result in both increased speed and reduced key size for a given level of security. ECC has potential advantages in applications where bandwidth, power and silicon area are at a premium. Daly et al. propose a new architecture for modular division using what is essentially a look-ahead strategy. They precompute elements of the algorithm before finalizing the most time-consuming, magnitude comparison operation to yield circuits that are 40% faster than prior work. In Chapter 19, Kim and colleagues also focus on ECC. They propose a new systolic architecture that can perform both multiplication and division. This is a parameterizable architecture that is regular, modular and is unidirectional with respect to data flow. Consequently it can handle arbitrary irreducible polynomials and is scalable with respect to the size of the underlying Galois field.

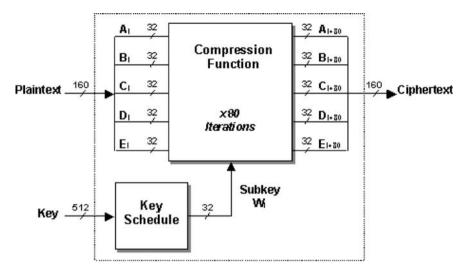

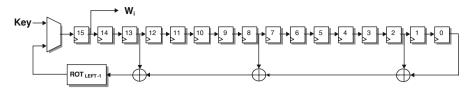

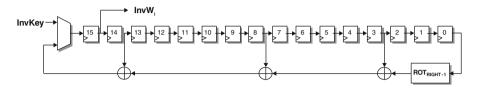

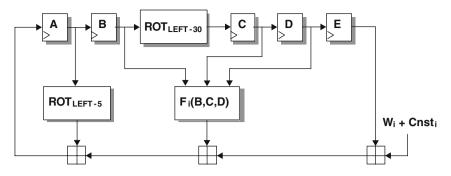

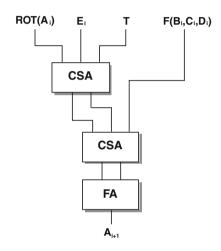

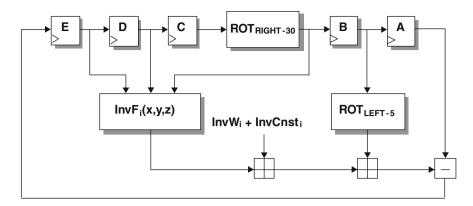

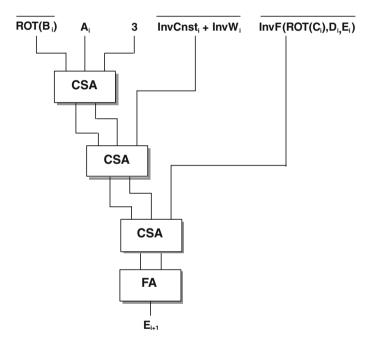

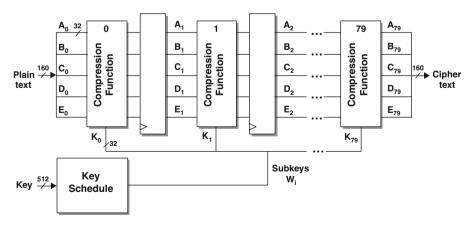

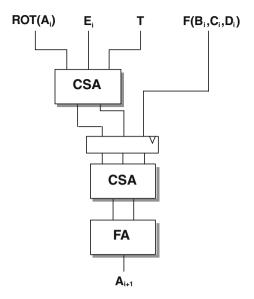

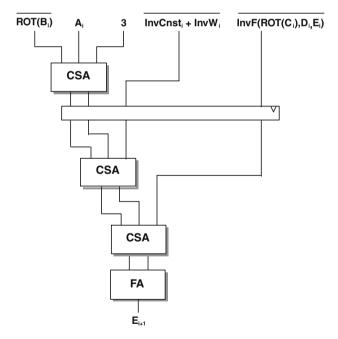

McLoone and McCanny present an algorithm for decryption of the SHACAL-1 block cipher along with new implementations of the SHACAL-1/2 encryptionand decryption algorithms. SHACAL is a block cipher from Gemplus International that has its origins in ANSI's Secure Hashing Algorithm (SHA) used in encryption mode. The authors describe both compact, iterative implementations and fast, highly-pipelined implementations. Impressive throughputs of 23 Gbps for SHACAL-1 and 26 Gbps for SHACAL-2 are reported with Xilinx Virtex-II FPGAs.

Our discussion of security closes with a survey performed by Wollinger and Paar on the issues concerning the use of FPGAs in secure systems. The paper is noteworthy for the catalogue of methods of attack that it considers. Some of the more esoteric of these have not yet been applied to FPGAs to the best of the authors knowledge. While they do not recommend FPGAs in general for secure applications, the authors do note that physical attacks against FPGAs are very complex and even more difficult that analogous attacks against mask programmed ASICs.

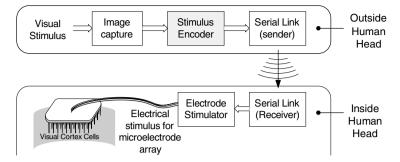

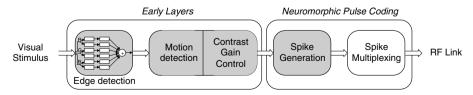

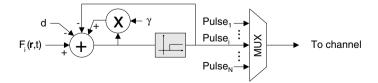

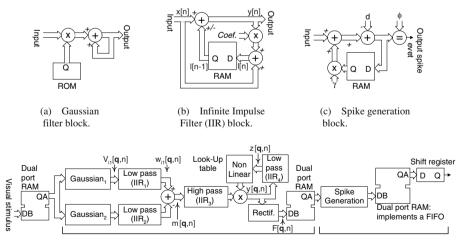

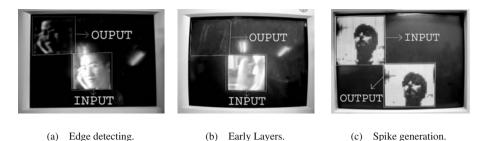

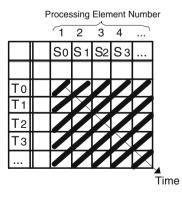

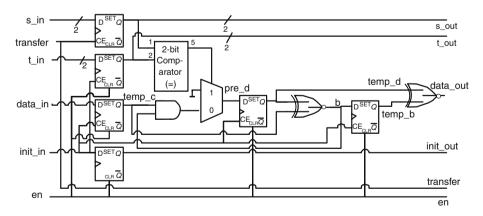

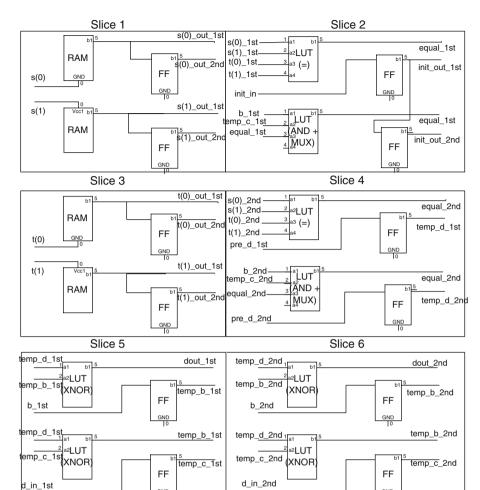

Sousa and colleagues report on their use of FPGAs to develop a visual encoding system that may be used to construct a portable visual neuroprosthesis for profoundly blind people. The authors are able to exploit time-shared circuit techniques while still satisfying the real-time response of their system. They also exploit the FPGA reconfigurability to tailor devices to the requirements of individual patients.

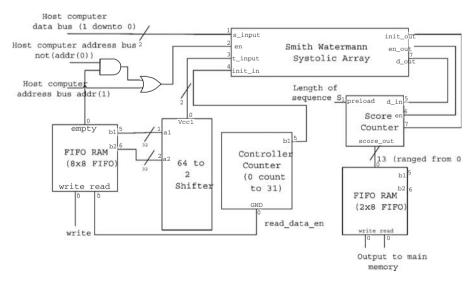

In Chapter 23, Yu et al describe a new design for a Smith-Waterman systolic cell. The Smith-Waterman algorithm can be used for sequence alignment when searching large databases of DNA information. It makes all pair-wise comparisons between string pairs thus achieving high sensitivity. However, this is offset by higher computation costs than more popular techniques, hence the motivation for faster implementations. The authors design allows the edit distance between two strings to be computed without the need to use runtime reconfiguration as was required with earlier implementations that achieved comparable performance.

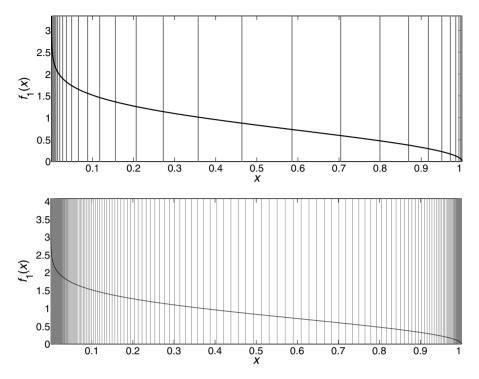

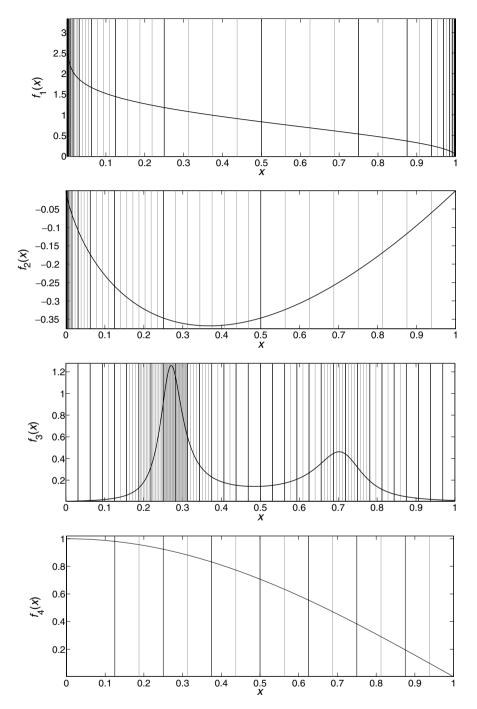

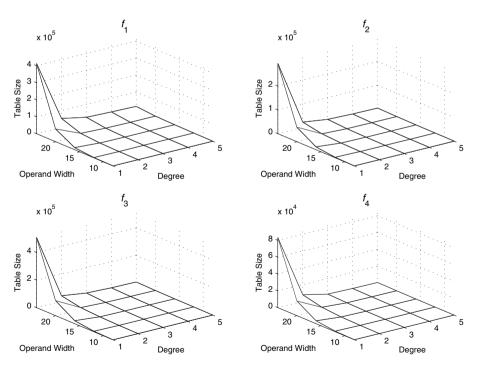

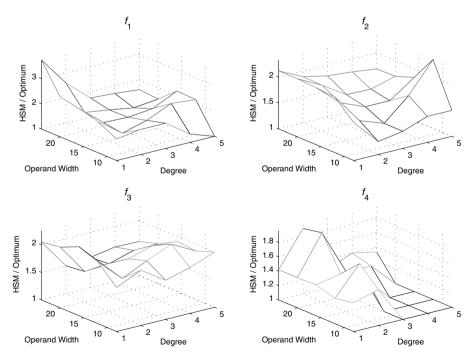

In the final chapter, Lee et al. explore the influence of polynomial degrees on the calculation of piecewise approximation of mathematical functions using hierarchical segmentation. Mathematical functions can be computationally expensive to evaluate so approximations such as look-up tables are commonly deployed. However for complex functions, the size of the tables becomes impractical. An alternative is to segment the continuous function and perform piecewise approximation with one or more polynomials of varying degrees over the closed interval. Another innovation is to use a hierarchy of uniform segments and segments whose sizes vary by powers of two. Lee reports that hierarchical function segmentation (HFS) is particularly effective for non-linear regions and that it outperforms optimum uniform segmentation by a factor of two over a wide range of operand widths and polynomial degrees. Furthermore, second order polynomials start to outperform first order approximations at operand widths of sixteen bits.

## About the Editors

**Patrick Lysaght** is a Senior Director in Xilinx Research Labs, San Jose, California where he is responsible for research into reconfigurable and embedded systems and for the Xilinx University Program. Prior to joining Xilinx in 2001, he was a Senior Lecturer in the Department of Electronic and Electrical Engineering at the University of Strathclyde in Glasgow and also at the Institute for System Level Integration in Livingston, Scotland. He has worked for Hewlett Packard in the UK in a number of roles including research and development, marketing, and sales. Patrick received his BSc (Electronic Systems) in 1981 from the University of Limerick, Ireland and his MSc (Digital Techniques) in 1987 from Heriot Watt University, Edinburgh, Scotland.

Patrick's research interests include real-time embedded systems, reconfigurable computing and system-level design. He is the author of more than forty technical papers and is active in the organization of several international conferences. He currently serves as chairman of the steering committee of the Field Programmable Logic Conference (FPL), the world's foremost conference dedicated to field programmable logic.

**Wolfgang Rosenstiel** is University Professor and holds the Chair for Computer Engineering at the University of Tübingen. He is also Managing Director of the Wilhelm Schickard Institute at Tübingen University, and Director for the Department for System Design in Microelectronics at the Computer Science Research Centre FZI. He is on the Executive Board of the German edacentrum.

His research areas include electronic design automation, embedded systems, computer architecture, multimedia, and artificial neural networks. He is member of the executive committees of DATE and ICCAD. As topic chair of the DATE program committee for configurable computing he was in charge of the contribution from DATE related papers to this book.

## Acknowledgements

Several people deserve our most sincere gratitude for making this book possible. First and foremost among these are the many authors who have contributed their time and expertise to the project. The technical program committees of the FPL'03 and DATE'03 conferences also provided considerable help in the selection of the papers. We were guided by the expertise of their review panels in determining which papers to include.

We are grateful to the staff of Kluwer Academic Publishers for continuing to provide a path by which the latest research can be quickly brought to publication. Mark de Jongh, our commissioning editor, deserves special acknowledgement for being the champion of this project.

Patrick Lysaght would like to thank his wife, Janette, and his daughters, Emily, Rebecca and Stephanie, for all their love and support.

Wolfgang Rosenstiel would like to thank his wife, Christel, and his children, Alexander, Felix and Simone for their love and support.

Finally, we hope that the work compiled here will prove useful to existing researchers and inspire new ones to enter this exciting field of research for the first time.

#### Patrick Lysaght and Wolfgang Rosenstiel

July 2004

Architectures

## Chapter 1

## **Extra-dimensional Island-Style FPGAs**

Herman Schmit

Department of ECE Carnegie Mellon University Pittsburgh, PA, 15213 USA herman\_schmit@ieee.org

Abstract This paper proposes modifications to standard island-style FPGAs that provide interconnect capable of scaling at the same rate as typical netlists, unlike traditionally tiled FPGAs. The proposal uses logical third and fourth dimensions to create increasing wire density for increasing logic capacity. The additional dimensions are mapped to standard two-dimensional silicon. This innovation will increase the longevity of a given cell architecture, and reduce the cost of hardware, CAD tool and Intellectual Property (IP) redesign. In addition, extra-dimensional FPGA architectures provide a conceptual unification of standard FPGAs and time-multiplexed FPGAs.

Keywords: FPGA Architecture, Interconnect, Rent Exponent

#### Introduction

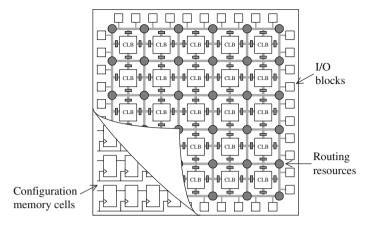

Island-style FPGAs consist of mesh interconnection of logic blocks, connection blocks and switchboxes. Commercial FPGAs from vendors such as Xilinx are implemented in an island-style. One advantage of island-style FPGAs is that they are completely tileable. A single optimized hardware tile design can be used in multiple products all with different capacity, pin count, package, etc., allowing FPGA vendors to build a whole product line out of a single relatively small design. The tile also simplifies the CAD tool development effort. The phases of technology mapping, placement, routing and configuration generation are all simplified by the regularity and homogeneity of the island-style FPGA. Finally, these tiled architectures are amenable to a re-use based design methodology. A design created for embedding in larger designs, often called a core, can be placed to any location within the array, while preserving routing and timing characteristics.

The inherent problem with tiled architectures is that they do not scale to provide the interconnect typical of digital circuits. The relationship of design interconnect and design size is called Rent's rule. This relationship is described in [12], where it is shown that a partition containing *n* elements has  $Cn^p$  pins either entering or leaving the partition. The quantity *p*, which is known as the Rent exponent, has been empirically determined to be in the range from 0.57 to 0.75 in a variety of logic designs. In a tiled architecture, the number of logic elements in any square bounding box is proportional to the number of tiles contained in the square, and the number of wires crossing the square is proportional to the perimeter of the square root of the logic capacity, and the "supplied" Rent exponent is 1/2. Supply therefore can never keep up with interconnect.

Commercial vendors have recognized this phenomenon. Succeeding generations of FPGAs always have more interconnect per logic block. This has the effect of keeping up with the Rent exponent by increasing the constant interconnect associated with each tile, i.e. increasing the C term in Rent's formula. There are several problems with this solution. First, it requires that the tile must be periodically redesigned, and all the CAD tools developed for that tile must be updated, tested and optimized. Second, all the cores designed for an early architecture cannot be trivially mapped to the new architecture.

What would be preferable would be to somehow scale the amount of interconnect between cells, while still providing the benefits of a tiled architecture, such as reduced hardware redesign cost and CAD tool development. This is impossible in conventional island-style FPGAs because they are two-dimensional, which means that the Rent exponent of supplied interconnect is fixed at one half. This paper proposes a new island-style architecture, based on three- and four-dimensional tiling of blocks, that can support Rent exponents greater than 0.5 across an entire family of FPGAs.

Three-dimensional FPGAs have been proposed frequently in the literature [14], [13], [1], [2], [8], but commercial three-dimensional fabrication techniques, where the transistors are present in multiple planes, do not exist. An optoelectrical coupling for three-dimensional FPGAs has also been proposed in [6], but there are no instances of such couplings in large commercial designs as yet. Four-dimensional FPGAs face even greater challenges to actual implementation, at least in this universe. Therefore, this paper proposes ways to implement three- and four-dimensional FPGAs in planar silicon technology. Surprisingly, these two-dimensional interconnect structures resemble double

and quad interconnect lines provided in commercial island-style FPGAs, albeit with different scaling behavior.

#### 1.1 Architecture

Extra-dimensional FPGAs can provide interconnect that matches the interconnect required by commercial designs and that scales with design size. This section describes how these extra dimensions provide scalable interconnect. Possible architectures for multi-dimensional FPGAs are discussed in the context of implementation on two-dimensional silicon. Three- and four-dimensional FPGA architectures are proposed, which will be the subject of placement and routing experiments performed in subsequent sections.

As discussed previously, a 2-D tiled FPGA provides a Rent exponent of 1/2 because of the relationship of the area and perimeter of a square. In a threedimensional FPGA, assuming that all dimensions grow at an equal rate, the relationship between volume and surface area is governed by an exponent of 2/3. Therefore in a perfect three-dimensional FPGA, the supplied interconnect has a Rent exponent of 2/3. By extension, the Rent exponent for a four-dimensional architecture is 3/4.

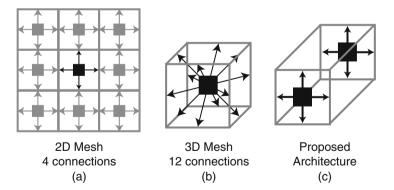

There are many ways to construct an extra-dimensional FPGA. A conventional island-style FPGA can be envisioned as an array of CLBs, each of which is surrounded by a square of interconnect resources. The CLB connects to each of the edges of the square that surrounds it, as shown in Figure 1.1(a). By extension, a 3-D FPGA would have a three dimensional interconnection mesh, with CLBs located in the center of the cubes that make up this mesh. Each CLB would

*Figure 1.1.* Two and three dimensional interconnect points: as shown in (a) a CLB in a 2D mesh must connect to 4 wires. A CLB in a 3D mesh must (b) connect to twelve points. The proposed architecture has 2D CLBs interconnected to the squares in a 3D mesh.

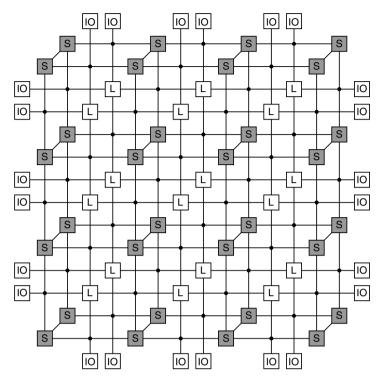

*Figure 1.2.* Three dimensional FPGA in two dimensions: This particular FPGA is a  $3 \times 3 \times 2$  array of CLBs. There are IOs around the periphery. Switch Blocks are labelled "S" and CLBs are labelled "L". Connections between *xy* planes take place in the diagonal channels between switch boxes. All lines in this figure are channels containing multiple wires.

have to connect to all twelve edges of the cube, as illustrated in Figure 1.1(b). This entails a three-fold increase in the number of places that CLB IOs connect, which either means greater delay, greater area, and perhaps worse placement and routing. In addition, this "cube" interconnect is very difficult to lay out in two-dimensional silicon. In a four-dimensional FPGA, the CLB would have to connect to thirty-two of the wires interconnecting a hypercube in the mesh, and is even harder to lay out in two dimensions.

An alternative proposal is to allow CLBs to exist only on planes formed by the x and y dimensions. These CLBs only connect to wires on the same xyplane. A multi-dimensional FPGA is logically constructed by interconnecting planes of two-dimensional FPGAs, as illustrated in Figure 1.1(c). This keeps the the number of IOs per CLB equal to conventional FPGAs, while still providing the benefits of an extra-dimensional FPGA.

In our proposed architecture, two adjacent xy planes of CLBs are interconnected by the corresponding switch boxes. For example, in a logically threedimensional FPGA, the switch box at (x, y) in plane z is connected to the

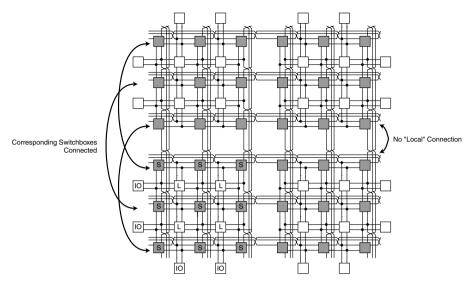

*Figure 1.3.* Four dimensional FPGA: This FPGA has dimensions of  $2 \times 2 \times 2 \times 2$  CLBs. The connections between dimensions take place on the long lines that go from one switch box to the corresponding box in another dimension.

switch box at (x, y) in plane z + 1 and plane z - 1. Such a three-dimensional switchbox architecture was used in [1].

A problem with these extra-dimensional switch boxes is the increased number of transistors necessary to interconnect any wire coming from three or four dimensions. When four wires meet within a switch box, coming from all four directions in a two-dimensional plane, six transistors are necessary to provide any interconnection. With three dimensions, six wires come from every direction, requiring 15 transistors to provide the same flexibility of interconnect. With four dimensions, 28 transistors are necessary at each of these switch points. We will assume that extra-dimensional switch boxes include these extra number of transistors. We will later show that this overhead is mitigated by the reduction in channel width due to extra-dimensional interconnect. It is worth noting that there are only 58 possible configurations of switch point in a 3D switch box,<sup>1</sup> and 248 possible configurations of a 4D switch point. Therefore the amount of configuration for these switch points could potentially be significantly reduced to six or eight bits. It is also possible that all 15 or 28 transistors are not necessary to provide adequate interconnect flexibility. Future work will explore optimizations of the switch box architectures for extra-dimensional FPGAs.

Figure 1.2 and Figure 1.3 show feasible layouts for three- and fourdimensional FPGAs in two-dimensional silicon. The four-dimensional layout is particularly interesting, because it allows for close interconnections between neighboring CLBs, and because it is symmetric in both x and y dimensions. The most interesting aspect of the four-dimensional FPGA is how the interconnect resembles the interconnect structure of commercial island-style FPGAs. Particularly, the interconnections between different xy planes resemble the double and quad lines in Xilinx 4000 and Virtex FPGAs. These lines skip across a number of CLBs, in order to provide faster interconnect over long distance.

The primary difference between the traditional island-style with double and quad lines and the proposed 4D FPGA is that the length of the long wires increases when the size of the xy plane increases. This is the key to providing scalable interconnect. The length of wires in the two-dimensional implementation of the 4D FPGA increases as the logical size of the device increases. This does mean that the delay across those long wires is a function of the device size, which presents an added complication to timing-oriented design tools. Fortunately, interconnection delay in commercial FPGAs is still dominated by the number of switches in any path and not the length of the net.<sup>2</sup>

The assumption that the physical channel width is proportional to the number of wires passing through that channel leads to the conclusion that the four-dimensional FPGA in Figure 1.3 would be much larger than the twodimensional FPGA with the same number of CLBs. In real FPGA layouts however, the largest contributor to channel width is the number of programmable interconnect points in the channel, and the width of the switch box. Because these points require one to six transistors, they are much larger than the minimum metal pitch. Most wires in the channel of the four-dimensional FPGA do not contact any interconnect points however. These wires can be tightly routed at a higher level of metal, and may only minimally contribute to total channel width.

A second substantial difference between the proposed 4D FPGA and the traditional island-style FPGA is that in the commercial FPGA, the local connections are never interrupted. In the 4D FPGA, there is no local interconnection from the boundary of one xy plane to the corresponding boundary of the adjacent xy plane. The reason for this is to provide for tiling of IP blocks. Suppose we want to use a four-dimensional core in a four-dimensional FPGA. To guarantee that this core will fit in this FPGA, all four dimensions of the core must be smaller than the four dimensions of the FPGA. If there are local connections between xy planes, that cannot be guaranteed. A core that was built on a device with x = 3, and which used local connections between two xy planes would only fit onto other devices with x = 3.

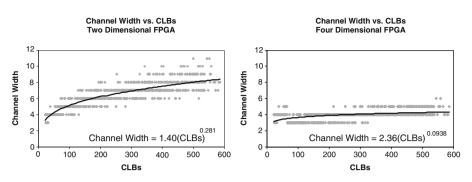

The next section will describe an experiment that compares the scaling of interconnect in two- and four-dimensional FPGA. First, Rent's rule is demonstrated by measuring how the channel width of a two-dimensional FPGA increases as the size of the design increases. When the same suite of netlists is placed and routed on an 4D FPGA, the channel width remains nearly constant.

## **1.2** Experimental Evaluation

In order to demonstrate the effectiveness of extra-dimensional FPGAs, a large set of netlists have been placed and routed on both two- and four-dimensional FPGAs. The minimum channel width required in order to route these designs is compared. In the two-dimensional FPGA, the channel width grows with respect to the logical size of the design. The four-dimensional FPGA scales to provide exactly the required amount of interconnect, and channel width remains nearly constant regardless of the design size.

A significant obstacle to performing this experiment was to acquire a sufficiently large set of netlists in order to make conclusions based on measured data. Publicly available circuit benchmark suites are small, both in the number of gates in the designs, and the number of designs in the suites. In this paper we use synthetic netlists generated by the CIRC and GEN tools [10, 11]. CIRC measures graph characteristics, and has been run on large sets of commercial circuits. GEN constructs random netlists that have the same characteristics as the measured designs. We used the characteristics measured by CIRC on finite state machines to generate a suite of 820 netlists ranging from 20 to 585 CLBs.

The placement and routing software we will use is an extended version of the VPR tool [3]. The modifications to this software were relatively simple. The placement algorithm is extended to use a multi-dimensional placement cost. The cost function is a straight-forward four-dimensional extension of the two-dimensional cost, which is based on the RISA cost function [4]. The cost of routing in the two additional dimensions is scaled by a small factor to encourage nets to be routed in a single xy plane.

The logic block architecture used for this experiment is the standard architecture used in VPR. This architecture consist of a four-input lookup table (LUT) and a bypassable register. The switch box architecture is the Xilinx-type (also known as subset or disjoint), where the n-th channel from one direction connects to the n-th channel in every other direction.

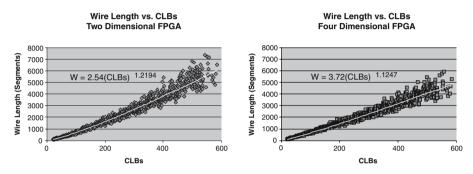

VPR works by first placing the design, and then attempting to find the minimal channel width that will allow routing of the design. It performs a binary search in order to find this minimal channel width. The results of routing the netlist suite on the two-dimensional and four-dimensional architecture are shown in Figure 1.4, which plots the maximum channel width versus the netlist size in CLBs. The best-fit power graph has been fit to this data, showing an exponent of 0.28 for the two-dimensional FPGA. As shown in [7] and [9], this indicates the Rent exponent of these designs is approximately 0.28 + 0.5 = 0.78, which is large, but possibly reasonable for the design of an FPGA architecture.

Even a four dimensional FPGA cannot provide interconnect with a Rent exponent of 0.78. In our experiment, the extra dimensions of the FPGA scale at one-eight the rate of the x and y dimensions. If the x and y dimensions are less

Figure 1.4. Two- and Four-Dimensional FPGA Channel Width.

Figure 1.5. Wirelengths for Two- and Four-dimensional FPGAs.

than eight, there is no other extra dimensions to the FPGA (the FPGA is simply two-dimensional). With x or y in the range of 8 to 16, there are two planes of CLBs in each of the extra dimensions.

The channel width for the four-dimensional FPGA, as shown in Figure 1.4 is comparatively flat across the suite of netlists. Figure 1.5 demonstrates the effectiveness of the technique by showing total wire length, in channel segments, for each design. When fit to a power curve, the two dimensional FPGA exhibits a much larger growth rate than the four dimensional FPGA. Superlinear growth of wire length was predicted by [7] as a result of Rent's rule. The four dimensional FPGA evidences a nearly linear relationship between wire length and CLBs, indicating that the supply of interconnect is keeping pace with the demand.

As mentioned in previously, the four dimensional switch box might have more than four times more bits per channel compared to the two dimensional switch box. Table 1.1 shows the number of configuration bits necessary to program the interconnect for a two- and four-dimensional FPGA with 576 CLBs. Using our data from the previous experiments, we have assumed a channel width of twelve for the two-dimensional FPGA, and six for the

| there is no configuration overhead. |                  |                      |                         |                       |                      |  |  |

|-------------------------------------|------------------|----------------------|-------------------------|-----------------------|----------------------|--|--|

| FPGA<br>Dimensions                  | Channel<br>Width | Switch<br>Point Bits | Total<br>Switchbox Bits | Total<br>Channel Bits | Total<br>Config Bits |  |  |

| $\overline{24 \times 24}$           | 12               | 6                    | 41,472                  | 27,648                | 69,120               |  |  |

| $2\times 12\times 12\times 2$       | 6                | 28                   | 96,768                  | 13,824                | 110,592              |  |  |

| $2 \times 12 \times 12 \times 2$    | 6                | 16                   | 55,296                  | 13,824                | 69,120               |  |  |

*Table 1.1.* Computation of configuration bits required for large two- and four- dimensional FPGAs. The larger number of bits per switch point the four-dimensional FPGA is countered by the reduced channel width. If the switch point configuration is encoded with sixteen bits, there is no configuration overhead.

four-dimensional FPGA. Considering both switch box and connection box bits, the four-dimensional FPGA requires 60% more configuration bits. If we can control the four-dimensional switch point with just sixteen bits, then the reduction in channel width completely compensates for the more complex switch point.

Four-dimensional FPGAs provide scalable interconnect across a wide suite of netlists. Required channel width can remain constant across a large family of devices, allowing the hardware and CAD tool development efforts to be amortized over many devices, and reducing the waste of silicon in smaller devices.

## **1.3** Time Multiplexing and Forward-compatibility

Since their proposal [17, 5, 15], time-multiplexed FPGAs have been thought of as fundamentally different creatures from standard FPGAs. The Xilinx and Sanders FPGAs operate by separating every logical cycle into multiple microcycles. Results from a micro-cycle are passed to subsequent micro-cycles through registers.

Time-multiplexed FPGAs could also be constructed using a threedimensional FPGA architecture like that shown in Figure 1.2. Micro-registers would be inserted on the inter-plane connections that exist between switchboxes. The number of registers between planes would correspond to the channel width, which allows it to be designed to provide scalable interconnect.

By viewing time as a third dimension, the scheduling task can be accomplished within the scope of a three dimensional placement algorithm. All combinational paths must go from a previous configuration, or plane, to a future one, and not vice-versa. Therefore real logical registers must be placed in a configuration that is evaluated after its entire fan-in cone. This is conceptually much simpler than the separate scheduling and place-and-route phases implemented in [16].

#### 1.4 Conclusions

This paper discussed the benefits of three- and four-dimensional FPGAs, and their implementation in conventional two-dimensional silicon. Primary among the benefits is the ability to provide interconnect that scales at the same rate as typical netlists. Four dimensional FPGAs resemble the double and quad lines in commercial FPGAs, although the key to providing scalable interconnect is to increase the length of those lines as the device grows.

#### Notes

1. This is determined by  $1 + \binom{6}{2} + \binom{6}{3} + \binom{6}{4} + \binom{6}{5} + \binom{6}{6} = 58$ .

2. The increasing "logical length" of these lines may also be counter-acted to some extent by the scaling of technology.

## References

- M. J. Alexander, J. P. Cohoon, J. L. Colflesh, J. Karro, and G. Robins. Three-dimensional fieldprogrammable gate arrays. In *Proceedings of the IEEE International ASIC Conference*, pages 253–256, September 1995.

- [2] M. J. Alexander, J. P. Cohoon, J. Karro J. L. Colflesh, E. L. Peters, and G. Robins. Placement and routing for three-dimensional FPGAs. In *Fourth Canadian Workshop on Field-Programmable Devices*, pages 11–18, Toronto, Canada, May 1996.

- [3] V. Betz and J. Rose. Effect of the prefabricated routing track distribution on FPGA area efficiency. *IEEE Transactions on VLSI Systems*, 6(3):445–456, September 1998.

- [4] C. E. Cheng. RISA: Accurate and efficient placement routability modeling. In Proceedings of IEEE/ACM International Conference on CAD (ICCAD), pages 690–695, November 1996.

- [5] A. DeHon. DPGA-coupled microprocessors: Commodity ICs for the early 21st century. In D. A. Buell and K. L. Pocek, editors, *Proceedings of IEEE Workshop on FPGAs for Custom Computing Machines*, pages 31–39, Napa, CA, April 1994.

- [6] J. Depreitere, H. Neefs, H. Van Marck, J. Van Campenhout, R. Baets, B. Dhoedt, H. Thienpont, and I. Veretennicoff. An optoelectronic 3-D field programmable gate array. In R. Hartenstein and M. Z. Servit, editors, *Field-Programmable Logic: Architectures, Synthesis and Applications. 4th International Workshop on Field-Programmable Logic and Applications*, pages 352–360, Prague, Czech Republic, September 1994. Springer-Verlag.

- [7] W. E. Donath. Placement and average interconnection lengths of computer logic. *IEEE Transactions on Circuits and Systems*, pages 272–277, April 1979.

- [8] Hongbing Fan, Jiping Liu, and Yu-Liang Wu. General models for optimum arbitrary-dimension fpga switch box designs. In *Proceedings of IEEE/ACM International Conference on CAD (ICCAD)*, pages 93–98, November 2000.

- [9] A. El Gamal. Two-dimensional stochastic model for interconnections in master slice integrated circuits. *IEEE Transactions on Circuits and Systems*, 28(2):127–138, February 1981.

- [10] M. Hutton, J.P. Grossman, J. Rose, and D. Corneil. Characterization and parameterized random generation of digital circuits. In *Proceedings of the 33rd ACM/SIGDA Design Automation Conference (DAC)*, pages 94–99, Las Vegas, NV, June 1996.

- [11] M. Hutton, J. Rose, and D. Corneil. Generation of synthetic sequential benchmark circuits. In 5th ACM/SIGDA International Symposium on Field Programmable Gate Arrays, (FPGA 97), February 1997.

- [12] B. S. Landman and R. L. Russo. On pin versus block relationship for partions of logic circuits. *IEEE Transactions on Computers*, C-20:1469–1479, 1971.

- [13] M. Leeser, W. M. Meleis, M. M. Vai, W. Xu S. Chiricescu, and P. M. Zavracky. Rothko: A threedimensional FPGA. *IEEE Design and Test of Computers*, 15(1):16–23, January 1998.

- [14] W. M. Meleis, M. Leeser, P. Zavracky, and M. M. Vai. Architectural design of a three dimensional FPGA. In *Proceedings of the 17th Conference on Advanced Research in VLSI (ARVLSI)*, pages 256– 268, September 1997.

- [15] S. Scalera and J. R. Vazquez. The design and implementation of a context switching FPGA. In D. A. Buell and K. L. Pocek, editors, *Proceedings of IEEE Workshop on FPGAs for Custom Computing Machines*, pages 78–85, Napa, CA, April 1998.

- [16] S. Trimberger. Scheduling designs into a time-multiplexed FPGA. In 6th ACM/SIGDA International Symposium on Field Programmable Gate Arrays, (FPGA 98), pages 153–160, February 1998.

- [17] S. Trimberger, D. Carberry, A. Johnson, and J. Wong. A time-multiplexed FPGA. In J. Arnold and K. L. Pocek, editors, *Proceedings of IEEE Workshop on FPGAs for Custom Computing Machines*, pages 22–28, Napa, CA, April 1997.

## Chapter 2

# A Tightly Coupled VLIW/Reconfigurable Matrix and its Modulo Scheduling Technique

Bingfeng Mei,<sup>1,2</sup> Serge Vernalde,<sup>2</sup> Diederik Verkest,<sup>1,2,3</sup> and Rudy Lauwereins<sup>1,2</sup>

<sup>1</sup> IMEC vzw, Kalpeldreef 75, Leuven, Belgium

<sup>2</sup> Department of Electrical Engineering, Katholieke Universiteit Leuven, Belgium

<sup>3</sup> Department of Electrical Engineering, Vrije Universiteit Brussel, Belgium

## 2.1 Introduction

Coarse-grained reconfigurable architectures have become increasingly important in recent years. Various architectures have been proposed [1-4]. These architectures often comprise a matrix of functional units (FUs), which are capable of executing word- or subword-level operations instead of bit-level ones found in common FPGAs. This *coarse* granularity greatly reduces the delay, area, power and configuration time compared with FPGAs. However, these advantages are achieved at the expense of flexibility. Usually the reconfigurable matrix alone is not able to execute entire applications. Most coarse-grained architectures are coupled with processors, typically RISCs. The computationalintensive kernels, typically loops, are mapped to the matrix, whereas the remaining code is executed by the processor. So far not much attention has been paid to the integration of these two parts. The coupling between the processor and the matrix is often loose, consisting essentially of two separate parts connected by a communication channel. This results in programming difficulty and communication overhead. In addition, the coarse-grained reconfigurable architecture consists of components which are similar to those used in processors. This resource-sharing opportunity is not extensively exploited in traditional coarse-grained architectures.

To address these problems, in this chapter we present an architecture called ADRES (*Architecture for Dynamically Reconfigurable Embedded System*), which tightly couples a VLIW (very long instruction word) processor and a coarse-grained reconfigurable matrix. The VLIW processor and the coarse-grained reconfigurable matrix are integrated into one single architecture but with two virtual functional views. This level of integration has many advantages compared with other coarse-grained architectures, including improved performance, a simplified programming model, reduced communication costs and substantial resource sharing.

Any new architecture can hardly be successful without good design methodology. Therefore, we developed a compiler for ADRES. The central technology is a novel modulo scheduling technique, which is able to map kernel loops to the reconfigurable matrix by solving placement, routing and scheduling simultaneously in a modulo constrained space. Combined with traditional ILP (instruction-level parallelism) compilation techniques, our compiler can map an entire application to the ADRES architecture efficiently and automatically.

This chapter is organized as follows: section 2.2 discusses the architectural aspects of ADRES; section 2.3 describes the modulo scheduling algorithm in details; section 2.4 presents the experimental results and section 2.5 concludes the chapter.

#### 2.2 ADRES Architecture

#### 2.2.1 Architecture Description

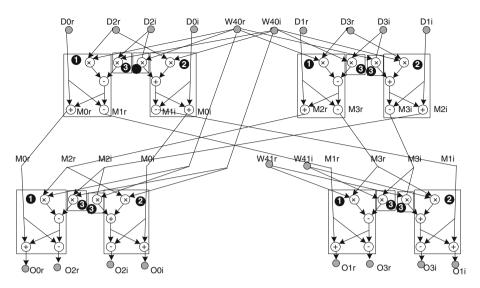

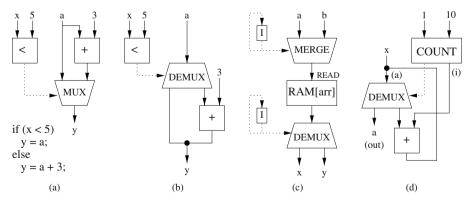

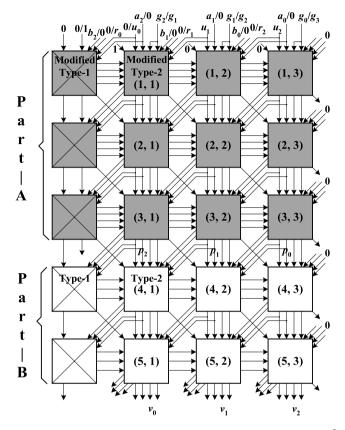

The ADRES architecture (Fig 2.1) consists of many basic components, including mainly FUs and register files(RFs), which are connected in a certain topology. The FUs are capable of executing word-level operations selected by a control signal. The RFs can store intermediate data. The whole ADRES matrix has two functional views, the VLIW processor and the reconfigurable matrix. These two functional views share some physical resources because their executions will never overlap with each other thanks to the processor/co-processor model. For the VLIW processor, several FUs are allocated and connected together through one multi-port register file, which is typical for VLIW architecture. Some of these FUs are connected to the memory hierarchy, depending on available ports. Thus the data access to the memory is done through the load/store operations available on those FUs.

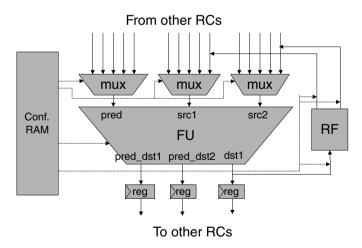

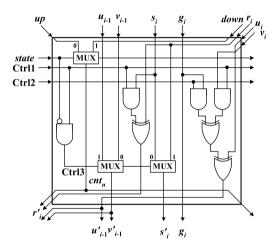

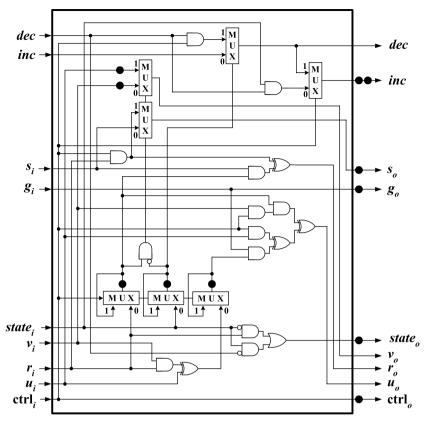

For the reconfigurable matrix part, apart from the FUs and RF shared with the VLIW processor, there are a number of *reconfigurable cells* (RC) which basically comprise FUs and RFs too (Fig. 2.2). The FUs can be heterogeneous supporting different operation sets. To remove the control flow inside loops,

Figure 2.1. ADRES core

the FUs support predicated operations. The distributed RFs are small with less ports. The multiplexors are used to direct data from different sources. The configuration RAM stores a few configurations locally, which can be loaded on cycle-by-cycle basis. The configurations can also be loaded from the memory hierarchy at the cost of extra delay if the local configuration RAM is not big

Figure 2.2. Example of a Reconfigurable Cell

enough. Like instructions in ISPs, the configurations control the behaviour of the basic components by selecting operations and multiplexors. The reconfigurable matrix is used to accelerate the dataflow-like kernels in a highly parallel way. The access to the memory of the matrix is also performed through the VLIW processor FUs.

In fact, ADRES is a template of architectures instead of a fixed architecture. An XML-based architecture description language is used to define the communication topology, supported operation set, resource allocation and timing of the target architecture [5]. Even the actual organization of the RC is not fixed. FUs and RFs can be put together in several ways. For example, two FUs can share one RF. The architecture shown in Fig. 2.1 and Fig. 2.2 is just one possible instance of the template. The specified architecture will be translated to an internal architecture representation to facilitate compilation techniques.

#### 2.2.2 Improved Performance with the VLIW Processor

Many coarse-grained architectures consist of a reconfigurable matrix and a relatively slow RISC processor, e.g. TinyRisc in MorphoSys [1] and ARM in PACT XPP [3]. These RISC processors execute the unaccelerated part of the application, which only represents a small portion of execution time. However, such a system architecture has problems due to the huge performance gap between the RISC and the matrix. According to Amdahl's law [6], the performance gain that can be obtained by improving some portion of an application can be calculated according to equation 2.1. Suppose the kernels, representing 90% of execution time, are mapped to the reconfigurable matrix to obtain an acceleration of 30 times over the RISC processor, the overall speedup is merely 7.69. Obviously a high kernel speedup is not translated to a high overall speedup. Speeding up the unaccelerated part, which is often irregular and control-intensive code, is important for the overall performance. Though it is hard to exploit higher parallelism from it on the reconfigurable matrix, it is still possible to discover instruction-level parallelism (ILP) using a VLIW processor, where 2-4 times speedup over the RISC is reasonable. If we recalculate the speedup with the assumption of 3 times acceleration for the unaccelerated code, the overall acceleration is now 15.8, much better than the previous scenario. This simple calculation proves that using VLIW in ADRES can improve the overall speedup dramatically in certain circumstances.

$$Speedup_{overall} = \frac{1}{(1 - Fraction_{enhanced}) + \frac{Fraction_{enhanced}}{Speedup_{enhanced}}}$$

(2.1)

## 2.2.3 Simplified Programming Model and Reduced Communication Cost

A simplified programming model and reduced communication cost are two important advantages of the ADRES architecture. These are achieved by making the VLIW processor and the reconfigurable matrix share access to the memory and the register file.

In other reconfigurable architectures, the processor and the matrix are essentially separated. The communication is often through explicit data copying. Though some techniques are adopted to reduce the data copying, e.g., wider data bus and DMA controller, the overhead is still considerable in terms of performance and energy. From the programming point of view, the separated processor and reconfigurable matrix require significant code rewriting. Starting from a software implementation, we have to identify the data structures used for communication and replace them with communication primitives. Data analysis should be done to make sure as few as possible data are actually copied. In addition, the kernels and the remaining code have to be cleanly separated in such a way that no shared access to any data structure remains. These transformations are often complex and error-prone.

In ADRES, the data communication is performed through the shared RF and memory. This feature is very helpful to map high-level language code such as C without major changes. When a high-level language is compiled to a processor, the local variables are allocated in the RF, while the static variables and arrays are allocated in the memory space. When the control of the program is transferred between the VLIW processor and the reconfigurable matrix, those variables used for communication can stay in the RF or the memory as they were. The copying is unnecessary because both the VLIW and the reconfigurable matrix share access to the RF and memory hierarchy. The code doesn't require any rewriting and can be handled by the compiler automatically.

#### 2.2.4 Resource Sharing

Since the basic components such as the FUs and RFs of the reconfigurable matrix and those of the VLIW processor are basically the same, it is natural to think that resources might be shared to have substantial cost-saving. In other coarse-grained architectures, the resources cannot be effectively shared because the processor and the matrix are two separate parts. For example, the FU in the TinyRisc of MorphoSys cannot work cooperatively with the reconfigurable cells in the matrix. In ADRES, since the VLIW processor and the reconfigurable matrix are indeed two virtual functional views of the same physical entity, many resources are shared among these two parts. Due to its processor/co-processor

model, only the VLIW processor or the reconfigurable matrix is active at any time. This fact makes resource sharing possible. Resource sharing of the powerful FUs and the multi-port RF of the VLIW by the matrix can greatly improve the performance and schedulability of kernels mapped on the matrix.

#### 2.3 Modulo Scheduling

The objective of modulo scheduling is to engineer a schedule for one iteration of the loop such that this same schedule is repeated at regular intervals with respect to intra- and inter-iteration dependency and resource constraints. This interval is termed the *initiation interval* (II), essentially reflecting the performance of the scheduled loop. Various effective heuristics have been developed to solve this problem for both unified and clustered VLIWs [9, 11–13]. However, they cannot be applied to a coarse-grained reconfigurable architecture because the nature of the problem becomes more difficult, as illustrated next.

#### 2.3.1 Problem Illustrated

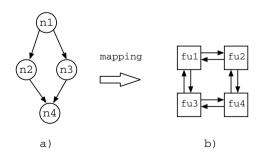

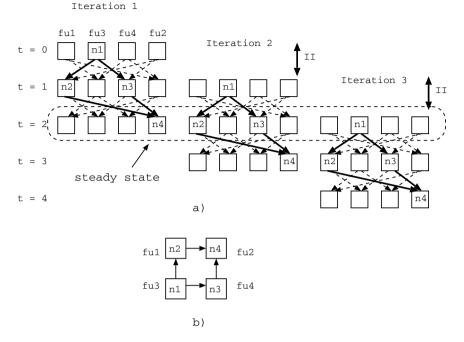

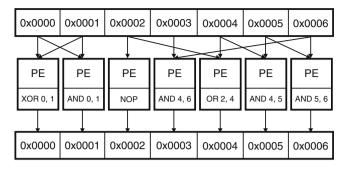

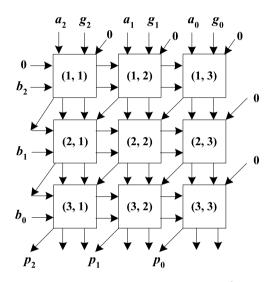

To illustrate the problem, consider a simple dependency graph, representing a loop body, in Fig. 2.3a and a  $2 \times 2$  matrix in Fig. 2.3b. The scheduled loop is depicted in Fig. 2.4a, where the  $2 \times 2$  matrix is flattened to  $1 \times 4$  for convenience of drawing. Nevertheless, the topology remains the same.

Fig 2.4a is a space-time representation of the scheduling space. From Fig. 2.4a, we see that modulo scheduling on coarse-grained architectures is a combination of 3 sub-problems: *placement, routing and scheduling*. Placement determines on which FU of a 2D matrix to place one operation. Scheduling, in its literal meaning, determines in which cycle to execute that operation. Routing connects the placed and scheduled operations according to their data dependencies. If we view *time* as an axis of 3D space, the modulo scheduling can be simplified to a placement and routing problem in a modulo-constrained 3D space, where the routing resources are asymmetric because any data can only

*Figure 2.3.* a) A simple dataflow graph; b) A  $2 \times 2$  reconfigurable matrix

*Figure 2.4.* a) Modulo scheduling example; b) Configuration for  $2 \times 2$  matrix

be routed from smaller time to bigger time, as shown in Fig. 2.4a. Moreover, all resources are modulo-constrained because the execution of consecutive iterations which are in distinct stages is overlapped. The number of stages in one iteration is termed *stage count* (SC). In this example, II = 1 and SC = 3. The schedule on the  $2 \times 2$  matrix is shown in Fig. 2.4b. FU1 to FU4 are configured to execute n2, n4, n1 and n3 respectively. In this example, there is only one configuration. In general, the number of configurations that need to be loaded cyclically is equal to II.

By overlapping different iterations of a loop, we are able to exploit a higher degree of ILP. In this simple example, the instruction per cycle (IPC) is 4. As a comparison, it takes 3 cycles to execute one iteration in a non-pipelined schedule due to the data dependencies, corresponding to an IPC of 1.33, no matter how many FUs in the matrix.

#### 2.3.2 Modulo Routing Resource Graph

We develop a graph representation, namely *modulo routing resource graph* (MRRG), to model the ADRES architecture internally for the modulo scheduling algorithm. MRRG combines features of the *modulo reservation table*(MRT) [7] for software pipelining and the *routing resource graph* [8] used

in FPGA P&R, and only exposes the necessary information to the modulo scheduling algorithm. An MRRG is a directed graph  $G = \{V, E, II\}$  which is constructed by composing sub-graphs representing the different resources of the ADRES architecture. Because the MRRG is a time-space representation of the architecture, every subgraph is replicated each cycle along the time axis. Hence each node v in the set of nodes V is a tuple (r, t) where r refers to the port of resource and t refers to the time stamp. The edge set  $E = \{(v_m, v_n) | t(v_m) \le t(v_n)\}$  corresponds to switches that connect these nodes. The restriction  $t(v_m) \le t(v_n)$  models the asymmetric nature of the MRRG. Finally, II refers to the initiation interval. MRRG has two important properties. First, it is a modulo graph. If scheduling an operation involves the use of node  $(r, t_i)$ , then all the nodes  $\{(r, t_k)|t_i \mod II = t_k \mod II\}$  are used too. Second, it is an asymmetric graph. It is impossible to find a route from node  $v_i$  to  $v_i$ , where  $t(v_i) > t(v_i)$ . As we will see in section 2.3.3, this asymmetric property imposes big constraints on the scheduling algorithm. During scheduling we start with a minimal II and iteratively increase the II until we find a valid schedule (see section 2.3.3). The MRRG is constructed from the architecture specification and the II to try. Each component of the ADRES architecture is converted to a subgraph in MRRG.

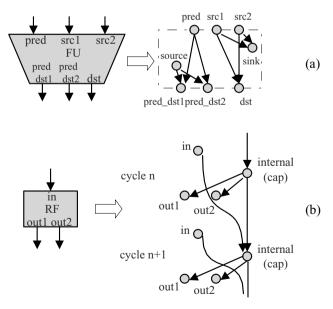

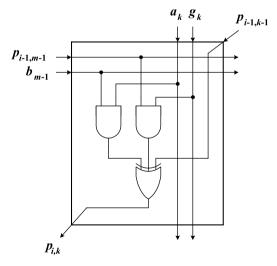

Fig. 2.5 shows some examples. Fig. 2.5a is a 2D view of a MRRG subgraph corresponding to a FU, which means in the real MRRG graph with time dimension, all the subgraphs have to be replicated each cycle along the time

Figure 2.5. MRRG representation of ADRES architecture parts

axis. For FUs, all the input and output ports have corresponding nodes in the MRRG graph. Virtual edges are created between src1 and dst, src2 and dst, etc. to model the fact that a FU can be used as routing resource to directly connect src1 or src2 to dst, acting just like a multiplexor or demultiplexor. In addition, two types of artificial nodes are created, namely *source* and *sink*. When a commutative operation, e.g., add, is scheduled on this FU, the source or sink node are used as routing terminals instead of the nodes representing ports. Thus the router can freely choose which port to use. This technique improves the flexibility of the routing algorithm and leads to higher routability. Fig. 2.5b shows a space-time MRRG subgraph for a register file with one write port and two read ports. The idea is partly from [10]. Similar to the FU, the subgraph has nodes corresponding to each input and output port, which are replicated over each cycle. Additionally, an internal node is created to represent the capacity of the register file. All internal nodes along the time axis are connected one by one. The input nodes are connected to the internal node of next cycle, whereas the output nodes are connected to the internal node of this cycle. In this way, the routing capability of the register file is effectively modelled via its write-store-read functionality. Moreover, a cap property is associated with the internal node which is equal to the capacity of the register file. Therefore, the register allocation problem is implicitly solved by our scheduling algorithm. Other types of components such as bus and multiplexor can be modelled in a similar way. This abstraction, all routing resources, whether physical or virtual, are modelled in a universal way using nodes and edges. This unified abstract view of the architecture exposes only necessary information to the scheduler and greatly reduces the complexity of the scheduling algorithm.

## 2.3.3 Modulo Scheduling Algorithm

By using MRRG, the three sub-problems (placement, routing and scheduling) are reduced to two sub-problems (placement and routing), and modulo constraints are enforced automatically. However, it is still more complex than traditional FPGA P&R problems due to the modulo and asymmetric nature of the P&R space and scarcity of available routing resources. In FPGA P&R algorithms, we can comfortably run the placement algorithm first by minimizing a good cost function that measures the quality of placement. After minimal cost is reached, the routing algorithm connects placed nodes. The coupling between these two sub-problems is very loose. In our case, we can hardly separate placement and routing as two independent problems. It is very hard to find a placement algorithm and a cost function which can foresee the routability during the routing phase. Therefore, we propose a novel approach to solve these two sub-problems in one framework. The algorithm is described in Fig. 2.6.

```

SortOps();

II := MII(DDG);

while not scheduled do

InitMrrg(II);

InitTemperature();

InitPlaceAndRoute();

(1)

while not scheduled do

for each op in sorted operation list

RipUpOp();

for i := 1 to random_pos_to_try do

pos := GenRandomPos();

success := PlaceAndRouteOp(pos); (3)

if success then

new_cost := ComputeCost(op);

(4)

accepted := EvaluateNewPos();

(5)

if accepted then

break;

else

continue;

endif

(2)

endfor

if not accepted then

RestoreOp();

else

CommitOp();

if get a valid schedule then

return scheduled;

endfor

if StopCriteria() then

(6)

break;

UpdateOverusePenalty();

(7)

UpdateTemperature();

(8)

endwhile

TT++:

endwhile

```

Figure 2.6. Modulo scheduling algorithm for coarse-grained reconfigurable architecture

First all operations are ordered by the technique described in [11]. Priority is given to operations on the critical path and an operation is placed as close as possible to both its predecessors and successors, which effectively reduces the routing length between operations. Like other modulo scheduling algorithms, the outermost loop tries successively larger II, starting with an initial value equal to the minimal II (MII), until the loop has been scheduled. The MII is computed using the algorithm in [9].

For each II, our algorithm first generates an initial schedule which respects dependency constraints, but may overuse resources (1). For example, more than one operation may be scheduled on one FU in the same cycle. In the inner loop (2), the algorithm iteratively reduces resource overuse and tries to come up with a legal schedule. At every iteration, an operation is ripped up from the existing schedule, and is placed randomly (3). The connected nets are re-routed accordingly. Next, a cost function is computed to evaluate the new placement and routing (4). The cost is computed by accumulating the cost of all used MRRG nodes incurred by the new placement and routing of the operation. The cost function of each MRRG node is shown in eq. 2.2. It is constructed by taking into account the penalty of overused resources. In eq. 2.2, there is a basic cost (base\_cost) associated with each MRRG node. The occ represents the occupancy of that node. The cap refers to the capacity of that node. Most MRRG nodes have a capacity of 1, whereas a few types of nodes such as the internal node of a register file have a capacity larger than one. The *penalty* factor associated with overused resources is increased at the end of each iteration (7). Through a higher and higher overuse penalty, the placer and router will try to find alternatives to avoid congestion. However, the penalty is increased gradually to avoid abrupt increases in the overused cost that may trap solutions into local minima. This idea is borrowed from the *Pathfinder* algorithm [8], which is used in FPGA P&R problems.

$$cost = base\_cost \times occ + (occ - cap) \times penalty$$

(2.2)

In order to escape from local minima, we use a *simulated annealing* strategy to decide whether each move is accepted or not (5). In this strategy, if the new cost is lower than the old one, the new P&R of this operation will be accepted. On the other hand, even if the new cost is higher, there is still a chance that the move may be accepted, depending on the "*temperature*". At the beginning, the temperature is very high so that almost every move is accepted. The temperature is decreased at the end of the each iteration (8). Therefore, the operation is increasingly difficult to move around. In the end, if the termination criteria is met without finding a valid schedule (6), the schedule algorithm starts with the next II.

## 2.4 Experimental Results

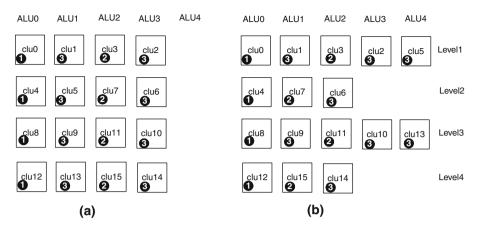

In the experiments, an architecture resembling the topology of MorphoSys [1] is instantiated from the ADRES template. In this configuration, a total of 64 FUs are divided into four tiles, each of which consists of  $4 \times 4$  FUs. Each FU is not only connected to the 4 nearest neighbor FUs, but also to all FUs within the same row or column in this tile. In addition, there are row buses and column buses across the matrix. The first row of FUs is also used by the

| Loop    | No. of<br>ops | Live-in<br>vars | Live-out<br>vars | II | IPC  | Sched.<br>density |

|---------|---------------|-----------------|------------------|----|------|-------------------|

| idct1   | 93            | 4               | 0                | 3  | 31   | 48.4%             |

| idct2   | 168           | 4               | 0                | 4  | 42   | 65.6%             |

| adpcm-d | 55            | 9               | 2                | 4  | 13.8 | 21.5%             |

| mat_mul | 20            | 12              | 0                | 1  | 20   | 31.3%             |

| fir_cpl | 23            | 9               | 0                | 1  | 23   | 35.9%             |

Table 2.1. Scheduling results of kernels

VLIW processor, and are connected to a multi-port register file. Only the FUs in the first row are capable of executing memory operations, i.e., load/store operations.

The testbench consists of 4 programs, which are derived from C reference code of TI's DSP benchmarks and MediaBench [14]. The *idct* is a  $8 \times 8$  inverse discrete cosine transformation, which consists two loops. The *adpcm-d* refers to an ADPCM decoder. The *mat\_mul* computes matrix multiplication. The *fir\_cpl* is a complex FIR filter. They are typical multimedia and digital signal processing applications with abundant inherent parallelism.