# Hardware Verification with C++

A Practitioner's Handbook

# **HARDWARE VERIFICATION WITH C++**

A Practitioner's Handbook

# HARDWARE VERIFICATION WITH C++ A Practitioner's Handbook

MIKE MINTZ ROBERT EKENDAHL

Cover art from the original painting "Every other now and then" by John E. Bannon, johnebannon.com

Mike Mintz Robert Ekendahl

Hardware Verification with C++: A Practitioner's Handbook

Library of Congress Control Number: 2006928441

ISBN 0-387-25543-5 e-ISBN 0-387-36254-1 ISBN 9780387255439

Printed on acid-free paper.

#### © 2006 Springer Science+Business Media, LLC

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now know or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed in the United States of America.

9 8 7 6 5 4 3 2 1

springer.com

For Joan, Alan, and Brian. Thanks for your patience.

Mike

For Chantal. Thanks for your understanding, love, and active support.

And to Newton. For many missed walks.

Robert

| Preface                                                                                                                                                            | xix                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Acknowledgments                                                                                                                                                    | xxi                       |

| Chapter 1: Introduction                                                                                                                                            | 1                         |

| Background                                                                                                                                                         | . 3                       |

| What is Functional Verification?                                                                                                                                   | . 4                       |

| Why Focus on C++?                                                                                                                                                  | . 4                       |

| A Tour of the Handbook                                                                                                                                             | . 5                       |

| For Further Reading                                                                                                                                                | . 6                       |

| Part I:                                                                                                                                                            |                           |

| Part I: C++ and Verification (The Why and How)  Chapter 2: Why C++?                                                                                                |                           |

| C++ and Verification (The Why and How)                                                                                                                             | 9                         |

| C++ and Verification (The Why and How)                                                                                                                             | <b>9</b><br>10            |

| C++ and Verification (The Why and How)                                                                                                                             | 9<br>10<br>11             |

| C++ and Verification (The Why and How)                                                                                                                             | 9<br>10<br>11<br>13       |

| C++ and Verification (The Why and How)  Chapter 2: Why C++?  Overview  C++: A Good Verification Language  A Look at Hardware-Verification Languages                | 9<br>10<br>11<br>13<br>13 |

| C++ and Verification (The Why and How)  Chapter 2: Why C++?  Overview  C++: A Good Verification Language  A Look at Hardware-Verification Languages  Randomization | 9<br>10<br>11<br>13<br>13 |

| Other Benefits of Using C++                             | 6    |

|---------------------------------------------------------|------|

| Drawbacks of Using C++                                  | 7    |

| For Further Reading                                     | 7    |

|                                                         |      |

| Chapter 3: OOP, C++, and Verification $\dots$           | . 19 |

| Overview                                                | 0    |

| The Evolution of OOP and C++                            | 1    |

| Assembly programming: The early days                    | 1    |

| Procedural languages: The next big step 2               | 1    |

| OOP: Inheritance for functionality 2                    | 2    |

| OOP: Inheritance for interface                          | 4    |

| OOP: Templates                                          | 4    |

| C++: The standard template library 2                    | 5    |

| The Evolution of Functional Verification 2              | 5    |

| Verification through inspection 2                       | 5    |

| Verification through randomness 2                       | 6    |

| The emergence of hardware verification languages        | 7    |

| OOP: A current trend in hardware verification languages | 7    |

| OOP: Problems with the current approach 2               | 8    |

| OOP: A possible next step                               | 8    |

| OOP Using C++                                           | 9    |

| Data abstraction through classes 2                      | 9    |

| A DMA descriptor example 2                              | 9    |

| Access control                                          | 1    |

| Constructors and destructors                            | 2    |

| Member methods and variables                            | 3    |

| Operator overloading                                    | 4    |

| Inheritance for functionality                           | 4    |

| Inheritance for interface                               | 6    |

| Templating                                              | 8    |

| A word about user-defined templates 3                   | 9    |

| Namespaces                                              | 9    |

viii • • • • • •

| Summary                                      | ł I       |

|----------------------------------------------|-----------|

| For Further Reading                          | 11        |

| Chapter 4: A Layered Approach                | . 43      |

| Overview                                     |           |

| A Whiteboard Drawing                         |           |

|                                              | 17        |

|                                              | 17        |

|                                              | 48        |

| · · · · · · · · · · · · · · · · · · ·        | 19        |

|                                              | 50        |

|                                              | 52        |

|                                              | 53        |

|                                              | 54        |

|                                              | 56        |

|                                              | 58        |

| The Test Irritator                           | 60        |

| A Complete Test                              |           |

| Summary                                      |           |

| For Further Reading                          |           |

| -                                            |           |

| Part II: An Open-Source Environment with C++ | . 65      |

|                                              |           |

| Chapter 5: Teal Basics                       | . 67      |

| Overview                                     | 58        |

| What Teal provides                           | <b>68</b> |

| Teal's similarity to HDLs                    | 59        |

| A tiny but complete example                  | 59        |

| Teal's Main Components                       | 71        |

| Using Teal                                   | 73        |

| -                                            | 73        |

| Your C++ test                                | 74        |

| Registers                                    | 74        |

| Creating registers                                |

|---------------------------------------------------|

| Working with a reg or vreg                        |

| Logging Output                                    |

| Using Test Parameters                             |

| Accessing Memory                                  |

| A memory note example 82                          |

| Constrained Random Numbers 84                     |

| Required initialization                           |

| Using random numbers84                            |

| Working with Simulation Events and Concurrency 86 |

| Summary                                           |

| For Further Reading                               |

|                                                   |

| Chapter 6: Truss: A Standard Verification         |

| Framework91                                       |

| Overview92                                        |

| General Considerations                            |

| Using a language other than C++ 93                |

| Keeping it simple                                 |

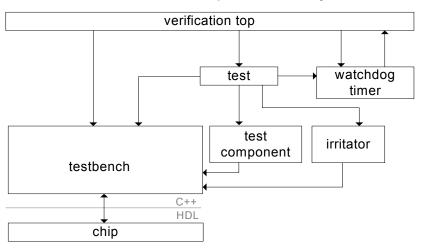

| Major Classes and Their Roles 95                  |

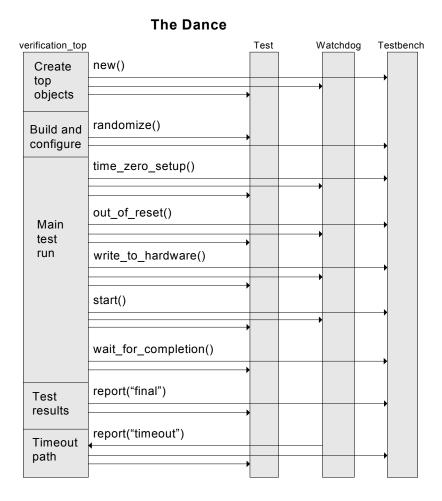

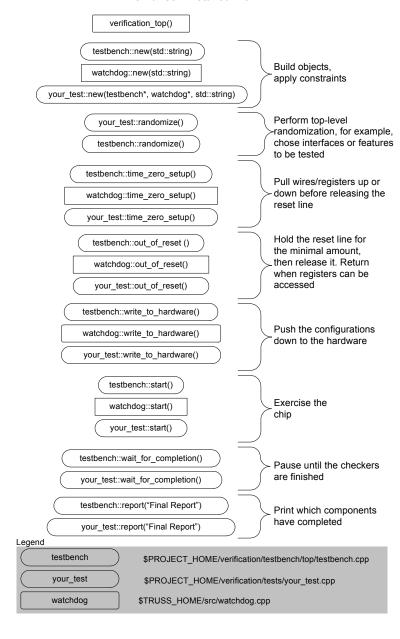

| Key test algorithm: The "dance" 96                |

| The verification_component Abstract Base Class 99 |

| Detailed Responsibilities of the Major Components |

| The testbench class                               |

| Watchdog timer                                    |

| Test class                                        |

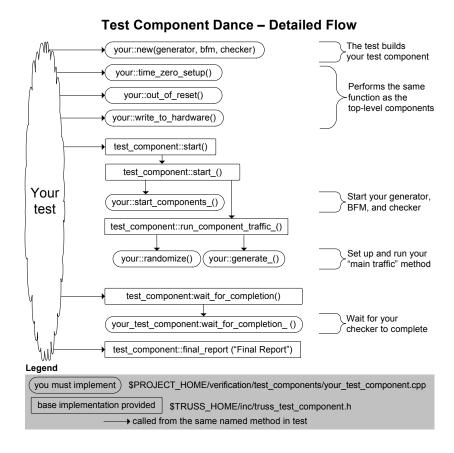

| Test Component and Irritator Classes              |

| The test component abstract base class            |

| An AHB example                                    |

| Test-component housekeeping functionality 109     |

| The irritator abstract base class                 |

| Using the irritator112                            |

| Summary 113                                       |

Hardware Verification with C++

| Chapter 7: Truss Flow                                  |

|--------------------------------------------------------|

| Overview116                                            |

| About verification_top.cpp                             |

| The Test Component Dance                               |

| The Irritator Dance                                    |

| Compiling and Running Tests                            |

| Truss run script                                       |

| Switches                                               |

| The Truss makefile                                     |

| The First Test: A Directed Test                        |

| The Second Test: Adding Channels and Random Parameters |

| Building the second test                               |

| Building the second test's test_component              |

| Adjusting the second test's parameters                 |

| The Remaining Tests: Mix-and-Match Test Components     |

| Summary                                                |

| Chapter 8: Truss Example139                            |

| Overview140                                            |

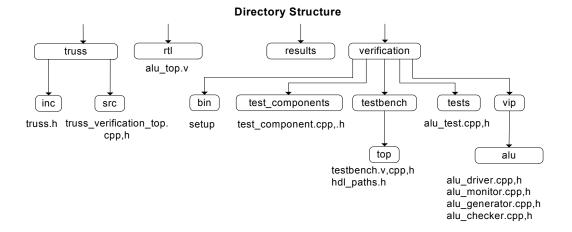

| Directory Structure                                    |

| Theory of Operation                                    |

| Running the Simple ALU Example                         |

| Points of Interest                                     |

| Power-on Reset                                         |

| Driver and Monitor Protocol                            |

| The alu_test_component                                 |

| Checking the Chip147                                   |

| Completing the Test                                    |

| Summary                                                |

| Part III:<br>Using OOP for Verification                  |

|----------------------------------------------------------|

| (Best Practices)153                                      |

| Chapter 9: Thinking OOP                                  |

| Overview                                                 |

| Sources of Complexity                                    |

| Essential complexity vs. implementation complexity       |

| Flexibility vs. complexity                               |

| Apparent simplicity vs. hiding inherent complexity       |

| Example: How hiding complexity can create confusion      |

| Example: How apparent simplicity leads to later problems |

| Team dynamics                                            |

| Team roles                                               |

| Using a "code buddy"                                     |

| Creating Adaptable Code                                  |

| Achieving adaptability                                   |

| Why is adaptability tricky?                              |

| Architectural Considerations to Maximize Adaptability    |

| Changes are easy—or just plain impossible 168            |

| Where is adaptation likely to happen?                    |

| Separating Interface from Implementation                 |

| Interface, Implementation, and Base Classes 171          |

| Summary                                                  |

| For Further Reading                                      |

xii • • • • • • Hardware Verification with C++

| Chapter 10: Designing with OOP175                  |

|----------------------------------------------------|

| Overview                                           |

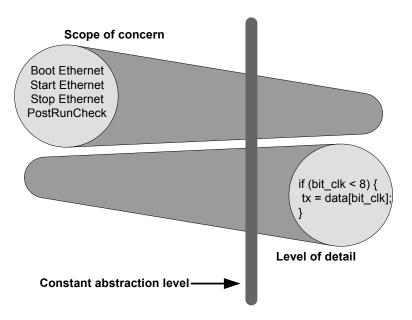

| Keeping the Abstraction Level Consistent           |

| Using "Correct by Construction"                    |

| The Value of Namespaces                            |

| Data Duplication—A Necessary Evil                  |

| Designing Well, Optimizing Only When Necessary 184 |

| Using the Interface, Only the Interface185         |

| Verification Close to the Programming Model 186    |

| The Three Parts of Checking                        |

| Separating the Test from the Testbench             |

| Summary                                            |

| For Further Reading                                |

|                                                    |

| Chapter 11: OOP Classes193                         |

| Overview194                                        |

| Defining Classes                                   |

| How Much Electricity?                              |

| Classes                                            |

| Namespaces196                                      |

| Operator overloading                               |

| Pointers and virtual functions                     |

| Even more electricity197                           |

| Smart pointers                                     |

| Global Services198                                 |

| Namespaces198                                      |

| Static methods                                     |

| Singletons—A Special Case of Static Methods 200    |

| Namespaces or static methods?                      |

| Other considerations                               |

| Class Instance Identifiers                         |

| Object memory address as identifiers203            |

| Strings as identifiers                             |

| Static integers as identifiers                      | . 204                                     |

|-----------------------------------------------------|-------------------------------------------|

| Combination identifiers                             | . 204                                     |

| Class Inheritance for Reuse                         | . 205                                     |

| A BFM base class example                            | . 205                                     |

| A BFM agent class                                   | . 206                                     |

| Reusing the BFM class                               | . 206                                     |

| Class Inheritance for Interfaces                    | . 207                                     |

| Inheritance for a verification component            | . 208                                     |

| Inheritance for a payload interface                 | . 208                                     |

| Operator Overloading for Common-Currency Classes    | . 210                                     |

| Operator overloading in a communications channel.   | . 211                                     |

| Considerations                                      | . 212                                     |

| Creating Classes— What the Compiler Will Do for You | . 212                                     |

| Advanced Class Techniques                           | . 214                                     |

| Summary                                             | . 215                                     |

| For Further Reading                                 | . 216                                     |

|                                                     |                                           |

| Chapter 12: OOP Connections                         | 217                                       |

| Overview                                            | . 218                                     |

| How Tight a Connection?                             | . 219                                     |

| Types of Connections                                | . 221                                     |

| Peer-to-peer connections                            | . 221                                     |

| Master-to-slave and push-vspull connections         | . 221                                     |

| Two Tight Connection Techniques                     | . 223                                     |

| Using pointers                                      | 222                                       |

| Haller of Salar address as                          | . 223                                     |

| Using inheritance                                   |                                           |

| Threads and Connections                             | . 224                                     |

| -                                                   | . 224<br>. 226                            |

| Threads and Connections                             | . 224<br>. 226<br>. 226                   |

| Threads and Connections                             | . 224<br>. 226<br>. 226<br>. 227          |

| Threads and Connections                             | . 224<br>. 226<br>. 226<br>. 227<br>. 229 |

xiv • • • • • • Hardware Verification with C++

| Action object connections                                 |

|-----------------------------------------------------------|

| Summary                                                   |

| For Further Reading234                                    |

|                                                           |

| Chapter 13: Coding OOP                                    |

| Overview                                                  |

| "If" Tests—A Necessary Evil                               |

| "If" tests and abstraction levels                         |

| "If" tests and code structure                             |

| Repeated "if" expressions                                 |

| "If" tests and factory functions                          |

| A factory function example                                |

| Coding Tricks                                             |

| Coding only what you need to know                         |

| Reservable resources                                      |

| Using register fields instead of hard-coded integers      |

| Using data members carefully                              |

| Coding Idioms                                             |

| The singleton idiom                                       |

| Public nonvirtual methods: Virtual protected methods      |

| Pointers for change, references for efficiency 251        |

| Avoiding accessor methods—                                |

| using constant references instead                         |

| Enumeration for Data, Integer for Interface253            |

| Using the constructor and destructor to simplify the code |

| Using a boolean to indicate success                       |

| What's in a Name?                                         |

| Keeping class name the same as file name257               |

| Keeping class and instance names related                  |

| Coding with Style                                         |

| Proceeding with caution                                   |

A Practitioner's Handbook

| General syntax conventions                    |

|-----------------------------------------------|

| Syntactic sugar                               |

| Using override and non_virtual                |

| Using owner and cached                        |

| Identifying private and protected members 263 |

| Using Templates                               |

| Standard templates for data management264     |

| Writing templates for adaptable code          |

| Summary                                       |

| For Further Reading                           |

| Part IV: Examples (Putting It All Together)   |

| Chapter 14: Block Level Testing273            |

| Overview                                      |

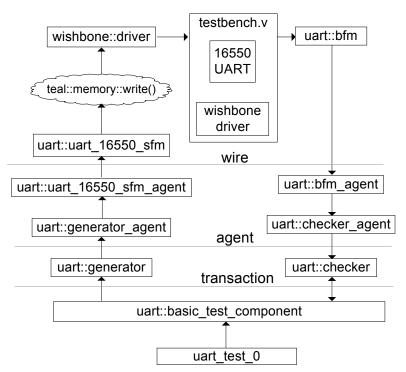

| Theory of Operation                           |

| Verification environment                      |

| Verification IP                               |

| UART VIPs                                     |

| Wishbone VIP                                  |

| The verification dance                        |

| Running the UART Example                      |

| Points of Interest                            |

| Configuration                                 |

| VIP UART configuration class                  |

| Randomization of enums                        |

| UART 16550 configuration class                |

| Configuring the Chip                          |

| Register access                               |

| The wishbone_memory_bank and wishbone_driver  |

| Traffic Generation 290                        |

xvi • • • • • • Hardware Verification with C++

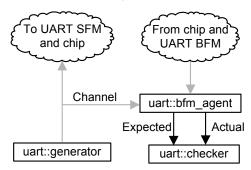

| The generator_agent and uart_bfm_agent classes 291 |   |

|----------------------------------------------------|---|

| The Checker                                        |   |

| Checking the data                                  |   |

| Connecting It All Together                         |   |

| The testbench                                      |   |

| Building the channels                              |   |

| Building the configuration and interface port 297  |   |

| Building the interface-layer objects               |   |

| The wishbone objects                               |   |

| The test component                                 |   |

| The uart_basic_test_component::randomize()         |   |

| method301                                          |   |

| The basic data test                                |   |

| More Tests                                         |   |

| Summary                                            |   |

|                                                    |   |

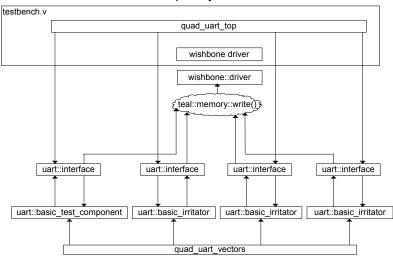

| Chapter 15: Chip Level Testing307                  | , |

| Overview                                           |   |

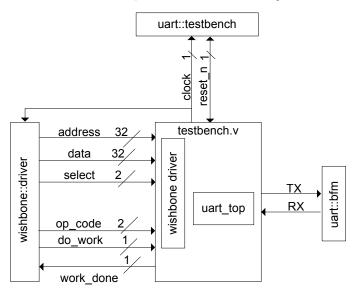

| Theory of Operation                                |   |

| Verification environment                           |   |

| Running the UART Example                           |   |

| The quad_test_components Test                      |   |

| The quad_uart_irritators Test                      |   |

| UART irritator class                               |   |

| The test                                           |   |

| The quad_uart_vectors Test                         |   |

|                                                    |   |

| The uart_test_0 Test                               |   |

| Chapter 16: Things to Remember    | 321 |

|-----------------------------------|-----|

| Part I: Use C++ and Layers!       | 322 |

| Part II: An Open-Source Approach  | 322 |

| Part III: OOP—Best Practices      | 323 |

| Part IV: Examples—Copy and Adapt! | 324 |

| Conclusion to the Conclusion      | 325 |

|                                   |     |

| Index                             | 327 |

xviii • • • • • •

#### **Preface**

So what makes a person write a book? Insanity is a definite probability. Another possibility is a strong desire to help. We are not special people. We have worked in several companies, large and small, made mistakes, and generally muddled through our work. There are many people in the industry who are smarter than we are, and many coworkers who are more experienced.

We have been in the lab when we bring up the chips fresh from the fab, with customers and sales breathing down our necks. We've been through software bring-up and worked on drivers that had to work around bugs, er, features, in production chips.

What we feel makes us unique is our combined broad experience from both the software and hardware worlds. Mike has over 20 years of experience from the software world that he applies in this book to hardware verification. Robert has over 12 years of experience with hardware verification, with a focus on environments and methodology.

So what we bring to the task of functional verification is over three decades of combined experience, from design, verification, software development, and management. It is our experiences that speak in this handbook. It is our desire that others might learn and benefit from these experiences.

We have had heated discussions over each line of code in this book and in our open-source libraries. We rarely agree at first, but by having to argue our cases we arrive at what we feel are smart, efficient, flexible, and simple solutions. Most of these we have "borrowed" from the software industry but have applied to the field of verification.

We believe that the verification industry can benefit from the lessons learned from the software domain. By using the industry-standard C++ language, the verification domain can adapt techniques and code from over twenty calendar years of software effort, the scope of which is nothing short of stunning. Many brilliant people have paved the way in the software field. Although the field of verification is much younger, we could benefit greatly from listening, learning, and adapting mature programming techniques to the production of products of the highest quality.

So why did we include open-source software with the handbook? Open-source software is a key to uniting and increasing the productivity of our industry.

There is almost no successful closed-source ("hard macro") intellectual property (IP), for a good reason. Without the ability to look at the source and edit as necessary, the task is much more difficult and the chances for success are slim.

You can find the open-source software and the examples used in this handbook on the accompanying CD. We've also included a simulator, which can be used for 30 days. The installer should run automatically, but in case it does not on your system, you can find the code at the top level of the CD.

The writing of this handbook has been a great and interesting, if slightly tiring, ride for us. We hope that the reading—and better yet, the application—of the basic principles inside will be of value for you.

Hardware Verification with C++

# **Acknowledgments**

It takes a village to raise a child, and it takes a village to create a book. There is a core family, and a few relatives, and a whole lot of helpful neighbors. The authors would like to bow humbly to our village.

This book would have been abysmal without the help of Tori Hunter and Gerry Ventura, who read through many, many early incarnations. Henrik Scheuer also provided great feedback, both detailed and "big picture." His feedback helped improve many chapters substantially.

Chris Kappler introduced Mike to hardware verification with C++ many years ago. Mike takes his hat off to Chris. David Kelly of Mentor Graphics deserves special mention. Ever since we discussed Teal with Dave several year ago, he has been a stalwart supporter.

Kate Pulnik did the graphic design. Without her our book would still have that "paper napkin scribbled on by engineers" look.

Michael Meyer was our main technical editor, turning our gibberish into English and making clear where we where unclear. This book would not have been readable without him.

We are truly grateful for all the reviewers, their time, and their suggestions during both the early and near final stages of the book. In particular we thank Ed Arthur, Per Bojsen, John DeRoo, Bob Fredieu, Ziad Hachem, Bennet Ih, Göran Knutson, Achot Matevossian, Andy Meyer, Jeff Paquette, Rex Perkins, Andrew Scougal, Brian Slater, Chris Spear, Bjarne Stroustrup, and Sterling Wight.

We can't forget Felix Unogwu and Andrew Zoneball, who really wanted to be mentioned in this book.

We are also grateful for the support and encouragement of the producers of the HDL simulators. In particular, we thank the following simulator companies—Aldec, Cadence, Mentor Graphics, and Synopsis—for providing licenses to their products, so we could confirm that the examples in this handbook work.

# Introduction

CHAPTER 1

Coding is a human endeavor. Forget that and all is lost.

Bjarne Stroustrup, father of C++

There are several books about hardware verification, so what makes this handbook different? Put simply, this handbook is meant to be useful in your day-to-day work. The authors are like you, cube dwellers, with battle scars from developing chips. We must cope with impossible schedules, a shortage of people to do the work, and constantly mutating hardware specifications.

We subtitled this book A Practitioner's Handbook because it contains real-world code examples and techniques. Sure, we talk about programming theory, but the theme of this book is writing code. We focus mainly on object-oriented programming (OOP) techniques and coding in C++. We back this up with a CD-ROM containing working, open-source Verification Intellectual Property (VIP), scripts, and several complete test systems.

We cover the following topics:

- C++ as a verification language

- The evolution of OOP, C++, and verification

- How to use OOP to build a flexible and adaptable verification system

- How to use specific OOP techniques to make verification code both simpler and more adaptable, with reference to actual situations (both good and bad) that the authors have encountered

- Useful C++ code, both as snippets, complete examples, and code libraries—all available as open source

This handbook is divided into four major sections:

- *Part I* provides an overview of OOP concepts, then walks through transforming a block-level view of a typical verification system into code and classes.

- Part II describes two free, open-source code libraries that can serve as a basis for a verification system—or as inspiration for your own environment. The first, called Teal, is a C++-to-HDL (hardware description language) interface. The second, called Truss, is a complete verification system framework. Both are available as open source and are included on the companion CD-ROM.

- Part III describes how to use OOP to make your team as productive as possible, how to communicate design intent better, and how to benefit from "lessons learned" in the software world.

- Part IV describes several complete real-world examples that illustrate the techniques described in the earlier parts of this book. In these examples we build complete verification environments with makefiles, scripts, and tests. These examples can serve as starting points for your own environment.

For the curious, each of the chapters in Part I and Part III ends with a section called "For Further Reading," which recommends relevant landmark papers and books from the software domain. 1

Hardware Verification with C++

2

<sup>1.</sup> The references in these sections, though not academically rigorous, should be sufficient to help you find the most recent versions of these works on the Internet

# **Background**

The silicon revolution<sup>2</sup> has made computers, cell phones, wireless networks, and portable MP3 players not only ubiquitous but in a constant state of evolution. However, the major impediment to introducing new hardware is no longer the hardware design phase itself, but the verification of it.

Costs of \$1M or more and delays of three to six months for new hardware revisions of a large and complex application-specific integrated circuits (ASICs) are common, providing plenty of incentive to get it right the first time. Even with field-programmable gate arrays (FPGAs), upgrades are costly, and debugging an FPGA in the lab is very complex for all but the simplest designs.

For these reasons, functional verification has emerged as a team effort to ensure that a chip or system works as intended. However, functional verification means different things to different people. At the 30,000-foot level, we write specifications, make schedules, and write test plans. Mainly, though, we code. This handbook focuses on the coding part.

White papers are published almost daily to document some new verification technique. Most of you probably have several papers on your desk that you want to read. Well, now you can throw away those papers! This handbook compresses the last ten years of verification techniques into a few hundred pages. Of course, we don't actually cover that decade in detail (after all, this is not a history book), but we have picked the best techniques we found that actually worked, and reduced them to short paragraphs and examples.

Because of this compression, we cover a wide variety of topics. The handbook's sections range from talking about C++, to introducing OOP, to using OOP at a fairly sophisticated level.

A Practitioner's Handbook

3

<sup>2.</sup> Moore's law of 1965 is still largely relevant. See "Cramming more components onto integrated circuits," by Gordon Moore, *Electronics*, Volume 38, Number 8, April 19, 1965.

## What is Functional Verification?

Asking "what is functional verification?" brings to mind the familiar poster, "A View of the World from Ninth Avenue," in which the streets of New York City are predominant and everything beyond is tiny and insignificant. Every one of us has a different perspective, all of which are, of course, "correct." Put simply, functional verification entails building and running software to make sure that a device under test (DUT, or in layman's terms, the chip) operates as intended—before it is mass-produced and shipped.

We perform a whole range of tasks where the end goal is to create a high degree of confidence in the functionality of the chip. Mostly we try to find errors of logic, by subjecting the chip to a wide variety of conditions, including error cases (where we validate graceful error handling and ensure that the chip at least does not "lock up"). We also make sure that the chip meets performance goals, and functions in uncommon combinations of parameters ("corner cases"), and confirm that the register, interrupt, and memory-map interfaces work as specified.

As with the view of New York City, the perspectives of every company, indeed even of the design and test teams within a company, will naturally be slightly different. Nevertheless, as long as the chip works as a product, there are a number of ways to achieve success. That's why this handbook does not focus on what the specific tasks are; you know what you have to do. Rather, we focus on how you can write your code as effectively as possible, to alleviate the inevitable pain of verification.

# Why Focus on C++?

A major development in the field of functional verification is the increasingly mainstream use of OOP techniques. Basically, those of us in the verification field need those techniques to handle increasingly complex tasks effectively. While most of techniques presented in this handbook

<sup>&</sup>lt;sup>3.</sup> Saul Steinberg, cover of *The New Yorker*, March 29, 1976.

are adaptable to any number of languages such as Vera or System Verilog, we focus on C++; the marriage of the C programming language and OOP.

At its core, OOP is designed to manage complexity. All other things being equal, simpler code is better. Because of the flexibility inherent in using OOP, we can write code that is simpler to use, and therefore more adaptable. In short, we can write reusable code that outlives its initial use.

This handbook is all about providing techniques, guidelines, and examples for using C++ in verification, allowing you to make more use of some "lessons learned" by software programmers. We distill the important bits of knowledge and techniques from the software world, and present them in the light of verification.

#### A Tour of the Handbook

The four parts of this handbook provide a variety of programming tips and techniques.

- Part I walks through the main concepts of OOP, introducing how to transform your high-level "whiteboard" idea for a verification system into separate roles and responsibilities. The goal is to build appropriately simple and adaptable verification systems.

- Part II uses these techniques and presents two open-source code libraries for verification called Teal and Truss. Teal is a C++-to-HDL interface (or gasket) that is lightweight and unobtrusive. Truss is a verification framework that encourages the use of the canonical form described in Part One. Both are used by several companies and run under most simulators.

- Part III introduces the OOP landscape in a fair amount of detail. OOP thinking, design, and coding are illustrated by means of code snippets representative of problems that verification engineers commonly have to solve. The chapters in Part Three provide a handbook of techniques that are used in the software world to write simple, adaptable code.

- Part IV provides several complete examples of verification test systems, providing real-world examples and more details on how the OOP techniques discussed are actually used. Part Four is all about code. While a handbook may not be the best vehicle for

#### Chapter 1: Introduction

describing code, it can be a good reference tool. We start with a relatively simple example of how the verification of a single block of the ubiquitous UART<sup>4</sup> can be done. Then we show how this block-level environment can be expanded to a larger system.

The authors sincerely hope that, by reading this handbook, you will find useful ideas, techniques, and examples that you can use in your day-to-day verification coding efforts.

# For Further Reading

- On the topic of coding well, *Writing Solid Code*, by Steve McGuire, is a good tour of the lessons Microsoft has learned.

- Principles of Functional Verification, by Andreas Meyer, provides an introduction to the broad topic of chip verification.

- Writing Testbenches: Functional Verification of HDL Models, Second Edition, by Janick Bergeron, gives another view of the process of functional verification.

Hardware Verification with C++

<sup>4.</sup> Universal asynchronous receiver-transmitter.

# Part I: C++ and Verification (The Why and How)

This part of the handbook explores the authors' choice of C++ for verification. In the next chapter we take a brief look at the other choices available, and then look at the benefits and drawbacks of using C++.

Next, we weave three different themes together: the evolution of programming in general and C++ in particular, the creation of object-oriented programming (OOP) techniques, and the evolution of functional verification. The reason we chose to look at these three themes is to show why OOP exists and how it can be harnessed to benefit verification.

A major theme of this handbook is to build a verification system in layers. C++ in general, and OOP techniques specifically, are well-suited to this approach. In the last chapter of this section, we'll look at a canonical verification system by using a standard approach to building verification components.

# Why C++?

CHAPTER 2

A language is a dialect with an army.

Old proverb

We, in the functional verification trade, write code for a living. Well, we do that, and also puzzle over code that has been written and that has yet to be written. Because functional verification is a task that only gets more complex as designs become more complex, the language we work in determines how well we can cope with this increasing complexity.

The authors believe that C++ is the most appropriate choice for functional verification, but as with any choice, there are trade-offs. This chapter discusses the advantages and disadvantages of using C++ for functional verification. We'll look at the following topics:

- An abbreviated comparison of the languages and libraries available for functional verification

- Why C++ is the best choice for verification

- The side benefits of using C++, such as the ability to share code among the software, diagnostics, and modeling teams

- The disadvantages of using C++

#### Overview

Coding for functional verification can be separated into two parts. One is the generic programming part, and the other is the chip testing part. The generic part includes writing structures, functions, and interactions, using techniques such as OOP to manage complexity. The chip testing part includes connecting to the chip, running many threads, and managing random variables.

The generic programming part becomes more and more crucial as the complexity of the hardware to be tested grows. While the problem of connecting to a more complex chip tends to grow only linearly, the overall problem of dealing with this increased complexity grows exponentially.

The authors believe the generic part of programming is served well by C++. That language's features and expressive capabilities far exceed those of any other language currently in widespread use for functional verification. There is already more software written today in C++ than will ever be written for just verification alone. (If one assumes that coders for both domains are equally productive, there are over three million programmers currently, which is and will always will be greater than the number of C++ verification engineers.)

Still, the most important factor is getting our job done. What about the specific issues of connecting to and exercising a chip? Aren't specific languages (such as Vera or "e") better? The answer depends on you, your team, and your project. The verification-specific languages can make it easier to wiggle the chip's "wires," exercise the chip's functionality simultaneously, and vary the configuration of and traffic through the chip. While these tasks are not trivial, the percentage of lines of code required tend to be small.

The tasks that are made simpler by a verification-specific language generally increase linearly with the complexity of the chip. In other words, there are more wires to connect, more independent threads to run, more variables to constrain, and so on.

Hardware Verification with C++

<sup>1.</sup> The authors collectively have written in 14 languages and been paid to code in seven of them.

By contrast, it is much more difficult to make the complexity of a chip increase only linearly. So, as a verification system gets bigger, things tend to get out of hand quickly. Our ability to understand a complex verification system is often more important than how we actually connect to the hardware description language (HDL) wires.

Realize that connecting to the chip does not need to be hard in C++. Teal,<sup>2</sup> an open-source C++-to-HDL interface, provides a simple way for C++ code to connect to and interact with a chip. (Teal is provided on the companion CD.)

# C++: A Good Verification Language

Several attempts have been made to move verification away from HDLs, such as in the case of Verilog or VHDL.<sup>3</sup> An HDL does a good job of spanning design concepts (called the *register transfer level*, or RTL) down to a few primitives that are used in great numbers to implement a design (called the *gate level*). However, HDLs are not adept at "moving up" in abstraction level to handle modern programming techniques. Specifically, HDLs do not provide for object-oriented concepts. While SystemVerilog makes a step in this direction, it is not clear that such a large span of concepts as SystemVerilog tries to cover can be integrated well into a single language.

The table on the following page lists the pros and cons of various languages suitable for verification.

<sup>&</sup>lt;sup>2.</sup> Test Environment Abstraction Layer.

<sup>3.</sup> VHSIC (Very High-Speed Integrated Circuit) HDL.

| Language            | Pros                                                                      | Cons                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Verilog, VHDL       | Simple, no extra license required                                         | No class concept, no separation of verification and chip concerns                                                                                                                                                              |

| Cadence Specman "e" | Rich feature set                                                          | Proprietary, nonorthogonal language design                                                                                                                                                                                     |

| OpenVera            | C++ "like", better feature<br>set than HDL                                | Effectively proprietary,<br>interpreted, lacking full OOP<br>support                                                                                                                                                           |

| SystemVerilog       | IEEE standard, one tool does all, C interface                             | Covers all aspects from gates to OOP, implementation compliance is weak, language is large, yet programming feature set is small compared to C++ (no operator overloading, templating, multiple inheritance), weak C interface |

| SystemC (C++)       | Well-known language, open<br>source, does not need a<br>simulator         | Big footprint, focus is on<br>modeling, heavy use of<br>templating, coverage and<br>constraint system dominates<br>coding, long compile times,<br>hard to learn                                                                |

| Teal (C++)          | Well-known language, good<br>use of C++, open source, few<br>source files | Not a product, no inherent automatic garbage collection                                                                                                                                                                        |

| Homegrown PLI/C     | Free, well known                                                          | Not usually multithreaded,<br>usually called from HDL as a<br>utility function                                                                                                                                                 |

Many organizations use proprietary C code to implement the verification strategy. These proprietary systems are usually "bolted on" to the HDL code, serving mainly as utility computation functions.

In some sense, open-source Teal and C++ are the natural evolution of this process. Teal allows the verification system to be in control much like the proprietary model that "e," Vera, and SystemVerilog provide. Teal is different in that it is a minimal, yet sufficient, implementation of a modern verification-specific language that uses C++, thus making it easier to learn, use, and maintain.

# A Look at Hardware-Verification Languages

Languages dedicated solely to hardware verification did not spring up spontaneously. They were created and are somewhat successful because they have filled a need that languages such as Verilog and VHDL couldn't fill.

As we mentioned earlier, HDLs do a good job of describing hardware concepts, but fall short when it comes to testing hardware—because testing is mainly a software endeavor. Furthermore, HDLs are limited in their ability to manage randomization (which is generally not found in working hardware), and they do not encourage modern programming concepts, such as OOP.

#### Randomization

It is not simple to manage randomized parameters. It certainly is not clear that we, as an industry, understand enough about managing randomization to have a "best" solution. However, hardware verification languages (HVLs) do address one aspect of randomization: they fill the need for multiple independent streams of random numbers. This feature is necessary for the independent, simultaneous testing of different features of a chip. In addition, the generators are stable across multiple runs, given the same master seed. This is necessary, among other things, to keep the verification system "steady," so that the hardware model can be modified to fix bugs and the exact same test sequence can be run again to confirm that the updated hardware has solved the problem.

The random-number management solution used in HVLs includes a *constraint language*. It is not clear to the authors that this is a benefit. Sure, at some level we have to constrain random numbers to a range (or disjoint ranges), and possibly skew the distribution so that it is nonuniform. However, adding a declarative sublanguage within a procedural verification language is not a clear win. In addition to having to learn an HVL, the application of hierarchical and overlapping constraints is not intuitive.

For example, in one company we used the recommended method of extending a class to add constraints. This is "obvious" in theory, but in

a real system one often cannot find, or keep in mind, all the classes and their subclasses. We kept adding constraints that conflicted at run time, and other testers added constraints to a class that many people were already using—even though the added constraints were applicable to only a single test. Finally, we decided that all constraints were to be local to a class, and not in the inherited classes.<sup>4</sup>

#### Coverage

In addition to using constraints to guide the randomization, HVLs add a *coverage* sublanguage. While coverage is an important concept, the authors are not certain that the industry has a clear solution to apply it. It is a relatively simple matter to collect data, but many questions remain.

- Do you keep the time that the coverage event occurred?

- How do you fold a large coverage range (such as an integer or a real) into coverage bins?

- Most important, what is the relationship between the covered events and the constraints that control the randomization?

This last point is critical. It is the key to the goal of managing randomization in order to meet some coverage goals, so that the system can adjust itself without the need for human intervention. While many papers have been written on automated coverage-driven verification, the authors believe that this is a research question that may not even have a solution for real-world situations.

# Object-oriented support

HVLs provide the ability to express verifications systems using OOP techniques. Although each of the HVLs has implemented OOP to some degree or another, this is actually the strong point of C++. While C++ is not the first language to have OOP techniques, it is the most widely used, and has a more extensive and mature OOP implementation than any other current verification language.

Hardware Verification with C++

<sup>&</sup>lt;sup>4.</sup> Don't worry if the terms are a bit confusing in this paragraph. They will be explained in the next chapter.

# Main Benefits of Using C++

There is a vast difference between the things you think about when coding an RTL design and the things you think about when coding for verification. Using C++ as the verification language helps to clarify this separation of concerns.

C++ is well known, with many books and experts. (A quick web search for "C++" yielded over 77 million references!) The language is well thought out and has been through many revisions, so no sharp edges remain; it has been polished by thousands of engineer-years of practical use. As a result, the features of the language are very orthogonal, meaning that the constructs are consistent regardless of context.

Furthermore, C++ has powerful and proven debugging tools, such as GDB<sup>5</sup> and DDD.<sup>6</sup> Also, because C++ is a superset of C, the existing millions of lines of C code can be easily integrated, including system calls (such as sockets, login, and rsh), shells (such as tcl, Perl, and Python), and databases.

Many companies have C or C++ models of their core algorithms. Common examples include digital signal-processing (DSP) libraries, graphics pipes, or packet-routing algorithms. There are also many public-domain implementations of standard algorithms. Even with specialized algorithms of interfaces, there is often a C-model implementation.

It is odd that hardware verification languages don't work seamlessly with C/C++. These language interfaces support only the integral types (such as ints and chars), and cannot pass structures or objects to and from a C/C++ model (which is curious, because many HVLs use C++ as the implementation language).

C++ has a wealth of programming features. It supports the concept of interface versus implementation, allowing the user of an interface to concentrate on what the interface can do, not on how it is implemented. C++ also provides operator overloading, templating, namespace, and multiple inheritance, to mention only a few features. Techniques that use

A Practitioner's Handbook

<sup>5.</sup> GNU Debugger.

<sup>6.</sup> Data Display Debugger, a popular graphical user interface for command-line debuggers.

such features, to be illustrated in subsequent chapters, allow your verification system to be simple, robust, and adaptable.

# Other Benefits of Using C++

In addition to the benefits mentioned above, there are some additional benefits of using C++. These side benefits all revolve around the ability to integrate with the software team—which may or may not be important in your company. With C++ you can enlist members of the software team for your verification effort, either on a short-term or long-term basis. Using C++ for verification also enables the efficient coverification of software and hardware. (The converse is also true.)

As long as a portion of the software team is available as a pool of talent, the flexibility and modularity of C++ makes it possible to use these team members (perhaps with a little help) to aid in writing header files, algorithms, and tests. In addition, the experience of the software team can be used as a "sounding board" for the verification architecture and test plans.

The software team benefits as well. In addition to having a say in the design before it is hardened, they get already debugged header files and key algorithms as well as a better understanding of the chip. There is also the social component of working together, which is beneficial when debugging in the lab.

Coverification is the ability to write and debug some of the system software before the hardware is fabricated. For SoCs, a common technique is to compile a program to binary and load it to the boot RAM in the HDL simulator model. Then during simulation the CPU boots and executes the compiled binary code on the chip.

Instead, by using and executing C++ natively on the simulation host and accessing the chip through bus functional models (BFMs), software algorithms and drivers run orders of magnitude faster. This is because the compiled code runs in the host machine's native language, and drops to the simulator only when a change occurs on a monitored chip signal.

# Drawbacks of Using C++

While there are many benefits to using C++, there are, of course, some drawbacks. One drawback is that, by itself, C++ is not a verification solution. Even with Teal or SystemC as the interface between Verilog and C++, additional code must be written.

Another drawback, ironically, is that C++ is a rich language—with the "dangerous" power of expression that this implies. While you will be quite proficient with the language within a few weeks, its expressive capability is immense. Consequently, because it is designed for production software, there are many ways to express the same concept.

Consequently, it can take time to learn how to use C++ effectively, and because there are no marketing teams from large electronic design automation (EDA) companies giving presentations on the design methodology of verification with C++, you have to find your own way. This, by the way, is not necessarily a bad thing.

The purpose of this handbook is to lessen the effects of these drawbacks by providing proven OOP techniques from the software world, and by illustrating, through real examples, how they are applicable to functional verification.

Also, because C++ is an established language, some convenient HDL syntax features cannot be added (for example, "\_" or "\$" in literals, the "24'hx330z99" notation, or the @ posedge or negedge operators).

In addition, C++ lacks specific verification sublanguage constructs, such as constraint and coverage language declarations. While these can still be added to C++ as libraries, the best implementation is still unclear, because the overall problem is not yet well-understood.

# For Further Reading

Software Engineering: A Practitioner's Approach, by Roger S. Pressman, has a great section on the evolution of programming. This handbook also has references to landmark papers and books.

#### Chapter 2: Why C++?

- The SystemC and Testbuilder manuals have discussions on why C++ is good for verification. SystemC information can be found at www.systemc.org, and Testbuilder information can be found at www.testbuilder.net.

- There are several standards for verification and simulation, such as IEEE 1364-1999 (for VHDL), IEEE 1995-2001 (for Verilog), IEEE 1076, P1647 (for the IEEE version of Cadence "e") and P1800 (for SystemVerilog). The web site www.openvera.org provides the OpenVera specification.

# OOP, C++, and Verification

C H A P T E R 3

Progress has not followed a straight ascending line, but a spiral with rhythms of progress and retrogression, of evolution and dissolution.

Johann Wolfgang von Goethe

This chapter looks at why and how object-oriented programming was developed, and reflects on why OOP is the right choice for managing the increasing complexity of verification. It then shows how OOP is expressed in C++. The OOP techniques shown in this chapter are used throughout the remainder of this handbook.

#### Overview

OOP is a programming technique that is often touted as a cure-all for verification. While it is true that OOP is an essential tool in a programmer's toolbox, it is by no means the most important one. One's experience, intelligence, and team environment are far more important to the success of verification than any language feature or technique. That said, OOP is a useful tool for communicating and enforcing design intent for large projects and teams, in addition to being a good way to build adaptable and maintainable code.

This handbook is intended for those with at least some familiarity with OOP. Many verification engineers already have some experience with OOP through languages such as Vera, Specman, SystemVerilog, or SystemC.

The first part of this chapter looks at the history of OOP and why it is well-suited to functional verification. The second part shows how C++ expresses the most common elements of OOP.

For readers with limited experience in OOP, there are several suggestions at the end of this chapter. If you have some, but limited, experience with OOP, or if some time has passed since you used it last, then *don't worry!*

Some of the aspects presented in this and subsequent chapters might seem confusing at first, but the main part of this handbook shows a complete working verification environment. It is the authors' hope and intent that you will "copy and paste" from this environment as well as from the examples provided. This handbook is designed to give you a jump start on using C++ for verification without having to design every class from scratch.

The "basic" OOP techniques expressed in this chapter are the foundation of the techniques used and discussed throughout the remainder of this book.

#### The Evolution of OOP and C++

OOP techniques, and C++, have been proven to help large programming teams handle code complexity. One key to coping with such complexity is the ability to express the *intent* of the code, thus allowing individual programmers to develop their part of the code more effectively. This understanding of the intent allows programmers to build upon already working code and understand the overall structure into which their code must fit.

#### Assembly programming: The early days

Programming has changed a lot over the years. It started with the use of assembly language<sup>1</sup> as a way to express a "simple" shorthand notation for the underlying machine language. This simple abstraction allowed programmers to focus on the problem at hand, instead of on the menial and error-prone task of writing each instruction as a hexadecimal or octal integer. Simply put, abstraction allowed an individual programmer to become more productive.

Here is an example of some assembly language:

```

MOV.W R3, #100

MOV.L R1, #7865DB

loop: ADDQ.W R1, #4

TST.W R1, R2

BNZ loop

```

#### Procedural languages: The next big step

With the increase in complexity of the problems programmers were asked to handle, procedural languages such as FORTRAN,<sup>2</sup> C, and Pascal were developed. These procedural languages became very popular and allowed individual programmers to become highly productive.

Here is an example of  $\mathsf{FORTRAN}, ^3$  a common procedural language:

<sup>1.</sup> The first assembly language was created by Grace Hopper in 1948.

<sup>&</sup>lt;sup>2.</sup> For FORmula TRANslator, created by John W. Backus in 1952.

```

DO 3, LOOP = 1, 10

READ *, MGRADE, AVERAGE

IF (.NOT. (AVERAGE .GT. 6.0 E -1)) THEN

PRINT *, 'Failing average of ', AVERAGE

STOP

ELSE

PRINT *, 'Passing average of', AVERAGE

AVERAGE = (MGRADE / 1 E 2) + AVERAGE

END IF

3 CONTINUE

```

Interestingly, as the size of the programs grew, the focus of programming switched from the productivity of the individual to the productivity of the larger team. It was found that procedural languages were not well-suited to large programming efforts, because communicating the intent of the code was difficult. OOP, with its ability to build classes upon classes and define interfaces, proved an effective response to this problem.

#### OOP: Inheritance for functionality

By necessity, OOP developed in stages. The first stage focused on what is often called *data hiding* or *data abstraction*. This is a way to organize large amounts of code into more manageable pieces. With large amounts of procedural code, it became very complicated to keep track of all structures and the procedures that could operate on those structures. It was also hard to expand, in an organized way, upon existing code without directly editing the code—a process that, as we all know, is error prone.

To address these problems, a language called "C with Classes" was developed by Bjarne Stroustrup in 1981. Based on Simula, a simulation language developed in 1967, this new language was recognized as the first language to introduce object-oriented concepts. One of Simula's first uses was as a hardware simulator. "C with Classes" merged these OOP concepts with the C programming language.

"C with Classes" included ways to organize data structures and the functions that operate on those structures, and called this organizational

<sup>3.</sup> Okay, you got us—this is actually FORTRAN 77, the "new" FORTRAN (ANSI X3.9, 1978).

concept a *class* (loosely based on Simula's class). The functions, now scoped within a class, are called *methods*. In addition, it included ways for one class to expand upon another through *inheritance* (also from Simula).

Classes allowed for the grouping of code with data, while inheritance allowed a way to express increasingly intricate functionality through the reuse of smaller working modules. This technique is often called *inheritance for functionality*. (Later in this chapter, we'll show how C++ expresses both these features—grouping into classes and reuse through inheritance—in more detail.) This new approach was sort of like the Industrial Revolution of the programming world, increasing team productivity by an order of magnitude.

So "C with Classes" helped improve the productivity of programming teams, by helping to organize the code in layers—with one layer inheriting from, and enhancing upon, a lower layer. This meant that the code could now be "reasoned about." With this technique, changes and bug fixes are made only to the appropriate module, without the changes echoing, or propagating undesirably, throughout all of the code.

Furthermore, as code was structured into layers through hierarchy trees, several patterns became visible. For example, it became clear that certain layers were not involved with manipulating the data (in the classes) directly, but rather with ordering, structuring, and tracking events.

These framework layers became more and more important to understanding the system. To get a large program to be "reasonable," more and more standard infrastructure was needed. These framework layers had no "interest" in how the actual data were manipulated; rather, the important feature was that now the data could be assumed to be manipulated in predefined ways.

As an example, as long as each class in a particular framework layer had a start() or a randomize() function, working with classes of that type was reasonable. As these framework layers were written, it became clear that they could be generalized as long as each class followed the rules for that type of "component." The problem was that "C with Classes" provided no way of enforcing these rules.

#### OOP: Inheritance for interface

What was needed was a way to express the rules that a class had to follow in order to "fit in." The solution, known as *virtualization*, was included from day one in the language that would become known as C++. With virtualization one could define classes called *abstract base classes*, which simply expressed the *interface* a component must conform to in order to fit into the larger system.

Each developer of the actual classes that fit in a particular structure would then inherit from this abstract base class, and implement the details for how a particular function should be implemented for the problem at hand. This technique of defining the interface through virtualization, often called *inheritance for interface*, is frequently used in OOP-based projects.

The clever thing is that now one could write the code for the framework layer using abstract base classes. This not only allowed the framework to be implemented concurrently with the data-based classes, but it also allowed the framework layer to be developed in a much more generic way. This virtualization of base classes has proven to be a powerful technique for creating and maintaining large and complex systems.

#### OOP: Templates

Virtual base classes are a great development for generic programming, and are a very powerful tool for expressing how an environment or program should be structured. However, there are certain problems that are even more generic in nature, such as linked lists or dynamic arrays. For example, verification code often maintains arrays of generated data and arrays of the data that have been received.

For these container-based problems, the point of the base class is algorithmic and independent of the data. Consequently, it would be clumsy to have to inherit from a base class just to use the algorithm. Instead, a technique called *templating* was developed. A template is, not surprisingly, a reusable pattern for code, rather than an implementation. (Templates are discussed later in this chapter.) The idea was to abstract the algorithm away from the data it operated on. In effect, this is also a framework of sorts.

#### C++: The standard template library

The most common grouping of templates is the Standard Template Library for C++ (commonly known as "the STL"). The STL is a large selection of container and algorithmic templates that solve a lot of common programming problems, such as the storing, ordering, transforming, and managing of groups of data. The STL is an indispensable tool for day-to-day work, and has proven to be more efficient (in time and space) than what most programmers can write.

C++ contains many more features, but its key strength is that it allows for a programmer's intent to be expressed through the ability to build upon known working classes. C++ is built upon layers of work in earlier languages.

#### The Evolution of Functional Verification

#### Verification through inspection

There are similarities with the development of OOP and that of functional verification, and while hardware verification is a younger field than software programming, it has (not surprisingly) followed a similar path.

As readers of this handbook surely know, functional verification has come a long way from its recent humble beginning as a (mostly manual) process of verifying simulation waveforms. From there, it evolved into "golden" files; a current simulation run was compared to a known-to-begood result file—the golden file. For this technique to work it required fixed stimuli, often provided in simple text format. Golden files were an acceptable technique for small designs, where the complete design could be tested exhaustively through a few simulation runs.

<sup>&</sup>lt;sup>4.</sup> Invented by Alex Stepanov in 1992.

#### Verification through randomness

The simple technique of using golden files became impossible to use as the size of the hardware being tested grew both in size and complexity, so other techniques were needed. For larger projects it was no longer possible to test the "state space" of a chip completely. To do so would require an unobtainable amount of computer time, even on the fastest machines. To address the reality that the chips being developed could no longer be tested exhaustively, random testing was introduced. Using randomness in tests changes the input stimuli every time a test is run. The goal is to cover as much of the state space as possible through ongoing regression runs.

Unfortunately, several problems were found in using randomness with current hardware description languages (such as Verilog or VHDL). To begin with, the result checking became more complex as golden files could no longer be used (because the input stimuli changed for each run). This meant that verification models that could predict the outcome from any set of input stimuli were needed. Writing these models has become a major task for the verification projects of today.

However, this technique also posed other problems. It was discovered that using randomness was a tricky thing. If you use random stimuli and your testing fails because of a hardware bug, then you later would want to rerun the exact same sequence of stimuli to verify that the bug has been solved. This is easier said than done.

You can either record all the stimuli that generated the test run, then use some mechanism to replay the stimuli later; alternatively, you can track the "seed" from which the (pseudo) random generator starts and then pass that number into your next simulation run.

Both techniques can be problematic, because storing all the generated stimuli requires a lot of disk space and directory infrastructure, and because controlling randomness through a seed requires good control over your "random" generator.

The current most common solution to this problem is to control and store the "random" seed, then use it to replay a given stimuli sequence over and over.

## The emergence of hardware verification languages

We can see that controlling the generation of random stimuli requires many things. We need verification models that can predict results from any given set of stimuli. We also need control over how the random generator works, to be able to replay a given stimuli sequence. It was found that using HDL languages, such as Verilog and VHDL, was difficult with respect both to writing high-level models quickly and controlling randomness. In Verilog, for example, you couldn't control the random seed back in 1987.

As a result, people started looking at other languages for verification. The natural first step was connecting C to Verilog, but soon languages such as "e" and Vera were introduced. These languages made it easier to do random testing, in turn making it possible to test much larger chips.

## OOP: A current trend in hardware verification languages

The problems we are facing today in verification are similar to the problems software faced when OOP was adopted. We now have to deal with very large amounts of code and multitudes of modules, all of which must be compiled, instantiated, controlled, randomized, and run. This is not an easy task, and we spend more and more time solving these basic framework problems.

It seems clear that adopting OOP techniques should help make these problems more manageable. Unfortunately, there are still not enough people in the field of verification who have sufficient experience and understanding of how to develop an appropriate OOP infrastructure.

Engineers in our field are just starting to adopt OOP techniques, and as we are early in this process, they are taking many different approaches. Vera and SystemVerilog offer one approach, by trying to marry many different concepts into one complete verification language.

SystemVerilog, for example, covers many more aspects beyond just OOP, including an RTL language, a temporal assertion language, a constraint language, and even a code coverage language.

Contrast this with the development of C++, where there was always an effort to keep the language small. Most of the syntax of C++ is still compatible with C. New techniques were carefully explored before they were introduced, as can be seen, for example, in virtualization. The concept of virtualization was known before "C with Classes," but it was left out of the language until it could be implemented well.

#### OOP: Problems with the current approach