### Ata Elahi · Trevor Arjeski

# ARM Assembly Language with Hardware Experiments

ARM Assembly Language with Hardware Experiments

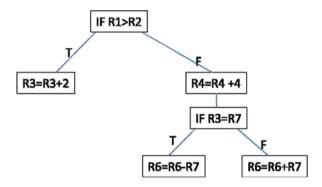

Ata Elahi • Trevor Arjeski

## ARM Assembly Language with Hardware Experiments

Ata Elahi Southern Connecticut State University New Haven Connecticut USA Trevor Arjeski Southern Connecticut State University New Haven Connecticut USA

ISBN 978-3-319-11703-4 ISBN 978-3-319-11704-1 (eBook) DOI 10.1007/978-3-319-11704-1

Library of Congress Control Number: 2014955658

Springer Cham Heidelberg New York Dordrecht London

© Springer International Publishing Switzerland 2015

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

#### Preface

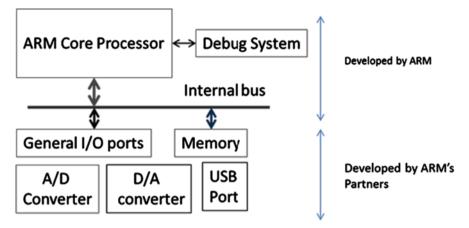

ARM is one of the leading suppliers of microprocessors for the entire world. ARM has designed and developed a CPU that partner companies can manufacture and add more peripherals to the processor. An ARM processor has a wide range of application in today's technology, such as mobile phones, tablets, televisions, and automobiles. Learning the ARM instruction set and ARM assembly programming is an essential tool in the development of low-level applications for the ARM processor. Engineers will benefit significantly from the understanding of computer architecture and assembly language, especially if they are working in an industry where performance is crucial or hardware is being developed.

**Organization** This book contains seven chapters. The reader does not require any background in ARM assembly language to understand material of this book.

Chapters one and two of this book form a foundation for the rest of the chapters.

Chapter 1 covers some necessary knowledge of digital signals, analog signals, number systems and transmission methods.

Chapter 2 covers logic gates, registers and an introduction to computer architecture.

Chapters 3 and 4 cover the ARM processor architecture with its instructions.

Chapter 5 covers ARM assembly language programming using Keil development tools.

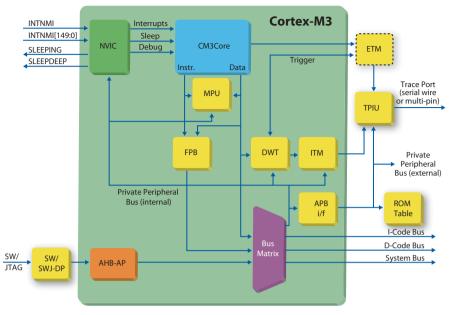

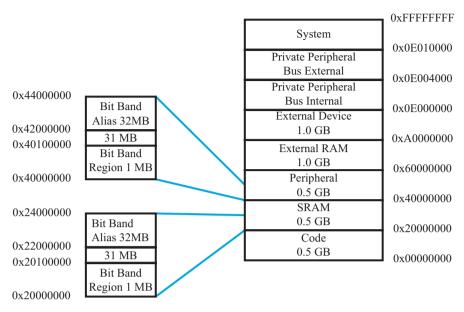

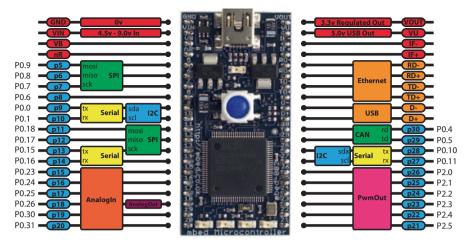

Chapter 6 covers ARM Cortex-M3 processor architecture, the MBED NXP LPC1768 and basic GPIO Programming.

Chapter 7 covers lab experiments that include:

- · Creating a binary counter using onboard LEDs

- Configuring an Analog-To-Digital Converter (ADC)

- Creating a voltmeter with an ADC

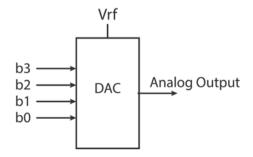

- Configuring Digital to Analog Converter (DAC)

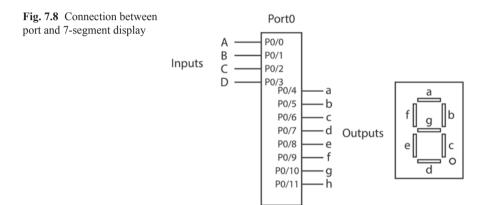

- Converting binary to output for a hexadecimal display

- Configuring a Real-Time Clock (RTC)

**Intended Audience** This book is written primarily as an introduction to assembly language for students who are studying computer science, computer engineering,

or hobbyists who are simply interested in learning ARM assembly programming with hands-on experiments. This book can be used as a first course in computer system which covers numbers systems, Digital Logics, Introduction to Computer Architecture and Assembly language for computer science and computer technology students.

#### Contents

| 1 | Nun  | iber Systems and Data Communication                         | 1  |

|---|------|-------------------------------------------------------------|----|

|   | 1.1  | Introduction                                                | 1  |

|   | 1.2  | Analog Signals                                              | 1  |

|   | 1.3  | Digital Signals                                             | 4  |

|   | 1.4  | Number System                                               | 4  |

|   | 1.5  | Coding Schemes                                              | 10 |

|   | 1.6  | Clock                                                       | 12 |

|   | 1.7  | Transmission Modes                                          | 13 |

|   | 1.8  | Transmission Methods                                        | 14 |

| 2 | Logi | c Gates and Introduction to Computer Architecture           | 17 |

|   | 2.1  | Introduction                                                | 17 |

|   | 2.2  | Logic Gates                                                 | 17 |

|   | 2.3  | Integrated Circuit (IC) Classification                      | 21 |

|   | 2.4  | Registers                                                   | 22 |

|   | 2.5  | Introduction to Computer Architecture                       | 22 |

|   | 2.6  | Memory                                                      | 27 |

|   | 2.7  | Multiplexer and Decoder                                     | 30 |

| 3 | ARN  | A Instructions Part I                                       | 35 |

|   | 3.1  | Introduction                                                | 35 |

|   | 3.2  | Instruction Set Architecture (ISA)                          | 38 |

|   | 3.3  | ARM Instructions                                            | 39 |

|   | 3.4  | Register Swap Instructions (MOV and MVN)                    | 42 |

|   | 3.5  | Shift and Rotate Instructions                               | 43 |

|   | 3.6  | ARM Unconditional Instructions and Conditional Instructions | 46 |

|   | 3.7  | ARM Data Processing Instruction Format                      | 47 |

|   | 3.8  | Stack Operation and Instructions                            | 49 |

|   | 3.9  | Branch (B) and Branch with Link Instruction (BL)            | 51 |

|   | 3.10 |                                                             | 53 |

| 4  | ARM   | A Instructions and Part II                          | 57  |

|----|-------|-----------------------------------------------------|-----|

|    | 4.1   | ARM Data Transfer Instructions                      | 57  |

|    | 4.2   | ARM Addressing Mode                                 | 59  |

|    | 4.3   | Data Transfer Instruction Format                    | 61  |

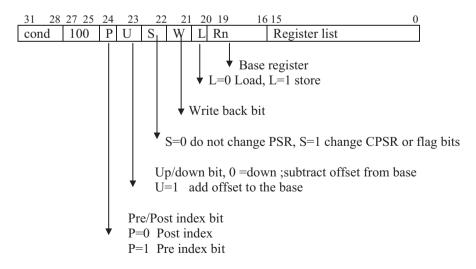

|    | 4.4   | Block Transfer Instruction and Instruction Format   | 62  |

|    | 4.5   | Swap Memory and Register (SWAP)                     | 62  |

|    | 4.6   | Bits Field Instructions                             | 63  |

|    | 4.7   | Data Representation and Memory                      | 65  |

| 5  | ARM   | A Assembly Language Programming Using Keil          |     |

|    | Dev   | elopment Tools Introduction                         | 69  |

|    | 5.1   | Introduction                                        | 69  |

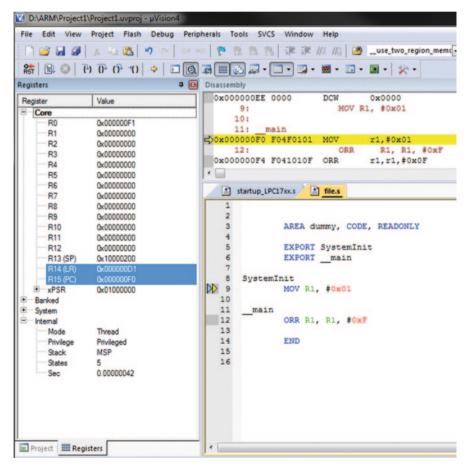

|    | 5.2   | Keil Development Tools for ARM Assembly             | 69  |

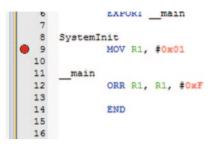

|    | 5.3   | Program Template                                    | 76  |

|    | 5.4   | Programming Rules                                   | 76  |

|    | 5.5   | Directives                                          | 77  |

| 6  | ARN   | 1 Cortex-M3 Processor and MBED NXP LPC1768          | 83  |

|    | 6.1   | Introduction                                        | 83  |

|    | 6.2   | MBED NXP LPC1768                                    | 86  |

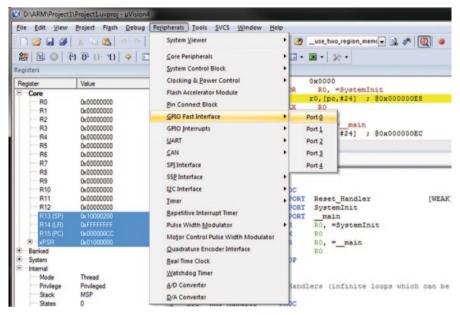

|    | 6.3   | Basic GPIO Programming                              | 88  |

|    | 6.4   | Flashing the NXP LPC1768                            | 95  |

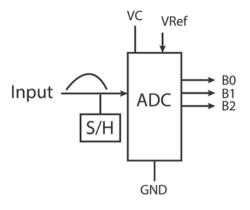

| 7  | Lab   | Experiments                                         | 97  |

|    | 7.1   | Introduction                                        | 97  |

|    | 7.2   | Lab#1 Binary Counter Using Onboard LEDs             | 97  |

|    | 7.3   | Lab2: Configuring the Real-Time Clock (RTC)         | 100 |

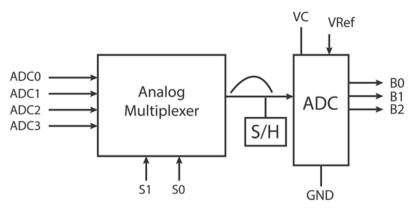

|    | 7.4   | Lab#3 Configuring Analog-To-Digital Converter (ADC) | 104 |

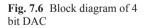

|    | 7.5   | Lab #4: Digital to Analog Converter (DAC)           | 113 |

|    | 7.6   | Experiment #5: Binary to Hexadecimal Display        | 116 |

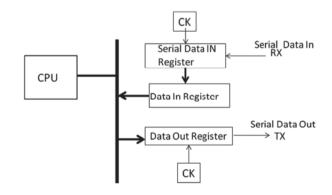

|    | 7.7   | Universal Asynchronous Receiver/Transmitter (UART)  | 118 |

| So | lutio | to the Problems and Questions                       | 123 |

| Re | feren | ces                                                 | 139 |

#### Chapter 1 Number Systems and Data Communication

#### 1.1 Introduction

In order to understand network technology it is important to know how information is represented for transmission from one computer to another. Information can be transferred between computers in one of two ways: an analog signal or a digital signal.

#### 1.2 Analog Signals

An analog signal is a signal whose amplitude is a function of time and changes gradually as time changes. Analog signals can be classified as non-periodic and periodic signals.

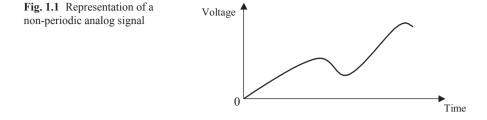

**Non-Periodic Signal** In a non-periodic signal there is no repeated pattern in the signal as shown in Fig. 1.1.

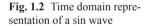

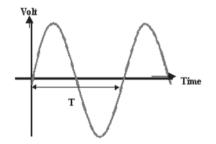

**Periodic Signal** A signal that repeats a pattern within a measurable time period is called a periodic signal and completion of a full pattern is called a *cycle*. The simplest periodic signal is a sine wave, which is shown in Fig. 1.2. In the time domain, a sine wave's amplitude a(t) can be represented mathematically as  $a(t) = ASin(\omega t + \theta)$  where A is the maximum amplitude,  $\omega$  is the angular frequency and  $\theta$  is the phase angle.

A periodic signal can also be represented in the frequency domain where the horizontal axis is the frequency and the vertical axis is the amplitude of signal. Figure 1.3 shows the Frequency domain representation of a sine wave signal.

Usually an electrical signal representing voice, temperature or a musical sound, is made of multiple waveforms. These signals have one fundamental frequency and multiple frequencies that are called harmonics.

**Characteristics of Analog Signal** The characteristics of a periodic analog signal are frequency, amplitude, and phase.

**Frequency:** Frequency (F) is the number of cycles in one second;  $F = \frac{1}{T}$ , represented in *Hz* (Hertz). If each cycle of an analog signal is repeated every one second, the frequency of the signal is one *Hz*. If each cycle of an analog signal is repeated 1000 times every second (once every millisecond) the frequency is:

$$f = \frac{1}{T} = \frac{1}{10^{-3}} = 1000Hz = 1kHz$$

Table 1.1 shows different values for frequency and their corresponding periods.

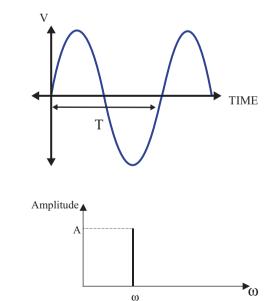

**Amplitude:** The Amplitude of an analog signal is a function of time as shown in Fig. 1.4 and may be represented in volts (unit of voltage). In other word, the amplitude is its voltage value at any given time. At the time of  $t_1$ , the amplitude of signal is  $V_1$ .

**Fig. 1.3** Frequency representation of a sine wave

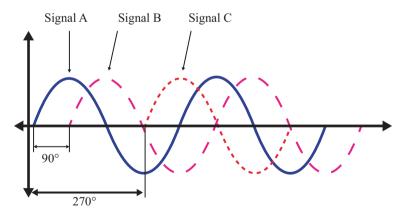

**Phase:** Two signals with the same frequency can differ in phase. This means that one of the signals starts at a different time from the other one. This difference can be represented by degree, from 0 to 360 degrees or by radians where  $360^{\circ} = 2\pi$  radians. A sine wave signal can be represented by the equation  $a(t) = ASin(\omega t + \theta)$  where A is the peak amplitude;  $\omega$  (omega) is frequency in radians per second; *t* is time in seconds; and  $\theta$  is the phase angle. Cyclic frequency *f* can be expressed in terms of  $\omega$  according to  $f = \frac{\omega}{2\pi}$ . A phase angle of zero means the sine wave starts at time *t* = 0 and phase angle of 90° mean the signal start at 90° as shown in Fig. 1.5.

**Example 1.1:** Find the equation for a sine wave signal with frequency of 10 *Hz*, maximum amplitude of 20 V and phase angle of zero.

$$\omega = 2\pi f = 2 \times 3.1416 \times 10 = 62.83 \frac{rad}{sec}$$

$$a(t) = 20\sin(62.83t)$$

| 21                 | 1 7 1              |                           |                     |

|--------------------|--------------------|---------------------------|---------------------|

| Units of frequency | Numerical value    | Units of period           | Numerical value     |

| Hertz (Hz)         | 1 <i>Hz</i>        | Second (s)                | 1 s                 |

| Kilo Hertz (kHz)   | 10 <sup>3</sup> Hz | Millisecond (ms)          | 10 <sup>-3</sup> s  |

| Mega Hertz (MHz)   | 10 <sup>6</sup> Hz | Micro Second (µs)         | 10 <sup>-6</sup> s  |

| Giga Hertz (GHz)   | 10 <sup>9</sup> Hz | Nanosecond (ns)           | 10 <sup>-9</sup> s  |

| Tera Hertz (THz)   | $10^{12} Hz$       | Pico Second ( <i>ps</i> ) | 10 <sup>-12</sup> s |

Table 1.1 Typical units of frequency and period

Fig. 1.4 A sine wave signal over one cycle

#### 1.3 Digital Signals

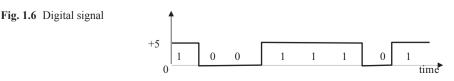

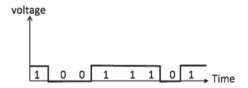

Modern computers communicate by using digital signals. **Digital signals** are represented by two voltages: one voltage represents the number 0 in binary and the other voltage represents the number 1 in binary. An example of a digital signal is shown in Fig. 1.6, where 0 V represents 0 in binary and +5 V represents 1.

#### 1.4 Number System

Numbers can be represented in different bases, consider the following number in decimal:

$$356 = 6 + 50 + 300 = 6 \times 10^{\circ} + 5 \times 10^{1} + 3 \times 10^{2}$$

356 has a base of 10 or, more commonly called, decimal.

In general, a number can be represented in the form

$(a_5\,a_4\,a_3\,a_2\,a_1\,a_0.a_{-1}\,a_{-2}\,a_{-3})\,r$  where r is base of the number and  $a_i$  has to be less then r

Equation 1.1 can be used to converting a number in given base to decimal

$$\underbrace{(\underbrace{a_{5} a_{4} a_{3} a_{2} a_{1} a_{0}}_{\text{Integer}} \cdot \underbrace{a_{-1} a_{-2} a_{-3}}_{\text{Fraction}})_{r}}_{\text{Fraction}} = a_{0} \times r^{0} + a_{1} \times r^{1} + a_{2} \times r^{2} + a_{3} \times r^{3} + \dots + a_{-1} \times r^{-1} + a_{-2} \times r^{-2} + a_{-2} \times r^{-3} \dots$$

(1.1)

Fig. 1.5 Three sine waves with different phases

Example 1.2 Converting (27.35)<sub>8</sub> to base 10

$$(27.35)_{8} = 7 * 8^{0} + 2 * 8^{1} + 3 * 8^{-1} + 5 * 8^{-2} = 7 + 16 + .375 + .078125 = (23.45)_{10}$$

Example 1.3 Convert 1101111 to decimal

$$\begin{aligned} (1101111)_2 = 1 * 2^0 + 1 * 2^1 + 1 * 2^2 + 1 * 2^3 + 0 * 2^4 + 1 * 2^5 + 1 * 2^6 \\ = 1 + 2 + 4 + 8 + 32 + 64 = (111)_{10} \end{aligned}$$

Converting from Binary to Decimal Equation 1.2 represent any binary number.

$$(a_5 a_4 a_3 a_2 a_1 a_0 \cdot a_{-1} a_{-2} a_{-3})_2$$

(1.2)

where

$a_i$  is a binary digit or bit (either 0 or 1) Equation 1.2 can be converted to decimal number by using Eq. 1.1

$$(\underbrace{a_{5} a_{4} a_{3} a_{2} a_{1} a_{0}}_{\text{Integer}} \cdot \underbrace{a_{-1} a_{-2} a_{-3}}_{\text{Fraction}})_{2} = a_{0} \times 2^{0} + a_{1} \times 2^{1} + a_{2} \times 2^{2} + a_{3} \times 2^{3} + \dots + a_{-1}$$

$$\times 2^{-1} + a_{-2} \times 2^{-2} + \dots (a_{5} a_{4} a_{3} a_{2} a_{1} a_{0} \cdot a_{-1} a_{-2} a_{-3})_{2}$$

$$= a_{0} + 2a_{1} + 4a_{2} + 8a_{3} + 16a_{4} + 32a_{5} + 64a_{6} + \frac{1}{2} * a_{-1} + \frac{1}{4} * a_{-2} + \frac{1}{8} * a - 3$$

(1.3)

**Example 1.4:** To convert (110111.101)<sub>2</sub> to decimal:

$$(110111.101)_{2} = 1 * 2^{0} + 1 * 2^{1} + 1 * 2^{2} + 0 * 2^{3} + 1 * 2^{4}$$

$$+ 1 * 2^{*5} + 1 * 2^{-1} + 0 * 2^{-2} + 1 * 2^{-3} = 55.625$$

Or

$$32+16+0+4+2+1+1/2+0+1/8$$

**Binary**, or Base-2 numbers, are represented by 0's and 1's. A binary digit, 0 or 1, is called a bit. Eight bits are equal to one byte, and 4 bytes is called a word.

**Converting From Decimal Integer to Binary:** To convert an integer number from decimal to binary, divide the decimal number by the new base (2 for binary), which will result in a quotient and a remainder (either 0 or 1). The first remainder will be the least significant bit of the binary number. Continually divide the quotient by the new base, while taking the remainders as each subsequent bit in the binary number, until the quotient becomes zero.

Example 1.5: Convert 34 in decimal to binary.

|          | Quotient | Remainder    |

|----------|----------|--------------|

| 34/2 =   | 17       | $0 = a_0$    |

|          |          |              |

| 17/2 =   | 8        | $1 = a_1$    |

| 8/2      | 4        | $0 = a_2$    |

| 4/2      | 2        | $0 = a_3$    |

| 2/2      | 1        | $0 = a_4$    |

| 1/2      | 0        | $1 = a_5$    |

|          |          |              |

| Therefor | e 34 =   | $(100010)_2$ |

**Converting Decimal Fraction to Binary:** A decimal number representation of  $(0.XY)_{10}$  can be converted into base 2 resulting in the representation,  $(0.a_{-1} a_{-2} a_{-3}...)_2$ .

The fraction number is multiplied by 2, the result of integer part is  $a_{-1}$  and fraction part multiply by 2 and then separate integer part from fraction, the integer part represent  $a_{-2}$ , this processes continues until the fraction becomes zero.

| (0.35) <sub>1</sub>                        | -0=         | (                 |             | ) 2                                                  |

|--------------------------------------------|-------------|-------------------|-------------|------------------------------------------------------|

| 0.35*2<br>0.7*2<br>0.4*2<br>0.8*2<br>0.6*2 | =<br>=<br>= | 1.4<br>0.8<br>1.6 | =<br>=<br>= | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$ |

Sometime the fraction does not reach zero and how many bits a decimal fraction should be represented depend on accuracy the user define.

The 0.35 = 0.01011 in binary

The hexadecimal number system has a base of 16, and therefore has 16 symbols (0 through 9, and A through F). Table 1.2 shows the decimal numbers, their binary values from 0 to 15, and their hexadecimal equivalents.

| Table 1.2 Decimal numbers           with binary and hexadecimal           aquivalents | Decimal | Binary (base 2) | Hexadecimal (Base<br>16) or HEX |

|---------------------------------------------------------------------------------------|---------|-----------------|---------------------------------|

| equivalents                                                                           | 0       | 0000            | 0                               |

|                                                                                       | 1       | 0001            | 1                               |

|                                                                                       | 2       | 0010            | 2                               |

|                                                                                       | 3       | 0011            | 3                               |

|                                                                                       | 4       | 0100            | 4                               |

|                                                                                       | 5       | 0101            | 5                               |

|                                                                                       | 6       | 0110            | 6                               |

|                                                                                       | 7       | 0111            | 7                               |

|                                                                                       | 8       | 1000            | 8                               |

|                                                                                       | 9       | 1001            | 9                               |

|                                                                                       | 10      | 1010            | A                               |

|                                                                                       | 11      | 1011            | В                               |

|                                                                                       | 12      | 1100            | С                               |

|                                                                                       | 13      | 1101            | D                               |

|                                                                                       | 14      | 1110            | Е                               |

|                                                                                       | 15      | 1111            | F                               |

Converting from Binary to Hex: Table 1.2 can also be used to convert a number from hexadecimal to binary and from binary to hexadecimal.

Example 1.5 Convert the binary number 001010011010 to hexadecimal. Each 4 bits are grouped from right to left. By using Table 2.2, each 4-bit group can be converted to its hexadecimal equivalent.

| 0010 | 1001 | 1010 |

|------|------|------|

| 2    | 9    | Α    |

**Example 1.6:** Convert (3D5)<sub>16</sub> to binary. By using Table 2.2, the result in binary is

| 3    | D    | 2    |

|------|------|------|

| 0011 | 1101 | 0101 |

The resulting binary number is: 001111010101

**Example 1.7:** Convert 6DB from hexadecimal to binary. By using Table 1.2, the result in binary is

| 6    | D    | В    |

|------|------|------|

| 0110 | 1101 | 1011 |

The resulting binary number is: 011011011011

**Example 1.8:** Convert (110111.101), to decimal:

$$(110111.101)_2 = 1*2^0 + 1*2^1 + 1*2^2 + 0*2^3 + 1*2^4 + 1*2^{*5}$$

+ 1\*2<sup>-1</sup> + 0\*2<sup>-2</sup> + 1\*2<sup>-3</sup> = 55.625

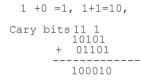

**Binary Addition:**

**Complement and Two's Complement:** The complement of 1 is zero and complement of 0 is one.

The complement of a binary number is calculated by complementing each bit of the number.

Example 1.9: The complement of 101101 is 010010

Two's Complement of a number=Complement of a number+1

**Example 1.10:** The two's complement of 101011 is

010100 (complement) +1 = 010101

**Example:** Find the two's complement of 10000

011111 (complement) + 1 = 10000

Subtraction using Two's Complement: Following procedure describe to subtract  $B=b_5 b_4 b_3 b_2 b_1 b_0$  from  $A=a_5 a_4 a_3 a_2 a_1 a_0$ .

- 1. Add Two's complement of B to the A

- 2. Check if result produce carry

- a. If result produce carry then discard the carry and result is positive

- b. If result does not produce carry, take two's complement of result and result is negative.

```

Example: Subtract B=101010 from A=110101

Step1; find two's complement of B, ComplementB +1

Two's complement of B = 010101+1 =010110

Add 2's complementofB to A

110101

+ 010110

_____

10 01011

Carry overflow, discard the carry and result is + 001011

Example1.11: Subtract B= 110101 from A=101010

Two's complement of B is 001010+1= 001011

Add 2's complement of B to A

001011

101010

+

_____

110101

```

As we can see, adding two 6 bit number results in a 6 bits answer. There is no carry over flow so we just take the two's complement of the result.

Two's Complement of 110101 = 001010 + 1 = -001011

**Unsigned, Signed Binary and Signed Two's Complement Numbers:** In an unsigned number all bits are used to represent the number but in a signed number the most significant bit of the number represents the sign. A 1 represents a negative sign and 0 represents a positive sign. The unsigned number 1101 is 13

**Signed Number:** In a signed number the most significant bit represents the sign, where 1101=-5 or 0101=+5

**Signed Two's Complement:** A signed two's complement apply to negative number, if the sign bit of number is negative, the number is represented by signed two's complement.

**Example 1.12:** Representing – 5 with 4 bits in signed two's complement.

-5 in signed number is 1101, the two's complement of 101 (5) is 011 then 1011 represent -5 in signed two's complement.

**Example 1.13:** Represent –23 with 8 bit signed two's complement

23 in binary is 10111,

23 in 8 bit signed number is 10010111, the two's complement (not including the sign) is

11101001

**Binary Coded Decimal (BCD):** In daily life we use decimal numbers where the largest digit is 9, which is represented by 1001 in binary. Table 1.3 shows decimal number and corresponding BCD code.

| Decimal | BCD  |

|---------|------|

| 0       | 0000 |

| 1       | 0001 |

| 2       | 0010 |

| 3       | 0011 |

| 4       | 0100 |

| 5       | 0101 |

| 6       | 0110 |

| 7       | 0111 |

| 8       | 1000 |

| 9       | 1001 |

**Table 1.3** Binary CodedDecimal (BCD)

**Example 1.14** Converting 345 to BCD.

Using the table: 0011 0100 0101.

**Example 1.15** Converting  $(10100010010)_{BCD}$  to decimal, separate each four bits from right to left and substituting the corresponding decimal number with BCD results in 512.

#### 1.5 Coding Schemes

Since computers can only understand binary numbers (0 or 1), all information (such as numbers, letters and symbols) must be represented as binary data. One commonly used code to represent printable and non-printable characters is the American Standard Code for Information Interchange (ASCII).

**ASCII Code** Each character in ASCII code has a representation using 8 bits, where the most significant bit is used for parity bit. Table 2.3 shows the **ASCII code** and its hexadecimal equivalent.

Characters from hexadecimal 00 to 1F and 7F are control characters which are nonprintable characters, such as NUL, SOH, STX, ETX, ESC and DLE (data link escape).

**Example 1.16** Convert the word "Network" to binary and show the result in hexadecimal. By using Table 1.4 each character is represented by seven bits and results in:

| 1001110      | 1100   | 101 | 1110100 | 1110111 | 1101111 | 1110010 | 1101011 |

|--------------|--------|-----|---------|---------|---------|---------|---------|

| Ν            | e      |     | t       | W       | 0       | r       | k       |

| or in hexade | ecimal |     |         |         |         |         |         |

| 2            | 4E     | 65  | 74      | 77      | 6F      | 72 6B   |         |

| Binary  | Hex | Char | Binary     | Hex | Char | Binary  | Hex  | Char | Binary  | Hex C | ıar |

|---------|-----|------|------------|-----|------|---------|------|------|---------|-------|-----|

| 0000000 | 00  | NUL  | 0100000    | 20  | SP   | 100000  | 0 40 | (a)  | 1100000 | 60    | ,   |

| 0000001 | 01  | SOH  | 0100001    | 21  | !    | 100000  | 1 41 | Ă    | 1100001 | 61    | a   |

| 0000010 | 02  | STX  | 0100010    | 22  | "    | 100001  | 0 42 | В    | 1100010 | 62    | b   |

| 0000011 | 03  | ETX  | 0100011    | 23  | #    | 100001  | 1 43 | С    | 1100011 | 63    | с   |

| 0000100 | 04  | EOT  | 0100100    | 24  | \$   | 100010  | 0 44 | D    | 1100100 |       | d   |

| 0000101 | 05  | ENQ  | 0100101    | 25  | %    | 100010  | 1 45 | E    | 1100101 | 65    | e   |

| 0000110 | 06  | ACK  | 0100110    | 26  | &    | 100011  | 0 46 | F    | 1100110 | 66    | f   |

| 0000111 | 07  | BEL  | 0100111    | 27  | •    | 100011  | 1 47 | G    | 1100111 |       | g   |

| 0001000 | 08  | BS   | 0101000    | 28  | (    | 100100  |      | н    | 1101000 |       | h   |

| 0001001 | 09  | HT   | 0101001    | 29  | )    | 100100  | 1 49 | Ι    | 1101001 | 69    | i   |

| 0001010 | 0A  | LF   | 0101010    | 2A  | *    | 100101  | 0 4A | J    | 1101010 | 6A    | j   |

| 0001011 | 0B  | VT   | 0101011    | 2B  | +    | 100101  |      | K    | 1101011 |       | k   |

| 0001100 | 0C  | FF   | 0101100    | 2C  | ,    | 100110  |      | L    | 1101100 |       | 1   |

| 0001101 | 0D  | CR   | 0101101    | 2D  | -    | 100110  | 1 4D | Μ    | 1101101 |       | m   |

| 0001110 | 0E  | SO   | 0101110    | 2E  |      | 100111  |      | Ν    | 1101110 |       | n   |

| 0001111 | 0F  | SI   | 0101111    | 2F  | /    | 100111  |      | 0    | 1101111 |       | 0   |

| 0010000 | 10  | DLE  | 0110000    | 30  | 0    | 101000  |      | Р    | 1110000 |       | р   |

| 0010001 | 11  | DC1  | 0110001    | 31  | 1    | 101000  |      | Q    | 1110001 |       | q   |

| 0010010 | 12  | DC2  | 0110010    | 32  | 2    | 101001  |      | R    | 1110010 |       | r   |

| 0010011 | 13  | DC3  | 0110011    | 33  | 3    | 101001  |      | S    | 1110011 |       | S   |

| 0010100 | 14  | DC4  | 0110100    | 34  | 4    | 101010  |      | Т    | 1110100 |       | t   |

| 0010101 | 15  | NACK |            | 35  | 5    | 101010  |      | U    | 1110101 |       | u   |

| 0010110 | 16  | SYN  | 0110110    | 36  | 6    | 101011  |      | V    | 1110110 |       | v   |

| 0010111 | 17  | ETB  | 0110111    | 37  | 7    | 101011  |      | W    | 1110111 |       | W   |

| 0011000 | 18  | CAN  | 0111000    | 38  | 8    | 101100  |      | Х    | 1111000 |       | х   |

| 0011001 | 19  | EM   | 0111001    | 39  | 9    | 101100  |      | Y    | 1111001 |       | У   |

| 0011010 | 1A  | SUB  | 0111010    | 3A  | :    | 101101  |      | Z    | 1111010 |       | Z   |

| 0011011 | 1B  | ESC  | 0111011    | 3B  | ;    | 101101  |      | [    | 1111011 |       | [   |

| 0011100 | 1C  | FS   | 0111100    | 3C  | <    | 101110  | 0 5C | \    | 1111100 | 7C    | \   |

| 0011101 | 1D  | GS   | 0111101 31 | ) - | = 10 | 11101 : | 5D ] | 1    | 111101  | 7D    | }   |

| 0011110 | 1E  | RS   | 0111110    | 3E  | <    | 101111  | 0 5E | ^    | 1111110 | 7E    | ~   |

| 0011111 | 1F  | US   | 0111111    | 3F  | ?    | 101111  | 1 5F | -    | 1111111 | 7F    | DEL |

|         |     |      |            |     |      |         |      |      |         |       |     |

Table 1.4 American Standard Code for Information Interchange (ASCII)

**Universal Code or Unicode:** Unicode is a new 16-bit character-encoding standard for representing characters and numbers in most languages such as Greek, Arabic, Chinese and Japanese. The ASCII code uses eight bits to represent each character in Latin, and it can represent 256 characters. The ASCII code does not support mathematical symbols and scientific symbols. Since Unicode uses 16 bits it can represent 65536 characters or symbols. A character in Unicode is represented by 16-bit binary, equivalent to four digits in hexadecimal. For example, the character B in Unicode is U0042H (U represents Unicode). The ASCII code is represented between  $(00)_{16}$  to  $(FF)_{16}$ . For converting ASCII code to Unicode, two zeros are added to the left side of ASCII code; therefore, the Unicode to represent ASCII characters is between  $(0000)_{16}$  to  $(00FF)_{16}$ . Table 1.5 shows some of the Unicode for Latin and Greek characters. Unicode is divided into blocks of code, with each block assigned to a specific language. Table 1.6 shows each block of Unicode for some different languages.

| Latin     |            | Greek     | Greek      |  |

|-----------|------------|-----------|------------|--|

| Character | Code (Hex) | Character | Code (Hex) |  |

| А         | U0041      | φ         | U03C6      |  |

| В         | U0042      | α         | U03B1      |  |

| С         | U0043      | γ         | U03B3      |  |

| 0         | U0030      | μ         | U03BC      |  |

| 8         | U0038      | β         | U03B2      |  |

Table 1.5 Unicode values for some Latin and Greek characters

Table 1.6 Unicode block allocations

| Start Code(Hex) | End Code(Hex) | Block name       |

|-----------------|---------------|------------------|

| U0000           | U007F         | Basic Latin      |

| U0080           | U00FF         | Latin supplement |

| U0370           | U03FF         | Greek            |

| U0530           | U058F         | Armenian         |

| U0590           | U05FF         | Hebrew           |

| U0600           | U06FF         | Arabic           |

| U01A0           | U10FF         | Georgian         |

#### 1.6 Clock

0 and 1 continuously repeated is called clock as shown in Fig. 1.7.

Each cycle of clock consist of 1 and 0 and it is measured by time, if one cycle represented by T and unit of T is second then

F (Frequency) = 1/T the unit of frequency is Hertz (Hz) and unit of T is second Example: What is frequency of a clock if one cyle of the clock equal to 5 ms

$$F = 1/T = 1/0.5 \times 10^{-3} = 2000 \text{ Hz}$$

| 1000 Hz            | KHz (kilo Hertz) |

|--------------------|------------------|

| 10 <sup>6</sup> Hz | MHz (Mega Hertz) |

| 10 <sup>9</sup> Hz | GHz (Giga Hertz) |

Fig. 1.7 Clock signals

#### 1.7 Transmission Modes

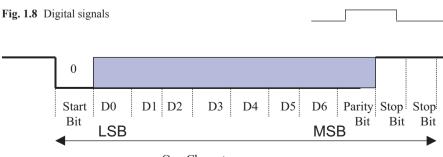

When data is transferred from one computer to another by digital signals, the receiving computer has to distinguish the size of each signal to determine when a signal ends and when the next one begins. For example, when a computer sends a signal as shown in Fig. 1.8, the receiving computer has to recognize how many ones and zeros are in the signal. Synchronization methods between source and destination devices are generally grouped into two categories; Asynchronous and synchronous.

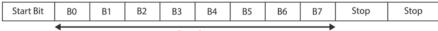

Asynchronous Transmission Asynchronous transmission occurs character by character and is used for serial communication, such as by a modem or serial printer. In asynchronous transmission each data character has a start bit which identifies the start of the character, and one or two bits which identifies the end of the character, as shown in Fig. 1.9. The data character is 7 bits. Following the data bits may be a parity bit, which is used by the receiver for error detection. After the parity bit is sent, the signal must return to high for at least one bit time to identify the end of the character is coming and allows the receiving side to synchronize its clock. Since the receiver and transmitter clock are not synchronized continuously, the transmitter uses the start bit to reset the receiver clock so that it matches the transmitter clock. Also, the receiver is already programmed for the number of bits in each character sent by the transmitter.

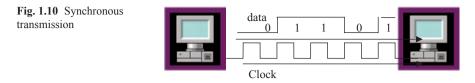

**Synchronous Transmission** Some applications require transferring large blocks of data, such as a file from disk or transferring information from a computer to a printer. **Synchronous transmission** is an efficient method of transferring large blocks of data by using time intervals for synchronization.

One method of synchronizing transmitter and receiver is through the use of an external connection that carries a clock pulse. The clock pulse represents the data rate of the signal, as shown in Fig. 1.10, and is used to determine the speed of data transmission. The receiver of Fig. 2.9 reads the data as 01101, each bit width represented by one clock.

One Character

Fig. 1.9 Asynchronous transmission

Figure 1.10 shows an extra connection is required to carry the clock pulse for synchronous transmission. In networking, one medium is used for transmission of both information and the clock pulse. The two signals are encoded in a way that the synchronization signal is embedded into the data. This can be done with Manchester encoding or Differential Manchester encoding.

#### 1.8 Transmission Methods

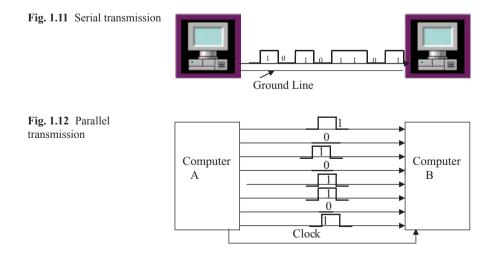

There are two types of transmission methods used for sending digital signals from one station to another across a communication channel: serial transmission and parallel transmission.

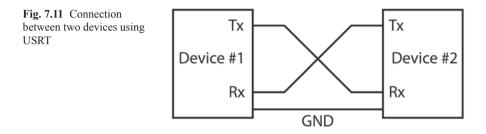

**Serial Transmission** In **serial transmission**, information is transmitted one bit at a time over one wire as shown in Fig. 2.11.

Ground Line (Fig. 1.11)

**Parallel Transmission** In **parallel transmission**, multiple bits are sent simultaneously, one byte or more at a time, instead of bit by bit as in serial transmission. Figure 1.12 shows how computer A sends eight bits of information to computer B at the same time by using eight different wires. Parallel transmission is faster than serial transmission, at the same clock speed.

#### **Problems and Questions**

- 1. Show an analog signal

- 2. Show a digital signal

- 3. Convert following decimal numbers to binary

- a. 35

- b. 85

- c. 23.25

- 4. Convert following binary numbers to decimal

- a. 1111101

- b. 1010111.1011

- c. 11111111

- d. 1000000

- 5. Convert following Binary numbers to Hexadecimal

- a. 1110011010

- b. 1000100111

- c. 101111.101

- 6. Convert following number to binary

- a. (3FDA)<sub>16</sub>

- b. (FDA.5F)<sub>16</sub>

- 7. Find two's complements of following numbers

- a. 11111111

- b. 10110000

- c. 1000000

- d. 0000000

- 8. Convert the word "LOGIC" to ASCII then represent each character in hex

- 9. Subtract following numbers using two's complement

- a. 11110011-11000011

- b. 10001101-11111000

- 10. List the types of transmission modes.

- 11. Why does a synchronous transmission require a clock?

- 12. What is frequency of an Analog signal repeated every 0.05 ms

#### Chapter 2 Logic Gates and Introduction to Computer Architecture

#### 2.1 Introduction

The basic components of an Integrated Circuit (IC) is logic gates which made of transistors, in digital system there are three basic logic operations and they are called AND, OR and NOT.

#### 2.2 Logic Gates

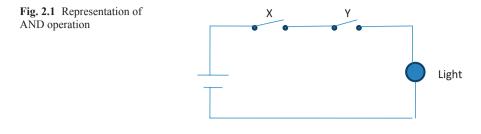

**AND Logic** The AND Logic is represented by ".". The most of the time, the period is left out. X.Y or XY is pronounced as X AND Y.

X AND Y = Z, Z = 1 if and only if X = 1 and Y = 1 otherwise Z = 0. The AND logic operation can represented by electrical circuit of Fig. 2.1.

Assume X and Y are switches and Z is the light, X=0, Y=0 means switches are open and light off means zero and light on means one, then we can make a Table 2.1 shows the operation of Fig. 2.1.

Figure 2.2 shows 2-Input AND gate and Table 2.2 show Truth table for AND gate. The output of AND gate is one when both inputs are one.

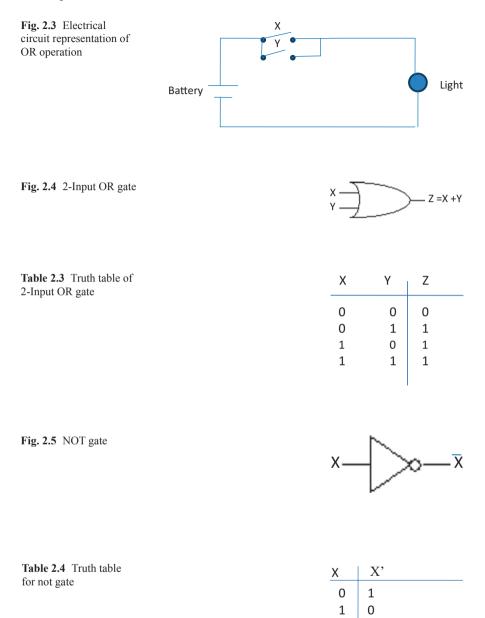

**OR Logic** The OR operation is represented by a+ or V, where + is the most popular symbol used. X+Y is pronounced X OR Y.

X + Y = Z, Z = 1 if X = 1 OR Y = 1 or both X = 1 and Y = 1.

This OR operation can be represented by the electrical circuit in Fig. 2.3. In Fig. 2.3, the light is off when both switches are off, and light is on when at least one switch is close. Figure 2.4 shows 2-Input OR gate and Table 2.3 shows truth table for 2-Input OR gate.

| Table 2.1         Operation of           Fig. 2.1         Fig. 2.1 | Х                      | Y                      | Light                   |

|--------------------------------------------------------------------|------------------------|------------------------|-------------------------|

|                                                                    | Off<br>Off<br>On<br>On | Off<br>On<br>Off<br>On | Off<br>Off<br>Off<br>On |

| Fig. 2.2 2-Input AND gate                                          | x<br>Y                 |                        | )—z=xy                  |

| Table 2.2       AND gate         truth table                       | Х                      | Y                      | Z                       |

|                                                                    | 0                      | 0                      | 0                       |

|                                                                    | 0<br>1                 | 1<br>0                 | 0<br>0                  |

**NOT Logic** The NOT logic performs a complement, meaning it converts a 1 to 0 and 0 to 1. Also called an inverter, the NOT X is represented by X' or  $\overline{X}$ . Figure 2.5 shows NOT gate and Table 2.4 shows truth table for NOT gate (Inverter)

**NAND Gate** Figure 2.6 shows 2-input NAND gate, The NAND gate can be made from an AND and a NOT gate as shown in Fig. 2.7, Table 2.5 shows truth table of 2-Input NAND gate

| Fig. 2.6 2-Input NAND gate                               |                                                                                                           |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Fig. 2.7 AND-NOT                                         | X Y                                                                                                       |

| Table 2.5       Truth table of         2-Input NAND      | X Y XY                                                                                                    |

|                                                          | $\begin{array}{cccc} 0 & 0 & 1 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 0 \end{array}$                        |

| Fig. 2.8 NOR gate                                        | $X \to X + Y$                                                                                             |

| Table 2.6       Truth table         for 2-Input NOR gate | $\begin{array}{c ccc} X & Y & X+Y \\ \hline 0 & 0 & 1 \\ 0 & 1 & 0 \\ 1 & 0 & 0 \\ 1 & 1 & 0 \end{array}$ |

**NOR Gate** Figure 2.8 shows a NOR logic gate. NOR gates are made of OR and NOT gates, Table 2.6 shows Truth table of 2-Input NOR gate.

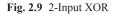

**Exclusive OR Gate** Figure 2.9 shows an exclusive OR gate. Exclusive OR is represented by  $\odot$  and labeled XOR and Table 2.7 shows truth table for XOR gate.

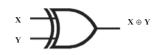

**Exclusive NOR Gate** Figure 2.10 shows an exclusive NOR gate. Exclusive NOR is represented by  $\odot$  and labeled XNOR and Table 2.8 shows Truth Table for Exclusive NOR gate.

Y

0

1

0

1

X⊕Y

0

1

1 0

Х

0

0

1

1

**Table 2.7** Truth tablefor XOR gate

**Table 2.8**Truth tablefor exclusive NOR gate

| Х | Y | $X \odot Y$ |

|---|---|-------------|

| 0 | 0 | 1           |

| 0 | 1 | 0           |

| 1 | 0 | 0           |

| 1 | 1 | 1           |

#### 2.3 Integrated Circuit (IC) Classification

A transistor is a basic component of Integrated Circuits (IC). The Fig. 2.11 shows a transistor with an IC. Transistors act like a switch in Integrated Circuits. An Integrated circuit is made from 100 to millions transistors.

Integrated circuit classified based on number of the gates such SSI, MSI, LSI and VLSI.

Small Scale Integration (SSI) SSI refers to an IC that has less than 10 gates.

**Medium Scale Integration (MSI)** Refers to an IC that contains between 10 and 100 gates such as Decoders and Multiplexers.

**Fig. 2.11** Transistor (*left*), IC (*right*)

**Large Scale Integration (LSI)** Refers to an IC that contains between 100 to 1000 gates.

**Very Large Scale integration (VLSI)** Refers to an IC that contains more than 1000 gates.

#### 2.4 Registers

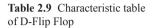

The registers are read/write memory that holds information inside the CPU. Each bit of a register is made of a D-flip flop as shown in Fig. 2.12 and Table 2.9 shows characteristic table for D-flip flop.

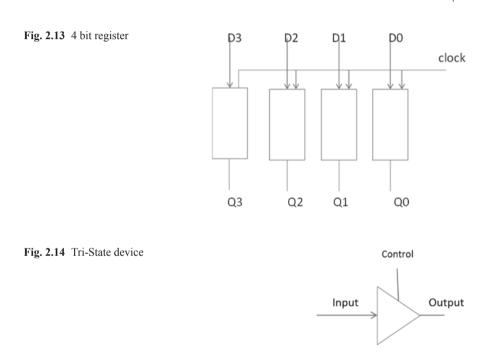

**D** Flip-Flop Operation As shown in Fig. 2.12, if the input of the flip flop is D=0 then by applying a clock pulse the output is set to zero. If D=1, applying a clock pulse sets the output to 1. The data will be stored in the flip-flop after applying a clock pulse. A register uses multiple D flip-flops that have a common clock pulse. Figure 2.13 shows 4 bit register.

If 32 D flip-flops use a common clock then it is called a 32-bit register.

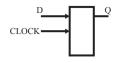

**Tri-State Device** Figure 2.14 shows the diagram of tri-state device, the control line controls the operation of tri state device.

In Fig. 2.14 if control line set to zero there is no connection between input and output. If control line set to one the output value is equal to the input value.

#### 2.5 Introduction to Computer Architecture

Just as the architecture of a building defines its overall design and functions, so computer architecture defines the design and functionality of a computer system. The components of a microcomputer are designed to interact with one another, and this interaction plays an important role in the overall system operation.

Fig. 2.12 D-Flip Flop

#### **Components of a Microcomputer** 2.5.1

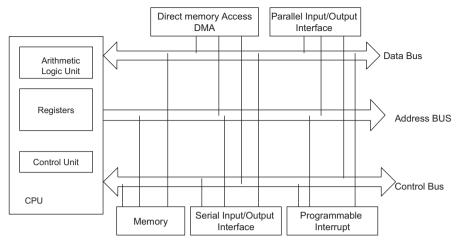

A standard microcomputer consists of a microprocessor (CPU), buses, memory, parallel input/output, serial input/output, programmable I/O interrupt and direct memory access DMA. Figure 2.15 shows components of microcomputer.

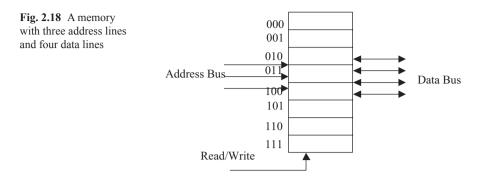

Central Processing Unit (CPU) The central processing unit (CPU) is the "brain" of the computer and is responsible for accepting data from input devices, processing the data into information, and transferring the information to memory and output devices. The CPU is organized into the following three major sections:

CLOCK DIQ CK

CK 1 1

0 0

Fig. 2.15 Components of a microcomputer

- 1. Arithmetic Logic Unit (ALU)

- 2. Control Unit

- 3. Registers

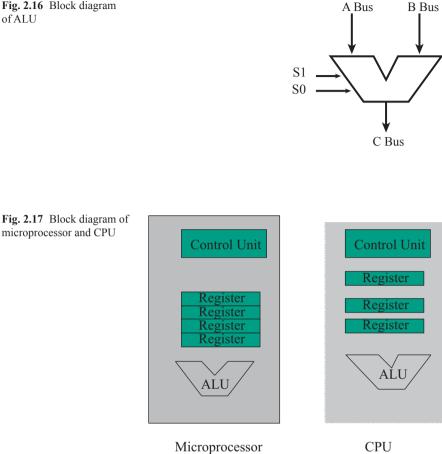

Arithmetic Logic Unit (ALU: The function of the Arithmetic Logic Unit (ALU) is to perform arithmetic operations such as addition, subtraction, division and multiplication, and logic operations such as AND, OR and NOT. Figure 2.16 shows block diagram of ALU

**Control Unit** The function of the **control unit** is to control input/output devices, generate control signals to the other components of the computer such as read and write signals, and perform instruction execution. Information is moved from memory to the registers; the registers then pass the information to the ALU for logic and arithmetic operations.

It should be noted that the function of the microprocessor and CPU are the same. If the control unit, registers and the ALU are packaged into one integrated circuit (IC), then the unit is called a microprocessor, otherwise the unit is called a CPU. The difference in packaging is shown in Fig. 2.17.

There are two types of technology used to design a CPU: Reduced Instruction Set Computer (RISC) and Complex Instruction Set Computer (CISC).

**CISC Architecture** In 1978, Intel developed the 8086 microprocessor chip. The 8086 was designed to process a 16-bit data word; it had no instruction for floating point operations. At the present time, the Pentium processes 32-bit and 64-bit words and it can process floating-point instructions. Intel designed the Pentium processor in such a way that it can execute programs written for earlier  $80 \times 86$  processors.

#### 2.5 Introduction to Computer Architecture

The characteristics of 80×86 are called Complex Instruction Set Computers (CISC), which include instructions for earlier Intel processors. Another CISC processor is VAX 11/780, which can execute programs for the PDP-11 computer. The CISC processor contains many instructions with different addressing modes, for example: the VAX 11/780 has more than 300 instructions with 16 different address modes.

The major characteristics of CISC processor are:

- 1. A large number of instructions

- 2. Many addressing modes

- 3. Variable length of instructions

- 4. Most instruction can manipulate operands in the memory

- 5. Control unit is microprogrammed

**RISC Architecture** Until the mid-1990s, computer manufactures were designing complex CPUs with large sets of instructions. At that time, a number of computer manufacturers decided to design CPUs capable of executing only a very limited set of instructions.

One advantage of reduced-instruction set computer is that they can execute their instructions very fast because the instructions are simple. In addition, the RISC chip requires fewer transistors then the CISC chip. Some of the RISC processors are the PowerPC, MIPS processor, IBM RISC System/6000, ARM and SPARC. The major characteristics of RISC processors are:

- 1. All instructions are the same length (they can be easily decoded)

- 2. Most instructions are executed in one machine clock cycle

- 3. Control unit is hardwired

- 4. Few address modes

- 5. A large number of registers

**Computer Bus** When more than one wire carries the same type of information, it is called a bus. The most common buses inside a microcomputer are the address bus, the data bus, and the control bus.

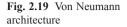

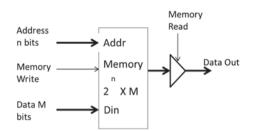

Address Bus The address bus defines the number of addressable locations in a memory IC by using the  $2^n$  formula, where n represents the number of address lines. If the address bus is made up of three lines then there are  $2^3 = 8$  addressable memory locations, as shown in Fig. 2.18. The size of the address bus directly determines the maximum numbers of memory locations that can be accessed by the CPU.

**Data Bus** The data bus is used to carry data to and from the memory and represents the size of each location in memory. In Fig. 2.14 each location can hold only four bits. If a memory IC has eight data lines, then each location can hold eight bits. The size of a memory IC is represented by  $2n \times m$  where n is the number of address lines and m is the size of each location. In Fig. 3.3, where n=3 and m=4, the size of the memory is:

$$2^3 * 4 = 32$$

bits

**Control Bus** The control bus carries control signals from the control unit to the computer components in order to control the operation of each component. In addition, the control unit receives control signals from computer components. Some of the control signals are as follows:

**Read signal** The read signal is used to read information from memory or input/ output (I/O) devices.

Write signal The write line is used to write data into the memory.

Interrupt Indicates an interrupt request.

**Bus request** The device is requesting to use the computer bus.

Bus Grant Gives permission to the requesting device to use the computer bus.

I/O Read and Write I/O read and write is used to read from or write to I/O devices.

#### 2.5.2 CPU Architecture

There are two types of CPU architecture and they are:

#### a. Von Neumann Architecture

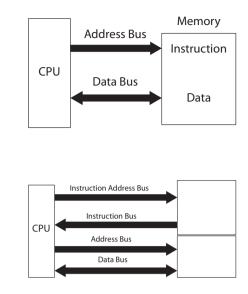

A program is made of code (instructions) and data. Figure 2.19 shows a block diagram of the Von Neumann Architecture. Von Neumann uses the data bus to transfer data and instructions from the memory to the CPU.

#### b. Harvard Architecture

Harvard Architecture uses separate buses for instructions and data as shown in Fig. 2.20. The instruction address bus and instruction bus are used for reading instructions from memory. The address bus and data bus are used for writing and reading data to and from memory.

#### 2.6 Memory

In general, memory can hold information either temporarily or permanently. The following are some types of memory:

- Semiconductor Memory or Memory IC

- Floppy disk and Hard disk

- Tape

- CD ROM (Compact Disk-Read Only Memory)

- Flash ROM

Fig. 2.20 Harvard

architecture

**Semiconductor Memory** There are two types of **semiconductor memory**: Random Access Memory (RAM) and Read only Memory (ROM).

*Memory* Memory holds instruction and data. Figure 2.21 shows the block diagram of memory unit.

Memory is defined by the number of address lines it has (n) and size of each of its locations (M). The size of a memory is defined by  $2^n \times M$ .

Memory requires two control signals and they are:

**Memory Write** CPU writes data into memory by placing an address on the address bus and data on the data bus then activating the memory write signal. The data will then be stored in the specified memory location.

**Memory Read** CPU places the address on address bus and activates memory read signal. The data stored in memory is then placed on the data bus.

Data can be read from or written into **Random Access Memory (RAM)**. The RAM can hold the data as long as power is supplied to it.

There are many types of RAM, such as **Dynamic RAM (DRAM)**, **Synchronous DRAM (SDRAM)**, **EDO RAM, DDR SDRAM, RDRAM**, and **Static RAM (SRAM)**.

Dynamic RAM (DRAM) is used in main memory. It needs to be refreshed (recharged) about every 1 ms. The CPU cannot read from or write to memory while the DRAM is being refreshed—this makes DRAM the slowest running memory. A DRAM comes in different types of packaging such as the SIMM (Single In-Line Memory Module) and the DIMM (Dual In-Line Memory Module). The SIMM is a small circuit board that holds several chips. It has a 32-bit data bus.

Fig. 2.21 Block diagram of a memory

The DIMM is a circuit board that holds several memory chips. A DIMM has a 64-bit data bus.

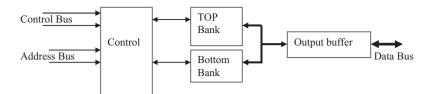

• Synchronous DRAM (SDRAM) technology uses DRAM and adds a special interface for synchronization. It can run at much higher clock speeds than DRAM. SDRAM uses two independent memory banks. While one bank is recharging, the CPU can read and write to the other bank. Figure 2.22 shows a block diagram of SDRAM.

Extended Data Out RAM (EDORAM) transfers blocks of data to or from memory.

- **Double Data Rate SDRAM (DDR SDRAM)** is a type of SDRAM that transfers data at both the rising edge and the falling edge of the clock.

- **Rambus DRAM (RDRAM)** was developed by Rambus corporation. It uses multiple DRAM banks with a new interface that enables DRAM banks to transfer multiple words and also transfer data at the rising edge and the falling edge of clock. The RDRAM refreshing is done by the interface. The second generation of RDAM is called DRDRAM (Direct RDRAM) and it can transfer data at a rate of 1.6 Gbps. Figure 2.23 shows a RDRAM module.

**DRAM Packaging** DRAM comes in different types of packaging such as: SIMMs (Single In-Line Memory Module) and DIMM (Dual-in Line Memory Module).

Figure 2.24 shows SIMM, which is a small circuit board that holds several chips. It has a 32 bit data bus.

DIMM is a circuit board that also holds several memory chips, but has a 64 bit data bus.

- Static RAM (SRAM) is used in cache memory. SRAM is almost twenty times faster than DRAM and is also much more expensive.

- ROM (Read Only Memory)

Like its name suggest, information can be ready only from **Read Only Memory** (**ROM**). ROM holds information permanently, even while there is no power to the ROM. Two types of ROM are listed below:

Fig. 2.22 Block diagram of SDRAM

Fig. 2.23 Rambus memory module. (Courtesy Samsung Corp)

Fig. 2.24 DRAM SIMM

- Erasable Programmable Read Only Memory (EPROM): EPROM can be erased with ultraviolet light and reprogrammed with a device called an EPROM programmer. Flash ROM is a type of EEPROM.

- Electrically Erasable PROM (EEPROM): EEPROM can be erased by applying specific voltage to one of the pins and can be reprogrammed with an EPROM programmer.

- Flash Memory: Flash memory is a type of EEPROM that allows multiple memory location to be written or erased one operation but EEPROM only one memory location at a time to be erased or written

### 2.7 Multiplexer and Decoder

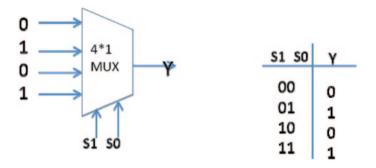

**Multiplexer (MUX)** Multiplexer has n inputs and one ouytput, Fig. 2.25 showes a 2\*1 MUX, if S=0 the outpout is A and if S=1 then output is B.

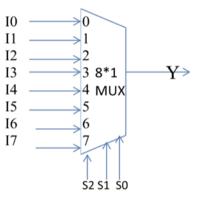

Figure 2.26 shows 8\*1 mux and Table 2.10 shows the function of multiplexer, S2 S1 S0 seclet the input to the MUX.

**Decoder** The function of decoder is to generate minterms of input at the ouput of decoder.

Fig. 2.25 2\*1 MUX

A 2\*4 decoder has 2 inputs and 4 outputs, outputs represent minterms of inputs Fig. 2.27 shows a block diagram of 2\*4 decoder and Table 2.11 shows truth table of 2\*4 decoder.

B

$\rightarrow 1$

S

Fig. 2.26 8\*1 MUX

| <b>Table 2.10</b> | Operation of |

|-------------------|--------------|

| 8*1 MUX           |              |

| S2 S1 S0 | Y  |

|----------|----|

| 000      | 10 |

| 001      | 11 |

| 010      | 12 |

| 011      | 13 |

| 100      | 14 |

| 101      | 15 |

| 110      | 16 |

| 111      | 17 |

→ output

| Fig. 2.27 | Block | diagram |

|-----------|-------|---------|

| of 2*4 De | coder |         |

|    |         | →X'Y'=m0 |

|----|---------|----------|

| Х> | 2*4     | →X'Y=m1  |

| Y→ | Decoder | →XY'=m2  |

|    |         | →XY=m3   |

| Table 2.11  | shows    |

|-------------|----------|

| decoder tru | th table |

| <u>X Y</u> | m0 | m1 | m2 | m3 |

|------------|----|----|----|----|

| 00         | 1  | 0  | 0  | 0  |

| 01         | 0  | 1  | 0  | 0  |

| 10<br>11   | 0  | 1  | 0  | 0  |

| 11         | 0  | 0  | 0  | 1  |

#### **Short Answer Questions**

- 1. List the components of a microcomputer.

- 2. Explain the functions of a CPU.

- 3. List the functions of an ALU.

- 4. What is the function of a control unit?

- 5. What does RAM stand for?

- 6. What is SRAM? discuss its applications

- 7. Define DRAM and SDRAM and explain their applications.

- 8. Explain the function of an address bus and a data bus.

- 9. What does IC stand for?

- 10. What is the capacity of a memory IC with 10 address lines and 8 data buses?

- 11. What is ROM?

- 12. What does EEPROM stand for, and what is its application?

- 13. What does RDRAM stand for?

- 14. What is SIMM?

- 15. Explain the function of cache memory and give its location.

- 16. What is the application of a parallel port?

- 17. What is the application of a serial port?

- 18. Explain the difference between CISC processors and RISC processors

Explain difference between Von Neumann and Harvard Architecture.

#### Problems

1. If A=11001011 and B=10101110 then, what is the value of following operation

- a. a. A AND B

- b. b. A OR B

2. If A=11001011 and B=10101110, what is the value of following Operations

- a. A NOT

- b. A XOR B

- c. A AND 0F

- d. A AND F0

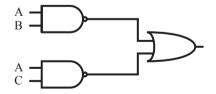

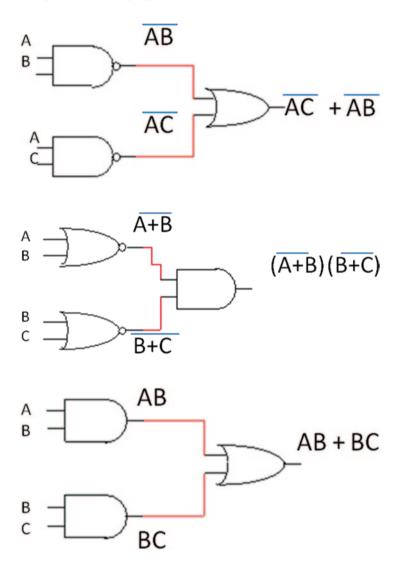

- 3. Draw logic circuit for following functions

A. F(X,Y,Z) = X'Y' + XZ'

B.F(X,Y,Z) = (X + Y)(X + Z)

4. Find the truth table for following function

F(X,Y,Z) = XY' + YZ' + XZ'

- 5. If A=10110110 and B=0110110011, then find

- a. A. A NAND B

- b. B. A NOR B

- c. C. A XOR B

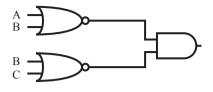

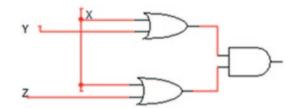

- 6. Show output of following logic circuits

Β.

C.

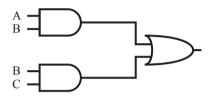

### 7. Following multiplexer is given show the output

## Chapter 3 ARM Instructions Part I

### 3.1 Introduction

Advanced RISC Machine (ARM) was developed by the Acorn Company. ARM is a leader supplier of microprocessors in the world, ARM develop the core CPU and thousand of suppliers add more functional units to the core. ARM uses two types instruction called Thumb and Thumb-2. Thumb instructions are 16 bits and thumb-2 instructions are 32 bits, currently most ARM processors uses 32 bit instructions.

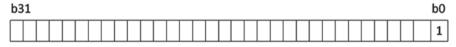

ARM contains 15 registers called R0 through R15, R0 and R12 called general propose registers. ARM able to execute Thumb instructions (16 bit instructions) and Thumb-2 32 bits instruction, Thumb instructions use on R0 through R7 registers.

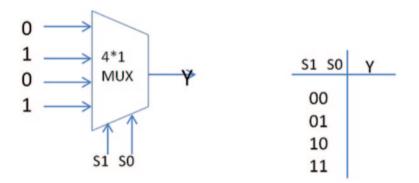

ARM is intended for applications that require power efficient processors, such as Telecommunications, Data Communication (protocol converter), Portable Instrument, Portable Computer and Smart Card. ARM is basically a 32-bit RISC processor (32-bit data bus and address bus) with fast interrupt response for use in real time applications. A block diagram of ARM7 processor is shown in Fig. 3.1.

**Instruction Decoder and Logic Control:** The function of instruction decoder and logic control is to decode instructions and generate control signals to other parts of processor for execution of instructions.

Address Register: To hold a 32-bit address for address bus.

Address Increment: It is used to increment an address by four and place it in address register.

**Register Bank:** Register bank contains thirty-one 32-bit registers and six status registers.

Barrel Shifter: It is used for fast shift operation.

ALU; 32-bit ALU is used for Arithmetic and Logic Operation.

Fig. 3.1 Block diagram of ARM7 architecture

Write Data Register: The processor put the data in Write Data Register for write operation.

**Read Data Register:** When processor reads from memory it places the result in this register.

#### ARM Operation Mode: ARM can operates in one of the following mode:

- 1. User Mode: Use for normal operation.

- 2. IRQ Mode: This Interrupt mode is designed for handling interrupt operations.

- 3. Supervisory Mode: Used by operating system.

- 4. FIQ Mode: Fast Interrupt mode.

#### Fig. 3.2 User

| Z       | С          | V  | Unused | Ι | F        | Т      | M4 | M3 | M2 | M1  | M0 |

|---------|------------|----|--------|---|----------|--------|----|----|----|-----|----|

| 30      | 29         | 28 | 27     | 7 | 6        | 5      |    | 3  |    |     | 0  |

|         |            |    |        |   |          |        |    |    |    |     |    |

|         |            |    |        |   | R1       | 5 (PC) |    |    | Cl | PSR |    |

|         |            |    |        |   | R1       |        |    |    |    |     |    |

|         |            |    |        |   | R1       |        |    |    |    |     |    |

|         |            |    |        |   | R1       |        | _  |    |    |     |    |

|         |            |    |        |   | R1       |        | _  |    |    |     |    |

|         |            |    |        |   | R9<br>R1 |        | _  |    |    |     |    |

|         |            |    |        |   | R8       |        | _  |    |    |     |    |

|         |            |    |        |   | R7       |        |    |    |    |     |    |

|         |            |    |        |   | R6       |        |    |    |    |     |    |

|         |            |    |        |   | R5       |        |    |    |    |     |    |

|         |            |    |        |   | R4       |        |    |    |    |     |    |

|         |            |    |        |   | R3       |        |    |    |    |     |    |

|         |            |    |        |   | R2       |        |    |    |    |     |    |

|         |            |    |        |   | R1       |        |    |    |    |     |    |

|         |            |    |        |   | R0       |        |    |    |    |     |    |

| ser moo | de registe | rs |        |   | 31       |        | 0  |    |    |     |    |

Fig. 3.3 Storage format for CPSR

31

Ν

- 5. Undefined Mode: When an undefined instruction executed.

- 6. Abort Mode: This mode indicates that current memory access cannot be completed, such as when data is not in memory and processor require more time to access disk and transfer block of data to memory.

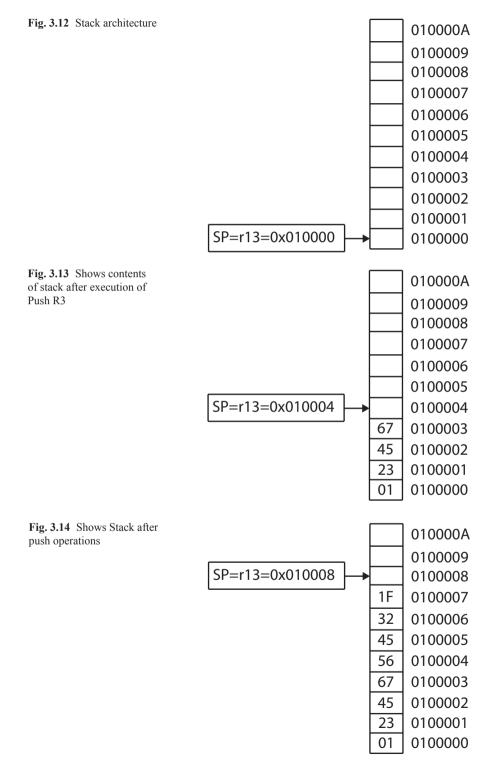

**ARM Registers:** ARM7 has 31 general registers and 6 status registers. At user mode only 16 registers and one Program Status Register (PSR) are available to programmers. The registers are labeled R0 through R15. R15 is used for Program Counter (PC), R14 is used for Link Register and R13 is used for Stack Pointer (SP). Figure 3.2 shows user mode registers.

Current Program Status Register (CPSR): Figure 3.3 shows the format of PSR. This register is used to store control bits and flag bits. The flag bits are N, Z, C and V, and the control bits are I, F, and M0 through M4. The flag bits may be changed during a logical, arithmetic and compare operation.

Flag Bits N (negative): N=1 means result of an operation is negative and N=0means result of an operation is positive.

Z (zero): Z=1 means result of an operation is zero and Z=0 result of an operation is not zero.

C (carry): C=1 means result of an operation generated a carry, and C=0 means result of an operation did not produce a carry.

*V* (overflow): V=1 means result of an operation generated an overflow and V=0 means result of an operation did not generate an overflow.

**Control Bits** *I* (*interrupt bit*): When this bit set to one, it will disable the interrupt and this means the processor does not accept any software interrupt.

F bit is used to disable and enable fast interrupt request mode (FIQ) mode.

M4, M3, M2, M1 and M0 are mode bits and they are equal to 10000 for user mode.

T (State bit): T=1 Processor executing thumb instructions, T=0 processor executing ARM instructions

#### **3.2** Instruction Set Architecture (ISA)

Manufacturers of CPUs publish a document that contains information about the processor such as list of registers, function of each register, size of data bus, size of address bus and list of instructions that can be executed by the CPU. Each CPU has a known instruction set that a programmer can use to write assembly language programs. Instruction sets are specific to each type of processor. That being said, Pentium processors use a different instruction set than ARM processors. The Instructions are represented in *mnemonic* form means abbreviation, for example, the Addition instruction represented by "ADD" Subtraction instruction represent by "SUB" for example, the addition instruction is represented by

ADD R1, R2, R3; means add contents of R2 with R3 and store results in R1. R1, R2, and R3 are called operands

#### A. Classification of Instruction base on number of operands

**No Operand Instructions**: The following are some of the instructions that do not require any operands:

HLT-Halt the CPU

**NOP**—No operation

PUSH operand: Push operand into top of the stack

**POP operand**: Remove the operand from top of the stack

**One Operand Instructions:** The following are some of the instructions that require one operand.

INC operand Example: INC R1 - Increment register R1 by 1 DEC operand Example: DEC R1 - Decrement register R1 by 1 J target Jump to memory location labeled by target ADD operand Add operand to the accumulator (ACC) ACC + ACC + operand **Two Operand Instructions:** The following are some of the instructions that require two operands:

ADD Rd, Rn Example: ADD R1, R2-R1  $\leftarrow$  R1+R2 Intel Instruction Set Architecture uses two operands. MOV EAX, EBX ; EAX  $\leftarrow$  EBX

**Three Operand Instructions:** Most modern processors use instructions with three operands, such ARM, MIPS and Itanium.

ADD R1, R2, R3 ; R1 🗲 R2 +R3

### 3.3 ARM Instructions

ARM Architecture support Thumb 16 bit and Thumb-2 32 bit instruction set. Most of the ARM instructions use three operands. These instructions are classified based on their instructions format and are listed as followings:

- A. Data Processing Instructions

- B. Single Data Swap

- C. Shift and Rotate Instructions

- D. Unconditional Instructions and Conditional Instructions:

- E. Stack Operations

- F. Branch

- G. Multiply Instructions

- E: Data Transfer

### 3.3.1 Data Processing Instructions

The data processing instructions are as follows: AND, EOR, SUB, RSB, ADD, ADC, SBC, RSB TST, TEQ, CMP, CMN, ORR, MOV, BIC and MNW. Data processing instructions use register operands and immediate operand. The general format of Data processing instructions is

Mnemonic {S}{Condition} Rd, Rn, operand2 Mnemonic: Mnemonic is abbreviation of an operation such as ADD for addition

{}: Commands inside the { } is optional such as S and condition

**S:** When an instruction contains S mean update the Processor Status Register (PSR) flag bits

Condition: Condition define the instruction will executed if meet the conditionRd is destination registerRn: Rn is operand1Operand2: Operand2 can be register or immediate value

**A. Registers Operands:** The operands are in registers. First register is destination register, second register is operand1 and third register is operand2.

Following are Arithmetic and Logic operations Instructions with register operands

| ADD R0, R1, R2  | ;R0=R1+R2 Add contents of register R1 with<br>register R2 and place the result in<br>register R0.                               |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------|

| ADC R0, R1, R2; | ;R0 = R1+R2 +C Add with carry C is carry bit.                                                                                   |

| SUB R0, R2, R3  | ;R0=R2-R3 where R2 is first operand and R3 is second operand                                                                    |

| SBC R0, R2, R3; | ;R0=R2-R3+C-1 SUB with carry.                                                                                                   |

| RSB R0, R2, R5  | ;R0= R5-R2 Reverse SUB.                                                                                                         |

| RSC R0, R2, R5  | ;R0=R5-R2+C-1 Reverse sub with carry.                                                                                           |

| AND R0, R3, R5  | ;R0= R3 AND R5.                                                                                                                 |

| ORR R7, R3, R5; | ;R7=R3 OR R5.                                                                                                                   |

| EOR R0, R1, R2  | ;R0 = R1 Exclusive OR with R2.                                                                                                  |

| BIC R0, R1, R2  | ;Bit clear. The one in second operand clears corresponding bit in first operand and stores the results in destination register. |

**B. Immediate Operand:** In immediate operand, operand2 is an immediate value and maximum can be 12 bits

| ADD R1, R2, #0x25 | ;R1=R2+&25, # means immediate and & means |

|-------------------|-------------------------------------------|

|                   | the immediate value is in hexadecimal.    |

| AND R2, R3, #0x45 | ;R2 = R3 AND &45.                         |

| EOR R2, R3, #0x45 | ;R2 = R3 Exclusive OR &45.                |

**Example 3.2:** What is contents of R1 after executing following instruction, assume R2 contains 0x12345678

```

ADD R1, R2, #0x345

```

The ADD instruction will add contains of R2 with 0x2345 and store the result in R1, then R1=0x123459BD

**Setting Flag Bits of PSR:** The above instructions do not affect the flag bit of PSR because the instructions do not have option S. By adding suffix S to the instruction, the instruction would affect the flag bit.

ADDS R1, R2, R3 ;The suffix S means set appropriate flag

bit.

SUBS R1, R2, R2; ;The will set zero flag to 1.

**Compare and Test Instructions:** ARM processor uses the compare and test instructions to set flag bits of PSR and following are Compare and Test instructions

**CMP, CMN, TST, and TEQ:** These instruction uses two operands for compare and test, the result of their operations do not write to any register

**CMP Instruction (Compare Instruction):** The CMP instruction has following format

**CMP Operand 1, Operand2:** The CMP instruction compares Operand1 with Operand2, this instruction subtract Operand2 from Operand 1 and sets the appropriate flag. The flag bit set based on the result of the operation as follow

Z flag set if Operand2 equal operand 1N flag is set if operand1 less than operand2C flag is set if result of operation generate carry

**Example 3.4:** Assume R1 contains 0x00000024 and R2 contains 0x00000078, the operation CMP R1, R2 will set N flag to 1

CMP Rd, immediate value, the immediate value can be 8 bits such as CMP R1, #0xFF CMN Compare Negate: The CMN has following format

**CMN Operand1, Operand2:** The instruction will add operand1 with operand 2 and set appropriate flag bit

**Example 3.5:** Assume R1 contains 0x00000024 and R2 contains 0x13458978, the operation CMN R1, R2 with result carry and set C flag to 1.

TST (Test Instruction): The test instruction has following format

**TST Oprand1, Operand2:** The Test Instruction performs AND operation between operand1 and Operand2 and set appropriate flag bit. The operand to can be immediate value or Register such as

| TST R1, R2           |              | instructior<br>ion and sets | •          |          |         | R2 |

|----------------------|--------------|-----------------------------|------------|----------|---------|----|

| OR                   |              |                             |            |          |         |    |

| TST R1, immediate, t | ho immo      | diato valuo                 | can bo 9 k | ite cue  | h ac    |    |

| ISI KI, Immediate, t | .110 1111110 | ulace value                 |            | JILS SUC |         |    |

| TST R1, 0xFF         |              |                             |            |          |         |    |

|                      |              |                             |            |          |         |    |

| TEQ R1, R2           | This         | instruction                 | nerforms   | R1 Fx    | clusive | OR |

|                      | R2.          | 1115 CF UC C1011            |            |          | 0100100 | on |

If R1 equal to R2 then Z flag set to one

### 3.4 Register Swap Instructions (MOV and MVN)

The register swap instructions has following general formats

A. MOV{S} {condition} Rd, Rm; Move the contents of Rm to Rd

**Example 3.6:** What is contents of R1 after Execution of following instruction Assume R2 contains 0X0000FFFF

a. MOV R1, R2;R1 ← R2 R2=0x0000FFFF

b. MVN R1, R2; R1 ← NOT R2 R2= 0xFFFF0000

#### MOV{S}{condition} Rd, immediate value

Immediate value is 16 bits, The range of immediate value if from 0x00000000 to 0x0000FFFF

Example 3.7: MOV R2, # 0x45, the contents of R2 will be 0x00000045

MOV Rn, Rm, lsl # n ; shift Rm n times to the left and store the result Rn

#### **Conditional MOV**

MOVEQ R2, 0x56 ; if zero bit is setthen executes MOVEQ

#### 3.5 Shift and Rotate Instructions

ARM combined the Rotate and Shift operation with other Instructions, the ARM processor performs following shift operations

| LSL | Logical Shift Left     |

|-----|------------------------|

| LSR | Logical Shift Right    |

| ASR | Arithmetic Shift Right |

| ROR | Rotate Right           |

**Logical Shift Left (LSL):** In logical shift left operations each bit of register shifted to the left as shown in Fig. 3.4 and a zero will placed in the least significant bit, the logical shift left multiply the contents of register by 2.

LSL R1, R1, n; shift to left R1 n times and store result in R1

Fig. 3.4 Logical shift left

Fig. 3.5 Logical Shift Left

**Example 3.8:** What is contents of R1 after executing following Instruction, assume R1 contains 0x00000500.

# LSL R1, R1, 8

R1 = 0x00050000

**Logical Shift Right (LSR):** In logical shift right operations each bit of register shifted to the right as shown in Fig. 3.5 and a zero will placed in the most significant bit, the logical right divides the contents of register by 2.

$LSR \ R1, \ R1, \ n$  ;shift to right R1 n times and store result in R1

**Example 3.9** What is contents of R1 after executing following Instruction, assume R1 contains 0x00000500.

LSR R1, R1, 4 R1= 0x0000050

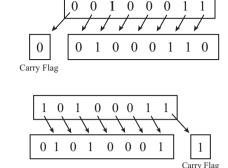

Arithmetic Shift Right (ASR): In Arithmetic shift right the most significant bit does not change and each bit shifted to the right as shown in Fig. 3.6.

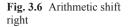

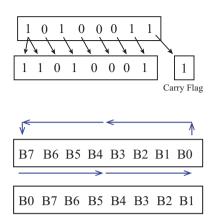

**Rotate Right:** Figure 3.7 shows an eigth bit rgister and Fig. 3.7 shows the regiter after rotating one times

44

Fig. 3.7 Rotate right operation

**Example 3.10** What is content of R1 after rotating 16 times, assum R1 contains 0x0000FFFF

ROR R1, R1 , #16 R1= 0xFFFF0000

ARM combines data processing instructions and shift operation, shift operation is applied to the second operand of the instruction.

**Example 3.11:** Register R2 containes 0xEEEEFFFF, by executing

MOV R1, R2, ROR # 16 ;the R2 rotate 16 times and store results in R1

by rotating 16 times the contains of R1 will be 0xFFFFEEE

ADD R1, R2, R3, LSL #4 ;R1= R2 + R3 x 2<sup>4</sup>, R3 is shifted 4 times to the left and result is added to R3 and placed in R1.

Also a register can hold number of times the operand2 must be shifted.

```

ADD R1, R2, R3, LSL R4 ;R1= R2 + R3 X 2<sup>R4</sup>, Number of times R3 to be shifted is in R4.

```

```

MOV R0, R1, LSL #3 ;Shift R1 to the left three times and move the result to R0.

```

# **3.6 ARM Unconditional Instructions and Conditional Instructions**

Figure 3.8 shows the general format of an ARM instruction. ARM instruction defines two types of instructions, namely:

- 1. Unconditional Instruction

- 2. Conditional Instruction

Condition code defines the type of conditions. If this field is set to 1110 then the instruction is an unconditional instruction, otherwise the instruction is a conditional instruction. To use an instruction as a conditional instruction, the condition will suffix to the instruction. The suffixes are:

| Condition Code | Condition   |                               |

|----------------|-------------|-------------------------------|

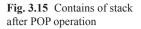

| 0000           | EQ          | Equal                         |