Advances in Intelligent Systems and Computing 305

Rituparna Chaki Khalid Saeed Sankhayan Choudhury Nabendu Chaki *Editors*

# Applied Computation and Security Systems

## **Advances in Intelligent Systems and Computing**

Volume 305

#### Series editor

Janusz Kacprzyk, Polish Academy of Sciences, Warsaw, Poland e-mail: kacprzyk@ibspan.waw.pl

#### About this Series

The series "Advances in Intelligent Systems and Computing" contains publications on theory, applications, and design methods of Intelligent Systems and Intelligent Computing. Virtually all disciplines such as engineering, natural sciences, computer and information science, ICT, economics, business, e-commerce, environment, healthcare, life science are covered. The list of topics spans all the areas of modern intelligent systems and computing.

The publications within "Advances in Intelligent Systems and Computing" are primarily textbooks and proceedings of important conferences, symposia and congresses. They cover significant recent developments in the field, both of a foundational and applicable character. An important characteristic feature of the series is the short publication time and world-wide distribution. This permits a rapid and broad dissemination of research results.

#### Advisory Board

#### Chairman

Nikhil R. Pal, Indian Statistical Institute, Kolkata, India e-mail: nikhil@isical.ac.in

#### Members

Rafael Bello, Universidad Central "Marta Abreu" de Las Villas, Santa Clara, Cuba e-mail: rbellop@uclv.edu.cu

Emilio S. Corchado, University of Salamanca, Salamanca, Spain e-mail: escorchado@usal.es

Hani Hagras, University of Essex, Colchester, UK e-mail: hani@essex.ac.uk

László T. Kóczy, Széchenyi István University, Győr, Hungary e-mail: koczy@sze.hu

Vladik Kreinovich, University of Texas at El Paso, El Paso, USA e-mail: vladik@utep.edu

Chin-Teng Lin, National Chiao Tung University, Hsinchu, Taiwan e-mail: ctlin@mail.nctu.edu.tw

Jie Lu, University of Technology, Sydney, Australia e-mail: Jie.Lu@uts.edu.au

Patricia Melin, Tijuana Institute of Technology, Tijuana, Mexico e-mail: epmelin@hafsamx.org

Nadia Nedjah, State University of Rio de Janeiro, Rio de Janeiro, Brazil e-mail: nadia@eng.uerj.br

Ngoc Thanh Nguyen, Wroclaw University of Technology, Wroclaw, Poland e-mail: Ngoc-Thanh.Nguyen@pwr.edu.pl

Jun Wang, The Chinese University of Hong Kong, Shatin, Hong Kong e-mail: jwang@mae.cuhk.edu.hk

More information about this series at http://www.springer.com/series/11156

Rituparna Chaki · Khalid Saeed Sankhayan Choudhury · Nabendu Chaki Editors

## Applied Computation and Security Systems

Volume Two

*Editors* Rituparna Chaki A.K. Choudhury School of Information Technology University of Calcutta Kolkata, West Bengal India

Sankhayan Choudhury Nabendu Chaki Department of Computer Science and Engineering University of Calcutta Kolkata, West Bengal India

Khalid Saeed Faculty of Physics and Applied Computer Sciences AGH University of Science and Technology Cracow Poland

ISSN 2194-5357 ISSN 2194-5365 (electronic) ISBN 978-81-322-1987-3 ISBN 978-81-322-1988-0 (eBook) DOI 10.1007/978-81-322-1988-0

Library of Congress Control Number: 2014947644

Springer New Delhi Heidelberg New York Dordrecht London

© Springer India 2015

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law. The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

## Preface

The First International Doctoral Symposium on Applied Computation and Security Systems (ACSS 2014) took place during Apr 18–20, 2014 in Kolkata, India. This symposium is aimed to facilitate the Ph.D. students to present and discuss their research work leading towards high-quality dissertation. This symposium will provide a friendly and supportive environment for doctoral students to present and discuss their work both with their peers and with a panel of distinguished experts. ACSS Doctoral Symposium allowed researchers working in different fields of computer science such as Image processing, Remote Healthcare, Biometrics, Pattern Recognition, Embedded Systems, Data Mining, Software Engineering, Networking, and Network Security. The symposium evolved as a joint venture between two collaborative universities: the University of Calcutta, India, and the AGH University of Science and Technology, Poland.

The program committee members of ACSS 2014 were instrumental in disseminating the objectives of the symposium among the scholars and faculty members in a very short time. This resulted in a large number of submissions from Ph.D. scholars from India and abroad. These papers underwent a minute and detailed blind-review process with voluntary participation of the committee members and external expert reviewers. The metrics for reviewing the papers had been mainly the novelty of the contributions, technical content, organization, and clarity in presentation. The entire process of initial paper submission, review, and acceptance were done electronically. The hard work done by the Organizing and Technical Program Committees led to a superb technical program for the symposium. The ACSS 2014 resulted in high-impact and highly interactive presentations by the doctoral students.

The Technical Program Committee for the symposium has selected only 25 papers for publication out of a total 70 submissions. Session chairs were entrusted with the responsibility of submitting feedbacks for improvements of the papers presented. The symposium proceeding has been organized as a collection of papers, which were presented and then modified as per reviewer's and session chair's comments. This has helped the scholars to further improve their contributions.

We would like to take this opportunity to thank all the members of the Technical Program Committee and the external reviewers for their excellent and time-bound review works. We especially thank Prof. Indranil Sengupta of IIT, Kharagpur for his suggestions towards designing the Technical Program for ACSS-2014. We thank all our sponsors who have come forward towards organization of this symposium. These include Tata Consultancy Services (TCS), Springer India, ACM India, M/s Business Brio, M/s Enixs. We appreciate the initiative and support from Mr. Aninda Bose and Ms. Kamiya Khatter his colleagues in Springer for their strong support towards publishing this post-symposium book in the series "Advances in Intelligent Systems and Computing." Last, but not the least, we thank all the authors without whom the symposium would not have reached up to this standard.

On behalf of the editorial team of ACSS 2014, we sincerely hope that the different chapters of this book will be beneficial to all its readers and motivate them towards further research.

Rituparna Chaki Khalid Saeed Sankhayan Choudhury Nabendu Chaki

## Contents

#### Part I Software Engineering

| Non-functional Property Aware Brokerage Approach             |    |

|--------------------------------------------------------------|----|

| for Cloud Service Discovery                                  | 3  |

| Adrija Bhattacharya and Sankhayan Choudhury                  |    |

| A DWT-based Digital Watermarking Scheme for Image Tamper     |    |

| Detection, Localization, and Restoration.                    | 17 |

| Sukalyan Som, Sarbani Palit, Kashinath Dey, Dipabali Sarkar, |    |

| Jayeeta Sarkar and Kheyali Sarkar                            |    |

| Service Insurance: A New Approach in Cloud Brokerage         | 39 |

| Adrija Bhattacharya and Sankhayan Choudhury                  |    |

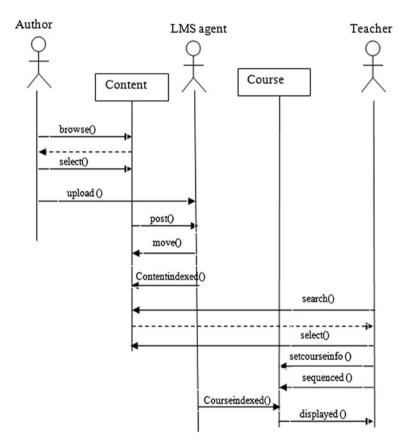

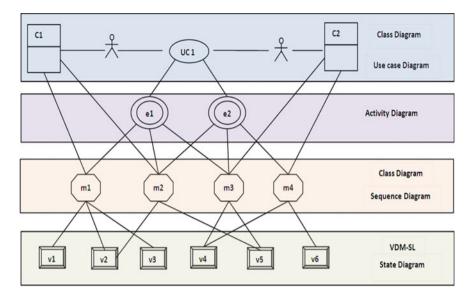

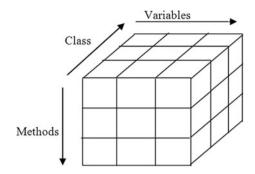

| Using Semiformal and Formal Methods in Software Design:      |    |

| An Integrated Approach for Intelligent Learning              |    |

| Management System                                            | 53 |

| Souvik Sengupta and Ranjan Dasgupta                          |    |

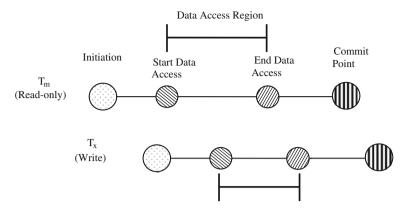

| A Lightweight Implementation of Obstruction-Free Software    |    |

| Transactional Memory                                         | 67 |

| Ankita Saha, Atrayee Chatterjee, Nabanita Pal,               |    |

| Ammlan Ghosh and Nabendu Chaki                               |    |

|                                                              |    |

#### Part II Cryptography

| Multiplicative Polynomial Inverse Over GF(7 <sup>3</sup> ): Crisis |    |

|--------------------------------------------------------------------|----|

| of EEA and Its Solution                                            | 87 |

| J.K.M. Sadique Uz Zaman and Ranjan Ghosh                           |    |

| A Novel Biometric Template Encryption Scheme |     |

|----------------------------------------------|-----|

| Using Sudoku Puzzle                          | 109 |

| Arnab Kumar Maji and Rajat Kumar Pal         |     |

#### Part III Computer Aided Design

| An ESOP-Based Reversible Circuit Synthesis Flow<br>Using Simulated Annealing<br>Kamalika Datta, Alhaad Gokhale, Indranil Sengupta and Hafizur Rahaman                            | 131 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| An Efficient Algorithm for Reducing Wire Length in Three-Layer<br>Channel Routing<br>Swagata Saha Sau and Rajat Kumar Pal                                                        | 145 |

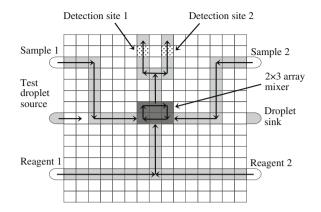

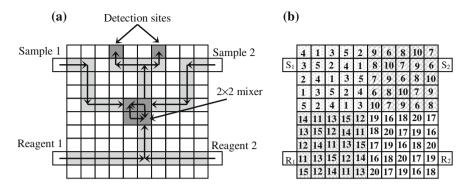

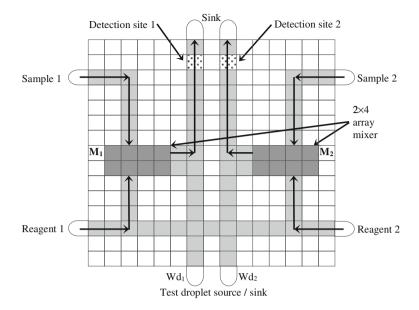

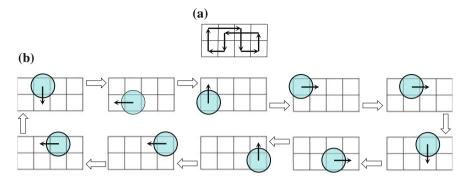

| A New Move Toward Parallel Assay Operations in a Restricted<br>Sized Chip in Digital Microfluidics<br>Debasis Dhal, Arpan Chakrabarty, Piyali Datta and Rajat Kumar Pal          | 157 |

| A 2D Guard Zone Computation Algorithm for Reassignment<br>of Subcircuits to Minimize the Overall Chip Area<br>Ranjan Mehera, Arpan Chakrabarty, Piyali Datta and Rajat Kumar Pal | 183 |

| Author Index                                                                                                                                                                     | 211 |

### **About the Editors**

**Rituparna Chaki** is an Associate Professor in the A.K. Choudhury School of Information Technology, University of Calcutta, India since June 2013. She joined the academia as faculty member in the West Bengal University of Technology in 2005. Before that she has served under Government of India in maintaining industrial production database. Rituparna has done her Ph.D. from Jadavpur University in 2002. She has been associated in organizing many conferences in India and abroad as Program Chair, OC Chair, or as member of Technical Program Committee. She has published more than 60 research papers in reputed journals and peer-reviewed conference proceedings. Her research interest is primarily in Ad-hoc networking and its security. She is a professional member of IEEE and ACM.

Khalid Saeed received the B.Sc. Degree in Electrical and Electronics Engineering from Baghdad University in 1976, the M.Sc. and Ph.D. Degrees from Wroclaw University of Technology, in Poland in 1978 and 1981, respectively. He received his D.Sc. Degree (Habilitation) in Computer Science from Polish Academy of Sciences in Warsaw in 2007. He is a Professor of Computer Science with AGH University of Science and Technology in Poland. He has published more than 200 publications-edited 23 books, Journals and Conference Proceedings, 8 text and reference books. He supervised more than 110 M.Sc. and 12 Ph.D. theses. His areas of interest are Biometrics, Image Analysis, and Processing and Computer Information Systems. He gave 39 invited lectures and keynotes in different universities in Europe, China, India, South Korea, and Japan. The talks were on Biometric Image Processing and Analysis. He received about 18 academic awards. Khalid Saeed is a member of more than 15 editorial boards of international journals and conferences. He is an IEEE Senior Member and has been selected as IEEE Distinguished Speaker for 2011–2016. Khalid Saeed is the Editor-in-Chief of International Journal of Biometrics with Inderscience Publishers.

**Sankhayan Choudhury** is Associate Professor in the Department Computer Science and Engineering, University of Calcutta, India. Currently, he is head of this department. Moreover, he is Co-ordinator of TEQIP-II, University of Calcutta. Dr. Choudhury has obtained his B.Sc. (Hons.) in Mathematics under University of Calcutta. Thereafter he has obtained B.Tech. and M.Tech in Computer Science and Engineering from University of Calcutta. He has completed Ph.D. from Jadavpur University, India in 2006. His research interests include Mobile Computing, Networking, Sensor Networking, Cloud Computing, etc. Besides authoring a book, Dr. Choudhury has published close to 50 peer-reviewed papers in international journals and conference proceedings. He has also served in the Program Committees of several international conferences and has also chaired the Program and Organizing Committees of a few. Dr. Choudhury is a professional member of ACM and an executive committee member for the local ACM professional chapter in Kolkata, India.

**Nabendu Chaki** is a Senior Member of IEEE and an Associate Professor in the Department Computer Science and Engineering, University of Calcutta, India. Besides editing several volumes in Springer in LNCS and other series, Nabendu has authored three textbooks with reputed publishers like Taylor and Francis (CRC Press), Pearson Education, etc. Dr. Chaki has published more than 120 refereed research papers in Journals and International conferences. His areas of research interests include image processing, distributed systems, and network security. Dr. Chaki has also served as a Research Assistant Professor in the Ph.D. program in Software Engineering in U.S. Naval Postgraduate School, Monterey, CA. He is a visiting faculty member for many universities including the University of Ca'Foscari, Venice, Italy. Dr. Chaki has contributed in SWEBOK v3 of the IEEE Computer Society as a Knowledge Area Editor for Mathematical Foundations. Besides being in the editorial board of Springer and many international journals, he has also served in the committees of more than 50 international conferences. He is the founding Chapter Chair for ACM Professional Chapter in Kolkata, India since January 2014.

## Part I Software Engineering

## Non-functional Property Aware Brokerage Approach for Cloud Service Discovery

#### Adrija Bhattacharya and Sankhayan Choudhury

**Abstract** In the fast growing service-oriented domain, cloud computing becomes the focal issue of the current research initiatives. Increase in cloud services, providers, consumers and their requirements demands efficient handling of the inherent complexity in a cloud environment. Cloud service broker (CSB) is one of such initiative. Research on CSB, an inter-mediatory, has opened an unexplored domain of service provisioning techniques. Seamless service provisioning with better QoS (such as cost and time) is one of the major challenges in CSB design. In this paper, an attempt has been made to propose a framework for facilitating service provisioning techniques within CSB. The non-functional parameter (NFP) along with functional one plays important role in service discovery from a set of offered services. The service discovery process based only on functionality may lead to an infeasible, hence unaccepted solution to a consumer. The meta-model, a proposed component within CSB, in the form of a lattice is introduced for speed up and to select more relevant set of services satisfying requirements of the consumers. The lattice grabs service information for all possible NFP combinations in a structured way. Different lattices with respect to each cloud layers are constructed independently. These lattices are exploited for finding the most relevant services. Moreover, it is expected to behave better in terms of search time.

Keywords Service discovery · Lattice · Cloud broker

S. Choudhury e-mail: sankhayan@gmail.com

A. Bhattacharya  $(\boxtimes) \cdot S$ . Choudhury

Department of Computer Science and Engineering, University of Calcutta, Kolkata, India e-mail: adrija.bhattacharya@gmail.com

<sup>©</sup> Springer India 2015

R. Chaki et al. (eds.), *Applied Computation and Security Systems*, Advances in Intelligent Systems and Computing 305, DOI 10.1007/978-81-322-1988-0\_1

#### **1** Introduction

In the fast growing service-oriented domain, cloud computing becomes the focal issue of the current research initiatives. The cloud services are very much different [1] and efficient with respect to Web services. Cloud actually offers software (computational), platform (behavioural) and infrastructural data resources as service from remote sources on demand. It consists of three types of models: Software as a Service (SaaS), Platform as a service (PaaS) and Infrastructure as a Service (IaaS) [2]. These three types of cloud services are often combined in different manner to satisfy user requests.

The increase in different service offering as well as numbers of service providers has put up a new challenge to the cloud researchers as these poses enormous different service provisioning with similar functionality but varying performance. The Service Level Agreement (SLA) is a mediator document that has to be satisfied for providing service to any consumer. In cloud computing paradigm, a consumer may be an end user or another service provider. In spite of developing and maintaining SLAs, cloud services often need mediation for coordinating SLAs, consumer management, reporting, pricing and accounting, etc. In this context, the cloud service broker (CSB) is proposed as a solution [3].

Cloud service provisioning through brokers is an open problem area of research. A broker may be considered as an upgradation on classical multi-source integrator used in distributed environments [4]. The service with similar functionality in a cloud environment is differentiated by performance attributes such as granularity, outcome, governance and control which works for betterment of cloud service systems with the help of CSBs. Thus, service provisioning techniques offered by a broker becomes a challenge.

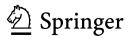

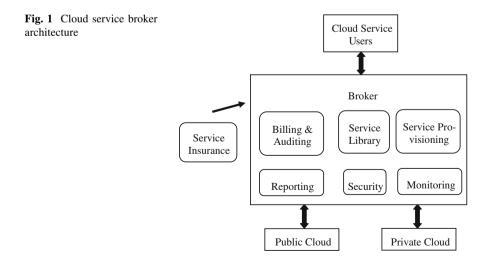

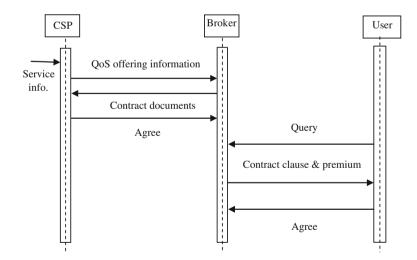

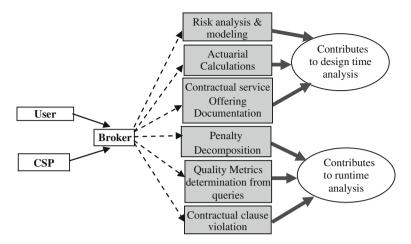

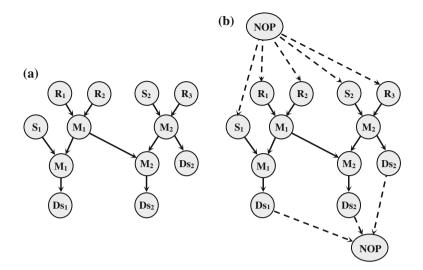

An overall description of a broker is depicted in Fig. 1. There exists no such standardized architecture of CSB. There are three major aspects, namely aggregation, integration and customization, based on which a CSB can be formed. Aggregation composes two or more service from one or more providers and then delivers it to the user or any other service provider. Appstore is a typical example of service aggregation through broker. Integration is another role that leads to substantially new values to community management in cloud domain [5]. Gmail contact list is the real-life example of integration by cloud broker. In customization, newer functionalities are added to improve the existing service functionality. The offered functionality of a broker can be customized in a flexible way based on a specific application domain. Thus, automatic and technically advanced methodologies are needed to enhance the strength of CSBs.

In Fig. 1, the component, marked in yellow, is the area of interest. In this paper, our objective is to provide an enhanced service discovery mechanism with the help of proposed meta-model. The said meta-model holds the detailed service information and can be used for finding most relevant services in service provisioning. Proposed enhanced service discovery mechanism is expected to behave in a more

Fig. 1 Cloud service broker

efficient way in terms of overhead (time). The penalty is to be paid in terms of time needed for model creation. This is insignificant as it is created offline, but can be used several times to satisfy user query.

#### 2 Related Work

This section gives a brief review on service provisioning role of cloud broker. In recent time, a significant upgradation on existing cloud service architecture has been done. A collaborative cloud market model [6] is proposed for collaboration among service clouds by means of resource sharing. Guaranteed QoS [7] from consumer side is considered for the first time, but this issue demands higher overhead in terms of time. In another research work, a ranking system for cloud service composition and goal-based method based on proposed SLA template for discovering proper monitoring services have been incorporated [2]. Cloud service provisioning varies in many ways with respect to service provisioning policies in Web. Lack of standardized representation of the cloud providers' criteria and varying format and content of SLAs made the existing Web service discovery and selection policies infeasible to implement in cloud domain [1]. The tightly coupled nature of services of a cloud often lacks flexibility, and as a result, one may not be able to club services offered by different providers. Like, if a user has chosen Amazon S3 cloud storage, then he is compelled to use Amazon provider's services [8]. Besides that challenge, due to complex relationship among cloud service providers, the existing service composition policies also failed to accumulate required cloud services within a composed single service. References [3, 9] have mentioned the required functionalities of Cloud brokers such as service monitoring and service aggregation.

The work of service description is the foremost to remember. A formal and detailed functional description about CSB and its role can be primarily identified in [10]. Through the review work, an interesting taxonomy among the existing

works has been identified. A few of these comment on the service selection techniques used. Several mathematical techniques are used for ranking-based service selection [11]. The relevance of selection and discovery of cloud services depends on the required functionality and non-functional parameters (NFP) specification in query. A Key Performance Indicator (KPI)-based ranking [12] of cloud services was proposed. This approach uses a set of NFPs, among which some of the important are time, accuracy, interoperability, cost, reliability, usability, etc. Only ranking strategy alone cannot be efficient enough for service discovery and selection. A few feedback-based selections were incorporated in [13, 14, 15]. Customer's feedback is the key point considered in the approach. The reliability of feedback raises a big question here. A prediction-based discovery approach is described in [16]. The prediction bases are huge volume of previous data. It is quiet infeasible in a real time system. Another prediction-based selection is in [17]. But all of these are domain-specific applications. None of these takes all possible NFPs into account, most of these dealing with the parameter "cost". Obviously, it is the most important one, but it alone cannot be taken as the key criteria for service selection.

Often the broker has a role in service decision-making and resource optimization. A set of works on this exists; for example, [18, 19] can be thought as pioneer in the domain. But the optimization often leads to cost optimization which is not the only need. Another cost optimization-based selection is done in [20]. It uses two-way optimization, but this is a very problem-specific method and can only be applied in feature placement problem.

The above discussion, especially on service provisioning, establishes the need for a better service discovery mechanism that should consider the functional as well as non-functional attributes as requested by consumers in a cloud environment. Most of the existing techniques are not considering all relevant NFPs used in the query, and as a result, it may generate an infeasible solution for the consumer. The scope of the work offers a meta-model that holds service information in the contexts all possible NFPs such that it can be used for better service provisioning as a whole.

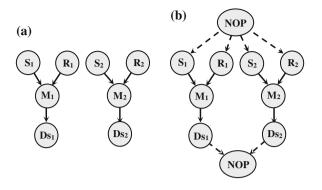

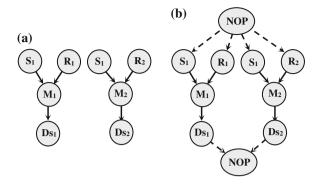

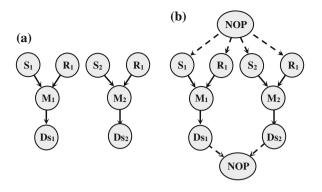

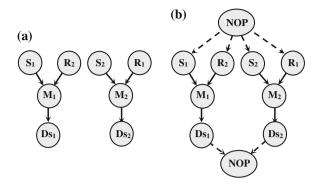

#### **3** Proposed Solution

The service provisioning in the area of cloud computing involves three main entities in a dialogue session. Consumer agent and provider agent both interact through third entity, broker agent or a set of broker agents. Brokers hold information about multiple cloud providers and their services. Each service (SaaS, PaaS, IaaS, etc.) has some non-functional specifications from provider's end. Consumer's requirement has two parts one is functional and another is nonfunctional requirements. Functional requirements of a query may be satisfied by either a single service (any of SaaS, PaaS, IaaS, etc.) or a set of multiple services (any combination of SaaS, PaaS, IaaS, etc.). In both of the cases, a minimum required non-functionality (specified by user) has to be satisfied. The reason behind is that in multi-cloud environment, information about all the service offerings is large in size and impossible to accumulate at single point from where a consumer can look for. In the process of searching, the consumer's requested services along with specified non-functionality held difficult due to huge amount of information available at broker's end. The proposed framework consisting of brokerage meta-model is useful to manage the inherent complex relations among the cloud providers in a much easier way. This is an efficient way to handle information with intelligence, so that the time of search is decreased.

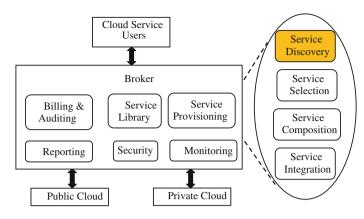

After the inclusion of our proposal within the framework, it runs in the manner as depicted in Fig. 2. The query processing and extraction of service non-functional specification from the query is the preliminary need.

The following steps are depicted in Fig. 2 to illustrate the enhanced service discovery mechanism:

- First step considers the query from consumer.

- Functionalities are extracted from the query in second stage. Necessary SaaS, PaaS and IaaS are identified.

- Matching of necessary NFPs is done in this stage.

- The proposed meta-model is consulted for finding relevant feasible services.

- An NFP adjustment scheme may be needed for providing an integral solution.

The focus of the paper lies on the proposition of the meta-model and to describe the service discovery mechanism using the proposed work in Fig. 2.

#### 3.1 The Proposed Meta-Model

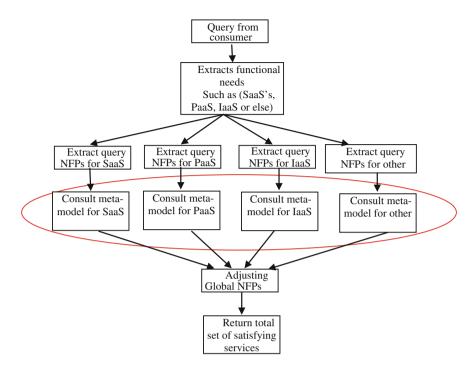

The proposed meta-model grabs the non-functional information of the services and arranges those in a structured way. The meta-model is lattice based. This is immense helpful to use lattice as it contains all possible combinations of NFP in a structured way. It is important for better discovery. If a set of NFP at a specific level of lattice cannot satisfy the consumer-specified NFPs, it transfers to the next lower level or levels which are connected. These lower level nodes are nothing but the subsets of query NFPs. This actually increases the speed of discovery. Another benefit of lattice is that it maintains a hierarchy among the nodes.

The proposed structure contains all unique combinations of non-functional properties as elements. The elements together are defined as a set (say S). If the non-functional properties (NFP) are denoted by the letters (A, B and C), then

$$S = \{A, B, C, AB, AC, BC, ABC\}$$

Now each element in the set is actually a structure with varying dimension. The dimension of the structure depends on the number of NFPs, such as ABC is a three-dimensional structure as there are three NFPs (A, B, C). Node ABC has all services

Fig. 2 Work flow of proposed cloud service discovery

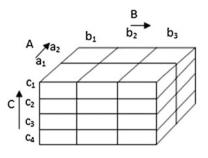

whose specification has mentioned the values of NFP about A, B and C. Thus, the structure can be conceptualized by Fig. 3.

Two binary operations have been defined as "consolidation" and "diversification" on S.

**Consolidation**: It means accumulating common services from two different nodes into a single node (from *AB* and *AC* to *ABC*).

**Diversification**: It means a higher order node is decomposed into lower order nodes that is inclusion of more services in lower order nodes (AB to A and B).

Now from the definition of these two operations on the set S, following conclusions are drawn.

- Any node can be generated by higher level node using diversification or from lower node using consolidation. As the structure has unique nodes, reflexivity holds.

- Say nodes (X and Y) at level-p are generated by diversification from node Z at level-p + 1. Again applying consolidation on X or Y cannot regenerate Z. Antisymmetry holds.

- Say a consolidation on M at level-p generates N at level-(p + 1). Now the same is applied on N to generate K at level-(p + 2). It shows that K could be generated from M using consolidation. Hence, transitivity holds.

Fig. 3 Framework introduced

S satisfies the reflexivity, anti-symmetry and transitivity properties. Thus, it is a poset. Any two combination of level-*i* in the structure can be mapped to a unique node in the level-(i - 1) which has all the common services of two selected level-i nodes, but the reverse is not true. Two nodes from level-*i* and node in level-(i - 1) are related by consolidation. So there exists unique least upper bound of any two nodes in the structure.

Similarly, any two combination of level-*i* is connected with a unique level-(i + 1) node by diversification, but also the reverse is not true. So there exists unique greatest lower bound for any two elements (nodes). The poset contains the unique least upper bound and unique greatest lower bound with respect to these two operations defined. Thus, it is proved as a lattice. Lattice will contain  $2^{N}$  nodes in case of *N* NFPs. (*N* + 1) will be the number of levels in the structure.

The direction of consolidation and diversification within the lattice is also decided that helps into take dynamic decision at the time of discovery. For less NFP information and more number of services, **diversification** is indicated, i.e. the search will proceed from upper to lower nodes. Alternately, with more NFP information and lesser services, search will have lower to upper direction execution by the operation **consolidation**. This model works also for partial matching of NFP information though the existing ignores services with partial matches.

#### 3.2 Description of the Framework

Consumer's query is defined here as q(FS, NFS), where FS is the functional specification and NFS is the non-functional specification. Again NFS can look like  $(A = a_1, B = b_2)$  or  $(A = a_1 - a_k, B = b_2 - b_j)$  where A and B are two NFPs. Number of NFPs are essentially 5, but can also vary within 8 to 10 for particular domain-specific SaaSs or general PaaS, IaaS, etc. The lattice in Fig. 3 has all services access pointers in the lowest level. Next level contains the one NFP

Fig. 4 Example node of the structure

grouping of services; it is by the use of consolidation operation. In the next level, services are arranged by two NFPs at a time. This way the lattice structure is constructed. The lattice construction is primarily done at design time so the total overhead of the structure is only due to maintenance. Each of the nodes is a structure having dimensions. A typical structure is defined in Fig. 4.

The node *ABC* in Fig. 2 is internally looking like the above figure. Here, *A*, *B* and *C* are assumed as NFPs (such as cost, time and security).  $a_1$  and  $a_2$  are the different values assigned to the NFP *A*. The structure contains 24 cells  $(2 \times 3 \times 4)$ . Each cell contains service access pointer through which the original services can be invoked. The very first cell in the above figure has edge labelled as  $c_1$ ,  $a_1$  and  $b_1$  that means the cell contains the access pointers of the services whose description contains NFPs *A*, *B* and *C* and that too in the form of  $(A = a_1, B = b_1 \text{ and } C = c_1)$ .

This lattice model is introduced for containing service information in a structured way. Broker must have many lattices such as SaaS-lattice, PaaS-lattice and IaaS-lattice. A SaaS-lattice contains information regarding SaaS, which are accumulated and similar kind of structures formed for each of PaaS, IaaS, etc.

#### 3.3 Service Discovery Algorithm

In this subsection, service discovery algorithm is defined. The described algorithm works within a lattice model. This is a generic algorithm that will work for every lattice within the framework. The following points are some prerequisite for understanding the algorithm

- All the NFPs are declared in the power of 2, i.e. for 3 NFPs A, B and C. So, A = 2°, B = 2<sup>1</sup>, C = 2<sup>2</sup> AB = 2° + 2<sup>1</sup> = 3. So all NFP combinations are declared as unique sums

- The algorithm works for all levels of the lattice.

- It is clear from the model that the number of NFP is equals the level of the lattice from where search is to proceed.

- The algorithm passes execution to next lower level if no services in *i*th level are matched with NFP specified.

- The algorithm will be recursively called several times until the services are found satisfying NFP.

- If failing to find all NFP satisfying services, the structure returns all possible combinations. For example, if the query specifies *A*, *B* and *C* and if at level-3 node *ABC* (in Fig. 3) has no matching services, then it will return services from *AB*, *BC*, *AC*, *A*, *B*, *C* nodes and the last node at bottom also.

#### Algorithm for searching services at the *i*th level of the lattice

| Step 0:   | [Initialize] Define unique weights to each NFPs. Set Source = level who called level- $i$ , $N$ = number of non-functional criteria passed by the user, Count = 1, Found[ $N$ ] = false, fail = 1 (no of failed combination) |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Step 1:   | For the <i>i</i> th non-functional criteria do                                                                                                                                                                               |

| Step 1.1: | If the user given non-functional criteria is valid then<br>Mark-no = <i>i</i> , [Mark it with <i>i</i> ]<br>End If                                                                                                           |

| Step 2:   | For all non-functional criteria, repeat step 1                                                                                                                                                                               |

| Step 3:   | Calculate unique sums for valid NFPs using defined weights.                                                                                                                                                                  |

| Step 4:   | Collect services with corresponding unique sums                                                                                                                                                                              |

| Step 5:   | For all existing services do                                                                                                                                                                                                 |

| ~~r • · · | Begin                                                                                                                                                                                                                        |

|           | If the all <i>i</i> non-functional criteria and functional criteria are simultaneously satisfied with user query, then                                                                                                       |

|           | set a flag Found[ $i$ ] = true<br>Print "The service found with id".                                                                                                                                                         |

|           | Endif                                                                                                                                                                                                                        |

|           | End For                                                                                                                                                                                                                      |

| Step 6:   | Increment count by 1.                                                                                                                                                                                                        |

| Sup 0.    | Repeat the steps from step 1 to step 4 for all combinations of valid <i>i</i> th                                                                                                                                             |

|           | NFPs                                                                                                                                                                                                                         |

| Step 7:   | If Found[ $i$ ] = true for all $i$ then                                                                                                                                                                                      |

| 1         | If $Source = manager$ then                                                                                                                                                                                                   |

|           | Send a finish message to the manager.                                                                                                                                                                                        |

|           | Else                                                                                                                                                                                                                         |

|           | Send a found message to the Source.                                                                                                                                                                                          |

|           | End If                                                                                                                                                                                                                       |

|           | Else                                                                                                                                                                                                                         |

|           | If Source $=$ manager then                                                                                                                                                                                                   |

|           | Call its previous level $(i - 1)$ .                                                                                                                                                                                          |

|           | Else                                                                                                                                                                                                                         |

|           | Send a not found message to the Source.                                                                                                                                                                                      |

|           | End If                                                                                                                                                                                                                       |

|           | End If                                                                                                                                                                                                                       |

| Step 8:   | After all combination checked                                                                                                                                                                                                |

|           | If fail = no of all combination of all $i$ NFPs then                                                                                                                                                                         |

|           | Call $(i - 2)$ level                                                                                                                                                                                                         |

|           | End if                                                                                                                                                                                                                       |

This multi-dimensional structure consists of several dimensions. These dimensions often contain hierarchy, such as location. If the service declaration has NFP, Location = "West Bengal". Then, the hierarchy information is held in the lattice that "Kolkata" is in "West Bengal". So the services relevant to West Bengal will be retrieved, if the query demands it from Kolkata.

#### **4** Illustration with Example

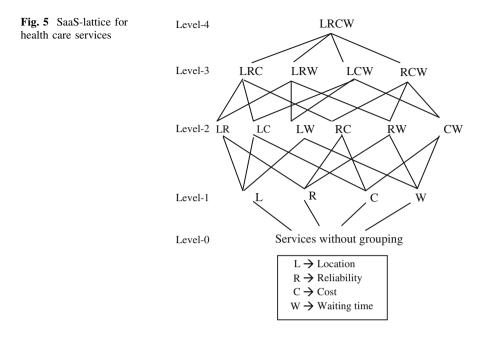

In this example, it is assumed that the framework consisting of five lattices for SaaS, PaaS, IaaS, DaaS (data as a service) and Communication as a service (CaaS). The example primarily is built upon a typical domain of SaaS. It is fixed as health care. So SaaS may include cost, waiting time, reliability and location as relevant NFPs with respect to health care services; particularly, emergency accidental care services are considered as the functionality. Thus, a SaaS-lattice formed containing emergency health services. Functionality of services includes diagnostic test services, general medicine, orthopaedics and nursing care. Figure 5 illustrates the SaaS-lattice.

Four NFPs are specified in the lattice of different services irrespective of functionalities, considering NFPs. A typical consumer query is of the following form:

**Query**: Brain scan imaging with maximum 2-h waiting time in Kolkata within cost Rs. 2,000 and the communication service with minimum delay to the services.

**Solution**: Here, a SaaS-lattice and another CaaS-lattice have to be exploited for satisfying the query. SaaS-lattice will be searched at level-2 and node CW. After finding a set of relevant services with respect to cost and waiting time from SaaS-lattice, a set of CaaS are to be found. Further, the CaaS-lattice is exploited with minimum delay that will connect any of the scan services satisfying the user NFP specification and Delay in CaaS.

#### 5 Conclusion

Several discovery methods already exist in cloud domain; some of them are nonfunctional property-based mechanisms. In this approach, a methodology is proposed that works first to strike out the non-relevant NFP information. Further based on the remaining NFPs, any of the existing search algorithms can work.

Lattice that is a mathematical structure is used in cloud service domain. Few operations are there to explore the properties of the structure. Identification of the lattice framework, construction of it and searching on this model are the major contributions of this work. This model considers incomplete NFP information also and gives all possible combinations of those NFPs. These enable consumers to compromise at one of the NFPs and then subscribe the service where in existing works no such provision was there. Offered solution should be considered as a relevant one.

Scalability is another issue in this context. Huge number of services may occur within service cells in each structure, if there are no functional differences considered. In the proposed work, the domain of deployment is limited to a small set of cloud providers and they are related in some way. So the functionalities of services vary within a small set. However, the proposed work can be combined with any of the existing functionality-based solution of services discovery. As the number of NFPs within closed domains varying over 8–10, the construction and maintenance is easier.

In future, lattice of service units could be degenerated to work with only the important service NFP combinations and ignoring the rest. Besides, the multidimensional structure, referred here as node, could be exploited further. This may lead to the discovery of new set of operations and further optimizations. The identification of hierarchy and accordingly formation of new service at different granular level is an important research area where different mathematical models could be analysed.

#### References

- Sundareswaran, S., Squicciarini, A., Lin, D.: A Brokerage-Based Approach for Cloud Service Selection. In: IEEE 5th International Conference on Cloud Computing, Honolulu, HI. ISBN: 978-1-4673-2892-0, June 2012

- Subashini, S., Kavitha, V.: A survey on security issues in service delivery models of cloud computing. J. Netw. Comput. Appl. 34(1), 1–11 (2011)

- 3. Lheureux, B.: Cloud Services Brokerages: the Dawn Of The Next Intermediation Age. Published in Gartner Blog Network, 8 Nov 2010

- 4. Lawler, C.M.: Cloud Service Broker Model, Green IT Cloud Summit, Washington, D.C, April 18, Sheraton Premier, Tysons Corner, http://www.greenitsummit.org/summit/ (2012)

- 5. Houidi, I., Mechtri, M., Louati, W., Zeglache, D.: Cloud service delivery across multiple cloud platforms. IEEE International Conference on Service Computing (SCC) (2011)

- 6. Nguyen, D.K., Lelli, F., Taher, Y., Parkin, M., Papazoglou, M.P., van den Heuvel, W.J. : Blueprint Template Support for Engineering Cloud-Based Services, Springer LNCS, Towards a Service-Based Internet. In: Proceedings of 4th European Conference, ServiceWave 2011 Poznan, Poland, 26–28 Oct 2011

- Siebenhaar, M., Lampe, U., Lehrig, T., Zoller, S., Schulte, S., Steinmetz, R.: Complex Service Provisioning in Collaborative Cloud Markets, Springer LNCS, Towards a Service-Based Internet. In: Proceedings of 4th European Conference, ServiceWave 2011 Poznan, Poland, 26–28 Oct 2011

- 8. Tsai, W.T., Sun, X., Balasooriya, J.: Service-Oriented Cloud Computing Architecture. In: IEEE Seventh International Conference on Information Technology 2010

- Mondal, A., Yadav, K., Madria, S.: Ecobroker: An Economic Incentive-Based Brokerage Model for Efficiently Handling Multiple-Item Queries to Improve Data Availability via Replication in Mobile-P2P Networks. In: 6th International Workshop in Databases in Networked Information Systems, pp. 274–283 (2010)

- Buyya, R., Yeo, C., Venugopal, S., Broberg, J., Brandic, I.: Cloud computing and emerging it platforms: vision, hype, and reality for delivering computing as the 5th utility. J. Future Gener. Comput. Syst. 25(6), 599–616 (2009)

- World Wide Web consortium (W3C): Web Service Activity Statement. Retrieved from http:// www.w3.org/2002/ws/Activity on 03 June 2007

- Garg, S.K., Versteeg, S., Buyya, R.: A framework for ranking of cloud computing services. J. Future Gener. Comput. Syst. 29(4), 1012–1023 (2013)

- Qu, L., Wang, Y., Orgun, M.A.: Cloud Service Selection Based on the Aggregation of User Feedback and Quantitative Performance Assessment. In: IEEE 10th International Conference on Services Computing 978-0-7695-5026-8/13

- Villegas, D., Bobroff, N., Rodero, I., Delgado, J., Liu, Y., Devarakonda, A., Fong, L., Masoud Sadjadi, S., Parashar, M.: Cloud federation in a layered service model. J. Comput. Syst. Sci. 78, 1330–1344 (2012)

- 15. Heng, D.Y., et al.: A user centric service-oriented modeling approach. J. World Wide Web 14(4), 431–459 (2011)

- Narayanan, D., Flinn, J., Satyanarayanan, M.: Using history to improve mobile application adaptation. In: Proceedings of Third IEEE Workshop on Mobile Computing Systems and Applications, 2000

- Balan, R., Satyanarayanan, M., Park, S., Okoshi, T.: Tactics-Based Remote Execution for Mobile Computing. In: Proceedings of the 1st International Conference on Mobile Systems, Applications and Services, ACM, pp. 273–286 (2003)

- Kusic, D., Kandasamy, N.: Risk-aware limited look ahead control for dynamic resource provisioning in enterprise computing systems. In: Proceedings of the IEEE International Conference on Autonomic Computing, vol. 10(3); pp. 337–350 (2010)

- Kofler, K., Haq, I.U., Schikuta, E.: User-Centric, Heuristic Optimization of Service Composition in Clouds. In: 16th International Euro-Par Conference, vol. 6271, Springer, Berlin, pp. 405–417 (2010)

- Moens, H., Truyen, E., Walraven, S., Joosen, W., Dhoedt, B., De Turck, F.: Cost-effective feature placement of customizable multi-tenant applications in the cloud. J. Netw Syst. Manag. (2013). doi:10.1007/s10922-013-9265-5

## A DWT-based Digital Watermarking Scheme for Image Tamper Detection, Localization, and Restoration

Sukalyan Som, Sarbani Palit, Kashinath Dey, Dipabali Sarkar, Jayeeta Sarkar and Kheyali Sarkar

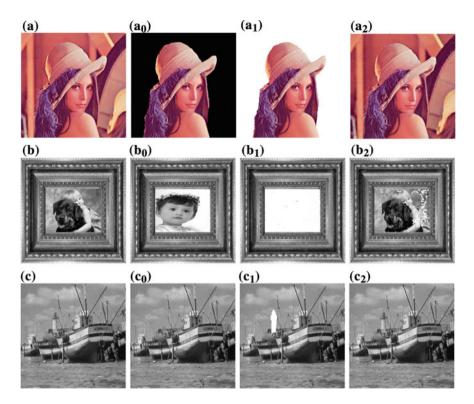

**Abstract** The provision of image tamper detection, localization and restoration forms an important requirement for modern multimedia and communication systems. A discrete wavelet transform (DWT)-based watermarking scheme for this purpose is proposed in this communication. In our scheme, the original image is first partitioned into blocks of size  $2 \times 2$  in which a 1D DWT is applied to produce a watermark which is embedded in four disjoint partitions of the image to enhance the chance of restoration of the image from different cropping attack-based tampers. The validity and superiority of the proposed scheme is verified through extensive simulations using different images of two extensively used image databases.

**Keywords** Discrete wavelet transform (DWT)  $\cdot$  Least significant bits (LSBs)  $\cdot$  Peak signal-to-noise ratio (PSNR)  $\cdot$  Mean squared error (MSE)  $\cdot$  Structural SIMilarity (SSIM) index

S. Som (🖂) · J. Sarkar · K. Sarkar

Department of Computer Science, Barrackpore Rastraguru Surendranath College, Barrackpore, West Bengal, India e-mail: sukalyan.s@gmail.com

J. Sarkar e-mail: sarkar.jayeeta9@gmail.com

K. Sarkar e-mail: chelsea.kheyali9@gmail.com

S. Palit · D. Sarkar CVPR Unit, Indian Statistical Institute, Kolkata, West Bengal, India e-mail: sarbanip@isical.ac.in

D. Sarkar e-mail: mampisarkar333@gmail.com

K. Dey

Department of Computer Science and Engineering, University of Calcutta,

92, APC Road, Kolkata 700009, West Bengal, India

e-mail: kndey55@gmail.com

#### 1 Introduction

Tampering of digital media and its detection has been an interesting problem since long time. Its importance has increased with the stepping up of the use of digital media on the Internet. The volume of data transmission, especially that of images and videos, has gone up exponentially and has naturally drawn the interest of many including, unfortunately, fraudulent persons who would tamper with the transmitted data to suit their purpose. The detection of tampering followed by restoration of the original image is hence an important task. Most of the research carried out so far has been of tamper detection, while more recent work includes recovery of the image as well.

A number of digital watermarking schemes have been reported during the past decade for different purposes and considerations. In [1], an image tamper detection and recovery system has been developed based on the discrete wavelet transform (DWT) technique where some information has been extracted as the eigenvalue of the image and is embedded in the middle-frequency band of the frequency domain. Such embedding has been used for tamper detection and localization. In [2], a novel fragile watermarking scheme based on chaotic system for image authentication or tamper proofing is proposed. The watermark is generated by using pixel values as input values of a chaotic system, and a secret key controls a set of parameters of the chaotic system. A quantization function is introduced to embed and detect watermarks. This method can effectively detect minor alteration in a watermarked image. In [3], a tamper detection and retrieval scheme has been proposed. Special characteristic values of the low-frequency sub-band are embedded in the middlefrequency sub-bands. The embedded data with a digital signature and a public key are used to prove the authenticity of the image. Recovery with visually acceptable quality has also been achieved. In [4], the watermark of a particular image is generated from both frequency domain and spatial domain. The number of encoding stages of each DWT coefficient during the multistage encoding is taken as frequency watermark, and the mean values of blocks are stored as spatial watermark. The watermark is embedded into SPIHT encoded list of significant pixels (LSP) bit stream. By comparing the embedded watermark and the corresponding message extracted from decoded image, authentication is ensured. In [5], the semifragile watermark is designed from low-frequency band of wavelet-transformed image and is embedded into the high-frequency band by the human visual system (HVS). The robustness for mild modification such as JPEG compression and channel additive white Gaussian noise (AWGN) and fragility to malicious attack are analyzed. In [6], the proposed scheme extracts content-based image features from the approximation sub-band in the wavelet domain to generate two complementary watermarks. An edge-based watermark sequence is generated to detect any changes after manipulations. A content-based watermark is also generated to localize tampered regions. Both watermarks are embedded into the high-frequency wavelet domain to ensure the watermark invisibility. In [7], the original image is divided into two regions: region of interest (ROI), which is important region that requires protection against malicious modification, and region of embedding (ROE), which is the rest of the image where watermark sequence is embedded. In [8], dual visual watermarks using DWT and singular value decomposition (SVD) are presented. One is color image the same as original image, and the other is ownership watermark which is grayscale image. Both of them are embedded into original image using DWT-SVD to prove robustness. For recovery signal embedding, luminance signal and chrominance signal of original image were embedded into surplus chrominance space of original image using matrix transpose replacement embedding method. In [9, 10], two watermarks are used, generated from the low-frequency band and embedded into the high-frequency bands, one for detecting the intentional content modification and indicating the modified location and another for recovering the image. In [11], a multipurpose image watermarking method based on the wavelet transform is proposed for content authentication and recovery of the tampered regions where the original image is first divided into nonoverlapping blocks and each block is transformed into the wavelet domain. The image features are subsequently extracted from the lowest frequency coefficients of each block as the first embedded watermark. Next, the whole image is decomposed into the two-level wavelet transform, and the orientation adjustment is calculated based on the wavelet coefficients in the middle-frequency sub-bands for image authentication. In addition, a logo watermark is embedded into the given middlefrequency sub-bands.

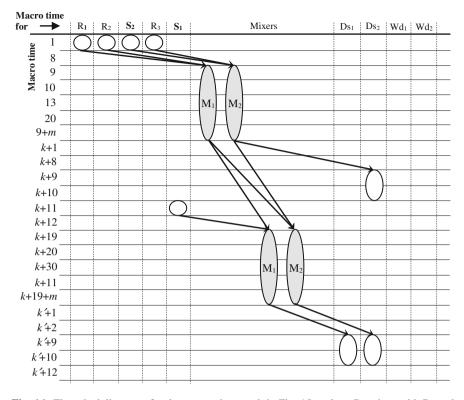

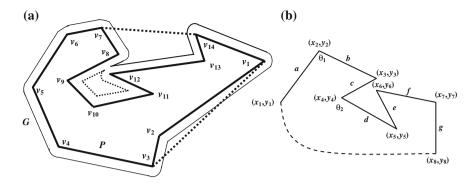

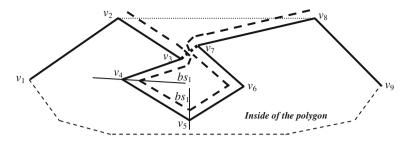

The rest of the paper is organized as follows. In Sect. 2, a brief introduction to DWT using Haar wavelet is given. In Sect. 3, the proposed scheme is presented wherein watermark generation, watermark embedding, and watermark extraction for the purpose of image tamper detection, localization, and recovery are explained. Section 4 demonstrates the experimental results with conclusions being drawn in Sect. 5.

#### 2 Background

#### 2.1 Discrete Wavelet Transform

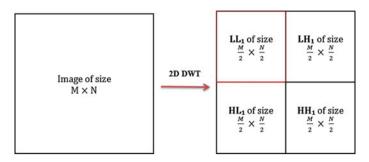

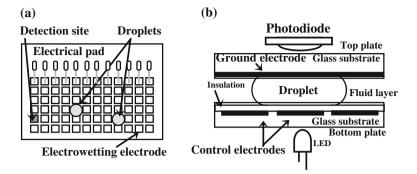

The single-level 2D DWT decomposes an input image into four components, namely LL, LH, HL, and HH where the first letter corresponds to applying either a low-pass or a high-pass frequency operation to the rows and the second letter refers to the filter applied to the columns. The lowest frequency sub-band LL consists of the approximation coefficients of the original image. The remaining three frequency sub-bands consist of the detail parts and give the vertical high (LH), horizontal high (HL), and high (HH) frequencies. Figure 1 demonstrates single-level 2D DWT. For an one-level decomposition, the discrete 2D wavelet transform of the image function f(x, y) can be written as follows:

Fig. 1 Discrete wavelet transform

$$LL = [(f(x, y) \times \phi - x\phi - y)(2n, 2m)]_{(n,m) \in \mathbb{Z}^2}$$

$$LH = [(f(x, y) \times \phi - x\psi - y)(2n, 2m)]_{(n,m) \in \mathbb{Z}^2}$$

$$HL = [(f(x, y) \times \psi - x\phi - y)(2n, 2m)]_{(n,m) \in \mathbb{Z}^2}$$

$$HH = [(f(x, y) \times \psi - x\psi - y)(2n, 2m)]_{(n,m) \in \mathbb{Z}^2}$$

where  $\phi(t)$  is a low-pass scaling function and  $\psi(t)$  is the associated band-pass wavelet function. For computational simplicity, we have performed DWT using Haar wavelet.

#### **3** Proposed Scheme

The proposed method has three distinct phases. Firstly, a watermark is generated from the image itself which is fragile to content modification as well as robust to common image processing after a preparation for doing so. Secondly, the generated watermark is embedded in the image. Finally, the watermark is extracted from the image (the one that has gone several degradations due to cropping attacks and/or noise attacks) to detect and localize tamper and recover the image as close as possible to the original one.

#### 3.1 Watermark Preparation

A block mapping sequence is used to scramble watermark information. A 1D transformation algorithm, found in [12], shown in Eq. (1) is used to obtain a one-to-one mapping sequence where  $X, X' (\in [0, N-1])$  the block number,  $k(a \text{ prime and } \in Z - \{\text{factors of } N\})$  is a secret key, and  $N(\in Z - \{0\})$  is the total number of blocks in the image of size  $N = 2^n \times 2^n$ ,  $n \ge 2$ , and  $n \in N$ .

A DWT-based Digital Watermarking Scheme...

$$X' = [f(x) = (k \times X) \mod N] + 1 \tag{1}$$

A lookup table is constructed using the following algorithm to record the mapping address of each block in the image.

#### 3.1.1 Block Mapping Address Generation Algorithm

- 1. Divide the image into non-overlapping blocks of  $2 \times 2$  pixels.

- 2. Assign a unique nonnegative integer  $X \in \{0, 1, 2, ..., N-1\}$  to each block from top left in row major order,  $N = 2^{n-1} \times 2^{n-1}$ .

- 3. Choose a prime number  $k \in [1, N 1]$ .

- 4. For each block number X, obtain X' and its mapping block by Eq. (1). All the X's construct the lookup table.

A push-aside operation is used to modify the lookup table. The watermarks of the left half of the image are concentrated in the right half region of the image, and the watermarks of the right half of the image are concentrated in the left half region of the image. We simply push right the columns which originally belong to the left half and push left the columns which originally belong to the right half and thus result in a modified lookup table.

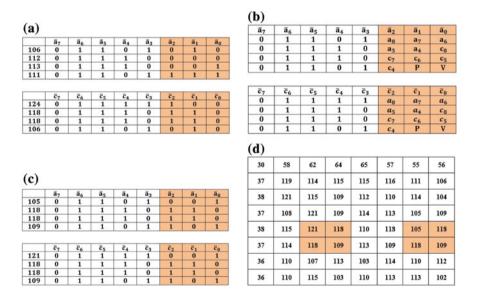

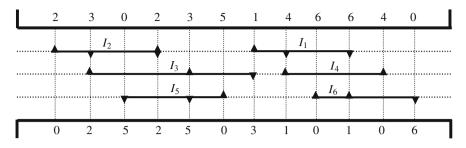

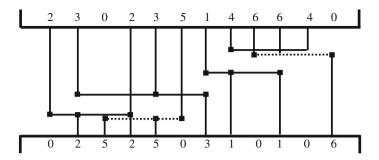

As an illustration, an image of size  $8 \times 8$  is considered as the original image. The original image along with its corresponding block index matrix, lookup table generated using Eq. (1), and modified lookup table after push-aside operation is shown in Fig. 2.

#### 3.2 Watermark Generation

- Step 1: Decompose each  $2 \times 2$  sized block by the DWT decomposition yielding from each block the approximation coefficient matrix LL<sub>1</sub> and the detail matrices HL<sub>1</sub>, LH<sub>1</sub>, and HH<sub>1</sub>.

- Step 2: The watermark is generated from the coefficient of the  $LL_1$  sub-band of each decomposed block. As  $LL_1$  wavelet coefficients may be beyond the recovery scope, its value must be adjusted. Therefore, the coefficients, after computation, are modified subsequently such that its value falls within the recovery range, as done in [5].

- Step 3: The original image is divided horizontally and vertically into four equal parts. Let blocks A, B, C, and D be located at those four parts, respectively, such that C is situated at the opposite angle of A and D is situated at the opposite angle of B. Partner blocks of part A are located at the same position of part C and vice versa. Partner blocks of part B are located at the same position of part D and vice versa.

- Step 4: The representative information of block A is constructed by extracting the five most significant bits (MSBs) of LL<sub>1</sub> sub-band coefficient of block A

| (a)        |     |     |     |     |     |              |     | <b>(b)</b> |     |     |     |     |     |     |     |

|------------|-----|-----|-----|-----|-----|--------------|-----|------------|-----|-----|-----|-----|-----|-----|-----|

| 30         | 58  | 62  | 64  | 65  | 57  | 55           | 56  | 30         | 58  | 62  | 64  | 65  | 57  | 55  | 56  |

| 37         | 119 | 114 | 115 | 115 | 116 | 111          | 106 | 37         | 119 | 114 | 115 | 115 | 116 | 111 | 106 |

| 38         | 121 | 115 | 109 | 112 | 110 | 114          | 104 | 38         | 121 | 115 | 109 | 112 | 110 | 114 | 104 |

| 37         | 105 | 121 | 109 | 114 | 113 | 105          | 109 | 37         | 108 | 121 | 109 | 114 | 113 | 105 | 109 |

| 38         | 115 | 124 | 118 | 110 | 118 | 106          | 112 | 38         | 115 | 124 | 118 | 110 | 118 | 106 | 112 |

| 37         | 114 | 118 | 106 | 113 | 109 | 113          | 111 | 37         | 114 | 118 | 106 | 113 | 109 | 113 | 111 |

| 36         | 110 | 107 | 113 | 103 | 114 | 110          | 112 | 36         | 110 | 107 | 113 | 103 | 114 | 110 | 112 |

| 36         | 110 | 115 | 103 | 110 | 113 | 113          | 102 | 36         | 110 | 115 | 103 | 110 | 113 | 113 | 102 |

| <b>c</b> ) |     |     |     |     | (   | ( <b>d</b> ) |     |            | -   |     | (e) |     |     |     |     |

| 0          | 1   |     | 2   | 3   |     | 1            | 14  | 11         | 8   |     | 11  | 1   | 8   | 1   | 14  |

| 4          | 5   |     | 6   | 7   | 1 [ | 5            | 2   | 15         | 12  |     | 15  | 1   | 2   | 5   | 2   |

| 8          | 9   |     | 10  | 11  | 1   | 9            | 6   | 3          | 0   | 1   | 3   |     | )   | 9   | 6   |

| 12         | 13  | 3   | 14  | 15  | 1 [ | 13           | 10  | 7          | 4   |     | 7   |     | 4   | 13  | 10  |

Fig. 2 a The original image matrix; b the original image matrix subdivided into  $2 \times 2$  nonoverlapping blocks; c the original block matrix; d the lookup table; and e the modified lookup table after push-aside operation

and is then combined with (1) the representative information of block C and (2) the in-block parity-check bits and its complementary bit p and v, respectively, to construct the joint 12-bit watermark for blocks A and C. Similarly, the representative information of block B is used to construct the joint 12-bit watermark for blocks B and D.

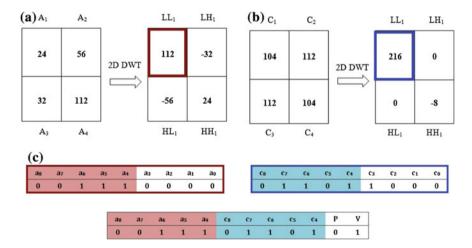

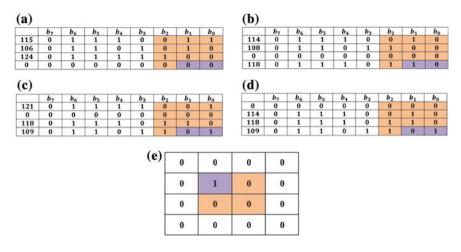

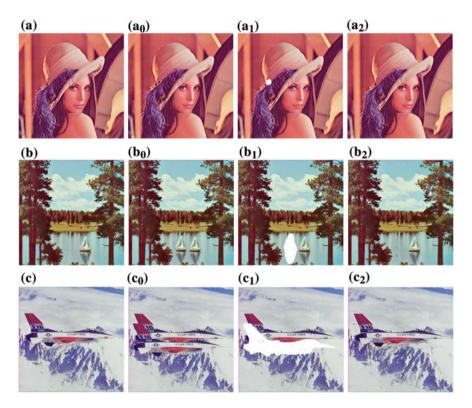

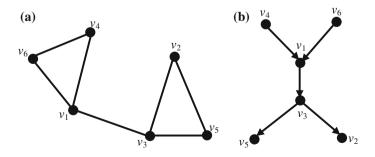

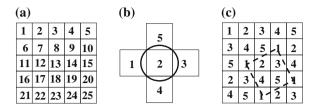

The watermark generation technique is illustrated in Figs. 3 and 4.

#### 3.3 Watermark Embedding

Two mapping blocks are needed to embed the joint 12-bit watermark of block A (or B) and its partner blocks C (or D). The lookup table helps find these mapping blocks. The watermark is embedded into the three LSBs of each pixel of a block. Suppose blocks  $\overline{A}$  and  $\overline{C}$  (or  $\overline{B}$  and  $\overline{D}$ ) are the two mapping blocks which are going to be used to embed the 12-bit watermark resulted from blocks A and C (or B and D). Both blocks  $\overline{A}$  and  $\overline{C}$  contain the same 12-bit watermark and the same embedding sequence in the corresponding locations. That is to say, for each block of size  $2 \times 2$  pixels in the image, we have two copies of its representative information hidden somewhere in the image. Therefore, if one copy is tampered by any chance, we have two chances to recover this block from the other copy.

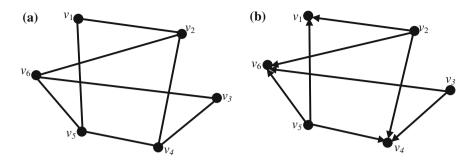

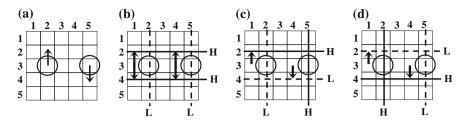

Figures 5 and 6 demonstrate the watermark embedding technique.

|     |     |   |   | (a) | 30 | 58  | 62  | 64  | 65  | 57  | 55  | 56  | 1 |   |   |   |   |

|-----|-----|---|---|-----|----|-----|-----|-----|-----|-----|-----|-----|---|---|---|---|---|

|     |     |   |   |     | 37 | 119 | 114 | 115 | 115 | 116 | 111 | 106 | 1 |   |   |   |   |

|     |     |   |   |     | 38 | 121 | 115 | 109 | 112 | 110 | 114 | 104 | ] |   |   |   |   |

|     |     |   |   |     | 37 | 108 | 121 | 109 | 114 | 113 | 105 | 109 |   |   |   |   |   |

|     |     |   |   |     | 38 | 115 | 124 | 118 | 110 | 118 | 106 | 112 |   |   |   |   |   |

|     |     |   |   |     | 37 | 114 | 118 | 106 | 113 | 109 | 113 | 111 |   |   |   |   |   |

|     |     |   |   |     | 36 | 110 | 107 | 113 | 103 | 114 | 110 | 112 |   |   |   |   |   |

|     |     |   |   |     | 36 | 110 | 115 | 103 | 110 | 113 | 113 | 102 |   |   |   |   |   |

|     | (b) |   |   |     |    |     |     |     |     | (c) |     |     |   |   |   |   |   |

| 30  | 0   | 0 | 0 | 1   | 1  | 1   | 1   | 0   | 24  | 0   | 0   | 0   | 1 | 1 | 0 | 0 | 0 |

| 58  | 0   | 0 | 1 | 1   | 1  | 0   | 1   | 0   | 56  | 0   | 0   | 1   | 1 | 1 | 0 | 0 | 0 |

| 37  | 0   | 0 | 1 | 0   | 0  | 1   | 0   | 1   | 32  | 0   | 0   | 1   | 0 | 0 | 0 | 0 | 0 |

| 119 | 0   | 1 | 1 | 1   | 0  | 1   | 1   | 1   | 112 | 0   | 1   | 1   | 1 | 0 | 0 | 0 | 0 |

|     | (d) |   |   |     |    |     |     |     |     | (e) |     |     |   |   |   |   |   |

| 110 | 0   | 1 | 1 | 0   | 1  | 1   | 1   | 0   | 104 | 0   | 1   | 1   | 0 | 1 | 0 | 0 | 0 |

| 118 | 0   | 1 | 1 | 1   | 0  | 1   | 1   | 0   | 112 | 0   | 1   | 1   | 1 | 0 | 0 | 0 | 0 |

| 113 | 0   | 1 | 1 | 1   | 0  | 0   | 0   | 1   | 112 | 0   | 1   | 1   | 1 | 0 | 0 | 0 | 0 |

| 109 | 0   | 1 | 1 | 0   | 1  | 1   | 0   | 1   | 104 | 0   | 1   | 1   | 0 | 1 | 0 | 0 | 0 |

**Fig. 3** a First two partner blocks (block 0 and block 10) in the original image matrix; **b** binary equivalent of each of the four pixels of block 0; **c** modified pixel values of block 0 after replacing three LSBs with 0s; **d** binary equivalent of each of the four pixels of block 10; and **e** modified pixel values of block 10 after replacing three LSBs with 0s

**Fig. 4 a** and **b** Application of 2D DWT using Haar wavelets into block 0 and block 10, respectively, resulting in the approximation coefficient matrix  $LL_1$  and detail matrices  $LH_1$ ,  $HL_1$ , and  $HH_1$  and **c** the 12-bit watermark generated from the five MSBs of the  $LL_1$  sub-band coefficient of block 0 and block 10 followed by a in-block parity-check bit *P* and its complement *V*

|           |                 |    | (b) | )   |     |     |     |     | (c) | g |    |    |    |

|-----------|-----------------|----|-----|-----|-----|-----|-----|-----|-----|---|----|----|----|

| (a)       |                 |    |     | 11  | 8   | 1   | 1   | .4  |     | D | 1  | 2  | 3  |

| Block No. | Mapping Block N | ю. |     | 15  | 12  | 5   |     | 2   |     | 4 | 5  | 6  | 7  |

| 0         | 11              |    |     | 3   | 0   | 9   |     | 6   | 1   | 8 | 9  | 10 | 11 |

| 10        | 9               |    | 7   |     | 4   | 13  | 10  |     | 1   | 2 | 13 | 14 | 15 |

|           | ( <b>d</b> )    | 30 | 58  | 62  | 64  | 65  | 57  | 55  | 56  |   |    |    |    |

|           |                 | 37 | 119 | 114 | 115 | 115 | 116 | 111 | 106 |   |    |    |    |

|           |                 | 38 | 121 | 115 | 109 | 112 | 110 | 114 | 104 |   |    |    |    |

|           |                 | 37 | 108 | 121 | 109 | 114 | 113 | 105 | 109 |   |    |    |    |

|           |                 | 38 | 115 | 124 | 118 | 110 | 118 | 106 | 112 |   |    |    |    |

|           |                 |    |     |     |     |     |     |     |     |   |    |    |    |

**Fig. 5** a Mapping blocks block 11 and block 9 of block 0 and block 10, respectively, found from the modified lookup table; **b** mapping blocks highlighted in the modified lookup table; **c** mapping blocks highlighted in the original block matrix; and **d** pixels of mapping blocks highlighted in the original image matrix

106 113 109

m

113

37

36 110 107 113 103 114 110 112

36 110 115 103 110 113 113 102

114 118

**Fig. 6** a Binary representation of each of the four pixels of the mapping blocks—block 11 and block 9; **b** embedding of the same 12-bit watermark into block 11 and block 9; **c** modified block 11 and block 9 after watermark embedding; and **d** modified block 11 and block 9 in the original image matrix

#### 3.4 Watermark Extraction: Tamper Detection, Localization, and Restoration

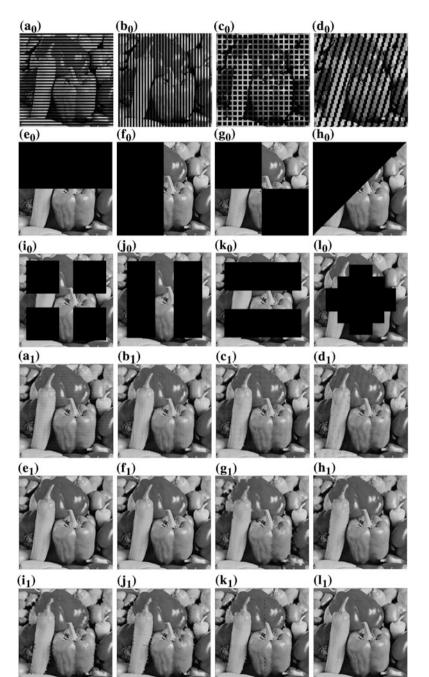

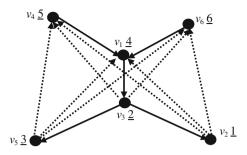

The watermarked image is tampered with different cropping attacks and covering and replacement attacks. Figure 7 represents the watermarked image of Fig. 6e cropped 25 % from center.

**Tamper detection and localization** A three-level hierarchical tamper detection and localization algorithm has been employed as proposed in [12].

Level 1 detection: For each non-overlapping block B of size  $2 \times 2$ ,

- 1. Retrieve the 12-bit watermark information from the block.

- 2. Get the parity-check bits p and v, respectively, from the 11th and 12th bits of the retrieved watermark.

- 3. Perform exclusive-OR operation on the 10 MSBs of the 12-bit watermark, denoted by p'.

- 4. If p = p' and  $p \neq v$ , mark block B valid; otherwise, mark it invalid.

Figure 8 demonstrates the level 1 tamper detection method.

*Level 2 detection*: For each block B marked valid after level 1 detection, check four triples (N, NE, E), (E, SE, S), (S, SW, W), and (W, NW, N) of the  $3 \times 3$  neighborhood of block B. If at least one triple has all of its blocks marked invalid, mark block B invalid.

*Level 3 detection*: For each block B marked valid after level 2 detection, if at least five of the  $3 \times 3$  neighboring blocks of block B are marked invalid, mark block B invalid.

**Recovery of invalid blocks** After the tamper detection process, all blocks in the image are marked either valid or invalid. Those invalid blocks need only to be recovered. A two-stage recovery scheme is applied for tamper recovery as follows:

Stage 1 recovery: For each non-overlapping block B of size  $2 \times 2$  pixels which is marked invalid,

1. Find the mapping block of B from the lookup table, denoted by  $\overline{B}$

| a) |     |     |     |     |     |     |     |

|----|-----|-----|-----|-----|-----|-----|-----|

| 26 | 58  | 58  | 68  | 67  | 58  | 50  | 60  |

| 39 | 114 | 116 | 117 | 118 | 117 | 108 | 109 |

| 35 | 122 | 115 | 106 | 114 | 108 | 115 | 106 |

| 38 | 109 | 124 | 0   | 0   | 118 | 108 | 105 |

| 34 | 116 | 121 | 0   | 0   | 114 | 105 | 118 |

| 38 | 118 | 118 | 109 | 118 | 109 | 118 | 109 |

| 35 | 106 | 106 | 114 | 98  | 114 | 106 | 114 |

| 38 | 109 | 118 | 102 | 111 | 114 | 118 | 102 |

| -  |     |     |     |     |     |     |     |

|----|-----|-----|-----|-----|-----|-----|-----|

| 26 | 58  | 58  | 68  | 67  | 58  | 50  | 60  |

| 39 | 114 | 116 | 117 | 118 | 117 | 108 | 109 |

| 35 | 122 | 115 | 106 | 114 | 108 | 115 | 106 |

| 38 | 109 | 124 | 0   | 0   | 118 | 108 | 105 |

| 34 | 116 | 121 | 0   | 0   | 114 | 105 | 118 |

| 38 | 118 | 118 | 109 | 118 | 109 | 118 | 109 |

| 35 | 106 | 106 | 114 | 98  | 114 | 106 | 114 |

| 38 | 109 | 118 | 102 | 111 | 114 | 118 | 102 |

Fig. 7 a Tampered image after cropping 25 % from the center of the watermarked image and **b** image in (a) with blocks highlighted

Fig. 8 Level 1 tamper detection and localization: **a** four pixels of block 5 with their binary equivalents; **b** four pixels of block 6 with their binary equivalents; **c** four pixels of block 9 with their binary equivalents; **d** four pixels of block 10 with their binary equivalents; and **e** localization of tampered block(s) after level 1 detection

- 2. If  $\overline{B}$  is valid, then  $\overline{B}$  is the candidate block, go to 5.

- 3. Find the mapping block of B's partner block, denoted by  $\overline{B}$ .

- 4. If  $\overline{B}$  is valid, then  $\overline{B}$  is the candidate block; otherwise stop, leave block B alone.

- 5. Retrieve the 12-bit watermark information from the candidate block.

- 6. If block B is located in the upper half of the image, the 5-bit representative information of block B starts from the first bit (the leftmost bit) of the 12-bit watermark; otherwise, it starts from the sixth bit.

- 7. Pad four 0s to the end of the 5-bit representative information to form a new 9-bit coefficient.

- 8. Perform the inverse DWT operation based on this coefficient as the approximation coefficient which generates a new block of size  $2 \times 2$ .

- 9. Replace block B with this new block and mark block B as valid.

The method for stage 1 recovery is shown in Fig. 9.

*Stage 2 recovery*: Recover the remaining invalid blocks after stage 1 recovery from the neighboring pixels surrounding them. Corresponding to a central block B being processed, the  $3 \times 3$  neighboring blocks can be found as directional triples (N, NE, E), (E, SE, S), (S, SW, W), and (W, NW, N) where each of the neighboring blocks being denoted as N<sub>1</sub>–N<sub>8</sub> from NW to W in a clockwise manner. After the two-stage recovery process, lost blocks are reconciled by interpolating pixel values.

Figure 10 presents the reconstructed image of Fig. 7 after stage 2 recovery.

| (a)[ | Tamm                  | how                   |    | famm                  |                | ] (b) |                | b7                    | <b>b</b> <sub>6</sub> | bs         | b4                    | b3  | b2                    | b1 | <i>b</i> <sub>0</sub> |     |

|------|-----------------------|-----------------------|----|-----------------------|----------------|-------|----------------|-----------------------|-----------------------|------------|-----------------------|-----|-----------------------|----|-----------------------|-----|

| ` '  | ramp                  |                       |    | Iapp                  |                |       | 35             | 0                     | 0                     | 1          | 0                     | 0   | 0                     | 1  | 1                     |     |

|      | Block                 | No.                   | B  | lock                  | No.            | 8     | 106            | 0                     | 1                     | 1          | 0                     | 1   | 0                     | 1  | 0                     |     |

| ł    | 2                     |                       | ~  |                       |                | 4     | 38             | 0                     | 0                     | 1          | 0                     | 0   | 1                     | 1  | 0                     |     |

|      | -                     |                       |    | 10                    |                |       | 109            | 0                     | 1                     | 1          | 0                     | 1   | 1                     | 0  | 1                     |     |

| l    | 5                     |                       |    | 12                    |                | ]     |                |                       |                       |            |                       |     |                       | (  | <b>d</b> )            |     |

| (c)  |                       |                       |    |                       |                |       |                |                       |                       |            |                       |     |                       |    | 106                   | 104 |

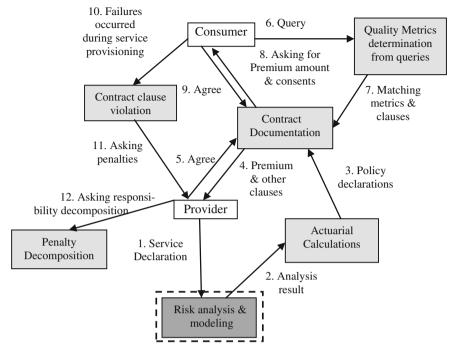

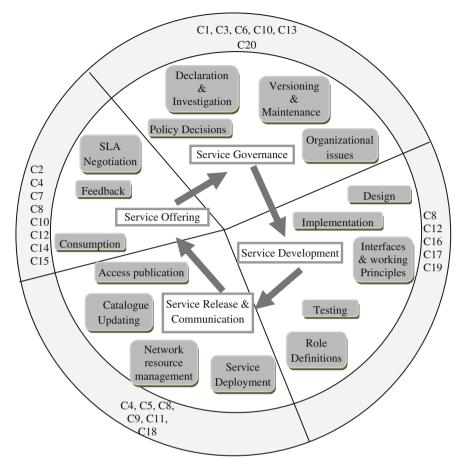

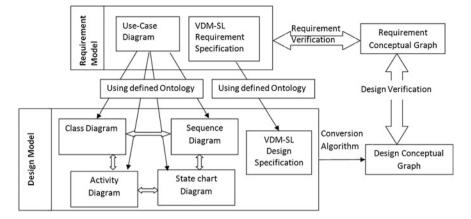

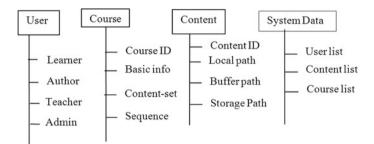

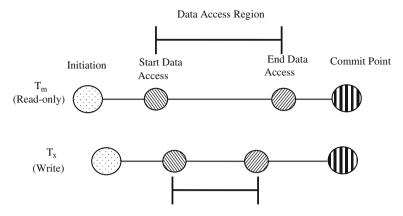

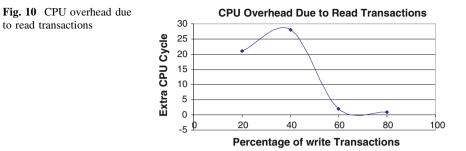

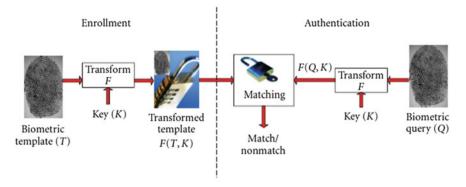

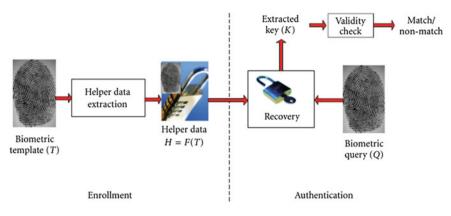

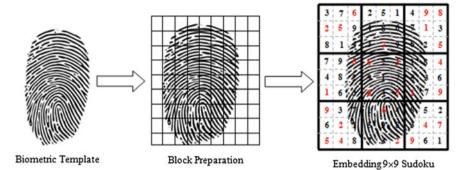

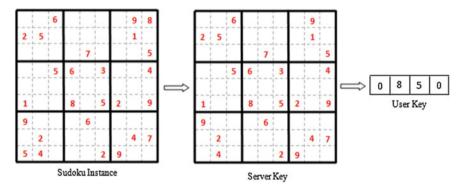

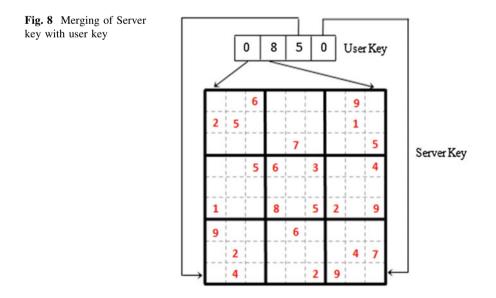

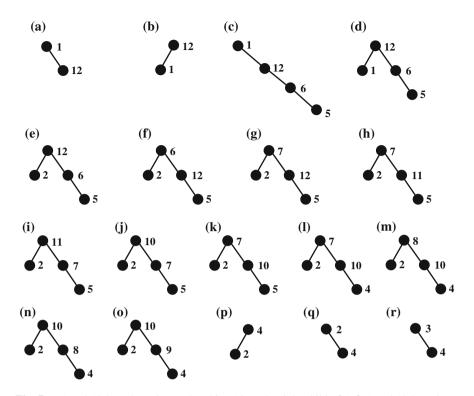

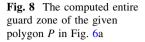

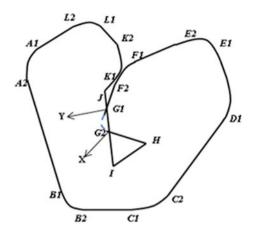

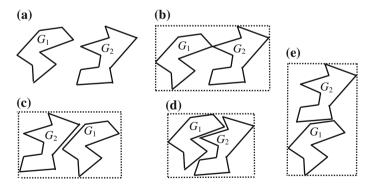

|      | <i>a</i> <sub>8</sub> | <i>a</i> <sub>7</sub> |    | <i>a</i> <sub>6</sub> | a <sub>5</sub> |       | a <sub>4</sub> | <i>a</i> <sub>3</sub> | 0                     | <b>1</b> 2 | <i>a</i> <sub>1</sub> |     | <i>a</i> <sub>0</sub> | Ì  | 104                   | 104 |