## FUNDAMENTALS OF SWITCHING THEORY AND LOGIC DESIGN

# Fundamentals of Switching Theory and Logic Design

# A Hands on Approach

by

#### JAAKKO T. ASTOLA

Institute of Signal Processing, Tampere University of Technology, Tampere, Finland

and

#### RADOMIR S. STANKOVIĆ

Dept. of Computer Science, Faculty of Electronics, Niš, Serbia

A C.I.P. Catalogue record for this book is available from the Library of Congress.

ISBN-10 0-387-28593-8 (HB) ISBN-13 978-0-387-28593-1 (HB) ISBN-10 0-387-30311-1 (e-book) ISBN-13 978-0-387-30311-6 (e-book)

Published by Springer, P.O. Box 17, 3300 AA Dordrecht, The Netherlands.

www.springer.com

Printed on acid-free paper

All Rights Reserved © 2006 Springer No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Printed in the Netherlands.

## Contents

| Preface                                  |            |                                    | xi              |

|------------------------------------------|------------|------------------------------------|-----------------|

| Ac                                       | Acronyms x |                                    |                 |

| 1. SETS, RELATIONS, LOGIC FUNCTIONS      |            |                                    |                 |

|                                          | 1          | Sets                               | 1               |

|                                          | 2          | Relations                          | 2               |

|                                          | -3         | Functions                          | 4               |

|                                          |            | Representations of Logic Functions | 9               |

|                                          | 1          | 4.1 SOP and POS expressions        | 13              |

|                                          |            | 4.2 Positional Cube Notation       | 16              |

|                                          | 5          | Factored Expressions               | 17              |

|                                          | 6          | Exercises and Problems             | 19              |

| 2. ALGEBRAIC STRUCTURES FOR LOGIC DESIGN |            |                                    | 21              |

|                                          | 1          | Algebraic Structure                | 21              |

|                                          | 2          | Finite Groups                      | 21              |

| 1                                        |            | Finite Rings                       | 24              |

|                                          | 4          | Finite Fields                      | 25              |

|                                          | 5          | Homomorphisms                      | 27              |

|                                          | 6          | Matrices                           | 30              |

|                                          | 7          | Vector spaces                      | 33              |

|                                          | 8          | Algebra                            | 37              |

|                                          | 9          | Boolean Algebra                    | 38              |

|                                          | 5          | 9.1 Boolean expressions            | $\frac{38}{40}$ |

|                                          | 10         | Graphs                             | 42              |

| 1                                        |            | Exercises and Problems             | 44              |

| vi                                                                   | vi FUNDAMENTALS OF SWITCHING THEORY AND LOGIC DESIGN |                                                                                          |            |

|----------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------|------------|

| 3.<br>FU                                                             |                                                      | NCTIONAL EXPRESSIONS FOR SWITCHING<br>FIONS                                              | 47         |

|                                                                      | 1                                                    | Shannon Expansion Rule                                                                   | 50         |

|                                                                      | 2                                                    | Reed-Muller Expansion Rules                                                              | 51         |

|                                                                      | 3                                                    | Fast Algorithms for Calculation of RM-expressions                                        | 56         |

|                                                                      | 4                                                    | Negative Davio Expression                                                                | 57         |

|                                                                      | 5                                                    | Fixed Polarity Reed-Muller Expressions                                                   | 59         |

|                                                                      | 6                                                    | Algebraic Structures for Reed-Muller Expressions                                         | 62         |

|                                                                      | 7                                                    | Interpretation of Reed-Muller Expressions                                                | 63         |

|                                                                      | 8                                                    | Kronecker Expressions                                                                    | 64         |

|                                                                      |                                                      | 8.1 Generalized bit-level expressions                                                    | 67         |

|                                                                      | 9                                                    | Word-Level Expressions                                                                   | 68         |

|                                                                      |                                                      | 9.1 Arithmetic expressions                                                               | 70         |

|                                                                      |                                                      | <ul><li>9.2 Calculation of Arithmetic Spectrum</li><li>9.3 Applications of ARs</li></ul> | 73<br>74   |

|                                                                      | 10                                                   | 11                                                                                       | 74<br>77   |

|                                                                      | 10                                                   | Walsh Expressions<br>Walsh Functions and Switching Variables                             | 80         |

|                                                                      | 11 $12$                                              | Walsh Series                                                                             | 80         |

|                                                                      | 12 13                                                | Relationships Among Expressions                                                          | 82         |

|                                                                      | 13                                                   | Generalizations to Multiple-Valued Functions                                             | 85         |

|                                                                      | 14 $15$                                              | Exercises and Problems                                                                   | 85<br>87   |

|                                                                      |                                                      |                                                                                          |            |

| 4. DECISION DIAGRAMS FOR REPRESENTATION OF 89<br>SWITCHING FUNCTIONS |                                                      |                                                                                          | 89         |

|                                                                      | 1                                                    | Decision Diagrams                                                                        | 89         |

|                                                                      | 2                                                    | Decision Diagrams over Groups                                                            | 97         |

|                                                                      | 3                                                    | Construction of Decision Diagrams                                                        | 99         |

|                                                                      | 4                                                    | Shared Decision Diagrams                                                                 | 102        |

|                                                                      | 5                                                    | Multi-terminal binary decision diagrams                                                  | 103        |

|                                                                      | 6                                                    | Functional Decision Diagrams                                                             | 103        |

|                                                                      | 7                                                    | Kronecker decision diagrams                                                              | 108        |

|                                                                      | 8                                                    | Pseudo-Kronecker decision diagrams                                                       | 110        |

|                                                                      | 9                                                    | Spectral Interpretation of Decision Diagrams                                             | 112        |

|                                                                      |                                                      | 9.1 Spectral transform decision diagrams                                                 | 112        |

|                                                                      |                                                      | 9.2 Arithmetic spectral transform decision diagrams                                      | 114        |

|                                                                      | 10                                                   | 9.3 Walsh decision diagrams                                                              | 115        |

|                                                                      | 10                                                   | Reduction of Decision Diagrams                                                           | 119<br>199 |

|                                                                      | 11                                                   | Exercises and Problems                                                                   | 122        |

| Ca | onten | ts                                                | vii |

|----|-------|---------------------------------------------------|-----|

| 5. | CL    | ASSIFICATION OF SWITCHING FUNCTIONS               | 125 |

|    | 1     | NPN-classification                                | 126 |

|    | 2     | SD-Classification                                 | 129 |

|    | 3     | LP-classification                                 | 133 |

|    | 4     | Universal Logic Modules                           | 137 |

|    | 5     | Exercises and Problems                            | 145 |

| 6. | SY    | NTHESIS WITH MULTIPLEXERS                         | 147 |

|    | 1     | Synthesis with Multiplexers                       | 149 |

|    |       | 1.1 Optimization of Multiplexer Networks          | 151 |

|    |       | 1.2 Networks with Different Assignments of Inputs | 153 |

|    |       | 1.3 Multiplexer Networks from BDD                 | 154 |

|    | 2     | Applications of Multiplexers                      | 157 |

|    | 3     | Demultiplexers                                    | 162 |

|    | 4     | Synthesis with Demultiplexers                     | 162 |

|    | 5     | Applications of Demultiplexers                    | 166 |

|    | 6     | Exercises and Problems                            | 168 |

| 7. | RE    | ALIZATIONS WITH ROM                               | 171 |

|    | 1     | Realizations with ROM                             | 171 |

|    | 2     | Two-level Addressing in ROM Realizations          | 176 |

|    | 3     | Characteristics of Realizations with ROM          | 180 |

|    | 4     | Exercises and Problems                            | 181 |

| 8. | RE    | ALIZATIONS WITH PROGRAMMABLE                      | 183 |

|    | LO    | GIC ARRAYS                                        |     |

|    | 1     | Realizations with PLA                             | 184 |

|    | 2     | The optimization of PLA                           | 186 |

|    | 3     | Two-level Addressing of PLA                       | 189 |

|    | 4     | Folding of PLA                                    | 191 |

|    | 5     | Minimization of PLA by Characteristic Functions   | 194 |

|    | 6     | Exercises and Problems                            | 196 |

| 9. | UN    | IVERSAL CELLULAR ARRAYS                           | 199 |

|    | 1     | Features of Universal Cellular Arrays             | 199 |

|    | 2     | Realizations with Universal Cellular Arrays       | 201 |

|    | 3     | Synthesis with Macro Cells                        | 205 |

|    | 4     | Exercises and Problems                            | 208 |

| viii                                                                 | FU | UNDAMENTALS OF SWITCHING THEORY AND LOGIC DES          | SIGN |

|----------------------------------------------------------------------|----|--------------------------------------------------------|------|

| 10. FIELD PROGRAMMABLE LOGIC ARRAYS 211                              |    |                                                        |      |

|                                                                      | 1  | Synthesis with FPGAs                                   | 221  |

|                                                                      | 2  | Synthesis with Antifuse-Based FPGAs                    | 222  |

|                                                                      | 3  | Synthesis with LUT-FPGAs                               | 224  |

|                                                                      |    | 3.1 Design procedure                                   | 225  |

|                                                                      | 4  | Exercises and Problems                                 | 233  |

| 11. BOOLEAN DIFFERENCE AND APPLICATIONS IN<br>TESTING LOGIC NETWORKS |    |                                                        | 235  |

|                                                                      | 1  | Boolean difference                                     | 236  |

|                                                                      | 2  | Properties of the Boolean Difference                   | 237  |

|                                                                      | 3  | Calculation of the Boolean Difference                  | 238  |

|                                                                      | 4  | Boolean Difference in Testing Logic Networks           | 242  |

|                                                                      |    | 4.1 Errors in combinatorial logic networks             | 242  |

|                                                                      |    | 4.2 Boolean difference in generation of test sequences | 246  |

|                                                                      | 5  | Easily Testable Logic Networks                         | 250  |

|                                                                      |    | 5.1 Features of Easily Testable Networks               | 251  |

|                                                                      | 6  | Easily Testable Realizations from PPRM-expressions     | 251  |

|                                                                      | 7  | Easily Testable Realizations from GRM-expressions      | 257  |

|                                                                      | 0  | 7.1 Related Work, Extensions, and Generalizations      | 263  |

| 8 Exercises and Problems                                             |    |                                                        | 265  |

| 12. SEQUENTIAL NETWORKS                                              |    |                                                        | 269  |

|                                                                      | 1  | Basic Sequential Machines                              | 271  |

|                                                                      | 2  | State Tables                                           | 274  |

|                                                                      | 3  | Conversion of Sequential Machines                      | 277  |

|                                                                      | 4  | Minimization of States                                 | 278  |

|                                                                      | 5  | Incompletely Specified Machines                        | 281  |

|                                                                      | 6  | State Assignment                                       | 283  |

|                                                                      | 7  | Decomposition of Sequential Machines                   | 287  |

|                                                                      |    | 7.1 Serial Decomposition of Sequential Machines        | 287  |

|                                                                      |    | 7.2 Parallel Decomposition of Sequential Machines      | 290  |

| 8 Exercises and Problems 29                                          |    |                                                        | 294  |

| 13. REALIZATION OF SEQUENTIAL NETWORKS29'                            |    |                                                        | 297  |

|                                                                      | 1  | Memory Elements                                        | 298  |

|                                                                      | 2  | Synthesis of Sequential Networks                       | 302  |

|                                                                      | 3  | Realization of Binary Sequential Machines              | 304  |

| Content | s                                              | ix  |

|---------|------------------------------------------------|-----|

| 4       | Realization of Synchronous Sequential Machines | 306 |

| 5       | Pulse Mode Sequential Networks                 | 309 |

| 6       | Asynchronous Sequential Networks               | 313 |

| 7       | Races and Hazards                              | 318 |

|         | 7.1 Race                                       | 319 |

|         | 7.2 Hazards                                    | 320 |

| 8       | Exercises and Problems                         | 322 |

| Referen | nces                                           | 325 |

| Index   |                                                | 339 |

Index

## Preface

Information Science and Digital Technology form an immensely complex and wide subject that extends from social implications of technological development to deep mathematical foundations of the techniques that make this development possible. This puts very high demands on the education of computer science and engineering. To be an efficient engineer working either on basic research problems or immediate applications, one needs to have, in addition to social skills, a solid understanding of the foundations of information and computer technology. A difficult dilemma in designing courses or in education in general is to balance the level of abstraction with concrete case studies and practical examples.

In the education of mathematical methods, it is possible to start with abstract concepts and often quite quickly develop the general theory to such a level that a large number of techniques that are needed in practical applications emerge as "simple" special cases. However, in practice, this is seldom a good way to train an engineer or researcher because often the knowledge obtained in this way is fairly useless when one tries to solve concrete problems. The reason, in our understanding, is that without the drill of working with concrete examples, the human mind does not develop the "feeling" or intuitive understanding of the theory that is necessary for solving deeper problems where no recipe type solutions are available.

In this book, we have aimed at finding a good balance between the economy of top-down approach and the benefits of bottom-up approach. From our teaching experience, we know that the best balance varies from student to student and the construction of the book should allow a selection of ways to balance between abstraction and concrete examples.

Switching theory is a branch of applied mathematics providing mathematical foundations for logic design, which can be considered as the part

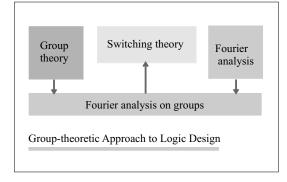

Figure 1. Switching theory and Fourier analysis.

of digital system design concerning realizations of systems whose inputs and outputs are described by logic functions. Thus, switching theory can be viewed as a part of Systems Theory and it is closely related to Signal Processing.

The basic concepts are first introduced in the classical way with Boolean expressions to provide the students with a concrete understanding of the basic ideas. The higher level of abstraction that is essential in the study of more advanced concepts is provided by using algebraic structures, such as groups and vector spaces, to present, in a unified way, the functional expressions of logic functions. Then, from spectral (Fourier-like) interpretation of polynomial, and graphic (decision diagrams) representations of logic functions, we go to a group-theoretic approach and to optimization problems in switching theory and logic design. Fig. 0.1 illustrates the relationships between the switching theory and Fourier analysis on groups. A large number of examples provides intuitive understanding of the interconnections between these viewpoints.

Consequently, this book discusses the fundamentals of switching theory and logic design from a slightly alternative point of view and also presents links between switching theory and related areas of signal processing and system theory. In addition, we have paid attention to cover the core topics as recommended in IEEE/ACM curricula for teaching and study in this area. Further, we provide several elective lectures discussing topics for further research work in this area.

JAAKKO T. ASTOLA, RADOMIR S. STANKOVIĆ

## Acronyms

| ACDD            | Arithmetic transform decision diagram        |

|-----------------|----------------------------------------------|

| ACDT            | Arithmetic transform decision tree           |

| BDD             | Binary decision diagram                      |

| BDT             | Binary decision tree                         |

| BMD             | Binary moment diagram                        |

| BMT             | Binary moment tree                           |

| *BMD            | *Binary moment diagram                       |

| DD              | Decision diagram                             |

| DT              | Decision tree                                |

| DTL             | Decision Type List                           |

| EVBDT           | Edge-valued binary decision diagram          |

| EVBDT           | Edge-valued binary decision tree             |

| ExtDTL          | Extended Decision Type List                  |

| $\mathbf{FFT}$  | Fast Fourier transform                       |

| FDD             | Functional decision diagram                  |

| FDT             | Functional Decision tree                     |

| FEVBDD          | Factored edge-valued binary decision diagram |

| FPGA            | Field-programmable gate array                |

| FPRM            | Fixed-polarity Reed-Muller expression        |

| KDD             | Kronecker decision diagram                   |

| KDT             | Kronecker decision tree                      |

| LUT             | Look-up-table                                |

| MPGA            | Mask programmable gate array                 |

| MTBDD           | Multi-terminal binary decision diagram       |

| MTBDT           | Multi-terminal binary decision tree          |

| PKDD            | Pseudo-Kronecker decision diagram            |

| PKDT            | Pseudo Kronecker decision tree               |

| PLA             | Programmable logic array                     |

| $\mathbf{PPRM}$ | Positive-polarity Reed-Muller expression     |

| POS             | Product-of-Sum expression                    |

| RAM             | Random-access memory                         |

| ROM             | Read-only memory                             |

| SBDD            | Shared binary decision diagrams              |

| SOP             | Sum-of-Product expression                    |

| STDT            | Spectral transform decision tree             |

| STDD            | Spectral transform decision diagram          |

| TVFG            | Two-variable function generator              |

| ULM             | Universal logic module                       |

| WDD             | Walsh decision diagram                       |

| WDT             | Walsh decision tree                          |

|                 |                                              |