Edited by Brian Bailey, Grant Martin and Thomas Anderson

# **Taxonomies** for the Development and Verification of **Digital Systems**

# Taxonomies for the Development and Verification of Digital Systems

Edited by Brian Bailey Grant Martin Thomas Anderson

# Taxonomies for the Development and Verification of Digital Systems

Library of Congress Cataloging-in-Publication Data

A C.I.P. Catalogue record for this book is available from the Library of Congress.

ISBN 0-387-24019-5 e-ISBN 0-387-24021-7 Printed on acid-free paper.

© 2005 Springer Science+Business Media, Inc.

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, Inc., 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now know or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks and similar terms, even if the are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed in the United States of America.

9 8 7 6 5 4 3 2 1 SPIN 11329473

springeronline.com

## **Table of Contents**

| Abbreviations and Acronyms                          | xi  |

|-----------------------------------------------------|-----|

| Contributors                                        | xv  |

| Preface                                             | xix |

| Chapter 1 Introduction                              | 1   |

| 1.1 What is a Taxonomy?                             |     |

| 1.2 About this Collection of Taxonomies             | 1   |

| 1.3 The History of the Taxonomies                   | 2   |

| 1.3.1 Early Model Taxonomy Work                     | 2   |

| 1.3.2 First Model Taxonomy Industrial Effort        | 3   |

| 1.3.3 Work within the VSIA                          | 4   |

| 1.3.4 Extension into other Areas                    | 4   |

| 1.3.5 Latest Revisions                              | 5   |

| 1.4 Taxonomy Organization                           | 5   |

| 1.4.1 Use of this Book                              | 6   |

| Chapter 2 Model Taxonomy                            | 9   |

| 2.1 Introduction                                    |     |

| 2.1.1 Taxonomy Definition                           |     |

| 2.1.1.1 Temporal Resolution Axis                    |     |

| 2.1.1.2 Data Resolution Axis                        |     |

| 2.1.1.3 Functional Resolution Axis                  |     |

| 2.1.1.4 Structural Resolution Axis                  | 15  |

| 2.1.1.5 Software Programming Resolution Axis        | 16  |

| 2.1.2 Internal/External (Interface) Concept         |     |

| 2.1.3 Note on Structure/Behavior/Interface Concepts | 19  |

| 2.1.4 Additional Attributes                         | 21  |

| 2.1.5 Vocabulary                                    | 21  |

| 2.2 General Modeling Concepts                       | 22  |

| 2.2.1 Primary Model Classes                         | 23  |

| 2.2.1.1 Functional Model                            |     |

| 2.2.1.2 Behavioral Model                            | 25  |

| 2.2.1.3 Structural Model                            | 26  |

| 2.2.1.4 Interface Model                             |     |

| 2.2.1.5 System-Level Interfaces                     |     |

| 2.2.2 Specialized Model Classes                     | 30  |

| 2.2.2.1 Performance Model                           | 30  |

| 2.2.2.2 Mixed-Level Model                           | 31  |

| 2.9.2.7 Firmware                                       | .57 |

|--------------------------------------------------------|-----|

| 2.9.3 Information Classes                              | .58 |

| 2.9.3.1 Application Data                               |     |

| 2.9.3.2 Control Data                                   | .58 |

| 2.9.4 Design Process Terms                             | .58 |

| 2.9.4.1 Synthesis                                      | .58 |

| 2.9.4.2 Simulation                                     |     |

| 2.9.4.3 Emulation                                      | .59 |

| 2.9.4.4 Interface-Based Design                         | .59 |

| 2.9.4.5 Top-Down Design                                | .59 |

| 2.9.4.6 Prototype                                      | .60 |

| 2.9.4.7 Physical Prototype                             | .60 |

| 2.9.4.8 Virtual Prototype                              | .61 |

| 2.9.4.9 Virtual Prototyping                            |     |

| 2.9.5 Design-Tool Terms                                | .62 |

| 2.9.5.1 Model                                          | .62 |

| 2.9.5.2 Emulator                                       | .62 |

| 2.9.5.3 Simulator                                      | .62 |

| 2.9.6 Verification and Test-Related Terms              | .62 |

| 2.9.6.1 Testbench                                      | .62 |

| 2.9.6.2 Test Vector                                    | .62 |

| 2.9.6.3 Functional Test                                | .63 |

| 2.9.6.4 Operational Test                               | .63 |

| 2.9.6.5 Boundary Scan                                  | .63 |

| 2.9.6.6 Signature Analysis                             | .63 |

| 2.9.7 Requirements and Specifications                  | .63 |

| 2.9.7.1 Specification                                  | .63 |

| 2.9.7.2 Executable Specification (E-Spec)              | .64 |

| 2.9.7.3 Requirement Specification (Req-Spec)           | .64 |

| 2.9.7.4 Executable-Requirement Specification (ER-Spec) |     |

| 2.9.7.5 Design Specification (Design-Spec)             |     |

| 2.9.7.6 Executable Design Specification (ED-Spec)      | .64 |

| 2.9.8 Reusability and Interoperability                 | .65 |

| 2.9.8.1 Reusability                                    |     |

| 2.9.8.2 Model Interoperability                         | .65 |

| 2.9.9 Interface-Related Terms                          |     |

| 2.9.9.1 General Interface Terms                        |     |

| Chapter 3 Functional Verification Taxonomy             | .69 |

| 3.1 Introduction                                       |     |

| 3.1.1 Classifications of Verification                  | .69 |

| 3.1.2 Definitions                                      |     |

| 3.2 Intent Verification                                | .71 |

| 3.2.1 Dynamic Verification                           | 71 |

|------------------------------------------------------|----|

| 3.2.1.1 Deterministic Simulation                     | 71 |

| 3.2.1.2 Random Pattern Simulation                    | 72 |

| 3.2.1.3 Hardware Acceleration                        |    |

| 3.2.1.4 Hardware Modeling                            | 73 |

| 3.2.1.5 Monitors                                     |    |

| 3.2.1.6 Protocol Checkers                            | 73 |

| 3.2.1.7 Expected Results Checkers                    | 73 |

| 3.2.2 Static Functional Verification                 | 74 |

| 3.2.3 Formal Verification                            |    |

| 3.2.3.1 Property/Model Checking                      | 74 |

| 3.2.3.2 Theorem Proving                              | 75 |

| 3.2.4 Dynamic-Formal Hybrid Verification             | 76 |

| 3.2.4.1 Symbolic Simulation                          | 76 |

| 3.2.4.2 Dynamic Formal Verification                  | 76 |

| 3.2.4.3 Formal Coverage                              |    |

| 3.2.4.4 Formal Constraint-Driven Stimulus Generation | 77 |

| 3.2.5 Hardware/Software Co-Verification              | 77 |

| 3.2.6 Emulation                                      | 78 |

| 3.2.7 Physical Prototyping                           | 79 |

| 3.2.7.1 Emulation Systems                            | 79 |

| 3.2.7.2 Reconfigurable Prototyping System            | 80 |

| 3.2.7.3 Application-Specific Prototype               | 80 |

| 3.2.8 Virtual Prototyping                            | 80 |

| 3.2.9 Verification Metrics                           | 81 |

| 3.2.9.1 Hardware Code Coverage                       | 81 |

| 3.2.9.2 Functional Coverage                          | 82 |

| 3.2.10 Definitions                                   | 82 |

| 3.3 Equivalence Verification                         | 87 |

| 3.3.1 Dynamic Verification                           |    |

| 3.3.1.1 Deterministic Simulation                     |    |

| 3.3.1.2 Expected Results Checkers                    | 87 |

| 3.3.1.3 Golden Model Checkers                        |    |

| 3.3.1.4 Regression Testing                           |    |

| 3.3.1.5 Verification Test Suite Migration            | 88 |

| 3.3.2 Formal Equivalence Checking                    | 90 |

| 3.3.2.1 Boolean Equivalence Checking                 | 90 |

| 3.3.2.2 Sequential Equivalence Checking              | 90 |

| 3.3.3 Physical Verification                          | 91 |

| 3.3.4 Definitions                                    | 92 |

| 3.4 VC Verification                                  | 93 |

| 3.5 Integration Verification                         | 94 |

|                                                      |    |

| 3.6       | Functional Verification Mapping                          | 94  |

|-----------|----------------------------------------------------------|-----|

| 3.7       | Summary                                                  | 96  |

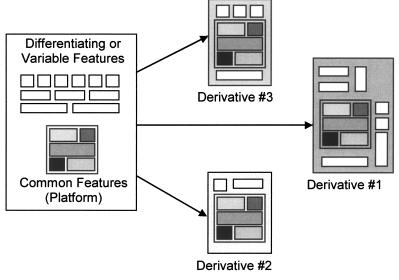

| Chapter - | 4 Platform-Based Design                                  | 103 |

| 4.1       | Platform-Based Design                                    | 103 |

| 4.1.      | .1 Introduction                                          | 105 |

|           | .2 Background and History                                |     |

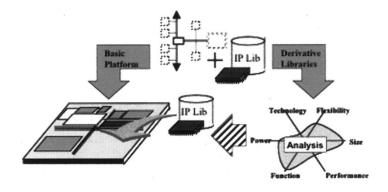

| 4.1.      | .3 Platform-Based Development System                     | 106 |

| 4.2       | Platform Taxonomies                                      |     |

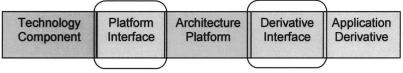

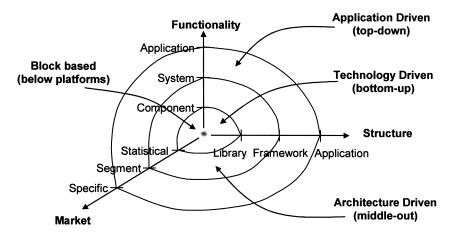

| 4.2.      | .1 Platform Object Complexity                            | 108 |

| 4         | 2.1.1 Complexity Levels                                  | 108 |

| 4         | 1.2.1.2 Interfaces                                       | 111 |

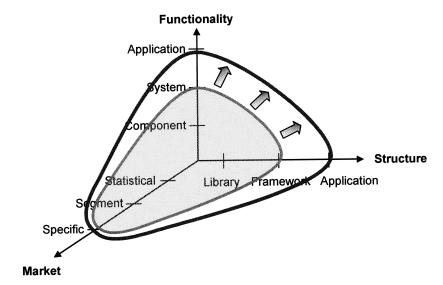

| 4.2.      | .2 Platform Specification Approaches                     | 113 |

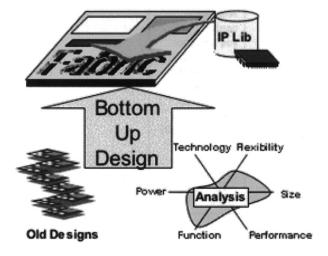

| 4         | 1.2.2.1 Technology-Driven (Bottom-Up) Specification      | 114 |

| 4         | 1.2.2.2 Architecture-Driven (Middle-Out) Specification   | 115 |

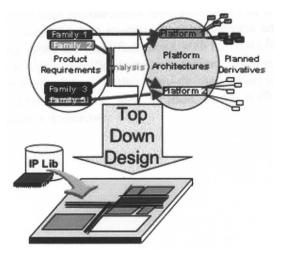

| 4         | 1.2.2.3 Application-Driven (Top-Down) Specification      | 116 |

| 4         | 1.2.2.4 Platform Specification Attributes                | 116 |

|           | 1.2.2.5 Metrics for Platform Specification Approaches    |     |

| 4         | 1.2.2.6 Alignment with Platform Specification Approaches | 127 |

| 4         | 1.2.2.7 On The Evolution of Platform Specifications      | 129 |

| 4.3       | Definitions                                              |     |

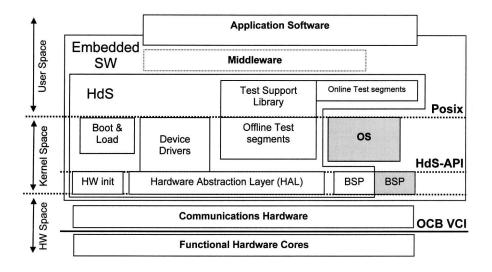

| Chapter   | 5 Hardware-dependent Software                            | 135 |

| 5.1       | Introduction                                             | 135 |

| 5.1.      | .1 Purpose of this Chapter                               | 135 |

| 5.1.      | .2 Intended Audience                                     | 136 |

| 5.2       | HdS Terms and Abbreviations                              | 136 |

| 5.2.      | .1 Basic HdS Definitions                                 | 137 |

| 5         | 5.2.1.1 HdS (Hardware-dependent Software)                | 137 |

| 5         | 5.2.1.2 HAL (Hardware Abstraction Layer)                 | 138 |

| 5.2.      | .2 HdS Terms                                             | 139 |

| 5.3       | HdS Taxonomy Axes                                        | 147 |

| 5.3.      | .1 Introduction                                          | 147 |

| 5.3.      | .2 Life Cycle Axis                                       | 148 |

| 5         | 5.3.2.1 System Development                               | 148 |

| 5         | 5.3.2.2 Software and Hardware Co-Development             | 148 |

| 5         | 5.3.2.3 Debug and Optimization                           | 148 |

| 5         | 5.3.2.4 Use                                              | 149 |

| 5         | 5.3.2.5 Retargeting                                      | 149 |

| 5         | 5.3.2.6 Variant or Derivative Development                | 149 |

|           | 5.3.2.7 Reuse                                            |     |

| 5.3.      | .3 Run-Time and Real-Time Axis                           | 149 |

| 5         | 5.3.3.1 Run Time                                         | 149 |

| 5         | 5.3.3.2 Real-Time                                        | 150 |

#### x Contents

| 5.3.3.3 Communication Mechanism                        | 150 |

|--------------------------------------------------------|-----|

| 5.3.4 Hardware Architecture Axis                       | 151 |

| 5.3.4.1 Architecture Synopsis                          | 151 |

| 5.3.4.2 OS Requirements                                | 156 |

| 5.3.4.3 Architecture of Software Defined by Hardware   | 157 |

| 5.3.4.4 Multiprocessor Architectures                   | 159 |

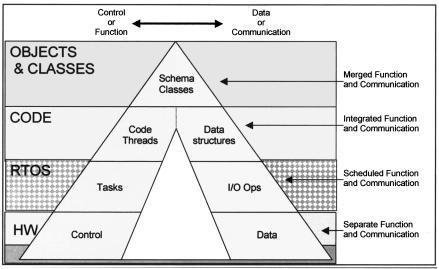

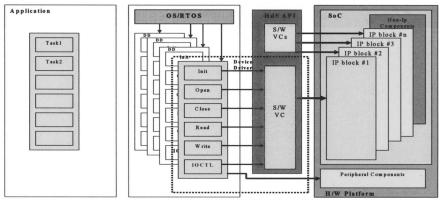

| 5.3.5 Software Layering Axis                           | 161 |

| 5.3.5.1 Basic model                                    | 161 |

| 5.3.5.2 Layers Included in the Layered API Model       |     |

| 5.3.5.3 Control, Data, Hardware, and Software Layering | 164 |

| 5.3.5.4 HdS API                                        | 165 |

| 5.3.5.5 Device Drivers                                 |     |

| 5.4 Conclusion                                         | 167 |

| References                                             | 169 |

| Index                                                  | 173 |

|                                                        |     |

## **ABBREVIATIONS AND ACRONYMS**

| ADC    | Analog-to-Digital Converter                      |

|--------|--------------------------------------------------|

| ALU    | Arithmetic-Logic Unit                            |

| API    | Application Programmers Interface                |

|        | (or Application Programming Interface)           |

| ASIC   | Application-Specific Integrated Circuit          |

| ASP    | Application-Specific Platform                    |

| BCA    | Bus-Cycle Accurate                               |

| BSP    | Board Support Package                            |

| CBR    | Constant Bit Rate                                |

| CC     | Cycle-Callable                                   |

| CISC   | Complex Instruction Set Computer                 |

| CPU    | Central Processing Unit                          |

| DAC    | Digital-to-Analog Converter                      |

|        | (or Design Automation Conference)                |

| DAT    | Dynamic-Address Translation                      |

| DDR    | Double Data Rate                                 |

| DEDI   | Data Exchange and Dispatcher Interface           |

| DFG    | DataFlow Graph                                   |

| DFT    | Design For Test (or Testability)                 |

| DFV    | Design For Verification                          |

| DMA    | Direct Memory Access                             |

| DRAM   | Dynamic Random-Access Memory                     |

| DRC    | Design Rules Check (or Checker)                  |

| DRL    | Dynamically Reconfigurable Logic                 |

| DSP    | Digital Signal Processor (or Processing)         |

| DUT    | Design Under Test                                |

| DUV    | Design Under Verification                        |

| DWG    | Development Working Group                        |

| EDA    | Electronic Design Automation                     |

| EDIF   | Electronic Design Interchange Format             |

| EEPROM | Electrically Erasable and Programmable Read-Only |

|        | Memory                                           |

| EIA    | Electronic Industries Alliance                   |

| EJTAG  | Extended JTAG (Joint Test Action Group)          |

| EPROM  | Erasable Programmable Read-Only Memory           |

| ERC    | Electrical Rules Check                           |

|        |                                                  |

## xii Abbreviation and Acronyms

| ESAPS | Engineering Software Architectures, Processes and |

|-------|---------------------------------------------------|

| EG 4  | Platforms for System-families                     |

| ESA   | European Space Agency                             |

| ESI   | European Software Institute                       |

| ESW   | Embedded SoftWare                                 |

| FIFO  | First In First Out                                |

| FFT   | Fast Fourier Transform                            |

| FPGA  | Field Programmable Gate Array                     |

| FPU   | Floating-Point Unit                               |

| FSM   | Finite State Machine                              |

| FTP   | File Transfer Protocol                            |

| FXP   | Functional XML Parser or Fixed Point              |

| GPP   | General-Purpose Processor                         |

| GPRS  | General Packet Radio System                       |

| GPS   | Global Positioning System                         |

| GUI   | Graphical User Interface                          |

| HAL   | Hardware Abstraction Layer                        |

| HDL   | Hardware Description Language                     |

| HDVL  | Hardware Design and Verification Language         |

| HdS   | Hardware-dependent Software                       |

| HLL   | High-Level Language                               |

| HTTP  | HyperText Transfer Protocol                       |

| HVL   | Hardware Verification Language                    |

| HW    | Hardware                                          |

| IC    | Integrated Circuit                                |

| ICE   | In-Circuit Emulator (or Emulation)                |

| I/O   | Input/Output                                      |

| IOCTL | IO ConTroL                                        |

| IP    | Internet Protocol (or Intellectual Property)      |

| ISA   | Instruction-Set Architecture                      |

| ISR   | Interrupt Service Routine                         |

| ISS   | Instruction-Set Simulator                         |

| JTAG  | Joint Test Action Group                           |

| LVS   | Layout versus Schematic                           |

| MCM   | Multi-Chip Module                                 |

| MMI   | Man-Machine Interface                             |

| MMU   | Memory Management Unit                            |

| MOC   | Model of Computation (or Model of Concurrency)    |

| MPEG  | Moving-Picture Experts Group                      |

| NMLO  | Non-Maskable Interrupt                            |

| OFLT  | OFf-Line Test                                     |

| OMT   | Object Modeling Technique                         |

|       | object wholening reeninque                        |

| OS        | Operating System                                            |

|-----------|-------------------------------------------------------------|

| OSCI      | Open SystemC Initiative                                     |

| PBA       | Printed Board Assembly                                      |

| PCB       | Printed Circuit Board                                       |

| PBD       | Platform-Based Design                                       |

| PBDS      | Platform-Based Design<br>System                             |

| PDA       | Personal Digital Assistant                                  |

| PLA       | Programmable Logic Array                                    |

| POSIX     | Portable Operating System Interface                         |

| PPP       | Point-to-Point Protocol                                     |

| PROM      | Programmable Read-Only Memory                               |

| PSoC      | Programmable System-on-Chip                                 |

| PV        | Programmers View                                            |

| PVT       | Programmers View with Timing                                |

| RAM       | Random Access Memory                                        |

| RASSP     | Rapid Prototyping of Application Specific Signal Processors |

| RISC      | Reduced Instruction-Set Computer                            |

| RMA       | Rate Monotonic Analysis                                     |

| ROM       | Read-only Memory                                            |

| RTL       | Register Transfer Level                                     |

| RTOS      | Real-Time Operating System                                  |

| RTTI      | Run-Time Type Information                                   |

| RTWG      | RASSP Terminology Working Group                             |

| SDF       | Synchronous DataFlow                                        |

| SEI       | Software Engineering Institute                              |

| SLD       | System-Level Design                                         |

| SLIP      | System-Level Design<br>Serial Line Interface Protocol       |

| SoC       |                                                             |

| SRAM      | System-on-Chip<br>Static Random-Access Memory               |

| SW        | Software                                                    |

| TF        | Technology Foundation                                       |

| 11        | or Timed Functional                                         |

| TLB       | Translation Look-aside Buffer                               |

| TLM       | Transaction-Level Modeling (or Model)                       |

| UART      | Universal Asynchronous Receiver/Transmitter                 |

| UML       | Unified Modeling Language                                   |

| UMTS      | Universal Mobile Telecommunications System                  |

| UTF       | Untimed Functional                                          |

| VBR       | Variable Bit Rate                                           |

| VDK<br>VC | Virtual Component                                           |

| VC<br>VCI | Virtual Component Interface                                 |

| VHDL      | VHSIC Hardware Description Language                         |

| VIIDL     | v 11510 Hardware Description Language                       |

## xiv Abbreviation and Acronyms

| VHSIC | Very High Speed Integrated Circuit |

|-------|------------------------------------|

| VLIW  | Very Long Instruction Word         |

| VM    | Virtual Memory                     |

| VSI   | Virtual Socket Interchange         |

| VSIA  | Virtual Socket Interface Alliance  |

| VoIP  | Voice over Internet Protocol       |

| VoP   | Voice over Packet                  |

| XML   | Extensible Markup Language         |

| WCET  | Worst-Case Execution Time          |

|       |                                    |

#### **CONTRIBUTORS**

The editors would like to apologize to anyone who contributed to this work, but whose name is not in the following lists.

#### **RASSP Taxonomy Working Group**

| Carl Hein           | Todd Carpenter      |

|---------------------|---------------------|

| Dr. Vijay Madisetti | Allan Anderson      |

| Arnold Bard         | J.P. Letellier      |

| Robert Klenke       | Dr. Greg Peterson   |

| Mark Pettigrew      | Dr. Perry Alexander |

| Dr. Geoffrey Frank  | Anthony Gadient     |

| Randy Harr          | Paul Kalutkiewicz   |

#### **VSIA Contributors**

Major Contributors: Bob Altizer Tom Anderson Wael Badawy Brian Bailey Robin Bhagat Neil Bryan Steve Burchfiel Ramesh Chandra Larry Cooke Mark Genoe M M Kamal Hashmi Anssi Haverinen Lisa Hsu Yaron Kashai

Other Contributors: Chris Adenyi-Jones Bert Aerts Jeff Barkley Mike Bartley Shay Ben-Chorin Robert Birch Chris Lennard Srinivas Madaboosi Roel Marichal Grant Martin Mehdi Mohtashemi Carlos Oliver-Yebenes Stephen Olsen Peter Paterson Frank Pospiech Richard Raimi Mandayam Srivas Colin Tattersall Jim Tobias Kumar Venkatramani

Ted Lehr Adriana Maggiore Daniel Martin Jean Mermet Dennis Mitchler Richard O'Connor

#### xvi Contributors

Sherri Bishop **Thomas Borgstrom** Mark Buchanan Annette Bunker Jean-Paul Calvez **David Courtright** Gialt de Jong Bryan Dickman John Emmitt Pierangelo Garino **Olivier** Giaume Dave Goldberg John Goodenough Martin Gregory Lisa M. Guerra Mariella Guerricchio Michael Hale **Thomas Harms** Takashi Hasegawa Frank Hellwig Merrill Hunt Takahide Inoue Mike Kaskowitz Holger Keding Peter Klapproth Klaus Kronlöf Joachim Kunkel Kun-Bin Lee

Mukund Patel Michael Payer C.Y. Pei Carl Pertry Mark Perver Ian Phillips Andrew Piziali Sreeni Rao Fabio Ricciato G. David Roberts Larry Rosenberg Jeff Russell Heinz-Josef Schlebusch Sandeep Shukla Juha-Pekka Soininen **Richard Stolzman** Ji-Suhn Suh Kari Tiensyrja Lee Todd Maura Turolla Ivo Vanderweerd Antonio Varriale Ralph von Vignau Glenn Vinogradov Janet Wedgwood John Wilson Parviz Yousefpour Frits Zandveld

#### **Companies and Organizations Represented by Contributors:**

0-In Design Automation Alcatel Analog Devices ARM ARPA BASYS Consulting Beach Solutions BOPS Cadence Design Systems Easics Nortel PalmChip Philips Semiconductors Qualis Design Rockwell RTI Center for System Eng. SCRA SES SIPAC Sonics

Contributors xvii

ECSI Fujitsu Elixent Georgia Inst. of Technology Honeywell Hewlett Packard IBM Infineon Intel IRESTE, University of Nantes Lockheed Martin Mentor Graphics Corp. Metamorfos Systems MIT Lincoln Labs Motorola National Semiconductor Naval Research Labs NCTU

Sony **ST Microelectronics** STARC Symbios Logic Synopsys Telecom Italia Lab Toshiba **TransEDA** University of Calgary University of Cincinnati University of Tennessee University of Texas, Austin **US Army** Verisity Design Verplex Virginia Tech University VSIA **VTT Electronics**

#### PREFACE

Yesterday's boards have become today's "Systems-on-Chips," consisting of specific architectures with embedded software components that can cooperate with dedicated co-processors. Due to the costly integration, processing and testing phases of the design cycle of such system chips, the modeling of the complete system or of specific aspects/components at various levels of abstraction is key. Moreover, high-level models allow us to specify and verify the system requirements, to analyze, explore, compare, and select different components of the system, and to explore several architectural choices. An essential element for efficient design practice is the capability to extensively re-use existing blocks or functions.

The goal of system, or high-level, models is to allow the user to evaluate and select the various components that are to be used for the System-on-Chip (SoC). Evaluation within the system environment, trade-off analysis, and subsequent decisions on items such as bandwidth, function, code size and performance can be determined within this environment in the context of the overall SoC specification.

However, meeting these system design challenges requires the unambiguous transfer of design information and communication about modeling modes between developers and providers. To address the need for conventions in modeling and terminology, this book is a collection of four taxonomies that were developed in a number of stages. This effort has included the work by a number of organizations, such as the Open SystemC Initiative (OSCI). Prior to this effort, the participating companies of the Virtual Socket Interface Alliance (VSIA) System Level Design (SLD) Development Working Group established several of the underlying taxonomies, of which the modeling taxonomy was based on the earlier Rapid Prototyping of Application Specific Signal Processors (RASSP) taxonomy and terminology efforts.

The modeling taxonomy contains an extended definition of a precision scale for the taxonomy, together with an elaborated classification of the different models used in design, implementation and verification at all levels, which are classified in system, architecture, hardware and software specific models. Most recently, multiple taxonomies covering different aspects of the design and verification process have been brought together and unified so that this single collection can cover a much larger portion of the whole space.

#### xx Preface

The underlying idea is that the design community, which includes system designers, software developers, product engineers, and hardware and verification design teams, will agree on a common acceptable nomenclature and classification of models, tools and techniques in use.

Where conflicting meanings exist in the different communities involved, the taxonomies in this collection endeavor to either choose the most common meaning or to synthesize an enveloping definition. Where this process is incomplete or impractical, all the relevant definitions and their context will be given, along with a recommended context-free default meaning.

## **CHAPTER 1 INTRODUCTION**

#### **1.1 What is a Taxonomy?**

The word *taxonomy* comes from the Greek *taxis*, meaning arrangement or division, and *nomos*, meaning law. Thus taxonomy is the science of classification according to a pre-determined system. The Webster online dictionary [WEB] defines taxonomy as:

A systematic arrangement of objects or concepts showing the relations between them, especially one including a hierarchical arrangement of types in which categories of objects are classified as subtypes of more abstract categories, starting from one or a small number of top categories, and descending to more specific types through an arbitrary number of levels.

Perhaps the most famous taxonomy is that created by the Swedish scientist Carl Linnaeus, who managed to create a classification for all living things. That classification, first published in 1735, is still in use today although with numerous modifications. In 1966, Flynn created a taxonomy for computer architectures that categorizes computers based on their streams of information. Many variants of this have since been created.

### **1.2** About this Collection of Taxonomies

Differing terminology has created confusion among Electronic Design Automation (EDA) tool vendors, component providers, semiconductor companies, and system houses. Some organizations use many common modeling terms with divergent meanings, while others use different words to describe the same type of models. Without a common language, the complete IC design community cannot effectively communicate, and the evaluation, selection, and validation of models and designs will be incompatible, and more difficult than necessary.

#### 2 Chapter 1

## **1.3** The History of the Taxonomies

Taxonomies such as the ones in this book do not just get created by a single group of people; instead they evolve over time, with each group adding a further level of refinement or understanding about the problem. At the same time, the industry moves on and what may have worked in the past needs to be updated to address new situations or emerging technologies. These taxonomies are no different and have already been through a number of significant stages of development and levels of refinement. The production of this book is just one of those stages, and will no doubt not be the last. With its publication, these taxonomies will become available to a much wider audience than in the past, and that is likely to lead to the identification of any number of possible problems, suggestions for improvement, refinements and corrections.

As designers and developers use these taxonomies, the editors expect that the definitions may be found inadequate in some respects, or not fully in line with evolving design practice. *We encourage feedback in order to improve the taxonomy definitions*. For the latest updates to this document, and discussion about any of the definitions given in any of the four taxonomies, the reader should go to the www.edataxonomy.com Web site.

## 1.3.1 Early Model Taxonomy Work

In the academic community, a number of model definition approaches were proposed and considered for use in the original formation of the precursors for the modeling taxonomy. Three of those model definition approaches (shown in Table 1-1) were examined and compared, feature for feature. The RASSP taxonomy (RTWG) is also shown in Table 1-1; it became the basis for the second stage of development of this taxonomy–the VSIA effort.

The Ecker and Madisetti spaces share two axes of comparison, while their remaining axes do not directly correspond. Both have an axis for time resolution and a second axis representing the resolution of data values in a model.

Ecker calls the second axis "Value," while Madisetti calls it "Format." The Y-chart's "Functional Representation" axis expresses some information that is similar to the value-format axes. However, the Y-chart's Functional-Representation axis does not exactly correspond to the value-format axes because it contains information about functionality as well.

The third axis of the Ecker cube is similar to the "Structural Representation" axis of the Y-chart but has no corresponding axis in the Madisetti case. (The latter situation arises intentionally.)

None of the remaining axes of the taxonomies directly correspond. The Y-chart seems limited to only the logic level. None of the taxonomies appeared to have directly addressed the hardware/software co-design aspect.

| Source -<br>Taxonomy            |                           |               |                                   | Axes                              |                                  |       | A. 4. 4. 4. 4. 4. 4. 4. 4. 4. 4. 4. 4. 4. |

|---------------------------------|---------------------------|---------------|-----------------------------------|-----------------------------------|----------------------------------|-------|-------------------------------------------|

| Gajski and<br>Kuhn: Y-<br>chart |                           |               | Structural<br>Represen-<br>tation | Functional<br>Represen-<br>tation | Geometric<br>Represen-<br>tation |       |                                           |

| Ecker:<br>Ecker Cube            | Timing                    | Value         | View                              |                                   |                                  |       |                                           |

| Madisetti<br>Taxonomy           | Timing                    | Format        |                                   |                                   |                                  | Value | State                                     |

| RASSP<br>RTWG<br>Taxonomy       | Timing<br>Resolu-<br>tion | Data<br>Value | Structural<br>Resolution          | Functional<br>Resolution          |                                  |       | Intern/<br>Extern                         |

Table 1-1 Comparison of Prior and RASSP Taxonomy Concepts

### **1.3.2 First Model Taxonomy Industrial Effort**

The concept of a model taxonomy for the industry was initiated by efforts of the RASSP Terminology Working Group (RTWG), which was formed on January 10, 1995, at the RASSP Principal Investigators meeting in Atlanta, Georgia, to address modeling and terminology challenges. The core working group consisted of members representing the two prime contractors, a technology base developer, the educator facilitator, and the government.

The RTWG's mission was to develop a systematic basis for defining model types and to use this basis for concisely and unambiguously defining a terminology that describes the models that are used within a RASSP design process. One crucial requirement for the basic taxonomy was that it must be useful for selecting, using, and building appropriate interoperable models for specific roles in a RASSP design process. Models are used for several purposes, which include specifying or documenting design solutions and testing and simulating proposed designs. The terminology was based on the commonly documented and applied vocabulary in the digital electronic design and modeling industry at that time, and it drew heavily from related earlier and ongoing efforts by the EIA, ESA, and the U.S. Army and Navy, and from the annals of related literature from the Design Automation Conference (DAC), VHDL International User's Forum, and text books.

Previous efforts focused on narrower domains than RASSP. RASSP spanned many domains, including parallel processing; multi-board and multi-chassis systems; software; digital signal processing; and application

#### 4 Chapter 1

functions, with strong interaction with other domains such as analog, mechanical, physical, and RF.

## 1.3.3 Work within the VSIA

The System-Level Design Development Working Group (SLD DWG) of the VSIA modified and augmented the previously defined terminology sets, broadened parochial definitions, distinguished overlapping definitions, equated close synonyms, removed inapplicable terms, added needed or missing terms, clarified poorly defined or misunderstood terms, and suggested new terms as replacements or synonyms to outdated terms. When appropriate existing definitions were not available for significant terms used within the VSIA community, the SLD DWG attempted to create them. At different places the definitions were illustrated by concrete examples.

Compared with the RASSP document, this taxonomy and model classification proposal was further elaborated by the working group by adding more appropriate details on the different precision scales, and by providing more concrete examples for each possible precision. In addition, several additional models were added, such as computational, architectural, and software models. Some of these extensions were adopted by the RTWG during the active period of work. Two major revisions of this taxonomy were released to the public through VSIA.

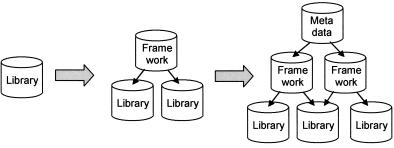

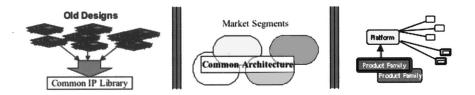

#### 1.3.4 Extension into other Areas

The launch of the VSI model taxonomy document was highly successful and for most months was the most downloaded document from the VSIA web site. For quite a few months it exceeded the number for all of the other documents combined. Based on this success, other groups that were started within the VSIA took, as their first goal, the production of similar documents for their particular spaces. This served to ensure that all of the working group members had a consistent language when talking about the follow-on documents and standards, and served as a learning process to uncover places of contention in the industry. Three other working groups produced these documents—the Functional Verification DWG, the Platform-Based Design DWG, and the Hardware-dependent Software DWG. Perhaps the most contentious of these was the document that came out of the Platform-Based Design working group, as it showed the enormous range of opinions and definitions for platforms in the community. All four of the VSIA-developed taxonomies are contained within this collection.

#### **1.3.5 Latest Revisions**

This book provides another chapter in the life of the taxonomies. Since the time of the last major revision to the model taxonomy, a number of new organizations have emerged that have added new terms, modified the boundaries set for certain abstractions, and defined completely new levels of abstraction. This revision considers the current state of the efforts within the Open SystemC Initiative's (OSCI) Transaction Level Modeling (TLM) group. While this group had not completed its standard at the time of this book's publication, and contains two rather different ways that the standard could evolve, both of these sets of models have been included as they provide concrete illustrations of a number of the model types.

In the earlier forms of the modeling taxonomy, little attention had been paid to the variety of models of computation that are used as the basis behind many of the models described in the taxonomy. A more encompassing description of these has been added, based on classifications and analysis approaches of Axel Jantsch, KTH, Sweden.

Significant updates have been made in all four taxonomies to reflect evolution in the industry since original publication, to incorporate recent work, and to better unify style and organization.

Given VSIA's focus on design reuse, the original taxonomies were largely developed from the perspective of a Virtual Component (VC), a design block intended for reuse in multiple chips. Since most of the terminology and model definitions in the taxonomies are applicable to any design, most references to VCs have been removed in this book. However, there are a number of cases in which the distinction between a reusable design block and the entire chip in which it is integrated are important, and in these cases the term has been retained.

## 1.4 Taxonomy Organization

This taxonomy collection is composed of four primary sections, each one dealing with a specific aspect of the design and verification process. The four sections are:

- **Model taxonomy:** this section of the collection defines the core of the model taxonomy. It provides a definition for each of the commonly used levels of abstraction and provides examples of how these are used within the industry.

- Functional Verification Taxonomy: this section deals with one of the biggest challenges in electronic system development-verifying

#### 6 Chapter 1

the functionality of a reusable design in different chips, in different physical implementations, and in different development environments. There are a number of tools, techniques, and methodologies used to accomplish the functional verification of the component and the system. This section of the collection is intended to provide a classification of the various verification technologies and uniform definitions of terms used in these technologies.

- **Hardware-dependent Software:** this section deals with software, which plays an increasing role in SoC design. Therefore, reusability considerations must now address software layers as well as hardware. At the lowest level, a software layer interacts directly with the interface offered by the SoC's hardware platform. This software layer is defined to hide hardware specifics from the upper layers of software. Hardware-dependent software (HdS) can be viewed from the perspective of a software platform, hardware platform, or SoC design life cycle.

- **Platform-Based Design:** this section contains the latest understanding regarding this newly emerging area. It attempts to define the key concepts of platform-based design and their meanings, and the attributes by which platforms can be classified. Its scope is all platform-related development at any level within an SoC.

In addition, other sections of the document provide definitions for the standard vocabulary used within the industry.

## 1.4.1 Use of this Book

This collection of taxonomies is intended to be of use to a wide audience. First, model developers, whether third-party or within large companies, can begin by re-classifying the various models provided with their components into the categories offered by the model taxonomy, and can refer to this book for explanations. Model integrators can then begin to request models according to the taxonomy definitions. EDA suppliers and designmethodology developers at semiconductor and systems companies can begin factoring these model types into their tools and methods. They can also use the taxonomy to clarify which types of models fit into their design flows, and how.

We also hope that evolution in design practices for components and component integration into SoCs will help identify which model types are critical to the methodologies, and which models may only be peripheral to them. This will help reduce the number of models requested and required to permit efficient design, and also clarify their characteristics along the resolution axes. Keeping the number of model types to a minimum will be a significant help in the evolution of the electronics industry toward a reuseoriented mindset by reducing the overhead required to produce a complete reusable design package.

The final uses of this book could be for educational purposes, and in industry standards efforts based on these model types. In this domain, the clarifications offered by the taxonomies and the definitions of models should help in teaching and using a better common language, which will assist in education, and help standards groups make quicker progress. Experience in system-level design across industry, university, and government groups indicates that a large part of the initial time involved in their activities is spent trying to agree on language, definitions, and model types. This book should reduce the time spent coming to a consensus on these terms.

## **CHAPTER 2 MODEL TAXONOMY**

#### 2.1 Introduction

A modeling taxonomy provides a means to categorize models according to a set of attributes. The attributes should be useful in distinguishing models intended for distinctly different purposes. The taxonomy is used to establish formal definitions that are concise and unambiguous for the various model types. Descriptions and definitions for many of the terms used in this document are provided in Section 2.9, "Supporting Terms" of this chapter.

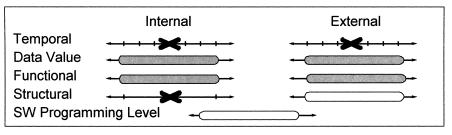

### 2.1.1 Taxonomy Definition

This taxonomy represents the model attributes that are relevant to designers and model users. It consists of a common set of attributes to independently describe a model's internal and external resolution. This taxonomy is based on terminology readily understood and used by designers.

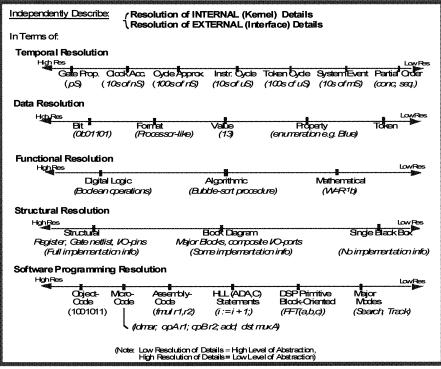

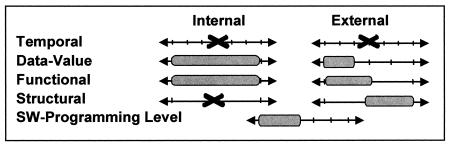

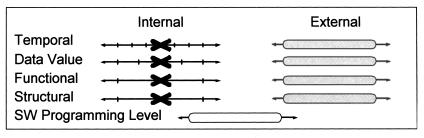

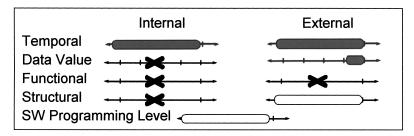

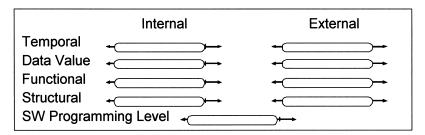

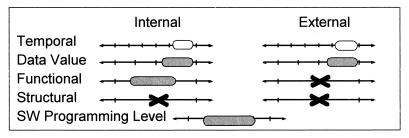

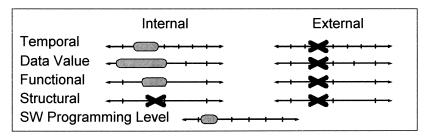

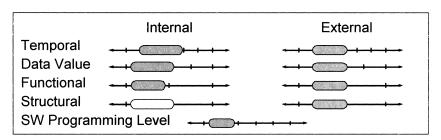

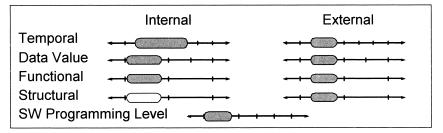

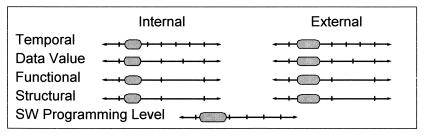

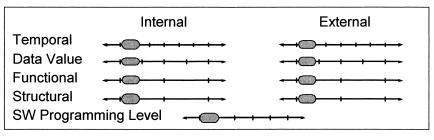

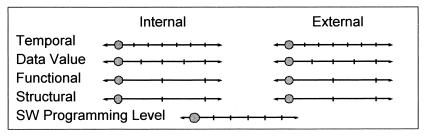

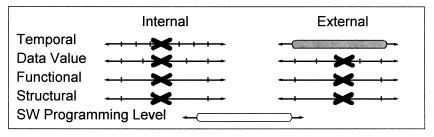

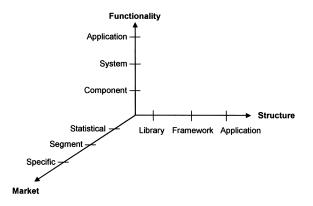

The axes explicitly characterize a model's relative resolution of details for important model details. The taxonomy axes, shown in Figure 2.1, identify four model characteristics:

- Temporal detail

- Data value detail

- Functional detail

- Structural detail

The temporal and data axes are clearly orthogonal to each other, and to the other two axes. In contrast, the relationship of the functional and structural axes is not totally orthogonal, but it is useful to consider these two aspects of a model through the different attribute filters even though they may be connected in some ways.

Distinguishing between the internal and external views is important in selecting, using, and building models because it enables clarity and precision. Previous terminologies often mixed attributes, as viewed from inside a model, with similar attributes, as viewed from the model's interface boundary.

#### 10 Chapter 2

- Internal resolution references how a model describes the timing of events, functions, values, and structures of the elements that are contained within the boundaries of the modeled device.

- External resolution describes how a model describes the interface of the modeled device to other devices. The external aspects refer to the input/output (I/O) details at the boundary of the modeled device. The external details relate to how the model describes a device's interaction with devices to which it connects. External details may include timing and functional aspects, commonly referred to as protocols, as well as port structure and signal values. All of these aspects may be abstracted to various levels in a model.

Because each aspect is specified from both an internal and external viewpoint, the taxonomy effectively contains eight attributes describing a model's descriptive level-*internal attributes:* temporal, value, structure, and function resolution; and *external attributes:* temporal, value, structure, and function resolution. The *resolution* of an axis defines the expected *precision* of the models at various points on the axis-the model itself would define its *accuracy* at that resolution or precision. These three terms, as used with respect to the axes and models, can be used in similar, confusable ways, but the recommendation is that accuracy is used for models, and precision or resolution is used for axis-related measures.

This set of eight attributes does not address the hardware or software codesign aspect of a model, because it does not describe how a hardware model appears to software. Therefore, the set is augmented with a ninth axis (shown at the bottom of Figure 2.1). This axis can either represent the level of software programmability of a hardware model or the abstraction level of a software component in terms of the complementary hardware model that will interpret it. This axis is not orthogonal to the temporal, data, functional, and structural axes, but is intended to make clear, in classical software notations, the level of the model in its software aspect. Thus, it is an aggregate property that reflects, to some extent, characteristics defined along the temporal, data, functional, and structural axes. Within this model taxonomy, the software programming resolution is clearly an approximation. For a full definition of the relationship between hardware and software, it is advised that you follow the definitions given in Chapter 5, "Hardwaredependent Software."

Figure 2.1 Taxonomy Axes

Although Sections 2.1 through 2.7 of this chapter define the vocabulary terms graphically to show their applicable coverage, a convenient method for specifying a particular model's information content is to use the Internal/External (temporal, value, function, structure) notation.

For example, the content of a particular RTL model could be specified as:

Internal(temporal=Gate Propagation, data=Bit, function=Digital Logic, structure=register), External(temporal=Clock Accurate, data=Bit, function=Digital Logic, structure=I/O Pins), SW-Program(Programming-Level=Assembly-Code)

For contrast, an example of a particular algorithm model could be specified as:

Internal(temporal=System Token, data=Value, function=Algorithmic, structure=none), External(temporal=none, data=Value, function=none, structure=none), SW-Program(Programming-Level=none)

## 2.1.1.1 Temporal Resolution Axis

The temporal resolution axis represents the degree of accuracy of events that are modeled along a time scale, or in time. There are several levels of precision implied on this axis:

- **Partially ordered event accurate**: at this level of precision, events have a complete or partial ordering relationship in terms of their starting and finishing, without specifying precisely when those events start and finish in terms of any temporal units. Thus, the precedence of events is indicated. This level of precision is common in dataflow analysis. The partial ordering means that independent threads of event occurrence may only be ordered within the thread and not have any ordering relationship between the threads.

- System event accurate: at this level, start and end times of major system functions are indicated in some units that may represent thousands or millions of "clock" cycles.

- **Token cycle accurate**: (also may be called *data cycle*) at this level, which especially applies in periodic and dataflow kinds of systems, precision of events is defined in terms of the regular progress of data and control tokens that "flow" from one functional processing unit to the next. For example, an image processing system may process, in a regular way, X frames of image data per second, and the periodic processing of image frames (tokens) defines a periodic "clock" interval: frame 1, frame 2, frame 3, and so on.

- **Instruction cycle accurate**: at this level, events are specified in terms of the processing of an instruction stream or transaction. This is more precise than the token cycle, in that several operations may be required to process one data token.

- Cycle-approximate accurate: at this level, approximate cycle counts are available for each operation, transaction or message that is processed, in terms of a system "clock." For example, a processor model may not completely model every aspect of the processing of an instruction stream such as the modeling of pipelining and cache effects. This means that cycle counts produced and accumulated may not be completely accurate, and thus the use of the term "cycle-approximate."

- Cycle-accurate: at this level, accurate cycle counts are available for each operation, transaction or message that is processed, in terms of a regular system clock. Events occurring during the processing of

such operations are indicated with exact precision as to which clock cycle they occur in.

• Gate propagation accurate: at this level, event starting and ending times are defined in terms of precise time units within clock cycles-for example, nanoseconds (ns) or picoseconds (ps)-not just on clock cycle edges or boundaries. The accuracy of these event timings depends on the degree of accuracy of the circuit level and the interconnect models used to predict them.

The concept of the "delta" cycle, which enables instantaneous concurrency, exists for all levels of abstraction. This is sometimes referred to as a zero-time sequence. Delta-cycles are particularly used in discrete event simulators such as HDL simulators although also used in many other simulation models and tools.

#### 2.1.1.2 Data Resolution Axis

The data resolution axis represents the precision with which the formats of values are specified in a model. The contents of a register could be described at these levels of resolution, from high to low:

- Binary (for example, 0b111)

- Signed integer (for example, -1)

- Enumerated (for example, blue)

Note that resolution is analogous to precision, as distinguished from accuracy. Each representation is equally accurate; however, the first case resolves the value closer to the form actually contained in the target device. The more abstract the representation of a value, the fewer implementation details are resolved.

The different precision items on this axis are as follows:

- **Token**: The token precision level is the highest abstraction level for data representation, containing no implementation (structure, size, values, and so on) details at all. The amount of information it contains is completely unspecified.

- **Property**: An example of a property precision is an enumeration: you decide that the datum "color" will have the properties "red," "blue" and "green". You may do this via an enumeration (which gives you some ordering properties), or you can do it in some other way (such as a string plus some object methods). This data format includes user-specified data formats based on previously defined or standard data formats (at a lower abstraction level).

- Value: At the value level, there are no implementation details. Although the value may be an integer or real, the details as to how

14 Chapter 2

this is represented, such as fixed point floating point, are not described at this level.

- Format (Processor-Like): A more detailed data precision level is the processor-like data format, for example, a "big-endian" or "littleendian" formatting of addressing the actual byte orders. This level includes such format concepts as whether a value is fixed-point or floating-point (with fixed mantissa and exponent), and so on.

- **Bit Logical:** Here, the final representation can be used on a bit-bybit basis. For each bit, its logical value may include binary and multi-valued representations. More details can be added in the possible values that each bit can represent (such as 1, O, X, Z, and so on).

A composite is a representation that is formed by a combination of types.

#### 2.1.1.3 Functional Resolution Axis

The functional resolution axis represents the level of detail with which a model describes the functionality of a component or system. A digital filter component could be represented by these levels of resolution, from high to low:

- **Mathematical Relationships:** At this level of abstraction, the functionality is represented as a set of mathematical equations, without sequencing, except for that defined by the rules of precedence for arithmetic equations.

- Algorithmic Processes: At this level, the selection of the algorithm will be made, such as a bubble-sort procedure. There are currently no details on the way this algorithm will be implemented. The algorithmic precision includes sequencing, since the ordering of operations and control flow is a key criterion for selection. The algorithm may be expressed in a number of ways, including decomposition into major functional portions linked in a network (for example, a dataflow diagram, or a process network). However, the structure of this decomposition does not necessarily imply anything about the implementation of a function: its implementation may be done in a completely different way. Any algorithmic decomposition here may be purely for convenience in defining the function.

- **Digital Logic/Boolean Operation**: At this level, the functionality will be specified at the level of Boolean operators (AND, OR, NOT, and so on). Thus the structural content and resolution of this type of model would probably be high.

#### 2.1.1.4 Structural Resolution Axis

The structural resolution axis represents the level of detail with which a model describes how a component is constructed from its constituent parts. An integrated circuit could be represented at these levels of resolution, from high to low:

- No Implementation Information:

- No structural information-one large block

- Some Implementation Information:

- Connection of large blocks, such as an ALU and register files

- Connection of computer networks

- Full Implementation Information:

- Connection of simple units, such as logic gates

- Connection of composite units, such as flip-flops

- Connection of more complex units, such as registers and multipliers; at this level the block diagram has been further expanded into basic operators such as adders, multipliers, shifters, and so on, or even into more detailed granularity such as logic gates

Structural resolution is not limited to the physical implementation of integrated circuits described in the previous examples. As in the definition, a model can be built out of constituent parts in non-physical ways. A design block that is implemented entirely as software is built out of sub-components such as procedures and processes linked in complex networks.

A dataflow function, implemented by mapping to dedicated hardware blocks, may have a one-to-one relationship between a functional decomposition and the basic implementation structures that realize each function.

The concept of black-box and gray-box models has some similarities to the structural resolution axis. A black-box model hides all the internal structure within the component. This is identical to the resolution level "no implementation information" on the structural resolution axis. A gray-box model is more complex. Some of the internal structure within the component is exposed, but the model hides most of the detail of combinational logic. Thus, a gray-box model contains all sequential devices, and represents combinational logic between sequential device pairs by timing arcs. This is a more complex version of structure than is contained on the current structural resolution axis; thus, these concepts are not completely unified.

#### 2.1.1.5 Software Programming Resolution Axis

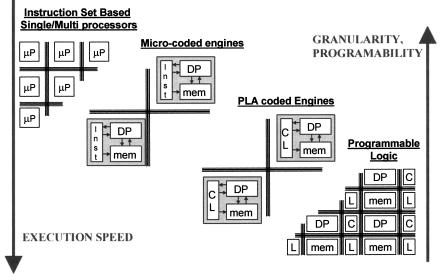

The software programming resolution axis is the granularity level of software instructions that the model of a hardware component interprets in executing target software. For instance, a network-performance model only interprets instructions on the level of dataflow primitives, such as matrix invert, vector multiply, or Fourier transform. Such primitives represent hundreds of lines of source code, but are interpreted as a single instruction in terms of a time-delay by a network performance model. An instruction-setarchitecture (ISA) model interprets individual assembly (or object code) instructions. In this sense, the ISA model is programmable at a much finer granularity, or higher precision, than the network-performance model.

At the lowest extreme, a model of a microcode programmable processor is programmable at an even lower level of granularity than the ISA model because it allows control of individual register and multiplexer structures within the device during execution of an assembly-level instruction. Software design components or non-programmable models are at the opposite extreme because neither interprets programmable instructions.

The software programming resolution axis in Figure 2.1 represents the granularity of software instructions that the model of a hardware component interprets in executing target software. In Chapter 5, "Hardware-dependent Software," a complete taxonomy of software utilizing multiple axes is defined. The view in Figure 2.1 is a simplification of the complete taxonomy and, thus, should only be used as an approximate guide. A programmable device could be represented at these levels of resolution, from high to low:

- **Major Modes:** At the highest precision level, the software is specified in terms of major working modes, such as searching, tracking, initialization, and so on.

- **DSP Primitive block-oriented:** At this level, the software is expressed as a block or function call and its parameters, for example, an FFT with parameters a, b, and c specified as FFT(a,b,c).

- **High-Level Language**: The software is specified at this precision level in terms of high-level language statements. Examples of such languages are C, C++, ADA, and Java.

- Assembly Code: A more detailed level is the assembly code level, which is a symbolic language that can be translated later into microcode and object code. Assembly code is usually the result of the usage of a compiler, but it can also be written manually.

- **Microcode**: The assembly code can be translated in even lower level of instructions, called microcode instructions, which are a representation of an set of control signals that are active on a given clock cycle, as well as the next micro-instruction to be executed.

• **Object Code**: The lowest level of precision contains the translation into binary code.

## 2.1.2 Internal/External (Interface) Concept

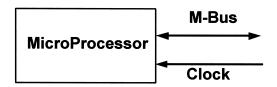

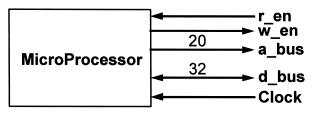

To better understand the internal/external concept, consider two views of an integrated circuit chip.

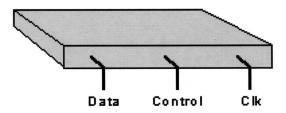

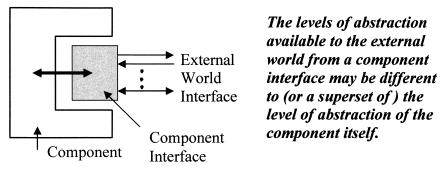

When viewed from outside, or externally, we observe only the structure and behavior of the pins (for example, how many pins there are, and what values they have when driven with various stimuli). But we cannot observe any details about how the chip is implemented inside the package, or internally, as in Figure 2.2.

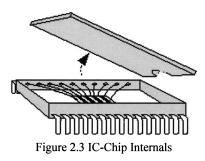

In contrast, we can imagine seeing an internal view if we were to pop the lid off the IC package as shown in Figure 2.3.

Notice that now we can see some detail about how the chip's insides, or internals, are implemented.

The external structure and behavior is the structure and behavior of the externally observable features, which in this case is the structure of the externally viewable ports or pins. Like the internal design, the external properties of a component can be viewed at many different levels of abstraction.

For example, Figure 2.4 depicts an abstract model of the external pins (interface) of a chip. The external implementation detail is resolved as two

#### 18 Chapter 2

signals (Data and Control) that are of an abstract type, integer. They are abstract because they do not reveal the bit-level implementation detail.

Figure 2.4 IC-Chip External Pins

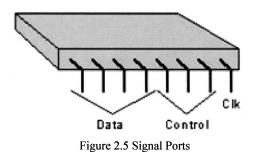

A less abstract model of the external interface of the component could show the actual bit-level implementation detail of the signal ports, as shown in Figure 2.5.

This more detailed view shows the hand-shaking lines and the data port resolved as individual pins at the bit level.

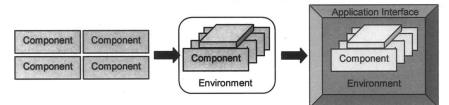

The internal/external partition concept simplifies the design process. A traditional method for managing complexity in a system is to use *divide-and-conquer* methods. In this approach, a system is divided by partitioning it into separate components. These components can, in turn, be further subdivided. This leads to the familiar hierarchical models used in most design methodologies.

However, this partitioning will not help the design task if, at each level of hierarchy, the designer has to consider each component's internal detail and its sub-components. What is needed is to be able to consider only a component's externally visible specification and not its internal detail. Most methodologies and languages try to do this by having separate structures for the *interface* and the *body* of a component. Users of a component only need to see its interface. Thus, an interface specification or interface model is the description of the externally visible part of a component.

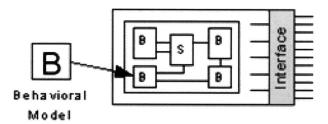

## 2.1.3 Note on Structure/Behavior/Interface Concepts

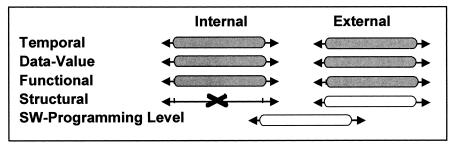

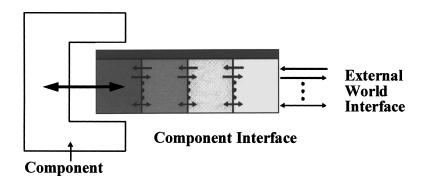

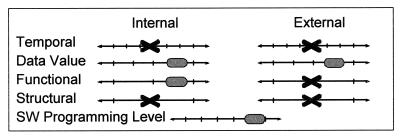

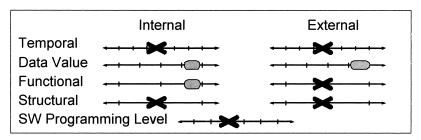

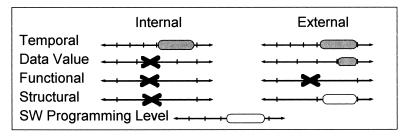

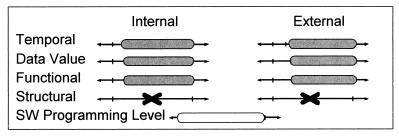

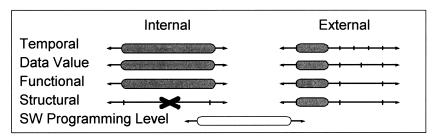

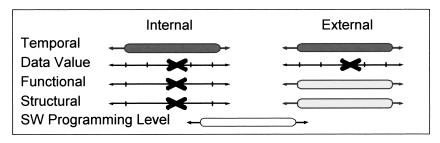

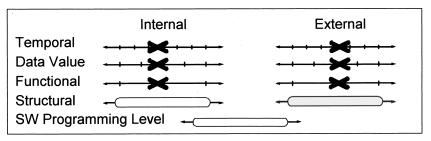

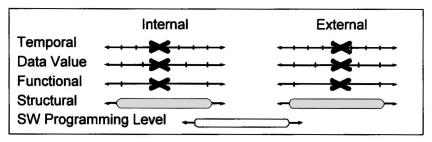

Another way of depicting the view of a model is shown in Figure 2.6 through Figure 2.9. These diagrams distinguish:

- Interface model (no internal details)

- Behavioral model (internal details described behaviorally)

- Structural model (internal structure described)

Figure 2.6 depicts an interface model. Notice that it contains details about the interface, or external ports, but contains no information about the internal implementation. Some level of external structure and data values can be observed, as well as some level of port function and timing response to interface activities. For example, the interface model can specify the data exchange and communication protocol, as implied in Figure 2.7.

Figure 2.6 External Interface

Figure 2.7 Internal Interface

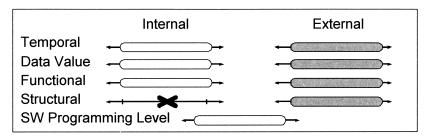

In contrast, Figure 2.8 depicts a behavioral model of the same component. Notice that this model contains information about the internal data values, functions, states, and timing aspects of the component, but no information about how the internal structure is implemented. Therefore, the internal view is said to be represented behaviorally.

Figure 2.8 Behavioral Model

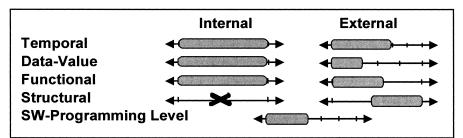

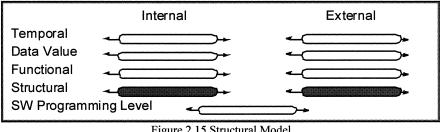

In contrast to this model, Figure 2.9 depicts a model that describes the internal structure of the component to some level of detail. Remember that structure is inter-connection information. Notice that this diagram shows a decomposition into internal blocks. Because it shows how the blocks are connected to each other, at some level of abstraction, it is called a structural model, or internal structure.

Figure 2.9 Internal Behavioral Model

The internal blocks of a structural model can either be described behaviorally, or can themselves be further decomposed structurally. If behaviorally described blocks exist at the bottom (leaf level) of a structural hierarchy, then the model can be simulated. Note that the behavior of such a composite model is provided by the underlying behavioral blocks, not completely by the structure. The structural descriptions merely provide the means for combining separate behavioral pieces. A different behavior would be exhibited if the underlying behaviors were changed.

If behavioral blocks do not exist at the bottom (leaf level) of a structural hierarchy, then the model is a purely structural model. No behavior can be inferred if the behaviors of the underlying blocks of a structural model are unknown.

The level of abstraction of the internal view depends on the level of implementation details. The structure could be described abstractly as the interconnection of high-level blocks, or concretely as the interconnection of logic gates. Independently, the timing and functional abstraction can be described for the high-level blocks abstractly as coarse events or concretely as specific times. They can be described for the gate-level model abstractly as the stable per-clock Boolean values, or all switching transitions can be resolved to picoseconds (intra-clock events) and signal levels.

## 2.1.4 Additional Attributes

In addition to the precision axes described earlier, the inclusion of additional attributes could be considered. For instance, the temporal resolution and data resolution axes could specify an accuracy aspect as a percent tolerance and whether a model describes actual, minimum, typical, or maximum values. A completeness aspect could also be considered that would specify the portion of functionality or particular functions that the model describes or excludes from the model. The accuracy and completeness aspects would accompany the axes in the same way that the internal/external aspect does.

## 2.1.5 Vocabulary

Words represent concepts and allow us to share and communicate ideas. Unambiguous communication requires not only that we have a common mapping of words to concepts, but that we have the right set of words to accurately describe the concepts we are dealing with. Developing, agreeing to, and using a concise common terminology are therefore vital to achieving the goals of this book.

The development of an efficient vocabulary, which assigns a minimal set of words to the appropriate concepts, is an orthogonalization process. The process develops a set of terms that represent all of the concepts to be distinguished. Separate words are selected for distinct concepts. Words for classes of concepts are selected to represent useful generalizations.

In defining the vocabulary terms, attempts were made to defer to the general English meaning of words as defined by the Webster's New Collegiate Dictionary [WEB] so that outsiders and newcomers may be more likely to rapidly understand and adopt the terminology.

Some terms may have multiple meanings (due to historic or domain overloading) that can be differentiated by context. We try to recognize and define each of these terms.

To avoid the problem of vague or circular definitions, a heavy emphasis was placed on providing examples to accompany the definitions. These examples should provide a level of understanding and concreteness to any discussions regarding the terms. The examples also tend to associate the terms to their intended uses and domains. To reduce the tendency of examples to limit or over-constrain the definitions, a range of typical and extreme cases are given and identified wherever possible.

To further avoid ambiguous definitions, attempts were made to eliminate definitions based purely on relative terms, such as "high," or "abstract," since their interpretation would be subject to one's point-of-view or experience. Instead, definitions should be based on absolute, concise, and testable statements, with special emphasis on differentiating related terms (such as "software/hardware/firmware").

Reaching the much-needed consensus on terminology requires compromise from everyone. The original contributors to this work and editors of this book have made a conscious attempt to borrow heavily (and somewhat evenly) from everything written by the community. All terms relative to the taxonomy axes described in this section are described in the following sections of this chapter. Although some terms may span a range of abstraction levels, a given model instance describes information at one specific level within the span. The remaining Sections 2.2 through 2.8 list the vocabulary terms and their definitions.

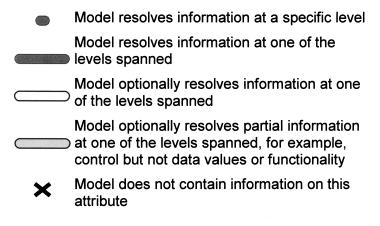

Figure 2.10 Symbol Key

# 2.2 General Modeling Concepts

The following sections contain definitions of concepts that are pervasive across many types and levels of models. The modeling concepts are divided into three groups:

- Primary Model Classes:

- Functional Model

- Behavioral Model

- Structural Model

- Interface Model

- Specialized Model Classes:

- Performance Model

- Hybrid (Mixed-Level) Model

- Computational Model Classes:

- Dataflow-Graph Model

- Other Models

### 2.2.1 Primary Model Classes

All models can be described in terms of one or more of the three primary aspects-behavioral, functional and structural-combined with an interface model.

Pure functional models are timeless algorithmic models. Behavioral models add time to the function, and structural models build up models from other models. Interface models exist to separate the specification of internal function in a model from the specification of its externally visible part, such as the communications protocol it uses.

The primary model classes are not specific to hardware or software, and they can be used for either. They can also be used for the system level (unmapped to hardware or software).

A functional or behavioral model may be composed of a number of smaller functional or behavioral models linked together in a network (for example, a dataflow decomposition, a process network, or multiple threads in a programming language). However, this "structural" decomposition of such models need not imply anything about the implementation of that function or behavior in the physical or software domains.

Recently the Open SystemC Initiative (OSCI) has been working on a set of model definitions that all operate at what they call the transaction level [DON 04], [DONBR 04]. They define the transaction level as being any abstraction above the RTL model but they do not provide any guidance as to whether a transaction is an atomic entity in terms of the data being transferred or not. It thus describes a concept rather than anything specific. At the same time, they have defined a specific kind of transaction called a transfer, which implies a level of timing accuracy for the transaction. While these are not very useful definitions by themselves, they are identifying a number of modeling stages which allow a flow to be defined starting with a high-level functional model, and refining this in a number of intermediate models down to a specific implementation.

Perhaps more importantly, SystemC provides for explicit separation of the function and interface, allowing each of them to be refined somewhat independently of the other. For many model definitions, they have not separated these concepts when they provided names to the various models, and this could create confusion when the abstraction level of the model internals and its interface do not match.

In the following definitions for model types, the corresponding models identified by the SystemC Transaction Level Modeling (TLM) group will be identified. It should be noted that this group has not yet finished its work and, within the group, there is some level of disagreement on the model levels that should be defined. In addition, some of the models under consideration do try to tie together the abstraction of the model and some specifics about the communications supported by the model. While this creates very highly specific types of models, direct applications for these models can be defined.

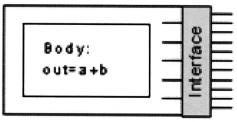

#### 2.2.1.1 Functional Model

Figure 2.11 A Model without Timing

A *functional* model describes the function of a system or component without describing a specific implementation. A functional model can exist at any level of abstraction, depending on the precision of implementation details. For example, a functional model can abstractly describe a signal-processing algorithm, or it can be a less abstract model that describes the function of an ALU for accomplishing the algorithm. The precision of internal and external data values depends on the model's abstraction level. The functional model does not specify any timing other than that implied by dependencies in the function. So, for example, a functional model expressed as a series of input-output relationships with no intermediate steps has no temporal specification information at all.

A functional model can also be more narrowly defined in the mathematical sense. That is, a functional model can be described in terms of mathematical functions, which define mappings from a subset of the set of interface variables (the input domain) onto another subset of the set of interface variables (the output domain). A partial functional model is one in which the union of these two subsets of interface variables is not equivalent to the complete set. If the two subsets are disjoint, then the first are pure "inputs" and the second are pure "outputs" of the functional model. Models that include time in either domain are more general and fall into the behavioral model definition provided in the next section.

In the SystemC TLM world this is identified as the *untimed functional* (UTF) model. The SystemC TLM definitions have also provided some hints on the external view of the model, by stating that communications occurs in the form of message passing and is point to point in nature. Communications is usually blocking, although there may be a FIFO of arbitrary depth placed in the communications channel.