# DYNAMIC CHARACTERISATION OF ANALOGUE-TO-DIGITAL CONVERTERS

Dominique Dallet and José Machado da Silva (Eds.)

#### DYNAMIC CHARACTERISATION OF ANALOGUE-TO-DIGITAL CONVERTERS

# THE KLUWER INTERNATIONAL SERIES IN ENGINEERING AND COMPUTER SCIENCE

ANALOG CIRCUITS AND SIGNAL PROCESSING Consulting Editor: Mohammed Ismail. Ohio State University

#### **Related** Titles:

DESIGN OF WIRELESS AUTONOMOUS DATALOGGER IC'S Claes and Sansen Vol. 854, ISBN: 1-4020-3208-0 MATCHING PROPERTIES OF DEEP SUB-MICRON MOS TRANSISTORS Croon, Sansen, Maes Vol. 851, ISBN: 0-387-24314-3 LNA-ESD CO-DESIGN FOR FULLY INTEGRATED CMOS WIRELESS RECEIVERS Leroux and Stevaert Vol. 843, ISBN: 1-4020-3190-4 SYSTEMATIC MODELING AND ANALYSIS OF TELECOM FRONTENDS AND THEIR BUILDING BLOCKS Vanassche, Gielen, Sansen Vol. 842, ISBN: 1-4020-3173-4 LOW-POWER DEEP SUB-MICRON CMOS LOGIC SUB-THRESHOLD CURRENT REDUCTION van der Meer, van Staveren, van Roermund Vol. 841, ISBN: 1-4020-2848-2 WIDEBAND LOW NOISE AMPLIFIERS EXPLOITING THERMAL NOISE CANCELLATION Bruccoleri, Klumperink, Nauta Vol. 840, ISBN: 1-4020-3187-4 SYSTEMATIC DESIGN OF SIGMA-DELTA ANALOG-TO-DIGITAL CONVERTERS Bajdechi and Huijsing Vol. 768, ISBN: 1-4020-7945-1 OPERATIONAL AMPLIFIER SPEED AND ACCURACY IMPROVEMENT Ivanov and Filanovsky Vol. 763, ISBN: 1-4020-7772-6 STATIC AND DYNAMIC PERFORMANCE LIMITATIONS FOR HIGH SPEED **D/A CONVERTERS** van den Bosch, Steyaert and Sansen Vol. 761, ISBN: 1-4020-7761-0 DESIGN AND ANALYSIS OF HIGH EFFICIENCY LINE DRIVERS FOR Xdsl Piessens and Steyaert Vol. 759, ISBN: 1-4020-7727-0 LOW POWER ANALOG CMOS FOR CARDIAC PACEMAKERS Silveira and Flandre Vol. 758, ISBN: 1-4020-7719-X MIXED-SIGNAL LAYOUT GENERATION CONCEPTS Lin, van Roermund, Leenaerts Vol. 751, ISBN: 1-4020-7598-7 HIGH-FREQUENCY OSCILLATOR DESIGN FOR INTEGRATED TRANSCEIVERS Van der Tang, Kasperkovitz and van Roermund Vol. 748, ISBN: 1-4020-7564-2 CMOS INTEGRATION OF ANALOG CIRCUITS FOR HIGH DATA RATE TRANSMITTERS DeRanter and Steyaert Vol. 747, ISBN: 1-4020-7545-6 SYSTEMATIC DESIGN OF ANALOG IP BLOCKS Vandenbussche and Gielen Vol. 738, ISBN: 1-4020-7471-9 SYSTEMATIC DESIGN OF ANALOG IP BLOCKS Cheung and Luong Vol. 737, ISBN: 1-4020-7466-2 LOW-VOLTAGE CMOS LOG COMPANDING ANALOG DESIGN Serra-Graells, Rueda and Huertas Vol. 733, ISBN: 1-4020-7445-X CIRCUIT DESIGN FOR WIRELESS COMMUNICATIONS Pun, Franca and Leme Vol. 728, ISBN: 1-4020-7415-8 DESIGN OF LOW-PHASE CMOS FRACTIONAL-N SYNTHESIZERS DeMuer and Steyaert Vol. 724, ISBN: 1-4020-7387-9 MODULAR LOW-POWER, HIGH SPEED CMOS ANALOG-TO-DIGITAL CONVERTER FOR EMBEDDED SYSTEMS Lin, Kemna and Hosticka Vol. 722, ISBN: 1-4020-7380-1

# DYNAMIC CHARACTERISATION OF ANALOGUE-TO-DIGITAL CONVERTERS

by

### **Dominique Dallet**

Laboratoire IXL-ENSEIRB, Bordeaux, France

and

#### José Machado da Silva

Universidade do Porto, INESC-Porto, Portugal

A C.I.P. Catalogue record for this book is available from the Library of Congress.

ISBN-10 0-387-25902-3 (HB) ISBN-13 978-0-387-25902-4 (HB) ISBN-10 0-387-25903-1 (e-book) ISBN-13 978-0-387-25903-1 (e-book)

> Published by Kluwer Academic Publishers, P.O. Box 17, 3300 AA Dordrecht, The Netherlands.

> > www.springeronline.com

Printed on acid-free paper

All Rights Reserved © 2005 Springer

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Printed in the Netherlands.

# Contents

| Preface             |                                                          | iX       |

|---------------------|----------------------------------------------------------|----------|

| Contrib             | uting Authors                                            | xi       |

| Introduc<br>José Ma | ction<br>achado da Silva                                 | XV       |

| Glossar             | у                                                        | xvii     |

| Part I              | ADC Characterisation Based on Sinewave Analysis          |          |

| 1                   |                                                          |          |

| ADC A               | pplications, Architectures and Terminology               | 3        |

| José Ma             | uchado da Silva, Hélio Mendonça                          |          |

| 1.                  | Introduction                                             | 3        |

| 2.                  | ADCs' applications                                       | 5        |

| 3.                  | ADCs' architectures                                      | 10       |

| 4.                  | Terminology                                              | 15       |

| 5.                  | Quantisation and A/D conversion                          | 20       |

| 6.                  | Output coding                                            | 27       |

| 7.<br>8.            | Errors, non-linearity, noise, and distortion             | 31<br>40 |

| o.<br>9.            | Data acquisition and processing<br>Input characteristics | 40 43    |

| 2                   | 1                                                        |          |

|                     | ve Test Setup                                            | 47       |

|                     | Vies Roy, Jacques Durand                                 |          |

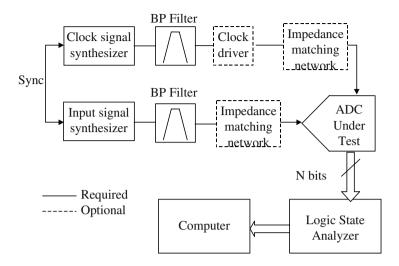

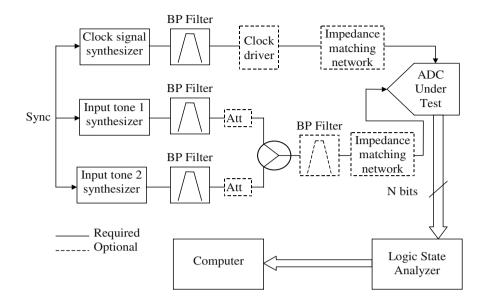

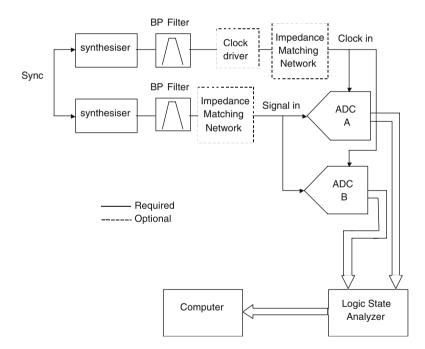

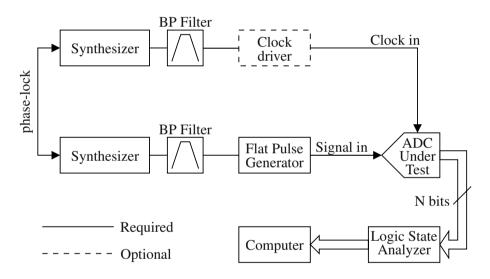

| 1.                  | Test Setup description                                   | 47       |

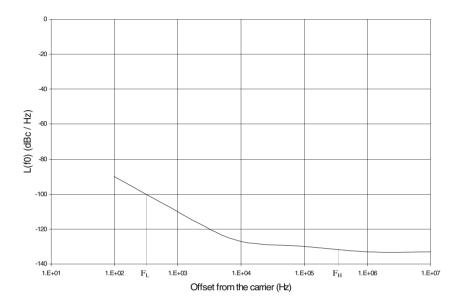

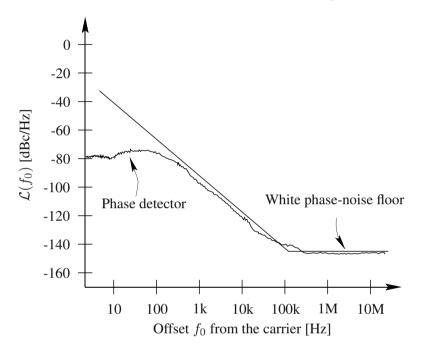

| 2.                  | Specification of the clock and input signal              | 49       |

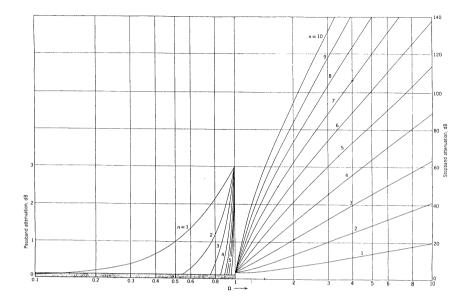

| 3.                  | Example of filter specification                          | 56       |

| 4.                  | Filter selection                                         | 57       |

| 5.                  | Taking a record of data                                  | 59       |

| 3                   |                                                          |          |

| Time-D              | omain Data Analysis                                      | 61       |

| Dominie             | que Dallet, Djamel Haddadi, Philippe Marchegay           |          |

| 1.                  | Introduction                                             | 61       |

| 2.                  | Calculation of the dynamic parameters                    | 62       |

| 3.                  | Definitions                                              | 62       |

ADC DYNAMIC CHARACTERISATION

|     | 4.<br>5. | The fixed-frequency method<br>The four-parameter method                                  | 63<br>65 |

|-----|----------|------------------------------------------------------------------------------------------|----------|

|     | 6.       | Definitions of $THD$ and $SNR$                                                           | 70       |

|     | 0.<br>7. | The multi-harmonic sine-wave fitting method                                              | 71       |

|     | 8.       | Estimation of the normalised angular frequency                                           | 73       |

|     | 9.       | Estimation of the linear parameters                                                      | 74       |

|     | 10.      | On the rank of $\mathbf{E}_P$                                                            | 75       |

|     | 10.      | The algorithm                                                                            | 76       |

|     | 12.      | Multitone test to circumvent signal purity problems                                      | 77       |

| 4   |          |                                                                                          |          |

|     |          | y-Domain Data Analysis                                                                   | 85       |

| Pie | erre-Yve | es Roy, Jacques Durand                                                                   |          |

|     | 1.       | Discrete Fourier Transform and Fast Fourier Transform                                    | 85       |

|     | 2.       | Choice of input and clock frequencies                                                    | 86       |

|     | 3.       | Windowing                                                                                | 86       |

|     | 4.       | Comment on the accuracy of the input frequency                                           | 88       |

|     | 5.       | Record size                                                                              | 90       |

|     | 6.       | Calculation of ADC dynamic parameters in the frequency domain                            | 92       |

| 5   | 1. 11.4  | т., т., т., с                                                                            | 105      |

|     |          | ogram Test                                                                               | 105      |

| Gu  |          | Chiorboli, Carlo Morandi                                                                 | 105      |

|     | 1.       | Introduction                                                                             | 105      |

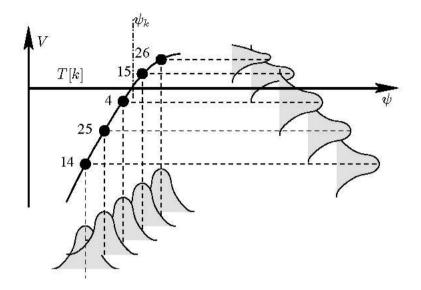

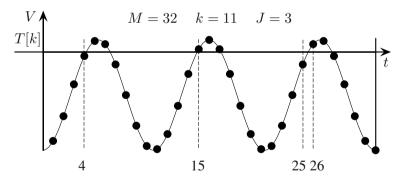

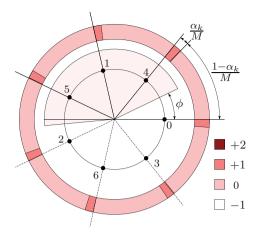

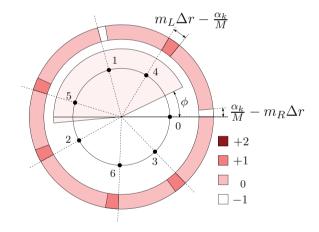

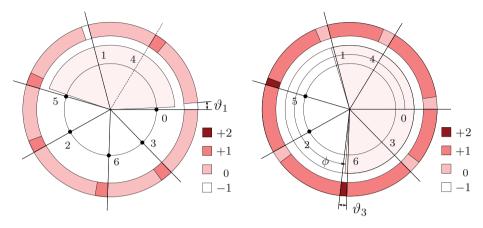

|     | 2.       | The sampling strategy and its contribution to count variance and measurement uncertainty | 108      |

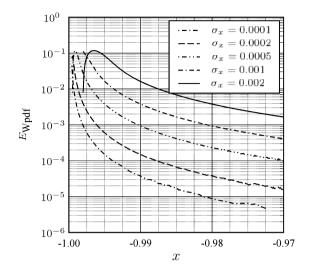

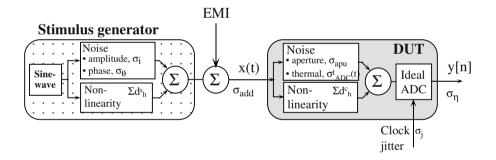

|     | 3.       | Additional contributions to count uncertainty: additive noise and jitter                 | 115      |

|     | 4.       | Factors affecting the p.d.f. of the input signal                                         | 122      |

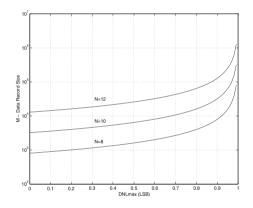

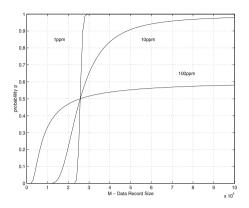

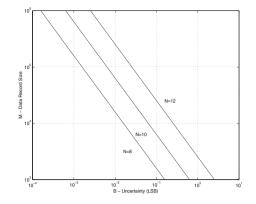

|     | 5.       | Required record length and number of records, expression of mea-<br>surement uncertainty | 133      |

|     | 6.       | Choice of the coverage factor                                                            | 139      |

|     | 7.       | Comparing the number of samples required by random and by syn-<br>chronous sampling.     | 141      |

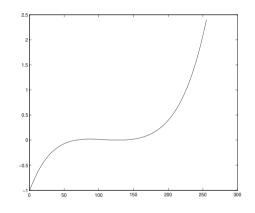

|     | 8.       | Determining the transfer characteristic                                                  | 142      |

|     | 9.       | Offset error and gain                                                                    | 143      |

|     | 10.      | Linearity errors                                                                         | 147      |

|     | 11.      | Appendix                                                                                 | 148      |

| 6   |          |                                                                                          |          |

| Co  | mparat   | ive Study of ADC Sinewave Test Methods                                                   | 157      |

| Jos | séMach   | ado da Silva, Hélio Mendonça, Sara Mazoleni                                              |          |

|     | 1.       | Introduction                                                                             | 157      |

|     | 2.       | General considerations                                                                   | 159      |

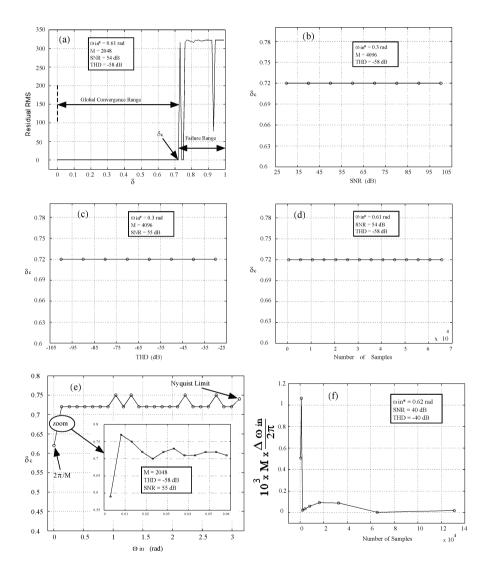

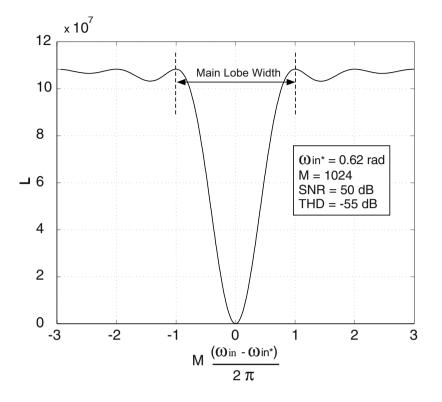

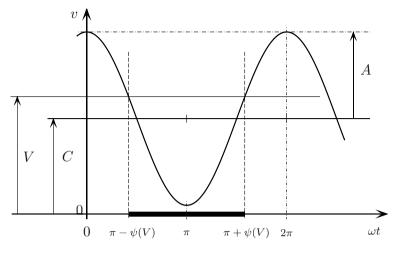

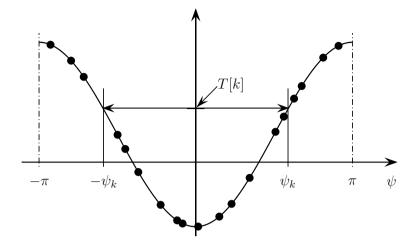

|     | 3.       | Simulation results                                                                       | 174      |

|     | 4.       | ATE Implementation                                                                       | 187      |

|     | 5.       | Conclusions                                                                              | 213      |

Part II Measurement of Additional Parameters

vi

| Content  | S                                                                | vii |

|----------|------------------------------------------------------------------|-----|

| 7        |                                                                  |     |

| Jitter M | easurement                                                       | 219 |

| Pierre-Y | ves Roy, Jacques Durand                                          |     |

| 1.       | Introduction                                                     | 219 |

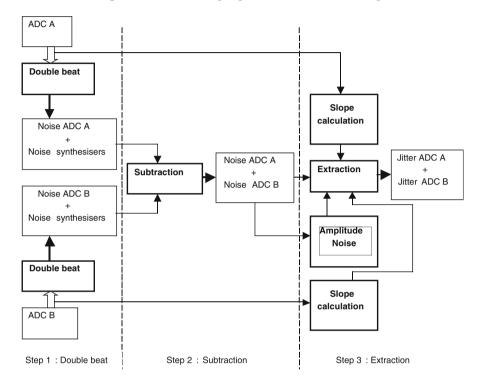

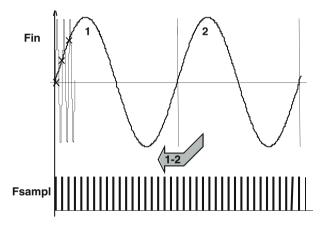

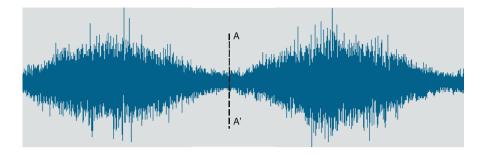

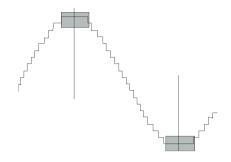

| 2.       | The double beat technique                                        | 220 |

| 3.       | The joint probability technique                                  | 230 |

| 4.       | Conclusion                                                       | 233 |

| 8        |                                                                  |     |

| Differer | tial Gain and Phase Testing                                      | 235 |

| JoséMa   | chado da Silva, Hélio Mendonça                                   |     |

| 1.       | Introduction                                                     | 235 |

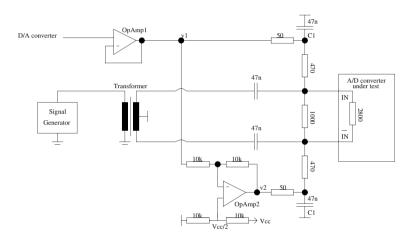

| 2.       | Test setup and hardware requirements                             | 236 |

| 3.       | Analysis                                                         | 237 |

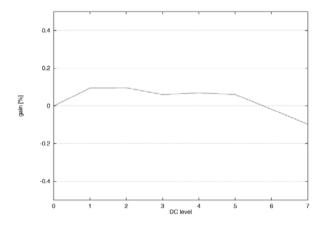

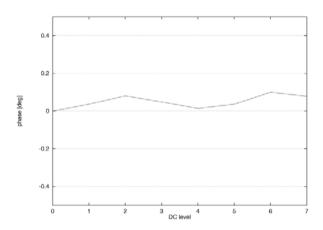

| 4.       | Test results                                                     | 240 |

| 5.       | Calculation of differential gain and phase from the test results | 241 |

| 9        |                                                                  |     |

| Step and | 1 Transient Response Measurement                                 | 243 |

|          | ii Chiorboli, Carlo Morandi                                      |     |

| 1.       | Introduction                                                     | 243 |

| 2.       | Settling time and transition duration of step response           | 245 |

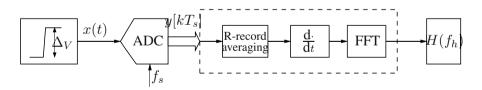

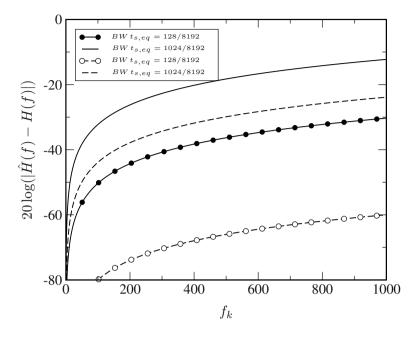

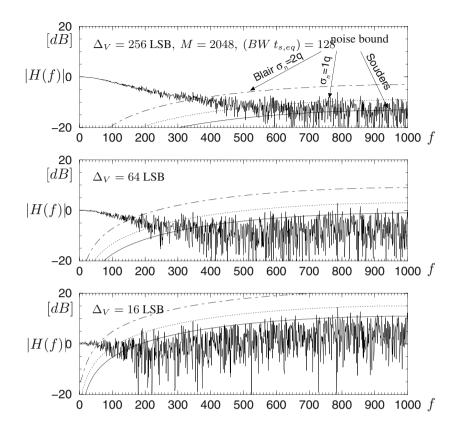

| 3.       | Frequency response measurement                                   | 249 |

| 10       |                                                                  |     |

| Hystere  | sis Measurement                                                  | 255 |

| Giovani  | ii Chiorboli, Carlo Morandi                                      |     |

| 1.       | Introduction                                                     | 255 |

| 2.       | Test conditions                                                  | 256 |

| 3.       | A practical case                                                 | 257 |

| 4.       | Collection of samples in $H_{C\uparrow}$ and $H_{C\downarrow}$   | 258 |

| 5.       | Some warning                                                     | 260 |

|          |                                                                  |     |

| Referen  | ces                                                              | 265 |

| Index    |                                                                  | 279 |

## Preface

The present book is one of the outcomes of the project DYNAD - Methods and Draft Standards for the Dynamic Characterization and Testing of Analogueto-Digital Converters. This project was held between 1997 and 2000, supported by the European Commission under the Standards, Measurements and Testing Programme, reference SMT4-CT98 2214, within the Framework IV activities. Its consortium comprised the University of Parma - Italy, the École Nationale Superieure d'Electronique, Informatique & Radiocommunications de Bordeaux - France, Thales (former TTM-Thomson CSF) - France, Italtel Spa - Italy, Infineon Technologies-Development Center Villach - Austria, and INESC-Porto - Portugal. Besides the authors of the different chapters of this book, other people contributed with their work to the start and success of the initiative. We acknowledge the efforts of Hubert Pernull, Otto Wiedenbauer, and Andreas Bertl from Infineon, Roberto Scotti from Italtel, Jorge Duarte and José Matos from INESC-Porto, M. Heuber and M. Zirnheld from Thales, and C. Rebai from ENSEIRB.

A state of the art overview of the methods and procedures employed for characterising the dynamic performance behaviour of analogue-to-digital converters using sinusoidal stimuli, is presented in this book. The three classical methods — histogram, sine wave fitting, and spectral analysis — are thoroughly described, and new approaches are proposed to circumvent some of their limitations.

This is a must-have compendium, which can be used by both academics and test professionals, to understand the fundamental mathematics underlining the algorithms of ADC testing, and as a handbook to help the engineer in the most important and critical details for their implementation.

Dominique Dallet, José Machado da Silva

# **Contributing Authors**

**CHIORBOLI, Giovanni** graduated in Electronic Engineering from the University of Bologna, Italy, in 1987. Until 1990, he was with the University of Bologna. Since 1990, he has been with the University of Parma, Italy, where he is currently an Associate Professor of Electronic Measurements. His scientific interests are in the field of electronic instrumentation, analogue-to-digital and digital-to-analogue modelling and testing, and electrical characterization of semiconductor devices and materials for microelectronics.

**DALLET, Dominique** was born in Rochefort/Mer, France, on July 3, 1964. He obtained his PhD degree in Electrical Engineering in 1995 from the University of Bordeaux 1, where he is currently a professor at the Electronic Engineering School of Bordeaux (ENSEIRB). His main research activities, carried-out at the IXL laboratory, focus on mixed-signal circuit design and testing, digital and analogue signal processing, and programmable devices' applications. His interests include also digital design and its application in BIST structures for the characterization of embedded A/D converters, as well as, digital signal processing applied to nondestructive techniques based on time-frequency representation.

**HADDADI, Djamel** was born in 1971. He received the Engineer degree in physics and the Master degree in signal processing in 1996 from the Institut National Polytechnique de Grenoble, and the PhD degree in Electronics from the Université Bordeaux 1. He is a product responsible at STMicroelectronics since 2000. His main interests include ATE test and qualification of high performance analogue and mixed-signal ICs.

**DURAND, Jacques** obtained his PhD degree from the Université de Paris Sud — Orsay-IEF in 1984. Since then he worked at THOMSON-CSF (Orsay) as an expert on analogue signal processing and IC measurement and testing. His main interests concerned high-speed ADC test and characterization, with emphasis on noise and jitter analysis. Along his career he participated as an examinator in the evaluation of several PhD thesis, and published various conference and journal papers on ADC roadmap and characterisation. He holds a patent on a phase noise measurement set-up.

**MACHADO da SILVA, José** received the Licenciatura and PhD, both in Electrical and Computer Engineering from the Faculdade de Engenharia da Universidade do Porto (FEUP), Portugal, in 1984 and 1998, respectively. He joined FEUP in 1984 as a lecturer, and INESC-Porto in 1991 as a senior researcher, where he has collaborated on and supervised national and European projects on analogue and mixed-signal testing. He is currently an Assistant Professor at FEUP and a project leader at Instituto de Engenharia de Sistemas e de Computadores (INESC-Porto), with teaching and research responsibilities on design and testing of electronic circuits. His research interests include analogue and mixed-signal design for testability, new testing methodologies, analogue and digital signal processing, and VLSI design.

**MARCHEGAY, Philippe** was born in France in 1942. He received his PhD in 1966 and the "Doctorat en Sciences Physiques" degree in 1979 from the University of Bordeaux (France) about the topic of the study of metastability of synchronizer circuits and coherence faults of random access sequential networks. At present his research interests concern functional testing of A/D converters and their design. He is professor at the graduate engineering school, Ecole Nationale Supérieure d'Electronique Informatique et Radiocommunications de Bordeaux (ENSEIRB) of which he ensured the direction between 1999 and 2004.

**MAZZOLENI, Sara** was born in Milano, Italy, in 1967. She received the degree in Solid State Physics at the University of Milano in 1991. From 1990 until 1992 she worked as a researcher studying the non-linear behaviour of solid state lasers. From 1992 until 2001, she worked in Italtel SpA as test engineer of analogue and mixed-signal electronic components for telecommunication equipments. Now she is Supplier Quality Manager in Italtel Spa.

#### Contributing Authors

**MENDONÇA, Hélio Sousa** was born in Porto, Portugal, in 1968. He received the Licenciatura and PhD Degrees, both in Electrical and Computer Engineering from the Faculdade de Engenharia da Universidade do Porto (FEUP), Portugal, in 1991 and 2004 respectively. He joined FEUP in 1994, where he is now an Assistant Professor. He is also a Senior Researcher at Instituto de Engenharia de Sistemas e de Computadores (INESC-Porto) since 1995. His main research interests are digital signal processing and dynamic testing of ADCs.

**MORANDI, Carlo** graduated in Electronic Engineering at the University of Bologna in 1971. He worked at the University of Bologna as a research assistant, then as an associate professor of Electronic Instrumentation. Full professor of Applied Electronics at the University of Ancona since 1986, in 1988 he moved to the Faculty of Engineering of the University of Parma. His scientific interest is focused on the design and testing of mixed-signal integrated circuits and on the development of dedicated electronic instrumentation. He coordinated several national and international research projects, among them the "Standards, Measurements and Testing" project DYNAD of the European Commission concerning the definition of standard test procedures for the dynamic characterization of A/D converters, which originated the present book. He is author or co-author of over 100 scientific publications on international journals or proceedings of international conferences.

**ROY, Pierre-Yves** received the Engineer Diploma of the Ecole Nationale Superieure De Telecommunication de Bretagne ENSTB in 1995. He started his carreer working for Thomson-CSF (Thales now); first for Thomson-CSF Airsys (Thales Air Defence Systems) as a radar receiver designer, and then for Thomson-CSF Technologies and Methods (Thales research and Technology) as an expert in data conversion. When he was in Thales, his main areas of interest concerned high dynamic signal receivers and the functional testing of ADCs. In 2000, he joined EADS Telecom to manage the design of the architecture (and of the associated components) of their 3G secured radiocommunication terminals. He is now terminal architect for EADS Telecom.

## Introduction

José Machado da Silva

ADCs are, eventually, the most pervasive analogue blocks in electronic systems. With the advent of powerful digital signal processing and digital communication techniques, ADCs are fast becoming critical components for system's performance and flexibility. Knowing accurately all the parameters that characterise their dynamic behaviour is crucial, on one hand to select the most adequate ADC architectures and characteristics for each end application, and on the other hand, to understand how they affect performance bottlenecks in the signal processing chain.

At present, most of the signal processing performed in electronic systems is becoming digital, and the role of the ADCs placed at the borders of the digital domain acquires a particular relevance, since the signal degradation introduced by these components cannot normally be recovered by subsequent processing. Both the markets of stand-alone ADCs and of ADC macrocells to be embedded in complex systems-on-chip, benefit from the availability of performance parameters accurately describing their expected behaviour, and of clearly specified test methods to be used for their measurement.

When the project DYNAD started, the standardization of ADC test procedures was not so well developed. Two standards existed, in particular, at that time — the IEC 60748 and the IEEE Std 1057. The former covers only quasi-static operation, while the second deals with dynamic testing but, being addressed at digital waveform recorders requires some adaptations to cover ADCs. A first aim of DYNAD project was then, to contribute to the improvement of the European rules concerning test methods for ADCs, by proposing an integration within IEC 60748 addressing the parameters specifying the dynamic behaviour of ADCs, measurement conditions, and data processing algorithms. By the end of year 2000 a working group from the IEEE Instrumentation and Measurement Society Technical Committee (TC-10) completed the IEEE 1241 Standard for Analog to Digital Converters. This standard, as well as contributions from the DYNAD project, are now being incorporated into an IEC standard on dynamic testing of ADCs. Other initiatives have been carriedout concerning standardization of ADC testing methods. One can also mention EUPAS (EUropean Project for ADC-based devices Standardization), and the IMEKO Technical Committee 4 (A/D and D/A Metrology WorkGroup).

The main objective of the DYNAD project was the study and evaluation of ADC testing methods based on the use of sinewave test stimulus. A second aim was to investigate and propose new test methods to circumvent the limits of the measurement instrumentation, which is strongly challenged by today's high resolution, high speed converters. Techniques for the measurement of parameters required by specific applications (e.g. audio hi-fi) and for the debugging of new converter designs were also investigated. Dissemination of the knowledge gathered during the activity was the third objective.

That work is now compiled in this book, which is structured in two main parts. Part one comprises chapters one to six. The first one provides an overview of the most important ADCs' architectures and respective fields of application. An introduction to the most relevant nomenclature and definitions of terms is also presented. Chapter two describes the generic architecture of an ADC test setup, and guidelines and best practice procedures are proposed in order to guarantee reliable test results. Chapters 3, 4, and 5 are devoted to the description of dynamic test techniques using sinewaves, respectively, sinewave fitting (time domain data analysis), discrete Fourier transform (frequency domain analysis), and code histogram test (statistical domain analysis). These techniques are thoroughly described, as well as the fundamental mathematical background behind the equations to be used to obtain ADCs' characterization parameters provided in each case. A comparison among these three methods is presented in chapter 6. The objective is not to find the best or the worst methods, but mainly to compare how they behave when test conditions are not ideal and to identify their requirements in terms of test time and volume of data. Examples of ATE implementation are also included.

The second part comprises chapters 7 to 10, which provide additional information to test for other relevant parameters, such as jitter, differential gain and phase, step and transient response, and hysteresis.

# GLOSSARY

- $\varepsilon$  error, used for total error and error band

- $\varepsilon_G(f)$  gain flatness error at frequency f

- $\varepsilon$ **[k]** difference between T[k] and the ideal T[k] computed from G and V<sub>os</sub>

- $\varepsilon_m(f)$  aliasing and first differencing magnitude errors

- $\varepsilon_{\theta}(f)$  aliasing and first differencing phase errors

- $\varepsilon_q$  quantisation error

- $\varepsilon_{rms}$  root-mean-square value of  $\varepsilon$

- $\theta$  phase, expressed as radians

- $\eta$ **[n]** a record of noise data

- $\eta_f$  noise floor

- $\pi$  constant, ratio of the circumference to the diameter of a circle

- $\rho$  reflection coefficient

- $\sigma$  standard deviation; sometimes used as noise *rms* amplitude, which is the standard deviation of the random component of a signal

- $\sigma_{\sigma}$  standard deviation of the standard deviation (for example, standard deviation of the noise amplitude)

- $\sigma_j$  jitter

- $\sigma_t$  aperture uncertainty

- $\sigma^2$  variance; sometimes used to describe random noise power

- $\tau$  sampling period, the inverse of  $f_s$

- $\omega$  angular frequency, expressed in radians per second

- $\omega_i$  angular input frequency in radians/second

- $\delta \mathbf{t}_{eq}$  sampling time error of equivalent time sampling

- $\delta \mathbf{t}_{fi}$  input frequency inaccuracy

- A sinusoidal amplitude

- **B** test tolerance in fractions of the nominal least significant bit (Q). Also used as an amplitude

- **BW** frequency bandwidth

- c general purpose constant

- C offset

**d**[**n**] dither component of output sample y[n]

**dest**[**n**] estimate of the dither component d[n]

- **D** general purpose integer

- **DFT** Discrete Fourier Transform

- DG differential gain

**DNL[K]** differential non-linearity of code k

- **DNL** maximum differential non-linearity over all k

- **DP** differential phase

- **DR** dynamic range

- ENBW equivalent noise bandwidth

- **f** frequency, Hz

- **f**(**n**) sinewave component of output sample y[n]

- $\mathbf{f}_{co}$  upper frequency for which the amplitude response is -3 dB

- $\mathbf{f}_d$  sampling frequency of a record after decimation by some integer D

- $\mathbf{f}_{eq}$  equivalent sampling rate

- $\mathbf{f}_h$  frequency of an harmonic of the input frequency

- $\mathbf{f}_i$  actual input frequency or approximate desired input frequency

- $\mathbf{f}_{imf}$  frequency of intermodulation distortion products

- $\mathbf{f}_{opt}$  optimum input frequency for testing

- $\mathbf{f}_m$  frequency of the mth component of a magnitude spectrum

- $\mathbf{f}_r$  input signal reference frequency or input signal repetition rate

- $\mathbf{f}_s$  sampling frequency

- $\mathbf{f}_{sp}$  frequency of a persistent spurious tone

- FR frequency response

- G static gain of the ADC under test

- G(f) dynamic gain of the ADC under test as a function of frequency

- **h** order of harmonic frequency

- **H** average number of histogram samples received in two code bins sharing the same transition level

- **H[f]** frequency response of the ADC under test

- H[i] number of histogram samples in bin i

- **Hc[j]** number in the jth bin of the cumulative histogram of samples

- $\mathbf{H}[\mathbf{f}_k] \quad \text{DFT of } \mathbf{h}(\mathbf{n})$

- **h**(**n**) discrete time impulse response of a system

- i general purpose index

- I general purpose factor

- IMD intermodulation distortion

- INL integral non-linearity

- **INL[k]** integral non-linearity at output code k

- J number of cycles in a record

- **k** code bin

- L general purpose integer

#### Glossary

- L(f) phase noise spectral power density

- mse mean square error

- M number of sequential samples in a record

- $M^+(x)$ ,  $M^-(x)$  number of measurements of the output value at the input value x for increasing and decreasing inputs respectively

Md number of samples in a record after decimation

MD number of samples in one period of pseudo-random dither

- **n** sample index within a record

- N number of bits

- $\mathbf{N}_{ef}$  number of effective bits

- NDR noise distortion ratio

NPR noise power ratio

- **p** probability

- PG processing gain

- **Q** ideal code bin width, expressed in input units

- r general purpose integer

- **R** minimum number of records required

- **S** set of samples collected over more than one record, also used as an error parameter or as total number of samples used in a histogram

SFDR spurious free dynamic range

SINAD signal to noise and distortion ratio

SNR signal to noise ratio

- $S_x(f)$  spectral power density of quantity x

- $\mathbf{t}_{eq}$  average equivalent time sampling period

- $\mathbf{t}_f$  top to base transition time; falltime

- $\mathbf{t}_r$  base to top transition time; risetime

- $\mathbf{t}_n$  discrete sample times

$\mathbf{t}_{wc}$  the center point of the aperture time associated with an output sample

**T[k]** code transition level between codes k-1 and k

$\mathbf{T}_{nom}[\mathbf{k}]$  nominal code transition level between codes k-1 and k

THD estimate of total harmonic distortion

**THD** total harmonic distortion

TSD total spurious distortion

**u** confidence level expressed as a fraction

- $\mathbf{V}_{cm}$  common mode signal

- $\mathbf{V}_{dm}$  differential mode signal

- $\mathbf{V}_{fs}$  full scale range

- $\mathbf{V}_{fsn}$  nominal full scale range

- $\mathbf{V}_{ifs}$  full scale input signal

- $\mathbf{V}_{OS}$  ADC input offset, ideally = 0

- $V_{OD}$  input signal overdrive; the amount by which an input signal exceeds the ADC full scale range

- V<sub>rir</sub> reduced ADC input range

- VSWR voltage standing wave ratio

- w estimated code error rate

- w' worst-case code error rate

- **w**[**n**] window function coefficient (for a DFT)

- **W[k]** code bin width of code bin k

- x ADC input signal value; or number of errors detected

- X number of standard deviations of a Gaussian distribution

- $\mathbf{X}_{avm}(\mathbf{f}_m)$  the averaged magnitude spectral component at discrete frequency  $\mathbf{f}_m$  after a DFT

- y[n] the nth output data sample within a record

- $\overline{y}[\mathbf{n}]$  average of  $y[\mathbf{n}]$  over M samples

- yn' best fit points to a data record

- **Y[k]** the k-point DFT of the M-sample record y[n]

- **Z**<sub>O</sub> transmission line impedance

- $\mathbf{Z}_t$  ADC input impedance

- **Zu/2** number of standard deviations that encompass 100(1-u) % of a Gaussian distribution about the center.

# ADC CHARACTERISATION BASED ON SINEWAVE ANALYSIS

## Chapter 1

# ADC APPLICATIONS, ARCHITECTURES AND TERMINOLOGY

#### José Machado da Silva

Universidade do Porto, FEUP – INESC-Porto Campus da FEUP, Rua Dr Roberto Frias 4200-465 Porto, Portugal jms@fe.up.pt

#### Hélio Mendonça

Universidade do Porto, FEUP – INESC-Porto Campus da FEUP, Rua Dr Roberto Frias 4200-465 Porto, Portugal hsm@fe.up.pt

#### 1. Introduction

An analogue-to-digital converter (A/D converter or ADC) takes a continuous analogue input signal, most often a voltage  $V_x$ , and converts it into an N-bit binary number, which can then be manipulated by a computer. This functionality leads ADCs to present a very important role in electronic systems for a wide range of applications. Traditional mixed-signal implementations comprehend high-performance analogue circuits combined with a few digital functions for control or interface — these are the so-called *register-controlled* analogue systems. With the development of semiconductors' technology and microprocessors, systems based in digital signal processing cores and provided with analogue inputs and outputs — the so-called *digitised analogue* systems - are becoming more and more the basis of the dominant architectures in electronic systems. The performance of the ADCs placed at these analogue/digital interfaces acquires a particular relevance, since the effects of the ADCs' behaviour on the signals being acquired, cannot easily be recovered by subsequent processing. Additionally, the performance of most recent systems for applications in fields such as telecommunications, test and measurement, or consumer electronics require ADCs with ever increasing capabilities in terms of resolution and speed.

To optimise a system's performance, designers using high-performance A/D converters must thoroughly understand their test techniques and limitations. The traditional ADCs' performance characterisation parameters obtained with static tests are not sufficient to fully characterise the device's behaviour. One such static test consists in placing the device under test within a DC servo-loop, in order to measure each code transition level individually [1]. This method is still quite useful to obtain the DC transfer characteristic of high resolution, low sampling-rate converters, and then to calculate parameters like integral and differential non-linearities, and monotonicity. However, instead of a steady DC level, the A/D converter is in general subject to a dynamically changing input signal. The best test approach would be to evaluate the ADC performance in the target system, but this is not always feasible. In this case the converter should be tested under conditions as close as possible to those required for the final application. Dynamically testing an ADC in the frequency range that covers the bandwidth of the application can provide that assurance, being the ADC performance given now in terms of dynamic or AC specifications.

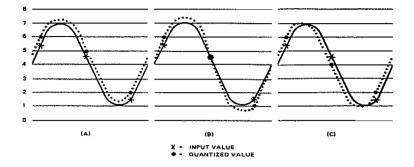

Three test methods are commonly used to dynamically characterize an ADC — histogram analysis, spectrum analysis, and time-domain analysis (also known as sine wave curve fitting). These three methods operate essentially in the same manner, i.e., a sine wave stimulus is applied to the ADC and one or more records of data are taken from the ADC output response, which are then processed to extract relevant parameters. As these methods differ in the data processing algorithms, and consequently in the type of errors detected, they do not provide, at the first approach, the same characterisation parameters. A fourth method — the beat frequency method — is often used as well, which is able to provide a quick yet simple visual demonstration of the ADC dynamic behaviour. However, as it is a qualitative test, it is not usually used as a reference method to provide numerical characterisation data.

Concerning the selection of the input stimulus waveform, the ramp is the simplest one for testing an ADC's linearity. This signal presents however a drawback that comes from the fact of being hard to generate with the proper linearity. The input stimulus ramp should have at least two to four bits of resolution more than that of the ADC under test, a requirement which might be difficult to meet when testing high-speed or high-resolution converters. Alternatively, a sine wave can overcome these problems, although its purity is critical to the success of the tests. A spectrally pure sinusoid is easier to obtain than a sharp and perfectly linear triangular wave, by taking a lower resolution sine wave and filtering it to the required purity. Often, synthesized sources are necessary to provide the short-term and long-term stability required by the dy-

namic range of the ADC. Anyway, precisely controlling the absolute amplitude and offset of a sinusoid waveform is not trivial.

A brief introduction to the problem of dynamically testing A/D converters was given above. One of the aspects to be taken into account is the necessity of testing the converter as much as possible under the same conditions as those found in the final application. As this is not usually possible, a central question concerns the identification of the ADCs' performance characterisation parameters that best evaluate its ability to perform the desired function.

In fact, often the generation of ADC tests is driven by the application characteristics or by the specificities of the ADC architecture, in order to adapt specification parameters limits, the test setup, or even the test methods themselves. For example, for certain applications absolute converted digital code combinations may not be as important a characteristic as relative converter response to the adjacent code combinations. This is the case, for instance, in digital audio applications where two important ADC performance characteristics are the non-linearity causing signal distortion and the intermodulation of high frequency tones to the baseband. The high resolution converters used in these applications require clock jitter to be considered for it causes a signal dependent modulation and additional noise. It is also important to avoid group delay differences which influence focus and stability of the sound sources in a stereo image — humans can detect time-of-arrival differences of about 7 microseconds [87]. Performance at low levels and at higher frequencies is vital for good sound quality.

This chapter continues with an overview of different application fields for ADCs, and the respective most critical parameters. Section 3 presents the most commonly used ADCs' architectures and the respective current rates of number of bits and sampling frequencies. Sections 4 to 9 address the non-harmonised approach seen today concerning the terminology used in the analogue-to-digital conversion domain, present definitions for different terms, and introduce acronyms used along this book. The information given herein was obtained from an extensive bibliography, as well as, from manufacturers data sheets and application notes. It is considered to be, at the time of writing and at the best of our knowledge, an updated state of the art overview of the technology in this domain. However, as technology is continuously developing, it is likely that part of this information becomes out-of-date.

#### 2. ADCs' applications

This section presents an overview on ADCs' most significant application fields, and for each one identifies the parameters which are the most critical for the overall system's performance.

| Application                                | Critical Performance<br>parameters                                                         | Performance<br>issues                                                                                                 |

|--------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Audio                                      | SINAD, Crosstalk                                                                           | Power consumption<br>Gain matching                                                                                    |

| Automatic control,<br>Sensors and robotics | Monotonicity, short term setting,<br>linearity, long-term stability,<br>temperature offset | Transfer function                                                                                                     |

| Data transmission                          | SFDR, BW, SINAD<br>DR, INL, DNL                                                            | Thermal noise<br>Phase non-linearity                                                                                  |

| Digital high-Speed<br>Instrumentation      | $N_{ef}$ , BW, out-of-range recovery, Word error rate                                      | SNR for better wide bandwith<br>amplitude resolution, SFDR to<br>minimize distortion, bit error rate<br>thermal noise |

| Geophysical                                | THD, SINAD, DR<br>Long-term stability                                                      | miliHz response                                                                                                       |

| Hard disk driving                          | Conversion time/latency                                                                    |                                                                                                                       |

| Medical                                    | SFDR, BW, INL, DR, SNR                                                                     |                                                                                                                       |

*Table 1.1.* Critical ADCs' performance parameters per application.

#### *Table 1.1 (continued)* Critical ADCs' performance parameters per application.

| Application                                                    | Critical performance<br>parameters                                        | Performance<br>issues                                                                                                             |

|----------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Military<br>communications                                     | SFDR, SINAD, THD,<br>IMD, NPR, NDR                                        | Linear dynamic range for detection of<br>low-level signals in a strong interference<br>environment                                |

| Electronic warfare                                             | SFDR, SINAD, NDR                                                          | Sampling frequency                                                                                                                |

| Mobile<br>telecommunications<br>and wireless<br>communications | SINAD, NPR, SFDR,<br>THD, SNR, IMD,<br>NDR                                | Wide input bandwidth channel bank Bit<br>error rate, word error rate Interchannel<br>crosstalk, compression, power<br>consumption |

| Monitoring, test<br>equipment and<br>instrumentation           | <i>N<sub>ef</sub></i> , BW, out-of-range recovery, word error rate        | SNR for better wide bandwidth,<br>amplitude resolution, SFDR to minimize<br>distortion, bit error rate                            |

| Radar and sonar                                                | SINAD, SFDR, INL,<br>BW Out-of-range<br>recovery                          | SINAD for clutter cancellation and Doppler processing                                                                             |

| Spectrum analysis                                              | SINAD, SFDR                                                               | SINAD and SFDR for high linear dynamic range measurements                                                                         |

| Speech and voice communications                                | SINAD, NPR                                                                |                                                                                                                                   |

| Video and television                                           | INL, DNL, FR, SNR,<br>DG, DP, SFDR, word<br>error rate, BW, THD,<br>SINAD | Differential gain and phase errors Power consumption                                                                              |

Table 1.1 presents a summary of ADCs' performance characterisation parameters and other behavioural aspects which are critical for different application fields. Regarding the selection and definition of these fields, some of them are somewhat similar in their essence but, due to significantly different performance requirements imposed on the ADCs used in the different applications, they were considered as distinct. This is the case, for instance, of audio and speech and voice communications applications, in which the later places less strict requirements (lower resolution and conversion rate) on the ADCs to be used. Similarly, ADCs for hard-disk drives are described as belonging to an application field of their own due to the exceptionally high conversion rates required (much higher than those in other control applications such as in automatic control and robotics). The same option was made for ADCs for geophysical applications, in which the required resolution is higher but the conversion rate lower. Also on this line, digital high-speed instrumentation, which comprises mainly instruments such as digital oscilloscopes, was considered a different application field from other test and monitoring equipment due to the higher performance requirements. Spectrum analysis was also considered a field apart from generic test and monitoring equipment, because it has precise requirements regarding the accurate conversion of different frequency components and the ability to detect even low power signals, spectral noise density and linearity being two key specifications in these applications.

In high-speed applications, such as video and wireless communications, whether they require undersampling or oversampling, the ADC must deliver high levels of dynamic performance. Since it generally is the front-end of the application, the overall system specifications will depend on the ADC's dynamic performance, characterized by parameters such as SFDR, THD and SNR [20]. SFDR is important in many applications because noise (including thermal noise) and harmonics restrict the dynamic range. In an IF (intermediate frequency) bandpass converter, for example, spurs may be interpreted as adjacent-channel information, giving rise to inter-channel mixing because different channels reside relatively close to each other.

The same can happen in military applications, such as signal intelligence and communications intelligence, where distortion within the ADCs, can lead to false readings [49]. High SFDR and low THD help to minimise the ADC's contribution to the overall distortion. In yet other applications, signals of interest may not be distinguishable from harmonics and spurious signals. In echocancelling modems (where the modem transmits and receives at the same time) the ADC must have sufficient dynamic range to capture the strong echo of the "send" signal and the weak "receive" signal (40-50 dB weaker than the "send" echo in long lines) without clipping the echo and without loosing the weak "receive" signal in the converter's quantisation noise. Echo clipping would cause distortion and ruin the signal because a synthesized copy of it is subtracted from the complete captured signal. This may require up to 1 MHz of bandwidth and up to 90 dB of dynamic range [94]. In high speed modems, where data is coded by phase-shift keying, phase non-linearity (or delay distortion) is also an issue.

In audio applications, particularly in stereo systems, phase non-linearity gives place to time-delay distortion which, for an input signal consisting of two or more frequencies, renders distortion caused by the different arrival times of these frequency components at the output of the ADC.

Radar applications demand the best possible SFDR and SINAD in order to prevent weak signals from being masked by harmonics or spurious signals. The harmonics responsible for poor radar SINAD performance (typically the second or third ones) arise due to poor INL at some particular frequency. Thus, bandwidth and slew rate can be key factors. Sonar is another application which also requires low noise and good SFDR. Geophysical sensor equipment requires high dynamic range. The signals which result from the execution of acoustic geophysical tests easily span dynamic ranges of over 120 dB [67].

Spread-spectrum techniques are used in both military (subject to very strong interference) and wireless communications where there are multiple users in the same frequency in overlapping networks. ADCs for these applications are required to present good SINAD, IMD, SFDR, and NPR characteristics with performance issues being low IMD for quantisation of small signals in a strong interference environment, low SFDR for spatial filtering, and high NPR for low interchannel crosstalk. It is important to successfully reject adjacent channels. Medical imaging applications, such as ultrasound systems, require ADCs with good dynamic performance at high sampling rates. Ultrasound systems' ADCs need wide dynamic range to prevent noise from masking subtle abnormalities in a diagnostic image. In these applications ADCs' useful bandwidth is determined by the amount of SFDR needed within the system.

Imaging and video applications need excellent linearity (DNL and INL). In fact, DNL is the most important specification parameter for the ADCs used to capture CCD (charge coupled devices) sensor signals. DNL affects intensity fidelity and causes improper gradation of the image scale with local imperfections. INL corrupts the entire image with a gradual non-linearity which in case of colour images may result in colour artifacts that may cause deceptive results [127]. They also require good low-noise (SNR and SINAD) performance. Some tasks require converters with a fast slew rate sample and hold amplifier to handle a full-scale step response from pixel to pixel. SNR over a wide bandwidth is important in the case of applications which may spread this change over several pixels [66]. SNR is also critical in medical imaging [49].

Low power consumption is an increasingly important specification in every application fields, but it finds particular importance in those where portability is required, such as in camcorders (video), cellular phones (personal communications), walkmans (audio) and portable instrumentation (hand-held measurement and monitoring equipment), where it is important to achieve ever greater autonomy with existing batteries.

#### 3. ADCs' architectures

Table 1.2 presents the most commonly used ADCs' architectures and their respective resolution and conversion (output data) rates for the same application fields depicted in table 1.1. Converters based on  $\Sigma\Delta$  modulation followed by decimation are the most popular for audio applications. Due to their conversion mechanism, the  $\Sigma\Delta$  converter is inherently monotonic and presents very low DNL. Some of the additional advantages are modest circuit accuracy and component matching and trimming requirements, which make them suitable for implementation using imprecise CMOS technologies. Also, the need for external anti-aliasing filtering is reduced by the (digital) decimation process. The requirement for sampling rates up to 48 kHz, 96 kHz, or even 192 kHz for more demanding applications, such as professional audio, are well within the possibilities of even very high resolution  $\Sigma\Delta$  converters. Some other high resolution low sampling rate applications, such as geophysical, make also good use of the advantages of  $\Sigma\Delta$  converters. In this latter case, however, the order of the  $\Sigma\Delta$  modulator must be increased in order to allow for lower oversampling ratios. This trade-off between oversampling ratio and modulator order is also found in  $\Sigma\Delta$  converters for other applications that require relatively high sampling rates (although with lower resolution), such as, sensors, instrumentation, GSM (Global System for Mobile communication), and data transmission. Fourth order, 13-bit, 270 kS/s  $\Sigma\Delta$  converters are used in GSM because the high sampling rate offers the necessary bandwidth to pass the adjacent channels and the blocking levels without aliasing them in the band of interest, and the decimator filter besides providing downsampling also performs channel filtering . The worst case blocking specs of the GSM standard require a conversion linearity of 14-16 bits to avoid a weak received signal being lost due to distortion artifacts [125]. Also, high dynamic range ( $\approx 80 \text{ dB}$ ) and SNR ranging from 86 to 98 dB are fundamental to allow demodulating low level signals immersed in strong adjacent channel interfering signals [76].

Anyway,  $\Sigma\Delta$  have somewhat high power consumption levels when compared with converters of similar resolution and conversion rate using other architectures (pipelined, for instance). Cost and power consumption issues require the use of such specific architectures to achieve high resolution and conversion rate at minimum power consumption, especially in the case of portable, hand-held devices. Equipment of this sort can mainly be found in applications such as mobile and wireless communications, instrumentation, and video. Latency and larger size are two other disadvantages to be taken into account.

| Application                                   | Converter architecture                                                                                       | Resolution (bits)                                            | <b>Conversion</b> rate                                         |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------|

| Audio                                         | ンム<br>ンム、4th-7th order ンム<br>SAR                                                                             | 14-18 for consumer audio<br>18-24 for professional equipment | 48-50 kS/s<br>48-96 kS/s<br>85 to 500 kS/s                     |

| Automatic Control,<br>Sensors and<br>Robotics | 5.0.0<br>と人<br>SAR<br>Integrating                                                                            | 24<br>24<br>8-18<br>18-20<br>16                              | 780 S/s<br>20-2000 kS/s<br>100-2000 S/s<br>192 kS/s            |

|                                               | Half-flash<br>(for high-speed servo control)                                                                 | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~                      | 200-400 kS/s, 1MS/s                                            |

| Data transmission<br>(cable)                  | $\Sigma\Delta$ and high-order (4th) $\Sigma\Delta$ for ISDN <sup><i>a</i></sup> and ADSL <sup><i>b</i></sup> | 12-16 for cancelling modems<br>13-16 for ISDN<br>13 for ADSI | 8 kS/s for modems<br>80-160 kS/s for ISDN<br>2-2 MS/s for ADSI |

| (optical fiber)                               | Pipeline<br>Half-flash                                                                                       | 12 for VDSL <sup><math>c</math></sup><br>8-12                | 40 MS/s for VDSL<br>400 kS/s-1.5 MS/s                          |

| Digital high-speed<br>instrumentation         | Flash, interleaved flash                                                                                     | 8<br>10-12                                                   | 150 MS/s-1 GS/s<br>10-40 MS/s                                  |

|                                               | Flash-SAK nybrid<br>SAR<br>Pipeline                                                                          | 12-10<br>8-18<br>8-14                                        | 82-166 KS/s<br>20-2000 KS/s<br>1-80 MS/s                       |

Table 1.2. Characteristics of ADCs per application.

<sup>&</sup>quot;Integrated services digital network bAsymmetrical digital subscriber loop "Very high data rate digital subscriber loop

| Application        | <b>Converter</b> Architecture       | Resolution(bits) | Conversion rate        |

|--------------------|-------------------------------------|------------------|------------------------|

| Hard disk driving  | Half-flash                          | 10               | 320 kS/s               |

| I                  | Pipeline                            | 8-12             | 800 kS/s-1.5 MS/s      |

|                    | SAR                                 | 8                | 100 kS/s               |

|                    | Flash                               | 9                | 30-140 MS/s            |

| Medical            | Interleaved flash (for $CAT^a$ )    | 8                | 150-750 MS/s           |

|                    | Flash                               | 8                | 1 GS/s                 |

|                    | SAR                                 | 8-18             | 20-2000 kS/s           |

|                    | $\Sigma\Delta$                      | 14-16            | 200-10000 kS/s         |

|                    | Pipeline                            | 8-14             | 1-80 MS/s              |

| Military           | Flash, interleaved flash            | 8                | 150-750 MS/s           |

| communications     | Subranging, pipeline,               | 10               | 1.5 GS/s               |

| Electronic warfare | Folding, and interpolating          | 12-14            | 50-100 MS/s            |

|                    |                                     | 8                | 3 GS/s                 |

| Mobile             | SAR for GSM                         | 8 for GSM        | 270 kS/s for GSM       |

| telecommunications | $\Sigma\Delta$ and high-order (4th) |                  |                        |

| and wireless       | $\Sigma\Delta$ for GSM              | 13 for GSM       |                        |

| communications     | Half-flash                          | 8-10             | 320-500 kS/s, 1 MS/s   |

|                    | Pipeline                            | 8-14             | 1-80 MS/s              |

|                    | Flash                               | 6 for satellite  | 40-80 MS/s             |

|                    | Flash and interleaved flash         | 8                | 150 MS/s-1 GS/s for RF |

|                    | Pineline                            | 12-14            | 18-65 MS/c for IF      |

<sup>a</sup>Computer axial tomography

Table 1.2 (continued)

| Application                                          | Converter architecture                                                                                                  | Resolution(bits)                              | Conversion rate                                                              |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------|

| Geophysical                                          | $\Sigma\Delta$                                                                                                          | 16-24                                         | 1-32 kS/s                                                                    |

| Monitoring,<br>test equipment and<br>instrumentation | ンム<br>Half-flash<br>SAR<br>ンム                                                                                           | 22-24<br>8<br>8-18<br>14-16                   | down to < 1 kS/s<br>400 kS/s<br>20-2000 kS/s<br>200-10000 kS/s               |

| Radar and sonar                                      | Flash and interleaved flash<br>Pipeline<br>Subranging, pipeline,<br>Folding and interpolating for radar<br>∑∆ for sonar | 8<br>12<br>12-14 for radar<br>16-18 for sonar | 150 Ms/s-1 GS/s<br>10-30 MS/s<br>50-100 MS/s for radar<br>200 kS/s for sonar |

| Spectrum<br>analysis                                 | Pipeline<br>SAR                                                                                                         | 10-12<br>12-14                                | 10-40 MS/s<br>300-500 kS/s                                                   |

| Speech and voice<br>communications                   | SAR<br>ΣΔ                                                                                                               | 8-18<br>11-14                                 | 20-2000 kS/s<br>8 kS/s                                                       |

| Video<br>and Television                              | Half-flash for professional video<br>Pipeline                                                                           | 8-12<br>8-12                                  | 10-40 MS/s<br>30-50 MS/s                                                     |

Table 1.2 (continued) Characteristics of ADCs per application. In the first GSM generation 8 bit SAR (successive approximations) converters were used. Comparing to  $\Sigma\Delta$  these converters present the advantage of joining smaller size, lower power, and lower latency, but on the other hand require stringent trimming to achieve good accuracy and more tight front-end anti-aliasing filtering. Automatic control is a field where their fast sampling with no latency and good resolution match well together.

Data communication is another application that demands frequently low power. Architectures for data transmission, with the increase in resolution and conversion rate requirements, have migrated from SAR and flash to  $\Sigma\Delta$ , and pipeline.  $\Sigma\Delta$  converters are used for instance in ISDN, with 3rd order architectures achieving 16 MHz sampling frequencies. In ADSL, due to the high Nyquist rates needed (2.2 MHz conversion rate), high order (4th)  $\Sigma\Delta$  converters are currently being used. In order to reduce power consumption pipelined converters with 8.8 MHz sampling frequency (2.2 MHz conversion rate) will be used in the future, the trade-off being stricter production tolerances.  $\Sigma\Delta$ converters are not an option for VDSL due to the high speed requirements. Full flash, subranging, folding and interpolating, and pipelined ADCs are better alternatives, the pipelined being the best option as it is possible to attain 10-12 bits resolution at 10-100 MS/s conversion rates. Pipelined architectures are also ideal for A/D converters requiring both high speed and high resolution [98], thus finding preferred use in applications such as video, data communications (for ADSL and VDSL) and medical imaging. Folding and interpolating converters, being capable of higher sampling rates but lower resolutions, are also becoming an alternative in these areas. Folding and interpolating 8-bit 3 GS/s, and pipelined 10-bit 1.5 GS/s state-of-the-art ADCs for defense applications have been reported [107].

In wireless communications the current trend is towards moving the signal quantisation procedure into the RF (radio frequency) stage and performing IF filtering in a digital form (the concept of "software radio") [86, 144]. This obviously creates the need for extremely high conversion rate converters with high SFDR to avoid interchannel mixing because the quantiser precedes the IF filter. This is an example of a perfect application field for parallel (flash) or time-interleaved pipelined converters, in which several pipeline converters sample the same signal in intermediate time instants, thus achieving a higher sample rate than a single converter with the wide dynamic range characteristics of slow converters.

Flash converters, from a power dissipation perspective, are acceptable only at low resolution (up to 8 bits) levels where the number of comparators is relatively small and their offset is non-critical — every extra bit requires doubling the comparators in number and accuracy. At resolutions in the 8-12 bits range, the only practical options for low power dissipation are multistep flash and pipeline configurations. Multistep flash has been successfully used in low-

power applications at the 10-bit level. Pipeline are also attractive and have the potential advantages of inherent single-path sampling of the signal, giving good high-frequency effective bit performance, and the capability of using non-critical purely dynamic comparators because of the amplification of the signal in the pipeline coupled with the use of digital correction. In video, for digitisation of the CCD sensor array information, and due to the amount and update rate of the same, a high-speed converter is necessary — flash (in the past) and pipeline being the preferred converter architectures.

#### 4. Terminology

In the ADCs' domain one can often find different terms meaning the same thing, or to find different definitions for the same terms. Currently, different terms and acronyms are likely to be found among data sheets from different ADC manufacturers — e.g., while some use DNL for Differential Non-Linearity, others use  $E_D$  [126, 153]. To designate the effective number of bits acronyms like ENB, NOEB, ENOB, E,  $b_{ef}$  are likely to be found. In this case we suggest to use  $N_{ef}$  as N is already used to identify the number of bits. In order to have a single symbol to identify common parameters,  $\eta$  is used to designate parameters or quantities related to noise,  $\varepsilon$  is used for those related to errors, and  $\sigma$  for those concerning deviation. For example,  $\eta_f$ ,  $\varepsilon_G$ , and  $\sigma_j$ , would identify respectively, noise floor, gain flatness error, and jitter.

Also, commonly the parameters specified in ADCs' data sheets are different for different manufacturers, being that dynamic characterisation parameters are not always specified. It is likely that only one of signal to noise ratio (SNR or S/N) and signal to noise and distortion ratio (SINAD) is specified. Frequently, the parameter total harmonic distortion plus noise (THD+N) is used instead of SINAD. Many manufacturers define the same specification differently, or use different methods to evaluate the parameters. For example, the range (number) of frequencies which are considered as harmonics (excluding DC) varies — some use the first ten harmonics [6], others only the second through the sixth harmonics [151], but specific applications may require considering all harmonics in the frequency range of interest.

This difference among terms and definitions used by different parties can also be found between standards. Table 1.3 presents a résumé of the terms described in standards IEEE-STD-1241 [6] and IEC 60748-4 [3]. At a first glance one can see that the IEC standard addresses mainly static performance characterisation terminology.

Looking at the definitions used in these two documents one can see that, in general, terms addressed by both are defined in a different manner. See, for example, the definition given for analogue-to-digital converter:

**IEEE** A device that converts a continuous time signal into a discrete-time discrete-amplitude signal.

Table 1.3. Comparison between IEEE 1241 and IEC 60748-4 terminologies.

| IEEE 1241                              | IEC 60748-4                          |

|----------------------------------------|--------------------------------------|

|                                        | absolute accuracy error, total error |

| AC-coupled ADC                         | •                                    |

| alternation band                       |                                      |

|                                        | conversion code                      |

| analog-to-digital converter (ADC)      | analog-to-digital converter (ADC)    |

|                                        | linear ADC, non-linear ADC           |

| aperture delay                         |                                      |

| aperture uncertainty                   |                                      |

| common-mode rejection ratio            |                                      |

| code bin k                             | step                                 |

| code bin width W[k]                    | step width                           |

| ideal code bin width (Q)               | 1                                    |

| code transition level                  |                                      |

| code transition level T[k]             | transition value                     |

| coherent sampling                      |                                      |

| common-mode out-of-range               |                                      |

| common-mode out-of-range recovery time |                                      |

| common-mode signal                     |                                      |

| 0                                      | conversion time                      |

| crosstalk                              |                                      |

| differential input impedance to ground |                                      |

| differential non-linearity             | differential linearity error         |

| differential signal                    | •                                    |

| epoch                                  |                                      |

| equivalent-time sampling               |                                      |

| full-scale range                       | full-scale ranges                    |

| -                                      | full-scale, zero-scale               |

|                                        | nominal full-scale value             |

| full-scale signal                      |                                      |

| full-width-at-half-max (FWHM)          |                                      |

|                                        | full-scale error                     |

|                                        | zero-scale error                     |

*Table 1.3 (continued)* Comparison between IEEE 1241 and IEC 60748-4 terminologies.

| IEEE 1241                            | IEC 60748-4                        |

|--------------------------------------|------------------------------------|

| gain and offset                      | gain, offset point, gain point     |

| (A) (independently based)            |                                    |

| (B) (terminal-based)                 |                                    |

|                                      | offset error, gain error           |

| harmonic distortion                  |                                    |

| hysteresis                           |                                    |

| incoherent sampling                  |                                    |

| input impedance                      |                                    |

| integral non-linearity               | (end-points) linearity error       |

|                                      | best-straight-line linearity error |

| kth code transition level T[k]       |                                    |

| large signal                         |                                    |

| least-significant bit (LSB)          | LSB                                |

| long-term settling error             |                                    |

| maximum common-mode signal level     |                                    |

| maximum operating common-mode signal |                                    |

| maximum safe input signal level      |                                    |

|                                      | missing code                       |

| monotonic ADC                        | monotonicity                       |

| noise (total)                        | noise                              |

| normal mode signal                   |                                    |

| equal to the differential signal     |                                    |

| overshoot                            |                                    |

| out-of-range input                   |                                    |

| passband                             |                                    |

| phase non-linearity                  |                                    |

| pipeline delay                       |                                    |

| precursor                            |                                    |

| probability density function         |                                    |

| quantization                         |                                    |

| quantization error/noise             | inherent quantization error        |

| random noise                         |                                    |

#### *Table 1.3 (continued)* Comparison between IEEE 1241 and IEC 60748-4 terminologies.

| IEEE 1241                                    | IEC 60748-4     |

|----------------------------------------------|-----------------|

| record of data                               |                 |

| relatively prime                             |                 |

| residuals                                    |                 |

|                                              | resolution      |

|                                              | roll-over error |

| root-mean-square (rms)                       |                 |

| root-sum-square (rss)                        |                 |

| sampling                                     |                 |

|                                              | conversion rate |

| settling time                                |                 |

| short-term settling time                     |                 |

| signal-to-noise and distortion ratio (SINAD) |                 |

| signal to full scale ratio (SFSR)            |                 |

| signal to non-harmonic ratio (SNHR)          |                 |

| single-ended ADC                             |                 |

| slew limit                                   |                 |

| spurious components                          |                 |

| spurious-free dynamic range (SFDR)           |                 |

| step (or pulse) baseline                     |                 |

| step response                                |                 |

| step (or pulse) topline                      |                 |

| synchronous and asynchronous sampling        |                 |

| timing jitter                                |                 |

| timing phase                                 |                 |

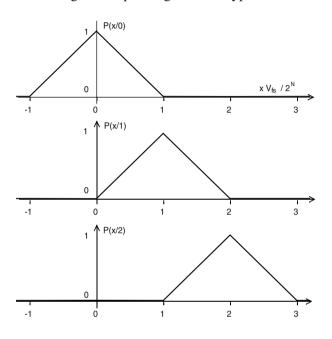

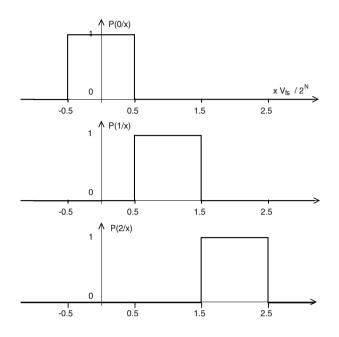

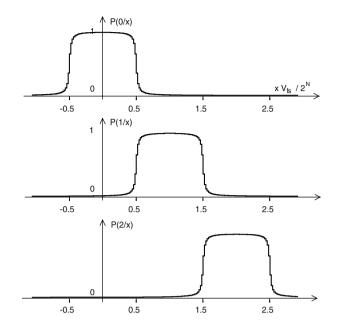

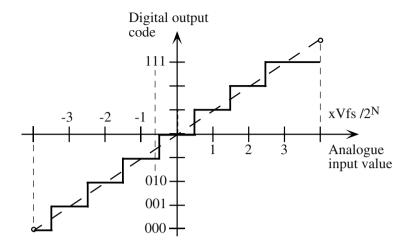

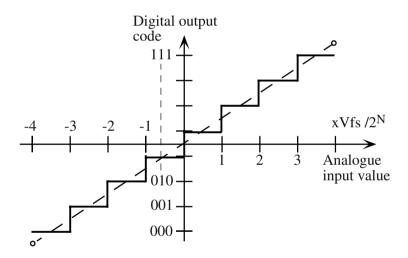

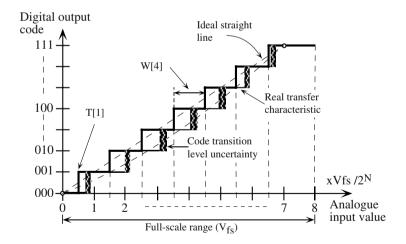

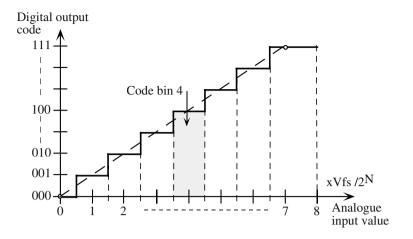

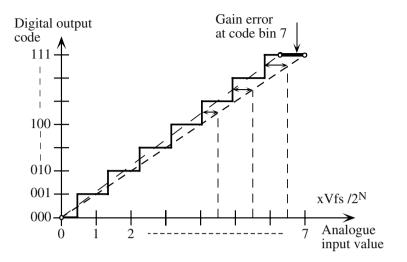

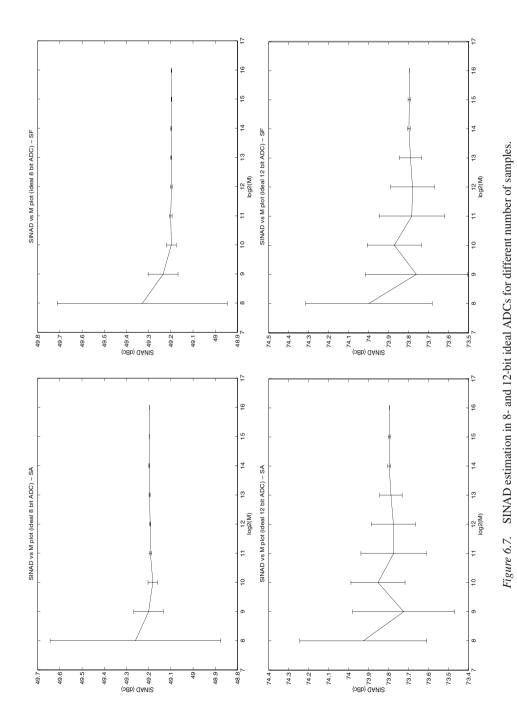

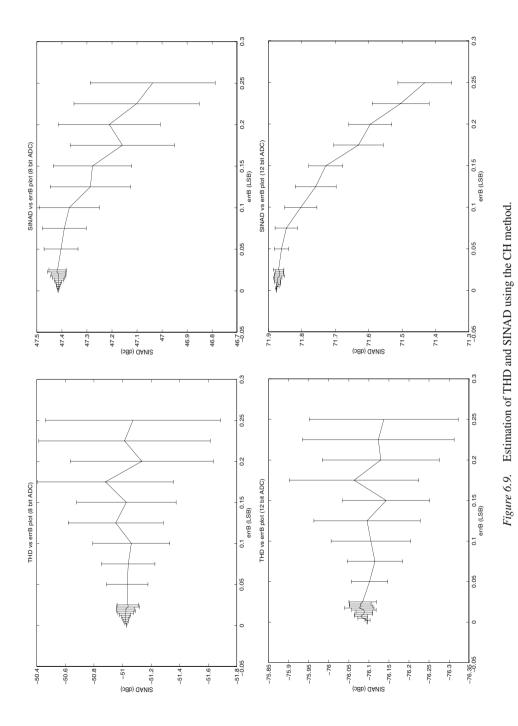

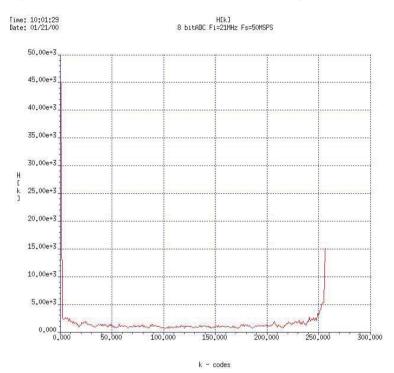

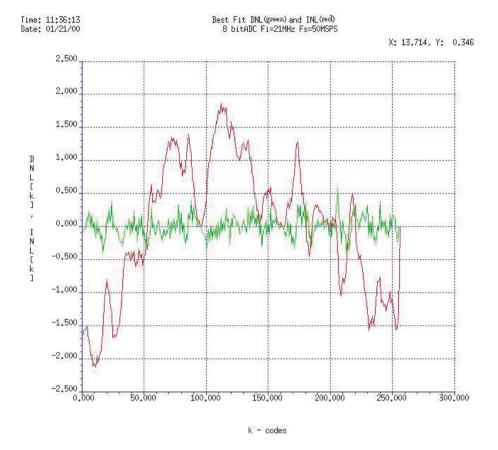

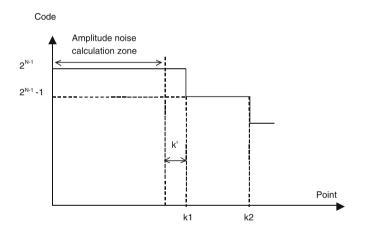

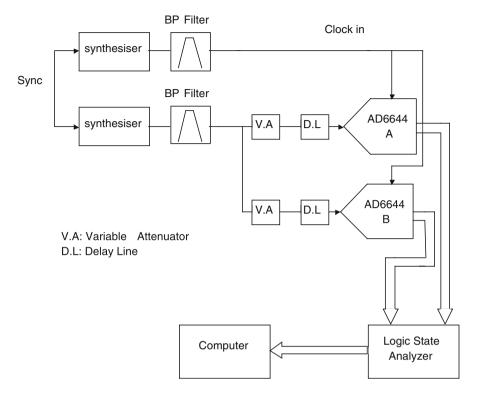

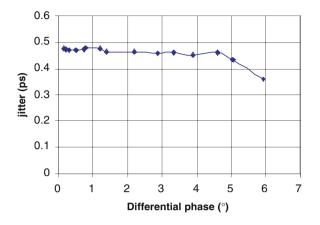

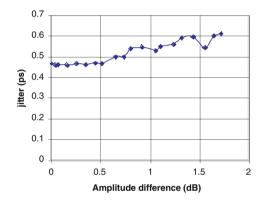

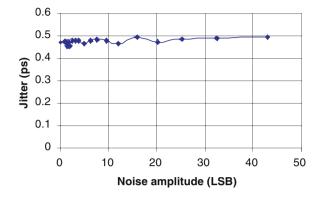

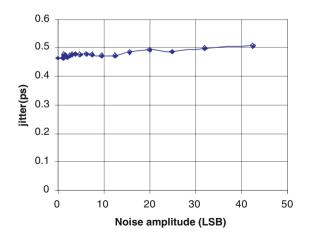

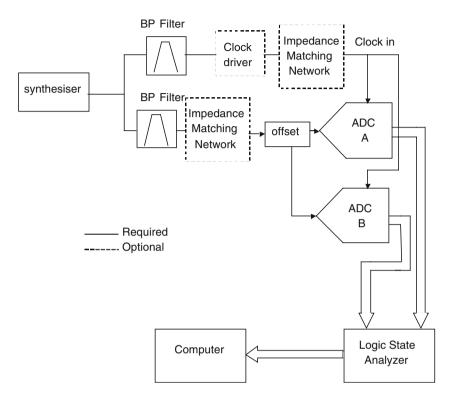

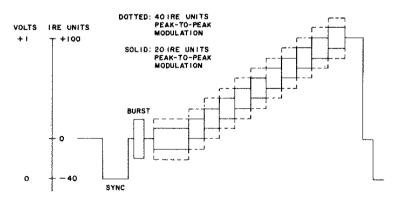

| total harmonic distortion (THD)              |                 |