## LOW-POWER PROCESSORS AND SYSTEMS ON CHIPS

## Christian Piguet

Neuchâtel, Switzerland

A CRC title, part of the Taylor & Francis imprint, a member of the Taylor & Francis Group, the academic division of T&F Informa plc.

This material was previously published in Low Power Electronics Design. © CRC Press LLC 2004.

Published in 2006 by CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742

© 2006 by Taylor & Francis Group, LLC CRC Press is an imprint of Taylor & Francis Group

No claim to original U.S. Government works Printed in the United States of America on acid-free paper 10 9 8 7 6 5 4 3 2 1

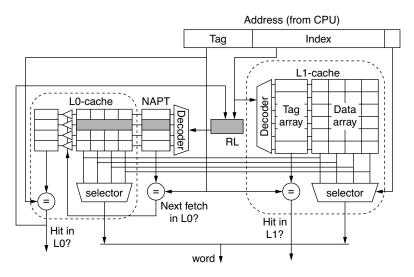

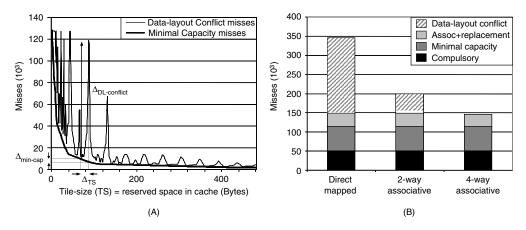

International Standard Book Number-10: 0-8493-6700-X (Hardcover) International Standard Book Number-13: 978-0-8493-6700-7 (Hardcover) Library of Congress Card Number 2005050175

This book contains information obtained from authentic and highly regarded sources. Reprinted material is quoted with permission, and sources are indicated. A wide variety of references are listed. Reasonable efforts have been made to publish reliable data and information, but the author and the publisher cannot assume responsibility for the validity of all materials or for the consequences of their use.

No part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access www.copyright.com (http://www.copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC) 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

Trademark Notice: Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

#### Library of Congress Cataloging-in-Publication Data

Piguet, Christian.

Low-power processors and systems on chips / Christian Piguet.

p. cm.

Includes bibliographical references and index.

ISBN 0-8493-6700-X (alk. paper)

1.Microprocessors – Power supply. 2. Systems on a chip. 3. Low voltage integrated circuits. I. Title.

TK7895.M5P54 2005 621.39'16—dc22

is the Academic Division of T&F Informa plc.

Visit the Taylor & Francis Web site at http://www.taylorandfrancis.com

2005050175

and the CRC Press Web site at http://www.crcpress.com

### Preface

#### Purpose and Background

The present book is a part of the book "Low-Power Electronics Design," edited by Christian Piguet, published in November 2004. It contains only the chapters that describe the design of low-power processors and systems-on-chips from microprocessors, DSP cores, reconfigurable processors, memories, systems-on-chip issues, applications such as ad hoc networks and finally embedded software. All the other chapters, describing microelectronics technologies, transistor models, logic circuits and CAD tools, are also included in another smaller book entitled "Low-Power CMOS Circuits: Technology, Logic Design and CAD Tools."

The goal of the present book "Low-Power Processors and Systems on Chips" is to cover all the aspects of the design of low-power microprocessors in deep submicron technologies. Today, the power consumption of microprocessors is considered as one of the most important problems for high-performance chips as well as for portable devices. For the latter, it is due to the limited cell battery lifetime, while it is the chip cooling for the first case. As a result, for any chip design, power consumption has to be taken into account very seriously. Before 1993–1994, only speed and silicon area were important in the design of integrated circuits, and power consumption was not an issue. Just after, it was recognized that power consumption has to be taken into account as a main design parameter. Many papers and books were written to describe all the first design methodologies to save power limited to circuit design. However, today, we have to cope with many new problems implied by very deep submicron technologies, such as leakage power, interconnect delays and robustness.

Today, we are close to designing one billion transistor microprocessor chips, down to 0.10  $\mu$ m and below, supplied at less than half a volt and working at some GHz. This is due to an unexpected evolution of the microelectronics technologies and to very innovative microprocessor architectures. This evolution is not yet at its end, so the next decade will also see some spectacular improvements in the design of microprocessor circuits. However, it is sure that the microprocessor architecture evolution is not always a revolution, but as pointed out by:

"I was greatly amused few years ago — when companies were introducing pipelined microprocessors — to learn that RISC technology enabled pipelining. That this could be responsible for pipelining, which has existed for more than 30 years, illustrates the amnesia present in computer engineering"

Michael J. Flynn

#### Organization

The first part of the proposed book starts with a chapter about the design of low-power microprocessors regarding the technology variations. The next three chapters present the design of Digital Signal Proces-

sors (DSP) for embedded applications. They have to provide huge power computation as well as very small power consumption. So many different DSP architectures have been proposed, well adapted to some specific DSP algorithms, working in cooperation with hardware accelerators or based on reconfigurable hardware. Asynchronous design for microprocessors is also proposed to reduce power consumption. In wireless communication, low-power baseband processors are a key issue for portable devices. However, a significant part of the power consumption is due to program and data memories, and the last three chapters of this first part present some techniques to reduce dynamic and static power at the electrical level as well as at the system level while using cache memories or specific memory organization.

The second part of the book is a set of chapters describing several aspects of low-power systems on chips (SoCs). They include hardware and embedded software aspects, such as operating systems (OS), data storage in an efficient way and networks on chips. The next chapters present some applications requiring very low power SoCs, such as ad hoc networks with very low-power radios as well as routing strategies and sensing and actuation devices.

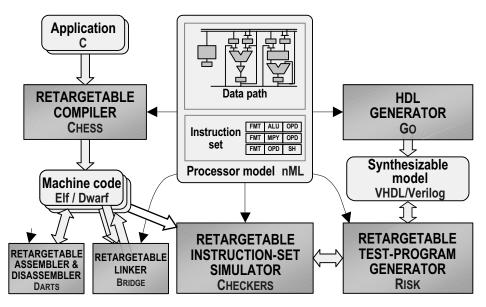

The third part of the book presents issues about embedded software, i.e., application software and compilers. The development tools including compilers, retargetable compilers, and coverification tools are presented in details.

The key benefits for readers will be this complete picture of what is done today for reducing power for microprocessors, DSP cores, memories, systems on chips, and embedded software.

#### **Locating Your Topic**

Several avenues are available to access desired information. A complete table of contents is presented at the front of the book. Each of the chapter is also preceded with an individual table of contents. Each contributed chapter contains comprehensive references including books, journal and magazine papers, and sometimes Web pointers.

#### Acknowledgments

The value of this book is completely based on the many excellent contributions of experts. I am very grateful to them, as they spent a lot of time writing excellent texts without any compensation. Their sole motivation was to provide readers excellent contributions. I would like to thank all these authors, as I am sure this book will be a very good text for many readers and students interested in low-power design. I am indebted to Prof. Vojin G. Oklobjzija for asking me to edit this book and trusting me with this project. I would also like to thank Nora Konopka and Allison Taub of CRC Press for their excellent work in putting all this material in the present form. It is the work of all that made this book.

## The Editor

**Christian Piguet** was born in Nyon, Switzerland, on January 18, 1951. He received the M. S. and Ph. D. degrees in Electrical Engineering from the Ecole Polytechnique Fédérale de Lausanne, Switzerland in 1974 and 1981, respectively.

He joined the Centre Electronique Horloger S.A., Neuchâtel, Switzerland, in 1974. He worked on CMOS digital integrated circuits for the watch industry, on low-power embedded microprocessors as well as on CAD tools based on a gate matrix approach. He is now Head of the Ultra-Low-Power Sector at the CSEM Centre Suisse d'Electronique et de Microtechnique S.A., Neuchâtel, Switzerland. He is presently involved in the design and management of low-power and high-speed integrated circuits in CMOS technology. His main interests include the design of very lowpower microprocessors and DSPs, low-power standard cell libraries, gated clock and low-power techniques as well as asynchronous design.

He is Professor at the Ecole Polytechnique Fédérale Lausanne (EPFL), Switzerland, and also lectures in VLSI and microprocessor design at the University of Neuchâtel, Switzerland and in the ALaRI master program at the University of Lugano, Switzerland. He is also a lecturer for many postgraduates courses in low-power design.

Christian Piguet holds about 30 patents in digital design, microprocessors and watch systems. He is author and coauthor of more than 170 publications in technical journals and of books and book chapters in low-power digital design. He has served as reviewer for many technical journals. He also served as Guest Editor for the July 1996 JSSC Issue. He is a member of steering and program committees of numerous conferences and has served as Program Chairman of PATMOS'95 in Oldenburg, Germany, co-chairman at FTFC'99 in Paris, Chairman of the ACiD'2001 Workshop in Neuchâtel, Co-Chair of VLSI-SOC 2001 in Montpellier and Co-Chair of ISLPED 2002 in Monterey. He was Chairman of the PATMOS executive committee during 2002. He was Low-Power Topic Chair at DATE 2004 and 2005.

> Christian Piguet, CSEM SA, Jaquet-Droz 1, 2000 Neuchâtel, Switzerland Christian.piguet@csem.ch

## Contents

#### I Low-Power Processors and Memories

| 1 | Techniques for Power and Process Variation Minimization1-1                                                    |

|---|---------------------------------------------------------------------------------------------------------------|

|   | Lawrence T. Clark and Vivek De                                                                                |

| 2 | Low-Power DSPs2-1                                                                                             |

|   | Ingrid Verbauwhede                                                                                            |

| 3 | Energy-Efficient Reconfigurable Processors                                                                    |

|   | Raphaël David, Sébastien Pillement, and Olivier Sentieys                                                      |

| 4 | Macgic, a Low-Power Reconfigurable DSP4-1                                                                     |

|   | Flavio Rampogna, Pierre-David Pfister, Claude Arm, Patrick Volet,<br>Jean-Marc Masgonty, and Christian Piguet |

| 5 | Low-Power Asynchronous Processors                                                                             |

|   | Kamel Slimani, Joao Fragoso, Mohammed Es Sahliene, Laurent Fesquet,<br>and Marc Renaudin                      |

| 6 | Low-Power Baseband Processors for Communications                                                              |

|   | Dake Liu and Eric Tell                                                                                        |

| 7 | Stand-By Power Reduction for SRAM Memories                                                                    |

|   | Stefan Cserveny, Jean-Marc Masgonty, and Christian Piguet                                                     |

| 8 | Low-Power Cache Design                                                                                        |

|   | Vasily G. Moshnyaga and Koji Inoue                                                                            |

| 9 | Memory Organization for Low-Energy Embedded Systems9-1                                                        |

|   | Alberto Macii                                                                                                 |

#### II Low-Power Systems on Chips

| 10 | Power-Performance Trade-Offs in Design of SoCs                                           | -1 |

|----|------------------------------------------------------------------------------------------|----|

|    | Victor Zyuban and Philip Strenski                                                        |    |

| 11 | Low-Power SoC with Power-Aware Operating Systems Generation11                            | -1 |

|    | Sungjoo Yoo, Aimen Bouchhima, Wander Cesario, Ahmed A. Jerraya,<br>and Lovic Gauthier    |    |

| 12 | Low-Power Data Storage and Communication for SoC12                                       | -1 |

|    | Miguel Miranda, Erik Brockmeyer, Tycho van Meeuwen, Cedric Ghez,<br>and Francky Catthoor |    |

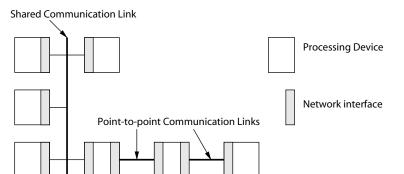

| 13 | Networks on Chips: Energy-Efficient Design of SoC Interconnect13-1                                 |

|----|----------------------------------------------------------------------------------------------------|

|    | Luca Benini, Terry Tao Ye, and Giovanni de Micheli                                                 |

| 14 | Highly Integrated Ultra-Low Power RF Transceivers for Wireless<br>Sensor Networks                  |

|    | Brian P. Otis, Yuen Hui Chee, Richard Lu, Nathan M. Pletcher,<br>Jan M. Rabaey, and Simone Gambini |

| 15 | Power-Aware On-Demand Routing Protocols for Mobile Ad Hoc Networks15-1                             |

|    | Morteza Maleki and Massoud Pedram                                                                  |

| 16 | Modeling Computational, Sensing, and Actuation Surfaces16-1                                        |

|    | Phillip Stanley-Marbell, Diana Marculescu, Radu Marculescu,<br>and Pradeep K. Khosla               |

#### III Embedded Software

| 17 | Low-Power Software Techniques                                                                                                |

|----|------------------------------------------------------------------------------------------------------------------------------|

|    | Catherine H. Gebotys                                                                                                         |

| 18 | Low-Power/Energy Compiler Optimizations                                                                                      |

|    | Ulrich Kremer                                                                                                                |

| 19 | Design of Low-Power Processor Cores Using a Retargetable Tool Flow                                                           |

|    | Gert Goossens, Peter Dytrych, and Dirk Lanneer                                                                               |

| 20 | Recent Advances in Low-Power Design and Functional Coverification<br>Automation from the Earliest System-Level Design Stages |

|    | Thierry JF. Omnès, Youcef Bouchebaba, Chidamber Kulkarni,<br>and Fabien Coelho                                               |

## Contributors

**Claude Arm** CSEM Neuchâtel, Switzerland

**Luca Benini** University of Bologna Bologna, Italy

**Youcef Bouchebaba** University of Nantes Nantes, France

**Aimen Bouchhima** TIMA Laboratory Grenoble, France

**Erik Brockmeyer** IMEC Leuven, Belgium

**Francky Catthoor** IMEC Leuven, Belgium and Katholiek University Leuven, Belgium

Wander Cesario TIMA Laboratory Grenoble, France

**Yuen Hui Chee** University of California–Berkeley Berkeley, California **Lawrence T. Clark** Arizona State University Tempe, Arizona

**Fabien Coelho** Ecole des Mines Paris, France

**Stefan Cserveny** CSEM Neuchâtel, Switzerland

**Raphaël David** ENSSAT/University of Rennes Lannion, France

**Vivek De** Intel Labs Santa Clara, California

**Peter Dytrych** Philips Digital Systems Laboratories Leuven, Belgium

**Laurent Fesquet** TIMA Laboratory Grenoble, France

**Joao Fragoso** TIMA Laboratory Grenoble, France

**Simone Gambini** Universita di Pisa Pisa, Italy **Lovic Gauthier** FLEETS Fukuoka, Japan

**Catherine H. Gebotys** University of Waterloo Waterloo, Ontario, Canada

**Cedric Ghez** IMEC Leuven, Belgium

**Gert Goossens** Target Compilers Technologies Leuven, Belgium

**Koji Inoue** Fukuoka University Fukuoka, Japan

**Ahmed A. Jerraya** TIMA Laboratory Grenoble, France

**Pradeep K. Khosla** Carnegie Mellon University Pittsburgh, Pennsylvania

Ulrich Kremer Rutgers University Piscataway, New Jersey

**Chidamber Kulkarni** University of California–Berkeley Berkeley, California

**Dirk Lanneer** Philips Digital Systems Laboratories Leuven, Belgium

**Dake Liu** Department of Electrical Engineering Linköping University Linköping, Sweden **Richard Lu** University of California–Berkeley Berkeley, California

**Alberto Macii** Politecnico di Torino Torino, Italy

**Morteza Maleki** University of Southern California Los Angeles, California

**Diana Marculescu** Carnegi Mellon University Pittsburgh, Pennsylvania

**Radu Marculescu** Carnegie Mellon University Pittsburgh, Pennsylvania

**Jean-Marc Masgonty** CSEM Neuchâtel, Switzerland

**Tycho van Meeuwen** IMEC Leuven, Belgium

**Giovanni de Micheli** Stanford University Stanford, California

**Miguel Miranda** IMEC Leuven, Belgium

**Vasily G. Moshnyaga** Fukuoka University Fukuoka, Japan

**Thierry J.-F. Omnès** Philips Semiconductors Eindhoven, The Netherlands **Brian P. Otis** University of California–Berkeley Berkeley, California

**Massoud Pedram** University of Southern California Los Angeles, California

**Pierre-David Pfister** CSEM Neuchâtel, Switzerland

**Christian Piguet** CSEM & LAP-EPFL Neuchâtel, Switzerland

**Sébastien Pillement** ENSSAT/University of Rennes Lannion, France

**Nathan M. Pletcher** University of California–Berkeley Berkeley, California

**Jan M. Rabaey** University of California–Berkeley Berkeley, California

**Flavio Rampogna** CSEM Neuchâtel, Switzerland

Marc Renaudin TIMA Laboratory Grenoble, France

**Mohammed Es Sahliene** TIMA Laboratory Grenoble, France **Olivier Sentieys** ENSSAT/University of Rennes Lannion, France

**Kamel Slimani** TIMA Laboratory Grenoble, France

**Phillip Stanley-Marbell** Carnegie Mellon University Pittsburgh, Pennsylvania

**Philip Strenski** IBM Watson Research Center Yorktown Heights, New York

**Eric Tell** Linköping University Linköping, Sweden

**Ingrid Verbauwhede** University of California–Los Angeles Los Angeles, California

**Patrick Volet** CSEM Neuchâtel, Switzerland

**Terry Tao Ye** Stanford University Stanford, California

**Sungjoo Yoo** TIMA Laboratory Grenoble, France

**Victor Zyuban** IBM Watson Research Center Yorktown Heights, New York

# Ι

## Low-Power Processors and Memories

| 1 | Techniques for Power and Process Variation Minimization                                                       | 1-1 |

|---|---------------------------------------------------------------------------------------------------------------|-----|

|   | Lawrence T. Clark and Vivek De                                                                                |     |

| 2 | Low-Power DSPs                                                                                                | 2-1 |

|   | Ingrid Verbauwhede                                                                                            |     |

| 3 | Energy-Efficient Reconfigurable Processors                                                                    | 3-1 |

|   | Raphaël David, Sébastien Pillement, and Olivier Sentieys                                                      |     |

| 4 | Macgic, a Low-Power Reconfigurable DSP                                                                        | 4-1 |

|   | Flavio Rampogna, Pierre-David Pfister, Claude Arm, Patrick Volet,<br>Jean-Marc Masgonty, and Christian Piguet |     |

| 5 | Low-Power Asynchronous Processors                                                                             | 5-1 |

|   | Kamel Slimani, Joao Fragoso, Mohammed Es Sahliene, Laurent Fesquet,<br>and Marc Renaudin                      |     |

| 6 | Low-Power Baseband Processors for Communications                                                              | 6-1 |

|   | Dake Liu and Eric Tell                                                                                        |     |

| 7 | Stand-By Power Reduction for SRAM Memories                                                                    | 7-1 |

|   | Stefan Cserveny, Jean-Marc Masgonty, and Christian Piguet                                                     |     |

| 8 | Low-Power Cache Design                                                                                        | 8-1 |

|   | Vasily G. Moshnyaga and Koji Inoue                                                                            |     |

| 9 | Memory Organization for Low-Energy Embedded Systems                                                           | 9-1 |

|   | Alberto Macii                                                                                                 |     |

# 1

## Techniques for Power and Process Variation Minimization

| 1.1    | Introduction                                                                                                                                                 | <b>1-</b> 1  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 1.2    | Integrated Circuit Power<br>Active Power and Delay • Leakage Power                                                                                           | 1-2          |

| 1.3    | Process Selection and Rationale<br>Effective Frequency                                                                                                       | <b>1-</b> 3  |

| 1.4    | Leakage Control via Reverse Body Bias<br>RBB on a 0.18-µM IC • Circuit Configuration • Layout •<br>Regulator Design • Limits of Operation • Measured Results | 1-5          |

| 1.5    | System Level Performance<br>System Measurement Results                                                                                                       | <b>1-</b> 11 |

| 1.6    | Process, Voltage, and Temperature Variations<br>Process Variation • Supply Voltage Variation • Temperature<br>Variation                                      | <b>1-</b> 13 |

| 1.7    | Variation Impact on Circuits and<br>Microarchitecture<br>Design Choice Impact • Microarchitecture Choice Impact                                              | <b>1-</b> 16 |

| 1.8    | Adaptive Techniques and Variation Tolerance<br>Body Bias Control Techniques • Adaptive Body Bias and Supply<br>Bias                                          | <b>1-</b> 17 |

| 1.9    | Dynamic Voltage Scaling<br>Clock Generation • Experimental Results                                                                                           | 1-20         |

| 1.10   | Conclusions                                                                                                                                                  | 1-23         |

| Refere | ences                                                                                                                                                        |              |

Lawrence T. Clark

Vivek De Intel Labs

#### 1.1 Introduction

For more than a decade, integrated circuit (IC) power has been steadily increasing due to higher integration and performance enabled by process scaling. As shrinking transistor dimensions are fabricated, and as the absolute value of the dimensions diminish, greater device variations must be addressed. Until recently, increased power was driven primarily by active switching power. Threshold voltages must be decreased to maintain performance at the lower supply voltages required by thinner oxides, however, raising drain to source leakage exponentially. Steeper doping gradients and higher electric fields increase other leakage components, giving rise in sub-0.25-µm generations to DC leakage currents that may limit overall power and performance in future chips. This comes on top of still increasing active power dissipation, driven by architectural changes such as greater parallelism and deeper pipelining. The latter implies fewer gates per stage and, in turn, requires more aggressive circuit techniques such as domino, which can also increase active power. Having fewer logic stages increases the susceptibility to process variations. Finally, as scaling requires lower voltages, in-die and system-level voltage variations are also increasingly problematic.

The focus of this chapter includes the design implications of increasing device variation and leakage. The mechanisms are a direct result of basic physics and will continue to grow in importance over time, requiring design effort to mitigate them. Variation in microprocessor frequency has been dealt with by "speed binning," whereby faster dies are separated and sold at a premium. Dies with inadequate speed or excessive standby current are discarded. These yield considerations are important for robust design. We also discuss design techniques, notably the application of body bias and supply voltage adjustment, which can help deal with both variation and average leakage, as well as active power. Examples from fabricated designs demonstrating the efficacy of the techniques are discussed.

#### 1.2 Integrated Circuit Power

Increasing leakage currents are a natural by-product of transistor scaling and comprise a significant portion of the total power since the 0.25-µm-process generation. By the 90-nm technology node, it can contribute over a fifth of the total IC power on high-performance products [1]. The profusion of batterypowered "hand-held" devices introduced in recent years (e.g., cell phones and personal digital assistants) has made power management a first-order design consideration. These sections focus on circuit design approaches to alleviate leakage power using reverse body bias (RBB) "Drowsy" mode when an IC is in a standby mode and later, in Section 18.9, optimizing the active power by dynamic voltage management (DVM). Although other implementations are briefly discussed, the bulk of the discussion describes the specific implementation on the 0.18-µm XScale microprocessor cores intended for system-on-chip (SoC) applications [2].

#### **1.2.1** Active Power and Delay

The total power of a static CMOS integrated circuit is given by

$$P_{tot} = P_{dyn} + P_{static} + P_{short-circuit}$$

(1.1)

representing the dynamic power (i.e., that due to charging and discharging capacitances during switching) the static leakage power, and the "short-circuit" or crowbar power due to both P and N transistors being on simultaneously during a switching event, respectively. The latter term tracks with the active power and is generally on the order of 5% or less for well-designed circuits. It is typically ignored, as it will be here. The dynamic power of a digital circuit follows the well-known

$$P_{dyn} = a/2 C V_{dd}^2 F$$

(1.2)

where C is the switched capacitance,  $V_{dd}$  is the power supply voltage, F is the operating frequency, and *a* is the switching activity factor measured in transitions per clock cycle. Leveraging the  $V_{dd}^2$  dependency is consequently the most effective method for lowering digital system power; however, the switching speed of a digital circuit with a fixed input slope and fixed load is given by Chen and Hu [3]:

$$T_{delay} = K V_{dd} / (V_{dd} - V_t)^{\alpha}$$

(1.3)

where  $\alpha^*$  is typically 1.1 to 1.5 for modern velocity saturated devices, tending toward the former for NMOS and the latter for PMOS [4], and K is a constant depending on the process. To first order, this

$<sup>\</sup>alpha$  is typically used as in the literature.

delay dependency on voltage can be treated as linear. The concept of DVM is to limit the  $V_{dd}$  and frequency such that the application latency constraints are met, but the energy to perform the application function is minimized by following the square law dependency of Equation (1.2) instead of linearly tracking F. The chosen frequency F, representing the reciprocal of the worst-case path delay, is constrained by Equation (1.3) for a given supply voltage.

#### 1.2.2 Leakage Power

Leakage power sources are numerous [5], with the primary contributor historically being transistor off state drain to source leakage ( $I_{off}$ ). For modern processes having gate dielectric thicknesses under 3 nm, gate leakage  $I_{gate}$  is becoming a larger contributor but is generally smaller than  $I_{off}$ , particularly at high temperatures, given the stronger temperature dependency of 8–12×/100°C for  $I_{off}$  vs. approximately 2×/ 100°C for  $I_{gate}$ .  $I_{off}$  increases on scaled transistors because, to maintain performance,  $V_t$  must be lowered to compensate for decrease in  $V_{dd}$ . This increases the leakage according to

$$I_{off} \propto e^{-V_t/(S/\ln 10)} \tag{1.4}$$

where S is the subthreshold swing given by

$$S = \frac{kT(\ln 10)}{q} \left( 1 + \frac{C_D}{C_{OX}} \right)$$

(1.5)

where k is the Boltzmann constant, T is the temperature in Kelvin, q is the elementary charge,  $C_D$  is the depletion layer capacitance, and  $C_{OX}$  is the gate oxide capacitance. Noting that  $C_D$  is nonvanishing, the subthreshold swing parameter S is essentially a fixed parameter for Si MOSFETs, typically 80–100 mV/ decade depending upon the process at room temperature. Referring to Equation (1.4), it is obvious that lowering  $V_t$  affects the  $I_{off}$  exponentially.

For gate oxide thicknesses below 3 nm, quantum mechanical (direct band-to-band) tunneling current becomes significant. This leakage is extremely voltage dependent, increasing approximately with V<sup>3</sup> [6]. It also increases dramatically with decreasing thickness (e.g., increasing 10× for a change from 2.2 nm to 2.0 nm [7]). Gate-induced drain leakage (GIDL) at the gate-drain edge is important at low current levels and high applied voltages. It is most prevalent in the NMOS transistors where it is about two orders of magnitude greater than for PMOS devices. For a gate having a 0-V bias with the drain at V<sub>dd</sub>, significant band bending occurs in the drain region, allowing electron-hole pair creation. Essentially, the gate voltage attempts to invert the drain region, but because the holes are rapidly swept out, a deep depletion condition occurs [8]. The onset of this mechanism can be lessened by limiting the drain to gate voltage. It can be exacerbated by high source or drain to body voltages. Diode area leakage components from both the source-drain diodes and the well diodes are generally negligible with respect to I<sub>off</sub> and GIDL components. This is also improved by compensation implants intended to limit the junction capacitance. However, transistor scaling requires increasingly steep (often halo) doping profiles increasing band-to-band tunneling (BTBT) currents at the drain to channel edge, particularly as the drain to bulk bias is increased. This component may also limit use of RBB on sub-0.18-µm processes. Controlling these leakages will be key to effective use of body biasing and will require careful circuit design as well as appropriate transistor architecture.

#### **1.3 Process Selection and Rationale**

Thinner oxides are required to allow transistor length scaling while maintaining channel control. These scaled oxides require lower supply voltages to limit electric fields to a reliable value. Additionally, to maintain performance at lower voltage by retaining gate overdrive  $V_{dd} - V_t$  it is necessary to lower  $V_t$ . For

handheld battery powered devices,  $V_t$  must be chosen to balance standby power with active power dissipation for maximum battery life. Absent clever design to mitigate leakage, the duty cycle between standby and active operation for the given application determines the optimal threshold voltage [9]. This leads to considerable divergence in future processes and considerable power constraints to scaling processes used for portable devices [10]. One of the purposes of circuit techniques to limit active and standby power is to help widen the allowable  $V_t$  and process performance range. Handheld battery lifetime requires IC standby currents below 500  $\mu$ A requiring total leakage under 100 pA/ $\mu$ m of transistor width. This implies a  $V_t$  over 500 mV, independent of supply voltage, increasing active power at the same performance level.

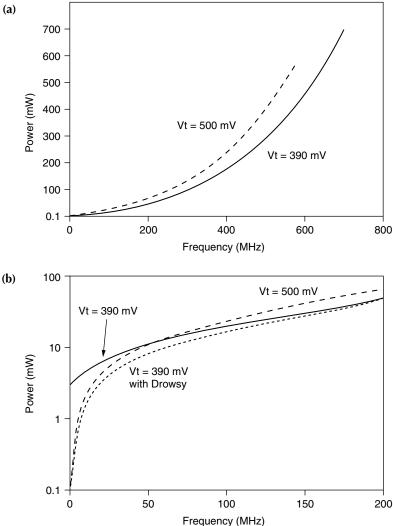

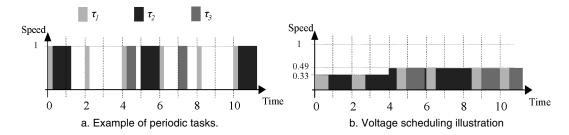

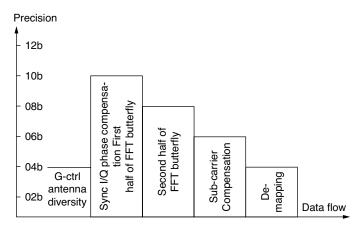

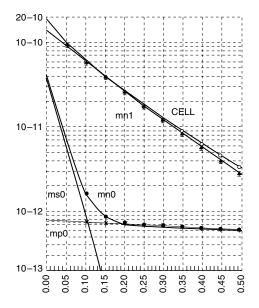

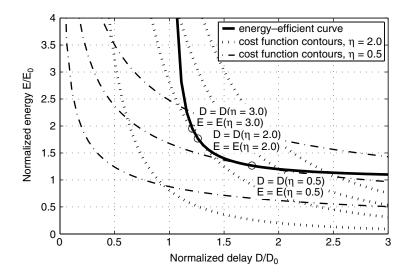

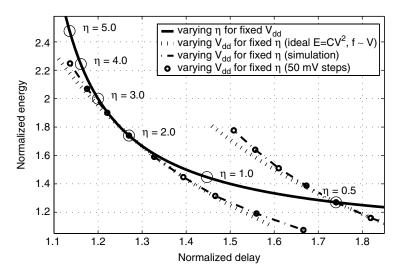

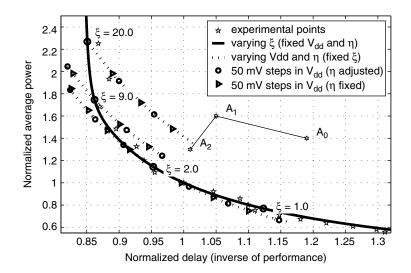

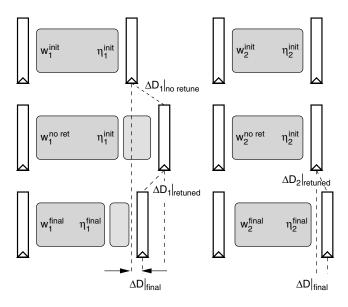

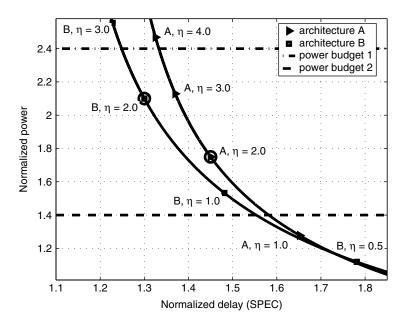

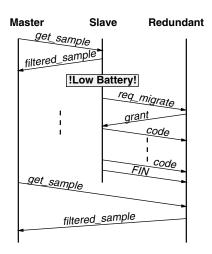

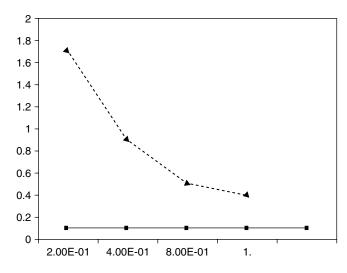

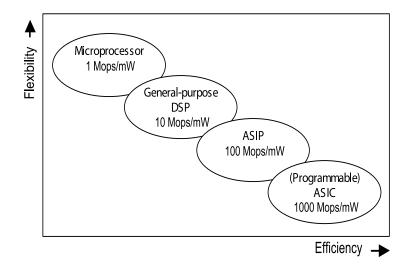

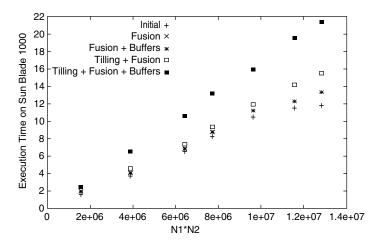

Figure 1.1 plots the simulated power vs. performance for a microprocessor operating at different frequencies on processes with different  $V_p$  assuming complete flexibility in the supply voltage or DVM (i.e., the voltage is chosen such that it is just sufficient to meet the processor frequency). The curves are based on the transistor performance metric described in Thompson [11] and normalized to the microprocessor performance with  $V_r$  of 390 mV (solid line in both plots) and 500 mV (dashed line in both plots). Figure 1.1(a) emphasizes the active power, which depicts the greater overall performance available from the lower  $V_t$  process. Note the improved power vs. the linear characteristic that would be obtained by scaling frequency alone. Figure 1.1(b) plots the log scale power for the low frequency ranges. At low frequencies, it is assumed that the power supply voltage cannot be scaled below a minimum value due to circuit functionality constraints. This value is 0.6 V for the 390-mV and 0.7 V for the 500-mV processes. Below the minimum operating voltage, the clock frequency is lowered resulting in a linear, instead of quadratic power savings. The break between square law and linear behavior is evident in the log scale plot of Figure 1.1(b). It is apparent that the lower  $V_t$  process has a higher leakage, as indicated by the zero frequency point, while it has a lower active power at the same frequency. It is also capable of higher overall performance. The lower active power is the result of reaching a given performance at a lower voltage, and its benefit was presented in Equation (1.2). The dotted line in Figure 1.1(b) demonstrates that with the addition of RBB Drowsy mode, the higher-performance process is power competitive at low effective frequencies with the slower process. The methods for achieving this comprise Section 1.4 and Section 1.5.

Nonstate-retentive sleep modes also incur power penalties. The present logical state must be saved before sleep and restored upon resuming active operation, requiring a low standby power storage medium. The data movement requires time and power that must be amortized by the leakage power savings achieved in the time in sleep. This can preclude frequent use. If the storage is off-chip, the higher IO voltages and off-chip capacitances increase the power penalty. A number of schemes, ranging from "greedy" to timeout based, have been proposed for determining when to enter a low-power state. The key considerations are achieving low energy cost to entry and exit, as well as low latency to awaken and respond to input.

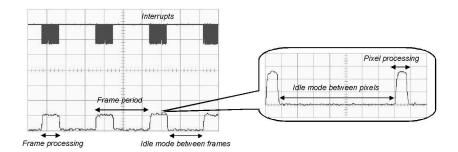

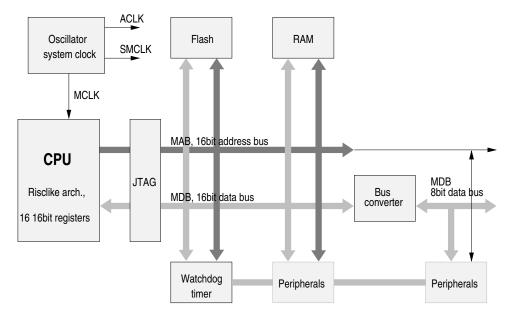

#### **1.3.1 Effective Frequency**

For compute intensive applications, the active power dominates as illustrated in Figure 1.1. The leakage power is of interest when the compute demands are modest, for instance when a processor is waiting for user input or in a cell phone, in the intervals between contacts with the cell. The former can be expected to be multiple times per second, and the latter less than once per second [12]. The total computed cycles per second is very low, although the frequency of the part might be higher as described next. Here, the term "effective frequency" is used to mean the number of cycles of computation accomplished over a given period. The actual frequency may vary during that time, according to whether the processor is running or is in a low-power Drowsy mode. Effective frequency is a measure of the average actual work performed by the processor. For example, assume that the processor receives interrupts at an average frequency determined by the application, for instance, from keystrokes on a keypad. Each interrupt awakens the processor where it computes for a number of cycles required to process the input (e.g., add it to the display buffer). The computational requirements might be quite different depending on the type of interrupt that is being serviced — it may be a command to sort mail messages. The effective frequency

**FIGURE 1.1** (a) The effect of  $V_t$  on power vs. frequency, and (b) the low frequency, leakage dominated power levels. In the upper plot, the low  $V_t$  with Drowsy is coincident with the non-Drowsy.

is then the total long-term average number of useful clocks per unit time (i.e., the number of instructions per interrupt times the number of interrupts). For example, with a 100-Hz interrupt rate and 100,000 instructions per interrupt, the processor will have an effective frequency of  $(100 \text{ Hz} \times 100(10)^3) = 10 \text{ MHz}$ , although the clock rate may be much higher (e.g., 300 MHz).

#### 1.4 Leakage Control via Reverse Body Bias

RBB has been suggested for leakage control for some time [13,14]. Essentially, this leverages the wellknown body effect, that raises the  $V_t$  of a transistor having a source voltage above the bulk, as commonly occurs in the upper transistors of an NMOS stack during switching. Although normally a designer's bane that reduces circuit speed, it can be used to advantage because

$$V_{t} = V_{FB} + \gamma_{\gamma} \langle \phi_{s} - V_{bs} - K_{2} (\phi_{s} - V_{bs}) - \eta V_{ds}$$

(1.6)

1-5

where  $\gamma$  is the body effect coefficient, which, along with  $K_2$  models nonuniform doping [15]. These coefficients represent the efficacy of a change in the source to body voltage in modulating  $I_{off}$ .  $\eta$  is the drain induced barrier lowering (DIBL) coefficient, which represents the ability to Control  $V_t$  by applying drain bias. Drain and body bias also affect the subthreshold slope.

RBB to modulate leakage has a number of advantages:

- 1. It is a circuit design approach.

- 2. It does not adversely affect the active performance.

- 3. It is state retentive.

The first point allows this approach to be utilized on any process. Longer channel lengths generally have a stronger body effect [16], under designer control at the resolution of the drawing grid. The second assumes that the implementation does not incur a significant IR drop or alternatively, it allows improved active power at the same standby current level vs. a device not so equipped. The final point is the advantage over "sleep" modes where the power supply is completely disconnected. With RBB, data is not lost when entering and exiting the low-power state — important in that it allows the power control to be transparent to the operating system and application software and saves significant energy. It is frequently difficult to predict *a priori* how long a device will be in a standby state, particularly when this depends upon user interaction. Retaining precisely the state of the IC before the entrance, as well as minimizing any power penalty to enter or exit the low-power mode makes the mode usable more frequently.

Body bias was used to limit leakage on a 1.8 V microprocessor implemented in a dual-well 0.25- $\mu$ m process described in Mizuno et al. [17]. This device used separate supplies for both the NMOS and PMOS bulk connections. A strong negative bias greater than 1 V was applied to the NMOS bulk via a charge pump and the PMOS bulks (N wells) were connected to the 3.3-V power supply rail during standby. Hundreds of local switches, distributed across the device, apply the body bias and provide a low impedance bulk connection, at the expense of routing the controls and supplies throughout the layout. This strong biasing is inappropriate for smaller geometry processes, where more abrupt doping and thinner oxides increase second order effects. This implementation of RBB increases GIDL, which can thus be the limiting leakage mechanism. Direct BTBT leakage in the source diodes of sub-130-nm halo doped transistors can be increased to also limit total standby current by reverse biasing the junctions. Consequently, to use RBB effectively on processes beyond 0.25  $\mu$ m, it will need to be comprehended in the transistor design and the RBB operation should use the lowest effective voltages.

#### 1.4.1 RBB on a 0.18-µM IC

The Intel 80200 microprocessor is an implementation of the XScale microarchitecture implemented in a 0.18- $\mu$ m process. Although sold commercially as a high-performance embedded device, it was also used as a development vehicle to develop Drowsy mode [18] circuitry and techniques. This mode utilizes RBB as well as V<sub>dd</sub> – V<sub>ss</sub> collapse to limit leakage power, achieved via large supply gating transistors that allow the source to be raised. They also allow full collapse of the core voltage, which produces the nonstateretentive "sleep" mode, essentially the classical multi-threshold CMOS (MTCMOS) approach to leakage control [19]. The manner in which RBB is applied, utilizing lower source to bulk voltages while collapsing the V<sub>dd</sub> – V<sub>ss</sub>, alleviates second order components. Drowsy mode retains state in all storage elements on the die and is exited on any interrupt. Sleep mode is not state-retentive, requiring a "cold-start." Consequently, asserting reset instead of an interrupt terminates it. The Drowsy implementation and results are described in detail in the following sections.

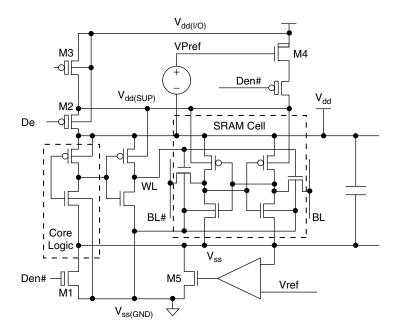

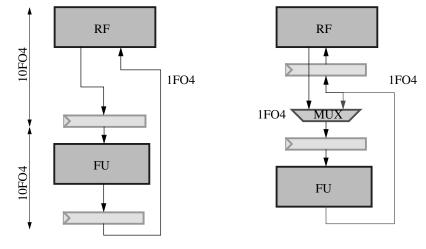

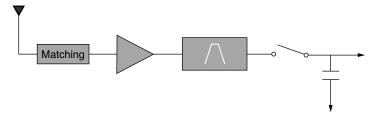

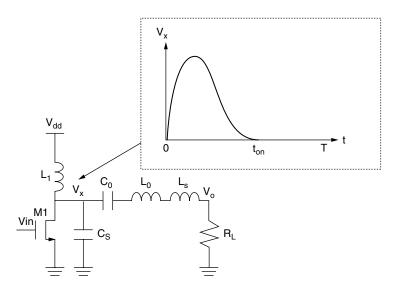

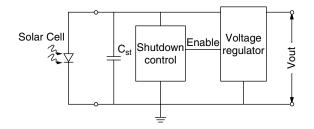

#### 1.4.2 Circuit Configuration

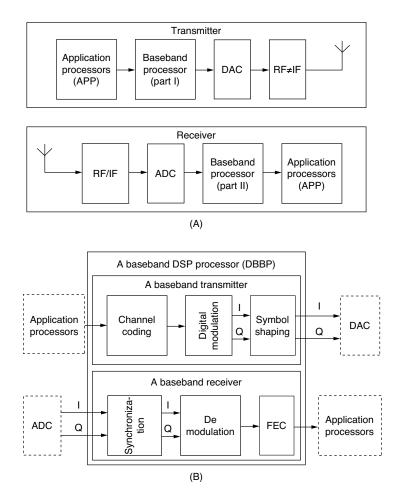

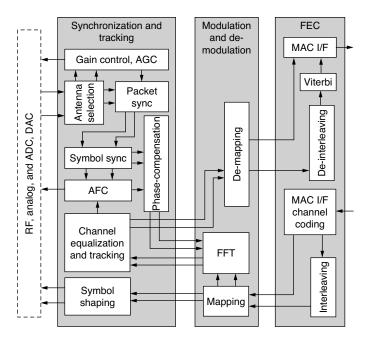

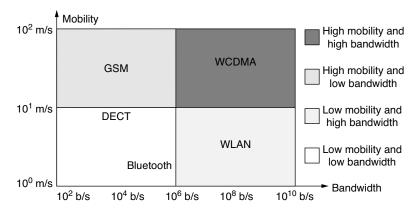

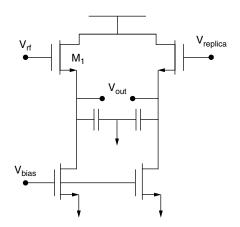

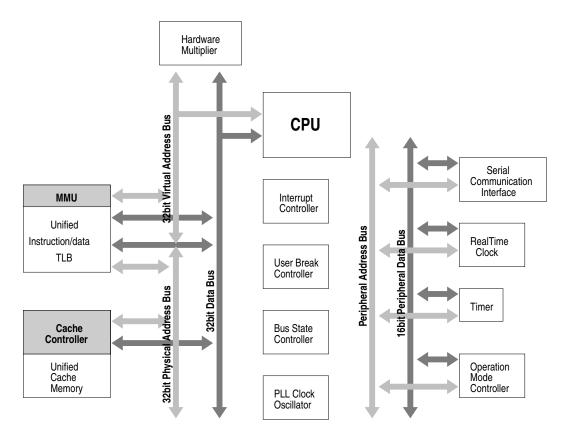

The circuit configuration is depicted in Figure 1.2. Power pads are on the  $V_{dd}$ ,  $V_{dd(IO)}$ , and  $V_{ss(GND)}$  pins. Large N channel devices M1 provide  $V_{ss}$  to the active circuitry during active operation. Simultaneously, large P channel devices M2 provide clamping of the N well ( $V_{dd(SUP)}$ ) providing the PMOS bulk connection

FIGURE 1.2 Circuit configuration for RBB Drowsy mode.

to  $V_{dd}$ . These transistors must be thick oxide because they are exposed to high voltages as indicated — here, the thick gate IO transistors are used. The PMOS clamping transistors carry no DC current and are 15 mm in total width. The NMOS clamp transistors carry the entire power supply current during operation and must do so with minimal IR drop. They are 85 mm in total width, which is less than 2% of the total transistor width of the microprocessor. This high ratio between the rest of the core is indicative of the low activity factor achieved by the design and relies on adequate on-die decoupling capacitance to provide instantaneous current demand. To this end, total of 55 nF of decoupling capacitance was interspersed among the active circuitry.

For sleep as well as Drowsy modes, the transistors comprising M1 are in cutoff. In the former cases, the core  $V_{ss}$  is allowed to float to  $V_{dd}$ , and power consumption is dominated by the leakage current through the NMOS clamp devices. The clamp devices should be high  $V_i$  to minimize this current because they do not have body bias applied. In Drowsy mode, to apply body bias to the NMOS devices,  $V_{ss}$  is allowed to rise toward  $V_{dd}$  but regulated to avoid losing state. Raising the NMOS source voltage instead of decreasing the NMOS body voltage is advantageous because it does not require a twin-tub or triple-well process, nor charge pump circuitry. It also lowers the  $I_{off}$  by the  $\eta$  coefficient of Equation (1.6) as well as limiting GIDL components because drain to bulk voltage is not increased. Because gate current is strongly affected by the drain to gate voltage, it is substantially reduced on processes with thin oxides. Another regulator provides a high voltage to the  $V_{dd(SUP)}$  node, to reverse body bias the PMOS transistors. In the static random access memory (SRAM), the word-lines are driven to  $V_{ss(GND)}$  as presented in Figure 1.2. This places a negative gate-to-source bias on the SRAM pass devices as presented, lowering the SRAM current a further 40%. This may not be desirable for thin oxides as it can increase the gate leakage component beyond the  $I_{off}$  savings.

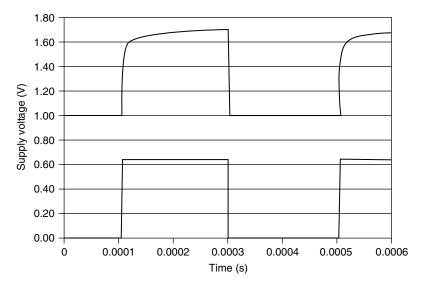

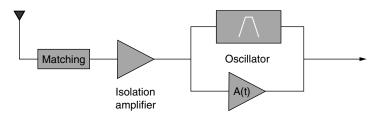

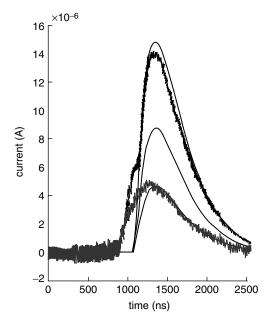

Simulated waveforms of the  $V_{ss}$  and  $V_{dd(SUP)}$  nodes are plotted in Figure 1.3, at 110°C. Minimal overshoot can be discerned in the figure. In Drowsy mode, the  $V_{ss}$  node rises to approximately 650 mV, with some PVT variation.  $V_{dd(SUP)}$  is driven to 750 mV above  $V_{dd}$ . At room temperature, the  $V_{ss}$  node takes approximately half an msec to rise because it is pulled toward  $V_{dd}$  solely by leakage. The advantage of this passive  $V_{ss}$  rise is that movement of this highly capacitive node is limited if Drowsy is exited soon after entrance, limiting the power cost of using this mode. No energy is explicitly expended to enter the mode because it achieved by transferring charge from the core nodes to the  $V_{ss}$  node, instead of supplying

FIGURE 1.3 Simulated V<sub>ss</sub> and V<sub>dd(SUP)</sub> waveforms at 110°C.

it from the IC power pins. This is not possible on the PMOS bulk node. This regulator circuit is designed with limited drive, as that node is less capacitive at 5 nF, and with low current demand, generally just the diode contributions of the N-well and PMOS source-and-drain diodes.

#### 1.4.3 Layout

Application of any body bias requires separate bulk and source supplies for both P and N transistors. This design opts for minimal intrusion due to the separate body connections. The power supply clamping transistors are provided in the pad ring only, occupying otherwise empty (or IO decoupling capacitor) space within the supply pins. Because the core was over 4000  $\mu$ m per side, circuits could be over 2000  $\mu$ m from the nearest clamp. Additionally, the bulk connections are routed sparsely through the logic circuitry, limiting the density impact. This is feasible because these provide no DC power, making resistance less important. A two-layer routing grid with 50  $\mu$ m between bulk supplies was utilized. The substrate is highly doped, providing an effective short circuit between V<sub>ss</sub> (ground) rails and limiting noise due to switching. N-wells are intentionally contiguous, forming a grid at the substrate level for V<sub>dd(SUP)</sub>.

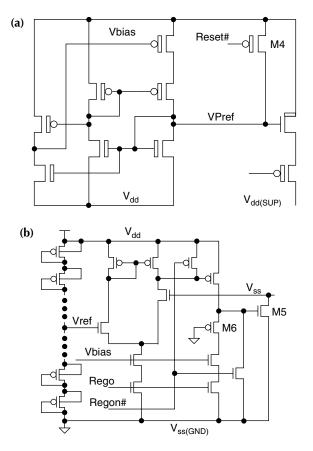

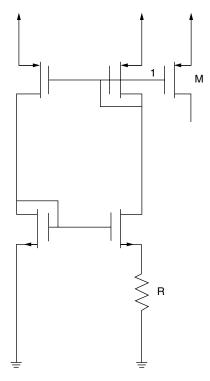

#### 1.4.4 Regulator Design

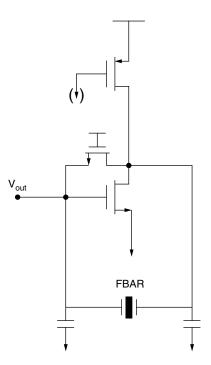

The  $V_{ss}$  regulator comprises Figure 1.4(a) and strictly limits the regulator overhead power. The output voltage must be essentially constant over 3 decades of current demand at all process, temperature, and voltage (P, V, T) corners (see Section 1.6). At the high end, when entering the low-power state directly from high frequency operation the die may be hot, where MOS drain to source leakage may be over 100× the RBB low temperature leakage and must be provided to avoid collapsing logic state. As expected, the amplifier compares the voltage on  $V_{ss}$  with a reference voltage. A PMOS stack simulating a resistor string, which allows it to vary with power supply variations, generates this reference. In this manner, higher supplies allow larger body bias — this flexibility was desirable for a test device. The resistor stack current is under 100 nA and is continuously biased in all modes. The regulator is a three-stage amplifier with an NMOS output transistor M5. Three stages were required due to the bias conditions and low current requirements to keep the regulator power consumption less than 5% of the total standby power at the typical process corner. The output transistor is sized to provide the full IC leakage current at high temperature and the worst-case process corner. The first stage is a differential operational transductance amplifier (OTA), while the second buffer stage provides increased voltage output range and current drive to the gate of M5. The first and second stages combined use less than 4  $\mu$ A at typical operating conditions.

**FIGURE 1.4**  $V_{ss}$  (a) and  $V_{dd(SUP)}$  (b) supply regulation circuits. All NMOS share substrate  $V_{ss(SUP)}$ , and all PMOS in (a) have  $V_{dd}$  and in (b)  $V_{dd(SUP)}$  body connections.

At such low current levels, gain is limited, which improves stability, as discussed next. Slew rate also suffers, which makes the step response poor. To address this, the buffer stage includes the diode connected transistor M6, which, combined with proper sizing keeps transistor M5 from completely cutting off, except in sleep mode. The enables are evident in the figure.

Stability must be ensured at all P, V, T conditions and overshoot on  $V_{ss}$  must be limited. Entering the body bias state, which is essentially a voltage step on  $V_{ss}$  represents the worst-case stability condition. Adequate phase margin ensures stability of the system comprised of the regulator and  $V_{ss}$  node on the IC. Overshoot on  $V_{ss}$ , even momentarily, can cause state loss. The circuit poles may be approximated by the dominant terms to simplify the analysis. The  $V_{ss}$  node is controlled to first order by the output conductance of transistor M5, while the amplifier pole is dominant. The former pole is at approximately 670 kHz calculated from the small signal parameters, while the latter is at 9 kHz. The low gain of the amplifier produces a low unity gain bandwidth and greater than 60 degrees of phase margin at the typical process. Essentially, the highly capacitive  $V_{ss}$  node low-pass characteristic does not require high amplifier speed for stability.

To back-bias the PMOS devices, two schemes may be used. At low IO voltages (e.g., 1.8V), the PMOS transistor bulk node may be directly connected to this voltage via M3. For higher IO voltages diminishing leakage reduction does not offset the greater charge switched in raising the well voltage. Therefore, in this case, this voltage is regulated. The open loop regulator is depicted in Figure 1.4(b), which derives a constant voltage from the IO supply  $V_{dd(IO)}$ . It is worth noting that as long as circuit configurations that accumulate the gates of the PMOS transistors are avoided, high voltages may be applied to the bulk without oxide stress or damage. The regulator is a bootstrapped voltage reference driving a wide NMOS vertical drain transistor in a source follower configuration as presented in Figure 1.4(b). This device (M4

in Figure 1.2) has a naturally low  $V_t$  and operates in subthreshold, providing a negligible voltage drop from the reference voltage to  $V_{dd(SUP)}$  in operation. The vertical drain configuration allows the thin gate oxide device to tolerate high drain to gate voltages as in Clark [21].

The relatively high active current of the phase-locked loop (PLL) necessitates disabling it in Drowsy mode. Leaving standby mode requires the PLL to restart and lock, triggered by an external interrupt. Because this takes approximately 20  $\mu$ s, the mode is usable often (e.g., between keystrokes). On the prototype, the lock time is set by a counter to enable deterministic testing. In actuality, the PLL lock time can be as low as 2  $\mu$ s depending on voltage. Faster interrupt latencies can be supported by providing the PLL reference clock directly to the IC, while the PLL locks. Consequently, PLL lock-time need not affect interrupt latency or limit the applicability of Drowsy usage.

#### **1.4.5** Limits of Operation

All memory, such as latches, need to be able to hold a "0" or a "1" with RBB applied. Although it is more difficult from a circuit aspect, holding state in all elements greatly simplifies logic design verification. As  $V_{dd}$  and  $V_{ss}$  collapse toward one another the transistors move from saturation into subthreshold, as the reverse body bias increases  $V_t$  and the increase in  $V_{ss}$  decreases  $V_{gs}$ . In subthreshold, these "on" transistors rapidly weaken with their current following the subthreshold slope. In a memory element, the voltage level of a node is maintained by an "on" transistor being able to supply enough current to overcome the leakage of all the attached "off" transistors. In normal, high  $V_{ds}$  operation, this is not a problem due to the large  $I_{on}$  to  $I_{off}$  ratio. As transistors reach subthreshold, the on current drops rapidly with  $V_{ds}$  (=  $V_{gs}$ ) due to

$$I_{ds,sat} = \frac{\mu C_{ox} Z}{2L} \left( V_{gs} - V_t \right)^{\alpha}$$

(1.7)

becoming Equation (1.4) as the gate overdrive  $(V_{gs}-V_t)$  is reduced below 0. Ideally,  $V_{dd}-V_{ss}$  can be lowered to drive all of the transistors into subthreshold operation because the  $I_{on}/I_{off}$  ratio will scale for all transistors. Assuming an 80-mV/decade transistor subthreshold characteristic, over three decades of current difference between on and off transistors will be maintained with 250 mV of  $V_{ds}$ . Lowering the voltage too far on future ultra-small devices will reach thermodynamic constraints [22]. The relative size and strength of the N and P transistors, including local channel length and  $V_t$  variation must be considered. In practice, state loss depends upon many factors such as the type of latch, the transistor ratios, the logic state being held, the local transistor  $V_t$  and the temperature. Domino circuits, with the largest N to P (keeper) width ratios, are the first to fail.

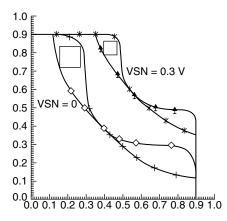

The fail point as a function of the PMOS body voltage and NMOS body voltage as measured on silicon is presented in Figure 1.5. Because in this design the  $V_{ss}$  is referenced to the  $V_{ss(GND)}$  supply node,  $V_{ss}$  is the applied NMOS body bias. Points lower on the vertical axis have higher NMOS  $V_t$  and further right have higher PMOS  $V_t$ . Measured parts retained state below the curve (Pass) and lost state above it after application of that level of reverse body bias (Fail). As  $V_{ss}$  is increased, the NMOS transistors have increasing reverse body bias applied to them, so "on" devices are in subthreshold. The right side of the curve represents a memory element failing as logic "0" is flipped to a "1." As  $V_{dd(sup)}$  increases the PMOS transistors leakage is reduced, so that the amount of reverse body bias that can be applied to the NMOS transistors can be increased, continuing until a maximum value of  $V_{dd(SUP)}$  and  $V_{ss}$  is reached. The left part of the curve represents the onverse case where the PMOS transistors are weakened with respect to the NMOS. With a large  $V_{dd(SUP)}$  applied "on" devices are in subthreshold and are eventually unable to supply enough current to overcome leakage from NMOS transistors. This left part of the curve represents a memory element holding a "1" flipping to a "0." The flat zone depicts the saturation of any body effect as voltage increases.

#### 1.4.6 Measured Results

When the leakage current from the microprocessor is low the voltage on  $V_{ss}$  will not rise to the reference voltage because the regulator does not actively drive its output. At  $V_{dd}$  of 1.05 V, the regulator clamps at

FIGURE 1.5 Shmoo plot of state retention with PMOS and NMOS body bias as parameters.

FIGURE 1.6 Standby current of the microprocessor with and without body bias.

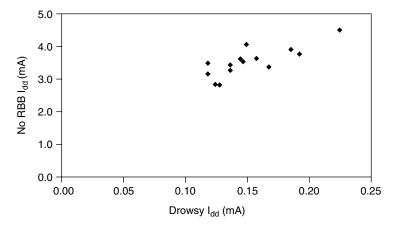

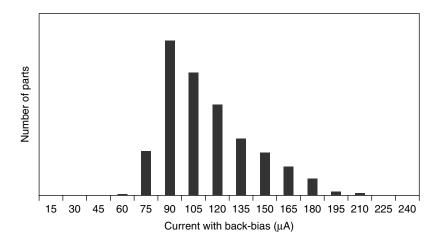

the reference voltage, about 0.73 V for high leakage. The leakage current is reduced by a factor of over 25 across most devices when the body bias is applied. Figure 1.6 plots the no body-bias (NBB) standby vs. the RBB Drowsy mode current. Figure 1.7 gives the distribution of the current with reverse body bias for all die on one wafer. A wide variation, due to variations in the process (e.g., threshold voltage and channel length) as well as the regulator output, is evident.

#### **1.5** System Level Performance

This section describes experiments using Drowsy mode to simulate low leakage by running an IC in short bursts of operation interspersed with time in the leakage control mode, time domain multiplexing (TDM) Drowsy mode [23]. The IC power is dominated by different components in different operating modes described in Section 1.1. First, the active power component dominates during intervals of operation. Second, there are the two primary leakage components, the active component, potentially multiplied by die heating, but still small compared with the active power, and leakage during Drowsy mode. Third, the PLL and clock-generation power, as well as that of the interrupt circuitry required to wake up the device from Drowsy mode. The former provide an active power component that runs during active operation and for 20 µs before each active interval. There is a small non-RBB leakage component

FIGURE 1.7 Standby current of the microprocessor with body bias.

during PLL startup, but the time is small enough to make this component negligible. Finally, the power cost of each power supply movement represents the "penalty" power of entering and exiting Drowsy mode. This low frequency high capacitance switching power is mitigated by the low-voltage swing utilized. The energy to transition the clamp transistors and their driver circuitry is small enough to be considered negligible because the total gate capacitance of the clamp transistors is 119 pF. Entry into the standby mode consumes no power on the  $V_{ss}$  node due to its being driven high by passive leakage of the core (i.e., redistribution of charge from the nodes within the core logic to  $V_{ss}$ ). Power dissipation is incurred only when leaving the mode. The total energy cost of a single entry into the low-power mode is calculated to be 30.6 nJ from measurements.

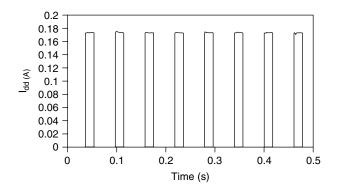

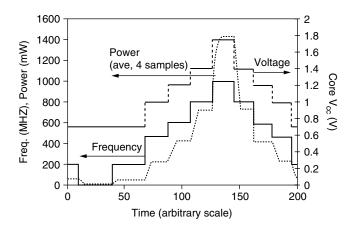

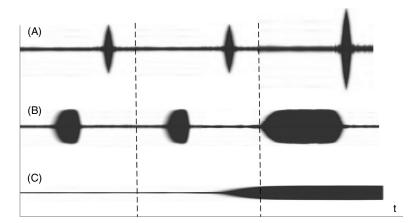

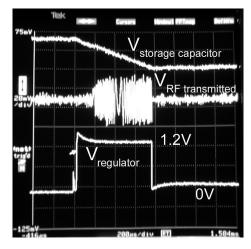

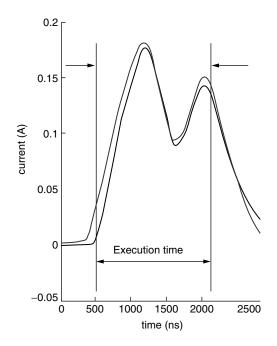

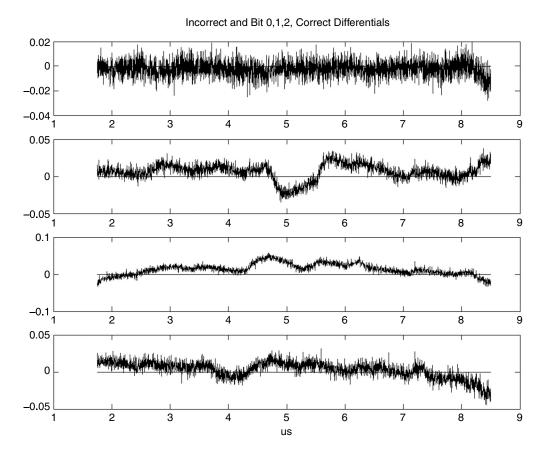

The experiments were performed on a microprocessor board [24] at 1 V  $V_{dd}$  running IO at 100 MHz and with a core frequency of 300 MHz. Separate core and analog PLL supplies connected to external power supply and ammeter connections allowed these currents to be distinguished. The Drowsy circuitry allows high performance — the device under test was run on the board to 800 MHz at 1.55 V. Instantaneous current demand was measured, while the interrupt signal was asserted at the chosen interrupt frequency. Each interrupt runs code comprised of a simple loop, intended to be representative of the power that would be consumed by the typical instructions, which are generally quite similar [25]. The number of instructions to run at each interrupt is set by a loop count parameter. At the end of the loop, the IC returns to Drowsy mode. Subsequent interrupts wake the microprocessor and begin the loop anew. Due to branch prediction, the processor executes one instruction per clock in the loop (i.e., there are no stall cycles). State retention while Drowsy maintains the cached instructions, so there are no misses after the first compulsory ones. The operating voltage was adjusted based on the reading from a locally connected voltmeter in order to account for IR loss in the power supply leads. Figure 1.8 is a representative power measurement.

#### 1.5.1 System Measurement Results

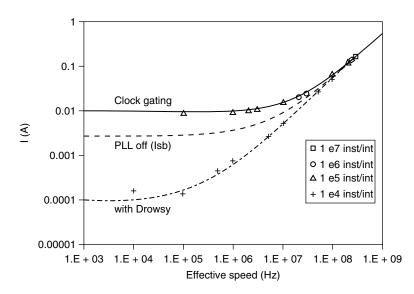

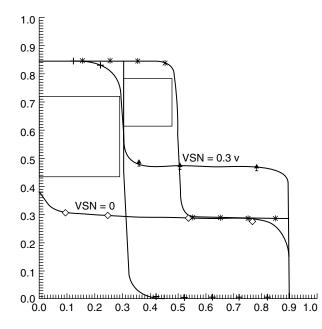

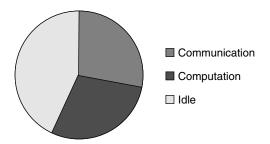

Drowsy power was measured to be 0.1 mA at 1 V on the IC used in these measurements. In a DC condition, the  $I_{sb}$  at room temperature (i.e., the standby core supply current with no clock running) was 2.8 mA at 1 V. The PLL consumes 6.6 mW at the same voltage. The processor was run at a number of interrupt frequencies and instruction per interrupt rates with the results plotted in Figure 1.9. As expected, the power shows a linear dependency on the effective frequency at high rates, where the active power dominates, while at low rates a floor due to leakage components is evident. The energy per instruction is calculated to be 0.5 nJ. All interrupt and instruction rates fall on the same curve as presented in the figure. Measurements made in "idle" mode, in which the PLL is kept active, no RBB is applied, but clocks that are gated at the PLL generate a relatively high power floor due to PLL power.

FIGURE 1.8 Current measurement with the time in standby and active modes evident.

FIGURE 1.9 Current measurement depicting active and leakage power dominated frequencies.

The power savings of using Drowsy mode over clock gating alone is approximately 100×. This is over 25× less than the I<sub>sb</sub> leakage power floor that would be obtained without Drowsy (e.g., by simply lowering the clock to a very low rate). Power is saved and the response time to external stimulus is improved by running in short bursts at high frequencies. Effective frequency allows direct comparison with devices running at lower frequency demonstrating that the efficacy of TDM Drowsy mode, matching the theoretical curve of Figure 1.1. By raising the  $V_t$  with RBB to achieve low standby power, it is combined with improved low voltage and higher maximum performance. The active power improvement can be estimated by considering the  $V_t$  increase required to match the I<sub>off</sub> reduction and the required V<sub>dd</sub> increase to achieve the same performance. By simulating the circuit metric mentioned previously, calibrated to the measured frequency vs. voltage performance of the microprocessor, a  $V_t$  increase of 110 mV (to a typical value of 500 mV) results in the same reduction. At this  $V_p$ , the same frequency at  $V_{dd} = 0.75$  V is obtained by an increase to 0.86 V demonstrating an active power savings of 24% by using Drowsy mode instead of a higher  $V_t$ .

#### 1.6 Process, Voltage, and Temperature Variations

Systematic and random variations in P, V, and T are posing a major challenge to future high-performance microprocessor design [26,27]. Technology scaling beyond 90 nm is causing higher levels of device

parameter variations, which are changing the design problem from deterministic to probabilistic [28,29]. The demand for low power and thinner gate oxides causes supply voltage scaling. Then, voltage variations become a significant part of the overall challenge. Finally, the quest for growth in operating frequency is manifested in significantly high junction temperature and within die temperature variation.

#### 1.6.1 Process Variation

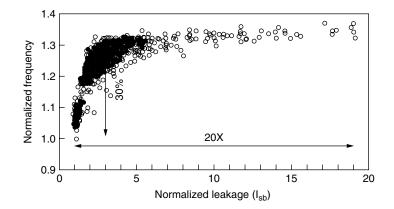

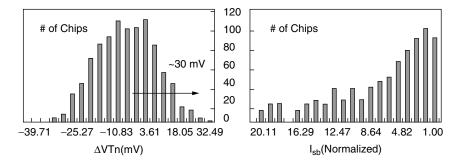

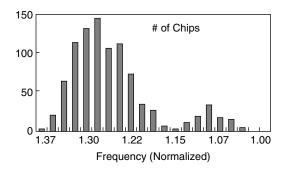

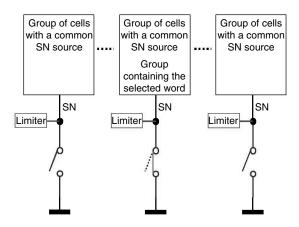

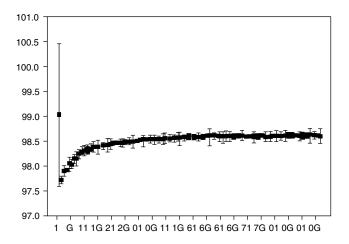

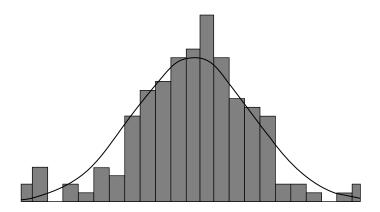

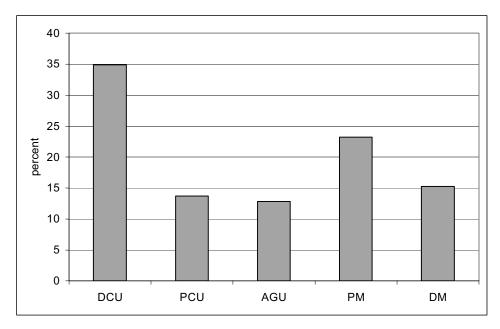

Distributions of frequency and standby leakage current (I<sub>sb</sub>) of microprocessors on a wafer are presented in Figure 1.10. The spread in frequency and leakage distributions is due to variation in transistor parameters, causing about 20× maximum variation in chip leakage and 30% maximum spread in chip frequency. This variation in frequency has led to the concept of "frequency binning" to maximize revenue from each wafer. Note that the highest frequency chips have a wide distribution of leakage, and for a given leakage, there is a wide distribution in the frequency of the chips. The highest-frequency chips with large  $I_{sb}$ , and low-frequency chips with too high  $I_{sb}$  may have to be discarded, thus affecting yield. Limits to maximum acceptable Ish are dictated by total active power as affordable by cost-effective cooling and current delivery capabilities, as well as idle power required to achieve a target battery life in portable applications. The spreads in standby current and frequency are due to variations in channel length and threshold voltage, both within die and from die to die. That leakages are affected exponentially, while delay is affected approximately linearly is evident in their relative magnitudes. Figure 1.11 illustrates the die-to-die V<sub>t</sub> distribution and its resulting chip  $I_{sb}$  variation. V<sub>t</sub> variation is normally distributed and its 3- $\sigma$  variation is about 30 mV in an 180-nm CMOS logic technology. This variation causes significant spreads in circuit performance and leakage. The most critical paths in a chip may be different from chip to chip. Figure 1.11 also presents the 20× Isb variation distribution in detail.

FIGURE 1.10 Leakage and frequency variations.

**FIGURE 1.11** Die-to-die  $V_{t}$ ,  $I_{sb}$  variation.

FIGURE 1.12 Supply voltage variation.

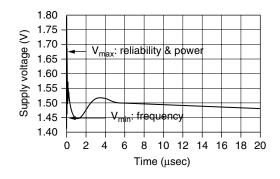

#### 1.6.2 Supply Voltage Variation

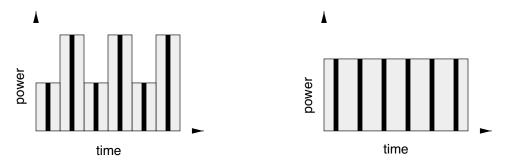

Uneven and variable switching activity across the die and diversity of the type of logic, result in uneven power dissipation across the die. This variation results in uneven supply voltage distribution and temperature hot spots, across a die, causing transistor subthreshold leakage variation across the die. Supply voltage ( $V_{dd}$ ) will continue to scale modestly by 15%, not by the historic 30% per generation, first, due to difficulties in scaling threshold voltage and second, to meet the transistor performance goals. Maximum  $V_{dd}$  is specified as a reliability limit for a process, and minimum  $V_{dd}$  is required for the target performance.  $V_{dd}$  variation inside the max–min window is plotted in Figure 1.12. This figure depicts a droop in  $V_{dd}$ , when IC current demand changes rapidly, which degrades the performance. This is the result of platform, package, and IC inductances and resistances that do not follow the scaling trends of CMOS process. Specifically, the time "0" point is relatively inactive, while a rapid change in power demand, by the processor leads to the large supply droop pictured. This problem is increased by good low-power design (e.g., clock gating). Power delivery impedance does not scale with  $V_{dd}$  and  $\Delta V_{dd}$  has become a significant percentage of  $V_{dd}$ .

#### 1.6.3 Temperature Variation

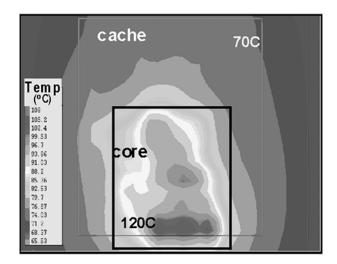

Figure 1.13 illustrates the thermal image of a leading microprocessor die with hot spots as high as 120°C. Within die temperature fluctuations have existed as a major performance and packaging challenge for

FIGURE 1.13 Within die temperature variation.

FIGURE 1.14 Die-to-die frequency variation.

many years. Both the device and interconnect performance have temperature dependence, with higher temperature causing performance degradation. Additionally, temperature variation across communicating blocks on the same chip may cause performance mismatches, which may lead to logic or functional failures. Because these thermal variations are the result of uneven local heating, they can be ignored in standby, where lower power dissipation creates minimal heating. Additionally, it can be assumed that the die temperature equals that of the ambient, typically room temperature.

#### 1.7 Variation Impact on Circuits and Microarchitecture

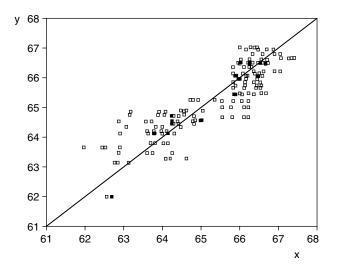

A primary consequence of the P, V, T variation manifests itself as maximum operating frequency ( $F_{max}$ ) variation. Figure 1.14 presents the distribution of microprocessor dies in 180-nm technology across a frequency range. The data is taken at a fixed voltage and temperature, and thus this  $F_{max}$  variation is caused by the process variations discussed previously. This frequency distribution has serious cost implications associated with it — low performing parts need to be discarded, which in turn affects the yield and hence the cost. The P, V, T variations consequently impact all levels of design. For instance, products that have only one operating frequency of interest (e.g., networking devices that either do or do not meet a specific standard) must be designed conservatively. Frequently this means designing all circuits to the worst-case P, V, T corner. This section highlights some of the impact that process has on circuit and microarchitecture design choices.

#### 1.7.1 Design Choice Impact

Dual-V<sub>t</sub> circuit designs [30,31] can reduce leakage power during active operation, burn-in, and standby. Two V<sub>t</sub> are provided by the process technology for each transistor. High-V<sub>t</sub> transistors in performance critical paths are either upsized or are made low-V<sub>t</sub> to provide the target chip performance. Because upsizing has limited benefit in gate-dominated paths, as capacitive load is added at the same rate as current drive, lower V<sub>t</sub> can be beneficial. Larger transistor sizes increase the relative probability of achieving the target frequency at the expense of switching power. Increasing low-V<sub>t</sub> usage also boosts the probability of achieving the desired frequency, but with a penalty in leakage power. It was demonstrated in Karnik et al. and Tschanz et al. [30,31], that by carefully employing low-V<sub>t</sub> devices, 24% delay improvement is possible to trade off leakage and switching power components, while maintaining the same total power. However, a design optimized for lowest power by careful assignment of transistor sizes and V<sub>t</sub> values is more susceptible to frequency impact due to within-die variations because they sharpen the path delay distributions making a larger number of paths and transistors critical.

#### 1.7.2 Microarchitecture Choice Impact

The number of critical paths that determine the target frequency vary depending on both microarchitecture and circuit design choices. Microarchitecture designs that demand increased parallelism and/or

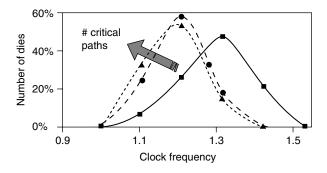

FIGURE 1.15 Die-to-die critical path distribution.

functionality require increase in the number of critical paths. Designs that require deeper pipelining, to support higher frequency of operation, require increase in the number of critical paths and decrease in the logic depth. The impact process variation has on these choices are described next. Test chip measurements in Figure 1.15 demonstrate that as the number of critical paths on a die increases, within-die delay variations among critical paths cause both mean ( $\mu$ ) and standard deviation ( $\sigma$ ) of the die frequency distribution to become smaller. This is consistent with statistical simulation results [26] indicating that the impact of within-die parameter variations on die frequency distribution is significant. As the number of critical paths exceeds 14, there is no noticeable change in the frequency distribution. So, microarchitecture designs that increase the number of critical paths will result in reduced mean frequency because the probability that at least one of the paths is slower will increase.

Historically, the logic depth of microarchitecture critical paths has been decreasing to accommodate a 2× growth in the operating frequency every generation, faster than the 42% supported by technology scaling. As the number of logic gates per pipeline stage that determine the frequency of operation reduces, the impact of variation in device parameter increases. Measurement on 49-stage ring oscillators demonstrated that  $\sigma$  of the within-die frequency distribution was 4× smaller than  $\sigma$  of the device saturation current distribution [26]; however, measurements on a test chip containing 16-stage critical paths demonstrate that  $\sigma$  of within die (WID) critical path delay distributions and NMOS/PMOS drive current distributions are comparable. Specifically, NMOS I<sub>dsat</sub>  $\sigma/\mu = 5.6\%$ , PMOS I<sub>dsat</sub>  $\sigma/\mu = 3.0\%$ , while the 16stage delay  $\sigma/\mu = 4.2\%$ . The impact of process variation on the microarchitecture design choices can be summarized as follows: with either smaller logic depth or with increasing number of microarchitecture critical paths, performance improvement is possible. The probability of achieving the target frequency that translates to performance, however, drops due to the impact of within-die process variation.

#### 1.8 Adaptive Techniques and Variation Tolerance

This section describes some of the research and design work to enhance the variation tolerance of circuits and microarchitecture and to reduce the variations by clever circuit and microarchitectural techniques. These techniques expand on those discussed previously by expanding the use of body bias from only RBB to include forward body bias (FBB) to reduce  $V_t$  and thereby improve circuit speed. Adjusting the voltage to the optimal required as determined at test time is introduced as another method to increase yield in the presence of variation.

#### **1.8.1 Body Bias Control Techniques**

Lowering  $V_t$  can improve device performance, with the commensurate increase in leakage and standby current ( $I_{sb}$ ) as described earlier. One possible method to trade off performance with leakage power is to apply a separate bias to critical devices. In addition to application of RBB to reduce leakage,  $V_t$  can be modulated for higher performance by forward body bias (FBB). This method also reduces the impact

FIGURE 1.16 Optimal FBB for sub-90-nm generations.

FIGURE 1.17 Forward body bias results.

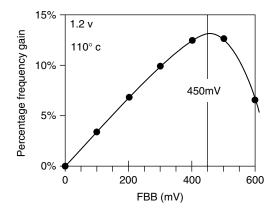

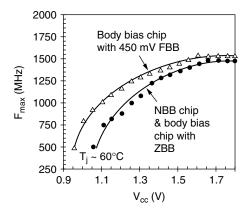

of short channel effects, hence reducing  $V_t$  variations. Figure 1.16 plots the percentage frequency gain as a function of FBB. It was demonstrated empirically that 450 mV is the optimal FBB for sub-90-nm generations at high temperature [32]. A 6.6-M transistor communications router chip [33], with on-chip circuitry to provide FBB to PMOS transistors during active operation and zero body bias (ZBB) during standby mode, was implemented in a 150-nm CMOS technology. Performance of the chip is compared with the original design that has no body bias (NBB) in Figure 1.16. The maximum operating frequency ( $F_{max}$ ) of the NBB and FBB router chips are compared from 0.9 V to 1.8 V V<sub>dd</sub> at 60°C (see Figure 1.17). The FBB chip with forward body bias achieves 1GHz operation at 1.1 V, compared with 1.25 V required for the NBB chip, or 23% less switching power at 1 GHz. The frequency of FBB is 33% higher than NBB at 1.1 V. Area overhead supporting ABB was approximately 2%, while the power overhead was 1%.

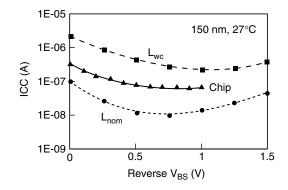

RBB was also applied to the same device to reduce leakage. Figure 1.18 plots the leakage current for the worst-case channel length ( $L_{wc}$  dashed) and the nominal channel length ( $L_{nom}$  dotted) as a function of RBB. The measured full-chip leakage current is within these upper and lower leakage current bounds over a range of RBB values. The optimum RBB value derived from the measured chip for minimum leakage is 500 mV [34]. Higher RBB values cause the junction leakage current to increase and overall leakage power to go up because, as in Mizuno et al. [17], the V<sub>dd</sub> was not collapsed; however, effectiveness of RBB reduces as channel lengths become smaller or  $V_t$  is lowered. Essentially, the  $V_t$ -modulation capability by RBB weakens as short-channel effects become worse or body effect diminishes due to lower channel doping.

FIGURE 1.18 Leakage reduction by reverse body bias.

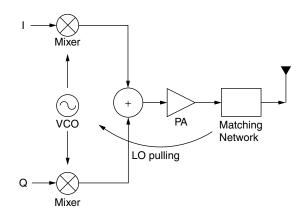

#### 1.8.2 Adaptive Body Bias and Supply Bias

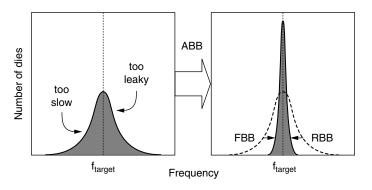

The previous two subsections presented the advantages of both FBB and RBB. It is possible to utilize both of these approaches as depicted in Figure 1.19. Due to the frequency spread in fabricated parts caused by process variations, the low frequency parts may be discarded for lower performance and the high frequency parts may be discarded for higher leakage power. As presented on the right side, devices can be adaptively biased to increase the performance of the slow parts by FBB and to decrease leakage power of the fast parts by RBB.

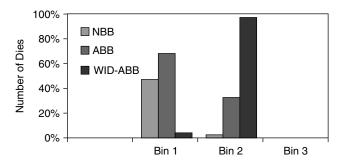

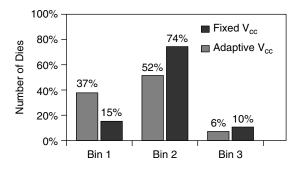

A test chip was implemented in a 150-nm CMOS technology to evaluate effectiveness of the adaptive body bias (ABB) technique for minimizing impacts of both die-to-die and within-die parameter variations on processor frequency and active leakage power [35]. The bias is based on a 5-bit digital code, which provides one of 32 different body bias values with 32 mV resolution to PMOS transistors. NMOS body is biased externally across the chip. Bidirectional ABB is used for both NMOS and PMOS devices to increase the percentage of dies that meet both frequency requirement and leakage constraint. As a result, die-to-die frequency variations ( $\sigma/\mu$ ) reduce by an order of magnitude, and 100% of the dies become acceptable (see Figure 1.20). Bin 2 is the highest frequency bin, while Bin 1 is the lowest acceptable frequency bin — any dies that are slower than Bin 1 are discarded. Almost 50% of dies with NBB fell below Bin 1 but are recovered using ABB. In addition, 30% of the dies are now in the highest frequency bin allowed by the power density limit. WID-ABB (applying multiple bias values per die to compensate for within-die as well as die-to-die variation) reduces  $\sigma$  of the die frequency distribution by 50%, compared with ABB. In addition, almost all the dies are accepted in the highest possible frequency bin, compared with 30% for ABB. Another technique to increase yield in the high frequency bins, is to apply adaptive V<sub>dd</sub>. Figure 1.21 presents the advantage of adaptive V<sub>dd</sub> over fixed V<sub>dd</sub>. Bin 3 is the highest

FIGURE 1.19 Target frequency binning by adaptive body bias.

FIGURE 1.20 Adaptive body bias results.

FIGURE 1.21 Bin improvement by adaptive V<sub>cc</sub>.

frequency bin, while Bin 1 is the lowest acceptable frequency bin. The dark bars indicate that adaptive  $V_{dd}$  ( $V_{cc}$  in the figure) has pushed more than 20% dies from Bin 1 to Bin 2 and even Bin 3, as well as recovered those dies that fell below Bin 1.

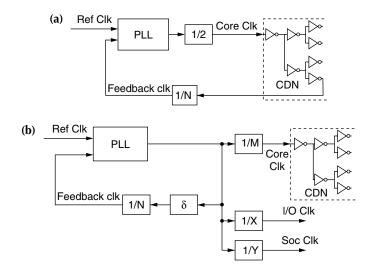

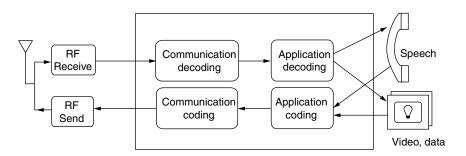

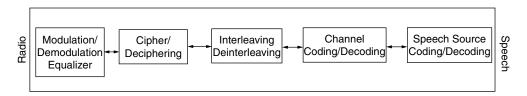

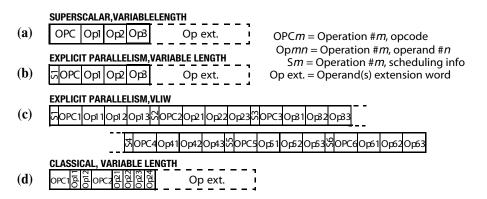

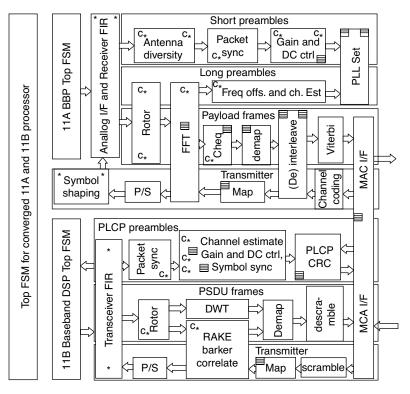

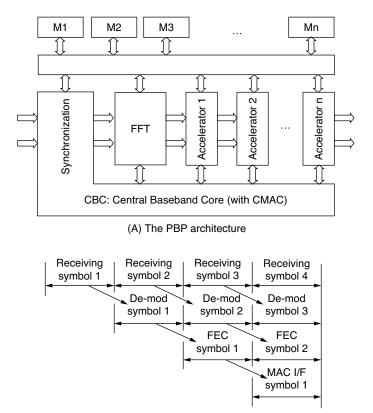

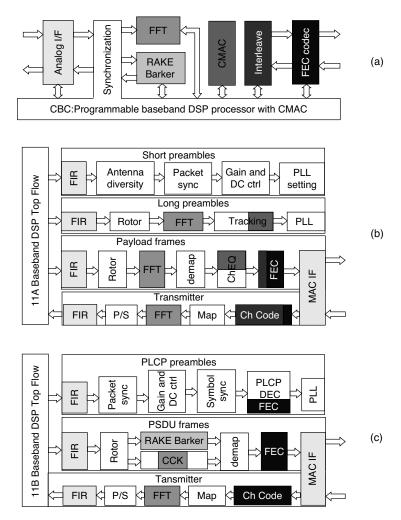

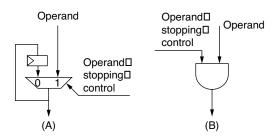

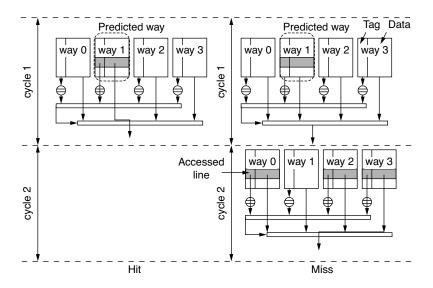

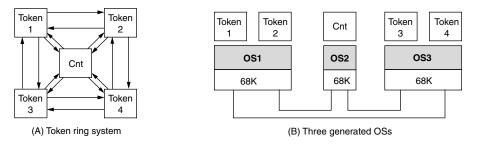

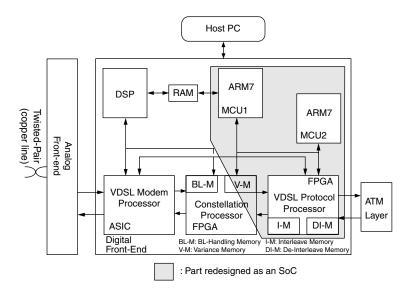

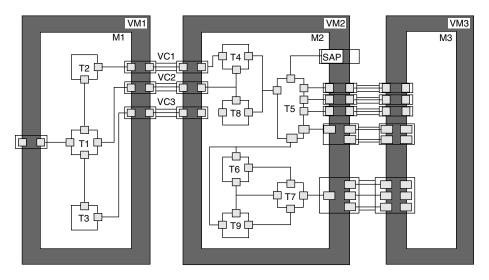

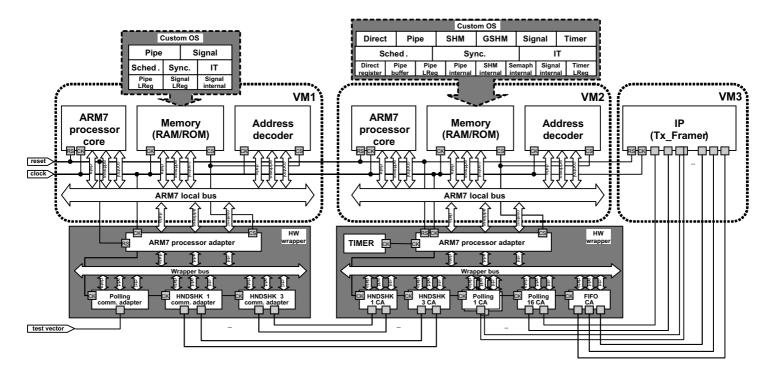

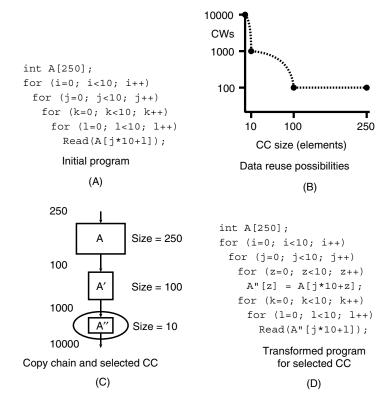

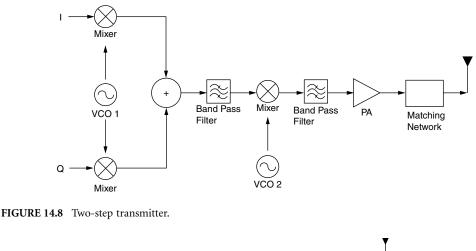

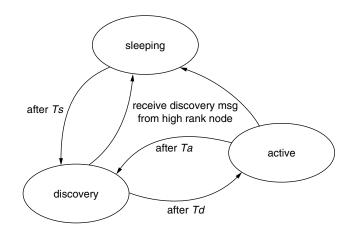

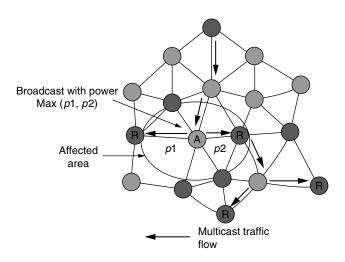

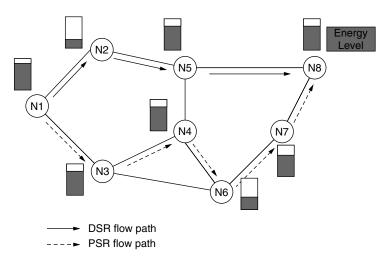

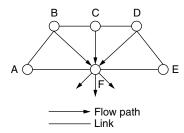

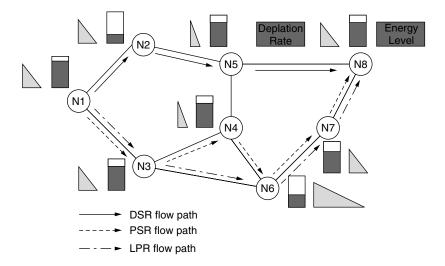

#### 1.9 Dynamic Voltage Scaling