Manoj Sachdev José Pineda de Gyvez

DEFECT-ORIENTED TESTING FOR NANO-METRIC CMOS VLSI CIRCUITS  $2^{\mbox{\scriptsize nd}}\mbox{ Edition}$

### FRONTIERS IN ELECTRONIC TESTING

### Consulting Editor

#### Vishwani D. Agrawal

#### Books in the series:

### Digital Timing Measurements - From Scopes and Probes to Timing and Jitter

Maichen, W., Vol. 33

ISBN 0-387-32418-0

#### Fault-Tolerance Techniques for SRAM-based FPGAs

Kastensmidt, F.L., Carro, L. (et al.), Vol. 32

ISBN 0-387-31068-1

#### **Data Mining and Diagnosing IC Fails**

Huisman, L.M., Vol. 31 ISBN 0-387-24993-1

## **Fault Diagnosis of Analog Integrated Circuits**

Kabisatpathy, P., Barua, A. (et al.), Vol. 30

ISBN 0-387-25742-X

#### Introduction to Advanced System-on-Chip Test Design and Optimi...

Larsson, E., Vol. 29

ISBN: 1-4020-3207-2

### **Embedded Processor-Based Self-Test**

Gizopoulos, D. (et al.), Vol. 28 ISBN: 1-4020-2785-0

## Advances in Electronic Testing

Gizopoulos, D. (et al.), Vol. 27

ISBN: 0-387-29408-2

#### **Testing Static Random Access Memories**

Hamdioui, S., Vol. 26

ISBN: 1-4020-7752-1

# Verification by Error Modeling

Redecka, K. and Zilic, Vol. 25

ISBN: 1-4020-7652-5

#### Elements of STIL: Principles and Applications of IEEE Std. 1450

Maston, G., Taylor, T. (et al.), Vol. 24

ISBN: 1-4020-7637-1

#### Fault injection Techniques and Tools for Embedded systems Reliability...

Benso, A., Prinetto, P. (Eds.), Vol. 23

ISBN: 1-4020-7589-8

#### Power-Constrained Testing of VLSI Circuits

Nicolici, N., Al-Hashimi, B.M., Vol. 22B

ISBN: 1-4020-7235-X

#### **High Performance Memory Memory Testing**

Adams, R. Dean, Vol. 22A

ISBN: 1-4020-7255-4

### SOC (System-on-a-Chip) Testing for Plug and Play Test Automation

Chakrabarty, K. (Ed.), Vol. 21

ISBN: 1-4020-7205-8

## Test Resource Partitioning for System-on-a-Chip

Chakrabarty, K., Iyengar & Chandra (et al.), Vol. 20

ISBN: 1-4020-7119-1

#### A Designers' Guide to Built-in Self-Test

Stroud, C., Vol. 19

ISBN: 1-4020-7050-0

#### **Boundary-Scan Interconnect Diagnosis**

de Sousa, J., Cheung, P.Y.K., Vol. 18

ISBN: 0-7923-7314-6

# DEFECT-ORIENTED TESTING FOR NANO-METRIC CMOS VLSI CIRCUITS

# 2<sup>nd</sup> Edition

by

Manoj Sachdev University of Waterloo Ontario, Canada

and

José Pineda de Gyvez Philips Research Laboratories, and Eindhoven University of Technology Eindhoven, The Netherlands

| A C.I.P. Catalogue record for this book is available from the Library of Congress.                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ISBN-10 0-387-46546-4 (HB)<br>ISBN-13 978-0-387-46546-3 (HB)<br>ISBN-10 0-387-46547-2 (e-book)<br>ISBN-13 978-0-387-46547-0 (e-book)                                                                                                                                                                                                                                                                                                       |

| Published by Springer, P.O. Box 17, 3300 AA Dordrecht, The Netherlands.                                                                                                                                                                                                                                                                                                                                                                    |

| www.springer.com                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Printed on acid-free paper                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| All Rights Reserved                                                                                                                                                                                                                                                                                                                                                                                                                        |

| © 2007 Springer  No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. |

# **Dedication**

"To Santosh and Baldev Sachdev; Savitri and Dharm Bir Sawhney"

Manoj Sachdev

"To my teachers Jochen Jess and Edgar Sánchez-Sinencio for their invaluable knowledge"

José Pineda de Gyvez

# **Contents**

| Dedication                                                    | V        |

|---------------------------------------------------------------|----------|

| Preface                                                       | xiii     |

| Foreword                                                      | xvii     |

| Foreword for the First Edition                                | xix      |

| Acknowledgements                                              | xxi      |

| Chapter 1. Introduction                                       | 1        |

| 1. Evolution of CMOS Technology                               | 1        |

| 2. The Test Complexity                                        | 5        |

| 3. Quality and Reliability Awareness                          | 9        |

| 4. Building Quality and Reliability                           | 11       |

| 5. Objectives of this Book                                    | 15       |

| 6. Book Organization                                          | 16       |

| Chapter 2. Functional and Parametric Defect Models            | 23       |

| Brief Classification of Defects     Defect-Fault Relationship | 23<br>26 |

| viii | Defect-oriented Testing for Nano-metric CMOS VLSI Circuits |

|------|------------------------------------------------------------|

|------|------------------------------------------------------------|

| 2. Inductive Fault Analysis                                      | 28  |

|------------------------------------------------------------------|-----|

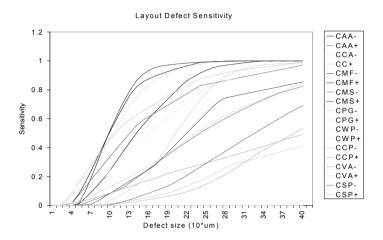

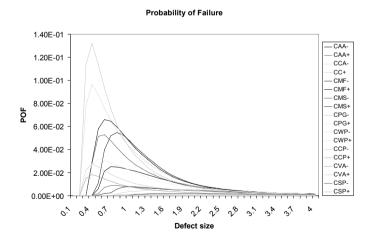

| 2.1 IC Design and Layout Related Defect Sensitivity              | 29  |

| 2.2 Defect Sensitive Design                                      | 29  |

| 2.3 Basic Concepts of IFA                                        | 30  |

| 3. Parametric Defect and Fault Models                            | 32  |

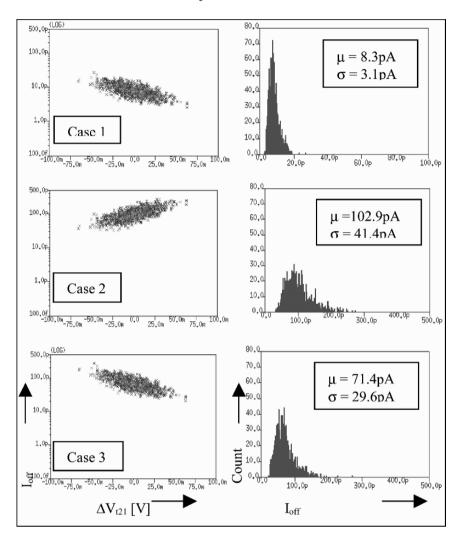

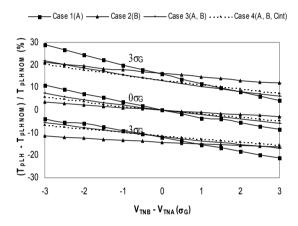

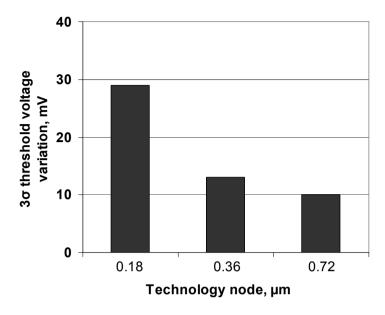

| 3.1 Threshold Voltage Mismatch ( $\Delta V_t$ ) Fault Modeling   | 32  |

| 3.2 Sources of Threshold Voltage Variability                     | 33  |

| 3.3 Leakage Current due to V <sub>t</sub> Mismatch               | 34  |

| 3.4 Delay in Parallel-connected Networks                         | 39  |

| 3.5 Delay Variation Model with $\Delta V_t$ for Parallel         |     |

| Transistor Networks                                              | 41  |

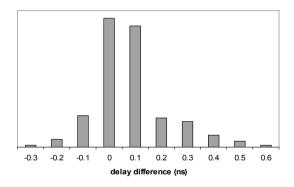

| 3.6 Spot Defect Statistics: Resistive Opens                      | 45  |

| 4. Functional Defect Models                                      | 50  |

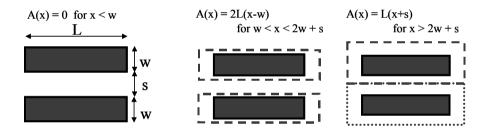

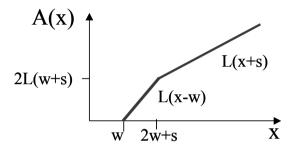

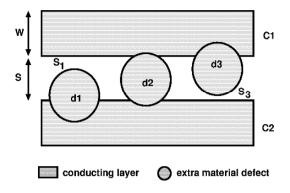

| 4.1 Critical Areas                                               | 53  |

| 4.2 Defect Statistics                                            | 54  |

| 4.3 Average Probability of Failure of Long Interconnects         | 58  |

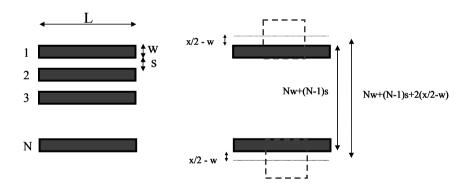

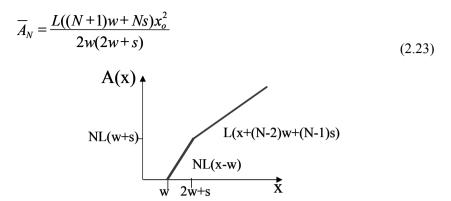

| 4.4 Average Critical Area of N Conductors                        | 61  |

| 5. Conclusions                                                   | 64  |

| Chapter 3. Digital CMOS Fault Modeling                           | 69  |

| 1. Objectives of Fault Modeling                                  | 69  |

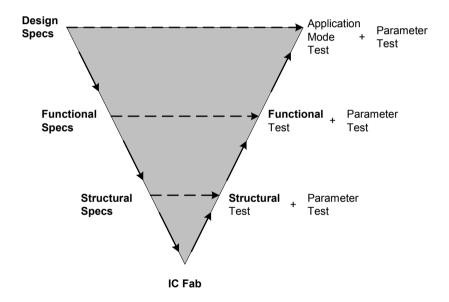

| 2. Levels of Testing                                             | 71  |

| 3. Levels of Fault Modeling                                      | 73  |

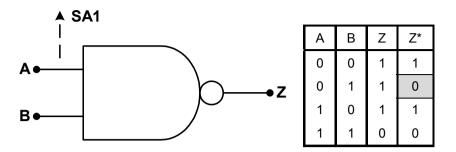

| 3.1 Logic Level Fault Modeling                                   | 73  |

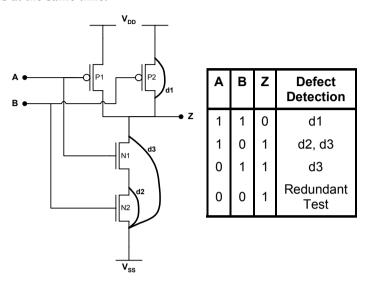

| 3.2 Transistor Level Fault Modeling                              | 81  |

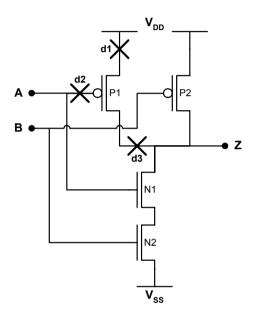

| 3.3 Layout Level Fault Modeling                                  | 90  |

| 3.4 Function Level Fault Modeling                                | 91  |

| 3.5 Delay Fault Models                                           | 92  |

| 3.6 Leakage Fault Model                                          | 97  |

| 3.7 Temporary Faults                                             | 98  |

| 4. Conclusions                                                   | 102 |

| Chapter 4. Defects in Logic Circuits and their Test Implications | 111 |

| 1. Introduction                                                  | 111 |

| Contents | ix |

|----------|----|

|----------|----|

| 2. Stuck-at Faults and Manufacturing Defects                 | 113  |

|--------------------------------------------------------------|------|

| 2.1 Study by Galiay, Crouzet and Vergniault                  | 114  |

| 2.2 Study by Banerjee and Abraham                            | 115  |

| 2.3 Study by Maly, Ferguson and Shen                         | 120  |

| 2.4 Gate Oxide Shorts: Study by Hawkins and Soden            | 123  |

| 3. IFA Experiments on Standard Cells                         | 126  |

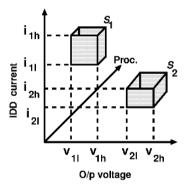

| 4. I <sub>DDQ</sub> versus Voltage Testing                   | 130  |

| 5. Defects in Sequential Circuits                            | 133  |

| 5.1 Undetected Defects                                       | 135  |

| 5.2 Defect Detection Technique                               | 137  |

| 5.3 I <sub>DDQ</sub> Testable Flip-flop                      | 139  |

| 5.4 Defects and Scan Chains                                  | 139  |

| 6. Defect Classes and their Testing                          | 143  |

| 7. Application of IFA in Nano-metric Technologies            | 143  |

| 8. Conclusions                                               | 146  |

| Chapter 5. Testing Defects and Parametric Variations in RAMs | 151  |

| 1. Introduction                                              | 151  |

| 2. Traditional RAM Fault Models                              | 153  |

| 2.1 Stuck-at Fault Model                                     | 153  |

| 2.2 Coupling Fault Model                                     | 154  |

| 2.3 Pattern Sensitivity Fault Model                          | 154  |

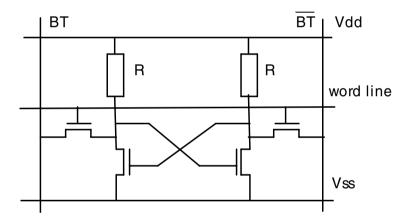

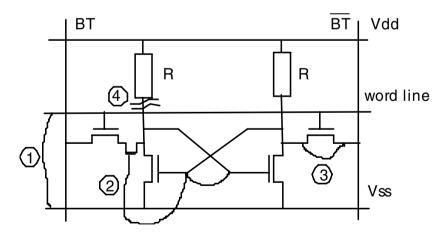

| 3. Defect Based RAM Fault Model Development                  | 155  |

| 3.1 Defect based SRAM Fault Models and Test                  |      |

| Algorithms                                                   | 155  |

| 3.2 Subsequent Defect-oriented SRAM Test                     |      |

| Development                                                  | 160  |

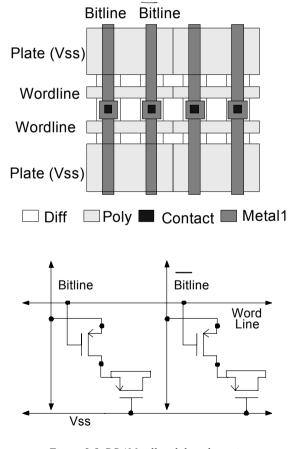

| 3.3 Defect based DRAM Fault Models and Test                  | 1.62 |

| Algorithms                                                   | 163  |

| 3.4 TCAM Fault Models and Test Algorithms                    | 176  |

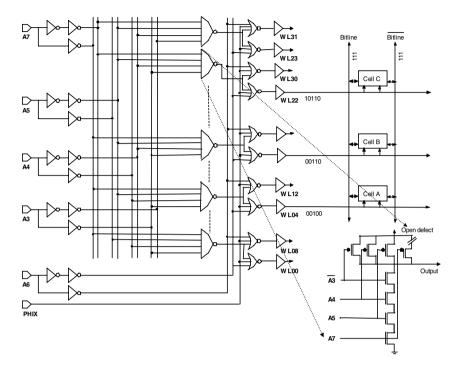

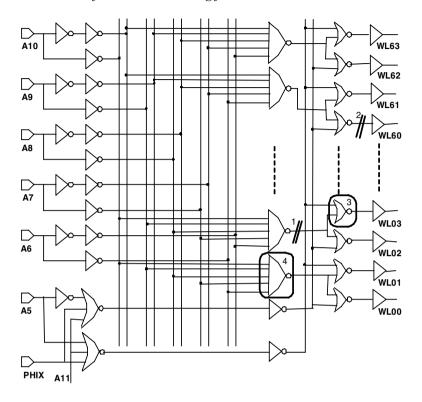

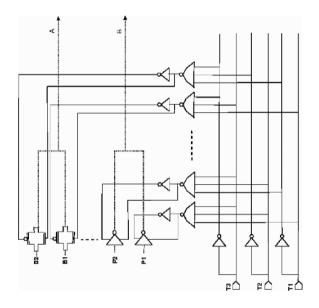

| 4. Address Decoder Defects                                   | 185  |

| 4.1 Early Work on Address Decoder Faults                     | 187  |

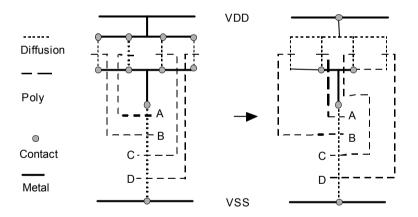

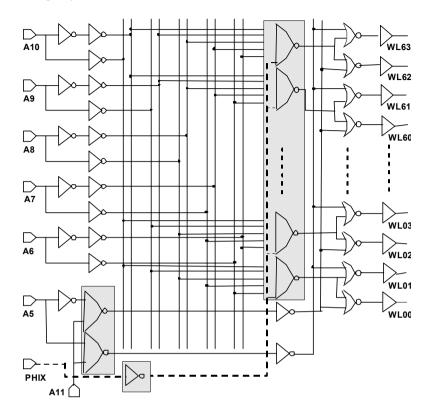

| 4.2 Technological Differences                                | 187  |

| Defect-oriented | Testing for | r Nano-metric | CMOS VL | SI Circuits |

|-----------------|-------------|---------------|---------|-------------|

|-----------------|-------------|---------------|---------|-------------|

X

| 4.3 Failure and Analysis                            | 189 |

|-----------------------------------------------------|-----|

| 4.4 Why Non-detection by March Tests?               | 192 |

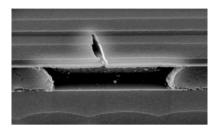

| 4.5 Address Decoder Open Defects                    | 193 |

| 4.6 Supplementary Test Algorithm                    | 195 |

| 4.7 Testability Techniques for Decoder Open Defects | 197 |

| 4.8 Recent Work on Address Decoder Defects          | 200 |

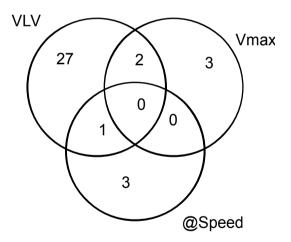

| 5. Parametric Testing of SRAMs                      | 200 |

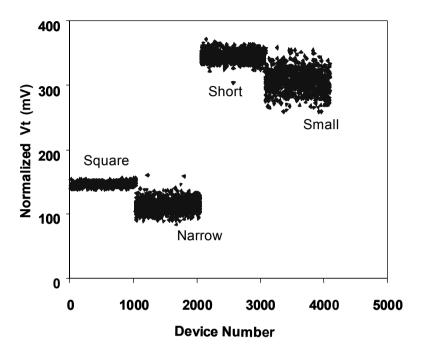

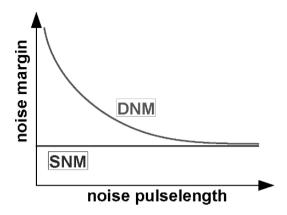

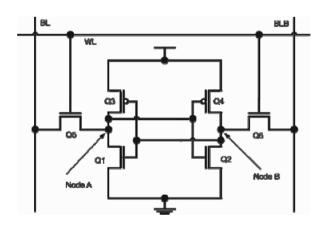

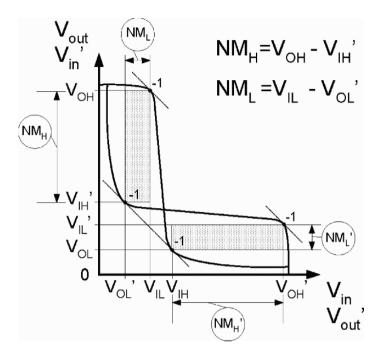

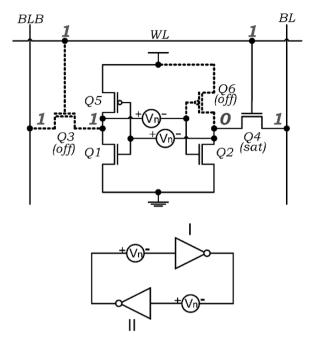

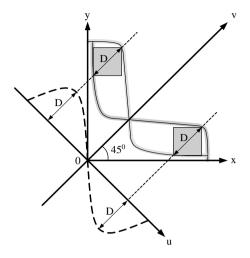

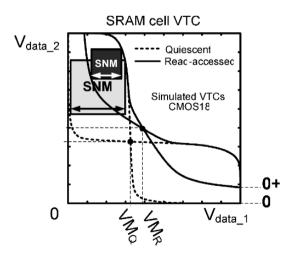

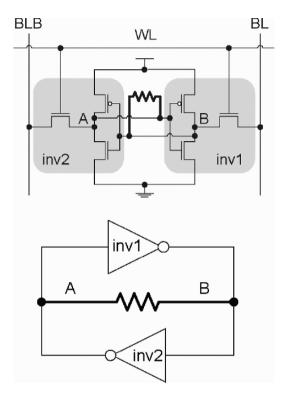

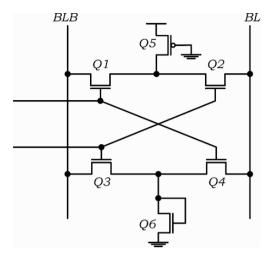

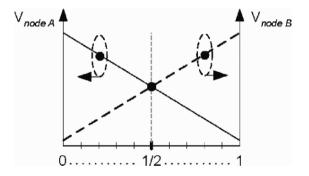

| 5.1 SRAM Cell and SNM                               | 203 |

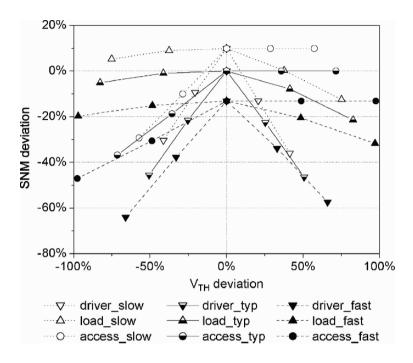

| 5.2 Process Variation and SNM                       | 207 |

| 5.3 Manufacturing Defects and SNM                   | 209 |

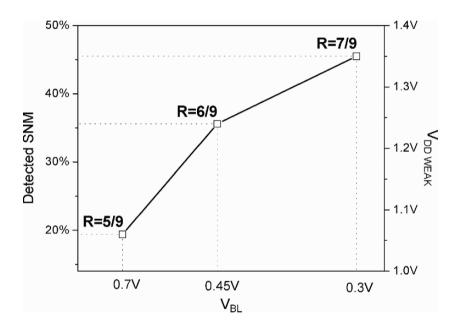

| 5.4 Weak Cell Fault Model                           | 210 |

| 5.5 DfT Techniques to Detect Weak Cells             | 211 |

| 6. I <sub>DDQ</sub> Based RAM Testing               | 215 |

| 7. Conclusions                                      | 215 |

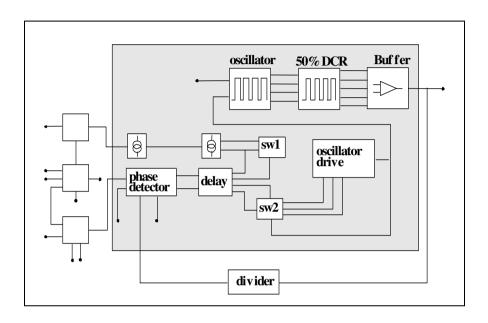

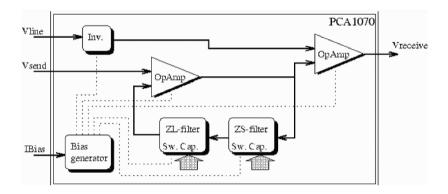

| Chapter 6. Defect-oriented Analog Testing           | 225 |

| 1. Introduction                                     | 226 |

| 2. Analog Test Complexity                           | 227 |

| 3. Previous Work                                    | 228 |

| 3.1 Estimation Method                               | 228 |

| 3.2 Topological Method                              | 228 |

| 3.3 Taxonomical Method                              | 230 |

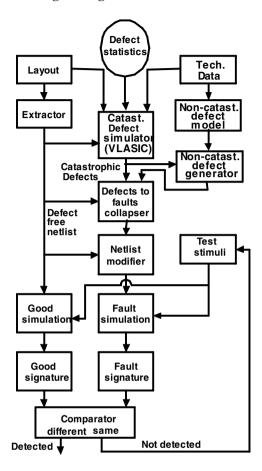

| 4. Defect Based Realistic Fault Dictionary          | 230 |

| 4.1 Implementation                                  | 234 |

| 5. A Case Study                                     | 240 |

| 5.1 Fault Matrix Generation                         | 240 |

| 5.2 Stimuli Matrix                                  | 242 |

| 5.3 Simulation Results                              | 243 |

| 5.4 Silicon Results                                 | 244 |

| 5.5 Observations and Analysis                       | 248 |

| 5.6 IFA: Strengths and Weaknesses                   | 249 |

| 6. Input Stimuli Generation                         | 251 |

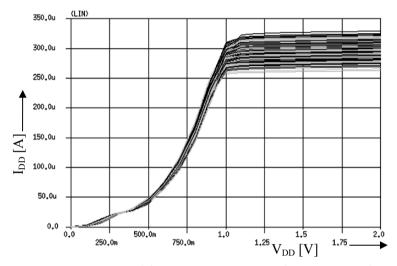

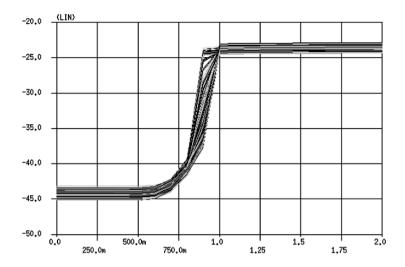

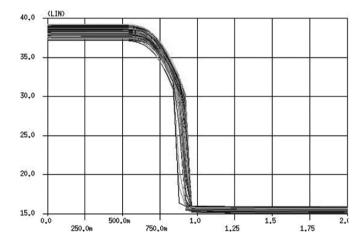

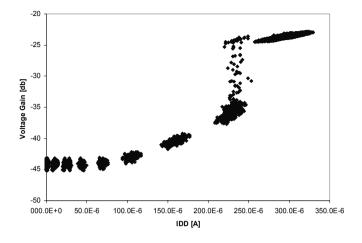

| 6.1 Power Supply Ramp Input Test Stimuli            | 252 |

| 6.2 Amplifier Specs                                 | 254 |

| <ul><li>6.3 Structural vs. Functional Fault Coverage</li><li>6.4 Experimental Results</li></ul>                                                                                                                                     | 259<br>264                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| <ul> <li>7. IFA Based Fault Grading and DfT for Analog Circuits</li> <li>7.1 A/D Converter Testing</li> <li>7.2 Description of the Experiment</li> <li>7.3 Fault Simulation Issues</li> <li>7.4 Fault Simulation Results</li> </ul> | 268<br>268<br>269<br>270<br>272 |

| 8. High Level Analog Fault Models                                                                                                                                                                                                   | 278                             |

| 9. Conclusions                                                                                                                                                                                                                      | 281                             |

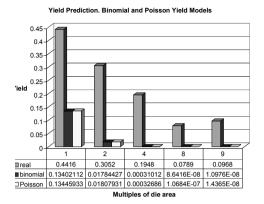

| Chapter 7. Yield Engineering                                                                                                                                                                                                        | 289                             |

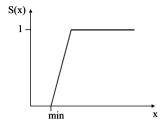

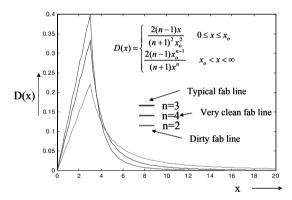

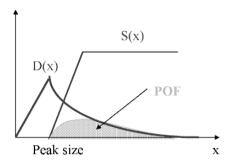

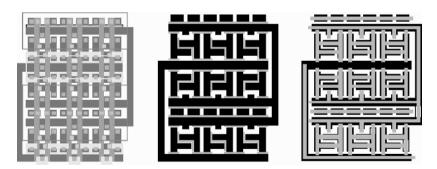

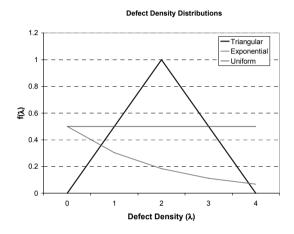

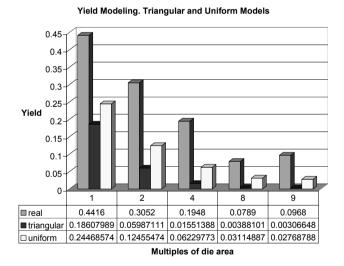

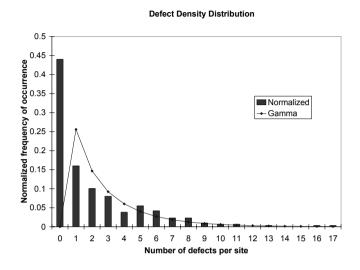

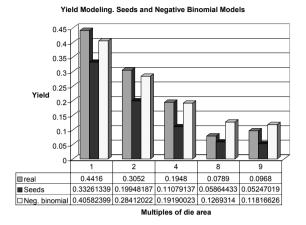

| Mathematical Models for Yield Prediction     1.1 Layout Oriented Yield Prediction                                                                                                                                                   | 289<br>300                      |

| 2. Yield Engineering                                                                                                                                                                                                                | 301                             |

| 3. Economics and Yield Forecasting                                                                                                                                                                                                  | 306                             |

| 4. Conclusions                                                                                                                                                                                                                      | 312                             |

| Chapter 8. Conclusion                                                                                                                                                                                                               | 317                             |

| Test and Yield Engineering Complexity in Nano-metric     Technologies                                                                                                                                                               | 317                             |

| <ul><li>2. Role of Defect-oriented Testing</li><li>2.1 Strengths of Defect-oriented Testing</li><li>2.2 Limitations of Defect-oriented Testing</li></ul>                                                                            | 320<br>320<br>321               |

| 3. Future Directions                                                                                                                                                                                                                | 321                             |

| Index                                                                                                                                                                                                                               | 325                             |

# Preface

Defect-oriented testing methods have come a long way from a mere interesting academic exercise to a hard industrial reality. Many factors have contributed to its industrial acceptance. Traditional approaches of testing modern integrated circuits have been found to be inadequate in terms of quality and economics of test. In a globally competitive semiconductor market place, overall product quality and economics have become very important objectives. In addition, electronic systems are becoming increasingly complex and demand components of the highest possible quality. Testing in general and defect-oriented testing in particular help in realizing these objectives.

For contemporary System on Chip (SoC) VLSI circuits, testing is an activity associated with every level of integration. However, special emphasis is placed for wafer-level test, and final test. Wafer-level test consists primarily of dc or slow-speed tests with current/voltage checks per pin under most operating conditions and with test limits properly adjusted. Basic digital tests are applied and in some cases low-frequency tests to ensure analog/RF functionality are exercised as well. Final test consists of checking device functionality by exercising RF tests and by applying a comprehensive suite of digital test methods such as I<sub>DDQ</sub>, delay fault testing, stuck-at testing, low-voltage testing, etc. This partitioning choice is actually application dependent.

The relevance of defect-oriented testing in nanometer regime is more than ever. Higher packing density, ever larger systems on chip configurations, increased process complexity and process spread are making designs sensitive to subtle manufacturing defects. Tests professionals are expected to face numerous challenges in their quest to improve quality, reliability and yield of contemporary integrated circuits. Some of these challenges are mentioned below, and described through the book.

For economic reasons, test simplification is needed for SoC VLSI circuits. It is not unusual that an analog test engineer spends 20% of his/her efforts on software development, 30% on hardware test debugging and 50% on tester RF measurements. For a digital test engineer this workload is reversed, e.g. the digital test engineer spends most of his/her time at devising the appropriate test methodologies, designing the DfT, and generating test patterns. His/her post-silicon tasks are primarily concerned with product debugging and ensuring low test escapes. This can translate into several months of test development depending upon the maturity of the device and fabrication process. Test strategies may also be driven by a time to market window. Under this scenario wafer test is geared to improve yield only and most of the attention is devoted on final test.

Until now RF functionality has been provided by individual ICs such as mixers, PLLs, Multiple Output PLL, transceivers. Often, functionality and specifications are tested with "laboratory" or test-bench-like methods. Future ICs, in either silicon or Multi Chip Module (MCM) integration form, will force us to deliver more integrated functions with new tests challenges. Since these RF IPs will be embedded in the SoC, it will be difficult to access all RF ports and as such current RF test practices will not longer be applicable or will need to be revised. It is also evident that RF test times need to be reduced to acceptable limits within the digital-testing time domains through incorporation of DfT, BIST and silicon debug techniques. In addition, the RF testing will need to shrink the gap between customer needs in terms of PPM and testing methods.

Due to the device and voltage scaling scenarios for present and future nanometer CMOS technologies, it is inevitable that the attention will shift to testing parametric defects. As we know, the nano-metric regime brings new technological problems that did not exist before or that were not relevant in the past. Elevated leakage current, and signal integrity issues in interconnects are examples of new problems in modern technologies. Similarly, there are design and test challenges that are on the horizon. For example, transistor gate leakage,  $V_t$  mismatch, excessive substrate noise, etc. These issues, if left unattended, have the potential to erode yield, quality and reliability of integrated circuits. To deal with them, there is a need for (i) debugging, (ii) diagnosis, (iii) system-oriented testing, and (iv) "technology-oriented" test methods. Traditional stuck-at testing, will have difficulties

*Preface* xv

catching many of these new "process-related defects" and as such comprehensive nano-metric test methodologies are imperative.

Without loss of generality, any comprehensive test program has the following challenges:

- Design for test.

- Need to deliver known good die (KGD).

- Need to guarantee low test escapes.

- Need to achieve very low cost testing.

- Need to diagnose failures

In this second edition, we have made an attempt to provide the reader with current trends in the field of defect-oriented testing. The target audience of this book consists of design and test professionals. However, this book may also be used as a reference book for graduate level courses on VLSI testing, or on VLSI quality and reliability. Our motivation to write the second edition comes from two diverse sources. Firstly, the field of defect-oriented testing is more than two decades old. However, the information on the subject is fragmented and distributed in various conferences and journal papers. Secondly, there is a wide disparity among various companies as well as academic institutions on the level of knowledge on this subject. A vast majority of research is carried out by a few companies and academic institutions. Therefore, it is intended that this book will help in spreading the knowledge of the subject.

Manoj Sachdev and José Pineda de Gyvez July 2006

# **Foreword**

Almost ten years would have passed since the publication of the original book by the time this second edition reaches the hands of a reader. Let's ask what has changed in the last decade. We find that chips have become systems. Besides, nanotechnology has crept into them. Testing, traditionally considered at the gate level, has advanced in two opposite directions. Upward, on one hand, to the system level and downward, on the other hand, to the nano-device level. A test engineer now needs to reach out in both directions. This second edition brings the updates to allow us to stretch upward as well as downward.

I can summarize the main differences from the first edition as follows:

- 1. A new chapter on *functional and parametric defect models* is added.

- 2. Enhancements to the chapter on *fault models* include inductive fault analysis for nano-metric technologies, radiation induced faults, and defects causing delay faults.

- 3. The chapter on testing of *RAMs* is extensively updated. New material on strategies of design for testability and test algorithms for weak cells in embedded SRAMs and address decoder faults has been added.

- 4. The chapter on analog testing is thoroughly revised. Notably, new test techniques, such as a power supply ramp testing method, have been added.

- 5. A new chapter on yield engineering is added.

This edition will be useful to those who work or plan to work in the area of VLSI testing, namely, practicing engineers and students. I thank the authors for their timely effort. I must, however, remind them that technology is never static. The changes in the next decade may be even more rapid than in the past. I hope the authors, Manoj Sachdev and Jose Pineda de Gyvez, will continue this work.

Vishwani D. Agrawal vagrawal@eng.auburn.edu August 2006

# **Foreword for the First Edition**

We have made great strides in designing complex VLSI circuits. A laborious design verification process ensures their functional correctness. If no defects occur in manufacturing then testing will not be required. However, the world is not so perfect. We must test to obtain a perfect product.

An exact repetition of the verification process during manufacture is too expensive and even impossible. So, we test for a selected set of modeled faults. There is no unified modeling procedure for the variety of VLSI chips we make. Stuck-at model applies only to some types of digital circuits. Besides, there are problems, such as, (a) some stuck-at faults cannot occur in the given VLSI technology and (b) some actual manufacturing defects have no stuck-at representation. Numerous known problems with the present-day test procedures point to a defect-oriented testing. This simply means that we use the knowledge about the manufacturing process to derive tests. Such tests provide the greatest improvement in the product quality for the minimum cost of testing.

Dr. Sachdev has done original work on defect-oriented testing. He takes experimental defect data and applies the inductive fault analysis to obtain specific faults for which tests should be derived. His work is done in an industrial setting and has been put to practice at Philips Semiconductors and elsewhere. The material in this book is collected from his PhD dissertation, research papers and company reports.

A strength of this book is its breadth. Types of designs considered include analog and digital circuits, programmable logic arrays, and memories. Having a fault model does not automatically provide a test. Sometimes, design for testability hardware is necessary. Many design for testability ideas, supported by experimental evidence, are included.

In addition to using the functional and other conventional tests, Dr. Sachdev takes full advantage of the defect-isolating characteristics of non-functional tests. Imagine taking a multiple-choice examination. All of us can remember making a guess some time and succeeding. Suppose, I connect you to a lie detector while you checked those choices. The lie detector may tell me to fail you even on some correct answers. Also, given the new procedure, we can design special tests. Current measurements similarly bring out the internal conflicts whose effects may not be visible by conventional logic tests. Such tests, though non-functional, improve the defect coverage. Current measurement is an important subject discussed in this book.

Non-functional tests are not without their pitfalls. Not much is accomplished if one who is going to be an electrical engineer passes or fails an examination in history. Clearly, there is need for matching the test with the function. In electronic circuits a non-functional test, designed to isolate a real defect, can reject a circuit with some other functionally acceptable defect. This phenomenon, known as yield loss due to non-functional tests, impacts costs similar to the design for testability overhead. In both cases, the costs are associated with quality improvement. A central theme in this book is to minimize such costs and it wonderfully succeeds in putting the economics of test and manufacture into practice.

Vishwani D. Agrawal Bell Labs Murray Hill, New Jersey va@research.bell-labs.com September 1997

# Acknowledgements

During the various phases of the work we had the opportunity to exchange ideas and learn from experts in the field. We would like to acknowledge the following people of Philips Research. Guido Gronthoud for his continuous support and encouragement on various topics such as analog testing, and process-aware testing. Rodger Schuttert for providing us with the data for the yield engineering section. Paul Volf and Rosa Rodríguez Montañez for their challenging minds and insight during the development of the work on resistive vias. Maurice Lousberg for his always open mind and interest in our work. Rene Segers for his support on various topics. Stefan Eichenberger and Bram Kruseman for their vast experience in defectoriented testing. The young and challenging "analog and RF testing" minds of Amir Zjajo, Estella Silva and Shaji Krishnan deserve also being mentioned. We also like to acknowledge the support of Kees Veelenturf and Paul Simon, of Philips Semiconductors, for our early research on DfM.

The book would not be in this form if several of graduate students and post doctoral fellow in the electrical and computer engineering department at University of Waterloo had not participated tirelessly. In particular, contributions of Derek Wright, S. M. Jahinuzzaman, Oleg Semenov are worth mentioning. Authors would also like to thank Chuck Hawkins of University of New Mexico for reviewing some of the chapters of the book. Finally, the management support of Ad ten Berg at Philips Research is gracefully recognized.

Manoj Sachdev, and José Pineda de Gyvez

# Chapter 1

# INTRODUCTION

This chapter introduces some key test issues, namely test complexity, quality, reliability, and economics faced by the semiconductor industry. These issues form a basis for subsequent chapters.

# 1. EVOLUTION OF CMOS TECHNOLOGY

The microelectronics industry has been growing at an astounding pace in the last two decades, primarily due to the integration capability of complementary metal oxide semiconductor (CMOS) manufacturing processes. Ever increasing clock speeds of micro-processors and bigger, cheaper dynamic random access memories (DRAMs) are enabling applications that were unthinkable just a few years ago. A foray of CMOS technology in numerous application domains such as telecommunications, computing, and consumer applications continues at the cost of other manufacturing technologies such as bipolar, GaAs, etc. This trend is likely to continue for some time as we move forward in the 21st century [22].

The concept of a metal oxide semiconductor (MOS) transistor was independently described by Lilienfeld, and Heil, respectively in 1930s [27,20]. However, it could not be manufactured owing to poor Si-SiO<sub>2</sub> interface. The bipolar junction transistor (BJT) was invented at Bell laboratories in 1947 [6,45]. It took several years to exploit the transistor's true potential with the invention of integrated circuits (ICs) in the late 1950s by Jack Kilby [25]. Modern ICs owe their root to Frank Wanlass. He invented the concept of CMOS logic in 1963 [52] and called it nanowatt logic [53]. However, CMOS technology did not gain popularity until the late 1970s. Since then, CMOS has been the technology of choice for a vast majority of applications owing to its relatively simple, inexpensive

manufacturing process, integration capability, and extremely small power consumption compared to other integrated circuit technologies.

The recent surge in information technology related industries is largely enabled by our abilities to design and manufacture complex ICs. The semiconductor industry is unique in having sustained such a spectacular growth over a significantly long period. As a result, industry has provided electronic products at substantially lower cost per function with higher performance year after year.

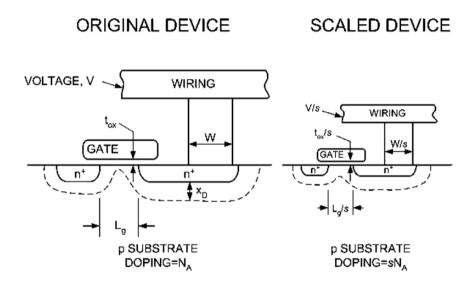

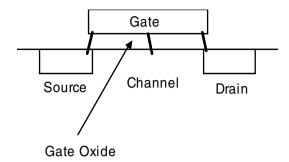

Figure 1-1. MOS transistor scaling.

For several technology generations, the shrinking of metal oxide semiconductor (MOS) transistors has been governed by the concept of scaling [33,10,5,13]. Figure 1-1 depicts the concept. All dimensions of a MOS transistor are scaled by a factor s (s > 1) to produce a smaller transistor while preserving its behavior. If all the dimensions and voltages are reduced by a factor s, and doping densities are increased by s, the electric field inside the device remains as before. This type of scaling is known as *constant electric field scaling* (CFS). Since the electric field remains constant, this type of scaling does not result in device damage due to excessive electric field. As evident from the second column of Table 1-1, scaling results in higher relative gate density ( $s^2$ ), lower gate delay (1/s), and reduced power dissipation ( $1/s^2$ ).

Table 1-1. Scaling concepts for MOS transistor.

| Parameter             | Relation           | Constant<br>Electric<br>Field<br>Scaling | Constant<br>Voltage<br>Scaling | General<br>Selective<br>Scaling |

|-----------------------|--------------------|------------------------------------------|--------------------------------|---------------------------------|

| W, L, t <sub>ox</sub> |                    | 1/ <i>s</i>                              | 1/s                            | 1/ <i>s</i>                     |

| $V_{DD}, V_{t}$       |                    | 1/s                                      | 1                              | 1/g                             |

| Area                  | WL                 | $1/s^2$                                  | $1/s^2$                        | $1/s^2$                         |

| C <sub>ox</sub>       | 1/ t <sub>ox</sub> | S                                        | S                              | S                               |

| $C_{\mathrm{gate}}$   | WL Cox             | 1/s                                      | 1/s                            | 1/s                             |

| I <sub>sat</sub>      | $C_{ox}WV$         | 1/ <i>s</i>                              | 1                              | 1/g                             |

| Gate delay            | $VC_{ox}/I_{sat}$  | 1/ <i>s</i>                              | 1/s                            | 1/s                             |

| Power dissipation     | $I_{sat}V$         | $1/s^2$                                  | 1                              | $1/g^2$                         |

| Power Density         | Power/Area         | 1                                        | $s^2$                          | $s^2/g^2$                       |

Constant electric field scaling is not always possible. Very often, power supply voltage is determined due to system considerations, or to keep newer devices compatible with existing parts. Therefore, earlier devices (until 0.8  $\mu$ m) followed the constant voltage scaling (CVS) path. However, it was subsequently abandoned in favor of CFS owing to higher electric fields inside the device and its implications on long-term device reliability. Deep sub-micron devices often follow general selective scaling (GSS) where the device dimensions and voltages are scaled by different factors. Several intrinsic voltages inside a MOS transistor such as built-in junction potential are material parameters, while others such as threshold voltage (V<sub>t</sub>) cannot be scaled by the same factor. Therefore, voltage should be scaled less aggressively by a factor g (where g > 1). GSS offers the performance benefits of CFS or CVS while its power dissipation is in between CFS and CVS.

It appears that the industry is now in a deep sub-micron regime, and a number of technical challenges threaten the continuation of what is known as Moore's Law [33]. The difficulty of design and manufacture has increased to a point where exploitation of its full potential seems to be unrealistic. For example, the above mentioned scaling scenarios assume insignificant leakage current increase with scaling. However, this component is significantly large in sub-0.18 µm technologies. Increased leakage current consumption in modern ICs is causing long term reliability concerns. Elevated leakages result in increased power dissipation which, in turn causes higher junction temperature. Recently, Semenov et al. [46] estimated a 1.45 times increased in junction temperature per technology generation under nominal operational conditions. Higher junction temperature is one of the major contributors to poor device reliability.

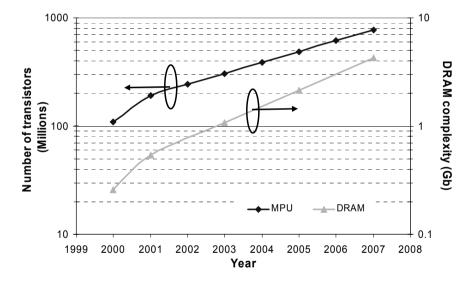

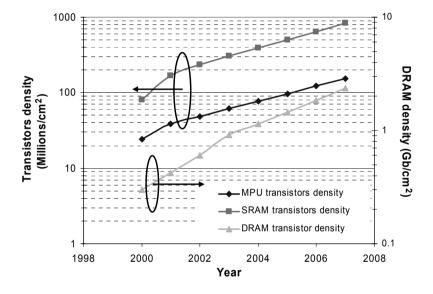

Figure 1-2. Giga scale integration [22].

Similarly, nominal functionality of scaled transistors is extremely susceptible to natural manufacturing process spreads. Varying impurity densities, gate oxide thickness, and junction depths may cause transistors parameters such as  $V_t$  to shift resulting in abnormal delays and leakages. Finally, as more transistors are crammed per unit area, tiny defects and imperfections created during the manufacturing process can cause failures.

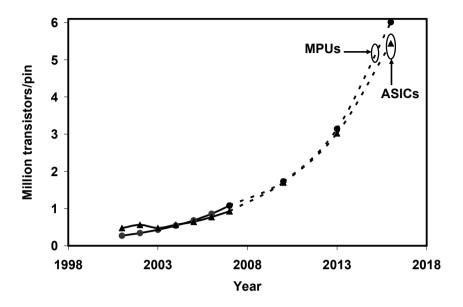

Figure 1-3. Number of transistors per IO pin for microprocessors and ASICs [22].

# 2. THE TEST COMPLEXITY

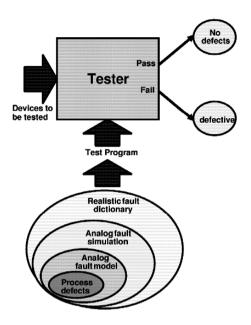

Imperfections in the manufacturing process necessitate testing of the manufactured ICs. The fundamental objective of the testing is to distinguish between good and faulty ICs. This objective can be achieved in several ways. Earlier, when ICs were relatively less complex, this objective was achieved by functional testing. Functional tests are closely associated with the IC function. Therefore, these tests are comparatively simple and straightforward. A 4-bit binary counter can be exhaustively tested by  $2^4 = 16$ test vectors. However, as the complexity of the fabricated ICs increased, it was soon discovered that the application of a functional test is rather expensive on test resources and is inefficient in catching the manufacturing process imperfections (or defects as they are popularly known). For example, a digital IC with 32 inputs has only a modest design complexity by today's very large scale integration (VLSI) standards, but will require  $2^{32}$  = 4,294,967,296 test vectors for exhaustive functional testing. If these are applied at the rate of 10<sup>6</sup> vectors per second, it will take 71.58 minutes to test a single IC. The test becomes even longer if the IC contains sequential logic. Moreover, exhaustive testing may not be enough to detect defective parts if the faulty behavior becomes sequential. In this case, newer test methods such as delay testing as well as stressing conditions including temperature and low power supply voltage are needed. Obviously, it is too expensive a test solution to be practical.

The test problem is further compounded by the rapid development of CAD tools in the areas of IC design and manufacturing, which help engineers to design and fabricate complex ICs. For example, recent trends towards silicon reuse (core based systems on chip (SoC) design styles) are resulting in shrinking design cycles. However, test and testability Computer Aided Design (CAD) tools are lagging. The need for simulation tools for test and testability analysis became visible only when testing was recognized as a bottleneck in achieving increasingly important quality, reliability and time to market goals. Figure 1-2 illustrates this complexity vividly. As it is abundantly clear from the graph, we are into the giga-scale integration regime.

Figure 1-3 shows this complexity from the test perspective. This figure illustrates the growing number of transistors per IO pin for microprocessors and application specific integrated circuits (ASICs). The number of input and output pads or pins has not been able to keep up with increased integration. This packaging limitation puts severe additional constraints on the testing of complex ICs. For example, the number of transistors on a chip continues to double every 1.5-2.0 years. However, the number of package pin/balls grows at an annual rate of approximately 11% [22]. Typically, larger, bigger ICs require an increased number of pads and pins to allow data flow to and from the IC. Additionally, more pads and pins are required to provide adequate power and noise immunity. The issue of power delivery and power supply noise is critical in high performance circuits. Approximately two-thirds of all pads are dedicated to power and ground so as to deliver excess of 100 W of power to hungry transistors. In high performance ASICs the situation is better and only approximately half of the total number of pads is for power and ground.

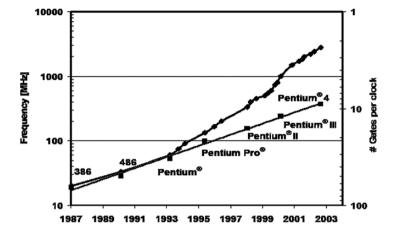

Irrespective of application domains, the number of transistors per signal pad is growing rapidly, and Figure 1-3 illustrates its projections. Figure 1-4 depicts the growing transistor density of ICs. Effectively, the depth of logic that is to be accessed from primary pins increases for each successive generation of chips. In other words, controllability and observability objectives become much more difficult to achieve for modern ICs from outside the chip. As a result, test vector sequences are becoming longer and are adding to the test cost. At the same time, the cost of general-purpose automatic test equipment (ATE) is also increasing significantly. A state of

the art ATE can now cost a few million dollars. The expensive ATE and the longer test vector sequences push the test costs to unacceptable levels.

The test complexity can also be segregated in terms of (i) quantitative issues, and (ii) qualitative issues. Tens of millions of transistors on a chip must be tested in a reasonable and economically viable test time. The builtin self test (BIST) has become a de-facto standard testing of embedded memories, while significant progress has been made on BIST for logic and analog circuits.

Figure 1-4. Growing transistor density [22].

The above-mentioned scenario matches with the evolution of the semiconductor memory market. Each successive DRAM generation has grown in complexity by a factor of four and the access time has decreased by a factor 0.8 for each new generation. Therefore, testing time is increased by 3.2 times for each new generation. This results in a tremendous increase in testing cost which prevents the cost per bit from coming down despite increased integration. Small feature size and huge chip size result in an enormous critical area [12] for defects. Since RAMs must be mass produced, their test strategies are under severe pressure to ensure the quality of the tested devices while maintaining the economics of the production. In other words, testing of RAMs in an efficient, reliable, and cost effective manner is becoming an increasingly challenging task [29].

For example, a study of DRAMs identified the test cost, along with process complexity, die size, and equipment costs as a major component in future DRAM chip costs [23]. The test cost of a 64 Mbit DRAM was projected to be 240 times that of a 1 Mbit DRAM. For a 64 Mbit DRAM, the test cost to total product cost ratio was expected to be 39%. If the conventional test methods are used, test costs will grow at a rapid rate. The SRAM test cost was also expected to follow a similar trend. Moreover, RAMs are the densest and one of the biggest chips ever to be tested. DRAM chip size has grown by 40 to 50% while the cell size has decreased by 60 to 65% for each successive generation. The chip size of 64 Mbit DRAM is in the range of 200 mm<sup>2</sup>.

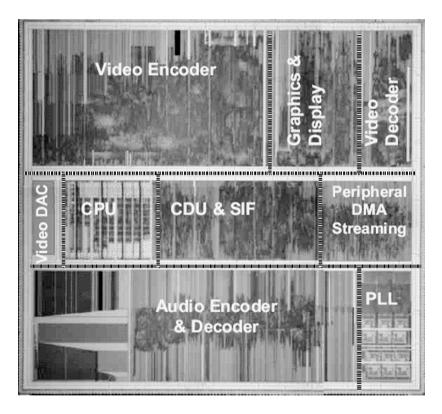

Figure 1-5. A typical systm on chip [17].

This IC test cost explosion is not limited to RAMs. There has been a dramatic increase in SoC designs, which can include digital, analog, RF, mixed-signal, and memory all on the same die, as is illustrated in the die

shown in Figure 1-5 [18]. It is a single chip MPEG-2 decoder for use in DVD players that illustrates how both digital (CPU), mixed-signal (video DAC), and analog (PLL) circuits now reside on the same die. Since each of these circuit types requires different tester capabilities, testers must now be able to test different kinds of functionality. Also, there are an increasing number of chips per wafer, which necessitates either testers with more channels for testing, or fewer channels with more touchdowns (the number of times the probes of the tester have to move to a new location). The end result is a dramatic increase in testing time and costs, to the point where in some cases the cost of testing dominates the overall cost of manufacturing [51]. For example, the test development time for complex single chip television ICs manufactured by Philips is reported to be many man years! Such developments have caused a surge of interest in the economics of test [3]. A number of studies have been reported on test economics [1,8,57]. Dislis et al. [8] demonstrated that economic analysis can be a powerful aid in the selection of an optimal set of design for test (DfT) strategies, and in the organization of production test processes.

# 3. QUALITY AND RELIABILITY AWARENESS

Ever since the invention of the transistor in late 1940s, the semiconductor industry has grown into diverse applications areas. These range from entertainment electronics to space applications. Computers and telecommunication are other notable applications. Irrespective of the application areas, the quality and reliability demands for semiconductor devices have significantly increased [15,16]. This requirement is not difficult to understand.

It is a well known rule of thumb that if it costs one dollars to test a defective component at the chip level, it will cost ten dollars at the board level and hundred dollars at the system level to test, diagnose and replace the same defective component. Therefore, economically it makes a lot of sense to build a system with high quality components. As a well known example, a version of the Pentium processor was released with an undetected error in the floating-point unit. This design flaw was discovered only after the processor had been integrated into systems and sold to consumers as desktop computers. The replacement and lost inventory charges cost Intel Corporation \$475M. Better design verification and testing could have detected this error very early in the design phase for a fraction of the cost [38]. ICs for the automotive branch are just another example of the need for quality and reliability with preferably zero ppm levels. DfT strategies have

an important role to play in reducing high costs associated with testing and debugging at the sub-system and/or system level. Researchers have shown that such strategies improve quality and decrease test costs by an order of magnitude [36].

Pulat and Streb [34] put numbers into the escalating cost of building products with quality and reliability. Imagine a component with 1% test escapes. It will cause a shipment of 10,000 defective parts per million items produced. If 30 such components are required to make a product, each with 1% test escape, the overall product yield would be only 74%. Hence, modest failure rates at the component level may result in a significant likelihood of failure at the board or system level. The increasing system complexities require still better quality from IC suppliers so as to make economic, quality systems.

On the other hand, market economics forced what were known as purely digital ICs to incorporate embedded memories as well as analog blocks so as to offer cheaper and more reliable SoC solutions. As mentioned in the previous section, these SoCs have many different functional blocks all on the same substrate, which makes circuits such as RAMs, analog blocks more susceptible to a variety of manufacturing process defects. Higher degree of integration, though far reaching in terms of market penetration, caused anxiety amongst design, process, and test professionals.

As systems became more complex, their upkeep, maintenance, and repair became more costly. Often specialists are required for such functions. Therefore, reliable system operation over its lifetime became another absolute requirement. These developments led to slogans like Design for Quality and Design for Reliability. The terms quality and reliability are often misunderstood. Here, for the sake of clarity, we must distinguish between the terms quality and reliability.

According to Hnatek [15]; the words "reliability" and "quality" are often used interchangeably as though they were identical facets of a product's merit; however, they are different. Quality pertains to the population of faulty devices among the good ones as they arrive at the user's plant. Or, in another view, quality is related to the population of faulty devices that escape detection at the supplier's plant... Reliability is the probability that an IC will perform in accordance with expectations for a predetermined period of time in a given environment. Thus reliability is quality on a time scale, so to speak, and testing (screening) compresses the time scale.

# 4. BUILDING QUALITY AND RELIABILITY

Design, manufacturing, and test form three major activities in the development of an IC. It is futile to believe that overall quality of any IC can be achieved considering only design, manufacturing, or test alone. In other words, robust design, controlled manufacturing process, and effective test strategy together result in a quality product.

The role of design and manufacturing in building IC quality and reliability has been investigated in depth and is the focus of further investigations [50]. From the manufacturing standpoint, fabrication process and device technologies in the deep sub-micron region (90-32 nm) are approaching practical limits, and therefore concurrent achievements in high performance, high packing density, and high reliability are expected to become increasingly difficult. Besides, quality and reliability issues for VLSI (with as many as 10<sup>9</sup> transistors on a chip) are becoming more stringent due to required escape rates of less than 100 parts per million (PPM) and required failure rates of less than 10 failures in time (FIT) [9,44]. One device failure in 10<sup>9</sup> device-operating hours is termed as one FIT. Furthermore, due to the large initial investment required by the fabrication process complexity, it has recently become a matter of considerable debate whether such an investment is profitable. Similarly, contribution of design to improve quality and reliability of ICs has been outstanding, and is beyond the objectives of this book.

The often-stated objective of testing is to ensure the quality of the designed systems. Testing is the last check-post before the product is shipped to its destination. In other words, it is the last opportunity to prevent the faulty product from being shipped. Pulat and Streb [34] stressed the need for component (IC) testing in total quality management (TOM). In a large study spreading over three years and encompassing 71 million commercial grade ICs, Hnatek [15] reported differences in quality seen by IC suppliers and users. One of the foremost conclusions of the study was that IC suppliers often do not do enough testing. How thorough must the functional testing of digital ICs be to guarantee adequate quality? Is fault grading necessary? If yes, how high must the single-stuck fault coverage be for a given quality? These were the objectives of a study conducted by Agrawal et al. [2]. They described a model-based technique for evaluating the fault coverage requirement for a given field escape rate (PPM). In their subsequent paper [47], the authors showed that the fault simulation results with tester data can also predict the yield and fault coverage requirements for a given PPM for an IC. It was shown that for 1000 PPM, about 99% fault coverage will be needed. Similar results were obtained by McCluskey and Buelow [31]. The

result of their theoretical analysis as well as experimental evidence indicated that logic production test fault coverage of greater than 99% is necessary for manufacturing and selling high quality ICs.

At the same time, it was discovered that classical voltage based test methods for digital CMOS ICs are grossly inadequate in ensuring the desired quality and reliability levels [11,35]. Many commonly occurring defects like gate oxide defects often are not detected by logic tests [11,42]. Therefore, such escaped defects are quality and reliability hazards. This increased quality awareness brought in new test techniques like quiescent current measurements (QCM), or  $I_{DDQ}$  as it is popularly known, in the test flow for digital CMOS ICs [35,4,19,30]. Arguably,  $I_{DDQ}$  is the most effective test method in catching manufacturing process defects. Perry [35] reported that with the implementation of  $I_{DDQ}$  testing on ICs, the system failure rate dropped by a factor of six. Gayle [17] reported that with implementation of  $I_{DDQ}$  testing the defect rate had fallen down from a high 23,000 parts per million to a more acceptable 200 parts per million. Similarly, Wiscombe [54] reported improvement in quality levels.

In the late 1990s, several researchers [41,55,56] identified that increasing MOSFET off-currents ( $I_{OFF}$ ), together with a higher degree of integration is going to erode the benefits of  $I_{DDQ}$  testing. Contemporary MOSFETs are scaled using the concept of general selective scaling, as depicted in Table 1-1. Hence,  $V_{DD}$  and  $V_t$  are scaled down proportionately with scaling of the MOSFET dimensions. An 80-100 mV reduction in the  $V_t$  of a MOSFET increases its  $I_{OFF}$  by a factor of 10. In recent years with each successive technology generation, the  $V_t$  was reduced by 100-200 mV. As a consequence, the  $I_{OFF}$  was increased between 10-100 times for a given transistor width with scaling. As the total chip leakage current approaches the mA range, the defect-free and defective  $I_{DDQ}$  distributions begin to overlap, hence reducing its effectiveness.

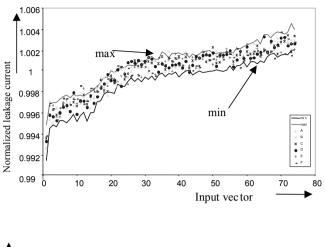

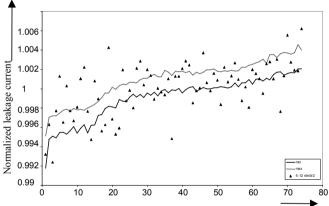

Despite the decreasing effectiveness of traditional  $I_{DDQ}$  measurements, researchers continue to devise new current-based test methods that are effective in deep sub-micron technologies [43]. Some of these methods, namely  $\Delta I_{DDQ}$  and  $I_{CCQ}$ , exploit differential measurement to cancel the increasing common-mode leakage current [32, 26]. Maxwell et al. argued that both approaches are based on some threshold of current differences and therefore, they suffer from the effects of process variation. Setting a threshold based on either maximum allowable current or the difference between currents will be difficult because of large vector-to-vector, or dieto-die, variations. Maxwell et al. suggested plotting  $I_{DDQ}$  in ascending order as a function of test vectors, and characterizing it [28]. Some researchers

also explored the feasibility of transient current measurements and characterized its effectiveness compared to  $I_{DDO}$  [42].

Analog test complexities are different from that of digital circuits. The application of digital DfT schemes has been largely unsuccessful in the analog domain [40]. As a result, a vast majority of analog circuits are tested by verifying the functionality (specifications) of the device. Since different specifications are tested in different manners, it makes analog functional testing costly and time consuming. Moreover, often extra hardware is needed to test various specifications. Limited functional verification does not ensure that the circuit is defect-free and escaped defects pose quality and reliability problems. Defect-oriented testing provides a structured analog test methodology which improves the quality, reliability, and economics of tested devices.

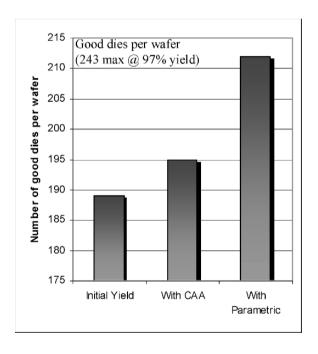

Figure 1-6. DfY techniques improve yield [54].

A recent trend towards a closer relationship between design, manufacturing, and test is called design for yield (DfY). A design and its layout are implemented to be insensitive to the most common manufacturing defects for a given process. Similarly, the testing strategies are devised to catch the likely defects. Critical area analyses (CAA) of layouts help to find

areas where faults are likely to occur. Parametric analysis helps designers to estimate the impact of process variation on the performance of analog circuits. A study reported by Rencher illustrates the benefits of DfY strategies. A summary of results are depicted in Figure 1-6. The yield of a product is improved significantly with the help of critical area and parametric analysis tools [37].

Testing is required to improve the quality and reliability of manufactured ICs. As devices become smaller, integration becomes higher, and economics dictate even better quality, hence testing has moved from being an afterthought of designers to a forefront issue of IC design and manufacture. High-level functional testing with a limited number of test vectors has evolved into to full defect modeling, BIST,  $I_{DDQ}$ , DfT, DfY, etc. Improved testing is increasingly critical in the race to extend Moore's Law.

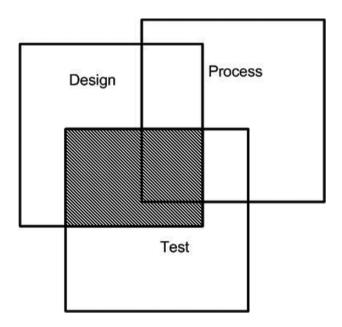

Figure 1-7. Major steps in IC realization and the focus of the book.

In modern semiconductor facilities, "closing the loop" between design and fabrication is needed to accelerate yield maturity. While in the past process control monitors (PCM) and yield engineering monitors (YEM) were primarily used for yield ramp up, the complexity of modern technologies is such that the use of this kind of monitors is not longer sufficient. Namely, results of testing actual chips are used to identify process weaknesses, and test data is used to guide in-situ failure analysis in

pinpointing the exact location of the problems. Testing plays, thus, a critical role in "closing the loop" between design and manufacturing [21].

# 5. OBJECTIVES OF THIS BOOK

Design, fabrication process and test constitute three major steps in the realization of an IC. In an idealized environment these three steps should perfectly match. For example, an ideal design realized in an ideal fabrication process environment will have 100% yield. Therefore, test in an ideal environment is redundant and not required. The real world is far from an idealized one where all these steps have a certain amount of uncertainty associated with them. Figure 1-7 symbolically illustrates the non-idealized IC realization process with the three major steps having partial overlap with each other. The partial overlap signifies an imperfect relationship amongst the steps. In other words, only a subset of fabricated ICs is defect-free and only a subset of defective ICs is caught by the test. As a result, a set of design, test, and process professionals have to make a conscious effort to strive for a near optimum relationship for better product quality and economics. For example, the test should cover all the likely defects in the design, or the design should work within the constraints of the process, or the test should incorporate the process defect information for optimum utilization of resources.

In this broad spectrum, this book focuses on the darkened area of Figure 1-7. The primary objective of the book is to make readers aware of process defects and their impact on test and quality. The target audience of this book is practicing VLSI design and test professionals. The motivation of the book comes from the fact that costs of IC testing have risen to absurd levels and are expected to rise further for SoCs. According to experts, design and test professionals have to focus on defects rather than higher level fault models to reduce the test cost while improving the quality and reliability of products. It is a daunting task given the complexity of modern ICs. Furthermore, shrinking technology makes circuits increasingly prone to defects. Millions of dollars are spent in state of the art manufacturing facilities to reduce particulate defect count (the primary cause of yield loss), defect monitoring, yield improvement, etc. Therefore, in such a scenario, knowledge of what can go wrong in a process should be advantageous to design and test professionals. This awareness can lead to robust design practices such that the probabilities of many types of defects are reduced, or alternatively their detection is simplified. Similarly, test solutions for dominant types of defects may be generated to rationalize test costs.

There are a number of defect types that may occur in a circuit and often different circuit types have to co-exist on the same die. Depending upon the circuit type (dynamic, static, digital, RAM, PLAs, or analog) defects influence the operation differently. Hence, such circuits should be addressed separately and optimum test solutions for each circuit type should be evolved. For example, certain classes of defects are not detected by logic testing, however, are readily detected by I<sub>DDQ</sub>. A good DfT scheme is the one that works within the constraints of a given circuit type. A few of these schemes are suggested in subsequent chapters and may be used to create test modes such that the defect coverage of the test is enhanced or very few tests are needed for defect detection.

Why this book? The field of defect-oriented testing is nearly two decades old. The information on defect-oriented testing is fragmented and distributed in various conference and journal papers. There is hardly any book providing a cohesive treatment this field deserves. In this book an attempt is made to bridge this gap and provide an overview of this field. Our focus in this book is to study the impact of defects on various circuit types and draw conclusions on defect detection strategies. This book does not pretend to include all the work done in this area. However, an effort is made to include the most practically relevant information in this area and present it in a readable format. The book is written keeping practical VLSI aspects in mind. The DfT strategies described in the book are realizable in CMOS technology and many have actually been implemented at Philips Semiconductors and elsewhere.

The relevance of defect-oriented testing in nano-metric regime is more than ever. Higher packing density, ever larger systems on chip configurations, increased process complexity and process spread are making designs sensitive to subtle manufacturing defects. Traditional approaches of testing are inadequate, and practicing engineers have to focus on defects in their quest to improve quality, reliability and yield of contemporary integrated circuits.

# 6. BOOK ORGANIZATION

A wealth of knowledge is available on manufacturing defects. Chapter 2 provides an overview of defects. Defects are segregated into several categories. The chapter addresses the modeling issues of defects and their circuit impact is described. Particular attention is devoted to process variability in nano-metric geometries and its impact on circuit performance. The second half of the chapter is devoted to the fundamental concepts of the

inductive fault analysis (IFA) techniques for realistic fault model development. The relationship between process deformations and IC failures is illustrated.

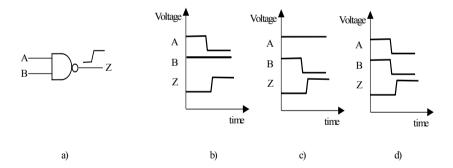

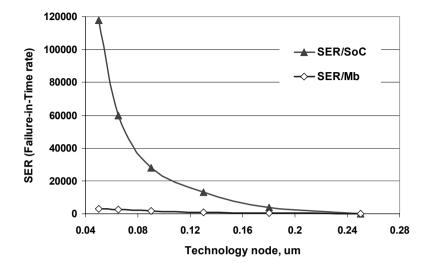

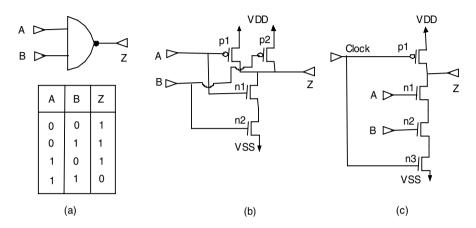

In *Chapter 3*, a review of digital fault models is provided. These fault models are classified according to the level of abstraction. The relative merits and shortcomings of these methods are also reviewed. The differences between functional and structural testing are brought out and the impracticality of functional testing for complex VLSIs is highlighted. Attention is paid on delay fault models, and temporary faults (e.g., soft errors) which are becoming prominent in nano-metric technologies.

"How do different models fare in real life?" is the focus of Chapter 4. This chapter provides a summary of some of the important studies conducted on defect-oriented testing in the last two decades. The earlier work on defects in simple NMOS and CMOS logic circuits is studied. Early studies on the effectiveness of the stuck-at (SA) fault model in detecting defects in CMOS circuits are discussed and their conclusions are summarized. Work on Maly et. al., on the effectiveness of IFA is highlighted and the pioneering work on gate oxide defects and its impact on IC quality and reliability by Hawkins and Soden is presented. Often such defects are not detected by voltage testing and I<sub>DDQ</sub> measurements are needed to detect them. Subsequently, the studies on Boolean and I<sub>DDQ</sub> testing are described and important conclusions are noted. Enhanced leakage current and delay effects of realistic defects in CMOS circuits are illustrated. Finally, how IFA is being used in nano-metric technologies described. It is worth noting that researchers have analyzed Pentium microprocessor using IFA tools.

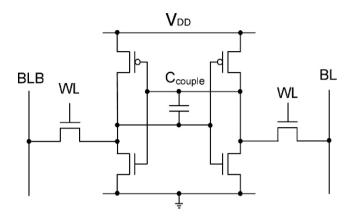

Random access memories (RAMs) are integral parts of modern ICs as well as systems. Proliferation of microprocessor, DSP, and micro-controller based systems require a large amount of embedded and dedicated RAMs. As far as their testing is concerned, RAMs suffer from quantitative issues of digital testing as well as qualitative issues of analog testing. In *Chapter 5*, we address the application of defect-oriented test method to RAMs. The application of this method results in efficient algorithms whose effectiveness is demonstrated with silicon test data. Particular attention is paid on address decoder defects and stability faults in SRAMs. The latter is becoming a growing concern with technology scaling. Transistors in SRAM cells are susceptible to process variations owing to their small geometries. Traditional test approaches are unlikely to detect such parametric failures. In this chapter, causes of poor SRAM stability due to process and manufacturing defects and circuit techniques to test them are described.

In *Chapter 6*, the defect-oriented test methodology is applied to find non-specification based analog test methods. Owing to the non-binary nature of their operation, analog circuits are influenced by process defects in a different manner than digital circuits. In this chapter, we demonstrate with the help of real CMOS circuits that simple test stimuli, like DC, transient, and AC can detect most of the modeled process defects. This test methodology is structured and simpler, and therefore results in substantial test cost reduction. Furthermore, we tackle the issue of analog fault grading. The quality of the test, and hence the tested device, depends heavily on the defect (fault) coverage of the test vectors. Therefore, it is of vital importance to quantify the fault coverage. We demonstrate how the IFA technique can be exploited to fault grade given (conventional) test vectors. Once, the relative fault coverage of different blocks is known for given test vectors, an appropriate DfT scheme can be applied to the areas where fault coverage of existing test methods is relatively poor.

Chapter 7 discusses issues related to manufacturing yield. Manufacturing of integrated circuit is extremely expensive venture where manufacturing yield plays a crucial role. Manufacturing defects and its knowledge is important to yield ramp up and yield improvement.

Finally, in *Chapter 8* conclusions on defect-oriented testing are given. Its advantages and limitations are outlined. Some potential research directions are recommended

#### References

- 1. M. Abadir, and A.P. Ambler, Economics of Electronic Design, Manufacture and Test, Boston: Kluwer Academic Publishers, 1994.

- 2. V.D. Agrawal, S.C. Seth, and P. Agrawal, "Fault Coverage Requirement in Production Testing of LSI Circuits", IEEE Journal of Solid State Circuits, vol. SC-17, no.1, pp. 57–61, February 1982.

- 3. A.P. Ambler, M. Abadir, and S. Sastry, Economics of Design and Test for Electronic Circuits and Systems, New York: Ellis Horwood, 1992.

- 4. K. Baker, "QTAG: A Standard for Test Fixture Based I<sub>DDQ</sub>/I<sub>SSQ</sub> Monitors," Proceedings of the IEEE International Test Conference, pp. 194–202, 1992.

- 5. G. Baccarani, M.R. Wordeman, and R.H. Dennard, "Generalized Scaling Theory and its Application to a ¼ micrometer MOSFET design," IEEE Transactions on Electron Devices, vol. ED-31, pp. 452–462, Apr. 1984.

- 6. J. Bardeen, and W. Brattain, "The Transistor, a Semiconductor Triode," Phys. Rev., vol. 74, pp. 230, Jul. 1948.

- 7. S.D. Brown, Field-Programmable Devices: Technology, Applications, Tools, 2nd Edition, Los Gatos: Stan Baker Associates, 1995.

1. Introduction 19

8. C. Dislis, J.H. Dick, I.D. Dear, and A.P. Ambler, Test Economics and Design For Testability, New York: Ellis Horward, 1995.

- 9. D.L. Crook, "Evolution of VLSI Reliability Engineering," Proceedings of the IEEE International Reliability Physics Symposium, pp. 2–11, 1990.

- R.H. Dennard, F.H. Gaensslen, H.N. Yu, V.L. Rideout, E. Bassous, and A.R. Leblanc, "Design of ion-implanted MOSFETs with very small physical dimensions," IEEE Journal of Solid State Circuits, vol. SC-9, pp. 256–268, Oct. 1974.

- 11. F.J. Ferguson, and J.P. Shen, "Extraction and Simulation of Realistic CMOS Faults using Inductive Fault Analysis," Proceedings of the IEEE International Test Conference, pp. 475–484, 1988.

- 12. A.V. Ferris-Prabhu, "Computation of the critical area in semiconductor yield theory," Proceedings of the European Conference on Electronic Design Automation, pp.171–173, 1984.

- D.J. Frank, R.H. Dennard, E. Nowak, P.M. Solomon, Y. Taur, and H.P. Wong, "Device Scaling Limits of Si MOSFET and Their Application Dependencies," Proceedings of the IEEE, vol. 89, no. 3, Mar. 2001.

- 14. C. Hawkins, and J. Soden, "Reliability and Electrical Properties of Gate Oxide Shorts in CMOS ICs," Proceedings of the IEEE International Test Conference, pp. 443–451, 1986.

- 15. E.R. Hnatek, "IC Quality Where Are We?" Proceedings of the IEEE International Test Conference, pp. 430–445, 1987.

- 16. E.R. Hnatek, Integrated Circuits Quality and Reliability 2nd Edition, New York: Marcel Dekker, Inc., 1995.

- R. Gayle, "The Cost of Quality: Reducing ASIC Defects with I<sub>DDQ</sub>, At-Speed Testing and Increased Fault Coverage," Proceedings of the IEEE International Test Conference, pp. 285–292, 1993.

- 18. J. Geerlings, E. Desmicht, and H. de Perthuis, "A single-chip MPEG2 CODEC for DVD+RW", IEEE International Solid-State Circuits Conference, vol. 1, pp. 40–41, 2003.

- R. Gulati, and C. Hawkins, I<sub>DDQ</sub> Testing of VLSI Circuits, Boston: Kluwer Academic Publishers, 1993.

- 20. O. Heil, "Improvements in or relating to electrical amplifiers and other control arrangements and devices", British Patent no. 439,457, 1935.

- C. Hora, R. Segers, S. Eichenberger, M. Lousberg, "An effective Diagnosis Method to Support Yield Improvement," Int. Test Conference, pp. 260–269, Oct. 2002

- 22. International Technology Roadmap for Semiconductors [Online], Available: http://public.itrs.net.

- 23. M. Inoue, T. Yamada, and A. Fujiwara, "A New Testing Acceleration Chip for Low-Cost Memory Test," IEEE Design and Test of Computers, vol. 10, pp. 15–19, Mar. 1993.

- 24. J. Khare, and W. Maly, From Contamination to Defects, Faults and Yield Loss, Boston: Kluwer Academic Publishers, 1996.

- 25. J. Kilby, "Semiconductor Device-and-Lead Structure," U.S. Patent no. 2,981,877, 1959.

- J. P. M. van Lammeren, "I<sub>CCQ</sub>: A Test Method for Analogue VLSI Based on Current Monitoring," IEEE International Workshop on I<sub>DDQ</sub> Testing, pp. 24– 28, 1997.

- 27. J. E. Lilenfeld, "Method and apparatus for controlling electric currents", U.S. Patent no. 1,745,175, 1926.

- P. Maxwell, P. O'Neill, R. Aitken, R. Dudley, N. Jaarsma, M. Quach, D. Wiseman, "Current ratios: a self-scaling technique for production I<sub>DDQ</sub> testing," Proceedings of the IEEE International Test Conference, pp. 1148–1156, 2000.

- P. Mazumder, and K. Chakraborty, Testing and Testable Design of High-Density Random-Access Memories, Boston: Kluwer Academic Publishers, 1996.

- 30. S. D. McEuen, "I<sub>DDQ</sub> Benefits," Proceedings of the IEEE VLSI Test Symposium, pp. 285–290, 1991.

- 31. E.J. McCluskey, and F. Buelow, "IC Quality and Test Transparency," Proceedings of the IEEE International Test Conference, pp. 295–301, 1988.

- 32. A. C. Miller, "I<sub>DDQ</sub> Testing in Deep Submicron Integrated Circuits," Proceedings of the IEEE International Test Conference, pp. 724–729, 1999.

- 33. G. Moore, "Cramming More Components into Integrated Circuits," Electronics, vol. 38, no. 8, Apr. 1965.

- 34. B. Mustafa Pulat, and L. M. Streb, "Position of Component Testing in Total Quality Management (TQM)," Proceedings of the IEEE International Test Conference, pp. 362–366, 1992.

- 35. R. Perry, "I<sub>DDQ</sub> testing in CMOS digital ASICs," Journal of Electronic Testing: Theory and Applications, vol. 3, pp. 317–325, Nov. 1992.

- 36. J. Rajski, "DFT technology for low cost IC manufacture test", Electronic Engineering Design, pp. 21, Jun. 2002.

- 37. M. Rencher, "Yields can be improved via design techniques", EE Times special publication: "What's Yield Got To Do With IC Design?," 2003.

- 38. J. Roberts, and S. Burke, "Intel to take \$475M charge to cover costs in Pentium recall", Computer Reseller News, iss. 614, pp. 135, Jan. 1995.

- 39. M. Sachdev, "A Defect Oriented Testability Methodology for Analog Circuits," Journal of Electronic Testing: Theory and Applications, vol. 6, no. 3, pp. 265–276, Jun. 1995.

1. Introduction 21

M. Sachdev, "Reducing the CMOS RAM Test Complexity with I<sub>DDQ</sub> and Voltage Testing," Journal of Electronic Testing: Theory and Applications, vol. 6, no. 2, pp. 191–202, Apr. 1995.

- 41. M. Sachdev, "Deep Sub-micron I<sub>DDQ</sub> Testing: Issues and Solutions," Proceedings of the European Design and Test Conference, pp. 271–278, 1997.

- 42. M. Sachdev, P. Janssen, and V. Zieren, "Defect detection with transient current testing and its potential for deep sub-micron CMOS ICs," Proceedings of the IEEE International Test Conference, pp. 204–213, 1998.

- 43. M. Sachdev, "Current-Based Testing for Deep-Submicron VLSI", IEEE Design and Test of Computers, pp. 77–84, Mar. 2001.

- 44. A. Schafft, D. A. Baglee, and P. E. Kennedy, "Building-in Reliability: Making it Work," Proceedings of the IEEE International Reliability Physics Symposium, pp. 1–7, 1991.

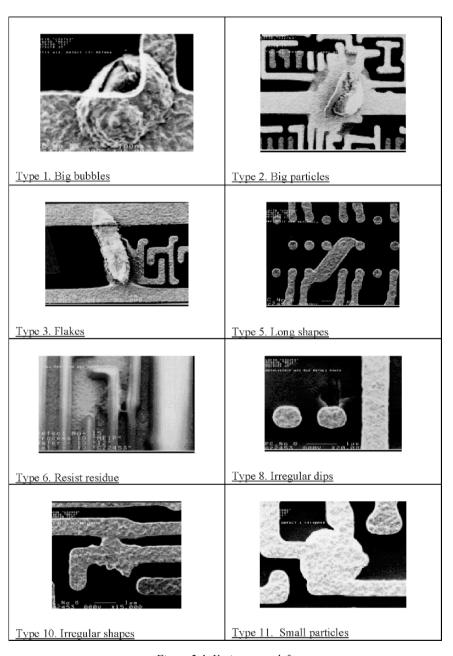

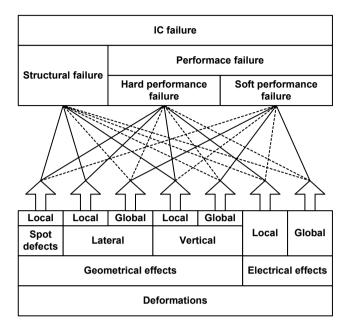

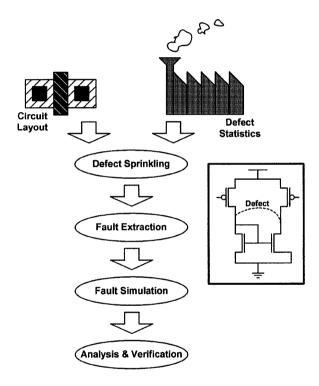

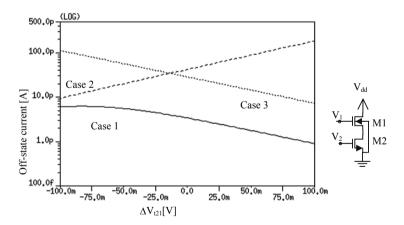

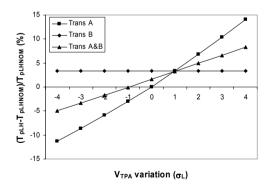

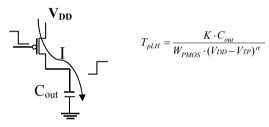

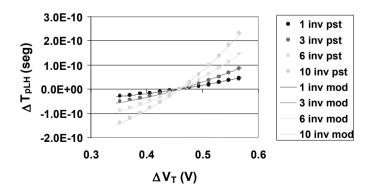

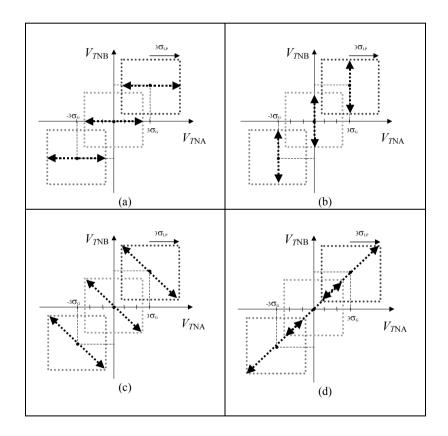

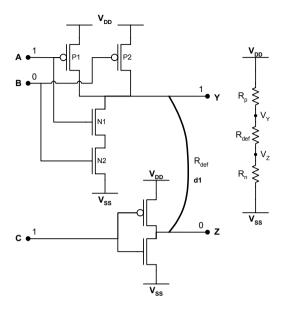

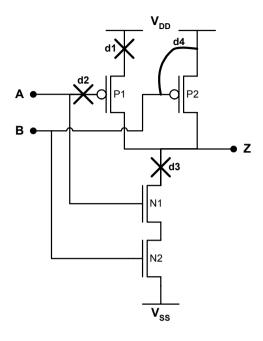

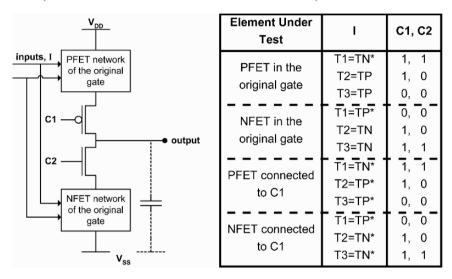

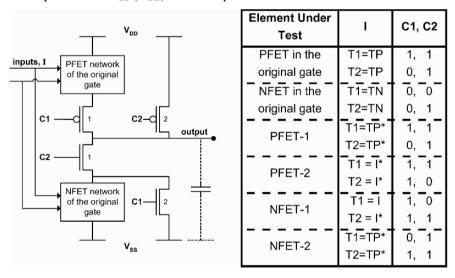

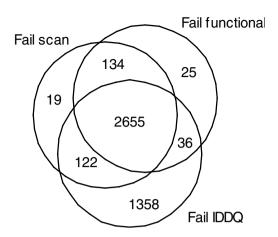

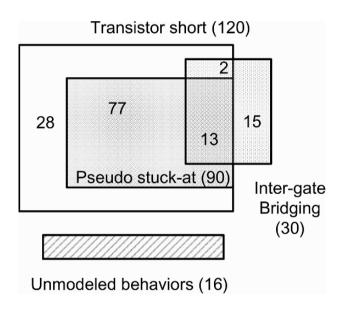

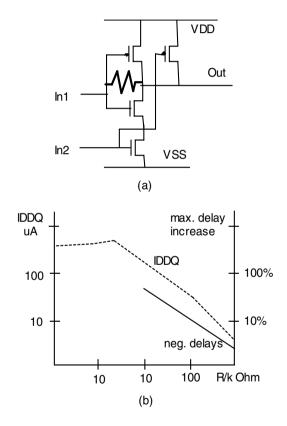

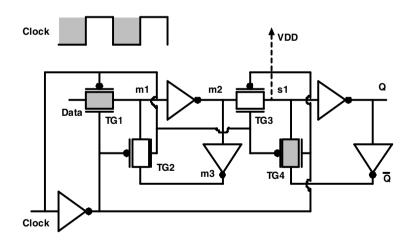

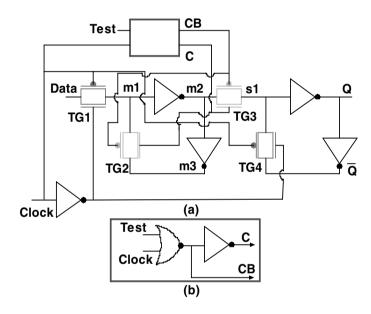

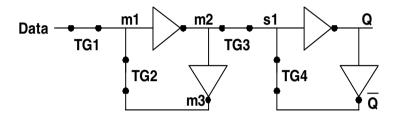

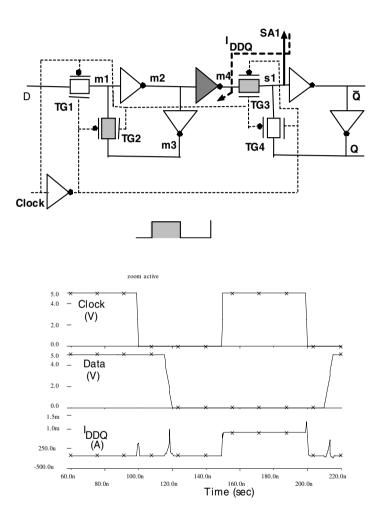

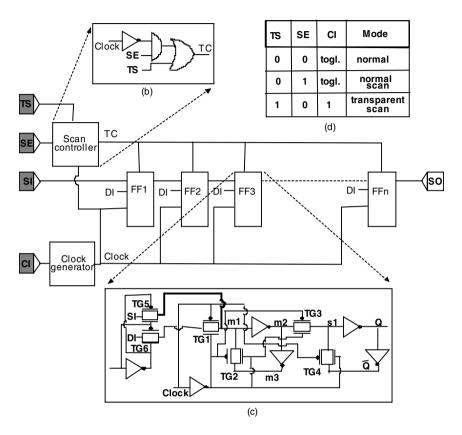

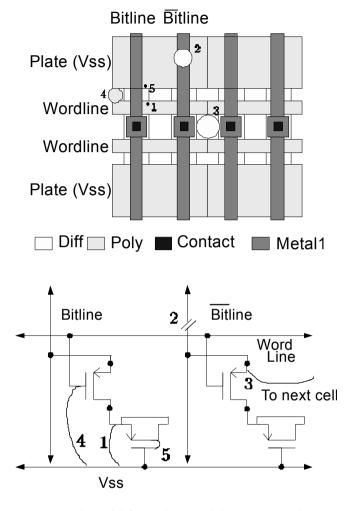

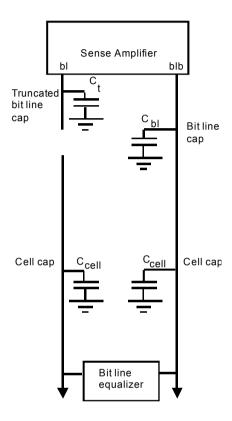

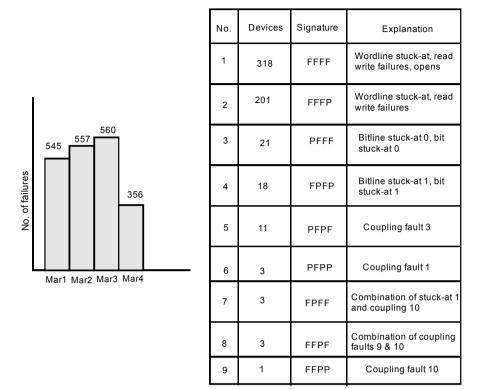

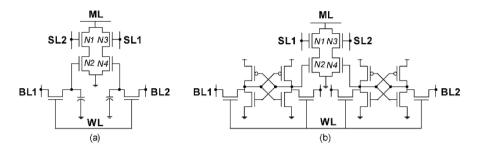

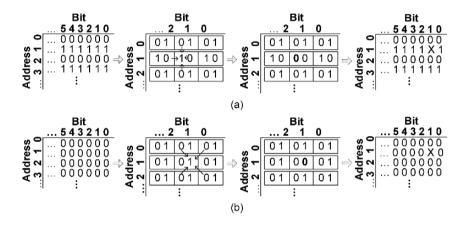

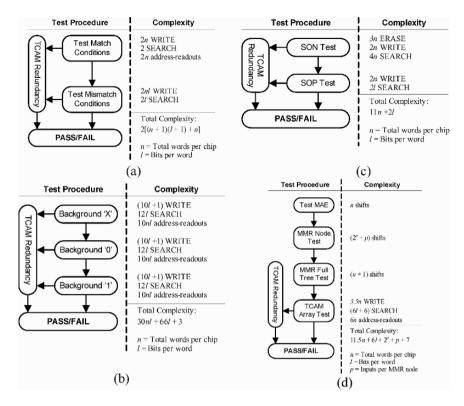

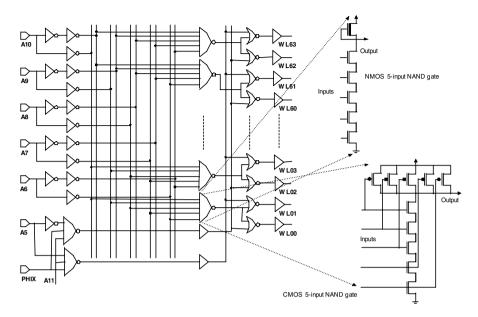

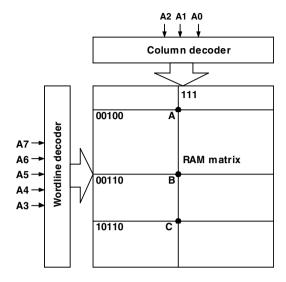

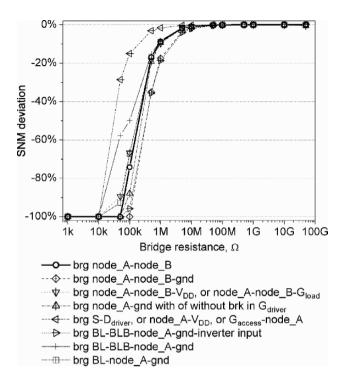

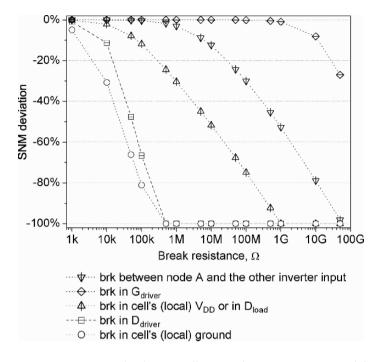

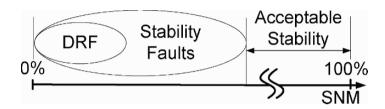

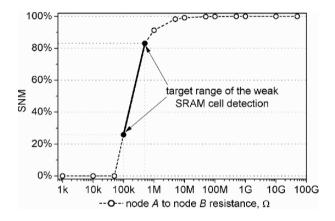

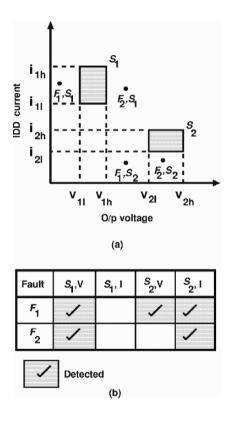

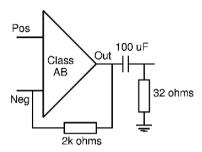

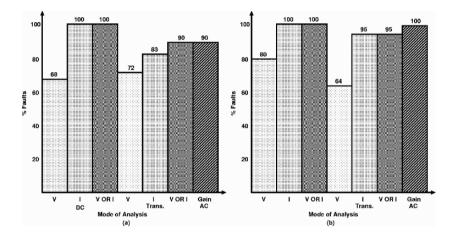

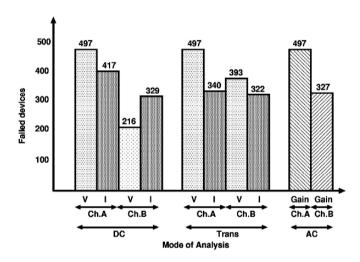

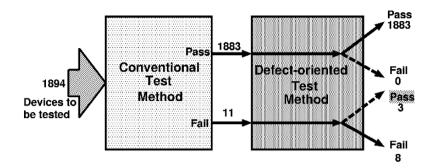

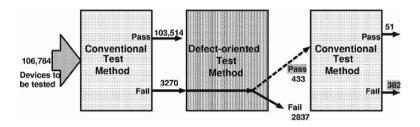

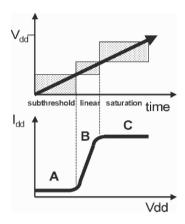

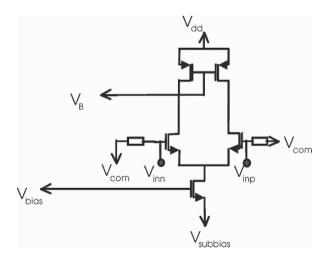

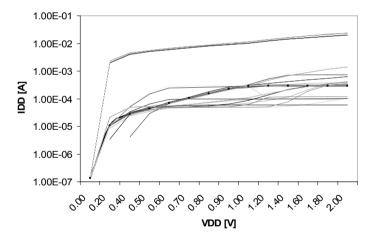

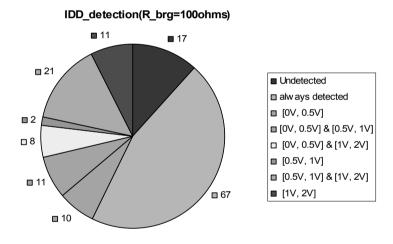

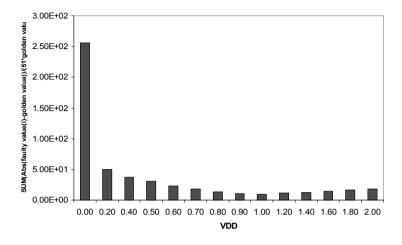

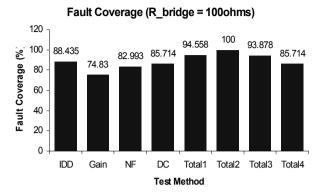

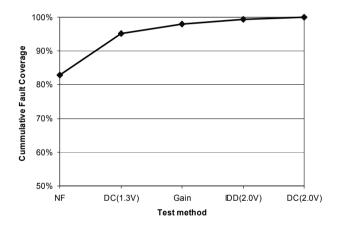

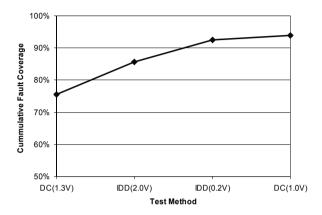

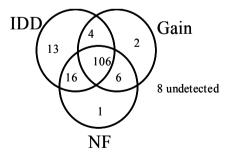

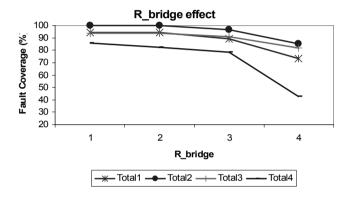

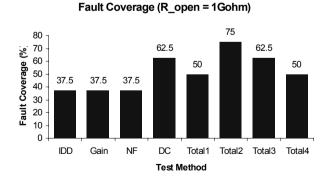

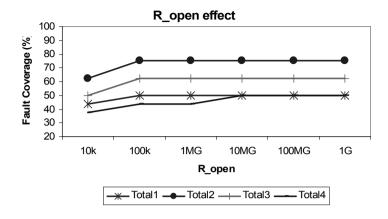

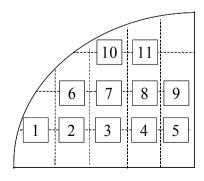

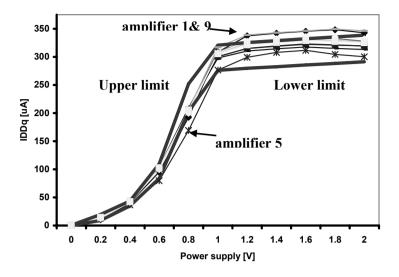

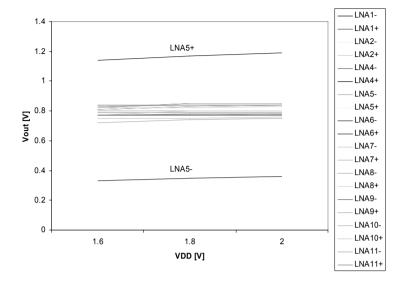

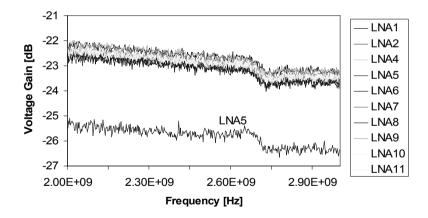

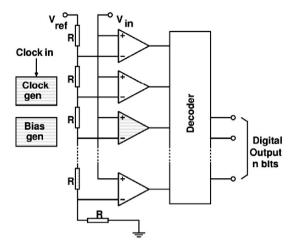

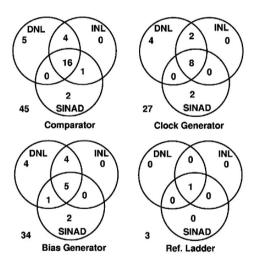

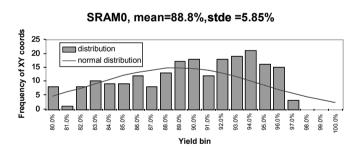

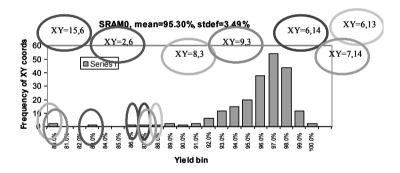

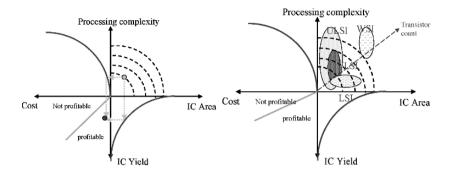

- 45. W. Schockley, "The Theory of pn-junction in Semiconductors and pn-junction Transistors," BSTJ, vol. 28, p. 435, 1949.