**Power Systems**

# Krzysztof Sozański

# Digital Signal Processing in Power Electronics Control Circuits

Power Systems

For further volumes: http://www.springer.com/series/4622 Krzysztof Sozański

# Digital Signal Processing in Power Electronics Control Circuits

Krzysztof Sozański Institute of Electrical Engineering University of Zielona Góra Zielona Gora Poland

ISSN 1612-1287 ISSN 1860-4676 (electronic) ISBN 978-1-4471-5266-8 ISBN 978-1-4471-5267-5 (eBook) DOI 10.1007/978-1-4471-5267-5 Springer London Heidelberg New York Dordrecht

Library of Congress Control Number: 2013939344

© Springer-Verlag London 2013

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law. The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

This book is dedicated to my dear parents Maria and Kazimierz, and my darling children, Anna, Mateusz and Andrzej

# Preface

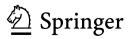

Power electronics circuits are increasingly important in the modern world due to the rapid progress in developments of microelectronics in areas such as microprocessors, digital signal processors, memory circuits, complementary metaloxidesemiconductors, analog-to-digital converters, digital-to-analog converters, and power semiconductors—especially metal–oxide–semiconductor field-effect transistors and insulated gate bipolar transistors.

Specifically, the development of power transistors has shifted the range of applications from a few amperes and hundreds of volts to several thousands of amperes and a few kilovolts, with a switching frequency measured in millions of hertz. Power electronics circuits are now used everywhere: in power systems, industry, telecommunications, transportation, commerce, etc. They even exist in such modern popular devices as digital cameras, mobile phones, and portable media players, etc. They are also used in micropower circuits, especially in energy harvesting circuits.

In the early years of power electronics, in the 1960s and 1970s, analog control circuits were most commonly used, meaning that only the simplest control algorithms could be applied. Some years later, in the 1980s and early 1990s, hybrid control circuits were used, which consisted of both analog and digital components. In subsequent years, there followed a slow transition to fully digitalized control systems, which are currently widely used and enable the application of more complex digital signal processing algorithms.

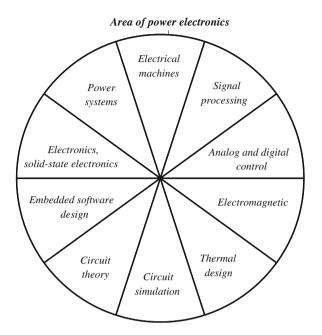

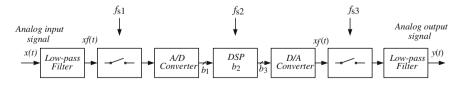

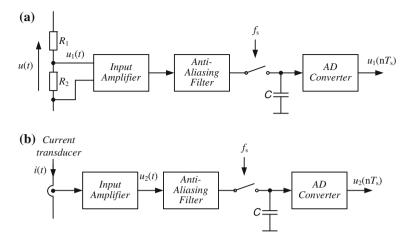

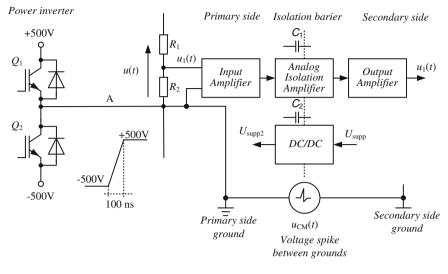

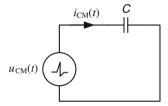

In this book, the author considers signal processing, starting from analog signal acquisition, through its conversion to digital form, methods of its filtration and separation, and ending with pulse control of output power transistors. The author has focused on two applications for the considered methods of digital signal processing: an active power filter and a digital class D power amplifier.

Both applications require precise digital control circuits with very high dynamic range of control signals. Therefore, in the author's opinion, these applications will provide very good illustrations for the considered methods. In this book, the author's original solutions for both applications are presented. In the author's opinion, the adopted solutions can also be extended to other power electronics devices.

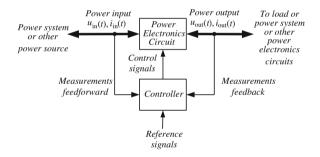

In relation to the first application-active power filters (APF)-to start with there is analysis of first harmonic detectors based on: IIR filter, wave digital filters, sliding DFT and sliding Goertzel, moving DFT. Then, there is a discussion of the author's implementation of classical control circuits based on modified instantaneous power theory. Next, the dynamics of APF is considered. Dynamic distortion of APF makes it impossible to fully compensate line harmonics. In some cases, the line current THD ratio for systems with APF compensation can reach a value of a dozen or so percent. Therefore, the author has dealt with this problem by proposing APF models suitable for analysis and simulation of this phenomena. For predictable line current changes, it is possible to develop a predictable control algorithm to eliminate APF dynamics compensation errors. In the following sections, the author's modification using a predictive circuit to eliminate dynamic compensation errors is described. In this book, control circuits with filter banks which allow the selection of compensated harmonics are described. There are considered filter banks based on: sliding DFT, sliding Goertzel, moving DFT and instantaneous power theory algorithms.

For unpredictable line current changes, the author has developed a multirate APF. The presented multirate APF has a fast response for sudden changes in the load current. So, using multirate APF, it is possible to decrease the THD ratio of line current even for unpredictable loads.

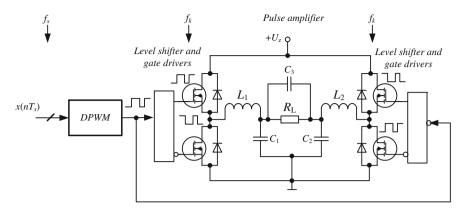

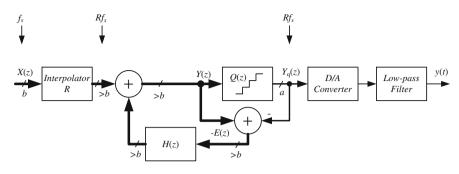

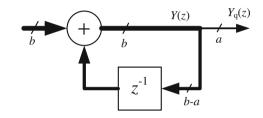

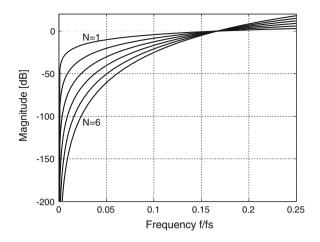

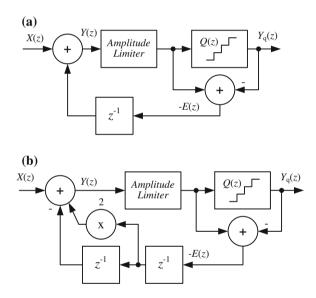

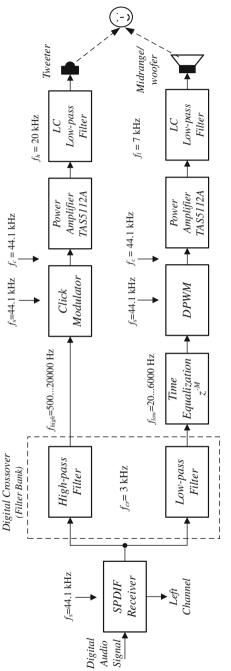

The second application is a digital class D amplifier. Both APFs and the amplifiers are especially demanding in terms of the dynamics of processed signals. However, in the case of a class D amplifier, the dynamics reaches 120 dB, which results in high requirements for the type of algorithm used and its digital realization. The author has proposed a modulator with a noise shaping circuit for a class D amplifier. Interpolators are also considered that allow for the increasing of the sampling frequency while maintaining a substantial separation of signal from noise. The author also presents an original analog power supply voltage fluctuation compensation circuit for the class D amplifier. The class D amplifier with digital click modulation is also given special consideration. Finally, two-way and three-way loudspeaker systems, designed by the author, are presented, where the signal from input to output is digitally processed.

The greater part of the presented methods and circuits is the original work of the author. Listings from Matlab or in C language are attached to some of the considered algorithms to make the application of the algorithms easier. The presented methods and circuits can be successfully applied to the whole range of power electronics circuits.

The issues concerning digital signal processing are relatively widely described in the literature. However, in the author's opinion, there are very few publications combining digital signal processing and power electronics, due to the fact that these two areas of knowledge have been developed independently over the years. The author hopes that this book will, to some extent, bridge the gap between digital signal processing and power electronics. This book may be useful for Preface

scientists and engineers who implement control circuits, as well as for students of electrical engineering courses. It may also be of some value to those who create new topologies and new power electronics circuits, giving them some insight into possible control algorithms.

Zielona Gora, Poland, December 2012

Krzysztof Sozański

# Acknowledgments

The author has written this book in his endeavor to abide by the following maxim nulla dies sine linea  $\leftrightarrow$  nie ma dnia bez kreski  $\leftrightarrow$  not a day without a line drawn. However, this is not always easily achieved.

I would also like to thank everyone who supported me during the writing of this book.

# Contents

| 1 | Intro      | oduction                                                                                                                    |

|---|------------|-----------------------------------------------------------------------------------------------------------------------------|

|   | 1.1        | Power Electronics Systems                                                                                                   |

|   | 1.2        | Digital Control Circuits for Power Electronics Systems 3                                                                    |

|   |            | 1.2.1 Analog Versus Digital Control Circuit 4                                                                               |

|   |            | 1.2.2 Causal and Noncausal Circuits                                                                                         |

|   |            | 1.2.3 LTI Discrete-Time Circuits                                                                                            |

|   |            | 1.2.4 Digital Filters 77                                                                                                    |

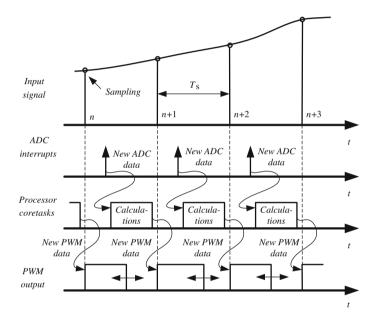

|   |            | 1.2.5 Hard Real-Time Control Systems                                                                                        |

|   |            | 1.2.6 Sampling Rate 11                                                                                                      |

|   |            | 1.2.7 Simultaneous Sampling                                                                                                 |

|   |            | 1.2.8 Number of Bits 11                                                                                                     |

|   | 1.3        | Multirate Control Circuits                                                                                                  |

|   | 1.4        | Active Power Filters 13                                                                                                     |

|   | 1.5        | Digital Class D Power Amplifiers 16                                                                                         |

|   | 1.6        | Symbols of Variables 17                                                                                                     |

|   | 1.7        | What is in This Book18                                                                                                      |

|   | Refe       | rences                                                                                                                      |

| 2 | Anal       | og Signals Conditioning and Discretization                                                                                  |

|   | 2.1        | Introduction                                                                                                                |

|   | 2.1<br>2.2 | Analog Input                                                                                                                |

|   | 2.2        | 2.2.1         Galvanic Isolation         23                                                                                 |

|   |            | 2.2.1         Galvanic Isolation         22           2.2.2         Common Mode Voltage         24                          |

|   |            | 2.2.2         Common Mode voltage         2-           2.2.3         Isolation Amplifiers         25                        |

|   | 2.3        | Current Measurements                                                                                                        |

|   | 2.3        | 2.3.1       A Resistive Shunt       30                                                                                      |

|   |            | 2.3.1       A Resistive shuft       30         2.3.2       Current Transformers       31                                    |

|   |            | 2.3.2       Current Hansformer's                                                                                            |

|   |            | 2.3.4       Current Transformer with Magnetic Modulation                                                                    |

|   |            | 2.3.4 Current Transformer with Magnetic Modulation 36<br>2.3.5 Current Transducer with Air Coil                             |

|   |            | 2.3.5       Current Hansducer with Air Cont.       30         2.3.6       Comparison of Current Sensing Techniques       38 |

|   | 2.4        | Z.5.0       Comparison of Current Sensing Techniques       36         Total Harmonic Distortion       38                    |

|   |            |                                                                                                                             |

|   | 2.5        |                                                                                                                             |

| 2.7       Noise Shaping Technique       2         2.8       Dither       2         2.9       Signal Headroom       2         2.10       Maximum Signal Frequency versus Signal       2         Acquisition Time       2         2.11       Errors in Multichannel System       2         2.12       Amplitude and Phase Errors of Sequential Sampling       4         A/D Conversion       2         2.13       Synchronization of Sampling Process       2         2.14       Sampling Clock Jitter       2         2.15       Effective Number of Bits       2         2.16       A/D Converters Suitable for Power Electronics       6         2.16.1       A/D Converter with Successive Approximation       6         2.16.2       A/D Converter with Delta Sigma Modulator       6         2.16.3       Selected Simultaneous Sampling A/D Converters       6         2.16.4       ADS8364       6       6         2.16.5       AD7608       6       6         2.16.6       ADS1278       6       6         2.16.7       TMS320F28335       6       7         References       7       7       7 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.8       Dither.       2         2.9       Signal Headroom       5         2.10       Maximum Signal Frequency versus Signal       5         2.10       Maximum Signal Frequency versus Signal       5         2.11       Errors in Multichannel System.       5         2.12       Amplitude and Phase Errors of Sequential Sampling       6         2.13       Synchronization of Sampling Process       5         2.14       Sampling Clock Jitter       5         2.15       Effective Number of Bits       6         2.16       A/D Converters Suitable for Power Electronics       6         2.16.1       A/D Converter with Successive Approximation       6         2.16.2       A/D Converter with Delta Sigma Modulator       6         2.16.3       Selected Simultaneous Sampling A/D Converters       6         2.16.4       ADS8364       6       6         2.16.5       AD7608       6       6         2.16.7       TMS320F28335       6       6         2.17       Conclusions       7                                                                                                |

| 2.10       Maximum Signal Frequency versus Signal<br>Acquisition Time       5         2.11       Errors in Multichannel System       5         2.12       Amplitude and Phase Errors of Sequential Sampling<br>A/D Conversion       5         2.13       Synchronization of Sampling Process       5         2.14       Sampling Clock Jitter       5         2.15       Effective Number of Bits       6         2.16       A/D Converters Suitable for Power Electronics       6         2.16.1       A/D Converter with Successive Approximation       6         2.16.2       A/D Converter with Delta Sigma Modulator       6         2.16.3       Selected Simultaneous Sampling A/D Converters       6         2.16.4       ADS8364       6         2.16.5       AD7608       6         2.16.7       TMS320F28335       6         2.17       Conclusions       7                                                                                                                                                                                                                                 |

| Acquisition Time       5         2.11       Errors in Multichannel System       5         2.12       Amplitude and Phase Errors of Sequential Sampling       6         A/D Conversion       5         2.13       Synchronization of Sampling Process       5         2.14       Sampling Clock Jitter       5         2.15       Effective Number of Bits       6         2.16       A/D Converters Suitable for Power Electronics       6         2.16.1       A/D Converter with Successive Approximation       6         2.16.2       A/D Converter with Delta Sigma Modulator       6         2.16.3       Selected Simultaneous Sampling A/D Converters       6         2.16.4       ADS8364       6         2.16.5       AD7608       6         2.16.7       TMS320F28335       6         2.17       Conclusions       7                                                                                                                                                                                                                                                                         |

| 2.11       Errors in Multichannel System.       5         2.12       Amplitude and Phase Errors of Sequential Sampling       6         2.13       Synchronization of Sampling Process       5         2.13       Synchronization of Sampling Process       5         2.14       Sampling Clock Jitter       5         2.15       Effective Number of Bits       6         2.16       A/D Converters Suitable for Power Electronics       6         2.16.1       A/D Converter with Successive Approximation       6         2.16.2       A/D Converter with Delta Sigma Modulator       6         2.16.3       Selected Simultaneous Sampling A/D Converters       6         2.16.4       ADS8364       6         2.16.5       AD7608       6         2.16.6       ADS1278       6         2.16.7       TMS320F28335       6         2.17       Conclusions       7                                                                                                                                                                                                                                    |

| 2.11       Errors in Multichannel System.       5         2.12       Amplitude and Phase Errors of Sequential Sampling       6         2.13       Synchronization of Sampling Process       5         2.13       Synchronization of Sampling Process       5         2.14       Sampling Clock Jitter       5         2.15       Effective Number of Bits       6         2.16       A/D Converters Suitable for Power Electronics       6         2.16.1       A/D Converter with Successive Approximation       6         2.16.2       A/D Converter with Delta Sigma Modulator       6         2.16.3       Selected Simultaneous Sampling A/D Converters       6         2.16.4       ADS8364       6         2.16.5       AD7608       6         2.16.6       ADS1278       6         2.16.7       TMS320F28335       6         2.17       Conclusions       7                                                                                                                                                                                                                                    |

| 2.12       Amplitude and Phase Errors of Sequential Sampling         A/D Conversion.       5         2.13       Synchronization of Sampling Process       5         2.14       Sampling Clock Jitter       5         2.15       Effective Number of Bits       5         2.16       A/D Converters Suitable for Power Electronics       6         2.16.1       A/D Converter with Successive Approximation       6         2.16.2       A/D Converter with Delta Sigma Modulator       6         2.16.3       Selected Simultaneous Sampling A/D Converters       6         2.16.4       ADS8364       6         2.16.5       AD7608       6         2.16.6       ADS1278       6         2.16.7       TMS320F28335       6         2.17       Conclusions       7                                                                                                                                                                                                                                                                                                                                     |

| A/D Conversion.52.13 Synchronization of Sampling Process52.14 Sampling Clock Jitter.52.15 Effective Number of Bits62.16 A/D Converters Suitable for Power ElectronicsControl Circuits.62.16.1 A/D Converter with Successive Approximation62.16.2 A/D Converter with Delta Sigma Modulator62.16.3 Selected Simultaneous Sampling A/D Converters.62.16.4 ADS836462.16.5 AD760862.16.7 TMS320F2833562.17 Conclusions.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

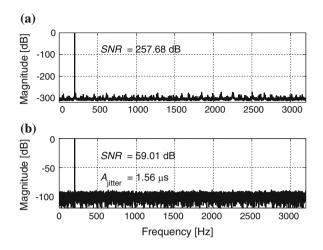

| 2.14Sampling Clock Jitter52.15Effective Number of Bits62.16A/D Converters Suitable for Power Electronics62.16.1A/D Converter with Successive Approximation62.16.2A/D Converter with Delta Sigma Modulator62.16.3Selected Simultaneous Sampling A/D Converters62.16.4ADS836462.16.5AD760862.16.6ADS127862.16.7TMS320F2833562.17Conclusions7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.14Sampling Clock Jitter52.15Effective Number of Bits62.16A/D Converters Suitable for Power Electronics62.16.1A/D Converter with Successive Approximation62.16.2A/D Converter with Delta Sigma Modulator62.16.3Selected Simultaneous Sampling A/D Converters62.16.4ADS836462.16.5AD760862.16.6ADS127862.16.7TMS320F2833562.17Conclusions7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

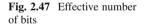

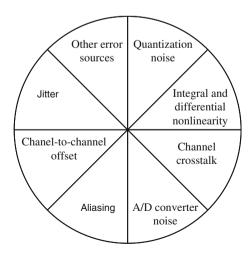

| 2.15Effective Number of Bits62.16A/D Converters Suitable for Power ElectronicsControl Circuits62.16.1A/D Converter with Successive Approximation2.16.2A/D Converter with Delta Sigma Modulator2.16.3Selected Simultaneous Sampling A/D Converters2.16.4ADS83642.16.5AD76082.16.6ADS12782.16.7TMS320F283352.17Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.16A/D Converters Suitable for Power Electronics<br>Control Circuits62.16.1A/D Converter with Successive Approximation62.16.2A/D Converter with Delta Sigma Modulator62.16.3Selected Simultaneous Sampling A/D Converters62.16.4ADS836462.16.5AD760862.16.6ADS127862.16.7TMS320F2833562.17Conclusions7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

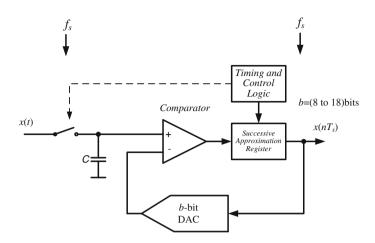

| 2.16.1       A/D Converter with Successive Approximation       6         2.16.2       A/D Converter with Delta Sigma Modulator       6         2.16.3       Selected Simultaneous Sampling A/D Converters       6         2.16.4       ADS8364       6         2.16.5       AD7608       6         2.16.6       ADS1278       6         2.16.7       TMS320F28335       6         2.17       Conclusions       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.16.1A/D Converter with Successive Approximation62.16.2A/D Converter with Delta Sigma Modulator62.16.3Selected Simultaneous Sampling A/D Converters62.16.4ADS836462.16.5AD760862.16.6ADS127862.16.7TMS320F2833562.17Conclusions7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

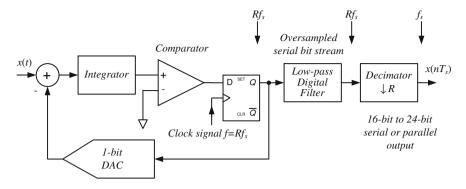

| 2.16.2       A/D Converter with Delta Sigma Modulator       6         2.16.3       Selected Simultaneous Sampling A/D Converters       6         2.16.4       ADS8364       6         2.16.5       AD7608       6         2.16.6       ADS1278       6         2.16.7       TMS320F28335       6         2.17       Conclusions       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.16.3       Selected Simultaneous Sampling A/D Converters.       6         2.16.4       ADS8364       6         2.16.5       AD7608       6         2.16.6       ADS1278       6         2.16.7       TMS320F28335       6         2.17       Conclusions       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

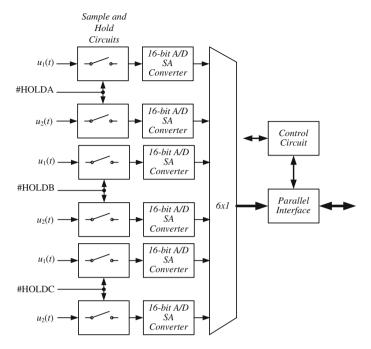

| 2.16.4       ADS8364       6         2.16.5       AD7608       6         2.16.6       ADS1278       6         2.16.7       TMS320F28335       6         2.17       Conclusions       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.16.5       AD7608       6         2.16.6       ADS1278       6         2.16.7       TMS320F28335       6         2.17       Conclusions       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

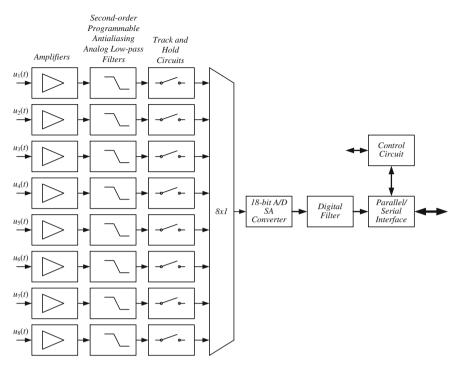

| 2.16.6       ADS1278       6         2.16.7       TMS320F28335       6         2.17       Conclusions       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.16.7       TMS320F28335       6         2.17       Conclusions       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.17 Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3 Selected Methods of Signal Filtration and Separation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| and Their Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.2 Digital Filters 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

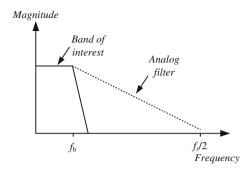

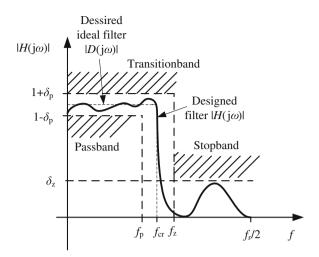

| 3.2.1 Digital Filter Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

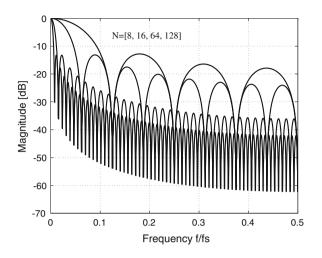

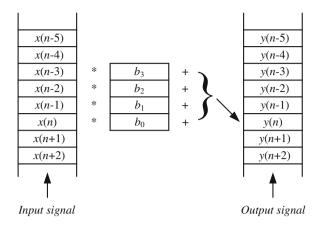

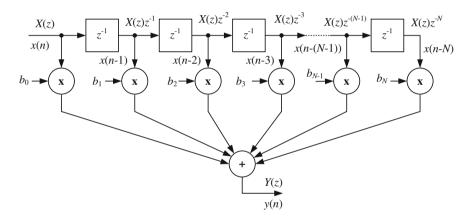

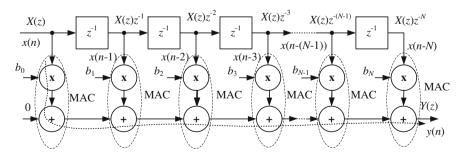

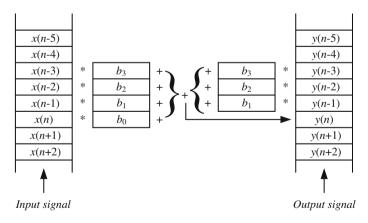

| 3.2.2 Finite Impulse Response Digital Filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

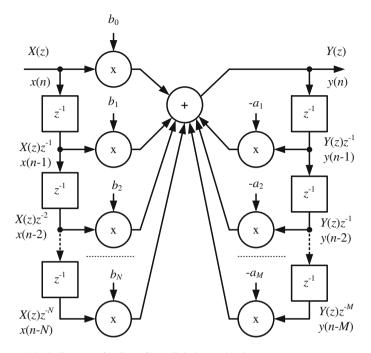

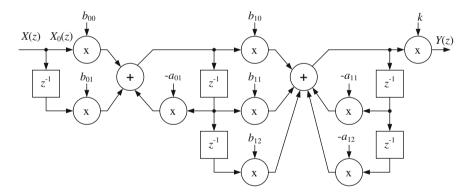

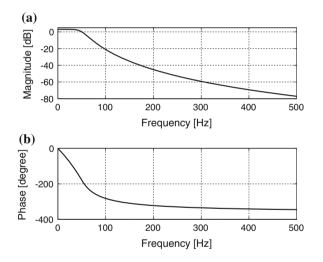

| 3.2.3 Infinite Impulse Response Digital Filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

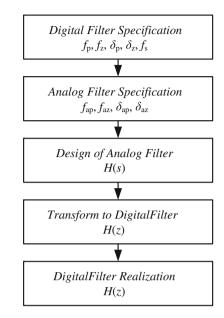

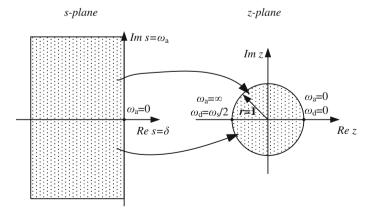

| 3.2.4 Designing of Digital IIR Filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

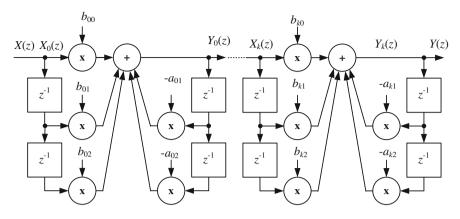

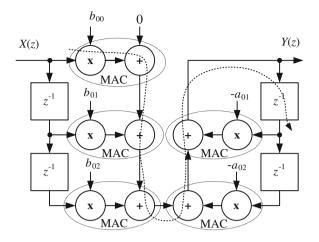

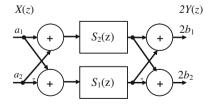

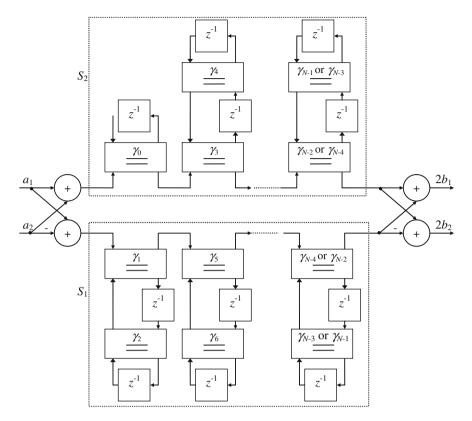

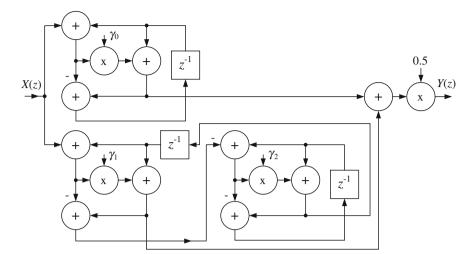

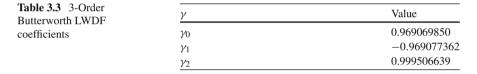

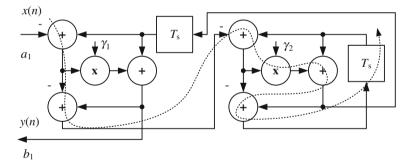

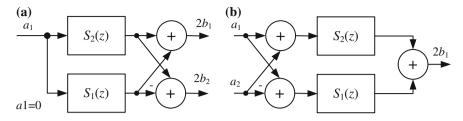

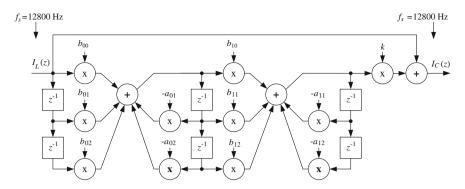

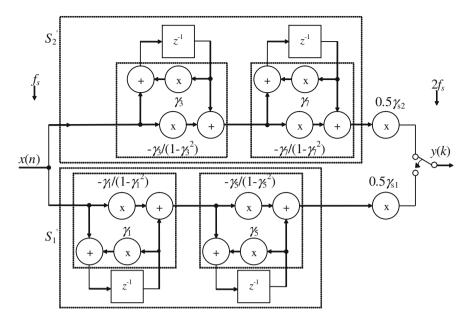

| 3.3 Lattice Wave Digital Filters 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <ul><li>3.3 Lattice Wave Digital Filters</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <ul> <li>3.3 Lattice Wave Digital Filters</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.3       Lattice Wave Digital Filters       8         3.3.1       Comparison of Classical IIR Filter and Lattice       8         Wave Digital Filter       8         3.3.2       Realization of LWDF       8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

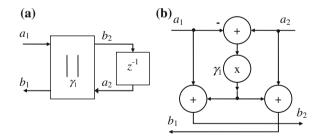

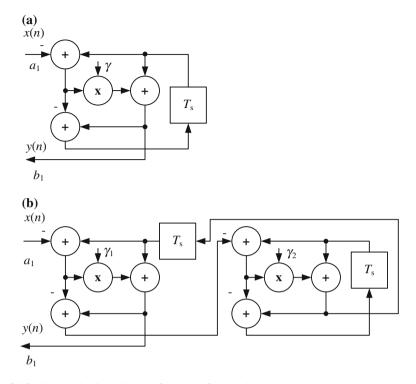

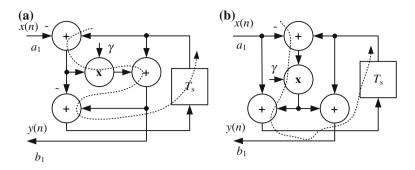

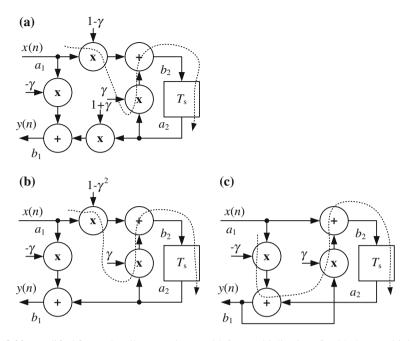

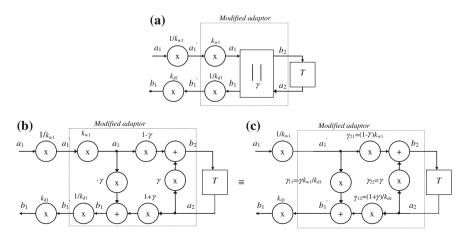

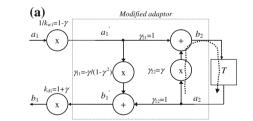

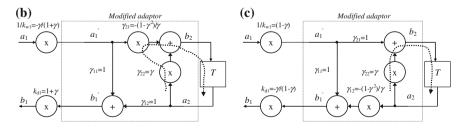

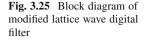

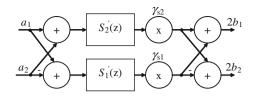

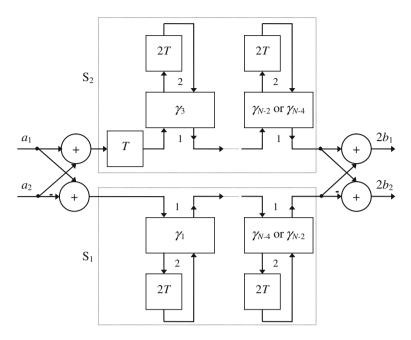

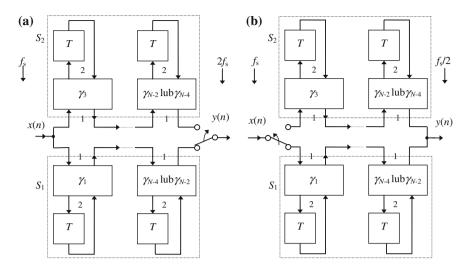

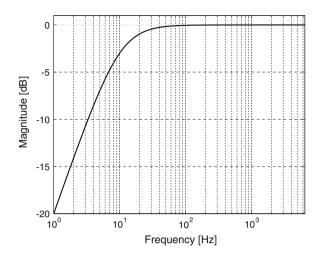

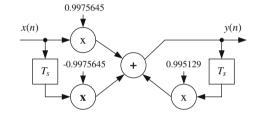

| 3.3       Lattice Wave Digital Filters       8         3.3.1       Comparison of Classical IIR Filter and Lattice       8         Wave Digital Filter       8         3.3.2       Realization of LWDF       8         3.4       Modified Lattice Wave Digital Filters       8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

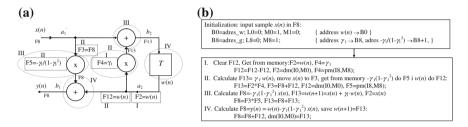

| 3.3       Lattice Wave Digital Filters       8         3.3.1       Comparison of Classical IIR Filter and Lattice       8         Wave Digital Filter       8         3.3.2       Realization of LWDF       8         3.4       Modified Lattice Wave Digital Filters       8         3.4.1       First-Order Sections       8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

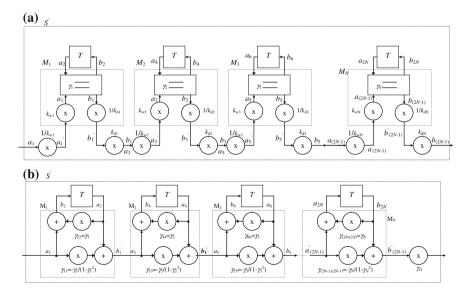

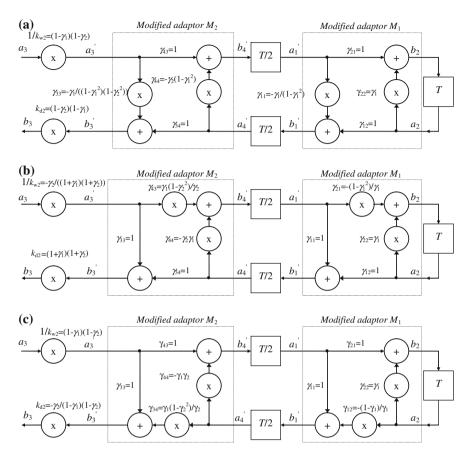

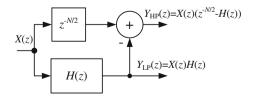

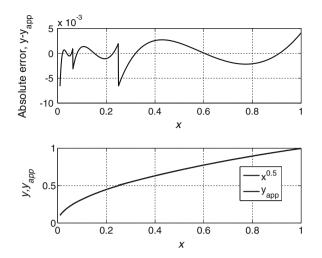

| 3.3       Lattice Wave Digital Filters       8         3.3.1       Comparison of Classical IIR Filter and Lattice       8         Wave Digital Filter       8         3.3.2       Realization of LWDF       8         3.4       Modified Lattice Wave Digital Filters       8         3.4.1       First-Order Sections       8         3.4.2       Second-Order Sections       9         3.5       Linear-Phase IIR Filters       9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

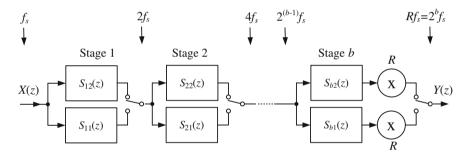

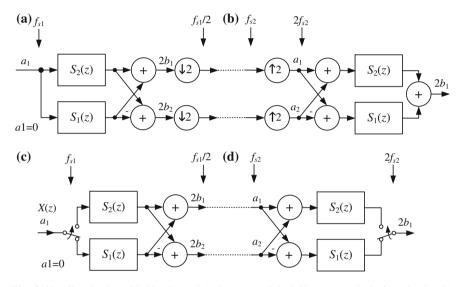

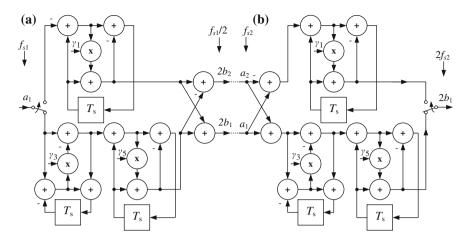

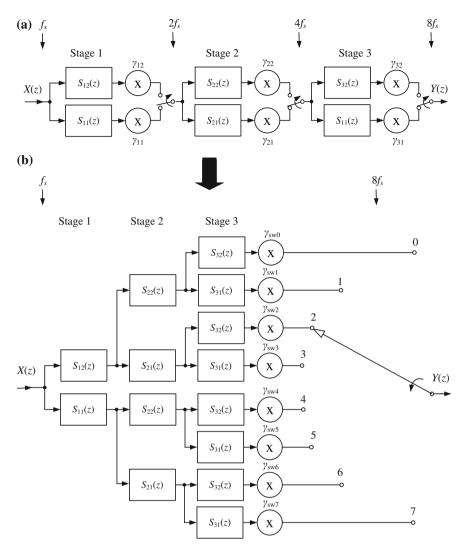

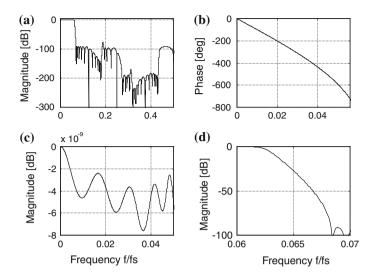

| 3.3       Lattice Wave Digital Filters       8         3.3.1       Comparison of Classical IIR Filter and Lattice       8         Wave Digital Filter       8         3.3.2       Realization of LWDF       8         3.4       Modified Lattice Wave Digital Filters       8         3.4.1       First-Order Sections       8         3.4.2       Second-Order Sections       9         3.5       Linear-Phase IIR Filters       9         3.6       Multirate Circuits       10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

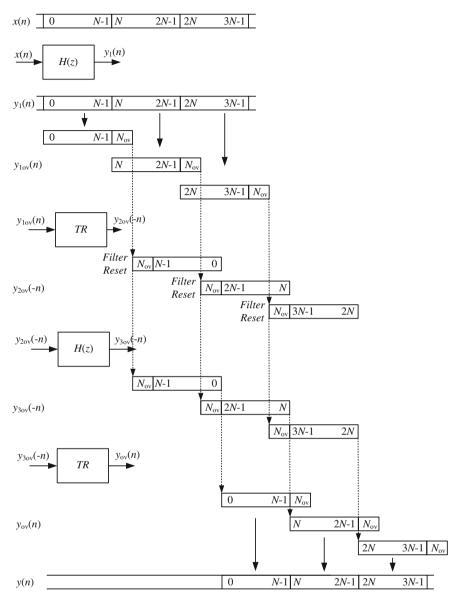

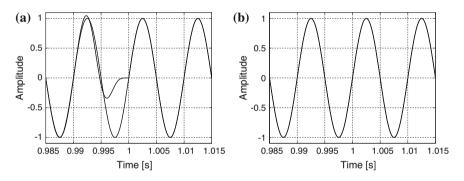

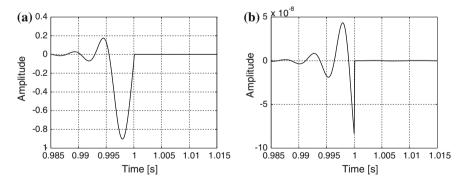

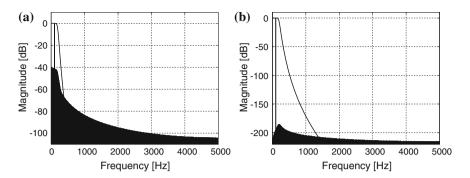

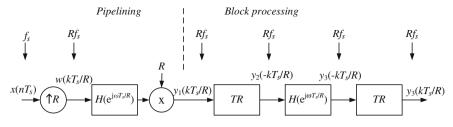

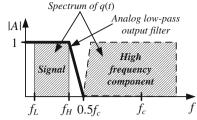

| 3.3       Lattice Wave Digital Filters       8         3.3.1       Comparison of Classical IIR Filter and Lattice       8         Wave Digital Filter       8         3.3.2       Realization of LWDF       8         3.4       Modified Lattice Wave Digital Filters       8         3.4.1       First-Order Sections       8         3.4.2       Second-Order Sections       9         3.5       Linear-Phase IIR Filters       9         3.6       Multirate Circuits       10         3.6.1       Signal Interpolation       10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.3       Lattice Wave Digital Filters       8         3.3.1       Comparison of Classical IIR Filter and Lattice       8         Wave Digital Filter       8         3.3.2       Realization of LWDF       8         3.4       Modified Lattice Wave Digital Filters       8         3.4.1       First-Order Sections       8         3.4.2       Second-Order Sections       9         3.5       Linear-Phase IIR Filters       9         3.6       Multirate Circuits       10         3.6.1       Signal Interpolation       10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

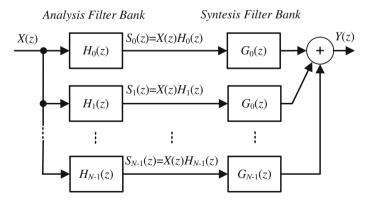

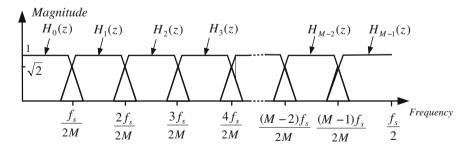

|   | 3.7   | Digital  | Filter Banks                                      | 108 |

|---|-------|----------|---------------------------------------------------|-----|

|   |       | 3.7.1    | Strictly Complementary Filter Bank                | 110 |

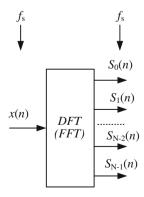

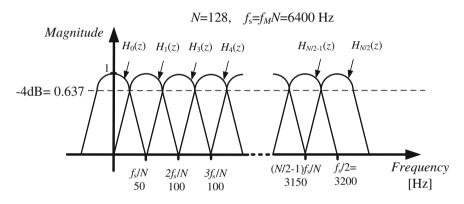

|   |       | 3.7.2    | DFT Filter Bank                                   | 112 |

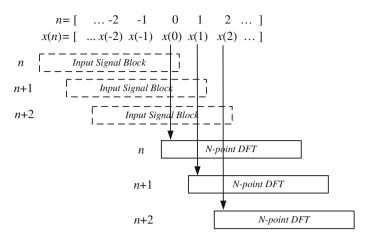

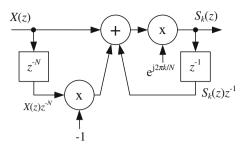

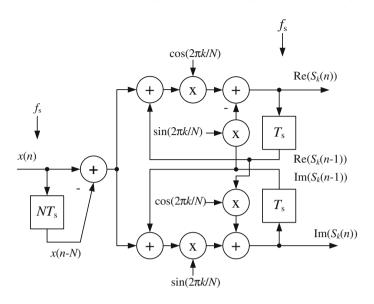

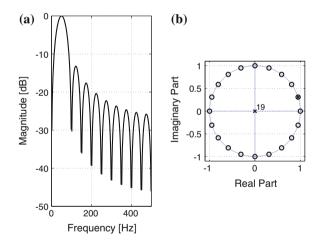

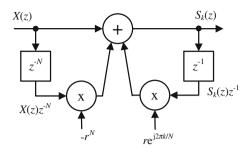

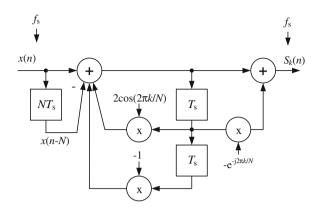

|   |       | 3.7.3    | Sliding DFT Algorithm.                            | 114 |

|   |       | 3.7.4    | Sliding Goertzel Algorithm                        | 117 |

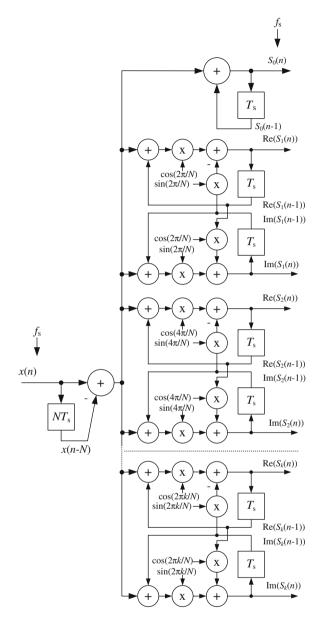

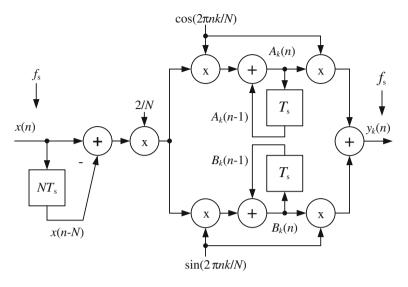

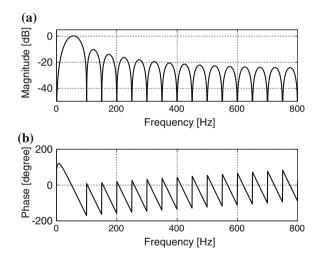

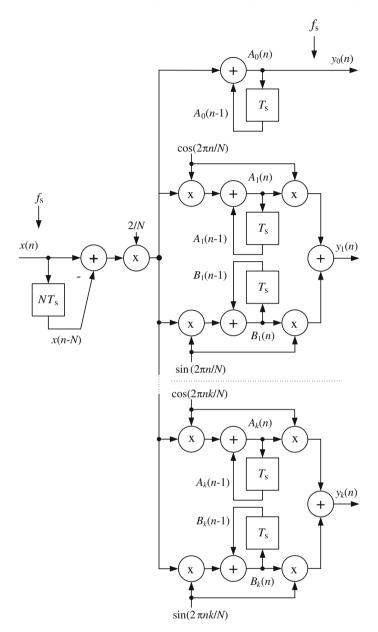

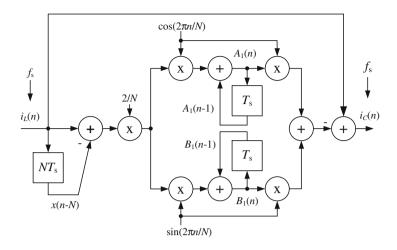

|   |       | 3.7.5    | Moving DFT Algorithm                              | 117 |

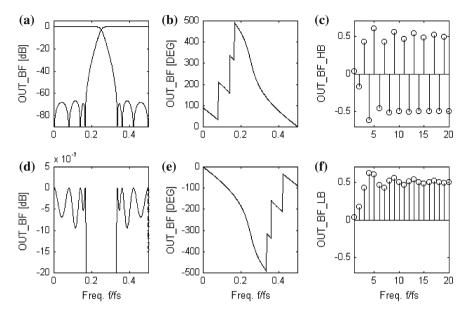

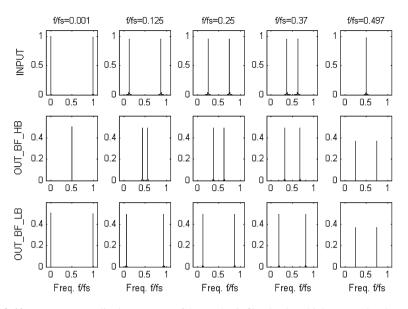

|   |       | 3.7.6    | Wave Digital Lattice Filter Bank                  | 121 |

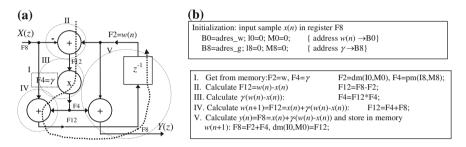

|   | 3.8   |          | nentation of Digital Signal Processing Algorithms | 126 |

|   |       | 3.8.1    | Basic Features of the DSP                         | 129 |

|   |       | 3.8.2    | Digital Signal Processors: SHARC Family           | 136 |

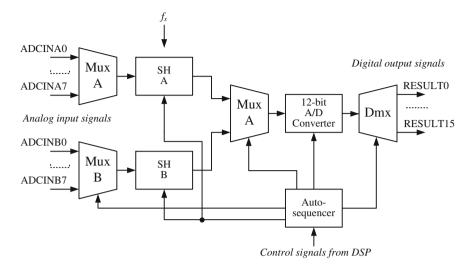

|   |       | 3.8.3    | Digital Signal Controller: TMS320F28xx Family     | 138 |

|   |       | 3.8.4    | Digital Signal Processor: TMS320C6xxx Family      | 139 |

|   | 3.9   | Conclu   | isions                                            | 140 |

|   | Refer | ences .  |                                                   | 140 |

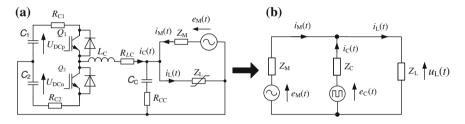

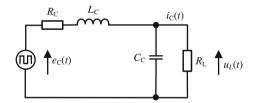

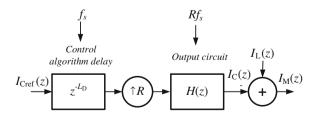

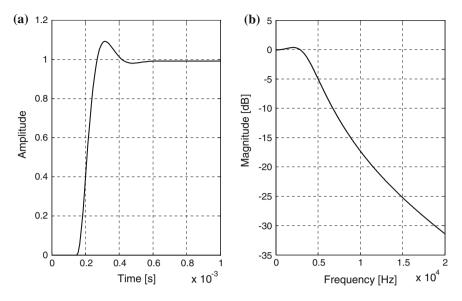

| 4 | Selec | ted Acti | ve Power Filter Control Algorithms                | 145 |

|   | 4.1   | Introdu  | uction                                            | 145 |

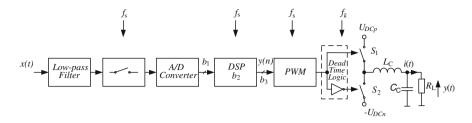

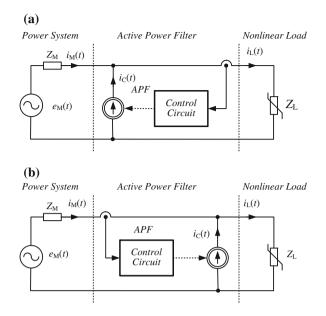

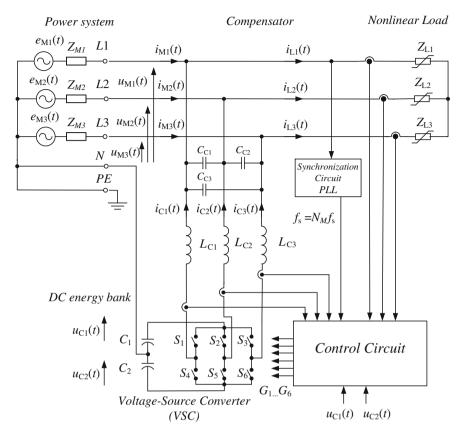

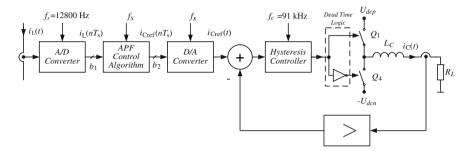

|   | 4.2   | Contro   | l Circuit of Shunt APFs                           | 146 |

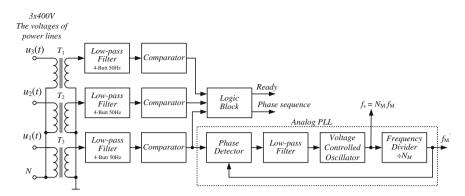

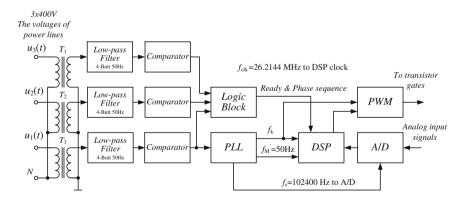

|   |       | 4.2.1    | Synchronization                                   | 147 |

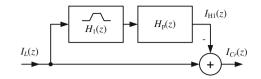

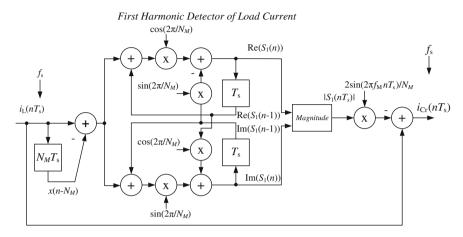

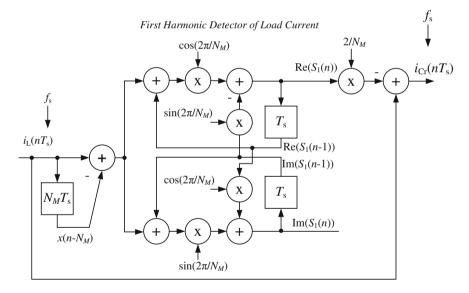

|   | 4.3   | APF C    | ontrol with First Harmonic Detector               | 150 |

|   |       | 4.3.1    | Control Circuit with Low-Pass 4-Order             |     |

|   |       |          | Butterworth Filter                                | 150 |

|   |       | 4.3.2    | Control Circuit with Low-Pass 5-Order             |     |

|   |       |          | Butterworth LWDF                                  | 154 |

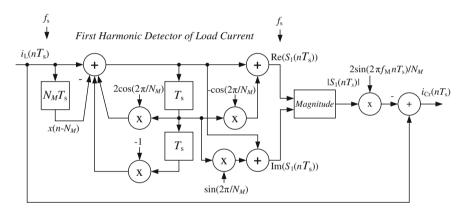

|   |       | 4.3.3    | Control Circuit with Sliding DFT                  | 154 |

|   |       | 4.3.4    | Control Circuit with Sliding Goertzel             | 157 |

|   |       | 4.3.5    | Control Circuit with Moving DFT                   | 159 |

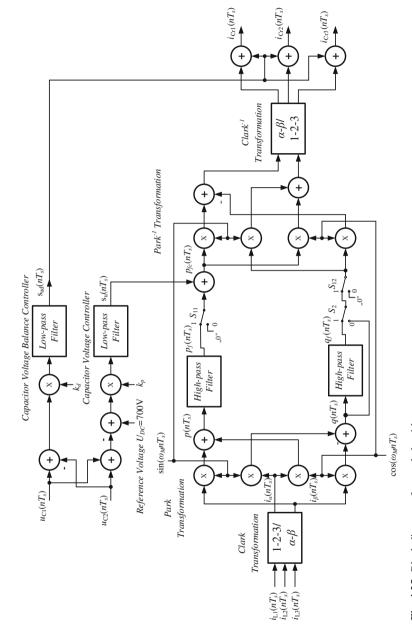

|   | 4.4   |          | - q Theory Control Algorithm for Shunt APF        | 160 |

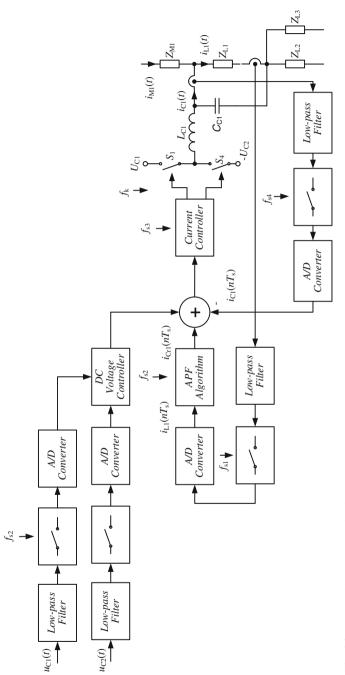

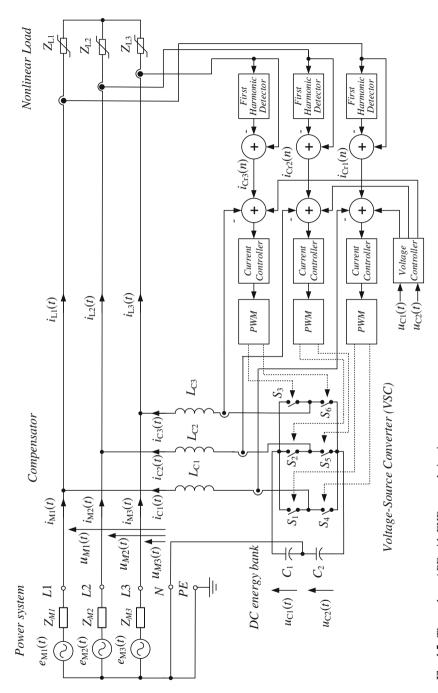

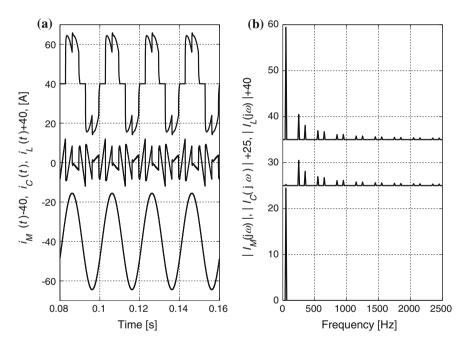

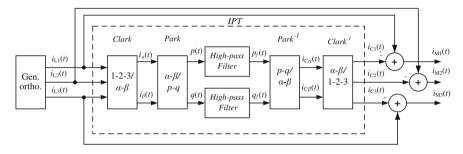

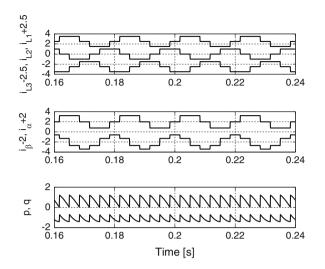

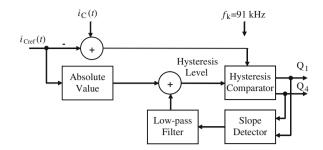

|   | 4.5   |          | APF Classical Control Circuit                     | 164 |

|   | 4.6   |          | nics of Shunt APF                                 | 171 |

|   | 4.7   |          | ds of Reducing APF Dynamic Distortion             | 176 |

|   |       | 4.7.1    | APF Output Current Ripple Calculation             | 178 |

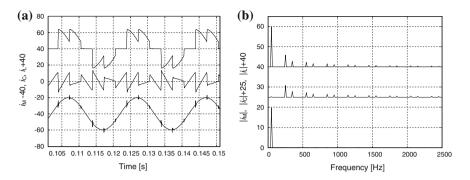

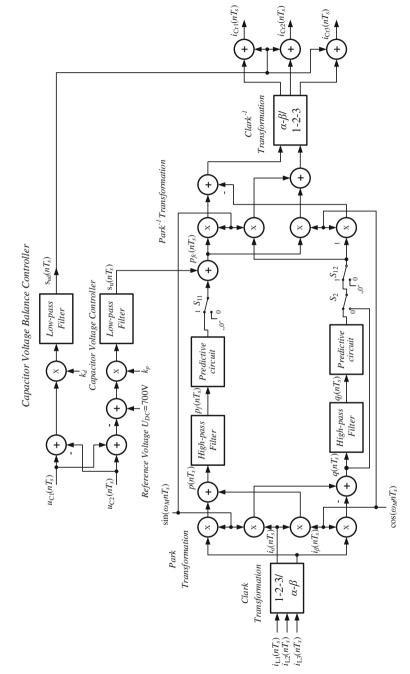

|   | 4.8   |          | ive Control Algorithm for APF                     | 180 |

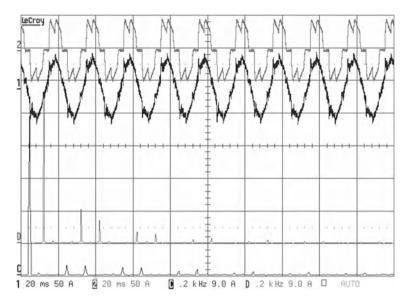

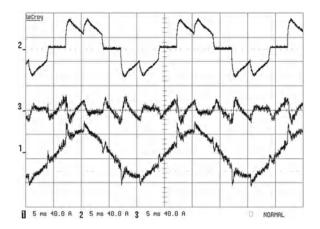

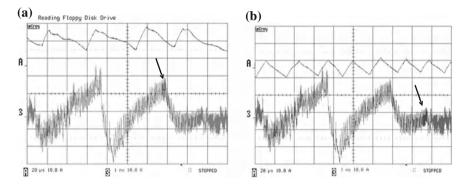

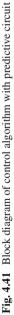

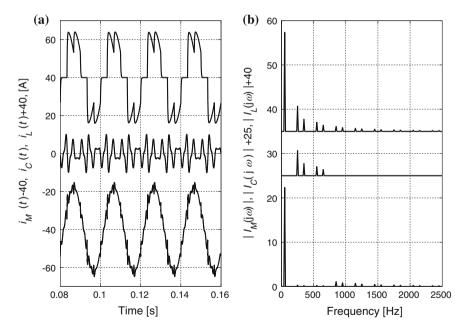

|   |       | 4.8.1    | Experimental Results                              | 181 |

|   |       | 4.8.2    | Step Response of APF                              | 184 |

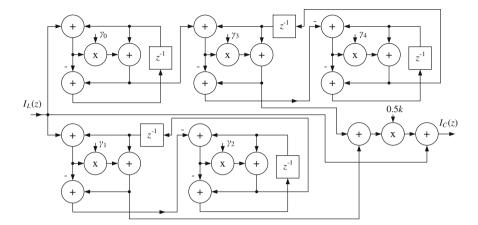

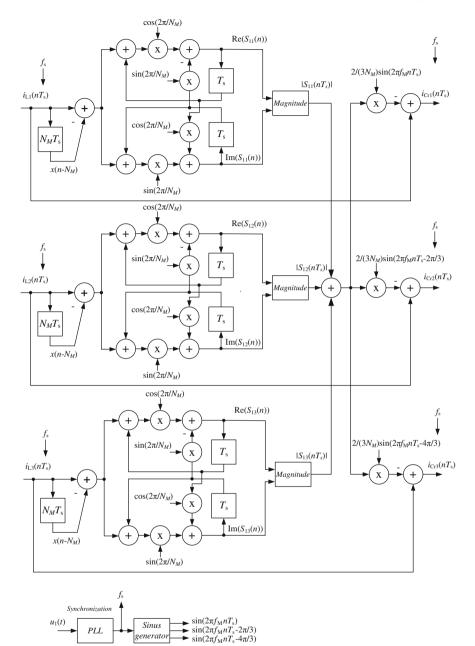

|   | 4.9   |          | ed Harmonics Separation Methods Suitable for APF  | 186 |

|   |       | 4.9.1    | Control Circuit with MDFT                         | 188 |

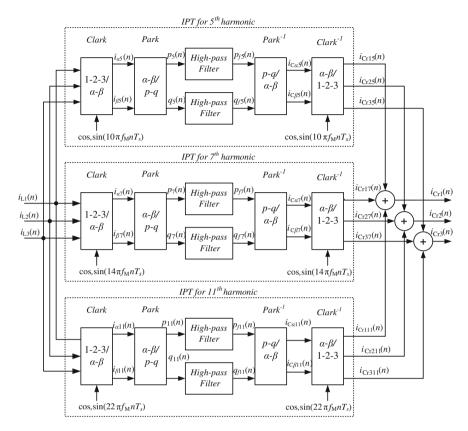

|   |       |          | Control Circuit with IPT Algorithm                | 188 |

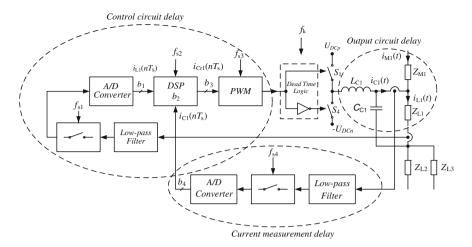

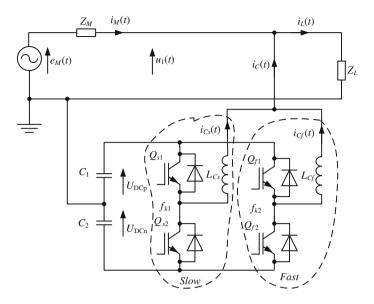

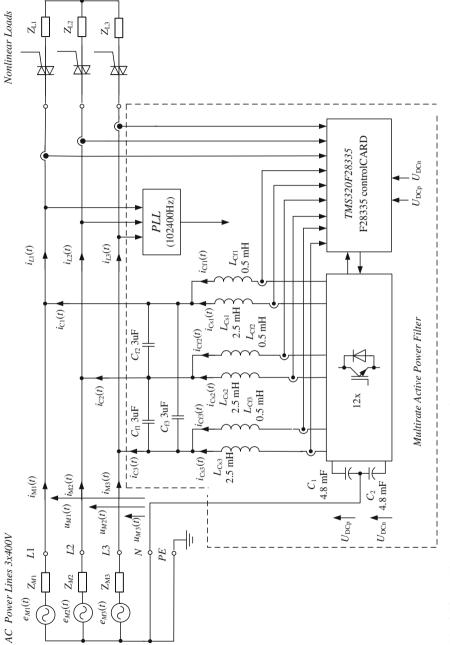

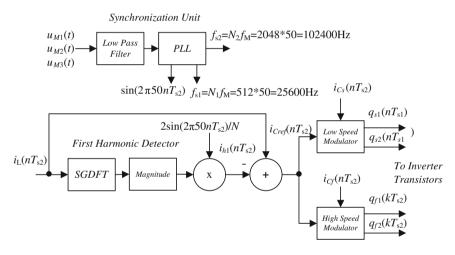

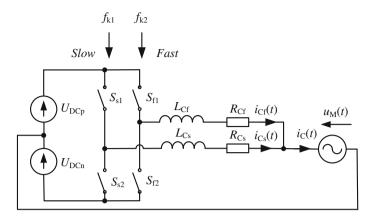

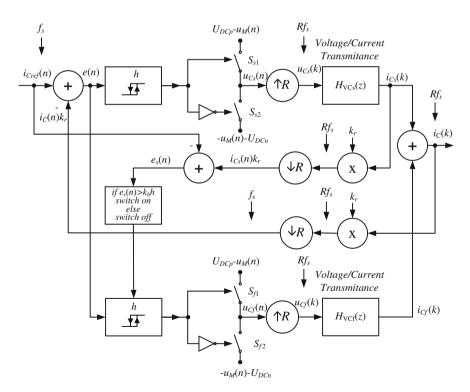

|   | 4.10  |          | ate APF                                           | 188 |

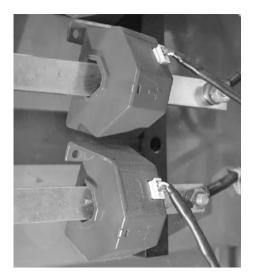

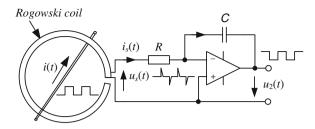

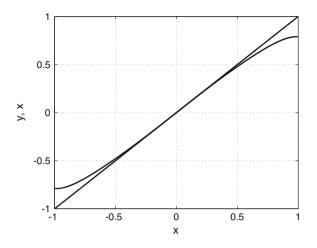

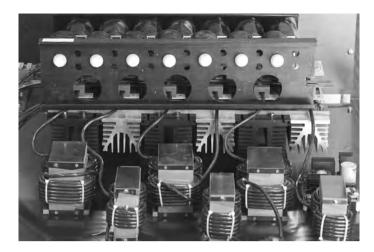

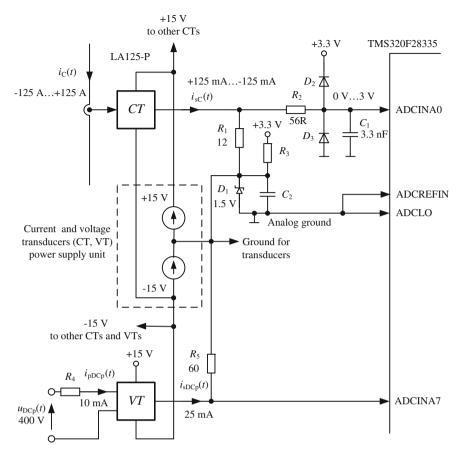

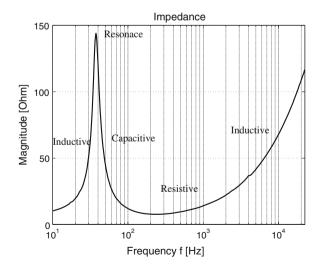

|   |       | 4.10.1   | Analog Input Circuit                              | 192 |

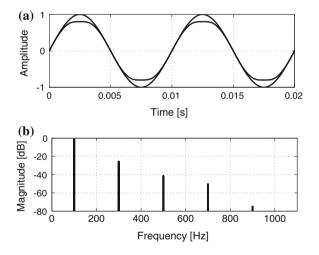

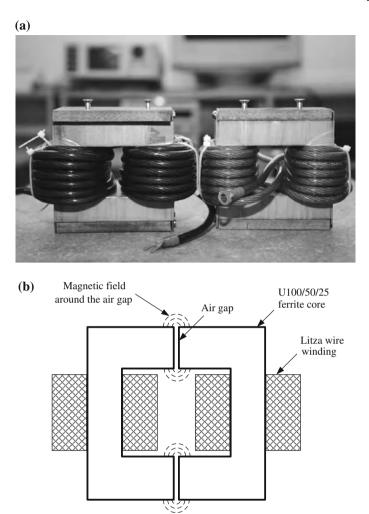

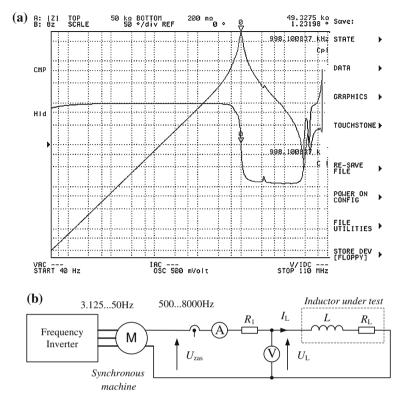

|   |       | 4.10.2   | Output Inductors                                  | 195 |

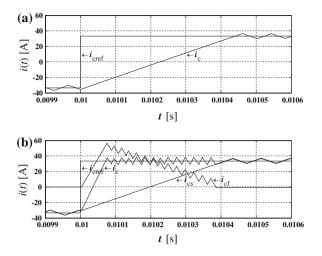

|   |       | 4.10.3   | APF Simulation Results                            | 197 |

|   | 4.11  |          | sion                                              | 201 |

|   | Refer | ences .  |                                                   | 202 |

|      |         | l Processing Circuits for Digital Class D      |

|------|---------|------------------------------------------------|

|      | -       | fiers                                          |

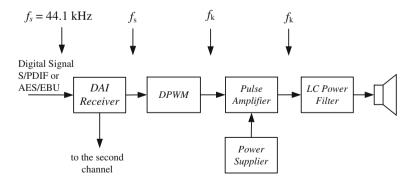

| 5.1  |         | ction                                          |

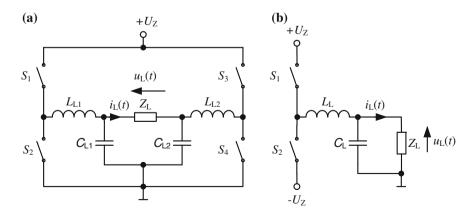

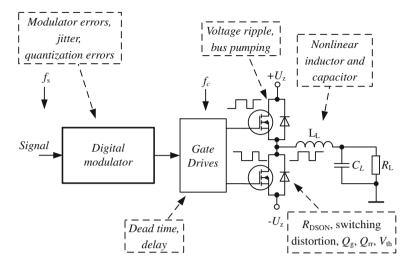

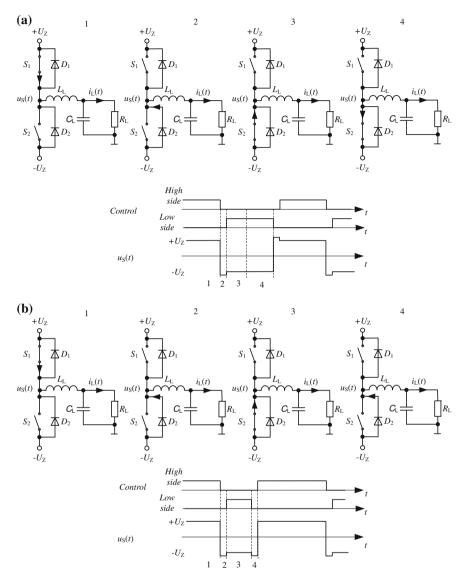

| 5.2  |         | Class D Power Amplifier Circuits               |

| 5.3  | Modula  | ators for Digital Class D Power Amplifiers     |

|      | 5.3.1   | Oversampled Pulse Width Modulator              |

| 5.4  | Basic 7 | Fopologies of Control Circuits for Digital     |

|      | Class I | O Power Amplifiers                             |

|      | 5.4.1   | Open Loop Amplifiers                           |

|      | 5.4.2   | Amplifiers with Digital Feedback               |

|      |         | for Supply Voltage                             |

|      | 5.4.3   | Amplifiers with Analog Feedback                |

|      |         | for Output Pulses                              |

|      | 5.4.4   | Amplifiers with Digital Feedback.              |

| 5.5  | Supply  | Units for Class D Power Amplifiers             |

| 5.6  | Click M | Aodulation                                     |

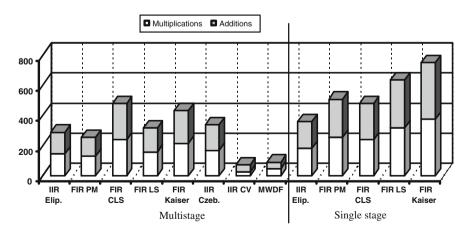

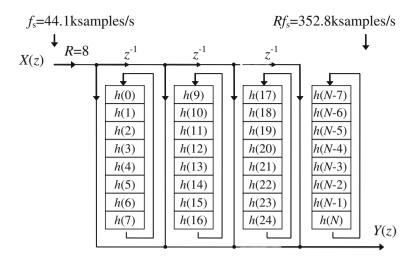

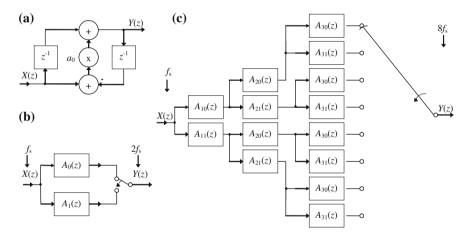

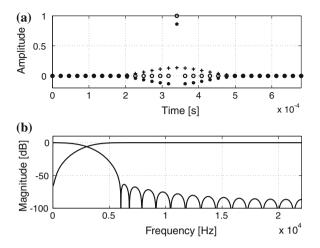

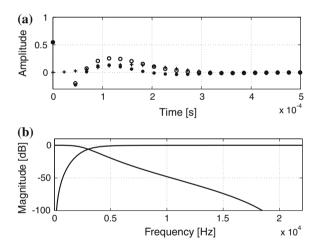

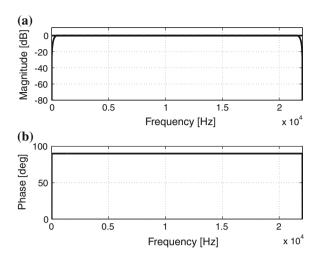

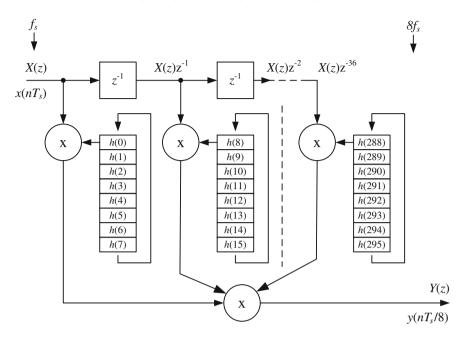

| 5.7  | Interpo | lators for High Quality Audio Signals.         |

|      | 5.7.1   | Single-Stage Interpolators                     |

|      | 5.7.2   | Multistage Interpolators                       |

| 5.8  | Class I | O Audio Power Amplifiers                       |

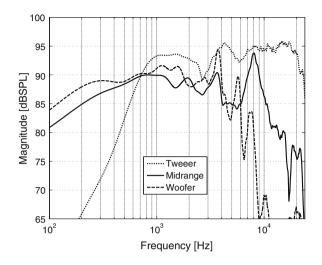

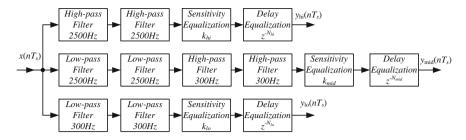

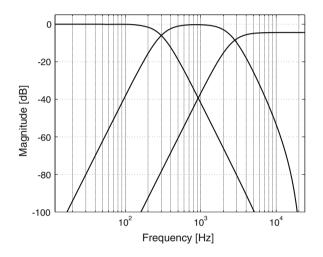

|      | 5.8.1   | Digital Crossovers                             |

|      | 5.8.2   | Loudspeaker Measurements                       |

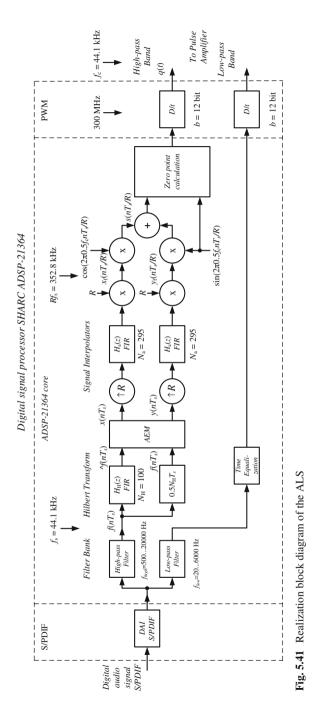

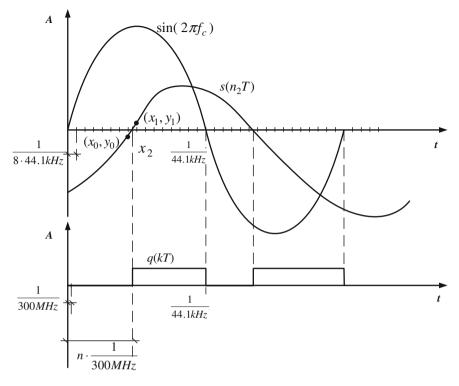

| 5.9  | Class I | D Power Amplifier with Digital Click Modulator |

|      | 5.9.1   | Digital Crossovers                             |

|      | 5.9.2   | Realization of Digital Click Modulator         |

|      | 5.9.3   | Experimental Results                           |

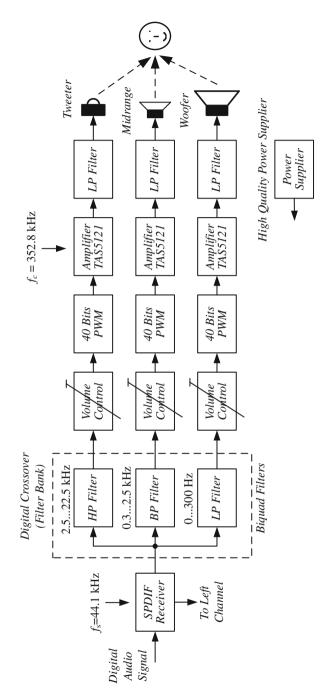

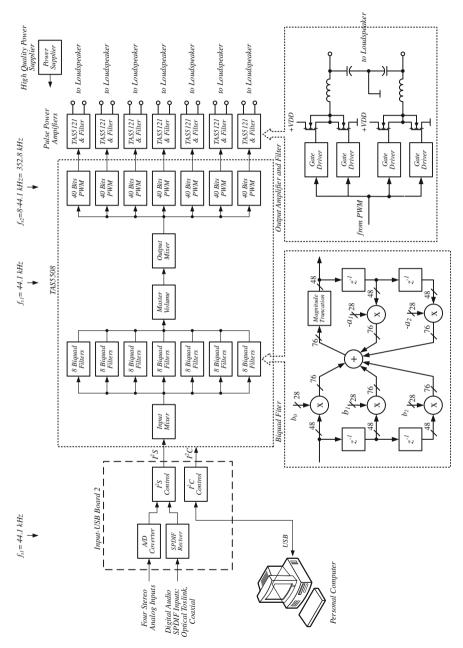

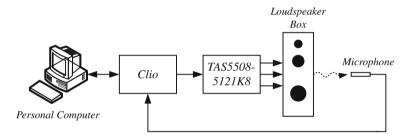

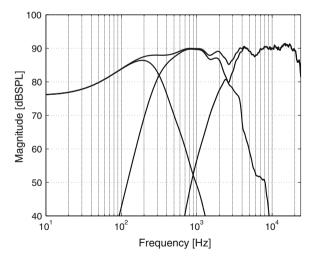

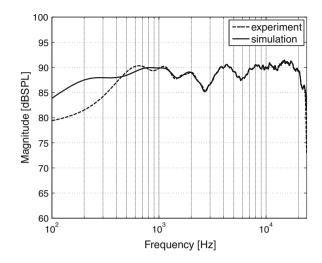

| 5.10 | Digital | Audio Class D Power Amplifier with             |

|      | TAS55   | 08 DSP                                         |

|      | 5.10.1  | TAS5508-5121K8EVM                              |

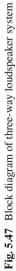

|      | 5.10.2  | Three-way Digital Crossover                    |

|      | 5.10.3  | Experimental Results                           |

| 5.11 | Conclu  | sions                                          |

| Refe | rences  |                                                |

| Cond | lusion. |                                                |

| 6.1  |         | ary of Results                                 |

| 6.2  |         | Work                                           |

|      |         |                                                |

# Acronyms

## Abbreviations

| AC    | Alternating current                                 |

|-------|-----------------------------------------------------|

| A/D   | Analog-to-digital converter                         |

| ALU   | Arithmetic-logic unit                               |

| APF   | Active power filter                                 |

| av    | Average value of signal                             |

| BPF   | Band-pass filter                                    |

| BSF   | Band-stop filter                                    |

| СМ    | Click modulator, also called zero position coding   |

| DAI   | Digital audio interface                             |

| D/A   | Digital-to-analog converter                         |

| dB    | Decibel, 20log(U2/U1), 10log(P2/P1)                 |

| DC    | Direct current                                      |

| DFT   | Discrete Fourier transform algorithm                |

| DPWM  | Digital pulse width modulation                      |

| DSM   | Delta sigma modulator                               |

| DSP   | Digital signal processor                            |

| D/t   | Digital-to-time converter                           |

| e.g.  | For example (exempli gratia-Latin)                  |

| EMI   | Electromagnetic interference                        |

| etc.  | And other things, or and so forth (et cetera-Latin) |

| FIR   | Finite impulse response digital filter              |

| FFT   | Discrete fast Fourier transform algorithm           |

| FLOPS | Floating-point operations per second                |

| FPGA  | Field programmable gate array                       |

| HPF   | High-pass filter                                    |

| IGBT  | The insulated gate bipolar transistor               |

| IC    | Integrated circuit                                  |

| i.e.  | This is (id est-Latin)                              |

|    | • |   | • |

|----|---|---|---|

| XV | 1 | 1 | 1 |

|    | - | 1 | • |

| IIR<br>IIS                      | Infinite impulse response digital filter<br>Inter-IC sound, integrated interchip sound, or IIS, is an electrical<br>serial bus interface standard used for connecting digital audio<br>devices together |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\operatorname{Im}(x), \Im(x)$  | Imaginary part of x                                                                                                                                                                                     |

| IPS                             | Instructions per second, MIPS                                                                                                                                                                           |

| IPT                             | Instantaneous power theory                                                                                                                                                                              |

| LC                              | LC circuit, circuit composed of capacitor and inductor                                                                                                                                                  |

| Log Chirp                       | Logarithmic swept sine chirp signal                                                                                                                                                                     |

| LSB                             | Last significant bit                                                                                                                                                                                    |

| LPF                             | Low-pass filter                                                                                                                                                                                         |

| LR                              | Linkwitz-Riley filter                                                                                                                                                                                   |

| LTI                             | Linear time-invariant circuit (system)                                                                                                                                                                  |

| LWDF                            | Lattice wave digital filter                                                                                                                                                                             |

| LBWDF                           | Lattice bireciprocal wave digital filter                                                                                                                                                                |

| MAC                             | Multiplication and accumulation, special arithmetic operation of                                                                                                                                        |

|                                 | DSP                                                                                                                                                                                                     |

| MDFT                            | Moving discrete Fourier transform algorithm                                                                                                                                                             |

| MIPS                            | Million instructions per second                                                                                                                                                                         |

| MLS                             | Maximal length sequence signal                                                                                                                                                                          |

| MOSFET                          | Metal-oxide-semiconductor field-effect transistor                                                                                                                                                       |

| MSB                             | Most significant bit                                                                                                                                                                                    |

| MWDF                            | Modified wave digital filters                                                                                                                                                                           |

| PCB                             | Printed circuit board                                                                                                                                                                                   |

| PCM                             | Pulse code modulation                                                                                                                                                                                   |

| PDF                             | Probability density function                                                                                                                                                                            |

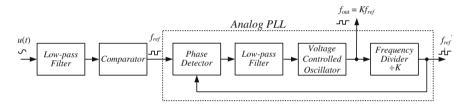

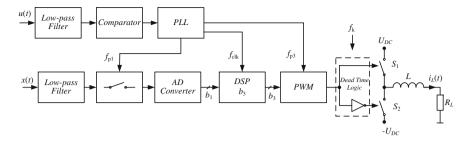

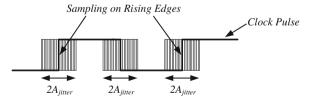

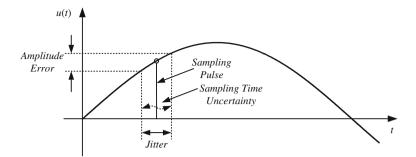

| PLL                             | Phase locked loop or phase lock loop circuit                                                                                                                                                            |

| PWM                             | Pulse width modulation                                                                                                                                                                                  |

| $\operatorname{Re}(x),  \Re(x)$ | Real part of x                                                                                                                                                                                          |

| RLC                             | Circuit, circuit composed of resistor, capacitor and inductor                                                                                                                                           |

| rms                             | Root mean square                                                                                                                                                                                        |

| SA                              | Successive approximation                                                                                                                                                                                |

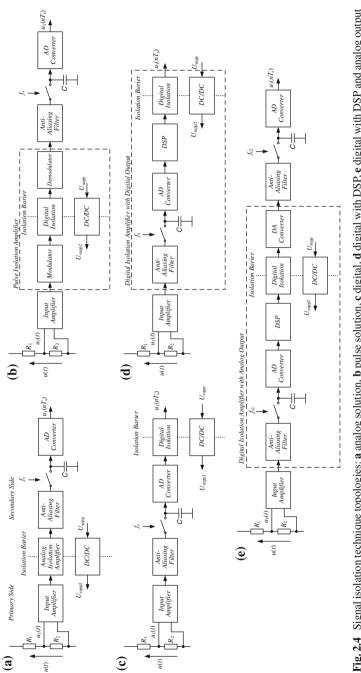

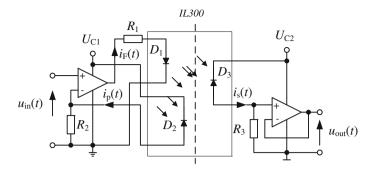

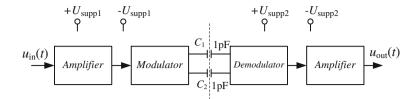

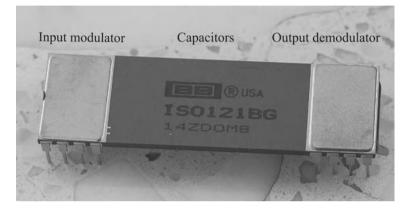

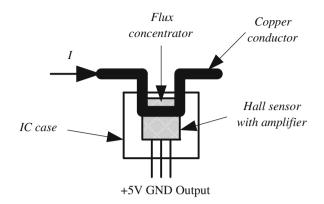

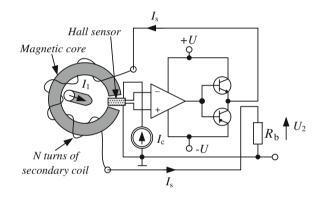

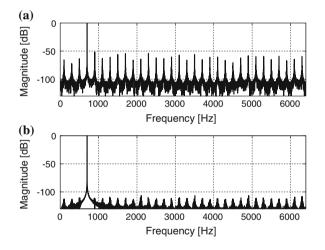

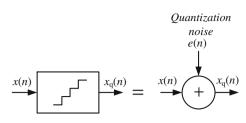

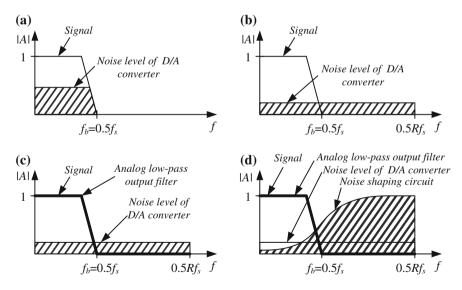

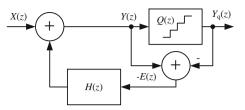

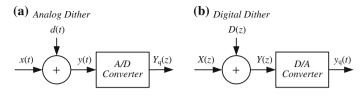

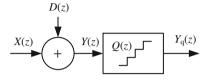

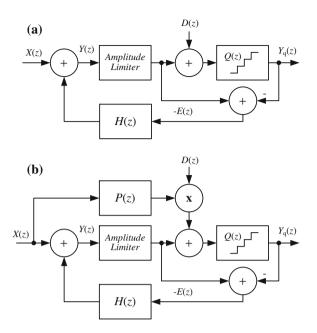

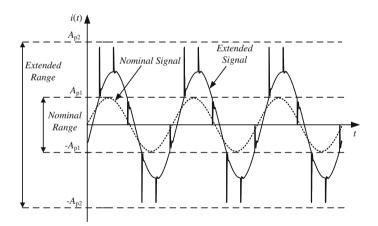

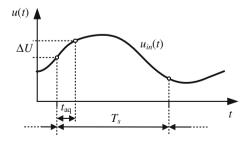

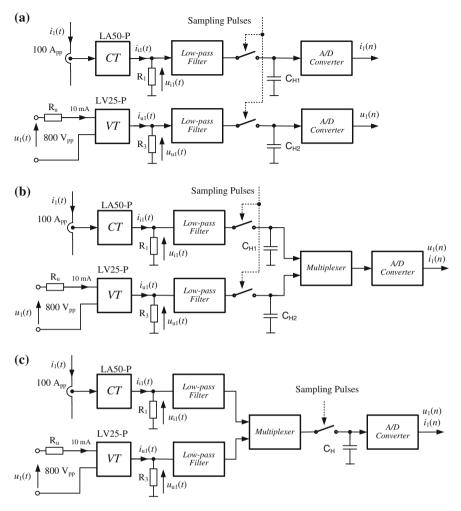

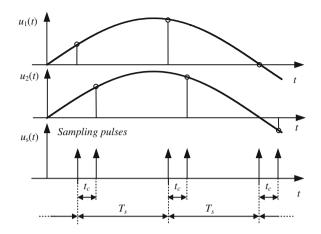

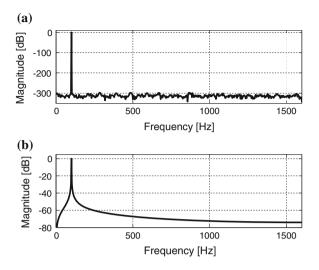

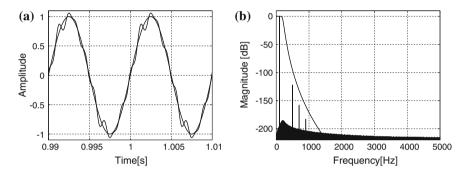

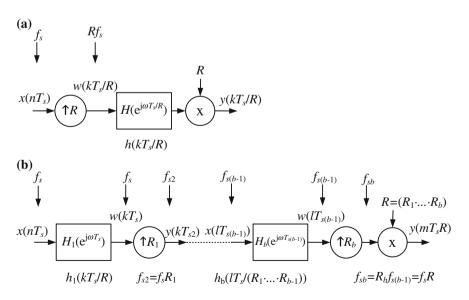

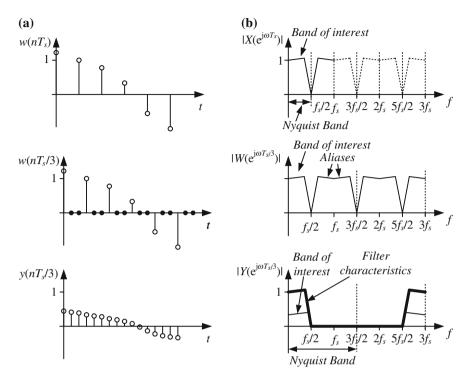

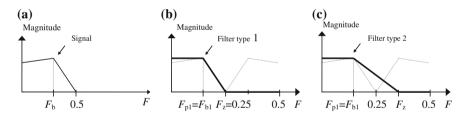

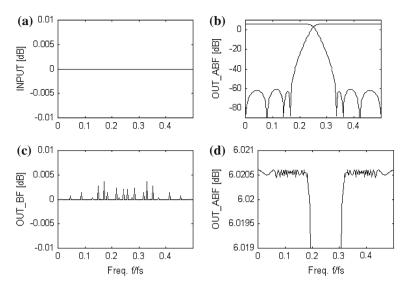

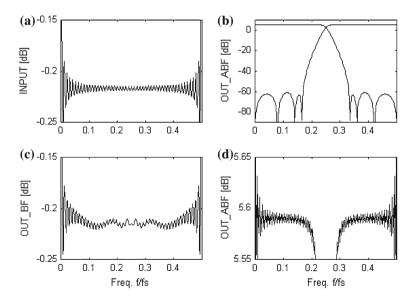

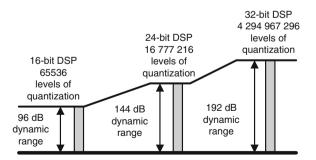

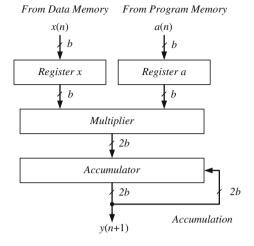

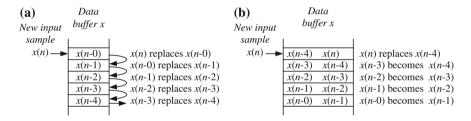

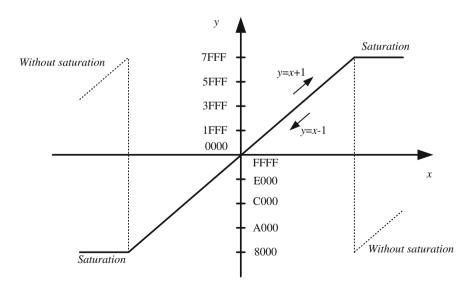

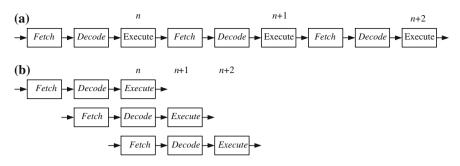

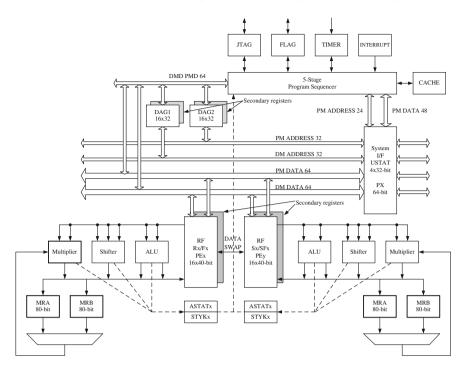

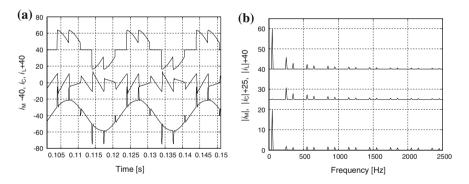

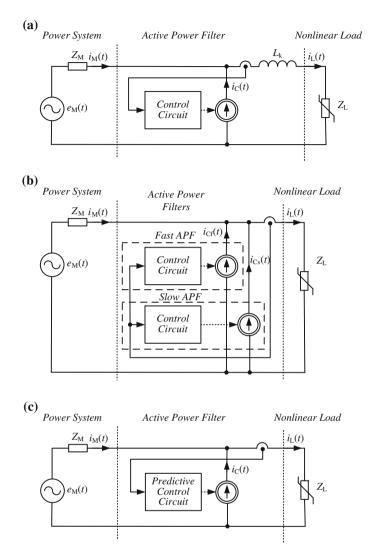

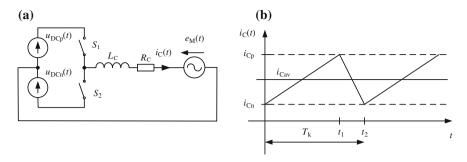

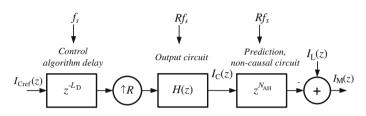

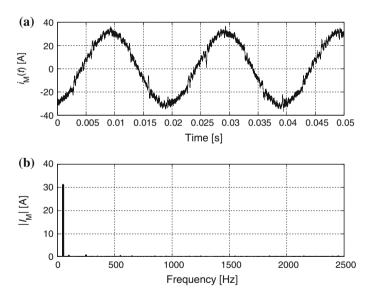

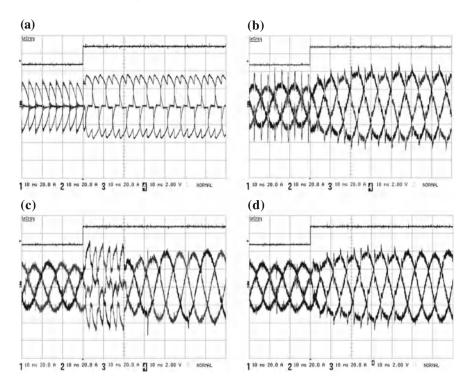

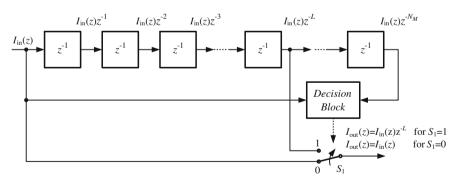

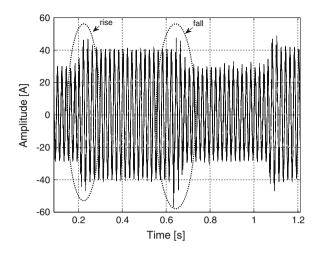

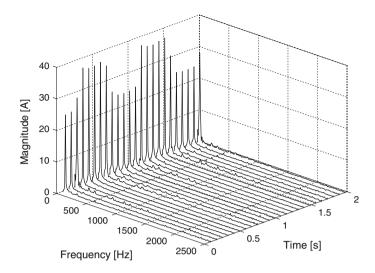

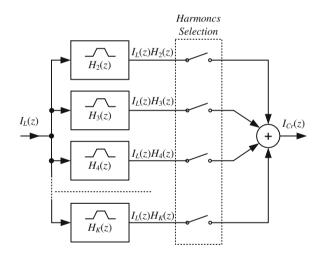

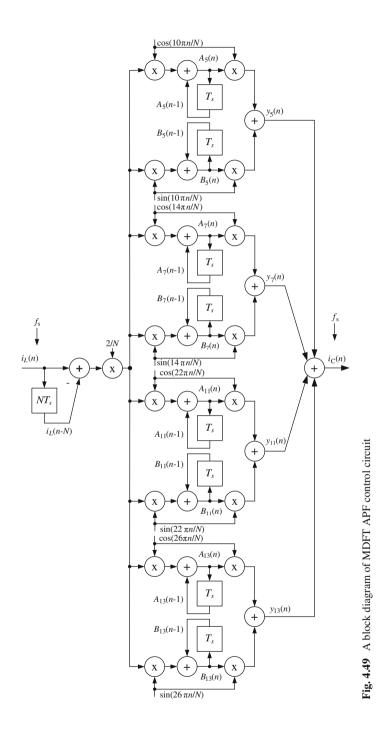

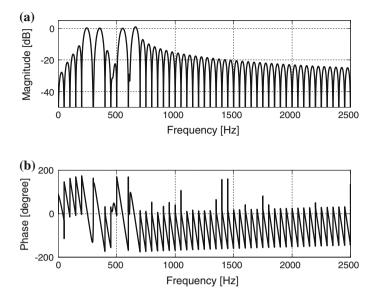

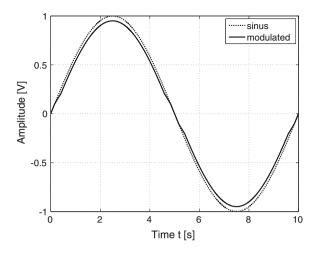

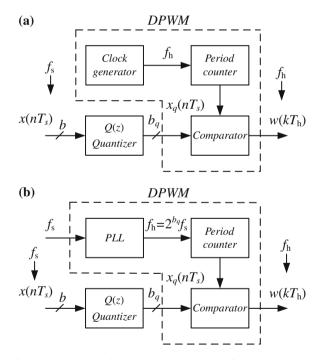

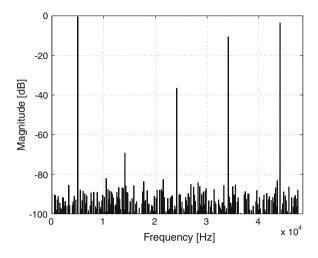

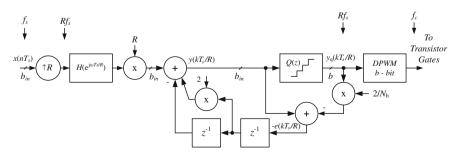

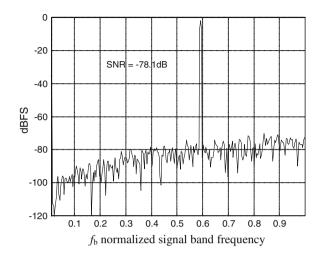

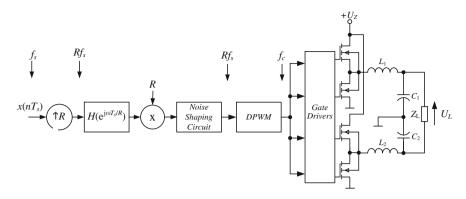

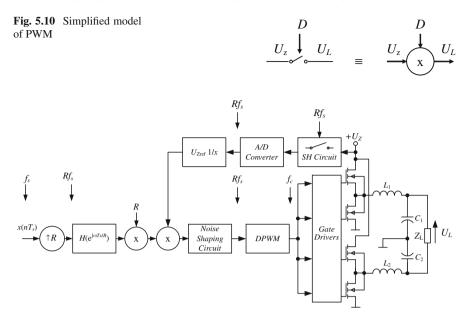

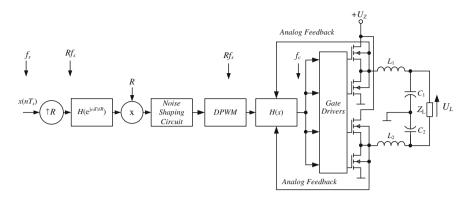

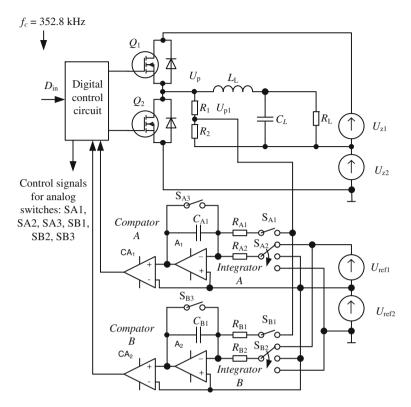

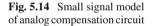

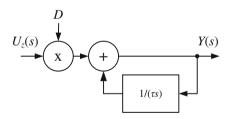

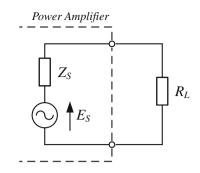

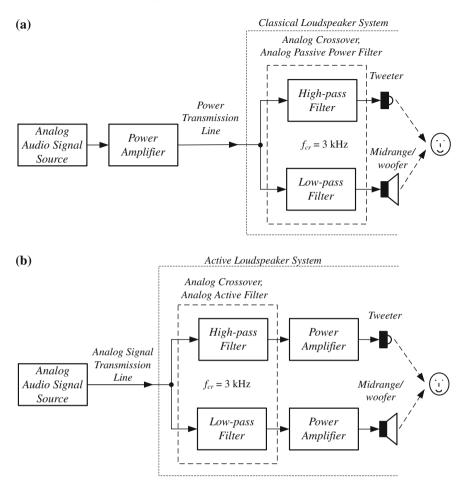

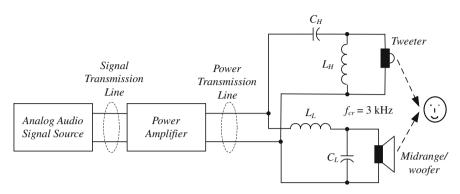

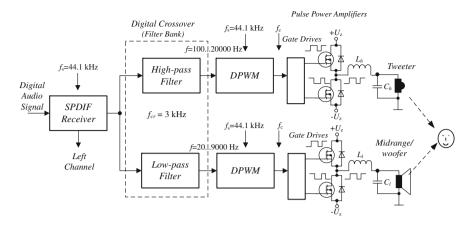

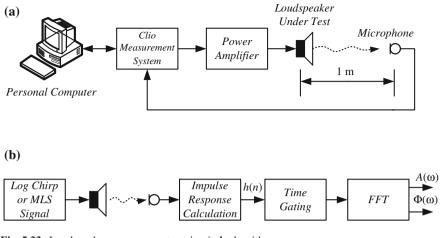

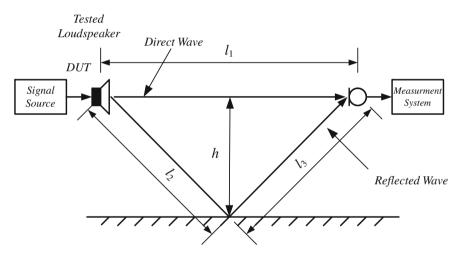

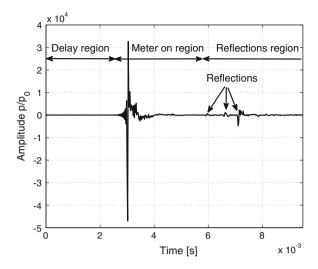

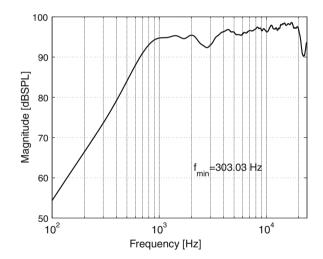

| SC                              | Strictly complementary digital filter bank                                                                                                                                                              |