# OPTIMAL VLSI ARCHITECTURAL SYNTHESIS

Area, Performance and Testability

## THE KLUWER INTERNATIONAL SERIES IN ENGINEERING AND COMPUTER SCIENCE

## VLSI, COMPUTER ARCHITECTURE AND DIGITAL SIGNAL PROCESSING Consulting Editor

Jonathan Allen

#### Latest Titles

Low-Noise Wide-Band Amplifiers in Bipolar and CMOS Technologies, Z.Y.Chang, W.M.C.Sansen, ISBN: 0-7923-9096-2 Iterative Identification and Restoration of Images, R. L. Lagendijk, J. Biemond ISBN: 0-7923-9097-0 VLSI Design of Neural Networks, U. Ramacher, U. Ruckert ISBN: 0-7923-9127-6 Synchronization Design for Digital Systems, T. H. Meng ISBN: 0-7923-9128-4 Hardware Annealing in Analog VLSI Neurocomputing, B. W. Lee, B. J. Sheu ISBN: 0-7923-9132-2 Neural Networks and Speech Processing, D. P. Morgan, C.L. Scofield ISBN: 0-7923-9144-6 Silicon-on-Insulator Technology: Materials to VLSI, J.P. Colinge ISBN: 0-7923-9150-0 Microwave Semiconductor Devices, S. Yngvesson ISBN: 0-7923-9156-X A Survey of High-Level Synthesis Systems, R. A. Walker, R. Camposano ISBN: 0-7923-9158-6 Symbolic Analysis for Automated Design of Analog Integrated Circuits, G. Gielen, W. Sansen, ISBN: 0-7923-9161-6 High-Level VLSI Synthesis, R. Camposano, W. Wolf, ISBN: 0-7923-9159-4 Integrating Functional and Temporal Domains in Logic Design: The False Path Problem and its Implications, P. C. McGeer, R. K. Brayton, ISBN: 0-7923-9163-2 Neural Models and Algorithms for Digital Testing, S. T. Chakradhar, V. D. Agrawal, M. L. Bushnell, ISBN: 0-7923-9165-9 Monte Carlo Device Simulation: Full Band and Beyond, Karl Hess, editor ISBN: 0-7923-9172-1 The Design of Communicating Systems: A System Engineering Approach, C. J. Koomen ISBN: 0-7923-9203-5 Parallel Algorithms and Architectures for DSP Applications, M.A. Bayoumi, editor ISBN: 0-7923-9209-4 Digital Speech Processing: Speech Coding, Synthesis and Recognition, A. Nejat Ince. editor ISBN: 0-7923-9220-5 Assessing Fault Model and Test Quality, Kenneth M. Butler, M. Ray Mercer ISBN: 0-7923-9222-1

# OPTIMAL VLSI ARCHITECTURAL SYNTHESIS

# Area, Performance and Testability

Catherine H. Gebotys and Mohamed I. Elmasry

University of Waterloo

Springer Science+Business Media, LLC

#### Library of Congress Cataloging-in-Publication Data

Gebotys, Catherine H.

Optimal VLSI architectural synthesis : area, performance, and testability / Catherine H. Gebotys and Mohamed I. Elmasry.

p. cm. -- (The Kluwer international series in engineering and computer science. VLSI, computer architecture, and digital signal processing)

Includes bibliographical references and index. ISBN 978-1-4613-6797-0 ISBN 978-1-4615-4018-2 (eBook) DOI 10.1007/978-1-4615-4018-2 1. Computer architecture. 2. Integrated circuits--Very large scale integration. I. Elmasry, Mohamed I., 1943- . II. Title. III. Series. QA76.9.A73G42 1992 004.2'2--dc20

91-31898 CIP

Copyright 1992 Springer Science+Business Media New York Originally published by Kluwer Academic Publishers in 1992 Softcover reprint of the hardcover 1st edition 1992

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, mechanical, photo-copying, recording, or otherwise, without the prior written permission of the publisher, Springer Science+Business Media, LLC.

Printed on acid-free paper.

То

# Robert Joseph and Kathleen Vanessa Gebotys

and

Elizabeth, Carmen, Samir, Nadia and Hassan Elmasry

# **Table of Contents**

| Preface                                     | xiii |

|---------------------------------------------|------|

| PART I: INTRODUCTION                        | 1    |

| 1. GLOBAL VLSI DESIGN CYCLE                 | 3    |

| 1.1 VLSI DESIGN CYCLE                       | 4    |

| 1.2 HYBRID SYSTEMS DESIGN                   | 10   |

| 1.3 IMPACT OF TECHNOLOGIES                  | 12   |

| 1.4 TEST CONSIDERATIONS                     | 14   |

| 1.5 BOTTLENECKS AND OPEN ISSUES             | 17   |

| 1.6 FOCUS OF TEXT                           | 19   |

| 2. BEHAVIORAL AND STRUCTURAL INTERFACES     |      |

|                                             | 21   |

| 2.1 INPUT TO AN ARCHITECTURAL SYNTHESIZER   |      |

|                                             | 21   |

| 2.2 INTERFACE PRIMITIVES FOR EXTERNAL       |      |

| PROCESSES                                   | 25   |

| 2.3 OUTPUT PRIMITIVES FROM AN ARCHITECTURAL |      |

| SYNTHESIZER                                 | 31   |

| PART II: REVIEW AND BACKGROUND              | 37   |

| 3. STATE OF THE ART SYNTHESIS               | 39   |

| 3.1 TERMINOLOGY AND SUBTASK DEFINITIONS     |      |

|                                             | 39   |

| 3.2 HIGH LEVEL TRANSFORMATIONS              | 43   |

| 3.3 INDEPENDENT SUBTASK OPTIMIZATION        | 45   |

| 3.3.1 Scheduling                                          | 45       |

|-----------------------------------------------------------|----------|

| 3.3.2 Resource Allocation                                 | 46       |

| 3.4 ITERATIVE AND SIMULTANEOUS APPROACHES                 |          |

|                                                           | 51       |

| 3.5 MATHEMATICAL APPROACHES                               | 55       |

| 3.5.1 Branch and Bound                                    | 55       |

| 3.5.2 Simulated Annealing                                 | 57       |

| 3.5.3 Makespan Scheduling                                 | 58       |

| 3.5.4 Feasibility Models                                  | 58       |

| 3.6 TIMING CONSTRAINED SYNTHESIS                          | 59       |

| 3.7 COST FUNCTIONS FOR DESIGN EVALUATION                  |          |

|                                                           | 61       |

| 4. INTRODUCTION TO INTEGER PROGRAMMING                    | ()       |

|                                                           | 63       |

| 4.1 APPLICATIONS AND MODELS                               | 64       |

| 4.2 SOLUTION OF UNSTRUCTURED IPs                          | 66       |

| 4.3 POLYHEDRAL APPROACHES TO SOLVING IPs                  | 71       |

|                                                           | 73       |

| 4.4 THE NODE PACKING PROBLEM                              | 73<br>78 |

| 4.5 THE KNAPSACK PROBLEM                                  | /0       |

| PART III: OPTIMAL ARCHITECTURAL SYNTHESIS WITH INTERFACES | 81       |

| 5. A METHODOLOGY FOR ARCHITECTURAL SYN-<br>THESIS         | 83       |

| 5.1 REQUIREMENTS FOR HIGH LEVEL SYNTHESIS TOOLS           | 83       |

| 5.2 HIGH LEVEL METHODOLOGY                                | 85       |

| 5.3 OASIC METHODOLOGY                       | 88  |

|---------------------------------------------|-----|

| 5.4 AN INTRODUCTION TO OASIC                | 90  |

| 5.5 OASIC TERMINOLOGY, ASSUMPTIONS, AND     |     |

| PREPROCESSING                               | 92  |

| 5.5.1 Terminology                           | 92  |

| 5.5.2 Assumptions                           | 94  |

| 5.5.3 Preprocessing                         | 94  |

| 6. SIMULTANEOUS SCHEDULING, AND SELECTION   |     |

| AND ALLOCATION OF FUNCTIONAL UNITS          | 97  |

| 6.1 THE FORMAL MODEL                        | 98  |

| 6.2 COST FUNCTIONS                          | 105 |

| 6.3 FUNCTIONAL UNIT TYPE SELECTION          | 106 |

| 7. OASIC: AREA-DELAY CONSTRAINED ARCHITEC-  |     |

| TURAL SYNTHESIS                             | 109 |

| 7.1 THE PRECEDENCE CONSTRAINED SCHEDULING   |     |

| MODEL                                       | 110 |

| 7.2 FUNCTIONAL UNIT ALLOCATION              | 111 |

| 7.3 REGISTER ALLOCATION                     | 111 |

| 7.4 BUS ALLOCATION                          | 114 |

| 7.5 COST FUNCTIONS                          | 119 |

| 7.6 APPLICATION SPECIFIC TIGHTENING OF CON- |     |

| STRAINTS                                    | 120 |

| 8. SUPPORT FOR ALGORITHMIC CONSTRUCTS       | 123 |

| 8.1 CONDITIONAL CODE                        | 123 |

| 8.2 LOOPS                                   | 126 |

| 8.3 FUNCTIONAL PIPELINING                   | 126 |

| 9. INTERFACE CONSTRAINTS                                           | 129 |

|--------------------------------------------------------------------|-----|

| 9.1 GENERAL INTERFACE: MINIMUM AND MAX-<br>IMUM TIMING CONSTRAINTS | 130 |

| 9.2 ANALOG INTERFACE: FIXED TIMING CON-<br>STRAINT                 | 131 |

| 9.3 ASYNCHRONOUS INTERFACE                                         | 132 |

| 9.4 UNKNOWN UNBOUNDED DELAYS                                       | 138 |

| 9.5 COMPLEX TIMING CONSTRAINTS                                     | 138 |

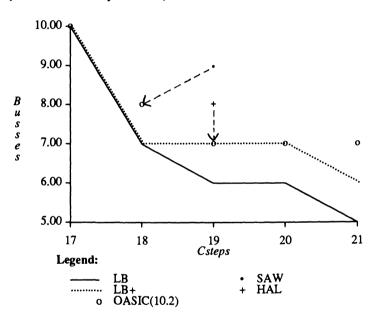

| 10. OASIC SYNTHESIS RESULTS                                        | 141 |

| 10.1 ELLIPTICAL WAVE FILTER                                        | 144 |

| 10.1.1 Structured Model                                            | 144 |

| 10.1.2 Area-Delay Optimized                                        | 150 |

| 10.2 NEURAL NETWORK ALGORITHM                                      | 162 |

| 10.3 CONDITIONAL CODE EXAMPLE                                      | 169 |

| 10.4 ANALOG AND ASYNCHRONOUS INTERFACE<br>EXAMPLES                 | 171 |

| 10.6.1 Analog Interface                                            | 172 |

| 10.6.2 Asynchronous Interface                                      | 172 |

| PART IV: TESTABLE ARCHITECTURAL SYNTHESIS                          | 177 |

| 11. TESTABILITY IN ARCHITECTURAL SYNTHESIS                         |     |

|                                                                    | 179 |

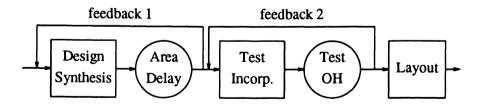

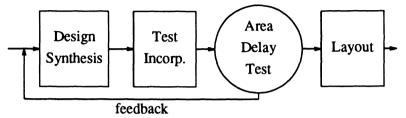

| 11.1 DESIGN AND TEST                                               | 180 |

| 11.1.1 Choices in Design and Test                                  | 183 |

| 11.2 APPROACHES TO TESTABILITY                                     | 188 |

| 11.2.1 Test Measures and Tools                                     | 188 |

| 11.2.2 Design Modifications for Testability                     | 193 |

|-----------------------------------------------------------------|-----|

| 11.3 PREVIOUS RESEARCH IN DESIGN FOR TEST                       | 200 |

|                                                                 | 200 |

| 11.4 APPROACHES TO TEST WITH SYNTHESIS                          | 202 |

| 11.4.1 Previous Research                                        | 202 |

| 11.4.2 Commercial Systems                                       | 203 |

| 11.5 INADEQUACIES OF CURRENT SYNTHESIS WITH                     |     |

| TEST                                                            | 204 |

| 11.5.1 Feedback                                                 | 204 |

| 11.5.2 Integration                                              | 205 |

| 11.5.3 Constraint Estimation                                    | 205 |

| 12. THE CATREE ARCHITECTURAL SYNTHESIS WITH                     |     |

| TESTABILITY                                                     | 207 |

| 12.1 PROBLEM DESCRIPTION                                        | 208 |

| 12.2 COMPARISON WITH PREVIOUS RESEARCH                          |     |

|                                                                 | 212 |

| 12.3 TWO SYNTHESIS WITH TEST METHODOLOGIES:<br>CATREE & CATREE2 | 213 |

| 12.4 CATREE DESIGN SYNTHESIS STAGES                             | 216 |

| 12.4.1 Input Specification                                      | 210 |

| 12.4.2 Design Allocation                                        | 217 |

| -                                                               | 217 |

| 12.4.3 CATREE Area and Delay Estimates                          |     |

| 12.4.4 Test Incorporation                                       | 226 |

| 12.4.5 Feedback                                                 | 231 |

| 12.5 CATREE SYNTHESIS RESULTS                                   | 235 |

| 12.6 CATREE DISCUSSION                                          | 239 |

| 12.7 CATREE2 DESIGN SYNTHESIS STAGES              | 243 |

|---------------------------------------------------|-----|

| 12.7.1 Tree Formation and Functional Unit Binding |     |

| •••••                                             | 244 |

| 12.7.2 Test Incorporation                         | 245 |

| 12.7.3 (Test) Register and Bus Binding            | 248 |

| 12.7.4 Feedback                                   | 250 |

| 12.8 CATREE2 EXPERIMENTS                          | 251 |

| 12.9 CATREE2 DISCUSSION                           | 254 |

| PART V: SUMMARY AND FUTURE RESEARCH               |     |

|                                                   | 259 |

| 13. SUMMARY AND FUTURE RESEARCH                   | 261 |

| 13.1 OASIC SUMMARY                                | 261 |

| 13.2 CATREE SUMMARY                               | 266 |

| 13.3 FUTURE EXTENSIONS                            | 267 |

| 13.4 CONCLUDING REMARKS                           | 269 |

| REFERENCES                                        | 271 |

| INDEX                                             | 287 |

## PREFACE

Although research in architectural synthesis has been conducted for over ten years it has had very little impact on industry. This in our view is due to the inability of current architectural synthesizers to provide area-delay competitive (or "optimal") architectures, that will support interfaces to analog, asynchronous, and other complex processes. They also fail to incorporate testability. The OASIC (optimal architectural synthesis with interface constraints) architectural synthesizer and the CATREE (computer aided trees) synthesizer demonstrate how these problems can be solved.

Traditionally architectural synthesis is viewed as NP hard and therefore most research has involved heuristics. OASIC demonstrates by using an IP approach (using polyhedral analysis), that most input algorithms can be synthesized very fast into globally optimal architectures. Since a mathematical model is used, complex interface constraints can easily be incorporated and solved.

Research in test incorporation has in general been separate from synthesis research. This is due to the fact that traditional test research has been at the gate or lower level of design representation. Nevertheless as technologies scale down, and complexity of design scales up, the push for reducing testing times is increased. On way to deal with this is to incorporate test strategies early in the design process. The second half of this text examines an approach for integrating architectural synthesis with test incorporation. Research showed that test must be considered during synthesis to provide good architectural solutions which minimize area delay cost functions.

Though originally developed separately, OASIC and CATREE can be integrated so that OASIC simultaneously schedules and allocates the architecture and CATREE performs binding (and reallocating) of the architecture for testability.

Part I introduces the motivation and current open problems with high level CAD. Part II provides the necessary background material on architectural synthesis and integer programming. This part includes a definition of problems in both areas and a brief review of previous approaches to solving these problems. Part III outlines the OASIC methodology, models, the solution techniques used, and some synthesized results. Part IV outlines the CATREE methodology, the algorithms and data structures used and some synthesized results. Part V provides a brief discussion and concluding remarks concerning how we will interface with CAD tools of the future.

The book can be used at the senior undergraduate and graduate levels in courses dealing with computer architectures, computer organization, VLSI design, computer-aided design, VLSI digital signal processing, testing, or integer programming. It will be also of value to researchers dealing with these topics.

C.H. Gebotys M.I. Elmasry Waterloo, Ontario, Canada

# **PART I: INTRODUCTION**

1.

# **GLOBAL VLSI DESIGN CYCLE**

The global VLSI (very large scale integration) systems design cycle is briefly discussed below with respect to relationships between design stages, bottlenecks, and current open issues for design automation (DA). The design cycle involves moving from an abstract design specification to gradually a more detailed single or multichip design that can be tested and fabricated. The VLSI design stages are very interdependent and therefore it is important to outline the purpose of each stage before one can address the problems of high level synthesis. Area, power, speed, timing issues, input and output pin limitations, testability, and many other criteria are important in the design process. Interfaces to other complex processes, design complexity with respect to implementation technologies and testability will also be discussed. In addition, an understanding of the current computer aided-design (CAD) bottlenecks and open issues will further emphasize the importance and impact of high level architectural synthesis (the focus of this text) on the VLSI design cycle.

### **1.1 VLSI DESIGN CYCLE**

The VLSI systems design cycle generally involves many transformations from a high level design specification to a low level of design representation. Stages include, but are not limited to : local and global transformations on the behavioral specification, partitioning of the behavior, architectural synthesis (transforming behavior into an architecture), logic synthesis, functional level simulation, module generation, placement and routing, timing analysis, and final mask layout and verification. The behavioral specification, also called the input algorithm, which is accompanied by a cost function that drives the design synthesis. For example the cost function may involve the minimization of chip area and power dissipation, or the maximization of chip speed and testability.

The time required for each design stage may be quite large depending upon how much automation is provided or the designers expertise. Feedback from one stage to a previous stage is often quite frequent and time consuming due to incorrect early decisions or false assumptions. For example a partitioning decision may lead to a chip which exceeds its area requirements and therefore feedback is required to correct the earlier partition decision. Feedback is often inevitable since each design cycle step is interdependent upon the others. For example a decision made during behavioral scheduling affects all lower stages such as hardware allocation and the final VLSI design layout. Yet it is very difficult to predict the effects that early decisions will have since the behavior is technology independent. It is believed to be impossible to simultaneously consider all stages (down to layout) due to the complexity and enormous amounts of data required. It is well known that early decisions made in the design cycle often have the greatest impact on the final design. Thus the high level stages are currently viewed as being very important and of great interest in the VLSI community.

Early steps of the VLSI design cycle have been defined as algorithm transformations, algorithm partitioning, and architectural synthesis. We will use the terms behavior or algorithm to describe the input into an architectural synthesizer. Decisions to partition the behavior among multiple chips (spatial), different analog and digital domains (technology), or into separate pipestages (time) are explored in these early steps. In industry these decisions are often done without the aid of design automation tools, yet it is this exploration which is considered critical for shortening the design cycle time and of great importance for designing high performance architectures.

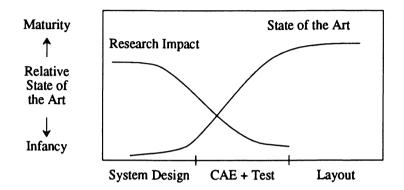

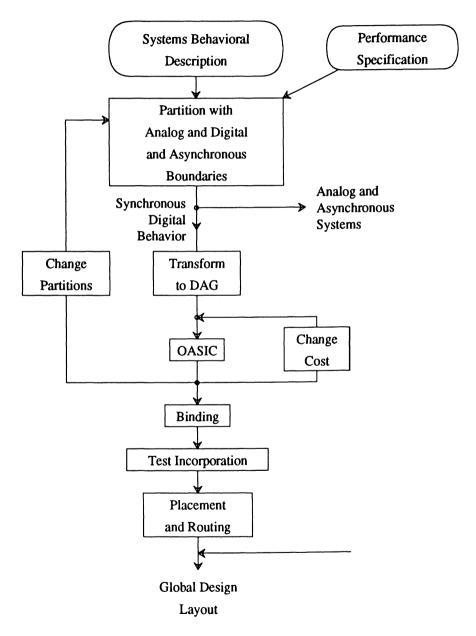

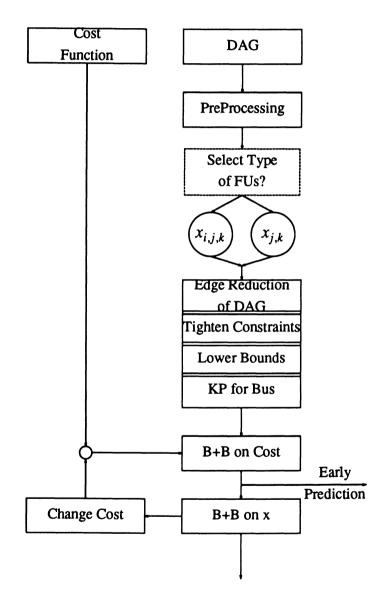

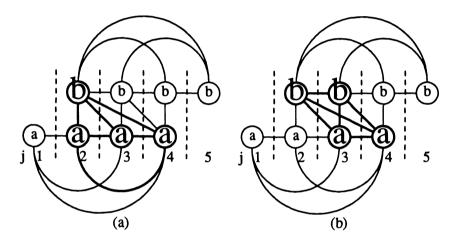

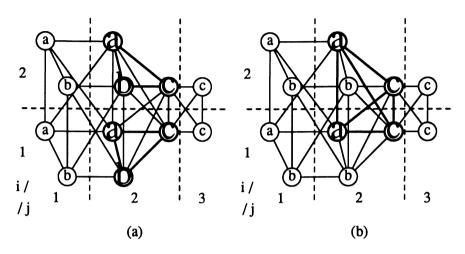

Even though research on high level architectural synthesis tools has been conducted for more than ten years, it has not had a significant impact on industry. This can be attributed to the known fact that the acceptance of new technologies occurs much faster in industry (Langeler, 1989) than the acceptance of new DA tools. Currently the most common and mature DA tools in industry perform low level tedious tasks such as module generation, placement, routing, and layout. Figure 1.1 illustrates the maturity of the various DA tools. More recently logic synthesis tools have been introduced into the CAD market for controller design. We believe there are several reasons why architectural synthesis and higher level tools have not found a place in industry. In order to understand why, we will first briefly introduce the subject of architectural synthesis, and then look at issues which have not been adequately addressed by researchers and consequently contribute to preventing the introduction of synthesis in industry. Chapters three and four, in part II, will review the field of architectural synthesis and integer programming respectively. In chapter five through nine, of part III, we will introduce our formal and practical approach to solving these issues optimally for

architectural synthesis.

Figure 1.1. The maturity of various CAD tools for VLSI.

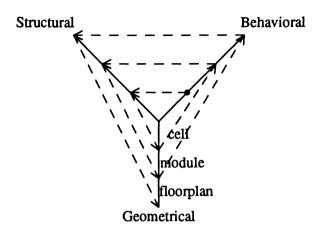

Architectural synthesis of digital synchronous chips refers to the transformation from a behavioral (or algorithmic) input description to a hardware architecture which implements the behavior (according to a schedule). The Y chart (Gajski, 1983) shown in figure 1.2, is most commonly used to represent the transformations performed during the design cycle. The three axis of the Y chart, behavioral, structural and geometrical axes, are used to represent different levels of design representation and the mappings required to design a chip. During the design of a system one starts with a behavioral design specification (in theory) and moves successively down the chart to refine the design into greater levels of detail. However we will give a brief look at the different levels of hierarchy by starting at the lowest level and moving up.

Starting at the inner bold dot in figure 1.2 on the behavioral axis, the lower level cells, such as a data storage element is defined. By moving up to the structural axis it becomes more refined as an interconnection of

Figure 1.2. The Y chart, illustrating design cycle transitions. The architectural synthesis is represented by the arc, at the top of the chart, from the behavioral axis to the structural axis.

transistors which implements for example a master-slave flip-flop or register. Finally a transition to the geometrical axis defines the actual mask layers required to fabricate the register as part of a chip. When all cells are available in a library one can continue to the module level. Modules are larger design components that are made from a number of cells. An example of a module is a register file, which is composed of a number of registers and control circuitry. The behavioral axis, at the module level, defines the control and functionality of the register file. By moving again to the structural axis the definition of this module in terms of an interconnection of cells is detailed. By moving again to the geometrical axis the module is defined according to the mask definitions of its cells and their interconnection. One more level up the hierarchy defines the behavior of a larger system of modules which could be a chip or system.

The transition from the behavioral axis to the structural axis, at the top of figure 1.2, represents architectural synthesis, the focus of this text. After performing architectural synthesis, a digital designer moves from the structural axis to the layout axis at the module and chip levels during the design cycle. This later procedure is now very well defined in industry. For example a behavior may be described as a z-diagram for digital filters or a programming language (such as 'C' or Pascal). We define a *code operation* as a single specific arithmetic operation in the algorithm. Code operations in the behavioral description may receive data or transfer data in the form of bits, bytes, arrays or strings for computation. Additionally there may be very complex timing constraints on data transfers or communication with external processes. The term external process will be used to describe a process or operation that communicates with the behavioral algorithm but is not being synthesized. The output of the high level architectural synthesizer is a hardware architecture and a schedule. An architecture is composed of hardware components, which include registers (memory), busses, and functional units (such as multipliers, arithmetic logic units (ALUs), etc). The architectural synthesis involves many tasks including scheduling and allocation. The schedule defines the mapping of code operations to control states. The allocation tasks determine the number of functional units, registers, and busses. The binding task defines the mapping of code operations to hardware components (functional units and registers), including data transfers to and from busses. Since synthesis is a one to many mapping, often a set of design constraints or a cost function are specified by the user to select among the design solutions or find the optimal one. For example each code operation can be mapped to many different control states and hardware components. The design constraints most often include area and speed (McFarland, 1986), however other constraints such as power (Petersen, 1986, Haroun, 1989) and test (Gebotys, 1989), may also be important.

One of the major purposes of architectural design synthesis is to decrease the VLSI design cycle time. In effect, because designs are synthesized faster (than humans can design) there is more time for design exploration and thus yielding 'better' or optimal architectures (with respect to other solutions produced by the synthesizer during design exploration). This tool also provides a good method for handling last minute design specification changes, since new architectures can be quickly synthesized.

Chip level design synthesis is viewed as an important stage in the VLSI design cycle. It follows the design specification stage, where designers define exactly what function their system will perform and how it will be partitioned among custom chips. It also precedes the layout stage. Since the synthesis stage, which determines the architecture of the design is estimated to be 30-40% of the total design effort (Fey, 1986), automation plays an important part in saving time and manpower.

As VLSI technologies scale up to ULSI (ultra-large-scaleintegration) levels the computational demands placed on DA tools increases. This burden affects synthesis tools directly. Behavioral design descriptions to be synthesized will be extremely complex and large. Very few synthesizers have synthesized more than 1000 lines of input code. Only synthesizers targeted for microprocessor designs (Rajan, 1989) have produced architectures for the M68000, using 2426 lines of input code. Most have used far less than 1000 lines of input code to synthesize examples (see the high level synthesis benchmarks at electronic address hlsw@decwrl.dec.com (Borriello, 1988) ). It is not clear what limits these architectural synthesis tools exhibit as design sizes increase. Furthermore some subtasks associated with design synthesis, have been classified as NP-hard (Garey, 1979) . This means that there will exist some problems that will require exponential time to solve. In the future, better algorithmic techniques to handle the complexity of the problem will be developed, such as partitioning and execution of synthesis tasks on multiprocessor architectures. The high level synthesis tools must be able to synthesize architectures from partitioned code segments and from input algorithms with a high degree of regularity. These techniques will provide solutions to handling the computational complexities and demands of large systems that need to be synthesized.

## **1.2 HYBRID SYSTEMS DESIGN**

Lacking even more automation is analog and asynchronous design, although recent research has shown much promise for both areas. It is believed that about 30% of ASICS have analog components and by the year 2000 this number is expected to double (Carley, 1989). Mixed analog/digital systems design may involve tightly coupled (embedded) hardware or loosely coupled (partitionable) mixed hardware components. An example of the former case is the implementation of the artificial neural network algorithm (ANN) where both analog and digital components can be used for different processing aspects. In some cases the advantages of analog or digital implementation may not be clearly identifiable for a particular application and design exploration will be extremely important to identify the optimized combination of digital signal processing (DSP) and analog signal processing (ASP). Loosely coupled mixed designs more commonly occur when a sequential pipeline of processing functions are synthesized. In these types of designs often the partition between analog and digital is well defined. For example a design to drive an RGB (red-green-blue) display may have DAC (digital to analog converter) circuitry on the same chip that provides digital graphics processing. It is believed that high level synthesis of analog and digital circuits is different enough to necessitate the use of separate CAD tools. Nevertheless the research in analog CAD tools greatly lags digital CAD tool research and high level synthesis tools have not been defined in analog design. However, it is important to have a formally defined

interface between analog and digital so that the concurrent execution of synthesizers can be performed. We define an *analog interface* to a synchronous digital circuit as a sequential synchronous data input/output at a fixed rate. For example data input to or output from a DAC or a ADC may be a part of the system behavior which is input to an architectural synthesizer. This model of interface will be discussed more in chapter 2.2.

Asynchronous designs are expected to increase due to the limits of global clocking of synchronous circuits including clock skew (Meng, 1989). Asynchronous circuits have task dependent or data dependent completion times. For example the next task cycle is started once the current task is completed. Asynchronous designs can be represented as bounded or unbounded delay circuits (Meng, 1989). We define an asynchronous interface of a digital synchronous system as inputs synchronized with the controllers (global) clock but are still indeterminate with respect to the control state (or control step) of the system (Hayati, 1989). We call the interface bounded if an earliest and a latest control state is defined. Thus it is known that input data from the external asynchronous process will arrive at a control state greater than or equal to the earliest state and less than or equal to the latest state. Analogously the data could be output to an asynchronous process. In this case, the interface would be used to control the use of the register hold time for transferring output data. There are a number of designs for interfacing asynchronous circuits to digital synchronous systems such as data detectors, spacers, multivalued circuits or other types of synchronizers. The design of these synchronizer components will not be addressed however found in be information on these can more (Balraj, 1986, Brzozowski, 1990, Meng, 1989).

In totally synchronous digital multichip designs, it may be very difficult to guarantee that the clock signal will arrive at the same time at all parts of the circuits (Brzozowski, 1990). Thus external data inputs may be delayed by different amounts. Hence it is often necessary to consider asynchronous behavior, even in totally distributed synchronous systems. As geometries scale down, clock skew, slower transition times, and the capacitance and resistance effects will become increasingly dominant (Subrahmanyam, 1988). Preliminary analysis indicates that for large designs self timed disciplines may be necessary. Additionally in globally synchronous circuits there may also be asynchronous behavior when access to a shared resource is requested. Finally, the systems design may involve loosely coupled VLSI circuits which can be locally synchronous but globally self timed and therefore require asynchronous behavioral interfaces. Asynchronous designs offer many advantages such as increased operating speeds and they can be designed to handle bounded metastable states.

The focus of this text will be on the automated architectural design of digital synchronous circuits with interface to both analog and asynchronous circuits.

#### **1.3 IMPACT OF TECHNOLOGIES**

There are many technological factors which also may drive the performance of VLSI designs. For example not only will constraints for data transfer between multichips on a printed circuit board (PCB) board be important for architectural synthesis but also data transfers on a silicon substrate (multichip modules) (Weber, 1989), or on a wafer (wafer scale integration) will be important. An example of these data transfer constraints are die to die communication delays. Each new technology brings a new set of constraints which must be incorporated into automated architectural synthesis tools. In addition to the medium of data transfer between chips, the implementation technology of the chip itself is also important. For example the area and delay characteristics of the module library will change when new technologies are introduced. Thus architectural synthesizers must have adaptable cost functions which will take these changes into consideration in finding optimal architectural solutions. These factors will also have a great impact on the types of architectures which may be suited for a technology. For example if interconnect is very expensive (ie. maybe the technology only allows two levels of metal) then busses must be minimized and used to yield a more efficient solution than the use of a random topology (ie. local interconnections).

Another technological impact which affects architectural synthesizers is at the application end. For example artificial neural network (ANN) algorithms are being used in many systems applications such as pattern recognition (Treleavan, 1989). The ability to embed these algorithms in a systems design has become very important. Systolic (Kung, 1988) and multiprocessor network implementations have already been investigated. Their use as input to architectural synthesizers however has not been explored. For example the VLSI implementation of the ANN may be one part of a larger design of analog signal processing (ASP) or digital signal processing (DSP). It is possible that the execution of the ANN does not conflict in time with other DSP postfiltering and thus the sharing of hardware may be possible.

Architectural synthesizers must be able to handle a wide range of algorithms. These types of algorithms have not been input to existing architectural synthesizers and are characterized by an extremely large number of data transfers between code operations. This factor leads to extremely large interconnect requirements. Since most synthesizers deal with interconnect during the final stages of the design it is possible that they would output unsuitable architectures (where the interconnect complexity is too high). The architectural synthesizer we will present can optimize interconnect at an early stage.

### **1.4 TEST CONSIDERATIONS**

Test is required to verify that the fabricated VLSI chip or multichip system works fault-free or operates satisfactorily (McCluskey, 1990). In other words a test set or set of test vectors is used to detect faults present in the chip. These faults may be due to the fabrication process or layout errors. Test is not the same as design verification. Design verification, refers to proving that the synthesized design solution (not fabricated chip) is correct with respect to the behavioral input given. In our case we assume the user has already verified that the solution executes the behavior correctly by using a functional set of test vectors. One solution to testing chips is to create a set of test vectors to control and observe every fault possible in the chip design. This is called through the pins testing (McCluskey, 1986). In other words we wish to detect at the output pins the presence or absence of faults while applying proper stimulants at the input pins. Another approach to test is called the structured design for test approach (Williams, 1983, McCluskey, 1986) . This approach, discussed in section 11.2.2, modifies the design to increase the testability or ease the generation of test vectors.

There are two main reasons why test is important. One is the cost view. The cost to detect an error increases by a factor of 10 at each level of design (Williams, 1983, Goel, 1980). For example the chip design, board design, system design, and system design in the field are the four main levels where this cost factor increases, for example, from 10 at the chip level to 10,000 at the systems field level. Hence to avoid these large costs, testing at all design levels, from the chip to the system, is important. Testing at the chip level, the most complex of the three levels, due to the large number of faults and inability to probe internal nodes,

requires detecting faults present at any of the internal nodes of the chip. Testing for faults on board-level wires and on connections between boards are required at the board and system level respectively. At these later two levels, the number of faults is smaller and most can be directly probed on board or at the system level interconnections between boards. We will concentrate our discussion in this book on chip level testing. The degree to which test is important may also depend upon the application. For example in military, avionics or automobile applications the test requirements may be very high.

Two related topics in test are redundancy and diagnosability. Redundancy at the systems level is very useful for fault tolerant design. However at the chip level redundancy leads to undetectable faults thus causing problems. We will not discuss system level redundancy. Determining why a chip is failing or where the fault exists is the purpose of a diagnosis test tool. These test tools maintain diagnostic libraries which relate output responses to faulty nodes. Diagnosis will not be discussed in this book.

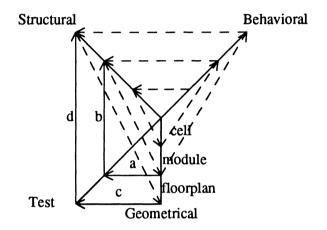

The test stage is most traditionally viewed as occurring after the layout stage (Agrawal, 1984) . In particular for through-the-pins-testing the test vectors may be generated after layout and often this test generation process could continue until the fabricated chips are returned from the foundry. For structured design techniques the incorporation of scan registers would occur after the structural design is completed before layout. However the scan chain interconnection may occur after layout as in (Agrawal, 1984) . We could view the test process as a perpendicular line extending from the Y chart as shown in figure 1.3. In this figure the test stage can be performed after the system is laid out by arrow c. In structured test, transition a, b and c would occur. If test constraints are not met, the transition arrow, d, from the test axis to the structural axis illustrates the required redesign for testability. This may also occur if the area and time constraints are exceeded during the test stage.

Figure 1.3. Modification of the Y chart to include the test stage.

The test problem is further complicated by the fact that as the number of transistors increase (from VLSI to ULSI) the number of primary inputs and outputs (or those accessible by pins of chip) do not proportionately increase (Tsui, 1986). Thus it becomes even more difficult to access internal nodes of the chip for control and observation by using through the pins testing. The test generation problem for combinational circuits is NP-complete (Ibarra, 1975, Fujiwara, 1982, Aho, 1974). The structured design for test problem, discussed in section 11.3, has also been shown to be NP-complete (Craig, 1988). Approaches to the test problem are discussed in detail in sections 11.2 and 11.3.

structured design for techniques test have been automated (Agrawal, 1984, Craig, 1988) . and some research such as (Abadir, 1985, Beausang, 1987) and (Fung, 1986, Gebotys, 1989) have discussed and published their integration of synthesis with test. These will be discussed in section 11.3 and 11.6.

### **1.5 BOTTLENECKS AND OPEN ISSUES**

One high level bottleneck of the VLSI design cycle is the integration and synthesis of analog and digital behavioral specifications of a VLSI system. Different design methodologies and complex interfaces between the two domains pose many challenges for the design automation industry. There is a lack of DA tools to support these designs and currently industry relies on the communication between designers to define and design a correct interface. It has been estimated in the literature that it would take a larger effort than the design itself to take a self contained synchronous synthesized design and modify it to interface to other hybrid processes (Zahir, 1989).

Since the design cycle steps are interdependent, low level bottlenecks can be partially alleviated by better high level design exploration. For example an architecture with fewer interconnect will decrease the problems at the lower level by easing the layout task to be performed. This is one example of relationship between the technology and the high level design.

In summary there exist a number of open problems in high level CAD for VLSI. The problems we will focus on are related to high level behavioral synthesis and are outlined below. In addition we believe these play a major role in currently preventing the high level tools from being accepted in industry.

- 1. Support for complex interfaces and timing constraints.

- 2. Optimized architectures for area-delay cost functions.

- 3. Long testing times for complex VLSI designs.

Problem one defines a realistic need to provide practical and usable tools for the mixed analog and digital or large systems VLSI design. Problem two delineates the requirement to make better decisions at the high level by providing DA tools which can communicate between different methodologies and make accurate estimates of the effect of high level decisions on the final systems design. Area (Sarma, 1990) and delay optimized architectures must be synthesized by these tools. The third problem defines a need to efficiently test a design to increase the probability that there exists no functional, logical, or performance errors in the fabricated chip. One possible solution to all these problems is to provide a rigorous adaptable mathematical framework (Gebotys, 1991x) which can support optimized design exploration. In addition it should model complex timing constraints and interfaces which may be combinations of of digital synchronous, asynchronous or analog processing units.

State of the art synthesizers to date can find at best "locally optimal" architectures with respect to an area delay cost function, and support simple timing constraints. Very few synthesizers have demonstrated how to use regularity and hierarchy of input algorithms to decrease the problem complexity. Hardly any architectural synthesizers at all even consider testability. We will focus on these problems in the next section and later in the text present a methodology to solve and advance the state of the art.

## **1.6 FOCUS OF TEXT**

The aim of this text is to attack the three open high level CAD issues addressed in the previous section. Our solution is to provide a digital synchronous architectural synthesis tool which supports interfaces between different domains such as separately clocked synchronous processes, asynchronous circuits, and analog signal processing modules. The new general contributions of this research are outlined in the five points below.

- 1. Cost-constrained optimized high level VLSI architectural synthesis of digital synchronous systems.

- 2. Both local and complex timing constraints are to be supported for interfacing to asynchronous, analog or other external processes.

- To provide a theoretical framework in which synthesis design automation tools can be developed for different types of architectures and clocking.

- 4. To explore a new mathematical approach to solving the synthesis problem. This approach involves a polyhedral approach aimed at providing global optimum solutions.

- 5. Ensure designs are testable at the architectural level through exploring design for test plans and structures.

We will not address other fields of synthesis such as logic (or controller) synthesis. Higher level behavioral partitioning techniques and transformations (such as those used in optimizing compilers) will also not be addressed, except to show how we can use their output for concurrent architectural synthesis whose inputs are partitioned behaviors or transformed code. In this chapter we have looked at how problems in architectural synthesis impact higher level problems of system design and lower level problems such as routing. It was also outlined in general how improvements in architectural synthesis will improve the overall VLSI design cycle time. The next chapter will look closer at architectural synthesis with respect to its input and output primitives. The definition of input primitives for defining interfaces to external processes such as analog or asynchronous signal processing are also presented. Support for these interfaces are necessary in order for architectural synthesizers to have an impact on industry. It is our opinion that generally they have not received enough attention. 2.

## **BEHAVIORAL AND STRUCTURAL INTERFACES**

This chapter will briefly discuss the structure of input and output primitives for high level architectural synthesis tools. The general structure of the behavioral input to an architectural synthesizer and a definition of its interface to external processes will follow below. Interface descriptions for analog and asynchronous or data dependent tasks are examined. Both the definition of a schedule and the specification of hardware primitives output from an architectural synthesizer are also included.

## 2.1 INPUT TO AN ARCHITECTURAL SYNTHESIZER

There have been many different languages and types of flow graphs constructed for describing behavioral input to previous architectural synthesizers, however we will not review these in detail (Barbacci, 1981, Kuchcinski, 1988). Unfortunately there are no standards for input languages of architectural synthesis. We will examine why a generalized directed acyclic graph (or generalized DAG) is in our opinion the most useful input representation for architectural synthesis even if it is not explicitly constructed. The DAG also serves as an important medium for describing the function of different architectural synthesis subtasks (McFarland, 1988).

There are many different types of behavior (or input algorithms) ranging from matrix multiplication (and digital filters) to communication protocols. The representation of control in a behavioral description will also be outlined. The difference between controller synthesis and architectural synthesis is defined with respect to the input primitives, output primitives, and their mapping of software to hardware (driven by the implementation technology of output primitives).

### **Flow Graphs**

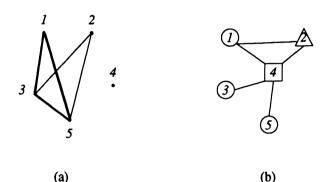

Compilers have an intermediate form consisting of a mixture of flow graphs and DAGs. These intermediate forms play an important role in the efficient mapping of software to hardware especially for multiprocessor architectures. The DAGs in general provide an excellent medium for parallelism extraction and are used in conjunction with flow graphs in many optimizing compilers (Ellis, 1986). The flow graphs, defined in compiler theory (Aho, 1974), are used to define the control of a software specification. The nodes of the flow graph represent computations to be performed. These computations are essentially basic blocks of code, represented by DAGs. Basic block of code represent straight line code, which is code that contains no branch or loop constructs. An algorithm for constructing a DAG from straight line code is given in (Aho, 1974). The arcs of the flow graph represent the flow of control. For example figure 2.1 illustrates the control and data flow graphs

merged for representation of an input algorithm. The loop has an arc originating and terminating at the node representing the code inside the loop.

Figure 2.1. Merged DAG and flow graph for input representation for architectural synthesis.

In architectural synthesis many researchers have tried to merge the two graphs so there exists one medium with both control and data constructs. At a higher level there have been a number of languages introduced for input to architectural synthesis, such as ISPS (Barbacci, 1981), Pascal (Kuchcinski, 1988), and many others such as VHDL (which is also used as a standard for all levels of CAD representation). These languages have intermediate forms which bare some resemblance to DAGs, such as the value trace (Walker, 1987).

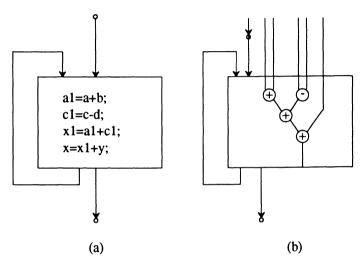

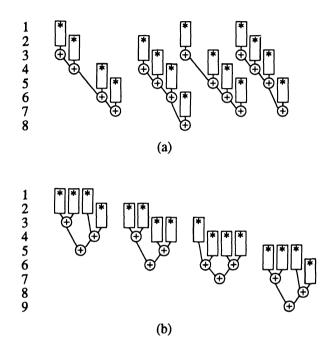

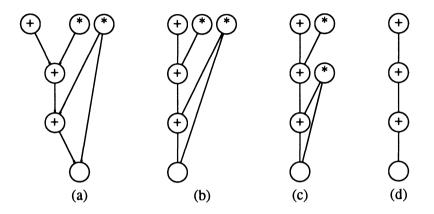

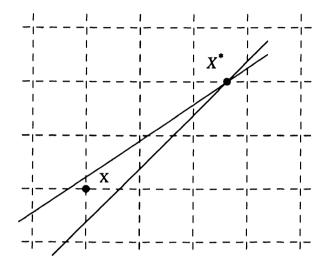

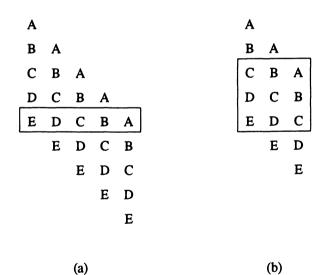

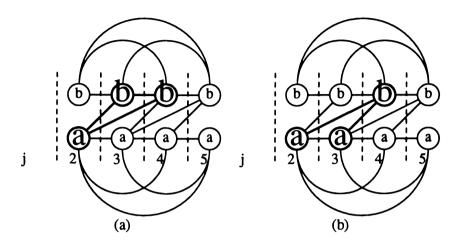

In the following discussion we will demonstrate why DAGs in a flow graph can in fact represent more information than some higher level languages. Let us consider the following example of a matrix multiplication. In a mathematical notation it is:  $Ac^T = b$  or  $\sum_{i} a_{i,j}c_j$ ,  $\forall i$ . and in a algorithmic notation it is: for (i=1,...,m) { $b_0=0$ ; for (j=1,...,n) $\{b_j=b_{j-1}+a_{i,j}c_j\}$ . This can be represented as a number of different types of DAGs depending upon the order of operations. Each DAG may have significant differences in lower bounds on execution time. For example in (Papadimitriou, 1990) execution time is to be minimized and an infinite or very large number of processors are available. Therefore in their DAG, a tree is formed with multiplication operations at the leaves (degree one) and other nodes (of degree three) are the addition operations. A DAG is formed for each  $b_i$  calculation. This DAG is shown in figure 2.2b), where 9 clock periods are required for three multipliers and three adders. However in another application where accuracy of the computation is very important, the algorithm can be implemented as multiplier accumulator streams shown in figure 2.2a), requiring 8 clock periods for three adders and three multipliers. Each DAG may compute different values due to the ordering of the operations and error truncation. In this example and others the DAG offers the clearest representation for input to a high level architectural synthesizer as compared with languages that do not specify the order of operations. In summary we will focus on the mapping of the DAG to optimized hardware as opposed to the problem (ie. matrix multiplication) which may be represented by many different DAGs.

Instead of using a single language that many readers may not be familiar with we will instead use the generalized DAG, illustrated in figure 2.1, as the notation to represent an input primitive throughout this text. This avoids the ambiguity of operation ordering in languages and provides a good example for illustrating the architectural synthesis subtasks. In summary the notation uses control nodes (for branches, joins, etc), operation nodes, arcs for data transfer (and hence implied partial order),

Figure 2.2. Impact of order of operations on the DAG formation.

arcs for partial order alone, and the specification of timing constraints.

#### **2.2 INTERFACE PRIMITIVES FOR EXTERNAL PROCESSES**

The definition of an interface is perhaps one of the most important features for behavioral input description for an architectural synthesizer, yet it has not been given enough attention in the architectural synthesis field. Previous researchers had assumed that the interface was not critical to the system performance and post processing was used to synthesize circuitry (Borriello, 1987). Interfaces are very important since most custom chips are not designed as standalone systems. Very often a correct architecture or schedule cannot be guaranteed unless interface constraints are obeyed. In such cases, interface constraints may have a significant impact on the final speed or area of the chip. The complexity of an interface may vary from a simple data transfer off of a chip, to requesting data from a cache controller that is shared with other processes. In the later case the transfer of the requested data may occur after an unknown amount of time.

We will present four categories of interfaces and show how all other instances of interface constraints, that we know of, can be mapped into these categories. Secondly we will show that it is necessary to know or estimate the clock period of the design to be synthesized. The controller and architecture synthesized are responsible for transfer of data to and from interface circuitry at valid times in the most optimal manner. In the most optimal manner may mean to minimize the total execution time and therefore process the incoming data as soon as it arrives.

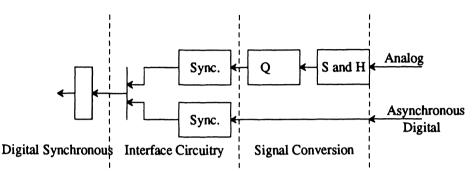

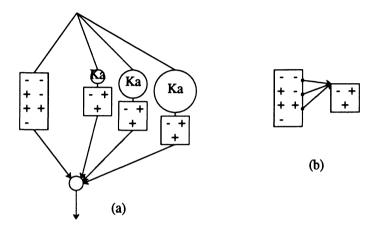

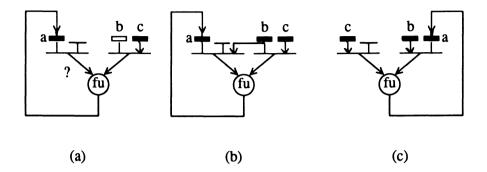

#### The Boundary

The four categories of interface constraints are (1) local, (2) analog, (3) asynchronous bounded and (4) asynchronous unbounded. Some local interface constraints are minimum, maximum or a combination of both timing constraints. The more complex constraints, (2) through (4), involve interfacing to analog or asynchronous processes. An example of the different layers of circuitry required to interface an external analog or asynchronous process with a digital synchronous process is shown in figure 2.3. The far left dashed line indicates the division of circuitry that we are concerned with. To the left of this line is the digital synchronous circuitry that will be synthesized. The multiplexor is used for illustrations purposes only. The first input to the multiplexor is an analog interface. An example of this interface is sampling an analog signal at a fixed rate and transforming this signal into a digital value (using an analog to digital converter circuit, ie. performing sample and hold (S&H) which outputs analog discrete time signals, and quantization (Q) which outputs digital discrete time signals) to enable subsequent digital signal processing. We will therefore define an *analog interface* to a synchronous digital circuit as a sequential synchronous data input or data output at a fixed rate. The third and fourth categories of interfaces are asynchronous interfaces. An asynchronous interface of a digital synchronous system is defined as inputs synchronized with the global clock but are indeterminate with respect to the control state of the system (Hayati, 1989). In figure 2.3 a synchronizer (Synch.) is used to illustrate the possibility of having to synchronize the external signal with the clock of the digital component being synthesized. An example of an asynchronous interface is receiving data input from asynchronous circuitry or data dependent operations. Other examples of an asynchronous interface can result from transferring data between two synchronized processes, where each process uses a different local clock. It may also be possible that the two processes are using the same global clock, but the processes are loosely coupled causing the delay in clock signal to vary and therefore behave as if it were an asynchronous interface. Another example is the transfer of data (not necessarily at a fixed rate) to an analog process (DAC) for analog signal processing and subsequent receipt of the new analog processed output data (ADC). In this case we do not particularly care whether the external process is analog or digital. We can use an asynchronous interface if the processing time is data dependent or we can use minimum and maximum constraints otherwise.

#### **Minimum and Maximum Delay Constraints**

There exist many examples of minimum and maximum timing constraints. These constraints may also be applied locally to a DAG for example to describe a delay of two clock periods (or control states) for a multiplication operation. In this case a minimum timing constraint between the multiplication operation and the next operation which receives the output data can be used to represent extra clock periods

Figure 2.3. Levels of Interface between digital synchronous circuitry and external processes.

required by the multiplication to perform its function. In an interface scenario, the minimum and maximum timing constraints are also very important. For example if the output data must be valid in an output port register for at least three clock periods, in order for an external process to read the data, then a minimum timing constraint of three clock periods is required on the storage of the variable. On the other hand if incoming data is only valid at an input port for three clock periods then a maximum timing constraint of three clock periods then a maximum timing constraint of three clock periods on all operations which use this variable is required.

#### **Analog Interface**

There exist many examples of analog interfaces, as defined in this chapter. Let us assume that  $t_c$  is the period of the clock (in nanoseconds), and the incoming data,  $d_s$ , is arriving at a fixed rate of one sample every  $j_s$  clock periods (or every  $t_s$  nanoseconds), where  $j_s = \lfloor t_s/t_c \rfloor$ ,  $t_s \ge t_c$ . If  $t_s \le t_c$  then we assume a high speed interface will collect the data into a large register (or queue) which is available to the

synchronized system to be synthesized at each clock cycle. Other choices for the design with high speed interfaces will be discussed in chapter 5. Also let us assume that the digital synchronous behavior to be synthesized must ensure that all initial computations on the previous incoming data  $d_s$  have already been completed before the next data value arrives. Operations which input  $d_s$  must be scheduled after  $d_s$  arrives and before  $d_{s+1}$  arrives. Assuming the same computation is to be performed on each incoming data value then the algorithm would be a part of a loop, where at each iteration new data is received. Therefore a fixed timing constraint between operations which input  $d_i$  in successive iterations of i should be equal to the  $j_s$ .

#### **Asynchronous Interfaces**

We will now study the impact of asynchronous interfaces on digital architectural synthesis. As discussed in the previous section this is not necessarily an interface with asynchronous circuitry, but may also include interfaces to data dependent processes (Ku, 1989a). Two types of asynchronous interfaces are discussed below, bounded and unbounded. We will show that the later case can be transformed into a bounded and wait-state interface. These interfaces are quite complex and impact both the scheduling of the DAG and the allocation of hardware. We will further discuss these interactions in chapter 7.

#### **Bounded Delays.**

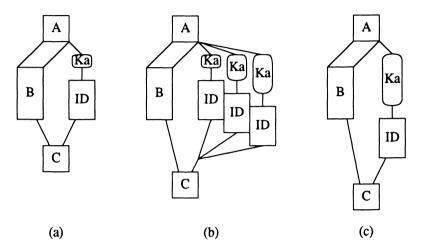

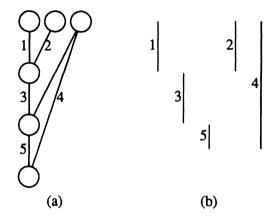

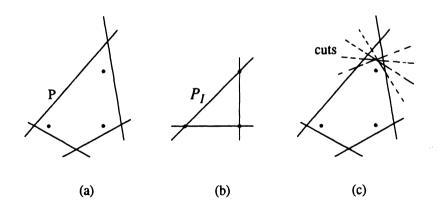

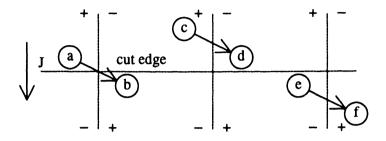

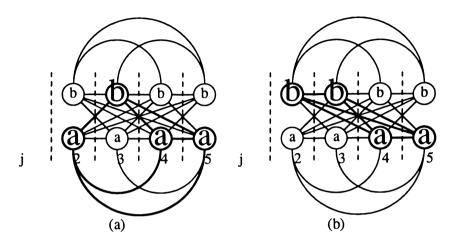

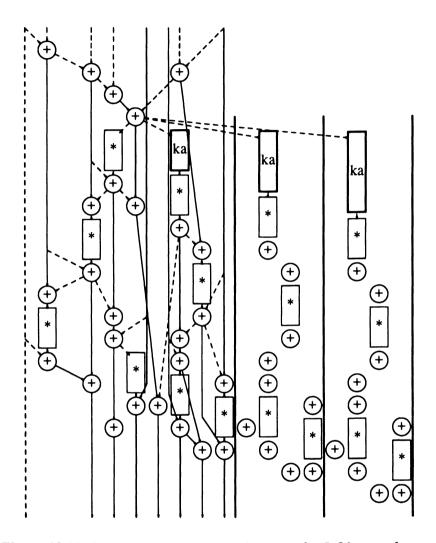

A bounded asynchronous interface is defined as an asynchronous interface where the lower bounds and upper bounds on the indeterminate control state are known. The bounded asynchronous interface can be represented by constructing a flow graph from the DAG with the asynchronous interface. In figure 2.4 a) the DAG is transformed into the flow graph of 2.4b) where the bound of three clock periods for receiving data

from  $K_a$  is represented as a three way branch, starting after basic block (defined in section 2.1) A, with a delay of one cstep for each branch. Before the three way branch is placed in the DAG the operations must be partitioned into interface dependent and interface independent basic blocks. In the first case an operation is *interface dependent* if there exists a path from the vertex representing the asynchronous operation to the vertex of the specific code operation (ID and C are interface dependent in figure 2.4). If there is no path between these two operations in the DAG then the operation is interface independent (such as the basic block of code B in figure 2.4). The flow graph is constructed by placing interface dependent operations in a separate basic block. The interface independent basic block may eventually end, at a particular control state, after which all code operations must precede the interface dependent code (in figure 2.4 basic block C is all interface dependent code).

#### **Unbounded Delays.**

Unbounded or  $\infty$  bounded asynchronous interfaces are asynchronous interfaces where the bound on the control states is not known; for example designing with a synchronizer, or data dependent loops. An example of a general DAG with unbounded delays can be shown in figure 2.4c). Although most researchers discuss partitioning the graph at the  $\infty$ bounded operation vertices, we will discuss a different partitioning into three groups of operations for DAGs where the interface independent basic block ends before the interface dependent operations as shown in figure 2.4b). In these cases the  $\infty$  bound can be removed and it is possible to decompose the unbounded interface into a bounded interface and a wait state. The bounded interface occurs from the earliest control state that the asynchronous operation may output data to the last control state required to complete the interface independent code. In figure 2.4c) this requires the three way branch. After this cstep, if data is still not available from the external process, the controller must essentially wait (ie.

Figure 2.4. Bounded delay interface illustrated in (a) with code partitioning. In (b) the conditional branches are used to model this bounded delay and the wait state in (c) along with (b) are used to represent an ∞ bounded interface.

perform no operations until the data is available from the asynchronous operation). In figure 2.4c) the schedule and allocation of DAGs with bounded or unbounded interfaces can have a significant impact on controller complexity and area and delay of the architecture.

# 2.3 OUTPUT PRIMITIVES FROM AN ARCHITECTURAL SYNTHESIZER

In this section we will discuss hardware architectural primitives that are used in architectural synthesis. Essentially the hardware primitives are output from the synthesizer and later refined into more detailed modules to be placed and routed. The output primitives are divided into storage primitives, processing elements, and interconnect primitives. Each section below defines the generalized primitives which are necessary to understand architectural synthesis.

#### **Processing Elements**

The processing elements receive input data and after a defined amount of time produce new output data. The processing elements perform computations which we will call functions. This terminology is used to avoid the confusion with the term operations, used to describe the nodes of the DAG or specification of the input algorithm. For example an adder (a processing element) performs the function addition. Some processing elements may have more than one function they can compute. The term functional unit is used to refer to a particular processing element and each functional unit has a corresponding module in the VLSI library of cells. Therefore each functional unit is defined by a set of functions that it can perform. The set of functions of two functional units may or may not overlap. Additionally two functional units may have identical sets of functions but they may require different amounts of time to compute their outputs. To distinguish functional units by these characteristics we use the term, type. The type of a functional unit is the most detail we will use for high level synthesis. For example one type of functional unit is a two cycle multiplier and another is a pipelined multiplier. Both functional units compute the same function, however, their timing characteristics are different. An ALU and an adder are two other types of functional units. For convenience we will illustrate the functional units using a circle or vertically placed rectangle.

#### **Storage Primitives**

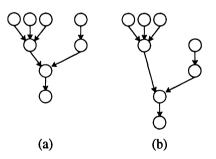

There are many different types of storage primitives. In fact most systems have a hierarchy of storage starting at the bottom level with registers, register files, and moving up to memory caches, main memory, etc. The simplest and most common storage primitives for architectural

32

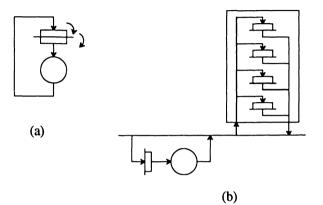

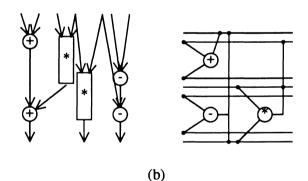

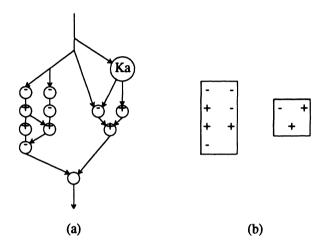

synthesis are the register and register files. Their difference is illustrated in figure 2.5. We will concentrate on *registers*. In phase one of the clock a master/slave register transfers the input data to the output of the register. In other words, a new data value is placed at the inputs of the functional unit. During phase two, the output from the functional unit is latched into the register. Note that the bus is only active during phase two. The register files can be visualized as splitting a register into two latches and moving one latch to a register file and keeping the other latch at the input of the functional unit. When this is done the busses can be used for data transfer during both phases of the clock. Transfer from the register file to the latch at the input of the functional unit occurs at phase one. Phase two transfers the output data from the functional unit onto the bus and into the register file. Phase one in the register file architecture is one example of a storage to storage primitive transfer. It is interesting to note that by using only one bus for input and output from each register file as in (Haroun, 1989) some variables must be stored in more than one register file for concurrent accesses with other variables. This can account for more latches in a register file architecture than registers in a register architecture. We will assume that we are dealing with the register architecture, shown in (a), unless otherwise stated that the architecture is the register file architecture. For illustration purposes registers will be represented by a horizontally placed rectangle with a horizontal line through it to represent the two phase operation.

#### **Interconnect Primitives**

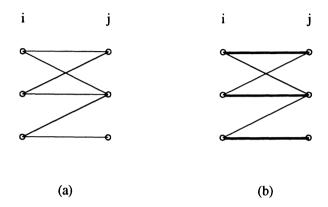

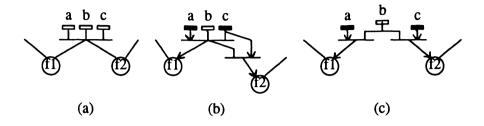

Interconnect primitives are an important part of architectural synthesis, and often the most controversial. Interconnect primitives can include busses, multiplexors, demultiplexors, and multi-level combinations of these interconnects. It is not clear how to measure interconnect so that high level architectural solutions (that have not been placed and routed) can be compared. In the most general terms we will define a

Figure 2.5. An example of (a) the random topology architecture and (b) the register file architecture.

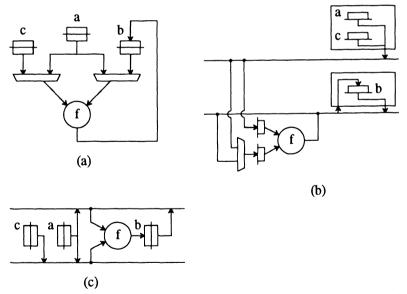

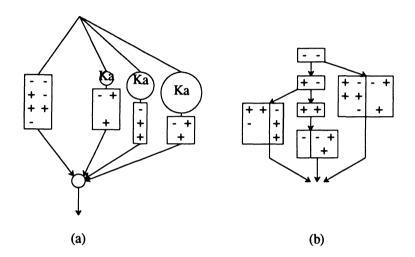

general bus as an interconnection with one or more inputs and one or more outputs. This is a good definition to use since it provides an exact number of general busses at a high level of abstraction, unlike other measures of busses (Haroun, 1989) which do not account for multiplexors at the inputs to registers or functional units. These busses interconnect storage elements to functional units, and vice versa. For example in figure 2.6a) there are 3 busses. The first bus connects registers a and c to functional unit f, the second bus connects register a and b to functional unit f, and finally the third bus connects functional unit f to register b in figure 2.6a). These three busses are also shown in figure 2.6c). In figure 2.6b) there are 2 busses and 1 multiplexor. The two busses are illustrated with horizontal lines and the multiplexor connects both busses to one input latch of functional unit f in figure 2.6b). Using the general bus definition, the architecture in figure 2.6b) also has three busses. This is obtained by adding the number of busses (connecting functional units to register files) to the number of multiplexors (connecting register files to

inputs of functional units). Other measures of complexity have been proposed as counting the number of bus drivers or multiplexor inputs, number of equivalent two to one multiplexors (Ly, 1990) or even the number of connections to busses or multiplexors (Cloutier, 1990). In general there is no standard for comparing interconnects even for solutions using the same type of architecture, for example register architectures. It is clear that for a schedule and an allocation of hardware resources (prior to binding) the only measure one can obtain is the number of general busses. Additionally interconnect primitives, which will not be explicitly analyzed in this manuscript are bus connections or bus drivers, since these are defined during binding.

Figure 2.6. A behavior implemented in (a) random topology and (b) register file architecture, and (c) a random topology with busses instead of multiplexors.

In this chapter we have defined specifically the input/output and interface specifications associated with architectural synthesis. Now that the reader has an idea of what goes in and comes out of an architectural synthesizer we can define the transformations that must be performed in the next chapter. Chapter 3 also gives a brief introduction to previous research in architectural synthesis, concentrating on optimization approaches as opposed to the many heuristics that have been developed. Different approachs to solving architectural synthesis are examined from independent subtask optimizations to more recent simultaneous approaches are covered.

## PART II: REVIEW AND BACKGROUND

3.

### STATE OF THE ART SYNTHESIS

State of the art high level synthesis approaches will be reviewed in this chapter. Each section will provide a definition of the problems and an introduction to the mathematics involved in solving these problems. We examine previous research as it relates to each problem including independent subtask optimizations, simultaneous approaches to synthesis, and mathematical models. In addition we will briefly discuss feasibility models, cost functions, high level partitioning tools and timing considerations in logic and architectural synthesis.

#### 3.1 TERMINOLOGY AND SUBTASK DEFINITIONS

We define some frequently used terms the reader will find helpful in understanding the function of different subtasks of synthesis research. As briefly discussed in section 2.1 there exist various media for input representation. We will assume the most general (intermediate) form of an input algorithm, a directed acyclic graph (DAG), where the nodes represent the code operations, and the directed edges (arcs) represent the variable transfers between code operations. Any algorithm or z-diagram can be represented by a DAG. Hardware output primitives for architectural synthesis were defined in chapter 2. However we will review briefly some additional terminology here. Modules refer to hardware units which will be defined (in functionality) with operations at some later point. Functional units refer to digital hardware units (for example an ALU) that perform a defined set of computations on the input data and provide new output data. For example one functional unit may be a 2 cycle pipelined multiplier and another functional unit may be a 3 cycle non-pipelined multiplier. Scheduling refers to the assignment of code operations to time. Since processing is synchronized with a global clock, time is an integer value. We use the term control step (cstep) to represent the state of the synthesized architecture where control step 1 is present after the architecture is powered up and initialized. The execution time of the algorithm (Te) is defined as the minimum number of csteps required to execute the input algorithm or DAG on the synthesized architecture. Allocation is the determination of the number of hardware units such as functional units, registers, and busses. For example, four registers may be allocated, however the variables that are stored in each register have not yet been determined. A schedule may require 3 modules, which may be defined (through binding code operations; addition and multiplication) as 2 adders and one add/multiply functional unit. If the add/multiply functional unit does not exist in the library then 4 functional units (3 adders and 1 multiplier) may be necessary. The number of modules is a lower bound on the number of functional units to be allocated. In general the term resource will refer to functional units, busses, and registers.

Additional terms will be used to compare with other synthesizer techniques. When one fixes a number of resources, for example one can fix the number of registers at ten, this means that one does not minimize the number of registers, but places an upper bound on the number of registers of ten. *Estimated* refers to using some heuristic to minimize a particular resource. *Calculated* refers to an exact computation of a number of units after a schedule is found. A fixed schedule or hardware allocation means that the schedule or allocation has already been performed by some earlier algorithm and therefore is a constraint on the remaining problem.

The output of the architectural synthesizer that we will address are the following:

- total number of control steps, functional units, busses and/or multiplexors, registers and/or register files, memory.

- *scheduling*: code operations to control steps.

- functional unit allocation and selection

- register allocation

- interconnect allocation

The hardware units listed above were defined in section 2.3. One must also determine the type of hardware (type of functional units or memory versus registers) to be used in the final architecture. In some cases the former is done during architectural synthesis. The final schedule and binding produced by the architectural synthesizer can be transformed into a control table for input to a logic synthesizer.

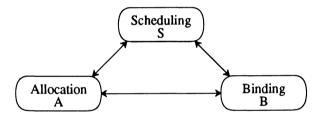

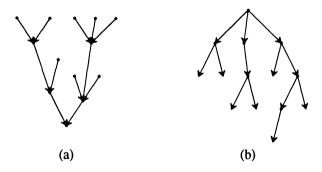

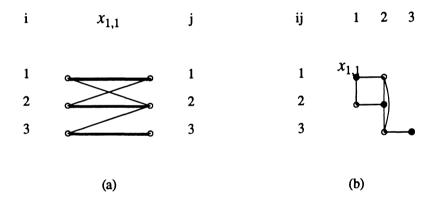

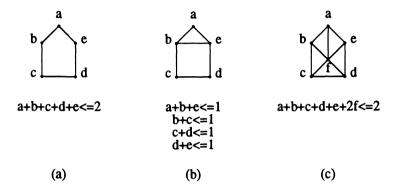

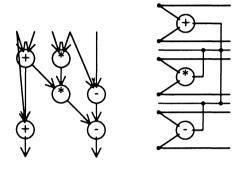

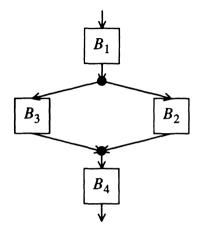

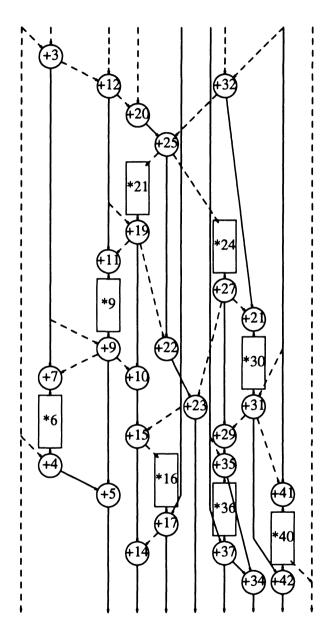

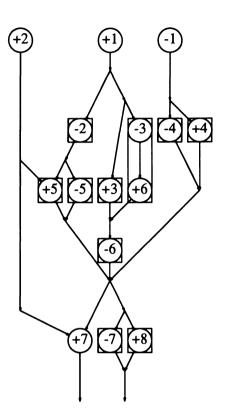

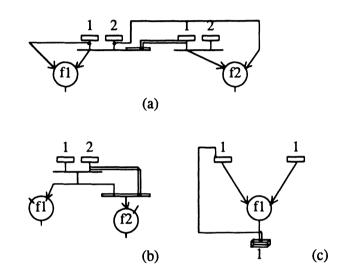

The architectural synthesis problem involves many subtasks such as scheduling (S), resource allocation (A), and resource binding (B). We will use the term resource to describe the hardware primitives or registers, functional units, and busses. However each of these steps are heavily interdependent. An example of the interdependence between the subtasks is shown in figure 3.1. For example a fixed schedule directly determines the minimum number of functional units and registers (allocation). The subsequent binding of these resources directly determines the minimum number of multiplexors (allocation) required in a multiplexed architecture ( $S \Rightarrow A \Leftrightarrow B$ ). Another design approach which illustrates the interdependence in figure 3.1 is to first perform resource allocation. This allocation will constrain the scheduling and subsequently constrain the binding ( $A \Rightarrow S \Rightarrow B$ ). It is also easy to see that binding affects scheduling ( $B \Rightarrow S$ ). For example operations bound to the same resource cannot be scheduled at the same time.

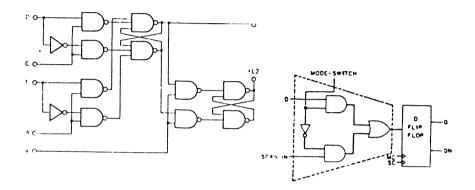

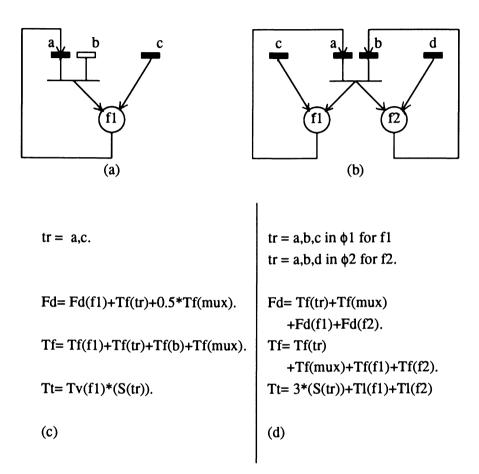

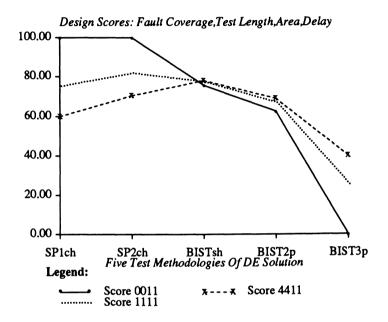

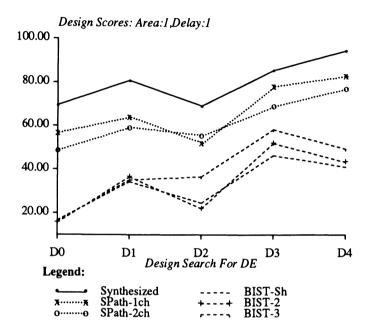

Figure 3.1. Subtask interdependence in architectural synthesis.

Ideally the optimal approach to solving architectural synthesis is to simultaneously consider all tasks at the same time. However since this is a very complex approach most researchers have concentrated on one or a limited number of subtasks to be solved simultaneously. We will briefly review research in this field with emphasis on graph theoretical results and integer programming (IP) approaches. We will describe the complexity of these subtasks and overview the iterative/simultaneous approaches to architectural synthesis. More detailed analysis of architectural synthesis material can be found in papers such as (McFarland, 1988, McFarland, 1990).

#### **3.2 HIGH LEVEL TRANSFORMATIONS**

Many high level transformations of algorithms for architectural synthesis have been borrowed from compiler research (Aho, 1974) We will concentrate on reviewing partitioning of behaviors and some (compilerlike) transformations used within the context of architectural synthesis.

Partitioning of behavioral descriptions for architectural synthesis of multichips has been investigated by a number of different researchers. APARTY (Lagnese, 1989) evaluates different partitions of the DAG but schedules the graph entirely without partitions. The algorithm passes heuristic suggestions to other allocation and binding subtasks to use partitioning information only during allocation. This occurs because it is not known how to define interfaces between the partitioned behavioral specifications in order that they be concurrently and independently synthesized. Also in (Gupta, 1990) partitioning of behavioral specifications is performed after a binding (which defines hardware sharing) for multichip design. The hypergraph partitioning bounds the latency of the partitioned implementation.

Other research (Depuydt, 1990) deals with partitioning large complex signal flow graphs. Various clustering techniques are used to partition into more manageable sized flow graphs for separate scheduling using better or more optimal techniques which work well on smaller input flow graphs.

Research at Carnegie Mellon University (Walker, 1987) has examined implementation of behavioral code transformations in a user interface environment that is tied into their architectural synthesizers, DAA. Although these transformations are the same as those found in optimizing compilers <sup>1</sup> (Ellis, 1986), it is unknown what effect the transformations have on the final architectural synthesized design.

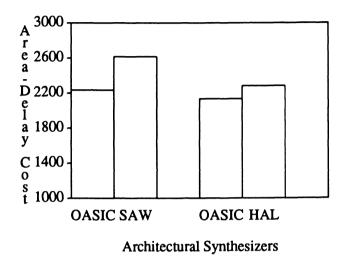

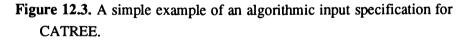

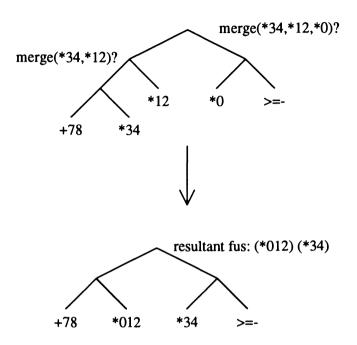

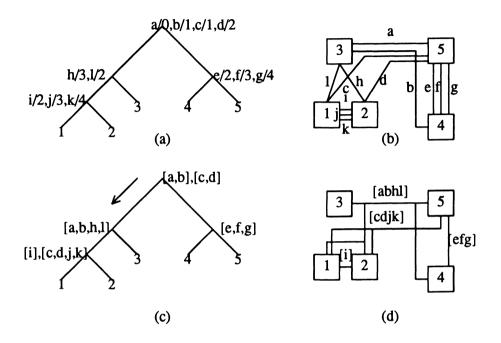

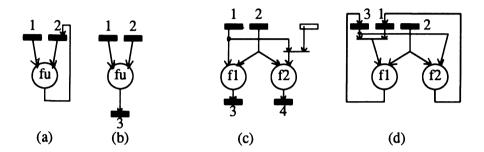

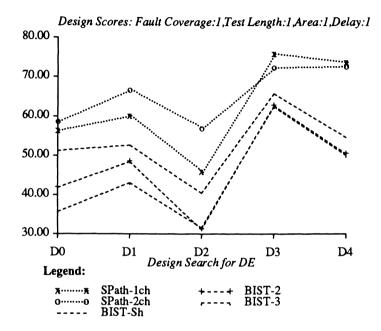

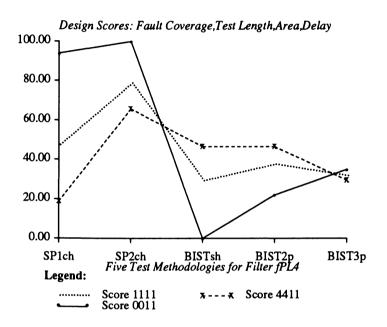

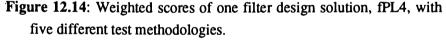

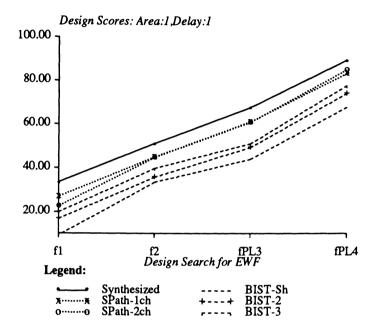

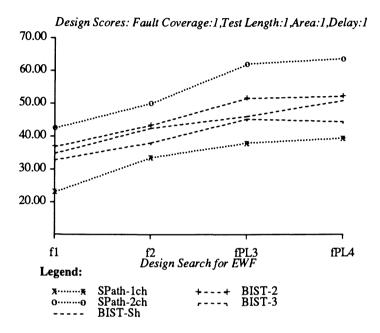

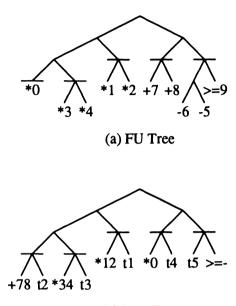

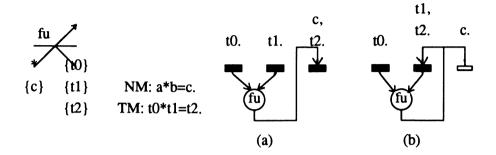

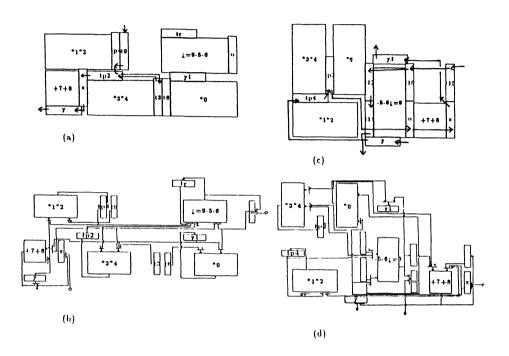

<sup>1</sup> Optimizing compilers do not optimize, but they heuristically attempt to extract further parallelism from the input code.