## Practical Guide to Organic Field-Effect Transistor Circuit Design

**Antony Sou**

### Practical Guide to Organic Field-Effect Transistor Circuit Design

**Antony Sou**

A Smithers Group Company

Shawbury, Shrewsbury, Shropshire, SY4 4NR, United Kingdom Telephone: +44 (0)1939 250383 Fax: +44 (0)1939 251118 http://www.polymer-books.com

#### First Published in 2016 by

#### Smithers Rapra Technology Ltd

Shawbury, Shrewsbury, Shropshire, SY4 4NR, UK

© 2016, Smithers Rapra Technology Ltd

All rights reserved. Except as permitted under current legislation no part of this publication may be photocopied, reproduced or distributed in anyform or by any means or stored in a database or retrieval system, without the prior permission from the copyright holder.

A catalogue record for this book is available from the British Library.

Every effort has been made to contact copyright holders of any material reproduced within the text and the authors and publishers apologise if any have been overlooked.

ISBN: 978-1-91024-270-4 (softback) 978-1-91024-271-1 (ebook)

Typeset by Integra Software Services Pvt. Ltd.

# Preface

Currently, the field of organic transistor design is fascinating in its breadth and depth. It is at that early stage in its life cycle where the understanding and knowledge of *everything organic* are still accessible. This makes organic electronics a natural melting pot for physicists, chemists, circuit designers, and modelling engineers to come together. However, it also makes it difficult for small research groups to move beyond their usual boundaries. Until now there has been no single concise and coherent work adequately spanning this broad field. This book aims to guide the reader through these different branches with a straightforward text covering the physics and chemistry of the materials, the software construction of the simulation models, and the engineering challenges of the design flow and circuit design.

This book is intended for two main readerships: firstly, physics researchers who have thus far designed circuits using only basic drawing software; secondly, silicon CMOS VLSI Design engineers who are already experienced in the design of full custom transistor level circuits but are not familiar with organic devices or thin film transistor devices. Examples of designs, samples, and measurements are given, allowing the reader to see real-world imperfect devices instead of idealised textbook illustrations. After an introduction in Chapter 1, we begin in Chapter 2 with the physics and chemistry of organic materials and the common fabrication methods. The general principles of field-effect transistors are discussed in Chapter 3. Next, the equations of transistor modelling and their translation to a form suitable for simulation are explored in Chapter 4. Chapter 5 describes the design and simulation environments that are necessary to ensure robust reliable design. Finally, all the work dovetails as digital and analogue circuits are described in Chapters 6 and 7.

The devices that were designed, fabricated, and analysed in this book were partly fabricated by Guillaume Fichet, Jerome Joimel, Srinivasan Madabhushi, and Liz Speechley at Plastic Logic (now FlexEnable), and by Sungjune Jung and Enrico Gili at the University of Cambridge Cavendish Laboratory. Any references to Plastic Logic's technology has been with their kind permission, although some commercially sensitive details have been withheld. Additional assistance in the cleanroom and labs was provided by Lang Jiang and Vincenzo Pecunia, while further general discussion, conversation, and amusement were amply furnished by Kal Banger, Tom Kehoe, and the entire Optoelectronics department. Furthermore, I am extremely grateful to Professor Henning Sirringhaus for his advice and guidance, and also to Professor

#### Practical Guide to Organic Field-Effect Transistor Circuit Design

Andrew Flewitt who has been a source of help throughout. This book, and the research from whence it came, would not have been possible without the patience, encouragement, and occasional chiding of my wife Tina, and my daughters Louisa and Alicia.

Antony Sou

# ontents

| Pre | face                     | •••••                    | •••••       |                            | iii |

|-----|--------------------------|--------------------------|-------------|----------------------------|-----|

| 1   | Intro                    | oduction                 | l <b></b>   |                            | 1   |

|     | References               |                          |             |                            | 3   |

| 2   | Organic Semiconductors   |                          |             |                            |     |

|     | 2.1                      |                          |             |                            |     |

|     | 2.1                      |                          | ntroduction |                            |     |

|     |                          |                          |             |                            |     |

|     | 2.3                      | Charge Carrier Transport |             |                            |     |

|     |                          | 2.3.1                    |             | Transport                  |     |

|     | 2.4                      | 2.3.2                    | _           | Trap and Release           |     |

|     | 2.4                      |                          |             |                            |     |

|     |                          | 2.4.1                    |             | ductors                    |     |

|     |                          |                          | 2.4.1.1     | Small Molecule             |     |

|     |                          |                          | 2.4.1.2     | ,,                         |     |

|     |                          |                          | 2.4.1.3     | Donor-Acceptor Copolymers  | 11  |

|     |                          | 2.4.2                    | Dielectri   | cs                         |     |

|     | 2.5                      | 2.5 Summary              |             |                            |     |

|     | Refe                     | erences                  |             |                            |     |

| 3   | Field-Effect Transistors |                          |             |                            |     |

|     | 3.1 Introduction         |                          |             |                            | 17  |

|     | 3.2                      |                          |             |                            | 17  |

|     | 3.3 Transistor Operation |                          |             |                            |     |

|     | 3.4                      | *                        |             |                            |     |

|     |                          | 3.4.1                    | _           | ation of Linear Region     |     |

|     |                          | 3.4.2                    |             | ation of Saturation Region |     |

|     |                          |                          | 1           | 8                          |     |

#### Practical Guide to Organic Field-Effect Transistor Circuit Design

|   | 3.5                      | 5 Mobility                                               |                             |    |  |  |

|---|--------------------------|----------------------------------------------------------|-----------------------------|----|--|--|

|   | 3.6                      | Contact Resistance                                       |                             |    |  |  |

|   | 3.7                      | Summary                                                  |                             |    |  |  |

|   | Refe                     | References                                               |                             |    |  |  |

| 4 | Modelling and Simulation |                                                          |                             |    |  |  |

|   | 4.1                      | Introdu                                                  | action                      | 29 |  |  |

|   | 4.2                      |                                                          | Types                       |    |  |  |

|   |                          | 4.2.1                                                    | Physical                    | 30 |  |  |

|   |                          | 4.2.2                                                    | Empirical                   |    |  |  |

|   |                          | 4.2.3                                                    | Table-based Modelling       |    |  |  |

|   | 4.3                      | Organi                                                   | c Models                    |    |  |  |

|   | 4.4                      |                                                          |                             |    |  |  |

|   | 4.5                      | Parame                                                   | eter Extraction             | 34 |  |  |

|   |                          | 4.5.1                                                    | Manual Parameter Extraction | 34 |  |  |

|   |                          | 4.5.2                                                    | Non-Linear Least-Squares    | 35 |  |  |

|   | 4.6                      | Modell                                                   | ing                         | 36 |  |  |

|   |                          | 4.6.1                                                    | Classic MOS Model           | 36 |  |  |

|   |                          | 4.6.2                                                    | Intrinsic Core              | 36 |  |  |

|   |                          | 4.6.3                                                    | Extrinsic Network           | 39 |  |  |

|   | 4.7                      | Transistor Measurements and Parameter Extraction Results |                             |    |  |  |

|   | 4.8                      | Summary                                                  |                             |    |  |  |

|   | Refe                     | erences                                                  |                             | 42 |  |  |

| 5 | Circuit Design           |                                                          |                             |    |  |  |

|   | 5.1                      | 1 Introduction                                           |                             |    |  |  |

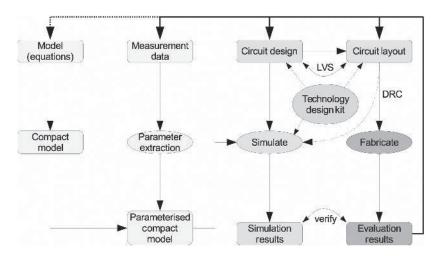

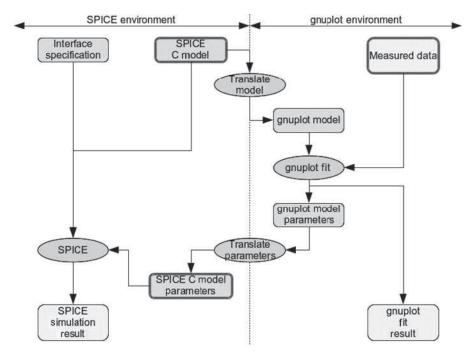

|   | 5.2                      | Design                                                   | Flow                        | 46 |  |  |

|   |                          | 5.2.1                                                    | SPICE                       | 48 |  |  |

|   |                          | 5.2.2                                                    | Electric VLSI Design System | 48 |  |  |

|   |                          | 5.2.3                                                    | gnuplot                     | 49 |  |  |

|   | 5.3                      | Modelling Ecosystem                                      |                             |    |  |  |

|   | 5.4                      | Design                                                   | Tolerances                  | 50 |  |  |

|   |                          | 5.4.1                                                    | Monte Carlo                 | 51 |  |  |

|   |                          | 5 4 2                                                    | Worst Case                  | 52 |  |  |

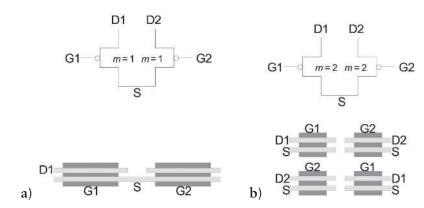

| 5.5         | Layout             | Design    |                                          | 53 |

|-------------|--------------------|-----------|------------------------------------------|----|

| 5.6         | Design for Test    |           |                                          | 53 |

| <b>5.</b> 7 | 7 Multichip Wafers |           |                                          | 55 |

| 5.8         | 8 Summary          |           |                                          | 56 |

| Refe        | erences            |           |                                          | 56 |

| Digital     |                    |           |                                          | 59 |

| 6.1         | Introdu            | duction   |                                          |    |

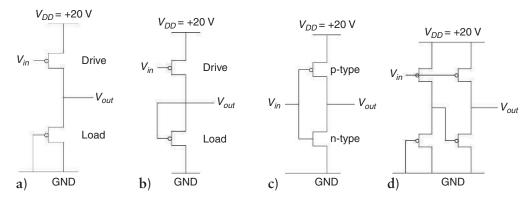

| 6.2         | Logic Types        |           |                                          | 60 |

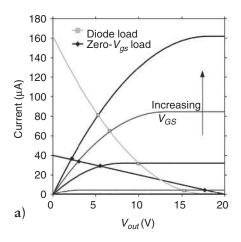

|             | 6.2.1              | Diode-co  | onnected Load                            | 60 |

|             | 6.2.2              | Zero Gat  | te-Source Voltage Load                   | 61 |

|             | 6.2.3              | Complen   | nentary Logic                            | 61 |

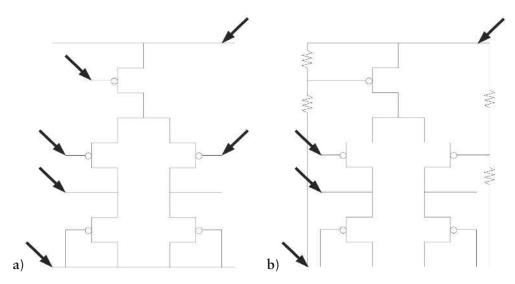

|             | 6.2.4              | Pseudoco  | omplementary Logic                       | 62 |

| 6.3         | Logic Gates        |           |                                          | 63 |

|             | 6.3.1              | Inverter. |                                          | 63 |

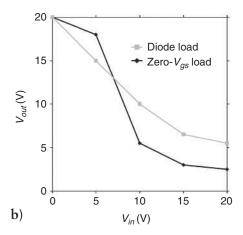

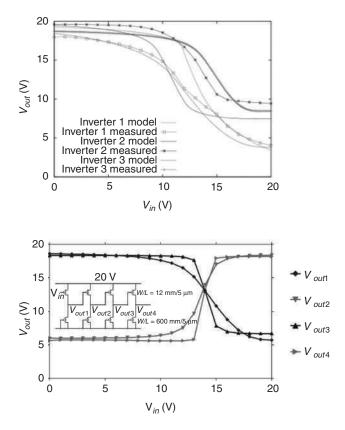

|             |                    | 6.3.1.1   | DC Transfer Characteristics              | 64 |

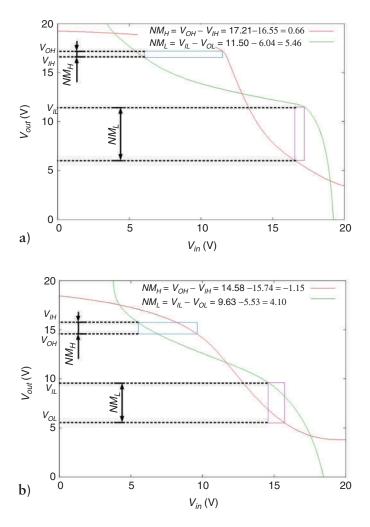

|             |                    | 6.3.1.2   | Noise Margin                             | 65 |

|             |                    | 6.3.1.3   | Monte Carlo Analysis                     | 67 |

|             |                    | 6.3.1.4   | Transient Switching Characteristics      | 68 |

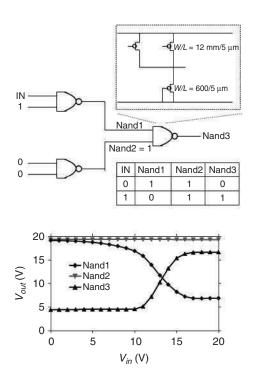

|             | 6.3.2              | Two-Inp   | ut NAND                                  | 69 |

|             | 6.3.3              | 71 1 1 7  |                                          | 71 |

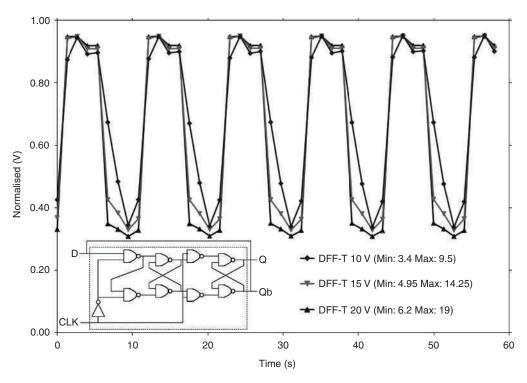

| 6.4         | Digital Subsystems |           |                                          | 73 |

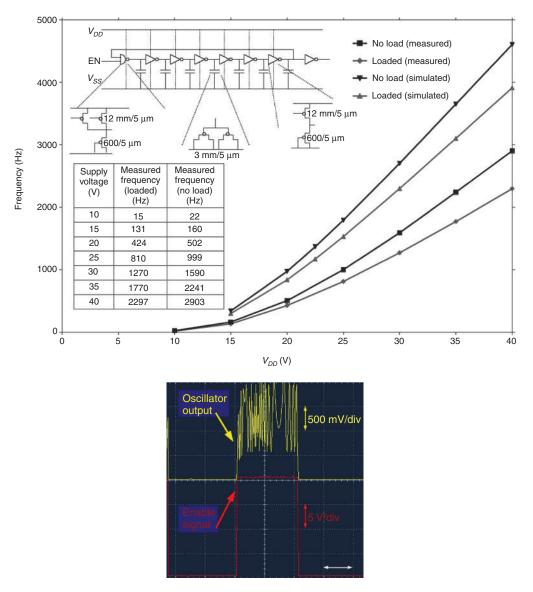

|             | 6.4.1              | Ring Osc  | cillator                                 | 73 |

|             |                    | 6.4.1.1   | 7-Stage Ring Oscillator                  | 73 |

|             |                    | 6.4.1.2   | 9-Stage Ring Oscillator                  | 75 |

|             |                    | 6.4.1.3   | 17-Stage Ring Oscillator (1)             | 75 |

|             |                    | 6.4.1.4   | 17-Stage Ring Oscillator (2)             | 75 |

|             |                    | 6.4.1.5   | Oscillator Summary                       | 75 |

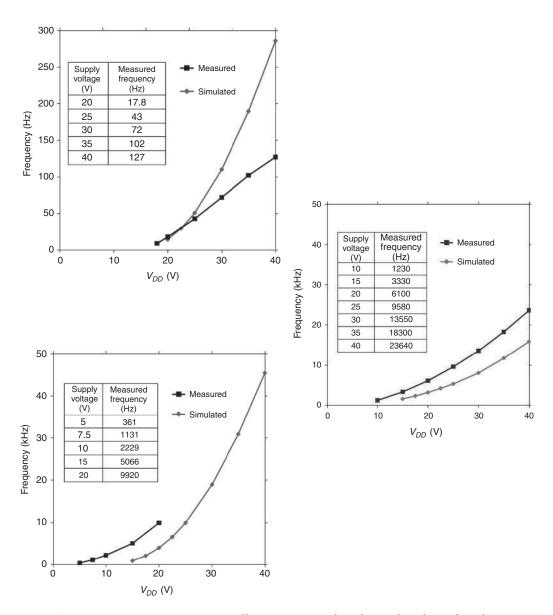

|             |                    | 6.4.1.6   | Monte Carlo Simulations (Yield Analysis) | 78 |

|             |                    | 6.4.1.7   | Worst-case Simulations                   | 78 |

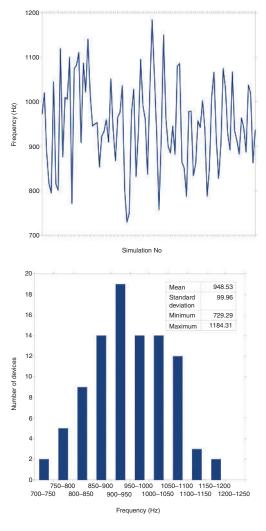

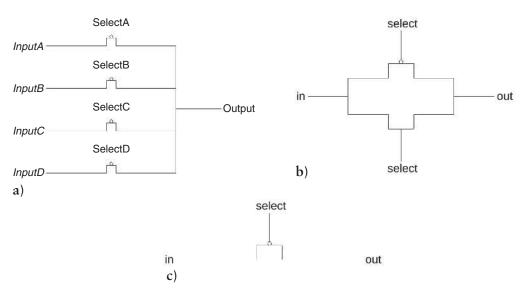

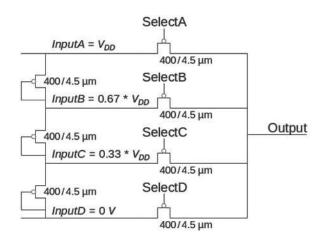

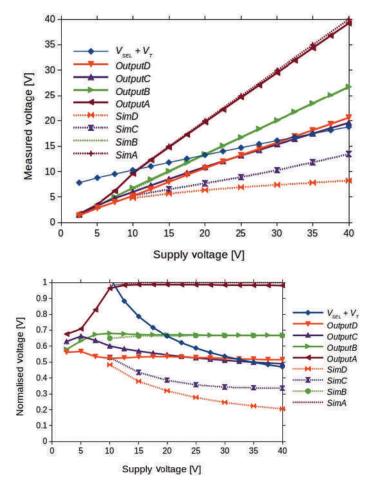

|             | 6.4.2              | Program   | mable Array Logic                        | 80 |

| 6.5         | Summa              | ary       |                                          | 83 |

| Refe        | rences             |           |                                          | 83 |

#### Practical Guide to Organic Field-Effect Transistor Circuit Design

| 7   | Analogue   |                        |                                               | 87  |

|-----|------------|------------------------|-----------------------------------------------|-----|

|     | 7.1        | 1 Introduction         |                                               |     |

|     | 7.2        | Analogue Selector      |                                               | 88  |

|     |            | 7.2.1                  | Description                                   | 88  |

|     |            | 7.2.2                  | Experimental                                  | 89  |

|     |            | 7.2.3                  | Results                                       | 89  |

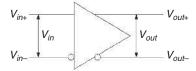

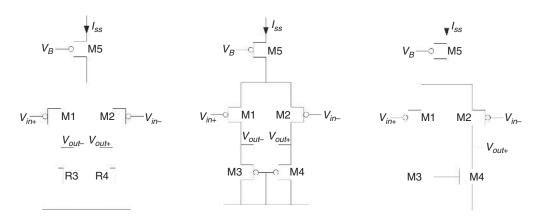

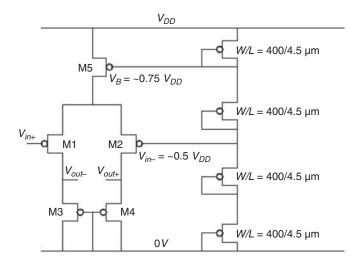

|     | 7.3        | Differential Amplifier |                                               | 92  |

|     |            | 7.3.1                  | Description                                   | 92  |

|     |            | 7.3.2                  | Experimental                                  | 94  |

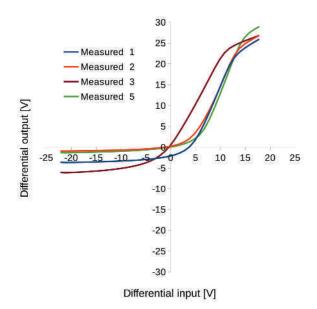

|     |            | 7.3.3                  | Results and Analysis                          | 94  |

|     |            | 7.3.4                  | Monte Carlo Simulation                        | 97  |

|     |            | 7.3.5                  | Comparison with Published Work                | 97  |

|     | 7.4        | Summa                  | ary                                           | 99  |

|     | References |                        |                                               | 100 |

| App | endix      | s Simula               | tion Program with Integrated Circuit Emphasis | 101 |

| Abl | revia      | tions                  |                                               | 107 |

Introduction

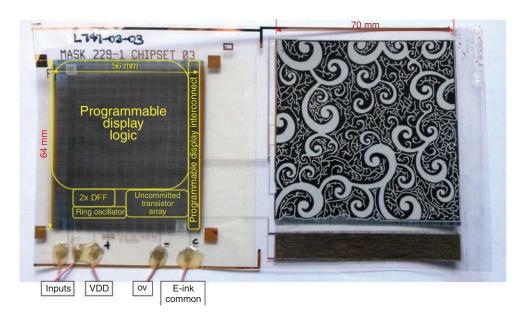

When the first organic field-effect transistor(s) (OFET) was fabricated in 1987 [1], the established microprocessor of the day was the Intel 80386, which had a minimum channel length of 1.5 µm and 275 000 transistors in an area of 104 mm². Nearly 30 years later, the 5.5 billion transistors of the state-of-the-art 18-core Intel Xeon have a minimum channel length of 22 nm in an area of 661 mm². Since that first OFET in 1987, there have also been notable advances in the large-scale integration of organic transistors. Recent publications have demonstrated fairly complex circuit functions such as 8 bit, 64 bit, and 128 bit radio frequency identification tags [2–4], programmable logic devices [5], and an 8 bit microprocessor with 3381 transistors at a channel length of 5 µm [6]. These achievements, which are roughly comparable with the Intel 4004 of 1971, are pushing the current envelope of integrated organic transistor circuit design while also benefiting from some of the main advantages of organic transistor technology, such as large area, flexibility, low-temperature fabrication, and solution processing.

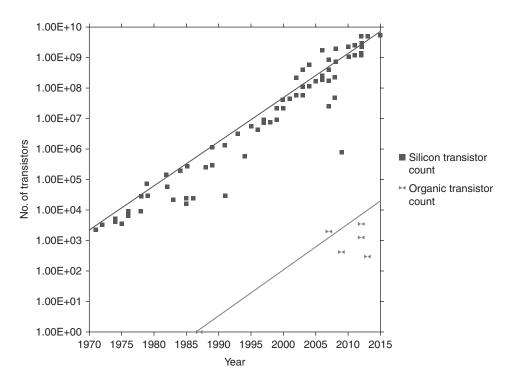

Back in 1965, Gordon Moore, the cofounder of Intel Corporation, observed that the number of transistors on an integrated silicon chip had doubled every year since 1958. This observation, though slightly modified to the doubling of transistors every 2 years, was subsequently coined Moore's law [7]. Remarkably, in its much shorter lifetime, the organic transistor count is increasing at almost the same rate, doubling every 25.5 months (Figure 1.1). As a consequence, organic transistor circuit design is now experiencing the very same growing pains as its silicon counterpart once did. Continuing exponential increases in circuit complexity and transistor density will not be possible unless accompanied with accurate behavioural modelling and structured design flows.

Thus far, the only Nobel Prize that has been awarded in the field of organic electronics was in 2000 to Alan J. Heeger, Alan G. MacDiarmid, and Hideki Shirakawa [8] 'for the discovery and development of conductive polymers'. Their landmark publication in 1977 for their work on synthesising conducting polymers [9] was the first in a series of notable organic electronics discoveries; namely, the organic photovoltaic(s) (OPV) cell (1986), the OFET (1987), and the organic light-emitting diode(s) (OLED) (1987) [10]. Interest in this new field of research and development has since been rapid, with an increase in scientific publications from 80 in 1999, 393 in 2004 [11], to 602 in 2010. Organic electronics is also beginning to attract real industrial interest

on a global scale, with several active companies such as PolyIC, Polyera, Isorg, and Disasolar. A particular hotbed of organic electronics is in Cambridge, UK. There, the Cavendish Laboratory of the University of Cambridge, UK, has spawned three spin-off companies – Eight19, Cambridge Display Technology, and Plastic Logic (now known as FlexEnable) – which are active in their respective fields of OPV, OLED, and OFET and have attracted significant investment.

Figure 1.1 Progression of silicon and organic transistor count on a single chip or foil. Both are exhibiting Moore's law, a doubling of transistors approximately every 2 years [2–4, 6]

Despite their poorer performance when compared with their silicon counterparts, organic semiconductors nevertheless have complementary features that make them suitable for alternative applications. Technologically, organic electronics offer the potential for mechanically flexible or conformable devices covering large areas with solution processing. There is also the tantalising promise of system-on-foil, which is the integration of OPV, OFET, and OLED manufactured in a single fabrication process on a single flexible transparent substrate, as a natural goal of organic research to deliver a very elegant final product. In financial terms, the capital outlay necessary for organic electronics is orders of magnitude less than that of silicon foundries. This makes it a

viable proposition for small and medium-sized companies to research and develop, and hopefully industrialise and commercialise. Environmentally too, processing is cleaner and friendlier at lower, even room, temperatures. The first applications of organic semiconductors that have been announced have been based on a large-area matrix of devices with electronic paper displays from companies such as Plastic Logic, but there is also progress in the logic design of more complex circuits.

#### **References**

- 1. H. Koezuka, A. Tsumura and T. Ando, Synthetic Metals, 1987, 18, 699.

- 2. B.K.C. Kjellander, W.T.T. Smaal, K. Myny, J. Genoe, W. Dehaene, P. Heremans and G.H. Gelinck, *Organic Electronics*, 2013, **18**, 768.

- 3. E. Cantatore, T.C.T. Geuns, G.H. Gelinck, E. van Veenendaal, A.F.A. Gruijthuijsen, L. Schrijnemakers, S. Drews and D.M. de Leeuw, *IEEE Journal of Solid-State Circuits*, 2007, 42, 84.

- 4. K. Myny, S. Steudel, P. Vicca, M.J. Beenhakkers, N.A.J.M. van Aerle, G.H. Gelinck, J. Genoe, W. Dehaene, and P. Heremans, *Solid-State Electronics*, 2009, 53, 1220.

- 5. A. Sou, Sungjune Jung, E. Gili, V. Pecunia, J. Joimel, G. Fichet and H. Sirringhaus, *Organic Electronics*, 2014, 15, 3111.

- 6. K. Myny, E. van Veenendaal, G.H. Gelinck, J. Genoe, W. Dehaene and P. Heremans, *IEEE Journal of Solid-State Circuits*, 2012, 47, 284.

- 7. G.E. Moore, Proceedings of the IEEE, 1998, 86, 82.

- 8. The Nobel Prize in Chemistry 2000, Nobelprize.org, 2000. http://www.nobelprize.org/nobel\_prizes/chemistry/laureates/2000/

- 9. H. Shirakawa, E. Louis, A. MacDiarmid, S. Chiang and A. Heeger, *Journal of the Chemical Society Chemical Communications*, 1977, 16, 578.

- 10. D. Braga and G. Horowitz, Advanced Materials, 2009, 21, 1473.

- 11. H. Sirringhaus, Advanced Materials, 2005, 17, 2411.

## Organic Semiconductors

#### 2.1 Introduction

In order properly to appreciate designing with organic transistors, an understanding of the physics and chemistry of organic semiconductors is helpful. Organic electronics is so called because it is based on the carbon atom, on which all known life is based, hence the term *organic*. The modern plastics industry is built upon the same organic polymers made from chains of carbon atoms, so organic electronics is also more popularly known as plastic electronics. This chapter will start by presenting the molecular structure and charge transport properties of organic semiconductors, before discussing and reviewing the current state-of-the-art organic semiconductor materials [1–4].

#### 2.2 Molecular Structure

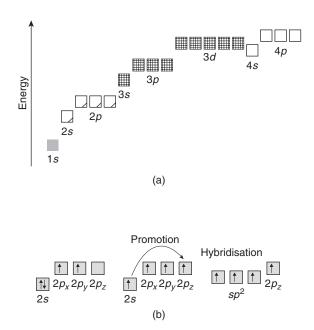

Organic semiconductors are based on the carbon atom, which has four valence electrons, each able to form a covalent single, double, or triple bond with other atoms. The four valence electrons are found in two atomic orbitals – two electrons in the 2s orbital, and two in the 2p orbital. Bonding occurs when atoms share electrons to complete their electron shells, and this proceeds via intermediate steps of promotion, where an electron is promoted from the full 2s to the empty  $2p_z$  energy level to give four unpaired electrons rather than two, and hybridisation to give identical hybrid orbitals [4] (Figure 2.1). These hybrid orbitals have their own distinctive shapes, as follows:

- $sp^3$  hybrid orbitals have four symmetrical fingers in space at 109.5°. In this form, carbon can share four bonds, e.g. CH<sub>4</sub>, where each bond is a very strong  $\sigma$  (sigma) bond. The 109.5° bond angle forms the backbone of many conventional polymers. Diamond is an example of carbon formed entirely from  $\sigma$  bonds.

- $sp^2$  hybrid orbitals have three in-plane fingers at 120° and one perpendicular finger. To form a molecule, another  $sp^2$  hybrid is required. For example, in  $H_2C=CH_2$ , two of the three  $sp^2$  fingers of each carbon bond to hydrogen, and the third  $sp^2$  carbon  $\sigma$  bonds to the other carbon's  $sp^2$ . The remaining electron in the  $p_z$  orbital forms a delocalised weaker  $\pi$  (pi) bond.

• sp hybrid orbitals have two fingers at 180° in one axis and two remaining p orbitals. Carbon will bond with two hydrogens and another sp hybrid, resulting in one  $\sigma$  bond between the sp orbitals and two  $\pi$  bonds with the p orbitals.

Figure 2.1 (a) Orbital energy levels and (b) promotion and  $sp^2$  hybridisation [5]

To lower the overall energy and increase stability, polymer molecules form a conjugated system of connected p orbitals with a backbone based on the hexagonal benzene molecule [e.g., pentacene ( $C_{22}H_{14}$ ), Figure 2.4]. These conjugated molecules have alternating single/double or single/triple carbon bonds in which  $\pi$  electrons are delocalised through the entire molecule. The first arriving electrons cluster closely to the nucleus corresponding to the 1s orbital which does not participate in bonding. The final electrons go into delocalised  $\pi$  orbitals which do contribute to bonding.

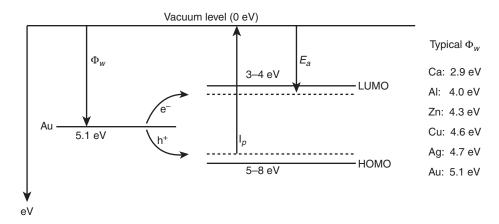

A system of bands for organic semiconductors can also be described. In this case, the last filled pair of electrons occupies a molecular orbit called the highest occupied molecular orbit (HOMO). The next molecular orbit beyond the HOMO, and therefore unfilled, is called the lowest unoccupied molecular orbit (LUMO). In this analogy, the energy difference between the HOMO and the LUMO is also called the bandgap (Figure 2.2).

Figure 2.2 Energy bands in an organic semiconductor at the interface with a metal (gold), and some typical work function values.  $E_a$ : electron affinity;  $I_p$ : ionisation potential; and  $\Phi_w$ : work function

#### 2.3 Charge Carrier Transport

Organic field-effect transistor(s) (OFET) are usually made from undoped materials. As there are no intrinsic carriers present, in order for a current to flow, charge carriers must be injected from the source metal electrode into the semiconductor channel, and collected at the other end of the channel by the drain metal electrode. The injected carriers occupy states in the semiconductor's HOMO and LUMO bands but may also occupy localised states in the bandgap that are induced by defects and unwanted impurities [6]. For the organic semiconductor-metal electrode interface, an ohmic connection is generally not possible, and sometimes exhibits a gate voltage and semiconductor thickness dependency [7, 8] requiring charge carriers to overcome energy barriers before entering or leaving the semiconductor. Organic semiconductors can operate in either electron or hole accumulation modes, or both in the case of ambipolar devices, depending on the polarity of the gate voltage. The amount and type of carrier injection is determined by the  $\Phi_w$  of the metal electrode and the  $E_a$ of the semiconductor for electron injection or the  $I_p$  of the semiconductor for hole injection. The energy barriers presented at the source and drain electrodes usually limit the devices to unipolar electron or hole accumulation mode operation only. Some typical metal work function values are shown in Figure 2.2.

After carriers have been injected into the semiconductor channel, they will move in the direction of the applied source–drain electric field, but their progress is limited by their mobility,  $\mu_0$ , and by disorder effects. In crystalline inorganic semiconductors

where there is long-range order and delocalised carriers, motion is coherent (band-like) and characterised by a wave vector k. However, in organic semiconductors at room temperature, the precise mechanisms of charge transport are not yet fully understood [9]. Transport is generally described as thermally activated, hopping through localised states and traps, and is thought to be always incoherent even in crystalline materials. Two models of charge transport are discussed later in this chapter.

The local intramolecular structure and intermolecular packing between molecules will greatly affect charge carrier transfer from molecule to molecule [10]. Motion through polycrystalline structures is dominated by grain boundaries impeding charge carriers. The molecular uniformity of the semiconductor–dielectric interface also has a huge influence on charge transport. There are obstacles impeding the progress of the charge, such as static structural and energetic disorder, which slow down carriers, resulting in a percolation motion. There is also current limiting by space charge, whereby the injection of carriers into a semiconductor causes a screening effect of the external electric field, reducing its effect upon other mobile charge carriers. Shallow or deep traps further inhibit the progress of charge carriers, causing a hopping mode of transport.

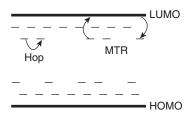

#### 2.3.1 Hopping Transport

Hopping transport (Figure 2.3) is a site-to-site phonon-assisted thermally activated tunnelling mechanism between localised bandgap states that are spatially and energetically close [11], classically described by Vissenberg and Matters [12]. In a charge transport model based on variable range hopping, localised charge carriers in amorphous organic films are not activated to a transport level, but instead are able to hop directly from site to site, either a short distance where there is high activation energy or a long distance where there is low activation energy. The model predicts that  $\mu_0$  will increase with increasing gate voltage. This can be explained qualitatively by assuming that accumulated charge carriers will fill lower-lying energy states first. As the lower energy traps are filled, it becomes less likely that other mobile charge carriers will become trapped, so trapping becomes less efficient and  $\mu_0$  rises. Subsequent charge carriers will occupy states with higher energies requiring less energy to hop between sites [9]. Mobility  $\mu_0$  also increases with temperature and is strongly dependent on the density of localised states [12].

#### 2.3.2 Multiple Trap and Release

Another model for (polycrystalline) organic materials is the MTR model (Figure 2.3) [13, 14]. In this transport model, the semiconductor consists of crystallites separated by grain boundaries. This model differs from hopping models in that it predicts that

charges will move in delocalised bands within crystallites until they are trapped at the grain boundaries. These traps may be caused by impurities or physical defects. Charge carriers fall into a trap of localised states in the bandgap and remain trapped until they are released by thermal activation to a transport level, whereupon they once again become active. The time spent in the trap depends on the temperature and on the depth of the trap.

Figure 2.3 Charge transport mechanisms showing hopping and multiple trap and release (MTR) between energy levels

#### 2.4 Materials

#### 2.4.1 Semiconductors

Current small-molecule and conjugated polymer materials have field-effect mobilities exceeding 1 cm<sup>2</sup>/Vs, an increase in performance of 3–4 orders of magnitude within the last 25 years [15]. In this section, an overview is given of the state-of-the-art solution-processable p-type organic semiconductors, including small-molecule-based materials, conjugated polymers, and the latest donor–acceptor conjugated polymers. This overview has been taken from an excellent 25<sup>th</sup> anniversary review article by Sirringhaus published in *Advanced Materials* [15].

#### 2.4.1.1 Small Molecule

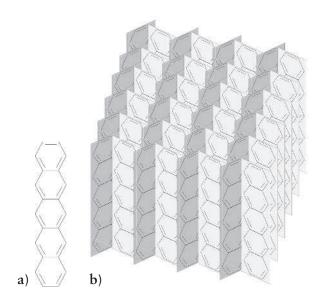

Perhaps the first popular organic semiconductor, and still the most used, is  $C_{22}H_{14}$ . By way of example,  $C_{22}H_{14}$  is described here to illustrate several key points about organic semiconductors.  $C_{22}H_{14}$  is an organic small molecule that consists of five benzene rings in a linear chain. This forms a planar molecular structure allowing delocalised electrons to move freely (Figure 2.4a). Within a monolayer,  $C_{22}H_{14}$  molecules are packed in a planar herringbone crystal structure (Figure 2.4b), where conductivity in the horizontal XY plane is higher than in the vertical Z direction [16]. The close molecule stacking of the herringbone crystal structure allows charge carriers easily to hop from one molecule to another by quantum mechanical tunnelling [17]. However, there are grain boundaries and defects that inhibit hopping and reduce  $\mu_0$ .

Figure 2.4 C<sub>22</sub>H<sub>14</sub> small molecule showing (a) benzene backbone and (b) herringbone stacking structure [1]

As with most organic semiconductors,  $C_{22}H_{14}$  is intrinsically ambipolar, able in principle to transport both holes and electrons depending on the gate voltage and the injection barriers at the source and drain. In air, the hole  $\mu_0$  in a  $C_{22}H_{14}$  transistor is around 0.1–1 cm²/Vs, but electron  $\mu_0$  is much lower. This is due to electrons in the  $C_{22}H_{14}$  molecule being very reactive to ambient water molecules, and hydroxyl groups at the semiconductor–dielectric interface acting like traps [1]. As a result,  $C_{22}H_{14}$  is considered to be a unipolar p-type semiconductor only, as is the case with most other organic semiconductors.

In general, small-molecule organic semiconductor mobility,  $\mu_0$ , depends on the molecular structure and the intermolecular packing, which determine the reorganisation energy and transfer integrals. The highest- $\mu_0$  materials have small reorganisation energy and large transfer integrals, with any static structural disorder minimised by material purification and interface control [18].

Many of the highest- $\mu_0$  solution-processed small molecules are based on substituting triisopropyl-silylethynyl (TIPS) onto a  $C_{22}H_{14}$  core [19]. Spin-coated 6,13-bis(triisopropyl-silylethynyl)pentacene (TIPS-P) films show a highly crystalline structure with a two-dimensional brick-wall cofacial  $\pi$ - $\pi$  stacking in the plane of the film with side chains normal to the substrate surface. Early spin-coated TIPS-P obtained mobilities exceeding 1 cm²/Vs [20]. Similar results were achieved with triethylsilylethynyl anthradithiophene (TESADT) [21] and difluorinated-triethylsilylethynyl anthradithiophene (dif-TESADT)

(dif-TESADT) [22]. Using a blade-coating technique, still higher mobilities of up to 11 cm<sup>2</sup>/Vs were attainable with TIPS-P [23, 24]. A class of materials based upon end-substituted phenylene-thiophene, selenophene, or thiazine fused ring systems invented by Takimiya [25, 26] led to a bottom-gate OFET with drop-cast di-alkyl end-substituted benzothienobenzothiophene (BTBT) derivative,  $C_8$ -BTBT, as the semiconductor and a  $\mu_0$  of 5 cm<sup>2</sup>/Vs [27]. The highest reported  $\mu_0$  so far of 31.3 cm<sup>2</sup>/Vs has been seen by Minewari and co-workers using a two-shot printing technique, also with  $C_8$ -BTBT [28].

In blended films of TIPS-P and dif-TESADT, where the small molecule tends to segregate to the surface, mobilities of 1 and 2.4 cm<sup>2</sup>/Vs have been reported [29]. The binder polymer strongly influences the crystallinity of the small molecule. More recently, dif-TESADT devices with an optimised binder have achieved mobilities of 4–5 cm<sup>2</sup>/Vs [30].

#### 2.4.1.2 Conjugated Polymers

Although fully amorphous conjugated polymers have achieved mobilities of  $0.01 \text{ cm}^2/\text{Vs}$ , the most successful conjugated polymers have been based on semicrystalline lamellar structures with an edge-on polymer orientation [15]. In these structures, alternating layers of conjugated backbones are formed, separated from each other by layers of flexible side chains that are parallel to the substrate plane. Charge transport in the plane of the film is thus not impeded by the insulating side chains. The best example of this structure has been using poly[2,5-bis(3-alkylthiophen-2-yl) thieno[3,2-b]thiophene] (PBTTT) to achieve a  $\mu_0$  of 1.1 cm²/Vs [31, 32].

#### 2.4.1.3 Donor-Acceptor Copolymers

Donor-acceptor copolymers are usually more complex and larger than conjugated polymers. Normally consisting of alternating electron-rich (donor) and electron-deficient (acceptor) units along the backbone, they exhibit a relatively low bandgap that aids in the selection of suitable electron- or hole-injecting contacts.

The first demonstrations of high- $\mu_0$  donor–acceptor polymers were a copolymer of polynaphthalate-bithiophene, an n-type material with a  $\mu_0$  of 0.8 cm²/Vs [33], and cyclopentadithiophene-benzothiadiazole (CDT-BTZ), which had a  $\mu_0$  of 3.5 cm²/Vs in dip-coated thin films [34]. Both polymers were originally thought to be amorphous but were later found to be semicrystalline. Ambipolar donor–acceptor copolymers based on the electron-deficient diketopyrrolopyrrole (DPP) have attracted much interest. The first ambipolar top gate with electron and hole mobilities greater than 1 cm²/Vs were reported in 2011 [35] and 2012 [36]. Using the same polymer and a

self-assembled monolayer-modified silicon dioxide gate dielectric, mobilities as high as 10 cm<sup>2</sup>/Vs have been achieved [37]. Meanwhile, indacenodithiophene (IDT)-based copolymers have reported a  $\mu_0$  of 3.6 cm<sup>2</sup>/Vs [38, 39], while IDT–BT copolymers have reported mobilities of 1.2–3.6 cm<sup>2</sup>/Vs [40, 41].

#### 2.4.2 Dielectrics

The performance of OFET is greatly influenced by the dielectric material and the semiconductor-dielectric interface. In general, a high-k dielectric material is preferable to a low-k dielectric material. A high-k material will allow a higher drive current at a lower voltage. Common dielectrics such as CYTOP<sup>TM</sup> (relative permittivity  $E_r = 2.1$ ) and polymethyl methacrylate (PMMA) ( $E_r = 3.6$ ) are easy to process but are relatively low-k materials. Newer materials such as aluminium oxide ( $E_r = 8-10$ ) and titanium dioxide ( $E_r = 20-41$ ) offer a higher k and lower voltage operation [2]. High-k polymer dielectrics have also been researched. These high-k relaxer ferroelectric polymers are of the polyvinylidene fluoride (PVDF) family and realise relative permittivities as high as  $E_r = 50$ , allowing low-voltage device operation in conjunction with several organic semiconductors [42].

#### 2.5 Summary

In this chapter, the molecular structure and charge transport mechanisms of organic semiconductors have been described. C<sub>22</sub>H<sub>14</sub> was introduced as an example of a common organic semiconductor, and the current state-of-the-art organic semiconductor materials were briefly reviewed. In the next chapter, these concepts are abstracted as the theory and operation of transistors is considered.

#### References

- 1. H. Marien, M. Steyaert and P. Heremans in *Analog Organic Electronics: Building Blocks for Organic Smart Sensor Systems on Foil*, Springer Science+Business Media, New York, NY, USA, 2013.

- 2. H. Sirringhaus, Advanced Materials, 2005, 17, 2411.

- 3. G.G. Malliaras and R. Friend, *Physics Today*, 2005, 58, 53.

- 4. M. Grell in *Masters Course in Nanotechnology Organic Semiconductors*, University of Sheffield, Sheffield, UK, 2009.

- 5. Helping You to Understanding Chemistry, Chemguide. http://www.chemguide.co.uk

- 6. S. Mijalkovic, D. Green, A. Nejim, G. Whiting, A. Rankov, S. Smith, J. Halls and C. Murphy in *Proceedings of the 26<sup>th</sup> International Conference on Microelectronics*, *MIEL 2008*, 11–14<sup>th</sup> May, Niš, Serbia, 2008, p.469.

- 7. T. Richards and H. Sirringhaus, *Journal of Applied Physics*, 2007, **102**, 094510.

- 8. J.A. Jiménez Tejada, K.M. Awawdeh, J.A.L. Villanueva, J.E. Carceller, M.J. Deen, N.B. Chaure, T. Basova and A.K. Ray, *Organic Electronics*, 2011, 12, 832.

- 9. D. Braga and G. Horowitz, Advanced Materials, 2009, 21, 1473.

- 10. H. Sirringhaus, M. Bird, T. Richards and N. Zhao, *Advanced Materials*, 2010, 4307, 3893.

- 11. S.G.J. Mathijssen, M. Cölle, H. Gomes, E.C.P. Smits, B. de Boer, I. McCulloch, P.A. Bobbert and D.M. de Leeuw, *Advanced Materials*, 2007, **19**, 2785.

- 12. M. Vissenberg and M. Matters, Physical Review B, 1998, 57, 964.

- 13. G. Horowitz, R. Hajlaoui and P. Delannoy, *Journal de Physique III*, 1995, 5, 355.

- 14. M.E. Gershenson, V. Podzorov and A.F. Morpurgo, *Reviews of Modern Physics*, 2006, 78, 973.

- 15. H. Sirringhaus, Advanced Materials, 25th Anniversary Article, January 2014.

- 16. J.C. Sancho-Garcia, G. Horowitz, J.L. Bredas and J. Cornil, *Journal of Chemical Physics*, 2003, 119, 12563.

- 17. G.H. Gelinck, E. van Veenendaal and R. Coehoorn, *Applied Physics Letters*, 2005, 87, 073508.

- 18. J. Brédas, J. Calbert, D. da Silva Filho and J. Cornil, *Proceedings of the National Academy of Sciences USA*, 2002, 99, 5804.

- 19. J.E. Anthony, J.S. Brooks, D.L. Eaton and S.R. Parkin, *Journal of the American Chemical Society*, 2001, 123, 9482.

- 20. M. Payne, S. Parkin, J.E. Anthony, C.C. Kuo and T.N. Jackson, *Journal of American Chemical Society*, 2005, 127, 4986.

- 21. S.S. Lee, C.S. Kim, E.D. Gomez, B. Purushothaman, M.F. Toney, C. Wang, A. Hexemer, J.E. Anthony and Y-L. Loo, *Advanced Materials*, 2009, 21, 3605.

- D.J. Gundlach, J.E. Royer, S.K. Park, S. Subramanian, O.D. Jurchescu, B.H. Hamadani, A.J. Moad, R.J. Kline, L.C. Teague, O. Kirillov, C.A. Richter, J.G. Kushmerick, L.J. Richter, S.R. Parkin, T.N. Jackson and J.E. Anthony, Nature Materials, 2008, 7, 216.

- 23. Y. Diao, B.C-K. Tee, G. Giri, J. Xu, D.H. Kim, H.A. Becerril, R.M. Stoltenberg, T.H. Lee, G. Xue, S.C.B. Mannsfeld and Z. Bao, *Nature Materials*, 2013, 12, 665.

- 24. G. Giri, E. Verploegen, S.C.B. Mannsfeld, S. Atahan-Evrenk, D.H. Kim, S.Y. Lee, H.A. Becerril, A. Aspuru-Guzik, M.F. Toney and Z. Bao, *Nature*, 2011, 480, 504.

- 25. K. Takimiya, H. Ebata, K. Sakamoto, T. Izawa, T. Otsubo and Y. Kunugi, *Journal of the American Chemical Society*, 2006, **128**, 12604.

- 26. T. Yamamoto and K. Takimiya, *Journal of the American Chemical Society*, 2007, **129**, 2224.

- 27. T. Uemura, Y. Hirose, M. Uno, K. Takimiya and J. Takeya, *Applied Physics Express*, 2009, **2**, 111501.

- 28. H. Minemawari, T. Yamada, H. Matsui, J. Tsutsumi, S. Haas, R. Chiba, R. Kumai and T. Hasegawa, *Nature*, 2011, 475, 364.

- 29. R. Hamilton, J. Smith, S. Ogier, M. Heeney, J.E. Anthony, I. McCulloch, J. Veres, D.D.C. Bradley and T.D. Anthopoulos, *Advanced Materials*, 2009, 21, 1166.

- 30. J. Smith, W. Zhang, R. Sougrat, K. Zhao, R. Li, D. Cha, A. Amassian, M. Heeney, I. McCulloch and T.D. Anthopoulos, *Advanced Materials*, 2012, 24, 2441.

- 31. I. McCulloch, M. Heeney, C. Bailey, K. Genevicius, I. MacDonald, M. Shkunov, D. Sparrowe, S. Tierney, R. Wagner and W. Zhang, *Nature Materials*, 2006, 5, 328.

- 32. B.H. Hamadani, D.J. Gundlach, I. McCulloch and M. Heeney, *Applied Physics Letters*, 2007, **91**, 243512.

- 33. H. Yan, Z. Chen, Y. Zheng, C. Newman, J. Quinn, F. Dotz, M. Kastler and A. Facchetti, *Nature*, 2009, 457, 679.

- 34. H.N. Tsao, D. Cho, J.W. Andreasen, A. Rouhanipour, D.W. Breiby, W. Pisula and K. Müllen, *Advanced Materials*, 2009, **21**, 209.

- 35. H. Bronstein, Z. Chen, R.S. Ashraf, W. Zhang, J. Du, J.R. Durrant, P.S. Tuladhar, K. Song, S. E. Watkins, Y. Geerts, M.M. Wienk, R.A.J. Janssen, T. Anthopoulos, H. Sirringhaus, M. Heeney and I. McCulloch, *Journal of the American Chemical Society*, 2011, 133, 3272.

- 36. Z. Chen, M.J. Lee, R. Shahid Ashraf, Y. Gu, S. Albert-Seifried, M. Meedom Nielsen, B. Schroeder, T. Anthopoulos, M. Heeney, I. McCulloch and H. Sirringhaus, *Advanced Materials*, 2012, 24, 647.

- 37. J. Li, Y. Zhao, H. Tan, Y. Guo, C. Di and G. Yu, *Scientific Reports*, 2012, 2, 754.

- 38. T. Lei, J-H. Dou and J. Pei, Advanced Materials, 2012, 24, 6457.

- 39. J. Mei, D.H. Kim, A.L. Ayzner, M.F. Toney and Z. Bao, *Journal of the American Chemical Society*, 2011, **133**, 20130.

- 40. W. Zhang, J. Smith, S.E. Watkins, R. Gysel, M. McGehee, A. Salleo, J. Kirkpatrick, S. Ashraf, T. Anthopoulos, M. Heeney and I. McCulloch, *Journal of the American Chemical Society*, 2010, 132, 11437.

- X. Zhang, H. Bronstein, A. J. Kronemeijer, J. Smith, Y. Kim, R.J. Kline,

L.J. Richter, T. Anthopoulos, H. Sirringhaus, K. Song, M. Heeney,

W. Zhang, I. McCulloch and D.M. DeLongchamp, *Nature Communications*,

2013, 4, 2238.

- 42. J. Li, D. Liu, Q. Miao and F. Yan, *Journal of Materials Chemistry*, 2012, 22, 15998.

## Field-Effect Transistors

#### 3.1 Introduction

The first point-contact transistor was invented in 1947 by Bardeen, Brattain, and Shockley, who subsequently received the Nobel Prize for their work in 1956 [1]. Not commercially successful, the point-contact transistor gave way to the subsequent inventions of bipolar junction transistor(s) (BJT) and especially field-effect transistors, which have now become ubiquitous in nearly all electronics products. The premise of the transistor is simple – a voltage-controlled electronic switch, or amplifier – yet transistors have gone on to become the cornerstones of the modern digital world.

In the previous chapter, the concepts, physics, and materials of organic transistors were discussed. In this chapter, their application as transistors is introduced, their operation is explained, and their key parameters are explored.

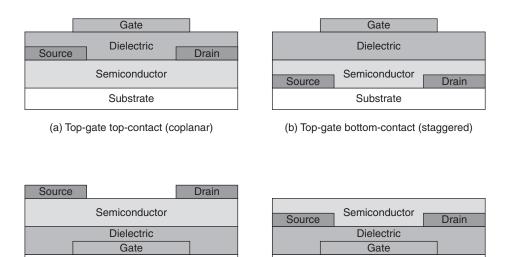

#### 3.2 Transistor Configurations

An organic field-effect transistor (OFET) is a three-terminal device – gate, source, and drain - where, conventionally, the conductivity of the device is controlled by a vertical electric field from the gate terminal acting upon a horizontal conduction channel that has been formed in the semiconductor between the source and drain electrodes. An organic thin-film transistor (OTFT) is a special case of an OFET in which the semiconductor and dielectric are deposited as thin films on top of an inactive substrate that plays no part in the transistor behaviour. There are four possible configurations of gate, source, and drain in an OTFT (Figure 3.1). The most popular configurations are the bottom-gate bottom-contact architecture, for its ease of fabrication in research labs, and the top-gate bottom-contact architecture, which offers the largest area for charge injection and extraction. There is a further classification of staggered or coplanar device, depending on the charge carrier path within the gate-induced accumulation channel. The current path within a coplanar configuration is almost entirely horizontal, whereas in a staggered configuration the current path is vertical near the source and drain, which offers a larger area for charge injection into the semiconductor.

#### Practical Guide to Organic Field-Effect Transistor Circuit Design

(c) Bottom-gate top-contact (staggered)

Substrate

(d) Bottom-gate bottom-contact (coplanar)

Substrate

Figure 3.1 Thin-film transistor(s) (TFT) gate and contact configurations

The OTFT is fabricated when the organic semiconductor is deposited across the source and drain electrodes to form the transistor channel. The semiconductor itself is separated from the gate electrode by a thin layer of gate dielectric material. Although the source and drain are physically identical, the source electrode is conventionally considered as the source of charge carriers. Transistors are primarily described by their conduction channels: p-type transistors are those with hole-accumulated channels, while n-type transistors are those that operate with electron-accumulated channels. For p-type transistors, as holes are the charge carriers, the source is the most positive terminal, and is often made of a high-work-function metal such as gold (5.1 eV). Conversely, for n-type transistors, electrons are injected from the negative source terminal, which is ideally a low-work-function metal such as calcium (2.9 eV), though these may not be environmentally stable [2].

It is convenient to reference all transistor voltages to the source electrode. In this respect, a drain-source voltage ( $V_{DS}$ ) and a gate-source voltage ( $V_{GS}$ ) are applied. The application of  $V_{GS}$  modulates an electric field across the transistor channel, which causes an accumulation of charge carriers at the semiconductor–dielectric interface. The depth of the conducting layer is very thin, no more than a few nanometres at the surface of the semiconductor at the interface.

Transistors may be either enhancement mode or depletion mode. Both p- and n-type enhancement-mode transistors have no conductive channel in the absence of a

gate voltage, while there is always a conduction channel in depletion-mode devices which require an opposite-polarity gate voltage to turn off the transistor. As organic semiconductors are normally undoped with no intrinsic carriers available, organic transistors are usually enhancement mode.

#### 3.3 Transistor Operation

When a gate voltage is applied, a field is induced at the semiconductor–insulator interface that causes the highest occupied molecular orbit and lowest unoccupied molecular orbit to shift relative to the source and drain Fermi levels which are held at a fixed value by external voltages [3]. If the gate voltage is large enough, mobile charge carriers will flow from the source contact into the semiconductor. When a potential difference is then applied to the source–drain, charge carriers will flow to the drain contact, completing the electrical circuit.

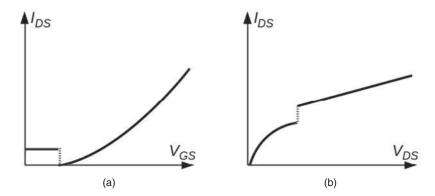

Transistors operate in distinct regimes or regions (Figures 3.2 and 3.3):

1. In the off state,  $V_{GS} << V_T$ , there is no accumulated conducting channel. The sourcedrain current,  $I_{DS}$ , is very small and is determined by the intrinsic conductivity of the bulk semiconductor:

$$I_{DS(cut-off)} = I_{leak} \text{ when } V_{GS} << V_T$$

(3.1)

where  $I_{leak}$  is a small intrinsic leakage current in the bulk semiconductor and  $V_T$  is the threshold voltage.

2. In the subthreshold region,  $V_{GS} < V_T$ , the source–drain current,  $I_{DS}$ , increases exponentially with gate voltage, similarly to the current due to a forward-biased diode. This exponential behaviour is often attributed to deep trap states [4]:

$$I_{DS(subthreshold)} = I_{S0}e^{\frac{V_{CS}}{nV_{th}}} \text{ when } V_{GS} \le V_T$$

(3.2)

where  $V_{th} = kT/q$  is the thermal voltage (~26 mV at room temperature), n is the subthreshold slope factor, and  $I_{S0}$  is a process-dependent parameter that also has some dependence on  $V_T$ . These two parameters,  $I_{S0}$  and  $V_T$ , are best extracted from experimental data [5]. In organic devices, owing to the large values of  $V_T$ , subthreshold behaviour is important and accounts for a significant amount of current. This current is often considered to be a parasitic leakage current in digital circuits, but in analogue circuits it may be utilised very efficiently in a similar manner to BJT devices or low-power metal-oxide semiconductor field-effect

transistor (MOSFET) devices. Performance of a device in the subthreshold region is measured by the subthreshold slope parameter n, which is defined as the change in  $V_{GS}$  needed to effect a decade increase in  $I_{DS}$  current.

3. In the linear region,  $V_{GS} \ge V_T$  and  $V_{DS} < V_{GS} - V_T$ . A conducting channel at the semiconductor-dielectric interface is only formed when  $V_{GS}$  is greater than the  $V_T$ . An equal amount of charge, but opposite in sign, appears on either side of the dielectric. The  $V_T$  is the result of either shallow traps in the semiconductor, which need to be filled, or charged dipoles already in the channel, which need additional gate voltage to form the channel [6]:

$$I_{DS(linear)} = \frac{W}{L} \mu C_{diel} \left[ (V_{GS} - V_T) V_{DS} - \frac{1}{2} V_{DS}^{2} \right] \text{ when } V_{DS} < V_{GS} - V_T$$

(3.3)

where  $\mu$  is the surface mobility of the channel,  $C_{diel}$  is the capacitance per unit area of the gate dielectric, W is the channel width, and L is the channel length.

4. Saturation occurs when  $V_{GS} \ge V_T$  and  $V_{DS} \ge V_{GS} - V_T$ . At these terminal voltages, the potential at some point in the channel drops to zero. At this position in the channel, approximately where  $V_{GS} < V_{DS}$ , there is now no longer an effective  $V_{GS}$  to maintain the charge in the channel. A region depleted of charge carriers forms next to the drain, and the channel is pinched off, with the source–drain current saturated. Further increases in  $V_{DS}$  will widen the depletion region next to the drain and move the pinch-off point towards the source, resulting in a shorter accumulated channel length, less resistance, and a small increase in  $I_{DS}$ .  $I_{DS}$  is now substantially independent of  $V_{DS}$  and is mainly controlled by  $V_{GS}$ . By substituting  $V_{DS} = V_{GS} - V_T$  in Equation 3.3, and adding a parameter for the channel length modulation, the source–drain current for the saturation region can be derived:

$$I_{DS(sat)} = \frac{1}{2} \frac{W}{L} \mu C_{diel} (V_{GS} - V_T)^2 (1 + \lambda V_{DS}) \text{ when } V_{DS} < V_{GS} - V_T$$

(3.4)

where  $\lambda$  is the channel length modulation parameter.

For convenience, in **Equations 3.3** and **3.4**, a transistor gain factor,  $\beta$ , may be defined:

$$\beta = \left(\mu C_{diel}\right) \frac{W}{L} = \left(\mu \frac{\epsilon_r \epsilon_0}{d_{diel}}\right) \frac{W}{L} \tag{3.5}$$

Gain factor  $\beta$  can be further separated into two other factors, a geometry gain

factor (W/L) and a process gain factor (

$$\kappa' = \mu C_{diel}$$

) or  $\left(k' = \mu \frac{\epsilon_r \epsilon_0}{d_{diel}}\right)$ , where  $\epsilon_r$  is

the relative permittivity of the gate dielectric and  $d_{diel}$  is the thickness of the gate dielectric. The process gain factor  $\kappa$ ' may be occasionally referenced when the semiconductor's mobility  $\mu$ , the dielectric's relative permittivity  $\varepsilon_r$ , and the dielectric's thickness  $d_{diel}$  are commercially sensitive and not disclosed. For the purposes of calculations in this book, the dielectric's relative permittivity has been assumed to be  $\varepsilon_r = 3.6$  throughout, and the thickness of the dielectric has been assumed to be based on a standard value  $d_{diel} = 850$  nm.

**Figure 3.2** Linear and saturation transistor regions of operation shown in (a) a transfer curve and (b) an output curve. The subthreshold transfer characteristic is shown in (c)

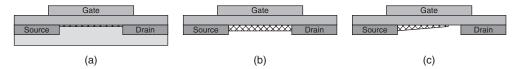

Figure 3.3 Channel region for (a) off state, (b) linear mode, and (c) saturation mode

#### 3.4 Threshold Voltage

OFET operate in accumulation mode with no intrinsic carriers and no depletion layer to isolate the conduction channel from the bulk. Therefore, the  $V_T$  is the gate voltage when a depleted channel becomes one in accumulation [7]. At equilibrium, the Fermi level is located in the middle of the bandgap. At low gate bias, most charge carriers go into localised states in the bandgap, and transport occurs with low mobility by hopping between these localised states. As the gate bias increases, more states are filled and the Fermi level moves towards the conduction band. This leads to an increase in carrier concentration in the conduction band and a rise in mobility. In other words, the  $V_T$  corresponds to a gate-bias-dependent mobility [8].

The  $V_T$  can be extracted from drain current or capacitance measurements [9]. In a paper by Ortiz-Conde [10], 13 methods of  $V_T$  extraction for MOSFET were investigated, 11 of which were from the linear region of operation, and two from the saturation region, which proved to be the most accurate. These were compared with an n-channel single-crystal bulk MOSFET and an n-channel hydrogenated amorphous silicon (a-Si:H) thin-film MOSFET. A similar paper by Boudinet analysed eight  $V_T$  extraction techniques for n-type OFET [11]. The two most popular and most often used threshold extraction methods are presented here now.

#### 3.4.1 Extrapolation of Linear Region

By extrapolating the  $I_{DS}$  current in the linear region (ELR) of the transfer curve measurement (Equation 3.3),  $V_T$  is calculated from the intercept with the x-axis:

$$\beta \left[ \left( V_{GS} - V_T \right) V_{DS} - \frac{1}{2} V_{DS}^2 \right] = 0 \tag{3.6}$$

$$V_T = V_{GS} - \frac{1}{2} V_{DS} (3.7)$$

#### 3.4.2 Extrapolation of Saturation Region

By extrapolating the square root of the  $I_{DS}$  current in the saturation region (ESR) of a transfer curve measurement (Equation 3.4),  $V_T$  is given from the intercept with the x-axis:

$$\frac{1}{2}\beta(V_{GS} - V_T)^2 = 0 {(3.8)}$$

$$V_T = V_{GS} \tag{3.9}$$

#### 3.5 Mobility

The conducting channel in the semiconductor of an OFET is only a few nanometres thick and located adjacent to the dielectric. It is unsurprising, then, that the charge carrier mobility depends not only on the semiconductor but also on the dielectric and the semiconductor–dielectric interface [12]. Mobility is affected by factors such as the roughness of the semiconductor–dielectric interface and by dipoles in the dielectric. For organic semiconductors, there is a gate-voltage-dependent mobility [13, 14], usually modelled as

$$\mu = \mu_0 \left( \frac{V_{GS} - V_T}{V_{aa}} \right)^{\gamma} \tag{3.10}$$

where  $\gamma$  and  $V_{aa}$  are empirical fitting parameters, and  $\mu_0$  is normally taken to be the band mobility. Parameter  $\gamma$  is related to the conduction mechanism and can describe both an increase or a decrease in mobility with  $V_{GS}$ . With an increase in mobility,  $\gamma > 0$ , which is typical of amorphous and nanocrystalline devices and is related to a trap conduction mechanism. A decrease in mobility with gate voltage,  $\gamma < 0$ , appears in polycrystalline TFT when surface scattering starts to be important [15].

#### Practical Guide to Organic Field-Effect Transistor Circuit Design

There are four different types of mobility [16], which can be calculated to a first order as follows:

- Hall mobility commonly used for bulk or material measurements.

- Effective mobility calculated from the drain conductance  $(g_d)$  in the linear region of the output curve:

$$g_d = \frac{\delta I_{DS}}{\delta V_{DS}} V_{GS} = const$$

(3.11)

$$\mu_{eff} = \frac{L}{W} \frac{g_d}{C_{diel} (V_{GS} - V_T)}$$

(3.12)

• Field-effect mobility – calculated from the transistor transconductance  $(g_m$  is the slope of the transfer curve) in the linear region:

$$g_{m} = \frac{\delta I_{DS}}{\delta V_{GS}} V_{DS} = const$$

(3.13)

$$\mu_{fet} = \frac{L}{W} \frac{g_m}{C_{diel} V_{DS}} \tag{3.14}$$

Any discrepancy between  $\mu_{fet}$  and  $\mu_{eff}$  is due to the neglect of any gate-voltage-dependent mobility effects.

• Saturation mobility – derived from plotting  $\sqrt{(I_{DS(sat)})}$  against  $(V_{GS} - V_T)$  from the output curve:

$$m = \frac{\delta \sqrt{I_{DS}}}{\delta (V_{GS} - V_T)} V_{DS} = const$$

(3.15)

$$\mu_{sat} = \frac{L}{W} \frac{2m^2}{C_{diel}} \tag{3.16}$$

As with  $\mu_{fet}$ ,  $\mu_{sat}$  also neglects any gate-dependent effects. Also, by definition, in the pinch-off region there are no charge carriers at the pinched-off drain electrode, but there are plenty of charge carriers at the source electrode. As the density of charge carriers varies considerably along the saturated channel,  $\mu_{sat}$  can therefore only

measure the mean mobility along the channel. For this reason, it is often better to extract mobility when the transistor is in the linear region, where the charge carrier distribution is more uniform [6].

#### 3.6 Contact Resistance

The source and drain electrodes do not usually present a low-resistance ohmic connection to the organic semiconductor. Instead, there is a high-resistance ohmic connection or a non-ohmic (Schottky) contact resistance [17], manifest as a flattened characteristic at low  $V_{DS}$  in a transistor's output curve. An example is shown in Figure 3.4a. A model for contact resistance to explain the non-linear behaviour is shown in Figure 3.4b [13], in which parasitic Schottky diodes in series with the source or drain resistance cause the observed non-linearities [18, 19].

Figure 3.4 Contact resistance: (a) typical transistor output curves showing nonlinear behaviour and (b) equivalent circuit with non-linear source and drain contact resistances [13]

#### 3.7 Summary

In this chapter, the operation of organic transistors has been summarised. Transistor operating regions have been described, and the key parameters of mobility and  $V_T$  have been analysed. These concepts will be used for circuit design and simulation in the next chapters.

#### References

- 1. The Nobel Prize in Physics, Nobelprize.org, 1956. http://www.nobelprize.org/nobel\_prizes/physics/laureates/1956/

- 2. J. Zaumseil and H. Sirringhaus, Chemical Reviews, 2007, 107, 1296.

- 3. C.R. Newman, C.D. Frisbie, D. da Silva Filho, J-L. Brédas, P.C. Ewbank and K.R. Mann, *Chemistry of Materials*, 2004, **16**, 4436.

- S. Abdinia, F. Torricelli, G. Maiellaro, R. Coppard, A. Daami, S. Jacob,

L. Mariucci, G. Palmisano, E. Ragonese, F. Tramontana,

A.H.M. van Roermund and E. Cantatore, Organic Electronics, 2014, February, 1.

- 5. P.E. Allen and D.R. Holberg in CMOS Analog Circuit Design, Holt, Rinehart & Winston, Inc., New York, NY, USA, 1987.

- 6. D. Braga and G. Horowitz, Advanced Materials, 2009, 21, 1473.

- 7. D. Braga and G. Horowitz, *Applied Physics A Materials Science and Processing*, 2009, **95**, 193.

- 8. G. Horowitz, R. Hajlaoui, H. Bouchriha, R. Bourguiga and M. Hajlaoui, *Advanced Materials*, 1998, **10**, 923.

- 9. H. Sirringhaus, Advanced Materials, 2009, 21, 3859.

- 10. A. Ortiz-Conde, F.J. Garcia Sanchez, J.J. Liou, A. Cerdeira, M. Estrada and Y. Yue, *Microelectronics Reliability*, 2002, **42**, 583.

- 11. D. Boudinet, G. Le Blevennec, C. Serbutoviez, J-M. Verilhac, H. Yan and G. Horowitz, *Journal of Applied Physics*, 2009, **105**, 084510.

- 12. V. Coropceanu and J-L. Brédas, Nature Materials, 2006, 5, 929.

- 13. P.V. Necliudov, M.S. Shur, D.J. Gundlach and T.N. Jackson, *Journal of Applied Physics*, 2000, 88, 6594.

- 14. E. Cantatore, T.C.T. Geuns, G.H. Gelinck, E. van Veenendaal, A.F.A. Gruijthuijsen, L. Schrijnemakers, S. Drews and D.M. de Leeuw, *IEEE Journal of Solid-State Circuits*, 2007, 42, 84.

- 15. M. Estrada, A. Cerdeira, J. Puigdollers, L. Resendiz, J. Pallares, L. Marsal, C. Voz and B. Iniguez, *Solid State Electronics*, 2005, **49**, 1009.

- 16. D. Vasileska in Mobility Modeling, Arizona State University, Tempe, AZ, USA.

- 17. G. Horowitz, Journal of Materials Research, 2004, 19, 1946.

- 18. T. Richards and H. Sirringhaus, *Journal of Applied Physics*, 2007, **102**, 094510.

- 19. M.S. Shur, D. Veksler, V. Chivukula and A. Koudymov, *Electrochemical Society Transactions*, 2007, 8, 165.

## **Modelling and Simulation**

## 4

### 4.1 Introduction

This chapter introduces the more abstract concepts of models, compact models, and parameter extraction. An example of how a physical model might be developed and used is presented after a study of an existing physical model.

Physical models and simulation algorithms are useful to help understand the behaviour of a material or device on a computer. By abstracting key physical parameters, models aid in the characterisation of materials and devices. Organic transistor behaviour is qualitatively similar to silicon transistor behaviour; however, the fundamentals are different, necessitating new physical models to be developed.

In general use, circuit simulation is performed at the transistor level, although it is acknowledged that this is only suitable when there are few devices in a circuit, as the computation overheads soon become severe with larger designs. And a note on the terminology – the mathematical equations are the *model*, and the computer software implementation is the *compact model*. Although these terms are not strictly adhered to in the literature, the meaning can be usually inferred from the context. Alternatively, there are circuit simulators that delve even deeper into the transistor by modelling devices directly at the level of the materials. These device simulators are used exclusively for research and development of the processing and fabrication and are not suitable even for a small circuit containing no more than a handful of devices.

## 4.2 Model Types

Models can be broadly split into three different classifications: physical, empirical, and table based. Each type of model has its own distinct advantages and disadvantages, which are listed below and summarised in **Table 4.1**. For example, the history of modelling in the silicon industry has swung from the first physical models (Shichman–Hodges), to the empirical [the very popular Berkeley short-channel IGFET model (BSIM), BSIM2, and HSPICE28], and back to the physical [BSIM3, Enz–Krummenacher–Vittoz (EKV)] [1]. The model used in this book and described later in this chapter is a physical model.

## 4.2.1 Physical

Physical models are derived from a first-principles study of the physics of the devices and of the characteristics of the measured data in order to arrive at a mathematical representation, or equation, of the terminal behaviour of the transistor. Usually there is considerable simplification of the physics in order to arrive at a working model, which may result in a model that does not fully agree with the experimental data. Although there may be some fine tuning and empirical fitting, most of the parameters are representative of a specific physical attribute, such as  $V_T$  or mobility. Having physical parameters will facilitate other simulations that would not be possible in table-based or pure empirical modelling, such as Monte Carlo modelling where a (physical) parameter is systematically altered across simulations. Physical models should, however, have as few parameters as possible [2] (leading to the oxymoron, 'A model shall be simple and accurate' [3]).

## 4.2.2 Empirical

In the most extreme and purest form, using only mathematical techniques, an equation is generated that fits the observed data. The skill of the programmer and capability of the algorithm determine the final form of the equation, although this may not be available to the user for further analysis, particularly if the algorithm or software is proprietary or confidential. A template equation may possibly be used, which may have been derived from a similar or related physical model and generally fits the expected data. There are companies such as Infiniscale that specialise in this type of data solving and modelling, from which very good (subjectively) data fitting is achievable. In any case, extracted parameters have little or no physical correspondence. Extrapolation outside the observed dataset is likely to be inaccurate.

## 4.2.3 Table-based Modelling [3]

The measured data are coded into a look-up table. Between data points, linear interpolation is used to estimate values. If the data points are closely spaced, then a reasonable prediction may be made. However, as with empirical models, behaviour beyond the observed boundaries is unreliable, and there are no physical parameters that may be extracted for further analysis. This form of modelling is simple to code for simulation purposes, although examples of the use of this type of model are rare.

| Table 4.1 Qualitative comparison of model types against different criteria |                 |                      |                       |  |  |  |  |

|----------------------------------------------------------------------------|-----------------|----------------------|-----------------------|--|--|--|--|

| Criteria                                                                   | Physical        | Empirical            | Table-based modelling |  |  |  |  |

| Time to first model                                                        | Very long       | Moderate             | Very quick            |  |  |  |  |

| Parameter extraction   Might be difficult   Mig                            |                 | Might be difficult   | Easy                  |  |  |  |  |

| Parameters                                                                 | Mainly physical | Little or no meaning | Have no meaning       |  |  |  |  |

| Interpolation                                                              | Yes             | Yes                  | Yes                   |  |  |  |  |

| Extrapolation                                                              | Yes             | No                   | No                    |  |  |  |  |

| Simulation speed                                                           | OK              | OK                   | Good                  |  |  |  |  |

## 4.3 Organic Models

Having earlier discussed charge transport within organic semiconductors, the challenge now is to produce a model that can best describe the transistor's terminal behaviour. Simple modelling of an organic thin-film transistor (OTFT) is possible with the classic expressions used by silicon metal-oxide semiconductor (MOS) crystalline devices, sometimes with small empirical modifications. But OTFT differ from silicon devices in several ways, such as mobility changes with  $V_{GS}$  or  $V_{DS}$ . Non-linear behaviour due to non-ohmic source or drain contacts or injection barriers have already been discussed, and leakage currents have been observed to be greater than in silicon devices.

All these organic properties require new models to be developed, and work is ongoing in this area of research. **Table 4.2** is a selected list of publications where the authors have sought to address these challenges of OTFT modelling. For another recent perspective on these models and modelling, see the excellent review article by Kim and co-workers [4].

| Table 4.2 Selected list of physical organic modelling papers |                  |                                                                             |  |  |  |

|--------------------------------------------------------------|------------------|-----------------------------------------------------------------------------|--|--|--|

| Author – Year                                                | No. of citations | Comments                                                                    |  |  |  |

| Estrada – 2005 [5]                                           | 23               | Used in a simulation of an organic inverter [12]                            |  |  |  |

| Fadlallah – 2006 [6]                                         | 11               | Used to compare fully printed unipolar and complementary organic logic [13] |  |  |  |

| Mijalkovic – 2008 [7]                                        | _                | _                                                                           |  |  |  |

| Yaghmazadeh – 2009 [8]                                       | 3                | Similar to Estrada – 2005                                                   |  |  |  |

| Marinov – 2009 [9]                                           | 33               | _                                                                           |  |  |  |

| Torricelli – 2009 [10]                                       | 14               | _                                                                           |  |  |  |

| Marinov – 2013 [11]                                          | 4                | Quasi-static model                                                          |  |  |  |

## 4.4 Compact Modelling

After the theoretical aspects of model derivation have been discussed, and the mathematical equations have been formed to describe the transistor's operating regions, the equations must then be transcribed into computer software code for the simulation program with integrated circuit emphasis (SPICE) simulator. The code itself may take the form of a software programming language (such as C, or C++), or a hardware description language (HDL) (such as Verilog-A or very-large-scale integration HDL). (An HDL differs from a software programming language in that the HDL is primarily designed to code electronic circuits and includes the concept of time.) Compact models are more than a mere transcription of the equations into computer code. It is necessary to account for systematic or transient error conditions, such as negative values, negative logarithms, negative square-route functions, or division-by-zero. Any discontinuities between transistor operating regions, either in the source–drain current or in its derivative, will cause numerical problems, so transitioning between operating regions must be accomplished by smoothing functions.

Compact models should fulfil certain criteria in order to make simulation easier [14]:

- The models should consistently represent organic field-effect transistor (OFET) behaviour.

- The source-drain behaviour for a symmetrical OFET source-drain should be symmetrical.

- The models should be analytical, without integrals or differentiation.

- They should be simple and easily derivable.

- It should be easy to determine, or even to guess, the parameters.

- The models should be modular.

- It should be possible to justify the relations physically.

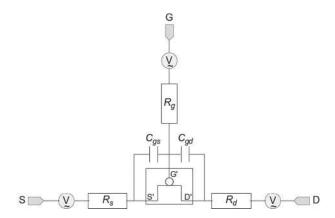

Compact models of transistors for circuit design are split into two parts, an intrinsic core and an extrinsic network (Figure 4.1). The intrinsic core of the model relates to the DC or static aspects of transistor behaviour. This is the part that the compact model equations have coded in a programming language. The extrinsic network is built around the intrinsic core using existing library components from the simulator and models the transient (time-dependent) and AC (frequency-dependent) effects. The extrinsic network may be captured as either a drawn schematic or as a netlist, which

is a textual representation of the schematic. Using the extrinsic network in this way, it should be possible to model other frequently observed behaviours of OFET, such as bias stress [15] and hysteresis [7].

Figure 4.1 Compact model of a transistor structure, showing the intrinsic core and extrinsic network of resistors, capacitors, and noise source components

## Intrinsic core features [16]:

- Smooth interpolation of current between regions;

- Gate-voltage-dependent parasitic resistance;

- Gate-voltage-dependent mobility;

- Source-drain leakage current model; and

- Physical temperature scaling.

#### Extrinsic network features [16]:

- Source-drain contact series resistance;

- Resistor and capacitor (RC) modelling for frequency;

- Overlap capacitance;

- Noise model; and

- Memory (charge storage) effects.

#### 4.5 Parameter Extraction

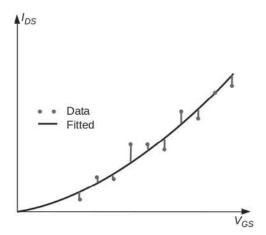

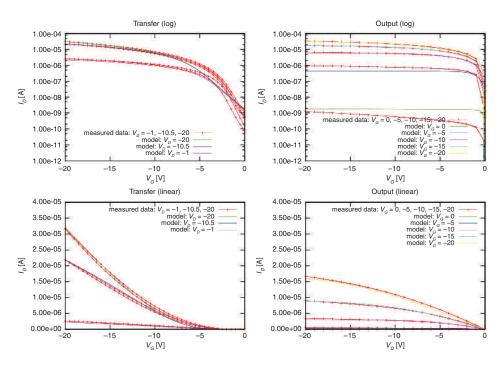

Parameter extraction is the procedure by which the model parameters are calculated optimally to fit the measured transistor data. There are two primary sets of measurements that are required for transistor characterisation [6]: the transfer characteristic ( $I_{DS}$ – $V_{GS}$ ), and the output characteristic ( $I_{DS}$ – $V_{DS}$ ). The Institute of Electrical and Electronics Engineers standard IEEE1620-2008 [17] describes measurement and reporting standards for these types of measurement. Capacitance-voltage characterisation is sometimes used [11], but small values of capacitance make this a difficult measurement task. As well as a good model, it is important to have good parameter extraction. The consequences of a poor model or poor parameter extraction will lead to incorrect values being assigned to the model's physical parameters [2]. For this reason, in the literature, many models are also accompanied with a systematic manual parameter extraction method. However, there are also numerical methods that are used to extract model parameters. Numerical methods fall into two main categories: a least-squares approach, used in this book, and fuzzy logic parameter extraction [18, 19].

#### 4.5.1 Manual Parameter Extraction

Most models have been designed with a view to easing the parameter extraction procedure, allowing the parameter extraction to be performed in a systematic and repeatable manner [6]. The techniques generally involve a gradient approximation or partial integration of the measurements. Usually, independent parameters are extracted first, then those parameters that have the most sensitivity, and finally the empirical and region-smoothing parameters. The sequence of parameter extraction, which may also be applicable to numerical methods, generally proceeds as follows:

- 1. Extraction of leakage and subthreshold parameters.

- 2. Extraction of the  $V_T$ .

- 3. Extraction of mobility.

- 4. Extraction of the source and drain resistance.

- 5. Extraction of the channel length modulation factor (output conductance).

- 6. Extraction of empirical and smoothing parameters.

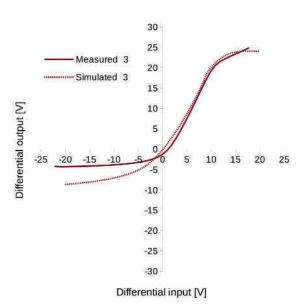

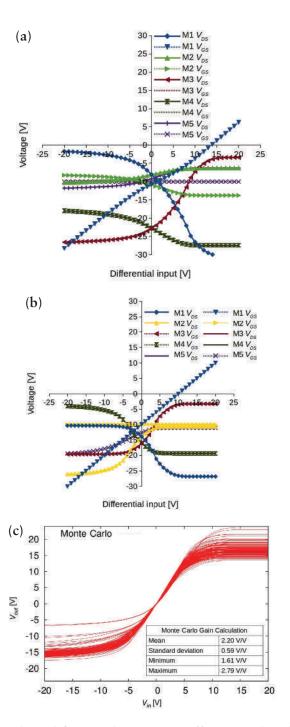

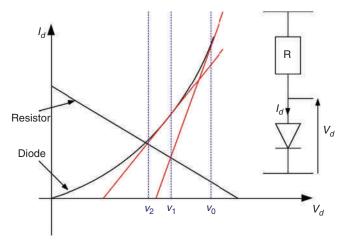

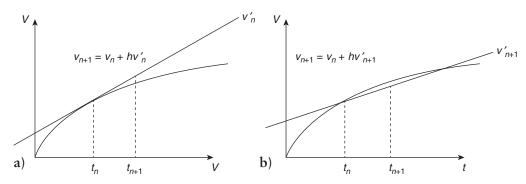

One disadvantage of many manual parameter extraction procedures is that, once a parameter has been extracted, it is not usually altered or refined following subsequent