# Design Methods and Applications for Distributed Embedded Systems

Edited by Bernd Kleinjohann, Guang R. Gao, Hermann Kopetz, Lisa Kleinjohann, Achim Rettberg

## DESIGN METHODS AND APPLICATIONS FOR DISTRIBUTED EMBEDDED SYSTEMS

#### **IFIP – The International Federation for Information Processing**

IFIP was founded in 1960 under the auspices of UNESCO, following the First World Computer Congress held in Paris the previous year. An umbrella organization for societies working in information processing, IFIP's aim is two-fold: to support information processing within its member countries and to encourage technology transfer to developing nations. As its mission statement clearly states,

*IFIP's mission is to be the leading, truly international, apolitical organization which encourages and assists in the development, exploitation and application of information technology for the benefit of all people.*

IFIP is a non-profit making organization, run almost solely by 2500 volunteers. It operates through a number of technical committees, which organize events and publications. IFIP's events range from an international congress to local seminars, but the most important are:

- The IFIP World Computer Congress, held every second year;

- Open conferences;

- Working conferences.

The flagship event is the IFIP World Computer Congress, at which both invited and contributed papers are presented. Contributed papers are rigorously refereed and the rejection rate is high.

As with the Congress, participation in the open conferences is open to all and papers may be invited or submitted. Again, submitted papers are stringently refereed.

The working conferences are structured differently. They are usually run by a working group and attendance is small and by invitation only. Their purpose is to create an atmosphere conducive to innovation and development. Reference is less rigorous and papers are subjected to extensive group discussion.

Publications arising from IFIP events vary. The papers presented at the IFIP World Computer Congress and at open conferences are published as conference proceedings, while the results of the working conferences are often published as collections of selected and edited papers.

Any national society whose primary activity is in information may apply to become a full member of IFIP, although full membership is restricted to one society per country. Full members are entitled to vote at the annual General Assembly, National societies preferring a less committed involvement may apply for associate or corresponding membership. Associate members enjoy the same benefits as full members, but without voting rights. Corresponding members are not represented in IFIP bodies. Affiliated membership is open to non-national societies, and individual and honorary membership schemes are also offered.

## DESIGN METHODS AND APPLICATIONS FOR DISTRIBUTED EMBEDDED SYSTEMS

IFIP 18th World Computer Congress TC10 Working Conference on Distributed and Parallel Embedded Systems (DIPES 2004) 22–27 August 2004 Toulouse, France

Edited by

Bernd Kleinjohann University of Paderborn, Germany

Guang R. Gao University of Delaware, USA

Hermann Kopetz Technische Universität Wien, Austria

Lisa Kleinjohann University of Paderborn / C-LAB Germany

Achim Rettberg University of Paderborn / C-LAB, Germany eBook ISBN: 1-4020-8149-9 Print ISBN: 1-4020-8148-0

©2004 Springer Science + Business Media, Inc.

Print ©2004 by International Federation for Information Processing. Boston

All rights reserved

No part of this eBook may be reproduced or transmitted in any form or by any means, electronic, mechanical, recording, or otherwise, without written consent from the Publisher

Created in the United States of America

Visit Springer's eBookstore at: and the Springer Global Website Online at: http://www.ebooks.kluweronline.com http://www.springeronline.com

## Contents

|   | Preface<br>Conference Committee                                                                                            | ix<br>xi |

|---|----------------------------------------------------------------------------------------------------------------------------|----------|

| 1 | Modelling and Specification                                                                                                |          |

|   | MDA Platform for Complex Embedded Systems Development<br>Chokri Mraidha, Sylvain Robert, Sébastien Gérard,<br>David Servat | 1        |

|   | On Detecting Deadlocks in Large UML Models<br>Michael Kersten, Wolfgang Nebel                                              | 11       |

|   | Verification Framework for UML-Based Design of Embedded<br>Systems<br>Martin Kardos, Yuhong Zhao                           | 21       |

| 2 | Verification and Analysis                                                                                                  |          |

|   | LTL's Intuitive Representations and its Automaton Translation<br>Yuhong Zhao                                               | 31       |

|   | Modeling and Verification of Hybrid Systems Based on Equations                                                             |          |

|   | Kazuhiro Ogata, Daigo Yamagishi, Takahiro Seino,<br>Kokichi Futatsugi                                                      | 43       |

|   | Distribution of Time Interval Between Successive Interrupt<br>Requests                                                     |          |

|   | Wojciech Noworyta                                                                                                          | 53       |

#### Fault Detection and Toleration

|   | A Membership Agreement Algorithm Detecting and Tolerating                                                                                                                          |     |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | Asymmetric Timing Faults<br>Håkan Sivencrona, Mattias Persson, Jan Torin                                                                                                           | 63  |

|   | Temporal Bounds for TTA: Validation<br>Karen Godary, Isabelle Augé-Blum, Anne Mignotte                                                                                             | 73  |

|   | An Active Replication Scheme that Tolerates Failure in<br>Distributed Embedded Real-Time Systems<br><i>Alain Girault, Hamoudi Kalla, Yves Sorel</i>                                | 83  |

| 4 | Automotive and Mechatronic Systems Design                                                                                                                                          |     |

|   | Development of Distributed Automotive Software:<br>The DaVinci Methodology<br>Uwe Honekamp, Matthias Wernicke                                                                      | 93  |

|   | Experiences from Model Based Development of<br>Drive-By-Wire Control Systems<br>Per Johannessen, Fredrik Törner, Jan Torin                                                         | 103 |

|   | Hardware Design and Protocol Specification for the Control<br>and Communication within a Mechatronic System<br>André Luiz. de Freitas Francisco, Achim Rettberg,<br>Andreas Hennig | 113 |

| 5 | Networks and Communication                                                                                                                                                         |     |

|   | A Decentralized Self-Organized Approach for Wireless Sensor<br>Networks<br>Jean-Paul Jamont, Michel Occello, André Lagrèze                                                         | 123 |

|   | A Software Architecture and Supporting Kernel for Largely<br>Synchronously Operating Sensor Networks<br>K. H. (Kane) Kim, C. S. Im, M. C. Kim, Y. Q. Li, S. M. Yoo,<br>L. C. Zheng | 133 |

|   | Adaptive Bus Encoding Schemes for Power-Efficient Data<br>Transfer in DSM Environments<br>Claudia Kretzschmar, Markus Scheithauer, Dietmar Müller                                  | 145 |

vi

### 6 Scheduling and Resource Management

| A Novel Approach for Off-Line Multiprocesor Scheduling in<br>Embedded Hard Real-Time Systems                                                           |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Raimundo Barreto, Paulo Maciel, Marília Neves,<br>Eduardo Tavares, Ricardo Lima                                                                        | 157 |

| Schedulability Analysis and Design of Real-Time Embedded<br>Systems with Partitions<br>David Doose, Zoubir Mammeri                                     | 167 |

| Flexible Resource Management<br>A Framework for Self-Optimizing Real-Time Systems<br>Carsten Boeke, Simon Oberthuer                                    | 177 |

| Hardware Architectures and Synthesis                                                                                                                   |     |

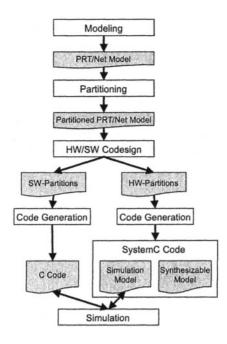

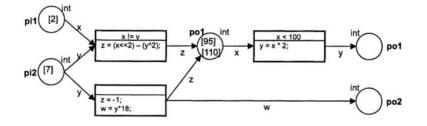

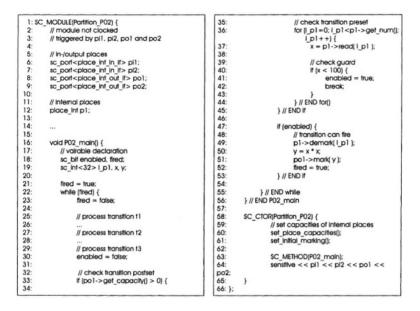

| Automatic Synthesis of SystemC-Code from Formal<br>Specifications                                                                                      | 105 |

| Carsten Rust, Achim Rettberg                                                                                                                           | 187 |

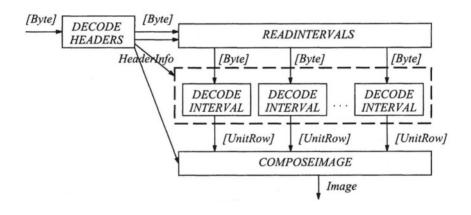

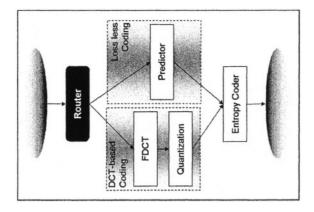

| Hardware Synthesis of a Parallel JPEG Decoder from its<br>Functional Specification<br>John Hawkins, Ali E. Abdallah                                    | 197 |

| A Self-Controlled and Dynamically Reconfigurable Architecture <i>Florian Dittman, Achim Rettberg</i>                                                   | 207 |

| Design Space Exploration                                                                                                                               |     |

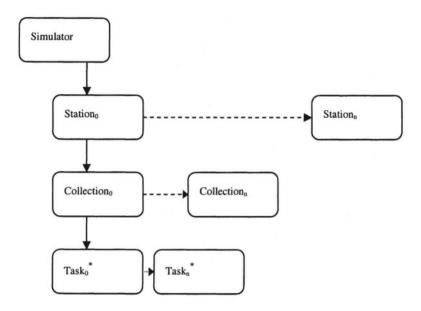

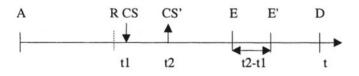

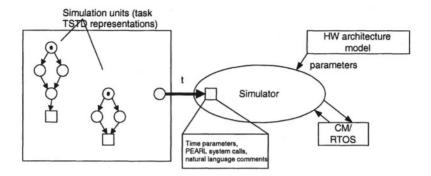

| Profiling Specification PEARL Designs<br>Roman Gumzej, Matjaž Colnarič, Wolfgang A. Halang                                                             | 217 |

| A Multiobjective Tabu Search Algorithm for the Design Space<br>Exploration of Embedded Systems<br><i>Frank Slomka, Karsten Albers, Richard Hofmann</i> | 227 |

|                                                                                                                                                        | ,   |

| Design Space Exploration with Automatic Generation of IP-Based Embedded Software                                                                       |     |

| Júlio C. B. de Mattos, Lisane Brisolara, Renato Hentschke,<br>Luigi Carro, Flávio Rech Wagner                                                          | 237 |

|                                                                                                                                                        |     |

### 9 Design Methodologies and User Interfaces

|    | A Multi-Level Design Pattern for Embedded Software<br>Ricardo J. Machado, João M. Fernandes                                                                                               | 247 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | A Petri Net Based Approach for the Design of Dynamically<br>Modifiable Embedded Systems<br><i>Carsten Rust, Franz J. Rammig</i>                                                           | 257 |

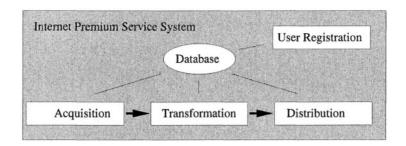

|    | Internet Premium Services for Flexible Format Distributed<br>Services<br>Brigitte Oesterdiekhoff                                                                                          | 267 |

| 10 | Short Papers                                                                                                                                                                              |     |

|    | Evaluating High-Level Models for Real-Time Embedded<br>Systems Design<br>Lisane Brisolara, Leandro B. Becker, Luigi Carro, Flávio R.<br>Wagner, Carlos Eduardo Pereira                    | 277 |

|    | A Dataflow Language (AVON) as an Architecture Description<br>Language (ADL)<br>Ashoke Deb                                                                                                 | 287 |

|    | Engineering Concurrent and Reactive Systems with Distributed<br>Real-Time Abstract State Machines<br>Uwe Glässer, Mona Vajihollahi                                                        | 297 |

|    | The Implications of Real-Time Behavior in Networks-on-Chip<br>Architectures<br><i>Edgard de Faria Corrêa, Eduardo W. Basso, Gustavo R. Wilke,</i><br><i>Flávio R. Wagner, Luigi Carro</i> | 307 |

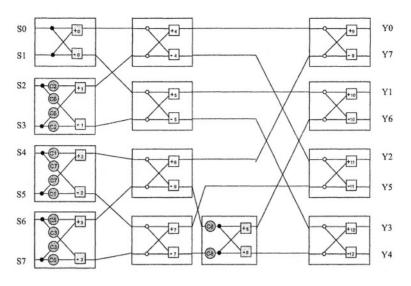

|    | ME64 – A Parallel Hardware Architecture for Motion Estimation<br>Implemented in FPGA                                                                                                      | 215 |

|    | Diogo Zandonai, Sergio Bampi, Marcel Bergerman                                                                                                                                            | 317 |

viii

### Preface

The IFIP TC-10 Working Conference on Distributed and Parallel Embedded Systems (DIPES 2004) brings together experts from industry and academia to discuss recent developments in this important and growing field in the splendid city of Toulouse, France.

The ever decreasing price/performance ratio of microcontrollers makes it economically attractive to replace more and more conventional mechanical or electronic control systems within many products by embedded real-time computer systems. An embedded real-time computer system is always part of a well-specified larger system, which we call an *intelligent product*. Although most intelligent products start out as stand-alone units, many of them are required to interact with other systems at a later stage. At present, many industries are in the middle of this transition from stand-alone products to networked embedded systems. This transition requires reflection and architecting: The complexity of the evolving distributed artifact can only be controlled, if careful planning and principled design methods replace the adhoc engineering of the first version of many standalone embedded products.

The topics which have been chosen for this working conference are thus very timely: model-based design methods, design space exploration, design methodologies and user interfaces, networks and communication, scheduling and resource management, fault detection and fault tolerance, and verification and analysis. These topics are supplemented by hardware and application oriented presentations and by an invited talk on "new directions in embedded processing - field programmable gate arrays and micro-processors" given by Patrick Lysaght, (Senior Director, Xilinx Research Labs, Xilinx Inc., USA). We hope that the presentations will spark

stimulating discussions and lead to new insights. Since this working conference is organized within the 18th IFIP World Computer Congress, there are many possibilities to interact with experts from other scientific areas and to place the field of embedded systems into a wider context. We all hope that this working conference in this beautiful part of the world will be a memorable event to all involved.

Hermann Kopetz, Bernd Kleinjohann, Guang R. Gao,

Lisa Kleinjohann and Achim Rettberg

## IFIP TC10 Working Conference on Distributed and Parallel Embedded Systems (DIPES 2004) World Computer Congress, August 22-27, 2004, Toulouse, France

General Chair Bernd Kleinjohann Co-Chairs

Guang R. Gao & Hermann Kopetz

#### **Program Committee**

Bernd Kleinjohann (Chair, Germany) Guang R. Gao (Co-Chair, USA) Hermann Kopetz (Co-Chair, Austria) Arndt Bode (Germany) Nikil Dutt (USA) Bernhard Eschermann (Switzerland) Uwe Glässer (Canada) Uwe Honekamp (Germany) Joachim Stroop (Germany) Ahmed Jerraya (France) Kane Kim (USA) Moon Hae Kim (Korea) Lisa Kleinjohann (Germany) Rainer Leupers (Germany) Erik Maehle (Germany) Carlos E. Pereira (Brazil) Peter Puschner (Austria) Franz J. Rammig (Germany) Achim Rettberg (Germany) Bernd-Heinrich Schmitfranz (Germany) Flavio R. Wagner (Brazil) Heinz-Dietrich Wuttke (Germany) Ying C. (Bob) Yeh (USA)

### **Organizing** Committee

Lisa Kleinjohann and Achim Rettberg

### Sponsoring and Co-Organizing Institution

IFIP TC 10, WG 10.5, SIG-ES in co-operation with WG 10.1, 10.3, 10.4

### Acknowledgement

We thank the entire organizing committee of the IFIP World Computer Congress 2004, the Congress Chair Jean-Claude Laprie and the Programme Chair Reino Kurki-Suoni for their support and for the local arrangements in Toulouse.

### MDA PLATFORM FOR COMPLEX EMBEDDED SYSTEMS DEVELOPMENT

Chokri Mraidha, Sylvain Robert, Sébastien Gérard, David Servat *CEA LIST – CEA SACLAY* F-91191 Gif-sur-Yvette Cedex France Phone : +33 169 085 039 {chokri.mraidha; sylvain.robert; sebastien.gerard ; david.servat}@cea.fr

Abstract: Moving from code-centric to model-centric development seems to be a promising way to cope with the increasing complexity of embedded real-time systems. The Object Management Group (OMG) has been recently promoting this approach, known as Model Driven Architecture (MDA). It relies on UML model refinement and transformation as the basic step of an iterative design process. This model-centric posture has raised many questions, among which the need for an integrated MDA-based developing environment is probably the most severe one. It directly affects the reality of the adoption of this good practice by software engineers. For several years, the CEA-LIST has been involved in the field of real-time systems research and development. This work resulted in the completion of the Accord/UML toolkit, which aims at providing users with a model-driven method and supporting tools. This paper outlines the Accord/UML approach focusing on the solving of complex real-time/embedded systems development issues in this MDA process.

Keywords: Model driven development, UML, Real-time embedded systems

### 1. INTRODUCTION

Over the last few years, engineers have been faced with the problem of developing more and more complex embedded real-time systems in a world where time-to-market constraints are constantly increasing. Moving from code-centric to model-centric development brings significant answers to software complexity management. With its standardization the Unified Modeling Language (UML) [1] has become the lingua franca of objectoriented modeling. Existing UML-based approaches for real-time systems development [2, 3] still result in models that are hard to maintain and reuse. This drawback is principally due to the lack of model development methodologies.

The Model Driven Architecture (MDA) [4] initiative introduces architectural separation of concerns in order to provide portability, interoperability, maintainability and reusability of models. To achieve these goals, MDA recommends different kinds of models and describes ways to obtain these models from one another through model transformation processes. MDA relies on three kinds of models, which are the Computation Independent Model (CIM), the Platform Independent Model (PIM) and the Platform Specific Model (PSM).

The CIM is a view of a system from a computation independent viewpoint. This model focuses on the requirements of the system and its interactions with the environment while hiding the details of the structure of the system. In other words, the system is seen as a black box. The PIM focuses on the structure and operations of the system from a platform independent viewpoint while hiding details specific to a particular platform. In the PIM, the system is seen as a white box. The PSM combines the PIM with details specific to a particular platform to obtain a model dependent of that platform.

The idea is then to apply MDA tenets in order to facilitate development of real-time applications. Accord/UML [5, 6] is an MDA-oriented methodology entirely based on UML which aims at facilitating real-time software development by engineers who are not real-time experts. The first section of this paper gives an overview of the Accord/UML methodology, enhancing its compliance with the MDA approach. The second section accounts for several directions of research to deal with platform specificities issues for complex embedded real-time systems development, while putting emphasis on code generation process, before giving a short conclusion.

### 2. OUTLINES OF THE ACCORD/UML PLATFORM

Accord/UML aims at providing users with an MDA-compliant methodology and connected tools dedicated to real-time systems design. This section briefly introduces of the Accord/UML methodology before giving an overview of its associated workbench.

### 2.1 The Accord/UML methodology

A prototype development with the Accord/UML methodology basically consists of three successive phases, each producing one of the three MDA model kinds. For each phase, Accord/UML provides guidelines and UML extensions (gathered in a UML profile), which enable users to model system real-time features. Moving from one phase to another is facilitated by partially automating model transformations.

The preliminary analysis phase deals with requirements capture. System requirements are identified and reformatted in a set of UML diagrams (use case diagrams and high-level scenario diagrams). The resulting model gives a better-formalized view of system functionalities regardless of its internal structure. This model, called Preliminary Analysis Model (PAM) in our methodology stands for the CIM MDA model.

In the detailed analysis phase, the objective is to move from the PAM to the Detailed Analysis Model (DAM), which is the Accord/UML vision of PIM. The system is decomposed in complementary and consistent sub models: structural models (mainly class diagrams), detailed interaction models (detailed scenarios diagrams), and behavioral model (statecharts and activity diagrams). Structural models are built following a generic pattern, which consists in separating system core features from its relationships with its environment. This approach notably favors reusability and permits to define a generic mapping from PAM to DAM. Modeling real-time structural features is eased by introducing the Real-Time Object concept [7, 8], an extension of UML active objects. As far as behavioral modeling is concerned, two aspects are separated [9]: the control view through statecharts, and the algorithmic view through activity diagrams completed by an UML Action Semantics [1] compliant Action Language [10]. To ensure determinism in modeling behavioral aspects, Accord/UML also provides through its profile a set of rules to specify UML semantics variation points in the one hand and clarify some ambiguous points on the other hand. The resulting model gives an *implementation language independent* executable specification of the system.

Finally, the aim of the prototyping phase is to obtain a complete running mock-up of the application from its DAM [11]. This model is the Prototyping Model (PrM), an Accord/UML equivalent of PSM. This model is then used as an input to a specialized C++ generator, handling notably system real-time features implementation. Eventually, a runtime framework is provided to support the execution of the synthesized code on top of a Real-Time Operating System: the Accord real-time kernel, and the Accord virtual machine. The so-obtained prototype can thus be validated by test.

### 2.2 The Accord/UML workbench

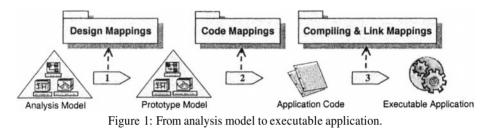

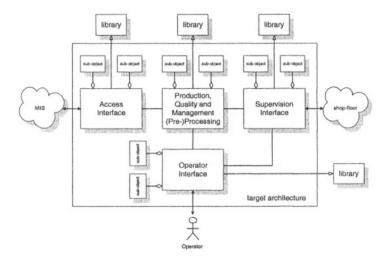

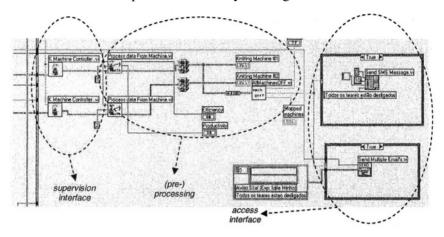

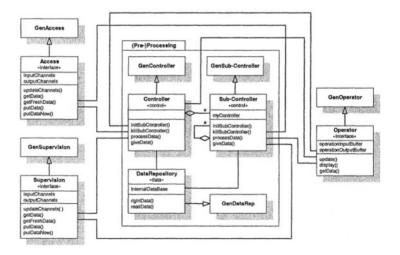

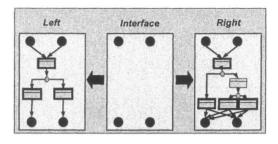

As depicted in Figure 1, the Accord/UML methodology support consists mainly of three parts: automatic synthesis of specific design patterns relating to real-time and distribution issues; full code generation (structure + behavior) toward the Accord runtime platform; the Accord platform itself implementing high level concepts of the methodology and running on Unix, Linux or VxWorks.

The Accord/UML workbench relies on a generic UML-based CASE tool, Objecteering [12], which we customize for distributed real-time embedded systems design. This offers possibilities through its profile builder tool to implement UML profiles. Our toolset is then made of the Objecteering tool completed with additional modules implementing the Accord/UML profiles.

More precisely, in modeling phases, building models is done thanks to the Objecteering UML modeler, which provides a complete set of UML elements (e.g. use cases diagrams, class diagrams, state-machine diagrams, sequence diagrams...), but also using additional model elements defined in the context of the Accord/UML profiles and ensuring real-time features modeling. Stepping from one model to another is done as much as possible via Accord/UML specific model transformation rules. For instance, Accord/UML sets mapping rules to ensure automatic model transformation from Use Cases diagrams to Classes diagrams. The tenets of the approach being to define and implement as often as possible modeling rules to assist the engineer in building the application model. One could speak of MAC ("Modeling Assisted by Computer").

In addition, the Accord/UML tools provide the developer with means of validation in the earlier phases of the development. Firstly, structural and functional validation is carried out on the behavioral models. To this end, a connection has been made between Accord/UML and the Agatha tool [13-15], enabling automatic test case generation from the behavioral diagrams obtained during the detailed analysis phase. Secondly, a validation of quality of service (QoS) in terms of timing requirements is performed by a

schedulability analysis of UML models [16]. This point will be discussed in more details in the following sections.

Once application models are completed, one may perform code generation from this model. To this purpose, Accord/UML provides a specialized code generator targeting C++ code (a C code generator being under development). This generator has been upgraded to integrate real-time features support conformant to the Accord/UML specification. This means that the generated code can be executed with support from the Accord kernel and Accord virtual machine [17] running on top of various operating systems, namely VxWorks, UNIX, or Linux.

### 3. PLATFORM DEPENDANCE ISSUES IN AN MDA PROCESS

In this section, we present the strategy adopted in Accord/UML to deal with real-time/embedded issues, before providing several examples assessing the relevance of our choices.

### 3.1 Rationale

Targeting real-time embedded applications instead of mainstream ones imposes a superset of constraints on the software developed, among which platform-related considerations and real-time features validation are prevailing. Actually, traditional real-time software design processes provide strategies and support tools to validate temporal (either application-specific or non-functional) properties of the system during the earlier phases of the design cycle. Moreover, in the context of embedded applications, the characteristics of the HW platform have a major influence on the final system temporal behavior and have to be taken into account to make relevant design choices. Integrating these issues in our MDA-compliant approach is thus one of the major challenges we had to face.

As a consequence, two principal objectives were aimed to in the design of our development methodology and tools: to provide a sufficient level of real-time features integration and providing ways to validate the application with respect to the HW platform, in a UML-based model-centric approach. This comes actually to an attempt to merge conflicting aspects, since the ultimate goal of the MDA approach is precisely to shield concerns linked to the platform (in terms of implementation language as well as targeted HW). Furthermore, the UML is a language, which natively provides only "raw" materials (model elements, extension mechanisms), which are voluntarily platform-independent and generalist. As a consequence, UML tools are usually designed to support mainstream software development and provide therefore very poor means of validating real-time properties. All these considerations have led us to differentiate three kinds of actions to perform:

- Adapt the UML to real-time issues, by adding or extending (with UML profiles) native model elements to provide proper ways to represent temporal features at the model level.

- Adapt existing validation strategies to our approach: this implies notably to bridge the gap between the UML and other more formal languages, and between UML modeling tools and validation tools.

- Ensure the suitability of the application with respect to its embeddability, by trying to express the HW platform characteristics at the model level and thus enabling to make design choices in accordance.

These directions have been applied and refined all along the design of our platform. In the next sections, we account for this process, by describing works addressing several specific aspects of MDA adaptation to real-time/embedded issues.

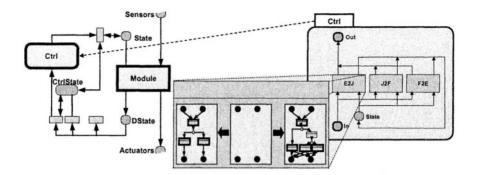

## **3.2** A generic architecture for smart-sensor networked application

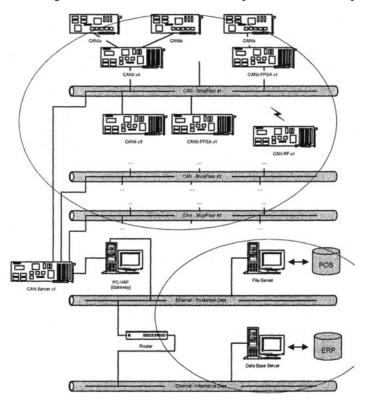

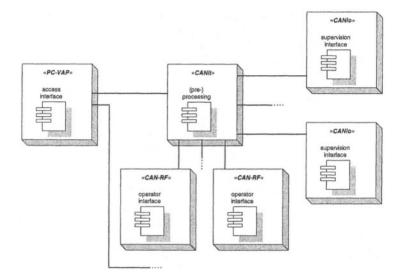

This thread of work is focused on architectural aspects when dealing with embedded applications. Smart-sensor networked applications stand as the prototypical example of such complex, but fairly common type of architectures, featuring both a central computing resource, such as an embedded PC, and several electronic devices, such as sensors and actuators.

To cope with the integration of such heterogeneous type of both hardware and software pieces, the component paradigm is of great help. It helps give a likewise abstract view of the various parts of the system. Then the question remains as how to integrate those parts, given that, most of the time, each of them is devised in an independent fashion, which prevents from easy coping of, among many, communication matters.

This work [18, 19] is an attempt to provide a generic integration scheme in the form of a component-partition of such networked applications. In his proposition, a sensor is represented both at the application (embedded PC) and at hardware level by various components:

- At the hardware device level, the sensor is seen as two components. The first one provides interface to the hardware logic. It is specified according to the existing standards (IEEE and OMG [20, 21]). The second one embeds the user logic and functional features. Apart from some predefined interfaces it is left to the engineer to develop

- At the embedded PC level, each sensor is represented by a device-driver component, which realizes one among predefined communication patterns and provides specific service interfaces to talk to the sensor through the network. Both CAN and Ethernet protocols have been taken into account so far and special care has been given to the design of synchronization algorithms among all the device driver components, so that the whole communication delay is handled. All this logic is embedded in the device-driver model construct, from which code can then be generated.

This is a typical example of what MDA is promoting. The definition of generic integration patterns, giving a sound basis for modeling, which in turn, via code generation, is finely-tuned to specific targeted electronic device platforms.

### **3.3** Schedulability and performance analysis

This thread of work can be seen as a general concern for assessing system properties – functional as well as extra-functional – at the level of the model. Among those, schedulability and performance stand as the most severe ones that embedded systems are expected to provide.

Three subsequent PhD thesis have been led on this topic within our team. The pursued goal was, on the one hand to broaden the coverage of those aspects within the UML, and on the other hand to bridge the gap between such UML modeling constructs and the use of external validation tools.

As concerns the first aspect, a dedicated UML profile was designed to define a generic Action Language [10] suitable for expressing control and functional algorithms in an implementation-language-independent fashion. Besides, another profile was developed to enable the expression of worst-case execution time (WCET) properties at the model level. Based on these, both a static and a dynamic WCET analysis of the overall models are possible.

The second part consisted in an effort to derive from Accord/UML standard models a specific, scheduling-oriented model [16], suitable for interpretation within a symbolic execution based validation tool, Agatha [13, 14], developed at CEA-LIST. Once established, this link between both tool-chains enables a complete assessment of the scheduling properties of an application model, provided that WCET information is fed to the models. This approach was mainly intended for critical real-time systems, for which precise knowledge of WCET are more likely to be known.

Finally, an ongoing work is focused on performance assessment, based on the use of the enhancement of the Scheduling, Performance and Time UML profile [22] and on the generation of Layered Queuing Networks (LQN) [23] from standard Accord/UML application models. In the same way as was done for the scheduling issue, we foresee here the opportunity to bridge the gap with tools that were devised to extract LQN properties.

### **3.4** From models to code

Real-time embedded systems have to meet various design constraints including consumption of energy or memory and a sufficient level of performance to satisfy real-time requirements. There are actually several kinds of real-time embedded systems. They cover a wide range of domains going from cell phones applications to nuclear power plants control systems or also spacecrafts embedded calculators. Each domain has its own constraints to meet. This concern takes place at every stage of the design process but the fact that code of the application is the last link in the chain, makes code generation an essential and critical phase of model-centric development. Code provided by generators has to meet constraints of the RT/E application itself but also has to take into account the limitation of the resources provided by the hardware supports of the application. Hence, code generation needs to be optimized for each targeted platform depending of the features it offers. Besides, there are often several solutions to generate code from a given model. For example, a state-transition model may be generated under the form of a set of nested switches [24], or using the state pattern [25], but also by generating tables. These three patterns of code generation will not have the same impact on energy, memory and performance features of the generated code.

These different patterns of code generation are proposed in the Accord/UML workbench. Hence, code for different optimization purposes can be generated from the same model. Currently, the user has to manually make the choice of the code generation pattern, but our goal is to have a "smart" code generator capable of making this choice as automatically as possible. More than constraints specifications, this requires an elaborated platform description model to gather sufficient amount of information and we also need to elaborate some heuristics, keeping in mind combinatorial explosion issues, to be able to make the most appropriate choice.

Another axis of our ongoing work on optimized code generation concerns the ability to quantify the efficiency of the generated code in terms of energy, memory or performance in order to validate the fulfilment of requirements. From our point of view, this is a very important challenge in order for model-driven development to be a success in real-time embedded system development domain.

### 4. CONCLUSIONS

We strongly believe that the MDA approach, or more generally design processes centered on models design, constitutes a powerful mean to facilitate real-time embedded systems development. However, this statement will be completely true only if support tools and design processes guidelines are defined and refined, taking into account the very specific aspects of this application domain.

This paper expands this core rationale by describing the Accord/UML platform, a combination of an MDA-compliant methodology and a supporting workbench for developing real-time systems. In Accord/UML, going through development process is eased by models transformation automation and code generation, and support is provided until code execution. In order to mitigate concerns linked to implementation, a seamless integration of embedded and real-time features is performed all along the development process, for instance by providing methods and tools for temporal validation, or by extending the UML to a "real-time UML". The relevance of our approach has been assessed in various applications from the automotive and telecom industry in the context of European project such as AIT-WOODDES, EAST, or ARTIST.

### REFERENCES

- 1. OMG, Unified Modeling Language: Superstructure Version 2.0. 2003.

- 2. B.P. Douglass, *Real-Time UML : Developing Efficient Objects for Embedded Systems*. Object technology Series, ed. Addison Wesley. 98.

- 3. Bran Selic, Garth Gullekson, and Paul T. Ward, *Real time Object-oriented Modeling*. Wiley Professional Computing. 94: John Wiley & Sons, Inc.

- 4. OMG, MDA Guide Version 1.0.1. 2003, OMG.

- Sébastien Gérard, et al. Efficient System Modeling of Complex Real-time Industrial Networks Using The ACCORD/UML Methodology. in Architecture and Design of Distributed Embedded Systems (DIPES 2000). 2000. Paderborn University, Germany: Kluwer Academic Publishers.

- 6. S. Gérard, F. Terrier, and Y. Tanguy. *Using the Model Paradigm for Real-Time Systems Develoment: ACCORD/UML.* in *OOIS'02-MDSD.* 2002. Montpellier: Springer.

- 7. François Terrier, et al. *A Real Time Object Model.* in *TOOLS Europe'96.* 1996. Paris, France: Prentice Hall.

- 8. Sébastien Gérard, et al. A UML-based concept for high concurrency: the Real-Time Object. in The 7th IEEE International Symposium on Object-oriented Real-time distributed Computing (ISORC 2004). 2004. Vienna, Austria.

- 9. Chokri Mraidha, et al. A Two-Aspect Approach for a Clearer Behavior Model. in The 6th IEEE International Symposium on Object-oriented Real-time distributed Computing (ISORC'2003). 2003. Hakodate, Hokkaido, Japan: IEEE.

- 10. Chokri Mraidha, et al., Action Language Notation for ACCORD/UML. 2003, CEA.

- 11. Patrick Tessier, et al. A Component-Based Methodology for Embedded System Prototyping. in 14th IEEE International Workshop on Rapid System Prototyping (RSP'03). 2003. San Diego, USA: IEEE.

- 12. Softeam, Objecteering, http://www.obecteering.com.

10

- 13. C. Bigot, et al. Automatic test generation with AGATHA. in TACAS. 2003. Warsaw, Poland.

- 14. D. Lugato, et al., Validation and automatic test generation on UML models : the AGATHA approach. special issue of the STIT (Software Tools for Technology Transfer), 2004.

- 15. C. Bigot, et al. A Semantics for UML specification to be validated with AGATHA. in ERTS'04. 2004. Toulouse, France.

- Trung Hieu Phan, et al. Scheduling Validation for UML-modeled Real-Time Systems. in ECRTS 2003. 2003. Porto, Portugal.

- 17. David Servat, et al. *Doing Real-Time with a Simple Linux Kernel*. in *RTLWS*'2003. 2003. Valencia, Spain.

- 18. C. Jouvray, et al. Smart Sensor Modeling with the UML for Real-Time Embedded Applications. in IV2004. 2004. Parma, Italy.

- 19. C. Jouvray, et al. Networked UML modeling sensors. in ICTTA'04. 2004. Damascus, Syria.

- 20. IEEE Standard for a Smart Transducer Interface for Sensors and Actuators, in Network Capable Application Processor (NCAP) Information Model, IEEE Std 1451.1. 26 june 99.

- 21. OMG, Smart Transducers Interface OMG. 07 dec. 01.

- OMG, UML Profile for Schedulability, Performance and Time (ptc/02-03-02). 2003, OMG. p. 154.

- 23. D.C. Petriu and C.M. Woodside, *Performance Analysis with UML: Layered Queuing Models from the Performance Profile*, in *UML for Real: Design of Embedded Real-Time Systems*. 2003, Kluwer Academic Publishers.

- 24. Miro Samek, Practical Statecharts in C/C++: Quantum Programming for Embedded Systems. 2002.

- 25. Erich Gamma, et al., *Design Patterns. Elements of Reusable Object-Oriented Software.* 1994: Addison-Wesley.

## ON DETECTING DEADLOCKS IN LARGE UML MODELS

Based on an Expressive Subset

Michael Kersten and Wolfgang Nebel University of Oldenburg Department of Computing Science michael.kersten@informatik.uni-oldenburg.de, nebel@informatik.uni-oldenburg.de

- Abstract: The paper describes a method for the detection of deadlocks in large UML models of reactive systems. Therefore a multi-phase-approach will be presented which consists of the four phases: property extraction, potential deadlock analysis, deadlock reachability analysis and result visualisation.

- **Keywords:** Deadlock detection, cycle detection, graph theory, reachability analysis, UML.

### 1. INTRODUCTION

In the last few years the Unified Modeling Language (UML) emerged to the standard modelling language in the field of object-oriented design. Even in technical domains like automotive and aircraft industry the application of UML has grown appreciable. Due to the fact of high safety requirements in these areas the combination of UML and formal methods is a popular object of research.

A very specific but practically relevant part of this field of investigation is the detection of deadlocks in UML models. Since they are very easy to model but hard to find by manual inspection, automatic methods for deadlock detection are convenient to reduce development costs and to enhance quality. Recent contributions (e.g. [3],[8]) allow the detection of deadlocks in UML models using model checking techniques. They are very general and allow the proof of absence of deadlocks as well as many other properties. Currently the systems to be checked are limited in size (see [1],[2],[6]) depending on the state representation used. A further restriction of the regarded contributions is the small supported subset of UML.

Hence, the model checking approach cannot be used for any given project without additional effort. In particular the rich set of expressive modelling concepts provided is the payoff of UML.

The presented contribution aims at the automatic detection of deadlocks in large reactive system designs modelled by a rich UML subset.

Therefore in section 1 an expressive UML subset for reactive systems, containing class, statechart, sequence and collaboration diagrams is introduced.

Based on this, in section 2, a multi-phase analysis method is provided, which allows the automatic detection of deadlocks. Subsequently we conclude the presented work.

### 2. AN EXPRESSIVE UML SUBSET FOR REACTIVE SYSTEMS

In order to provide an expressive UML subset for reactive systems with the full usability it is necessary to include the most commonly used concepts. A minimal but complete subset of necessary concepts is hard to define by academic means. In the present case the concepts included are the achievement of an academia/industry co-project described in [5]. These are essentially concepts for the structural and logical decomposition, modelling of concurrency/parallelism aspects, and the definition of the behaviour of the system under development.

For the definition of the static structure the class diagram concepts of UML are used. Within class diagrams the package concept is used to provide a high-level logical decomposition of the system under development. In order to define the system border the package level stereotype  $\ll system \gg$  is used. The further decomposition of the system under development is done using classes and associations.

One important aspect of reactive systems is the concurrency. The first design decision in the reactive system design is the distinction between active and passive components. Therefore the UML provides the feature *isActive* which is anchored as an attribute of *class* in the UML metamodel. Following the definition of the UML specification (see [7]) a class is an active class, if its meta-attribute *isActive* is set to 'true'. The class thus has an own thread of control. Whether active classes on the same hierarchy level of a UML model are executed concurrently or in parallel is left open on this level of abstraction. In the later design phases this aspect may be refined using the stereotypes  $\ll task \gg$  and  $\ll hw \gg$ . The former is used to denote software components which are running concurrently and the latter identifies hardware components which are running in parallel by default.

For the hardware/software-codesign more elaborate concepts are necessary which are beyond the scope of the present contribution.

Besides the structural modelling of the system under development the behavioural aspects are important. In our profile the internal behaviour of objects (instances of classes) is modelled using statemachines. For each active class a statemachine must be defined. Since passive classes have no own thread of control they have no own internal behaviour and therefore they have no associated statemachine. This does not apply for their operations. The behavioural modelling of class operations may be done using statemachines. For simplicity we state the following assumtions for the UML models under analysis:

- 1 Nested statecharts are not used,

- 2 Concurrent states are not used,

- 3 All active objects are created in the initial phase, later on, only passive objects are created using constructor methods,

- 4 Guards are boolean expressions over attribute and event-parameter values,

- 5 Time events are regarded as equal to completion events,

- 6 No usage of history states.

The assumptions 1-4 are only stated for simplicity reasons and do not limit the generality. Assumption 5 has no influence on the generality, too, but it is needed for the analysis. If time events are not regarded<sup>1</sup> as completion events the underlying deadlock model must be changed into a timed deadlock model. This would introduce a lot of effort without advancing the analysis.

Assumption 6 deliberately increases the generality of the modelling because from the authors standpoint the usage of the history state concept of the UML decreases the comprehensibility of the respective model in an irresponsible manner. Another important aspect of the reactive system modelling is the time modelling. In particular for real-time systems this is essential. For the purpose of deadlock detection we abstract from the timing aspects and therefore do not present our UML time modelling concepts (see [4]) within this paper.

<sup>&</sup>lt;sup>1</sup>Since in the deadlock analysis time events are only regarded as completion events, the developer may use them as accustomed.

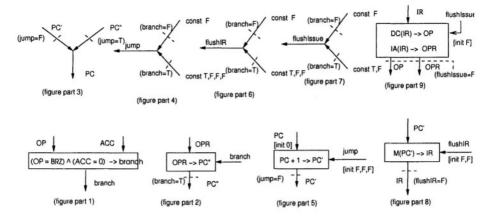

### 3. A MULTI-PHASE AUTOMATIC DEADLOCK DETECTION METHOD

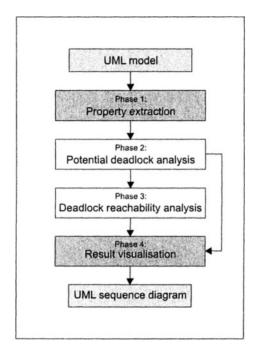

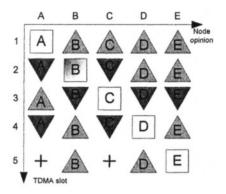

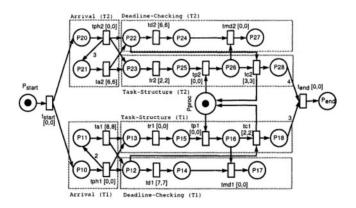

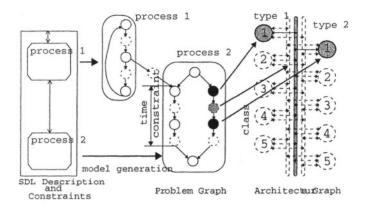

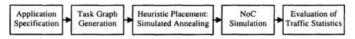

Our contribution is based on a multi-phase analysis process as shown in Fig. 1. In the first phase the deadlock relevant properties of the UML

Figure 1. The multi-phase-method

model are extracted and stored in mathematical structures (e.g. lists, sets, tuples) which allow effective algorithms in the second phase.

There the UML statechart diagrams are analysed statically in order to find out which "wait-for"-relations between active objects exist. For this purpose the State-Wait-Graph is introduced which allows white box deadlock detection. In contrast to classical wait graphs, the State-Wait-Graph representation considers the internal state of the active objects expressed as statechart diagrams. The detection of cycles in the State-Wait-Graph indicates the existence and location of potential deadlocks.

Whether these potential deadlocks are reachable at run-time, depends on the binding of attributes and parameters of operation calls between active objects to actual values. These aspects are analysed in the third phase of the method, which performs a deadlock reachability analysis. For this purpose relevant execution paths are derived from the model and the associated transitions are analysed. When a potential deadlock situation is reachable, this is detected by the method and the complete history of this deadlock can be stated. The included result visualisation mechanism generates a sequence diagram containing an illustration of the deadlock trace.

### **3.1 Property Extraction**

In the property extraction phase all active classes of the UML model are analysed concerning their communication aspects. In concrete terms this means that for each active class the set of produced events and consumed events is calculated and stored in producer and consumer lists. For this purpose call events are regarded as consumer and call actions are regarded as producer of events. Thereby events are only considered if their consumer and producer are suitably associated.

### 3.2 Potential Deadlock Analysis

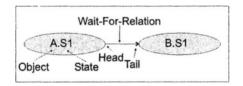

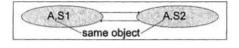

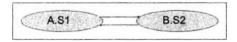

A potential deadlock is a cyclic wait situation between concurrent or parallel components of a system each within a specific state. Our respective deadlock model is the State-Wait-Graph (see Fig. 2). This is a directed graph in which each vertex represents an active object in a specific state (of the associated statechart diagram) and each edge represents a 'wait-for-relation'. The number of vertices of the State-

Figure 2. Principle of a State-Wait-Graph

Wait-Graph is the same as the number of states of all statechart diagrams of the model which are associated to active classes. The number of edges depends on the transitions defined in these statecharts. The head of each edge is connected with the vertex waiting for some specific event. The vertex connected with the tail of the edge is a potential producer of this particular event.

The potential deadlock analysis starts with the creation of a State-Wait-Graph. This is done by operating on the structures (e.g. consumer and producer lists) created in the property extraction phase.

Having created the full State-Wait-Graph of the system, potential deadlock situations can be detected. A potential deadlock situation is

a situation in which two or more objects (each in a specific state) are waiting mutually for the production of a particular event.

In our approach the next phase is to detect all cycles in the State-Wait-Graph and then sort out the relevant ones. In contrast to classical wait-graphs (e.g. [9]), where each detected cycle is a potential deadlock the procedure is more complicated for State-Wait-Graphs due to their white-box-nature. Cycles with all vertices being of the same object (as shown in Fig 3) are not potential deadlocks but logical errors in the corresponding statechart diagram. Cycles with two or more vertices of different objects

Figure 3. Cycle within one object

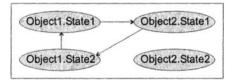

are potential deadlock situations, if no object is involved with more than one state. Otherwise we denote them as 'cycles with over-involved objects' (see Fig. 4). The detection of all cycles in the State-Wait-Graph

Figure 4. Over-involved object

is done using an advanced depth-first-search algorithm which calculates all cycles of the graph and the partitioning within a single run. The pruning of logical errors and cycles with over-involved objects is done using set-operations.

After the pruning the remaining potential deadlock situations need to be examined concerning outgoing edges. This is done by traversing the graph and calculating the out-degree of each vertex. If all vertices have the out - degree = 1 the potential deadlock situation is called a potential deadlock in our approach. If there are vertices with an out - degree > 1 (as shown in Fig. 5) it depends on the target object of the edge leading out of the cycle, whether the cycle under examination is a potential deadlock. When the target object is not involved in the cycle the examined cycle is not a potential deadlock. Otherwise it must be checked, if the edge connects two states of the same object. If the check evaluates to true the potential deadlock is combined with a logical error and the logical error should be corrected before going on in the

Figure 5. Out transition of a cycle

deadlock detection. If it evaluates to false we have a further cycle in the State-Wait-Graph. In this case the next phase can be initiated because our cycle detection ensures that all cycles are found and all cycles are handled seperately in the further analysis.

Potential deadlock means, that it is statically possible that the deadlock occurs but whether this really may happen at run-time depends on some dynamic aspects of the model which are analysed in the next phase, the deadlock analysis phase.

If no potential deadlock is found in this phase, the system is deadlock free and the next phase may be omitted.

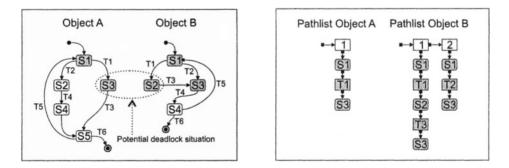

### **3.3 Deadlock Reachability Analysis**

The purpose of the deadlock reachability analysis phase is to provide evidence for each detected potential deadlock found in the previous phase. This means to calculate the possible paths into the potential deadlocks detected using a search algorithm and to analyse whether these paths are executable by an heuristic simulation approach. As illustrated

Figure 7. An example of path lists

in Fig. 6, the search algorithm performs a specialised depth-first search for each relevant statechart diagram and stores all paths to potential

deadlock states in a path list (see Fig. 7). Each path list contains all states and transitions of the respective path.

The path lists are used as input for the subsequent heuristic simulation. In the simulation the state machines are executed on a simulator which implements the exact UML semantics as defined in [7]. Besides very special features like the queue length and the evaluation order of expressions as defined in the semantics the following dynamic aspects of the model need to be considered: guard conditions, event parameter values and attribute values.

In the case that one or more paths into a potential deadlock situation exist it is sufficient to find one executable path during the simulation. The other case is the more expensive one. When all paths of the path list are executed once and no executable path is found, it cannot be stated whether there is an executable path or not. Even after theoretically infinitely many executions one cannot be sure that the next execution does not lead to a potential deadlock situation. In this case the simulation will break after an adjustable number of n executions and a corresponding warning is issued to the user.

The disadvantage of this heuristic simulation approach is that the nonexistance of deadlocks cannot be proved if there are potential deadlocks found in phase 2 into which no executable path could be found after nexecutions.

In this infrequent case only an exhaustive search over a completely unfolded state space as model checking does could help. Since our approach basically adresses models which are to large for model checking there is no other solution than the usage of manual abstraction techniques in conjunction with advanced model checking techniques.

### **3.4 Result Visualisation**

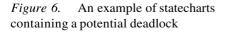

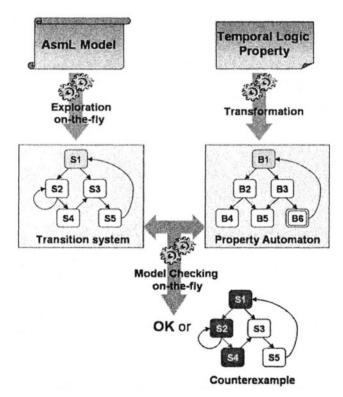

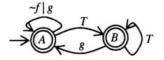

The last phase of the presented contribution is the result visualisation phase. Its task is to provide an easily comprehensible representation of the results of the deadlock detection procedure. Therefore extended UML sequence diagrams are applied. In Fig. 8 a simple deadlock situation is shown, in which, for simplicity, only the deadlocked states 'A.S1' and 'B.S2' are displayed. The corresponding result visualisation chart is

Figure 8. Cycle in the State-Wait-Graph

given in Fig. 9. There it is apparent that the active objects A and B are

running directly into a deadlock situation after being created from the system. Next to the sequence of communications ahead of the deadlock

Figure 9. Example of a deadlock trace

situation the participating objects and states are relevant and presented to the user. Other visualisations are possible but not in the focus of this contribution.

### 4. CONCLUSION

We have presented a method for the detection of deadlocks in UML models of reactive systems. The present approach has two main advantages. First, the method supports an expressive set of UML concepts and thus real-world UML models of reactive systems can be checked without modification. Second, the size of models to be checked, may be significantly larger than a model checker can handle. Since the evaluation of the presented method is in progress, we will not give a full complexity analysis within the scope of the presented contribution but a rough estimate causes the assumption that the overall algorithm will be linear in the number of states and transitions multiplied by a factor depending on the number of potential deadlocks found, the number of reachable execution paths and a set of further internal parameters.

The main drawback is that in seldom cases (as discussed in section 3.3) the freedom of deadlocks cannot be stated and thus the method is not complete. Since in this case a corresponding message is issued to the user the creditability is not affected.

Another disadvantage is the loss of generality in contrast to model checking, which allows the proof of almost any property expressible in the particular logic dialect used.

For a class of applications the criteria model size and expressiveness of the supported UML subset are more important than the generality of properties.

The property extraction and potential deadlock detection phases are experimentally evaluated using a prototype implementation. The first results of this evaluation are promising, but it turned out that the creation of adequate UML models as input for the method is an extensive and difficult task. Hence, we defer the continuation of the experimental evaluation in favour of a formal proof.

### REFERENCES

- J. R. Burch, E. M. Clarke, K. L. McMillan, D. Dill, and L. J. Hwang. Symbolic model checking: 10<sup>20</sup> states and beyond. In *Information and Computation*, volume (98)2, pages 142–170. IEEE, 1992. also in 5th IEEE LICS 90.

- [2] E. M. Clarke and H. Schlingloff. Model checking. In Alan Robinson and Andrei Voronkov, editors, *Handbook of Automated Reasoning*, chapter 21, pages 1367 – 1522. Elsevier Science Publishers B.V., 2000.

- [3] Alexandre David, M. Oliver Möller, and Wang Yi. Verification of UML Statecharts with Real-time Extensions. Technical report, Department of Information Technology, Uppsala University, http://www.it.uu.se/research, February 2003.

- [4] Michael Kersten, Ramon Biniasch, Wolfgang Nebel, and Frank Oppenheimer. Die Erweiterung der UML um Zeitannotationen zur Analyse des Zeitverhaltens reaktiver Systeme. In R. Drechsler et al., editors, *GI/ITG/GMM Workshop 2003*, pages 11–20, Bremen, February 2003. Shaker Verlag.

- [5] Michael Kersten, Jörg Matthes, Christian Fouda, Stephan Zipser, and Hubert B. Keller. Customizing UML for the Development of Distributed Reative Systems and Ada 95 Code Generation. *Ada User Journal*, 23(3), 2002.

- [6] K. L. McMillan. Symbolic model Checking. Kluwer Academic Publishers, 1993.

- [7] OMG. OMG Unified Modeling Language Specification (version 1.4). Technical report, OMG, http://www.omg.org, September 2001.

- [8] Timm Schäfer, Alexander Knapp, and Stephan Merz. Model Checking UML State Machines and Collaborations. *Electronic Notes in Theoretical Computer Science*, 47, 2001.

- [9] Mathias Weske. *Deadlocks in Computersystemen*. International Thomson Publishing GmbH, Bonn, Albany [u.a.], first edition, 1995. ISBN 3-929821-11-7.

## VERIFICATION FRAMEWORK FOR UML -BASED DESIGN OF EMBEDDED SYSTEMS<sup>\*</sup>

Martin Kardos and Yuhong Zhao

Heinz Nixdorf Institute, University of Paderborn, Germany

- Abstract: System level design incorporating system modeling and formal specification in combination with formal verification can substantially contribute to the correctness and quality of the embedded systems and consequently help reduce the development costs. Ensuring the correctness of the designed system is, of course, a crucial design criterion especially when complex distributed (real-time) embedded systems are considered. Therefore, this paper aims at presenting a verification framework designated for formal verification and validation of UML-based design of embedded systems. It first introduces an approach of using the AsmL language for acquiring formal models of the UML semantics and consequently presents an on-the-fly model checking technique designed to run the formal verification directly over those semantic models.

- Key words: embedded system design, UML, formal semantics, ASMs, AsmL, formal verification, model-checking

### 1. INTRODUCTION

The increasing complexity of today's embedded systems imposes new demands on the overall design process and on the used design languages and verification techniques. The *system level design* has become a hot topic in the research area of embedded systems and is gradually gaining popularity in the designer community. Typical for system level design are specification and modeling techniques offering facilities for coping with the system complexity such as structural decomposition, abstraction, refinement, etc. However, employment of these techniques into the design process of embedded systems can not succeed without appropriate support for

<sup>\*</sup>This work has been supported by the German National Science Foundation (DFG)

embedded systems can not succeed without appropriate support for verification. Therefore, verification techniques are needed that are able to identify the design errors hidden in the abstract and often incomplete models at the earlier stages of the system level design.

The work presented in this paper deals with formal verification of UMLbased design for embedded systems. The main objective resides in providing a unified verification framework based on a solid formal background that integrates formal verification techniques together with model-based validation techniques. In this way we believe that system designs of high complexity could be verified at early design phase of the system development lifecycle.

The remainder of the paper is organized as follows. Section 2 gives an overview of the proposed verification framework. Section 3 outlines the work on formalizing the UML semantics by means of the ASM-theory based specification language AsmL. Section 4 presents a model checking approach towards formal verification of the AsmL specifications. In this section, the focus is put on the description of an on-the-fly algorithm and its functional parts consequently followed by the introduction of possible enhancement towards the efficient model checking of distributed systems. In Section 5 the related work is discussed. Finally, the paper concludes with a brief outlook on the future work in Section 6.

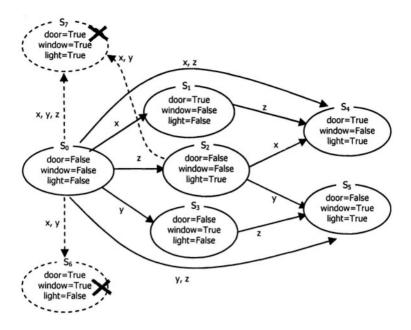

### 2. FRAMEWORK OVERVIEW

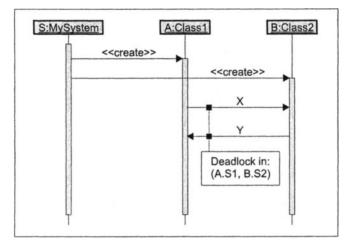

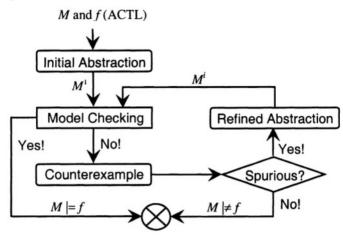

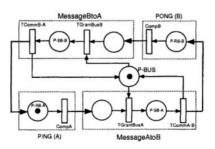

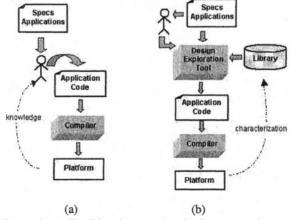

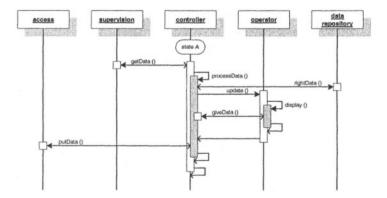

The proposed verification framework is depicted by means of a process flow diagram shown in the Figure 1. The input to the verification process (dashed box) is represented by an UML model describing the specified system. The verification process is further divided into two parallel branches, namely the formal verification and the validation. The main goal of the formal verification consists in proving the correctness of the required properties that a given UML model has to fulfill. This is achieved by incorporating model checking techniques into the verification framework. The validation branch, on the other hand, comprises of the methods for conventional model simulation amended by the model-based testing. Both branches are built upon a common formal background based on the theory of Abstract State Machines (ASMs) and are implemented in the AsmL language.

In the rest of the paper we focus only on the formal verification, i.e. the model checking of AsmL specifications. The simulation and model-based testing approaches are based on the tool support coming together with AsmL and are out of the scope of this paper.

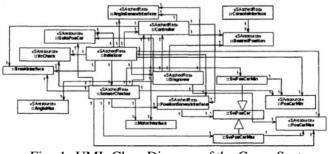

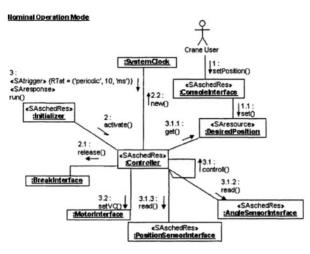

Figure 1. Verification framework for UML-based design

### **3. FORMALIZING UML SEMANTICS**

The main prerequisite for integration of the proposed verification methods into the verification framework is the presence of a rigorous formal semantics of the modeling paradigm, in our case represented by the Unified Modeling Language (UML 2.0) [1]. Therefore, choosing the right formal method is one of the crucial decisions to be taken. In our approach the *Abstract State Machines* (ASMs) [2] has been chosen as a suitable formalism to define the formal semantics of UML. The ASMs have approved their strong modeling and specification abilities in various application domains [3] also including work on formalization of selected parts of the older version of UML [4,5]. In particular, we adopted the AsmL language [6], an executable specification language built upon the theory of Abstract State Machines, to formally describe the UML semantics.

Formalizing the UML semantics is a tedious task, especially when the complexity and vastness of the whole UML 2.0 is considered. Therefore, our aim is not to formalize the complete semantics of UML. Instead, we consider only those UML diagrams that have been adopted into our design methodologies focusing on the two main application domains we are active in: the design of distributed production control systems and the design of self-optimizing multi-agent systems with mechatronic components. In the former, UML is applied to model distributed software for controlling

production lines. We use UML structure diagrams, collaboration diagrams and state machine diagrams combined with modeling of actions by means of so-called Story Diagrams [7]. In the latter, similar diagrams are employed except that the state machine diagrams are extended with discrete time semantics. Due to the fact that the formalization process is out of the scope of this paper we omit further details.

Although both application domains strongly overlap, there still exist specific semantic deviations that result in partially different semantic models of UML written in AsmL. However, the verification framework presented in this paper does not depend on any semantic deviations. The solution resides in using the AsmL as formal platform for all verification and validation methods of the framework that are designed in a way to support any AsmL specification regardless of what it describes.

# 4. MODEL CHECKING ASML MODELS

One of the qualities of AsmL is the high expressivity and richness of the language that allows us to keep the semantic models of UML in a readable and comprehensible form. This gives us flexibility in further maintenance of the semantic models and eases their modification and updating. However, in order to keep this advantage of AsmL we need to provide such a model checking approach that imposes least restrictions on the AsmL specification. Concretely, an AsmL specification should be allowed to fully exploit the robust data type system build in the AsmL, should allow dynamic object creation as well as usage of whole operational functionality provided by AsmL. The only constraint imposed on a specification is related to the size of its state space that has to be finite. The model checking approach presented in the next sections obeys all these requirements. It can be classified as an on-the-fly approach working over the explicit ASM state.

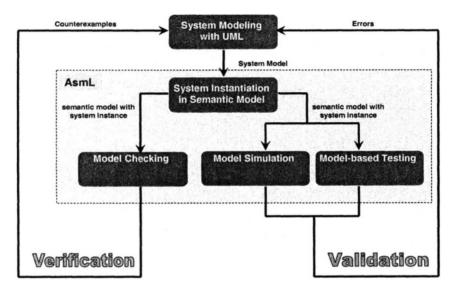

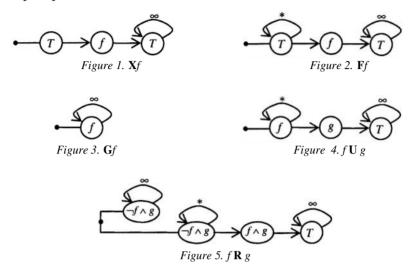

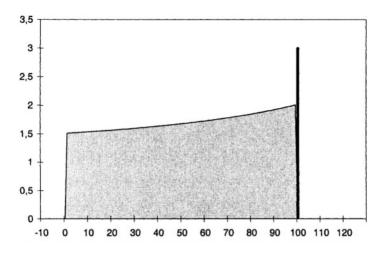

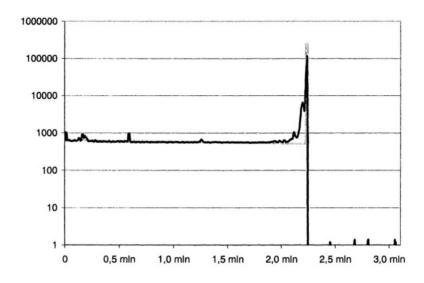

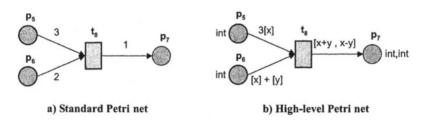

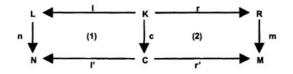

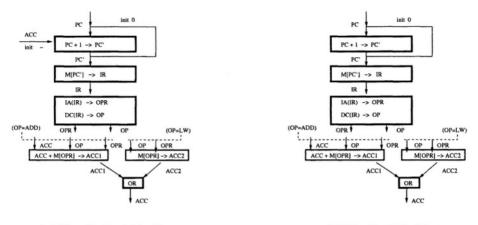

# 4.1 On-the-fly model checking

The intended model checking approach is depicted in the Figure 2. First of all, a particular AsmL specification and the property to be verified are provided as inputs. The property is specified in form of a temporal logic formula. In the first step, the temporal formula is transformed into a property automaton. As next, the AsmL specification is compiled and prepared for on-the-fly exploration. When both steps are successfully finished, the verification algorithm is started. During this process the state space exploration of a given AsmL specification is driven by the verification algorithm in an on-demand manner. The verification process may terminate in one of the following states: 1) in the OK state, after the whole state space has been explored and no contradiction of the property has been detected, 2) in the contradiction state, if a state of the system is found that does not satisfy the property and a counter example is produced 3) in the exception state, when an exception inside the specification is thrown during the state space exploration, and 4) in the user termination state, if the verification process was forced by the user to terminate.

Figure 2. On-the-fly model checking of AsmL

#### 4.1.1 Property specification and transformation

During model checking a system is verified against a property describing the desired system behavior. The property is expressed in form of a temporal logic formula. There exist several kinds of temporal logics, e.g. CTL, LTL, CTL\* which usually differ in the set of expressible behaviors. In our approach we consider the CTL\* logic that subsumes both CTL and LTL. The transformation of a CTL\* formula into an automaton is done following the method introduced in [8]. This method uses a set of predefined goaldirected rules to derive the states of specialized tree automata called alternating Büchi tableau automata (ABTAs). An ABTA represents the property automaton showed in Figure 2.

#### 4.1.2 Transition system construction

A transition system (a state transition graph) derived from an AsmL specification represents all possible runs of the specification. Obviously, the construction of such a transition system is, with respect to the needed time and resources, the most costly part of the overall model checking process. Therefore, we propose an on-the-fly construction approach that uses the exploration function built-in in the AsmL Toolkit. This function should allow us to drive the exploration of the system state space according to the demands of the verification algorithm. Additionally, the configurability of the exploration process gives us the apparatus to control how the state space is going to be explored. Thanks to this feature, even an infinite specification can be model checked within a fixed state space boundary (bounded model checking).

#### 4.1.3 Verification algorithm

The model checking algorithm adopted in our approach originates in the work presented in [8]. It works over a product automaton, constructed from the produced property automaton and the transition system. Since, in our case, the transition system is generated in an on-the-fly manner, the original algorithm had to be adapted accordingly. In addition, the algorithm was redesigned in order to achieve a certain generics with respect to the implementations of transition system and property automaton. This gives us towards more freedom for experiments achievement of optimal implementations.

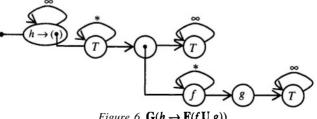

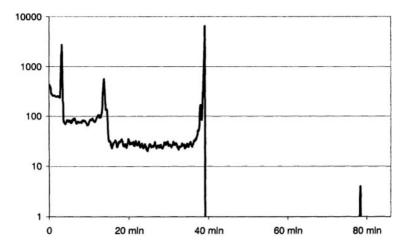

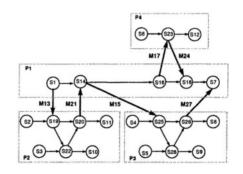

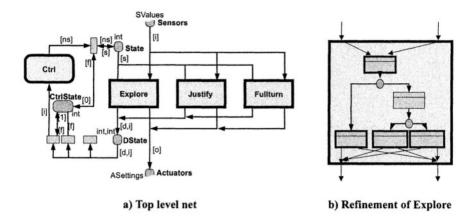

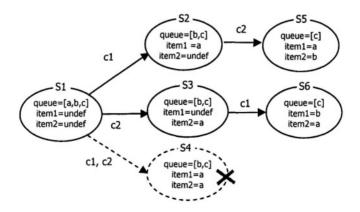

# 4.2 Incremental Model Checking

The presented model checking approach, similar to any other existing approaches, can show its weakness when it comes to verification of AsmL specifications that have a large state space. This is typical for example for distributed systems that consist of several interacting components running in parallel. In order to cope also with such distributed systems we propose a solution embedded into our verification framework. The main idea resides in defining an algorithm that is capable of executing the model checking in an incremental manner. The algorithm proposed here, depicted in Figure 3, can be seen as an enhancement of the on-the-fly algorithm presented above. It considers an AsmL specification consisting of several components (ASM

agents) running in parallel and affecting each other only through their precisely defined communication. In addition, the properties to be verified are constrained to only ACTL formulas (the CTL formulas with only universal quantifiers).

Figure 3. Control flow of incremental model checking

For an embedded system M with a finite set of variables  $V = \{v_1, v_2, ..., v_n\}$  $v_n$  where each variable  $v_i$  has an associated finite domain  $D_i$   $(1 \le i \le n)$ , the set of all possible states is  $D = D_1 \times D_2 \times \ldots \times D_n$ . Let P be the set of atomic propositions derived from the system. Then the system can be represented as a Kripke structure M = (S, I, R, L) where S = D is the set of states,  $I \subset S$  is the set of initial states,  $R \subseteq S \times S$  is the transition relation between states and L:  $S \rightarrow 2^{P}$  is the labeling function. Given an ACTL property f, to avoid checking the satisfiability of f directly on M due to the state space explosion problem, we can obtain an abstract model (initial abstraction) from the original system by applying an appropriate abstraction function h to M. Intuitively, the abstraction function h induces an equivalence relation  $\equiv_h$  on the domain D. That is, let d, e be states in D, then  $d \equiv_h e$  iff h(d) = h(e). It means that the equivalence relation  $\equiv_h$  partitions D into a set of equivalence class denoted as  $[D]_h = \{[d] \mid d \in D\}$  where  $[d] = \{e \in D \mid h(e) = h(d)\}$ . If we regard each equivalence class [d] as a state from an abstract view, an abstract *Kripke* structure  $M_h = (S_h, I_h, R_h, L_h)$  derived from M with respect to h can be defined as follows:

- 1.  $S_h$  is the abstract domain  $[D]_h$ ;

- 2.  $I_h = \{ [d] \mid \exists e (e \in [d] \land e \in I) \};$

- 3.  $R_h = \{([d_1], [d_2]) \mid \exists e_1 \exists e_2 (e_1 \in [d_1] \land e_2 \in [d_2] \land (e_1, e_2) \in R\};$

- 4.  $L_h([d]) = \bigcup_{e \in [d]} L(e).$

Usually, the abstraction function h can be obtained by analyzing the dependency relationship between the variables in the system as well as the effect of these variables on the property to be verified. It is obvious that  $M_h$

covers all possible behaviors of M but contains fewer states and fewer transitions than M. In this sense,  $M_h$  is an upper approximation to M, which means that an ACTL formula f true in  $M_h$  implies it's also true in M. However, in case that  $M_h$  falsifies f, the counterexample may be the result of some behavior in  $M_h$  which is not present in the original model M. Therefore, by refining  $M_h$  to a more precise model, i.e. far closer to M, it is possible to make the behavior which caused the erroneous counterexample disappear. For the refinement of  $M_h$ , we repeat the above procedure until a definite conclusion can be drawn. During this procedure, the initial abstraction  $M_h$  will be refined more and more close towards M. The refinement can be done based on the information derived from erroneous counterexamples [19]. As a result, the refined model is obtained by splitting the abstract state causing the erroneous counterexample into two subsets of the states, each of which represents a new abstract state. In this way, the erroneous counterexample does not exist in the refined model any more.

Given an abstraction function h, it is easy to know that the initial abstract model  $M_h$  can be constructed on-the-fly. Consequently, we can apply the onthe-fly model checking mentioned in section 4.1 to the abstract model of the original system M. If the abstract model satisfies f, then we can conclude the original system satisfies f. In case that a counterexample is found, we can locate the first abstract state which can cause the counterexample and then split the abstract state into two abstract states. Afterwards, we continue the on-the-fly model checking on this modified abstract model until a definite answer is obtained.

# 5. **RELATED WORK**

Many methods on model checking UML model [9,10,11,12,13] have been presented in recent years. The basic idea of all these methods is to transform the UML model to the input language of an existing model checking tool, say SMV, SPIN or UPPAAL for example. In other words, the semantics of the UML model is reflected through the input language of some model checker. The expressiveness of the model checker's input language usually limits the expressiveness of the checked UML model. Unlike these methods, our method presented in this paper uses the ASM-based executable specification language AsmL to define the semantics of the UML model. The expressive power of AsmL allows us to formalize the semantics of any complex UML model that implies no constraints on used UML diagrams at the user's side. In addition, the resulting AsmL specification can be executed or tested by the tools coming with AsmL.

Of course, AsmL can also be used to do model checking. Since AsmL is quite a new language, there are no published approaches aimed at model checking AsmL yet. However, a few papers can be found concerning model checking of Abstract State Machines [14,15,16]. Basically, we can identify two main approaches both based on translation of the selected subsets of ASMs into the input language of an existing model checking tool. In the [14,15] an ASM model is first simplified by flattening the data structure and the corresponding ASM rules, and then translated (by direct mapping) to the SMV [17] input language. The approach introduced in [16] follows similar strategy, but uses the SPIN [18] model checker and its PROMELA language. The main drawbacks of both approaches consist in the constraints imposed on the supported ASM models. On the other hand, imposing such constraints seemed to be an inevitable decision in order to bridge the gap between the different expressive power of ASMs and the model checker languages. Our method can avoid this problem by model checking AsmL specifications directly.

# 6. CONCLUSION AND FUTURE WORK