# Second Edition BUILDING A SUCCESSFUL BOARD-TEST STRATEGY

### Stephen F. Scheiber

Newnes

Test&Measurement

### Building a Successful Board-Test Strategy

This page intentionally left blank

## Building a Successful Board-Test Strategy

### **Second Edition**

Stephen F. Scheiber

Boston Oxford Johannesburg Melbourne New Delhi

Newnes is an imprint of Butterworth-Heinemann. Copyright © 2001 by Butterworth-Heinemann

**R** A member of the Reed Elsevier group

All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

Some material contained herein is derived from IEEE Std. 1014–1987, IEEE Standard for Versatile Backplane Bus: VMEbus, IEEE Std. 1049.1–1990, IEEE Standard Test Methods and Boundary-Scan Architecture, and IEEE Std. 1155–1992, IEEE Standard VMEbus Extensions for Instrumentation: VXIbus, copyrights by the Institute of Electrical and Electronics Engineers, Inc. The IEEE takes no responsibility for and will assume no liability for damages resulting from the reader's misinterpretation of said information resulting from the placement and context in this publication. Information is reproduced with the permission of the IEEE.

Recognizing the importance of preserving what has been written, Butterworth-Heinemann prints its books on acid-free paper whenever possible.

Library of Congress Cataloging-in-Publication Data

Scheiber, Stephen F.

Building a successful board-test strategy / Stephen F. Scheiber.

p. cm.

Includes bibliographical references and index.

ISBN 0-7506-7280-3 (pbk. : alk. paper)

1. Printed circuits-Testing. I. Title.

TK7868.P7 S34 2001

621.3815'310287-dc21

2001032680

British Library Cataloguing-in-Publication Data A catalogue record for this book is available from the British Library. The publisher offers special discounts on bulk orders of this book. For information, please contact: Manager of Special Sales Butterworth-Heinemann 225 Wildwood Avenue Woburn, MA 01801-2041 Tel: 781-904-2500 Fax: 781-904-2620

For information on all Newnes publications available, contact our World Wide Web home page at: http://www.newnespress.com

10 9 8 7 6 5 4 3 2 1

Printed in the United States of America

## Contents

| Pretace to the Second Edition |                                               | X  |

|-------------------------------|-----------------------------------------------|----|

| Cha                           | pter 1 What Is a Test Strategy?               | 1  |

| 1.1                           | Why Are You Here?                             | 3  |

| 1.2                           | It Isn't Just Testing Anymore                 | 3  |

| 1.3                           | Strategies and Tactics                        | 4  |

|                               | 1.3.1 The First Step                          | 5  |

|                               | 1.3.2 Life Cycles                             | 6  |

| 1.4                           | The Design and Test Process                   | 9  |

|                               | 1.4.1 Breaking Down the Walls                 | 10 |

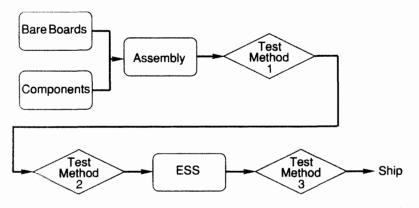

|                               | 1.4.2 Making the Product                      | 15 |

|                               | 1.4.3 New Challenges                          | 16 |

| 1.5                           | Concurrent Engineering Is Not Going Away      | 17 |

| 1.6                           | The Newspaper Model                           | 21 |

|                               | 1.6.1 Error Functions                         | 21 |

|                               | 1.6.2 What Do You Test?                       | 23 |

|                               | 1.6.3 Board Characteristics                   | 26 |

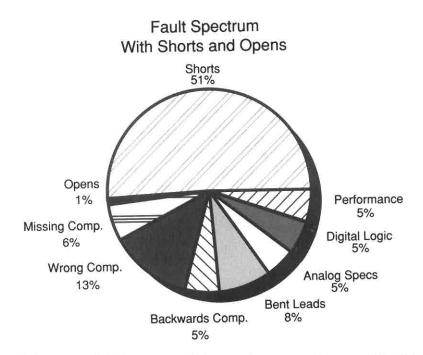

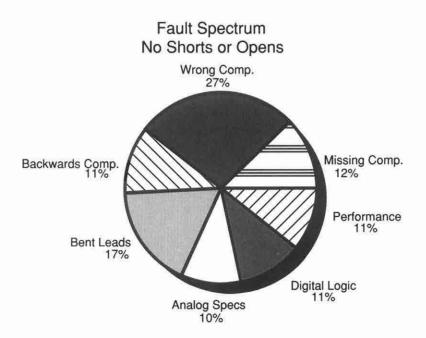

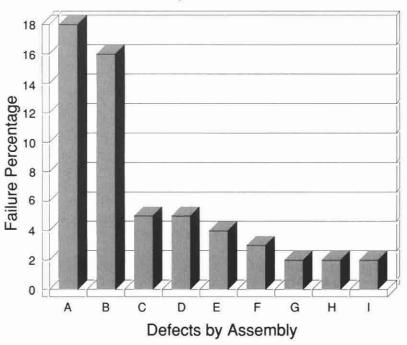

|                               | 1.6.4 The Fault Spectrum                      | 28 |

|                               | 1.6.5 Other Considerations                    | 34 |

|                               | 1.6.6 The How of Testing                      | 37 |

| 1.7                           | Test-Strategy Costs                           | 39 |

|                               | 1.7.1 Cost Components                         | 40 |

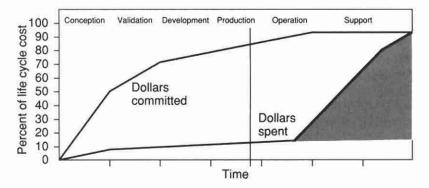

|                               | 1.7.2 Committed vs. Out-of-Pocket Costs       | 43 |

| 1.8                           | Project Scope                                 | 44 |

| 1.9                           | Statistical Process Control                   | 46 |

| 1.10                          | Summary                                       | 50 |

| Chaj                          | pter 2 Test Methods                           | 53 |

| 2.1                           | The Order-of-Magnitude Rule                   | 53 |

| 2.2                           | A Brief (Somewhat Apocryphal) History of Test | 55 |

| 2.3                           | Test Options                                  | 58 |

|                               | 2.3.1 Analog Measurements                     | 59 |

|     | 2.3.2    | Shorts-and-Opens Testers                             | 60  |

|-----|----------|------------------------------------------------------|-----|

|     | 2.3.3    | Manufacturing-Defects Analyzers                      | 61  |

|     | 2.3.4    | In-Circuit Testers                                   | 62  |

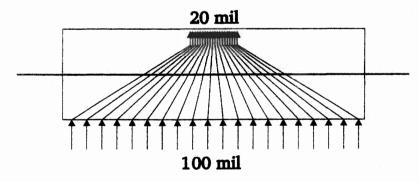

|     | 2.3.5    | Bed-of-Nails Fixtures                                | 68  |

|     | 2.3.6    | Bed-of-Nails Probe Considerations                    | 71  |

|     | 2.3.7    | Opens Testing                                        | 76  |

|     | 2.3.8    | Other Access Issues                                  | 79  |

|     | 2.3.9    | Functional Testers                                   | 80  |

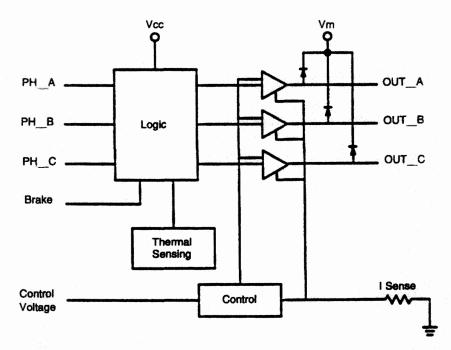

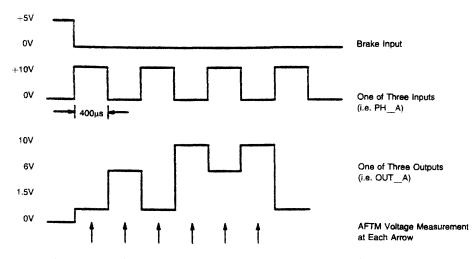

|     | 2.3.10   | Functional Tester Architectures                      | 83  |

|     | 2.3.11   | Finding Faults with Functional Testers               | 88  |

|     | 2.3.12   | Two Techniques, One Box                              | 91  |

|     | 2.3.13   | Hot-Mockup                                           | 92  |

|     | 2.3.14   | Architectural Models                                 | 93  |

|     | 2.3.15   | Other Options                                        | 96  |

| 2.4 | Summa    | ary                                                  | 96  |

| Cha | ntor 3 I | nspection as Test                                    | 97  |

|     | _ `      |                                                      |     |

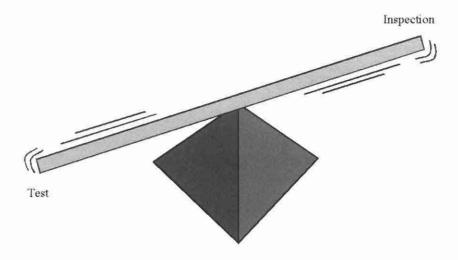

| 3.1 |          | g a Balance                                          | 98  |

| 3.2 |          | aste Inspection                                      | 101 |

| 3.3 |          | lacement/Post-Reflow                                 | 103 |

|     |          | Manual Inspection                                    | 107 |

|     |          | Automated Optical Inspection (AOI)                   | 108 |

|     |          | Design for Inspection                                | 111 |

|     | 3.3.4    | Infrared Inspection—A New Look at an Old Alternative | 111 |

|     |          | 3.3.4.1 A New Solution                               | 113 |

|     |          | 3.3.4.2 Predicting Future Failures                   | 114 |

|     |          | 3.3.4.3 The Infrared Test Process                    | 115 |

|     | 225      | 3.3.4.4 No Good Deed                                 | 116 |

|     | 3.3.3    | The New Jerusalem?—X-Ray Inspection                  | 117 |

|     |          | 3.3.5.1 A Catalog of Techniques                      | 121 |

|     |          | 3.3.5.2 X-Ray Imaging                                | 122 |

| 3.4 | Summ     | 3.3.5.3 Analyzing Ball-Grid Arrays                   | 124 |

| 2   |          |                                                      | 120 |

| Cha | pter 4 ( | Guidelines for a Cost-Effective "Test" Operation     | 129 |

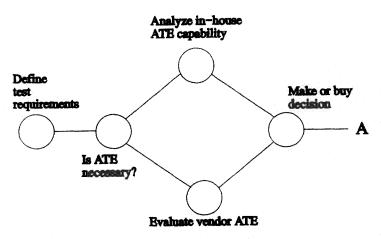

| 4.1 | Defin    | e Test Requirements                                  | 129 |

| 4.2 |          | tomatic Test or Inspection Equipment Necessary?      | 133 |

| 4.3 |          | ate Test and Inspection Options                      | 134 |

| 4.4 |          | Make-or-Buy Decision                                 | 137 |

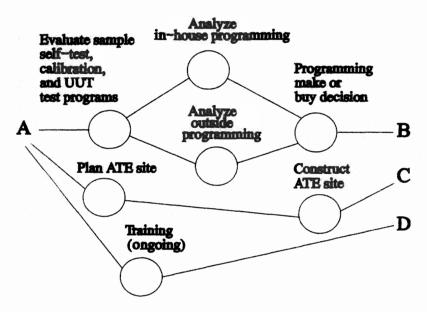

| 4.5 |          | ng Ready                                             | 138 |

| 4.6 | Progr    | amming—Another Make-or-Buy Decision                  | 140 |

| 4.7 | The T    | Test Site                                            | 143 |

| 4.8 | Train    |                                                      | 144 |

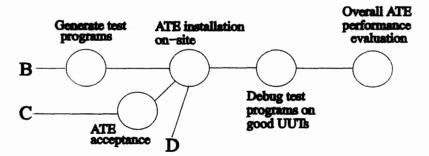

| 4.9 | Puttir   | ng It All in Place                                   | 145 |

| 4.10 | Managing Transition                                     | 147 |

|------|---------------------------------------------------------|-----|

| 4.11 | Other Issues                                            | 149 |

| 4.12 | Summary                                                 | 149 |

| Chaj | pter 5 Reducing Test-Generation Pain with Boundary Scan | 151 |

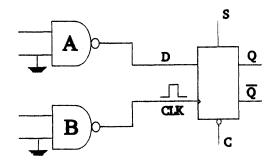

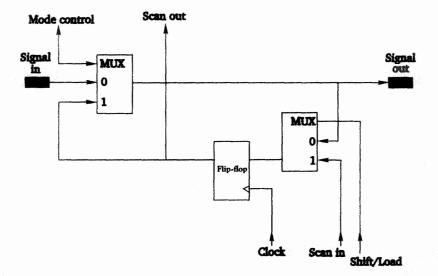

| 5.1  | Latch-Scanning Arrangements                             | 151 |

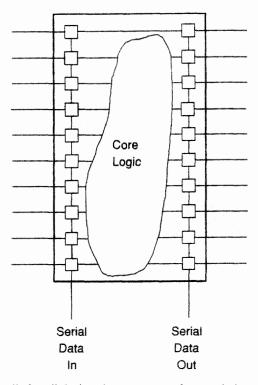

| 5.2  | Enter Boundary Scan                                     | 153 |

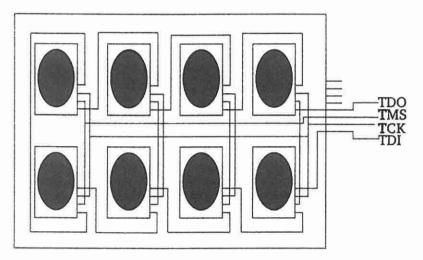

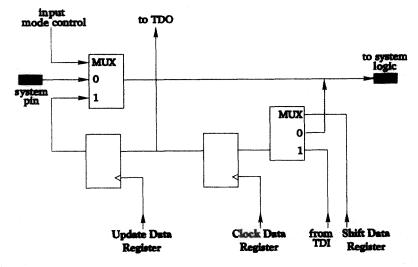

| 5.3  | Hardware Requirements                                   | 158 |

| 5.4  | Modes and Instructions                                  | 161 |

| 5.5  | Implementing Boundary Scan                              | 163 |

| 5.6  | Partial-Boundary-Scan Testing                           | 166 |

|      | 5.6.1 Conventional Shorts Test                          | 167 |

|      | 5.6.2 Boundary-Scan Integrity Test                      | 167 |

|      | 5.6.3 Interactions Tests                                | 168 |

|      | 5.6.4 Interconnect Test                                 | 169 |

| 5.7  | Other Alternatives                                      | 170 |

| 5.8  | Summary                                                 | 172 |

| Chaj | pter 6 The VMEbus eXtension for Instrumentation         | 173 |

| 6.1  | VME Background                                          | 174 |

| 6.2  | VXI Extensions                                          | 178 |

| 6.3  | Assembling VXI Systems                                  | 184 |

| 6.4  | Configuration Techniques                                | 190 |

| 6.5  | Software Issues                                         | 191 |

| 6.6  | Testing Boards                                          | 193 |

| 6.7  | The VXIbus Project                                      | 194 |

| 6.8  | Yin and Yang                                            | 196 |

| 6.9  | Summary                                                 | 197 |

| Chaj | pter 7 Environmental-Stress Screening                   | 199 |

| 7.1  | The "Bathtub Curve"                                     | 199 |

| 7.2  | What Is Environmental-Stress Screening?                 | 201 |

| 7.3  | Screening Levels                                        | 202 |

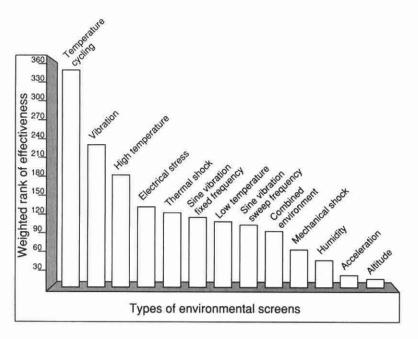

| 7.4  | Screening Methods                                       | 202 |

|      | 7.4.1 Burn-in                                           | 202 |

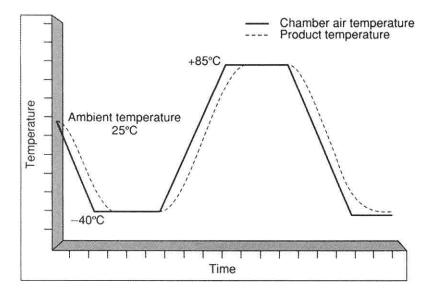

|      | 7.4.2 Temperature Cycling                               | 204 |

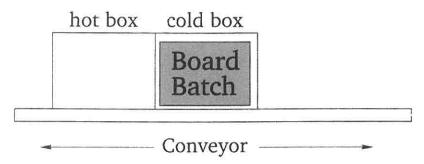

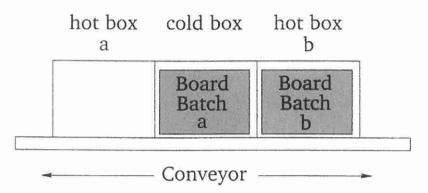

|      | 7.4.3 Burn-in and Temperature-Cycling Equipment         | 206 |

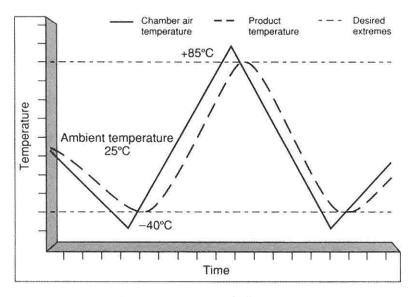

|      | 7.4.4 Thermal Shock                                     | 207 |

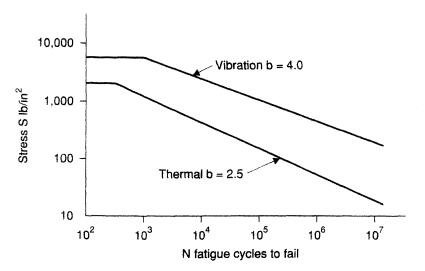

|      | 7.4.5 Mechanical Shock and Vibration                    | 208 |

|      | 7.4.6 Other Techniques                                  | 210 |

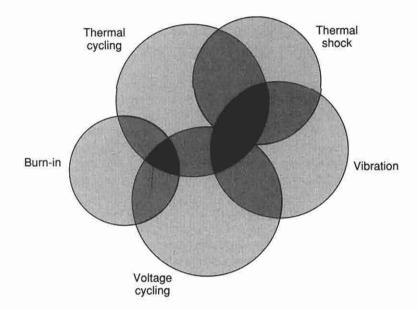

|      | 7.4.7 Combined Screens                                  | 210 |

| 7.5  | Failure Analysis                                        | 212 |

| 7.6  | ESS Costs                                               | 212 |

| 7.7<br>7.8<br>7.9 | To Screen or Not to Screen<br>Implementation Realities<br>Long-Term Effects | 213<br>214<br>215 |

|-------------------|-----------------------------------------------------------------------------|-------------------|

| 7.10              |                                                                             | 217               |

|                   | 7.10.1 Analogic                                                             | 217               |

|                   | 7.10.2 Bendix                                                               | 217               |

|                   | 7.10.3 Hewlett-Packard (now Agilent Technologies)                           | 218               |

| 7.11              | Summary                                                                     | 218               |

| Chaj              | pter 8 Evaluating Real Tester Speeds                                        | 219               |

| 8.1               | Resolution and Skew                                                         | 220               |

| 8.2               | Voltage vs. Time                                                            | 222               |

| 8.3               | Other Uncertainties                                                         | 224               |

| 8.4               | Impact of Test-Method Choices                                               | 225               |

| 8.5               | Summary                                                                     | 228               |

| Chaj              | oter 9 Test-Program Development and Simulation                              | 230               |

| 9.1               | The Program-Generation Process                                              | 230               |

| 9.2               | Cutting Test-Programming Time and Costs                                     | 232               |

| 9.3               | Simulation vs. Prototyping                                                  | 236               |

| 9.4               | Design for Testability                                                      | 237               |

| 9.5               | Summary                                                                     | 239               |

| Chaj              | oter 10 Test-Strategy Economics                                             | 241               |

| 10.1              | Manufacturing Costs                                                         | 242               |

| 10.2              | Test-Cost Breakdown                                                         | 243               |

|                   | 10.2.1 Startup costs                                                        | 244               |

|                   | 10.2.2 Operating costs                                                      | 246               |

|                   | 10.2.3 Maintenance and Repair                                               | 248               |

| 10.3              | Workload Analysis                                                           | 249               |

| 10.4              | An Order-of-Magnitude Rule Counterexample                                   | 251               |

| 10.5              | Comparing Test Strategies                                                   | 253               |

| 10.6              | Break-Even Analysis                                                         | 256               |

|                   | 10.6.1 Payback Period                                                       | 257               |

|                   | 10.6.2 Accounting Rate of Return                                            | 258               |

|                   | 10.6.3 The Time Value of Money                                              | 259               |

|                   | 10.6.4 Net Present Value                                                    | 260               |

|                   | 10.6.5 Internal Rate of Return                                              | 262               |

| 10.7              | Estimating Cash Flows                                                       | 263               |

| 10.8              | Assessing the Costs                                                         |                   |

| 10.9              | Summary                                                                     | 265               |

| Chapter 11 Formulating a Board-Test Strategy |                                                    |     |

|----------------------------------------------|----------------------------------------------------|-----|

| 11.1                                         | Modern Tester Classifications                      | 267 |

| 11.2                                         | Establishing and Monitoring Test Goals             | 268 |

| 11.3                                         | Data Analysis and Management                       | 270 |

| 11.4                                         | Indicators of an Effective Strategy                | 273 |

| 11.5                                         | Yin and Yang in Ease of Tester Operation           | 274 |

| 11.6                                         | More "Make-or-Buy" Considerations                  | 275 |

| 11.7                                         | General-Purpose vs. Dedicated Testers              | 278 |

| 11.8                                         | Used Equipment                                     | 279 |

| 11.9                                         | Leasing                                            | 280 |

| 11.10                                        | "Pay as You Go"                                    | 281 |

| 11.11                                        | Other Considerations                               | 282 |

| 11.12                                        | The Ultimate "Buy" Decision—Contract Manufacturing | 282 |

| 11.13                                        | Summary                                            | 285 |

| Chapter 12 Test-Strategy Decisions           |                                                    | 286 |

| 12.1                                         | A Sample Test Philosophy                           | 286 |

| 12.2                                         | Big vs. Small                                      | 288 |

| 12.3                                         | Do You Need a High-End Tester?                     | 290 |

| 12.4                                         | Assembling the Strategy                            | 291 |

| 12.5                                         | The Benefits of Sampling                           | 294 |

| 12.6                                         | Tester Trends                                      | 295 |

| 12.7                                         | Sample Strategies                                  | 297 |

| 12.8                                         | A Real-Life Example                                | 301 |

| 12.9                                         | Changing Horses                                    | 304 |

| 12.10                                        | Summary                                            | 305 |

| Chapte                                       | r 13 Conclusions                                   | 307 |

| Appen                                        | dix A Time-Value-of-Money Tables                   | 309 |

| Appen                                        | dix B Acronym Glossary                             | 318 |

| Works Cited and Additional Readings          |                                                    | 321 |

| Index                                        |                                                    | 329 |

### Preface to the Second Edition

When I wrote the first edition of *Building a Successful Board-Test Strategy*, my intent was to avoid (as much as possible) the malady that plagues many books in our industry: like the products they deal with, they become obsolete before release to the public. To accomplish this goal, the book discussed tools, alternatives, and ways to evaluate and select test strategies, rather than dictating what those strategies should be.

In many respects, I succeeded. Most of the comments in the original edition are as true today as when they were written. Nevertheless, the industry refuses to stand still. Test has undergone something of a transformation in the past few years. The migration of production capacity away from traditional manufacturers toward contractors continues to accelerate. Today's army of contractors ranges from "garage shops" catering to complex very-low-volume products to multibillion-dollar megaliths handling board volumes in the millions. This continuing evolution brings with it new challenges, the most significant of which is how to select a contract manufacturer. Such vendors are not like commodity products. As with pieces of test equipment, contractors offer a wide range of strengths and areas of expertise. Choosing one requires finding a combination of skills and capabilities that best matches your needs. Discussions throughout the new edition take this trend into account.

One development that I missed completely in the first edition was the plague that open circuits bring to our surface-mount world. Hidden nodes, board coplanarity (flatness), and other characteristics of today's boards require another look at test methods. A new section of Chapter 2 explores these issues.

The concept of what constitutes a "test" strategy is evolving as well. Various forms of inspection, once mere adjuncts to the quality process, have become intimately linked with more traditional forms of conventional test. Then, too, inspection is not a single technique, but in fact a menu of approaches, each of which has advantages and drawbacks. The new Chapter 3, "Inspection as Test," examines this solution in considerable detail.

This new edition also updates information in many places, adding examples and figures to prior discussions. Much of the additional material comes from seminars that I have given in the past few years—both my own work and material from attendees. Some of those contributions are attributed to their sources. Other examples must remain by their nature anonymous. Nevertheless, I appreciate all of the assistance I have received.

At the risk of leaving out some important names, I would like to thank certain people explicitly for their help. Bob Stasonis at GenRad, Jim Hutchinson at Agilent Technologies, Charla Gabert at Teradyne, and Robin Reid at CyberOptics provided considerable assistance for the chapter on inspection. Jon Titus, Editorial Director at *Test & Measurement World*, has provided constant encouragement along with a stream of contact suggestions and source recommendations over many years. And, of course, my family has once again had to endure my particular brand of craziness as I rushed to complete this project.

> Stephen F. Scheiber December 18, 2000

This page intentionally left blank

CHAPTER

### What Is a Test Strategy?

This book examines various board-test techniques, relating how they fit into an overall product design/manufacturing/test strategy. It discusses economic, management, and technical issues, and attempts to weave them into a coherent fabric. Looking at that fabric as a whole is much more rewarding than paying too close attention to any individual thread. Although some of the specific issues have changed in the past few years, the basic principles remain relatively constant.

Printed-circuit boards do not exist in a vacuum. They consist of components and electrical connections and represent the heart of electronic systems. Components, boards, and systems, in turn, do not spring to life full-blown. Designers conceive them, manufacturing engineers construct them, and test engineers make sure that they work. Each group has a set of tools, criteria, and goals. To be successful, any test strategy must take all of these steps into account.

Test managers coined the briefly popular buzzword "concurrent engineering" to describe this shared relationship. More recently, enthusiasm for concurrent engineering has waned. Yet the ideas behind it are the same ones that the test industry has been touting for as long as anyone can remember. The term represents merely a compendium of techniques for "design-for-marketability," "design-for-manufacturability," "design-for-testability," "design-for-repairability," and so on. The fact that the term "concurrent engineering" caught on for awhile was great. A company's overall performance depends heavily on everyone working together. Regardless of what you call it, many manufacturers continue to follow "design-forwhatever" principles. For those who do not understand this "we are all in it together" philosophy, a new term for it will not help.

Concurrent engineering boils down to simple common sense. Unfortunately, as one basic law of human nature so succinctly puts it, "Common sense isn't." In many organizations, for example, each department is responsible only for its own costs. Yet, minimizing each department's costs does not necessarily minimize costs across an entire project. Reducing the costs in one department may simply push them off to someone else. Achieving highest efficiency at the lowest cost requires that all of a project's participants consider their activities' impact on other departments as well as their own.

The test-engineering industry is already feeling the effects of this more global approach to test problems. Trade shows geared exclusively toward testing electronics—aside from the annual International Test Conference sponsored by the IEEE—have largely passed into the pages of history. Instead, test has become an integral part of trade shows geared to printed-circuit-board *manufacturing*. There are two basic reasons for this phenomenon. When test shows first appeared, test operations enjoyed little visibility within most organizations. The shows helped focus attention on testing and disseminated information on how to make it work. In addition, most companies regarded testing as an isolated activity, adopting the "over-the-wall" approach to product design. That is, "I designed it, now you figure out how to test it."

Today, neither of those situations exists. Everyone is aware of the challenges of product test, even as they strive to eliminate its huge costs and its impact on time to market. Managers in particular dislike its constant reminders that the manufacturing process is not perfect. They feel that if engineering and manufacturing personnel had done their jobs right the first time, testing would not be necessary.

Also, in the past few years, product-manufacturing philosophy has migrated away from the vertically integrated approach that served the industry for so long. Companies still design and market their creations, but someone else often produces them and makes sure that they work. Even within large companies that technically perform this task themselves, production flows through one or a few dedicated facilities. These facilities may differ legally from contract manufacturers, but from a practical standpoint they serve the same purpose, possessing both the same advantages and the same drawbacks.

Because of the popularity of at least the concept of concurrent engineering, considering test activities as distinct from the rest of a manufacturing process is no longer fashionable. Design engineers must deliver a clean product to either inhouse or contract manufacturing to facilitate assembly, testing, and prompt shipment to customers. Depot repair and field-service engineers may need to cope with that product's failure years later. With the constant rapid evolution of electronic products, by the time a product returns for repair, the factory may no longer make it at all.

Therefore, although this book is specifically about building board-test strategies, its principles and recommendations stray far afield from that relatively narrow venue. The most successful board-test strategy must include all steps necessary to ship a quality product, whether or not those steps relate directly to the test process itself.

The aim of this book is not to provide the ultimate test strategy for any specific situation. No general discussion can do that. Nobody understands a particular manufacturing situation better than the individuals involved. This book will describe technical and management tools and fit them into the sociology and politics of an organization. You must decide for yourself how to adapt these tools to your needs.

#### 1.1 Why Are You Here?

What drives you to the rather daunting task of reading a textbook on boardtest strategy? Although reasons can vary as much as the manufacturing techniques themselves, they usually break down into some version of the following:

- The manufacturing process is getting away from you,

- Test represents your primary bottleneck, and

- Test has become part of the problem rather than part of the solution.

The design-and-test process must treat "test" as an ongoing activity. Its goal is to furnish a clean product to manufacturing by designing for manufacturability and testability, while encouraging the highest possible product quality and reliability. (Product *quality* means that it functions when it leaves the factory. *Reliability* refers to its resistance to failure in the field.)

The purpose of manufacturing is to provide:

- The most products

- At the lowest possible cost

- In the shortest time

- At the highest possible quality

Debate has raged for years over the relative importance of these goals. Certainly, test people often maintain that quality should be paramount, while management prefers to look first at costs. Nevertheless, a company that cannot provide enough products to satisfy its customers will not stay in business for very long.

Suppose, for example, that you have contracted to provide 100,000 personalcomputer (PC) motherboards over some period of time, and in that time you can deliver 50,000 perfect motherboards. Despite superior product quality, if you cannot meet the contract's volume requirements, the customer will fly into the arms of one or more of your competitors who can.

Using similar reasoning, the purpose of "test" is to maximize product throughput, reduce warranty failures, and enhance your company's reputation thereby generating additional business and keeping jobs secure. We get there by designing the best, most efficient test strategy for each specific situation.

#### 1.2 It Isn't Just Testing Anymore

Therein lies part of the problem. What is "test"? Unless we broaden the concept to include more quality-assurance activities, verifying product quality through "test" will soon approach impossible.

Inspection, for example, is usually considered part of *manufacturing*, rather than test. Simple human nature suggests that this perception tends to make test engineers less likely to include it in a comprehensive strategy. Yet inspection can identify faults—such as missing components without bed-of-nails access or insufficient solder that makes proper contact only intermittently—that conventional test will miss.

Similarly, design for testability reduces the incidence of some faults and permits finding others more easily. Feeding failure information back into the process allows adjustments to improve future yields. These steps also belong as part of the larger concept of "test."

Embracing those steps in addition to the conventional definition of "test" allows test people to determine more easily the best point in the process to identify a particular fault or fault class. Pushing detection of certain faults further upstream reduces the cost of finding and repairing them. In addition, not looking for those same faults again downstream simplifies fixture and test-program generation, shortens manufacturing cycles, and reduces costs.

Test strategies have traditionally attempted to find every fault possible at each step. Adopting that approach ensures that several steps will try to identify at least some of the same faults. A more cost-effective alternative would push detection of all faults as far up in the process as possible, then avoid looking for any fault covered in an earlier step later on.

Self-test, too, forms part of this strategic approach. Many products include self-test, usually some kind of power-on test to assure the user that the system is functioning normally. Such tests often detect more than a third of possible fault mechanisms, sometimes much more. Which suggests the following "rules" for teststrategy development:

- · Inspect everything you can, test only what you must.

- Avoid looking for any problem more than once.

- Gather and analyze data from the product to give you useful information that allows you to improve the process.

#### **1.3 Strategies and Tactics**

Test strategies differ significantly from test tactics. In-circuit test, for example, is a tactic. Removing manufacturing defects represents the corresponding strategy. Other tactics for that strategy include manual and automated inspection, manufacturing-defects analysis (a subset of in-circuit test—see Chapter 2), and process improvement.

A strategy outlines the types of quality problems you will likely experience, then describes which of those problems you choose to fight through the design process during design verification, which you assign to test, and which you leave for "Let's wait until the product is in the field and the customer finds it."

The difference between strategies and tactics boils down to issues of term and focus. A test strategy lasts from a product's conception until the last unit in the field dies. During that time, the manufacturer may resort to many tactics. Also, a tactic addresses a particular place and time in the overall product life cycle. A strategy generally focuses on the whole picture.

In building a test strategy, we are always looking for "digital" answers to "analog" problems. That is, we must decide whether the product is good or bad. But how good is good? How bad does "bad" have to be before the circuit will not function? Suppose, for example, that the manufacturer of a digital device specifies a "0" as less than 0.8 volts. Based on that specification, a parametric measurement of a logic low at 0.81 volts would fail. Yet will the system actually not perceive a voltage of 0.81 as a clean "0"? How about 0.815 volts? The answer, of course, is a firm "It depends." The situation resembles the century-old conundrum: How many raindrops does it take before a baseball field is wet enough to delay the game? In that context, the question seems absurd. You can't count raindrops! Yet at some point, someone must make a value judgment. Most baseball people accept the fact that delaying the start of a game usually requires less rain than does stopping play once the game has begun. Similarly, the question of how closely a circuit must conform to published specifications may depend on surrounding circumstances. The *real* question remains: Does the product work? As product complexity continues to skyrocket, the necessity to accept the compromises implicit in this approach become glaringly apparent.

Compounding the challenge, issues of power consumption, heat dissipation, and portable-product battery life have required drastically reducing operating voltages for most digital systems. The 5V transistor-transistor logic (TTL) parts of the past have yielded to devices operating at less then 3V, with more to come. As a result, the gap between a logic "1" and a logic "0" narrows every day. Devices must perform more precisely; boards and systems cannot tolerate electromagnetic interference (EMI) and other noise that were commonplace only a few years ago. New generations of test equipment must cope with these developments, and test strategies must take them into account.

#### 1.3.1 The First Step

Consider a (loaded) question: What is the single most important consideration in developing a test strategy? The answer may seem obvious. Yet in board-teststrategy seminars from New York City to Singapore, responses range from budgets to design-for-testability to "Do we need to test?" to "Do we choose in-circuit or functional test?" Before facing any of these issues, however, designing a successful test strategy requires determining the nature of the product. That is, what are you trying to test? What is the product? What does it look like? How does it work? What design technologies does it contain? Who is designing it? Who is manufacturing it? Who is testing it? In many organizations, one obstacle to arriving at an effective test strategy is that the people involved decide on test-strategy components and tactics before answering these simple questions.

Test engineers do not design products. If nobody tells them what the product is, how it is designed, and what it is supposed to do, their decisions may make no sense. They might arrive at a correct strategy, but only by accident, and it would rarely represent both the most successful and the most economical approach.

Test components or test strategies that work for one company or product line may not be appropriate in another situation. If you do not know what you are trying to test, you cannot systematically determine the best strategy. Even if you find a strategy that works, thoroughly knowing the product will likely help you suggest a better one. Which brings us to the following definition: A successful test strategy represents the optimum blend of test methods and manufacturing processes to produce the best-quality boards and systems in sufficient number at the lowest possible cost.

Selling-price erosion among electronic products and electronic components of larger products exerts ever-increasing pressure on manufacturing and test operations to keep costs down. As they have for more than two decades, personal computers (PCs) provide an excellent case in point. The price of a particular level of PC technology declines by more than two-thirds every four years.

Looking at it another way, today's PCs are about 40 times as powerful as machines of only five years ago, at about the same price. Bill Machrone, one of the industry's leading analysts, describes this trend as what he calls "Machrone's Law": The computer you want will always cost \$5000. One could argue the magnitude of the number, which depends partly on the choice of printers and other peripherals, but the idea that a stable computer-equipment budget will yield increasingly capable machines is indisputable. Machrone's reputation as an industry prognosticator remains intact—especially when you consider that he coined the law in 1981!

Reasonably equipped PCs priced at under \$1000 have become increasingly common. Peripherals have reached commodity-pricing status. Even the microprocessors themselves are experiencing price pressure. PCs based on new microprocessors and other technologies rarely command a premium price for more than a few months before competition forces prices into line. Meanwhile, product-generation half-lives have fallen to less than a year, less than 6 months for some critical subsystems such as hard disk drives and CD-ROM readers and burners. Even flatpanel liquid-crystal displays (LCDs), once exorbitantly expensive, are beginning to replace conventional monitors—the last remaining tubes in common use.

Customers are forcing companies to cut manufacturing costs, while test costs remain stable at best and rise dramatically at worst. Test costs today often occupy one-third to one-half of the total manufacturing cost. Every dollar saved in testing (assuming an equivalent quality level) translates directly to a company's bottom line. For example, if manufacturing costs represent 40 percent of a product's selling price (a reasonable number) and test costs represent one-third of that 40 percent, then a strategy that reduces test costs by 25 percent reduces overall manufacturing costs to 36.67 percent, a difference of 3.33 percent. If the company was making a 10 percent profit, its profit increases to 13.33 percent, a difference of one-third. No wonder managers want to reduce test costs as much as possible!

#### 1.3.2 Life Cycles

A successful test strategy is a by-product of overall life-cycle management. It requires considering:

- Product development

- Manufacturing

- Test

- Service

- Field returns

- The company's "image of quality"

Note that only test, field returns, and service involve testing at all, and field returns do so only indirectly. Reducing the number of failures that get to the test process or the number of products that fail after shipment to customers also simplifies test activities, thereby minimizing costs.

Test-strategy selection goes far beyond merely choosing test techniques. Design issues, for example, include bare-board construction. An engineer once described a 50-layer board that was designed in such a way that it could not be easily repaired. To avoid the very expensive scrapping of bad boards, his colleagues borrowed a technique from designers of random access memory (RAM) components and large liquid-crystal-display (LCD) panels—they included redundant traces for most of the board's internal logic paths. Paths were chosen by soft switches driven by on-board components individually programmed for each board.

Although this solution was expensive, the board's \$100,000 price tag made such an expensive choice viable, especially because it was the only approach that would work. Without the redundancy, board yields would have been unacceptably low, and repair was impossible. Unfortunately, the solution created another problem. The board's components contained specific instructions to select knowngood paths. The bare board defied testing without component-level logic. Therefore, the engineers created a test fixture that meshed with the sockets on the board and mimicked its components. In addition to pass or fail information, the test would identify a successful path, then generate the program with which to burn the "traffic-cop" devices as part of its output. Including the redundancy as a design choice mandated a particular extremely complicated test strategy. Sometimes teststrategy choices reduce to "poor" and "none."

The acceptability of particular test steps depends on whether the strategy is for a new or existing facility, product, product line, or technology. In an existing facility, is there adequate floor space for expansion? Is the facility already running three work shifts, or can a change in strategy involve merely adding a shift?

Test managers must also decide whether to design their own test equipment or buy it from commercial vendors, whether they should try to "make do" with existing equipment, and whether new equipment must be the same type or from the same manufacturer as the installed base.

A test strategy's success also depends on aspects of the overall manufacturing operation. For instance, how does a product move from test station to repair station or from one test station to the next? Are there conveyors or other automated handlers, or do people transfer material manually? Concurrent-engineering principles encourage placing portions of the manufacturing process physically close to one another, thereby minimizing bottlenecks and in-transit product damage. This arrangement also encourages employees who perform different parts of the job to communicate with one another, which tends to increase manufacturing efficiencies and lower costs.

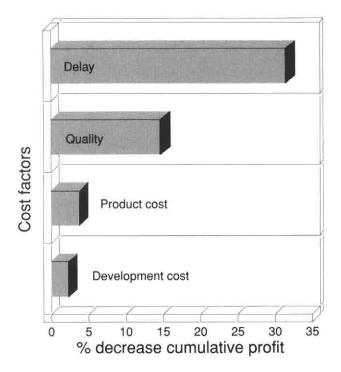

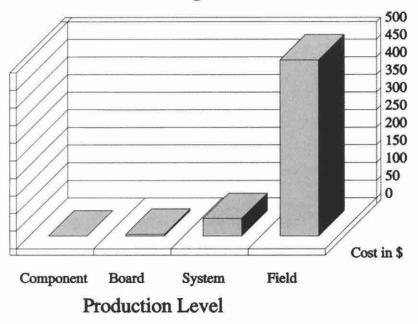

**Figure 1-1** The percent decrease in a product's overall profit potential resulting from a six-month delay in product introduction, a 10% product price discount to accommodate quality problems, a total product cost 10% higher than expected, and a 50% higher-than-expected development cost. Note that delaying the product has by far the most pronounced effect. Individual bar values are (from top to bottom): 31.5%; 14.9%; 3.8%; 2.3%. (Prang, Joe. 1992. "Controlling Life-Cycle Costs Through Concurrent Engineering," ATE & Instrumentation Conference, Miller-Freeman Trade-Show Division, Dallas, Texas.)

It seems fairly clear that company managers will not accept even the best test strategy if it exceeds allowable budgets. Yet, evidence suggests that increasing manufacturing costs is less damaging to a product's long-term profitability than is bringing the product to market late. Figure 1-1 shows such an example.

This figure assumes that the product has competitors. If a product is first in its market, delays shorten or eliminate the time during which it is unique and can therefore command a premium price. If a competitor gets in ahead of you because of delays, you lose all of your premium-price advantage. If you are addressing a market where someone else's product got there first, delays will reduce your new product's impact and may mean having to fight one or more additional competitors when it finally arrives.

Therefore, performing the absolute last test or getting out the very last fault may not be worthwhile. The commonly quoted Pareto rule states that the last 20 percent of a job requires 80 percent of the effort. In testing, the last 10 percent taking 90 percent of the effort might be more accurate.

This analysis is not meant to advocate shoddy product quality. Every company must establish a minimum acceptable level of quality below which it will not ship product. Again, that level depends on the nature of the product and its target customers.

Companies whose operations span the globe must also consider the enormous distances between design and manufacturing facilities. Language, time zones, and cultural differences become barriers to communication. In these situations, manufacturing must be fairly independent of product development. Design-tomanufacture, design-to-test, and similar practices become even more critical than for more centralized organizations.

Therefore, selecting an efficient, cost-effective test strategy is a mix of engineering, management, and economic principles, sprinkled with a modicum of common sense. This book tries to create a successful salad from those ingredients.

#### 1.4 The Design and Test Process

There are only three ways in which a board can fail.

*Poor-quality raw materials* result from inadequacies in the vendor's process or design. This category includes bad components; that is, components (including bare boards) that are nonfunctional or out of tolerance when they arrive from the vendor, rather than, for example, delicate CMOS components that blow up from static discharge during handling for board assembly.

If the board design is incorrect, it will not function properly in its target application, even if it passes quality-control or test procedures. An example would be a bare board containing traces that are too close together. Very fast signals may generate crosstalk or other kinds of noise. Impedance mismatches could cause reflections and ringing, producing errors in edge-sensitive devices ranging from microprocessors to simple flip-flops and counters. In addition, if the traces are too close together, loading components onto the board reliably while avoiding solder shorts and other problems may be impossible, so that even if the bare board technically contains no faults, the loaded board will not function.

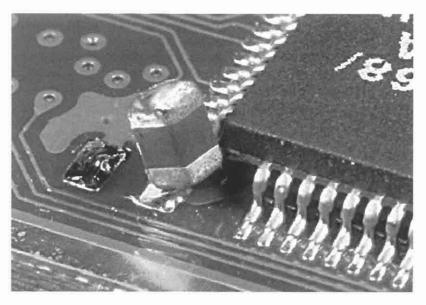

A board can also fail through *process variation*. In this case, the board design is correct but may not be built correctly. Faults can result from production variability, which can include the compounding of tolerances from components that individually lie within the nominal design specifications or from inconsistent accuracy in board assembly. Sometimes substituting one vendor's component for an allegedly equivalent component from another vendor will cause an otherwise functioning board to fail. Also in this group are design specifications, such as requiring components on both board sides, that increase the likelihood that the process will produce faulty boards. In addition, even a correct and efficient process can get out of control. Bent or broken device legs and off-pad solder or surface-mount parts fall into this category. The culprit might be an incorrectly adjusted pick-andplace machine, paste printer, or chip shooter. In these cases, test operations may identify the problem, but minimizing or preventing its recurrence requires tracing it back to its source, then performing equipment calibrations or other process-wide changes.

The relative occurrence of each of these failure mechanisms depends on manufacturing-process characteristics. Board-to-board process variation, for example, tends to be most common when assembly is primarily manual. You can minimize the occurrence of these essentially random failures by tightening component specifications or automating more of the assembly process.

More-automated manufacturing operations generally maintain very high consistency from board to board. Therefore, either almost all of a given board lot will work or almost all of it will fail. Examining and correcting process parameters may virtually eliminate future failures, a potent argument for feeding quality information back into the process. Under these conditions, quality assurance may not require sophisticated test procedures. For example, a few years ago, a pick-andplace machine in an automated through-hole line was miscalibrated, so that all of the device legs missed the holes. Obviously, the crimper failed to fasten the legs in place, and when the board handler picked the board up, all of the components from that machine slid off. Even a casual human visual inspection revealed that the board was bad, and the pattern of failures identified the correct piece of equipment as culprit.

It is important to recognize that even a process that remains strictly in control still produces some bad boards. However diligently we chase process problems as they occur, perfection remains a myth. Test professionals can rest assured that we will not be eliminating our jobs or our fieldoms within the foreseeable future.

You must determine your own failure levels and whether failures will likely occur in design, purchased parts, or assemblies. Fairly low first-pass yields, for example—perhaps less than 80 percent—often indicate assembly-process problems. Very high board yields suggest few such problems. Those failures that do occur likely relate to board design or to parts interactions. If board yields are very high but the system regularly fails, possible causes include board-to-board interactions, interactions of a board with the backplane, or the backplane itself. Understanding likely failure mechanisms narrows test-strategy choices considerably.

#### 1.4.1 Breaking Down the Walls

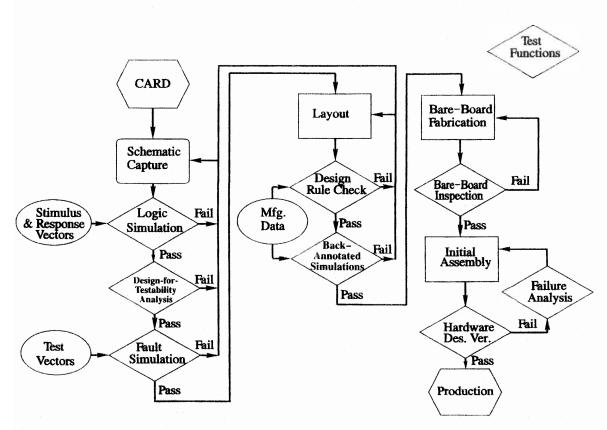

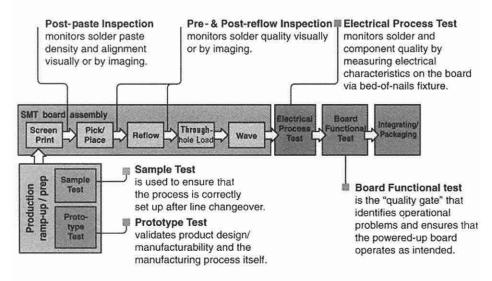

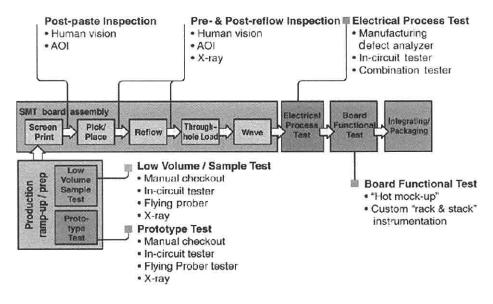

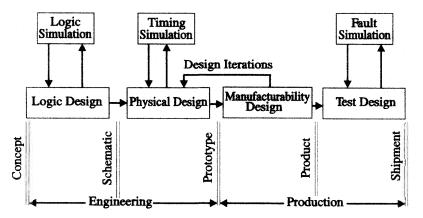

Test activities are no longer confined to the "test department" in a manufacturing organization. Design verification should occur even before prototyping. It represents one of the imperatives of the simulation portion of the design process, when changing and manipulating the logic is still relatively painless. In addition, inspection, once considered a manufacturing rather than a test step, can now reduce burdens on traditional test. In creating a test strategy, you must therefore take into account the nature and extent of inspection activities. In fact, test is an integral part of a product's life from its inception. Consider the sample design-and-test process in Figure 1-2. It begins with computer-aided research and development (CARD). A subset of computer-aided design and computer-aided engineering, CARD determines the product's function and begins to formulate its physical realization.

The output from CARD proceeds to schematic capture, producing logical information for design verification and analysis. Next comes logic simulation, which requires both a schematic (along with supporting data) and stimulus-andresponse vectors. Either human designers or computer-aided engineering (CAE) equipment can generate the vectors. The logic-simulation step must verify that the theoretical circuit will produce the correct output signals for any legitimate input.

The question remains, however, how many stimulus vectors are enough? The only answer is that, unless the input-stimulus set includes every conceivable input combination, it is possible that the verification process will miss a design flaw.

If logic simulation fails, designers must return to schematic capture to ensure correct translation from design concept to schematic representation. If no errors are evident from that step, another pass through CARD may become necessary.

If logic simulation passes, indicating that the theoretical circuit correctly expresses the designers' intentions, the next step is a design-for-testability (DFT) analysis. Notice that this analysis occurs long before a physical product is available for examination. At this point, there is not even a board layout. Design-for-testability attempts to confirm that if a logic fault exists, there is a place in the circuit to detect it.

If DFT analysis fails, engineers must return to schematic capture. Although logic simulation has shown the schematic to perform as designers intended, the circuit's logical structure prevents manufacturing operations from discovering if a particular copy of the circuit is good or bad.

This tight loop of DFT analysis, schematic capture, and logic simulation continues until the DFT analysis passes. The product then proceeds to a fault simulation. The analysis has determined that testing is possible. Fault simulation must determine if it is practical. For example, consider the test sequence necessary to verify on-board memory. The test must proceed from a known state. If there is no reset function, however, initializing the circuit before beginning the test may be difficult or time-consuming. The test may require cycling the memory until it reaches some known state before the test itself can begin. Similarly, if the memory array is very large, the test may take too long to warrant its use in high-volume production.

Similarly, fault simulation must determine the minimum number of functional test vectors required for confidence that the circuit works. Each fault may be testable, but achieving an acceptable fault coverage in a reasonable time during production may not be practical.

Like logic simulation, fault simulation requires a set of vector inputs and their expected responses. At the same time, however, these two techniques are fundamentally different. Logic simulation attempts to verify that the design works,

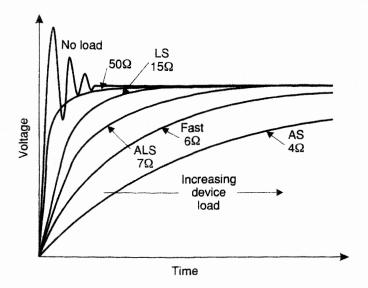

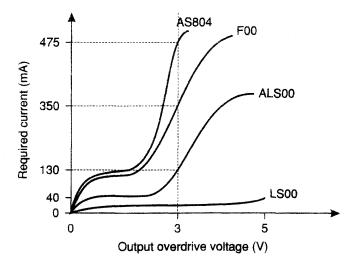

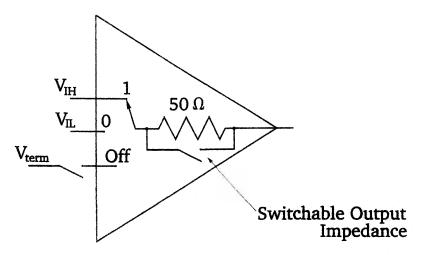

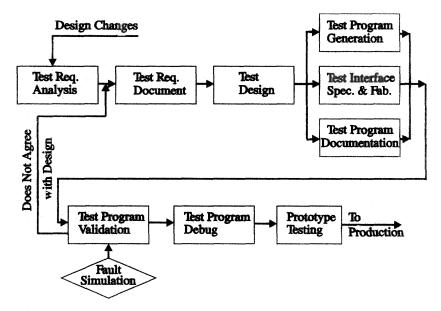

#### Figure 1-2 Sample design and test process.

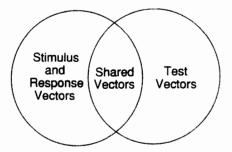

**Figure 1-3** Because the assumptions are different, stimulus-and-response vector sets for logic simulation and test vector sets for fault simulation resemble the overlapping circles of a Venn diagram. Some vectors are unique to logic simulation, others are unique to fault simulation. Certain vectors will be common to both techniques.

assuming that the product is built correctly. It therefore seeks only to ensure that an input stimulus that the board will experience in actual operation will produce the output pattern that the designer has specified.

Fault simulation works the other way around. It assumes that the design is correct and attempts to determine whether the assembly process has built it properly. If the board is built correctly, a particular set of inputs will produce a specific set of outputs. If it contains faults, some input vectors must produce incorrect signatures. Those incorrect signatures should pinpoint the exact cause of the problem.

Because the assumptions are different, input vector sets are different as well. They resemble the overlapping circles of a Venn diagram, as shown in Figure 1-3. Some vectors are unique to logic simulation, others are unique to fault simulation. Certain vectors will be common to both techniques.

When simulating a circuit for design verification, an engineer can apply vectors of unlimited flexibility. That is, issues such as resolution, access, and test times border on irrelevant. The object is to verify that, if the manufacturer produces the board according to specification, that it will work the first time.

When simulating for production test, the selected test equipment must be able to execute whatever vectors the engineer has proposed. Circuit access must be available either directly through a bed-of-nails or from the edge connector or indirectly using a technique such as boundary scan. (See Chapter 5.)

Perhaps the biggest difficulty with fault simulation is determining when it has covered all possible faults. Generally, there are very few ways to build a circuit correctly and a plethora of faulty alternatives. For most complex circuits, the number of input vectors required to cover every conceivable failure mechanism is far greater than a simulator can apply in a reasonable amount of time.

To estimate the fault coverage in a fault simulation, an engineer routinely injects faults into the simulated circuit, then ensures that the simulation process will uncover them. At some point, someone must decide that the fault-coverage percentage is the best it can be and move on. Consider a board on which U14 pin 12 is tied to ground. Injecting that fault into the simulation produces one of three results. If the input vector never causes pin 12 to go high, the output vector will be correct and the simulation does not detect that fault. If the vector tries to drive the pin high, the output will be incorrect. If the faulty output pattern is unique, the simulation has located the specific failure. If, however, the faulty output signature is identical to the output when the board contains a different fault, then that vector cannot be used to identify either fault. Another vector or vectors must be selected, adding to or replacing that vector in the set.

No matter how carefully an engineer performs fault simulation, some faults will always go undetected. The philosopher Voltaire once postulated that God is a comedian playing to an audience that is afraid to laugh. Every now and then, God plays a little joke to remind us that we are not as smart as we think we are. Very high estimated fault coverages often fall into that category.

At the device level, in its day the 80386 microprocessor was one of the most carefully designed components in the industry's history. Intel laid out design-fortestability rules, made sure that many of the most critical functions were verified by internal self-test, and otherwise took elaborate steps to guarantee the product's quality. They estimated a better than 97 percent fault coverage. Yet, despite all of their efforts, some of the earliest devices exhibited a very peculiar bug. If software was running in protected mode and the device resided in a particular temperature range, multiplying two numbers together from a specific numerical range might produce the wrong answer. The only saving grace was that there was no software at that time that required the protected mode. Everything had been designed for the 80286-class environment, which lacked that capability.

The now-classic problem with the original Pentium processors also illustrates this point, while graphically demonstrating how customer perceptions of such problems have changed. After the experience with the 80386, Intel redoubled its efforts in design and test to ensure that subsequent devices (the Pentium contained a then-staggering 3.2 million transistors on a piece of silicon the size of a dime) would work properly. To maximize processor calculation speeds, the Pentium employs a multiplication lookup table, rather than performing each calculation individually. This table, however, contained a small error in one of the entries. After thoroughly researching the problem, Intel contended at first that the error was so tiny that aside from astronomers and others making extremely precise empirical calculations, almost no computer users would ever notice the discrepancy.

Unfortunately for Intel, this adventure occurred after the proliferation of the Internet. Electronic bulletin boards everywhere carried news of the problem. Letters of complaint began to appear from people claiming to have reproduced the bug. Further investigation showed that these people had indeed performed a multiplication that had yielded the small discrepancy. This result was unavoidable. The exact location of the error had been posted on the Internet, and engineers had downloaded the information to check it out for themselves. Since the error resided in a lookup table, *any* calculation that included those specific locations in

the table would exhibit the problem. The resulting public-relations nightmare forced Intel to provide a replacement for any such Pentium at no cost to the computer customer—but an enormous expense for the company. The entire episode vividly illustrated that although electronic systems had become vastly more complex than they were only a few years ago, buyers of those systems have no tolerance at all for known bugs.

(Despite the fact that I understood how small the error really was, I must admit that I replaced the Pentium on my own computer. Like many engineers, I have a philosophical aversion to enduring a known bug when the solution is offered gratis. On the other hand, I was not so naïve as to believe that by doing so I had necessarily eliminated the only possible bug in that device, merely the only one that I knew about.)

At the board level, if devices start out good, the problem seems simpler. Yet, densely populated boards with hundreds of tiny surface-mounted components on both sides can exhibit problems that elude simulation steps to reveal them because they represent that last 2 or 3 percent of uncovered faults. At any stage, a new problem may emerge, which is why the process diagram in Figure 1-2 contains so many feedback loops. In addition, suppose instead of multitudes of individual components, the board contains highly integrated application-specific integrated circuits (ASICs) or similar alternatives. In that case, someone has to construct a test for the ASICs themselves, which in many respects resembles a functional board test, so test development becomes a series of separate but interrelated steps.

Again, if fault simulation fails, the design process loops back to schematic capture. Complex designs often require several iterations before passing all of these early steps. Once past fault simulation, the product moves into layout.

#### 1.4.2 Making the Product

The layout step creates a physical board description, including placement of traces, solder pads, vias (through-holes), and components. A design-rule check verifies that the layout conforms to the company's testability and manufacturability requirements for a reliable, high-quality product. Problems can include logic nodes under ball-grid arrays (BGAs) and other components, prohibiting either bed-of-nails fixturing of the loaded board or guided probing for functional-failure analysis. Perhaps test pads are too small or node spacing is 25 mils (.025") when the design specifies no less than 50, again to facilitate probing. Design rules may demand that all through-hole components reside on one side of the board or that the circuit's logic partitioning permit in-circuit cluster testing.

Whereas DFT analysis depends on the board's logic, a design-rule check examines its physical implementation. (One industry expert once observed that the term "design-rule checking" itself might be the greatest piece of marketing that test engineers in the electronics industry have ever done. Design rules are constraints that facilitate manufacturing and testing, two activities that many design engineers would rather leave to their manufacturing-engineering counterparts. Calling them design rules makes them a bit more palatable.) Failure at this step requires returning to layout, if not all the way to schematic capture.

Once the layout passes the design-rule check, the engineer must back-annotate the circuit simulations to ensure that they accurately reflect any design changes to this point and that the circuit still works. These two steps require data on the manufacturing operation, such as paste-printer and chip-shooter accuracies.

The design then proceeds to initial bare-board fabrication and inspection. Third-party suppliers usually manufacture the boards, but most companies (or their contract manufacturers) perform their own inspection of these early boards to guarantee that they conform to the final design. Even after production rampup, some manufacturers inspect the bare boards themselves, rather than relying on vendors to provide good products.

If the preceding steps have been done correctly, a hardware design-verification step after adding components to these early bare boards should not reveal any surprises. Manufacturers should also perform a functional test on the boards and analyze any failures. Theoretically, the only faults uncovered at this stage result from the assembly process. Once design and manufacturing engineers are confident that the board functions as intended and that the manufacturing process will produce good boards, full production ramp-up can begin.

Notice the number of test activities that occur even before the first productiontype test after bare-board fabrication. Test never really was an isolated activity.

#### 1.4.3 New Challenges

Today's components present greater challenges than ever before. As the gap between a digital device's logic "0" and logic "1" continues to narrow, manufacturers must reduce noise at both the device and the board level. Therefore, new designs tolerate much less noise than older ones did.

For example, with Gunning Transceiver Logic (GTL) and GTL+ (found in many Pentium-class devices), open-drain signals require termination to a  $V_{TT}$  supply that provides the high signal level. Receivers use a threshold voltage ( $V_{REF}$ ) to distinguish between a "1" and a "0". Unlike prior-generation PC systems, these designs include a tolerance requirement for  $V_{TT}$  of  $1.5 V \pm 3\%$  while the system bus is idle. A reliable system requires proper design techniques and a consistent, reliable termination. In this case, termination resistors must be  $56\Omega \pm 5\%$ .

Ever-lower noise margins also increase the circuit's vulnerability to "ground bounce." As speeds increase, transient-switching currents increase as well, creating a brief ground-level bounce as the current flows through the inductance of the ground pins. Through modeling, designers can predict this phenomenon. Nevertheless, you should permit no open ground pins during manufacturing.

Another issue complicating test-strategy decisions relates to the much stricter standards on EMI that international regulators have imposed on electronics manufacturers. In the U.S., the Federal Communications Commission demands no EMI between consumer products. Companies selling to customers in Europe must comply with even stricter requirements, as the European Community tries to ensure that products designated for sale in one country do not interfere with broadcast and cellular-phone frequencies in another. Products must undergo strict compliance testing and receive compliance engineering (CE) certification before they can be sold in the target country.

Other trends that will complicate test-strategy decisions include a tendency to pack ever more components onto a particular sized board, or (conversely) to shrink board size without comparably reducing component count. In either case, the resulting layouts offer much less space for test points and nodes for bed-of-nails probing than before. Where companies are integrating more functions onto ASICs and other complex devices, real estate is not an issue, and the *lower* parts count reduces the complexity of board-level tests. At the same time, however, this development pushes more test responsibility back to the device level, burdening device designers and manufacturers with the need to ensure that only good devices reach customers' hands. As in the past, manufacturers should not assemble boards from other than known-good components. That rule brings its own challenges.

In addition, the classic design-for-testability guideline that attempts to mandate components on only one board side is often impractical. Complex handheld products such as cellular phones must not exceed a certain size. Designers must therefore often get somewhat creative to cram sufficient functionality into the small permissible space.

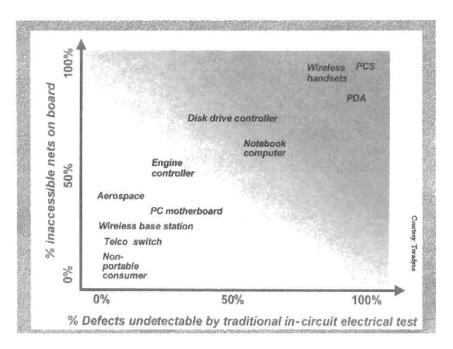

Not all products suffer from ever-shrinking footprint and declining nodal access, however. As Figure 1-4 shows, telephone company switches, aerospace electronics, and other products continue to enjoy through-hole access. At the other end of the spectrum, wireless cell-phone handsets, many notebook PCs, and personal digital assistants (PDAs—so-called "hand-held PCs") increasingly defy conventional access, and consequently confound traditional test methods.

#### 1.5 Concurrent Engineering Is Not Going Away

An old industry adage states that there is never enough time to do a job right but always enough time to do it again. In its purest form, concurrent engineering is an attempt to put paid to that attitude by setting forth a set of principles that maximize the likelihood that a job will be done right the first time. Sammy Shina, in his *Concurrent Engineering and Design for Manufacture of Electronic Components* (1991), defines the term as: "Integrating a company's knowledge, resources, and experience into development, manufacturing, marketing, and sales activities as early in the cycle as possible."

Companies that have adopted this philosophy have reaped substantial benefits. In the early 1990s, for example, AT&T managed to reduce its development time for new telephone products from two years to one. Hewlett-Packard printers that once took  $4\frac{1}{2}$  years from drawing board to production now get there in less than half that time.

In many cases, the time from customer order to product shipment has fallen even more dramatically. Concurrent engineering helped Motorola pagers to get out

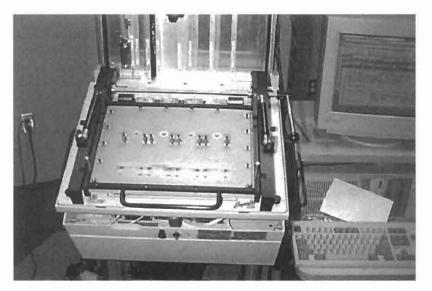

**Figure 1-4** Not all products experience "incredible shrinking electronics." (Courtesy Teradyne.)

the door in 2 hours instead of 3 weeks, and what is now Agilent Technologies reduced the time to ship test equipment from 4 weeks to 5 days. Accompanying these improvements were drastic reductions in inventory and associated holding costs, which translate directly to the company's bottom line.

Despite the fact that the term "concurrent engineering" has somewhat fallen out of favor, the imperative to embrace its concepts has not changed. Successfully introducing these concepts (whatever you choose to call them) into a manufacturing operation requires that designers learn to be proactive rather than simply reactive to the impact of their decisions on downstream activities. As wide a range as possible of design and manufacturing technologies deserves consideration if the product is to achieve its performance and economic goals. For example, incorporating boundary-scan circuitry into ASICs tends to minimize test-development times for devices, boards, and systems. Early adoption of these techniques minimizes their inconvenience without sacrificing their benefits.

Designers must solicit input from people in all departments involved in a product's life cycle. Marketers have to sell concept changes to customers, while warranty and field-service people contend with quality problems that escape the factory. Early involvement from these people drastically reduces the number of costly design changes late in the development process. Products destined for automobiles or other hostile environments, for example, must withstand very unfavorable conditions without breaking down. Service people's experiences can help designers make new products more reliable.

For companies whose manufacturing operations are half a world away from design teams, concurrent engineering makes the transfer of responsibility much smoother. Disk-drive manufacturers often develop their boxes and perform early production in their own country, then send the entire package to Asia (for example) for high-volume production. The single biggest impediment to this arrangement is a lack of communication across many time zones and thousands of miles. If manufacturing and test engineers participate in the design, the Asian side of the operation can become relatively self-sufficient.

Picture a Texas company with a manufacturing facility in south Asia running 30,000 boards a day. The Asian arm must be capable of dealing with most problems, from the trivial to the fairly serious, independently. Phone calls, faxes, and e-mails could take days to achieve results, during which time the production line is idle or showing unacceptable quality levels. If a stateside engineer has to hop an airplane to Asia to address the problem, delays get much worse and costs skyrocket. Unfortunately, a problem with the design itself may necessitate such drastic steps.

Perhaps the least disruptive time to introduce concurrent engineering into an existing facility is during new-product development. Extending the practice to other product lines can occur gradually later. The first step must document the capabilities and constraints of the existing manufacturing process. Eliminating redundant or superfluous operations and optimizing what remains represent a good beginning. Unfortunately, this step can be very difficult. Some organizations do not fully understand their manufacturing processes because the processes evolved over long periods and follow no master plan.

As stated earlier, one way to reduce the impact of increasing product complexity on test is to take advantage at each step of information that previous steps have generated and to avoid looking for faults that previous steps have already found. The principal drawback to this approach, however, is that test-programgeneration tools often cannot automatically know what faults or fault mechanisms to ignore. Therefore, engineers must allow the tools to generate complete test programs and eliminate redundant sections later or generate the programs manually neither alternative being particularly attractive. Fortunately, new tools are emerging that keep track of which test-and-inspection steps identify which fault types. These tools, properly implemented, can drastically reduce test-generation efforts as well as test times without sacrificing product quality.

Designers must be sure that CAD/CAE information transfers easily into manufacturing and test terms, reducing data-translation times and minimizing transcription errors. In addition, design requirements must not include specifications that manufacturing or test activities cannot achieve.

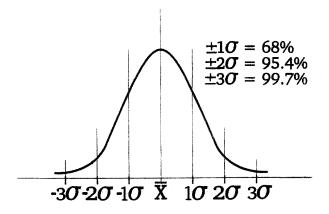

Part of the concurrent-engineering effort must include statistical process control (SPC), an online technique for determining whether the process is likely to create high-quality products and whether quality problems result from consistent process failures or random variations. Statistical process control is discussed further in Section 1.9.

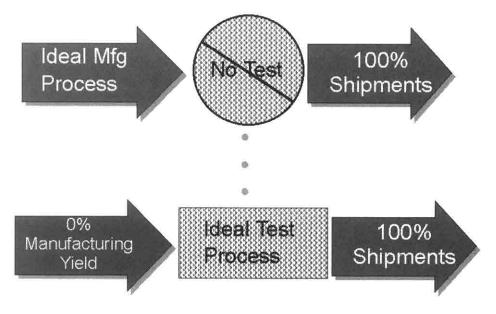

**Figure 1-5** 100% test effectiveness is possible even with no test or 0% manufacturing yield.

The effectiveness of any test strategy depends on the corresponding effectiveness of the manufacturing process. Consider, for example, a perfect manufacturing process that produces only good products. In that case, any test strategy—even no test at all—will produce 100 percent good products, as in Figure 1-5. Assuming that the process remains in control, any expenditure on test would prove—at best—superfluous.

In contrast, a perfect *test strategy* would ship 100 percent good products, even if every board and system off the manufacturing line contained defects. Of course, the economics of finding and repairing those defects might present a considerable challenge. Nevertheless, from the customer's standpoint, the result would not change. The *test effectiveness* in both cases (a combination of manufacturing and test processes) is 100 percent, although the strategies will likely be very different.

Real manufacturing operations lie somewhere in between. They never achieve the perfection of the first case, so some test strategy will be necessary. Nor do they experience the horrors of zero yield, so a less-than-perfect test strategy will probably suffice. The goal is always to strive for 100 percent test effectiveness, regardless of results from the individual segments.

One drawback to eliminating redundancy between test steps is concern that *over*elimination of test overlap will result in missed faults and, therefore, reduced product quality. To some extent, this concern is justified—as always, depending on the nature of the product under test. As with most engineering decisions, the line between thorough fault coverage and test overlap represents a tradeoff.

Each test engineer must consider that potential danger in designing the overall strategy, striking the most effective compromise for that particular combination of product, customer, and application, within the scope of the available test budget and test tools.

The complexity of today's electronic products makes facing these issues more difficult than ever before. Unfortunately, creating a qualitative list of the requirements is far easier than quantifying them.

#### 1.6 The Newspaper Model

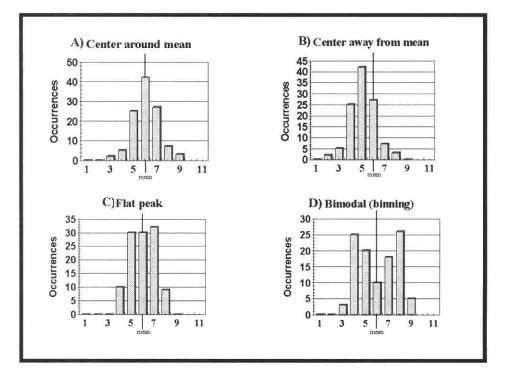

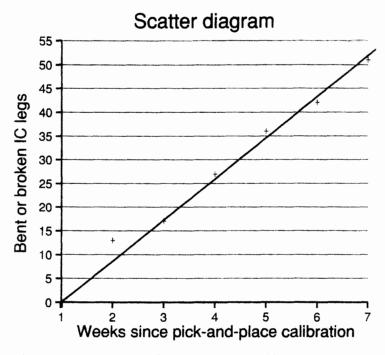

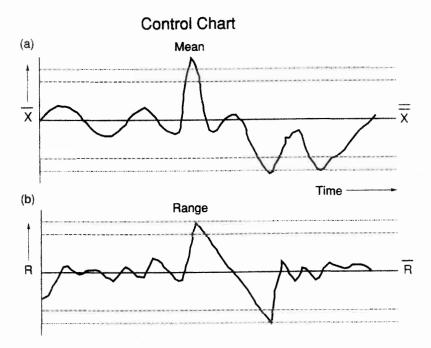

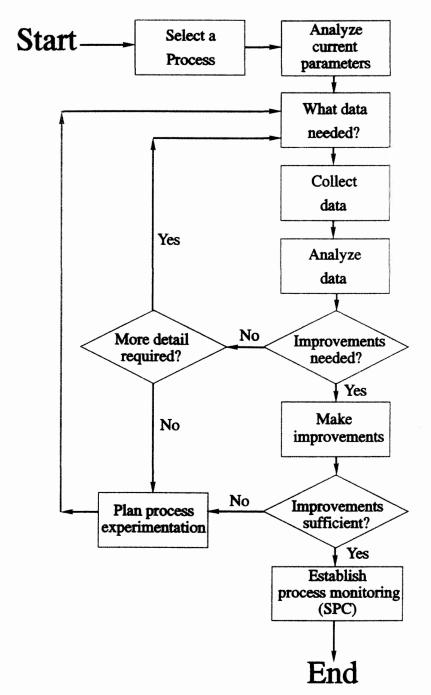

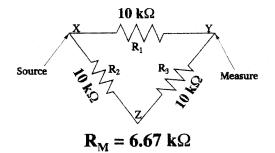

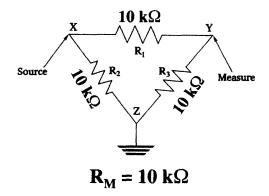

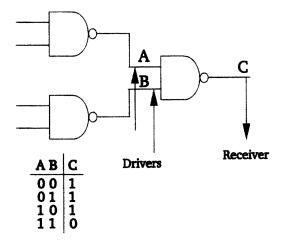

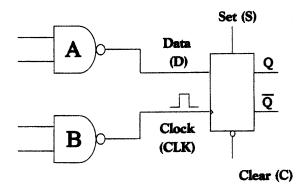

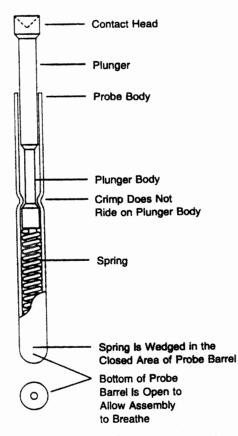

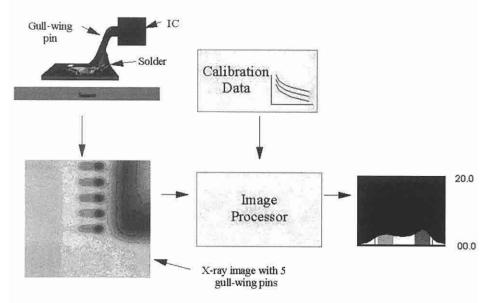

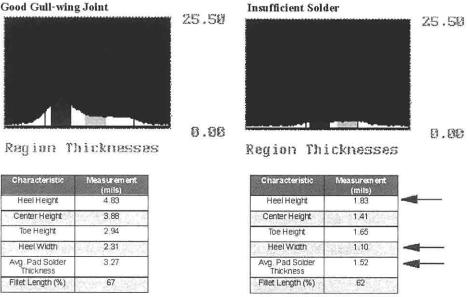

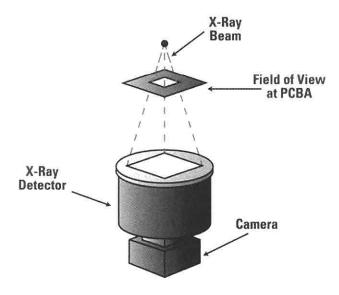

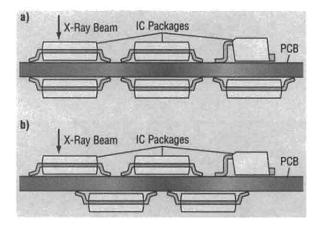

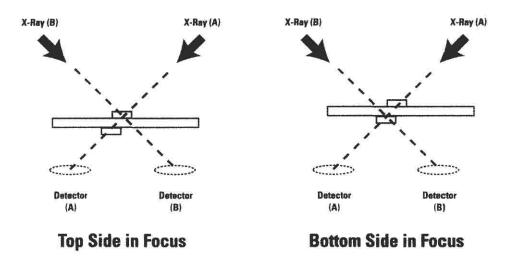

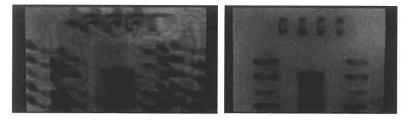

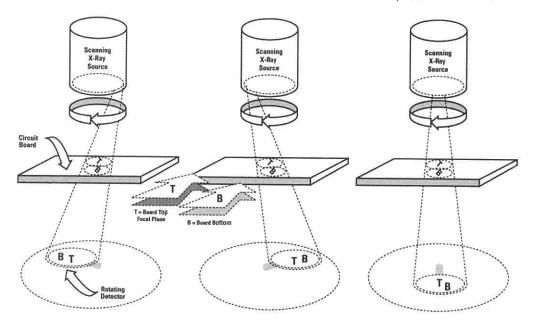

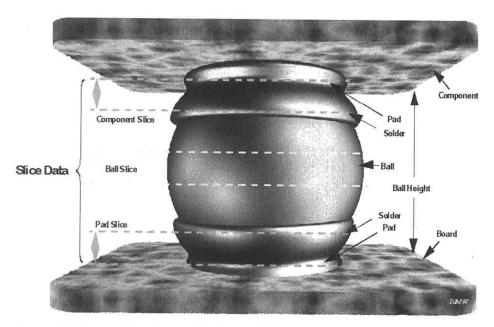

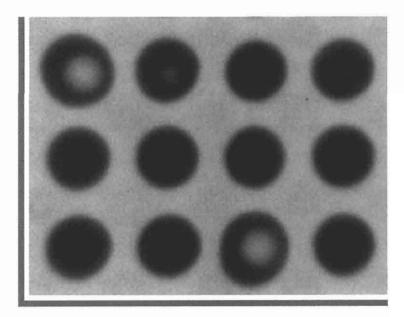

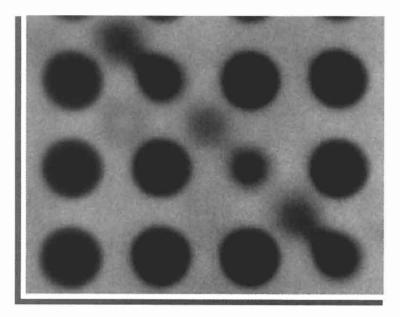

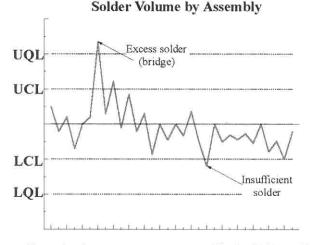

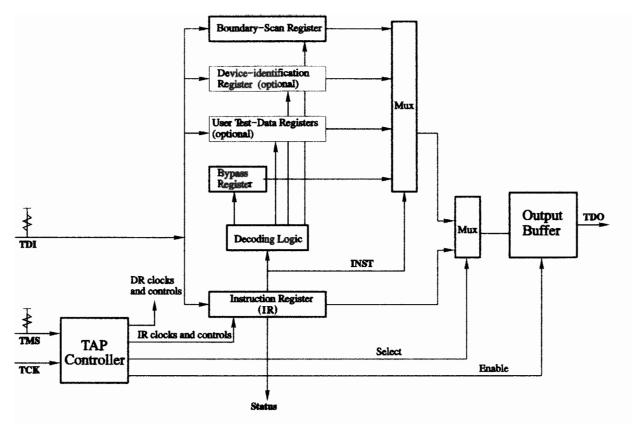

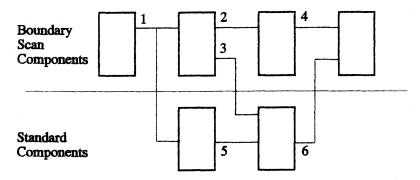

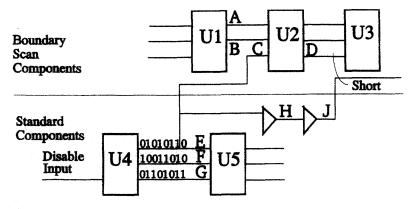

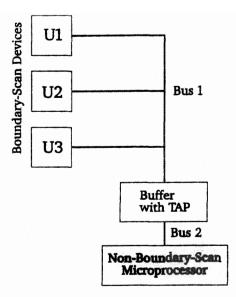

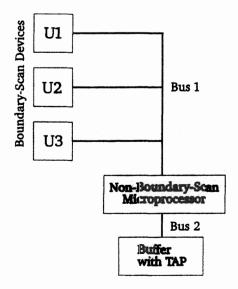

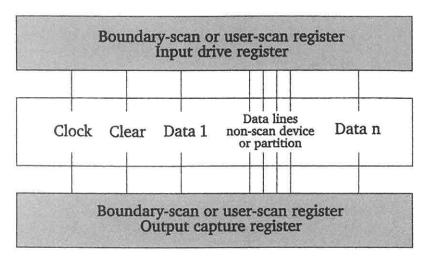

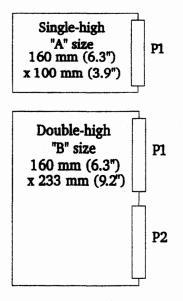

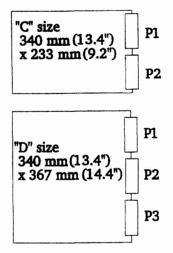

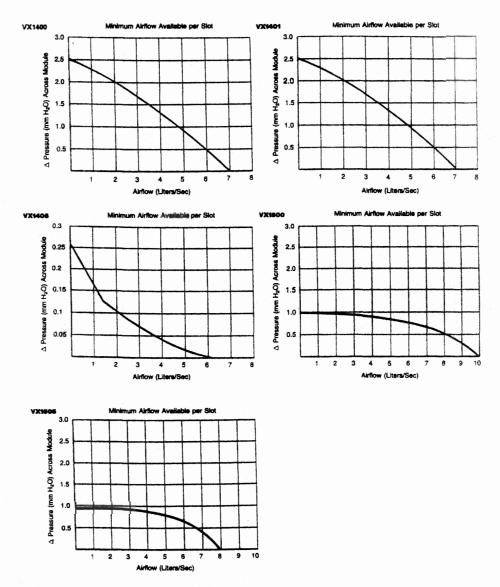

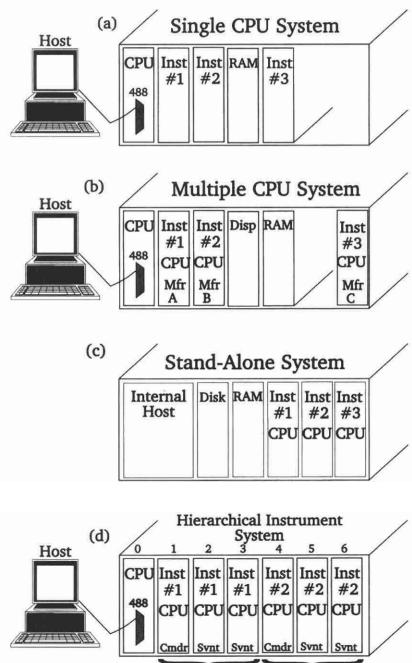

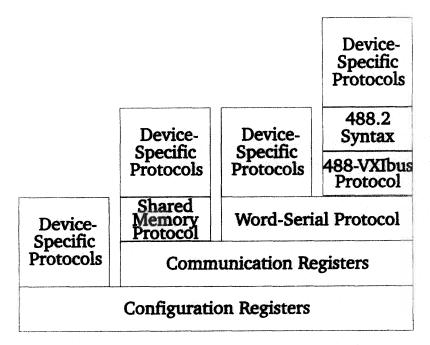

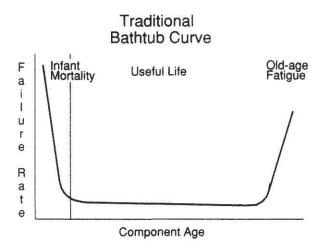

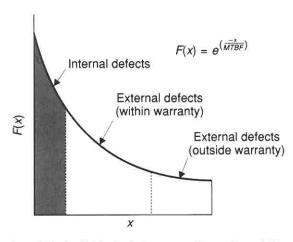

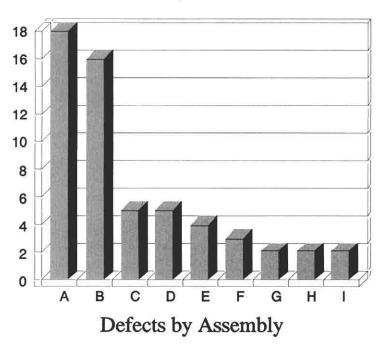

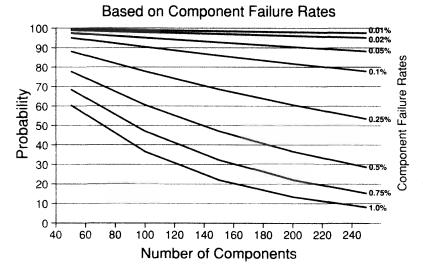

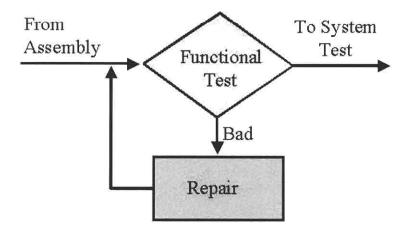

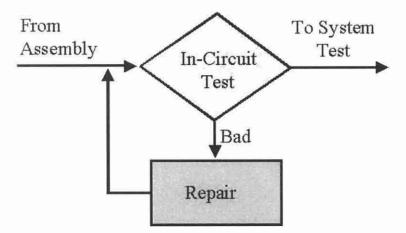

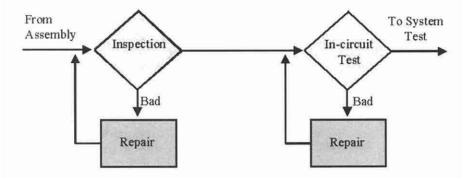

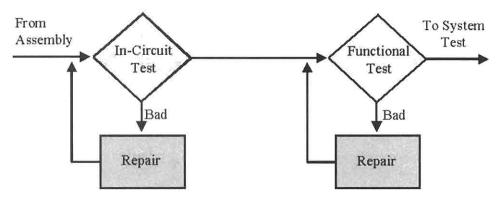

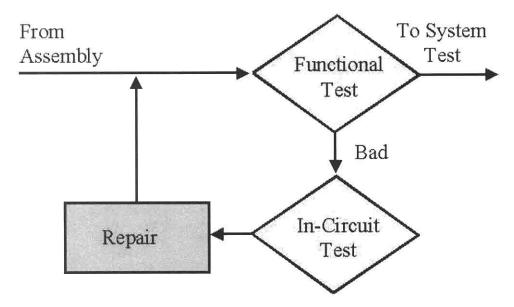

A board-test strategy consists of three basic elements: test techniques, diagnostic techniques to determine failure mechanisms or for statistical process control, and product flow from one process step to the next. Constructing a successful strategy requires asking the same questions one asks when writing a good newspaper story—the so-called "five Ws and an H": Who? What? When? Where? Why? How?—although not necessarily in that order.