# RF CMOS Power Amplifiers Theory, Design and Implementation

Mona M. Hella Mohammed Ismail RF CMOS Power Amplifiers: Theory, Design and Implementation

# THE KLUWER INTERNATIONAL SERIES IN ENGINEERING AND COMPUTER SCIENCE

### ANALOG CIRCUITS AND SIGNAL PROCESSING Consulting Editor: Mohammed Ismail. Ohio State University

**Related Titles:** POWER TRADE-OFFS AND LOW POWER IN ANALOG CMOS ICS M. Sanduleanu, van Tuijl ISBN: 0-7923-7643-9 **RF CMOS POWER AMPLIFIERS: THEORY, DESIGN AND IMPLEMENTATION** M.Hella, M.Ismail ISBN: 0-7923-7628-5 WIRELESS BUILDING BLOCKS J.Janssens, M. Stevaert ISBN: 0-7923-7637-4 CODING APPROACHES TO FAULT TOLERANCE IN COMBINATION AND DYNAMIC SYSTEMS C. Hadjicostis ISBN: 0-7923-7624-2 DATA CONVERTERS FOR WIRELESS STANDARDS C. Shi, M. Ismail ISBN: 0-7923-7623-4 STREAM PROCESSOR ARCHITECTURE S. Rixner ISBN: 0-7923-7545-9 LOGIC SYNTHESIS AND VERIFICATION S. Hassoun, T. Sasao ISBN: 0-7923-7606-4 VERILOG-2001-A GUIDE TO THE NEW FEATURES OF THE VERILOG HARDWARE DESCRIPTION LANGUAGE S. Sutherland ISBN: 0-7923-7568-8 IMAGE COMPRESSION FUNDAMENTALS, STANDARDS AND PRACTICE D. Taubman, M. Marcellin ISBN: 0-7923-7519-X ERROR CODING FOR ENGINEERS A.Houghton ISBN: 0-7923-7522-X MODELING AND SIMULATION ENVIRONMENT FOR SATELLITE AND TERRESTRIAL COMMUNICATION NETWORKS A.Ince ISBN: 0-7923-7547-5 MULT-FRAME MOTION-COMPENSATED PREDICTION FOR VIDEO TRANSMISSION T. Wiegand, B. Girod ISBN: 0-7923-7497- 5 SUPER - RESOLUTION IMAGING S. Chaudhuri ISBN: 0-7923-7471-1 AUTOMATIC CALIBRATION OF MODULATED FREQUENCY SYNTHESIZERS D. McMahill ISBN: 0-7923-7589-0 MODEL ENGINEERING IN MIXED-SIGNAL CIRCUIT DESIGN S. Huss ISBN: 0-7923-7598-X CONTINUOUS-TIME SIGMA-DELTA MODULATION FOR A/D CONVERSION IN RADIO RECEIVERS L. Breems, J.H. Huijsing ISBN: 0-7923-7492-4

# List of Figures

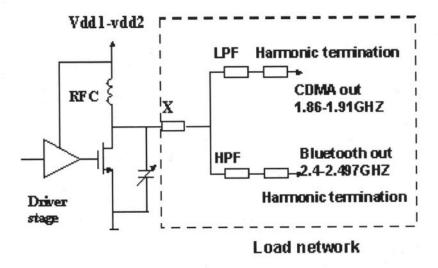

| 3.21 | A double section matching network to transform 50<br>Ohm load to two different optimum loads correspond-<br>ing to two different frequency bands              | 51 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

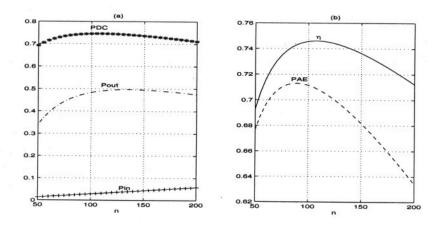

| 3.22 | DC power (PDC), input power (Pin), and output power<br>(Pout) (b) Efficiency and Power added efficiency (PAE)<br>versus number of gate fingers (CDMA 1.9GHz)  | 52 |

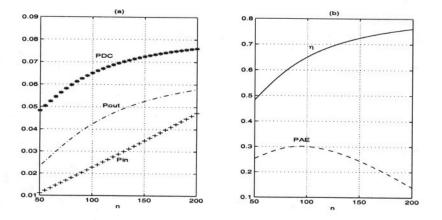

| 3.23 | (a) DC power (PDC), input power (Pin), and output<br>power (Pout) (b) efficiency and power added efficiency<br>(PAE) versus number of gate fingers (2.442GHz) | 52 |

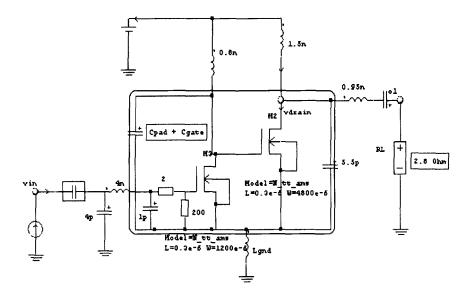

| 3.24 | Schematic of class E PA operating at 1.9GHz.                                                                                                                  | 53 |

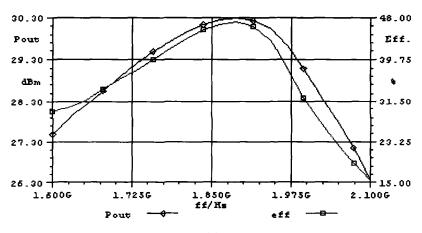

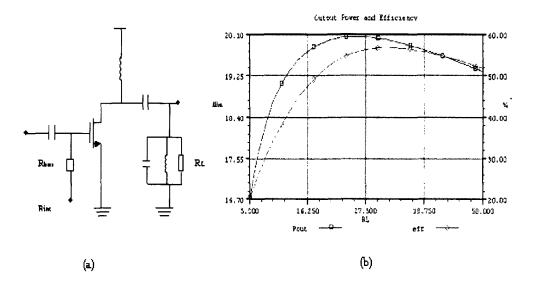

| 3.25 | <ul><li>(a)Variation of output power and efficiency at 1.9GHz,</li><li>(b) Input matching.</li></ul>                                                          | 54 |

| 4.1  | Simplified schematic of the power amplifier.                                                                                                                  | 57 |

| 4.2  | Determination of the optimum load.                                                                                                                            | 58 |

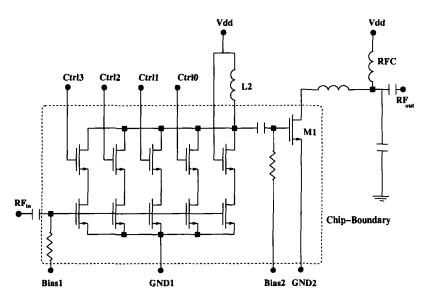

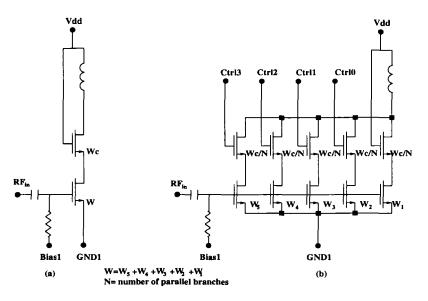

| 4.3  | (a) A Fixed gain band-pass stage, (b) Parallel band-pass stages to implement power control.                                                                   | 59 |

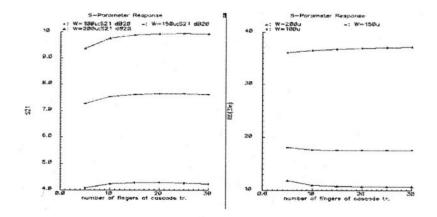

| 4.4  | The gain (S21) and the real part of the input impedance vs the number of fingers of the input transistor.                                                     | 60 |

| 4.5  | Effect of variation of the number of fingers on the out-<br>put power and efficiency                                                                          | 61 |

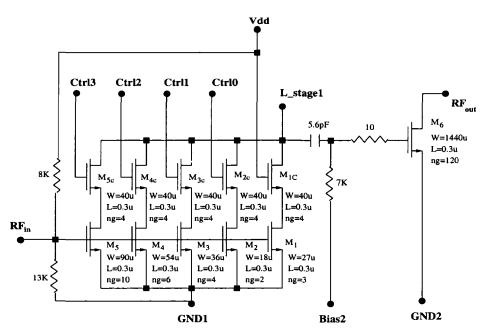

| 4.6  | The core of the controllable gain power amplifier.                                                                                                            | 61 |

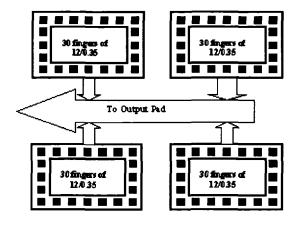

| 4.7  | Layout of the transistor in the output stage.                                                                                                                 | 62 |

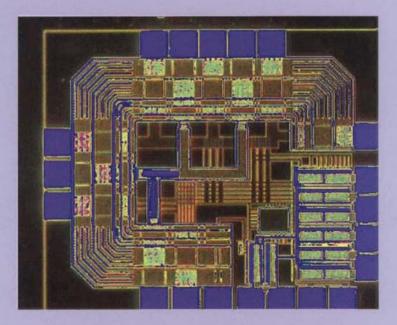

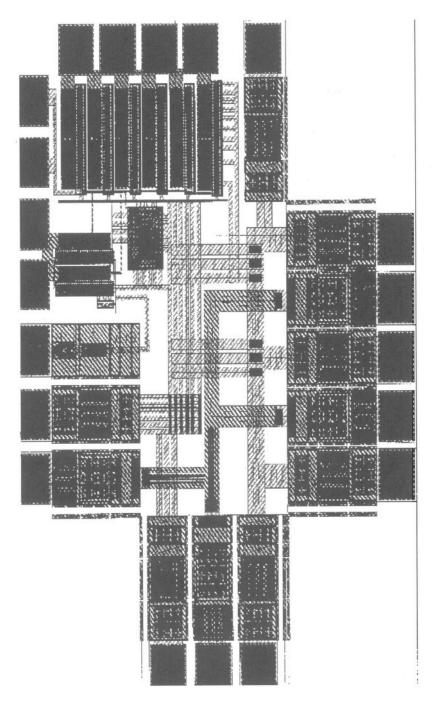

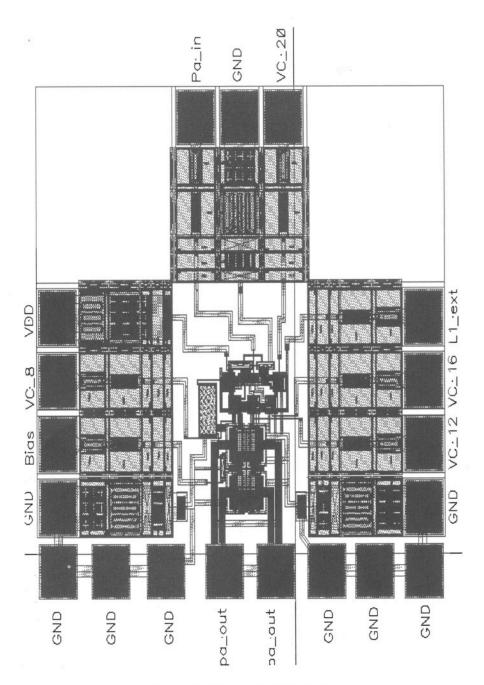

| 4.8  | The complete chip layout.                                                                                                                                     | 63 |

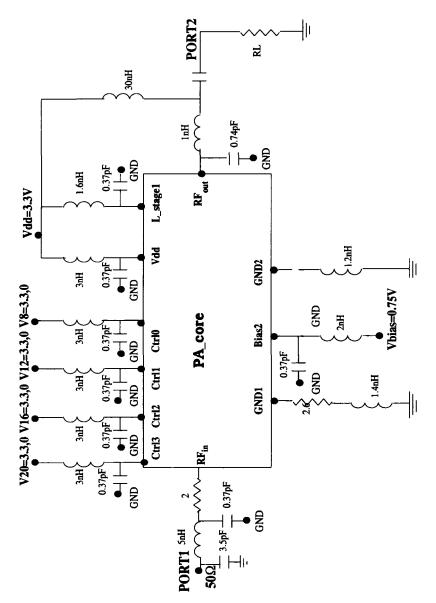

| 4.9  | The schematic of the amplifier together with pads, bond-<br>wire inductances, and the external matching elements.                                             | 64 |

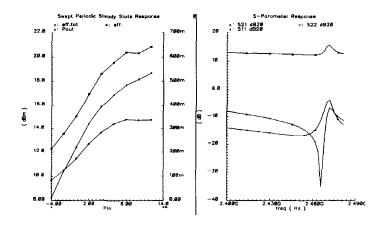

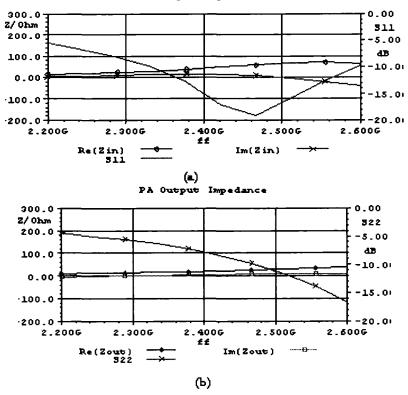

| 4.10 | Simulation results (a) The output power and efficiency, (b) Input and output S-parameters.                                                                    | 65 |

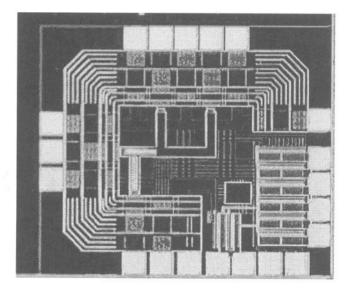

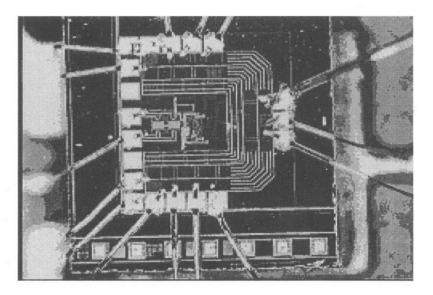

| 4.11 | Chip micrograph.                                                                                                                                              | 66 |

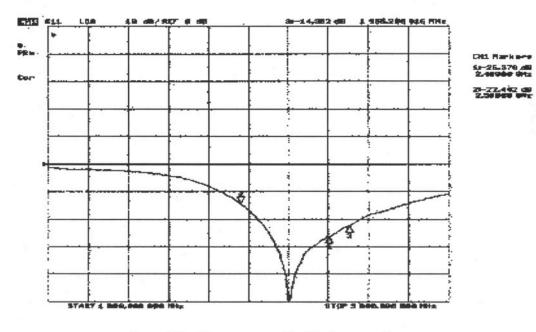

| 4.12 | Measurement results of the input matching.                                                                                                                    | 66 |

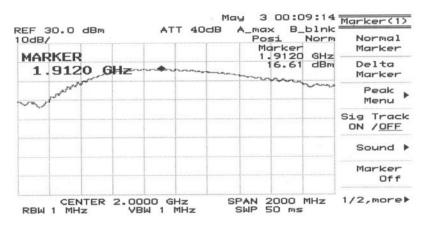

| 4.13 | Measured output power versus frequency.                                                                                                                       | 67 |

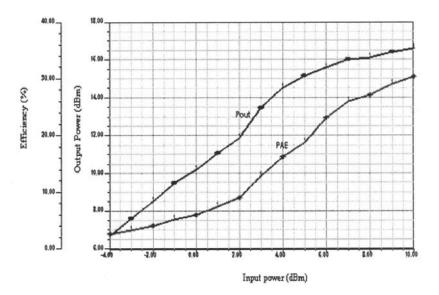

| 4.14 | Measured output power and PAE versus input power.                                                                                                             | 68 |

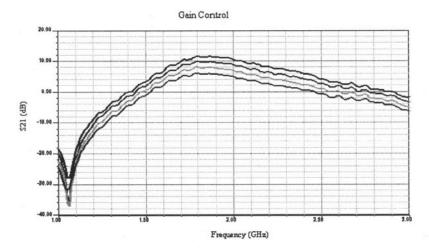

| 4.15 | Measured data showing the variation of the gain with control voltage settings.                                                                                | 68 |

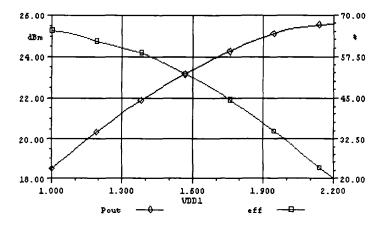

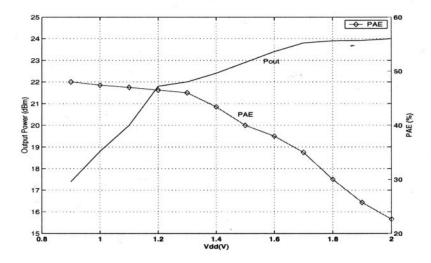

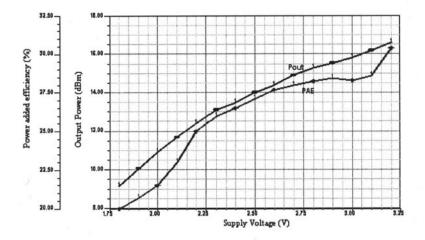

| 4.16 | Measured output power and efficiency vs. supply volt-<br>age at 1.91GHz.                                                                                      | 69 |

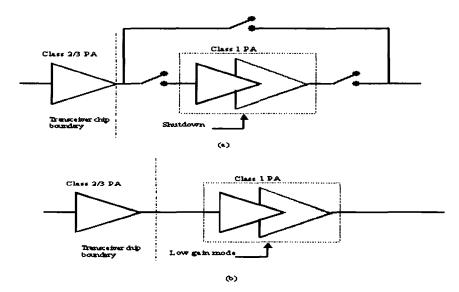

| 5.1  | Possible power amplifier arrangements to support all Bluetooth classes of transmission                                                                        | 72 |

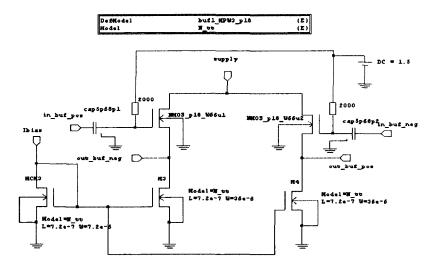

| 5.2  | The schematic of the buffer stage.                                                                                                                            | 73 |

|      | -                                                                                                                                                             |    |

eBook ISBN: 0-306-47320-8 Print ISBN: 0-792-37628-5

©2002 Kluwer Academic Publishers New York, Boston, Dordrecht, London, Moscow

All rights reserved

No part of this eBook may be reproduced or transmitted in any form or by any means, electronic, mechanical, recording, or otherwise, without written consent from the Publisher

Created in the United States of America

Visit Kluwer Online at: and Kluwer's eBookstore at: http://www.kluweronline.com http://www.ebooks.kluweronline.com

# Contents

| Lis | t of F | igures                                              | ix   |

|-----|--------|-----------------------------------------------------|------|

| Lis | t of T | ables                                               | xiii |

| Pre | face   |                                                     | XV   |

| 1.  | INTE   | RODUCTION                                           | 1    |

|     | 1      | RF CMOS Transceivers                                | 1    |

|     | 2      | CMOS Short Range Wireless Transceivers              | 2    |

|     | 3      | Wireless Transmission Protocols                     | 4    |

|     | 4      | CMOS PAs: Related Design Issues                     | 6    |

|     | 5      | CMOS PAs: Recent Progress                           | 7    |

|     | 6      | Motivation                                          | 10   |

|     | 7      | Outline                                             | 11   |

| 2.  | POW    | 'ER AMPLIFIER; CONCEPTS AND CHALLENGES              | 13   |

|     | 1      | Introduction                                        | 13   |

|     | 2      | Conjugate Match and Load line Match                 | 14   |

|     | 3      | Effect of the Transistor Knee Voltage               | 16   |

|     | 4      | Classification of Power Amplifiers                  | 17   |

|     |        | 4.1 Class A, B, AB, and C PAs                       | 17   |

|     |        | 4.2 Class E                                         | 19   |

|     |        | 4.3 Class F                                         | 21   |

|     | 5      | Power Amplifier Linearization                       | 22   |

|     |        | 5.1 Feed Forward                                    | 23   |

|     |        | 5.2 Doherty Amplifier                               | 24   |

|     |        | 5.3 Envelope Elimination and restoration            | 25   |

|     |        | 5.4 Linear Amplification Using Nonlinear Components | 26   |

|     | 6      | Spectral Regrowth                                   | 28   |

|    | 7  | Power Amplifier Stability Issues                  | 28 |

|----|----|---------------------------------------------------|----|

|    | 8  | Power Amplifier Controllability                   | 29 |

|    | 9  | Summary                                           | 30 |

| 3. | AS | 000MHZ CLASS E CMOS PA                            | 31 |

|    | 1  | Introduction                                      | 31 |

|    | 2  | Class E PA Circuit Design                         | 32 |

|    |    | 2.1 Driver Stage Design                           | 34 |

|    |    | 2.2 Simulated Performance                         | 36 |

|    | 3  | Effect of Finite Ground inductance                | 40 |

|    | 4  | Layout Considerations                             | 41 |

|    | 5  | Testing Procedures and Results                    | 42 |

|    | 6  | Towards a Multi-Standard Class E Power Amplifiers | 44 |

|    | 7  | Summary                                           | 46 |

| 4. | AC | CMOS PA FOR BLUETOOTH                             | 55 |

|    | 1  | Introduction                                      | 55 |

|    | 2  | CMOS Power Amplifier Design                       | 56 |

|    |    | 2.1 Design of the Output Stage                    | 57 |

|    |    | 2.2 Driver Stage                                  | 58 |

|    |    | 2.3 Power Control Implementation                  | 59 |

|    | 3  | Implementation and Simulation Results             | 60 |

|    | 4  | Experimental Results                              | 65 |

|    | 5  | Summary                                           | 68 |

| 5. | AC | COMPLETE BLUETOOTH PA SOLUTION                    | 71 |

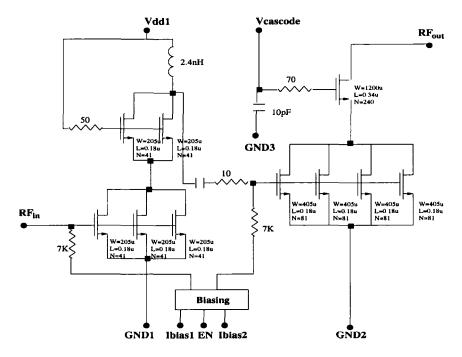

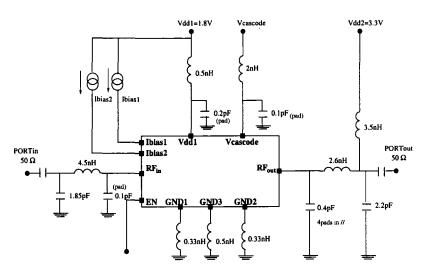

|    | 1  | A CMOS PA for Class 2/3 Bluetooth                 | 72 |

|    | 2  | A Class 1 Bluetooth PA in 0.18µmCMOS              | 75 |

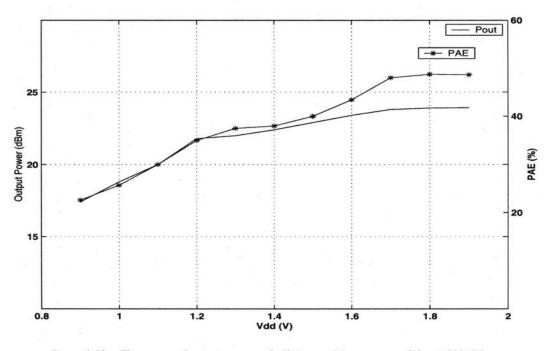

|    | 3  | Simulations Results                               | 78 |

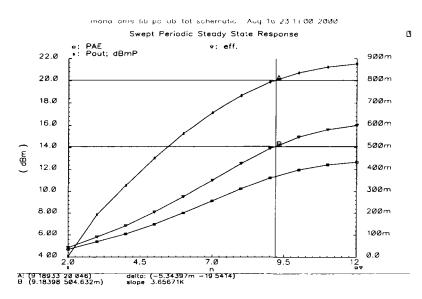

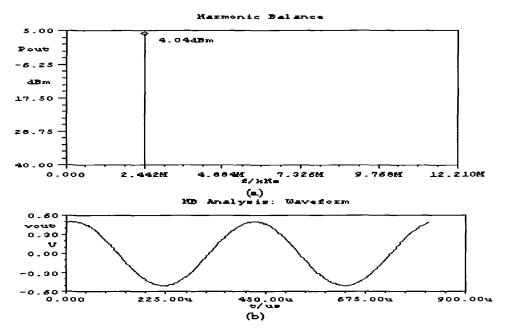

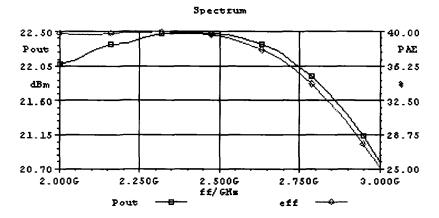

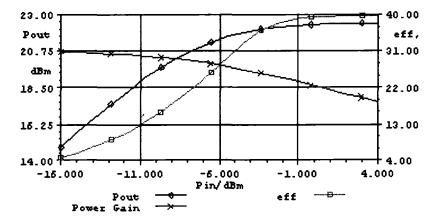

|    |    | 3.1 Large Signal Simulations                      | 79 |

|    |    | 3.2 Power Control                                 | 82 |

|    |    | 3.3 Gain and Matching                             | 83 |

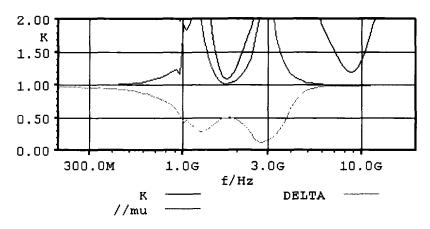

|    |    | 3.4 Stability                                     | 83 |

|    | 4  | Conclusion                                        | 83 |

|    | 5  | Summary                                           | 84 |

| 6. | CO | NCLUSION                                          | 87 |

#### Contents

### Index

vii

This page intentionally left blank

# List of Figures

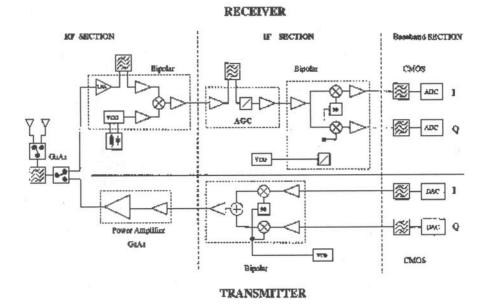

| 1.1  | Example of a super-heterodyne transceiver implemented using multiple technologies.                                                                                                                                                               | 3  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

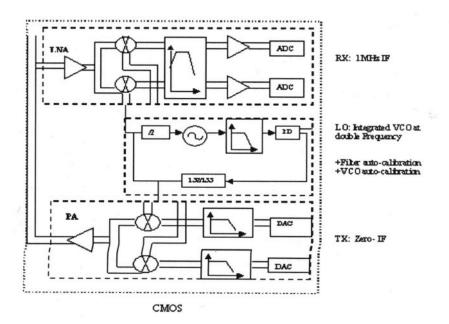

| 1.2  | A fully integrated single chip for Bluetooth                                                                                                                                                                                                     | 4  |

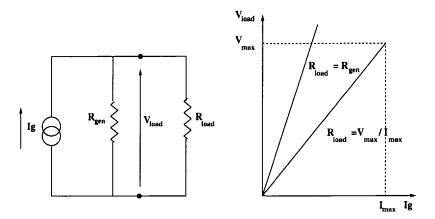

| 2.1  | Conjugate match and load-line match.                                                                                                                                                                                                             | 15 |

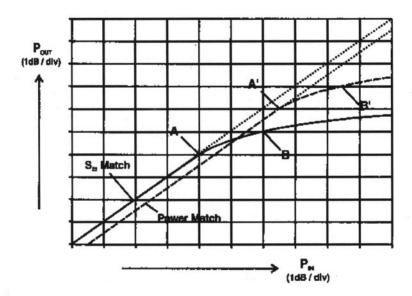

| 2.2  | Compression characteristics for conjugate match (S22)<br>(solid curve) and power match (dotted curve). 1 dB<br>gain compression points (B, B') and maximum power<br>points (A, A') show similar improvements under power-<br>matched conditions. | 15 |

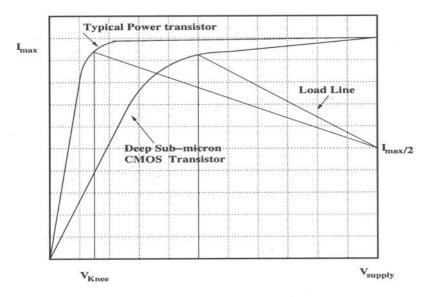

| 2.3  | Effect of the knee voltage on the determination of the optimum load.                                                                                                                                                                             | 17 |

| 2.4  | Traditional illustration of the schematic and current wave-<br>forms of classes A, B, AB, and C.                                                                                                                                                 | 18 |

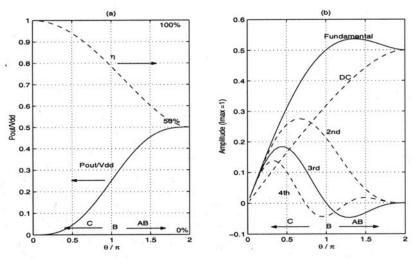

| 2.5  | (a) RF power and efficiency as a function of the con-<br>duction angle, (b) Fourier analysis of the drain current.                                                                                                                               | 19 |

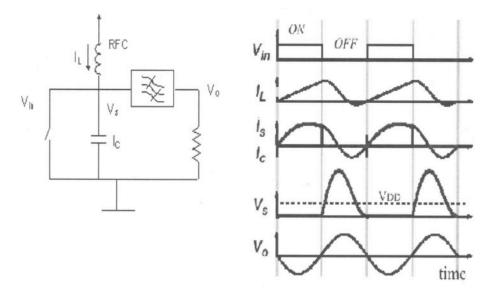

| 2.6  | A simplified class E power amplifier, and its steady state operation.                                                                                                                                                                            | 20 |

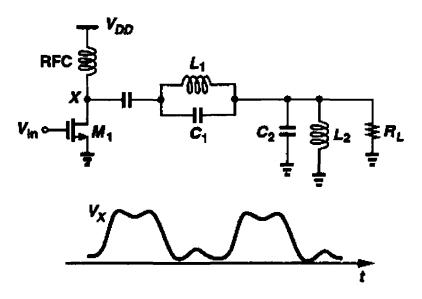

| 2.7  | Schematic, and output waveform of a typical class F stage.                                                                                                                                                                                       | 21 |

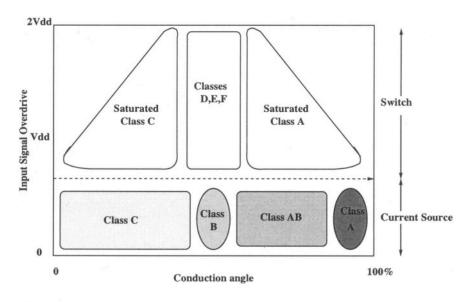

| 2.8  | Classical definition of power amplifier classes.                                                                                                                                                                                                 | 22 |

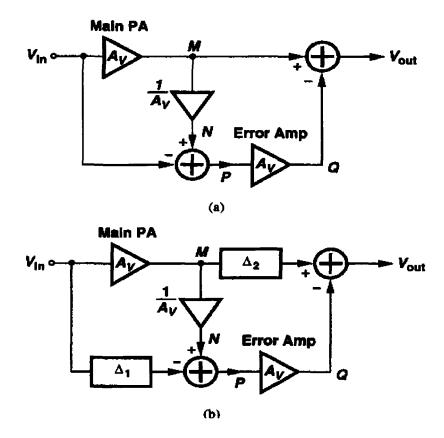

| 2.9  | (a) Simple Feedforward topology, (b) Addition of delay elements.                                                                                                                                                                                 | 23 |

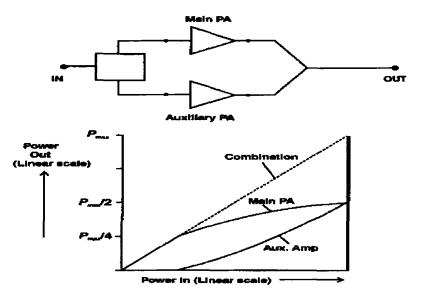

| 2.10 | Basic Doherty amplifier configuration                                                                                                                                                                                                            | 25 |

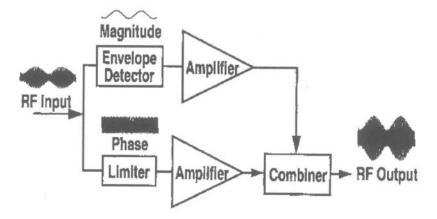

| 2.11 | Conceptual diagram of Envelope Elimination and Restora-                                                                                                                                                                                          |    |

|      | tion technique                                                                                                                                                                                                                                   | 26 |

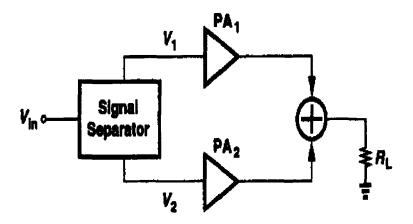

| 2.12 | Linear Amplification using Nonlinear Stages                                                                                                                                                                                                      | 27 |

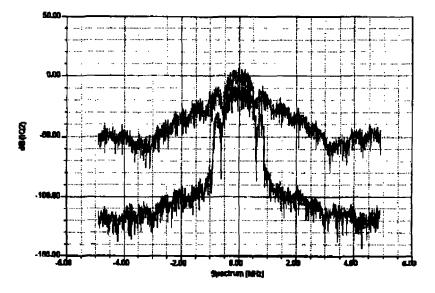

| 2.13 | Spectral regrowth due to amplifier nonlinearity                                                                                                                                                                                                  | 28 |

|      |                                                                                                                                                                                                                                                  |    |

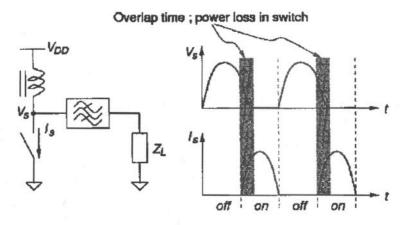

| 3.1  | Waveforms of a switching-mode power amplifier with hard switching.                                                                                                                                                      | 32 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

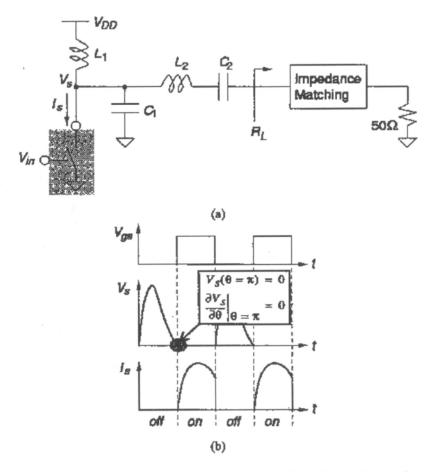

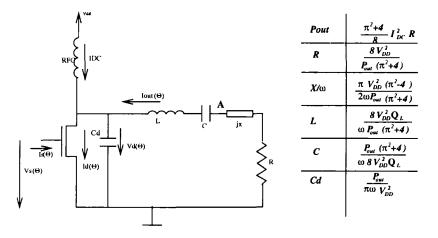

| 3.2  | (a) Typical schematic of a class E power amplifier, (b)<br>Its voltage and current waveforms showing the soft switch-<br>ing characteristics.                                                                           | 33 |

| 3.3  | Single-ended class E resonant power amplifier.                                                                                                                                                                          | 34 |

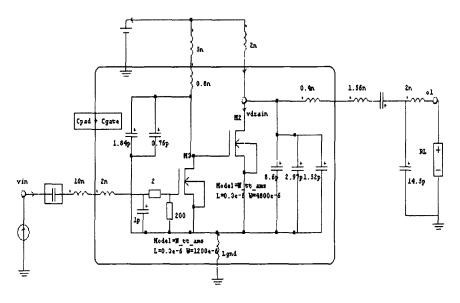

| 3.4  | Schematic of the 900MHz Class E Power Amplifier.                                                                                                                                                                        | 35 |

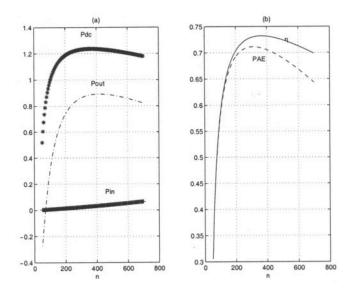

| 3.5  | (a) DC Power (PDC), input power (Pin), and output<br>power (Pout), (b) Efficiency and power added efficiency<br>(PAE) versus the number of fingers of the transistor in<br>the output stage.                            | 37 |

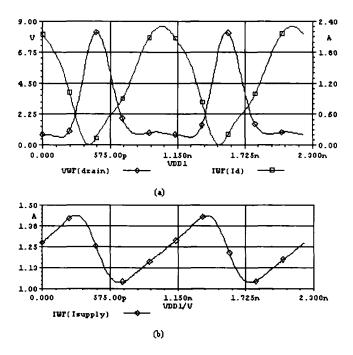

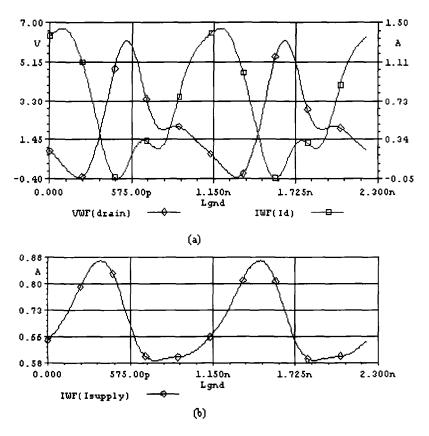

| 3.6  | Simulated waveforms of the class-E power amplifier,<br>(a) The drain voltage, and the drain current of the out-<br>put stage transistor, (b) the supply current.                                                        | 38 |

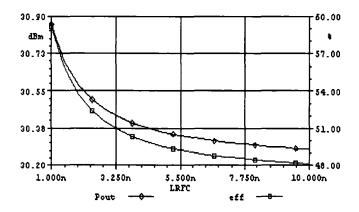

| 3.7  | The effect of having a finite de-feed inductance on the                                                                                                                                                                 |    |

|      | output power and efficiency of a class E Amplifier.                                                                                                                                                                     | 38 |

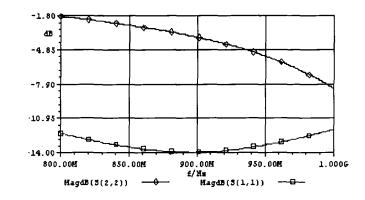

| 3.8  | $S_{11}$ , and $S_{22}$ of the power amplifier.                                                                                                                                                                         | 39 |

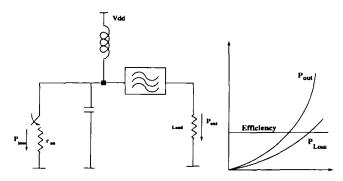

| 3.9  | Constant efficiency over supply voltage.                                                                                                                                                                                | 40 |

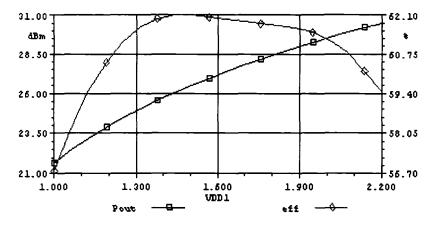

| 3.10 | Simulated output power and efficiency versus the sup-<br>ply voltage.                                                                                                                                                   | 40 |

| 3.11 | Simulated current and voltage waveforms of class E PA with 1nH source inductance.                                                                                                                                       | 41 |

| 3.12 | Simulated output power and efficiency versus the sup-<br>ply voltage of a class E PA with 1 nH source inductance.                                                                                                       | 42 |

| 3.13 | Layout of Class E PA.                                                                                                                                                                                                   | 47 |

| 3.14 | Chip micro-graph of the class E PA (output pads don't have ESD protection).                                                                                                                                             | 48 |

| 3.15 | Chip micro-graph of the class E PA (output pads with                                                                                                                                                                    |    |

|      | ESD protection).                                                                                                                                                                                                        | 48 |

| 3.16 | Bonded chip micro-graph.                                                                                                                                                                                                | 49 |

| 3.17 | Implementation of inductances using board traces.                                                                                                                                                                       | 49 |

| 3.18 | The measured output power, power added efficiency of<br>the power amplifier at 900MHz, indicating relatively<br>high ground inductance values that is affecting the op-<br>eration of the amplifier as a class E stage. | 50 |

| 3.19 | The measured output power and efficiency of the power amplifier at 900MHz.                                                                                                                                              | 50 |

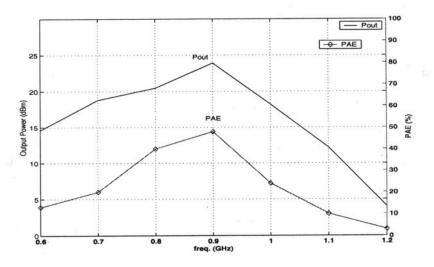

| 3.20 | The variation of output power and efficiency within the band of interest.                                                                                                                                               | 51 |

# RF CMOS POWER AMPLIFIERS: Theory, Design and Implementation

MONA MOSTAFA HELLA RF MICRO DEVICES Boston, MA

MOHAMMED ISMAIL Analog VLSI Laboratory The Ohio-State University

KLUWER ACADEMIC PUBLISHERS NEW YORK, BOSTON, DORDRECHT, LONDON, MOSCOW

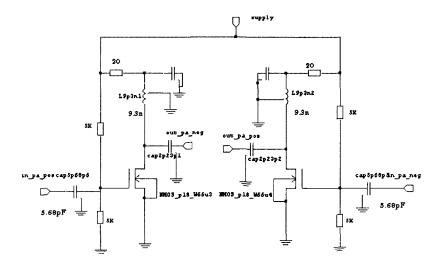

| 5.3  | The Schematic of the class A output stage.                                                                     | 74       |

|------|----------------------------------------------------------------------------------------------------------------|----------|

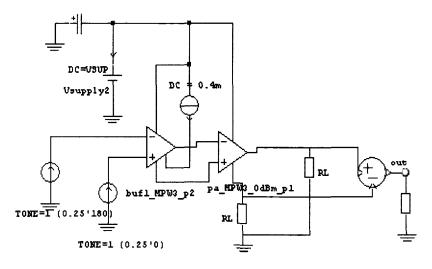

| 5.4  | The Block diagram of 0 dBm power amplifier.                                                                    | 74       |

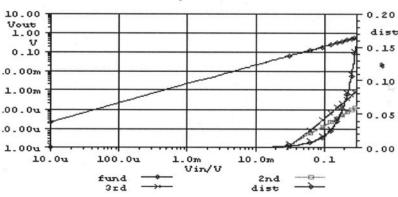

| 5.5  | Simulation results of the harmonic content of the PA.                                                          | 75       |

| 5.6  | The variation of the output voltage at the fundamental frequency, second, and third harmonics, and the distor- |          |

|      | tion level versus the input voltage.                                                                           | 76       |

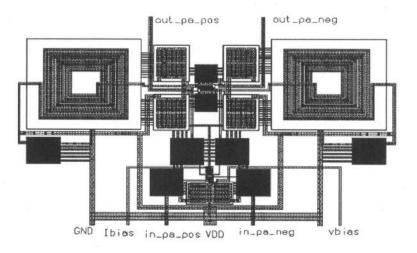

| 5.7  | The layout of class 3 power amplifier to be connected to the VCO in the Bluetooth transmitter chain.           | 76       |

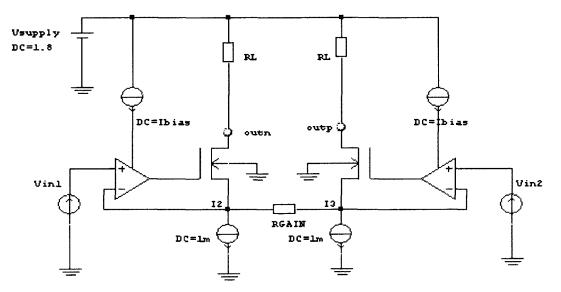

| 5.8  | Simplified schematic of the VGA employed in a class 2/3 Bluetooth amplifier.                                   | 77       |

| 5.9  | Simulation results of class 2 Bluetooth PA                                                                     | 77       |

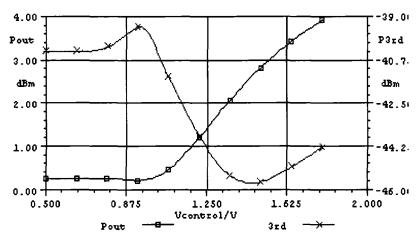

| 5.10 | The schematic of the core of the class AB power amplifier.                                                     | 79       |

| 5.11 | Power amplifier test setup.                                                                                    | 79       |

| 5.12 | The variation of output power, and PAE as a function of the input signal frequency.                            | 80       |

| 5.13 | The variation of output power, and PAE, and power gain versus input power.                                     | 81       |

| 5.14 | The input and output matching.                                                                                 | 81       |

| 5.15 | Variation of output power and efficiency versus the cas-<br>code bias voltage.                                 | 82       |

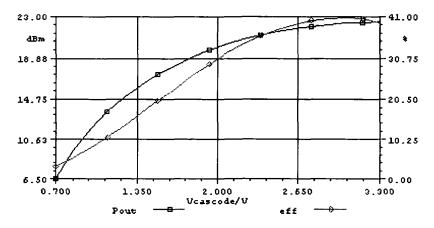

| 5.16 | Stability of the power amplifier (K >1 $\mu$ >1, and $\Delta$ <                                                |          |

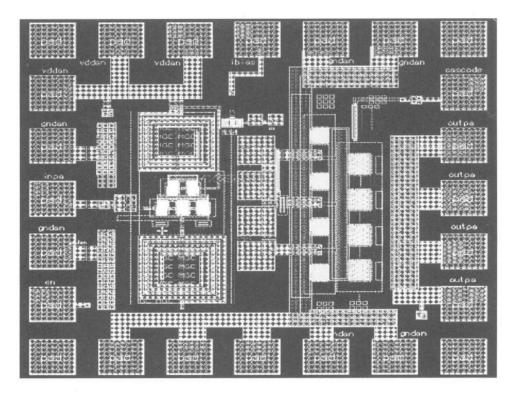

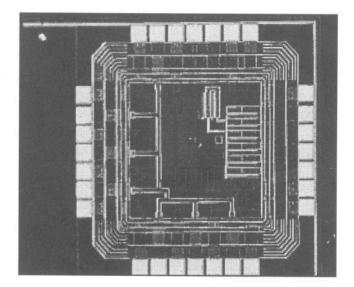

| 5.17 | <ol> <li>The layout of 0.18µm CMOS PA for class 1 Bluetooth<br/>standard.</li> </ol>                           | 84<br>85 |

|      |                                                                                                                |          |

# List of Tables

| 1.1 | Performance summary of CMOS RF transceivers            | 2  |

|-----|--------------------------------------------------------|----|

| 1.2 | Example of some digital wireless standards.            | 4  |

| 1.3 | Short-Range wireless standards.                        | 6  |

| 1.4 | Example of reported CMOS power amplifiers.             | 10 |

| 4.1 | Power classes for Bluetooth                            | 56 |

| 4.2 | Performance comparison of CMOS PAs.                    | 69 |

| 5.1 | DC operating conditions                                | 78 |

| 5.2 | Input signal parameters                                | 80 |

| 5.3 | Harmonic-Balance and process corner simulations        | 82 |

| 5.4 | Small signal S-parameter variation with process corner |    |

|     | and temperatures                                       | 83 |

| 5.5 | Summary of simulated electric characteristics          | 84 |

|     |                                                        |    |

This page intentionally left blank

# Preface

The convergence of home electronics, computer, and communication technologies is one of the most exciting technological and business trends of the next decades. The key to a wireless solution is the building of intelligent units, that can communicate clearly in a wire-free environment, occupy as little space as possible, and consume low power to maximize battery life. All these criteria are best met by highly integrated, low power, battery operated micro-systems.

Wireless applications are witnessing tremendous growth with proliferation of different standards covering wide, local and personal area networks (WAN, LAN and PAN). The trends call for designs that allow 1) smooth migration to future generations of wireless standards with higher data rates for multimedia applications, 2) convergence of wireless services allowing access to different standards from the same wireless device.

The key to integration, and reduction in costs is the correct choice of the implementation technology. CMOS technology has played an important role in providing higher functionality and complexity at low costs. The performance of power amplifiers is a crucial issue for the overall performance of the transceiver's chain. Until now, power amplifiers for wireless applications have been produced almost exclusively in GaAS technologies, with few exceptions in LD-MOS, Si BJT, and SiGe HBT. Sub-micron CMOS processes are now considered for power amplifier design due to the higher yield, and the lower costs it can provide. A typical power amplifier module for wireless communications consists of 3 dies, and 15-20 passive components plus decoupling. A CMOS power amplifier design solution could lead to component count that can be reduced to one die and 3-5 passives plus decoupling. This reduction in component count leads to a significant reduction in power amplifier cost.

The is the first monograph addressing RF CMOS power amplifier design for emerging wireless standards. The focus will be on power amplifiers for short distance wireless personal and local area networks (PAN and LAN), however the design techniques are also applicable to emerging wide area networks (WAN) infrastructures using micro or pico cell networks. The book discusses CMOS power amplifier theory and design principles, describes the architectures and tradeoffs in designing linear and nonlinear power amplifiers. It then details design examples of RF CMOS power amplifiers for short distance wireless applications (e.g,Bluetooth, WLAN) including designs for multi-standard platforms. Design aspects of RF circuits in deep submicron CMOS are also discussed.

This book will serve as a reference for RF IC design engineers, RF and R&D managers at industry, and for graduate students conducting research in wireless semiconductor IC design in general and with CMOS technology in particular. The book focuses mainly on the design procedure and the testing issues of CMOS RF power amplifiers and is divided into five main chapters.

Chapter 2 discusses the basic concepts of power amplifiers; optimum load, load line theory, and gain match versus power match. Performance parameters such as efficiency and linearity are presented. Different power amplifier classes are discussed and compared in terms of linearity and efficiency. Finally some common power amplifier linearization techniques are briefly investigated.

Chapter 3 presents the design and optimization techniques used to implement a 900MHz class E power amplifier. The theory behind class E operation is illustrated, the effects of some circuit components on the performance of the amplifier are demonstrated. The potential for applying the same concepts to multi-standard operation is also discussed. Finally testing procedure and measurement results are given.

Chapter 4 deals with extending the limits of the used technology to achieve 2.4GHz operation, and satisfy the Bluetooth standard. This is the first reported work on class 1 Bluetooth power amplifiers. Section 4.2 describes the details of the 2.4GHz power amplifier design, together with the implementation of the power control mechanism. Section 4.3 presents the simulation results, while experimental data is given in section 4.4. Chapter 5 presents an improved version of the power amplifier , using 0.18 micron technology in which class 1, class2, and class 3 power amplifiers are implemented. Finally conclusions are drawn in chapter 6.

This book has its roots in the doctoral dissertation work of the first author at the Analog VLSI Lab, The Ohio State University. We would like to thank all those who supported us at the Analog VLSI Lab and at other locations including the Radio Electronics Lab at the Swedish Royal Institute of Technology, and Spirea AB, Stockholm.

#### MONA MOSTAFA HELLA, MOHAMMED ISMAIL

Ohio, October 2001

Figure 5.17. The layout of  $0.18\mu$ m CMOS PA for class 1 Bluetooth standard.

the operation of the power amplifiers have been verified with simulation results at different operating conditions.

# Chapter 1

# INTRODUCTION

# 1. **RF CMOS Transceivers**

The expansion of the market for portable wireless communication devices has given tremendous push to the development of a new generation of low power radio frequency integrated circuit (RFIC) products. Cellular and cord-less phones, pagers, wireless modems, and RF ID tags, require more compact and power saving solutions to accommodate the ever-growing demand for lighter and cheaper products [1]. These listed devices use different standards employing a wide range of frequency from 900MHz to 5.6GHz.

Radio frequency integrated circuits, RFIC's, have to deal with performance issues such as noise, both broadband and near carrier, linearity, gain, and efficiency, in addition to the traditional requirements of power dissipation, speed, and yield. As a result, the optimum integrated circuit technology choices for RF transceivers in terms of optimum devices and levels of integration, are still evolving. Engineers planning to implement wireless transceivers are confronted with various possibilities: silicon CMOS, BiCMOS, and bipolar technologies, GaAs MESFET, hetero-junction bipolar transistor (HBT), and PHEMT, as well as discrete filters. Traditional commercial implementation of high performance wireless transceivers typically utilizes a mixture of these technologies in order to implement a complete system [2]. Even though RF designs contain fewer devices compared to digital chips, they are inherently more challenging, as very little automation is available for the design process. More-over, RF devices are typically pushed to their performance limits; thus, all the nonlinearities and second order effects need to be taken into account.

The optimum goal is to achieve low cost, low power, and high volume implementation of radio functions that are traditionally implemented using bulky, expensive, and power hungry hybrid components. Additionally, developers of

| Reference | Architecture | Application | Technology        | Power     |

|-----------|--------------|-------------|-------------------|-----------|

| [4]       | Homodyne     | ISM band    | $1.0\mu m CMOS$   | 177mW     |

| [5]       | Wideband-IF  | DECT        | 0.6µm CMOS        | 198mW     |

| [6]       | Low-IF       | DCS1800     | $0.25 \mu m$ CMOS | 192mW     |

| [7]       | Weaver       | GSM/DCS1800 | $0.6\mu m$ CMOS   | 72mW/75mW |

| [8]       | Heterodyne   | GSM         | $0.25\mu m$ CMOS  | 50mW      |

Table 1.1. Performance summary of CMOS RF transceivers

new wireless applications are also looking to provide consumers with both the convenience of added connectivity and the benefit of additional services provided by a transceiver able to operate with multiple RF standards. The VLSI capabilities of CMOS make this technology particularly suitable for very high levels of mixed signal radio integration while increasing the functionality of a single chip radio to cover multiple RF standards [3]. At the research level, CMOS RF technology is already expanding its applications to radio systems with stringent requirements such as cellular telephony, as shown in table 1.1, based on the work in [4], [5], [6], [7], [8]. For compact low cost, and low power portable devices, the prospect of a single chip CMOS radio has received considerable interest, even though it remains to be researched whether it is feasible to put the RF front end on the same die with the rest of the mobile terminal. Even the less ambitious objective of implementing the mobile phone as a set of separate chips in the same CMOS technology may bring considerable economic benefits [9].

# 2. CMOS Short Range Wireless Transceivers

The implementation of a single chip CMOS transceiver has recently been commercially available thanks to the fast growth of wireless computing technologies. Short-range wireless communication systems such as IEEE 802.11, Wireless Local Area Network (WLAN) and the Bluetooth standards have made wireless computing and other broadband services possible. Each radio device covers 10-100m range, and is required to have high bit rate. A short-range wireless system can be used in an environment where users are highly mobile such that wired network installations would require higher costs. Thus, there is much interest today in single-chip wireless transceivers which consume a small amount of power, need no off-chip components, support voice and data traffic over short ranges by transmitting modest power, implement power control, and are resilient to interferes [4].

The development that took place in the area of wireless communications is evident by comparing two figures. The first figure (Figure 1.1) is the traditional super-heterodyne transceiver, implemented using a combination of several in-

#### INTRODUCTION

tegrated circuits built using different technologies: GaAs, bipolar, and ceramic SAW filters are used for the RF section, bipolar for the IF section, and CMOS for base band. This design partitioning has changed recently, thanks to the advance in CMOS technology [1].

*Figure 1.1.* Example of a super-heterodyne transceiver implemented using multiple technologies.

On the other hand Figure 1.2 shows a very recent design of a complete transceiver for the new Bluetooth technology [10]. In contrast to traditional designs, CMOS has been used to implement all system blocks operating at 2.4GHz band. This fully integrated System-on-Chip (SoC) [10] includes the RF front-end, the digital baseband processor, the microprocessor, and the flash memory with the software stack. This achievement has been possible thanks to the relaxed performance requirements, and the low output power (OdBm-4dBm) of the Bluetooth standard, together with the use of deep sub-micron technologies.

The next challenge is to achieve higher levels of output power at such high frequencies as 2.4GHz, and ultimately at 5GHz. This work will focus on the transmit power amplifier as one of the most challenging building blocks for wireless transmitters as will be illustrated in the next sections.

Figure 1.2. A fully integrated single chip for Bluetooth

| Parameter             | NADC           | IS-95 CDMA | GSM      | DECT      |

|-----------------------|----------------|------------|----------|-----------|

| RF Tx. Freq. (MHz)    | 824-849        | 1860-1910  | 890-915  | 1880-1900 |

| Multiple access       | TDMA/FDM       | CDMA/FDM   | TDMA/FDM | TDMA/FDM  |

| Duplexing             | FDD            | FDD        | FDD      | TDD       |

| number of channels    | 832            | 20         | 124      | 10        |

| Channel spacing       | 30kHz          | 1.25MHz    | 200kHz   | 1.728MHz  |

| Modulation            | $\pi/4$ -DQPSK | QPSK/OQPSK | GMSK     | GFSK      |

| Peak to average ratio | 3.5dB          | 10dB       | 1.5dB    | 0dB       |

| Spectral regrowth     | medium         | high       | low      | low       |

Table 1.2. Example of some digital wireless standards.

### 3. Wireless Transmission Protocols

Second generation (2G) mobile radio systems have shown great success in providing wireless service worldwide with the use of digital technology, in contrast to the analog first generation systems. Digital modulation techniques provide improved spectral efficiency, enhanced voice recognition, and quality as well as security. The most important 2G systems are global system for mobile communication (GSM), North American Digital cellular NADC (IS-54, IS-136) and personal digital cellular in Japan. However, 2G systems are limited to voice and low data rate services.

Within the next few years, third generation wireless standards will be implemented and used to provide broadband multimedia and high data rate applications with the aim of providing universal access and global roaming [11]. UMTS, CDMA 2000, W-CDMA, and EDGE are examples of 3G systems. Once they are launched, there will be an increasing demand for multi-standard terminals. Such terminals should allow access to different systems providing various services, including backward compatibility to existing standards. The coexistence of the second generation with third generation cellular systems would then require multi- mode, multi-band mobile terminals [12]. The main characteristics of some 2G and 3G systems are summarized in Table 1.2.

Short-range wireless communication standards are defined in Table 1.3. These standards are defined at 2.4GHz, and 5GHz unlicensed Industrial Scientific, and Medical (ISM) band. The IEEE 802.11 committee established the five different standards, which are Infrared, 2.4GHz Frequency hopping Spread Spectrum (FHSS), 2.4GHz Direct Sequence Spread Spectrum (DSSS), 2.4GHz High Rate DSSS(HR/DSSS), and 5GHz Orthogonal Frequency Division Multiplexing (OFDM). Only the OFDM standard uses the 5GHz frequency band in the 802.11 standards, while the others use the 2.4GHz ISM band.

European Telecommunication Standards Institute (ETSI) high-performance radio LAN (HIPERLAN) also uses the 5GHz band. The first draft of HIPER-LAN standard adopted GMSK modulation scheme for high bit rate, and FSK for low bit rate. In order to harmonize the WLAN standards at 5GHz range and provide high speed access to a variety of networks, a new standard called HIPERLAN2 is developed. The multiple access method and modulation method of the HIPERLAN2 are the same as those of the 5GHz IEEE802.11 standard.

While the 802.11 and HIPERLAN standards are developed for the enterprise network, the Bluetooth and the HomeRF have their own special interests. The Bluetooth is for a short range Radio link between mobile PCs, mobile phones, and other portable devices. The HomeRF is for wireless voice, and data networking within the home at consumer price points. IEEE 802.11 FHSS, Bluetooth, and HomeRF standards use the same frequency hopping multiple access method, and same modulation scheme. However, they have different data rate, hopping rate, and Bluetooth has lower sensitivity than the others. Therefore, there is more room for higher noise figures in Bluetooth standard. The most important factor is that the Bluetooth standard focuses more on small size and low cost. HomeRF standard mainly focuses on home networking, which makes connections between the PC and internet throughout the home and yard.

Looking at these standards from the power amplifier design perspective, the modulation method along with the base band filtering utilized in digital systems may cause the modulated carrier to exhibit a non-unity peak to average power ratio, therefore requiring some degree of Linearity in the power amplifier. Table 1.2, and Table 1.3 shows the basic requirements of some standards.

| Standard    | Frequency Range | Multiple access | Modulation   | Data Rate       |

|-------------|-----------------|-----------------|--------------|-----------------|

| IEEE802.11  | 2.4GHz          | DSSS            | DBPSK        | 1Mbps           |

| DSSS        |                 |                 | DQPSK        | 2Mbps           |

| IEEE802.11  | 2.4GHz          | FHSS            | 2GFSK        | 1Mbps           |

| FHSS        |                 |                 | 4GFSK        | 2Mbps           |

| IEEE802.11  | 2.4GHz          | DSSS            | CCK          | 5.5Mbps         |

| HR/DSSS     |                 |                 |              | 11Mbps          |

| IEEE802.11a | 5.250GHz        | OFDM            | BPSK/QPSK    | 6,9,12,18 Mbps  |

| OFDM        | 5.775GHz        |                 | 16 or 64 QAM | 24,36,48,54Mbps |

| HIPERLAN    | 5.250GHz        | FDMA            | FSK          | 1.47 Mbps       |

| Type 1      |                 | TDMA            | GMSK         | 23.6 Mbps       |

| HIPERLAN    | 5.250GHz        | OFDM            | BPSK/QPSK    | 6,9,12,18 Mbps  |

| Type 2      | 5.6GHz          |                 | 16 or 64 QAM | 27, 36, 54 Mbps |

| Bluetooth   | 2.4GHz          | FHSS            | GFSK         | 1 Mbps          |

| HomeRF1.0   | 2.4GHz          | FHSS            | 2GFSK        | 1 Mbps          |

| (1 MHz)     |                 |                 | 4GFSK        | 2 Mbps          |

| HomeRF2.0   | 2.4GHz          | FHSS            | 2GFSK        | 5 Mbps          |

| (5 MHz)     |                 |                 | 4GFSK        | 10 Mbps         |

Table 1.3. Short-Range wireless standards.

Those techniques employing  $\pi/4$ -DQPSK and QPSK/OQPSK require highly linear power amplifier to limit spectral growth caused by their abrupt phase changes. Although those employing GMSK, FM, and GFSK do not require high linearity, some standards like GSM have power control mechanisms that necessitate efficiency enhancement techniques at lower power levels.

Another feature required of power amplifiers in digital wireless standards is the control of the output power. For example, in TDMA systems such as IS-54 and GSM, the PA is turned on and off periodically to save power. Also in IS-95, the output power must be variable in steps of 1 dB. In class 1 Bluetooth radio, the output power must be controlled from 4 dBm to 20dBm in steps of 2, 4, 6, or 8dB.

# 4. CMOS PAs: Related Design Issues

The design of power amplifiers in CMOS technology is mainly affected by the following factors:

1 Low breakdown voltage of deep sub-micron technologies. This limits the maximum gate-drain voltage since the output voltage at the transistor's drain normally reaches 2 times the supply for classes B, and F, and around 3 times the supply for class E operation. Thus, transistors have to operate at a lower supply voltage, delivering lower power. Additionally CMOS tech-

nology has lower current drive; i.e. the gain provided by the single stage is very low. Either multiple stages would be used or new design techniques that would reduce the number of stages by decreasing the input drive requirements of the large transistors in the PA, are employed [13].

- 2 In contrast to semi-insulating substrates, a highly doped substrate is common in CMOS technology. This results in substrate interaction in a highly integrated CMOS IC. The leakage from an integrated power amplifier might affect the stability of, for example the VCO in a transceiver chain.

- 3 Conventional transistor models for CMOS devices have been found to be moderately accurate for RFICs, and need to be improved for analog operation at radio frequencies. Large signal CMOS RF models and substrate modeling are critical to the successful design and operation of integrated CMOS radio frequency power amplifiers, owing to the large currents and voltage changes that the output transistors experience [14]. As a result, traditional PA design relies heavily on data measured from single transistors.

- 4 Since the inherent output device impedance in the power amplifier case is very low, impedance matching becomes very difficult, requiring higher impedance transformation ratios. Additionally, the output matching elements require lower loss, and good thermal properties since there are usually significant RF currents flowing in these elements. If CMOS technology is used, the losses in the substrate will decrease the quality factor of the passive elements in the matching network. Usually the output- matching network is implemented off chip as the antenna itself is off chip.

- 5 The power amplifier delivers large output current in order to achieve the required power at the load. This current can be high enough that electro-migration and parasitic in the circuit may cause performance degradation [14].

# 5. CMOS PAs: Recent Progress

The research in the area of power amplifiers is divided into two main categories; the design and monolithic implementation of power amplifiers, and the integration of Linearization techniques. While the implementation of a complete transceiver was the focus of many publications ([4]- [6], [15]), the power amplifier was included in only two of the reported CMOS wireless transceivers [4], [15]. The first reported CMOS power amplifier targeted the 900MHz ISM band [16] delivering output power from  $20\mu$ W to 20 mW using a 3V supply, and was implemented in  $1\mu$ m technology. In an effort to provide higher integration level by having the de-feed inductors in the output stage on-chip, an extra fabrication step to remove the substrate beneath the inductor in order to improve the quality factor was employed. However, the measured drain efficiency of the power amplifier with the de-feed inductors of the output stage implemented on chip is 25%, compared to 40% with the inductors off-chip. No input matching to 50 Ohm was included since the power amplifier was integrated in the complete transceiver [4]. The output-matching network is implemented off-chip.

In [17] a 1W BiCMOS PA is reported. The design involves a negative resistance stage to boost the gain. The reported power added efficiency (PAE) is 30% using a 5V supply. External inductors are used as part of the interstage matching network, with the output-matching network completely off chip. Measurement results are reported for a chip-on-board die. While BiC-MOS is capable of supporting other RF transceiver functions and is a strong candidate as a low cost technology for realizing a single chip radio, the reduction in performance of a BiCMOS PA compared to GaAs is evident in this paper.

Many publications advocated that CMOS would be limited only to low power-low performance applications. In [18] a 1W-2.5V supply monolithic power amplifier was reported. The PA targeted NADC standards (824MHz-849MHz). A gain of 25dB is achieved through 3 gain stages (operating in class A, AB, and C), with the output stage operating in class D (the transistor is used as a switch). This power amplifier has a measured drain efficiency of 62% and a PAE of 42%. It does not achieve a high degree of integration sine the output-matching network is implemented off chip. Bond wires are also used as a part of the inter-stage matching network.

The use of nonlinear power classes has been limited to low frequency operation until a recent publication explored the possibility of using class E power amplifiers at the 900MHz band. In [19] a fully integrated, yet GaAs MESFET implementation of a class E PA is reported. This nonlinear power amplifier outputs 250mW at 835MHz with power added efficiency (PAE) of 50% in a 2.5V system. A class F amplifier is used as a driver stage to generate the required square wave input driving signal. Bias voltages are applied externally but all matching networks are included on chip. This paper illustrated the advantages of operating in class E rather than in classes C, B, or F considering the fact that it has higher optimum load and higher PAE under low voltage operation.

Class E power amplifiers have gained wide interest after the previously mentioned publication due to their inherent high efficiency. In [13] a 1.9GHz 1W class E PA is implemented in  $0.35\mu m$  CMOS technology using a 2V power supply. The input driving requirement of the output stage is greatly reduced by employing the concept of mode-locking in which the amplifier acts as an oscillator whose output is forced to run at the input frequency. The output-matching network is off chip, and all inductors included are bond wire inductors. The measured PAE using chip on board packaging is 48%. The draw back of the mode-locking (positive feedback) technique is that the PA is prone to locking onto interfering signals picked up by the antenna from adjacent mobile users.

While the trend in most publications is to adopt nonlinear power classes (class D [18], Class E [9], [13], [20], and [21], and class F ([22] - [23]) to implement high efficiency and high power amplifiers, the continuous decrease in the voltage breakdown of transistors for deep sub-micron technologies makes the use of Class E amplifiers more difficult. Class F emerged as a possible solution in this case [13-14]. However, modern communication standards employ non-constant envelope modulation techniques that require linear power amplifiers, which means that either added linearization circuitry would be required or traditional linear power amplifier classes are used [14], [24].

A sample of the publications listed in Table 1.4 shows that even though the inductors and capacitors that may be realized in CMOS technology are not suitable for high performance RF circuits, CMOS transistors have still adequate gain till 2GHz to allow the design of low cost hybrid 1W amplifiers. The real merits of CMOS PAs lie in the potential for integration. While the feasibility of a stand-alone CMOS PA does not imply its compatibility in a larger system, the integration issues will rely on system, circuit and layout solutions rather than the design of the individual block.

In the Linearization area, few papers were published that dealt with the monolithic implementation [25]- [26], while most of the published work focused on system simulations and discrete implementation [27], [28].

In [26] a phase correcting feedback system to reduce the AM to PM distortion of class E PA used in NADC standard was presented. The system employed a limiting amplifier, a phase detector, and a phase shifter all-operating at 835 MHz. In order to reduce the phase error in the output caused by class E amplifier, the output and input phases of the amplifier are compared and an error phase signal is generated. The error signal is applied to a phase shifter at the input of the PA. The phase correcting feedback system reduces the phase distortion from 30 degrees to 4 degrees, and consumed 21.5mW while the PA delivers 500mW.

In [25] a fully monolithic CMOS implementation of the Envelope Elimination and restoration linearization system that improves the Linearity of an efficient PA is fabricated in  $0.8\mu m$  CMOS process. A delta modulated switching power supply is employed to extend the modulation bandwidth to fit that of the NADC. The Linearization system improves the overall efficiency from 36% to 40% while increasing the maximum linear output power from 26.5dBm

| Reference | Technology | Frequency(MHz) | Pout(dBm) | PAE(%) |

|-----------|------------|----------------|-----------|--------|

| [16]      | 1µm        | 900            | 13        | 30-40  |

| [18]      | 0.8µm      | 824-849        | 30        | 42     |

| [9]       | 0.25µm     | 900            | 29.5      | 41     |

| [13]      | 0.35µm     | 1900           | 30        | 48     |

| [14]      | 0.25µm     | 1950           | 29.2      | 27     |

| [24]      | 0.35µm     | 1730           | 30.4      | 45     |

| [22]      | 0.25µm     | 1400           | 24.7      | 43     |

| [23]      | 0.2µm      | 900            | 31.7      | 43     |

Table 1.4. Example of reported CMOS power amplifiers.

to 29.5dBm. Compared to the usual discrete implementation of EER systems used in high power base station, this design is amenable to integration in a low cost CMOS technology and makes linearization affordable to handsets.

In [20] a 20dBm power amplifier for Linear Amplification with Non-linear Components (LINC) transmitters is reported. An open loop linearized PA has been realized by combining two nonlinear class E amplifiers. The paper deals with a portion of the transmitter, not the whole system, and achieves 35% of power added efficiency under linear operation.

# 6. Motivation

For applications requiring moderate to high power, the power amplifier contributes significantly to the total transceiver power consumption, making the PA efficiency critical to the overall system performance. Realizing high efficiency in CMOS is impeded by the technology's low breakdown voltage, low current drive and lossy substrate. In addition, maximum efficiency is normally achieved when the amplifier is operating at maximum power, which typically accounts for only a small portion of time in transceiver's normal operation.

In addition to efficiency and output power requirements, linearity in some modulation techniques is a major issue. Bandwidth-efficient modulation schemes require linear PAs to minimize spectral re-growth, and AM-PM conversion. This means that the modulated signal will leak into the neighboring channels. The leakage is characterized by the adjacent channel power ratio (ACPR), relating the power in the channel to the power leaked into the neighboring channel. All these effects will be discussed in chapter 2. Furthermore, amplifiers that simultaneously process many channels require linearity to avoid cross modulation [29].

There are two approaches to satisfy Linearity requirements for power amplifiers; either employ a linear operating class as an output stage, or start with a nonlinear-high efficiency amplifier and apply linearization techniques, Linearization techniques are usually utilized in complex, expensive RF and microwave systems but they have not yet found their way in low cost portable terminals on a large scale. This is mainly due to the fact that such systems require various adjustments and become less effective as device characteristics change with temperature and output power [29].

change with temperature and output power [29]. In order to realize a complete transceiver on chip, issues related to system specifications, individual block performance, and the layout of the whole chip have to be dealt with. Although many publications have proved the capabilities of CMOS in delivering power levels around 1W, integrating such high power amplifier with the rest of the transceiver would introduce temperature and substrate noise effects that will affect the performance of the rest of the transceiver. Integration can be a cost effective solution without compromising performance in the case of short-range wireless applications. Even without regarding the integration issue, a stand-alone power amplifier, implemented in CMOS, and capable of covering multi-frequency bands can provide low-cost solution to less demanding wireless standards, e.g. Bluetooth.

The objective of this work is to target the design issues encountered in the design and implementation of power amplifiers in standard CMOS technology, for short-range wireless applications. The investigation of class E power amplifiers for the 900MHz band and its capabilities to operate as a multi-band amplifier will be explored. In order to push the limits of the used technology to achieve high frequency operation above 2GHz, which is the highest reported frequency; the use of linear power classes to implement a class 1 Bluetooth power amplifier is discussed. A novel circuit implementation to realize power control, and satisfy the Bluetooth standard is presented. A  $0.18\mu m$  amplifier is also presented together with simulation results. Measurement results from two fabricated chips operating at the above mentioned frequencies are given.

# 7. Outline

This book focuses mainly on the design procedure and the testing issues of CMOS RF power amplifiers. It is divided into four main chapters. Chapter 2 discusses the basic concepts of power amplifiers; optimum load, load line theory, gain match versus power match. Performance parameters such as efficiency and linearity are presented. Different power amplifier classes are discussed and compared in terms of linearity and efficiency. Finally some common power amplifier linearization techniques are briefly investigated.

Chapter 3 presents the design and optimization techniques used to implement a 900MHz class E power amplifier. The theory behind class E operation is illustrated, the effects of some circuit components on the performance of the amplifier is demonstrated. The potential for applying the same concept to multi-standard operation is also discussed. Finally testing procedure and measurement results are given.

Chapter 4 deals with extending the limits of the used technology to achieve 2.4GHz operation, and satisfy the Bluetooth standard. This is the first reported work on class 1 Bluetooth power amplifiers. Section 4.2 describes the details of the 2.4GHz power amplifier design, together with the implementation of the power control mechanism. Section 4.3 presents the simulation results, while experimental data is given in section 4.4. Chapter 5 presents an improved version of the power amplifier , using  $0.18\mu m$  technology in which class 1, class2, and class 3 power amplifiers are implemented. Finally conclusions are drawn in chapter 6.

# Chapter 2

# POWER AMPLIFIER; CONCEPTS AND CHALLENGES

# 1. Introduction

Power Amplifiers are part of the transmitter front-end, and are used to amplify the signal being transmitted so that it can be received and decoded within a fixed geographical area The design of PAs, especially for linear, low-voltage operation, is still a difficult task. In practice, PA design has involved a substantial amount of trial and error, that is why discrete and hybrid implementations have traditionally been utilized. The main performance parameters for the power amplifier are the level of output power it can achieve, depending on the targeted application, linearity, and efficiency. There are two basic definitions for the efficiency of the PA. The drain efficiency is the ratio between the RF output power to the dc consumed power, and the power added efficiency (PAE) which is the ratio between the difference of the RF output power and the RF input power to the dc consumed power. The PAE is a more practical measure as it accounts for the power gain of the amplifier. As the power gain decreases, more stages will be required. Since each stage will consume a certain amount of power, the overall power consumption will increase, thus decreasing the overall efficiency.

While power efficiency is a performance issue, Linearity is imposed by the utilized modulation technique, or the level of output power back-off during operation.

Most power amplifiers employ a two-stage configurations, with matching network placed at the input, between the two stages, and at the output. Since the output stage typically exhibits a power gain of less than 10dB, a high-gain driver is added so as to lower the minimum required input level. The choice of the minimum input level depends on the driving capability of the preceding stage, the modulator or the up-converter. The output stage is commonly designed as a common-source stage with a large inductor connected between the output node, and the supply. The large inductor [called a "radio-frequency choke"] acts as a current source that can sustain positive and negative voltages.

Designing an integrated CMOS power amplifier is different from the traditional microwave PA design using discrete components. In traditional microwave PA design, a data sheet is usually provided by the manufacturer, giving the large signal input and output impedances at certain dc operating point. Thus, the optimum load of the amplifier can be determined. A load-pull technique is usually employed to obtain a functional relationship between the output power and output matching [30].

In designing a power amplifier, the designer has to choose the number of stages, the operating class of each stage, determine the optimum load of the output stage, and decide whether to use differential or single-ended structure. These issues depend on the used technology, the kind of modulation (constant-envelope, or nonconstant-envelope technique), and whether the amplifier will be integrated with the whole transceiver or will be on a separate chip.

This chapter presents the main concepts and challenges of RF power amplifiers. The difference between the matching of the power amplifier and any other front-end device is illustrated in the next section through the introduction of power match. The effect of the transistor knee (pinch-off) voltage especially for low-voltage operation is given. An overview of different power amplifier classes of operation, together with linearization/efficiency enhancement techniques is described. Finally, the effect of the nonlinearity of the PA on the output signal, the main stability issues, and means for controlling the output power are presented.

# 2. Conjugate Match and Load line Match

The concept of conjugate match is widely known as setting the value of the load impedance equals to the real part of the generator's impedance such that maximum output power is delivered to the load. However, this delivered power is limited by the maximum rating of the transistor acting as a current generator, together with the available supply voltage. By referring to Figure 2.1, it is evident that the device in this case would show limiting action at a current considerably lower than its physical maximum of  $I_{max}$ . This means that the transistor is not being used to its full capacity. To utilize the maximum current and voltage swing of the transistor, a load resistance of lower value than the real part of the generator's impedance value needs to be selected; this value is commonly referred to as the load-line match,  $R_{opt}$ , and in its simplest form is the ratio  $R_{opt} = V_{max}/I_{max}$ , assuming the generator's resistance is much higher

Figure 2.1. Conjugate match and load-line match.

than the optimum load resistance.

Thus the load-line match represents a real compromise that is necessary to extract the maximum power from RF transistor, and at the same time keep the RF voltage swing within the specified limits of the transistor and the available dc supply.

*Figure 2.2.* Compression characteristics for conjugate match (S22) (solid curve) and power match (dotted curve). 1 dB gain compression points (B, B') and maximum power points (A, A') show similar improvements under power-matched conditions.

Figure 2.2 illustrates the effect of the difference of gain match versus power (load-line) match on the output of a linear amplifier. The solid line shows the response of an amplifier that has been conjugately matched at much lower drive levels. The two pints A, and B, refer to the maximum linear power and the 1 dB compression power. In a typical situation, the conjugate match yields a 1 dB compression power about 2 dB lower than that which can be obtained by the correct power tuning, shown by the dotted line in Figure 2.2. This means the device would deliver 2 dB lower power than the device manufacturers specify. Since in power amplifier design, it is always required to extract the maximum possible power from the transistor, power-matched condition has to be taken more seriously, despite the fact that the gain at lower signal levels may be 1 dB or less than the conjugate-matched condition. Across a wide range of devices and technologies, the actual difference in output power, gained by power-matched condition, may vary over a range of 0.5dB to 3dB [30].

However, a load-line (power) matched rather than a conjugate (gain) match, might cause reflections and voltage standing wave ratio (VSWR) in a system to which it is connected. The reflected power is entirely a function of the degree of match between the antenna and the 50-Ohm system. The PA does present a mismatched reverse termination, which could be a problem is some situations. An Isolator or a balanced amplifier [31] is a simple and effective way of dealing with the problem.

# 3. Effect of the Transistor Knee Voltage

As mentioned earlier, traditional power amplifier design starts by determining the optimum load using the load line approach as shown in Figure 2.3. The knee voltage (pinch-off voltage) divides the saturation and the linear region of the transistor and can be defined as, for example,  $V_{ds}$  at the 95% of  $I_{max}$  point. The optimum load resistance is

# $R_{opt} = (v_{max} - V_{knee})/I_{max}$

While this is an effective approach for most power transistors, it is not suitable for sub-micron CMOS transistors. This is mainly due to the fact that  $V_{knee}$  is only about 10% to 15% of the supply voltage for typical power transistors, while it can be as high as 50% of the supply for deep sub-micron technologies as shown in Figure 2.3. Therefore, precluding the CMOS transistor from operating in the linear region does not result in optimum output power. In fact, a large portion of the RF cycle can be in the linear region. Therefore, both saturation and linear regions must be considered when determining the optimum load. This can be done using a general MOSFET equation valid in all regions of operation [23] or relying on harmonic balance simulations of circuits, with accurate transistor models, as will be discussed later in chapter 4.

Figure 2.3. Effect of the knee voltage on the determination of the optimum load.

### 4. Classification of Power Amplifiers

Power amplifiers have been traditionally categorized under many classes: A, B, C, AB, D, E, F, etc [32]. Power amplifier classes can be categorized either as bias point dependent, such as classes A, B, AB, and C, or depending on the passive elements in the output matching network that shape the drain voltage and current, provided that the transistor in this case operates as a switch. In the next subsections, the details of each operating class are discussed.

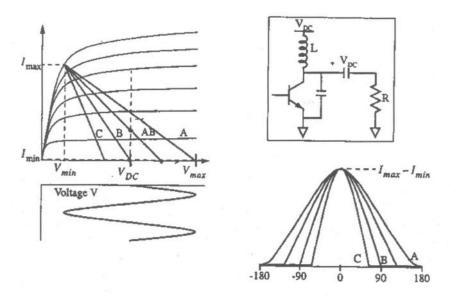

# 4.1 Class A, B, AB, and C PAs

The primary distinction between these power amplifier classes is the fraction of the RF cycle for which the transistor conducts. For class A PAs, the transistor is conducting for the entire RF cycle, whereas for class B PAs it is ON for half the RF cycle, and for less than half the RF cycle for class C. Class A, AB, and B amplifiers may be used as linear PAs, whereas class C are more nonlinear in nature [33]. Figure 2.4 illustrates the schematic and current waveforms for the above-mentioned classes of operation. While the third-order intercept point (IP3), adjacent channel power ratio (ACPR), 1 dB compression point, and harmonics are various measures of Linearity of PAs, drain efficiency and power added efficiency (PAE) of the PA are used to indicate the current drawn from the supply. The PAE is defined as

$$PAE = \frac{(P_{rf,out} - P_{rf,in})}{P_{dc}}$$

(2.1)

*Figure 2.4.* Traditional illustration of the schematic and current waveforms of classes A, B, AB, and C.

where  $P_{rf,out}$  is the RF output power,  $P_{rf,in}$  is the RF input power, and  $P_{dc}$  is the total dc power drawn from the supply.

The efficiency and output power for a power amplifier operating in class A, AB, B, or C, are given by [30];

$$\eta = \frac{v_{dd} - v_{dsat}}{v_{dd}} \frac{\theta - \sin\theta}{4(\sin\frac{\theta}{2} - \frac{\theta}{2}\cos\frac{\theta}{2})}$$

(2.2)

$$P_{out} = \frac{1}{2}(v_{dd} - v_{dsat})\frac{I_m}{2\pi}(\theta - \sin\theta)$$

(2.3)

where  $V_{dd}$  is the supply voltage,  $\theta$  is the conduction angle of the drain current,  $V_{dsat}$  is the pinch-off voltage (knee voltage), and  $I_m$  is the maximum drain current in the input transistor. Equations (2.2) and (2.3) are plotted in Figure 2.5(a). From this figure, it is evident that the increase in efficiency, obtained by reducing the conduction angle is achieved at the expense of the reduced output power from the power amplifier. In deep sub-micron technologies, the low output power of a reduced conduction angle is a major drawback. In order to achieve the required output power, the load resistance has to be lowered to impractical values considering the values of the parasitic resistances. As the conduction angle of the drain current decreases, the harmonic content of the current signal increases. The magnitude of the nth harmonic of the output drain current is given by [30];

*Figure 2.5.* (a) RF power and efficiency as a function of the conduction angle, (b) Fourier analysis of the drain current.

$$I_n = \frac{1}{\pi} \int_{-\frac{\theta}{2}}^{\frac{\theta}{2}} \frac{I_m}{1 - \cos(\frac{\theta}{2})} \left( \cos \alpha - \cos(\frac{\theta}{2}) \right) \cos n\alpha d\alpha \tag{2.4}$$

By examining Figure 2.5(b), it is clear that the dc component decreases monotonically as the conduction angle is reduced. In class B, the fundamental component is the same as in class A while the dc component is reduced by  $\pi/2$ . For conduction angles below  $\pi$ , corresponding to class C operation, the dc component continues to drop, but the fundamental component of the current signal also starts to drop below its class A level. This results in high efficiency, and lower power utilization factor (PUF). The odd harmonics can be seen to pass through zero at the class B point, For class AB mode, the third harmonic is not negligible. Still, class AB represents a compromise between linearity, PUF, and efficiency.

### 4.2 Class E

Figure 2.6 shows a conceptual picture of a class E power amplifier [34], [35]. In operation, the input signal  $v_{in}$  toggles the switch periodically with approximately 50% duty cycle. When the switch is ON, a linearly increasing current is built up through the inductor. At the moment the switch is turned off, this current is steered into the capacitor, causing the voltage across the switch  $V_s$  to rise. The tuned network is designed such that in steady state,  $V_s$  returns to zero with a zero slope, immediately before the switch is turned on. The band pass filter then selectively passes the fundamental component of  $V_s$  to the load, creating a sinusoidal output that is synchronized in phase and frequency with

the input. In practical applications,  $V_{in}$  may be phase or frequency modulated, in which case the information embedded in the modulation is also passed to the output with power amplification [13].

By comparing  $V_s$ , and  $I_s$  in Figure 2.6, it can be observed that the switch voltage and current are never simultaneously nonzero. Since the instantaneous power dissipation of the switch is the product of these two quantities, the switch is ideally lossless, and all the power from the dc supply is delivered to the radio frequency output. In addition, the capacitor is designed to be fully discharged before the switch is turned ON.

In high-speed operation, the switch transition time can become a significant fraction of a signal period. During these transitions, the switch voltage and current may be simultaneously nonzero, causing potential power loss in typical switching-mode amplifiers. For proper class E operation, this loss is alleviated at the turn on transistors by a zero switch current resulting from the simultaneously zero  $V_s$ , and  $dv_s/dt$ . On the other hand, turnoff transition loss is reduced by delaying the switch voltage rise until the switch is turned off. These properties have made class E-PAs attractive for high efficiency operations.

One of the features of class E amplifiers is the large peak voltage that the switch sustains in the off state, approximately  $3.56V_{dd}$ - $2.56V_{min}$ ; Where  $V_{min}$  is the minimum voltage across the transistor. Operating at class E requires either high transistor breakdown voltage, or operating at  $V_{DD}$  less than the specified value for a given technology. The equations describing the operation of class E will be discussed in Chapter 3.

Figure 2.6. A simplified class E power amplifier, and its steady state operation.

# 4.3 Class F

The basic idea behind class F and class D is to shape the output signal at the drain of the transistor such that it has more of a square shape than a sinusoidal shape. The load network provides a high termination impedance at the second or third harmonics, thus the voltage waveform across the switch exhibits sharper edges than a sinusoid, thereby lowering the power loss in the transistor.

Figure 2.7. Schematic, and output waveform of a typical class F stage.

Figure 2.7 shows an example of the class F topology. The tank consisting of  $L_1$  and  $C_1$  resonates at either  $2f_{in}$  or  $3f_{in}$ , where  $f_{in}$  is the input signal frequency, thus boosting the second or third harmonics at point X. Thus, the voltage across the switch approaches a rectangular waveform as the third harmonic becomes stronger. If the drain current of  $M_1$  is assumed to be a half sinusoid (i.e., half-wave rectified sinusoid), then it contains no third harmonic. The product of the rectangular drain voltage and half wave rectified current represent the power losses in the transistor. Since this power losses are minimum due to the shaping of the two signals, the efficiency can be relatively high. The theoretical efficiency of a class F power amplifier can reach 88%.

To summarize the discussion on previous classes, what determines the class of operation of the power amplifier is its conduction angle, input signal overdrive, and the output load network. Figure 2.8 shows how the PA relate to the conduction angle and the input signal over-drive. It illustrates that a given PA can be in any of the classical operating modes depending on the above two

Figure 2.8. Classical definition of power amplifier classes.

factors. For a small RF input signal  $V_{in}$ , the amplifier can operate in class A, AB, B, or C depending on the conduction angle (bias voltage relative to the transistor's threshold voltage). The PA efficiency can be improved by reducing its conduction angle by moving the design into class C operation, but at the expense of lower output power. An alternative approach to increasing efficiency without sacrificing output power is to increase the input over-drive such that the transistor acts as a switch. These are called saturated class A and C, class D, class E, or class F, depending on the conduction angle, and the shape of the load network.

# 5. Power Amplifier Linearization

Linearization techniques are mostly utilized in base stations due to their complexity. For mobile phones, increasing the talk time and lowering the weight of the terminal rely on having an efficient amplifier that does not consume a lot of dc power. On the other hand, an efficient amplifier is normally nonlinear, while a spectrally efficient modulation technique produces non-constant envelope signals. If this non-constant envelope signal is applied to a nonlinear amplifier, the signal will suffer spectral growth, which will lead to adjacent channel interference. One of the solutions would be to use an efficient nonlinear PA and apply a suitable linearization technique to restore Linearity.

The conventional techniques are feed forward, feedback, predistortion [30], [36], Envelope Elimination and restoration (EER) [37], Linearization using nonlinear components (LINC) [38], Bias adaptation, and Doherty amplifier [30]. The first three techniques are complex and need adjustments, or premeasured data to achieve the required Linearization. They are usually utilized in base stations. The simplicity of the last three techniques makes them amenable to integration depending on the degree of linearity required and the channel bandwidth. Even for modulation techniques that do not require linearization, some techniques like EER, LINC, Doherty's amplifier, and Bias adaptation can be used for efficiency enhancement at lower output power levels.

### 5.1 Feed Forward

Figure 2.9. (a) Simple Feedforward topology, (b) Addition of delay elements.

A nonlinear power amplifier generates an output voltage waveform that can be viewed as the sum of a linear replica of the input signal and an error signal. A feed forward topology computes this error and, with proper scaling, substrates it from the output waveform. Shown in Figure 2.9 is a simple example where the output of the main PA  $V_M$  is scaled down by  $1/A_v$ , generating  $V_N$ . The input is subtracted from  $V_N$ , and the result is scaled by  $A_v$  and subtracted from  $V_M$ . If  $V_M = A_V V_{in} + V_D$ , where  $V_D$  represents the distortion content, then  $V_N = V_{in} + V_D / A_V$ , yielding  $V_P = V_D / A_V$ , and  $V_Q = V_D$ , and hence  $V_{out} = A_V V_{in}$ . In practice, the two amplifiers in the circuit exhibit substantial phase shift at high frequencies, mandating the use of delay lines such that  $\Delta_1$  compensates for the phase shift of the PA, and  $\Delta_2$  for the phase shift of the error amplifier.