# Power Management Integrated Circuits

## Edited by Mona M. Hella • Patrick Mercier

## Power Management Integrated Circuits

#### Devices, Circuits, and Systems

#### **Series Editor**

*Krzysztof Iniewski* Emerging Technologies CMOS Inc. Vancouver, British Columbia, Canada

#### **PUBLISHED TITLES:**

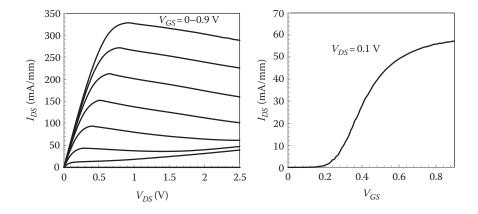

Analog Electronics for Radiation Detection Renato Turchetta

Atomic Nanoscale Technology in the Nuclear Industry Taeho Woo

Biological and Medical Sensor Technologies Krzysztof Iniewski

Building Sensor Networks: From Design to Applications Ioanis Nikolaidis and Krzysztof Iniewski

Cell and Material Interface: Advances in Tissue Engineering, Biosensor, Implant, and Imaging Technologies Nihal Engin Vrana

> **Circuits and Systems for Security and Privacy** Farhana Sheikh and Leonel Sousa

Circuits at the Nanoscale: Communications, Imaging, and Sensing Krzysztof Iniewski

> CMOS: Front-End Electronics for Radiation Sensors Angelo Rivetti

CMOS Time-Mode Circuits and Systems: Fundamentals and Applications

Fei Yuan

Design of 3D Integrated Circuits and Systems Rohit Sharma

Electrical Solitons: Theory, Design, and Applications David Ricketts and Donhee Ham

> Electronics for Radiation Detection Krzysztof Iniewski

**Electrostatic Discharge Protection: Advances and Applications** *Juin J. Liou*

> Embedded and Networking Systems: Design, Software, and Implementation Gul N. Khan and Krzysztof Iniewski

**Energy Harvesting with Functional Materials and Microsystems** Madhu Bhaskaran, Sharath Sriram, and Krzysztof Iniewski

Gallium Nitride (GaN): Physics, Devices, and Technology Farid Medjdoub

Graphene, Carbon Nanotubes, and Nanostuctures: Techniques and Applications James E. Morris and Krzysztof Iniewski

High-Speed Devices and Circuits with THz Applications Jung Han Choi

> High-Speed Photonics Interconnects Lukas Chrostowski and Krzysztof Iniewski

High Frequency Communication and Sensing: Traveling-Wave Techniques Ahmet Tekin and Ahmed Emira

High Performance CMOS Range Imaging: Device Technology and Systems Considerations Andreas Süss

Integrated Microsystems: Electronics, Photonics, and Biotechnology Krzysztof Iniewski

> **Integrated Power Devices and TCAD Simulation** *Yue Fu, Zhanming Li, Wai Tung Ng, and Johnny K.O. Sin*

Internet Networks: Wired, Wireless, and Optical Technologies Krzysztof Iniewski

Ionizing Radiation Effects in Electronics: From Memories to Imagers Marta Bagatin and Simone Gerardin

> Labs on Chip: Principles, Design, and Technology Eugenio Iannone

Laser-Based Optical Detection of Explosives

Paul M. Pellegrino, Ellen L. Holthoff, and Mikella E. Farrell

Low Power Emerging Wireless Technologies Reza Mahmoudi and Krzysztof Iniewski

Medical Imaging: Technology and Applications Troy Farncombe and Krzysztof Iniewski

> Metallic Spintronic Devices Xiaobin Wang

MEMS: Fundamental Technology and Applications Vikas Choudhary and Krzysztof Iniewski

Micro- and Nanoelectronics: Emerging Device Challenges and Solutions Tomasz Brozek

Microfluidics and Nanotechnology: Biosensing to the Single Molecule Limit Eric Lagally

MIMO Power Line Communications: Narrow and Broadband Standards, EMC, and Advanced Processing

Lars Torsten Berger, Andreas Schwager, Pascal Pagani, and Daniel Schneider

Mixed-Signal Circuits Thomas Noulis

Mobile Point-of-Care Monitors and Diagnostic Device Design Walter Karlen

Multisensor Attitude Estimation: Fundamental Concepts and Applications Hassen Fourati and Djamel Eddine Chouaib Belkhiat

Multisensor Data Fusion: From Algorithm and Architecture Design to Applications

Hassen Fourati

MRI: Physics, Image Reconstruction, and Analysis Angshul Majumdar and Rabab Ward

Nano-Semiconductors: Devices and Technology Krzysztof Iniewski

Nanoelectronic Device Applications Handbook James E. Morris and Krzysztof Iniewski

Nanomaterials: A Guide to Fabrication and Applications Sivashankar Krishnamoorthy

Nanopatterning and Nanoscale Devices for Biological Applications Šeila Selimovic

> Nanoplasmonics: Advanced Device Applications James W. M. Chon and Krzysztof Iniewski

Nanoscale Semiconductor Memories: Technology and Applications Santosh K. Kurinec and Krzysztof Iniewski

Novel Advances in Microsystems Technologies and Their Applications Laurent A. Francis and Krzysztof Iniewski

**Optical, Acoustic, Magnetic, and Mechanical Sensor Technologies** *Krzysztof Iniewski*

**Optical Fiber Sensors: Advanced Techniques and Applications** *Ginu Rajan*

Optical Imaging Devices: New Technologies and Applications Ajit Khosla and Dongsoo Kim

Organic Solar Cells: Materials, Devices, Interfaces, and Modeling Qiquan Qiao

> **Physical Design for 3D Integrated Circuits** *Aida Todri-Sanial and Chuan Seng Tan*

**Power Management Integrated Circuits and Technologies** Mona M. Hella and Patrick Mercier

> Radiation Detectors for Medical Imaging Jan S. Iwanczyk

Radiation Effects in Semiconductors Krzysztof Iniewski

**Reconfigurable Logic: Architecture, Tools, and Applications** *Pierre-Emmanuel Gaillardon*

> Semiconductor Radiation Detection Systems Krzysztof Iniewski

Smart Grids: Clouds, Communications, Open Source, and Automation David Bakken

> Smart Sensors for Industrial Applications Krzysztof Iniewski

**Soft Errors: From Particles to Circuits** *Jean-Luc Autran and Daniela Munteanu*

Solid-State Radiation Detectors: Technology and Applications Salah Awadalla

Structural Health Monitoring of Composite Structures Using Fiber Optic Methods Ginu Rajan and Gangadhara Prusty

> **Technologies for Smart Sensors and Sensor Fusion** *Kevin Yallup and Krzysztof Iniewski*

> > **Telecommunication Networks** *Eugenio Iannone*

**Testing for Small-Delay Defects in Nanoscale CMOS Integrated Circuits** Sandeep K. Goel and Krishnendu Chakrabarty

**Tunable RF Components and Circuits: Applications in Mobile Handsets** *Jeffrey L. Hilbert*

> VLSI: Circuits for Emerging Applications Tomasz Wojcicki

Wireless Medical Systems and Algorithms: Design and Applications Pietro Salvo and Miguel Hernandez-Silveira

Wireless Technologies: Circuits, Systems, and Devices Krzysztof Iniewski

Wireless Transceiver Circuits: System Perspectives and Design Aspects Woogeun Rhee

#### FORTHCOMING TITLES:

Advances in Imaging and Sensing Shuo Tang and Daryoosh Saeedkia

Introduction to Smart eHealth and eCare Technologies Sari Merilampi, Krzysztof Iniewski, and Andrew Sirkka

Magnetic Sensors: Technologies and Applications Laurent A. Francis and Kirill Poletkin

Nanoelectronics: Devices, Circuits, and Systems Nikos Konofaos

Radio Frequency Integrated Circuit Design Sebastian Magierowski

Semiconductor Devices in Harsh Conditions Kirsten Weide-Zaage and Malgorzata Chrzanowska-Jeske

X-Ray Diffraction Imaging: Technology and Applications Joel Greenberg and Krzysztof Iniewski

## Power Management Integrated Circuits

### Edited by Mona M. Hella

Rensselaer Polytechnic Institute, New York, USA

## Patrick Mercier

University of California, San Diego, USA

## Krzysztof Iniewski managing editor

Emerging Technologies CMOS Services Inc. Vancouver, British Columbia, Canada

CRC Press is an imprint of the Taylor & Francis Group, an **informa** business MATLAB<sup>\*</sup> is a trademark of The MathWorks, Inc. and is used with permission. The MathWorks does not warrant the accuracy of the text or exercises in this book. This book's use or discussion of MATLAB<sup>\*</sup> software or related products does not constitute endorsement or sponsorship by The MathWorks of a particular pedagogical approach or particular use of the MATLAB<sup>\*</sup> software.

CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742

© 2016 by Taylor & Francis Group, LLC CRC Press is an imprint of Taylor & Francis Group, an Informa business

No claim to original U.S. Government works Version Date: 20160407

International Standard Book Number-13: 978-1-4822-2894-6 (eBook - PDF)

This book contains information obtained from authentic and highly regarded sources. Reasonable efforts have been made to publish reliable data and information, but the author and publisher cannot assume responsibility for the validity of all materials or the consequences of their use. The authors and publishers have attempted to trace the copyright holders of all material reproduced in this publication and apologize to copyright holders if permission to publish in this form has not been obtained. If any copyright material has not been acknowledged please write and let us know so we may rectify in any future reprint.

Except as permitted under U.S. Copyright Law, no part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access www.copyright. com (http://www.copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC), 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

**Trademark Notice:** Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

Visit the Taylor & Francis Web site at http://www.taylorandfrancis.com

and the CRC Press Web site at http://www.crcpress.com

## Contents

| Preface      | xi                                                                                              |

|--------------|-------------------------------------------------------------------------------------------------|

| Series Edito | r xiii                                                                                          |

| Editors      |                                                                                                 |

| Contributor  | sxvii                                                                                           |

| Chapter 1    | Efficient On-Chip Power Management Using Fully<br>Integrated DC–DC Converters1                  |

|              | Saurabh Chaubey, Sudhir S. Kudva, and Ramesh Harjani                                            |

| Chapter 2    | Single-Inductor Multiple-Output DC–DC Buck Converter                                            |

|              | Ke-Horng Chen                                                                                   |

| Chapter 3    | SIMO Power Converters with Adaptive PCCM Operation71                                            |

|              | Yi Zhang and D. Brian Ma                                                                        |

| Chapter 4    | Circuit Techniques for Improving the Power Density<br>of Switched-Capacitor Converters          |

|              | Yutian Lei and Robert Pilawa-Podgurski                                                          |

| Chapter 5    | Resonant Switched Capacitor Power Converters<br>and Architectures145                            |

|              | Jason Stauth                                                                                    |

| Chapter 6    | Design of Recursive Switched-Capacitor DC-DC Converters 171                                     |

|              | Loai G. Salem and Patrick P. Mercier                                                            |

| Chapter 7    | GaAs Power Devices and Modules                                                                  |

|              | Vipindas Pala and T. Paul Chow                                                                  |

| Chapter 8    | Silicon and III–V Technologies for High Switching Speed<br>Monolithic DC–DC Power Converter ICs |

|              | Han Peng, Zemin Liu, and Mona Mostafa Hella                                                     |

## Preface

Big data generated by the Internet of Things (IoT), healthcare, and the world wide web (WWW) are changing our lifestyle and our society. Small chips are enabling this change through data sensing, gathering, processing, storing and networking through wireless and wired connections. This explosive growth of electronic devices and their deployment in new applications have sparked an urgency to address their environmentally benign and sustainable energy needs. The spread of mobile computing and the IoT devices is limited by both battery life and form factor. Research in the field of power management circuits and systems in the last 5–10 years has explored integrated power management units with a small form factor, increased power density, and efficient performance over a wide range of output power in the quest for replacing and/or more efficiently operating with conventional rechargeable batteries and carbon-based sources.

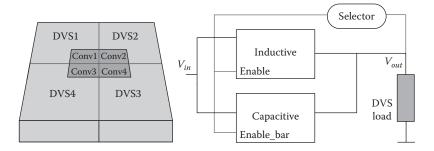

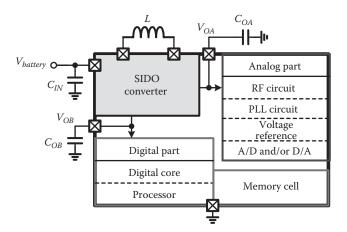

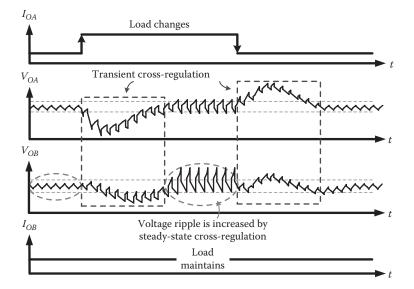

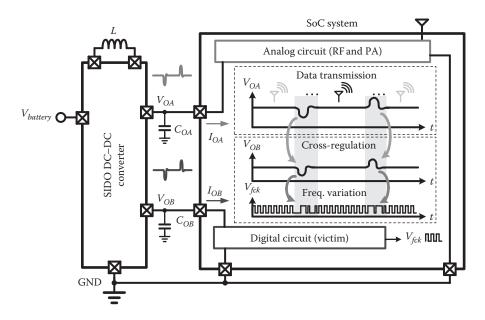

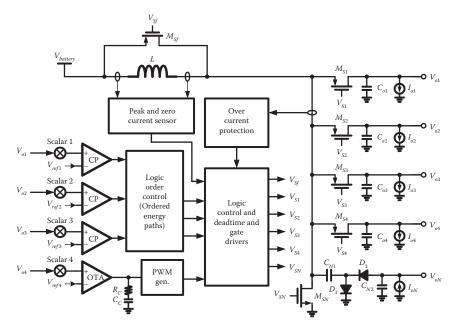

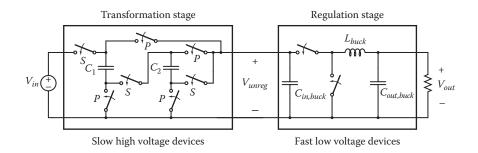

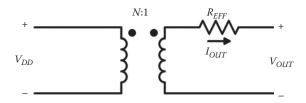

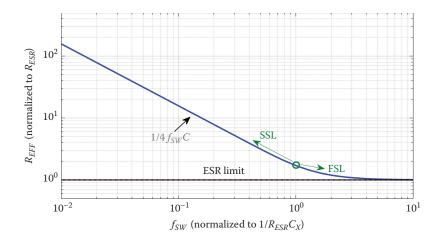

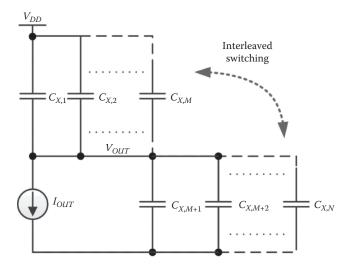

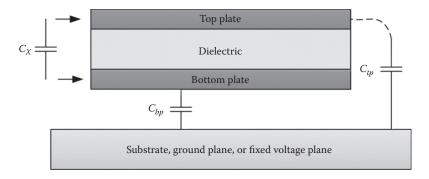

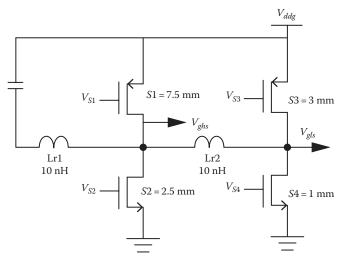

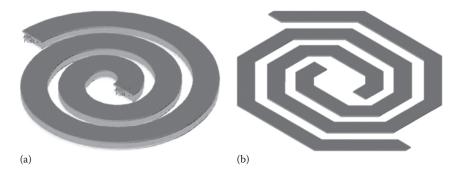

The book begins with a comparison between inductive and capacitive dc-dc converters in terms of their passive devices, amenability to integration, and efficiency at various load conditions. A hybrid inductive-capacitive converter is proposed for wide-range dynamic voltage scaling, with details on the static, dynamic performances and discussion of different loss mechanisms. Next, the design of single inductor dual output (SIDO) and single inductor multiple output (SIMO) converters are covered in detail in Chapters 2 and 3, including the presentation of different design goals such as reducing the number of power switches and their associated power losses, extending the output current range, reducing ripple, and improving dynamic performance. Various control techniques are discussed to meet the different design goals with an emphasis on adaptive pseudo-continuous conduction mode (PCCM) detailed in Chapter 3. Design aspects of switched capacitor (SC) dc-dc converters are given in Chapters 4 through 6. While advantageous in terms of their integration potential, switched capacitor converters have been limited to lower power density applications in addition to lower efficiencies as the load moves away from optimum design conditions. Techniques such as quasi-SC converters, soft-charging or resonant SC converters, and recursive SC converters are detailed to address some of the aforementioned limitations. Chapters 7 and 8 present a different perspective on power management units through the use of GaAs pHEMTs for efficient highfrequency switching converters. The details of device design, high-quality factor passives, and circuit design techniques tailored to GaAs technology are discussed in addition to reconfigurable output passive networks to maintain the high efficiency of GaAs converters over wider voltage and current ranges. Some of the circuit techniques such as resonant gate drivers are compared in both GaAs and CMOS technologies as in Chapter 8. While many of the chapters are focused around several key publications in the field, rather than republishing the original papers, the authors have expanded the material to provide more background and breadth than the original publications. As such, the book would complement a graduate level course on power electronics integrated circuits.

We hope you find this book useful in your exploration of power management integrated circuits and systems. There are many unique challenges to working with integrated circuits whether it is in standard nanometer scale silicon technologies or in III–V technologies. However, there are also many rewards to reap from having such a "power system-on-chip" (PSOC) platform. As the editors, we would like to thank the contributors to this book, including the graduate students and the contributing authors who have worked tirelessly to share their insights with you in this book.

#### Mona M. Hella Patrick P. Mercier

MATLAB<sup>®</sup> is a registered trademark of The MathWorks, Inc. For product information, please contact:

The MathWorks, Inc. 3 Apple Hill Drive Natick, MA 01760-2098 USA Tel: 508-647-7000 Fax: 508-647-7001 E-mail: info@mathworks.com Web: www.mathworks.com

## Series Editor

Krzysztof (Kris) Iniewski is managing R&D at Redlen Technologies Inc., a startup company in Vancouver, Columbia, Canada. Redlen's revolutionary production process for advanced semiconductor materials enables a new generation of more accurate, all-digital, radiation-based imaging solutions. Kris is also a founder of Emerging Technologies CMOS Inc. (www.etcmos.com), an organization of hightech events covering communications, microsystems, optoelectronics, and sensors. In his career, Dr. Iniewski held numerous faculty and management positions at the University of Toronto, University of Alberta, SFU, and PMC-Sierra Inc. He has published over 100 research papers in international journals and conferences. He holds 18 international patents granted in the USA, Canada, France, Germany, and Japan. He is a frequent invited speaker and has consulted for multiple organizations internationally. He has written and edited several books for CRC Press, Cambridge University Press, IEEE Press, Wiley, McGraw-Hill, Artech House, and Springer. His personal goal is to contribute to healthy living and sustainability through innovative engineering solutions. In his leisurely time, Kris can be found hiking, sailing, skiing, or biking in beautiful British Columbia. He can be reached at kris. iniewski@gmail.com.

## Editors

Mona Mostafa Hella received a BSc and an MSc with honors from Ain Shams University, Cairo, Egypt, in 1993 and 1996, respectively, and a PhD in 2001 from The Ohio State University, Columbus, Ohio, all in electrical engineering. She is currently an associate professor in the electrical, computer, and systems engineering department at Rensselaer Polytechnic Institute. Prior to that, she has held positions at several companies, including RF Micro Devices and Spirea AB. Dr. Hella was the recipient of the Egyptian Government Award of Excellence (1993), the Micrys Fellowship (1997–1998), and the Texas Instrument Fellowship (1999–2000). She was an associate editor of the IEEE Transactions on Very Large Scale Integration (VLSI) Systems from 2011 to 2014. She has served on the technical program committees for ISCAS, GLS-VLSI and RFIC symposium. She has been a member of the administrative committee of the microwave theory and technique society from 2007 to 2009. She has been a trust leader for the NSF-funded engineering research center on "smart lighting" since 2010 and a Fulbright scholar in 2015. Her research interests include the areas of high frequency circuit design and mixed signal design for energy harvesting and biomedical applications.

**Patrick P. Mercier** received a BSc in electrical and computer engineering from the University of Alberta, Edmonton, Alberta, Canada, in 2006, and an SM and a PhD in electrical engineering and computer science from the Massachusetts Institute of Technology (MIT), Cambridge, Massachusett, in 2008 and 2012, respectively.

He is currently an assistant professor in electrical and computer engineering at the University of California, San Diego (UCSD), where he is also the co-director of the Center for Wearable Sensors. His research interests include the design of energyefficient microsystems, focusing on the design of RF circuits, power converters, and sensor interfaces for miniaturized systems and biomedical applications.

Prof. Mercier received a Natural Sciences and Engineering Council of Canada (NSERC) Julie Payette fellowship in 2006, NSERC Postgraduate Scholarships in 2007 and 2009, an Intel PhD fellowship in 2009, the 2009 ISSCC Jack Kilby Award for Outstanding Student Paper at ISSCC in 2010, a Graduate Teaching Award in Electrical and Computer Engineering at UCSD in 2013, the Hellman Fellowship Award in 2014, the Beckman Young Investigator Award in 2015, and the DARPA Young Faculty Award in 2015. He currently serves as an associate editor of the *IEEE Transactions on Biomedical Circuits and Systems* and the IEEE *Transactions on Very Large Scale Integration* and is a coeditor of *Ultra-Low-Power Short-Range Radios* (Springer, 2015).

## Contributors

#### Saurabh Chaubey

Department of Electrical and Computer Engineering University of Minnesota Minneapolis, Minnesota

#### **Ke-Horng Chen**

Institute of Electrical Control Engineering National Chiao Tung University Hsinchu, Taiwan, Republic of China

#### T. Paul Chow

Rensselar Polytechnic Institute Troy, New York

#### Ramesh Harjani

Department of Electrical and Computer Engineering University of Minnesota Minneapolis, Minnesota

#### Mona Mostafa Hella

Department of Electrical, Computer, and Systems Engineering Rensselaer Polytechnic Institute Troy, New York

#### Sudhir S. Kudva Department of Electrical and Computer Engineering University of Minnesota Minneapolis, Minnesota

#### Yutian Lei

Department of Electrical and Computer Engineering University of Illinois at Urbana–Champaign Urbana, Illinois

#### Zemin Liu

Department of Electrical, Computer and Systems Engineering Rensselaer Polytechnic Institute Troy, New York

#### D. Brian Ma

Department of Electrical Engineering The University of Texas at Dallas Richardson, Texas

#### Patrick P. Mercier

Department of Electrical and Computer Engineering University of California, San Diego San Diego, California

#### Vipindas Pala

Department of SiC Power Devices Wolfspeed, A Cree Company, Research Triangle Park, North Carolina

#### Han Peng

Department of High frequency Power Electronic Lab GE Global Research Niskayuna, New York

#### Robert Pilawa-Podgurski

Department of Electrical and Computer Engineering University of Illinois at Urbana–Champaign Urbana, Illinois

#### Loai G. Salem

Department of Electrical and Computer Engineering University of California, San Diego San Diego, California

#### Jason Stauth

Dartmouth College Thayer School of Engineering Hanover, New Hampshire

#### Yi Zhang

Department of Electrical Engineering The University of Texas at Dallas Richardson, Texas

## 1 Efficient On-Chip Power Management Using Fully Integrated DC-DC Converters

Saurabh Chaubey, Sudhir S. Kudva, and Ramesh Harjani

#### CONTENTS

| 1.1 | Introd                    | duction                                           |    |  |  |

|-----|---------------------------|---------------------------------------------------|----|--|--|

| 1.2 | Inductive Converter       |                                                   |    |  |  |

|     | 1.2.1                     | Switch Scaling and Frequency Scaling Architecture | 6  |  |  |

|     |                           | 1.2.1.1 Switch Scaling                            |    |  |  |

|     |                           | 1.2.1.2 Frequency Scaling                         | 11 |  |  |

|     |                           | 1.2.1.3 Integrated Converter                      | 12 |  |  |

|     | 1.2.2                     | Load Current Detection and State Machine          | 13 |  |  |

|     |                           | 1.2.2.1 PWM Transient Speedup                     | 13 |  |  |

|     |                           | 1.2.2.2 Inductive Converter Passives              | 13 |  |  |

|     | 1.2.3                     | Measurement Results                               | 16 |  |  |

|     |                           | 1.2.3.1 Efficiency                                | 16 |  |  |

|     |                           | 1.2.3.2 Transient Response                        | 19 |  |  |

|     |                           | 1.2.3.3 Effect of Temperature                     |    |  |  |

|     | 1.2.4                     | Inductive Converter Summary                       | 22 |  |  |

| 1.3 | Capacitive Converter      |                                                   | 23 |  |  |

|     | 1.3.1                     | Introduction                                      | 23 |  |  |

|     | 1.3.2                     | Partial Charging/Discharging and Efficiency       | 25 |  |  |

|     | 1.3.3                     | Implementation                                    | 27 |  |  |

|     | 1.3.4                     | CC Measurement                                    |    |  |  |

|     | 1.3.5                     | CC Summary                                        |    |  |  |

| 1.4 | Combined Hybrid Converter |                                                   |    |  |  |

|     | 1.4.1                     | Introduction                                      |    |  |  |

|     | 1.4.2                     | Architecture                                      |    |  |  |

|     |                           | 1.4.2.1 Transition Circuits                       |    |  |  |

|      | 1.4.3      | Inductive Converter |                                   | 34 |  |  |

|------|------------|---------------------|-----------------------------------|----|--|--|

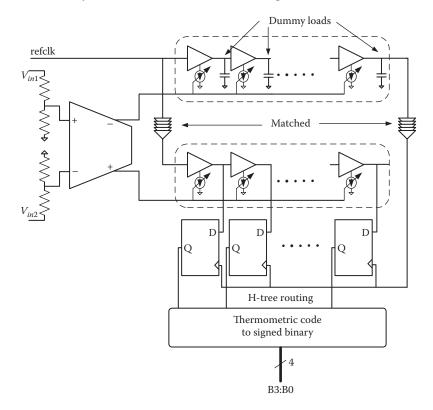

|      |            | 1.4.3.1             | Analog-to-Digital Converter       |    |  |  |

|      |            | 1.4.3.2             | Accumulator                       |    |  |  |

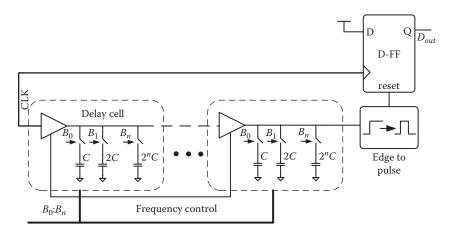

|      |            | 1.4.3.3             | Digital Pulse Width Modulator     |    |  |  |

|      |            | 1.4.3.4             | Efficiency Improvement Techniques |    |  |  |

|      | 1.4.4      | Capaciti            | ve Converter                      |    |  |  |

| ÷    |            | Hybrid (            | Converter Design                  |    |  |  |

|      | 1.4.6      | Hybrid (            | Converter Measurements            |    |  |  |

|      | 1.4.7      | Hybrid C            | Converter Summary                 | 40 |  |  |

| 1.5  |            | •                   | ·                                 |    |  |  |

| Refe | References |                     |                                   |    |  |  |

|      |            |                     |                                   |    |  |  |

#### 1.1 INTRODUCTION

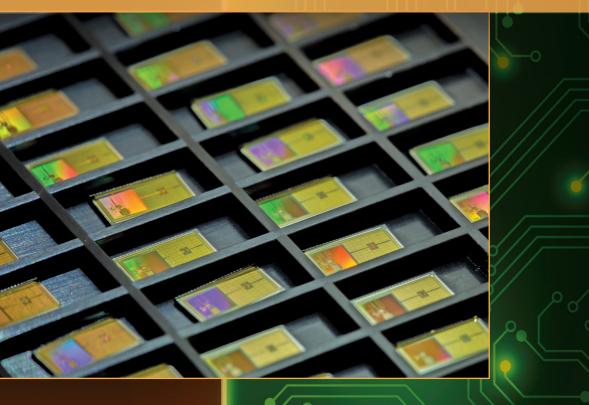

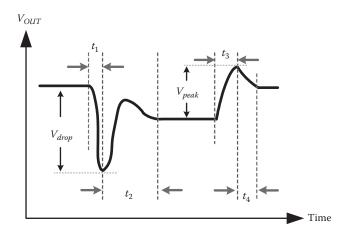

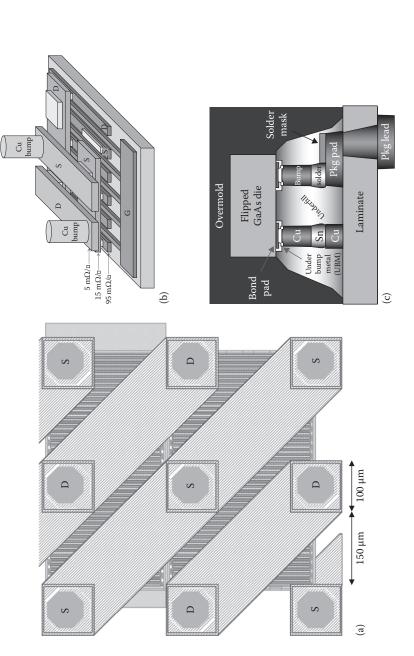

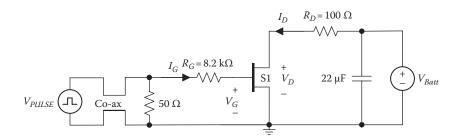

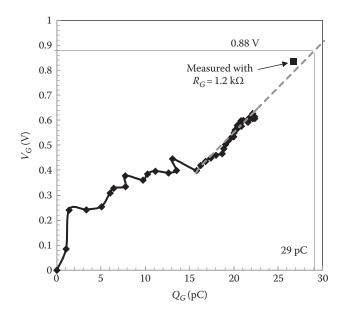

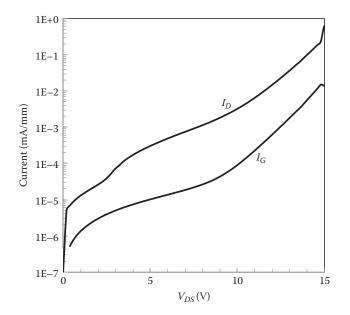

Device scaling has resulted in the implementation of entire systems on a single chip. The increased level of integration has reduced system costs and has proved advantageous from a signal integrity point of view by reducing the number of high-speed signals that need to be routed off-chip. Unfortunately, this higher level of integration has resulted in increased power dissipation in both mobile and stationary devices. Battery life of mobile devices and increased package and cooling costs for stationary devices are the driving forces behind the new focus on methods to reign power dissipation [1]. The supply voltage is one of the primary levers available to control power dissipation [2]. As shown in Equation 1.4, power dissipation in a digital system is approximately proportional to third power of the supply voltage  $(V_{DD}^3)$ . We can consider this by viewing Equations 1.1 through 1.4. The active power dissipation of a digital circuit is given by Equation 1.1, where  $C_{tot}$  is the total digital capacitor switched,  $V_{DD}$  is the supply voltage, and f is the frequency of switching. On-chip power conversion is a complex process especially in battery-operated devices. Figure 1.1a shows a typical teardown of a smartphone that indicates the requirement of different power domains, making it a complete system. It should be noted that the majority of the blocks are of digital or mixed signal type. The demand for small form factor and more features resulted in stacked integrated circuits (ICs) and double stacked printed circuit boards (PCBs). Chemical energy-based batteries are the primary power source in handheld devices. State-of-the-art batteries occupy 20% by volume and 25% by weight. Typical volume density of Li-ion batteries is 400 J/mL and a typical weight energy density of 900 J/g. According to Ref. [3], one word on 3G SMS will cost about 1 J and talking on 3G for 1 minute will cost about 30 J, which means, a best stateof-the-art system solution can provide 30 minutes of 3G talk per gram of lithium battery. These numbers throw light on the problem of energy density of such batteries. Another important aspect of Li-ion is the variation of its voltage with time as depicted in Figure 1.1b. Given a time-variant input voltage profile, we need to provide fairly time-constant voltages involving both buck and boost conversions. So the power conversion system not only requires good static performances (steady-state efficiencies) but excellent dynamic behavior (fast feedback at input and output side).

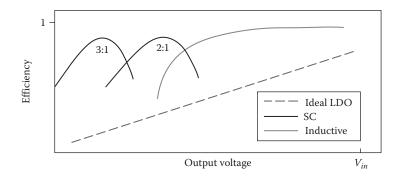

Linear regulators, inductive converters, and switched-capacitor (SC) converters are the primary DC–DC converter arsenal to tackle this problem. Inductive converters

**FIGURE 1.1** (a) Typical smartphone teardown showing different power domains. (b) Discharge profile of Li–ion battery and requirements of different voltage levels by different components.

require high-Q passives that are not always conveniently available in low-cost CMOS processes. Capacitive converters (CCs) are most easily implemented in modern CMOS processes as they primarily only need switches and capacitors. This ability to be easily integrated, finer device geometries, and newer technologies like deep trench capacitors have increased the interest in SC converters. The conversion efficiency of SC converters has traditionally not matched that of inductive converters, but a better understanding of the different topologies and their parasitic losses has slowly increased their efficiencies [4].

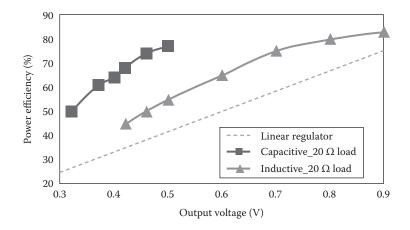

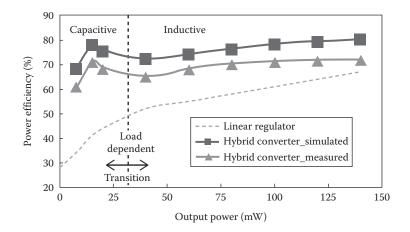

Inductive converters are more efficient at higher loads but show droop in efficiency at lower loads due to switching losses. On the other hand, CCs are easier to implement, perform better at lower loads, but fair poorly at higher loads due to increasing conduction losses. As the final part of this chapter presents, for a wide output range of dynamic voltage scaling (DVS)-based load, a hybrid of inductive and CC is required.

This chapter starts by discussing the design details of inductive converter and its static and dynamic performances. The design that we will discuss is a wide output inductive converter, suitable for DVS-based applications achieving 78% efficiency. Next, we will dwell on the capacitive conversion part of DC–DC power conversion. We will discuss the various loss mechanisms involved in the power conversions. Finally, we will look into the possibility of using a hybrid converter of both inductive

and capacitive nature. In this design, the inductive converter will support the higher loads and the CC will support the lighter loads. Major technical and design details for this chapter have been taken from Refs. [5–7].

#### **1.2 INDUCTIVE CONVERTER**

Device scaling has resulted in the implementation of entire systems on a single chip. The increased level of integration has reduced system costs and has proved advantageous from a signal integrity point of view by reducing the number of high-speed signals that need to be routed off-chip. Unfortunately, this higher level of integration has resulted in increased power dissipation in both mobile and stationary devices. Battery life of mobile devices and increased package and cooling costs for stationary devices are the driving forces behind the new focus on methods to reign in power dissipation [1]. The supply voltage is one of the primary levers available to control power dissipation [2]. As shown in Equation 1.4, power dissipation in a digital system is approximately proportional to third power of the supply voltage  $(V_{DD}^3)$ . We can consider this by viewing Equations 1.1 through 1.4. The active power dissipation of a digital circuit is given by Equation 1.1, where  $C_{tot}$  is the total digital capacitor switched,  $V_{DD}$  is the supply voltage, and f is the frequency of switching

$$P = C_{tot} V_{DD}^2 f \tag{1.1}$$

Likewise, the switching frequency is given by the following equation, where *I* is the current supplied to the circuit:

$$f = \frac{I}{C_{tot}V_{DD}}$$

(1.2)

The on current for the transistor is given by

$$I \propto (V_{DD} - V_T)^{-1-2} \tag{1.3}$$

where  $V_T$  is the threshold voltage. The exponential power term decreases as the short channel effects increase for smaller device dimensions [8]. Substituting Equations 1.2 and 1.3 into Equation 1.1, we arrive at

$$P = C_{tot} V_{DD}^2 \frac{I}{C_{tot} V_{DD}} \propto V_{DD}^{2-3}$$

(1.4)

If the supply voltage is reduced further to operate the circuit in the subthreshold region of operation, further savings can be achieved as the current decreases exponentially in this region as shown by the following equation [8]:

$$I = I_{S} e^{\frac{V_{GS}}{nkT/q}} \left(1 - e^{\frac{-V_{DS}}{kT/q}}\right) \left(1 + \lambda V_{DS}\right) \propto e^{V_{DD}}$$

(1.5)

where

k is the Boltzmann constant T is the absolute temperature in Kelvin  $I_s$  and n are empirical parameters

It is this strong dependence on  $V_{DD}$  that is utilized in DVS-based systems where the supply voltage is dynamically varied depending on the load being executed by the system. When running an application that can be run at a slower speed, the supply voltage and the frequency of operation are scaled down to reduce power dissipation. The advent of multicore and application-specific cores presents the next level of challenges in power management and distribution. Maximum power saving is possible when each of the cores forms separate voltage domains and DVS is applied to them individually [9-11]. This level of fine-grain power control is only possible with individual power regulators for each voltage domain. Off-chip voltage regulators require individual power pins to interface the regulated power to the onchip voltage domains and a few additional pins to interface with the off-chip power converter. The increased pin-count and multiple board-level regulators increase the system cost. Additionally, routing of the multiple separate regulated supply voltages increases the top-level system routing complexity and leads to increased losses in the power delivery network. For DVS to be successful, a fully integrated on-chip power converter appears as an optimal solution, which is the focus of this chapter.

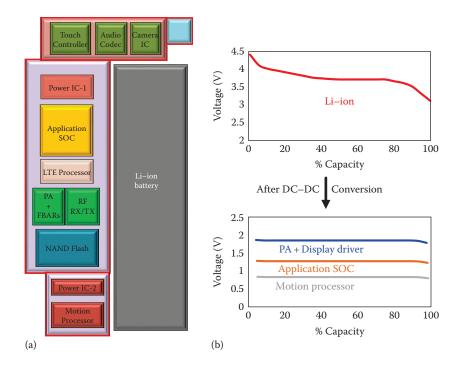

High-efficiency, fully integrated power converters have been demonstrated [12]. However, DVS places additional constraints on the converter. The power consumption of a digital block to which DVS is applied may vary over a wide range, as shown in Figure 1.2a (reconstructed plot using the data in Ref. [13]) for a low-voltage motion estimation accelerator. In this example, the power varies more than four orders of magnitude when the voltage is varied from 0.25 to 1.4 V. As the maximum performance of such application-specific cores is not always required, significant power savings can be achieved if the block voltage can be adapted to the load requirements dynamically. Ultra-DVS [14] using subthreshold operation has demonstrated significant energy savings. The feasibility of subthreshold operation has been shown in a wide variety of circuits [15,16], making it an important component in DVS systems. However, this necessitates a fully integrated DC-DC power converter that operates efficiently over a wide output power range. For testing purposes, we have chosen a ring oscillator (RO) as a representative digital circuit whose V-I profile is shown in Figure 1.2b. This matches the profile of variation of power with voltage of Figure 1.2a. We will use this V-I profile to load the converter, which will be explained in detail in Section 1.2.3.1.

There are different options available for implementing an on-chip voltage regulator, including linear, inductive switching and CCs. The efficiency of an inductive switching regulator depends only on the parasitics of its components, unlike the linear and CCs whose efficiency depends primarily on the conversion ratio [17]. Hence, inductive switching regulators or buck converters can achieve very high efficiencies and thus have been selected for this design. However, their efficiency decreases for lower-output powers. We have made additional improvements to the typical buck converter architecture to overcome these limitations and achieve high efficiency over a wide power range that is necessary for a DVS system.

**FIGURE 1.2** (a) Variation of power with change in supply voltage. (b) Variation of current with change in supply voltage.

The rest of this chapter is organized as follows. Section 1.2 focuses on the individual components and modifications made to the traditional buck converter architecture and summarizes the changes necessary for the integrated converter. Section 1.3 describes the additional changes made to improve the transient response and achieve automatic mode control. Measurement results are presented in Section 1.4, followed by comparison with other works in Section 1.5.

#### 1.2.1 Switch Scaling and Frequency Scaling Architecture

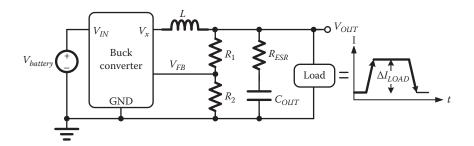

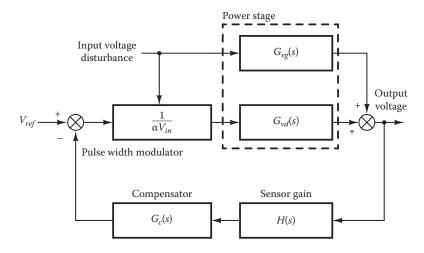

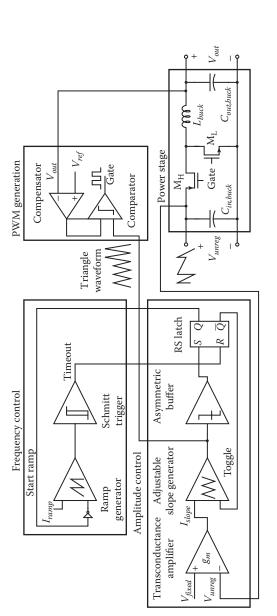

The block-level circuit diagram of a typical buck converter is shown in Figure 1.3. For a fully integrated implementation, the size of the passives that can be implemented

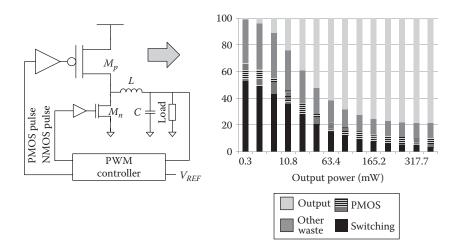

**FIGURE 1.3** A typical buck converter and % power dissipation versus load power for a pulse width modulated buck.

on-chip is limited due to the limited chip area available. The ripple on the output voltage is given by the following equation [18], where *L* and *C* are the inductance and filter capacitance, *D* is the duty cycle for generating the required output voltage, and  $f_{sw}$  is the switching frequency of the buck converter:

$$\Delta V = \frac{D(1-D)V_{DD}}{8LCf_{sw}^2} \tag{1.6}$$

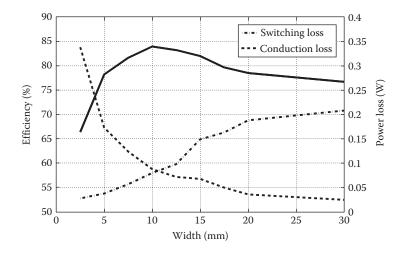

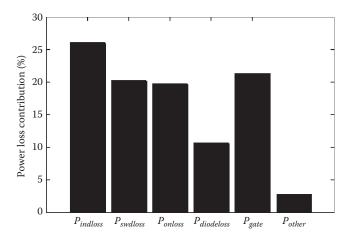

To mitigate the problem of the small size of the passive components, the switching frequency  $f_{sw}$  needs to be increased to meet the output ripple voltage specifications. However, increasing the operating frequency results in increased switching losses in the NMOS and PMOS power devices and their corresponding drivers. In Figure 1.3, we plot the simulated percentage of power dissipated in various components versus the power level for an integrated pulse width modulated (PWM) buck converter. The different components of input power  $P_{in}$  are as follows:

$$P_{in} = P_{out} + P_{sw} + P_{cond,PMOS} + P_{otherloss}$$

(1.7)

where  $P_{out}$  is the power supplied to the load

$$P_{sw} = C_{gate} V_{DD}^2 f_{sw} \tag{1.8}$$

$P_{sw}$  is the power consumed by switching the power device and its respective buffers, where  $C_{gate}$  is the total capacitance switched, which in turn is given by

$$C_{gate} = WLC_{ox} + \frac{WLC_{ox}}{\eta} + \frac{WLC_{ox}}{\eta^2} + \cdots$$

(1.9)

where

W is the width

L is the length of the power devices being switched

$C_{ox}$  is the gate capacitance per unit area

$\eta$  is the fan-out factor in a tapered buffer design

The PMOS and NMOS devices are in triode region of operation during conduction. Hence, the conductive loss in the PMOS device can be approximated by

$$P_{cond,PMOS} = \frac{I_{PMOS}^2}{\mu_p C_{ox}(W_p/L)(V_{DD} - V_{Tp})}$$

(1.10)

where

$\mu_p$  is the hole mobility in PMOS  $W_p$  is the width of the PMOS power device  $V_{Tp}$  is the threshold voltage of the PMOS device  $I_{PMOS}$  is the RMS current in the PMOS power device

The mean square value,  $I_{PMOS}^2$ , is given by  $I_{PMOS}^2 = D^2 I_{load}^2 + I_{PMOS,rms}^2$ , where  $I_{PMOS,rms}$  is the RMS value of  $I_{PMOS,ripple}$ .  $I_{PMOS,ripple}$ , in turn, is given by

$$I_{PMOS,ripple} = \begin{cases} -\frac{D(1-D)V_{DD}}{2Lf_{sw}} + (t-nT)\frac{(1-D)V_{DD}}{L} & \text{for } nT \le t \le (nT+DT) \\ 0 & \text{for } (nT+DT) \le t \le (n+1)T \end{cases}$$

(1.11)

$P_{otherloss}$  is the power lost in the rest of the circuit:

$$P_{otherloss} = P_{cond,NMOS} + P_{cond,L} + P_{sc}$$

(1.12)

where

$$P_{cond,NMOS} = \frac{I_{NMOS}^2}{\mu_n C_{ox}(W_n/L)(V_{DD} - V_{Tn})}$$

(1.13)

is the conductive losses in the NMOS power device, with an electron mobility of  $\mu_n$ , width of  $W_n$ , and  $I_{NMOS}$ . The RMS current through the NMOS power device, which is the sum of  $(1 - D)I_{load}$  and  $I_{NMOS,ripple}$  is given by

$$I_{NMOS,ripple} = \begin{cases} 0 & \text{for } nT \le t \le (nT + DT) \\ \frac{D(1-D)V_{DD}}{2Lf_{sw}} - (t - (n+D)T)\frac{DV_{DD}}{L} & \text{for } (nT + DT) \le t \le (n+1)T \end{cases}$$

(1.14)

$$P_{cond,L} = R_s I_{ind}^2 \tag{1.15}$$

is the loss in the inductor series resistance  $R_s$ , where  $I_{ind}$  is the RMS value of current through the inductor, and

$$P_{sc} = V_{DD}I_{sc} \tag{1.16}$$

is the loss due to the direct current flowing when the PMOS and NMOS devices are simultaneously *on*.

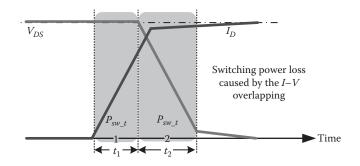

Different techniques have been implemented in this design to reduce each of these wasteful components of power, but special attention is paid to reducing the switching power losses as it forms a significant portion of this wasteful power. At low-output powers, more than 50% of the total input power is dissipated in switching the power devices and their associated buffers. The switching power losses can be reduced by either reducing the capacitance being switched or by reducing the frequency of operation. Both techniques will be applied to our converter.

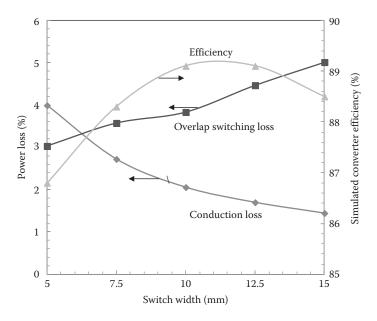

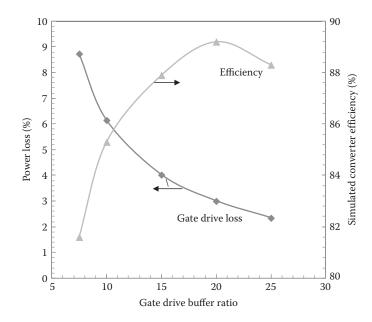

#### 1.2.1.1 Switch Scaling

The size of the switching power device is selected based on the maximum load current supported by the converter. When the load current decreases, using a smaller power device increases the efficiency by decreasing the switching power losses. In order to reduce the capacitance being switched, the power device along with its drivers is split into multiple parts. Depending on the load current requirement, an appropriately sized power device is switched and the remaining power devices and its drivers are completely turned off. By scaling the switch size [19,20], we reduce the switching losses at lower powers, increasing the overall efficiency. In this design, we have only scaled the PMOS power device and its corresponding drivers because the PMOS power devices are much larger than the NMOS power devices because of their smaller current per unit width. Also, in a DVS-based system, higher-output voltages correspond to larger load currents. Higher-output voltages in a buck converter are achieved by turning on the PMOS power device for a longer portion of the switching cycle, which necessitates a larger PMOS power device to reduce the conductive losses. Simulations showed that scaling the NMOS power device provides limited increase in efficiency and only adds to the design complexity. The optimal sizing of the PMOS power device can be calculated by considering both the switching power losses and the resistive losses in the PMOS device:

$$P_{sw\_PMOS} = P_{sw} + P_{cond,PMOS} \tag{1.17}$$

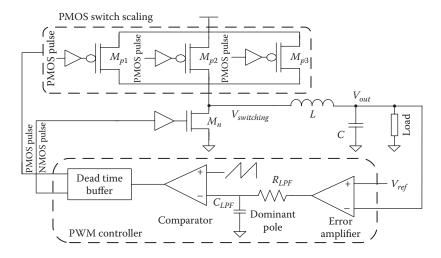

FIGURE 1.4 Constant frequency pulse width modulation mode with switch scaling.

Differentiating  $P_{sw_PMOS}$  with respect to  $W_p$  and setting  $dP_{sw_PMOS}/dW_p = 0$ , the optimum switching transistor width can be calculated as

$$W_{p,opt} = \frac{I_{PMOS}}{V_{DD}C_{ox}} \sqrt{\frac{1}{\mu_p (V_{DD} - V_{Tp}) f\left(1 + \frac{1}{\eta} + \frac{1}{\eta^2} + \cdots\right)}}$$

(1.18)

From Equation 1.18, it is evident that to minimize switching losses and PMOS conductive losses, the width of the PMOS power device needs to be scaled proportionally to the current through the PMOS power device. The current through the PMOS power device is in turn proportional to load current (and to the duty cycle). In order to cover the entire output load current range, the PMOS power device is split into three parts with widths 2, 6, and 12 mm. Using these devices, effective drive sizes of 2 mm (1×), 8 mm (4×), 14 mm (7×), and 20 mm (10×) are achievable. The NMOS power device is a single 2 mm wide device.

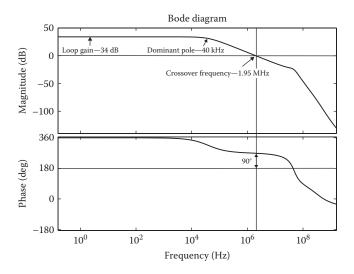

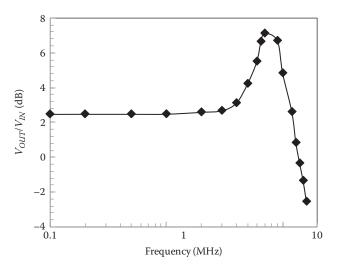

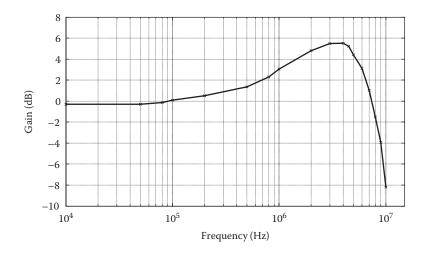

The switch scaled mode uses a fixed frequency-based PWM controller as shown in Figure 1.4. The switching frequency of the PWM-based controller is 300 MHz. The PWM controller uses the dominant pole-based compensation technique with the open-loop dominant pole set at approximately 40 kHz, achieved by an RC low-pass filter. Poles and zeros of the feedback loop path were extracted via circuit simulations and then used to create a MATLAB<sup>®</sup> model of the system to examine system stability [18]. The system simulations showed a phase margin of 90° at a gain crossover frequency of 1.95 MHz as shown in Figure 1.5. A large phase margin was used in this design to ensure stability of the system even after process variations. The dead time buffer following the comparator is used to reduce the  $P_{sc}$  component of the wasteful power. A tapered buffer design has been used to drive the NMOS and PMOS power devices with a fan-out factor of 8.

#### 10

FIGURE 1.5 Bode plot for full system MATLAB<sup>®</sup> simulation of the converter.

#### 1.2.1.2 Frequency Scaling

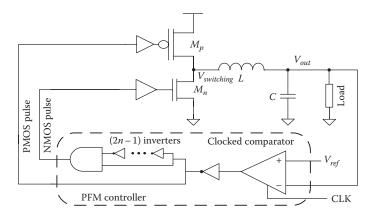

System-level simulations show that though switch scaling achieved efficiency improvements at high and medium output powers, the conversion efficiency was still low at lower-output powers. To combat this problem, we perform automatic frequency scaling at the lowest output powers to further increase the efficiency. Frequency scaling is implemented by operating the converter in pulse frequency modulation (PFM) mode. In this mode, when the output voltage dips below the reference voltage, the PMOS power device is turned *on* to charge the filter capacitor, which provides the load current. The NMOS power device is turned *on* for a short period of time after turning *off* the PMOS device to discharge the inductor. The feedback path uses a clocked comparator to sample the difference between the output voltage and the reference voltage and generates the switching pulses based on this difference as shown in Figure 1.6.

FIGURE 1.6 Frequency scaling using pulse frequency modulated controller.

Depending on the load current, the frequency at which the power devices are switched changes as shown in the following equation, where  $f_{PFM}$  is the switching frequency of the power devices in PWM mode and  $\Delta V$  is the ripple on the output voltage:

$$f_{PFM} = \frac{I_{load}}{C\Delta V} \tag{1.19}$$

The converter here operates in discontinuous conduction mode where both the PMOS and NMOS switches are *off* simultaneously for a part of the clock period. This mode of operation can only support low load currents because of the small size of the filter capacitor that provides the load current when both the PMOS and NMOS power devices are *off*. During this mode of operation, the width of the PMOS and NMOS devices are fixed at 2 mm each.

#### 1.2.1.3 Integrated Converter

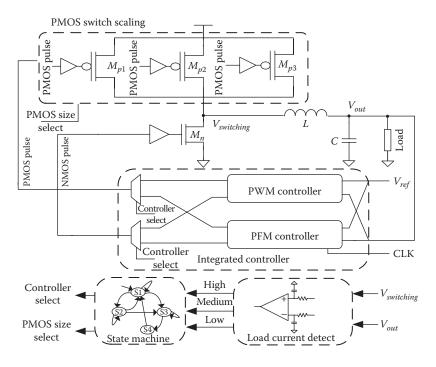

In order to obtain high efficiency over the entire output power range, the proposed converter operates in single-phase PWM mode at high-output powers and in PFM mode at low-output powers [21]. A block diagram for the multimode integrated converter is shown in Figure 1.7. A state machine, discussed in more detail in Section 1.2.2, selects the appropriate mode of operation—PWM or PFM and the appropriate size PMOS

FIGURE 1.7 Integrated converter with switch scaling and frequency scaling.

power device in that particular mode. When the output power is high, all the three switches are operational in the PWM mode (PWM-10X). At medium-output powers, the 12 mm switch along with its driver chain is switched *off* and the other two operational switches, with a combined size of 8 mm (PWM-4X), provide the output power. At low-output powers, only the 2 mm switch is functional in the PFM mode (PFM-1X).

In order to conserve power when one of the controllers is operational, the other controller is completely turned *off*. The PWM controller is turned *off* by shutting off the current sources and PFM mode is turned *off* by gating the clock to the clocked comparator.

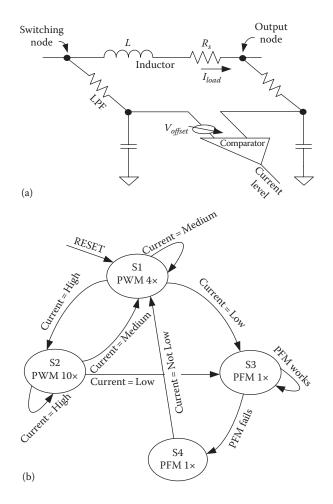

#### 1.2.2 LOAD CURRENT DETECTION AND STATE MACHINE

As shown in Equation 1.18, the optimum size of the PMOS switch is decided by the load current. Hence, in order to select the optimum size of the PMOS power device, a method to sense the current in the load is necessary. Addition of any resistance in the load current path for the purposes of current sensing results in additional losses and reduces efficiency. Hence, we make use of the parasitic series resistance of the inductor to detect the current as shown in Figure 1.8a. The DC voltage drop across the inductor is directly proportional to the load current. The voltage across the inductor. Based on this measurement, current consumption is deduced and the detector logic generates a current-level signal that takes on three discrete values—high, medium, or low—to be used by the state machine. Temperature and process variations can cause the inductor DC resistance to vary, leading to erroneous current-level signals. We compensate for this variation by altering the variable offset in the comparator generating the current-level signals. This variable offset signal can be generated with the help of on-chip temperature sensors [22].

In this prototype chip, a simple one-hot encoding-based state machine, shown in Figure 1.8b, operates the converter in three states: PWM-10X, PWM-4X, and PFM-1X modes. (For testing purposes, the state machine can be bypassed to operate the converter in additional states: PWM-7X and PWM-1X.) The state machine operates at a low-frequency dissipating minimal power.

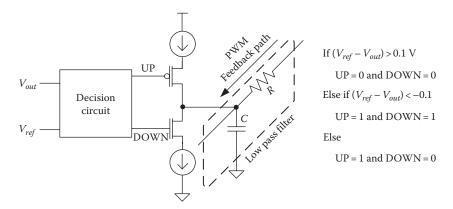

#### 1.2.2.1 PWM Transient Speedup

The PWM mode controller uses dominant pole compensation in the feedback loop. Because of the small bandwidth required to meet the stability criteria, the transient response is very slow. In order to speed up the transient response, current sources are added to charge the low-pass filter node when a large difference between the reference voltage and the output voltage is detected as shown in Figure 1.9. Under normal condition, the current sources are turned off and do not affect the controller. The algorithm implemented in the decision circuit is also shown in Figure 1.9.

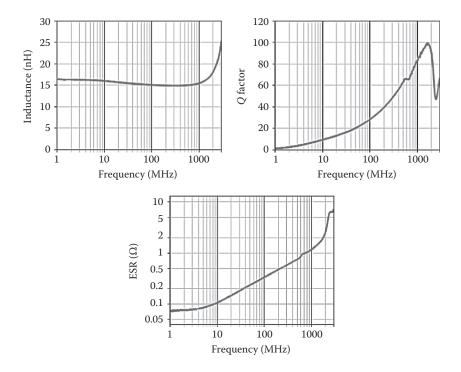

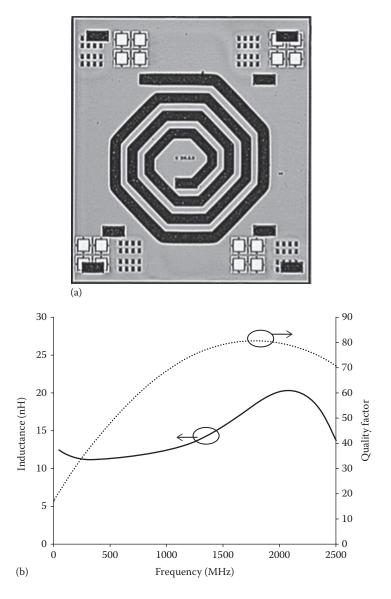

#### 1.2.2.2 Inductive Converter Passives

In our design, all the passive components required in the converter are implemented on-chip. These components occupy a large area and also affect the overall efficiency of the converter. Hence, on-chip passives need to be custom-designed to reduce the

FIGURE 1.8 (a) Current detection circuitry. (b) State machine for automatic mode change.

FIGURE 1.9 Pulse width modulated speedup circuit and decision circuit algorithm.

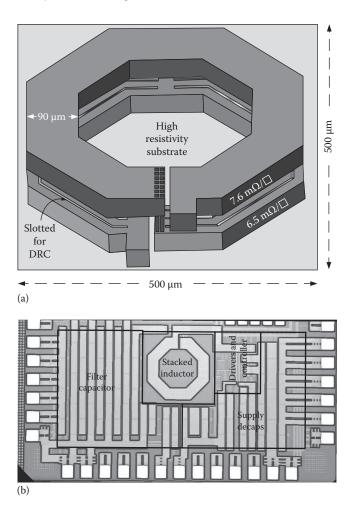

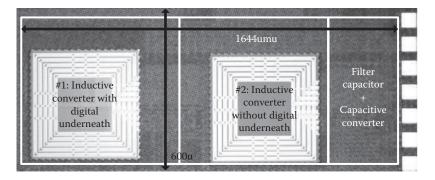

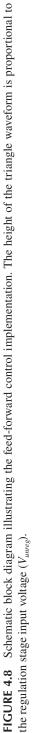

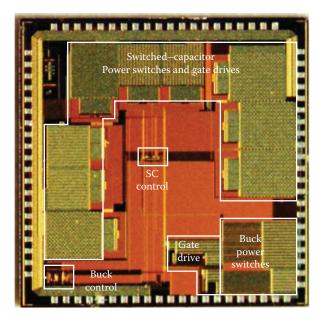

**FIGURE 1.10** (a) Layout of the stacked inductor fabricated. (b) Chip micrograph of the wide output range DC–DC converter.

area as well as to minimize the associated parasitics, which reduce the efficiency. The  $P_{cond,L}$  component of the wasteful power is directly proportional to the series resistance of the inductor (and the square of the inductor RMS current) and needs to be minimized. A custom-stacked inductor using the top two low-resistivity metal layers was designed as shown in Figure 1.10a. The inductor occupies an area of 500 µm × 500 µm.

Simulations of the inductor (with 90  $\mu$ m wide metals) placed over high-resistivity substrate in ADS momentum show an inductance of 2 nH and series resistance of 0.245  $\Omega$  at DC [23]. Only the bottom metal needed to be slotted to meet CMP DRC rules. The top metal was not slotted to reduce series resistance. The filter capacitor is of size 5 nF and effective series resistance (ESR) of 74 m $\Omega$  and is constructed using dual-MIMcaps and MOScaps stacked to conserve area.

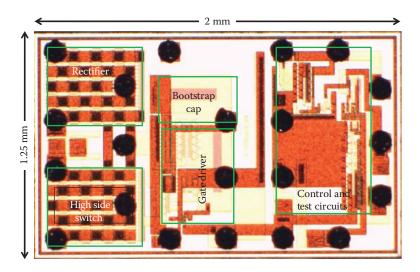

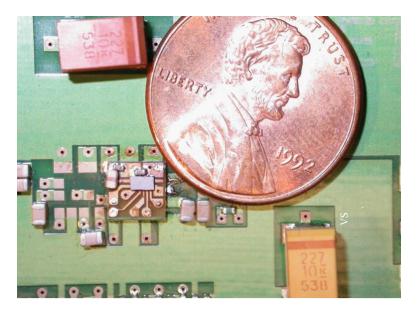

#### **1.2.3 MEASUREMENT RESULTS**

The prototype design was implemented in IBM 130 nm CMOS process. Figure 1.10b shows the die microphotograph of the wide output range DC–DC converter. The converter core occupies an area of 1.13 mm<sup>2</sup>, and the total design area including the decoupling capacitors is 1.59 mm<sup>2</sup>. A supply decoupling capacitor was added conservatively to this prototype due to the large package bondwire inductors and can be eliminated for low-inductance packages including flip-chip designs.

#### 1.2.3.1 Efficiency

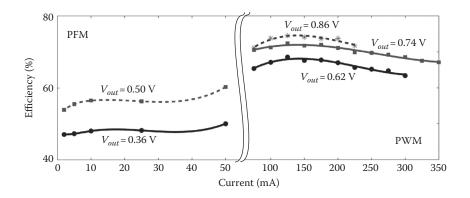

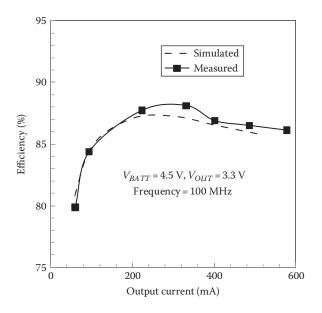

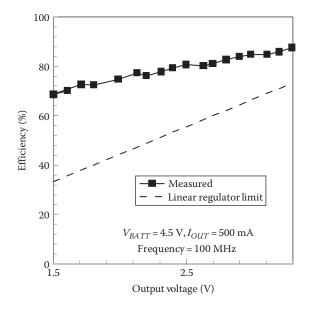

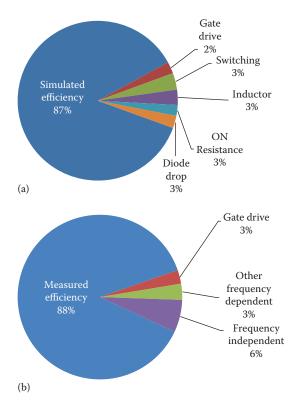

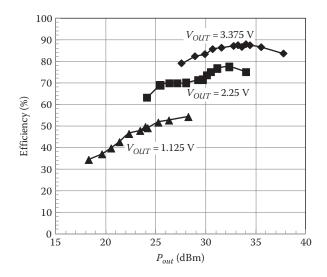

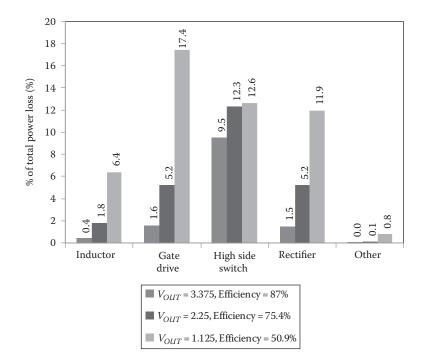

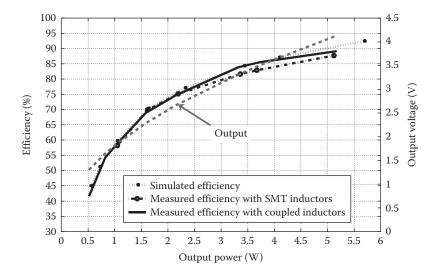

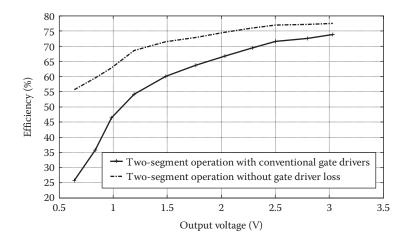

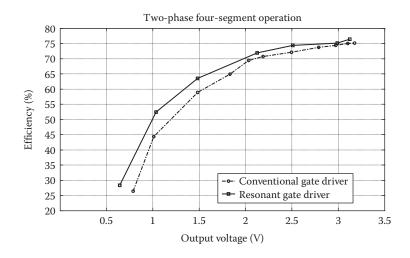

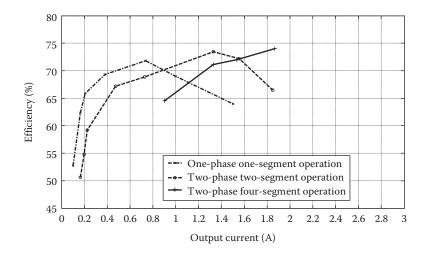

Figure 1.11 plots the measured efficiency of the converter in the PWM mode with a switching frequency of 300 MHz and in the PFM mode for varying output currents at different output voltages. A maximum efficiency of 74.45% is obtained at an output voltage of 860 mV and a load current of 125 mA while the system was operating in the PWM-4X mode. The maximum power supplied by the converter is 266 mW. In the PFM mode, the efficiency varies from 60.8% to 42.8%. The clock generation block (a RO) used during the PFM mode consumes 490  $\mu$ W of power. Our efficiency estimate excludes this power as we assume the presence of a system clock. However, if we include this power, the low-end efficiency reduces from 42.8% to 32.3% but it has minimal effect at higher powers.

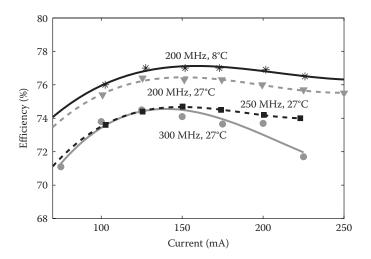

The system was designed for a switching frequency of 300 MHz. With a few adjustments in the reference current, the system was also made to operate in the PWM mode with switching frequencies of 250 and 200 MHz for evaluation purposes. The efficiency of the converter for an output voltage of 0.86 V and varying load currents is shown in Figure 1.12 for different operating frequencies and ambient temperature conditions. The maximum efficiency at 200 MHz and 27°C ambient temperature is 76.4%. The maximum efficiency increased to 77% when the ambient temperature around the chip was reduced to 8°C. (The effect of temperature and its significance on the design is explained in Section 1.2.3.3.) The improved efficiency at 200 MHz is largely a result of a reduction in switching losses.

**FIGURE 1.11** Efficiency of the converter in pulse width modulated and pulse frequency modulated modes for different output voltages.

**FIGURE 1.12** Converter efficiency for different switching frequencies  $V_{out} = 860 \text{ mV}$ .

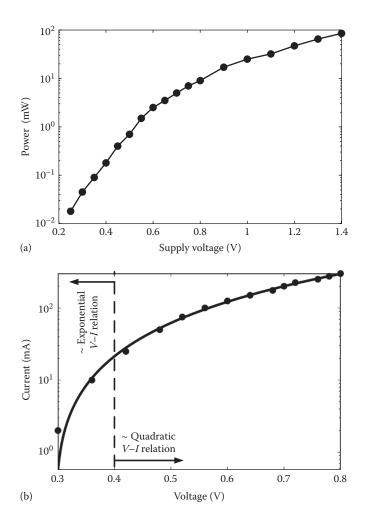

As discussed earlier, one of the motivations for this converter architecture was to supply power to digital DVS-based systems. In the case of digital systems, the current has a quadratic relation with supply voltage in strong inversion and an exponential relation with supply voltage in the subthreshold region of operation. Figure 1.13 shows the current consumption profile for a group of ROs, which is chosen as a representative digital circuit, when the supply voltage is varied. The region of operation when the RO circuit operates in the subthreshold region has been zoomed-in and plotted on a logarithmic scale. The power consumption varies from 0.6 mW at 0.3 V to 240 mW at 0.8 V, that is, a variation of 400× for a supply voltage variation of 2.6×. Here, both the output voltage and load current of the converter are being simultaneously varied, which results in the variation of power over this wide range.

**FIGURE 1.13** V–I profile of ring oscillator and efficiency of the converter for the V–I profile shown.

Figure 1.13 shows the efficiency of the converter when the just discussed load profile is loading the converter. The mode that provides the best efficiency is manually selected for testing purposes and plotted. At higher powers, the best efficiency is obtained when all the PMOS devices are switching (i.e., all the PMOS transistors are needed to supply the necessary current). But as the current consumption reduces, a smaller PMOS device provides better efficiency by reducing the switching losses. When the output power reduces further, the PFM mode with the minimum PMOS device becomes the most efficient architecture by effectively lowering the switching frequency, and thereby further cutting down the switching losses. For comparison purposes, the theoretical efficiency for a linear regulator is also plotted. Our converter performs better than the linear regulator at all output powers. Ripple in the output voltage is also shown at the corresponding output powers. We note that the ripple is fairly constant in the PWM mode and rises slightly as we reduce the load in the PFM mode due to the effective reduction in the switching frequency.

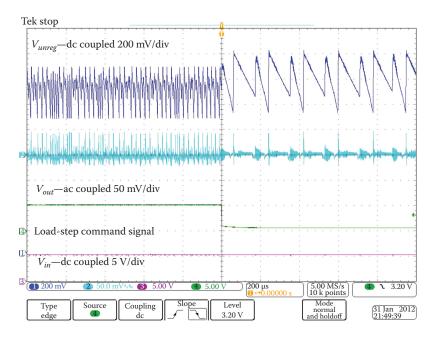

Ripple on the output voltage in the PWM mode at 300 MHz is shown in Figure 1.14a. We suspect that the high-frequency artifacts seen on the top graph of the PWM mode

**FIGURE 1.14** (a) Output voltage ripple in pulse width modulation. (b) Output voltage ripple in pulse frequency modulation.

## 18

are due to the reference square wave signal that is used in the ramp generation, which is buffered using a chain of inverters that is attached to the converter power supply. The current drawn by these buffers at different time instances, due to the individual inverter delays, during their transition results in high-frequency noise on the supply, which rides on top of the actual PWM ripple. When this high-frequency content is filtered out using a 600 MHz filter, the effective ripple on the output voltage reduces to 16 mV. The ripple on the output voltage in the PFM mode is shown in Figure 1.14b. As can be seen in this figure, the high-frequency ripple artifacts are absent in the PFM mode as the ramp generation unit is turned off. The output voltage is 750 mV for the PWM mode and 375 mV in the PFM mode. To get an enlarged view of the ripple on the output voltage, the signal was AC coupled to the oscilloscope and hence the lack of DC information. Also, please note that the timescale in the PFM mode is much larger than the timescale in the PWM mode because of the decrease in switching frequency with reduced load. As shown in Figure 1.12, higher efficiency can be achieved by reducing the switching frequency but reduction in switching frequency also results in increased ripple in the output voltage. Measured unfiltered ripple voltages at 200, 250, and 300 MHz are 46.2, 37.2, and 28.5 mV, respectively. Likewise, measured filtered (using a 600 MHz filter) ripple voltages at 200, 250, and 300 MHz are 31.8, 24.7, and 16 mV, respectively. The filtered ripple voltage values match the predicted values (Equation 1.6) reasonably well. The deviation of the unfiltered ripple voltage values can be attributed to high-frequency content injected by the buffers in the ramp signal generator.

Table 1.1 shows the switching + controller power in the different modes of operation. When operating in the PWM mode, the switching (+ controller) power component varies only with the size of the PMOS transistor and the associated driver chain. But in the PFM mode as the switching frequency changes, the switching power component changes even though the PMOS switch size is constant.

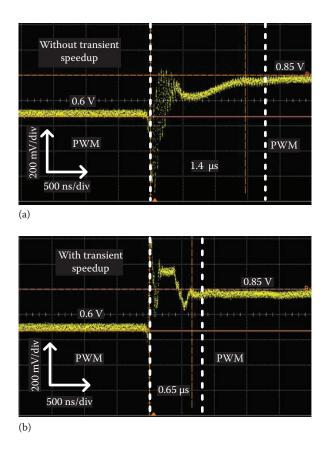

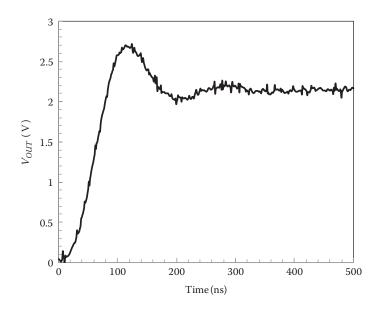

# 1.2.3.2 Transient Response

The transient response when switching from one reference voltage to another in the PWM mode with transient speedup turned off is shown in Figure 1.15a. Transition time for the output voltage to switch from 0.6 to 0.85 V is measured to be 1.4  $\mu$ s.

| TABLE 1.1                                       |  |

|-------------------------------------------------|--|

| Switching + Controller Power in Different Modes |  |

|      | PMOS Transistor<br>Size (mm) | Switching + Controller |          |  |

|------|------------------------------|------------------------|----------|--|

| Mode |                              | Power Loss in mW       |          |  |

|      |                              | Simulated              | Measured |  |

| PWM  | 20 (10×)                     | 17.74                  | 24.5     |  |

| PWM  | 14 (7×)                      | 12.6                   | 17.4     |  |

| PWM  | 8 (4×)                       | 8.44                   | 11.7     |  |

| PWM  | 2 (1×)                       | 3.84                   | 4.32     |  |

| PFM  | 2 (1×)                       | 0.43-2.077             | 0.6–4.7  |  |

**FIGURE 1.15** Transient response in pulse width modulated  $\rightarrow$  pulse frequency modulated mode with and without speedup.

The transition time with speedup enabled was measured to be 0.65  $\mu$ s as shown in Figure 1.15b, achieving an effective speedup of >2X. The transition from 0.85 to 0.6 V was measured to be 0.9  $\mu$ s for both the cases of with speedup and without speedup. As can be seen, the high  $\rightarrow$  low transition is much faster than the low  $\rightarrow$  high transition, which is the reason that turning on the speedup mechanism had little effect. We see some overshoot and undershoot in the transient response owing to the simple nature of the control system used in this design.

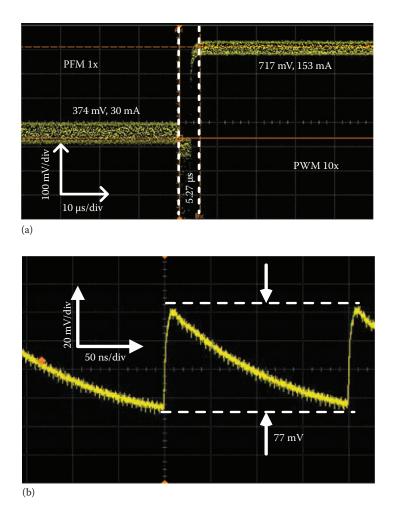

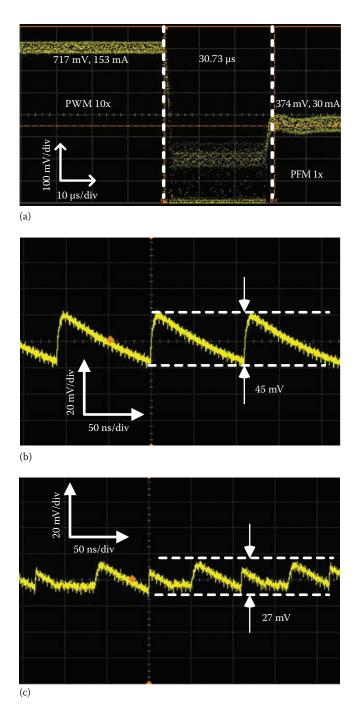

The transient response and adaptive mechanisms were further verified by switching from one extreme state to the other, that is, PWM-10X to PFM-1X and vice versa. Figure 1.16a shows the output voltage switch from 374 to 717 mV. The output current at 374 mV is 30 mA, and the output current at 717 mV is 152.5 mA. The converter is in PFM-1x PMOS for the lower-output power and switches to PWM-10x PMOS for the higher-output power. The time taken to make this transition is 5.27  $\mu$ s. Figure 1.16b shows the transient response in the reverse direction. The time taken to make this transition is 30.73  $\mu$ s. The longer transition time for the down transition is because at the lower-output voltage the converter in the PWM mode fails to track the reference

**FIGURE 1.16** (a) Transient voltage response to output current change from 30 mA to 152.5 mA. (b) Transient voltage response to output current change from 152.5 mA to 30 mA.

voltage, which delays the state machine from making a decision in favor of PFM-1X. Finally, when the converter enters the PFM-1X mode, the converter tracks the reference voltage. This is a particular problem due to an implementation issue in our prototype design that is easily fixed with a small change to the PWM feedback system.

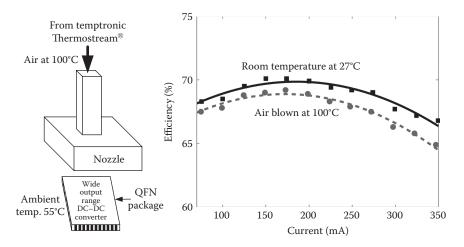

# 1.2.3.3 Effect of Temperature

The converter is a fully integrated implementation intended to supply power to digital circuits. Particularly, in the DVS mode, the temperature under which the converter has to operate may be significantly higher than the ambient temperature because of the heat dissipated by the digital circuitry surrounding the converter. To study the effect of temperature on the efficiency, the ambient temperature around the chip was raised by blowing air at 100°C using the Temptronic Thermostream thermal-inducing

**FIGURE 1.17** Efficiency variation with temperature  $V_{out} = 760 \text{ mV}$ .

system as shown in Figure 1.17. The independently measured ambient temperature around the chip was 55°C. The efficiency reduces with an increase in the temperature, and this reduction in efficiency is greater at higher load currents than at lower load currents as shown in Figure 1.17. An increase in the temperature results in an increase in series resistance of the inductor as well as an increase in the channel resistance of the PMOS and NMOS devices. This increase in the resistance causes larger conductive losses at higher load currents than at lower load currents when the resistive loss forms only a small fraction of wasteful power. The efficiency reduces by about 3% at 350 mA load current as compared to 1% at 75 mA of load current. The reduced efficiency at elevated temperature needs to be taken into account when calculating the total system efficiency in real-world operating conditions.

#### **1.2.4** INDUCTIVE CONVERTER SUMMARY

In this chapter, we have presented a wide output range, fully integrated on-chip power converter for DVS-based applications. To obtain high efficiency over the entire range of output powers, the converter switches between different modes of operation. At higher-output powers, switch scaling with a constant frequency PWM-based mode of operation is used. At low-output powers, a constant switch width but variable frequency-based PFM control is used. Switching between the different modes happens automatically with the converter tracking the output current. The prototype chip supplies output power from 0.6 to 266 mW. The converter achieves a peak efficiency of 77% under reduced temperature and a maximum efficiency of 74.45% over the entire wide power range, which, to the best of our knowledge, is the highest reported range for a fully integrated on-chip design.

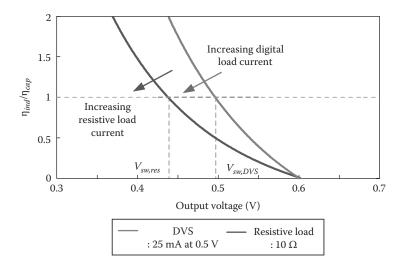

From this discussion, we conclude that we can achieve highly efficient power conversion with fairly less voltage ripple for higher loads. But at lower loads (for DVS application, this means lower voltage), in order to maintain the same absolute

voltage ripple, frequency of operation has to be increased, thus increasing the switching losses. But for lighter loads like around 1 mA and less, the CC performs better. So next we will see the details and design of a capacitive DC–DC converter, highlighting the just discussed observation.

# **1.3 CAPACITIVE CONVERTER**

#### 1.3.1 INTRODUCTION

Reduced power dissipation in integrated systems has become a critical design goal. One of the most effective methods to reduce power dissipation in digital system is to dynamically scale the supply voltage (DVS) based on the load conditions. Further savings in power can be obtained by using multiple independent voltage domains with DVS applied to each one of them. Designing for multiple voltage domains has necessitated that the power converter be fully integrated on-chip to overcome the constraints imposed by limited pin count and routing. Fully integrated inductive converters [6,12], linear regulators, and CCs [17] have been demonstrated.

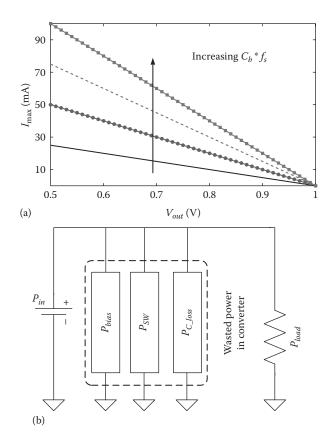

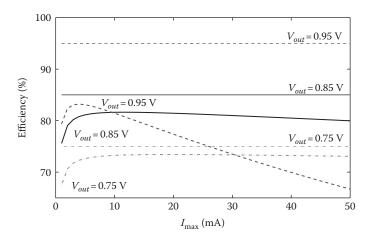

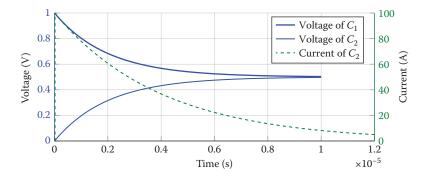

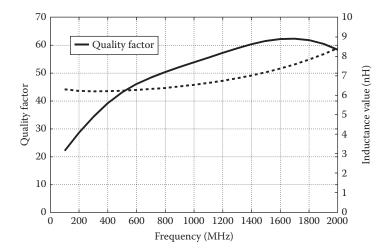

Among these, CCs are particularly well suited for digital CMOS processes as they require only capacitors and MOS transistors as switches. Additionally, CCs can be designed to be highly efficient with their theoretical maximum efficiency given by  $\eta = V_{out}/V_m$  [17], where  $V_m$  is the maximum unloaded voltage of the converter. Hence, maximum efficiency is achieved when  $V_{out}$  is close to  $V_m$ . However, the maximum load current supported by the converter is  $I_{\text{max}} \propto C_b f_s (V_m - V_{out})$ . In order to support the load current,  $C_b * f_s$  has to be appropriately selected. The value of  $C_b * f_s$  increases with an increase in the max load current to be supported by the converter as shown in Figure 1.18a. This results in an increase in the converter losses. The overall converter losses include switching losses  $(P_{SW})$ , losses in the converter core  $(P_{C lass})$ , and fixed loses due to biasing  $(P_{bias})$  as shown in Figure 1.18b. These losses can be modeled to calculate the overall efficiency as has been done for a 1:1 converter in Figure 1.19, where the thin dashed lines indicate the efficiency of the converter core and the thicker lines, the overall efficiency including the switching and bias loss in a 130 nm technology. The efficiency reduction for output voltages close to  $V_m$  is much higher than that for voltages away from  $V_m$  where the efficiency remains flat for varying  $I_{max}$ . Hence, the converter components are selected to optimize the overall efficiency and maintain a flat profile for a wide range of  $I_{\text{max}}$  values. For this design even though 0.95 V has a higher core efficiency, the overall efficiency is lower at higher load currents. However, selecting  $V_{out} = 0.85$  V results in a fairly constant and higher efficiency over the entire range. The loss in efficiency from an ideal converter depends on the converter configuration, including factors such as number of switches in series with the bucket capacitor, the effective overdrive on the gate of switches, etc., and may be more severe for multimode designs. Only the switching component of the loss scales with device technology and is proportional to  $L^2$ , where L is the smallest feature size. For the same load conditions and a smaller technology, the shape of the curves remains similar but the y values increase:

$$\Delta V_{ripple} = \frac{I_{load}}{C_{tank} f_s} \tag{1.20}$$

**FIGURE 1.18** (a) Variation of  $I_{\text{max}}$  with output voltage  $(V_o)$ . (b) Power components breakup for the converter.

FIGURE 1.19 Overall efficiency of the converter for different loads.

FIGURE 1.20 Catalogue of ripple control techniques.

All SC converters have output voltage ripple. However, fully integrated CCs suffer from the presence of significant ripple in the output due to the area-limited size of the tank ( $C_{tank}$ ) or the decoupling capacitor as shown in Equation 1.20. Here for a fixed ripple voltage and a smaller tank capacitor, the switching frequency has to increase. Unfortunately, increasing the switching frequency increases the switching losses and reduces the overall efficiency. For fully integrated CCs, there is a clear chip area versus efficiency trade-off.

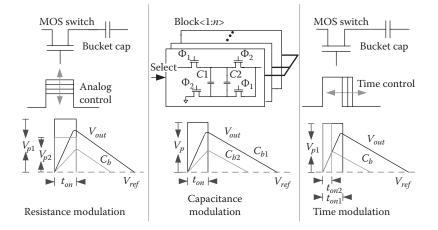

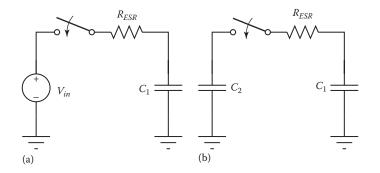

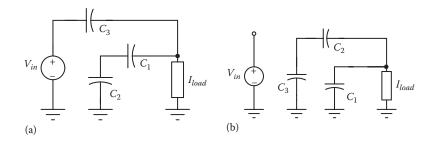

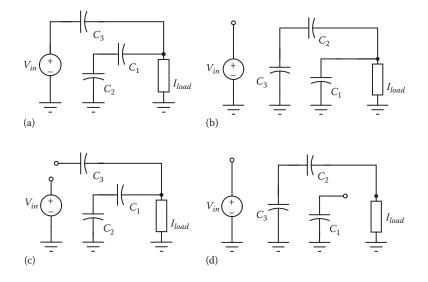

The root cause of the problem is that the bucket capacitor (*C*1 in Figure 1.21) values are selected depending on the maximum load current at the highest output voltage. For other operating conditions, the size of the bucket capacitor is larger than what is actually required. Therefore, when the output voltage or the load current decreases, the tank capacitor is overcharged by the bucket capacitors, resulting in increased ripple. The ripple can be reduced by reducing the amount of charge transferred to the tank capacitor. This can be achieved by modulating the resistance of switches, the size of the bucket capacitor, or the charge/discharge time of the bucket capacitors as shown in Figure 1.20. The first method of modulating the switch resistance requires analog amplifiers and hence is not very convenient from a scaling perspective. In this design, we use capacitance modulation for coarse ripple control and introduce digital bucket capacitor charge/discharge time modulation for fine ripple control both of which are digital in nature and hence suitable for easily scaling from one technology to other.

The power converter is targeted for near threshold to subthreshold voltage operation [14-16] and provides an output voltage in the 0.3–0.5 V range from a 1.2 V input.

#### 1.3.2 PARTIAL CHARGING/DISCHARGING AND EFFICIENCY

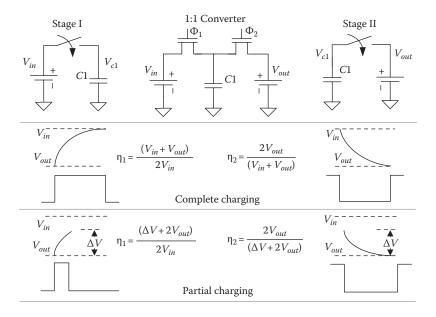

The effect of partial charging/discharging of the bucket capacitors on the efficiency of the converter is illustrated using a simple 1:1 converter in Figure 1.21. Assuming a constant output voltage, the efficiency of the energy transfer in two stages is evaluated,

FIGURE 1.21 Effect of partial charging on efficiency.

that is, from input to the bucket capacitor in stage I and from the bucket capacitor to output in stage II. The total converter efficiency is the product of efficiencies in stages I and II. For the fully charged/discharged case, the bucket capacitor is charged to  $V_{in}$  in stage I, the energy stored in the bucket capacitor in this phase is  $E_{cap1} = C_b (V_{in}^2 - V_{out}^2)/2$ , and the energy supplied by the input source is  $E_{in} = C_b V_{in} (V_{in} - V_{out})$ . In stage II, the bucket capacitor that was charged to  $V_{in}$  is discharged to  $V_{out}$ , the energy supplied by the bucket capacitor is  $E_{cap2} = C_b (V_{in}^2 - V_{out}^2)/2$ , and the energy delivered to the load is  $E_{out} = C_b V_{out} (V_{in} - V_{out})$ . Hence, the efficiency of the converter is  $\eta_1 = E_{cap1}/E_{in} = (V_{in} + V_{out})/2V_{in}$  and  $\eta_2 = E_{out}/E_{cap2} = 2V_{out}/(V_{in} + V_{out})$  in stages I and II, respectively, which results in a overall efficiency of  $\eta = \eta_1 \eta_2 = V_{out}/V_{in}$ .

The same exercise can be repeated for partial charging where in stage I the bucket capacitor is partially charged to  $V_{out} + \Delta V$  instead of  $V_{in}$ . The energy stored in the bucket capacitor in stage I is  $E_{cap1} = C_b(\Delta V^2 + 2V_{out}\Delta V)/2$ , and the energy delivered by the input supply is  $E_{in} = C_b V_{in} \Delta V$ . For stage II, the energy supplied by the bucket capacitor is  $E_{cap2} = C_b(\Delta V^2 + 2V_{out}\Delta V)/2$ , and the energy that is delivered to the output is  $E_{out} = C_b V_{out} \Delta V$ . The overall converter efficiency is  $\eta = \eta_1 \eta_2 = V_{out}/V_{in}$ , where  $\eta_1 = (\Delta V + 2V_{out})/2V_{in}$  and  $\eta_2 = 2V_{out}/(\Delta V + 2V_{out})$ .

The overall efficiency of the converter remains the same in both cases, but the intermediate efficiencies vary. In partial charging, the efficiency of the charging stage is less than that for complete charging. However, the efficiency in the discharging is tage for partially charging is higher than that for complete charging. *Hence, by utilizing partial charging/discharging, the overall efficiency of the converter does not change but the output ripple voltage is reduced*. Effectively, partial charging behaves like a smaller capacitor allowing for larger range of "capacitive modulation."

## 26

#### **1.3.3** Implementation

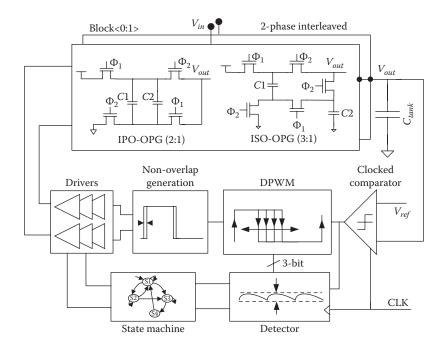

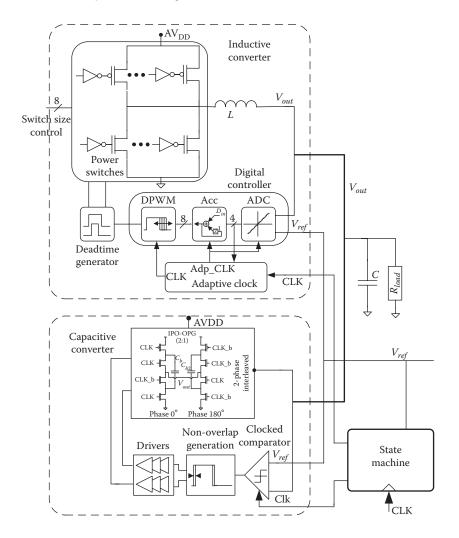

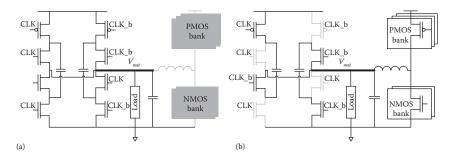

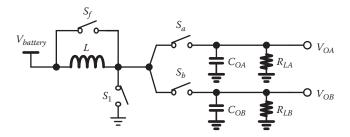

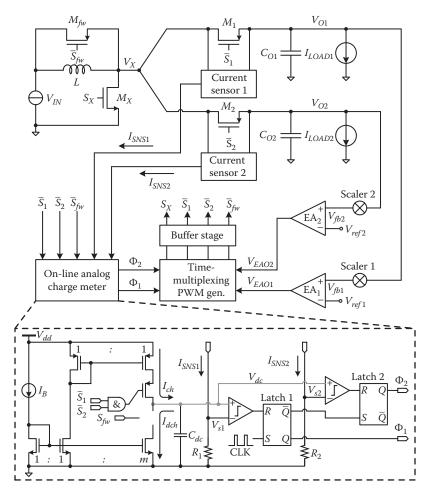

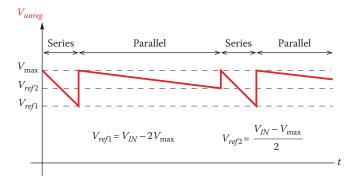

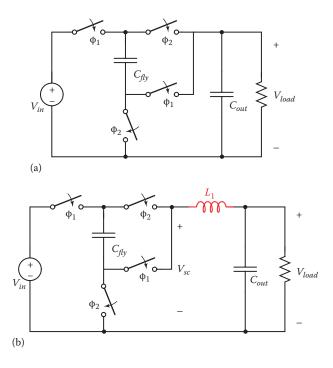

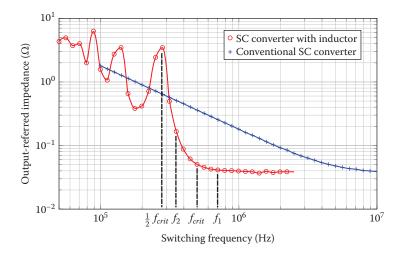

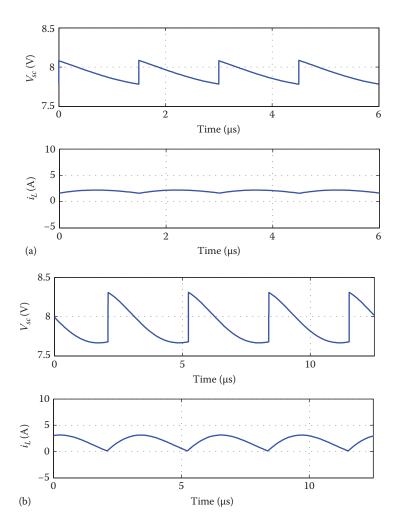

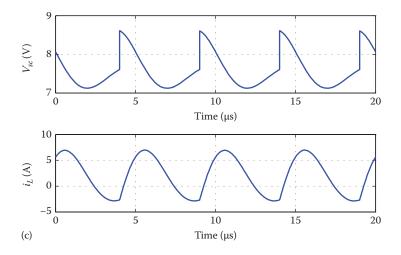

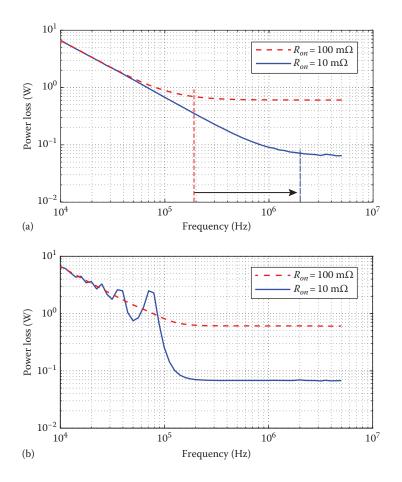

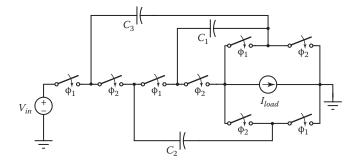

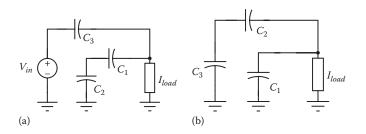

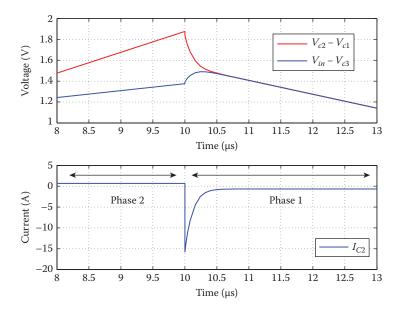

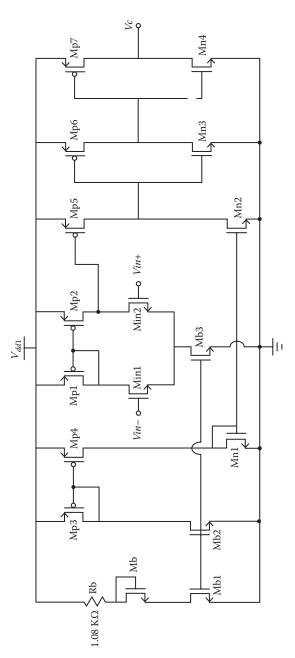

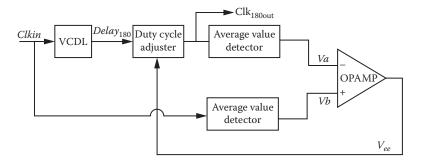

Figure 1.22 shows the block diagram of the fully integrated CC. The converter core uses two phases offset by 180°. Additionally, two CC modes of operation  $(V_m = V_{dd}/2)$ and  $V_m = V_{dd}/3$  are used to achieve high efficiency over the entire output voltage range [17]. In the  $V_m = V_{dd}/2$  mode, the bucket capacitor is connected between the input and output in phase 1 and in parallel with the output in phase 2. Whereas in the  $V_m = V_{dd}/3$  mode, two capacitors are connected in series in phase 1 and then both these capacitors are connected in parallel across the output in phase 2. The switches are arranged so as to reuse the same bucket capacitors in both modes of operations. Two copies of the converter core are connected in parallel. Either both the converter cores are used or only one of them is used to supply the output load. Regulation of the output voltage is achieved by a single bound hysteretic controller that forms the primary control loop. The primary loop changes the frequency of switching of the converter depending on the output voltage and the load current using a clocked converter to compare the output voltage to the reference voltage and initiates switching action when output dips below reference voltage. The switching frequency modifies the effective  $R_{out} = 1/(f_s \times C_b)$  of the converter, thereby achieving output voltage regulation.

A secondary loop is responsible for controlling the ripple on the output voltage. The frequency of oscillation measured using a counter is an indirect measure of the ripple on the output voltage, that is, the ripple increases with reduced frequency, and forms the input to the secondary loop. If the switching frequency is equal to the reference clock

FIGURE 1.22 Fully integrated capacitive converter.

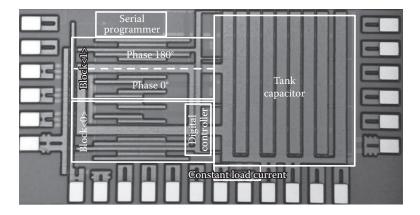

FIGURE 1.23 Die photograph of fully integrated capacitive converter.

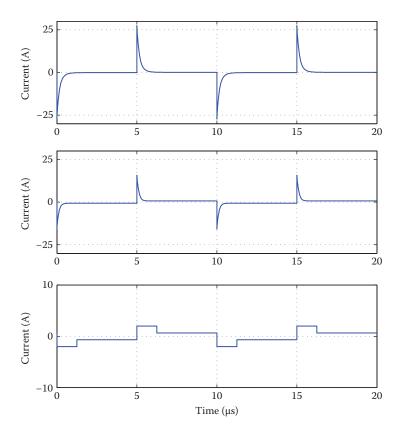

frequency, then both the converter cores are put in use and the pulse width is maximized for both charging/discharging of the bucket capacitors. If the switching frequency is less than 1/6 of the reference frequency, then only one of the converter cores is used and the minimum pulse width is used for charging/discharging the bucket capacitors. For any frequency in between these two limits, the number of converter cores used is retained from the previous cycle and only the charge/discharge time is modified based on the switching frequency. The changes instituted by the secondary loop do have second-order impact on the primary loop as well. Due to the reduced ripple on the output (as a result of less overcharging), the switching frequency set by the primary loop changes. The effective switching frequency of the converter is now set by the interplay between the two loops and varies continuously. The power dissipation of the secondary loop decreases as the load current decreases as it operates at the switching frequency of the converter.

The bucket capacitors are constructed using dual-MIMcaps in order to reduce losses due to the parasitic capacitances in which switches and control circuitry are placed below the bucket capacitors. The total size of the bucket capacitor was 936 pF reused by both converter modes. A 5 nF tank capacitor is built using both dual-MIMcaps and MOScaps for reduced area. The prototype fabricated in IBM's 130 nm CMOS process occupied a total area of 0.97 mm<sup>2</sup> including the tank capacitors and the decoupling cap on the input supply. The die photo of the fully integrated converter is shown in Figure 1.23.

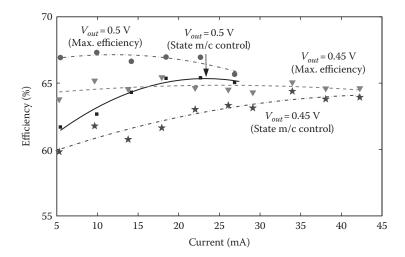

## 1.3.4 CC MEASUREMENT

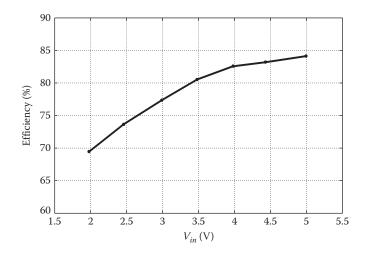

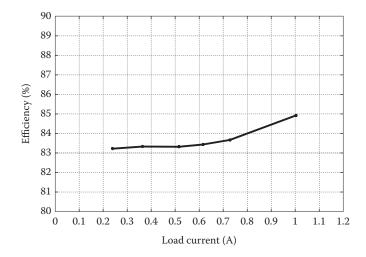

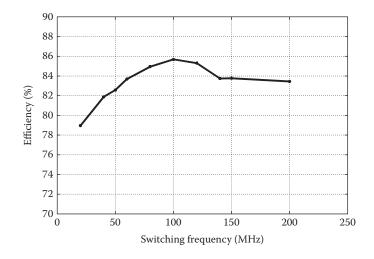

The efficiency of the converter at fixed output voltages and different load currents is shown in Figure 1.24. The converter achieves a maximum efficiency of 70% for  $V_{in} = 1.3$  V and  $V_{out} = 0.5$  V. The max efficiency represents the efficiency of the converter without charge/discharge time modulation and full capacitance switching. When the state machine is enabled, depending on the load conditions an appropriate number of converter cores and charge/discharge time of the bucket capacitors are modulated to reduce the overcharging of the output node. Due to reduced

FIGURE 1.24 Overall efficiency of the converter.

overcharging, the frequency of switching increases slightly as compared to the case where the state machine is disabled. This results in a slight decrease in efficiency due to increased switching loses. With a smaller technology, switching losses will have a lower impact on the overall efficiency and the efficiency decrease due to state machine action is expected to be minimal.

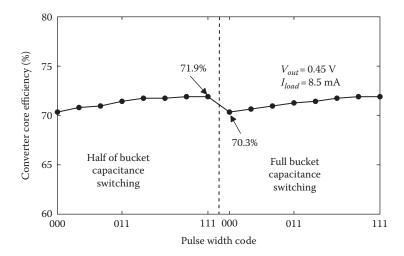

The converter can also be manually controlled to set the number of converter cores to be used and the time for charging/discharging the bucket capacitors can be set to the desired value. Figure 1.25 shows the efficiency of the converter core neglecting the power consumed in the controller and drivers, when charge/discharge pulse width

FIGURE 1.25 Core efficiency of the converter.

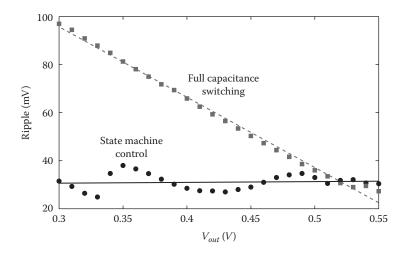

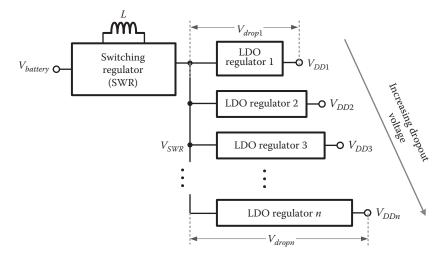

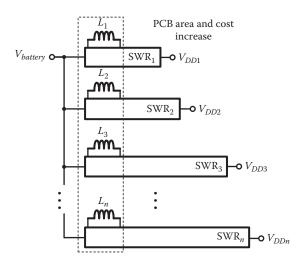

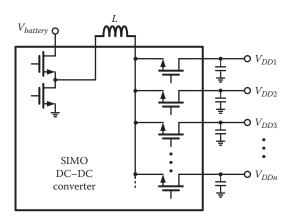

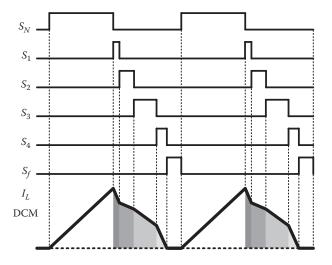

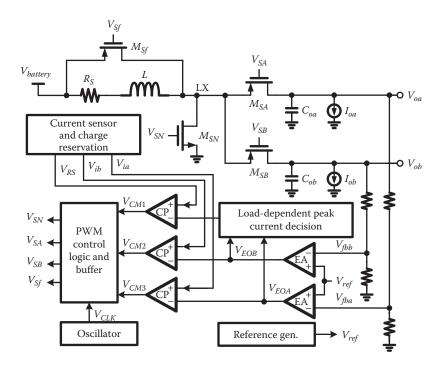

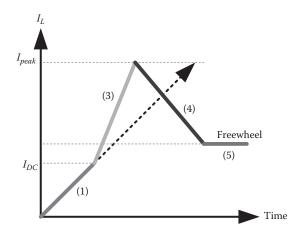

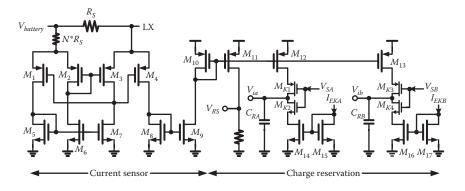

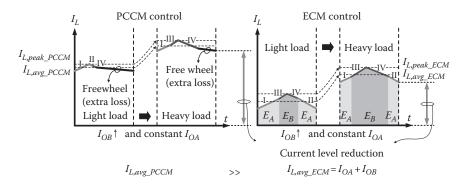

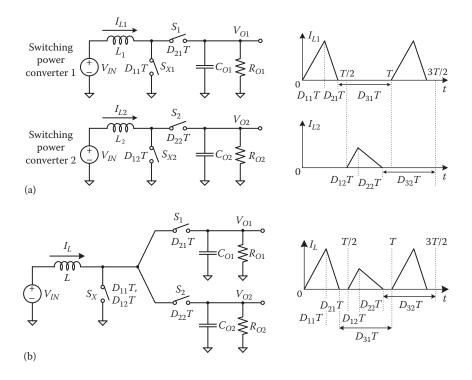

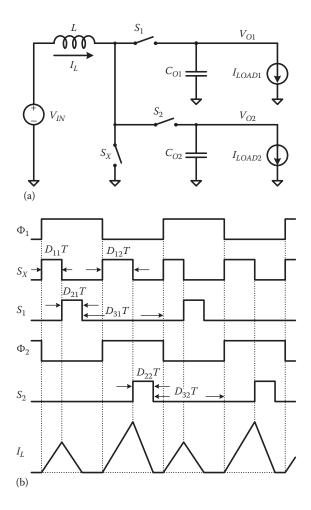

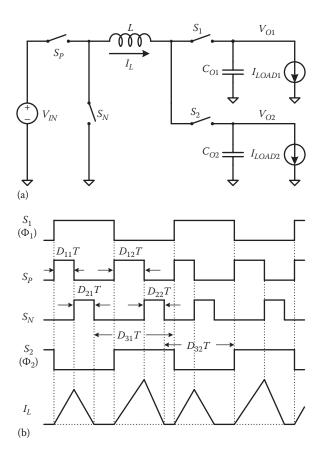

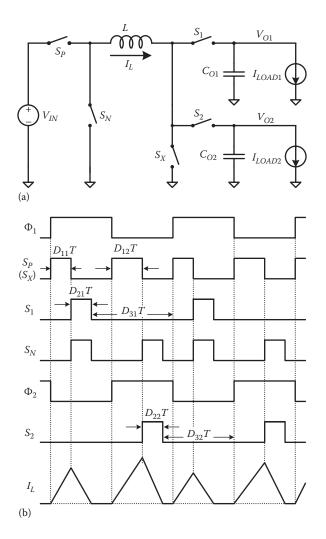

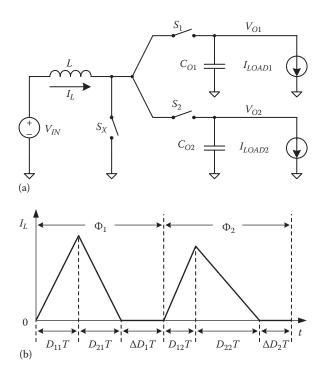

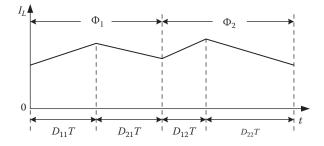

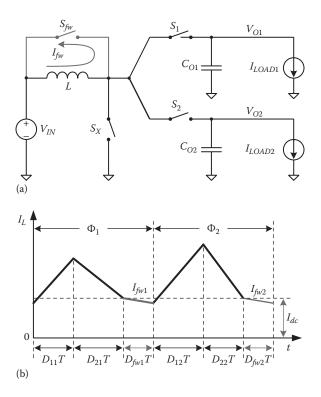

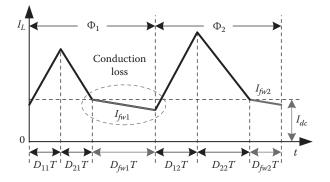

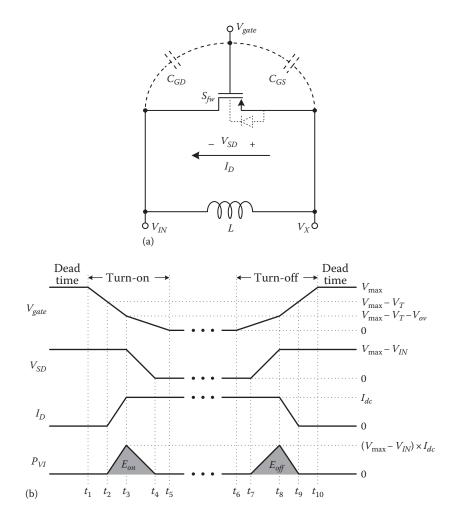

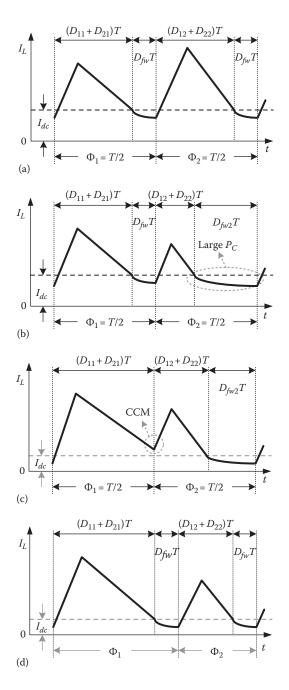

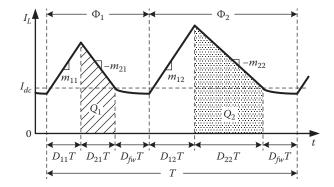

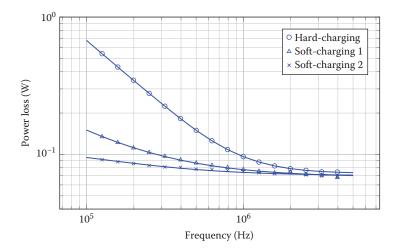

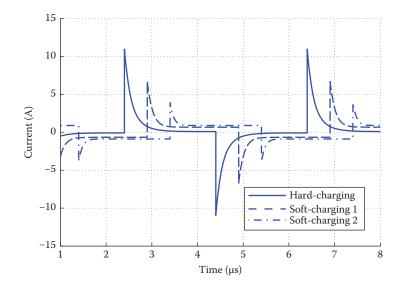

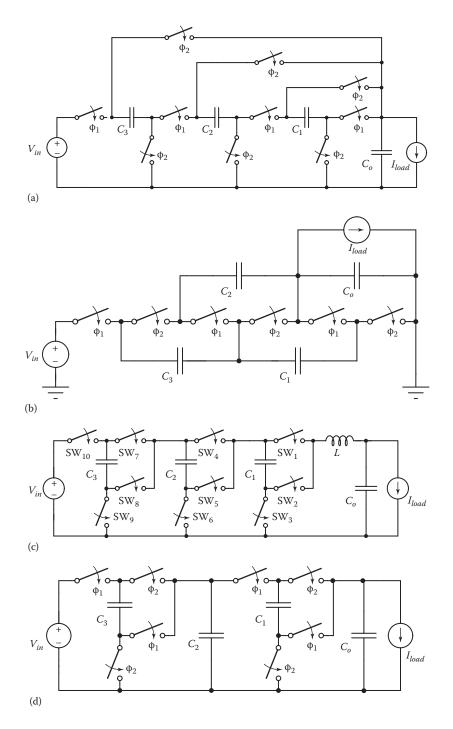

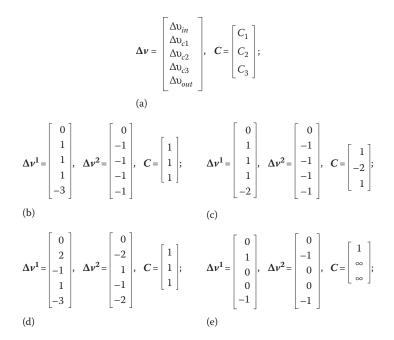

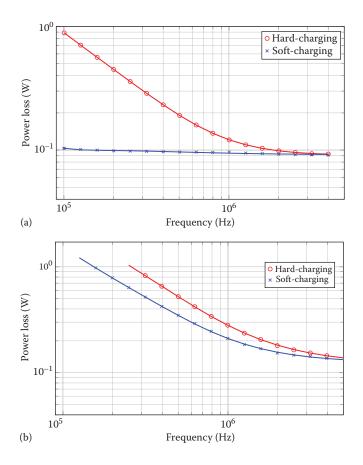

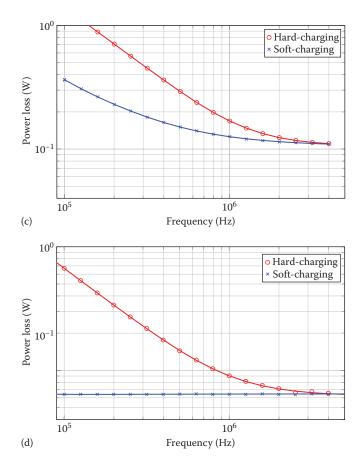

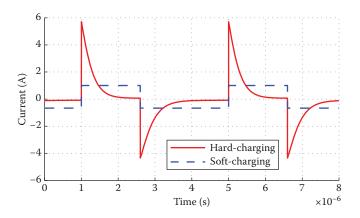

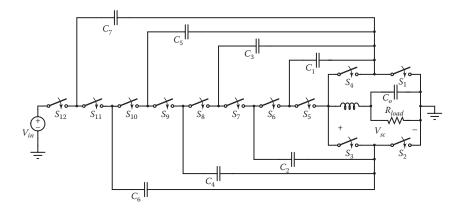

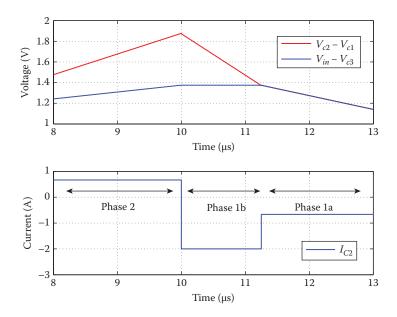

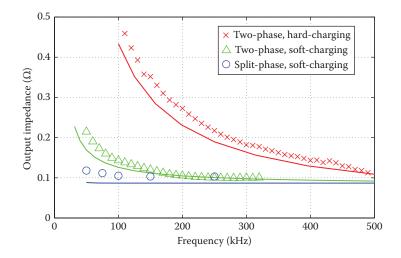

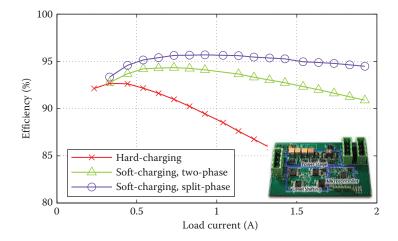

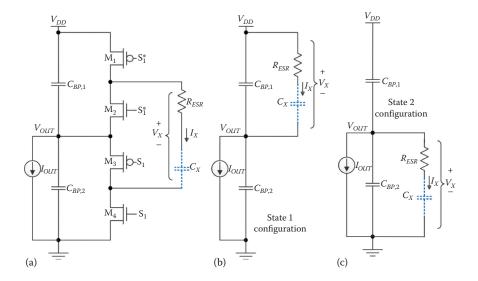

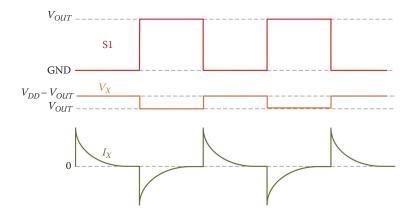

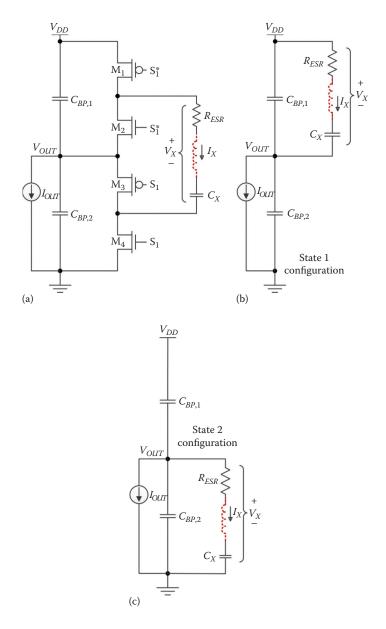

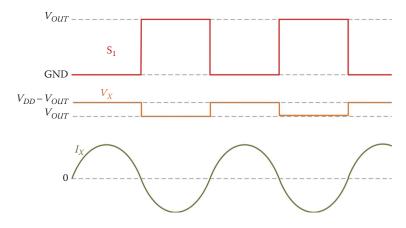

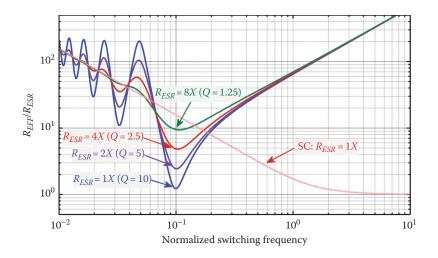

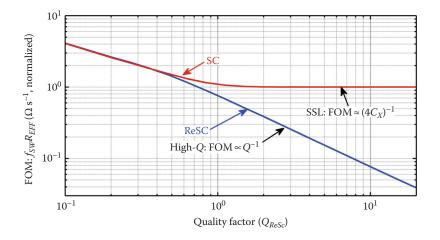

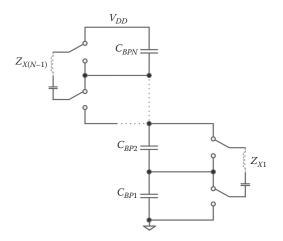

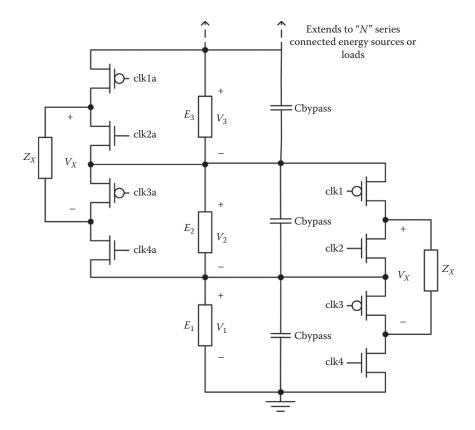

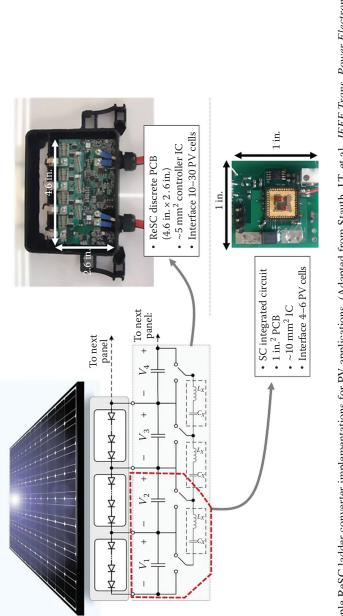

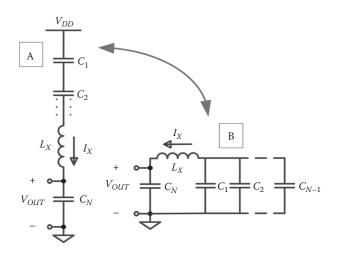

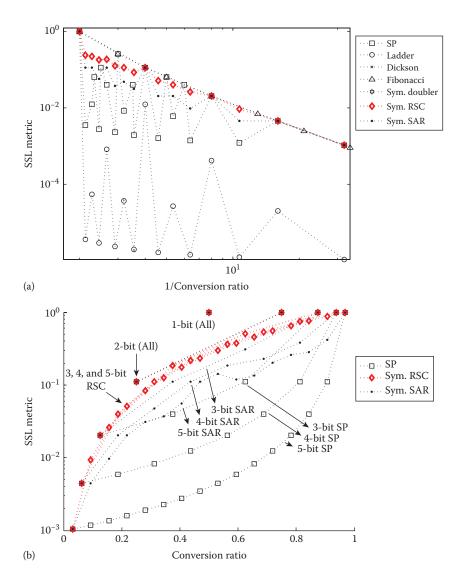

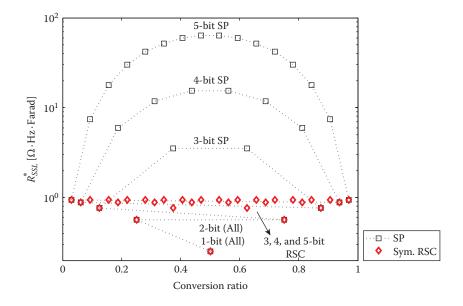

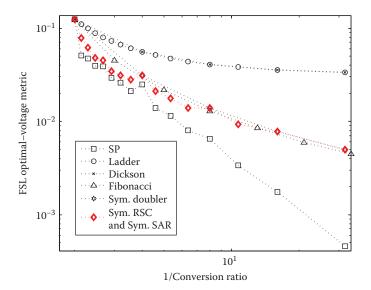

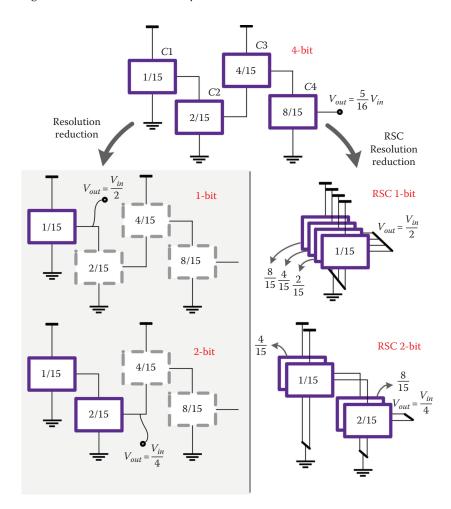

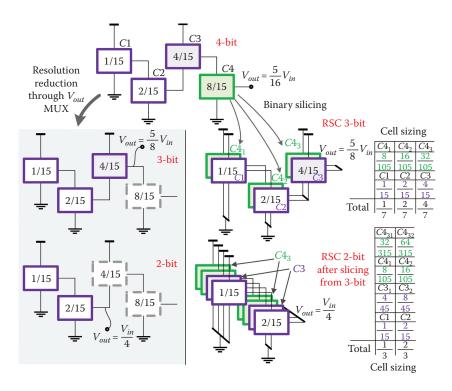

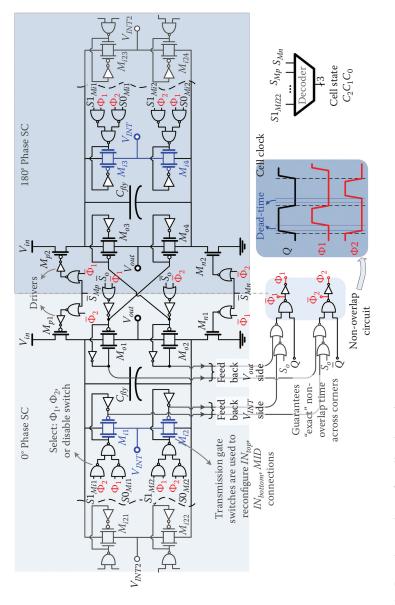

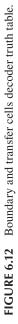

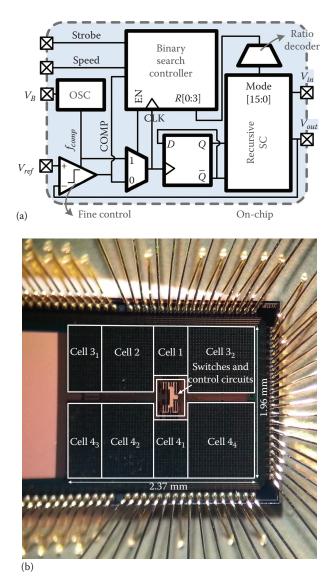

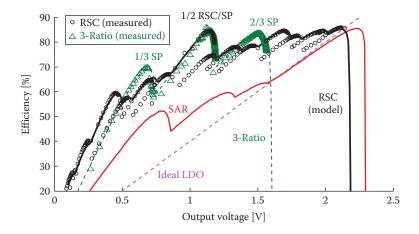

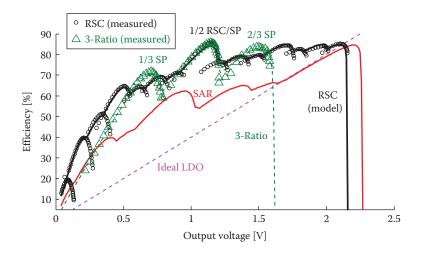

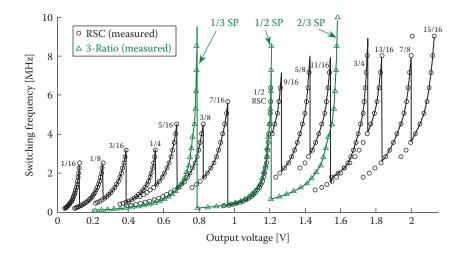

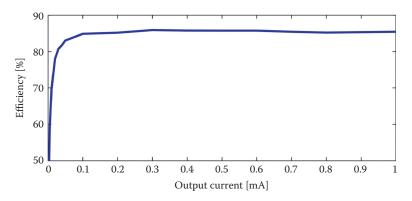

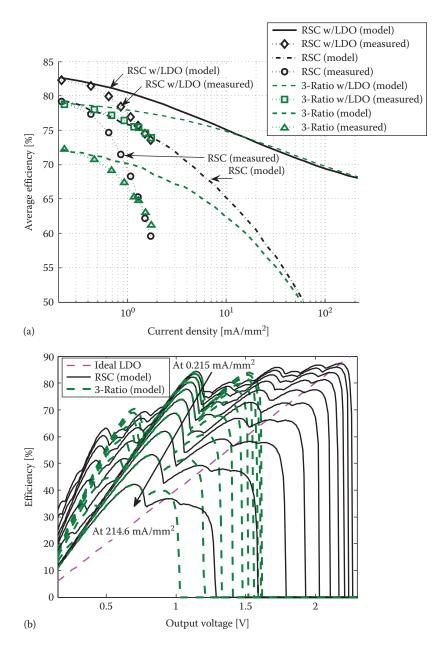

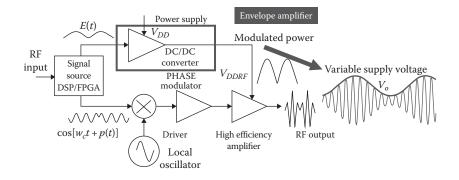

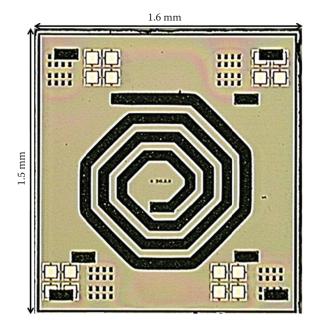

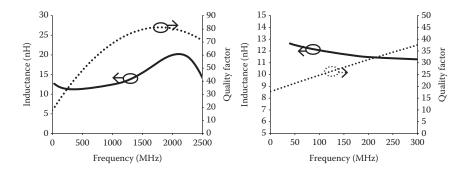

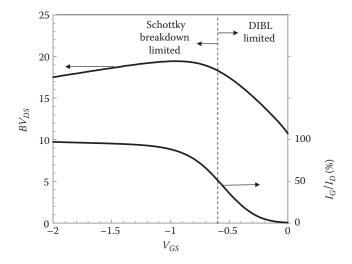

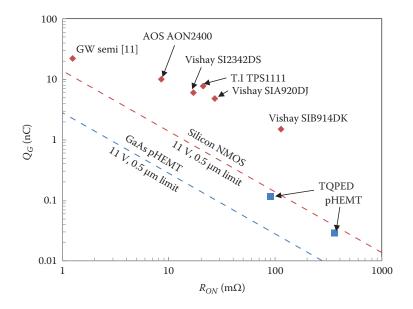

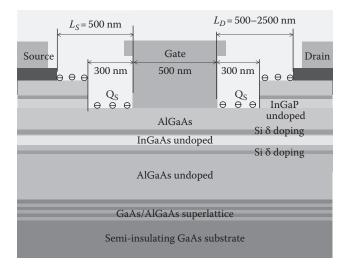

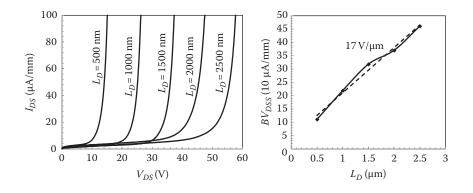

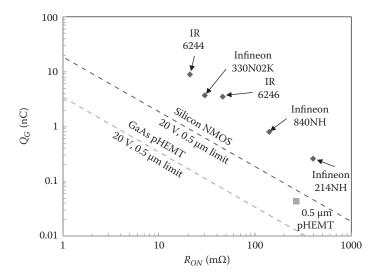

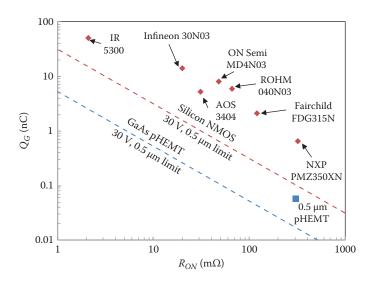

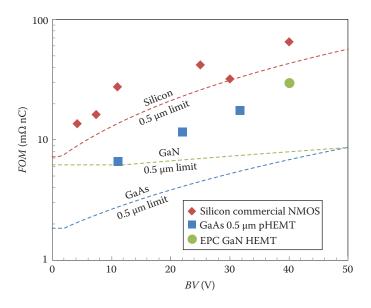

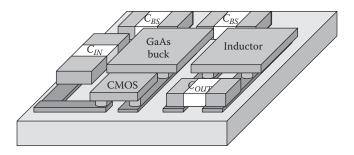

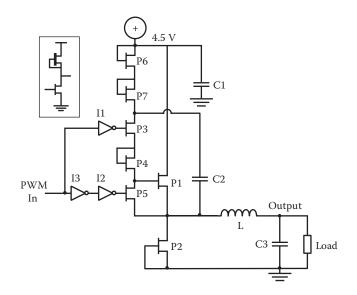

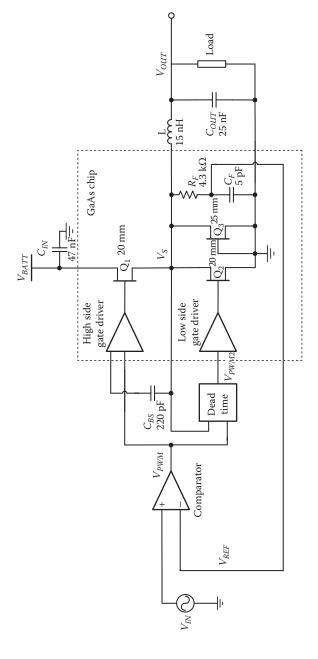

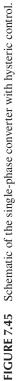

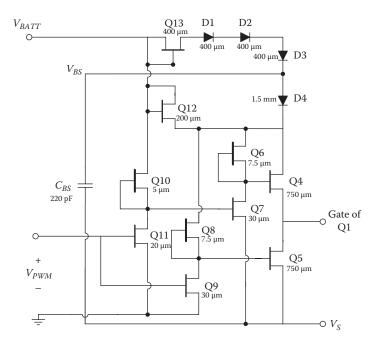

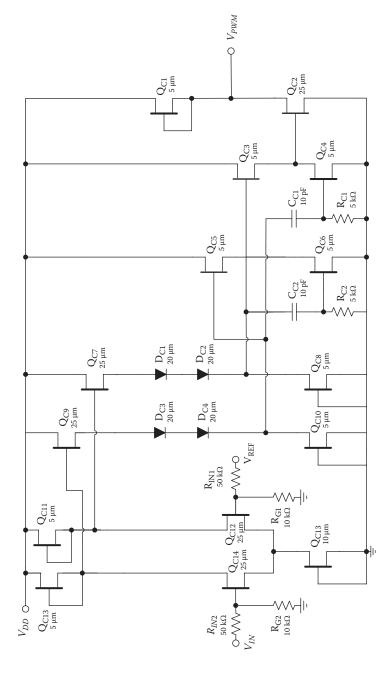

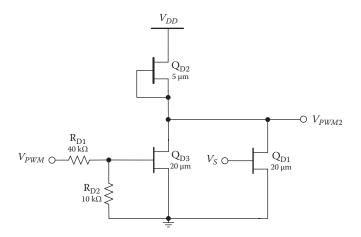

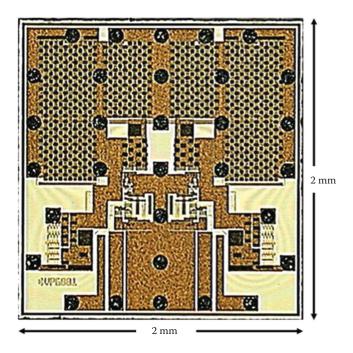

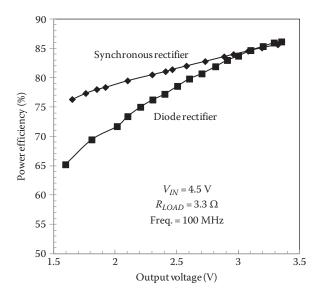

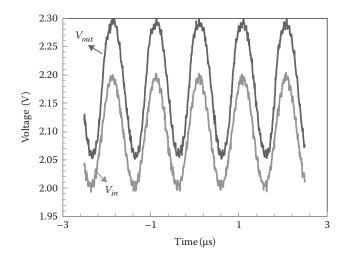

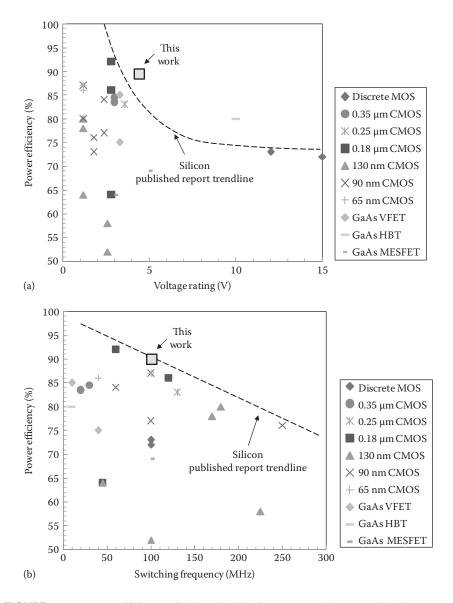

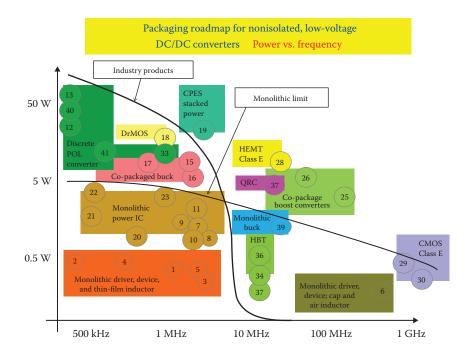

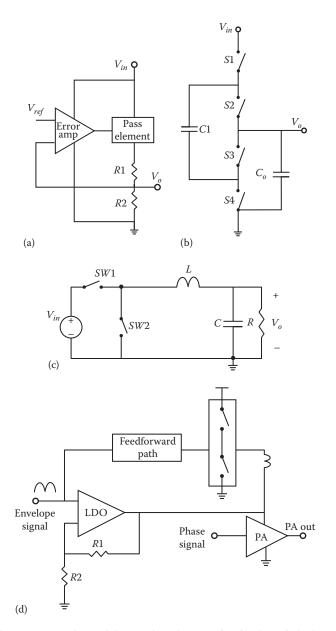

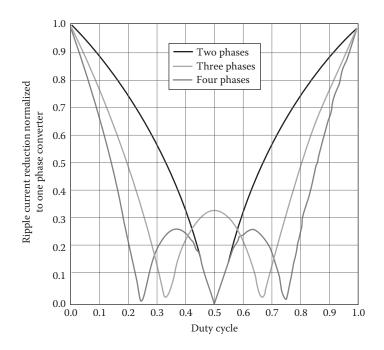

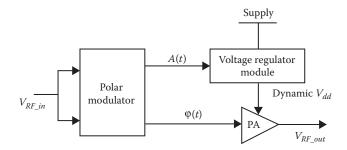

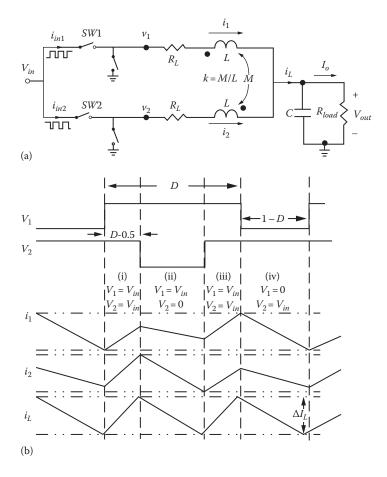

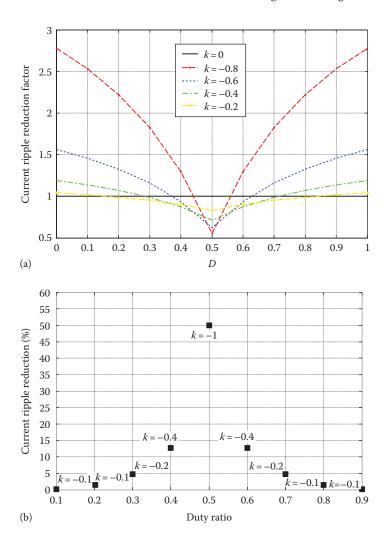

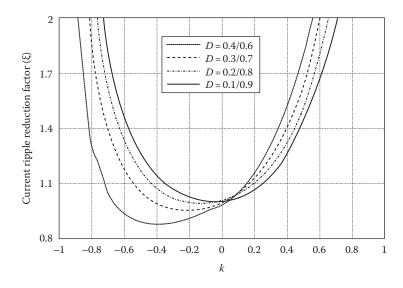

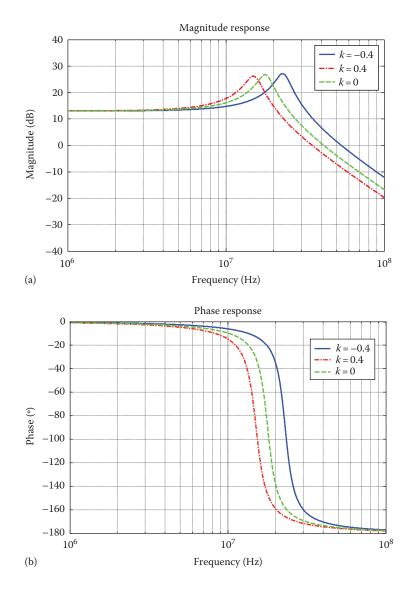

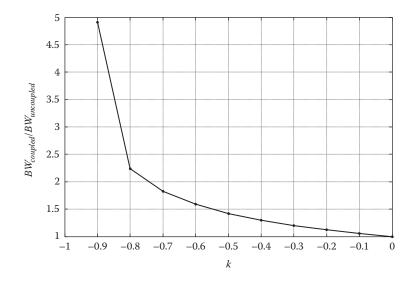

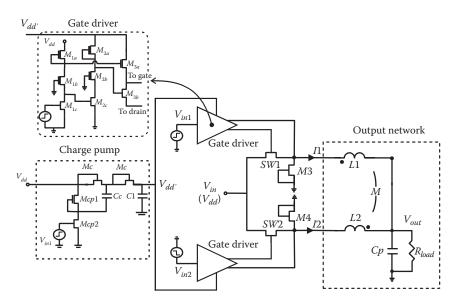

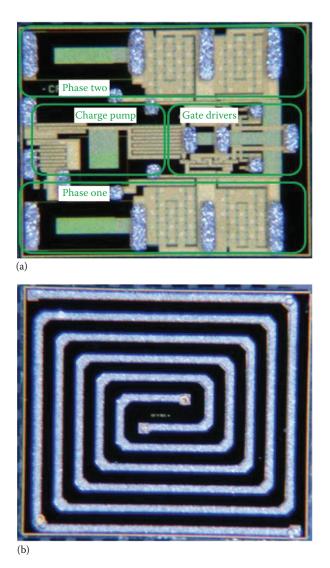

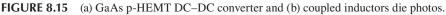

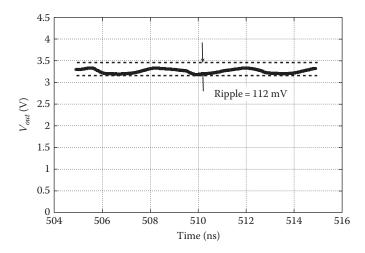

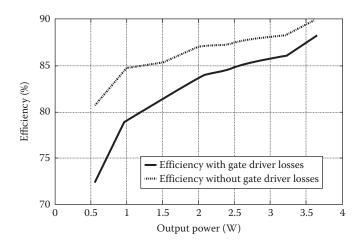

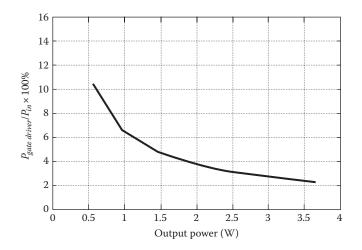

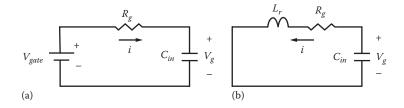

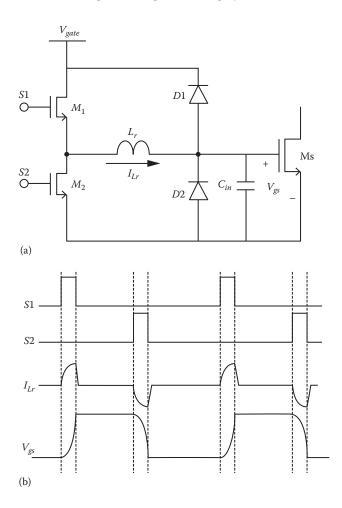

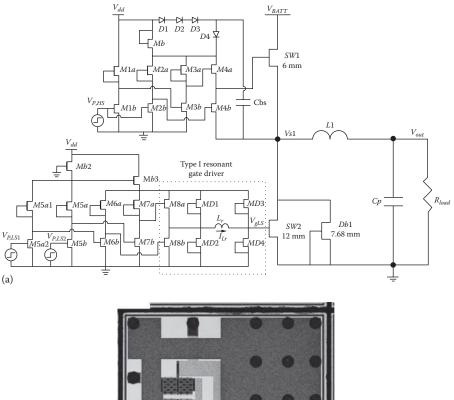

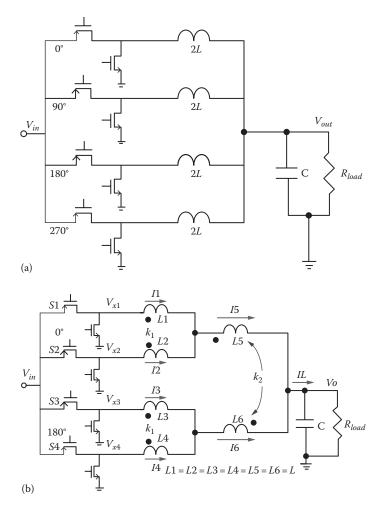

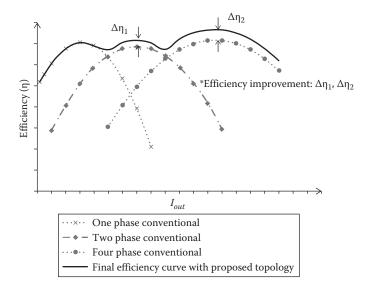

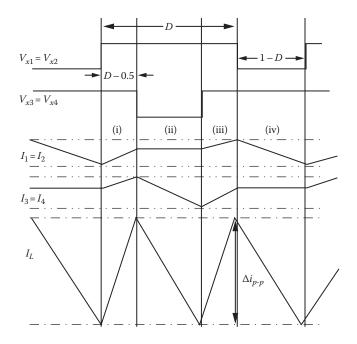

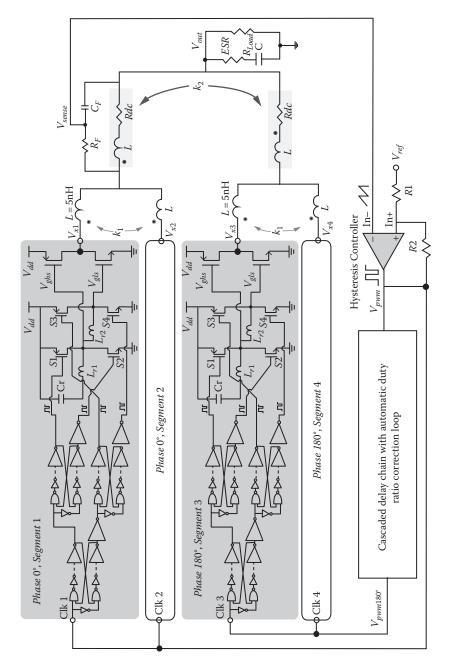

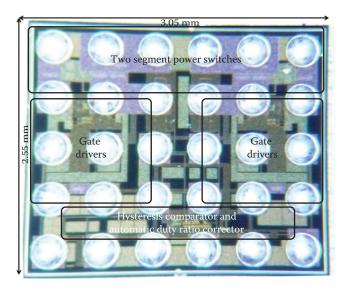

**FIGURE 1.26** Variation of ripple with  $V_{out}$  for  $I_{load} = 4$  mA.