Lecture Notes in Computer Science Edited by G. Goos, J. Hartmanis and J. van Leeuwen

2057

# Springer Berlin

Berlin Heidelberg New York Barcelona Hong Kong London Milan Paris Singapore Tokyo Matthew Dwyer (Ed.)

# Model Checking Software

8th International SPIN Workshop Toronto, Canada, May 19–20, 2001 Proceedings

Springer

Series Editors

Gerhard Goos, Karlsruhe University, Germany Juris Hartmanis, Cornell University, NY, USA Jan van Leeuwen, Utrecht University, The Netherlands

Volume Editor

Matthew Dwyer Kansas State University, Department of Computing and Information Sciences 234 Nichols Hall, Manhattan, KS 66506-2302, USA E-mail: dwyer@cis.ksu.edu

Cataloging-in-Publication Data applied for

Die Deutsche Bibliothek - CIP-Einheitsaufnahme

Model checking software : proceedings / 8th International SPIN Workshop, Toronto, Canada, May 19 - 20, 2001. Matthew Dwyer (ed.). -Berlin ; Heidelberg ; New York ; Barcelona ; Hong Kong ; London ; Milan ; Paris ; Singapore ; Tokyo : Springer, 2001 (Lecture notes in computer science ; Vol. 2057) ISBN 3-540-42124-6

CR Subject Classification (1998): F.3, D.2.4, D.3.1

ISSN 0302-9743 ISBN 3-540-42124-6 Springer-Verlag Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer-Verlag. Violations are liable for prosecution under the German Copyright Law.

Springer-Verlag Berlin Heidelberg New York a member of BertelsmannSpringer Science+Business Media GmbH

http://www.springer.de

© Springer-Verlag Berlin Heidelberg 2001 Printed in Germany

Typesetting: Camera-ready by author, data conversion by PTP-Berlin, Stefan SossnaPrinted on acid-free paperSPIN: 1078156906/31425 4 3 2 1 0

# Preface

Research on model checking has matured from a purely theoretical topic to encompass tool development and applications, in addition to more foundational topics. This diversity of model checking research is driving the area onward as foundational developments enable automation, development of robust tool support enables increasingly sophisticated applications, and feedback from applications spurs further work on the underlying theory and tools. The program of the eighth SPIN workshop reflected this diversity; it included three contributions on foundational topics, eight contributions on model checking tools, and eight contributions describing applications of model checking.

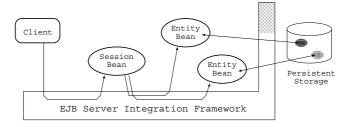

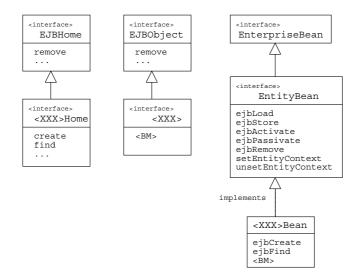

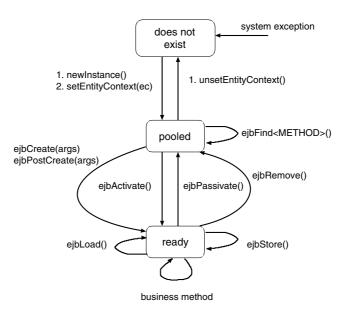

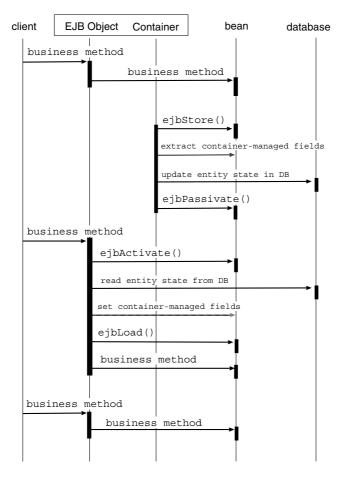

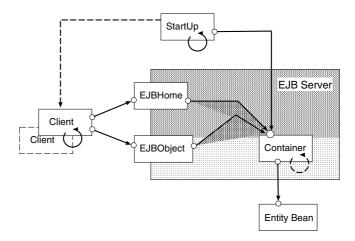

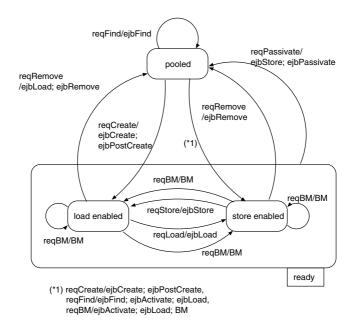

Continuing a trend begun in the seventh SPIN workshop, the eighth SPIN workshop emphasized the connections between model checking and program analysis. Research on static program analysis has a long history in both the compiler and software engineering communities. In an effort to establish a dialog between researchers in model checking and software analysis, this year's workshop was co-located with the 23rd International Conference on Software Engineering in Toronto. The workshop program contained several contributions that were clearly targeted at analyzing programs. Three contributions addressed tools for model checking of program source code, implemented in C and Java, and one contribution described model checking of a popular software component architecture.

The workshop featured 13 refereed technical papers selected from 26 submissions and two refereed descriptions of model checking tools selected from four submissions. Each submitted paper was reviewed by at least three members of the program committee; additional reviewers were used for several papers. The program committee discussed the merits of the submitted papers to arrive at the final 15 referred contributions. In addition to referred contributions, two leading experts in model checking technology and three groups that are applying model checking techniques in an industrial setting were invited to give presentations. The invited presentations were given by: Doron Peled (Bell Laboratories), Rob Gerth (Intel Corporation), Leszek Holenderski (Philips Research), Erik Engstrom (Honeywell Laboratories), and Bernhard Steffen (Metaframe Technologies). This proceedings issue contains four contributions detailing the content of the invited presentations. A panel session on the topic of "Prospects for and impediments to practical model checking" was organized to generate a dialog between those working on applying model checking and researchers working on extending model checking technologies.

Historically, the SPIN workshop has served as a forum for researchers interested in the subject of automata-based, explicit-state model checking technologies for the analysis and verification of asynchronous concurrent and distributed systems. In recent years, the scope of the workshop has broadened to encompass applications of model checking to software analysis. The workshop is named after the SPIN model checker, developed by Gerard Holzmann, which is one of the best known and most widely used model checking tools. The first SPIN workshop was held in October 1995 in Montréal. Subsequent workshops were held in New Brunswick (August 1996), Enschede (April 1997), Paris (November 1998), Trento (July 1999), Toulouse (September 1999), and at Stanford University (August 2000).

Acknowledgments. The editor wishes to thank the program committee members, and the referees, for their help in in organizing the workshop. Committee members volunteered many valuable suggestions as well as a significant amount of time for refereeing and discussing papers. The workshop organizers wish to thank the ICSE'2001 organizing committee for facilitating the co-location of the SPIN workshop and ACM SIGSOFT, Lucent Technologies, Microsoft Research, and the Office of Naval Research for their sponsorship and support of the SPIN workshop.

March 2001

Matthew B. Dwyer

# Organization

## **Organizing Committee**

General Chair: Moshe Y. Vardi (Rice University, USA) Program Chair: Matthew B. Dwyer (Kansas State University, USA) Local Arrangements Chair: Marsha Chechik (University of Toronto, Canada)

## **Program Committee**

George Avrunin (University of Massachusetts, USA) Thomas Ball (Microsoft Research, USA) Ed Brinksma (University of Twente, The Netherlands) Marsha Chechik (University of Toronto, Canada) Dennis R. Dams (Eindhoven University, The Netherlands) Klaus Havelund (QSS/Recom at NASA Ames Research Center, USA) Connie Heitmeyer (Naval Research Laboratory, USA) Gerard J. Holzmann (Bell Laboratories, USA) Fabio Somenzi (University of Colorado, USA) Willem Visser (RIACS at NASA Ames Research Center, USA) Pierre Wolper (Université de Liege, Belgium)

## Referees

| R. Bloem          | J. Katoen   |

|-------------------|-------------|

| D. Bosnacki       | R. Langerak |

| J. Geldenhuys     | F. Lerda    |

| D. Giannakopoulou | S. Park     |

| H. Hermanns       | C. Pecheur  |

| L. Holenderski    | G. Rosu     |

T. RuysR. de VriesB. Wolter

## **Sponsoring Organizations**

The eighth SPIN Workshop was sponsored by the ACM SIGSOFT (Special Interest Group on Software Engineering). Additional support was provided by: Bell Laboratories, Lucent Technologies, USA, Microsoft Research, Microsoft Inc., USA, and The Office of Naval Research, USA.

# **Table of Contents**

# Invited Keynotes

| From Model Checking to a Temporal Proof 1<br>Doron Peled (Bell Laboratories), Lenore Zuck (New York University)                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Model Checking if Your Life Depends on It:<br>A View from Intel's Trenches                                                                                   |

| Technical Papers and Tool Reports                                                                                                                            |

| Model-Checking Infinite State-Space Systems with Fine-GrainedAbstractions Using SPIN16Marsha Chechik, Benet Devereux, Arie Gurfinkel (University of Toronto) |

| Implementing LTL Model Checking with Net Unfoldings                                                                                                          |

| Directed Explicit Model Checking with HSF-SPIN                                                                                                               |

| Addressing Dynamic Issues of Program Model Checking 80<br>Flavio Lerda, Willem Visser (NASA Ames Research Center)                                            |

| Automatically Validating Temporal Safety Properties of Interfaces 103<br>Thomas Ball, Sriram K. Rajamani (Microsoft Research)                                |

| Verification Experiments on the MASCARA Protocol                                                                                                             |

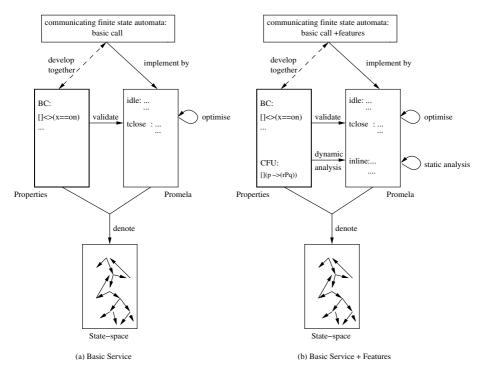

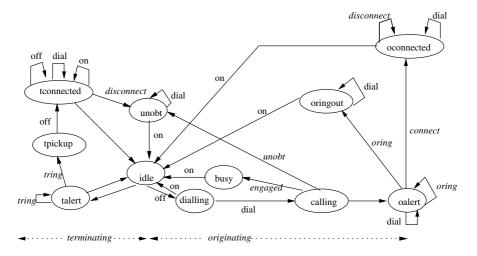

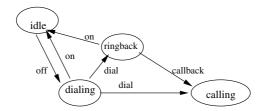

| Using SPIN for Feature Interaction Analysis – A Case Study 143<br>Muffy Calder, Alice Miller (University of Glasgow)                                         |

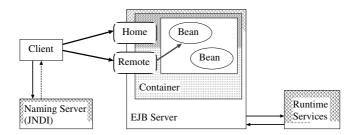

| Behavioural Analysis of the Enterprise JavaBeans <sup>TM</sup> Component<br>Architecture                                                                     |

| <ul> <li>p2b: A Translation Utility for Linking Promela and Symbolic Model</li> <li>Checking (Tool Paper)</li></ul>                                          |

| Transformations for Model Checking Distributed Java Programs 192<br>Scott D. Stoller, Yanhong A. Liu (SUNY at Stony Brook)          |

|-------------------------------------------------------------------------------------------------------------------------------------|

| Distributed LTL Model-Checking in SPIN                                                                                              |

| Parallel State Space Construction for Model-Checking 217<br>Hubert Garavel, Radu Mateescu, Irina Smarandache<br>(INRIA Rhône-Alpes) |

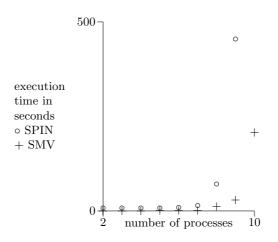

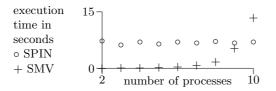

| Model Checking Systems of Replicated Processes with Spin                                                                            |

| A SPIN-Based Model Checker for Telecommunication Protocols                                                                          |

| Modeling and Verifying a Price Model for Congestion Control in Computer<br>Networks Using Promela/Spin                              |

| Invited Project Summaries                                                                                                           |

| A Model Checking Project at Philips Research                                                                                        |

| Applications of Model Checking at Honeywell Laboratories                                                                            |

| Coarse-Granular Model Checking in Practice                                                                                          |

| Author Index                                                                                                                        |

## From Model Checking to a Temporal Proof

Doron  $\mathrm{Peled}^1$  and  $\mathrm{Lenore}\ \mathrm{Zuck}^2$

Bell Laboratories, 600 Mountain Ave., Murray Hill, NJ 07974 doron@research.bell-labs.com

<sup>2</sup> Department of Computer Science, New York University zuck@cs.nvu.edu

**Abstract.** Model checking is used to automatically verify temporal properties of finite state systems. It is usually considered to be 'successful', when an error, in the form of a counterexample to the checked property, is found. We present the dual approach, where, in the presence of no counterexample, we automatically generate a proof that the checked property is satisfied by the given system. Such a proof can be used to obtain intuition about the verified system. This approach can be added as a simple extension to existing model checking tools.

## 1 Introduction

The automatic verification of finite state systems, often called *model checking* [1, 4], is highly successful in detecting bugs during software and hardware development. It involves modeling the inspected system, specifying its properties using some logical formalism, and using some graph algorithms to systematically detect whether there are executions of the model of the system that violate the specification. If such executions exist, (at least) one of them is reported as a counterexample.

If the search for counterexamples fails, we can conclude that the model of the system satisfies the specification. This is often considered as a failure of the model checking attempt. Some even go as far as to say that the goal of model checking is not 'verification', but 'falsification'. One reason for this is that the modeling process is itself prone to errors. The model of the checked system is often an oversimplification of the original system since model checking often requires that the model has finitely many states.

An alternative to model checking is the *deductive verification* approach, one of whose goals is to formally explain *why* the system satisfies the checked property. This approach often calls for creativity of the prover. Deductive verification is usually manual and time consuming.

In this paper, we emphasize the point of view that when no counterexample is found, model checking can also be used to *justify* why the verified system satisfies the checked property. We show that a failed systematic search for counterexamples can be used to generate a deductive proof that the model satisfies the checked property, by exploiting the information in the graph that is generated during the search. We apply the automata theoretic view [7,10]. Specifically, we start with an LTL (linear temporal logic) specification, and transform it into an automaton. In fact, it is the negation of the specification formula that is translated. The checked system is also represented as an automaton. We then construct the intersection of these two automata. If the intersection is nonempty, it contains a counterexample that can be reported. Otherwise, the model of the system satisfies the specification. We show how, in the latter case, the intersection graph can be used to produce a proof.

The main challenge is how to represent the proof, which is implicit in the intersection graph. We would like to present the proof in a way that would explain to the user why the property holds for the checked system.

#### 2 Preliminaries

We sketch the model checking procedure for Temporal Logic formulas over finite state formulas. For more details, see [3].

A Generalized Büchi automaton A is a 6-tuple  $(S, S_0, \delta, \mathcal{F}, L, \Sigma)$ , where S is a finite set of states,  $S_0 \subseteq S$  is a set of initial states,  $\delta \subseteq S \times S$  is a (nondeterministic) transition relation,  $\mathcal{F} \subseteq 2^{S \times S}$  is the set of acceptance sets,  $\Sigma$  is a set of labels and  $L: S \to \Sigma$  is a labeling function of the states.<sup>1</sup> A run of the automaton A is an infinite sequence of S-states  $\alpha = s_0, s_1, \ldots$  such that  $s_0 \in S_0$ , and for every  $i \geq 0$ ,  $(s_i, s_{i+1}) \in \delta$ . A run is accepting if for every  $F \in \mathcal{F}$ ,  $(s_i, s_{i+1}) \in F$ for infinitely many *i*'s. The language accepted by an automaton A, denoted by  $\mathcal{L}(A)$ , is the set of (labeled) sequences that are accepted by the automaton.

Let  $\Pi$  be a set of propositions. We consider here linear time propositional temporal logic (LTL) formulas over  $\Pi$ , using the Boolean connectives  $\vee$  and  $\neg$ , and the temporal operators *nexttime*  $\bigcirc$  and *until*  $\mathcal{U}$ . Temporal logic formulas are interpreted over infinite sequences over  $2^{\Pi}$  (see, e.g., [8]). Let  $\sigma = x_0 x_1 \dots$ be a sequence of states. Denote its suffix  $x_i x_{i+1} \dots$  by  $\sigma^i$ . We denote the fact that a sequence  $\sigma$  satisfies a temporal formula  $\varphi$  by  $\sigma \models \varphi$ . For a propositional formula  $\sigma^i \models \varphi$  if  $\varphi$  holds in the state  $x_i$ .  $\sigma^i \models \bigcirc \varphi$  if  $\sigma^{i+1} \models \varphi$ .  $\sigma^i \models \varphi \mathcal{U} \psi$ holds if there exists  $j \ge i$  such that  $\sigma^j \models \psi$ , and for each  $i \le k < j$ ,  $\sigma^k \models \varphi$ . The other Boolean connectives and Temporal operators ( $\Box$ ,  $\diamond$ ,  $\mathcal{V}$ , etc.) can be defined using the above operators, namely  $\diamond \varphi = true \mathcal{U} \varphi$ ,  $\Box \varphi = \neg \diamond \neg \varphi$  and  $\varphi \mathcal{V} \psi = \neg((\neg \varphi) \mathcal{U}(\neg \psi))$ .

We assume that all the temporal formulas are given in the *negation nor*mal form, i.e., with negation appearing only on propositions. This can be easily achieved by pushing negation inwards, using the equivalences  $\neg \neg \varphi = \varphi$ ,  $\neg \bigcirc \varphi = \bigcirc \neg \varphi, \neg (\varphi \lor \psi) = (\neg \varphi) \land (\neg \psi), \neg (\varphi \land \psi) = (\neg \varphi)_{\lor} (\neg \psi), \neg (\varphi \mathcal{U} \psi) =$

<sup>&</sup>lt;sup>1</sup> The definition of automata here is a variant of the standard definition for reasons that will become clear later. In particular, the labeling here is on the states, and each acceptance set is a set of transitions.

$(\neg \varphi) \mathcal{V} (\neg \psi)$  and  $\neg (\varphi \mathcal{V} \psi) = (\neg \varphi) \mathcal{U} (\neg \psi)$ . The *language* accepted by a temporal logic formula  $\varphi$ , denoted by  $\mathcal{L}(\varphi)$ , is the set of infinite sequences that satisfy  $\varphi$ . Given a temporal formula  $\varphi$ , we sketch how to construct an automaton  $A_{\varphi} = (X, X_0, \delta^A, \mathcal{F}^A, L^A, 2^{2^{\Pi}})$  such that  $\mathcal{L}(A_{\varphi}) = \mathcal{L}(\varphi)$ . The construction here is essentially the one in [5]. Each state of  $A_{\varphi}$  is labeled with a propositional formula over the variables  $\Pi$ , thus  $\Sigma = 2^{2^{\Pi}}$ .

With each state x of  $A_{\varphi}$ , we associate a formula  $\eta(x)$ , such that for every accepting run  $\sigma = x_0, x_1, \ldots$  of  $A_{\varphi}, \sigma^i \models \eta(x_i)$ . The formula  $\eta(x)$  is of the form

$$\left(\bigwedge_{i=1,\dots,m_x}\nu_i^x\right) \wedge \left(\bigwedge_{j=1,\dots,n_x}\bigcirc\psi_j^x\right). \tag{1}$$

Note that each temporal formula can be trivially brought into the form of Equation (1), when  $m_x = 1$  and  $n_x = 0$ . We denote by present(x) the set of  $\nu_i^s$  formulas, and by next(x) the set of  $\psi_i^x$  formulas. In addition to  $\eta(x)$ , we associate with each state a list of *incoming* edges from predecessor states. Nodes (states) are refined and split, according to the formulas in present(x).

We start the construction with a node x that initially contains the formula to be translated in present(x). The set next(x) is empty, and there is one incoming edge to x marked with *init*. This is a dummy edge, pointing to x, but without any predecessor node. We repeatedly apply to the nodes *refinement* and *splitting*, as follows:

Refinement: If  $\chi_1 \wedge \chi_2 \in present(x)$ , we add  $\chi_1, \chi_2$  to present(x). Similarly, if  $\chi_1 \mathcal{U}\chi_2 \in present(x)$ , we add to present(x) the formula  $\chi_2 \vee (\chi_1 \wedge \bigcirc (\chi_1 \mathcal{U}\chi_2))$ . If  $\chi_1 \mathcal{V}\chi_2 \in present(x)$ , we add to present(x) the formula  $\chi_2 \wedge (\chi_1 \vee \bigcirc (\chi_1 \mathcal{V}\chi_2))$ . Finally, if  $\bigcirc \chi \in present(x)$ , we add  $\chi$  to next(x).

Splitting: given a formula of the form  $\chi_1 \vee \chi_2$  in present(x), which was not used before for splitting, we split the current node into two nodes  $x_1$  and  $x_2$ . Then we set  $present(x_1)$  to be  $present(x) \cup \{\chi_1\}$  and the value of  $present(x_2)$ to be  $present(x) \cup \{\chi_2\}$ . The set of subformulas next(x) are copied to  $next(x_1)$ and  $next(x_2)$ . We also copy the list of incoming edges from x to  $x_1$  and to  $x_2$ .

We stop refining and splitting a node x when all the formulas in present(x) were used. We then add node x to the list X of automaton nodes if there exist no node x' with present(x) = present(x') and next(x) = next(x'). Otherwise, i.e., if there exists such a node x', we only update the list of incoming edges in x' by adding the incoming edges of the new node x. After a new node is added to X, we generate a successor node x', and set present(x') to be the next(x) formulas, and next(x') to be empty.

The acceptance conditions  $\mathcal{F}^A$  of  $A_{\varphi}$  guarantees that each  $\mathcal{U}$  subformula of  $\varphi$  is *fulfilled*. Thus, for every such subformula  $\chi_1 \mathcal{U} \chi_2$  of  $\varphi$  there is an acceptance condition in  $\mathcal{F}^A$  that includes all the outgoing edges from nodes x such that either  $\chi_2 \in present(x)$ , or that  $\chi_1 \mathcal{U} \chi_2 \not\in present(x)$ . The initial states  $X_0$  of  $A_{\varphi}$  consist of the states  $x \in X$  has the incoming edge *init*. The label  $L^A(x)$  of a node x is the propositional formula prop(x), defined as the conjunction of

the propositions and negated propositions that appear in present(x) after the construction of x.

**Theorem 1** For every temporal formula  $\varphi$  and automaton  $A_{\varphi}$  constructed as above,  $\mathcal{L}(A_{\varphi}) = \mathcal{L}(\varphi)$ .

For every state x of  $A_{\varphi}$ , we define  $\mu(x) = \neg \eta(x)$ , i.e.,

$$\mu(x) = (\bigvee_{i=1,\ldots,m_x} \neg \nu_i^x) \lor (\bigvee_{i=1,\ldots,n_x} \bigcirc \neg \psi_i^x)$$

The following lemma follows immediately from the construction:

**Lemma 1** If a node x in the constructed Büchi automaton has n immediate successors,  $x_1 \ldots x_n$ , then  $\eta(x) \to \bigvee_{i=1,n} \bigcirc \eta(x_i)$ . Equivalently,  $\bigwedge_{i=1,n} \bigcirc \mu(x_i) \to \mu(x)$ .

In order to simplify the automatically generated proof, presented in the sequel, we can remove from  $\eta(x)$  every formula that causes splitting (e.g., remove  $\chi_1 \lor \chi_2$ , once  $\chi_1$  or  $\chi_2$  is added), or refinement. The formula  $\mu(x)$  is changed accordingly.

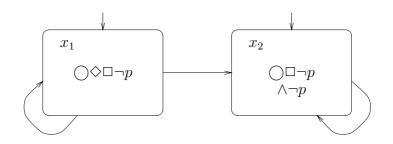

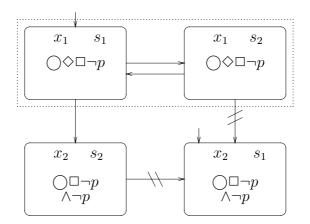

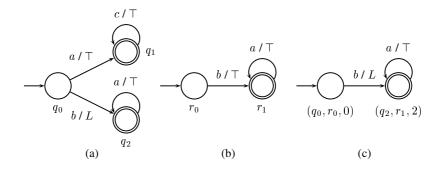

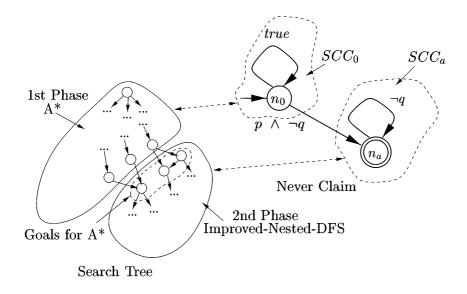

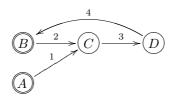

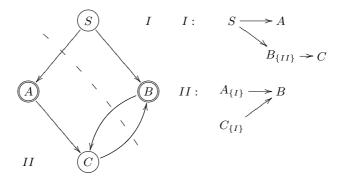

**Example.** Consider the case where we want to verify the property  $\varphi = \Box \diamond p$ , i.e., p happens infinitely often. Then, we translate  $\neg \varphi = \diamond \Box \neg p$ . We can rewrite this formula with the  $\mathcal{U}$  and  $\mathcal{V}$  operators as  $true \mathcal{U}(false \mathcal{V} \neg p)$  or change the translation algorithm to deal directly with the operator  $\Box$  and  $\diamond$ . The automaton obtained in this way appears in Figure 1. In this figure, we translated, for simplicity, the formulas back to the form with  $\Box$  and  $\diamond$ . We included in each node x the formula  $\mu(x)$ . There is one accepting set for this automaton, which includes a single transition  $(x_2, x_2)$ .

**Fig. 1.** An automaton for  $\neg \varphi = \Diamond \Box \neg p$

We consider finite state systems  $P = \langle V, \Theta, \mathcal{T}, \mathcal{F}^P \rangle$  consisting of:

V - A set of system variables. A state of the system provides an interpretation of the system variables V. For a state s and a variable v, we denote by s[v]the value assigned to v by the state s.

- $\Theta$  The *initial condition*, which is a propositional formula over the variables V characterizing the initial states.

- $\mathcal{T}$  A set of *transitions formulas* of the form  $\tau(V, V')$ , relating the values V of the system's variables in state  $s \in S$  to the values V' in a  $\tau$ -successor s'.

- $Fair^{P}$  A set of fair conditions, each element  $G \in Fair^{P}$  is a formula over V and V'.

A computation of the system P is an infinite sequence of states  $\sigma = s_0, s_1, \ldots$  satisfying:

- $-s_0$  is initial, i.e.,  $s_0 \models \Theta$

- For each  $i \ge 0$ , the state  $s_{i+1}$  is the  $\tau$ -successor of  $s_i$  for some  $\tau \in \mathcal{T}$ . That is,  $(s_i, s_{i+1}) \models \tau(V, V')$  where for each  $v \in V$ , we interpret v as  $s_i[v]$  and v' as  $s_{i+1}[v]$ .

- For every  $G \in Fair^P$ ,  $(s_i, s_{i+1}) \models G$  for infinitely many *i*'s.

It is easy to represent weakly fair transitions system as automata: The set of interpretations for the system variables is the set of states  $S^P$ . The initial states  $S^P_0$  are all the interpretations satisfying  $\Theta$ . The transition relation  $\delta^P$ is generated by the formulas in  $\mathcal{T}$ . Each acceptance condition  $F \in \mathcal{F}^P$  corresponds to the transitions that satisfy a fairness condition  $G \in Fair^P$ . The labeling functions  $L^P$  maps each state with an assignment over the set of propositions  $\Pi$ . Note that in some cases we have that  $V = \Pi$ . A weakly fair transitions system is thus represented by an automaton  $(S^P, S^P_0, \delta^P, \mathcal{F}^P, L^P, 2^{\Pi})$ . Let  $succ(s) = \{s' | (s, s') \in \delta^P\}$ , i.e., the set of successors of node s. Denote by  $s \longrightarrow \{s_1, \ldots, s_n\}$  the fact that s has, according to the automaton P, exactly nsuccessors,  $s_1, \ldots, s_n$ .

For a finite state system P and a temporal formula, we say that  $\varphi$  is valid over P, or that  $\varphi$  is P-valid, denoted by  $P \models \varphi$ , if for every fair computation  $\sigma$  of P,  $\sigma \models \varphi$ .

We are mainly interested in concurrent systems over a set processes  $\mathcal{P}$ . Each edge in  $\delta^P$  corresponds to a transition executed by one or more processes in P. Under weak process fairness [8], each acceptance condition F in  $\mathcal{F}^P$  corresponds to a process. It contains all the edges that exist from any state in which that process is disabled and all the edges that correspond to the execution of an atomic transition by this process.

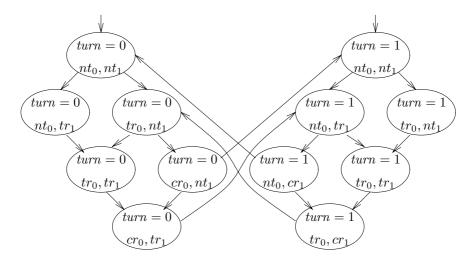

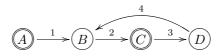

**Example.** Consider a system with two processes, competing on getting to a critical section. Each process in  $\mathcal{P} = \{T_1, T_2\}$  consists of three transitions. There is one Boolean variable *turn*, which arbitrates among the processes, to resolve the case where both want to enter the critical section. The program counter of each process  $pc_i$  can be in one of the following labels:

- $nt_i$  The process  $T_i$  is currently not trying to enter its critical section.

- $tr_i$  The process  $T_i$  is trying to enter its critical section.

- $cr_i$  The process  $T_i$  is in its critical section.

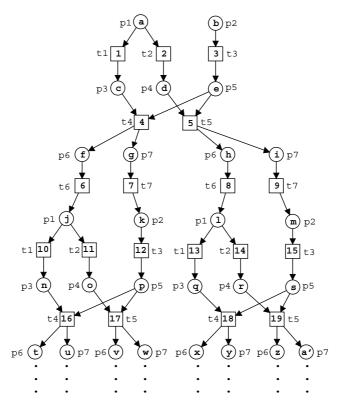

Fig. 2. A mutual exclusion system

There are three transitions for each process  $T_i$ :

$$t_{1i} = pc_{i} = nt_{i} \land pc_{i}' = tr_{i} \land pc_{1-i}' = pc_{1-i} \land turn' = turn$$

$$t_{2i} = pc_{i} = tr_{i} \land pc_{i}' = cr_{i} \land turn = i \land pc_{1-i}' = pc_{1-i} \land turn' = turn$$

$$t_{3i} = pc_{i} = cr_{i} \land pc_{i}' = nt_{i} \land pc_{1-i}' = pc_{1-i} \land turn' = 1 - turn$$

The initial condition is  $\Theta : pc_0 = nt_0 \wedge pc_1 = nt_1$ . The state space of this system is presented in Figure 2. For simplicity of the presentation, we do not impose any fairness constraint on this system (in fact, in this case, fairness would not make any difference). For a state  $s \in S$  and a temporal formula  $\varphi$ , denote by  $(P, s) \hookrightarrow \eta$ , the fact that there exists a suffix  $\sigma$  of a sequence accepted by the system automaton P, which starts with the state s, such that  $\sigma \models \eta$ . Denote by  $(P, s) \models \mu$  the fact that for every suffix  $\sigma$  of a sequence in P, which starts with the state  $s, \sigma \models \mu$ . We often omit P, when it is known from the context, and write  $s \models \mu$  instead of  $(P, s) \models \mu$ . Note that  $\hookrightarrow$  and  $\models$  are dual relations, since  $(P, s) \models \mu$  iff  $(P, s) \nleftrightarrow \neg \mu$ .

#### 3 Checking the Validity of a Formula over a Program

Our approach can be used to establish a proof that  $\sigma \models \varphi$  for every sequence  $\sigma$  accepted by the automaton P. We denote that by  $P \models \varphi$ .

In order to verify that  $\varphi$  is *P*-valid, we build an *intersection automaton* that accepts  $\mathcal{L}(\neg \varphi) \cap \mathcal{L}(P)$ , and show it to be empty. Let  $A_{\neg \varphi}$  be the automaton  $(X, X_0, \delta^A, \mathcal{F}^A, L^A, 2^{2^{II}})$ , which accepts  $\mathcal{L}(\neg \varphi)$ . Let *P* be the system automaton  $(S^P, S^P_0, \delta^P, \mathcal{F}^P, L^P, 2^{II})$ . The *product* automaton, that accepts  $\mathcal{L}(P) \cap \mathcal{L}(\neg \varphi)$ , is  $A^P_{\neg \varphi} = (S, S_0, \delta, \mathcal{F}, L, 2^{II})$ , where

1.  $S = X \times S^P$ .

In the intersection graph of  $A^P_{\neg\varphi}$ , we distinguish two kinds of nodes: *success* nodes of the form (x, s), where  $L^P(s) \in L^A(x)$ , i.e., the propositional assignment of s satisfies the propositional formula prop(x), and *failed nodes*, otherwise.

- 2.  $S_0 = X_0 \times S_0$ .

- 3.  $((x,s), (x',s')) \in \delta$  iff  $(x, x') \in \delta^A$ ,  $(s, s') \in \delta^P$  and  $L^P(s) \in L^A(x)$ . That is, the transition relation agrees with transition relations of both the system and the property automata. Moreover, there is a transition from a state  $(x, s) \in S$  only if it is a success node.

- 4. The accepting condition consists of the acceptance sets of both automata. Formally, we define an operator  $\bowtie$  such that for every sets  $A, B, C \subseteq A \times A$ , and  $D \subseteq B \times B$ ,

$$C\bowtie D = \bigcup_{(a,a')\in C; (b,b')\in D} \bigl((a,b), (a',b')\bigr).$$

- Then,  $\mathcal{F} = \{(X \times X) \bowtie F | F \in \mathcal{F}^P\} \cup \{F \bowtie (S^P \times S^P) | F \in \mathcal{F}^A\}.$

- 5.  $L(x,s) = L^{P}(s)$ ; i.e., the labeling of each state is its labeling in the system automaton.

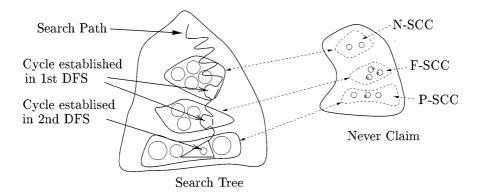

In order to check that  $\mathcal{L}(A^P_{\neg\varphi}) = \emptyset$ , it suffices to check that, in the graph defined by  $A^P_{\neg\varphi}$ , there is no path leading from  $S_0$  to a strongly connected component (SCC) that intersects each of the sets in  $\mathcal{F}$ . An immediate implication of the construction is:

**Theorem 2** Assume  $\mathcal{L}(A^P_{\neg \varphi}) = \emptyset$ . Then for every initial state  $(x_0, s_0)$  of  $A^P_{\neg \varphi}$ ,  $(P, s_0) \models \neg \varphi$ . Thus,  $P \models \bigwedge_{(x_0, s_0) \in S_0} \mu(x_0)$ .

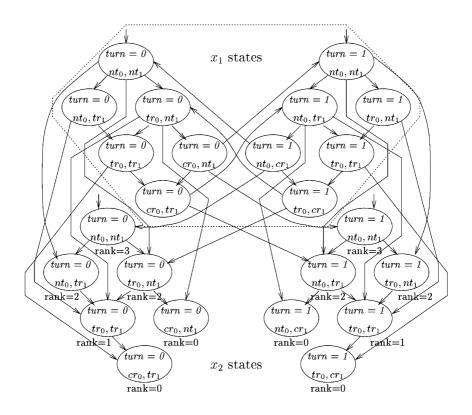

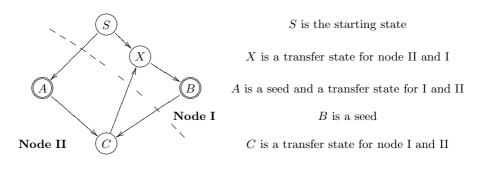

**Example.** Consider the system in Figure 2. We want to prove for it the property  $\Box \diamond (cr_0 \lor cr_1)$ . The property automaton construction is similar to the one in Figure 1, except that we replace p with  $cr_0 \lor cr_1$  (hence, we replace  $\neg p$  with  $\neg cr_0 \land \neg cr_1$ ). The intersection of the property automaton from Figure 1 with the state space in Figure 2 is shown in Figure 3.

## 4 Constructing a Temporal Logic Proof

In this approach, we transform  $A^P_{\neg\varphi}$  into a temporal proof formula. As a preparatory step, we perform Tarjan's algorithm on the the intersection graph for  $A^P_{\neg\varphi}$ , obtaining the strongly connected components.

There is a naturally induced partial order  $\prec$  between the strongly connected components such that  $C \prec C'$  if there is an edge from some node in C to some node in C'. In the proof, we need to complete the proof related to all the components C' such that  $C \prec C'$ , before we start dealing with C.

In this sound and complete proof system there are four kinds of correctness assertions:

Fig. 3. The intersection of the property automaton in Figure 1 and state space in Figure 2

**Failure axiom** FAIL. Let (x, s) be a failed node. Then we can conclude that  $s \models \mu(x)$ .

The justification for this axiom is simple: the node has failed because we have checked the assignment of the state s against the propositional claim in x, and the propositional claim has failed to hold. Thus,  $s \models \neg prop(x)$ . But, note that  $\neg prop(x) \rightarrow \mu(x)$ .

**Successors rule** SUCC. Let (x, s) be a successful node, such that x has n successors  $x_1, \ldots, x_n$ , and s has m successors  $s_1, \ldots, s_m$ . Then we have

$$\frac{s \longrightarrow \{s_1, \dots, s_m\}}{\text{For each } 1 \le i \le m, s_i \models \bigwedge_{j=1,n} \mu(x_j)}$$

$$\frac{s \models \mu(x)}{s \models \mu(x)}$$

The validity of this proof rule (see Also [2]) stems from the correctness of the construction. In particular, Lemma 1. Note that in fact, the failure axiom can be seen as a special case of the successors rule, with no premises.

**Induction** IND. Let C be a strongly connected component in  $A^P_{\neg\varphi}$ . Let Exit(C) be the set of nodes not in C, with an incoming arrow from a node in C. Assume first that the SCC C does not satisfy at least one acceptance condition that stems from the property automaton. That is, there exists at least one acceptance set  $F \in \mathcal{F}^P$  such that none of the edges in F is in C.

$$\begin{array}{l} \text{For each } (x,s) \in Exit(C), \ s \models \mu(x) \\ \hline \text{For each } (x,s) \in C, \ s \longrightarrow succ(s) \\ \hline \text{For each } (x,s) \in C, \ s \models \mu(x) \end{array}$$

In case that the SCC C satisfies all the acceptance conditions that stem from the property automaton, it must not satisfy at least one condition that stems from the system fairness (otherwise, the intersection would not be empty). In this case, we need to add a premise of the following form:

$$\bigwedge_{F\in\mathcal{F}^P}\Box\Diamond\Gamma_F$$

where  $\Gamma_F$  is a formula describing the pairs of adjacent states that belong to F.

**Conjunction rule** CONJ. This rule allows conjoining any pair of conclusions made on a given state, and making temporal logic interferences (we assume for the third premise a given sound and complete propositional temporal logic).

$$\frac{s\models\varphi_1,\,s\models\varphi_2,\,(\varphi_1\wedge\varphi_2)\to\varphi}{s\models\varphi}$$

We can now obtain the formal temporal proof, showing that if  $\mathcal{L}(A^P_{\neg \varphi}) = \emptyset$ , then each initial state  $s \in S^P_0$  satisfies  $s \models \varphi$ , i.e.,  $P \models \varphi$ . This is given according to the following steps:

- 1. Translate  $\neg \varphi$  into an automaton  $\mathcal{A}_{\neg \varphi}$ , according to the above algorithm. Construct the intersection graph  $\mathcal{A}^{P}_{\neg \varphi}$ .

- 2. Apply Tarjan's DFS to  $\mathcal{A}^{P}_{\neg \omega}$ . Find the SCCs.

- 3. If all the SCCs are discarded, goto Step 9.

- 4. Select a strongly connected component C that is not yet discarded, such that all the SCCs C' such that  $C \prec C'$  were discarded.

- 5. If C consists of a single node (x, s) that has no successor (a leaf), then it must be a failure node. Apply the rule FAIL.

- 6. If C is a trivial SCC, i.e., contains a single node (x, s) without a self loop, but with successors, apply Succ(x, s).

- 7. If C is a nontrivial SCC, apply IND. Note that some successors of the nodes of C are outside of the SCC, namely in Exit(C). These nodes were handled previously.

- 8. Discard C and go to Step 3.

9. Let s be an initial state of P, and  $x_1, \ldots, x_n$  be all the states such that  $(x_i, s)$  is a node in the intersection. Then apply n-1 times the rule CONJ to obtain that  $s \models \varphi$ .

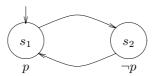

**Example.** Consider again the property automaton in Figure 1. We have  $\mu(x_1) = \bigcirc \Box \diamondsuit p$  and  $\mu(x_2) = p \lor \bigcirc \diamondsuit p$ . Consider the simple system *P* shown in Figure 4.

Fig. 4. A simple system

The intersection of the two automata appears in Figure 5. There are three strongly connected components:

- 1.  $\{(x_1, s_1), (x_1, s_2)\}.$

- 2.  $\{(x_2, s_2)\}.$

- 3.  $\{(x_2, s_1)\}.$

The latter two components are trivial. Moreover, the last one consists of a failed node. We obtain the following proof:

- 1. Using the FAIL axiom on the failed node  $(x_2, s_1)$ , we obtain  $s_1 \models p \lor \bigcirc \diamondsuit p$ .

- 2. Applying Succ to the node  $(x_2, s_2)$ , we obtain  $\begin{array}{c}

s_2 \longrightarrow \{s_1\} \\

\underline{s_1 \models p \lor \bigcirc \diamondsuit p} \\

\underline{s_2 \models p \lor \bigcirc \diamondsuit p}

\end{array}$

- 3. Applying line 1 as a premise to line 2, we obtain  $s_2 \models p \lor \bigcirc \diamondsuit p$ .

- 4. We apply the rule IND to the only strongly connected component in the graph,  $C = \{(x_1, s_1), (x_1, s_2)\}$ , where  $Exit(C) = \{(x_2, s_2), (x_2, s_1)\}$ . We obtain

$\begin{array}{c} s_1 \models p \lor \bigcirc \diamondsuit p \\ s_2 \models p \lor \bigcirc \diamondsuit p \\ s_1 \longrightarrow \{s_2\} \\ s_2 \longrightarrow \{s_1\} \\ \hline s_1 \models \bigcirc \Box \diamondsuit p \\ s_2 \models \bigcirc \Box \diamondsuit p \end{array}$

5. Applying lines 1, 3 as premises to line 4, we obtain  $s_1 \models \bigcirc \Box \diamond p$  and  $s_2 \models \bigcirc \Box \diamond p$

6. Using the rule CONJ, we obtain

$$\begin{aligned} s_1 &\models p \lor \bigcirc \Diamond p \\ s_1 &\models \bigcirc \Box \Diamond p \\ ((p \lor \bigcirc \Diamond p) \land \bigcirc \Box \Diamond p) \to \Box \Diamond p \\ s_1 &\models \Box \Diamond p \end{aligned}$$

7. Applying lines 1, 5 as premises to line 6, we obtain  $s_1 \models \Box \Diamond p$ .

**Fig. 5.** The intersection graph  $\mathcal{A}^{P}_{\neg\varphi}$

Consider the mutual exclusion system from Figure 2, and the checked property  $\Box \diamondsuit (cr_0 \lor cr_1)$ . The intersection graph appears in Figure 3. It includes a nontrivial SCC, whose states are encapsulated with a dotted line. These are the system states that are paired with the property automaton state  $x_1$ . The rest of the states are paired with  $x_2$ . There are four failed nodes, which have no successors.

The proof shows how the system progresses towards satisfying  $\diamond(cr_0 \lor cr_1)$ . Consider first the nodes outside the nontrivial SCC. From each such node, we progress into a failed node where either  $cr_0$  or  $cr_1$  hold. The proof proceeds from the failed nodes backwards, showing that for each node that contains an  $x_2$ component, we have  $s \models \diamond(cr_0 \lor cr_1)$ . The nontrivial SCC provides an induction over the execution of the system, hence obtaining  $P \models \Box \diamond(cr_0 \lor cr_1)$ . Note that we need only one application of the rule IND here, since there is only one nontrivial SCC.

#### 5 An Automatic Ranking Function

Together with the proof, we can construct a ranking function  $\rho$  that maps each strongly connected component in the intersection graph into a natural number. The ranking of an SCC measures the distance of the component from the bottom of the induced directed acyclic graph of SCCs. The ranking function provides additional intuition about the way the checked system progresses towards satisfying the checked property. In term of the constructed proof, it shows how the proof progresses towards the failed nodes. We denote by  $\rho(C)$  the rank of an SCC C, and further define  $\rho(t) = \rho(C)$  if  $t \in C$ .

The ranking function  $\rho$  must satisfy the following condition: if  $C \prec C'$  then  $\rho(C) > \rho(C')$ . In particular, if C is a trivial SCC consisting of a failed node, it is often convenient to set  $\rho(C) = 0$ .

Let m be the number of bits in the binary representation of the largest ranking constructed for a state in  $A^P_{\neg \varphi}$ . For any integer  $r \leq 2^m - 1$ , let  $bit_i(r)$ be the  $i^{th}$  bit in the m-bit binary representation of r. Let  $V_{aug}$  be the set V of system variables, augmented with a new variable whose value ranges over X, the set of  $A_{\neg \varphi}$ -states. This augmentation is needed since the same system state may have a different rank when combined with a different property automaton state.

For every rank r that is constructed, let  $states_r$  be a (propositional) formula over the state variables  $V_{aug}$  that describes the set of all (joint) states (x, s) such that  $\rho((x, s)) = r$ . Note that  $states_r$  can be obtained automatically from the above ranking construction.

The following formula,  $\gamma(V_{aug}, r_1, \ldots, r_m)$  represents the connection between states and their ranking.

$$\gamma = \bigvee_{r=1,\dots,2^m} (states_r \land \bigwedge_{i=1}^m (r_i = bit_i(r)))$$

Now, we can express each one of the bits in the binary representation of the ranking as a formula of the joint automata state.

$$\beta_i = \exists r_1, r_2, \dots, r_m \left( \gamma \wedge r_i \right)$$

Thus,  $\beta_i$  is true only in joint states for which the *i*th bit of the ranking function is 1. Finally, we can automatically obtain a formula  $\hat{\rho}$  as the ranking function, mapping a state (x, s) (or more precisely, the corresponding assignments to  $V_{aug}$ ) to its ranking  $\rho((x, s))$ . We assume that we can use in such a formula Boolean expressions that return the value 0 for *false* and 1 for *true*. A ranking formula  $\hat{\rho}(V_{aug})$  can be obtained as follows:

$$\hat{\rho} = \sum_{i=1,\dots,m} 2^{i-1} \times \beta_i.$$

Note that the formulas  $\beta_i$  can be simplified, e.g., using the help of a BDD package.

| $State\ formula$                             | $rank \ r$ | $bit_1(r)$ | $bit_0(r)$ |

|----------------------------------------------|------------|------------|------------|

| $cr_0 \lor cr_1$                             | 0          | 0          | 0          |

| $tr_0 \wedge tr_1$                           | 1          | 0          | 1          |

| $(tr_0 \wedge nt_1) \lor (nt_0 \wedge tr_1)$ | 2          | 1          | 0          |

| $nt_0 \wedge nt_1$                           | 3          | 1          | 1          |

**Example.** Consider for example a ranking for the intersection in Figure 3.

It is easy to see that the least significant bit of the binary representation,  $\beta_0$  can be expressed as  $(tr_0 \wedge tr_1) \vee (nt_0 \wedge nt_1)$ . The most significant bit  $\beta_1$  can be expressed as  $(nt_1 \wedge tr_0) \vee (nt_0 \wedge tr_1) \vee (nt_0 \wedge nt_1)$ .

The ranking function formula  $\hat{\rho}$  requires considerable simplification, before presenting the resulted expression to the user. For that, we can exploit the following options:

- We can use some additional conditions, regarding the relationship between the system variables. For example, in the mutual exclusion system, we can add the following conditions:  $(nt_0 \lor tr_0 \lor cr_0) \land (nt_1 \lor tr_1 \lor cr_1) \land \neg (nt_0 \land tr_0) \land \neg (nt_0 \land cr_0) \land \neg (tr_0 \land cr_0) \land \neg (nt_1 \land tr_1) \land \neg (nt_1 \land cr_1) \land \neg (tr_1 \land cr_1)$ .

- The definition of the ranking function gives us some freedom in assigning the actual ranks to SCCs (and their nodes). For example, in the mutual exclusion system, we decided to give a ranking of 0 to all the failure nodes. However, we could have decided to give a ranking of 0 to the nodes where  $(cr_0 \wedge tr_1) \lor (tr_0 \wedge cr_1)$ , and a ranking of 1 to the nodes where  $(cr_0 \wedge nt_1) \lor (nt_0 \wedge cr_1)$ .

- After finding the expressions for the different bits, we can attempt to collect together similar terms in order to simplify the ranking formula  $\hat{\rho} = \sum_{i=1,...,m} 2^{i-1} \times \beta_i$ . Terms that appear in different  $\beta_i$ 's should be grouped together, with their multiplication constants added together.

## 6 Conclusions

Model checking is mostly identified with finding errors. We presented an algorithm for the automatic construction of a proof that the checked property holds in the verified system. The proof is automatically obtained directly from a graph (of an automaton) that is generated by model checking. Such a proof may help in gaining more intuition about the verified system. The ability to automatically form such a proof can be further exploited to conclude new properties of the verified system.

The algorithm presented here can be added to model checking systems that are based on automata theory. In particular, the SPIN system [6] contains an implementation of the LTL translation algorithm in [5]. Acknowledgements. We would like to thank Elsa Gunter and Amir Pnueli for inspiring discussions about this subject. David Long has provided help with his OBDD package. It was brought to our attention that, in parallel with our work, Kedar Namjoshi has developed an algorithm for the automatic generation of proofs for the  $\mu$ -calculus [9].

## References

- 1. E. M. Clarke, E. A. Emerson, Design and synthesis of synchronization skeletons using branching time temporal logic. Workshop on Logic of Programs, Yorktown Heights, NY, 1981, LNCS 131, Springer-Verlag.

- G. Bhat, R. Cleaveland, O. Grumberg, Efficient on-the-fly model checking for CTL<sup>\*</sup>. Logic in Computer Science, 1995, San Diego, CA, 388-397

- 3. E. M. Clarke, O. Grumberg, D. Peled, Model Checking, MIT Press, 2000.

- E. A. Emerson, E. M. Clarke, Characterizing correctness properties of parallel programs using fixpoints, LNCS 85, Springer Verlag, Automata, Languages and Programming, July 1980, 169–181.

- R. Gerth, D. Peled, M. Y. Vardi, P. Wolper, Simple on-the-fly automatic verification of linear temporal logic, Protocol Specification Testing and Verification, 3–18, Warsaw, Poland, 1995. Chapman & Hall.

- G. J. Holzmann, Design and Validation of Computer Protocols, Prentice-Hall Software Series, 1992.

- R.P. Kurshan. Computer-Aided Verification of Coordinating Processes: The Automata-Theoretic Approach. Princeton University Press, Princeton, New Jersey, 1994.

- 8. Z. Manna, A. Pnueli, *The Temporal Logic of Reactive and Concurrent Systems:* Specification, Springer, 1991.

- 9. K. Namjoshi, Certifying model checkers, Submitted to CAV 2001.

- M. Y. Vardi, P. Wolper, An automata-theoretic approach to automatic program verification. Proc. 1st Annual Symposium on Logic in Computer Science IEEE, 1986.

# Model Checking if Your Life Depends on It: A View from Intel's Trenches

Rob Gerth

#### Strategic CAD Laboratories (SCL), Intel corp., USA rob.t.gerth@intel.com

**Abstract.** Hardware design is considered one of the traditional areas for formal (property) verification (FPV); in particular for symbolic model checking. Indeed, Intel, SUN, Motorola and IBM all develop and deploy model checking tools to ensure design correctness. On the other hand, hardware design is hostile territory because of the huge effort companies traditionally invest in classical testing and validation techniques which tend to be much more automated, require less sophistication from users and which will, in fact, discover many errors when deployed on such a scale. For these reasons FPV will never fully supplant traditional validation.

The real challenge lies in convincing processor design teams that diverting some of their validation resources to FPV leads to provably higher design quality. Complicating factors include the relatively high quality of traditional validation—at least within Intel—which raises the bar for FPV; and the fact that in high-performance processors design large parts of the RTL tends to remain unstable enough throughout the design to make it very hard to verify suitable micro-architectural abstractions. For these reasons, FPV within Intel traditionally targets the same RTL from which the schematics is derived and on which all traditional validation is performed.

Arguably the biggest (public) FPV success story within Intel is that of floating point hardware verification and it is illustrative to see how FPV is deployed in this area and how tool and methodology development is influenced.

The major challenge that we are now facing is to move formal verification upstream in the design flow. Not only because ever increasing microarchitectural complexity creates a strong demand for early verification on an algorithmic level, but also because the ever shortening design cycle forces formal verification to start much earlier in the design. It is here that hardware FPV and software verification start to merge and there are lessons to be learned for either side.

# Model-Checking Infinite State-Space Systems with Fine-Grained Abstractions Using SPIN

Marsha Chechik, Benet Devereux, and Arie Gurfinkel

Department of Computer Science, University of Toronto, Toronto, ON M5S 3G4, Canada. {chechik,benet,arie}@cs.toronto.edu

Abstract. In analyzing infinite-state systems, it is often useful to define multiple-valued predicates. Such predicates can determine the (finite) levels of desirability of the current system state and transitions between them. We can capture multiple-valued predicates as elements of a logic defined over finite total orders (FTOs). In this paper we extend automata-theoretic LTL model-checking to reasoning about a class of multiple-valued logics. We also show that model-checking over FTOs is reducible to classical model-checking, and thus can be implemented in SPIN.

## 1 Introduction

Currently, model-checking is essentially limited to reasoning about medium-sized finite-state models. Reasoning about large models, especially if these are not finite-state, is typically done using abstraction [CGL94]. Abstraction techniques, such as *abstract interpretation* [CC77], require the user to supply the mapping between concrete and abstract data types in their models. *Predicate abstraction*, introduced by Graf and Saidi [GS97], is a form of abstraction specified as a number of predicates over the concrete data. For example, if we are interested in checking whether x is always positive, we can define predicates x > 0 and  $x \leq 0$ , and use them to compute the abstract system. A number of researchers, e.g., [CU98,VPP00,BDL96,DDP99,SS99], explored the use of predicate abstraction.

However, boolean predicates often do not give the desired precision. For example, consider reasoning about a leader-election protocol, parameterized by N – the number of processes engaged in it. We can either set N to be a (small) constant, and define predicates on the exact number of processes that have agreed on the elected leader; or leave N as is, and define predicates such as "everyone agreed on the leader", "no one agreed on the leader", etc. In this situation we cannot ask questions about the likelihood of the agreement, whereas such questions may be desirable.

As an alternative, we propose modeling such systems using multiple-valued predicates, where their values form a linear order. In the above situation, we can assign different values to the level of agreement on the leader: "everyone agreed", "the agreement is likely", "no information is available", "the agreement is unlikely", "no one agreed", obtaining a linear order on the level of agreement. Furthermore, if we do not limit ourselves to classical logic, our model-checking procedure will distinguish between different values of agreement, e.g., between cases where no agreement has been reached and where complete agreement has not been reached, but the majority have agreed. Taking this reasoning one step further, we can assign values to transitions. Intuitively, a transition value is the *possibility* that it will be taken. Thus, we can potentially distinguish between paths that can always be taken, paths that can likely be taken, etc.

In fact, giving predicates values from a linear order can be useful in a variety of situations: (a) consensus-building, where the abstraction is over counting (e.g., the leader-election protocol mentioned above); (b) explicitly distinguishing between "regular" and "faulty" behaviors, where we may be interested in properties that hold always, and those that hold "most of the time", i.e., over "regular" behaviors; (c) rechecking a partial system after a change to it has been made, where we are interested in differentiating between possible effects of the change; (d) any situation where we want to assign "desirability" to a transition. This can happen in cases where we have varying tolerances, e.g., in analyzing families of SCR specifications [HJL96].

Note that using linear order-valued predicates does not increase the expressive power of our modeling language, since they can be encoded using a number of boolean predicates. However, such encoding results in cluttering the models with lots of auxiliary variables that bear no natural meaning, and, more importantly, greatly increases the sizes of the models, making model-checking less feasible [HK93].

Multiple-valued reasoning has been explored in a variety of domains. For example, a nine-valued logic is prescribed as a standard [IEE93] for VLSI design, where the interpretation of values is in terms of voltage thresholds. Other examples include databases [Gai79], knowledge representation [Gin87], and machine learning [Mic77]. However, most of the work concentrated on the 3-valued reasoning, with values "True", "Maybe" and "False". Melvin Fitting [Fit91,Fit92] has done seminal work in studying 3-valued modal logic, and our work on logic in this paper is somewhat similar to his. Three-valued logic has also been shown to be useful for analyzing programs using abstract interpretation [CD00,SRW99], and for analyzing partial models [BG99,BG00]. Bruns and Godefroid also proved that automata-theoretic model-checking on 3-valued predicates reduces to classical model-checking.

In this paper we give semantics to automata-theoretic model-checking over arbitrary finite linear orders. We define multiple-valued Büchi automata and multiple-valued LTL and show that such model-checking reduces to a classical problem, and thus can be implemented on top of SPIN. The rest of this paper is organized as follows: we review the definition of linear orders and define multiplevalued sets and relations over them in Section 2.  $\chi$ LTL, a multiple-valued extension of LTL, is defined in Section 3. Section 4 defines multiple-valued languages and Büchi automata. In Section 5 we show how to represent  $\chi$ LTL logic formulas

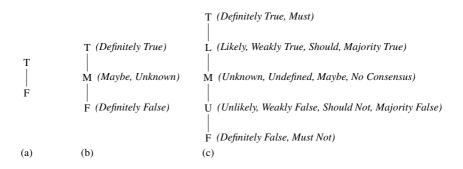

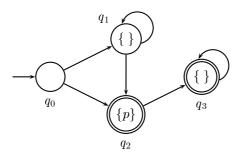

Fig. 1. (a) 2, the classical logic FTO; (b) 3, a three-valued logic FTO; (c) 5, a five-valued logic FTO and possible interpretations of its values.

as multiple-valued Büchi automata. Section 6 defines the model-checking problem on multiple-valued Büchi automata and shows that it reduces to a number of queries to a classical model-checker, such as SPIN. We conclude the paper in Section 7.

#### 2 Preliminaries

In this section we review the definition of logics based on total orders. We also define multiple-valued sets and relations over them.

#### 2.1 Finite Total Orders

A partial order is a relation which is reflexive, symmetric, and transitive. A partially ordered set, usually abbreviated poset, is a pair  $\mathcal{L} = (\mathcal{O}, \sqsubseteq)$  where  $\mathcal{O}$  is a set and  $\sqsubseteq$  a partial order defined on it. If, for all  $a, b \in \mathcal{O}$ , either  $a \sqsubseteq b$  or  $b \sqsubseteq a$ , then  $\sqsubseteq$  is a total order or linear order. We consider, for the purposes of this paper, only finite totally ordered sets, which we refer to as FTOs.

The operations of maximum and minimum are defined on FTOs as follows:

$a \sqcap b = a \Leftrightarrow a \sqsubseteq b$  (minimum)  $a \sqcup b = b \Leftrightarrow a \sqsubseteq b$  (maximum)  $b \sqcap a = a \Leftrightarrow a \sqsubseteq b$  (minimum)  $b \sqcup a = b \Leftrightarrow a \sqsubseteq b$  (maximum)

**Lemma 1.** Let  $(\mathcal{O}, \sqsubseteq)$  be an FTO. Then for all  $a, b, c \in \mathcal{O}$ ,

$$c \sqsubseteq a \sqcap b \Leftrightarrow (c \sqsubseteq a) \land (c \sqsubseteq b) \quad (\texttt{min-}\land) \\ c \sqsubseteq a \sqcup b \Leftrightarrow (c \sqsubseteq a) \lor (c \sqsubseteq b) \quad (\texttt{max-}\lor)$$

We further define  $\bot = \bigcup \mathcal{O}$  and  $\top = \bigsqcup \mathcal{O}$ .

Any FTO of height  $h^{\dagger}$  is isomorphic to the integers from 0 to (n-1) with the ordinary ordering. We call this isomorphism the *canonical isomorphism for the FTO* and denote it by  $\zeta_{\mathcal{L}}$ . The *difference* between two elements of an FTO is their absolute difference:

$$a \ominus b = |\zeta_{\mathcal{L}}(a) - \zeta_{\mathcal{L}}(b)|$$

and *negation* in the FTO can be defined in terms of difference:

$\neg a \triangleq \top \ominus a$  (def. of negation)

FTOs with this definition of negation satisfy the following properties:

$$\neg (a \sqcap b) = \neg a \sqcup \neg b \quad (\text{De Morgan}) \qquad \neg \neg a = a \qquad (\neg \text{ involution}) \\ \neg (a \sqcup b) = \neg a \sqcap \neg b \qquad a = b \Leftrightarrow \neg a = \neg b \quad (\neg \text{ bijective}) \\ \neg \bot = \top \qquad (\bot \text{ negation}) \qquad \neg \top = \bot \qquad (\top \text{ negation}) \\ a \sqsubseteq b \Leftrightarrow \neg a \sqsupseteq \neg b \quad (\neg \text{ antimonotonic})$$

In this paper we use multiple-valued logics whose truth values form an FTO. Conjunction and disjunction of the logic are defined as  $\sqcap$  and  $\sqcup$  (meet and join) operations of  $(\mathcal{O}, \sqsubseteq)$ , respectively, and negation is defined as the  $\neg$  operator of  $(\mathcal{O}, \sqsubseteq)$ . In fact, we will not distinguish between an FTO and a logic it defines, referring to both as  $\mathcal{L}$ . We also note that most of the usual laws of logic are obtained in  $\mathcal{L}$ , with the exception of the laws of Universality  $(a \sqcap \neg a = \bot)$  and Excluded Middle  $(a \sqcup \neg a = \top)$ .

Figure 1 presents several commonly-used FTOs: classical logic, a three-valued logic with uncertainty, and a five-valued logic with more degrees of uncertainty.

#### 2.2 Multiple-Valued Sets and Relations

Let  $\mathcal{L} = (\mathcal{O}, \sqsubseteq)$  be an FTO and D be some (finite) domain. We consider  $\mathcal{O}^D$ , the set of all total functions from D into  $\mathcal{O}$ , and refer to elements of  $\mathcal{O}^D$  as *multiple-valued subsets of* D, and, when D is clear from the context, just *multiple-valued sets* or MV-sets. We introduced this notion in [CDE01a], and briefly review it below.

**Definition 1.** Given multiple-valued sets  $A, B \in \mathcal{O}^D$ ,

| $x \in_{\mathcal{L}} A \triangleq A(x)$                                  | (MV-set membership)   |

|--------------------------------------------------------------------------|-----------------------|

| $x \in_{\mathcal{L}} A \cup_{\mathcal{L}} B \triangleq A(x) \sqcup B(x)$ | (MV-set union)        |

| $x \in_{\mathcal{L}} A \cap_{\mathcal{L}} B \triangleq A(x) \sqcap B(x)$ | (MV-set intersection) |

| $x \in_{\mathcal{L}} \overline{A} \triangleq \neg A(x)$                  | (MV-set complement)   |

Consider the multiple-valued set of Figure 2. In this example, we use the three-valued FTO **3** to model ambiguity about whether 0 is a positive integer. The MV-set is  $\mathbb{Z}^{+?} \in \mathbf{3}^{\mathbb{Z}}$ , where for all  $n \geq 1$ ,  $(n \in_{\mathcal{L}} \mathbb{Z}^{+?}) = \top$ ; for all  $n \leq -1$ ,  $(n \in_{\mathcal{L}} \mathbb{Z}^{+?}) = \bot$ ; and  $(0 \in_{\mathcal{L}} \mathbb{Z}^{+?}) = M$ .

Fig. 2. An example of a multiple-valued set over 3.

**Theorem 1.** [Gol99] Let D be a finite set, and  $(\mathcal{O}, \sqsubseteq)$  be an FTO. Define  $\sqsubseteq_{\mathcal{O}^D}$  as follows for any  $f, g \in \mathcal{O}^D$ :

$$f \sqsubseteq_{\mathcal{O}^D} g \Leftrightarrow \forall d \in D \cdot f(d) \sqsubseteq g(d).$$

Then  $(\mathcal{O}^D, \sqsubseteq_{\mathcal{O}^D})$  is an FTO, with MV-union and MV-intersection defined as join and meet, respectively.

The practical use of this result is that all of the properties defined for FTOs, such as the De Morgan rules and distributivity, carry over to MV-sets.

Given two sets P, Q, we can define a *multiple-valued relation* [CDE01a] on them as a multiple-valued subset of  $P \times Q$ , or an element of  $\mathcal{O}^{P \times Q}$ .

This work is, to our knowledge, the first use of valued subsets in formal verification; however, such theories are developed elsewhere [Eil78,Gol99].

#### 3 $\chi$ LTL

In this section we extend the semantics of LTL to allow reasoning over a given FTO  $\mathcal{L} = (\mathcal{O}, \sqsubseteq)$ , representing our multiple-valued logic. We refer to the resulting language as  $\chi$ LTL. Just like in classical propositional LTL, formulas in  $\chi$ LTL are built from a set *Prop* of values of atomic propositions and are closed under the application of propositional operators, the unary temporal connective  $\circ$  ("next") and the binary temporal connective  $\mathcal{U}$  ("until").  $\chi$ LTL is interpreted over multiple-valued computations. A computation is a function  $\pi : \mathbb{N} \to \mathcal{O}^{Prop}$  which assigns values from the logic  $\mathcal{L}$  to the elements of *Prop* at each time instant (natural number). For a computation  $\pi$  and a point  $i \in \mathbb{N}$ , we have:

$$\begin{aligned} \pi, i &\models_{\mathcal{L}} p &\triangleq p \in_{\mathcal{L}} \pi(i) \\ \pi, i &\models_{\mathcal{L}} \neg \varphi &\triangleq \neg(\pi, i \models_{\mathcal{L}} \varphi) \\ \pi, i &\models_{\mathcal{L}} \varphi \land \psi \triangleq \pi, i \models_{\mathcal{L}} \varphi \sqcap \pi, i \models_{\mathcal{L}} \psi \\ \pi, i &\models_{\mathcal{L}} \varphi \lor \psi \triangleq \pi, i \models_{\mathcal{L}} \varphi \sqcup \pi, i \models_{\mathcal{L}} \psi \end{aligned}$$

$\begin{array}{l} \varphi \, \mathcal{U} \, \psi = \psi \lor (\varphi \land \circ (\varphi \, \mathcal{U} \, \psi)) \\ \diamond \psi = \psi \lor \circ (\diamond \psi) \\ \Box \psi = \psi \land \circ (\Box \psi) \\ \varphi \, \mathcal{R} \, \psi = \psi \land (\varphi \lor \circ (\varphi \, \mathcal{R} \, \psi)) \end{array}$

**Fig. 3.** Properties of  $\chi$ LTL operators.

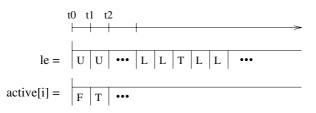

Fig. 4. A partial execution of the Leader Election protocol.

Now we define the temporal operators:

$$\begin{array}{l} \pi,i\models_{\mathcal{L}}\circ\varphi &\triangleq \pi,i+1\models_{\mathcal{L}}\varphi\\ \pi,i\models_{\mathcal{L}}\varphi\mathcal{U}\psi \triangleq \bigsqcup_{j\geq i} \bigl((\pi,j\models_{\mathcal{L}}\psi)\sqcap(\underset{i\leq k\neq j}{}\pi,k\models_{\mathcal{L}}\varphi)\bigr) \end{array}$$

The value of a property on a run is the value that it has in the 0th state of the run:

$$\pi \models_{\mathcal{L}} \varphi \ \triangleq \ \pi, 0 \models_{\mathcal{L}} \varphi$$

As usual,  $\Diamond \varphi = \top \mathcal{U} \varphi$ ,  $\Box \varphi = \neg \Diamond \neg \varphi$ , and  $\varphi \mathcal{R} \psi = \neg (\neg \varphi \mathcal{U} \neg \psi)$ . XLTL operators satisfy the expected LTL properties, for example, the fixpoint properties in Figure 3.

Consider the example in Figure 4. This figure presents partial execution of the Leader Election protocol specified using the five-valued logic 5. Let N be the number of processes (which we assume to be an even number), and K be the number that have agreed on the leader. We abstract K using the 5-valued predicate le ("leader elected") which is true when K = N, weakly true when (N/2) < K < N, undecided when K = N/2, weakly false when 0 < K < (N/2), and false when K = 0. Let active[i] indicate that the *i*th process is currently active. In this system,  $\pi, 0 \models_{\mathcal{L}} le$  is U,  $\pi, 0 \models_{\mathcal{L}} le \wedge active[i]$  is F ( $\perp$ ), and  $\pi, 0 \models_{\mathcal{L}} \neg active[i]$  is T ( $\top$ ). The value for le indicates that originally there was no consensus on the leader (U), then consensus started forming (L) and was reached (T). However, in the next state one of the processes changed its mind, and thus the consensus went back to L. For this run, the value of  $\diamond le$  is T, but the value of  $\diamond \Box le$  is L. Note that we get this value without the need to re-annotate our model under a different level of abstraction and rerun the check.

## 4 Multiple-Valued Languages and Automata

In the task of using multiple-valued logic for system specification and verification, it is natural to consider *multiple-valued formal languages* and *multiple-valued automata*. We introduce them in this section.

#### 4.1 Multiple-Valued Languages

Let  $\Sigma$  be a finite alphabet,  $\Sigma^*$  be the set of all *finite* words over  $\Sigma$ ,  $\Sigma^{\omega}$  be the set of all *infinite* words, and  $\Sigma^{\leq \omega} = \Sigma^* \cup \Sigma^{\omega}$ . We can catenate any two finite words, and consider the *empty string*  $\lambda$  as the identity for catenation:  $w\lambda = \lambda w = w$ . The empty string is contained in  $\Sigma^*$ , but not in  $\Sigma^{\omega}$ .

**Definition 2.** A multiple-valued language over an alphabet  $\Sigma$  is a multiplevalued subset of  $\Sigma^*$ , or an element in  $\mathcal{O}^{\Sigma^*}$ ; a multiple-valued  $\omega$ -language is an element in  $\mathcal{O}^{\Sigma^{\omega}}$ . A multiple-valued language X is proper if  $(\lambda \in_{\mathcal{L}} X) = \top$ .

We shall use the term "MV-language" to refer, indiscriminately, to any multiplevalued language or  $\omega$ -language, wherever the distinction is not important. An MV-language is an assignment of values to words. If  $\mathcal{O} = 2$ , then an MVlanguage is an ordinary formal language, where every word that is assigned value  $\top$  is considered to be in the language. The properness criterion assures that  $\lambda$  is contained in the language as the identity for catenation.

MV-languages are just MV-sets of words, so union, intersection, and complement are already defined on them. The standard language operation of *catenation* can be extended to the multiple-valued case, as given below.

**Definition 3.** Given  $X, Y \in \mathcal{O}^{\Sigma^*}$  and  $w \in \Sigma^*$ ,

$$w \in_{\mathcal{L}} XY \triangleq \bigsqcup_{\{u, v \mid w = uv\}} (u \in_{\mathcal{L}} X) \sqcap (v \in_{\mathcal{L}} Y) \text{ (MV-language catenation)}$$

Transitive closure (Kleene star) and infinite closure ( $\omega$ ) can be defined in terms of multiple-valued catenation.

Consider the two multiple-valued languages  $X = \{a \to T, ab \to L\}$  and  $Y = \{bc \to M, c \to U\}$ , defined on the logic **5**. We are interested in the value that *abc* has in *XY*. It can be formed either by catenating *a* and *bc*, with value  $T \sqcap M = M$ , or by catenating *ab* and *c*, with value  $L \sqcap U = U$ . By the definition, we take the maximum of those two values, making the value of  $abc \in_{\mathcal{L}} XY$  to be M.

#### 4.2 Multiple-Valued Automata

A multiple-valued finite automaton A takes any word  $w \in \Sigma^{\leq \omega}$  and computes its membership degree, a value in  $\mathcal{O}$ . Thus, an automaton corresponds to a multiple-valued language L(A). Details about multiple-valued automata on *finite* words (in the more general case, of semiring-valued languages) can be found elsewhere [Eil78]; our treatment of multiple-valued infinite words and their automata is, so far as we know, new, but it is a natural extension.

A multiple-valued Büchi automaton has transitions between states that take on some value ranging between  $\top$  or  $\perp$  of an FTO. This value, intuitively, is a *possibility* that a transition will be taken. Thus, we can assign possibilities to individual transitions and to infinite strings that the automaton receives.

**Definition 4.** A multiple-valued Büchi automaton, or  $\chi B$ üchi automaton, is a tuple  $(\mathcal{L}, Q, q_0, \Sigma, \Delta, F)$  where:

- $-\mathcal{L} = (\mathcal{O}, \sqsubseteq)$  is an FTO;

- -Q is a finite set of states;

- $-q_0$  is the unique initial state;

- $-\Sigma$  is a finite alphabet;

- $-\Delta \in \mathcal{O}^{\bar{Q} \times \Sigma \times Q}$  is the multiple-valued transition relation.  $\Delta(q, \alpha, q')$  gives the value of the transition from q to q' on symbol  $\alpha$ ;

- F is a set of accepting states.

The *runs* of the automaton are infinite sequences of states, always beginning with  $q_0$ . We define a projection of Q onto F as

$$\pi_F(q) = \begin{cases} q \text{ if } q \in F \\ \lambda \text{ otherwise} \end{cases}$$

which we extend to  $Q^{\omega}$ , and define the *accepting runs*  $\mathcal{AR}$  of the automaton to be the elements of

$$\{\sigma \mid \pi_F(\sigma) \in F^\omega\}.$$

Intuitively,  $\mathcal{AR}$  is the set of all runs in which some accepting state occurs infinitely often.

For a  $\chi$ Büchi automaton  $A, L(A) \in \mathcal{O}^{\Sigma^{\omega}}$  is the multiple-valued subset of  $\Sigma^{\omega}$  defined by the automaton. The value assigned by the automaton to a word  $w = w_0 w_1 w_2 \dots$  in  $\Sigma^{\omega}$  is given in terms of the accepting runs:

$$\left(w\in_{\mathcal{L}} L(A)\right) = \bigsqcup_{\sigma\in\mathcal{AR}} \lim_{i\in\mathbb{N}} \Delta(\sigma_i,w_i,\sigma_{i+1})$$

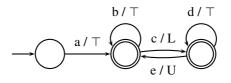

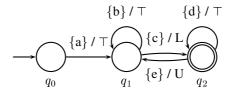

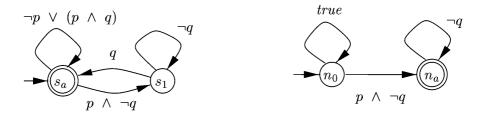

Consider the  $\chi$ Büchi automaton in Figure 5. This automaton assigns values from 5 to its inputs. In the input sequence  $abbcd^{\omega}$ , the prefix abb takes the automaton only through  $\top$ -valued transitions. Then, c follows an L-transition to an accepting state; after this occurs, the value of the whole sequence *cannot* exceed L. The automaton loops through the accepting state on the infinite sequence of d's, so this word is accepted with value L.

$\chi$ Büchi automata are similar in spirit to *Markov chains* [Fel68]. Markov chains also assign values, representing probabilities, to nonterminating finite-state computations, and have been used [VW86] to check probabilistic system specifications. Our approach is more *possibilistic*, motivated by the problem of

**Fig. 5.** An example  $\chi$ Büchi automaton.

requirements analysis. Given two independent events, the *probability* of the occurrence of at least one is the sum of their individual probabilities; but the *possibility* or *necessity* of at least one event occuring is the *maximum* of their individual possibilities.

#### 4.3 Composition

Our definitions of parallel composition, synchronous and asynchronous, are extensions of the standard construction [Tho90].

We start by defining synchronous parallel composition, or MV-intersection of languages. Let  $L_1$  and  $L_2$  be multiple-valued  $\omega$ -languages and  $A_1 = (\mathcal{L}, Q_1, q_0^1, \Sigma, \Delta_1, F_1)$  and  $A_2 = (\mathcal{L}, Q_2, q_0^2, \Sigma, \Delta_2, F_2)$  be  $\chi$ Büchi automata for  $L_1$  and  $L_2$ , respectively. We construct two classical automata,  $\hat{A}_i$  (for i = 1, 2), where  $\hat{\Delta}_i(q, \alpha, q')$  is true exactly if  $\Delta_i(q, \alpha, q') \neq \bot$ . Then we intersect the two classical automata, creating  $\hat{A}_{12} = (Q_1 \times Q_2 \times \{0, 1, 2\}, (q_0^1, q_0^2, 0), \Sigma, \hat{\Delta}_{12}, F_1 \times F_2 \times \{2\})$ . Finally, we create the *multiple-valued intersection* of the two  $\chi$ Büchi automata by transforming  $\hat{A}_{12}$  into a  $\chi$ Büchi automaton  $A_{12}$ with the new multiple-valued transition relation:

$$\Delta_{12}((q,r,j),\alpha,(q',r',j')) = \begin{cases} \Delta_1(q,\alpha,q') \sqcap \Delta_2(r,\alpha,r') \\ \text{if } \hat{\Delta}_{12}((q,r,j),\alpha,(q',r',j')) \\ \bot \text{otherwise} \end{cases}$$

for all  $j \in \{0, 1, 2\}$ .

**Theorem 2.** The value that  $A_{12}$  gives to a word w is the same as its value in  $L_1 \cap_{\mathcal{L}} L_2$ .

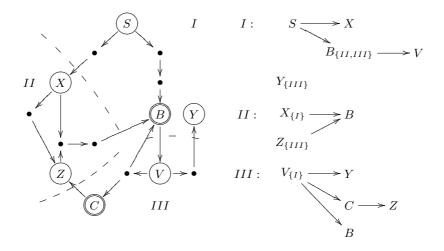

Figure 6 illustrates the intersection construction. The first automaton gives the value  $\top$  to  $ac^{\omega}$  and L to  $ba^{\omega}$ ; the second gives value  $\top$  to  $ba^{\omega}$ . Every other word evaluates to  $\bot$ . In the intersection,  $ac^{\omega}$  becomes  $\bot$ , and  $ba^{\omega}$  evaluates to the minimum of L and  $\top$ , namely L. Note that  $(q_2, r_1)$  is labelled with 2, making it an accepting state in the intersection automaton, because it is a final state in *both*  $A_1$  and  $A_2$ .

We proceed to define asynchronous composition on two  $\chi$ Büchi automata with (possibly different) alphabets and the same logic.

**Fig. 6.** Intersection of  $\chi$ Büchi automata. (c) shows the intersection of automata in (a) and (b).

**Definition 5.** Let  $A_1 = (\mathcal{O}, Q_1, q_0^1, \Sigma_1, \Delta_1, F_1)$ ,  $A_2 = (\mathcal{O}, Q_2, q_0^2, \Sigma_2, \Delta_2, F_2)$ be two  $\chi B \ddot{u} chi automata$ . The asynchronous composition  $A_1 \parallel A_2 = (\mathcal{O}, Q_1 \times Q_2, (q_0^1, q_0^2), \Sigma_1 \cup \Sigma_2, \Delta, F)$  of the two automata has the following transition relation:

$$\begin{aligned} \Delta \big( (q_1, q_2), \alpha, (q'_1, q_2) \big) &= \Delta_1(q_1, \alpha, q'_1) & \text{if } q_1 \neq q'_1 \\ \Delta \big( (q_1, q_2), \alpha, (q_1, q'_2) \big) &= \Delta_2(q_2, \alpha, q'_2) & \text{if } q_2 \neq q'_2 \\ \Delta \big( (q_1, q_2), \alpha, (q_1, q_2) \big) &= \Delta_1(q_1, \alpha, q_1) \sqcup \Delta_2(q_2, \alpha, q_2) & \text{otherwise} \end{aligned}$$

A state  $(q_1, q_2)$  of the asynchronous composition is considered final if either  $q_1$  or  $q_2$  are final, so

$$F = (F_1 \times Q_2) \cup (Q_1 \times F_2)$$

#### 5 Conversion between $\chi$ LTL and $\chi$ Büchi Automata

In this section we describe how to convert between  $\chi$ LTL formulas, defined in Section 3 and  $\chi$ Büchi automata. Our algorithm is based on the classical LTL to Büchi automata conversion algorithm presented in [GPVW95]. As in [GPVW95], we start by defining *Generalized*  $\chi$ Büchi Automata and Labeled Generalized  $\chi$ Büchi Automata (LG $\chi$ BA).

**Definition 6.** A Generalized XBüchi automaton (GXBA) is a tuple  $(\mathcal{L}, Q, q_0, \Sigma, \Delta, \mathcal{F})$  where  $\mathcal{L}, Q, q_0, \Sigma$  and  $\Delta$  are as in ordinary XBüchi automata, but  $\mathcal{F} = \{F_1, F_2, \ldots, F_k\}$  is a set of k sets of accepting states. Each set  $F_i$  has the projection  $\pi_{F_i}$  defined for it, and the accepting runs are those where at least one element from each  $F_i$  appears infinitely often:

$$\mathcal{AR} = \{ \sigma \mid \sigma \in q_0 Q^{\omega} \land \forall i \le k \cdot \pi_{F_i}(\sigma) \in F_i^{\omega} \}$$

**Definition 7.** A Labeled Generalized  $\chi$ Büchi Automaton (LG $\chi$ BA) is a tuple  $(\mathcal{L}, Q, q_0, \Sigma, \Delta, \mathcal{F}, Lab)$  where:

- $-\mathcal{L} = (\mathcal{O}, \sqsubseteq)$  is an FTO;

- -Q is a finite set of states;

- $-q_0$  is the unique initial state;

- $-\Sigma = \mathcal{O}^{Prop}$  is an alphabet consisting of all multiple-valued sets over the set Prop of propositional symbols;

- $\Delta \in \mathcal{O}^{Q \times Q}$  is a multiple-valued transition relation;

- $\mathcal{F} = \{F_1, F_2, \dots, F_n\}$  is a set of sets of accepting states;

- Lab:  $Q \to 2^{Prop \cup \neg Prop}$  is a labeling function that assigns a subset of  $Prop \cup \neg Prop$  to every state.

The set of accepting runs  $(\mathcal{AR})$  for a LG $\chi$ BA is defined the same as for a Generalized  $\chi$ Büchi automaton given in Section 4.

Notice that each element  $\alpha \in \Sigma$  is a total function from Prop to  $\mathcal{O}$ . We extend this function to elements of  $\neg Prop$  by defining  $\alpha(\neg p) \triangleq \neg \alpha(p), \forall p \in Prop$ . Let  $\hat{\alpha} : 2^{Prop \cup \neg Prop} \to \mathcal{O}$  be a set-wise extension of  $\alpha$ , defined as

$$\hat{\alpha}(D) \triangleq \underset{d \in \mathcal{D}}{\alpha(d)}$$

(set-wise extension)

For a Labeled Generalized  $\chi$ Büchi automaton  $A, L(A) \in \mathcal{O}^{\Sigma^{\omega}}$  is the multiplevalued subset of  $\Sigma^{\omega}$  defined by the automaton. The value assigned by the automaton to a word  $w = w_0 w_1 w_2 \dots$  in  $\Sigma^{\omega}$  is given in terms of the accepting runs:

$$w \in_{\mathcal{L}} L(A) = \bigsqcup_{\sigma \in \mathcal{AR}} \lim_{i \in \mathbb{N}} \Delta(\sigma_i, \sigma_{i+1}) \sqcap \hat{w}_i \left( Lab(\sigma_{i+1}) \right)$$

where  $\hat{w}_i$  is the set-wise extension of  $w_i$ .

Given an LTL property  $\varphi$ , the algorithm in [GPVW95] constructs a Labeled Generalized Büchi automaton in two major steps. In the first step, it uses the syntactic structure of the formula to construct a graph G = (V, E) together with three labeling functions, *New*, *Old*, and *Next*, that assign a subset from a *closure* of  $\varphi$  to each node of G. In the second step, the algorithm constructs an automaton, using G to define its basic structure, and the labeling functions to define its accepting states and state labels. The resulting Generalized Labeled Büchi automaton accepts a word if and only if the word satisfies  $\varphi$ . This automaton can be easily converted into a Büchi automaton with a polynomial blowout in its size.

Since  $\chi$ LTL is syntactically equivalent to LTL, we reuse the graph construction part of the algorithm in [GPVW95]. Thus, given a  $\chi$ LTL property  $\varphi$ , our algorithm starts by constructing a graph G = (V, E) and the node labeling functions *New*, *Old*, and *Next* using the procedure in [GPVW95]. However, we modify this procedure to ensure the correct handling of  $p \wedge \neg p$  (not necessarily  $\bot$ ) and  $p \vee \neg p$  (not necessarily  $\top$ ), where p is any propositional formula. The algorithm

**Fig. 7.** A LGXBA corresponding to  $\Diamond p$ .