# Lecture Notes in Computer Science

3965

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich. Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Moshe Y. Vardi

Rice University, Houston, TX, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

# Marco Bernardo Alessandro Cimatti (Eds.)

# Formal Methods for Hardware Verification

6th International School on Formal Methods for the Design of Computer, Communication, and Software Systems, SFM 2006 Bertinoro, Italy, May 22-27, 2006 Advanced Lectures

#### Volume Editors

Marco Bernardo Università degli Studi di Urbino "Carlo Bo" Istituto di Scienze e Tecnologie dell'Informazione Piazza della Repubblica 13, 61029 Urbino, Italy E-mail: bernardo@sti.uniurb.it

Alessandro Cimatti Istituto Trentino di Cultura (ITC) Istituto per la Ricerca Scientifica e Tecnologica (IRST) Loc. Panté, Povo, 38050 Trento, Italy E-mail: cimatti@irst.itc.it

Library of Congress Control Number: Applied for

CR Subject Classification (1998): D.2, D.3, F.3, C.3, C.2.4

LNCS Sublibrary: SL 2 – Programming and Software Engineering

ISSN 0302-9743

ISBN-10 3-540-34304-0 Springer Berlin Heidelberg New York

ISBN-13 978-3-540-34304-2 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© Springer-Verlag Berlin Heidelberg 2006 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 11757283 06/3142 5 4 3 2 1 0

# **Preface**

This volume presents a set of papers accompanying the lectures of the sixth edition of the International School on Formal Methods for the Design of Computer, Communication and Software Systems (SFM).

This series of schools addresses the use of formal methods in computer science as a prominent approach to the rigorous design of computer, communication and software systems. The main aim of the SFM series is to offer a good spectrum of current research in foundations as well as applications of formal methods, which can be of help for graduate students and young researchers who intend to approach the field.

SFM 2006 was devoted to formal techniques for hardware verification and covered several aspects of the hardware design process, including hardware design languages and simulation, property specification formalisms, automatic test pattern generation, symbolic trajectory evaluation, BDD-based and SAT-based model checking, decision procedures, refinement, theorem proving, and the verification of floating point units.

The opening paper by Bombieri, Fummi, and Pravadelli provides a general view on simulation-based modeling and verification strategies for developing embedded systems. In particular, the paper is focussed on describing state-of-the art co-simulation approaches and verification strategies based on fault simulation and assertion checking.

The paper by Drechsler and Fey reviews the basic concepts and algorithms for the postproduction test of integrated circuits. The then authors present an advanced SAT-based tool for automatic test pattern generation.

The paper by Claessen and Roorda concentrates on simulation-based model-checking techniques, which do not need to represent the states of the design, but only the values that flow through each signal. In particular, the authors introduce a high-performance simulation-based model-checking technique called symbolic trajectory evaluation.

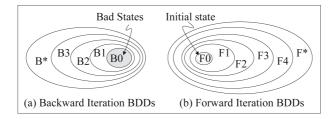

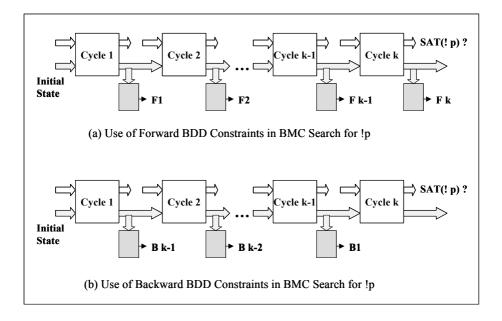

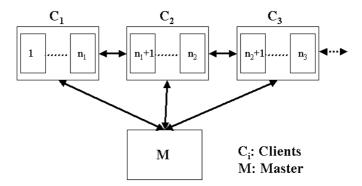

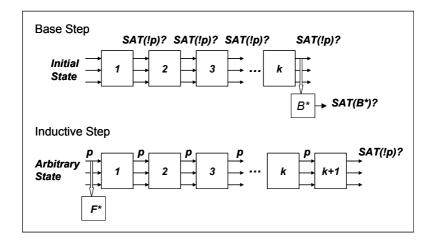

The paper by Cabodi and Murciano overviews binary decision diagrams (BDD) and their application in formal hardware verification. The paper by Gupta, Ganai, and Wang illustrates instead a promising alternative to BDD-based symbolic model-checking methods that relies on Boolean satisfiability (SAT).

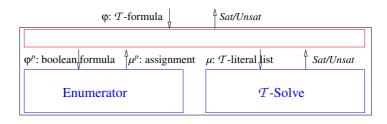

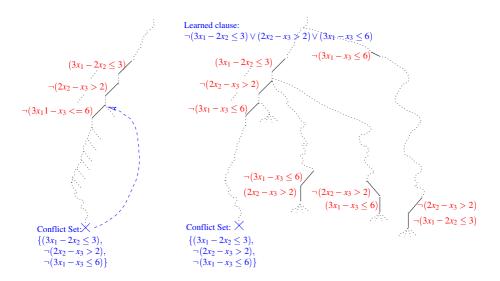

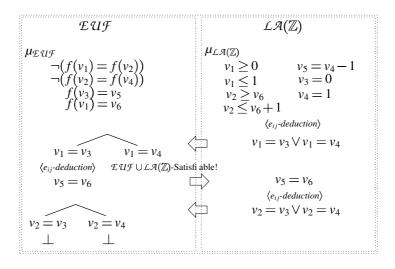

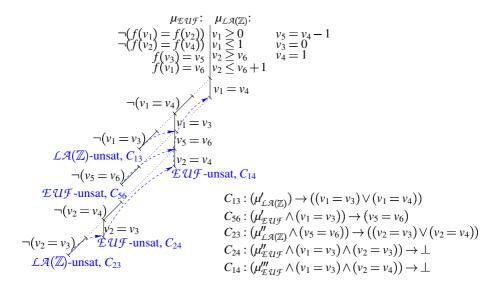

The paper by Cimatti and Sebastiani deals with decision procedures for verification problems that can be represented as satisfiability problems in some decidable fragments of first-order logic. The authors focus on integration techniques for combining technology for propositional satisfiability and solvers able to deal with the theory component.

The paper by Manolios addresses theorem-proving systems and shows how they can be employed to model and verify hardware using refinement. Theorem

#### VI Preface

proving is considered also in the closing paper by Harrison, where it is used for the verification of floating-point algorithms.

We believe that this book offers a comprehensive view of what has been done and what is going on worldwide in the field of formal methods for hardware verification. We wish to thank all the lecturers and all the participants for a lively and fruitful school. We also wish to thank the entire staff of the University Residential Center of Bertinoro (Italy) for the organizational and administrative support.

May 2006

Marco Bernardo and Alessandro Cimatti SFM 2006 Directors

# **Table of Contents**

| Nicola Bombieri, Franco Fummi, Graziano Pravadelli                                                               | 1   |

|------------------------------------------------------------------------------------------------------------------|-----|

| Automatic Test Pattern Generation  Rolf Drechsler, Görschwin Fey                                                 | 30  |

| An Introduction to Symbolic Trajectory Evaluation  Koen Claessen, Jan-Willem Roorda                              | 56  |

| BDD-Based Hardware Verification  Gianpiero Cabodi, Marco Murciano                                                | 78  |

| SAT-Based Verification Methods and Applications in Hardware Verification  Aarti Gupta, Malay K. Ganai, Chao Wang | 108 |

| Building Efficient Decision Procedures on Top of SAT Solvers  *Alessandro Cimatti, Roberto Sebastiani            | 144 |

| Refinement and Theorem Proving  Panagiotis Manolios                                                              | 176 |

| Floating-Point Verification Using Theorem Proving  John Harrison                                                 | 211 |

| Author Index                                                                                                     | 243 |

# Hardware Design and Simulation for Verification

Nicola Bombieri, Franco Fummi, and Graziano Pravadelli

Università di Verona, Strada le Grazie 15, 37134 Verona, Italy {bombieri, fummi, pravadelli}@sci.univr.it

Abstract. The development of more and more complex embedded systems constitutes a very challenging task for EDA experts, due to their HW/SW-mixed nature joint to the high demand for quality and reliability. Recently, both industrial engineers and academic researchers have developed a very large number of techniques for dynamic verification in terms of co-simulation, which, in particular, address the different nature of hardware and software components of an embedded system. However, a widely accepted methodology does not exist. Thus, this paper is intended to provide a general view on simulation-based modeling and verification strategies for developing embedded systems. In particular, the paper is focussed on describing state-of-the art co-simulation approaches and verification strategies based on fault simulation and assertion checking.

#### 1 Introduction

An embedded system can be defined as a computer that is a component in a large system and that relies on its own microprocessor [1, 2]. Thus, it can be viewed as a mix of cooperating hardware and software parts, which are able to provide a wider and more adaptable set of complex functionality with respect to ASIC and ASIP, without requiring the large amount of resources needed by general purpose systems. Examples of embedded systems include controllers for industrial processes, automotive appliances, medical devices, multimedia portable systems, data acquisition systems, etc. The main characteristic of embedded systems is the reactivity: they must continuously react to asynchronous input events. Furthermore, since such systems are particularly suited in real-time contexts, where tasks must be performed within a given deadline, predictability (determinism) can become a key issue. In such application domains, the adaptability is required too. In fact, when determinism is required, it must be preserved also when the system is operating in a highly non-deterministic environment.

Even if embedded systems historically operate with bounded resources, as memory and computational power, nowadays they are increasing their resources, leveraging on the improvements of silicon technology. In fact, technology scaling always offers new opportunities and new challenges to system designers. Moore's law predicts a doubling on systems complexity (expressed as the number of transistors per integrated circuits) every couple of years. Chips composed of tens of million of gates, and therefore of more than a hundred million transistors, are

today feasible in commercial production lines with a 90 nm technology. Thus, a system that yesterday was developed as a set of several chips connected on a printed board, nowadays can be developed in a single chip, composed of several complex subsystems integrated on the same silicon die. Such a system is known as System-on-a-Chip (SoC) and it represents a strong paradigm for embedded systems [3]. Several advantages make this way to develop a system very attractive for system developers. When the system complexity increases, the number of pins also tends to increase, so it becomes simpler and cheaper to connect many subsystems on a single chip than several chips on a printed board. Furthermore, the on-chip wire capacitances are smaller than their on-board counterparts, and this implies higher performance and lower energy requirements.

On the other side, developing a single, very complex, SoC poses many challenges for the developers. First, when the technology scales, designers have to face new issues, like the short channel effects [4] and the crosstalking problem [5]. Even if such problems are usually faced by foundries, the system developers must be aware of them, because high-level design choices can have a strong impact on lower levels of abstraction.

Another issue is represented by the power quest [6]. The energy budget for embedded systems is usually strictly limited. Those systems are often batterybased, and the improvements on the battery capacitance cannot keep pace with the increase on the system complexity. Thus, to obtain a usable system (in terms of activity time), the designer must take into account the optimization of the energy consumption. Such an optimization is pressing also for the higher power density involved in modern integrated circuits. As the gate size reduces and the power consumption increases, the power density to dissipate strongly increases. Current high-performance systems, as the state of the art microprocessors, have already reached very high power densities, and, in the near future, power density is expected to increase even more. Those levels of power density imply a high quantity of heat to dissipate and this fact causes an increasing cost of the package to use. Moreover, the higher temperature of functioning has a direct impact on the reliability and on the life time of the systems. Therefore, the energy consumption minimization of a system is nowadays a key issue for the developer, which has to keep it under control at every stage of the design process.

Also the development time spent is a key factor that must be accurately considered when an embedded system is designed. The growing complexity of the development of such systems pushes towards component reuse [2]. Designers are bound to use use pre-designed subsystems, called *Intellectual Property* (IP) components, as far as possible. Such components can be of several kinds, ranging from cell libraries over blocks which perform a standard task (e.g., MPEG decoder, USB controller, etc.), to very complex components, like processor cores (ARM, MIPS and other families of microprocessors are commercially available as pre-designed IP cores). IP components are specified at several levels of abstraction, so that they can be used during all steps of the system design flow. Moreover, they are often customizable and configurable, thus designers can use them in their own systems, tuning them according to their needs.

The modern approach of design reuse introduces the concept of platform [7]. A platform is a fully defined interconnection structure and a collection of customizable IP blocks. A developer can start from an available platform and configure it choosing the parameters for the given IP blocks, adding new hardware devices, and removing useless IP blocks. A platform is then conceived as a highly reusable system that a designer can adapt to his own needs and purposes.

The need of taking into account all the previous challenges, and the intrinsic heterogeneous nature of embedded systems (HW and SW) makes the development of such systems a harder task compared with more traditional digital systems. In particular, the high demands for quality and reliability for embedded systems have led to complementary quality assurance efforts: hardware engineers have developed techniques for verification in terms of co-simulation, which, in particular, addresses the different nature of hardware and software components. Thus, these techniques are tailored for design and verification flows which comprises dedicated models for the hardware and the software parts.

In this context, the paper is intended to provide a review of design and verification techniques based on simulation for developing embedded systems. The paper is organized as follows. Section 2 describes a typical embedded system design flow. Section 3 is devoted to present techniques for simulation and co-simulation. Section 4 focuses on verification approaches which exploit testbenches and assertions, and the related issues. Section 5 reports some experimental results for the verification techniques presented in Section 4. Finally, concluding remarks are summarized in Section 6.

# 2 Design Modeling

The design of an embedded system is a very challenging task which involves the cooperation of different experts: system architects, SW developers, HW designers, verification engineers, etc. Each of them operates on different views of the system starting from a very abstract informal specification and refining the model through the abstraction layers reported. At every level of abstraction, a model of an embedded system can be viewed as a black box that processes the information received at its inputs to produce corresponding outputs. This I/O mapping defines the behavior of the system.

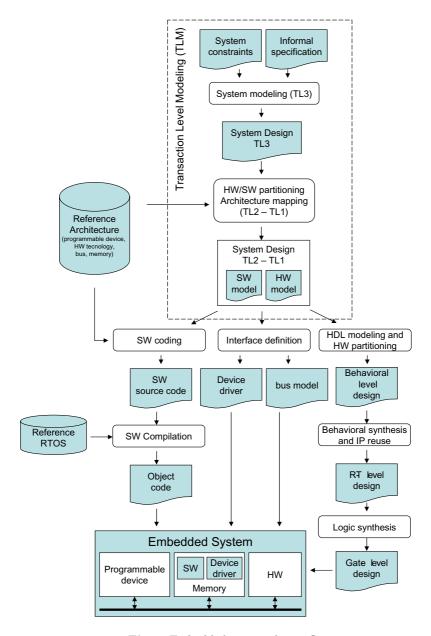

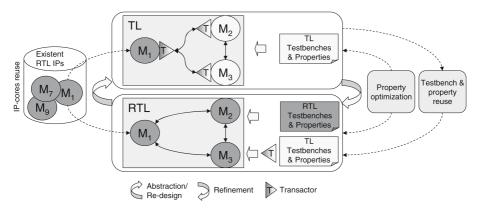

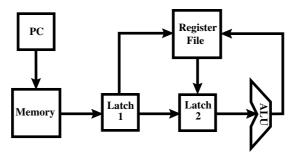

Figure 1 represents the classical design modeling flow where system level is refined by applying the new transactional level modeling (TLM) style [8]. A TLM-based design flow starts from an abstract system description and it evolves toward more detailed implementations till it gets to RTL. In particular, verification activity involves three main phases: first, the design implemented at the higher abstraction level is validated considering the system functionality; then, once the design is optimized following architecture exploration and performance analysis, it is validated taking into account the temporal behavior. Finally, whenever a step of the refinement flow implies a change in the system design, a further verification check is required in order to preserve the golden model functionality ascertained at the preceding step.

Fig. 1. Embedded system design flow

In spite of its name, transaction-level does not denote a single level of description; rather, it refers to a group of abstraction levels, each varying in the degree of functional or temporal details used and expressed.

A common agreement on terminology for TLM levels is still missing so far. Different interpretations (and terminology for the same concepts) have been

| Level | Use                                                                                                                                                                        | Features                                                                                                                                                                                                                                                                                                                 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TL3   | Executable specifications and first level of functional partitioning of data and control. System proof of concepts.                                                        | Implementation architecture-abstract.     Untimed functionalities modeling.     Event-driven simulation semantics.     Point-to-point Initiator-Target connection.     Abstract data types.                                                                                                                              |

| TL2   | Hardware architectural performance and detailed behavior analysis. HW/SW partitioning and co-development. Cycle performance estimation.                                    | Mapping ideal architecture into resource-constrained world.     Memory/Register map accurate.     Event driven simulation with time estimation.     Bit-width and transfer-size constrained data types to allow mapping to bus bursts or fragments of bursts.     Split, pipelined with time delays.                     |

| TL1   | Detailed analysis and low level SW development. Modeling CA interfaces for abstract simulation models of IP blocks such as embedded processors. CA performance simulation. | Clock-accurate protocols mapped to the chosen HW interfaces and bus structure.     Interface pin are hidden.     Byte-accurate data Transactions have internal structure (protocols, data, clock).     Transactions map directly to bus cycles.     Parametizable to model different bus protocol and signal interfaces. |

Fig. 2. TLM levels use and features

proposed by both industry and academia [8, 9, 10, 11]. However, factoring out common elements, key concepts are:

- 1. To implement a system at higher level means to implement the system in a more abstract way, that is to leave implementation details in order (mainly) to speed-up simulation for functional verification purposes.

- 2. To implement a system at lower level means to add implementation details to the system in order to simulate it in a more accurate way (for performance analysis purpose).

Hence, taking OCP-IP definition as reference, main use and features of every TLM level (e.g., TL3, TL2, and TL1) are summarized in Figure 2.

SystemC, as a broad-range level of abstraction modeling language, well addresses TLM. However, lack of established standards and methodologies means that each organization adopting TLM has to invent its own usage methodologies and API's. In addition to this redundant cost, these methodologies easily differ, making IP exchange and reuse more difficult. In this context, OSCI TLM library [12] based on SystemC represents a valuable set of templates and implementation rules aiming at establishing a reference for TLM API's implementation.

A typical TLM-based SoC design flow consists of the following steps.

- System modeling (TL3). Informal specification and system constraints are analyzed to provide a system level model of the design. At this level, there is no distinction between the HW components and the embedded SW. Indeed, the embedded system is considered as an interconnection of independent functional blocks which communicate by using blocks of words (messages) or shared memory. Implementation details like communication

protocols, delay analysis, computation algorithms, etc. are not taken into consideration. The most important issues of system modeling are represented by efficiency (i.e., the model must be quickly developable), flexibility (i.e., the model must be easily adaptable to explore different design implementations), and functionality (i.e., the behavior of the system must reflect the informal specification and it must satisfy the system constraints). Finite state machines (FSMs) [13], Labeled Transition Systems [14], Kripke structures [15], Petri nets [16, 17], process networks [18], etc. are valuable alternatives to formally model the functionality of embedded systems at such a level. The adoption of such semantic models makes the system level a good target for formal verification issues. However, to evaluate different architectural alternatives and to carry out performance analysis, semantic models are typically translated into simulatable descriptions. In this context, SystemC [19] is a very suitable language for system level modeling<sup>1</sup>: it joins the flexibility of C++ and the standard features of the traditional hardware description languages (HDLs), like VHDL [20], Verilog [21], etc.

- HW/SW partitioning and architecture mapping (TL2, TL1). The system level description is then mapped onto an architecture to obtain a transactional level model. This requires to decide which tasks will be implemented by SW and which ones by HW. The partitioning is actually a critical design choice, since there is no unique way to decide which task must be mapped into HW and which ones into SW. Moreover, some decisions about the configuration of the final system must be taken. In particular, the designers must select the following components:

- the programmable device where the SW will run;

- the memory model;

- the HW/SW communication architecture and the bus typology;

- the HW technology (ASIC, FPGA, etc.) where HW tasks will be mapped.

HW/SW partitioning and architecture mapping provides a transactional level model where the communication is completely separated from computation. The focus is on the data rather than on the way transfer is executed. At this level, simulation is used intensively for evaluating different architectures. Thus, the transactional model aims at minimizing the amount of events and the information processed during simulation in order to reduce the verification time. SystemC represents an attractive alternative also at the transactional level, since it allows one to describe very accurately both SW and HW components. In this way, HW/SW partitioning is simplified, because functional tasks can be moved from SW to HW and viceversa without the need of code translations, which are required when two different languages are used to model SW and HW components.

<sup>&</sup>lt;sup>1</sup> SystemC is a C++ class library which can be used to define methodologies to effectively model software algorithms, hardware architectures, and HW/SW interfaces. The class library includes a simulation engine (the *SystemC kernel*) that can be linked with the user descriptions. This allows us to obtain a single executable which exhibits the behavior of the modeled system.

- SW coding. After partitioning, SW and HW parts follow a different design flow. In particular, SW tasks are implemented by using a programming language (C/C++ represents an immediate solution when SystemC is adopted at system and transactional levels), and typical SW engineering techniques are used to optimize the resulting code. At this level, SW developers consider the HW part as a black box which communicates with SW via device drivers. Thus, SW coding must take into account constraints depending on the programmable device selected during the architecture mapping, and constraints depending on the communication interface.

- SW compilation. After the coding, the SW is compiled to object code. The compilation process generally depends on a Real Time Operating System (RTOS) which is selected to take care of load distribution, task scheduling, and communication with the HW interface. However, in some cases, RTOS may be absent, and the SW directly interacts with the device driver.

- Interface definition. Splitting the design tasks in HW components and pieces of SW introduces the need for an interface between the two parts that, often, is not specified in the initial requirements. This interface has to translate the timing information from the SW to the HW, and viceversa, because HW and SW rely on very different timing models. The HW model is typically event driven, while the SW model is cycle based, assuming it is executed by a programmable device. For this reason, the design of the interface between SW and HW parts is one of the most challenging task in the embedded system design flow. It requires to implement the device drivers for the programmable devices where the SW runs, and the communication bus to connect HW components, memory and programmable devices. The device drivers represent the interface between the RTOS and the HW components. Its purpose consists of hiding the HW to the SW layers by providing a set of functions to control the operation of the peripheral devices. Complementary, the purpose of the bus consists of defining the communication protocol taking into account many parameters like cost, bandwidth, reliability, etc..

- HDL modeling and HW partitioning. The HW model generated at the transactional level must be refined and optimized by executing different synthesis steps to obtain a gate-level description. Historically, the highest level of abstraction for HW components is represented by the behavioral level. The HW model is implemented by using an HDL focussing on the logic function of the HW components and ignoring implementation details. Moreover, the HW model is possibly partitioned into various interacting modules that better characterize the different HW units. Some books dealing with Electronic Design Automation (EDA) [22] make a more accurate classification and refer to this level as the functional level, while a behavioral level model is intended as a functional representation of the design coupled with a description of the associated timing relations. Any of these two abstraction levels keeps the complexity of digital system models quite low, allowing their rapid simulation.

- Behavioral synthesis and IP reuse. The functional/behavioral model of each HW component is further refined into a Register Transfer Level (RTL)

model by means of behavioral synthesis. The functionality of the design is decomposed and represented by a structural connection of combinational and sequential components (generally described as finite state machines with datapath (FSMD) [23]). At this level, IP reuse is performed too. Thus, already existing components are connected with new ones to provide the final RTL model. IP reuse sensibly decreases the time-to-market and it allows designers to concentrate the effort in implementing the very critical functionality of the system.

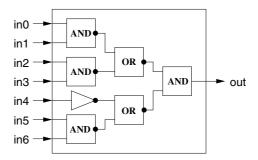

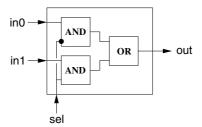

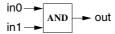

- Logic Synthesis. Finally, logic synthesis is used to translate the RTL model to a gate-level model, where the design is mapped into a structural view of primitive components (AND, OR, flip-flop, etc.) from which the physical mask can be easily generated to physically produce the circuit.

A verification/testing phase is mandatory after each step of the embedded system design flow to avoid the propagation of errors between the different abstraction levels. Indeed, synthesis is a dangerous process since it may introduce further bugs. This can be due to different causes: incorrect use of synthesis tools, incorrect code writing style that may prevent the synthesis tool to adequately infer the required logic, bugs of the synthesis tool, etc..

Thus, most of the publications focusing on the field of EDA start claiming the importance of verification [24] and testing [22] for shipping successful embedded systems. While the purpose of testing is to verify that the design was manufactured correctly, verification aims at ensuring that the design meets its functional intent before manufacturing. In particular, functional verification of embedded systems is the process of ensuring that the logical design of the system satisfies the architectural specification by detecting and removing every possible design error. As digital systems become more complex with each generation, verifying that the behavior is correct has become a very challenging task. Between 60% and 80% of the design group effort is now dedicated to verification [24]. The trend is particularly crucial for embedded systems, which are composed of a heterogeneous mix of hardware and software modules, and where the presence of design errors in the early phases of the design flow may lead to a complete failure of time-to-market fulfillment. In this context, both formal verification and simulation-based verification represent effective solutions to remove design errors.

There exist formal verification approaches to deal with the analysis and check of each of the grey products in Fig. 1. On the contrary, since one needs executable specifications to do simulation, simulation-based verification plays a predominant role in the later stages of the design process, i.e. once a design is already available, while formal verification must do most of the work at the border with the higher levels of abstraction. Typical abstraction-bridging verification tasks include checking a system level design vs. constraints or abstract specifications, checking the behavioral level design vs. partial models, checking component design vs. behavioral properties. Of course, the different approaches cover different aspects, thus they belong to different communities of scientists (like requirement engineering at the specification level, code analysis around a compilation task,

etc.). Indeed, advanced design process methodologies always foresee verification loops when working on a single artefact (e.g., to get the system constraints or the system level design right), and verification approaches for the transformations from one or more intermediate products to another one (e.g. given a system level design and a reference architecture, get the architecture-specific incarnation of that model right).

As we see, a large area of the design flow is common ground between simulation-based verification and formal verification, indicating a large potential for synergies between the two techniques which are still insufficiently exploited.

# 3 Design Simulation

Dynamic verification faces the correctness of a design by means of simulation-based techniques. In dynamic verification the model functionality is essentially verified by generating a high number of input stimuli (test set) that are simulated to observe the behavior of the design under verification at primary outputs. The test set generated at a specific abstraction level can be re-used (and possibly incremented) at the lower levels after each synthesis step up to manufacturing test.

Traditional simulation-based approaches can be adopted to verify the whole embedded system before HW/SW partitioning, as well as, HW and SW components separately after HW/SW partitioning. However, the most challenging task is to perform *co-verification* between HW and SW components. The integration and the synchronization of HW and SW modules requires a permanent control of consistency and correctness that can be efficiently achieved only by exploiting a co-simulation environment.

#### 3.1 Co-simulation Approaches

Co-simulation becomes a mandatory step after HW/SW partitioning. For this reason, several co-simulation platforms [25, 26, 27, 28, 29, 30, 31, 32] have been developed in the past years. In spite of the variety of architectural targets, performance efficiency, and description languages, we can classify these different solutions in three main categories: homogeneous, heterogeneous, and semi-homogeneous co-simulation environments.

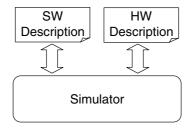

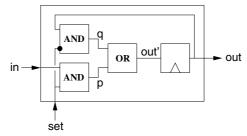

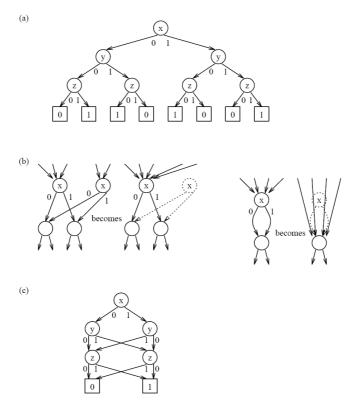

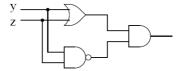

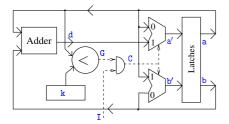

Homogeneous Environments. Homogeneous environments use a single engine for the simulation of both HW and SW components (see Fig. 3). The Ptolemy [25] and Polis [26] environments are pioneering works in that direction. In these approaches, homogeneity is achieved by abstracting away the distinction between hardware and software parts that are described as functional blocks. Homogeneous environments simplify the design modeling and they provide good simulation performance. However, they are suitable only in a very initial phase of the design, prior to HW/SW partitioning, since the HW and SW sides needs different techniques and different tools when the abstraction level decreases toward a real implementation.

Fig. 3. A homogeneous co-simulation environment

Fig. 4. A heterogeneous co-simulation environment

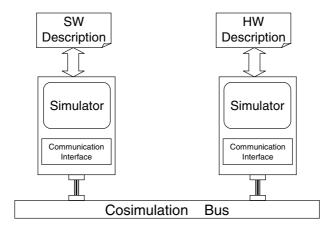

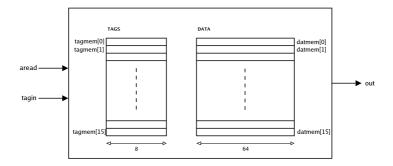

Heterogeneous Environments. Heterogeneous environments ensure a more accurate tuning between HW and SW components in comparison to homogeneous ones. This allows us to use a level of abstraction lower than the behavioral for HW and to evaluate the SW in its compiled (binary code) form. Such a binary code is obtained, from the high level SW description, using standard tools as a compiler, an assembler and a linker (see Fig. 1).

Most of the heterogeneous frameworks essentially address the same problem: how to efficiently link an event-driven hardware simulator and a cycle-based Instruction Set Simulator  $(ISS)^2$  (see Fig. 4). In order to model the connection between HW components and the microprocessor, where the SW will be executed, a communication channel (a bus) is needed. However, such a bus causes the reduction of the simulation speed, because it requires to model the signals involved in the communication. Thus, the resulting simulation is very slow.

Earlier HW/SW co-simulation frameworks [29, 30, 31] were mainly focused on HW described in several hardware description languages, like Verilog, VHDL or SystemC, and on software developed in various programming languages, like C, C++, Java, etc.

<sup>&</sup>lt;sup>2</sup> An ISS provides an accurate simulation of a programmable device allowing to verify SW before hardware is available.

All these heterogeneous approaches are quite similar in that their main effort aims at solving the issue of controlling and synchronizing two (or more) simulation engines. This heterogeneous style is sub-optimal in terms of simulation performance and ease of integration, since there is the burden of the communication between two very different engines. However it was the only possible choice when VHDL or Verilog was the highest possible description level for modeling HW. Some commercial tools, such as Mentor Graphics Seamless [28] and Synopsys Eaglei [27], also provide heterogeneous co-simulation capabilities. However, they only allow HW/SW co-simulation at bus level, where each bus transaction involves all signals necessary to accomplish the bus function, thus degrading the co-simulation performance.

Semi-Homogeneous Environments. The advent of design flows based on SystemC allowed the definition of efficient semi-homogeneous approaches [33, 34, 35, 36, 37], where the bus is not modeled at signal level. Rather, the bus is usually modeled with a small number of simple functions which provide information on the time required by the communication, without the need to evaluate each signal. By using such bus abstractions, the model results less accurate compared with a heterogeneous description where the bus is completely modeled, but the simulation speed is considerably faster. Moreover, in a semi-homogeneous approach, the accuracy is higher than the one obtained with an unpartitioned (homogeneous) description. Thus, the semi-homogeneous environments lie between the heterogeneous and the homogeneous ones, exploiting both their benefits, and allowing us to reach an optimal tradeoff between accuracy and simulation speed.

Semi-homogeneous approaches are homogeneous from the language point of view, since both HW and SW are described using C++ constructs (note that SystemC is simply a C++ library). This definitely simplifies the implementation of the initial model, as well as the subsequent HW/SW partitioning. However, these approaches are heterogeneous from the simulation point of view, since HW and SW can be executed using different simulators: the SystemC simulation kernel for the HW components and an ISS for the SW programs.

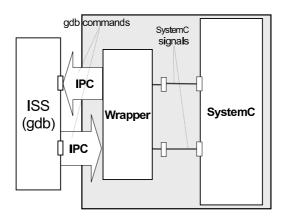

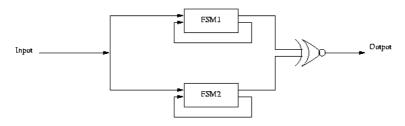

In this way, a more accurate performance estimation can be achieved, since the heterogeneous model reflects closely the final embedded system. All these environments are based on two basic issues (see Fig. 5):

- Interprocess communication (IPC). IPC is a software mechanism to allow different processes to communicate, even on different computers. It is used to realize the communication between the ISS, where the SW part runs in its binary form, and the SystemC simulator, that models the HW part. The simulators run as distinct processes on a host system.

- Bus wrapper. A wrapper is a SW layer which allows an existing piece of software to interact with an environment that is different from its originally intended one. The bus wrapper allows the use of a high level model of the bus within an environment where the SW model is cycle-accurate and the HW is modeled at a signal-accurate level of abstraction. Such a bus wrapper

ensures synchronization between the system simulation and the ISS, and it translates the information coming from the ISS into cycle-accurate bus transactions.

Most of these approaches [33, 34, 35] define a custom interface between the bus wrappers and the ISS. This makes the integration of new processor cores within the co-simulation framework harder, because the ISS needs to be modified to support the IPC primitives defined by the co-simulation system. This issue is addressed in [32], where a standardized interface between the bus wrapper and the ISS is proposed. It is based on the remote debugging primitives of GDB [38], which is both an instruction-level debugger and an ISS. In this way, any ISS that can communicate with GDB (that is, basically any, since GDB is a SW application) can also become part of a system-level co-simulation environment. The approach of [32] still suffers from some performance bottlenecks, since the ISS and the SystemC simulators evolve in lock-step, because the synchronization is driven by the host operating system via IPC.

In [36] the authors solve some limitations of previous approaches by proposing two alternatives co-simulation methodologies that allow a SystemC description of hardware and an ISS to efficiently co-execute. The two proposed solutions differ with respect to the simulation kernel (SystemC or ISS) that drives the co-simulation. The aim is to reduce the overhead of the IPC calls, which are very expensive in terms of time. When the master is the HDL simulator, the reduction of the IPC calls can be achieved by using and optimizing the bus wrapper, in order to minimize the amount of data exchanged between the two engines. On the other side, when the master is the ISS, it is possible to exploit the system calls of the RTOS. In fact, a device driver can be added to the RTOS, and the communication between SW and HW is handled by the software, invoking the device driver routines.

The timing synchronization is also an important issue in a co-simulation environment. Both simulators, the ISS and the HW simulator, have their own timing

Fig. 5. A semi-homogeneous co-simulation environment based on SystemC and ISS

information. Forcing the two sides to remain strictly synchronized can be too burdening for the performance. However, relaxing too much the synchronization, can impact the simulation accuracy. Several tradeoffs between accuracy and performance are addressed in the literature [39, 40, 41]. It is possible to annotate the SW execution delay into the application (and RTOS) code [39, 40], or to add a channel between the simulators in order to exchange timing information [41]. The latter approach allows better portability, since it is independent of the used RTOS. Furthermore, it allows a fine tuning of the performance/accuracy tradeoff, because the granularity of the exchanged timing information can be varied.

#### 4 Simulation for Verification

Simulation represents the main verification technique when the functionality of large heterogeneous embedded systems has to be verified. In particular, simulation techniques for embedded systems verification are classified in two main categories:

- Simulation by testbenches.

- Assertion-based verification.

Next sections present the key concepts that distinguish the two techniques. Moreover, some approaches are described to evaluate the quality of verification carried out by using testbenches and assertions. Finally, a transaction-based verification (TBV) approach is presented to show how testbenches and assertions defined at higher levels of abstraction (e.g., at transaction level) can be reused at lower levels (e.g., at RTL).

#### 4.1 Simulation by Testbenches

Simulation techniques based on testbenches essentially validate the model functionality by dynamically generating a high number on input stimuli (test set) that are simulated to observe the behavior of the design under verification (DUV) at primary outputs. What we need to perform such a dynamic verification is: a simulatable model of the design, a simulator, a testbench to apply stimuli to the primary input of the design, and a "method to establish the correctness" of the design with respect to the results of the simulation. Generally, the stimuli generator and the simulation engine are integrated in a single SW application, called automatic test pattern generator (ATPG).

While the first three ingredients of dynamic verification are almost straightforward, the last one is the crucial aspect. If state explosion is the big problem

of formal verification, the big problem of simulation is represented by the lack of

exhaustiveness of the verification process. Thus, like for formal verification, dynamic verification is very good in finding bugs, but it cannot ensure their absence.

Simulation can hypothetically provide an exhaustive answer to the problem of

design correctness only if the set of all possible input stimuli, applied to the design, results, after design simulation, in a set of values for the primary outputs

consistent with the set of expected values. Unfortunately, this is almost impossible for two reasons: the set of expected values is typically not available, and

the set of input stimuli for sequential circuits is exponentially large in time and space. Thus, the quality of dynamic verification, and in particular the quality of the generated set of stimuli, is measured by means of *code coverage* or *fault coverage*. Depending on which of these two strategies is used, we can distinguish between two kinds of dynamic verification: *logic simulation* and *fault simulation*.

**Logic simulation.** In logic simulation, the quality of the set of stimuli is measured by using code coverage. This is a class of metrics that has been used in software engineering [42] for quite some time to analyze whether test suites cover the required functionality. The most popular metrics adopted in logic simulation are: statement coverage, condition coverage and path coverage.

- Statement Coverage. It measures how much of the total lines of code are executed by the test set. To bring the statement coverage metric up to 100%, a desirable goal, it is necessary to understand what conditions are required to cause the execution of the uncovered statements. Then, it is necessary to understand why they never occurred. It is because the test set does not contain a stimulus able to activate the condition or it is because the condition can never occur? In the first case, a larger number of (or higher quality) test cases must be generated. On the contrary, if the condition can never occur, the code in question is effectively unreachable. Thus, either the code (and the condition) could be removed, or the design requires some most general refinement to allow the activation of the condition.

- Condition Coverage. It measures the various ways paths through the code are executed. Consider for example an if statement whose condition is ((a < 10) or (a > 20)). The then part of such a statement can be executed in two ways: when the value of a is less than 10 (first term of the condition) and when the value of a is greater than 20 (second term of the condition). Thus, it is evident that the statement coverage of a code can be 100%, while the condition coverage is lower. To increase condition coverage, it is necessary to identify the possible terms of conditions that are not executed, and if these terms can never be excited or they cannot be activated by the current test set.

- Path Coverage. It measures all possible ways you can execute a sequence of statements. Again it is important to determine the possible conditions that cause the uncovered path to be executed, and if these conditions can never occur or they cannot be activated by the current test set. Full 100% path coverage is very difficult to achieve, since the number of paths in a sequence of statements grows exponentially with the number of control-flow statements.

What does 100% code coverage means? Not much, it indicates how thoroughly the generated test set exercises the source code, but it does not provide precise indications about the correctness of the DUV. Nevertheless, code coverage can help to identify possible corner cases that are not exercise by the testbench, and that can be symptoms of design errors.

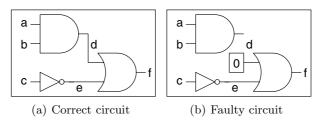

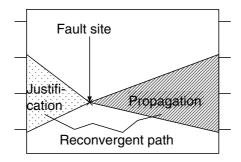

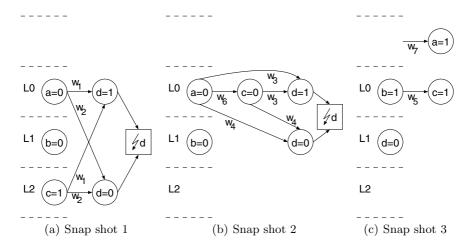

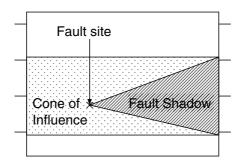

Fault simulation. Traditional code coverage metrics derived from SW testing represent a low cost popular solution. However, they are based on controllability information, i.e., the activation of statements, branches or sequences of statements, and they do not address observability requirements, i.e., to see whether effects of possible errors activated by tests can be observed at the DUV outputs. The fact that a statement with a bug has been activated by input stimuli does not mean that the observed outputs will be incorrect. An alternative approach is represented by the use of high-level fault models [43], which include the characteristics of both coverage metrics and logic-level fault models [44]. Thus, fault simulation consists of simulating a design in presence of logical faults, which emulate the effect of physical faults on the behavior of a system description. Faults can be modeled by means of different fault models, targeting various kind of errors that may affect a design, depending on the considered abstraction level. Independently from its typical implementation (perturbed assignment, operator substitution, mutants, saboteurs, etc.), an high-level fault provides an abstraction of a possible design error, since it produces perturbed DUV behaviors. Thus, the analysis of its nature allows an effective verification of the expected and unexpected behavior of the DUV, particularly when faults are directly injected into TL or RTL code, which is very familiar to the designer.

Comparing the fault simulation results with those of the fault-free simulation of the same design, simulated by using the same test set, we can determine the fault coverage as the ratio between the number of faults detected by the test set and the number of simulated faults. In such a way, the fault coverage is used as a metrics to evaluate the quality of testbenches as well as to reveal design errors. Achieving 100% fault coverage is generally harder than 100% statement or condition coverage. Then, stimuli generators targeted to fault coverage allow a wider exploration of the DUV state space. Thus, they provide better test cases with respect to ones obtained by using traditional coverage metrics. For this reason, fault simulation is generally preferred to logic simulation. Indeed, as for code coverage, we cannot completely ensure the correctness of the design by relying on the fault coverage. In fact, even a test set which achieves 100% fault coverage may still fail to detect faults modeled by a different fault model.

#### 4.2 Assertion-Based Verification

Functional verification based on assertions represents a valuable alternative to fault simulation [45]. Assertion-based verification (ABV) joins formal verification and simulation based verification to provide a more powerful and easy way to verify complex digital systems. To test these complex systems, too much time is spent constructing tests as design deficiencies are discovered, requiring test-benches to be rewritten or modified, as the previous testbench code did not address the newly discovered complexity. This process of working through the bugs causes defects in the testbenches themselves. ABV dramatically improves the efficiency of verifying correct behavior, detecting bugs and fixing bugs throughout the design process. Thus, more and more it is proposed into SoC verification methodologies.

In ABV, assertions are the central focus of the verification process; they detect bugs and guide testbenches in the stimuli production. An assertion, sometimes called a checker or monitor, is a precise description of what behavior is expected when a given input is presented to the design. It raises the level of verification from RTL to TL where users can develop tests and debug their designs closer to design specifications. Consequently, design functions are exercised efficiently (with minimum required time) and monitored effectively by detecting hard-to-find bugs. This methodology is called assertion based verification, since the assertions are the primary basis for ensuring that the DUV meets the criteria of design quality. ABV supports two methods: dynamic verification using simulation, and formal or semi-formal verification using model checking. In this second case, for historical reasons, the term property is usually adopted instead of assertion. However, the terms assertion and property are interchangeable, thus, in the following we use the more traditional term property.

Similarly to simulation by testbenches, ABV can prove the presence of bugs, but not their absence. Indeed, a design which satisfies all the defined properties is not guaranteed to be correct. In fact, the verification engineers can forget to written some properties, missing a complete verification. Thus, a design implementation that satisfies an incomplete set of properties cannot be considered bug-free. For this reason, a mechanism is needed to evaluate the quality of the defined properties, as well as a metric is used to evaluate the quality of testbenches for simulation. In this case, we use the term property coverage to indicate the percentage of the DUV behaviors checked by the defined properties.

Different papers [46, 47, 48, 49, 50] have been proposed to address the problem of property coverage. The majority of them [46, 47, 48, 49] propose formal method-based methodologies which statically analyze the effectiveness of properties in covering all states of the DUV. The main limitation of such techniques is represented by the state explosion problem that may arise in case of mediumlarge DUVs.

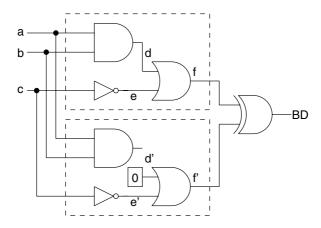

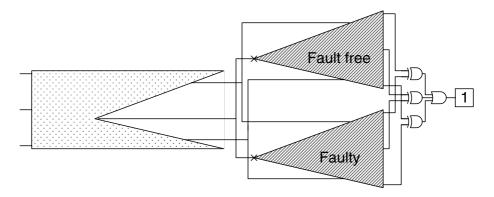

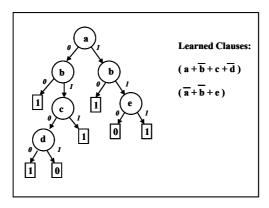

A different approach based on dynamic verification is presented in [50], where the property coverage is computed by analyzing, via simulation, the property capability of detecting DUV perturbations. In this case, the proposed property coverage methodology is applied on a set of properties which hold on the DUV, and an high-level fault model is used to generate different perturbations that modify the original functionality of the DUV implementation. The presence of a detectable fault implies that the behavior of the perturbed implementation differs from the behavior of the unperturbed one. Thus, while the set of properties is satisfied by the original unperturbed implementation, at least one of them should be refuted if checked on the perturbed implementation. On the contrary, the set of defined properties is unable to completely explore the DUV state space, thus it is incomplete. Summarizing, the property coverage methodology proposed in [50] can be described as follows:

- 1. a checker is generate for each defined property, by using for example FoCs [51];

- 2. the DUV is perturbed by using an high-level fault model to obtain a set of faulty implementations whose behavior differs from the fault-free one;

3. faulty implementations are simulated and their behavior is monitored by the checkers. Fault f is *covered* by property p if its checker fails during the simulation of the faulty implementation corresponding to f.

If a checker fails in presence of a fault f, the corresponding property p is able to distinguish between the faulty and the fault-free DUVs. This means that p covers the logic cone of the DUV that may be affected by f. Thus, according to the selected fault model, the property coverage  $C_P$  of a set of properties P is defined as:

$$C_p = \frac{\text{\# of faults covered by at least one property } p \in P}{\text{\# of generated perturbations}}.$$

(1)

All faulty implementation, whose behavior differs from the faulty-free one, must be covered by the property set, i.e. property coverage must achieve 100%. A lower property coverage is symptom that the property set is incomplete, and new properties must be added to addresses the uncovered perturbations.

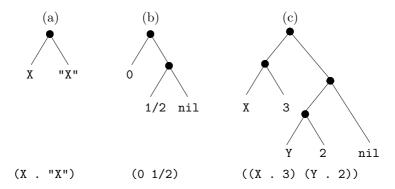

#### 4.3 Reuse by Transactor-Based Verification

Fault simulation and ABV are generally faster than formal verification techniques, and they allow to effectively verify large systems reducing the risk of incurring in the state explosion problem. This motivates the recent trend of proposing design and verification methodologies based on TLM, simulation and ABV (see Figure 6). However, such a tendency should not leave out of consideration the concept of reuse to further save time. Reuse has to be intended in two directions: from TL to RTL and viceversa. In the first case, verification engineers are interested in reusing testbenches and properties, once the TL components are refined into RTL descriptions. On the contrary, the second case is motivated by the fact that many vendors provide standard IPcores together with corresponding verification kits including testbenches and properties. In this way, already

Fig. 6. Reuse of IP-cores, testbenches and properties in a mixed TL-RTL design and verification flow

existing IP-cores can be composed and integrated with new ones to create different and more complex systems. However, already existent IP-cores are generally available at RTL, while new components are modeled at transaction level. Thus, TL-RTL mixed descriptions are becoming very common in practice to quickly obtain high-level design implementations.

The benefits deriving from the reuse of testbenches and properties for ABV moving through all transactional levels till to RTL and the reuse of RTL IP-cores in a TLM context are evident. However, this arouses new challenges for both designers and verification engineers. In fact, it is evident the lack of methodologies and tools to automatically derive the RTL implementation, once the TL design has been carried out. The refinement process from TL to RTL is much more difficult than logic synthesis from RTL to gate level. A synthesizable RTL design contains all information required by the synthesis tool to generate the corresponding gate-level netlist. On the contrary, a TL description is very far from including the implementation details which must be added at RTL. Then, a fully automatized process to convert TL designs into RTL implementations is still an utopia. For this reason, it is mandatory that new design and verification methodologies are proposed in order to efficiently check the correctness of the TL-to-RTL manual conversion.

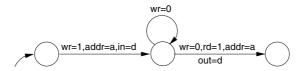

In this context, some approaches based on Transactor-based Verification (TBV) have been recently proposed from both EDA companies and academic researchers [52, 53, 54, 55]. Despite of technical details, all of them exploit the concept of transactor to allow a mixed TL-RTL co-verification (Triangle shape in Figure 6). A transactor works as a translator from a TL function call to an RTL sequence of statements, i.e., it provides the mapping between transaction-level requests, made by TL components, and detailed signal-level protocols on the interface of RTL IPs. Thus, testbenches and properties, defined to check the TL design, can be directly reused, through the transactor, to verify the RTL implementation. This avoids time-consuming and error-prone manual conversion of testbenches and properties moving from TL to RTL.

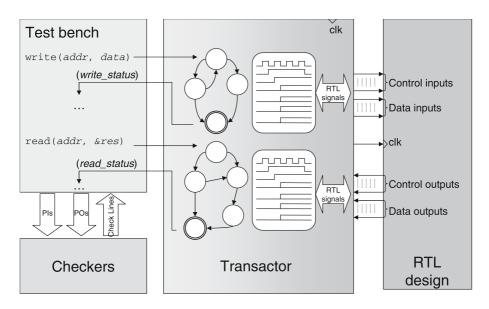

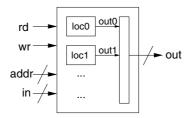

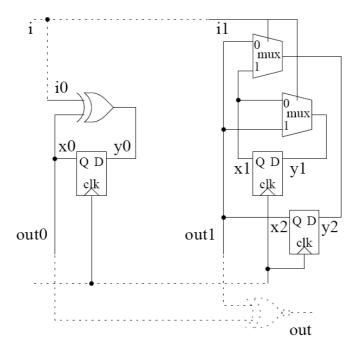

Figure 7 shows how the transactor is exploited to reuse TL testbenches and assertions on the RTL design [52,53]. The testbench carries out one transaction at time, composed by two TL function calls (write() and read()). First, data are provided to the RTL design by means of write(addr, data). The transactor converts the write() call to the RTL protocol-dependent sequence of signals required to drive control and data inputs of the design under verification. Moreover, the write status is reported to the testbench to notify about successes or errors. Then, the testbench asks for the DUV result by calling read(addr, &res). The transactor waits until the DUV result is ready by monitoring the output control ports, and, finally, it gets the output data. Then, testbench can carry on with the next transaction. If property checking is desired, the parameter of the function calls (addr, data, write\_status, &res, read\_status), which represent inputs and outputs of the RTL computation, are provided to the checkers. The testbench is modeled at transaction level, thus, properties are checked when write() and/or read() return according to the aim of properties.

Fig. 7. The role of the transactor in TBV

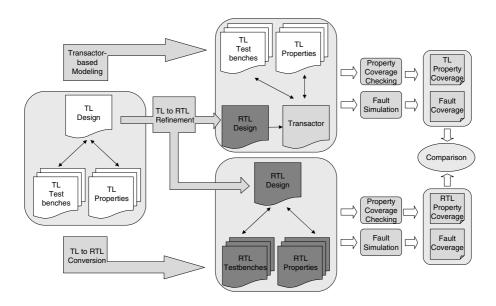

Fig. 8. Evaluation methodology flow

The effectiveness of the TBV with respect to a fully RTL verification, which requires to manually convert TL testbenches and properties into RTL ones, has been proved in [56]. The comparison methodology is summarized in Figure 8. The TL design is refined in an equivalent RTL description by following a standard

semi-automatic TL design flow. Then, in the upper side, the RTL module is embedded in the transactor-based verification architecture, where it interacts with TL testbenches and TL properties through the transactors. In this way, both the simulation engine and the ABV infrastructure are unchanged moving from TL to RTL. On the contrary, in the lower side of the Figure, the RTL description communicates directly with ad-hoc RTL testbenches. Moreover, a model checker is used to verify the RTL properties manually derived from the TL properties. Such a twofold evaluation methodology, based on fault coverage and assertion/property coverage, shows that the transactor-based verification is not only valuable for time savings and conversion error avoidance, but also because it is at least as effective as RTL verification. Next sections describes the theoretical basis upon which the TBV evaluation methodology relies.

#### 4.4 Testbench Reuse

A general high-level fault model is considered to theoretically show that reusing TL testbenches by means of a transactor allows to detect the same set of faults detectable by applying a testbench directly to the RTL model. This conjecture relies on the following definitions and theorem.

**Definition 1.** Given the implementation,  $\mathcal{I}$ , of the DUV, a set of faults,  $\mathcal{F} = \{f_1, \ldots, f_n\}$ , a set of perturbed implementations,  $\mathcal{I}_{\mathcal{F}} = \{\mathcal{I}_f | f \in \mathcal{F}\}$ , the environment,  $\mathcal{E}$ , where  $\mathcal{I}$  is embedded, and the set of FSM retroactive networks originated by  $\mathcal{E}$ ,  $\mathcal{N}_{\mathcal{I}\mathcal{E}} \cup \mathcal{N}_{\mathcal{I}\mathcal{F}\mathcal{E}}$  3, where  $\mathcal{N}_{\mathcal{I}\mathcal{F}\mathcal{E}} = \{\mathcal{N}_{\mathcal{I}f\mathcal{E}} | f \in \mathcal{I}_{\mathcal{F}}\}$ , a fault  $f \in \mathcal{F}$  is:

**Detectable** if there is at least an input sequence,  $\iota = (i_1, \ldots, i_n)$ , such that at least one output of  $\mathcal{I}$  differs from the respective output of  $\mathcal{I}_f$  when  $\iota$  is simultaneously applied to  $\mathcal{I}$  and  $\mathcal{I}_f$ . We say that  $\iota$  is a test sequence for f on  $\mathcal{I}$ .

$\mathcal{E}$ -detectable if there is at least an input sequence  $\iota = (i_1, \ldots, i_n)$ , such that at least one output of  $\mathcal{N}_{\mathcal{I}\mathcal{E}}$  differs from the respective output of  $\mathcal{N}_{\mathcal{I}\mathcal{E}}$  when  $\iota$  is simultaneously applied to  $\mathcal{N}_{\mathcal{I}\mathcal{E}}$  and  $\mathcal{N}_{\mathcal{I}\mathcal{F}\mathcal{E}}$ . We say that  $\iota$  is a test sequence for f on  $\mathcal{N}_{\mathcal{I}\mathcal{E}}$   $^4$ . We call  $\mathcal{E}$ -det the set of  $\mathcal{E}$ -detectable faults.

**Definition 2.** Under the same conditions of Def. 1 and assuming that the implementation  $\mathcal{I}$  is modeled at transaction level, a fault is TLM-detectable if there is a test vector such that the outputs of the unperturbed and perturbed DUVs differ when the test vector is simultaneously applied to both the designs. The fault is TLM-undetectable if such a test vector does not exist.

**Definition 3.** Under the same conditions of Def. 1 and assuming that the implementation  $\mathcal{I}$  is modeled at RTL, a fault is RTL-detectable if there is a test sequence such that the outputs of the unperturbed and perturbed DUVs differ when the test sequence is simultaneously applied to both the designs. The fault is RTL-undetectable if such a test sequence does not exist.

<sup>&</sup>lt;sup>3</sup> An FSM retroactive network  $\mathcal{N}_{\mathcal{I}\mathcal{E}}$  is composed of two FSMs:  $\mathcal{I}$ , which describes the DUV, and  $\mathcal{E}$ , which models the environment where  $\mathcal{I}$  is embedded. Some output lines of  $\mathcal{I}$  are connected to the input lines of  $\mathcal{E}$ , and some output lines of  $\mathcal{E}$  are connected to input lines of  $\mathcal{I}$ .

<sup>&</sup>lt;sup>4</sup> Note that  $\iota$  is also a test sequence for f on  $\mathcal{I}$ .

It is worth to note that, at TL, testbenches are composed of test vectors, while, at RTL, we need test sequences generally composed of more than one test vector. This is due to the fact that TLM is untimed (eventually a clock can be introduced at level 1), thus the result of a transaction is instantaneously available once a single test vector is applied. On the contrary, at RTL the design is generally modeled as an FSMD where the result is available after a number of clock cycles and it may depends on values provided to the primary inputs at different times. When a TL testbench is applied to an RTL design, the transactor converts test vectors in the corresponding test sequences modeling the communication protocol needed by the RTL design. From this observation the following definition derives.

**Definition 4.** Under the same conditions of Def. 1 and assuming that the implementation  $\mathcal{I}$  is modeled at RTL and wrapped by a TL-to-RTL transactor as defined in Section 4.3, a fault is<sup>5</sup>:

- Functionally T-detectable, if there is a test vector such that the outputs of the transactor connected to the unperturbed and perturbed DUVs are available at the same time and they differ, once the transactor has simultaneously applied the test sequence derived from the test vector to both the designs.

- Timing T-detectable, if there is a test vector such that the outputs of the transactor connected to the unperturbed and perturbed DUVs are available at different times, but they are equal, once the transactor has simultaneously applied the test sequence derived from the test vector to both the designs.

- Functionally and timing T-detectable, if there is a test vector such that the outputs of the transactor connected to the unperturbed and perturbed DUVs are available at different times, and they differ, once the transactor has simultaneously applied the test sequence derived from the test vector to both the designs.

- **T-detectable**, if it is functionally T-detectable and/or timing T-detectable.

- **T-undetectable**, if for each test vector the outputs of the transactor connected to the unperturbed and perturbed designs are available at the same time and they are equal, once the transactor has simultaneously applied the test sequence derived from the test vector to both the designs.

#### **Theorem 1.** An RTL-detectable fault is also T-detectable.

**Proof:** If a fault is RTL-detectable there exist a test sequence such that it propagates the effect of the fault to at least one output of the perturbed RTL DUV (Def. 3). Note that, such a test sequence respects the protocol imposed by the environment constraints that must be connected to the RTL DUV as required by Def. 1.

Let us consider that the fault is propagated to a data output. Accordingly to the transactor implementation described in Section 4.3 and Def. 4, such a fault

<sup>&</sup>lt;sup>5</sup> Please, note that in this case the environment constraints are directly modeled by the transactor.

becomes functionally T-detectable (then, T-detectable) when the RTL design is connected to a TL testbench through the transactor. In fact, the same test sequence generated by the RTL testbench can be obtained by applying an opportune test vector to the transactor (which acts like the environment constraints).

On the contrary, let us consider that the fault is propagated to a control output. In this case, the communication protocol between the transactor and the perturbed RTL DUV is necessarily changed. This causes that: the result of the perturbed DUV is provided to the transactor with a timing discrepancy with respect to the unperturbed DUV. Thus, according to Def. 4, the fault is timing T-detectable (then, T-detectable).

Theorem 1 shows that the TBV is at least as effective as the RTL verification from the fault coverage point of view. The Theorem assumes that the TL testbenches are able to produce a set of test vectors that can be converted from the transactor into a set of test sequences which includes the test sequences directly generated by the RTL testbenches. However, such an assumption is reasonable, since it is much more difficult to create efficient RTL testbenches than TL ones [52].

#### **Property Reuse** 4.5

Let us compare now TL property coverage and RTL property coverage to show the effectiveness of reusing TL properties at RTL through TBV, instead of converting them into properties specifically tailored to the RTL design. The desired goal is to show that TL properties cover the same set of behaviors covered by the corresponding RTL properties.

As already described, the property coverage measures the quality of properties to detect design errors in all parts of the DUV description. It is computed by analyzing the capability of properties to highlight differences between the unperturbed and the perturbed implementations of the same design. If a property, which holds on the unperturbed design, fails in presence of a fault, then the behavior perturbed by the fault is covered by the property.

**Definition 5.** Under the same assumption of Definition 1, the RTL property coverage,  $C_P^{RTL}$ , and the TL property coverage,  $C_P^{TL}$ , are defined as:

$$C_P^{RTL} = \frac{\# \text{ of faults that causes an RTL property failure}}{\# \text{ of RTL-detectable faults}}$$

(2)

$$C_P^{RTL} = \frac{\# \text{ of faults that causes an RTL property failure}}{\# \text{ of RTL-detectable faults}}$$

$$C_P^{TL} = \frac{\# \text{ of faults that causes a TL property failure}}{\# \text{ of T-detectable faults}}$$

(3)

Given the previous Definition and Theorem 1, TL property coverage and RTL property coverage can be compared. In fact, the methodology presented in [50] for RTL property coverage can be reused for TL property coverage, provided that, the definition of RTL-detectable faults is substituted with the definition of T-detectable faults.

For sake of completeness, it is worth to note that a set of assertions, achieving 100% property coverage on the TL design, may not achieve 100% on the RTL design. This is due to the fact that at TL no properties can be defined related to communication protocols and timing between events, since such details are not modeled at transaction level. However, this observation does not affect the effectiveness of reusing TL properties at RTL, since they allows to check the functionality of the RTL design. Then, new RTL properties must be added only to verify timing and communication protocols.

### 5 Experimental Results

This section reports some experimental results showing the effectiveness of the simulation-based techniques, described in Section 4, to verify a complex embedded system. Moreover, an experimental confirmation is reported to show the effectiveness of reusing test benches and properties by TBV.

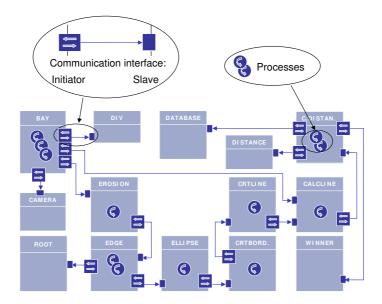

The case study is represented by the STMicroelectronics Face Recognition System shown in Figure 9. In particular, the ROOT, DIV and DISTANCE modules are considered, since they were selected to become HW components. Their characteristics are showed in Table 1 whose columns report the number of gates and flip-flops, and the number of TL and RTL faulty implementations generated to perform functional verification by using test benches and ABV.

| Module   | Gates | FFs | TL faults | RTL faults |

|----------|-------|-----|-----------|------------|

| ROOT     | 7802  | 155 | 196       | 1627       |

| DIV      | 11637 | 269 | 1017      | 2333       |

| DISTANCE | 40663 | 100 | 2327      | 3061       |

**Table 1.** Characteristic of the case study

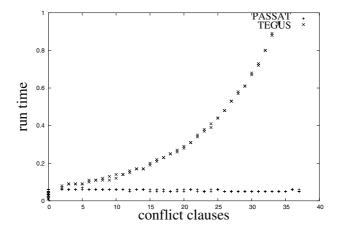

#### 5.1 Functional Verification by Test Benches and ABV

The TL descriptions of ROOT, DIV and DISTANCE have been verified by using both fault simulation by test benches and ABV. In particular, a set of test sequences have been generated by using Laerte++ [57], a functional ATPG equipped with different pseudo-deterministic engines, and the corresponding fault coverage has been computed. Then, a set of properties have been defined and their effectiveness have been evaluated by computing the related property coverage. Table 2 reports the achieved results, where FC%, #TV, PC% and #Prop. refer, respectively, to the fault coverage, the number of generated test vectors, the property coverage and the number of defined properties.

#### 5.2 TBV Evaluation

The effectiveness of TBV has been experimentally confirmed by comparing the fault coverage and the property coverage achieved by reusing TL test benches and properties through TBV, and the fault coverage and property coverage achieved by generating ad-hoc RTL test benches and by manually converting TL properties into corresponding RTL ones.

|          | AT   | PG              | ABV  |        |  |

|----------|------|-----------------|------|--------|--|

| Module   | FC%  | $\#\mathrm{TV}$ | PC%  | #Prop. |  |

| ROOT     | 99.0 | 23              | 99.0 | 11     |  |

| DIV      | 99.0 | 20              | 99.0 | 5      |  |

| DISTANCE | 99.0 | 8               | 99.0 | 3      |  |

Table 2. Fault coverage and property coverage at TL

Fault Coverage Comparison. Table 3 reports the results related to the fault coverage comparison. Columns FC%, #TV and Time show, respectively, the achieved fault coverage, the number of test vectors generated by Laerte++, and the time required to generate/simulate such vectors, for TBV and the RTL verification flow. In particular, TBV (reuse) is related to the reuse of TL test benches at RTL via transactor, while TBV (reuse+ATPG) is related to the integration of the TL test benches by adding new test vectors generated by applying an Laerte++ to the RTL module via transactor. As expected from theoretical results reported in Section 4, the TBV fault coverage is greater than or equal to the RTL one for all the modules. Moreover, it is interesting to note that the number of test vectors and the time required by TBV is lower than the corresponding RTL quantities. In particular, the time spent by TBV is extremely lower than the one needed at RTL. This derives from the fact that, at RTL, test vectors must be completely generated ex-novo. On the contrary, TBV can reuse the ones generated during the verification of the TL descriptions. Thus, fault simulation is required instead of ex-novo test generation when TBV is applied. Indeed, the reuse of high-quality TL test vectors could be insufficient

Fig. 9. The Face Recognition System

|          | TBV (reuse) |     |          | TBV  | (reuse | e+ATPG)  | RTL  |      |          |

|----------|-------------|-----|----------|------|--------|----------|------|------|----------|

| Design   | FC%         | #TV | Time(s.) | FC%  | #TV    | Time(s.) | FC%  | #TV  | Time(s.) |

| ROOT     | 94.5        | 23  | 23       | 98.5 | 25     | 145      | 97.8 | 741  | 2050     |

| DIV      | 84.3        | 20  | 31       | 97.0 | 191    | 112      | 86.6 | 1073 | 1774     |

| DISTANCE | 90.7        | 8   | 57       | 98.9 | 15     | 316      | 94.2 | 254  | 11540    |

Table 3. Fault coverage comparison by reusing test benches through TBV

to achieve an high-fault coverage also on the RTL design (TBV (reuse)). For this reason, the TL test benches have been integrated by generating new test vectors achieving the fault coverage reported in TBV (reuse+ATPG). Thus, the TBV time is composed by summing the time required for fault simulation and the time required for test bench integration.

**Property Coverage Comparison.** Table 4 shows the property coverage percentage (PC%) achieved by applying the ABV methodology. As already reported in Table 2 the TL description of the considered modules has been verified by defining a total number of 19 properties which achieve 99% property coverage. After TL-to-RTL refinement the RTL implementation was verified by:

- 1. reusing TL properties through TBV (TL Prop. Reuse);

- 2. converting the TL properties into RTL ones (Manual Conv.);

- 3. adding new properties to check implementation details and the communication protocol added at RTL (New ad-hoc Prop.).

After RTL refinement, the TL properties have been checked on the RTL implementation by using TBV. Then, they have been manually converted into RTL properties and verified by using the SMV model checker. Finally, the corresponding property coverage have been computed and compared on the RTL implementation. The results reported in Table 4 confirms the effectiveness of TBV, since property coverages achieved by TL property reuse and manual conversion are equal for all modules. However, as observed in Section 4.5, TL properties are not enough to completely verify the RTL implementations, even if they do it at TL. This emphasizes the fact that TL properties, but also the corresponding RTL properties, are not able to identify perturbations that affect behaviors depending on timing synchronization or communication protocols typical of the RTL implementation. This has been confirmed by analyzing the

|     |                  | ROOT  |     | DIV   |     | DISTANCE |     | TOTAL |     |

|-----|------------------|-------|-----|-------|-----|----------|-----|-------|-----|

|     |                  | #Prop | PC% | #Prop | PC% | #Prop    | PC% | #Prop | PC% |

| TLM | TL Prop.         | 11    | 99% | 5     | 99% | 3        | 99% | 19    | 99% |

| RTL | TL Prop. Reuse   | 11    | 95% | 5     | 86% | 3        | 87% | 19    | 89% |

|     | Manual Conv.     | 11    | 95% | 5     | 86% | 3        | 87% | 19    | 89% |

|     | New ad-hoc Prop. | 1     | 99% | 3     | 96% | 4        | 96% | 8     | 97% |

Table 4. Experimental results

nature of high-level faults not covered by the TL properties. Thus, column *New ad-hoc Prop.* reports the final property coverage achieved after new properties have been added to check the timing synchronization and the communication protocol.

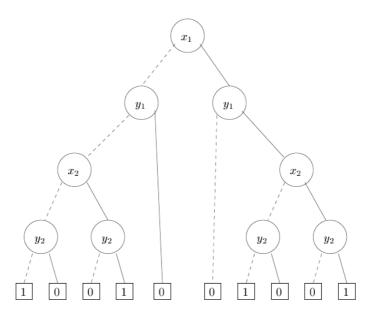

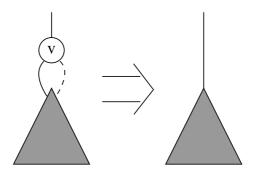

# 6 Concluding Remarks