**Energy Systems in Electrical Engineering**

# Anindya Dasgupta Parthasarathi Sensarma

# Design and Control of Matrix Converters

Regulated 3-Phase Power Supply and Voltage Sag Mitigation for Linear Loads

# **Energy Systems in Electrical Engineering**

Series editor

Muhammad H. Rashid, Pensacola, USA

More information about this series at http://www.springer.com/series/13509

Anindya Dasgupta · Parthasarathi Sensarma

# Design and Control of Matrix Converters

Regulated 3-Phase Power Supply and Voltage Sag Mitigation for Linear Loads

Anindya Dasgupta Avionics Department Indian Institute of Space Science and Technology Thiruvananthapuram, Kerala India Parthasarathi Sensarma Department of Electrical Engineering Indian Institute of Technology Kanpur Kanpur, Uttar Pradesh India

ISSN 2199-8582

ISSN 2199-8590 (electronic)

Energy Systems in Electrical Engineering

ISBN 978-981-10-3829-7

ISBN 978-981-10-3831-0 (eBook)

DOI 10.1007/978-981-10-3831-0

ISBN 978-981-10-3831-0

ISBN 978-981-10-3831-0 (eBook)

Library of Congress Control Number: 2017931048

#### © Springer Nature Singapore Pte Ltd. 2017

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by Springer Nature The registered company is Springer Nature Singapore Pte Ltd. The registered company address is: 152 Beach Road, #21-01/04 Gateway East, Singapore 189721, Singapore

## Preface

Improving power density of converters, apart from conversion efficiency, has been one of the major drivers of modern developments in power electronics. Tracing the evolution of power electronics reveals that improvement in semiconductor devices, digital control with ever-increasing computational capability, improved packaging techniques combined with parallel development of converter topologies, switching schemes and advanced control techniques have kept on redefining the benchmarks with every passing day. The power converter which forms the core of any power electronic application is an electrical network involving only semiconductor switches and passive storage elements, with the latter largely contributing to the volume and weight of the converter. Therefore it is quite natural that, among competing candidates for a given application, the topology with the highest semiconductor to passives ratio—both in terms of component count and size would offer the highest power density. For this specific possibility, the Matrix Converter—a generic name for any converter having only semiconductor devices in its power stage—demands focused investigation.

Matrix converters were proposed in the 1980s and almost immediately generated a lot of research interest, mostly in the domain of 3-phase AC-AC power conversion, and there has been several significant breakthroughs in modulation methods, multi-step commutation and space vector pulse width modulation. With respect to applications, academic and industrial research interest in Matrix Converters has been largely confined to motor drives. But since the last decade, there had been an emerging interest towards using Matrix Converters in power system applications. Most of these applications demand faster dynamic performance than the industrial drives, which have high plant inertia and thus do not require such response speeds. Absence of any intermediate energy buffering element makes the Matrix Converter a dynamically tightly coupled input–output unit and the overall system design, particularly controller design, challenging.

The research efforts which led to this book were a part of this effort to expand the application domain of Matrix Converter to power systems. Two target applications for synchronous systems have been addressed—regulated 3-Phase voltage supply and voltage sag mitigation. The objective of the book has been subsequently

categorized into the following—developing a dynamic model which provides adequate design insight, filter design and devising a control scheme. The low-frequency dynamic model is first analysed for regulated voltage supply assuming balanced system. A linearized dynamic model is developed and it is shown that depending on the input power, input voltage and filter parameters a possibility of appearance of a set of right half zeros exist.

The design of filters is considered next. Apart from general issues like ripple attenuation, regulation, reactive current loading and filter losses, additional constraints which may be imposed by dynamic requirements and commutation are also addressed.

In the third stage, voltage controller design is detailed for 3-Phase regulated voltage supply. In the synchronous *dq* domain, output voltage control represents a multivariable control problem. The control problem is reduced to a single variable one while retaining all possible right half zeros, thereby preserving the internal stability of the system. Consequently, standard single variable control design technique has been used to design a controller. The analytically predicted dynamic response has been verified by experimental results. The system could be operated beyond the critical power boundary where the right half zeros emerge.

Finally, the developed control approach has been extended to voltage sag mitigation with adequate modifications. A 3-wire linear load has been considered. Both symmetrical and asymmetrical voltage sags have been considered.

Thiruvananthapuram, India Kanpur, India Anindya Dasgupta Parthasarathi Sensarma

# Contents

| 1 | Introduction. |                                                             |  |

|---|---------------|-------------------------------------------------------------|--|

|   | 1.1           | Overview of 3-Phase Matrix Converter    5                   |  |

|   |               | 1.1.1 Hardware Design 6                                     |  |

|   |               | 1.1.2 Commutation 8                                         |  |

|   |               | 1.1.3 Topology 14                                           |  |

|   |               | 1.1.4         Modulation         14                         |  |

|   |               | 1.1.5 Dynamic Model for Controller Design    19             |  |

|   | 1.2           | Motivation and Objectives                                   |  |

|   | 1.3           | Assumptions and Scope 21                                    |  |

|   | 1.4           | Layout of the Book    21                                    |  |

| 2 | Low           | Frequency Dynamic Model         23                          |  |

|   | 2.1           | Low Frequency Gain of 3-Phase MC 24                         |  |

|   |               | 2.1.1 Indirect Space Vector Modulation (ISVM) Approach 25   |  |

|   | 2.2           | Linearized Model                                            |  |

|   | 2.3           | Composition of $G_c(s)$ . 41                                |  |

|   |               | 2.3.1    Poles and Zeros of CdTM    41                      |  |

|   |               | 2.3.2 Poles and Zeros of $G_c(s)$                           |  |

|   | 2.4           | Concluding Remarks 48                                       |  |

| 3 | Filte         | <b>Design</b>                                               |  |

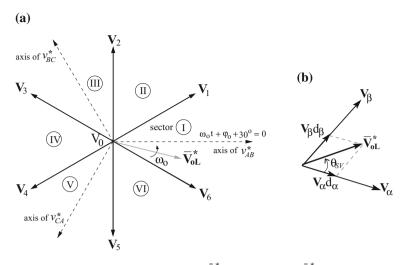

|   | 3.1           | Input Filter Design                                         |  |

|   |               | 3.1.1 Attenuation to Switching Frequency Ripple             |  |

|   |               | and Gain to Lower Order Harmonics                           |  |

|   |               | 3.1.2 Voltage Regulation and Reactive Current Loading 55    |  |

|   |               | 3.1.3 Selecting Damping Resistor $R_d$                      |  |

|   |               | 3.1.4 Lower Limit of $C_f$                                  |  |

|   |               | 3.1.5 Effect of $L_s$                                       |  |

|   |               | 3.1.6 Design Modifications for a Non-minimum Phase Plant 68 |  |

|    | 3.2                           | Output Filter                                   | 69  |

|----|-------------------------------|-------------------------------------------------|-----|

|    |                               | 3.2.1 Lower Limit of $L_o$                      | 70  |

|    | 3.3                           | Selection of Parameter Values                   | 71  |

|    | 3.4                           | Results and Discussion.                         | 72  |

|    |                               | 3.4.1 Open Loop Experimental Results            | 73  |

|    | 3.5                           | Concluding Remarks                              | 76  |

| 4  | Con                           | troller Design for Regulated Voltage Supply     | 77  |

|    | 4.1                           | Specifications and Assumptions                  | 77  |

|    | 4.2                           | SISO Based Control                              | 78  |

|    |                               | 4.2.1 $N_{ff}(s)$ and $H_v(s)$                  | 80  |

|    | 4.3                           | Experimental Results and Discussion             | 85  |

|    | 4.4                           | Concluding Remarks                              | 89  |

| 5  | Volt                          | age Sag Mitigation                              | 91  |

|    | 5.1                           | Topology and Voltage Injection Method           | 92  |

|    | 5.2                           | Plant Model                                     | 94  |

|    | 5.3                           | Control Scheme for DVR                          | 96  |

|    |                               | 5.3.1 FB Controller                             | 97  |

|    |                               | 5.3.2 FF Controller                             | 100 |

|    | 5.4                           | Experimental Results and Discussion             | 101 |

|    | 5.5                           | Concluding Remarks                              | 106 |

| 6  | 6 Conclusion                  |                                                 | 107 |

|    | 6.1                           | Conclusions and Contributions                   | 107 |

|    | 6.2                           | Scope of Future Work                            | 108 |

|    | 6.3                           | Relevance of This Work at Present               | 108 |

| Ap | pend                          | ix A: Derivations Associated with Low Frequency |     |

|    |                               | Dynamic Model                                   | 111 |

| Ap | pend                          | ix B: 3 Phase Direct Matrix Converter Prototype | 115 |

| Ap | Appendix C: Phase Locked Loop |                                                 |     |

| Re | References                    |                                                 |     |

|    |                               |                                                 |     |

### About the Authors

**Dr. Anindya Dasgupta** is an assistant professor of Avionics at the Indian Institute of Space Science and Technology, Thiruvananthapuram. Dr. Dasgupta received his Ph.D. (Electrical Engineering) from the Indian Institute of Technology (IIT) Kanpur, India. He completed his M.E. (Control System, Electrical Engineering) in 2006 at Bengal Engineering and Science University, Shibpur, and B.E. (Electrical Engineering) in 2000 at the Jadavpur University, Kolkata.

**Dr. Parthasarathi Sensarma** is an associate professor of Electrical Engineering at IIT Kanpur, India. Dr. Sensarma completed his Ph.D. (Electrical Engineering) in 2001 at the Indian Institute of Science (IISc), Bangalore, India. He was awarded his M.Tech. (Machine Drives and Power Electronics) in 1992 from IIT Kharagpur and B.E.E. (Electrical Engineering) in 1990 from Jadavpur University, Kolkata. He has supervised several Ph.D. and M.Tech. students. Dr. Sensarma has filed patent application at the Indian Patent Office for seven of his projects. He has published 56 technical papers in national and international conferences and journals.

# List of Figures

| Figure 1.1  | Power processing stage of 3 phase to 3 phase back                     |   |

|-------------|-----------------------------------------------------------------------|---|

|             | to back inverters                                                     | 2 |

| Figure 1.2  | Buck converter realized with a single pole double                     |   |

|             | throw switch                                                          | 2 |

| Figure 1.3  | a 3-phase diode rectifier. b Output voltage                           | 3 |

| Figure 1.4  | A 3-phase to 1-phase AC converter power stage                         | 3 |

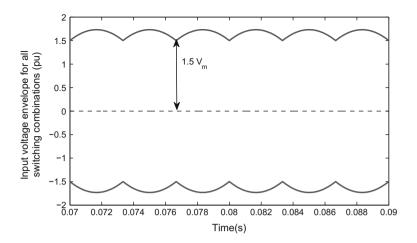

| Figure 1.5  | Envelope of the input voltage waveform                                | 4 |

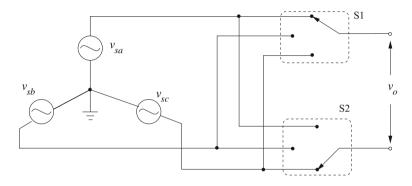

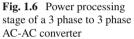

| Figure 1.6  | Power processing stage of a 3 phase to 3 phase<br>AC-AC converter     | 4 |

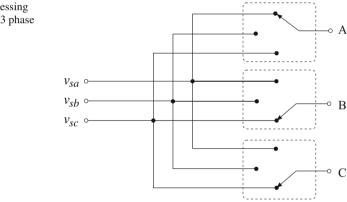

| Figure 1.7  | Power processing stage of a 3 phase to 3 phase MC                     | 5 |

| Figure 1.8  | Realizing bidirectional switch. a Diode bridge with IGBT,             |   |

| -           | <b>b</b> common emitter, <b>c</b> common collector, <b>d</b> reverse  |   |

|             | blocking IGBTs                                                        | 6 |

| Figure 1.9  | a Power stage of MC looking from source and load side.                |   |

|             | <b>b</b> Input filter. <b>c</b> Output filter                         | 7 |

| Figure 1.10 | Clamp circuit                                                         | 8 |

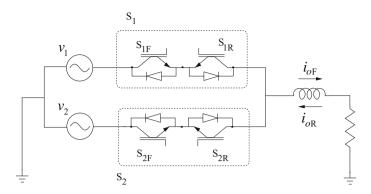

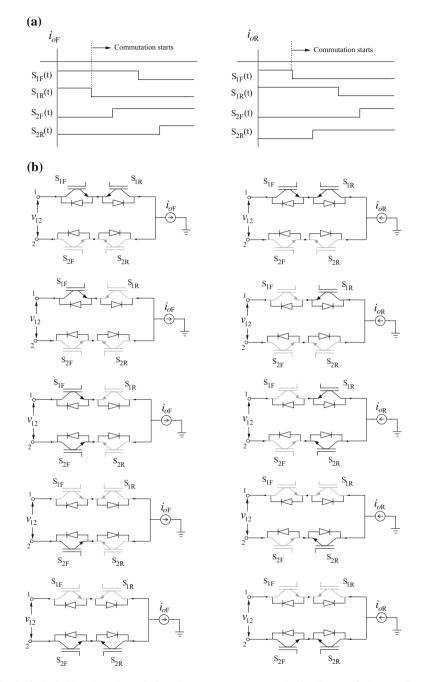

| Figure 1.11 | 2 phase to 1 phase MC                                                 | 9 |

| Figure 1.12 | Switching from $S_1$ to $S_2$ based on output current.                |   |

|             | a Timing diagram. b Stages of commutation 1                           | 0 |

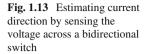

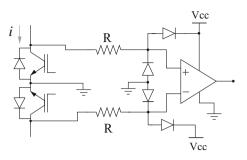

| Figure 1.13 | Estimating current direction by sensing the voltage across            |   |

|             | a bidirectional switch                                                | 1 |

| Figure 1.14 | Switching from $S_1$ to $S_2$ based on relative magnitude of $v_1$    |   |

|             | and $v_2$ . <b>a</b> Timing diagram. <b>b</b> Stages of commutation 1 | 2 |

| Figure 1.15 |                                                                       | 4 |

| Figure 1.16 | a Input voltage. b Output voltage envelope for all                    |   |

|             | 27 switching combinations 1                                           | 5 |

| Figure 1.17 | a Input voltages. b Input and target output voltages.                 |   |

|             | c Target output voltages along with common mode                       |   |

|             | voltages. d Reshaped target voltages. e Input along                   |   |

|             |                                                                       | 5 |

| Figure 1.18 | Decoupled rectifier-inverter construct 1                              | 6 |

| Figure 1.19 | Mapping the switching functions                                                         | 17 |

|-------------|-----------------------------------------------------------------------------------------|----|

| Figure 1.20 | Describing the discontinuous carrier signals                                            | 18 |

| Figure 2.1  | Schematic of a 3-ph MC                                                                  | 24 |

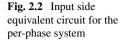

| Figure 2.2  | Input side equivalent circuit for the per-phase system                                  | 25 |

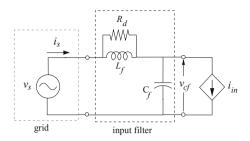

| Figure 2.3  | Decoupled current and voltage source converter                                          |    |

|             | construct                                                                               | 25 |

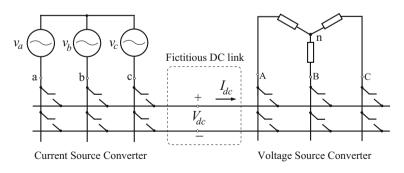

| Figure 2.4  | <b>a</b> Output voltage stationary vectors and $\bar{\mathbf{V}}_{oL}^*$ .              |    |

|             | <b>b</b> Synthesizing $\bar{\mathbf{V}}_{0\mathbf{L}}^*$                                | 27 |

| Figure 2.5  | Input current vectors                                                                   | 30 |

| Figure 2.6  | Low frequency gain of MC                                                                | 35 |

| Figure 2.7  | Single phase diagram including source inductance                                        | 35 |

| Figure 2.8  | Equivalent circuit of the linearized system. a, b Input,                                |    |

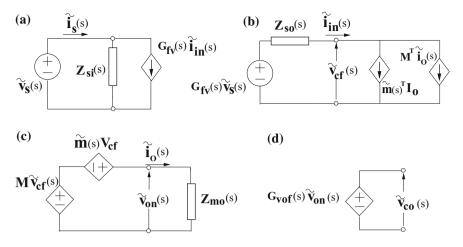

| -           | c, d Output side                                                                        | 39 |

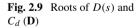

| Figure 2.9  | Roots of $D(s)$ and $C_d(\mathbf{D})$                                                   | 43 |

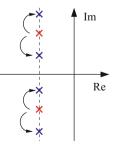

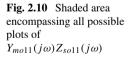

| Figure 2.10 | Shaded area encompassing all possible plots of                                          |    |

|             | $Y_{mo11}(j\omega)Z_{so11}(j\omega)$                                                    | 45 |

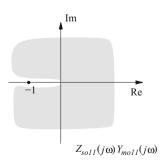

| Figure 2.11 | Frequency response of $Z_{sol1}(s)$                                                     | 47 |

| Figure 2.12 | Generic DC-DC converter having same power stage                                         |    |

|             | as MC                                                                                   | 48 |

| Figure 2.13 | Equivalent circuit of the linearized system                                             | 49 |

| Figure 3.1  | Input filter                                                                            | 52 |

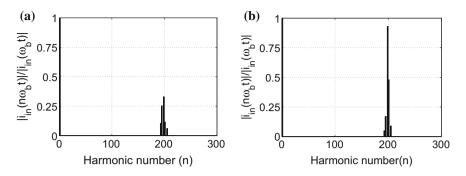

| Figure 3.2  | $ i_{in}(n\omega_b t) / i_{in}(\omega_b t) $ for <b>a</b> $m = 1$ , <b>b</b> $m = 0.5$  | 53 |

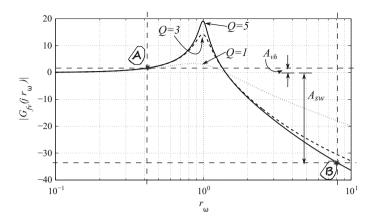

| Figure 3.3  | $ G_{fv}(jr_{\omega}) $ (dB) with $Q = 1, 3$ and $5 \dots$                              | 55 |

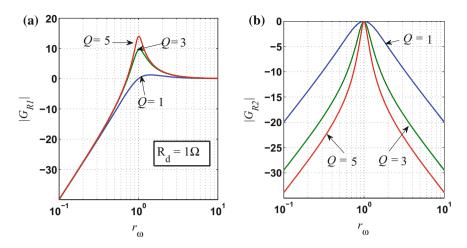

| Figure 3.4  | <b>a</b> $ G_{R1}(j\omega) (dB)$ for $R_d = 1\Omega$ , <b>b</b> $ G_{R2}(j\omega) (dB)$ | 57 |

| Figure 3.5  | Commutation between input phases (a, b)                                                 | 59 |

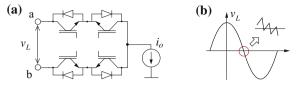

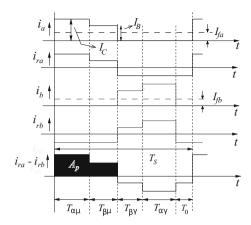

| Figure 3.6  | Input current and filter capacitor voltage                                              | 60 |

| Figure 3.7  | a Decoupled CSC-VSC construct, b Input current                                          |    |

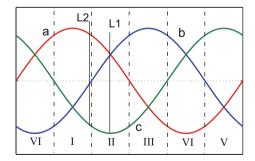

|             | hexagon, c Output voltage hexagon, e Synthesizing $\bar{I}_{in}$ ,                      |    |

|             | <b>d</b> Synthesizing $\overline{V}_{OL}$                                               | 61 |

| Figure 3.8  | Fundamental $(I_{fa}, I_{fb})$ and switching frequency $(i_{ra}, i_{rb})$               |    |

|             | components of input currents $(i_a, i_b)$                                               | 62 |

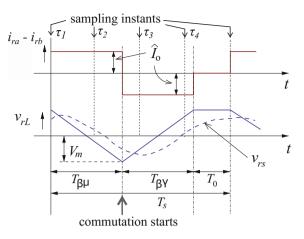

| Figure 3.9  | Error in measuring $v_{rL}$ around its maximum value                                    | 64 |

| Figure 3.10 | Instantaneous positions of $i_{fa}$ , $i_{fb}$ , $v_{fa}$ and $v_{fb}$                  |    |

|             | at the beginning of commutation from phase- <i>a</i> to <i>b</i>                        | 64 |

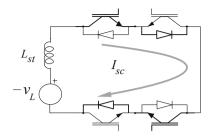

| Figure 3.11 | Path of short circuit current                                                           | 66 |

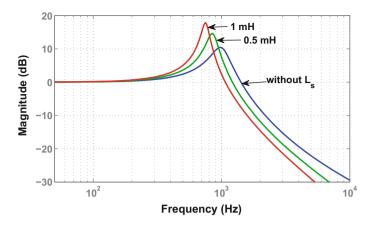

| Figure 3.12 | Magnitude plot of $G_{fv}(s)$ for $L_s$ of 0.5 and 1 mH                                 | 68 |

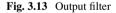

| Figure 3.13 | Output filter                                                                           | 69 |

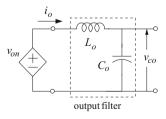

| Figure 3.14 | <b>a</b> Voltage across $R_d$ : 10 V/div, time: 10 ms/div. <b>b</b> $v_L$ :             |    |

|             | 100 V/div, time: 500 $\mu$ s/div. <b>c</b> $v_L$ : 20 V/div, time:                      |    |

|             | 100 μs/div                                                                              | 73 |

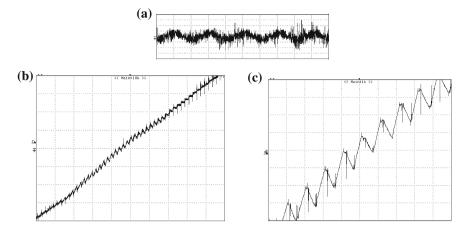

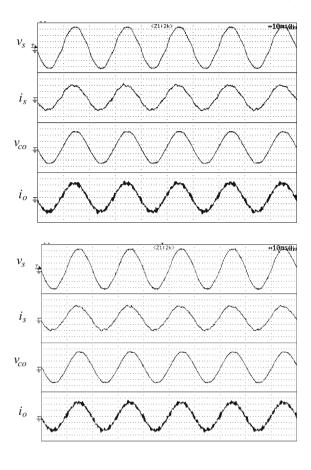

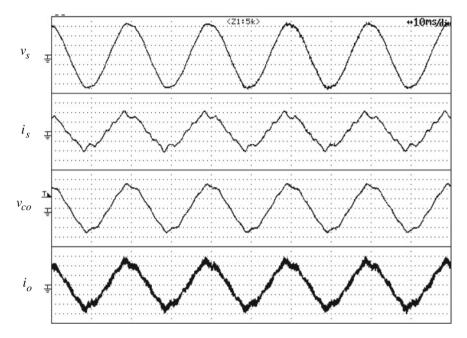

| Figure 3.15 | Open loop experimental results. $v_s$ : 100 V/div, $i_s$ :                              |    |

|             | 5 A/div, $v_{co}$ : 100 V/div, $i_o$ : 5 A/div. Time: 10 ms/div                         | 74 |

| Figure 3.16 | Open loop results with a $L_s$ of 1mH. $v_s$ : 100 V/div, $i_s$ :<br>5 A/div $r_s$ = 100 V/div $i_s$ = 5 A/div Times 10 mg/div | 74       |

|-------------|--------------------------------------------------------------------------------------------------------------------------------|----------|

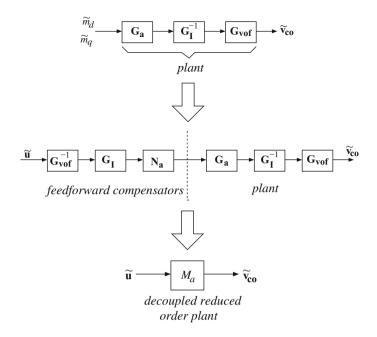

| Eigung 4.1  | 5 A/div, $v_{co}$ : 100 V/div, $i_o$ : 5 A/div. Time: 10 ms/div A chieving a radius order scalar plant $M_{co}$                | 74<br>81 |

| Figure 4.1  | Achieving a reduced order scalar plant $M_a(s)$                                                                                | 01       |

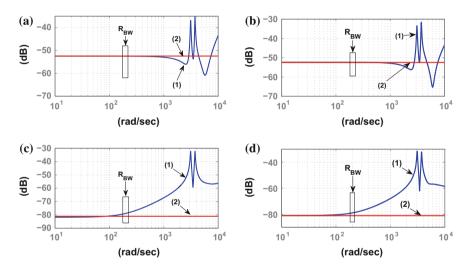

| Figure 4.2  | Plot (1): $N_{ff}(s)$ , Plot (2): $A_N(s)$ . <b>a</b> , <b>b</b> Diagonal elements.                                            | 01       |

| E           | c, d Off-diagonal elements.                                                                                                    | 82       |

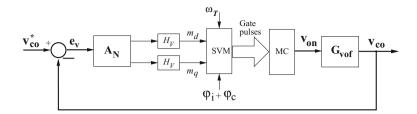

| Figure 4.3  | Control scheme                                                                                                                 | 84       |

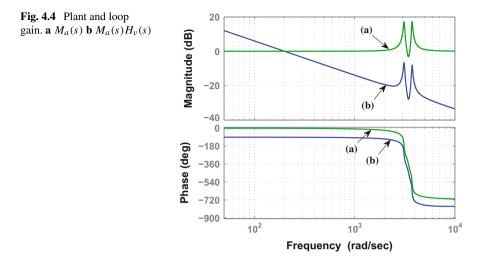

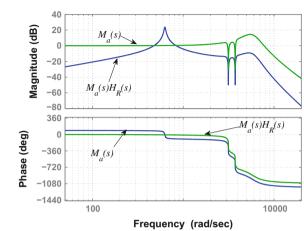

| Figure 4.4  | Plant and loop gain. <b>a</b> $M_a(s)$ <b>b</b> $M_a(s)H_v(s)$                                                                 | 85       |

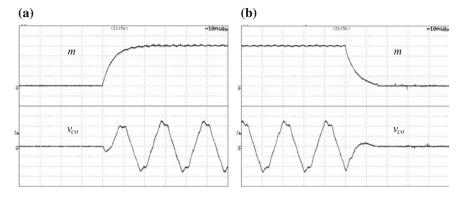

| Figure 4.5  | Dynamic response of $v_{co}$ . <b>a</b> Step reference of 170 V                                                                |          |

|             | <b>b</b> reference reset to zero. <i>m</i> , scale: 0.2 /div. $v_{co}$ , scale:                                                | 06       |

|             | 100 V/div. Time: 10 ms/div                                                                                                     | 86       |

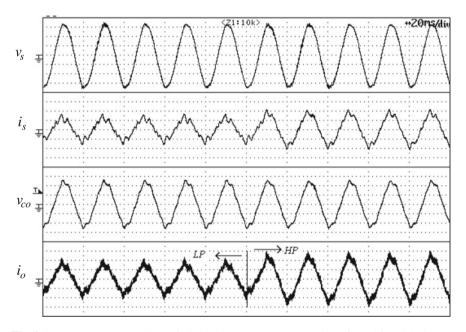

| Figure 4.6  | Response to a step change in load. Output current $i_o$                                                                        |          |

|             | stepped up from 5.3 to 8 A. Source voltage $v_s$ (100 V/div),                                                                  |          |

|             | $i_s$ (5 A/div), $v_{co}$ (100 V/div), $i_o$ (5 A/div). Time:                                                                  | 0.6      |

|             | 20 ms/div                                                                                                                      | 86       |

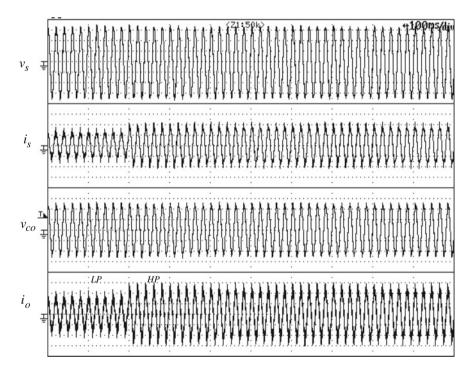

| Figure 4.7  | Response to the step change in load shown over a larger                                                                        |          |

|             | period of time. $v_s$ (100 V/div), $i_s$ (5 A/div),                                                                            | ~ -      |

| -           | $v_{co}$ (100 V/div), $i_o$ (5 A/div). Time: 100 ms/div                                                                        | 87       |

| Figure 4.8  | Steady state plots while operating in the HP region.                                                                           |          |

|             | $v_s$ (100 V/div), $i_s$ (5 A/div), $v_{co}$ (100 V/div), $i_o$ (5 A/div).                                                     |          |

|             | Time: 10 ms/div                                                                                                                | 88       |

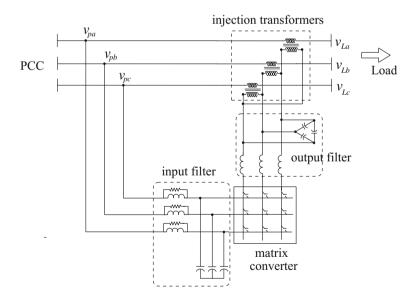

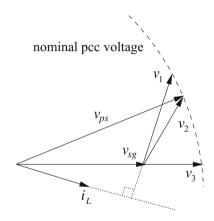

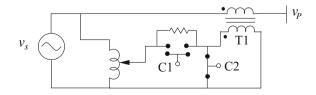

| Figure 5.1  | 3-phase MC connected as a DVR                                                                                                  | 92       |

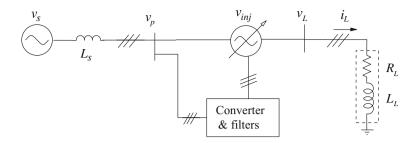

| Figure 5.2  | Single line representation of the system.                                                                                      | 93       |

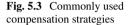

| Figure 5.3  | Commonly used compensation strategies                                                                                          | 93       |

| Figure 5.4  | Per phase equivalent circuit                                                                                                   | 95       |

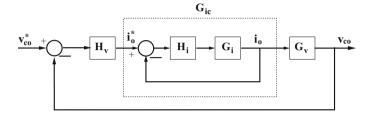

| Figure 5.5  | Conventional multiloop control                                                                                                 | 95       |

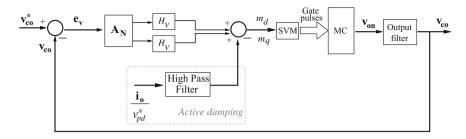

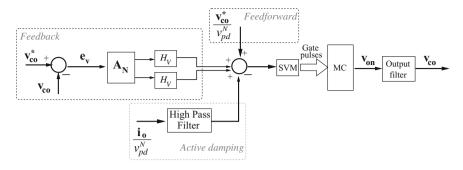

| Figure 5.6  | Control scheme with active damping                                                                                             | 96       |

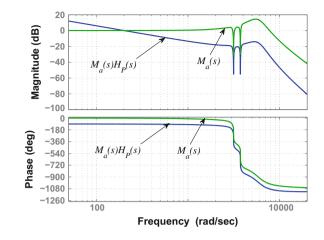

| Figure 5.7  | Bode plot of $M_a(s)$ and $M_a(s)H_P(s)$                                                                                       | 98       |

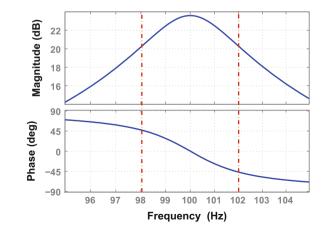

| Figure 5.8  | Bode plot of $H_R(s)$                                                                                                          | 98       |

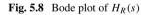

| Figure 5.9  | Bode plot of $M_a(s)$ and $M_a(s)H_R(s)$                                                                                       | 99       |

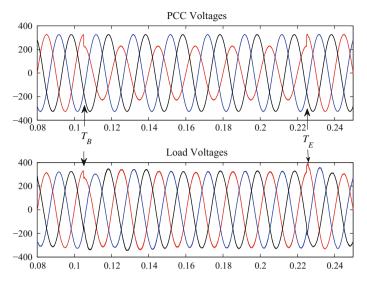

| Figure 5.10 | Simulation result with FB controller. Phase a red,                                                                             |          |

|             | b <i>blue</i> , c <i>black</i> (colour online)                                                                                 | 100      |

| Figure 5.11 | Control scheme                                                                                                                 | 101      |

| Figure 5.12 | Sag generation setup shown for one phase                                                                                       | 101      |

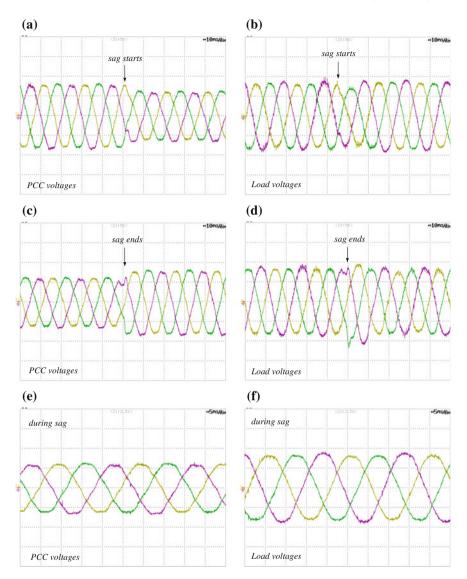

| Figure 5.13 | Experimental waveforms for symmetrical voltage sag.                                                                            |          |

|             | Phase a yellow, b green, c purple. Voltage scale:                                                                              |          |

|             | 200 V/div. Time: 10 ms/div for (a)-(d) and 5 ms/div                                                                            |          |

|             | for (e) and (f) (colour online)                                                                                                | 102      |

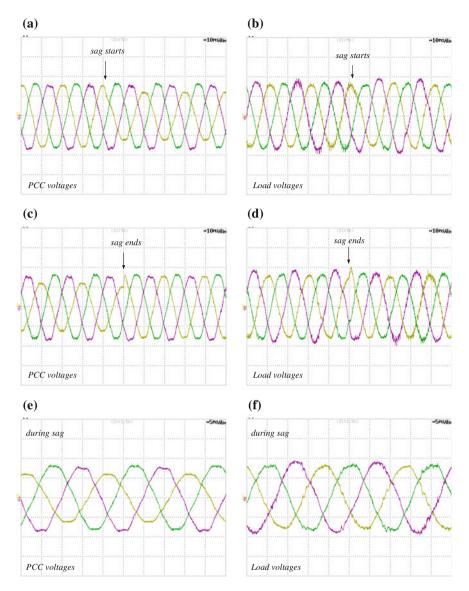

| Figure 5.14 | Experimental waveforms for asymmetrical voltage sag.                                                                           |          |

|             | Phase a yellow, b green, c purple. Voltage scale:                                                                              |          |

|             | 200 V/div. Time: 10 ms/div for (a)-(d) and 5 ms/div                                                                            |          |

|             | for (e) and (f) (colour online)                                                                                                | 104      |

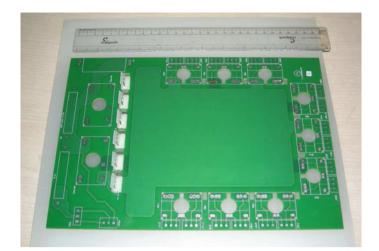

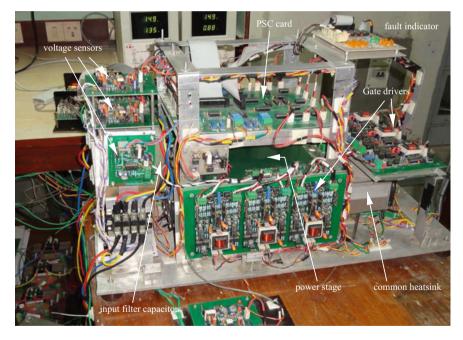

| Figure B.1  | PCB housing the power stage and also the clamp                                                                                 |          |

|             | protection circuit                                                                                                             | 116      |

| Figure B.2 | Overall converter assembly with the gate driver, |     |

|------------|--------------------------------------------------|-----|

|            | protection and sensor cards                      | 116 |

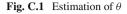

| Figure C.1 | Estimation of $\theta$                           | 118 |

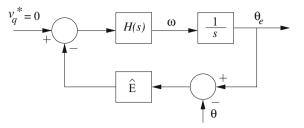

| Figure C.2 | PLL proposed in [51]                             | 118 |

|            |                                                  |     |

# List of Tables

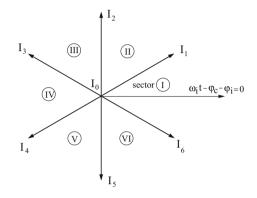

| Table 2.1  | Switching state vectors for the VSC                                     | 26 |

|------------|-------------------------------------------------------------------------|----|

| Table 2.2  | Line voltages, when $\bar{\mathbf{V}}_{\mathbf{oL}}^*$ is in sector I   | 28 |

| Table 2.3  | Ratio of line voltages to $V_{dc}$ , $\theta_{SV}$ for sectors II to VI | 29 |

| Table 2.4  | Switching state vectors for CSC                                         | 29 |

| Table 2.5  | Input currents when $\bar{\mathbf{I}}_{in}^*$ is in sector I            | 30 |

| Table 2.6  | Ratio of input currents to $I_{dc}$ , $\theta_{SI}$ for sectors II–VI   | 31 |

| Table 2.7  | Mapping from CSC VSC construct to 9 Qsw MC                              | 33 |

| Table 3.1  | Nominal/rated parameters                                                | 52 |

| Table 3.2  | $Q$ and $f_c$ from forward gain                                         | 54 |

| Table 3.3  | $L_{f, \max}$ and $C_{f, \max}$ from regulation and reactive loading    | 56 |

| Table 3.4  | Harmonics in $i_{in}$ from simulation at $m = 1$                        | 58 |

| Table 3.5  | F1 and F2                                                               | 58 |

| Table 3.6  | $L_{f, \min}$ and $C_{f, \min}$ from regulation, reactive loading       |    |

|            | and fixed $f_c$                                                         | 58 |

| Table 3.7  | Input-output connections in MC for $\overline{I}_{in}$ in sector II     |    |

|            | and $\bar{V}_{OL}$ in sector III                                        | 61 |

| Table 3.8  | $C_{f,\min}$                                                            | 66 |

| Table 3.9  | Boundary values for parameters of output filter                         | 70 |

| Table 3.10 | Input and output filter parameters                                      | 71 |

| Table 3.11 | Input and output filter parameters                                      | 72 |

| Table 3.12 | Measured values                                                         | 74 |

| Table 3.13 | Harmonics in one phase of $v_s$ , $i_s$ and $v_{co}$                    | 75 |

| Table 3.14 | Harmonics $v_s$ , $i_s$ and $v_{co}$ with $L_s = 1$ mH                  | 75 |

| Table 4.1  | Dynamic specifications                                                  | 78 |

| Table 4.2  | System parameters                                                       | 82 |

| Table 4.3  | Compensator and controller parameters                                   | 85 |

| Table 4.4  | Power delivered to load—measured                                        | 87 |

| Table 4.5  | Significant harmonic components of experimental                         |    |

|            | waveforms                                                               | 87 |

|            |                                                                         |    |

| Nominal parameters                                    | 97                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input and output filter parameters                    | 97                                                                                                                                                                                                                                                                                                                                                                                                             |

| Parameters of $H_R(s)$                                | 99                                                                                                                                                                                                                                                                                                                                                                                                             |

| Harmonic components during symmetrical sag            | 103                                                                                                                                                                                                                                                                                                                                                                                                            |

| Harmonic components before initiating symmetrical sag | 103                                                                                                                                                                                                                                                                                                                                                                                                            |

| Positive and negative sequence components in PCC      |                                                                                                                                                                                                                                                                                                                                                                                                                |

| and load voltage before and during asymmetrical sag   | 105                                                                                                                                                                                                                                                                                                                                                                                                            |

| Harmonic components during asymmetrical sag           | 105                                                                                                                                                                                                                                                                                                                                                                                                            |

| Harmonic components before initiating                 |                                                                                                                                                                                                                                                                                                                                                                                                                |

| asymmetrical sag                                      | 105                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                       | Input and output filter parameters $\dots$<br>Parameters of $H_R(s)$<br>Harmonic components during symmetrical sag $\dots$<br>Harmonic components before initiating symmetrical sag $\dots$<br>Positive and negative sequence components in PCC<br>and load voltage before and during asymmetrical sag $\dots$<br>Harmonic components during asymmetrical sag $\dots$<br>Harmonic components before initiating |

## Chapter 1 Introduction

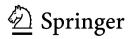

Matrix Converter (MC) is a class of switched mode power converters (SMPC) which contains only semiconductor devices in its power processing stage. These converters were conceived as an alternative to the Back to back inverter (B2BI) topology used in 3-phase to 3-phase power conversion. The necessity of finding an alternative to B2BI in the form of a more silicon reliant solution can be understand by analyzing its power stage. Figure 1.1a, shows the power conversion stage of B2BI.

The power stage of B2BI is made up of two inverters connected back to back through a capacitor which is also commonly referred to as the DC link capacitor. The inverter at the input side transforms the 3-phase sinusoidal AC voltage applied to its input terminals to a switched DC voltage which appears across the DC capacitor. The inverter at the output side requires a very stiff DC link voltage at its input terminals. Consequently a large electrolytic capacitor has to be used as the DC link capacitor. A significant portion of volume and weight of the converter is attributed to the DC link capacitor. Moreover, it has a higher failure rate than the semiconductors. Therefore, a 3-phase AC to AC converter whose power stage is realized only with semiconductor devices is likely to have a higher power density and lifetime than the B2BIs. This was the motivation behind finding a more semiconductor reliant mechanism for power conversion.

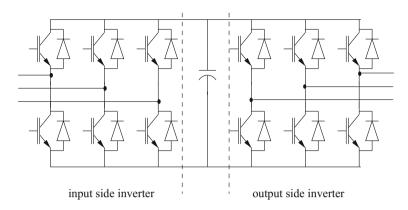

Topologically MC is similar to buck converter. Although the former is mostly associated with AC power and the latter strictly with DC, a look at the evolution of a buck converter helps to appreciate how MCs work. Figure 1.2 shows the power stage of a buck converter where the single pole double throw switch Sw is periodically connected to the positive and negative terminals of the input DC voltage source  $V_{in}$ . This results in a pulsating voltage  $v_{sw}$  at the output. The DC component of  $v_{sw}$  can be obtained by averaging the pulse waveform over the switching period  $T_s$  as

$$V_{sw} = \frac{1}{T_s} \int_0^{T_s} v_{sw} dt = dV_{in}.$$

(1.1)

© Springer Nature Singapore Pte Ltd. 2017

A. Dasgupta and P. Sensarma, *Design and Control of Matrix Converters*, Energy Systems in Electrical Engineering, DOI 10.1007/978-981-10-3831-0\_1 1

Fig. 1.1 Power processing stage of 3 phase to 3 phase back to back inverters

Fig. 1.2 Buck converter realized with a single pole double throw switch

Thus, by regulating the duty cycle d it is possible to synthesize a desirable DC component of the switched voltage  $v_{sw}$ . The switching frequency  $(f = 1/T_s)$  components and its harmonics which are also present in  $v_{sw}$  can be subsequently attenuated to a large extent by using a *LC* filter. The important point to note here is that any desirable value of the DC component of the output voltage can be generated as long as this value is less than the source voltage  $V_{in}$ .

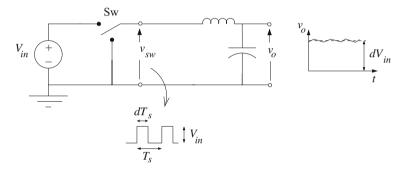

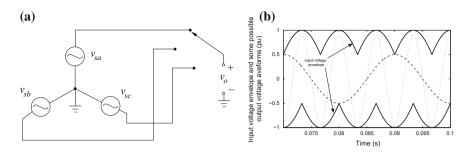

Another useful aid in the analysis of 3-phase MC is the output voltage of a 3-phase AC to DC rectifier. Figure 1.3a shows a diode rectifier and the output voltage is shown in Fig. 1.3b. Let the input voltages be

$$v_{sa} = sin2\pi50t, \quad v_{sb} = sin(2\pi50t - 120^\circ) \quad \& \quad v_{sc} = sin(2\pi50t + 120^\circ).$$

(1.2)

Replacing the 3 diodes connected to each of the output terminals by a fully controllable single pole-triple throw(SPTT) switch results in the converter shown in configuration Fig. 1.4. S1 and S2 are the two SPTT switch. Presence of the two SPTT switches makes it possible to synthesize a sinusoidal voltage at the output terminals. The pole of each SPTT switch is connected to the output terminal which ensures that

Fig. 1.3 a 3-phase diode rectifier. b Output voltage

Fig. 1.4 A 3-phase to 1-phase AC converter power stage

the output is always connected to any one of the input voltages. It ensures that the path of the current through the load is never interrupted—a mandatory requirement for inductive load. Figure 1.5 shows the envelope of the input voltages for all possible switching combinations. Taking cue from the operation of buck converter, it should be possible in a similar manner to generate the desired fundamental component of a target AC voltage from the 3-phase source. If the turn-on and turn-off durations of the individual SPTT switches can be properly regulated it is possible to synthesize an output voltage  $v_o$  with a desired fundamental frequency component. The only restriction towards achieving this is that the fundamental component must be completely encapsulated within the input voltage envelope. Referring to Fig. 1.5, this restriction implies that the maximum amplitude of  $v_o$  is 0.866 times that of the input line-line voltage amplitude. Within this amplitude limit, a fundamental component of  $v_o$  having any amplitude, phase and frequency can be produced by appropriately regulating the SPTT switches.

The mode of operating a 3 to 1-phase AC converter can be extended to 3-phase to 3-phase AC conversion as well. Figure 1.6 shows a 3-phase to 3-phase AC to AC converter structure made up of 3 SPTT switch. Since the 3-phase output voltages have to be synthesized directly from the 3 input phases all possible 3-phase output voltage envelopes must be completely encapsulated by the input voltage envelope. Consequently, the maximum achievable gain in voltage amplitude is 0.866. Apart

Fig. 1.5 Envelope of the input voltage waveform

from this fundamental limitation, there is no theoretical limitation on the possible set of output voltage waveforms. Therefore, the operational requirements are simply realization of the SPTT switches by using available semiconductor switches and devising an appropriate scheme for controlling them.

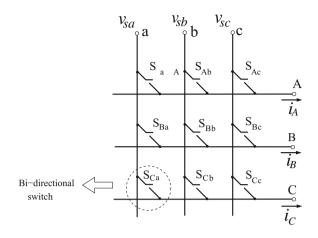

Each SPTT switch can be realized by 3 single pole-single throw (SPST) switch. By replacing the SPTT switch by 3 SPST switch with common poles connected to an output phase, the topology shown in Fig. 1.7 is obtained. The 9 SPST appears to be arranged in a  $3 \times 3$  matrix and hence the topology is referred to as Matrix converter.

The input terminals of the MC are connected to voltage source and consequently the output terminals has to be connected either resistive or inductive load. The nature of the source and loads which are mostly inductive sets up the following fundamental switching law which must be obeyed

- input terminals should never be shorted,

- output terminals should never be left opened.

#### 1 Introduction

**Fig. 1.7** Power processing stage of a 3 phase to 3 phase MC

These constraints can be expressed in terms of switching functions as

$$S_{ja}(t) + S_{jb}(t) + S_{jc}(t) = 1$$

, where,  $j \in \{A, B, C\}$ . (1.3)

At any instant, a switching function  $S_{xy}(t)$  is either 0 if the switch  $S_{xy}$  is open or 1 if it is closed. There can be 27 (3 × 3 × 3) switching combinations for connecting the output with input side, which obey these fundamental switching rules.

Figure 1.7 represents the conceptual building block of MC topology. Realization of a fully operational converter involves realization of the switches by means of available commercial devices and a control law for controlling these devices. Since AC variables are dealt with at the input as well as output side, these SPST switch must be capable of blocking voltages of both polarity and conducting current in both directions.

This book chapter aims to elaborate only on some aspects of design and control of MC from the perspective of low to medium power level applications in the distribution side of power system. Before moving to the details, an overview of 3-phase MC is provided in the following sections to impart an overall understanding of the key design and operational aspects of MC. Those readers who are familiar with MCs may skip this part and start from Sect. 1.2.

#### 1.1 Overview of 3-Phase Matrix Converter

The different design/operational aspects of MC can be broadly be categorized into the following: hardware design, commutation of switches, structure of the topology, modulation and control schemes. These are summarized in the following sections.

#### 1.1.1 Hardware Design

Hardware design begins with the realization of a bidirectional switch. If the switching laws are violated it may lead to short circuit at the input side leading to high input current and eventually failure of the converter. On the other hand if the current flowing through an inductive load is interrupted due to error in switching it would result in high voltage appearing across the switch and eventually lead to its failure. So a protection mechanism for the switches in these situations is a critical feature in design of the hardware. Another very important aspect in hardware design is designing the switching frequency ripple filters. Each of these aspects are discussed below.

#### 1.1.1.1 Realization of a Bidirectional Switch

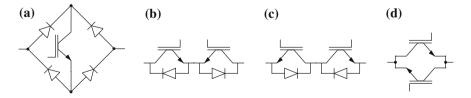

A bidirectional switch should be capable of conducting current as well as blocking voltages of both polarity. This cannot be achieved by using a single discrete semi-conductor device and thus it has to be configured by using more than one switch.

Different ways of realizing a bidirectional switch with discrete IGBT and diodes are shown in Fig. 1.8. Figure 1.8a shows one of the configurations, which is however not used in MCs. One of the reasons behind this is presence of highest number of devices in the current conduction path, leading to higher conduction losses. A more important reason is that it is not possible to selectively allow or block current of a particular direction through this bidirectional switch. So if an output phase has to be switched from one input phase to another, it cannot be done without turning off this switch which leads to violation of the fundamental switching rules. Readily available anti parallel arrangement of diode and IGBTs can be connected to form either the common emitter (CE) or common collector (CC) configurations shown in Fig. 1.8b, c respectively. In terms of device count, bidirectional switch using Reverse blocking (RB) IGBTs shown in Fig. 1.8d is clearly the best option. However RB IGBTs are still not widely available.

Fig. 1.8 Realizing bidirectional switch. a Diode bridge with IGBT, b common emitter, c common collector, d reverse blocking IGBTs

Fig. 1.9 a Power stage of MC looking from source and load side. b Input filter. c Output filter

#### 1.1.1.2 Filter Design

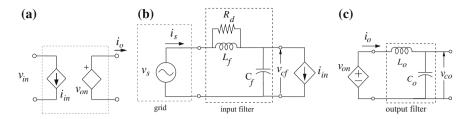

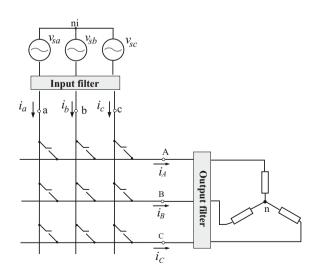

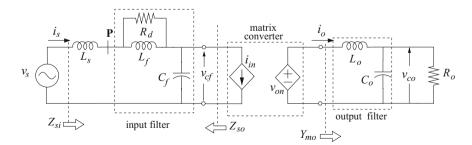

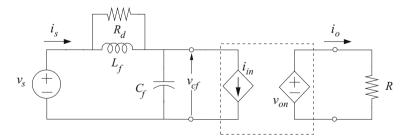

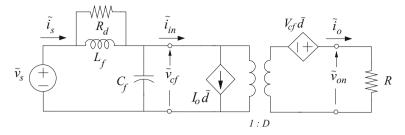

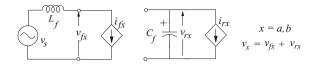

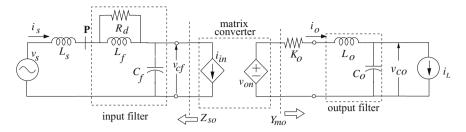

Like a buck converter, the power stage of MC presents current and voltage stiff terminal properties when viewed from the source and load respectively. This is shown in Fig. 1.9a where the MC is modeled as appropriate controlled sources. Balanced 3 phase system has been considered which allows analysis on a single phase basis.

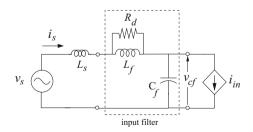

The controlled sources shown in Fig. 1.9a are composed of fundamental as well as switching frequency  $(f_s)$  components. Hence, the input side has to be interfaced to the input source through ripple filters to ensure only low-frequency interaction at fundamental frequency. Input filter is an essential requirement of this topology for providing a local circulating path to the switching frequency current. Output side filters are also necessary in applications which require a filtered voltage to be applied to the load. At the same time it has to be ensured through design that addition of filters do not degrade performance parameters like voltage regulation, efficiency and size. These place conflicting demands on the choice of filter elements. Moreover, as the basic structure of MC is made of bi-directional switches, the only associated inertial elements in this topology are the filter components. Consequently the filter parameters affect the system dynamics significantly.

Input filter design has been discussed in [1-6], where, from cost and weight considerations, single stage LC filter has been found to be the most appropriate topology. Figure 1.9b, c show the widely used input and output filter configurations. It is not possible to control the input current in MC, hence a damping resistor is used for the input filters. Although the set of filter elements  $(L_f, C_f)$  for a particular resonant frequency is infinite, [2] advocates a maximum  $C_f$  to ensure minimum leading Input Displacement Factor (IDF) at low loading conditions. However, in a distribution system most of the loads are inductive and hence this should not be a major concern at lighter loads. An exhaustive treatment of input/output filters with focus on reducing electromagnetic interference and common-mode voltages has been provided in [7]. However, most of these have not investigated the comprehensive design of filters in the context of dynamic performance requirements or reliability of commutation hardware. Filter design, considering stability limits detailed in [8, 9], has been discussed in [6]. However, it will be discussed in a subsequent chapter of this book, that with a proper choice of the modelling paradigm, the derived plant has non-minimum phase zeros but minimum phase poles for all operating points.

Fig. 1.10 Clamp circuit

Therefore a stable plant is obtained. The relation between filter parameters and nonminimum phase zeros would be detailed and the modifications necessary in filter design will also be discussed.

#### 1.1.1.3 Protection Schemes

Standard protection schemes like overcurrent and overvoltage protection used in any converter are also necessary in MCs. The switches need to be protected in the event of short circuit at input side and open circuit at the output side. Protection for high current during shorting of input terminals can be realized on the gate drivers of the switches themselves. Standard technique like sensing the collector to emitter voltage across an IGBT to detect short circuit can be employed.

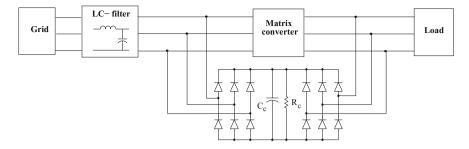

Interruption of load current, during communication or due to activation of protection circuit following any fault, may result in high voltage at the output side. Normally a diode clamp circuit along with a capacitor ( $C_c$ ) and discharging resistor ( $R_c$ ) as shown in Fig. 1.10 is used to absorb the energy of inductive load [4]. Design of the clamp capacitor has been presented in [5]. Clamp circuits requiring lesser number of diodes have also been proposed in the same paper. This circuit also protects the MC from overvoltages at grid side. Overvoltage protection using varistors and zener diodes with high blocking capability is reported in [10].

#### 1.1.2 Commutation

One of the major hurdles in controlling MCs is switching a load from one input terminal to another without violating the fundamental switching rules. This difficulty in switching can be understood with the example of a two phase to single phase MC feeding an inductive load shown in Fig. 1.11. The bidirectional switch are realized through the CE configuration using discrete IGBTs and diodes. IGBTs in each bidirectional switch ( $S_1$  and  $S_2$ ) supporting conduction in the forward (towards

Fig. 1.11 2 phase to 1 phase MC

load) or backward are denoted with additional subscripts F and R respectively. Load was initially connected to  $v_1$  and a switchover to  $v_2$  is required. Now, simultaneous switching of S<sub>1</sub> and S<sub>2</sub> shorts the input terminals, while sequential switching leads to momentary opening of load terminal.

To avoid this a multi-step commutation process based on either output current direction or relative input voltage magnitude [11, 12] becomes necessary. The objectives of these methods are to ensure that the current is not interrupted and at the same time input terminals are not shorted at any instant during the process of commutation. These approaches are detailed in the following subsections.

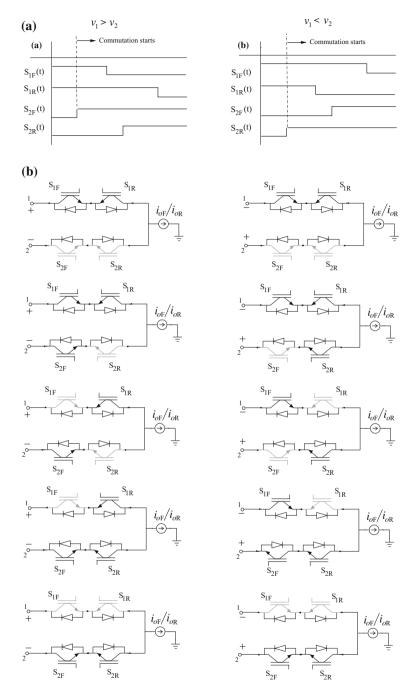

#### 1.1.2.1 Output Current Direction Based Commutation

Output current direction must be correctly determined for this method to be successful. Figure 1.12a shows the switching sequence from  $S_1$  to  $S_2$  for forward  $(i_{oF})$  and reverse  $(i_{oR})$  direction of  $i_o$ , respectively. The sequence is shown in terms of switching function of each IGBT. As an example, commutation sequence for  $i_{oF}$  is described. Figure 1.12b shows the different stages of commutation in the two phase to single phase MC. IGBTs shown in bolder mark are those which are turned on (gating pulses are provided), while those which are shown in grey shade indicate the turned off IGBTs.

- Step 1. Non conducting IGBT  $(S_{1R})$  in the outgoing bidirectional switch  $S_1$ , is first turned off.

- Step 2. Next, the IGBT in the incoming S<sub>2</sub> that can support conduction of  $i_{oF}$  i.e. S<sub>2F</sub> is turned on. If  $v_2 > v_1$ , then natural commutation from S<sub>1</sub> to S<sub>2</sub> takes place at this stage.

- Step 3.  $S_{1F}$  is turned off subsequently. If  $v_1 > v_2$ , then forced commutation from  $S_1$  to  $S_2$  occurs at this stage.

- Step 4. Finally,  $S_{2R}$  is turned on.

Fig. 1.12 Switching from  $S_1$  to  $S_2$  based on output current. **a** Timing diagram. **b** Stages of commutation

In steady state, both IGBTs in a bidirectional switch are turned-on to allow reversal of current. The commutation process is thus achieved through 4 steps of turn off-on-off-on sequence. Since turning on times of IGBTs are much lower than the turn off duration, the second and third step can be concurrently executed thereby resulting in a three step commutation method.

Since the first step involves turning off an IGBT, incorrect current direction measurement would lead to open circuit of the load. During the zero crossovers (ZC) of  $i_o$ , correctly sensing its direction may become difficult. To overcome this, a method where the direction of  $i_o$  is derived by measuring voltage across each device has been reported in [13]. Conceptually this amounts to using an arrangement similar to what is shown in Fig. 1.13. The collector voltage of each device is fed to a comparator, whose output state determines the instantaneous current direction. For example, if the direction of current *i* is downward as shown, the comparator output would be approximately V<sub>cc</sub>. Since the device has to block the input line to line voltage in blocking mode, the voltage at input of the comparator has to be clamped to the control voltage level. Hence, the major fraction of the voltage appears across R. So the value of R has to be high enough to restrict the power loss to an acceptable level. Apart from the increased number of components in this method, use of a high R along with unavoidable stray capacitances makes the measurement prone to errors due to the inherent delays involved [14, 15].

#### 1.1.2.2 Input Voltage Magnitude Based Commutation

This method requires knowledge of the relative magnitudes of input voltages. Figure 1.14a, b shows the switching sequence from  $S_1$  to  $S_2$  for different polarities of  $v_1 - v_2$ . For  $v_1 > v_2$ , the commutation process as shown in these figures is achieved in the following manner.

- Step 1.  $S_{2F}$  is turned on. This activates the conduction path for  $i_{oF}$  in  $S_2$ , while ensuring that there is no circulation current between the two input phases.

- Step 2.  $S_{1F}$  is turned off. At this instant, if  $i_o$  is in forward direction ( $i_o = i_{oF}$ ), conduction is taken up by  $S_2$  i.e. forced commutation takes place here. However, if  $i_o$  is in the backward direction ( $i_o = i_{oR}$ ) conduction would still be supported by  $S_1$ .

**Fig. 1.14** Switching from  $S_1$  to  $S_2$  based on relative magnitude of  $v_1$  and  $v_2$ . **a** Timing diagram. **b** Stages of commutation

Step 3.  $S_{2R}$  is turned on. Therefore conduction path for  $i_{oR}$  gets activated in  $S_2$  and since  $v_1 > v_2$ , natural commutation occurs for reverse current flow.

Step 4. Finally  $S_{2F}$  is turned off.

If the relative voltage magnitudes can be clearly distinguished the first two steps and the third and fourth step can be merged to form a two step sequence.

Voltage based commutation starts with a turning on process. Here, the major concern is correct polarity detection of phase to phase input voltage during its ZC. Falsely detecting this polarity would lead to shorting of the two input terminals. The difficulty in detecting the polarity is compounded by the presence of switching frequency ripple component. Around ZC of the line to line voltage the magnitude of its fundamental component is small but the same does not hold for the ripple component. Also it is much more difficult to accurately measure the switching frequency component than the slowly varying fundamental component.

This issue has been addressed in various papers on commutation. In [16], an analysis of critical window width around ZC of input line voltages has been provided, based on the magnitude of fundamental component of input voltage and resonant component that appears due to the input filter oscillations. During commutation between two phase voltages lying in this defined window, an intermediate step is introduced where the switch over takes place through the third phase. However the effect of the input switched current which plays the major role behind switching frequency ripple in input voltage has been ignored.

In [17], it is shown that with proper zero vector placement for Space vector modulation (SVM) based approaches, safe commutation can be achieved in spite of voltage measurement inaccuracies. This method is restricted to operation within a certain input displacement angle  $(\pm \theta^{\circ})$  around voltage ZC, where  $\theta$  is to be decided on the basis of the specific input ripple voltage measurements for a given hardware. Moreover, as this method depends on minimum duration of zero vectors it is not applicable to all operating points. For all operating regions and in applications requiring wider control of IDF [18, 19], commutation at ZC of line-line voltage is still difficult, particularly at high output current amplitude.

There is no guide for conclusively selecting a particular method for an application. However, applications having a high inductance at the output side will have a low switching ripple component in the output current. Therefore it is easier to sense to measure the output current correctly and thus current based techniques may be better suited for such conditions. For applications requiring a regulated sinusoidal output voltage, an output filter becomes necessary. The inductor in this filter which is in series with the output terminals must be small so that the voltage drop is less. Consequently the ripple components of the current would be large and so would be the magnitude of error in measuring it. The applications considered in this work falls in the latter category. Existing input voltage based commutation method is adopted in this work. A closed-form expression of the ripple voltage in the input filter capacitor and error in measurement has been derived. This is used to derive the minimum size of filter capacitor as would be detailed in a subsequent chapter.

#### 1 Introduction

Fig. 1.15 Indirect MC

#### 1.1.3 Topology

The structure shown in Fig. 1.7 is referred to as the Direct Matrix Converter (DMC). The operational challenges associated with DMC have prompted engineers to find out variants of this basic structure that may simplify some of the operational issues.

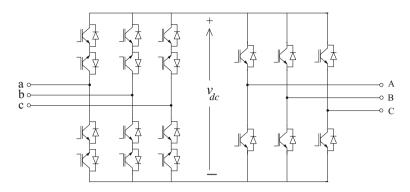

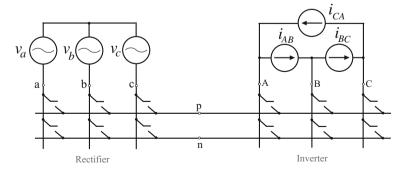

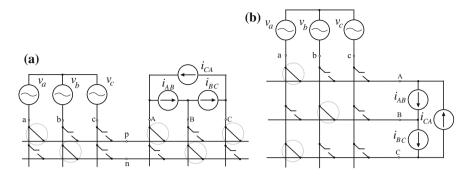

Figure 1.15 shows a variant of the basic MC topology. This is known as Indirect MC (IMC) [20]. The power processing in this structure is achieved through rectification and inversion process as found in B2B VSIs. Commutation is reported to be simpler than DMCs [20, 21], as the rectifier stage bidirectional switches can be switched when the inverter side is in free wheeling mode. In this condition, commutation at the rectifier side is not constrained by any restriction on the opening of the output terminals and only needs to ensure that the input terminals are never shorted. Since the DC link voltage ( $v_{dc}$ ) has to be positive, IDF can be controlled in the range 0.866–1. Reduction of IMC structure leading to varying forms of 'Sparse Matrix Converters' has been summarized in [21].

This work is related to power system applications for synchronous systems. In such applications reactive power plays a significant role. Although control of input reactive power has not been attempted in this work, it can be included in future investigations by extending the analysis presented here. Since DMC offers a much wider scope of IDF control than IMC, it has been adopted here. Hence, subsequent discussions are related to DMCs. However since the basic functional feature of both DMC and IMCs are same, discussion related to dynamic model, filter design and modulation applies equally to both topologies.

#### 1.1.4 Modulation

A large number of modulation techniques have been reported, dating back to the inception of MC. A few of those, which have been critically evaluated, are discussed here.

Fig. 1.16 a Input voltage. b Output voltage envelope for all 27 switching combinations

Fig. 1.17 a Input voltages. b Input and target output voltages. c Target output voltages along with common mode voltages. d Reshaped target voltages. e Input along with reshaped target output voltages

#### **1.1.4.1** Direct Transfer Function Based Approach

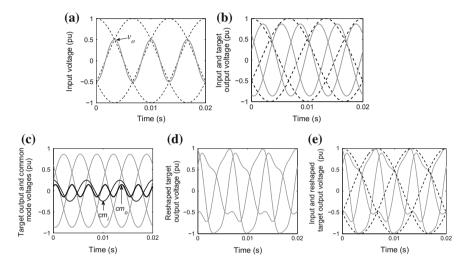

One of the earliest papers [22] known to provide a rigorous analysis of a 3-phase MC demonstrated this approach (Fig. 1.16).

This method derives the low frequency modulation signals directly from the reference and input voltages. In the first algorithm [22] the envelope of output voltage waveform to be synthesized must remain within the input voltage envelope at all instants of time. Consequently, as shown in Fig. 1.17a, the maximum achievable output voltage ( $v_o$ ) amplitude is 0.5 times of the input. The performance was significantly improved in the second algorithm [23] where the maximum 0.866 voltage gain ratio could be reached. The essence of the second algorithm is explained with the help of Fig. 1.17b–e. Figure 1.17b shows the input and target output voltages whose amplitude are 0.866 times of the input. The output waveform is observed to exceed the input waveform envelope at some intervals. By appropriately adding common mode (*cm*) terms, the second algorithm reshapes the target voltage envelope to completely fit into the input envelope. Figure 1.17c shows the third harmonic *cm* components for input (*cm<sub>i</sub>*) and output (*cm<sub>o</sub>*) which are added on to the target output waveform. Figure 1.17d shows the reshaped target waveforms, the envelope of which is now completely enclosed by that of the input waveform, as shown in Fig. 1.17e. Since the load and supply neutrals are usually isolated and the *cm* terms disappear from the line to line voltages, addition of these low frequency terms are justified. Denoting the input and target output voltage amplitude and frequency as  $\hat{V}_i$ ,  $\hat{V}_o^*$ , and  $\omega_i$ ,  $\omega_o$  respectively, the described procedure is equivalent to generating the output voltage references as [23],

$$\hat{V}_{o}^{R} \begin{bmatrix} \cos(\omega_{o}t) \\ \cos(\omega_{o}t - 120^{\circ}) \\ \cos(\omega_{o}t + 120^{\circ}) \end{bmatrix} = \hat{V}_{o}^{*} \begin{bmatrix} \cos(\omega_{o}t) \\ \cos(\omega_{o}t - 120^{\circ}) \\ \cos(\omega_{o}t + 120^{\circ}) \end{bmatrix} + \underbrace{\frac{\hat{V}_{i}}{4} \begin{bmatrix} \cos(3\omega_{i}t) \\ \cos(3\omega_{i}t) \\ \cos(3\omega_{i}t) \\ \cos(\omega_{i}t) \end{bmatrix}}_{cm_{i}} - \underbrace{\frac{\hat{V}_{o}^{*}}{6} \begin{bmatrix} \cos(3\omega_{o}t) \\ \cos(3\omega_{o}t) \\ \cos(3\omega_{o}t) \\ \cos(3\omega_{o}t) \\ \cos(3\omega_{o}t) \end{bmatrix}}_{cm_{o}} \tag{1.4}$$

If the output load angle  $(\phi_L)$  can be measured, IDF can also be controlled using the second algorithm. The same maximum voltage gain and IDF control can be achieved by other modulation methods without the necessity of measuring  $\phi_L$  and therefore having a relatively simple hardware realization. They are described in the following section.

#### 1.1.4.2 Space Vector Modulation (SVM)

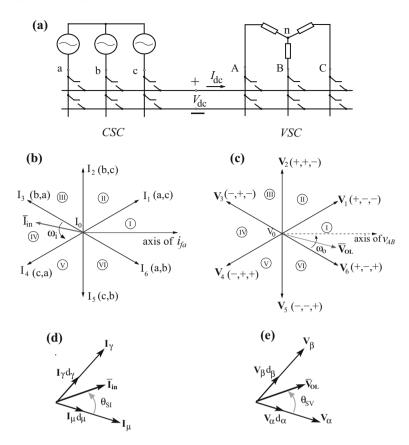

The power stage of MC can be viewed [24] as a cascaded rectifier-inverter stage coupled by a fictitious DC link as shown in Fig. 1.18. SVM based on this decoupled construct allowing control of IDF has been described in [25]. This method is referred

Fig. 1.18 Decoupled rectifier-inverter construct

Fig. 1.19 Mapping the switching functions

in this book as Indirect space vector modulation (ISVM). Here, the duty ratios of the switches for individual stages are initially calculated and then combined on the basis of instantaneous active power balance between input and output. Thereafter, the switching functions for the twelve switches are mapped to the nine 4Qsws MC structure. An example of this mapping from the 12 to 9 switch structure is shown in Fig. 1.19a, b. Suppose the input terminal a in the decoupled structure needs to be connected to output terminals A and C, while terminal b to output terminal B as shown in Fig. 1.19a. The corresponding switches which need to be closed in the 9 switch structure are shown in Fig. 1.19b.

A maximum voltage gain of 0.866 for unity IDF is attainable with ISVM. Hardware realization of ISVM is simpler than direct approaches and knowledge of  $\phi_L$  is not required for IDF control. Moreover, space vector based schemes offers substantial freedom in choosing the switching sequence which can be used for reducing common mode voltage at the output [26], output current ripple [27], reducing switching losses [28] etc. These features make SVM one of the most widely adopted modulation method in MCs. The basic working principle of ISVM has been briefly discussed later in this book.

#### 1.1.4.3 Other Pulse Width Modulation (PWM) Based Methods

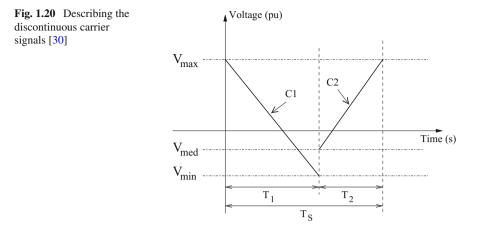

One of the often stated disadvantages of SVM lies in the use of look-up tables for hardware realization. This has been the primary inspiration for alternate PWM methods like [29] where *cm* terms are added to modulation signals in order to achieve a voltage gain of 0.866. Control of IDF is also possible in this scheme. Another carrier based method [30] emulates the input line to line voltages as the DC link voltage of an inverter and by doing so tries to extend modulation strategies for VSI to MC. The method proposes to use two input line to line voltage as the imaginary DC link voltage over a switching cycle. The input voltages are denoted as  $V_{max}$ ,  $V_{med}$  and  $V_{min}$  based upon their relative magnitudes, as shown in Fig. 1.20. The switching period  $T_s$  is divided into two parts  $T_1$  and  $T_2$  depending on the input voltage angle.

Now for the two separate parts of the switching cycle, two carriers ( $C_1$  and  $C_2$ ) are defined as the difference between the values of input voltages. The argument behind using two carriers, is, utilization of all three input voltages during a switching period [30]. If two inputs are only used, one of the input phase currents would remain zero thereby leading to higher input current distortion. A voltage gain of 0.866 in the linear modulation region and unity IDF is ensured with this method.

The PWM based methods are gradually becoming an active area of research. The performance in terms of voltage gain and controllable IDF has been proven to be equivalent to SVM methods. However the superiority or equivalence of these in context of the flexibility shown by SVM schemes in choosing and placing the zero vectors is yet to be established.

#### 1.1.4.4 Discrete Methods Based on Predictive Model

Modulation methods based on discrete models have been a very actively researched topic in the last decade. These methods use discrete-time models of the load, filter and converter to predict behaviour of variables like load current, reactive power etc. For example, if the objective is to control the output current ( $i_o$ ), its value at k + 1th sampling instant is first computed using the predictive models for all valid switching states. The resulting absolute error between the reference and predicted values for a single valid switching state can be represented as

$$\Delta i_o(k+1) = \left| i_o^*(k+1) - i_o^p(k+1) \right|, \tag{1.5}$$

where \* and <sup>*p*</sup> denote reference and predicted values respectively. Subsequently, the state that gives minimum  $\Delta i_o(k + 1)$  is chosen as the k + 1th switching state. However, as no current feedback is used, this may cause unchecked deviation of actual current. The strength of the method lies in its flexibility to address multiple

control objectives. An example of this was reported in [31], where the objective was to control  $i_o$  and minimize input reactive power  $q_s$ . A quality function ( $Q_G$ ) was defined as

$$Q_G = W1 \cdot \Delta i_o(K+1) + W2 \cdot \Delta q_s(K+1), \tag{1.6}$$

where W1, W2 are weighting functions. An analytical approach of choosing the weighting functions is yet to be reported. On basis of a particular set of W1 and W2,  $Q_G$  is calculated for all the 27 valid switching states of MC. Thereafter the state resulting in minimum  $Q_G$  is selected at the next switching instant. Applications of this predictive model based approach for different control objectives are summarized in [32].

Keeping aside the obvious concern regarding the accuracy of the predictive models, on-line computation of  $Q_G$  for all valid switching states would increase the computational burden to a great extent. Superiority of this technique over the performance obtained with SVM approaches has not been established yet [32].

#### 1.1.5 Dynamic Model for Controller Design

Tight coupling between the input and output side of MC complicates controller design, particularly for applications requiring high bandwidth. Hence, for stable operation, a proper control scheme based on a tractable dynamic model becomes necessary—an area, which has not received sufficient attention. This has been acknowledged in [33] which presents a dynamic model for MC used as an interface between high speed micro turbine generator and the utility grid. The model is developed using state matrices, which is subsequently utilized for design of active and reactive power control. State feedback approaches based on eigenvalue analysis has been used in [34] for voltage sag mitigation, another application which demands high dynamic performance. With available tools like MATLAB control toolbox, designing controllers using state matrices is not difficult and desired dynamic performance is guaranteed provided the system is well modeled. But these methods provide little insight into the system as associating the eigenvalues, or critical dynamic behavior, with specific physical elements becomes increasingly difficult with higher order systems.

In the context of stable operation of MCs, [8, 9, 35–38] have reported and analyzed existence of a throughput power limit ( $P_{lim}$ ) for stable operation. In all these studies, for output voltage control, the reference  $\bar{V}_o^*$  is obtained treating the output filter and the load as plant. Subsequently the modulation signals are essentially computed as

$$\bar{m} = \frac{\bar{V}_o^*}{\bar{V}_{in}},\tag{1.7}$$

where  $\bar{V}_{in}$  is voltage vector of the input voltage  $v_{in}$  ( $v_{cf}$ ) applied at the input terminals shown in Fig. 1.9a, b. Although  $\bar{m}$  is not extracted exactly through a scalar division as it appears in (1.7), the conceptual basis is essentially same. This method is sometimes referred as feed forward compensation of input voltages [8].  $P_{lim}$  is prescribed by investigating the input side of MC assuming constant active power transfer through it. Investigation of how filtering  $\bar{V}_{in}$  affects the system eigenvalues has been reported in [36]. Examination of how sampling delays in measuring  $\bar{V}_{in}$  affects  $P_{lim}$  has been detailed in [8, 9] considering constant output power. More recently [38] has proposed use of the source voltage i.e.  $v_s$  in Fig. 1.9b in place of  $v_{cf}$  which improves the stability limit for grids having a low source impedance.

A detailed discussion on the dynamic model and appropriate controller design has been provided later in this book chapter.

#### **1.2 Motivation and Objectives**

Out of the different research tracks highlighted in the last section, major effort has been spent in investigating modulation algorithms that can extract the optimal performance out of MC in terms of voltage gain, IDF control, relative ease of hardware realization, switching losses etc. This has been followed by devising reliable commutation and protection strategies, alternative topologies with reduced number of switches in certain cases where unidirectional flow of power is required, input filter design etc. One of the lesser investigated area has been the development of a dynamic model that provides a physical insight into the system.

From the applications perspective, although MC is perceived as an alternative to B2B VSI (DAB), research efforts has been largely confined to motor/drive. The last decade have witnessed an emerging academic interest in using MC for power system applications. For example, it has been reported to be used as a reactive power compensator [18, 19], voltage sag compensator [34], regulated utility power supply [39], Unified power flow controller [40] to name a few.

A major motivation of writing this book is to introduce to the reader the considerations for using the MC for synchronous power system applications. Two typical applications were chosen for investigation—regulated voltage supply and voltage sag mitigation. Of course, several research publications have reported MC based solutions, along with dynamic model and control techniques, for interfacing with utility power systems. Section 1.1.5 of this book shows that some of these approaches, which are either based on feed forward compensation of input voltages or on state feedback based schemes, have specific limitations. Some reports, e.g. [34], incorporate an additional flywheel energy storage which negates the high power density advantages of the MC. Hence, the broad aim of this book is categorized into the following objectives.

1. Complexity of control has been widely acknowledged to be one of the major reasons for the low industrial acceptance of MC, even after three decades of

#### 1.2 Motivation and Objectives

intensive research. Control may become more difficult as one moves out of the motor/drives domain to power system applications, which demand faster dynamic performance. For a tightly coupled input-output unit like the MC, the system designer cannot take an independent approach towards design of sub components like filter and controller, without addressing common constraints that bind both. A dynamic model that helps to identify such common links and also aid the physical understanding of the system is presented in this book. So development of a tractable dynamic model by which the stated concerns can be addressed was set to be the first objective of the work.

- 2. The next goal was to obtain a design guideline for filters which should also take into consideration the constraints that emerge from the dynamic model and sizing of passives for reliable commutation.

- 3. Once the first two targets were achieved, controller design naturally became the third objective. Given that a recurring argument against using MC has been the difficulty of control, emphasis was given on finding a control scheme that is easily realizable.

- 4. Experimental validations of the analytical claims was set as the final objective.

## **1.3** Assumptions and Scope

The analysis presented in this book uses a set of assumptions, which are routinely made in MC analysis but are stated nevertheless for clarity. This also helps to delineate the scope of this book, which are listed below to enable correct evaluation of the material presented here.

- Plant model is derived assuming 3 phase balanced system. Harmonic distortions in supply voltage has not been considered.

- Modelling is confined to synchronous applications.

- Ideal converter and filter elements have been assumed.

- Dynamics of Phase lock loop (PLL) have not been considered.

- Harmonic analysis of MC has not been carried out.

- For voltage sag mitigation a 3 wire linear load is considered thereby removing any possibility of zero sequence component in load.

## 1.4 Layout of the Book

The rest of the book is structured in the sequence the objectives were described. The next chapter i.e. Chap. 2 describes the development of linearized plant model based on the low frequency gain of MC. The same model is used for the investigation of the plant for non-minimum phase poles/zeros. Chapter 3 presents the filter design approach where the different performance criteria are set in the process to