# Cryptographic Engineering

# Cryptographic Engineering

Çetin Kaya Koç Editor

# Cryptographic Engineering

Editor

Çetin Kaya Koç

City University of Istanbul

Tophane, Istanbul

Turkey

and

University of California Santa Barbara

Santa Barbara, CA

USA

ISBN: 978-0-387-71816-3 e-ISBN: 978-0-387-71817-0

DOI 10.1007/978-0-387-71817-0

Library of Congress Control Number: 2008935379

#### © Springer Science+Business Media, LLC 2009

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

While the advice and information in this book are believed to be true and accurate at the date of going to press, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

springer.com

To all scientists and engineers whose ideas gave birth to modern cryptography, particularly, Claude Shannon, Whit Diffie, Martin Hellman, Ralph Merkle, Don Coppersmith, Ron Rivest, Adi Shamir, Len Adleman, and Neal Koblitz.

# **Preface**

Cryptography is an ancient art. Chinese, Roman, and Arab cultures often used ciphers to protect military and state communications or secret society documents. Cryptographic engineering, on the other hand, is a relatively new subject. A cryptographic engineer designs, implements, tests, validates, and sometimes reverse-engineers or attempts to break cryptographic systems. The designers of Enigma, an electromechanical cipher machine, were cryptographic engineers; so was Alan Turing who contributed to its cryptanalysis. In our view, anyone who designs and builds electromechanical, electronic, or quantum-mechanical systems in order to encrypt, decrypt, sign or authenticate data is a cryptographic engineer. However, in this book we have narrowed our definition to only electronic systems, specifically, hardware and software systems.

Cryptographic engineering is a complicated, multidisciplinary field. It encompasses mathematics (algebra, finite groups, rings, and fields), electrical engineering (hardware design, ASIC, FPGAs) and computer science (algorithms, complexity theory, software design, embedded systems). It is rather difficult to be a master of all subjects; one usually has to be content with being a master of one. In order to practice state-of-the-art cryptographic design, mathematicians, computer scientists, and electrical engineers need to collaborate.

This book was born out of the class notes of the lecturers who have been meeting since 2002 in Lausanne, Switzerland, at the campus of EPFL, to teach a one-week course to graduate students, faculty, and researchers from academia, and engineers from industry. In order to create this book, I compiled the lecture notes together, wrote some of the material, and also invited other prominent researchers to contribute. This book is intended to constitute a first step towards becoming a cryptographic engineer. We hope that it will successfully serve its purpose.

Istanbul & Santa Barbara

Çetin Kaya Koç

# **Contents**

| 1 | Abou             | it Cryptographic Engineering                                     | 1  |  |  |  |  |

|---|------------------|------------------------------------------------------------------|----|--|--|--|--|

|   | Çetir            | ı Kaya Koç                                                       |    |  |  |  |  |

|   | 1.1              | Introduction                                                     | 1  |  |  |  |  |

|   | 1.2              | Chapter Contents                                                 | 2  |  |  |  |  |

|   | 1.3              | Exercises and Projects                                           | 4  |  |  |  |  |

| 2 | Ran              | dom Number Generators for Cryptographic Applications             | 5  |  |  |  |  |

|   | Werner Schindler |                                                                  |    |  |  |  |  |

|   | 2.1              | Introduction                                                     | 5  |  |  |  |  |

|   | 2.2              | General Requirements                                             | 6  |  |  |  |  |

|   | 2.3              | Classification                                                   | 7  |  |  |  |  |

|   | 2.4              | Deterministic Random Number Generators (DRNGs)                   | 7  |  |  |  |  |

|   |                  | 2.4.1 Pure DRNGs                                                 | 8  |  |  |  |  |

|   |                  | 2.4.2 Hybrid DRNGs                                               | 11 |  |  |  |  |

|   |                  | 2.4.3 A Word of Warning                                          | 13 |  |  |  |  |

|   | 2.5              | Physical True Random Number Generators (PTRNGs)                  | 14 |  |  |  |  |

|   |                  | 2.5.1 The Generic Design                                         | 14 |  |  |  |  |

|   |                  | 2.5.2 Entropy and Guesswork                                      | 16 |  |  |  |  |

|   | 2.6              | Non-physical True Random Number Generators (NPTRNGs):            |    |  |  |  |  |

|   |                  | Basic Properties                                                 | 18 |  |  |  |  |

|   | 2.7              | Standards and Evaluation Guidances                               | 20 |  |  |  |  |

|   | 2.8              | Exercises                                                        | 20 |  |  |  |  |

|   | 2.9              | Projects                                                         | 21 |  |  |  |  |

|   | Refe             | rences                                                           | 21 |  |  |  |  |

| 3 | Eval             | <b>Evaluation Criteria for Physical Random Number Generators</b> |    |  |  |  |  |

|   | Wern             | Werner Schindler                                                 |    |  |  |  |  |

|   | 3.1              | Introduction                                                     | 25 |  |  |  |  |

|   | 3.2              | Generic Design                                                   | 26 |  |  |  |  |

|   | 3.3              | Evaluation Criteria for the Principle Design                     | 27 |  |  |  |  |

|   | 3.4              | The Stochastic Model                                             | 20 |  |  |  |  |

x Contents

|   | 3.5    | Algorithmic Postprocessing                             | 37 |

|---|--------|--------------------------------------------------------|----|

|   | 3.6    | Online Test, Tot Test, and Self Test                   | 41 |

|   |        | 3.6.1 Online Tests                                     | 42 |

|   | 3.7    | Alternative Security Philosophies                      | 49 |

|   | 3.8    | Side-channel Attacks and Fault Attacks                 | 50 |

|   | 3.9    | Exercises                                              | 51 |

|   | 3.10   | Projects                                               | 51 |

|   | Refere | ences                                                  | 52 |

| 4 | True   | Random Number Generators for Cryptography              | 55 |

|   | Berk S | Sunar                                                  |    |

|   | 4.1    | Introduction                                           | 55 |

|   | 4.2    | TRNG Building Blocks                                   | 56 |

|   | 4.3    | Desirable Features                                     | 57 |

|   | 4.4    | Survey of TRNG Designs                                 | 57 |

|   |        | 4.4.1 Baggini and Bucci                                | 58 |

|   |        | 4.4.2 The Intel TRNG Design                            | 58 |

|   |        | 4.4.3 The Tkacik TRNG Design                           | 59 |

|   |        | 4.4.4 The Epstein et al. TRNG Design                   | 60 |

|   |        | 4.4.5 The Fischer–Drutarovský Design                   | 61 |

|   |        | 4.4.6 The Golić FIGARO Design                          | 62 |

|   |        | 4.4.7 The Kohlbrenner–Gaj Design                       | 63 |

|   |        | 4.4.8 The Bucci–Luzzi Testable TRNG Design Framework   | 64 |

|   |        | 4.4.9 The Rings Design                                 | 65 |

|   |        | 4.4.10 The PUF–RNG Design                              | 66 |

|   |        | 4.4.11 The Yoo et al. Design                           | 67 |

|   |        | 4.4.12 The Dichtl and Golić RNG Design                 | 67 |

|   | 4.5    | Postprocessing Techniques                              | 68 |

|   | 4.6    | Exercises                                              | 70 |

|   | Refere | ences                                                  | 71 |

| 5 | Fast I | Finite Field Multiplication                            | 75 |

|   |        | r Süer Erdem, Tuğrul Yanık, and Çetin Kaya Koç         |    |

|   | 5.1    | Introduction                                           | 75 |

|   | 5.2    | Finite Fields                                          | 76 |

|   | 5.3    | Multiplication in Prime Fields                         | 77 |

|   |        | 5.3.1 Integer Multiplication                           | 78 |

|   |        | 5.3.2 Integer Squaring                                 | 80 |

|   |        | 5.3.3 Integer Modular Reduction                        | 80 |

|   | 5.4    | Multiplication in Binary Extension Fields              | 87 |

|   |        | 5.4.1 Polynomial Multiplication over $\mathbb{F}_2$    | 88 |

|   |        | 5.4.2 Polynomial Squaring over $\mathbb{F}_2$          | 90 |

|   |        | 5.4.3 Polynomial Modular Reduction over $\mathbb{F}_2$ | 90 |

|   | 5.5    | Multiplication in General Extension Fields             | 96 |

|   |        | 5.5.1 Field Multiplication in OEF                      | 97 |

|   |        | 5.5.2 Coefficient Multiplication and Reductions        | 98 |

|   |        |                                                        |    |

Contents xi

|   | 5.6   | Karatsuba–Ofman Algorithm                                  | 99  |

|---|-------|------------------------------------------------------------|-----|

|   |       | 5.6.1 Complexity                                           | 100 |

|   |       | 5.6.2 Number of Scalar Multiplications                     | 100 |

|   | 5.7   | Exercises                                                  | 102 |

|   | 5.8   | Projects                                                   | 103 |

|   | Refe  | rences                                                     | 103 |

| 6 | Effic | eient Unified Arithmetic for Hardware Cryptography         | 105 |

|   |       | y Savaş and Çetin Kaya Koç                                 |     |

|   | 6.1   | Introduction                                               | 105 |

|   | 6.2   | Fundamentals of Extension Fields                           | 106 |

|   | 6.3   | Addition and Subtraction                                   |     |

|   | 6.4   | Multiplication                                             | 110 |

|   |       | 6.4.1 Montgomery Multiplication Algorithm                  | 110 |

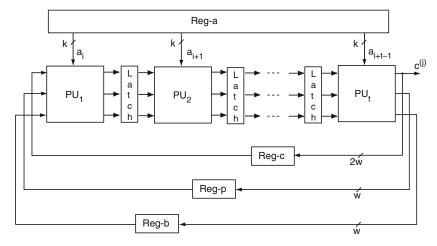

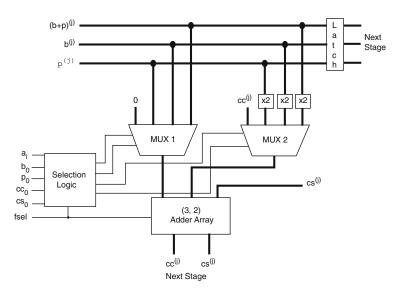

|   |       | 6.4.2 Dual-Radix Multiplier                                | 116 |

|   |       | 6.4.3 Support for Ternary Extension Fields, $GF(3^n)$      | 118 |

|   | 6.5   | Inversion                                                  |     |

|   |       | 6.5.1 Montgomery Inversion for $GF(p)$ and $GF(2^n)$       |     |

|   | 6.6   | Conclusions                                                |     |

|   | 6.7   | Exercises                                                  |     |

|   | 6.8   | Projects                                                   |     |

|   | Refe  | rences                                                     | 123 |

| 7 | Space | etral Modular Arithmetic for Cryptography                  | 125 |

| , |       | ay Saldamlı and Çetin Kaya Koç                             | 123 |

|   | 7.1   | Introduction                                               | 125 |

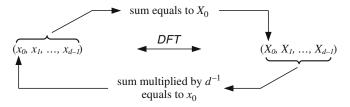

|   | 7.1   | Notation and Background                                    |     |

|   | 1.2   | 7.2.1 Evaluation Polynomials                               |     |

|   |       | 7.2.1 Evaluation Foryilonnals                              |     |

|   |       | 7.2.2 Properties of DFT: Time–frequency dictionary         |     |

|   | 7.3   | Spectral Modular Arithmetic                                |     |

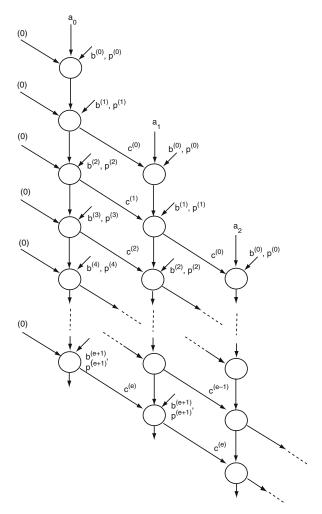

|   | 1.3   | 7.3.1 Time Simulations and Spectral Algorithms             |     |

|   |       | 7.3.2 Modular Reduction                                    |     |

|   |       | 7.3.3 Spectral Modular Reduction                           |     |

|   |       | 7.3.4 Time Simulation of Spectral Modular Reduction        |     |

|   |       | 7.3.5 Spectral Modular Reduction in a Finite Ring Spectrum |     |

|   |       | 7.3.6 Spectral Modular Multiplication (SMM)                |     |

|   |       |                                                            |     |

|   |       | 7.3.7 Spectral Modular Exponentiation                      |     |

|   | 7.4   | 7.3.8 Illustrative Example                                 | 152 |

|   | 7.4   | Applications to Cryptography                               |     |

|   |       | 7.4.1 Mersenne and Fermat rings                            |     |

|   |       | 7.4.2 Pseudo Number Transforms                             |     |

|   |       | 7.4.4 Parameter Selection for RSA                          |     |

|   | 75    | 7.4.4 Parameter Selection for ECC over Prime Fields        |     |

|   | 7.5   | Spectral Extension Field Arithmetic                        |     |

|   |       | 7.5.1 Binary Extension Fields                              | 158 |

xii Contents

|   |                | 7.5.2 Midsize Characteristic Extension Fields                | 161        |

|---|----------------|--------------------------------------------------------------|------------|

|   |                | 7.5.3 Parameter Selection for ECC over Extension Fields      | 164        |

|   | 7.6            | Notes                                                        | 165        |

|   | 7.7            | Exercises                                                    | 166        |

|   | 7.8            | Projects                                                     | 167        |

|   | Refer          | ences                                                        | 168        |

| 8 | Ellipt         | ic and Hyperelliptic Curve Cryptography                      | . 171      |

|   |                | Boston and Matthew Darnall                                   |            |

|   | 8.1            | Introduction                                                 | 171        |

|   | 8.2            | Diffie – Hellman Key Exchange                                | 172        |

|   | 8.3            | Introduction to Elliptic and Hyperelliptic Curves            | 172        |

|   | 8.4            | The Jacobian of a Curve                                      | 173        |

|   |                | 8.4.1 The Principal Subgroup and $Jac(C)$                    | 174        |

|   | 8.5            | Computing on $Jac(C)$                                        | 174        |

|   | 8.6            | Group Law for Elliptic Curves                                |            |

|   | 8.7            | Techniques for Computations in Hyperelliptic Curves          | 178        |

|   |                | 8.7.1 Explicit Formulae                                      |            |

|   |                | 8.7.2 Projective Coordinates                                 |            |

|   |                | 8.7.3 Other Optimization Techniques                          | 179        |

|   | 8.8            | Counting Points on $Jac(C)$                                  | 179        |

|   | 8.9            | Attacks                                                      | 181        |

|   |                | 8.9.1 Baby-Step Giant-Step Attack                            | 181        |

|   |                | 8.9.2 Pollard Rho and Lambda Attacks                         | 181        |

|   |                | 8.9.3 Pohlig–Hellman Attack                                  | 182        |

|   |                | 8.9.4 Menezes–Okamoto–Vanstone Attack                        |            |

|   |                | 8.9.5 Semaev, Satoh-Araki, Smart Attack                      |            |

|   |                | 8.9.6 Attacks employing Weil descent                         |            |

|   | 8.10           | Good Curves                                                  |            |

|   | 8.11           | Exercises                                                    |            |

|   | 8.12           | Projects                                                     | 185        |

|   | Refer          | ences                                                        |            |

| 9 | Inctr          | uction Set Extensions for Cryptographic Applications         | 101        |

| , |                | o Bartolini, Roberto Giorgi, and Enrico Martinelli           | . 1/1      |

|   | 9.1            | Introduction                                                 | 191        |

|   | 7.1            | 9.1.1 Instruction Set Architecture                           |            |

|   | 9.2            | Applications and Benchmarks                                  |            |

|   | 7.2            | 9.2.1 Benchmarks                                             |            |

|   |                | 9.2.2 Potential Performance                                  |            |

|   | 9.3            | ISE for Cryptographic Applications                           |            |

|   | 9.3            | 9.3.1 Instructions for Information Confusion and Diffusion . |            |

|   |                | 9.3.2 ISE for AES                                            |            |

|   |                | 9.3.3 ISE for ECC applications                               |            |

|   | 9.4            | Exercises                                                    |            |

|   | 9.4            | Projects                                                     |            |

|   |                | ences                                                        | 220<br>229 |

|   | TAGE IN COLUMN | UHUUN                                                        | 4./.7      |

Contents xiii

| 10 | FPGA   | and AS                    | SIC Implementations of AES                         | . 235 |  |  |

|----|--------|---------------------------|----------------------------------------------------|-------|--|--|

|    | Kris G | aj and P                  | awel Chodowiec                                     |       |  |  |

|    | 10.1   | Introdu                   | ction                                              | . 235 |  |  |

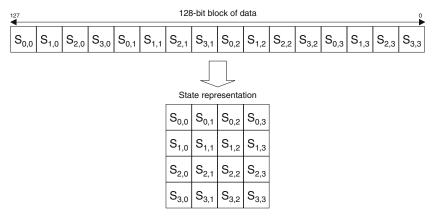

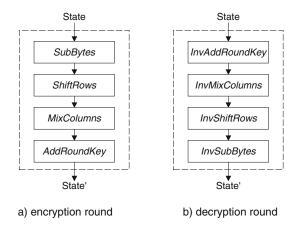

|    | 10.2   | AES Ci                    | pher Description                                   | . 236 |  |  |

|    |        | 10.2.1                    | Basic Features                                     | . 236 |  |  |

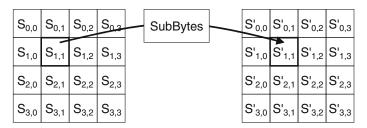

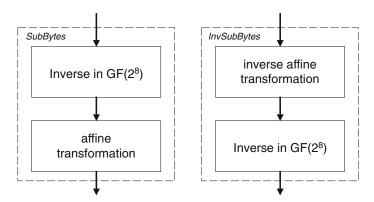

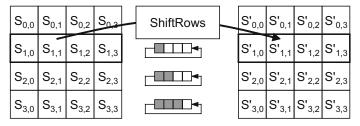

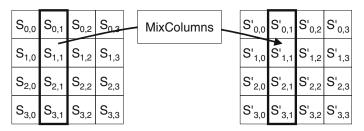

|    |        | 10.2.2                    | Round Operations                                   | . 237 |  |  |

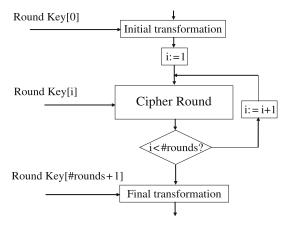

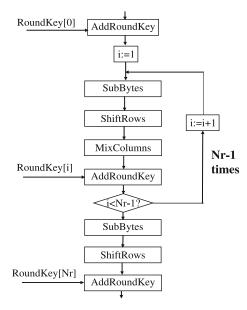

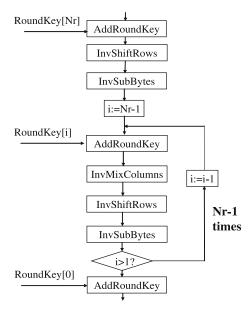

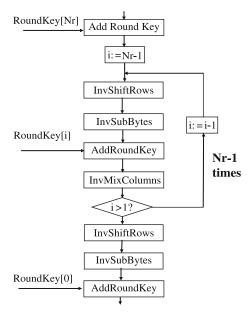

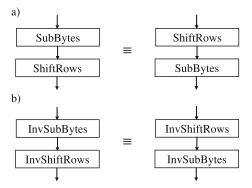

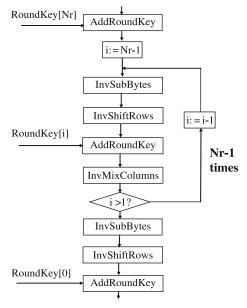

|    |        | 10.2.3                    | Iterative Structure                                | . 242 |  |  |

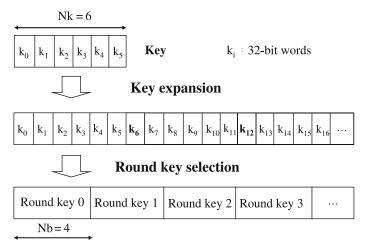

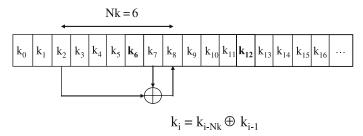

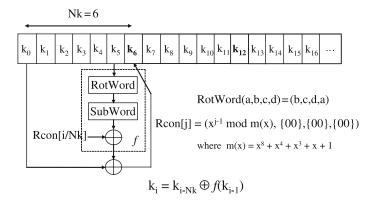

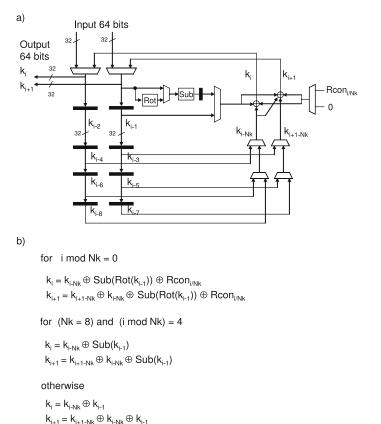

|    |        | 10.2.4                    | Key Scheduling                                     | . 243 |  |  |

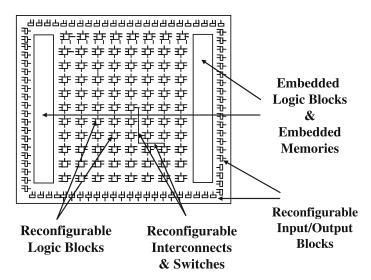

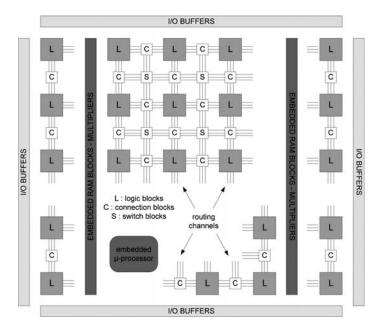

|    | 10.3   | FPGA a                    | and ASIC Technologies                              | . 247 |  |  |

|    | 10.4   | Parame                    | ters of Hardware Implementations                   | . 250 |  |  |

|    |        | 10.4.1                    | Throughput and Latency                             | . 250 |  |  |

|    |        | 10.4.2                    | Area                                               | . 250 |  |  |

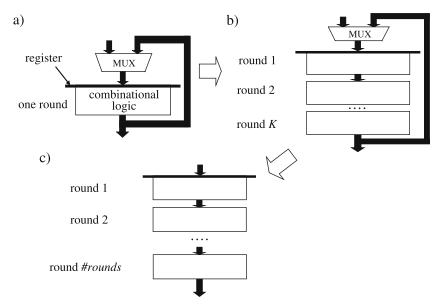

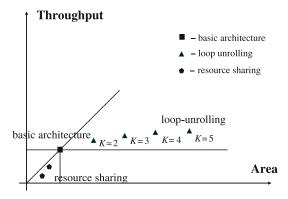

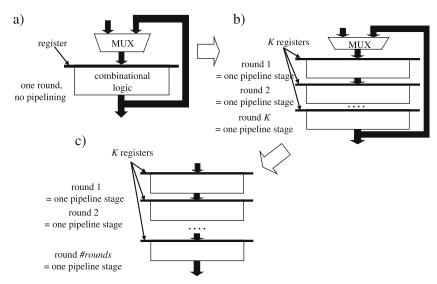

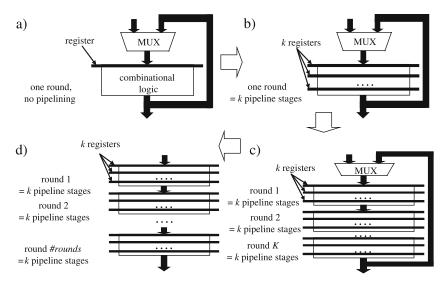

|    | 10.5   | Hardwa                    | are Architectures of Symmetric Block Ciphers       | . 251 |  |  |

|    |        | 10.5.1                    | Hardware Architectures vs. Block Cipher Modes      |       |  |  |

|    |        |                           | of Operation                                       | . 251 |  |  |

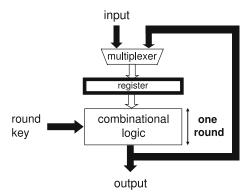

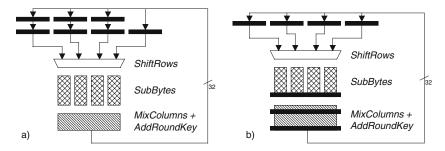

|    |        | 10.5.2                    | Basic Iterative Architecture                       | . 252 |  |  |

|    |        | 10.5.3                    | Loop Unrolling                                     | . 253 |  |  |

|    |        | 10.5.4                    | Pipelining                                         |       |  |  |

|    |        | 10.5.5                    | Limits on the Maximum Clock Frequency of Pipelined |       |  |  |

|    |        |                           | Architectures                                      | . 258 |  |  |

|    |        | 10.5.6                    | Compact Architectures with Resource Sharing        | . 260 |  |  |

|    | 10.6   | Implem                    | nentation of Basic Operations of AES in Hardware   |       |  |  |

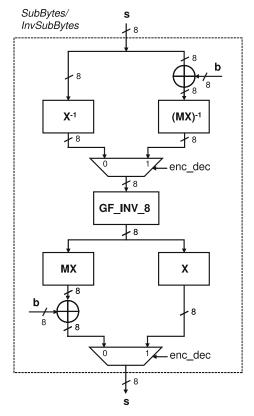

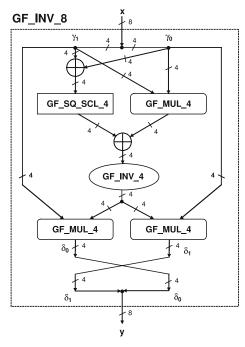

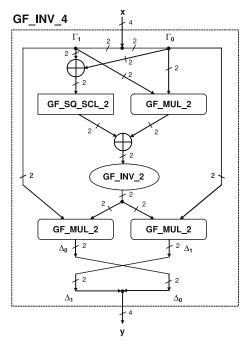

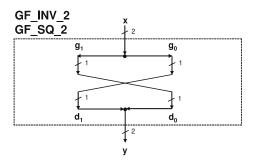

|    |        | 10.6.1                    | SubBytes and InvSubBytes                           |       |  |  |

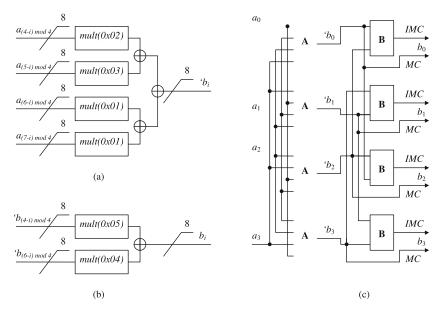

|    |        | 10.6.2                    | MixColumns and InvMixColumns                       |       |  |  |

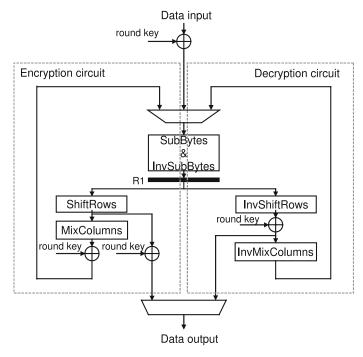

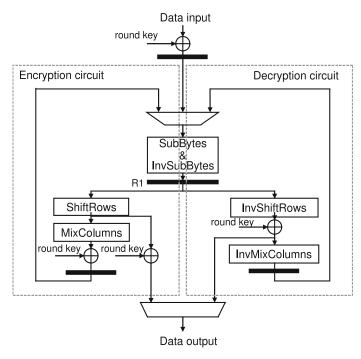

|    | 10.7   | Hardwa                    | are Architectures of a Single Round of AES         |       |  |  |

|    |        | 10.7.1                    |                                                    |       |  |  |

|    |        | 10.7.2                    | T-Box-Based Architecture                           | . 276 |  |  |

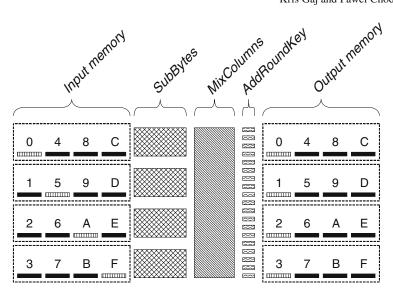

|    |        | 10.7.3                    | Compact Architectures                              | . 282 |  |  |

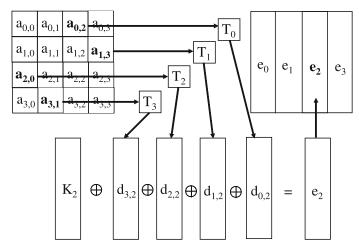

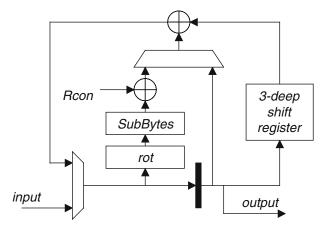

|    | 10.8   | Implem                    | entation of Key Scheduling                         |       |  |  |

|    | 10.9   |                           | m Choice of a Hardware Architecture for AES        |       |  |  |

|    | 10.10  |                           | es                                                 |       |  |  |

|    |        |                           | S                                                  |       |  |  |

|    |        |                           |                                                    |       |  |  |

|    |        |                           |                                                    |       |  |  |

|    |        |                           |                                                    |       |  |  |

| 11 |        |                           | fficient Implementation of Symmetric Encryption    |       |  |  |

|    |        | ,                         | g FPGAs                                            | . 295 |  |  |

|    | Franço | François-Xavier Standaert |                                                    |       |  |  |

|    | 11.1   |                           | ction                                              |       |  |  |

|    | 11.2   |                           | t FPGA Implementations                             |       |  |  |

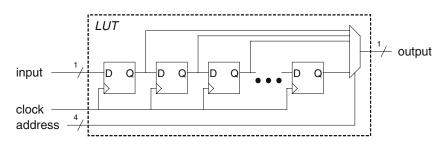

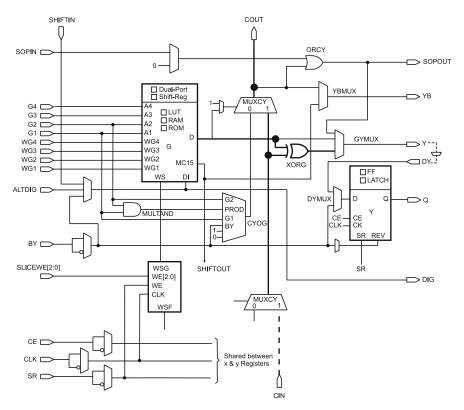

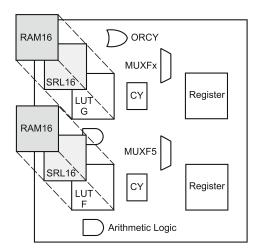

|    |        | 11.2.1                    | Exploiting the Slice Structure                     |       |  |  |

|    |        | 11.2.2                    | Exploiting Embedded Blocks                         |       |  |  |

|    |        | 11.2.3                    | Exploiting Further Features                        | . 302 |  |  |

|    |        | 11.2.4                    | Combining the Tricks: The Flexibility Versus       |       |  |  |

|    |        |                           | Efficiency Tradeoff                                |       |  |  |

|    | 11.3   | Fair Ev                   | aluation of a Cryptographic FPGA Design            | . 303 |  |  |

xiv Contents

|    |       | 11.3.1   | Design Goals                                      | 304 |

|----|-------|----------|---------------------------------------------------|-----|

|    |       | 11.3.2   | Performance Evaluation                            | 304 |

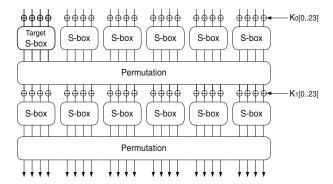

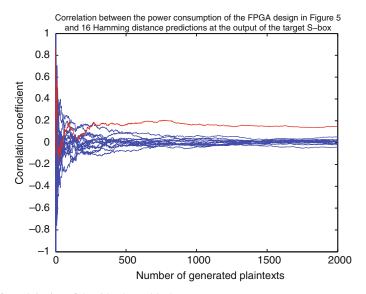

|    | 11.4  | Security | y of FPGAs Against Side-Channel Attacks           | 305 |

|    |       | 11.4.1   | Applicability of the Attack and FPGA Properties   |     |

|    |       | 11.4.2   | Countermeasures                                   |     |

|    |       | 11.4.3   | Measuring Side-Channel Resistance                 | 311 |

|    | 11.5  | Other S  | ecurity Issues                                    | 312 |

|    |       | 11.5.1   | Fault Attacks                                     | 312 |

|    |       | 11.5.2   | Bitstream Security                                | 312 |

|    | 11.6  | Conclus  | sions and Open Questions                          | 315 |

|    | 11.7  | Exercise | es                                                | 315 |

|    | 11.8  | Projects | 3                                                 | 317 |

|    | Refer | ences    |                                                   | 318 |

| 12 | Dlask | Cimbon   | Modes of Onesetion from a Handware                |     |

| 12 |       | _        | Modes of Operation from a Hardware on Perspective | 221 |

|    |       |          | aborty and Francisco Rodríguez-Henríquez          | 321 |

|    | 12.1  |          | ction                                             | 321 |

|    | 12.1  |          | Ciphers                                           |     |

|    | 12.3  |          | ction to AES                                      |     |

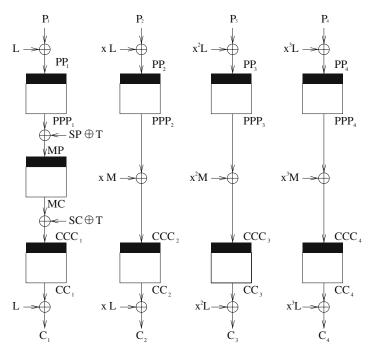

|    | 12.3  | 12.3.1   | Byte Substitution (BS) Step                       |     |

|    |       | 12.3.1   | Shift Rows (SR) Step                              |     |

|    |       | 12.3.3   | Mix Columns (MC) Step                             |     |

|    |       | 12.3.4   | Add Round Key (ARK) Step                          |     |

|    |       | 12.3.5   | Key Scheduling Algorithm                          |     |

|    | 12.4  |          | ground in Binary Extension Finite Fields          |     |

|    | 12    | 12.4.1   | Rings                                             |     |

|    |       | 12.4.2   | Fields                                            |     |

|    |       | 12.4.3   | Finite Fields                                     |     |

|    |       | 12.4.4   | Binary Finite Field Arithmetic                    |     |

|    | 12.5  |          | onal Modes of Operations                          |     |

|    |       | 12.5.1   | Electronic Code Book Mode                         |     |

|    |       | 12.5.2   | Cipher Block Chaining Mode                        | 333 |

|    |       | 12.5.3   | Cipher Feedback Mode                              |     |

|    |       | 12.5.4   | Output Feedback Mode                              | 334 |

|    |       | 12.5.5   | Counter Mode                                      | 335 |

|    | 12.6  | Security | y Requirements for Modes of Operations            | 336 |

|    |       | 12.6.1   | The Adversary                                     | 336 |

|    |       | 12.6.2   | Privacy Only Modes                                | 337 |

|    |       | 12.6.3   | Authenticated Encryption                          | 338 |

|    |       | 12.6.4   | Disk Encryption Schemes                           |     |

|    |       | 12.6.5   | Security Proofs                                   | 341 |

|    | 12.7  | Some M   | Modern Modes                                      | 341 |

|    |       | 12.7.1   | The Offset Codebook Mode                          |     |

|    |       | 12.7.2   | ECB-Mask-ECB Mode                                 | 344 |

Contents xv

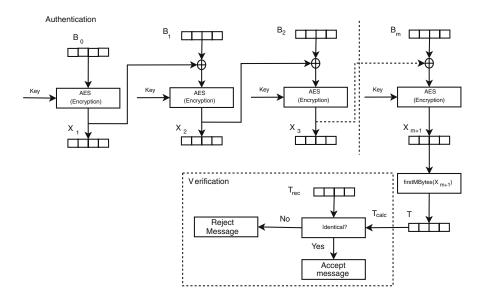

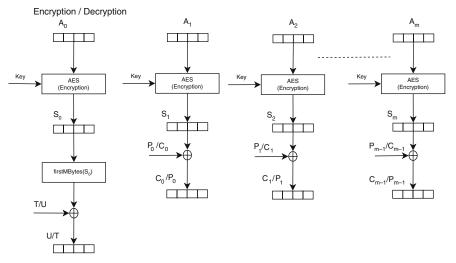

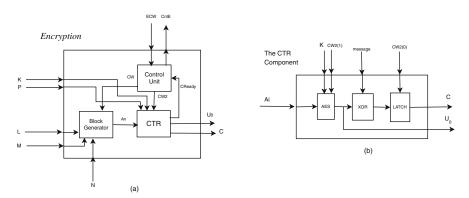

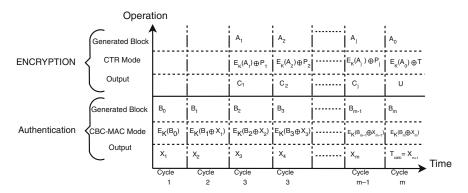

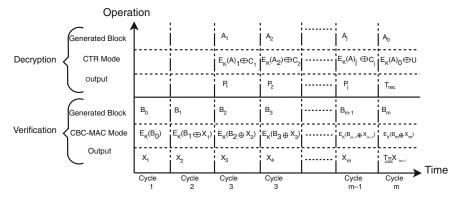

|    | 12.8      | The CCM Mode: A Case Study                           | 347     |

|----|-----------|------------------------------------------------------|---------|

|    |           | 12.8.1 The CCM Mode                                  |         |

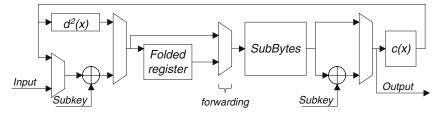

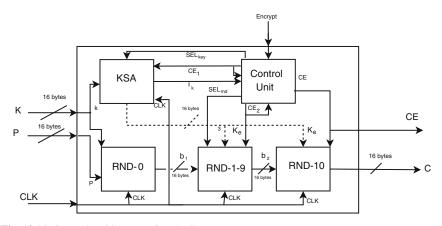

|    |           | 12.8.2 AES Encryptor Core Implementation             | 350     |

|    |           | 12.8.3 Hardware Implementation of the CCM Mode       | 353     |

|    |           | 12.8.4 Experimental Results and Comparison           | 357     |

|    | 12.9      | Conclusions                                          |         |

|    | 12.10     | Exercises                                            |         |

|    | 12.11     | Projects                                             | 359     |

|    |           | ences                                                |         |

| 13 | Basic     | s of Side-Channel Analysis                           | 365     |

|    | Marc      |                                                      |         |

|    | 13.1      | Introduction                                         | 365     |

|    | 13.2      | Timing Analysis                                      |         |

|    |           | 13.2.1 Attack on a Password Verification             | 366     |

|    |           | 13.2.2 Attack on an RSA Signature Scheme             | 367     |

|    | 13.3      | Simple Power Analysis                                | 368     |

|    |           | 13.3.1 Reverse-Engineering of an Algorithm           |         |

|    |           | 13.3.2 Attack on a Private RSA Exponentiation        |         |

|    |           | 13.3.3 Attack on a DES Key Schedule                  |         |

|    | 13.4      | Differential Power Analysis                          |         |

|    |           | 13.4.1 Bit Tracing                                   |         |

|    |           | 13.4.2 Attack on an AES Implementation               |         |

|    |           | 13.4.3 Attack on an RSA Signature Scheme (2)         |         |

|    | 13.5      | Countermeasures                                      |         |

|    | 13.6      | Exercises                                            |         |

|    | 13.7      | Projects                                             |         |

|    |           | ences                                                |         |

| 14 | Imnr      | oved Techniques for Side-Channel Analysis            | 381     |

| 17 | _         | ij Rohatgi                                           |         |

|    | 14.1      | Introduction                                         | 381     |

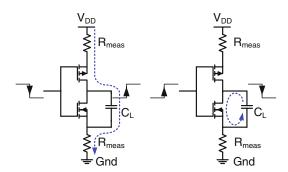

|    | 14.2      | CMOS Devices: Side-Channel Leakage Perspective       |         |

|    | - · · · - | 14.2.1 Intentional Current Flows                     |         |

|    |           | 14.2.2 Leakage Current Flows                         |         |

|    |           | 14.2.3 Information Leakage in Power and EM Side-Chan |         |

|    | 14.3      | Characterizing Side-Channel Leakage Using Maximum    | neis505 |

|    | 17.5      | Likelihood                                           | 385     |

|    |           | 14.3.1 Adversarial Model                             | 295     |

|    |           | 14.3.2 Maximum Likelihood and Best Attack Strategy   |         |

|    |           |                                                      |         |

|    | 111       | 14.3.3 Gaussian Assumption                           |         |

|    | 14.4      | Template Attacks                                     |         |

|    |           | 14.4.1 Classical Template Attacks: The Case of RC4   |         |

|    | 145       | 14.4.2 Single-Bit Templates and Applications         |         |

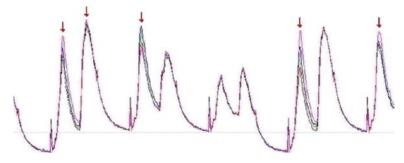

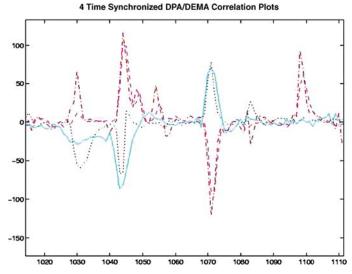

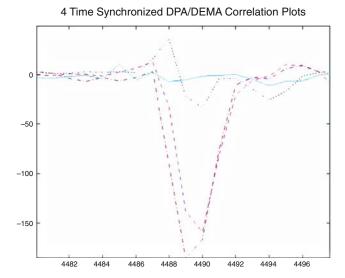

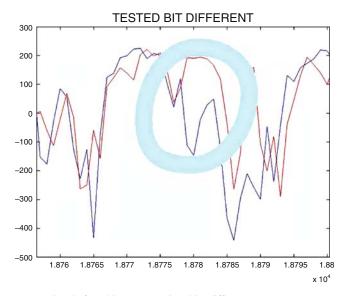

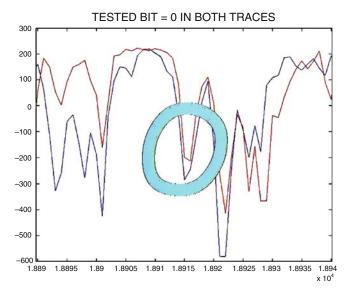

|    | 14.5      | Improved DPA/DEMA Metric                             |         |

|    |           | 14.5.1 Improving DPA                                 | 395     |

xvi Contents

|    | 14.6   | Multi-Channel Attacks                                 | 397 |

|----|--------|-------------------------------------------------------|-----|

|    |        | 14.6.1 Multiple Channel Selection                     | 397 |

|    |        | 14.6.2 Multi-Channel Template Attacks                 |     |

|    |        | 14.6.3 Multi-Channel DPA                              |     |

|    | 14.7   | Toward Information Leakage Assessment                 | 401 |

|    |        | 14.7.1 Practical Considerations                       | 402 |

|    | 14.8   | Projects                                              | 403 |

|    | Refere | ences                                                 | 405 |

| 15 | Electi | romagnetic Attacks and Countermeasures                | 407 |

|    | Panka  | j Rohatgi                                             |     |

|    | 15.1   | Introduction and History                              |     |

|    | 15.2   | EM Emanations Background                              |     |

|    |        | 15.2.1 Types of EM Emanations                         |     |

|    |        | 15.2.2 EM Propagation                                 |     |

|    | 15.3   | EM Capturing Equipment                                |     |

|    | 15.4   | EM Leakage Examples                                   |     |

|    |        | 15.4.1 Examples: Amplitude Modulation                 |     |

|    |        | 15.4.2 Examples: Angle Modulation                     | 422 |

|    | 15.5   | Multiplicity of EM Channels and Comparison with Power |     |

|    |        | Channel                                               |     |

|    | 15.6   | Using EM to Bypass Power Analysis Countermeasures     |     |

|    | 15.7   | Quantifying EM Exposure                               |     |

|    | 15.8   | Countermeasures                                       |     |

|    | 15.9   | Projects                                              |     |

|    | Refere | ences                                                 | 430 |

| 16 |        | age from Montgomery Multiplication                    | 431 |

|    |        | D. Walter                                             |     |

|    | 16.1   | Introduction                                          |     |

|    | 16.2   | Montgomery Reduction                                  |     |

|    | 16.3   | Montgomery Modular Multiplication                     |     |

|    | 16.4   | Exponentiation                                        |     |

|    | 16.5   | Space and Time Comparisons                            |     |

|    | 16.6   | Side Channel Analysis                                 |     |

|    | 16.7   | Frequencies of Conditional Subtractions               |     |

|    | 16.8   | Variance in Frequencies and SCA Errors                |     |

|    | 16.9   | A Surprising Improvement                              |     |

|    |        | Conclusions                                           |     |

|    |        | Exercises                                             |     |

|    |        | Projects                                              |     |

|    | Refere | ences                                                 | 448 |

| 17 |        | omized Exponentiation Algorithms                      | 451 |

|    |        | D. Walter                                             |     |

|    | 17.1   | Introduction                                          | 451 |

Contents xvii

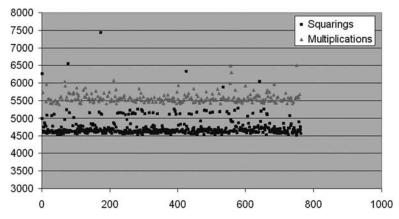

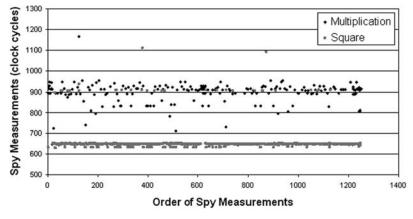

|     | 17.2    | The Big Mac Attack                                           | 452 |

|-----|---------|--------------------------------------------------------------|-----|

|     | 17.3    | Digit Representation and Exponentiation Algorithms           | 454 |

|     | 17.4    | Liardet-Smart                                                | 457 |

|     |         | 17.4.1 Attacking the Algorithm                               | 459 |

|     | 17.5    | Oswald–Aigner Exponentiation                                 | 460 |

|     |         | 17.5.1 Attacking the Algorithm                               | 461 |

|     | 17.6    | Ha–Moon                                                      | 462 |

|     |         | 17.6.1 Attacking the Algorithm                               | 463 |

|     | 17.7    | Itoh's Overlapping Windows                                   | 464 |

|     |         | 17.7.1 Attacking the Algorithm                               | 465 |

|     | 17.8    | Randomized Table Method                                      | 466 |

|     |         | 17.8.1 Attacking the Algorithm                               | 466 |

|     | 17.9    | The MIST Algorithm                                           | 467 |

|     |         | 17.9.1 Attacking the Algorithm                               | 468 |

|     | 17.10   | Conclusions                                                  |     |

|     | 17.11   | Exercises                                                    | 469 |

|     | 17.12   | Projects                                                     | 470 |

|     | Refere  | ences                                                        | 472 |

|     |         |                                                              |     |

| 18  |         | architectural Attacks and Countermeasures                    | 475 |

|     |         | Acıiçmez and Çetin Kaya Koç                                  |     |

|     | 18.1    | Introduction                                                 |     |

|     | 18.2    | Overview and Brief History                                   |     |

|     | 18.3    | Cache Analysis                                               |     |

|     |         | 18.3.1 Basics of Cache                                       |     |

|     |         | 18.3.2 Overview of Cache Attacks                             |     |

|     |         | 18.3.3 A Brief Survey on Cache Analysis                      |     |

|     |         | 18.3.4 Time-Driven and Trace-Driven Attacks                  |     |

|     |         | 18.3.5 Exploiting Internal Collisions in Time-Driven Attacks |     |

|     |         | 18.3.6 Access-Driven Attacks                                 |     |

|     |         | 18.3.7 Percival's Hyper-Threading Attack on RSA              |     |

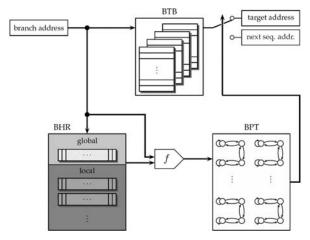

|     | 18.4    | Branch Prediction Analysis                                   |     |

|     |         | 18.4.1 The Concept of Branch Prediction                      |     |

|     |         | 18.4.2 Simple Branch Prediction Analysis                     | 492 |

|     | 18.5    | I-cache Analysis                                             | 494 |

|     | 18.6    | Exploiting Shared Functional Units                           | 496 |

|     | 18.7    | Comparing Microarchitectural Analysis Types                  | 497 |

|     | 18.8    | Countermeasures for Microarchitectural Analysis              | 498 |

|     | 18.9    | Exercises                                                    |     |

|     | 18.10   | Projects                                                     | 500 |

|     | Refere  | ences                                                        | 501 |

|     |         |                                                              |     |

| Aut | hors' B | Giographies                                                  | 505 |

| Ind | ex      |                                                              | 513 |

# **Acronyms**

2DEM 2D-Encryption Mode

ABC Accumulated Block Chaining

ABL Arbitrary Block Length

ACM Association for Computing Machinery

AES Advanced Encryption Standard

AE Authenticated Encryption

AEAD Authenticated Encryption with Associated Data

AIS Anwendungshinweise und Interpretationen zum Schema AIS Application Notes and Interpretation of the Scheme

ALU Arithmetic Logic Unit

ANSI American National Standards Institute

ARK Add Round Kev

ASIC Application Specific Integrated Circuits

BPA Branch Prediction Analysis

BPU Branch Prediction Unit

BTB Branch Target Buffer

BS Byte Substitution

CASR Cellular Automata Shift Register

CBC Cipher Block Chaining CCM Counter with CBC-MAC

CFB Cipher Feedback

CHES Cryptographic Hardware and Embedded Systems

CISC Complex Instruction Set Computer

CLB Configurable Logic Block

CMAC Cipher Based MAC CMC CBC Mask CBC

CMOS Complementary Metal-Oxide Semiconductor

CPLD Complex Programmable Logic Device

CPU Central Processing Unit CRT Chinese Remainder Theorem

CS Cipher State

Acronyms xx

**CTR** Counter Mode

**CWC** Carter Wegman with Counter

das digitized analog signal DE

Disk Encryption

**DEA** Data Encryption Algorithm

Differential Electromagnetic Analysis DEMA

DES **Data Encryption Standard** DFT Discrete Fourier Transform **DPA** Differential Power Analysis Digital Rights Management DRM

DRNG Deterministic Random Number Generator

**DSA** Digital Signature Algorithm DLP Discrete Logarithmic Problem DSS Digital Signature Standard

**EAX** Conventional Authenticated-Encryption Mode

**ECB** Electronic Code Book

Elliptic Curve Cryptography **ECC**

**ECDSA** Elliptic Curve Digital Signature Algorithm

ECB Mix ECB **EME**

**FEAL** Fast Data Encipherment Algorithm **FFSEM** Feistel Finite Set Encryption Mode

**FFT** Fast Fourier Transform

**FIGARO** Fibonacci Galois Ring Oscillator

Federal Information Processing Standard FIPS

FIPS PUB Federal Information Processing Standard Publication

**FPGA** Field Programmable Gate Array **FPLD** Field Programmable Logic Device

gcd Greatest Common Divisor **GCM** Galois Counter Mode

GF Galois Field

**HCH** Hash Encrypt Hash **HCTR** Hash Counter Hash

**HECC** Hyperelliptic Curve Cryptography

**HEH** Hash ECB Hash

**IACBC** Integrity Aware Cipher Block Chaining Integrity Aware Parallelizable Mode **IAPM**

Institute of Electrical and Electronics Engineers **IEEE**

International Data Encryption Algorithm **IDEA**

**IDFT** Inverse Discrete Fourier Transform

**IGE** Infinite Garble Extension

iid independent and identically distributed Institute of Mathematics and its Applications IMA

ISA Instruction Set Architecture Instruction Set Extension **ISE KFB** Key Feedback Mode

Acronyms xxi

LFSR Linear Feedback Shift Register

LNCS Lecture Notes in Computer Science

LRU Least Recently Used LRW Liskov Rivest Wagner LT LaGrande Technology

LUT Lookup Table

MA Microarchitectural Analysis

MAC Message Authentication Code

MC Mixed Columns

MD Message Digest

MDC Manipulation Detection Code

MMX Multimedia Extension

MSMP Modified Spectral Modular Product

MULGF Multiply in Galois Field

MULGF2 Multiply in Galois Field Base 2

NACSIM National Communications Security Information Memorandum NACSEM National Communications Security Emanation Memorandum

NTT Number Theoretical Transform

NIST National Institute of Standards and Technology NPTRNG Non-Physical Random Number Generator

NSA National Security Agency

NSTISSI National Training Standard for Information Systems Security

OCB Offset Code Book

OEF Optimal Extension Fields

OFB Output Feedback

OMAC One-Key CBC

ONB Optimal Normal Basis

OS Operating System

PC Personal Computer

PCFB Propagating Cipher Feedback

PEP Polynomial Hash Encrypt Polynomial Hash

PKC Public Key Cryptography

PKCS Public Key Cryptography Standards

PL Phase Locked Loop

PMAC Parallelizable Message Authentication Code

PNT Pseudo Number Transform

PRNG Physical Random Number Generator PTRNG Physical True Random Number Generator

PUF Physically Unclonable Functions

RAM Random Access Memory

RAMB Block RAM

RFID Radio Frequency Identification Device

RIPEMD RACE Integrity Primitives Evaluation Message Digest

RISC Reduced Instruction Set Computer

RMAC Randomized MAC

xxii Acronyms

RNG Random Number Generator RSA Rivest Shamir Adleman RSD Redundant Signed Digit

SBPA Simple Branch Prediction Analysis

SCA Side Channel Analysis

SEMA Simple Electromagnetic Analysis

SFU Shared Functional Units SHA Secure Hash Algorithm

SIAM Society for Industrial and Applied Mathematics

SIMD Single Instruction Multiple Data

SIV Synthetic IV

SME Spectral Modular Exponentiation

SMM Spectral Modular Multiplication

SMP Spectral Modular Product

SMT Simultaneous Multithreading

SPA Simple Power Analysis

SPRP Strong Pseudo Random Permutation

SR Shift Rows

TDEA Triple Data Encryption Algorithm

TEMPEST Transient Electromagnetic Pulse Emanation Standard

TET Hash ECB Hash

TMAC Two-Key CBC MAC

TRNG True Random Number Generator

TXT Trusted Execution Technology

VCO Voltage Controlled Oscillator

VHDL Very High Level Hardware Description Language

VLIW Very Long Instruction Word VT Virtualization Technology

WAIFI Workshop on the Arithmetic of Finite Fields

XCB Extended Code Book

XCBC Extended Cipher Block Chaining XECB Extended Electronic Code Book

# Chapter 1 About Cryptographic Engineering

Çetin Kaya Koç

#### 1.1 Introduction

Cryptographic engineering is the name we have coined to refer to the theory and practice of engineering of cryptographic systems, i.e., encryption and decryption engines, digital signature and authentication hardware and software systems, key generation, distribution, and management systems, and random number generators. A cryptographic engineer designs, implements, tests, and validates cryptographic systems. She is also interested in cryptanalyzing them for the purpose of checking their robustness and their strength against attacks, and also building countermeasures in them in order to thwart such attacks by reducing their probability of success.

This is a subject barely taught in our undergraduate and graduate schools. Most courses in cryptography deal with theory, generally introducing mathematically expressed algorithms without showing (or knowing) how they are realized in actual software or hardware. As expected, the devil is in the details: The fastest and most practical implementation of the RSA algorithm requires the implementation of Montgomery multiplication. However, the last step in this algorithm (the so-called final subtraction) yields information which allows an attacker capable of observing, recording, and analyzing the timings of the process to learn some of the private bits. One cannot deduce this information by looking at a mathematical description of the RSA algorithm found in a textbook.

Cryptographic engineering material is scattered among many journal and conference papers, and the practitioners are too busy to write books. A group of us got together in Lausanne, Switzerland, in 2002, and began to teach short courses to engineers and researchers from industry and academia. The idea of putting our course notes into a book was born there and then.

City University of Istanbul & University of California Santa Barbara e-mail: koc@cryptocode.net

2 Çetin Kaya Koç

Cryptographic engineering is a fast-moving field. Every year in conferences such as the CHES (Cryptographic Hardware and Embedded Systems) Workshop, new innovative hardware and software realizations of cryptographic algorithms are introduced or new attacks to cryptanalyze these actual hardware and systems are proposed. This explains the unwillingness of researchers in cryptographic engineering to write books; we are more interested in designing new cryptographic systems or breaking the systems designed by our colleagues!

However, people who are new to this exciting field need good introductions. Engineers from industry and students from our colleges and graduate schools can use this book as a first step to cryptographic engineering.

## 1.2 Chapter Contents

This book has 18 chapters. It can be divided into 4 parts; however, the sections are intimately interconnected and there is a logical construction of the sections starting from the first chapter. There are also chapters which can belong to more than one part, as one might expect.

Chapters 2, 3, and 4 constitute the *first part* of the book. These chapters investigate and uncover the roles of random numbers in cryptography, and propose evaluation methods and practical designs for random number generators. Random numbers are used in other sciences; for example, the so-called Monte Carlo methods use random numbers to simulate physical or mathematical systems. In cryptography, random numbers provide the uncertainty and unpredictability upon which we build the secrecy of our cryptographic keys. For us, their most important property is requirement R2 (see, Chapter 2) which says that the full knowledge of a current bit does not help us to guess its past or future companions better than 50% chance. Chapter 2 examines the general definitions, requirements, and classifications of random numbers while Chapter 3 proposes an evaluation criteria for true random number generators (TRNGs). The ideas behind Chapter 3 produced the world's first evaluation methodology for TRNGs, called AIS.

Chapter 4, on the other hand, proposes a few practical TRNG designs suitable for implementation using ASIC and reconfigurable logic blocks. There is no doubt that, as we improve our understanding of the evaluation of TRNGs, more practical (low power, small circuit area, etc.) TRNG designs will be produced. I believe we are just entering this exciting field of TRNG designs, which requires collaboration by analog and digital circuit designers and cryptographers.

The *second part* of the book (Chapters 5–9) concentrates on implementation (i.e., hardware and software realizations) of public-key cryptographic systems, such as RSA, Diffie-Hellman, and elliptic curve cryptography, and their underlying arithmetic which includes large-integer arithmetic, arithmetic in prime fields and binary extension fields. Chapter 5 gives a general introduction to finite field arithmetic and describes the basic algorithms. Chapter 6 introduces the so-called unified arithmetic (which is also called dual-field arithmetic). The unified arithmetic allows one to

design a single hardware unit with negligible additional cost that performs arithmetic in both GF(p) and  $GF(2^k)$ .

Chapter 7 introduces a new and compelling research area: the use of discrete Fourier transforms over finite rings in order to design parallel functional units for modular arithmetic. While the use of Fourier transforms to perform fast multiplication is well known, this chapter proposes the first spectral algorithm for modular multiplication.

Chapter 8 provides a high-level, mathematical view of elliptic and hyperelliptic curve arithmetic; it is also a good introduction to vulnerabilities of and attacks on elliptic and hyperelliptic curve cryptography. Finally, Chapter 9 provides a detailed account of instruction set architectures for cryptography, for both secret-key and public-key cryptographic algorithms. Chapter 8 provides a smooth transition from public-key cryptography to secret-key cryptography, a topic which we deal with in the subsequent part of the book.

The *third part* of the book studies implementation aspects of secret-key cryptographic algorithms, which are in Chapters 10, 11, and 12. The emphasis of these chapters is that they concentrate on hardware realizations of secret-key ciphers and their simple (ECB, CBS) and advanced (CCM) modes of operations. Chapter 10 covers both ASIC and FPGA realizations, while Chapter 11 particularly deals with FPGA implementations, exploiting logic structures more efficiently. Chapter 12, on the other hand, is a good summary on modes of operation, with special concentration on modern modes. The most important mode seems to be the CCM mode, which is an authenticated encryption mode used particulary in wireless communication protocols.

The final and *fourth part* of the book is the longest part (Chapters 13–18), and deals with the important topics of side-channel cryptanalysis and countermeasures against such attacks. Chapter 13 gives a brief introduction to the side-channel analysis. It covers the basic principles of side-channel cryptanalysis and introduces simple countermeasures to prevent side-channel leakage.

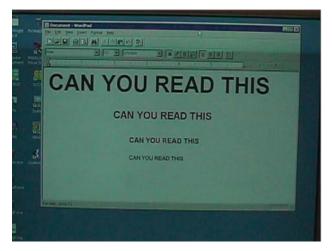

Chapter 14 delves into more advanced topics and shows how only a fraction of the information obtained from a side-channel can be used to cryptanalyze a practical system. Chapter 15 explains a particular type of side-channel: electromagnetic emanations from physical systems can be collected and analyzed by an attacker in order to capture messages not intended for others to see.

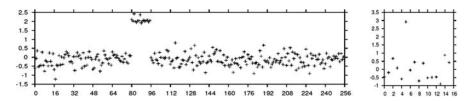

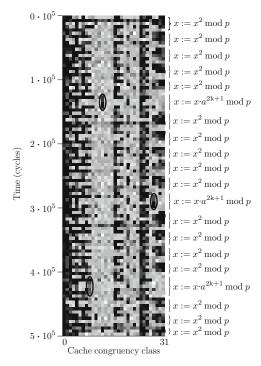

Chapters 16 and 17 show how algorithmic properties can be modeled and utilized to guess the bits of private keys. Chapter 16 focuses on how Montgomery multiplication leaks information, while Chapter 17 introduces methods to make the job of the attacker infeasible by using randomized exponentiations.

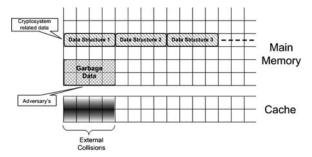

Finally, Chapter 18 introduces microarchitectural side-channel attacks, which allow an attacker to obtain information about cryptographic key bits from a cryptoprocess running on a client or server computer, by sneaking an unprivileged spy process into the same processor. These attacks slightly differ from the classic side-channel attacks, and are shown to be quite effective. It is very likely that future processors will have to be designed with hardware countermeasures against these microarchitectural side-channel attacks.

4 Çetin Kaya Koç

## 1.3 Exercises and Projects

Whenever appropriate, a chapter ends with two sections for the purpose of checking the reader's understanding of the chapter's technical material and leading her into research by describing a few doable projects. If the book is used in a graduate-level course, the *exercises* can be given as homework assignments. On the other hand, the *projects* are suitable for small groups (1 or 2 individuals) to implement.

**Acknowledgements** I would like to express my gratitude to all authors of the chapters in the book. Without their dedication, this book would not have come into existence.

I would also like to thank the staff of Springer US, particularly, Jason Ward, Caitlin Womersley, and Katelyn Stanne for helping me through the steps to completing the book, and also being patient with me and my co-authors, as we struggled to create time for this book from our other duties.

I thank my dear friends Vlado Valence and Caroline Huber of Mead Education, the co-organizers of the EPFL lectures in cryptographic engineering. Above all, I am indebted to Gabor Temes, who encouraged us to organize these lectures in the first place.

I thank my former and current students for contributing to this book by coauthoring chapters, reading and correcting portions of the material, and being lifelong collaborators. I would like to thank particularly Gökay Saldamlı, Serdar Erdem, Tuĝrul Yanık, Erkay Savaş, and Sultan Selçuk for helping in the creation and correction of the manuscript.

Finally, I thank my family for their constant patience and love.

Copyrights and Permissions A great many of figures and tables, and much of the other material found in this book are from the proceedings of the following conferences and workshops: Cryptographic Hardware and Embedded Systems, Cryptography and Coding, Computational Science and Its Applications, Field-Programmable Logic and Applications, Information Security and Cryptology, Information and Communications Security, CT-RSA, ASIACRYPT, and INDOCRYPT.

The above conference proceedings are published by Springer in the Lecture Notes of Computer Science series. This material is printed in this book with the kind permission of Springer Science+Business Media.

# Chapter 2 Random Number Generators for Cryptographic Applications

Werner Schindler

#### 2.1 Introduction

A large number of cryptographic applications require random numbers, e.g., as session keys, signature parameters, ephemeral keys (DSA, ECDSA), challenges or in zero-knowledge protocols. For this reason, random number generators (RNGs) are part of many IT-security products. Inappropriate RNGs may totally weaken IT systems that are principally strong, e.g., if an adversary is able to determine session keys.

It is intuitively clear that random numbers should remain unpredictable, even if an adversary knows a large number of other random numbers (predecessors or successors of the random numbers of interest) that have been generated with the same RNG, e.g., from openly transmitted challenges or session keys from messages that the adversary has received legitimately. Ideally, random numbers should be uniformly distributed on their range and independent. However, this characterizes an *ideal RNG*, which is a mathematical construction.

In Section 2.2 we formulate the general requirements RNGs should have, and in Section 2.3 we divide the entity of 'real-world' RNGs into several classes. The main classes are deterministic RNGs and true RNGs, the latter falling into two subclasses (physical and non-physical true RNGs).

The designer of an RNG is faced with two challenges. First he has to develop an appropriate design and implement it suitably. Especially for true RNGs the second task is usually even more difficult, namely to prove or at least to give strong evidence that the chosen design and the concrete implementation are indeed secure.

The main part of this chapter is devoted to deterministic RNGs (Section 2.4). The basic aspects of true RNGs are addressed in Sections 2.5 and 2.6. Evaluation criteria for physical RNGs are treated intensively in the following chapter. Section 2.7

Bundesamt für Sicherheit in der Informationstechnik e-mail: Werner.Schindler@bsi.bund.de

6 Werner Schindler

addresses important standards and evaluation guidances for RNGs. Sections 2.8 and 2.9 contain exercises and possible implementation projects.

### 2.2 General Requirements

Many cryptographic applications require random numbers. The protocol usually only demands 'generate a 64-bit challenge', 'generate a random prime', 'generate a random session key' etc., but does not specify any requirements these random values should have. Intuitively, the matter seems to be clear: Random numbers should assume all possible values with equal probability and should be independent from predecessors and successors. However, these (usually unspoken) requirements are very restrictive and characterize an ideal RNG. Note that even if a real-world RNG was ideal it is hardly possible to give evidence in a strict sense (cf. the next chapter).

A closer look at typical applications allows a positive formulation of necessary requirements. Absolutely inevitable is

• (R1) The random numbers should have good statistical properties.

Requirement (R1) is usually checked with a particular statistical test suite, ideally adjusted to the concrete RNG. For specific applications, as for many challenge–response protocols or openly transmitted IVs for block ciphers in CBC mode, (R1) should be fully sufficient. In particular, (R1) shall exclude replay attacks or correlation based attacks.

Unfortunately, (R1) is insufficient for sensitive applications. In Section 2.4.3 we will treat RNGs that have good statistical properties but allow an adversary to predict the whole sequence of random numbers from a small, known subsequence. The assumption that an adversary knows some random numbers is realistic for many applications. Consider, for instance, the generation of session keys if the same RNG is also used for challenges that are transmitted openly. Another example is a classical hybrid protocol where Alice encrypts a confidential message with a randomly selected session key  $k_{rnd}$  and sends  $k_{rnd}$  to the legitimate receiver, using a suitable key exchange protocol. Of course, the legitimate receiver of particular messages shall not be able to decrypt other messages. In this context, a legitimate receiver of a message is principally a privileged attacker since he knows at least one session key. If Alice represents a public server an adversary may learn millions of random numbers. This suggests the next requirement, namely.

(R2) The knowledge of subsequences of random numbers shall not allow one to

practically compute predecessors or successors or to guess these numbers with

non-negligibly larger probability than without knowledge of these subsequences.

In Section 2.4 we will introduce two further requirements that are characteristic for DRNGs.

#### 2.3 Classification

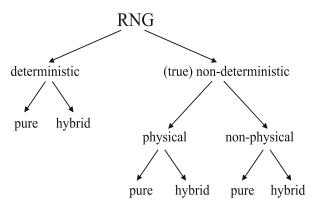

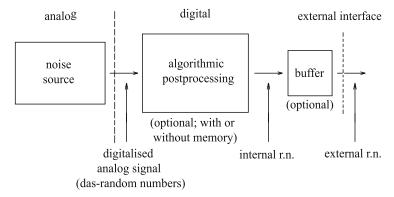

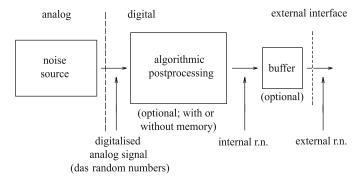

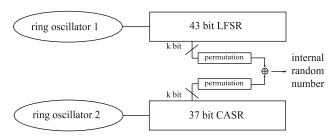

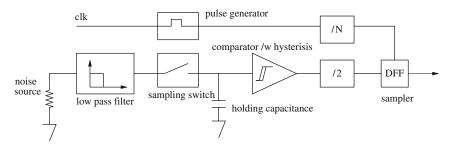

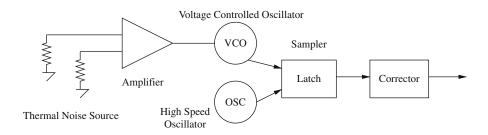

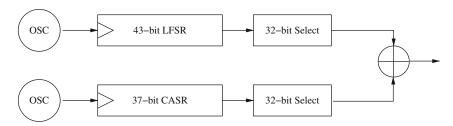

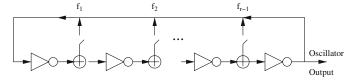

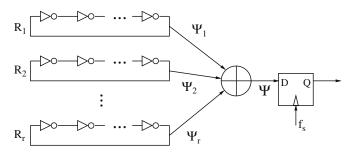

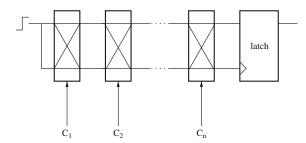

Following [1] (which narrows the focus to random bit generators) 'real-world' RNGs fall into two main classes. The first class consists of the deterministic RNGs (DRNGs, aka pseudorandom number generators). Starting with a seed, DRNGs generate pseudorandom numbers algorithmically. The true RNGs (TRNGs) form the second class, which falls into two subclasses: physical TRNGs (PTRNGs) and non-physical TRNGs (NPTRNGs). Physical TRNGs use non-deterministic effects of electronic circuits (e.g., shot noise from Zener diode, inherent semiconductor thermal noise, free-running oscillators) or physical experiments (e.g., time between emissions of radioactive decay, quantum random processes). NPTRNGs exploit non-deterministic events (e.g., system time, hard disk seek time, RAM content, user interaction). So-called hybrid RNGs have design elements from both DRNGs and TRNGs. Roughly speaking, the security of a DRNG essentially depends on the computational complexity of possible attacks ( $\rightarrow$  practical security), while TRNGs rely on the unpredictability of their output (  $\rightarrow$  theoretical security). We will illuminate this aspect later. Depending on their main 'security anchor' we distinguish between hybrid DRNGs and hybrid TRNGs (Figure 2.1).

Fig. 2.1 RNG classification.

# 2.4 Deterministic Random Number Generators (DRNGs)

In this section we consider deterministic random number generators. The main part of this section deals with pure DRNGs but we also consider hybrid DRNGs. We formulate and justify two additional DRNG-specific requirements (R3) and (R4). We illustrate the general principles by many examples, and we also address stochastic simulations and Monte Carlo integration.

8 Werner Schindler

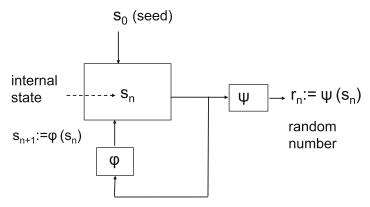

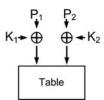

Fig. 2.2 Pure DRNG: Generic design.

#### 2.4.1 Pure DRNGs

This subsection considers the generic design and basic properties of pure DRNGs, and we analyze the security properties of several pure DRNG designs. Figure 2.2 illustrates the generic design of a *pure* DRNG. After n-1 random numbers

$$r_1, r_2, \ldots, r_{n-1} \in R$$

have been generated, the internal state of the DRNG attains the value  $s_n \in S$ . The finite sets S and R are called the *state space* and the *output space* of the DRNG. The *output transition function*  $\psi \colon S \to R$  computes the next random number  $r_n$  from the current internal state  $s_n$ . Then  $s_n$  is updated to  $s_{n+1}$  with the *state transition function*  $\phi$ , i.e.,  $s_{n+1} := \phi(s_n)$ . The first internal state  $s_1$  is derived from the *seed*  $s_0$ , e.g., simply  $s_1 = \phi(s_0)$ , or a more complicated mechanism may be used. Clearly, the seed  $s_0$  determines all internal states  $s_1, s_2, \ldots$  and all random numbers  $r_1, r_2, \ldots$  In order to fulfil requirement (R2) the seed must be selected randomly. A pure DRNG can be described by a 5-tuple

$$(S, R, \phi, \psi, p_S) \tag{2.1}$$

where  $p_S$  defines the probability distribution of the random seed. Note, however, that the seed generation is performed outside the DRNG boundaries. Usually the seed is generated by a TRNG.

A drawback of DRNGs (compared to TRNGs) is that the output is completely determined by the seed, and the future random numbers depend only on the current internal state. Thus the internal state must be protected even if the device is not active. In particular, implementing a pure DRNG on a PC and using its current internal state in the next session may be dangerous. Typically, DRNGs are implemented on smart cards. Of course, pseudorandom numbers cannot be truly random. On the positive side implementing a DRNG is relatively cheap, and unlike for physical RNGs, no dedicated hardware is needed.

We point out that (R2) demands that the seed entropy must be 'large' and that the state transition function and the output function are sufficiently complex. Pure DRNGs can at most provide *practical security* (computational security). In an information theoretical sense already a few random numbers fully determine the seed and all the generated random numbers completely. In this regard the situation is similar to that of cryptographic primitives (e.g., to block ciphers). In fact, DRNGs typically apply cryptographic primitives.

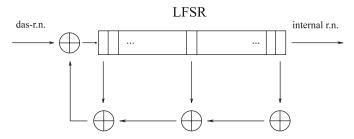

*Example 2.1.* Consider a linear feedback shift register (LFSR) over GF(2) with t cells and recursion formula  $a_{n+t+1} \equiv c_1 a_{n+t} + \dots + c_n a_{n+1} \pmod{2}$  with  $c_1, \dots, c_n \in \{0,1\}$ . In this example,  $S = \{0,1\}^t$ ,  $s_n := (a_n, \dots, a_{n+t-1})$ ,

$$s_{n+1} = \phi(s_n) = (a_{n+1}, \dots, a_{n+t})$$

,

$$R = \{0, 1\}, r_n = \psi(s_n) = a_n.$$

For primitive feedback polynomials the output sequence  $r_1, r_2,...$  is known to have good statistical properties unless t is too small. Hence this DRNG should fulfil (R1). Moreover, LFSRs can be implemented efficiently, and they are very fast. On the other hand, the random numbers  $r_1, r_2,...$  depend GF(2)-linearly on the initial state of the LFSR. If an adversary knows about t output bits he can easily recover  $s_1$  and hence the whole sequence  $r_1, r_2,...$  Consequently, LFSRs do not fulfil requirement (R2), and they are absolutely inappropriate for sensitive cryptographic applications.

Example 2.2. Assume that Enc:  $\{0,1\}^n \times \{0,1\}^m \to \{0,1\}^n$  defines a block cipher where  $\{0,1\}^n$  and  $\{0,1\}^m$  denote the plaintext space (respectively, the ciphertext space and the key space). Here  $S = \{0,1\}^n \times \{0,1\}^m$  and  $R = \{0,1\}^n$ . Further,  $s_n = (r_n,k)$  where the key k has to be kept secret. Finally,  $\psi(r_n,k) = r_n$  and  $s_{n+1} = (\operatorname{Enc}(r_n,k),k)$  for  $n \geq 0$ . For commonly used block ciphers no statistical weaknesses are known, and hence (R1) should be fulfilled.

Now assume that the adversary knows random numbers  $r_i, \dots, r_{i+j}$ . Since  $r_{t+1} = \operatorname{Enc}(r_t, k)$  the adversary knows j-1 (specific) (plaintext ciphertext) pairs. Hence finding  $r_{i-1}$  is at least as difficult as a chosen-input attack on Enc. (Actually, the situation is even close to a known plaintext attack.) Analogously, the computation of  $r_{i+j+1}$  cannot be easier than a chosen plaintext attack on the decryption function  $\operatorname{Enc}^{-1}$ . Against strong block ciphers chosen-plaintext attacks on Enc and  $\operatorname{Enc}^{-1}$  are not practically feasible. (Otherwise these algorithms would not be viewed as secure.) Provided that the seeding process guarantees that k cannot be guessed with non-negligible probability, we may assume that the DRNG fulfils (R2) if  $\operatorname{Enc}=\operatorname{AES}$  or  $\operatorname{Enc}=\operatorname{Triple-DES}$ , for instance.

Example 2.2 demonstrates a typical security proof for DRNGs where security properties are traced back to properties of well-studied primitives. Note that requirement (R2) is not fulfilled for Enc =DES, although in the eighties one would presumably have confirmed this property. This underlines another important property of DRNGs, namely that their assessment may change in the course of time.

Assume that an attacker gets knowledge of the current internal state  $s_n$ , e.g., because he has mounted a successful hardware attack on a smart card or has had interim access to a computer where this DRNG is implemented. Of course, then the

10 Werner Schindler

random numbers  $r_n, r_{n+1},...$  follow immediately from  $s_n$ . For many applications it is desirable that the DRNG additionally meets

(R3) The knowledge of the internal state shall not allow one to practically compute 'old' random numbers or even a previous internal state or to guess these values with non-negligibly larger probability than without knowledge of the internal state.

Requirement (R3) demands one-way state transition functions  $\phi : S \to S$ . We note that Example 2.2 does not fulfil (R3). Once an adversary knows k he simply decrypts  $r_{n-1} = \operatorname{Enc}^{-1}(r_n, k), r_{n-2} = \operatorname{Enc}^{-1}(r_{n-1}, k), \dots$

Example 2.3. Let  $S = R = \{0,1\}^{160}$  while  $\phi$  and  $\psi$  are given by the hash functions SHA-1 and RIPEMD-160. At this time both SHA-1 and RIPEMD-160 are assumed to meet the one-way property. As a consequence, this RNG meets (R3) (as well as (R1) and (R2)).

The next example underlines that not only  $\phi$  and  $\psi$  are relevant but also their interaction.

Example 2.4. [weak RNG] Let  $S = R = \{0,1\}^{256}$  and  $\phi = \psi = \text{SHA-256}$ . Obviously,  $s_{n+1} = \phi(s_n) = \psi(s_n) = r_n$ , and  $r_{n+1}, r_{n+2}, \ldots$  follow from  $r_n$ . In other words, this RNG does not meet (R2).

*Example 2.5.* Appendix 3.2 in [2] specifies the generation of pseudorandom ephemeral keys. The 'core' of this algorithm defines a DRNG:  $w_0 := f(s_n)$ ,

$$s' := (1 + s_n + w_0) \pmod{2^{\nu}}$$

,

$w_1 := f(s'), s_{n+1} := (1 + s' + w_1) \pmod{2^{\nu}}, r_n := (w_1, w_0)$  with a one-way function f which is defined in [2] (cf. Exercise 2).

We mention that occasionally even DRNGs proposed by adopted standards may contain security flaws. Bleichenbacher detected a weakness in the random number generation specified in the preceding version of [2, 3] which led to a change notice [33]. The problem was the following: Uniformly distributed random numbers  $r_n$  on  $Z_{2^{160}} := \{0,1,\ldots,2^{160}-1\}$  were transformed to random numbers on  $Z_p$  by computing  $r_n \pmod{p}$  where p denotes a 160-bit prime. Obviously, the small values in  $Z_p$  occur twice as often as the large ones. Although the weakness itself is obvious, the attack is not. Interestingly, a full paper that describes the attack in detail has never been published. Reference [4] shows that the DRNG that is used by Windows 2000 does not meet requirement (R3) (see also Section 2.6).

Remark 2.1. Many applications provide implicit information on the generated random numbers, e.g., by known (plaintext/ciphertext) pairs that correspond to a random session key. Sometimes less complicated formulae also exist that contain information on the unknown random numbers. For DSA- and ECDSA signatures, for instance, the adversary knows an underdetermined system of linear equations in the

signature key and the ephemeral keys. We point out that this aspect may be more relevant for PTRNGs that aim at security in an information theoretical sense. We will come back to this issue in the next chapter.

A class of DRNGs which is very interesting from a theoretical point of view are *cryptographically secure* RNGs. Their security relies upon intractability assumptions (e.g., that factoring large integers is hard). On the basis of this intractability assumption(s), security properties of the DRNGs, in respect of the random numbers can be proved.

Unfortunately, the security assertions concern the whole family of DRNGs, and in a strict sense, it is usually not clear what this means for a concrete member of this family, i.e., for a fixed DRNG. In this regard, the situation reminds us of DRNGs that rely on the security of (concrete) block ciphers or hash functions (where, not even an asymptotic security proof exists). A drawback of cryptographically secure DRNGs is their low output rate.

Example 2.6. (Blum-Blum-Shub DRNG) Let  $n = p_1 p_2$  for two m-bit primes  $p_1$  and  $p_2$  with  $p_i \equiv 3 \pmod{4}$ . Starting with a quadratic residue  $x_0 \in Z_n^* := \{0 \le j < n \mid gcd(j,n)=1\}$  (seed) we compute  $x_{n+1} \equiv x_n^d \pmod{n}$  and  $r_n := x_n \pmod{2^{t(m)}}$ .

The generation of t(m) random bits requires the modular exponentiation of a 2m-bit integer. It is known that a Blum-Blum-Shub DRNG – or more precisely, a family of Blum-Blum-Shub DRNGs – is asymptotically secure if  $t(m) = O(\log \log m)$ . Roughly speaking, a non-negligible advantage in guessing the next bit (compared to 'blind guessing') enabled an efficient factoring algorithm, contradicting the factoring intractability.

We mention also that RSA- and Rabin RNGs belong to the class of cryptographically secure RNGs (see [5], Section 5.5, and [6], for instance). We leave this field and refer the interested reader to the relevant literature.

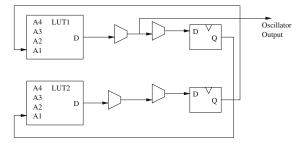

# 2.4.2 Hybrid DRNGs

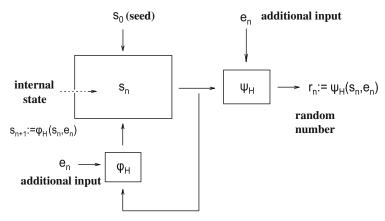

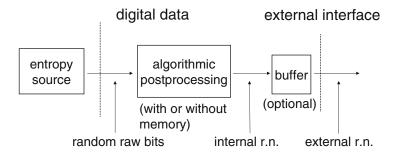

Pure DRNGs compute  $r_n := \psi(s_n)$  and update their internal state by  $s_n \to \phi(s_n)$ . Hybrid DRNGs allow additional input from a finite set  $E_0$ . The state transition function then reads  $\phi_H : S \times E \to S$  with  $E = E_0 \cup \{\infty\}$  where  $\infty$  means 'no additional input'. Formally, any pure DRNG can be viewed as a hybrid DRNG with additional input  $\infty$  in each step, i.e.,  $E = \{\infty\}$  (Figure 2.3).

Example 2.7. Consider Example 2.2 with  $E_0 = \{0,1\}^n$  and

$$\phi_H((r_n,k),e_{n+1}) = (\operatorname{Enc}(r_n \oplus e_{n+1}),k)$$

for  $e_{n+1} \in E_0$  and  $\phi_H((r_n, k), \infty) = (\operatorname{Enc}(r_n), k) = \phi(s_n)$ , and  $\psi_H = \psi$ . (As usual  $\oplus$  stands for the bitwise addition modulo 2.)

12 Werner Schindler

Fig. 2.3 Hybrid DRNG: Generic design.

Of course, a hybrid DRNG cannot be described by a 5-tuple  $(S, R, \phi, \psi, p_S)$  (cf. (2.1)). Instead, we use a 7-tuple

$$(S, R, E, \phi_H, \psi_H, p_S, (q_n)_{n \in N}).$$

(2.2)

The set E and the sequence  $(q_n)_{n\in\mathbb{N}}$  denote the set of additional input data and the probability distributions of the additional data. Note that if  $E = \{\infty\}$  and  $q_n = \varepsilon_{\infty}$  (Dirac measure, which has its total mass concentrated on  $\infty$ ) for all  $n \in \mathbb{N}$  ('never any additional input') the 7-tuple describes a pure DRNG.

Clearly, even if the input sequence  $e_1, e_2, ...$  is constant or completely known by a potential attacker this does not reduce the security of the hybrid DRNG below the security of the respective pure DRNG from Example 2.2. Whether the additional input actually increases the security depends on its randomness and unpredictability properties. If the additional input is derived from the current time, for instance, the security gain may be small, depending on the knowledge of the attacker.

For certain applications the following property is desirable, namely when an attacker gets knowledge of the current internal state of the DRNG (e.g., of a software DRNG implementation on a PC) without being noticed by the user of this DRNG, which generates further random numbers.

• (R4) Even the knowledge of the internal state shall not allow one to *practically* compute the next random numbers or to guess these values with non-negligibly larger probability than without the knowledge of the internal state.

Of course, pure DRNGs cannot fulfil (R4). Whether (R4) is met depends on the randomness of the additional input. Regular additional input from a strong TRNG clearly implies (R4). We will learn more about TRNGs in Sections 2.5 and 2.6 and in the next chapter.

In Example 2.7 we *updated* the internal state before applying the seed transition function  $\phi$ . In fact,  $\phi_H$  may be viewed as a two-step procedure. We note that in the

first step the mapping  $r_n \to r_n \oplus e_{n+1}$  is injective for any fixed  $e_{n+1}$ . This has the pleasant consequence that the security of the hybrid DRNG cannot drop below the level of the respective pure DRNG, regardless of the nature of the additional input and the adversary's knowledge of this input. Much more critical was *reseeding*, realized, for example, by  $\phi'_H((r_n,k),e'_{n+1}) = \operatorname{Enc}(r_n,e'_{n+1})$  with  $e'_{n+1} \in E' = \{0,1\}^m$ . For reseeding, the unpredictability of the additional input is absolutely inevitable.

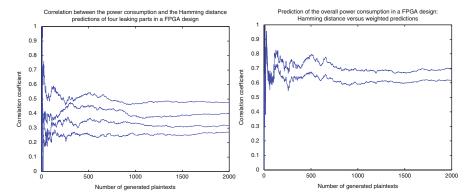

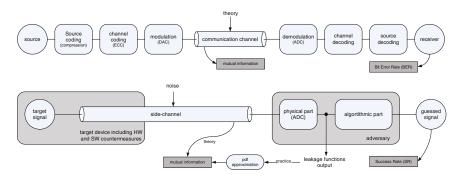

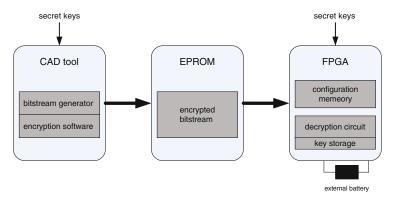

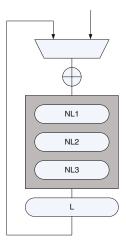

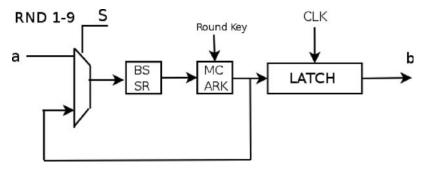

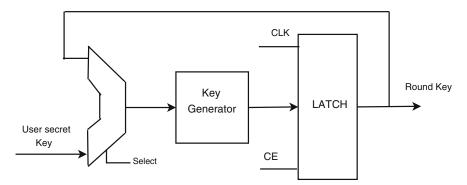

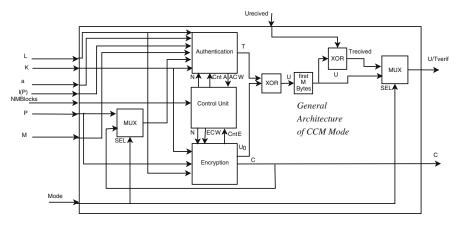

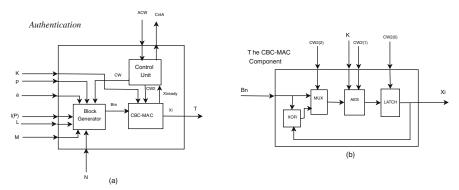

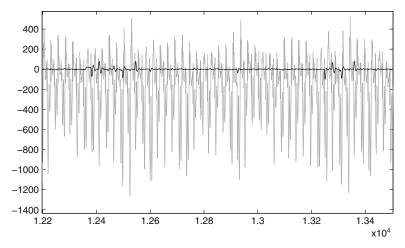

*Remark 2.2.* (i) Requirements (R3) and (R4) are specific DRNG requirements. For TRNGs, (R3) and (R4) are usually 'automatically' fulfilled if (R2) is valid.