# Xilin Liu · Jan Van der Spiegel

# Brain-Machine Interface

**Closed-loop Bidirectional System Design**

Brain-Machine Interface

Xilin Liu • Jan Van der Spiegel

# **Brain-Machine Interface**

Closed-loop Bidirectional System Design

Xilin Liu Department of Electrical and Systems Engineering University of Pennsylvania Philadelphia, PA, USA Jan Van der Spiegel Department of Electrical and Systems Engineering University of Pennsylvania Philadelphia, PA, USA

ISBN 978-3-319-67939-6 ISBN 978-3-319-67940-2 (eBook) https://doi.org/10.1007/978-3-319-67940-2

Library of Congress Control Number: 2017953003

#### © Springer International Publishing AG 2018

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by Springer Nature The registered company is Springer International Publishing AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

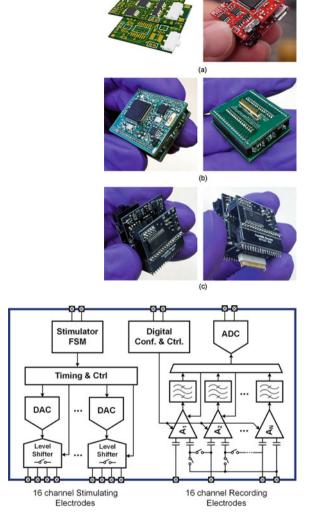

## Preface

Brain-machine interfaces (BMIs) create an artificial pathway between the brain and the external world. BMIs have broad applications in fundamental neuroscience research, neuroprosthetics development, neural disease treatment, and may eventually change the way that humans interact with the world. In the past decade, the research and application of BMIs have received enormous attention from the scientific community as well as the public. However, conventional medical instrumentation used in existing BMI research is not capable of studying the complex and dynamically changing behavior of the brain. Moreover, many neuroscience experiments need to be conducted on freely behaving animals during locomotion and social interaction. The key goal of this book is to address these challenges by the design of next-generation BMIs with innovative solutions from the neuronelectronics interface level up to the system architecture level.

This book provides an introduction to the emerging area of BMIs, with an emphasis on the electrical circuit and system design. This book can help electrical engineers, bioengineers, as well as neuroscience investigators to understand the next-generation bidirectional closed-loop BMIs. Background information, comprehensive surveys and reviews, and design specifications are presented, which will be beneficial for researchers who are new to this area or readers with general interests in this research. In addition, the in-depth discussion of circuit and system design methods, trade-offs, practical issues, and animal experiments will also be valuable for experienced researchers.

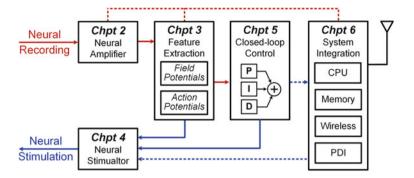

Design innovations have been proposed in neural recording front-end (Chap. 2), neural feature extraction module (Chap. 3), and neural stimulator (Chap. 4). Practical design issues of bidirectional closed-loop neural interface (Chap. 5) and overall system integration (Chap. 6) have been carefully studied and discussed. To the best of our knowledge, this work presents the first reported portable system to provide all required hardware for a closed-loop sensorimotor neural interface, the first wireless sensory encoding experiment conducted in freely swimming animals, and the first bidirectional study of the hippocampal field potentials in freely behaving animals. The circuit and system design details are presented with bench

testing and animal experimental results. The methods, circuit techniques, system topology, and experimental paradigms proposed in this work can be used in a wide range of relevant neurophysiology research and neuroprosthetics development, especially in experiments with freely behaving animals.

We would like to express our appreciation and gratitude to many individuals who have contributed to this book. During this research, we collaborated closely with Prof. Timothy H. Lucas, Dr. Andrew G. Richardson, and their team at the Department of Neurosurgery, University of Pennsylvania. Dr. Lucas directed the overall brain–machine interface research project with his expertise in neuroengineering and therapeutics. Dr. Richardson organized the research, especially the design, conduction, and analysis of the animal experiments presented in Chap. 6. Prof. Milin Zhang, former postdoc in our group, now at Tsinghua University, jointly organized the research. Dr. Zhang supervised the overall electronics design, and implemented the digital compressed sensing module presented in Chap. 2 and the stimulator's digital control module presented in Chap. 4.

We would like to thank our colleagues and friends for their help and insightful discussion during this research; they are Prof. Nader Engheta, Prof. Firooz Aflatouni, Prof. Naveen Verma, Dr. Xiaotie Wu, and Dr. Matt Hongjie Zhu. We would also like to thank Dr. Tao Xiong, Prof. Peter S. Chin, Prof. Trac D. Tran, and Prof. Ralph Etienne-Cummings at Johns Hopkins University for their collaboration in the work of the compressed sensing recording front-end presented in Chap. 2. Students from the Center for Sensor Technologies, University of Pennsylvania, helped in the embedded system programming, RTL implementation, and physical design; they are Rohit Dureja, Hanfei Sun, Tian Qiu, Wanqing Xin, Basheer Subei, and Jacob Sacks. The students and fellows in the Translational Neuromodulation Laboratory (TNL), University of Pennsylvania, carried most of the animal experiments presented in this book; they are Srihari Y. Sritharan, Yohannes Ghenbot, Sam DeLuccia, Pauline K. Weigand, Ivette Planell-Mendez, Solymar Torres Maldonado, and Gregory Boyek. We also appreciate Prof. Dengteng Ge and Prof. Shu Yang for their help in the device development presented in Chap. 6.

We would like to thank the National Science Foundation (NSF), National Institutes of Health (NIH), Defense Advanced Research Projects Agency (DARPA), and Catalyst Foundation for the grants that supported this research. We would like to thank the MOSIS Educational Program for fabricating the chips. We would also like to thank Shurui Zhou, Han Hao, Xinyi Chang, and Hao Gu for their reviews and suggestions during the writing of this book. Finally, we would like to thank the staff at Springer International Publishing AG for their efforts in producing this book.

Philadelphia, PA, USA

Xilin Liu Jan Van der Spiegel

# Contents

| 1 | Intr | oductio | on                                                 | 1  |

|---|------|---------|----------------------------------------------------|----|

|   | 1.1  | Backg   | round and Motivation                               | 1  |

|   | 1.2  | Review  | w of Prior Work                                    | 4  |

|   | 1.3  | Overv   | iew of the Bidirectional Closed-Loop Brain-Machine |    |

|   |      | Interfa | ace System                                         | 10 |

|   | 1.4  | Outlin  | e of This Book                                     | 13 |

| 2 | Neu  | ral Rec | cording Front-End Design                           | 17 |

|   | 2.1  |         | uction                                             | 17 |

|   |      | 2.1.1   | Signal Characteristics                             | 18 |

|   |      | 2.1.2   | Design Specifications                              | 19 |

|   | 2.2  | Desig   | n of a Low-Noise Neural Amplifier                  | 21 |

|   |      | 2.2.1   | Review of Prior Work                               | 21 |

|   |      | 2.2.2   | Circuit Implementation                             | 24 |

|   |      | 2.2.3   | Measurement Results                                | 29 |

|   | 2.3  | A Pre-  | -whitening Neural Amplifier                        | 32 |

|   |      | 2.3.1   | Introduction                                       | 32 |

|   |      | 2.3.2   | Analysis of Pre-whitening Neural Amplifier Design  | 33 |

|   |      | 2.3.3   | Circuit Implementation                             | 40 |

|   |      | 2.3.4   | Measurement Results                                | 41 |

|   | 2.4  | Design  | n of a Low-Power Analog-to-Digital Converter       | 45 |

|   |      | 2.4.1   | Introduction                                       | 45 |

|   |      | 2.4.2   | Circuit Implementation                             | 46 |

|   |      | 2.4.3   | Measurement Results                                | 48 |

|   | 2.5  | A Con   | npressed Sensing Neural Signal Acquisition System  | 51 |

|   |      | 2.5.1   | Introduction                                       | 51 |

|   |      | 2.5.2   | A Brief Background of Compressed Sensing           | 53 |

|   |      | 2.5.3   | System Overview                                    | 54 |

|   |      | 2.5.4   | Circuit Implementation                             | 56 |

|   |      | 2.5.5   | Measurement Results                                | 63 |

|   |      |         |                                                    |    |

| 3 | Neu  | ral Fea | ture Extraction                                         | 69  |

|---|------|---------|---------------------------------------------------------|-----|

|   | 3.1  | Introd  | luction                                                 | 69  |

|   | 3.2  | Natur   | al Logarithmic Domain Field Potential Energy Extraction | 71  |

|   |      | 3.2.1   | Introduction                                            | 71  |

|   |      | 3.2.2   | System and Circuits Implementation                      | 72  |

|   |      | 3.2.3   | Measurement Results                                     | 79  |

|   | 3.3  | Action  | n Potential Discrimination                              | 82  |

|   |      | 3.3.1   | Introduction                                            | 82  |

|   |      | 3.3.2   | Circuit Implementation                                  | 86  |

|   |      | 3.3.3   | Experimental Results                                    | 89  |

|   | 3.4  | Match   | ned Filter for Neural Feature Extraction                | 92  |

|   |      | 3.4.1   | Introduction                                            | 92  |

|   |      | 3.4.2   | Matched Filter and Pre-whitening for Optimum            |     |

|   |      |         | Correlation Detection                                   | 93  |

|   |      | 3.4.3   | Methodologies                                           | 95  |

|   |      | 3.4.4   | Experimental Results                                    |     |

|   |      | 1.00    | •                                                       |     |

| 4 |      |         | mulator Design                                          |     |

|   | 4.1  |         | luction                                                 |     |

|   |      | 4.1.1   | Background of Neurostimulation                          |     |

|   |      | 4.1.2   | Electrode and Electrolyte Interface                     |     |

|   | 4.2  |         | view of Electrical Stimulator Design                    |     |

|   |      | 4.2.1   | Methods of Stimuli Generation                           |     |

|   |      | 4.2.2   | Stimulation Waveform and Electrode Configuration        |     |

|   |      | 4.2.3   | Methods for Charge Balancing                            |     |

|   | 4.3  | -       | n of a General–Purpose Stimulator                       |     |

|   |      | 4.3.1   | Architecture of the Stimulator                          |     |

|   |      | 4.3.2   | Circuit Implementation                                  |     |

|   |      | 4.3.3   | Measurement Results                                     |     |

|   | 4.4  | An Er   | nergy Efficient Net-Zero Charge Neural Stimulator       |     |

|   |      | 4.4.1   | Introduction                                            |     |

|   |      | 4.4.2   | Motivation and Innovation                               |     |

|   |      | 4.4.3   | Circuit Implementation                                  |     |

|   |      | 4.4.4   | Experimental Results                                    | 130 |

|   |      | 4.4.5   | Conclusion                                              | 134 |

| 5 | Ridi | rection | al Neural Interface and Closed-Loop Control             | 137 |

| 5 | 5.1  |         | luction                                                 |     |

|   | 5.2  |         | lation Artifacts in the Bidirectional Neural Interface  | 138 |

|   | 5.2  | 5.2.1   | Introduction                                            |     |

|   |      | 5.2.1   | Review of Prior Work                                    |     |

|   |      | 5.2.2   | Analysis of Stimulation Artifacts                       |     |

|   |      | 5.2.5   | Methods                                                 |     |

|   |      | 5.2.4   | Experimental Results                                    |     |

|   |      | 5.2.5   | •                                                       |     |

|   |      | 5.2.0   | Conclusion                                              | 152 |

#### Contents

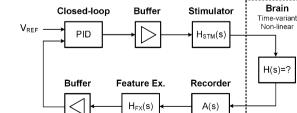

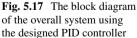

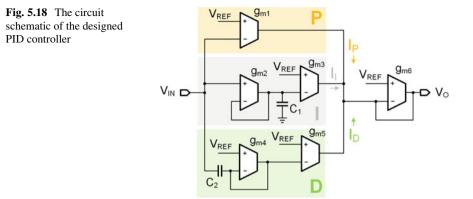

|    | 5.3   | Close   | d-Loop Neural Interface System                       | 155 |

|----|-------|---------|------------------------------------------------------|-----|

|    |       | 5.3.1   | Introduction                                         | 155 |

|    |       | 5.3.2   | Mechanism of Closed-Loop Neural Interface System     | 156 |

|    |       | 5.3.3   | Design of a Closed-Loop Neural Interface with a PID  |     |

|    |       |         | Controller                                           | 158 |

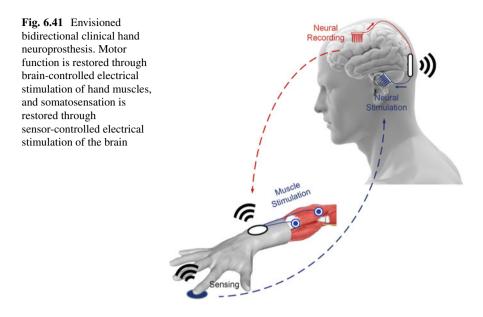

| 6  | Syst  | em Int  | egration and Experiments                             | 165 |

|    | 6.1   | Introd  | uction                                               | 165 |

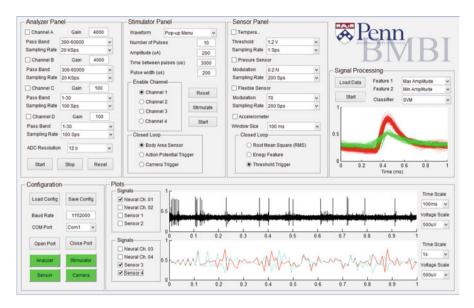

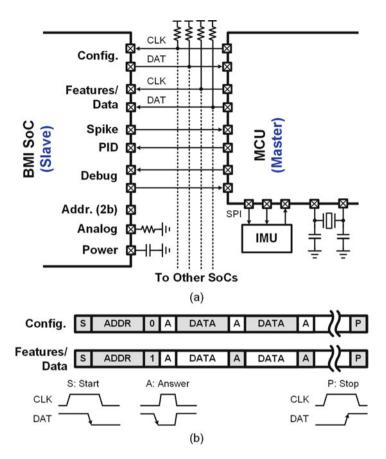

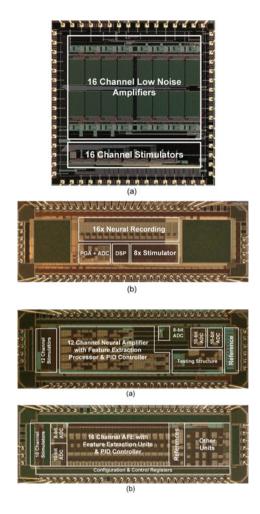

|    | 6.2   | The P   | ennBMBI: A General–Purpose Experimental Platform     | 166 |

|    |       | 6.2.1   | Introduction                                         | 166 |

|    |       | 6.2.2   | System Overview                                      | 167 |

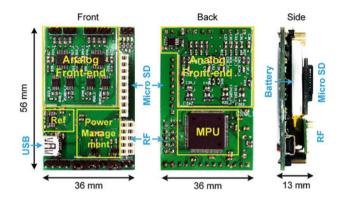

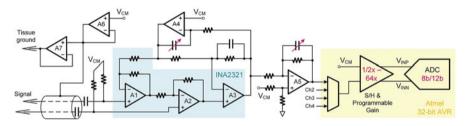

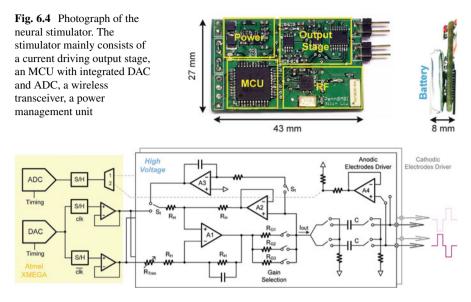

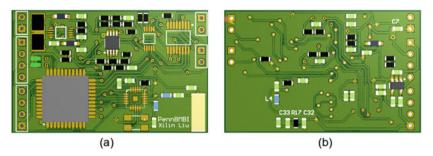

|    |       | 6.2.3   | Hardware Implementation                              | 169 |

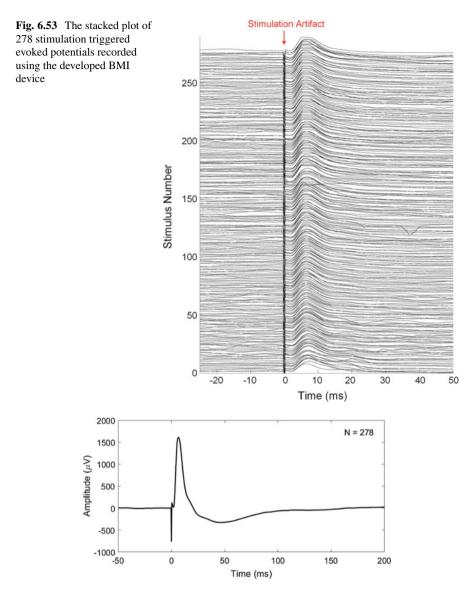

|    |       | 6.2.4   | Experimental Results                                 | 175 |

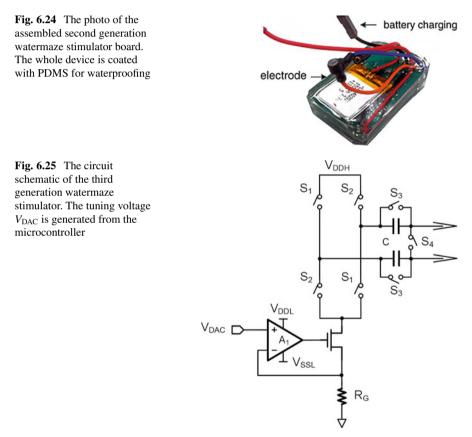

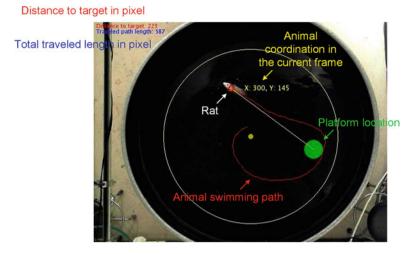

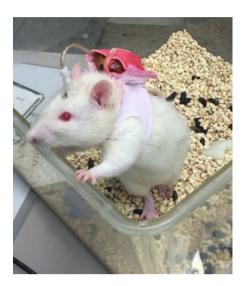

|    | 6.3   | The W   | Vatermaze                                            | 179 |

|    |       | 6.3.1   | Introduction and Background                          | 179 |

|    |       | 6.3.2   | System Overview                                      | 181 |

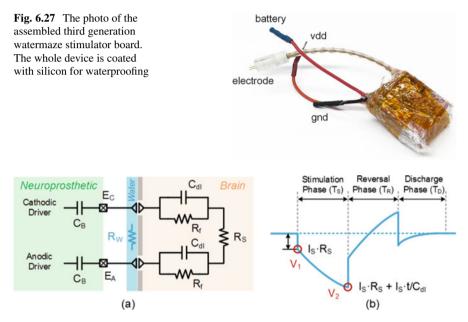

|    |       | 6.3.3   | Hardware Implementation                              | 182 |

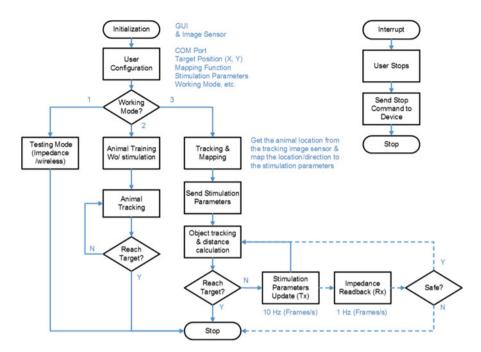

|    |       | 6.3.4   | Software Implementation                              | 190 |

|    |       | 6.3.5   | Experimental Results                                 | 196 |

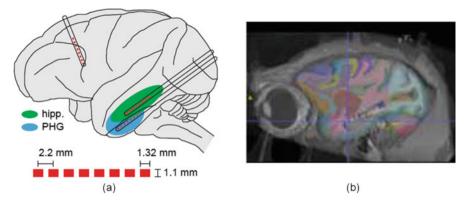

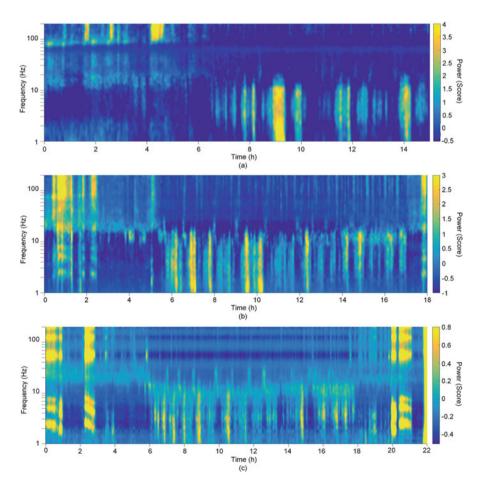

|    | 6.4   | Bidire  | ctional Neural Interface for Freely Behaving Macaque | 199 |

|    |       | 6.4.1   | Introduction and Background                          | 199 |

|    |       | 6.4.2   | Circuit and System Design                            | 200 |

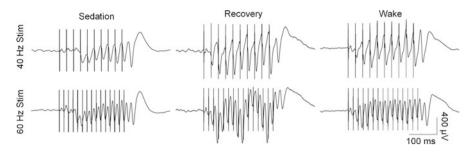

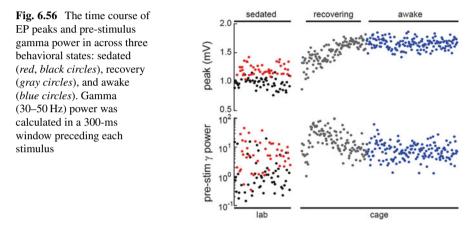

|    |       | 6.4.3   | Experimental Results                                 | 206 |

| 7  | Con   | clusion | and Future Direction                                 | 217 |

|    | 7.1   | Summ    | nary of the Work                                     | 217 |

|    | 7.2   |         | Direction                                            | 219 |

| Bi | bliog | raphy . |                                                      | 221 |

| In | dex   |         |                                                      | 237 |

### **About the Authors**

Xilin Liu received a B.S. degree in electrical engineering from the Harbin Institute of Technology, China, in 2011. He received M.S. and Ph.D. degrees in electrical engineering from the University of Pennsylvania, USA, in 2013 and 2017, respectively. He joined Qualcomm Inc., USA, in 2017. His research interests include analog and mixed-signal integrated circuits and system design, implantable medical electronics, brainmachine interface, high-performance data converters, and CMOS sensors.

Dr. Liu is a member of the IEEE, the IEEE Solid-State Circuits Society, and the IEEE Circuits and

Systems Society. He has served as a reviewer for the IEEE Transactions on Circuits and Systems (TCAS), the IEEE Transactions on Biomedical Circuits and Systems (TBioCAS), the IEEE Sensors Journal, and the Journal of Engineering (JoE). He has also served on several program and technical committees (ISCAS, BioCAS, MWSCAS, SOCC, and ISVLSI). Dr. Liu received the IEEE Solid-State Circuits Society (SSCS) 2015-16 Predoctoral Achievement Award, the Best Student Paper Award and the Best Track Award of the 2017 International Symposium on Circuits and Systems (ISCAS), the Best Paper Award (first place) of the 2015 Biomedical Circuits and Systems Conference (BioCAS), and the Best Paper Award of the BioCAS Track of the 2014 International Symposium on Circuits and Systems (ISCAS). He is also the recipient of the Student-Research Preview Award (Honorable Mention) of the 2014 IEEE International Solid-State Circuits Conference (ISSCC).

**Jan Van der Spiegel** is a professor of electrical and systems engineering and the director of the Center for Sensor Technologies at the School of Engineering and Applied Science at the University of Pennsylvania. He is the former chair of the Department of Electrical Engineering and interim chair of the Department of Electrical and Systems Engineering. Dr. Van der Spiegel received his master's degree in electromechanical engineering and his Ph.D. degree in electrical engineering from the University of Leuven, Belgium, in 1974 and 1979, respectively. His primary research interests are in mixed-mode VLSI design, bio-inspired

CMOS vision sensors, biologically based image sensors and sensory information processing systems, and brain-machine interface electronics. He has published over 250 journal and conference papers and is the coauthor of eight US patents.

He is a life fellow of the IEEE, received the IEEE Major Educational Innovation Award, and is the recipient of the IEEE Third Millennium Medal, the UPS Foundation Distinguished Education Chair, and the Bicentennial Class of 1940 Term Chair. He received the Christian and Mary Lindback Foundation Distinguished Teaching Award, the S. Reid Warren Award for Distinguished Teaching, the IBM Young Faculty Development Award, and the Presidential Young Investigator Award. He has served on several IEEE program committees (IEDM, ICCD, ISCAS, and ISSCC) and was the technical program chair of the 2007 International Solid-State Circuits Conference (ISSCC 2007).

Dr. Van der Spiegel is an associate editor of the *IEEE Transactions on Biomedical Circuits and Systems*, member of the Editorial Board of the Proceedings of the IEEE, and section editor of electrical and electronic engineering of the *Journal of Engineering* of the IET, and former editor of *Sensors and Actuators A* for North and South America. He has been the chair of the IEEE SSCS Chapters Committee from 1998 to 2015. He is currently the president of the IEEE Solid-State Circuits Society. He is a member of Phi Beta Delta and Tau Beta Pi. He spent a 6-month sabbatical at Tsinghua University, Beijing, as a distinguished visiting Professor in 2017–2018.

# Acronyms

| 4 D  |                                         |

|------|-----------------------------------------|

| AP   | Action Potential                        |

| ASIC | Application-Specific Integrated Circuit |

| BMI  | Brain–Machine Interface                 |

| CMRR | Common-Mode Rejection Ratio             |

| CN   | Cuneate Nucleus                         |

| CR   | Compression Ratio                       |

| CS   | Compressed Sensing                      |

| DAC  | Digital to Analog Converter             |

| DBS  | Deep brain stimulation                  |

| DNL  | Differential Non-linearity              |

| ECoG | Electrocorticography                    |

| EEG  | Electroencephalogram                    |

| ENOB | Effective Number of Bits                |

| FES  | Functional Electrical Stimulation       |

| FoM  | Figure of Merit                         |

| INL  | Integral Non-Linearity                  |

| LFP  | Local Field Potential                   |

| LNA  | Low Noise Amplifier                     |

| NEF  | Noise Efficiency Factor                 |

| NI   | Neural Interface                        |

| OTA  | Operational Transconductance Amplifier  |

| PEF  | Power Efficiency Factor                 |

| PGA  | Programmable Gain Amplifier             |

| PID  | Proportional-Integral-Derivative        |

| PSD  | Power Spectrum Density                  |

| SAR  | Successive Approximation Register       |

| SFDR | Spurious-Free Dynamic Range             |

| SNR  | Signal to Noise Ratio                   |

| SoC  | System on Chip                          |

| TIA  | Transimpedance Amplifier                |

|      | - *                                     |

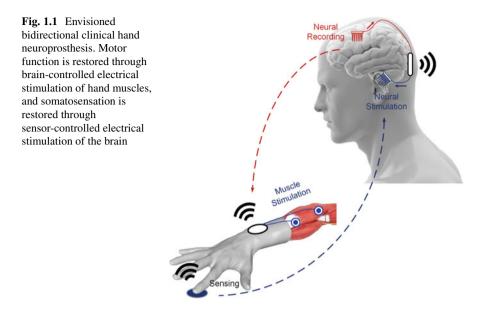

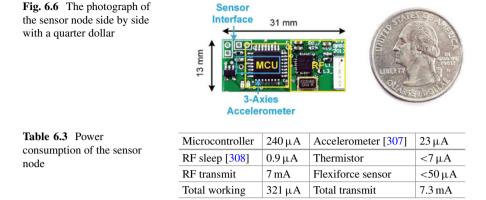

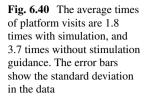

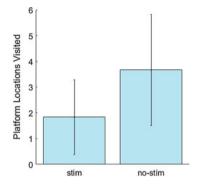

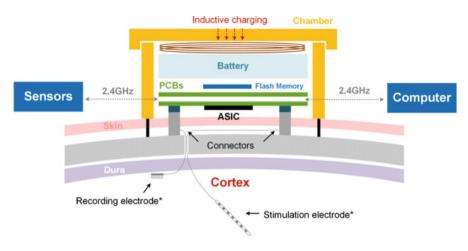

| Fig. 1.1 | Envisioned bidirectional clinical hand neuroprosthesis.                |    |

|----------|------------------------------------------------------------------------|----|

|          | Motor function is restored through brain-controlled                    |    |

|          | electrical stimulation of hand muscles, and somatosensation            |    |

|          | is restored through sensor-controlled electrical stimulation           |    |

|          | of the brain                                                           | 3  |

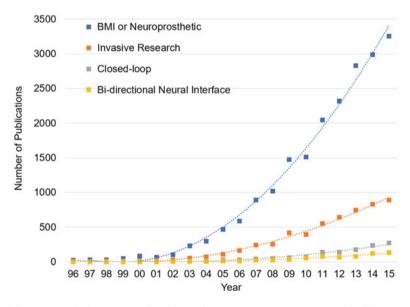

| Fig. 1.2 | The historical trend for publications of BMIs over the past            |    |

|          | 15 years. Specific categories of BMIs including invasive               |    |

|          | studies, closed-loop studies, and bidirectional studies are            |    |

|          | plotted for comparison                                                 | 4  |

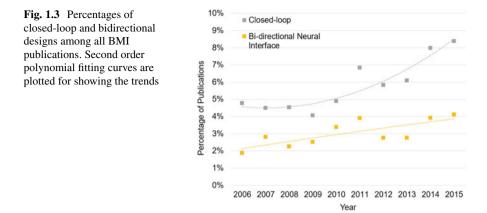

| Fig. 1.3 | Percentages of closed-loop and bidirectional designs among             |    |

|          | all BMI publications. Second order polynomial fitting                  |    |

|          | curves are plotted for showing the trends                              | 5  |

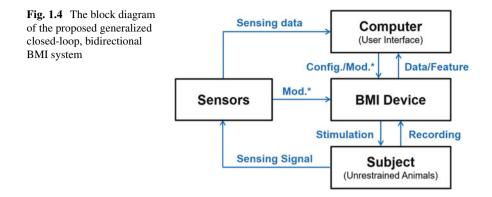

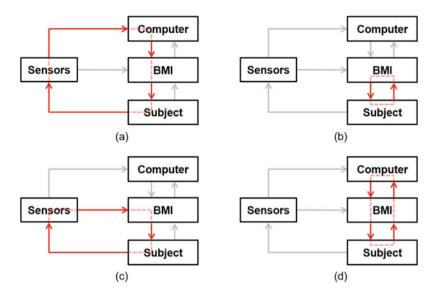

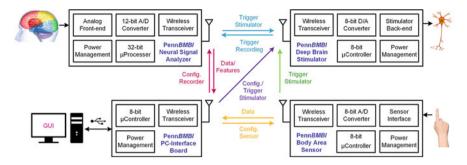

| Fig. 1.4 | The block diagram of the proposed generalized closed-loop,             |    |

|          | bidirectional BMI system                                               | 12 |

| Fig. 1.5 | Various closed-loop configurations of the proposed BMI                 |    |

|          | system                                                                 | 13 |

| Fig. 1.6 | The building blocks of a typical bidirectional closed-loop             |    |

|          | BMI system, and the organization of this book                          | 14 |

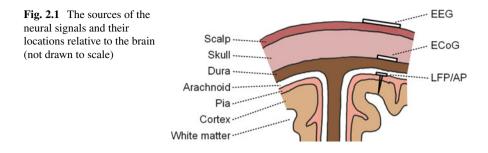

| Fig. 2.1 | The sources of the neural signals and their locations relative         |    |

| 8        | to the brain (not drawn to scale)                                      | 18 |

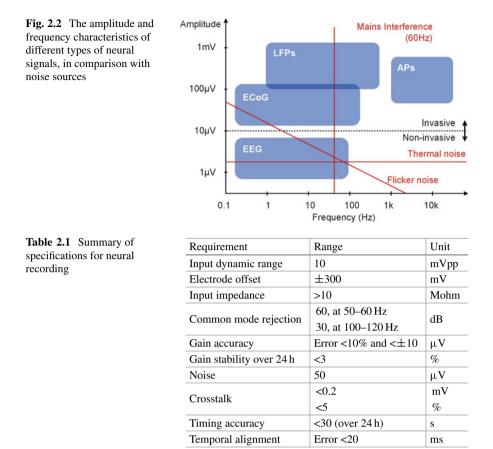

| Fig. 2.2 | The amplitude and frequency characteristics of different               |    |

| 0        | types of neural signals, in comparison with noise sources              | 19 |

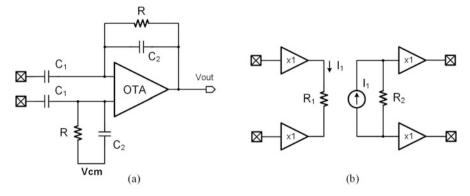

| Fig. 2.3 | The block diagram of the typical neural amplifiers with $(\mathbf{a})$ | -  |

| 0        | capacitive gain element and (b) resistive gain element. The            |    |

|          | x1 symbol is for a unity gain buffer                                   | 22 |

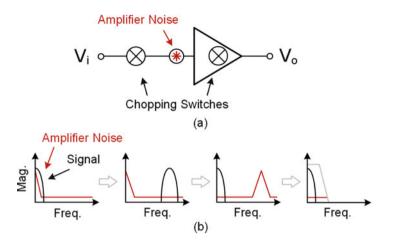

| Fig. 2.4 | (a) The block diagram of a chopping amplifier. (b)                     |    |

| U        | Illustration of the signal and noise spectrum before and after         |    |

|          | chopping                                                               | 24 |

| Fig. 2.5 | The block diagram of the proposed low-noise neural                     |    |

| C        | recording front-end                                                    | 25 |

|          |                                                                        |    |

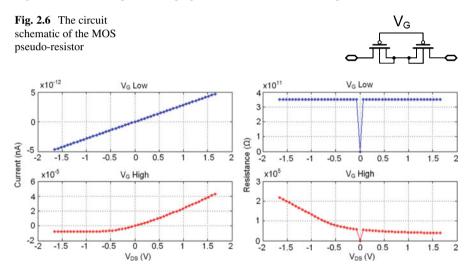

| Fig. 2.6        | The circuit schematic of the MOS pseudo-resistor                 | 25 |

|-----------------|------------------------------------------------------------------|----|

| Fig. 2.7        | The simulated resistance of the MOS pseudo-resistor. The         |    |

|                 | <i>left column</i> shows the current versus the voltage applied, |    |

|                 | and <i>right column</i> shows the derived resistance             | 25 |

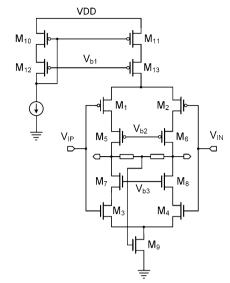

| Fig. 2.8        | The circuit schematic of the fully differential low-noise OTA    |    |

|                 | with a complementary input stage                                 | 26 |

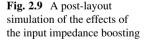

| Fig. 2.9        | A post-layout simulation of the effects of the input             |    |

|                 | impedance boosting                                               | 28 |

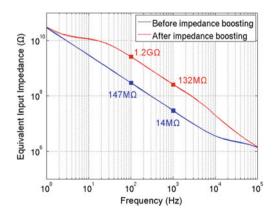

| Fig. 2.10       | The microphotograph and layout of one channel of the             |    |

|                 | neural recording front-end. Major building blocks are            |    |

|                 | highlighted in the layout                                        | 29 |

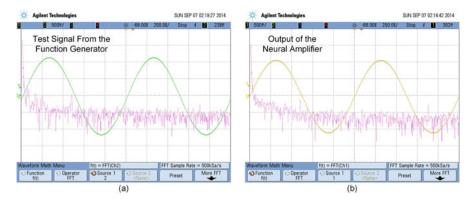

| Fig. 2.11       | The measured response of the neural amplifier with a 1 kHz       |    |

| U U             | sinusoidal input signal. The amplifier is configured with the    |    |

|                 | maximum gain of 1900. The midband gain error is 0.37%            | 30 |

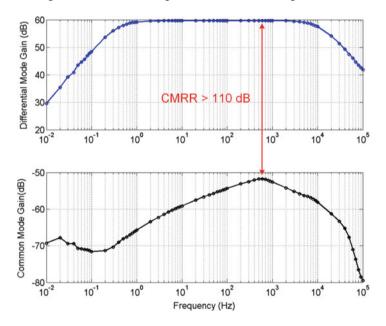

| Fig. 2.12       | The measured differential-mode and common-mode                   |    |

| 0               | frequency responses of the low-noise neural amplifier            | 30 |

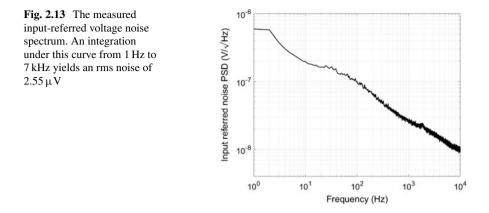

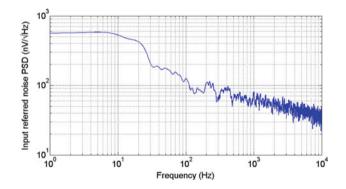

| Fig. 2.13       | The measured input-referred voltage noise spectrum. An           |    |

| 0               | integration under this curve from 1 Hz to 7 kHz yields an        |    |

|                 | rms noise of $2.55 \mu\text{V}$                                  | 31 |

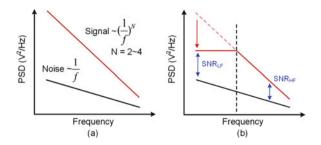

| Fig. 2.14       | Illustration of the pre-whitening filter. (a) The neural signal  |    |

| 8. =            | displays a $1/f^n$ power characteristic, while the recording     |    |

|                 | front-end has a $1/f$ noise power characteristic. (b) The        |    |

|                 | pre-whitening filter shapes the frequency response of the        |    |

|                 | recording front-end to reduce the overall dynamic range          |    |

|                 | requirement, while still preserves a sufficient SNR              | 33 |

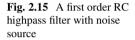

| Fig. 2.15       | A first order RC highpass filter with noise source               | 33 |

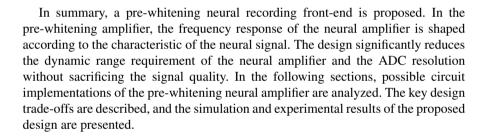

| Fig. 2.16       | Noise simulation of RC highpass filters with frequency           | 55 |

| 115. 2.10       | corners at 10 and 100 Hz. The capacitor value is set to be       |    |

|                 | 20 pF                                                            | 34 |

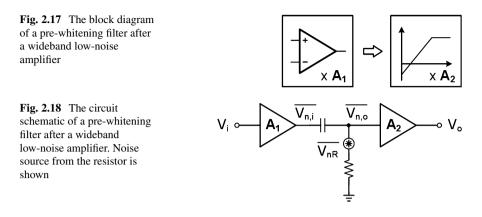

| Fig. 2.17       | The block diagram of a pre-whitening filter after a wideband     | 54 |

| 1 lg. 2.17      | low-noise amplifier                                              | 35 |

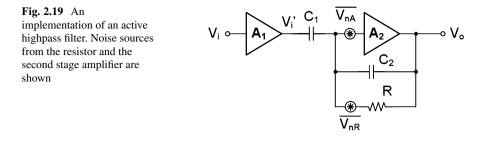

| Fig. 2.18       | The circuit schematic of a pre-whitening filter after a          | 55 |

| Fig. 2.10       | wideband low-noise amplifier. Noise source from the              |    |

|                 | resistor is shown                                                | 35 |

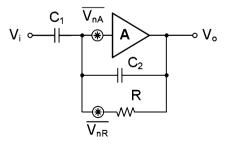

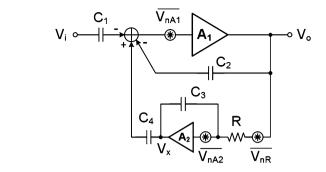

| Fig. 2.19       | An implementation of an active highpass filter. Noise            | 55 |

| Fig. 2.19       | sources from the resistor and the second stage amplifier are     |    |

|                 | · · ·                                                            | 26 |

| E:~ 2.20        | shown                                                            | 36 |

| Fig. 2.20       | A typical capacitor-coupled neural amplifier. Noise sources      | 27 |

| E. 2.21         | are marked in the figure                                         | 37 |

| Fig. 2.21       | A capacitor-coupled instrumentation amplifier with a DC          | 20 |

| E'. 2.22        | servo loop                                                       | 38 |

| Fig. 2.22       | A capacitor-coupled instrumentation amplifier with a DC          | 20 |

| <b>F</b> ' 2.22 | servo loop implemented by switched capacitor circuits            | 39 |

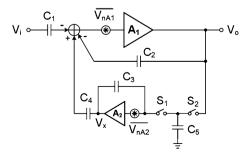

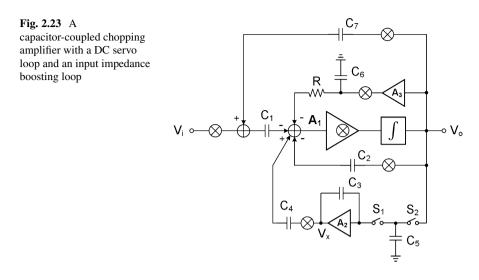

| Fig. 2.23       | A capacitor-coupled chopping amplifier with a DC servo           |    |

|                 | loop and an input impedance boosting loop                        | 40 |

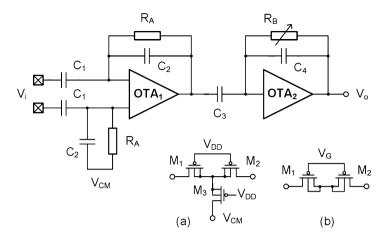

| Fig. 2.24               | The circuit schematic of the designed pre-whitening amplifier. The pseudo-resistors $R_A$ and $R_B$ used in the |    |

|-------------------------|-----------------------------------------------------------------------------------------------------------------|----|

|                         | first and second stage are shown in subplot (a) and (b),                                                        |    |

|                         | respectively                                                                                                    | 41 |

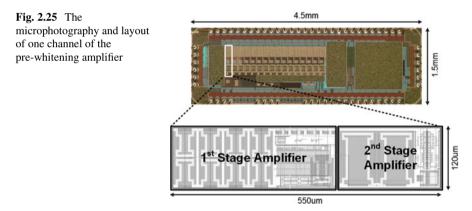

| Fig. 2.25               | The microphotography and layout of one channel of the pre-whitening amplifier                                   | 41 |

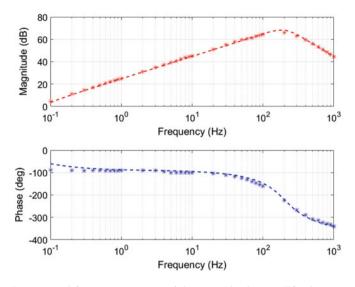

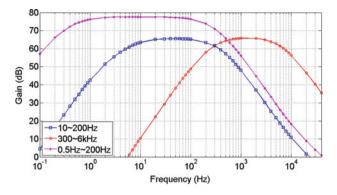

| Fig. 2.26               | The measured frequency response of the pre-whitening                                                            | 41 |

| Fig. 2.20               | amplifier in comparison with the simulation result                                                              | 42 |

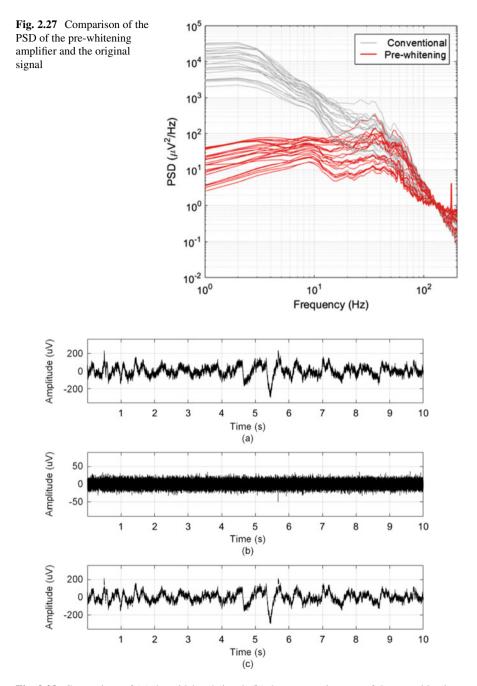

| Fig. 2.27               | Comparison of the PSD of the pre-whitening amplifier and                                                        | 42 |

| 1 'Ig. 2.27             | the original signal                                                                                             | 43 |

| Fig. 2.28               | Comparison of ( <b>a</b> ) the wideband signal, ( <b>b</b> ) the measured                                       |    |

| 8                       | output of the pre-whitening amplifier, and (c) the                                                              |    |

|                         | reconstructed signal from the pre-whitening amplifier's                                                         |    |

|                         | recording                                                                                                       | 43 |

| Fig. 2.29               | Comparison of the spectrum of (a) the original signal                                                           | -  |

| 0                       | and (b) the reconstructed signal from the pre-whitening                                                         |    |

|                         | amplifier's recording                                                                                           | 44 |

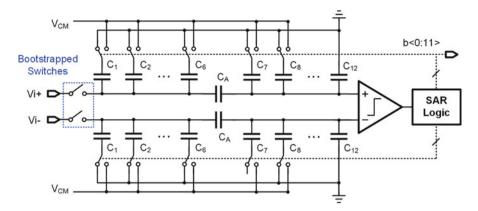

| Fig. 2.30               | The circuit diagram of the 10-bit voltage-mode SAR ADC                                                          | 46 |

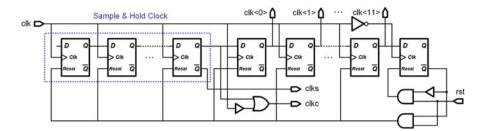

| Fig. 2.31               | The circuit schematic of the SAR timing generation module                                                       | 47 |

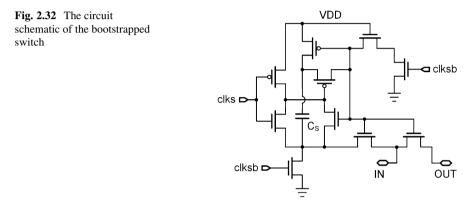

| Fig. 2.32               | The circuit schematic of the bootstrapped switch                                                                | 47 |

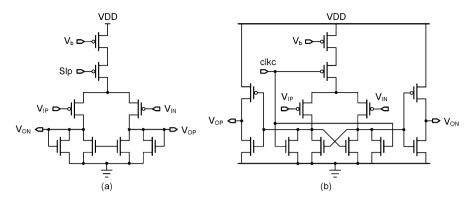

| Fig. 2.33               | The circuit schematic of the comparator. (a) A pre-amplifier,                                                   |    |

|                         | and ( <b>b</b> ) a dynamic latch                                                                                | 48 |

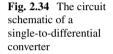

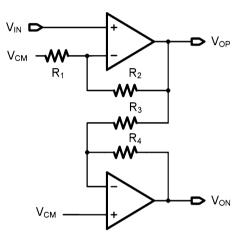

| Fig. 2.34               | The circuit schematic of a single-to-differential converter                                                     | 48 |

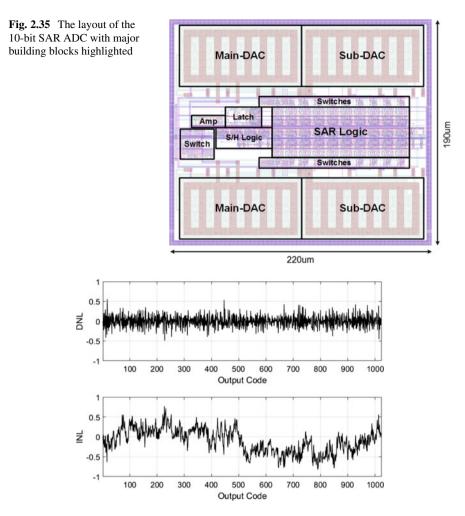

| Fig. 2.35               | The layout of the 10-bit SAR ADC with major building                                                            |    |

|                         | blocks highlighted                                                                                              | 49 |

| Fig. 2.36               | The measured DNL and INL of the 10-bit SAR ADC. The                                                             |    |

|                         | worst DNL is $-0.49/+0.56$ LSB, and the worst INL is                                                            |    |

|                         | -0.82/+0.77 LSB                                                                                                 | 49 |

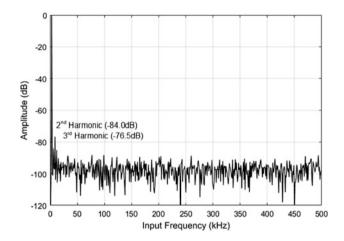

| Fig. 2.37               | The measured FFT spectrum at 1 MS/s with an input tone of                                                       |    |

|                         | 3 kHz. The SFDR is 76.54 dB and the SNDR is 56 dB. The                                                          | -  |

| <b>F</b> : <b>0 0</b> 0 | ENOB at 3 kHz is 9.01                                                                                           | 50 |

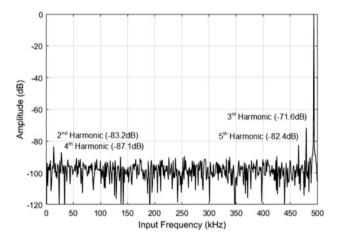

| Fig. 2.38               | The measured FFT spectrum at 1 MS/s with an input tone of                                                       |    |

|                         | 493 kHz. The SFDR is 71.6 dB and the SNDR is 54.6 dB.                                                           | 50 |

| E. 2.20                 | The ENOB at 493 kHz is 8.77.                                                                                    | 50 |

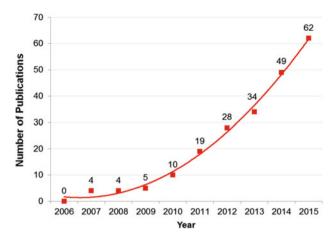

| Fig. 2.39               | Historical trend for publications using compressed sensing                                                      |    |

|                         | technique in biomedical signal acquisition in the past                                                          | 50 |

| Eig 2.40                | decade. Data retrieved from Web of Science                                                                      | 52 |

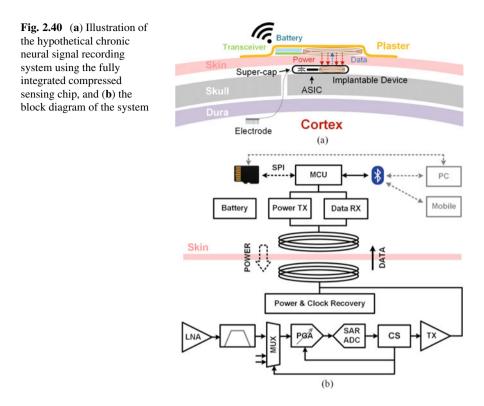

| Fig. 2.40               | (a) Illustration of the hypothetical chronic neural signal                                                      |    |

|                         | recording system using the fully integrated compressed                                                          | 55 |

|                         | sensing chip, and (b) the block diagram of the system                                                           | 55 |

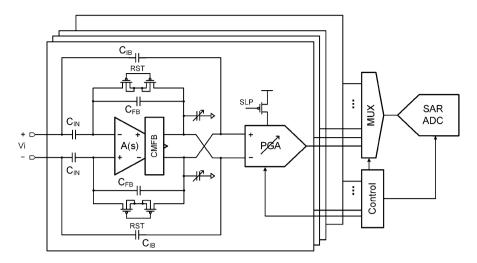

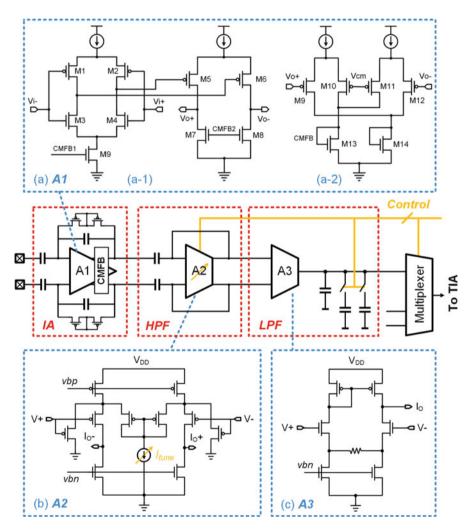

| Fig. 2.41 | The circuit schematic of one analog front-end channel of              |    |

|-----------|-----------------------------------------------------------------------|----|

|           | the proposed system (Part I). The signal chain includes:              |    |

|           | amplification, filtering, voltage-to-current conversion,              |    |

|           | multiplexing and digitization. The circuit schematic of               |    |

|           | (a) the low-noise neural amplifier, (b) the OTA with an               |    |

|           | extended linear range, and (c) the OTA with a programmable            |    |

|           | transconductance                                                      | 56 |

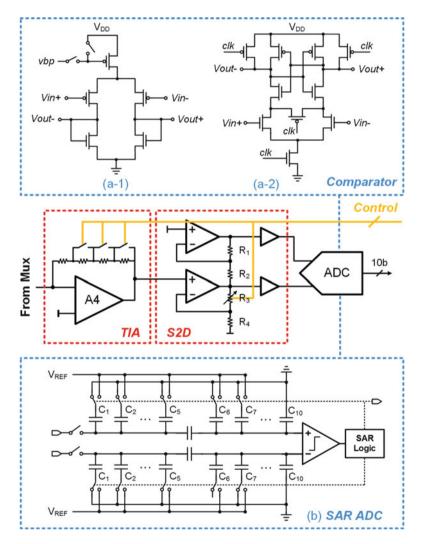

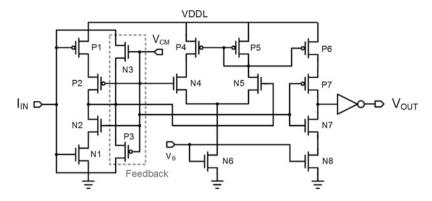

| Fig. 2.42 | The circuit schematic of the analog front-end of the                  |    |

|           | proposed system (Part II). A current-to-voltage conversion            |    |

|           | with a programmable gain and a 10-bit SAR ADC is used                 |    |

|           | to digitize the signal. The boxed windows show the circuit            |    |

|           | schematic of ( <b>a</b> ) the comparator and ( <b>b</b> ) the SAR ADC | 58 |

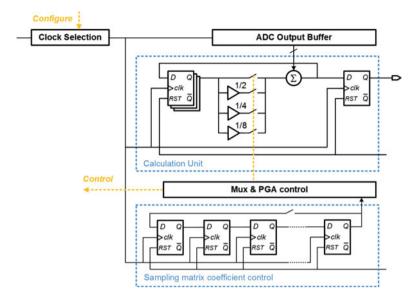

| Fig. 2.43 | The block diagram of the compressive sensing processing               |    |

|           | module. A linear congruential pseudo random number                    |    |

|           | generator is used to generate all the entries of the sampling         |    |

|           | matrix                                                                | 60 |

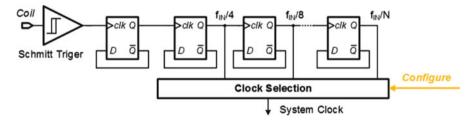

| Fig. 2.44 | The circuit schematic of the clock recovery and clock                 |    |

|           | division module                                                       | 61 |

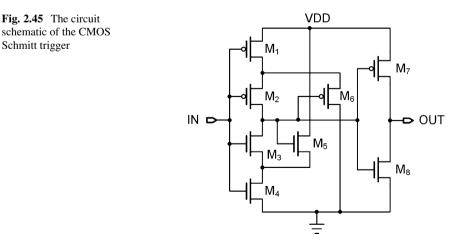

| Fig. 2.45 | The circuit schematic of the CMOS Schmitt trigger                     | 61 |

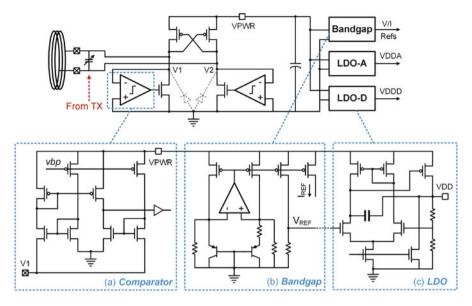

| Fig. 2.46 | Inductive power management module, including active                   |    |

| -         | rectifier and LDOs for analog and digital power supplies. (a)         |    |

|           | Circuit schematic of the comparator, (b) bandgap reference,           |    |

|           | and (c) LDO (start-up circuits are not shown)                         | 62 |

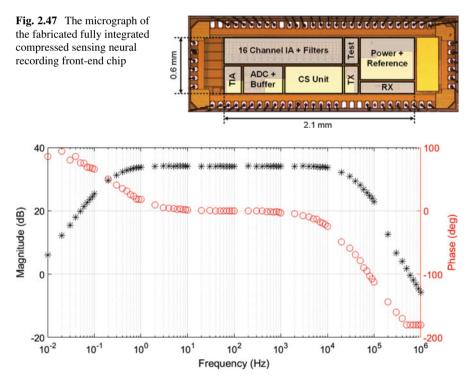

| Fig. 2.47 | The micrograph of the fabricated fully integrated                     |    |

|           | compressed sensing neural recording front-end chip                    | 63 |

| Fig. 2.48 | The measured frequency response of the low-noise amplifier            |    |

|           | (without filtering stages)                                            | 63 |

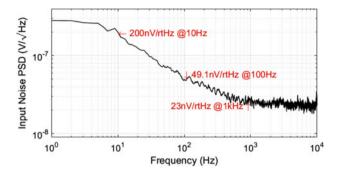

| Fig. 2.49 | The measured input-referred voltage noise spectrum                    | 64 |

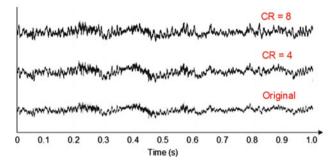

| Fig. 2.50 | A time-domain comparison between the uncompressed                     |    |

|           | recording and the data reconstructed from recordings in               |    |

|           | different compression ratios (CR)                                     | 64 |

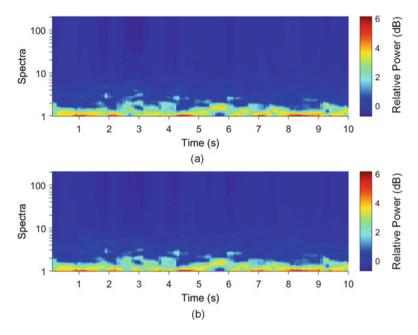

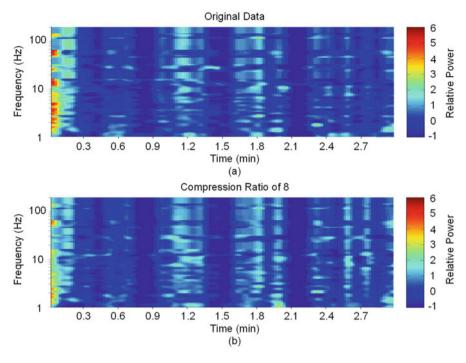

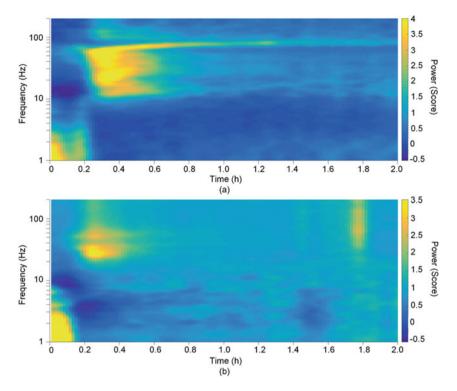

| Fig. 2.51 | A comparison of the spectrograms of (a) the uncompressed              |    |

|           | recording and (b) the data reconstructed from the recording           |    |

|           | with a CR of 8                                                        | 65 |

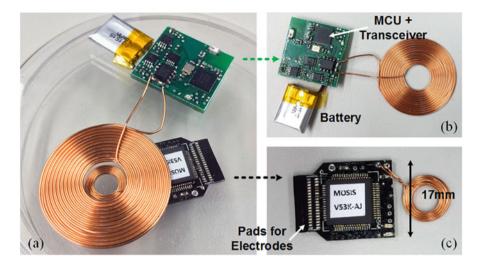

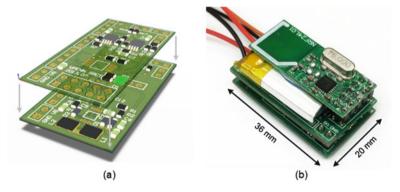

| Fig. 2.52 | Photograph of an assembled demonstration system. (a)                  |    |

|           | Power and data transmission testing setup across a 5 mm               |    |

|           | plastic cap, (b) the external transceiver board, and (c) the          |    |

|           | implantable device                                                    | 66 |

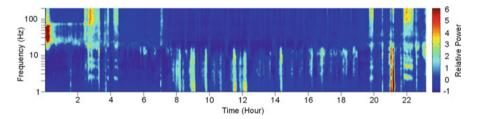

| Fig. 2.53 | A 24-h continuous recording in the hippocampus of a rhesus            |    |

|           | macaque during free behavior                                          | 66 |

xviii

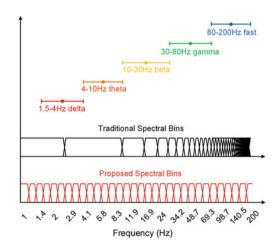

| Fig. 3.1              | Brain oscillation bands are shown in the natural logarithmic<br>domain. The frequency tuning bins for energy extraction |     |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------|-----|

|                       | in traditional linear steps and in the proposed natural                                                                 |     |

|                       | logarithmic domain are plotted for comparison. A total of 32                                                            |     |

|                       | steps in a frequency range from 1 to 200 Hz is used in both                                                             | - 1 |

| <b>F</b> ' <b>2.2</b> | cases for illustration                                                                                                  | 71  |

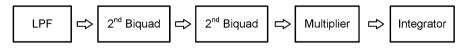

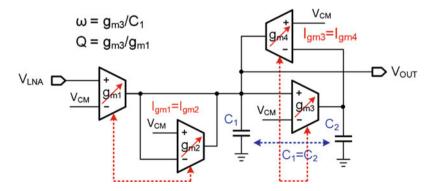

| Fig. 3.2              | The processing flow of the LFP energy extraction                                                                        | 72  |

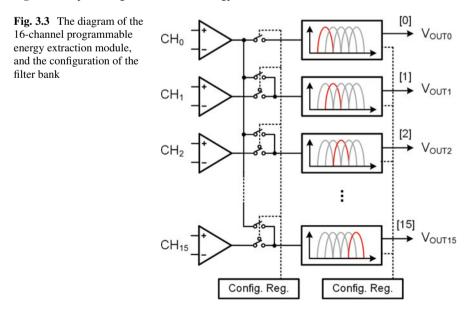

| Fig. 3.3              | The diagram of the 16-channel programmable energy                                                                       |     |

|                       | extraction module, and the configuration of the filter bank                                                             | 72  |

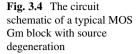

| Fig. 3.4              | The circuit schematic of a typical MOS Gm block with                                                                    | = 0 |

|                       | source degeneration                                                                                                     | 73  |

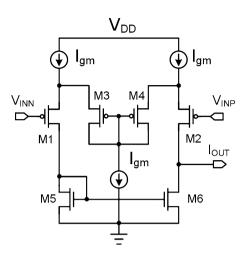

| Fig. 3.5              | The circuit schematic of the Gm block with a reduced                                                                    |     |

|                       | transconductance and an extended linear input range. The                                                                |     |

|                       | biasing current is used to tune the transconductance                                                                    | 74  |

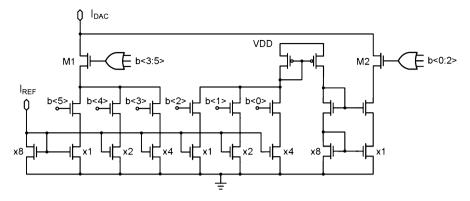

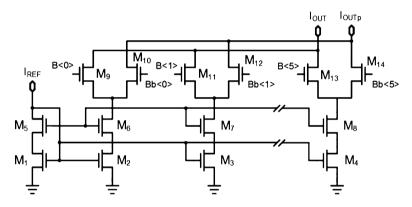

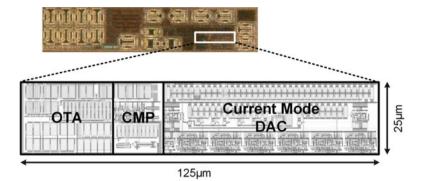

| Fig. 3.6              | The circuit schematic of the 6-bit current-mode DAC used                                                                |     |

|                       | for generating the biasing current for the Gm block                                                                     | 75  |

| Fig. 3.7              | The circuit schematic of the biasing current generation                                                                 |     |

|                       | module. A 64-step natural exponentially spaced biasing                                                                  |     |

|                       | current can be generated                                                                                                | 75  |

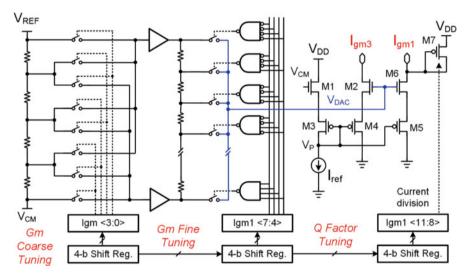

| Fig. 3.8              | The circuit schematic of the designed biquad filter. The                                                                |     |

|                       | center frequency and the quality factor of the filter can be                                                            |     |

|                       | tuned independently                                                                                                     | 77  |

| Fig. 3.9              | The circuit schematic of the Gilbert multiplier and the integrator                                                      | 79  |

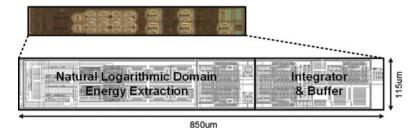

| Fig. 3.10             | The microphotograph and layout of one LFP energy                                                                        |     |

|                       | extraction channel. The major building blocks are                                                                       |     |

|                       | highlighted in the layout                                                                                               | 79  |

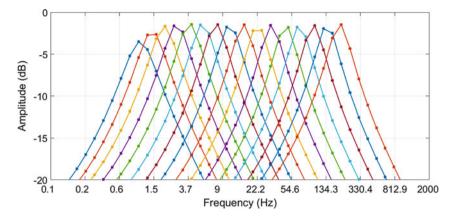

| Fig. 3.11             | The measured frequency response of the biquad filter tuning                                                             |     |

|                       | in the proposed natural logarithmic steps. A total of 16 steps                                                          |     |

|                       | were measured                                                                                                           | 80  |

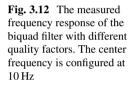

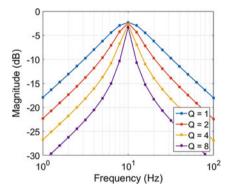

| Fig. 3.12             | The measured frequency response of the biquad filter with                                                               |     |

|                       | different quality factors. The center frequency is configured                                                           |     |

|                       | at 10 Hz                                                                                                                | 80  |

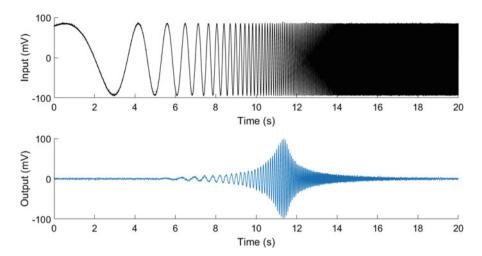

| Fig. 3.13             | The measured response of one biquad filter with a synthetic                                                             |     |

|                       | sine wave with frequency sweeping from 0.1 Hz to 1 kHz                                                                  | 81  |

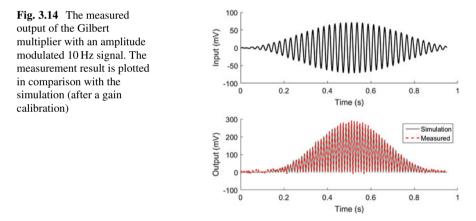

| Fig. 3.14             | The measured output of the Gilbert multiplier with an                                                                   |     |

|                       | amplitude modulated 10 Hz signal. The measurement result                                                                |     |

|                       | is plotted in comparison with the simulation (after a gain                                                              |     |

|                       | calibration)                                                                                                            | 81  |

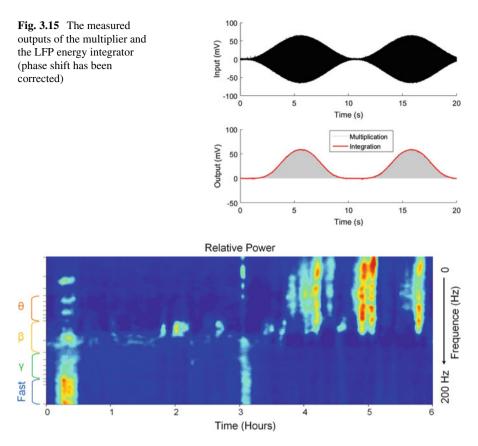

| Fig. 3.15             | The measured outputs of the multiplier and the LFP energy                                                               |     |

|                       | integrator (phase shift has been corrected)                                                                             | 82  |

| Fig. 3.16             | The spectrum of a 6-h continuous recording using the                                                                    |     |

|                       | prototype device. The animal's brain state changed from                                                                 |     |

|                       | awake (high-frequency oscillation more active) to sleep                                                                 |     |

|                       | (low-frequency oscillation more active) during the recording                                                            | 82  |

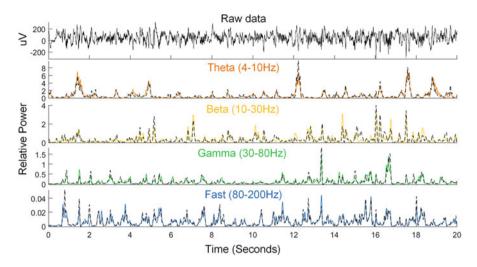

| Fig. 3.17  | In vivo recording of a Rhesus macaque using the designed<br>chip. The extracted energy in four brain oscillation bands<br>(Theta, Beta, Gamma, and Fast) compared with the |     |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|            | theoretical computations ( <i>dashed lines</i> )                                                                                                                           | 83  |

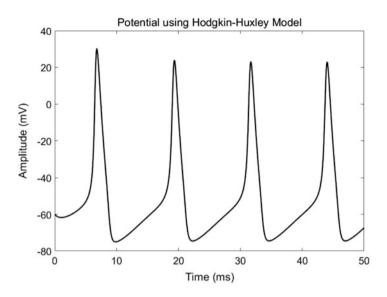

| Fig. 3.18  | Matlab simulation of the HHM model using Runge-Kutta                                                                                                                       |     |

| -          | method for solving the arithmetic solution                                                                                                                                 | 85  |

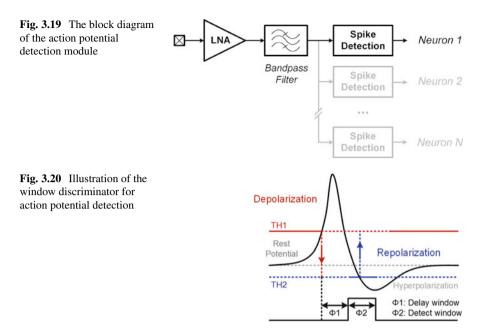

| Fig. 3.19  | The block diagram of the action potential detection module                                                                                                                 | 87  |

| Fig. 3.20  | Illustration of the window discriminator for action potential                                                                                                              |     |

|            | detection                                                                                                                                                                  | 87  |

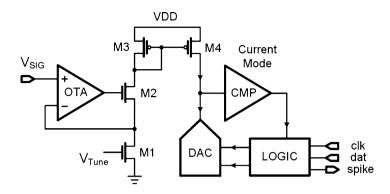

| Fig. 3.21  | The block diagram of the proposed current-mode action                                                                                                                      |     |

|            | potential detection unit with an integrated programmable                                                                                                                   |     |

|            | amplitude-window discriminator. The filtering stage is not                                                                                                                 |     |

|            | shown in this figure                                                                                                                                                       | 88  |

| Fig. 3.22  | The circuit schematic of the 6-bit current-mode DAC                                                                                                                        | 88  |

| Fig. 3.23  | The circuit schematic of the current-mode comparator                                                                                                                       | 89  |

| Fig. 3.24  | The microphotograph and layout of the designed action                                                                                                                      | 00  |

| Ein 2.05   | potential discrimination module                                                                                                                                            | 90  |

| Fig. 3.25  | The action potential signal used for testing the designed module. The real action potentials are marked by <i>triangle</i>                                                 |     |

|            | <i>markers</i> . (a) The original signal with an SNR of 25.7 dB.                                                                                                           |     |

|            | (b) and (c) are synthesized testing signal with added white                                                                                                                |     |

|            | noise and artifacts, the SNR is 20 dB and 15 dB, respectively                                                                                                              | 91  |

| Fig. 3.26  | A cluster analysis of the action potentials from two neurons.                                                                                                              | 71  |

| 1 15. 5.20 | (a) Normalized maximum and minimum amplitudes are                                                                                                                          |     |

|            | calculated and used as two features for the analysis. (b) The                                                                                                              |     |

|            | action potentials are labeled with different colors according                                                                                                              |     |

|            | to the classification results                                                                                                                                              | 92  |

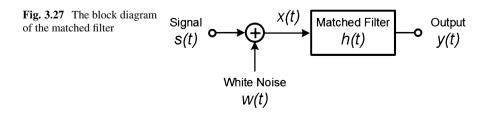

| Fig. 3.27  | The block diagram of the matched filter                                                                                                                                    | 93  |

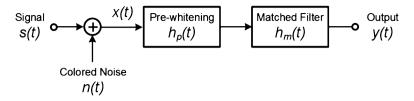

| Fig. 3.28  | The block diagram of the matched filter in combination with                                                                                                                |     |

|            | the pre-whitening filter for the correlation optimization                                                                                                                  | 95  |

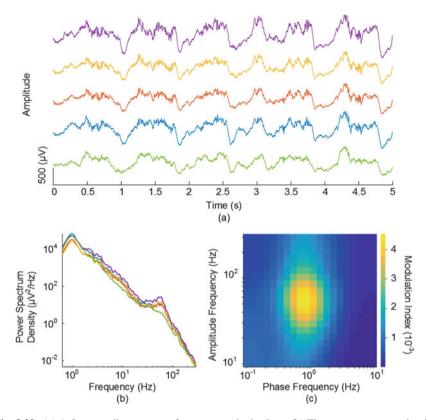

| Fig. 3.29  | (a) A 5-s recording segment from an anesthetized rat. (b)                                                                                                                  |     |

|            | The power spectrum density of the recording. (c) The                                                                                                                       |     |

|            | phase-amplitude coupling analysis of the signal                                                                                                                            | 96  |

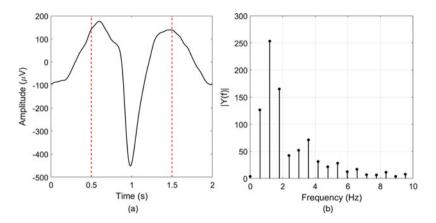

| Fig. 3.30  | (a) The neural feature waveform (template). The waveform                                                                                                                   |     |

|            | has more time in the "up-state" than the "down-state," so it                                                                                                               |     |

|            | is not a single frequency sinusoid wave. (b) The frequency                                                                                                                 |     |

|            | analysis of the neural feature template                                                                                                                                    | 97  |

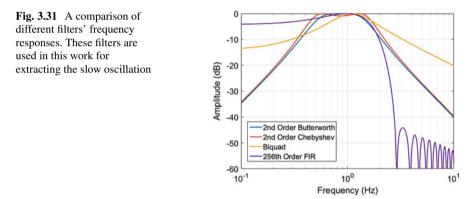

| Fig. 3.31  | A comparison of different filters' frequency responses.                                                                                                                    |     |

|            | These filters are used in this work for extracting the slow                                                                                                                | 07  |

| Eta 2.22   | oscillation                                                                                                                                                                | 97  |

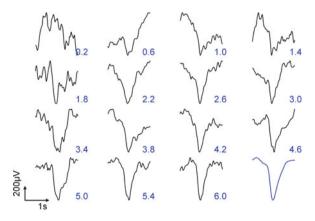

| Fig. 3.32  | Examples of the synthesized test signals with SNR ranging                                                                                                                  | 0.0 |

|            | from 0.2 to 6. The last one is the template                                                                                                                                | 98  |

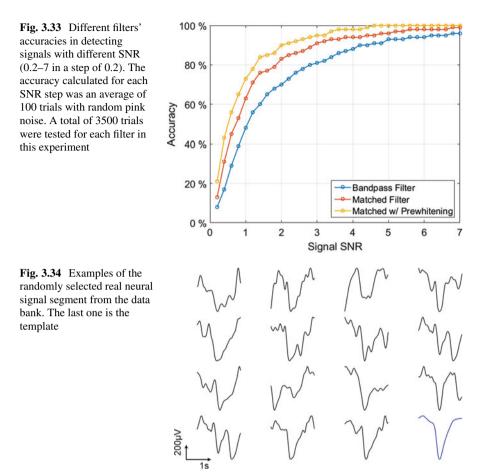

| Fig. 3.33 | Different filters' accuracies in detecting signals with different SNR (0.2–7 in a step of 0.2). The accuracy calculated for each SNR step was an average of 100 trials |     |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|           | with random pink noise. A total of 3500 trials were tested                                                                                                             |     |

|           | for each filter in this experiment                                                                                                                                     | 99  |

| Fig. 3.34 | Examples of the randomly selected real neural signal                                                                                                                   | ,,, |

| 119.0.01  | segment from the data bank. The last one is the template                                                                                                               | 99  |

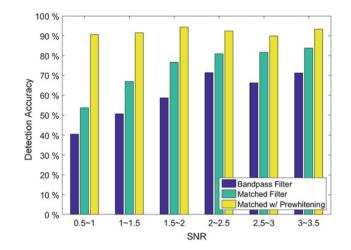

| Fig. 3.35 | Accuracies of different filters in detecting 100 signal                                                                                                                | //  |

| 119.0.00  | segments from randomly generated pink noise. A total of                                                                                                                |     |

|           | 10,000 trials were tested for each filter in this experiment.                                                                                                          |     |

|           | The detection result shows that the pre-whitening filter                                                                                                               |     |

|           | improves the matched filter's performance, especially in low                                                                                                           |     |

|           | SNR cases                                                                                                                                                              | 100 |

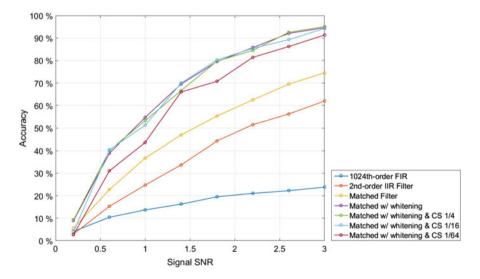

| Fig. 3.36 | Comparison of different filters' detection accuracies. The                                                                                                             | 100 |

| 119. 5.50 | experimental results show that the matched filter with                                                                                                                 |     |

|           | pre-whitening has the best performance. The compressive                                                                                                                |     |

|           | matched filter with pre-whitening and a compression ratio                                                                                                              |     |

|           | of $64 \times$ still has a better performance than the matched filter                                                                                                  |     |

|           | without pre-whitening                                                                                                                                                  | 101 |

|           |                                                                                                                                                                        | 101 |

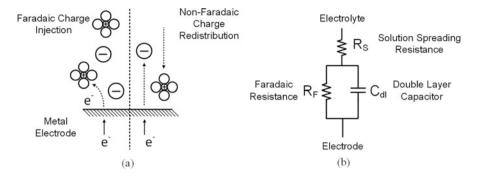

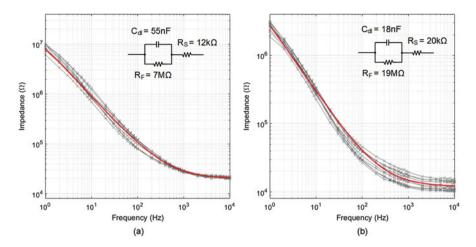

| Fig. 4.1  | Illustration of the electrode and electrolyte interface. (a)                                                                                                           |     |

|           | The physical representation, and ( <b>b</b> ) a simplified electrical                                                                                                  |     |

|           | circuit model                                                                                                                                                          | 105 |

| Fig. 4.2  | The measured impedances of two types of custom-made                                                                                                                    |     |

|           | tungsten electrodes. (a) and (b) shows the electrode with                                                                                                              |     |

|           | a diameter of 75 $\mu$ m and 50 $\mu$ m, respectively. Each figure                                                                                                     |     |

|           | shows an overlay of the measurements of ten electrodes in                                                                                                              |     |

|           | gray, and a fitting curve in red. The parameters of the fitting                                                                                                        |     |

|           | models are given                                                                                                                                                       | 106 |

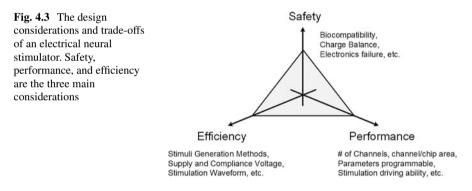

| Fig. 4.3  | The design considerations and trade-offs of an electrical                                                                                                              |     |

|           | neural stimulator. Safety, performance, and efficiency are                                                                                                             |     |

|           | the three main considerations                                                                                                                                          | 106 |

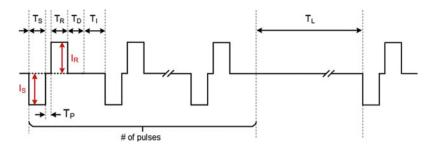

| Fig. 4.4  | Illustration of a typical biphasic stimulation waveform with                                                                                                           |     |

|           | the parameters marked. $I_S$ : stimulation current, $I_R$ : reversal                                                                                                   |     |

|           | current, $T_S$ : stimulation phase time, $T_R$ : reversal phase time,                                                                                                  |     |

|           | $T_D$ : discharging phase time, $T_P$ : phase interval, $T_I$ : pulse                                                                                                  |     |

|           | interval, <i>T<sub>L</sub></i> : pulse group interval                                                                                                                  | 109 |

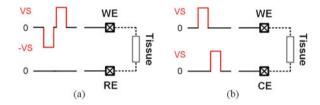

| Fig. 4.5  | Illustration of (a) monopolar and (b) bipolar stimulation                                                                                                              |     |

|           | methods. A voltage-regulated stimulation is used for                                                                                                                   |     |

|           | illustration, but a current-regulated stimulation can be                                                                                                               |     |

|           | applied in the same way                                                                                                                                                | 109 |

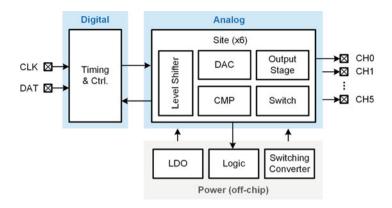

| Fig. 4.6  | The block diagram of the neural stimulator. The stimulator                                                                                                             |     |

|           | consists of an analog part and a digital part. The stimulator                                                                                                          |     |

|           | integrates four independent driving sites, and each site                                                                                                               |     |

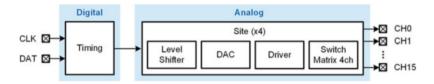

|           | demultiplexes to four channels                                                                                                                                         | 113 |

|           |                                                                                                                                                                        |     |

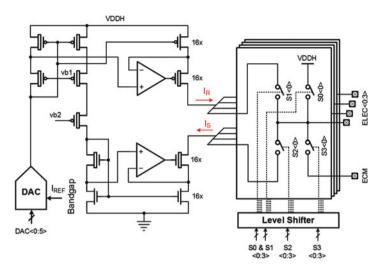

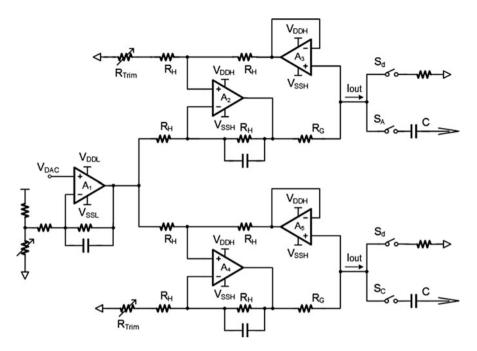

| Fig. 4.7      | The circuit schematic of the proposed multi-mode stimulator<br>site. Each site consists of: (1) a current-mode DAC which |     |

|---------------|--------------------------------------------------------------------------------------------------------------------------|-----|

|               | generates a reference for the output current, (2) a current                                                              |     |

|               | driver including current sink and source output stages with                                                              |     |

|               | high output impedance, and (3) high voltage switches with                                                                |     |

|               | level-shifters. Each site demultiplexes to four channels, and                                                            |     |

|               | provides near-simultaneous stimulation                                                                                   | 114 |

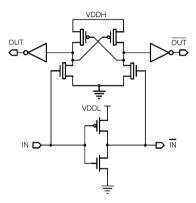

| Fig. 4.8      | The circuit schematic of the level shifter                                                                               | 114 |

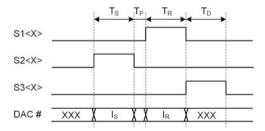

| Fig. 4.9      | The timing for generating a monopolar stimulation at the                                                                 |     |

| C             | electrode X. The DAC # and the electrode X locate in                                                                     |     |

|               | the same driving site ( $I_S$ : stimulation current, $I_R$ : reversal                                                    |     |

|               | current, $T_S$ : stimulation phase time, $T_R$ : reversal phase time,                                                    |     |

|               | $T_D$ : discharging phase time, $T_P$ : phase interval. The DAC                                                          |     |

|               | can be any value in the XXX state)                                                                                       | 115 |

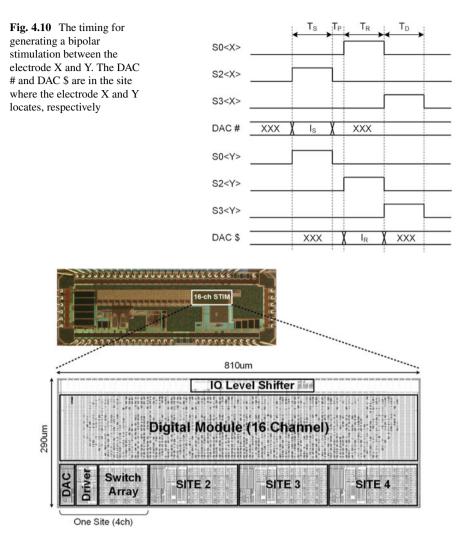

| Fig. 4.10     | The timing for generating a bipolar stimulation between the electrode X and Y. The DAC # and DAC \$ are in the site      |     |

|               | where the electrode X and Y locates, respectively                                                                        | 116 |

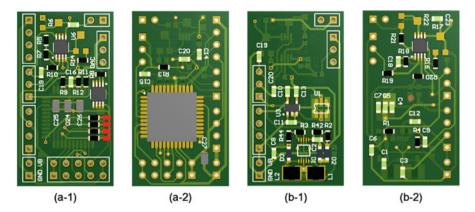

| Fig. 4.11     | The microphotograph and the layout of the neural stimulator.                                                             | 110 |

| 115. 1.11     | The major building blocks are highlighted in the layout                                                                  | 116 |

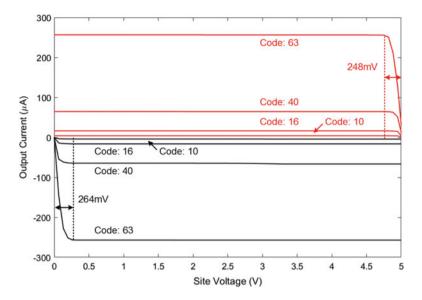

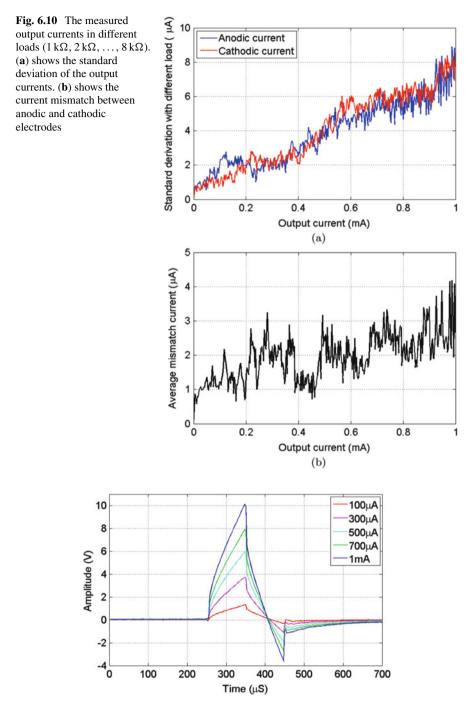

| Fig. 4.12     | The measured stimulator output current versus output                                                                     | 110 |

| 115. 4.12     | voltage                                                                                                                  | 117 |

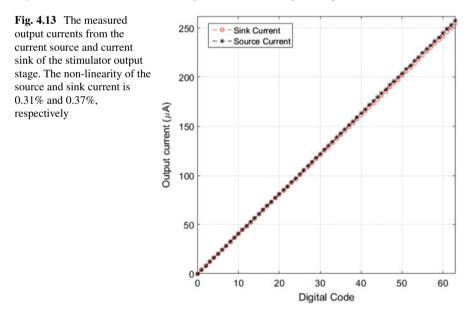

| Fig. 4.13     | The measured output currents from the current source and                                                                 | 11/ |

| 115. 4.15     | current sink of the stimulator output stage. The non-linearity                                                           |     |

|               | of the source and sink current is 0.31% and 0.37%, respectively                                                          | 117 |

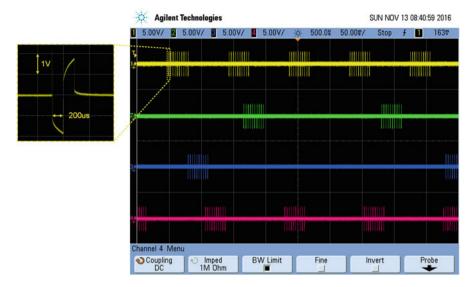

| Fig. 4.14     | The measured simultaneous stimulation output from four                                                                   | 11/ |

| 1'lg. 4.14    | independent channels. The boxed window shows the                                                                         |     |

|               | measurement of a single pulse in high resolution                                                                         | 118 |

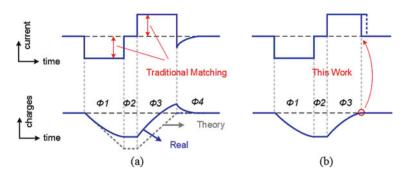

| Fig. 4.15     | (a) The traditional charge-balancing method matches the                                                                  | 110 |

| 11g. 4.15     | stimulation and reversal currents. The ideal charge curve on                                                             |     |

|               | the electrode is plotted in a <i>dashed line</i> . The practical charge                                                  |     |

|               |                                                                                                                          |     |

|               | curve deviates from the ideal curve due to the irreversible                                                              |     |

|               | reaction and the chemical products diffusion. (b) This work                                                              |     |

|               | terminates the reversal phase based on the monitoring the                                                                |     |

|               | net-zero charge crossing point. $\phi$ 1: stimulating phase, $\phi$ 2:                                                   | 120 |

| <b>F</b> 4.16 | interval phase, $\phi$ 3: reversal phase, $\phi$ 4: discharge phase                                                      | 120 |

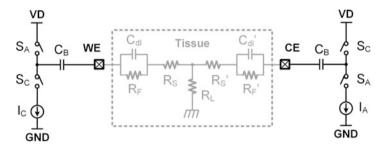

| Fig. 4.16     | The model for simulating the effects of non-ideal charge                                                                 | 100 |

|               | diffusion                                                                                                                | 120 |

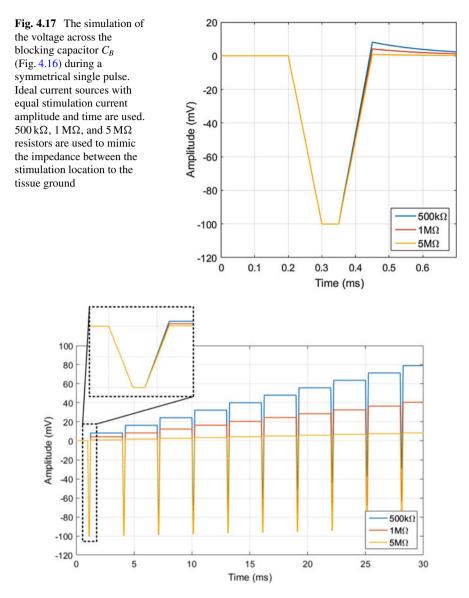

| Fig. 4.17     | The simulation of the voltage across the blocking capacitor                                                              |     |

|               | $C_B$ (Fig. 4.16) during a symmetrical single pulse. Ideal                                                               |     |

|               | current sources with equal stimulation current amplitude and                                                             |     |

|               | time are used. $500 \text{ k}\Omega$ , $1 \text{ M}\Omega$ , and $5 \text{ M}\Omega$ resistors are used                  |     |

|               | to mimic the impedance between the stimulation location to                                                               |     |

|               | the tissue ground                                                                                                        | 121 |

| Fig. 4.18  | The simulation of the voltage across the blocking capacitor                    |     |

|------------|--------------------------------------------------------------------------------|-----|

|            | of a stimulation pulse train without discharging. $500 \mathrm{k}\Omega$ ,     |     |

|            | 1 M $\Omega$ , and 5 M $\Omega$ resistors are used to mimic the impedance      |     |

|            | between the stimulation location to the tissue ground. The                     |     |

|            | charges build up even using the ideal current sources with                     |     |

|            | equal amplitude and pulse width                                                | 121 |

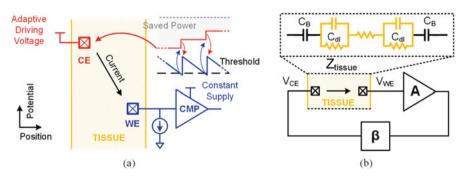

| Fig. 4.19  | Illustration of the adaptive driving voltage stimulation                       | 122 |

| Fig. 4.20  | The channel configuration of $(\mathbf{a})$ the traditional stimulation,       |     |

|            | and ( <b>b</b> ) the proposed work. Arbitrary channel configuration            |     |

|            | is feasible in the proposed work without pre-calibration                       | 123 |

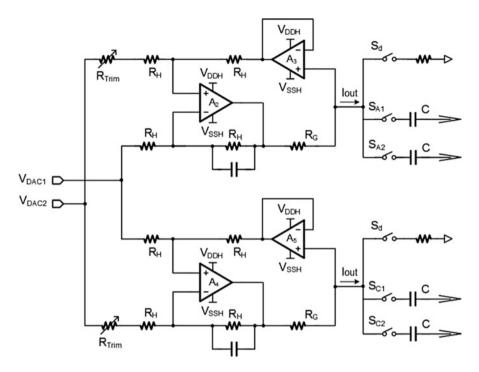

| Fig. 4.21  | The block diagram of the net-zero charge neural stimulation                    |     |

| U U        | system. The system consists of an analog core, a digital                       |     |

|            | module, and off-chip power management units                                    | 124 |

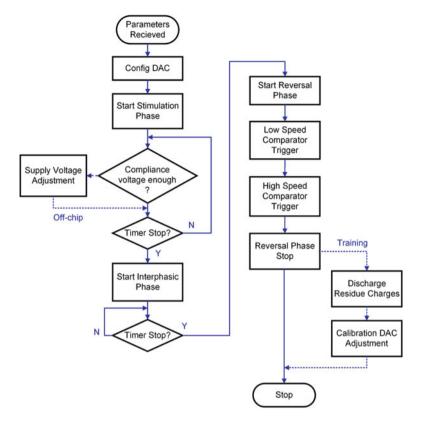

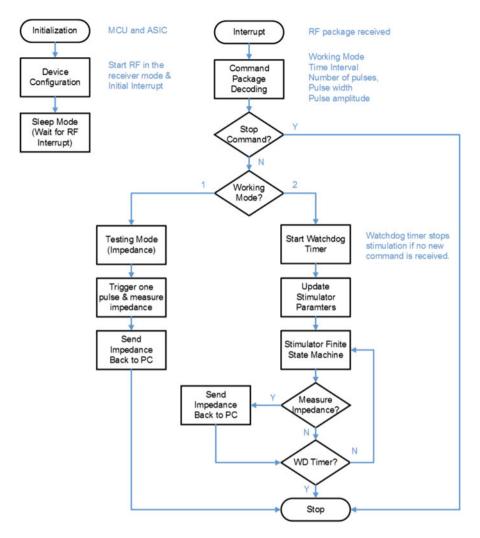

| Fig. 4.22  | The working flow chart of the proposed stimulation strategy                    | 125 |

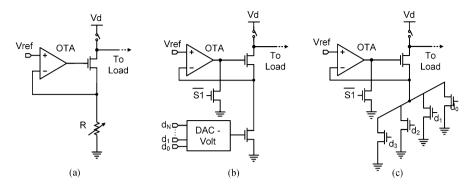

| Fig. 4.23  | Circuit schematic of ( <b>a</b> ) basic current generator, ( <b>b</b> ) output |     |

| 0          | stage with voltage-controlled transistor, modified from                        |     |

|            | [271], (c) output stage with digital-set DAC, modified from [256]              | 126 |

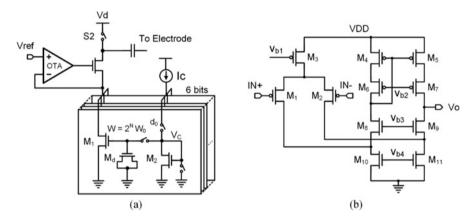

| Fig. 4.24  | (a) The proposed output stage with current set current-mode                    |     |

| 0          | DAC. (b) The OTA used in the work                                              | 126 |

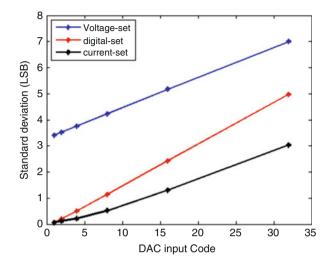

| Fig. 4.25  | 100 runs Monte-Carlo simulation of the different output                        |     |

| 0          | stage architectures with mismatch and process variation                        | 128 |

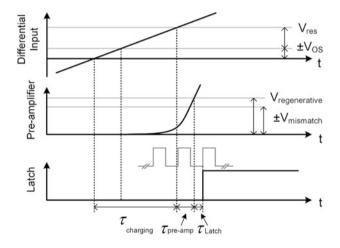

| Fig. 4.26  | Analysis of the comparator delay for determining the                           |     |

|            | zero-crossing point of the blocking capacitor                                  | 128 |

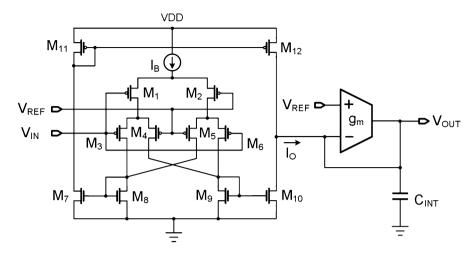

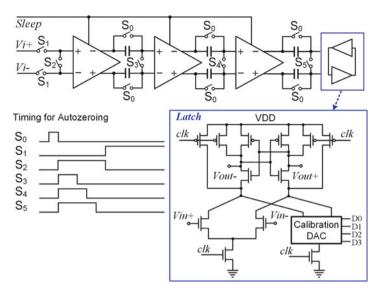

| Fig. 4.27  | The circuit schematic of the comparator consisting of a                        | 120 |

|            | three-stage pre-amplifier and latch. The pre-amplifier has                     |     |

|            | auto-zero calibration, and the latch has a 4-bit DAC for                       |     |

|            | calibration                                                                    | 129 |

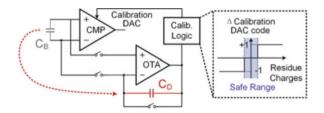

| Fig. 4.28  | The circuit schematic of the switched capacitor circuit used                   |     |

|            | to discharge the blocking capacitor. The circuit is also used                  |     |

|            | to amplify the residue voltage for the calibration purpose.                    |     |

|            | The amplified residue voltage is compared with two                             |     |

|            | pre-defined safe voltage window. If the residue charge is out                  |     |

|            | of the safe window, the calibration DAC of the comparator                      |     |

|            | will be changed accordingly                                                    | 130 |

| Fig. 4.29  | The micrograph of the fabricated stimulator chip. The                          | 100 |

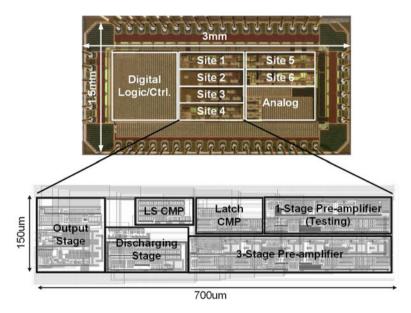

| 118        | occupied silicon area is $3 \times 1.5 \text{ mm}^2$                           | 130 |

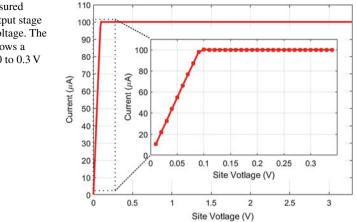

| Fig. 4.30  | The measured current from the output stage versus the                          | 100 |

| 1 ig. 1.50 | output voltage. The embedded figure shows a zoom-in plot                       |     |

|            | from 0 to 0.3 V                                                                | 131 |

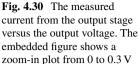

| Fig. 4.31  | The measured generated stimulation waveforms with a                            | 101 |

| 1.6. 1.51  | high impedance load. Channel 1 and channel 2 measure                           |     |

|            | the output of the WE and CE, respectively. The Math                            |     |

|            | channel calculates the difference between the two channels.                    |     |

|            | Channels D3–D6 show the states of the digital module                           | 132 |

|            | Chamiers DJ-DO show the states of the digital module                           | 132 |

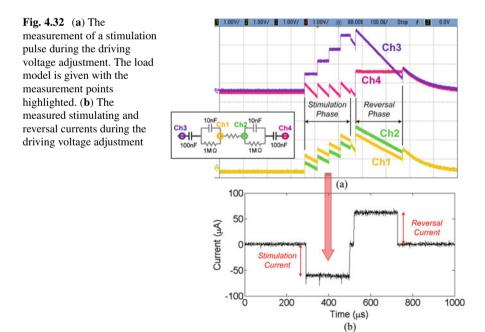

| Fig. 4.32 | <ul> <li>(a) The measurement of a stimulation pulse during the driving voltage adjustment. The load model is given with the measurement points highlighted. (b) The measured stimulating and reversal currents during the driving voltage adjustment</li> </ul>                                                                                                                           | 132        |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

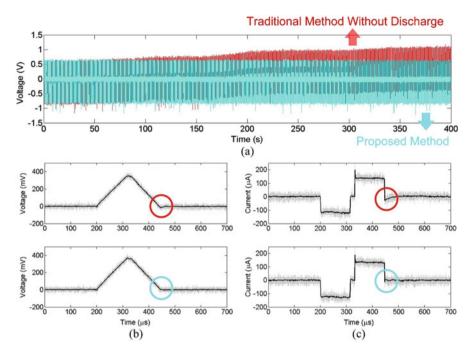

| Fig. 4.33 | The measurement of biphasic stimulation in the saline<br>solution using the traditional method ( <i>red</i> ) and the proposed<br>method ( <i>blue</i> ). ( <b>a</b> ) shows a 5-min continuous stimulation<br>without discharge. ( <b>b</b> ) and ( <b>c</b> ) show an overlay of 20<br>measurements of the voltage across the blocking capacitor<br>and the derived stimulation current | 133        |

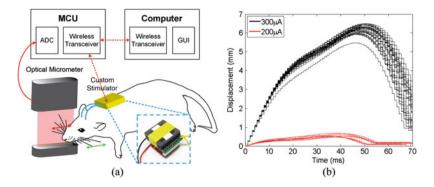

| Fig. 4.34 | In vivo experiment performed on a sedated rat. ( <b>a</b> ) Whisker<br>movements, as measured by an optical micrometer, were<br>reliably evoked by stimulation. ( <b>b</b> ) Whisker displacements<br>were a function of current intensity                                                                                                                                                | 134        |

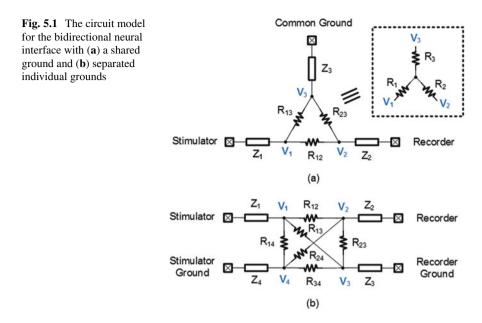

| Fig. 5.1  | The circuit model for the bidirectional neural interface with (a) a shared ground and (b) separated individual grounds                                                                                                                                                                                                                                                                    | 141        |

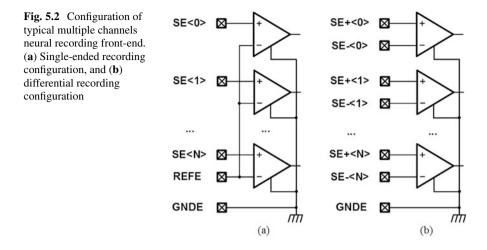

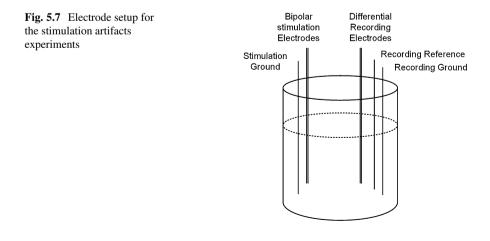

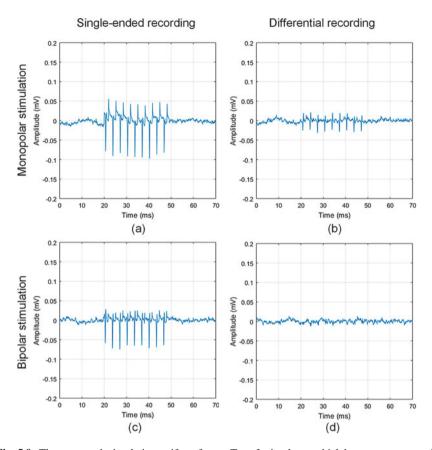

| Fig. 5.2  | Configuration of typical multiple channels neural recording<br>front-end. (a) Single-ended recording configuration, and (b)<br>differential recording configuration                                                                                                                                                                                                                       | 143        |

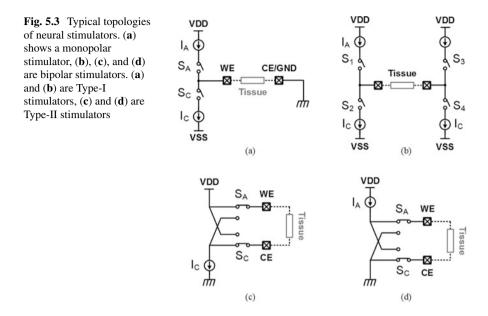

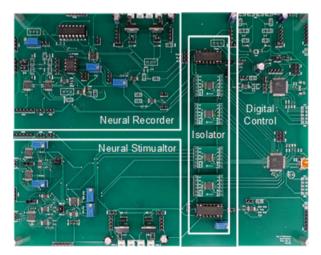

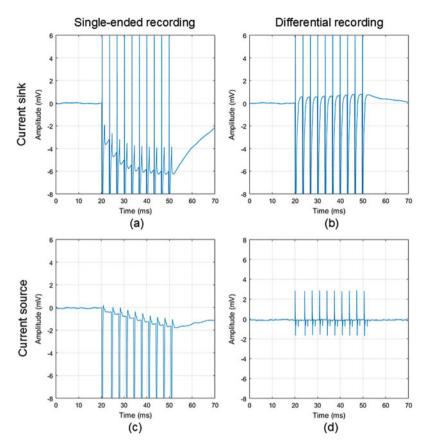

| Fig. 5.3  | Typical topologies of neural stimulators. ( <b>a</b> ) shows<br>a monopolar stimulator, ( <b>b</b> ), ( <b>c</b> ), and ( <b>d</b> ) are bipolar<br>stimulators. ( <b>a</b> ) and ( <b>b</b> ) are Type-I stimulators, ( <b>c</b> ) and ( <b>d</b> )<br>are Type-II stimulators                                                                                                           | 144        |

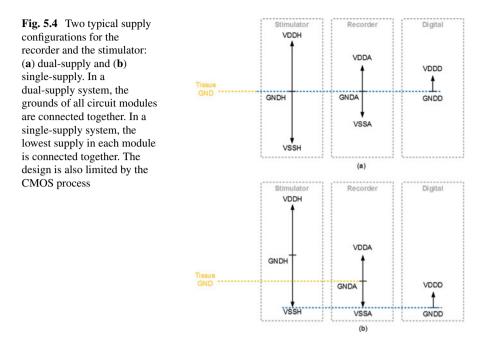

| Fig. 5.4  | Two typical supply configurations for the recorder and<br>the stimulator: (a) dual-supply and (b) single-supply. In a<br>dual-supply system, the grounds of all circuit modules are<br>connected together. In a single-supply system, the lowest<br>supply in each module is connected together. The design is                                                                            |            |

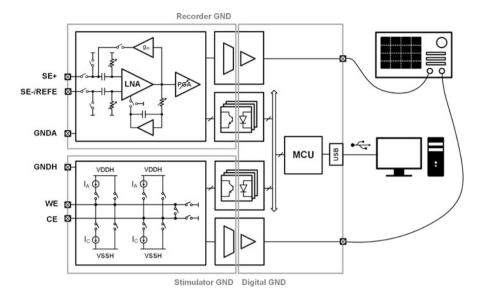

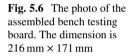

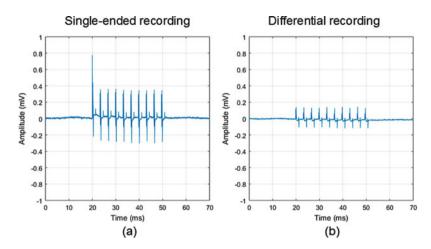

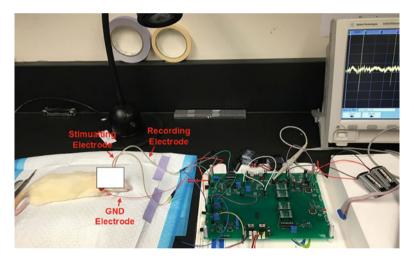

| Fig. 5.5  | also limited by the CMOS process<br>The block diagram of the bench testing board. The supplies<br>and grounds for the recorder, the stimulator, and the digital<br>modules are intentionally separated on the board                                                                                                                                                                       | 145<br>146 |

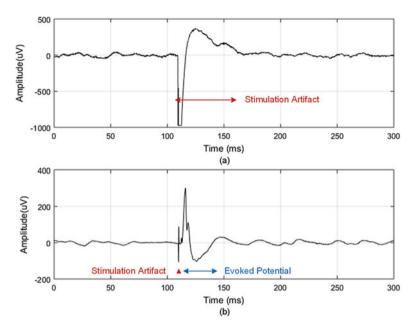

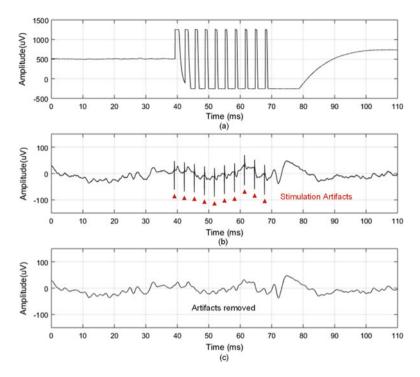

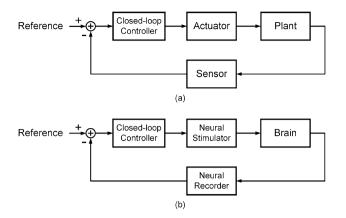

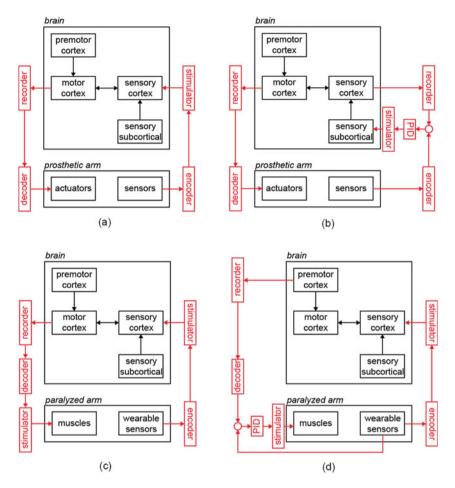

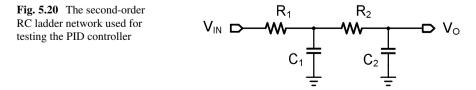

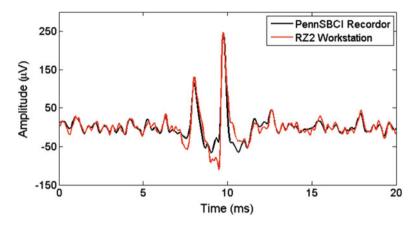

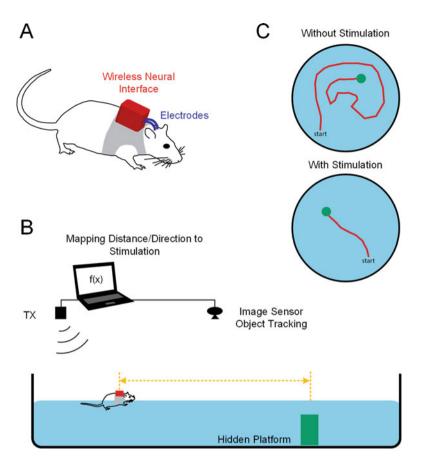

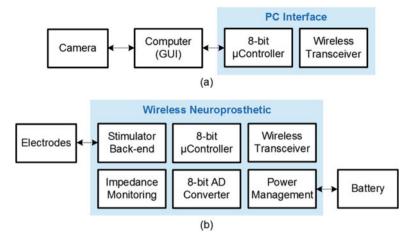

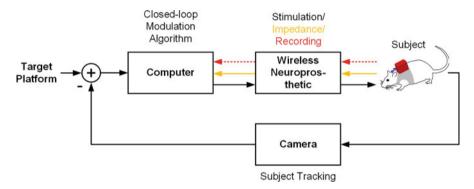

| Fig. 5.6  | The photo of the assembled bench testing board. The dimension is $216 \text{ mm} \times 171 \text{ mm}$                                                                                                                                                                                                                                                                                   | 146        |