NanoScience and Technology

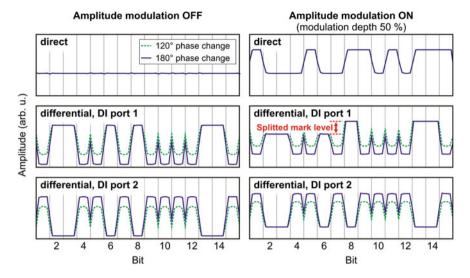

# Gadi Eisenstein Dieter Bimberg *Editors*

# Green Photonics and Electronics

# NanoScience and Technology

#### Series editors

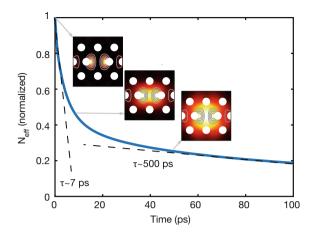

Phaedon Avouris, Yorktown Heights, USA Bharat Bhushan, Columbus, USA Dieter Bimberg, Berlin, Germany Cun-Zheng Ning, Tempe, USA Klaus von Klitzing, Stuttgart, Germany Roland Wiesendanger, Hamburg, Germany The series NanoScience and Technology is focused on the fascinating nano-world, mesoscopic physics, analysis with atomic resolution, nano and quantum-effect devices, nanomechanics and atomic-scale processes. All the basic aspects and technology-oriented developments in this emerging discipline are covered by comprehensive and timely books. The series constitutes a survey of the relevant special topics, which are presented by leading experts in the field. These books will appeal to researchers, engineers, and advanced students.

More information about this series at http://www.springer.com/series/3705

Gadi Eisenstein · Dieter Bimberg Editors

# Green Photonics and Electronics

Editors Gadi Eisenstein Departmenmt of Electriocal Engineeering and Russell Berrie Nanotechnology Institute Technion – Israel Institute of Technology Haifa Israel

Dieter Bimberg Center of NanoPhotonics Technical University of Berlin Berlin Germany

ISSN 1434-4904 NanoScience and Technology ISBN 978-3-319-67001-0 DOI 10.1007/978-3-319-67002-7 ISSN 2197-7127 (electronic) ISBN 978-3-319-67002-7 (eBook)

Library of Congress Control Number: 2017951174

#### © Springer International Publishing AG 2017

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by Springer Nature The registered company is Springer International Publishing AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

### Preface

The energy consumption associated with the Internet has become a major concern of the scientific and technological communities, the economic and political establishment as well as the media and the public at large. The vast increase in the Internet usage, driven by a continuous introduction of new applications, integration and reliance of public services and an increase in the number of users worldwide brought upon a situation where the ability of modern society to supply the required energy for the predicted consumption associated with future computing and communication came into question. While several apocalyptic predictions published in the early years of the third millennium will definitely not materialize, the problem is real and requires a solutions to which the technological community must dedicate itself.

Achieving an energy-efficient Internet requires a multi-facet solution that addresses all aspects of the complex data network. An important part of the solution will involve photonic devices and systems. The photonics technologies have traditionally not emphasized sufficiently energy issues but once it became clear that efficiency is paramount, large efforts aiming at reducing the power required by photonic devices, mainly lasers, have started. A new field called *Green Photonics* has emerged and quickly became popular.

However, photonic devices are driven by and feed electronic circuits, which are often energy inefficient and hence have to also be improved. Above and beyond this, the energy consumption is affected by the complete computing and communication systems. It is obvious, therefore, that what is needed are not photonic devices and systems that are *Green* but rather, the technological community should seek to develop a *Green Internet* where each part is as energy efficient as possible.

The development of a *Green Internet* requires a dialog and collaborations between experts of many fields including photonics, VLSI circuit design, computer architecture, networks, switching and information sciences. An additional aspect of the *Green Internet* is the use of renewable energy sources whenever possible.

The significance of holding this multidisciplinary dialog was recognized by the directors of the Russell Berrie Nanotechnology Institute at Technion – Israel Institute of Technology and the Center for Nano Photonics at the Technical

University of Berlin who joined forces and established a series of three annual *Green Photonics* symposia held alternatively in Haifa and Berlin between 2014 and 2016. These symposia which were funded by the Reinhart Frank Foundation brought together world famous experts in all fields related to the *Green Internet*. This book summarizes the three *Green Photonics* symposia highlighting the most important topics that were covered.

Optoelectronic semiconductor devices are addressed extensively. Energyefficient VCSELs for the common 850 nm range as well as for 1550 nm are covered in two separate Chaps. 1 and 2, respectively. The advantages of quantum dots are highlighted in two chapters one, Chap. 3 dealing with optical amplifiers and the second, Chap. 4 with mode-locked lasers. Low-energy fast switching is described in Chap. 5 which addresses nonlinear photonic crystal waveguides. The electronic aspects of a *Green Internet* is covered in a few chapters. Low-energy logic design is presented in Chap. 6, while power management in the so-called Network on Chip devices is presented in Chap. 7. The higher level system aspects cover the topics of optimization of large interconnect networks is addressed in Chap. 8. Finally, we include two chapters that deal with renewable energy sources; Chap. 9 is an extensive survey of the global impact of photovoltaics and Chap. 10 deals with futuristic solar cells based on thin film organic semiconductors.

The diverse issues covered by the 10 chapters of the book highlight the need for an extensive multidisciplinary dialog and for collaborations between experts from different fields. This joint effort is needed to ensure a future *Green Internet*, which will enable all the applications needed by the modern society at an energy cost that is affordable.

Haifa, Israel Berlin, Germany Gadi Eisenstein Dieter Bimberg

# Contents

| 1 | Energy-Efficient Vertical-Cavity Surface-Emitting Lasers |                                              |    |  |  |

|---|----------------------------------------------------------|----------------------------------------------|----|--|--|

|   | for (                                                    | Optical Interconnects                        | 1  |  |  |

|   |                                                          | ip Moser, James A. Lott and Dieter Bimberg   |    |  |  |

|   | 1.1                                                      | VCSEL Energy Efficiency                      | 1  |  |  |

|   | 1.2                                                      | Energy Efficiency Figures of Merit.          | 2  |  |  |

|   | 1.3                                                      | Resonance Frequency and Modulation Bandwidth | 4  |  |  |

|   | 1.4                                                      | Energy Efficiency Analysis                   | 7  |  |  |

|   | 1.5                                                      | Energy Efficient Data Transmission Results   | 10 |  |  |

|   | 1.6                                                      | Summary                                      | 13 |  |  |

|   | Refe                                                     | erences                                      | 14 |  |  |

| 2 | Hiol                                                     | h-Speed InP-Based Long-Wavelength VCSELs     | 17 |  |  |

| 4 | Silvia Spiga and Markus C. Amann                         |                                              |    |  |  |

|   |                                                          | InP-Based VCSELs                             | 18 |  |  |

|   | 2.1                                                      | 2.1.1     Active Region                      | 18 |  |  |

|   |                                                          | 2.1.2 Hybrid-Cavity Concepts                 | 19 |  |  |

|   |                                                          | 2.1.2     Tunnel-Junction Laser.             | 22 |  |  |

|   | 2.2                                                      |                                              | 23 |  |  |

|   |                                                          | 2.2.1 Hybrid Dielectric-Semiconductor VCSELs | 24 |  |  |

|   |                                                          | 2.2.2 Stationary Characteristics             | 25 |  |  |

|   |                                                          | 2.2.3 Dynamic Characteristics                | 28 |  |  |

|   | 2.3                                                      | VCSEL Arrays and Advanced Modulation Formats | 29 |  |  |

|   |                                                          | 2.3.1 Data Communication.                    | 29 |  |  |

|   |                                                          | 2.3.2 Telecommunication                      | 31 |  |  |

|   | 2.4                                                      | Conclusion                                   | 32 |  |  |

|   | Refe                                                     | erences.                                     | 33 |  |  |

| 3 | Quantum-Dot Semiconductor Optical Amplifiers for |                                                                    |     |

|---|--------------------------------------------------|--------------------------------------------------------------------|-----|

|   |                                                  | rgy-Efficient Optical Communication.                               | 37  |

|   | -                                                | ger Schmeckebier and Dieter Bimberg                                |     |

|   | 3.1                                              | Introduction                                                       | 38  |

|   | 3.2                                              | Basics of Quantum-Dot Semiconductor Optical Amplifiers             | 40  |

|   |                                                  | 3.2.1 Parameters of SOAs                                           | 40  |

|   |                                                  | 3.2.2 Dynamics of Conventional and QD SOAs                         | 42  |

|   |                                                  | 3.2.3 Design and Static Characteristics of QD SOAs                 | 44  |

|   |                                                  | 3.2.4 QD SOA Sample Series                                         | 45  |

|   | 3.3                                              | Phase Modulation of QD SOAs                                        | 46  |

|   |                                                  | 3.3.1 Introduction of the Concept.                                 | 46  |

|   |                                                  | 3.3.2 Prove of the Concept                                         | 47  |

|   | 3.4                                              | Concept of Dual-Communication-Band Amplifiers                      | 51  |

|   |                                                  | 3.4.1 Introduction of the Concept.                                 | 51  |

|   |                                                  | 3.4.2 Proof of Concept.                                            | 52  |

|   | 3.5                                              | Signal Processing—Wavelength Conversion                            | 56  |

|   |                                                  | 3.5.1 Non-linearities of SOA Gain Media                            | 57  |

|   |                                                  | 3.5.2 Four-Wave Mixing in QD SOAs                                  | 58  |

|   |                                                  | 3.5.3 Optimization of Static Four-Wave Mixing in QD SOAs           | 61  |

|   |                                                  | 3.5.4 FWM of D(Q)PSK Signals                                       | 64  |

|   | 3.6                                              | Summary                                                            | 68  |

|   |                                                  | prences.                                                           | 68  |

| 4 | Oua                                              | ntum-Dot Mode-Locked Lasers: Sources for Tunable Optical           |     |

|   |                                                  | Electrical Pulse Combs                                             | 75  |

|   |                                                  | n Arsenijević and Dieter Bimberg                                   |     |

|   | 4.1                                              | Quantum-Dot Mode-Locked Lasers                                     | 75  |

|   |                                                  | 4.1.1 Device Structures                                            | 76  |

|   |                                                  | 4.1.2 Passive Mode-Locking                                         | 77  |

|   | 4.2                                              | Jitter Reduction and Frequency Tuning                              | 79  |

|   |                                                  | 4.2.1 Hybrid Mode-Locking.                                         | 81  |

|   |                                                  | 4.2.2 Optical Injection                                            | 84  |

|   |                                                  | 4.2.3 Optical Self-Feedback                                        | 86  |

|   | 4.3                                              | Applications                                                       | 91  |

|   | т.5                                              | 4.3.1 Millimeter-Wave-Signal Generation                            | 91  |

|   |                                                  | 4.3.2 Optical Communication                                        | 96  |

|   | 4.4                                              | Conclusion                                                         | 101 |

|   |                                                  | erences.                                                           | 101 |

| _ |                                                  |                                                                    | 101 |

| 5 |                                                  | ophotonic Approach to Energy-Efficient Ultra-Fast<br>Optical Gates | 107 |

|   |                                                  | gory Moille, Sylvain Combrié and Alfredo De Rossi                  | 107 |

|   | 5.1                                              | Introduction: A Case for All-Optical Signal Processing             | 107 |

|   | 5.1<br>5.2                                       | Integrated All-Optical Gate.                                       | 107 |

|   | 5.4                                              |                                                                    | 102 |

|   |      | 5.2.1   | Technologies for Integrated On-Chip All-Optical |     |

|---|------|---------|-------------------------------------------------|-----|

|   |      |         | Processing                                      | 109 |

|   |      | 5.2.2   | Energy-Efficient All-Optical Gates              | 111 |

|   |      | 5.2.3   | III–V Photonic Crystals Resonators.             | 113 |

|   | 5.3  |         | near Dynamics in PhC Resonators                 | 115 |

|   |      | 5.3.1   | Microwatt Nonlinear Response                    | 115 |

|   |      | 5.3.2   | Fast Optical Nonlinearities in Semiconductors   | 116 |

|   |      | 5.3.3   | Nonlocal Nonlinear Response of PhC Cavities     | 118 |

|   | 5.4  |         | All-Optical Gate                                | 118 |

|   |      | 5.4.1   | Photon Molecule                                 | 121 |

|   |      | 5.4.2   | The Role of the Carrier Lifetime                | 121 |

|   |      | 5.4.3   | InP                                             | 123 |

|   |      | 5.4.4   | P-Doped InP                                     | 124 |

|   |      | 5.4.5   | Passivated GaAs                                 | 126 |

|   |      | 5.4.6   | Integration with Silicon Photonics              | 128 |

|   | 5.5  |         | cation Example: All-Optical Signal Sampling     | 129 |

|   |      | 5.5.1   | All-Optical Sampling.                           | 130 |

|   | 5.6  |         | usions                                          | 133 |

|   | Refe | rences. |                                                 | 133 |

| 6 | Alte | rnative | Logic Families for Energy-Efficient and High    |     |

|   |      |         | ce Chip Design                                  | 139 |

|   | Itam | ar Levi | and Alexander Fish                              |     |

|   | 6.1  | Introd  | uction                                          | 139 |

|   | 6.2  | Backg   | round                                           | 141 |

|   | 6.3  | DML     | Basics                                          | 155 |

|   | 6.4  |         | Utilization for Increased E-D Flexibility       | 158 |

|   | 6.5  | Summ    | ary                                             | 167 |

|   | Refe | rences. |                                                 | 167 |

| 7 | Secu | re Pov  | ver Management and Delivery Within Intelligent  |     |

| ' |      |         | works on-Chip                                   | 173 |

|   |      |         | Vaisband and Eby G. Friedman                    | 170 |

|   | 7.1  |         | Network on-Chip for Distributed Power Delivery  |     |

|   |      |         | lanagement                                      | 176 |

|   |      | 7.1.1   | Concept of Power Network-on-Chip                | 177 |

|   |      | 7.1.2   | Power Network-on-Chip Architecture              | 177 |

|   |      | 7.1.3   | Challenges in Distributed Power Delivery        | 180 |

|   | 7.2  | Power   | Routing in SoCs                                 | 181 |

|   |      | 7.2.1   | Power Routers.                                  | 181 |

|   |      | 7.2.2   | Locally Powered Loads.                          | 182 |

|   |      | 7.2.3   | Power Grid                                      | 182 |

|   |      | 7.2.4   | Case Study                                      | 183 |

|   | 7.3  |         | Distributed Power Delivery Systems              | 185 |

|   |      | 7.3.1 Experimental Evaluation of Stability Criterion         | 187   |  |

|---|------|--------------------------------------------------------------|-------|--|

|   | 7.4  | Secure Power Delivery and Management                         | 191   |  |

|   | 7.5  | Automated Design of Stable Power Delivery Systems            | 191   |  |

|   | 7.6  | Summary                                                      | 196   |  |

|   | Refe | erences                                                      | 198   |  |

| 8 |      | rgy Efficient System Architectures                           | 203   |  |

|   |      | noam Kolodny                                                 | • • • |  |

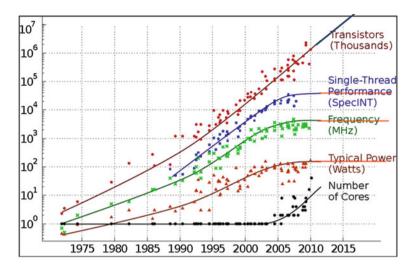

|   | 8.1  | Power Issues in Computing Systems                            | 203   |  |

|   | 8.2  | Characteristics of the Power Reduction Problem               | 204   |  |

|   |      | 8.2.1 The Disruption Principle                               | 204   |  |

|   |      | 8.2.2 The Locality Principle                                 | 205   |  |

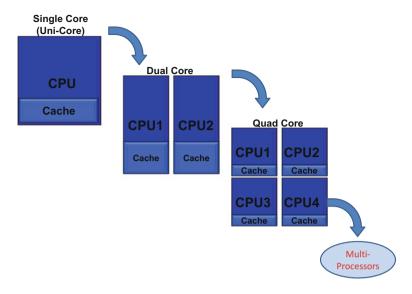

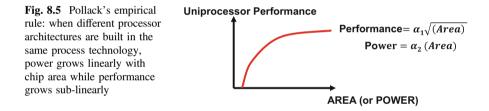

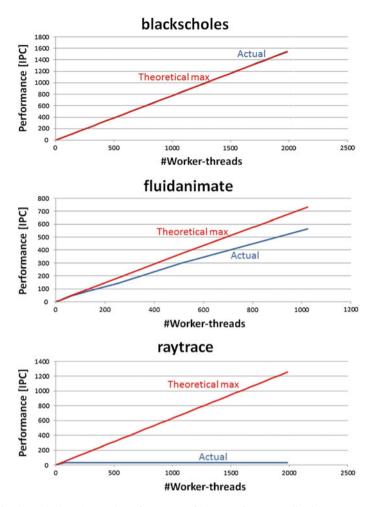

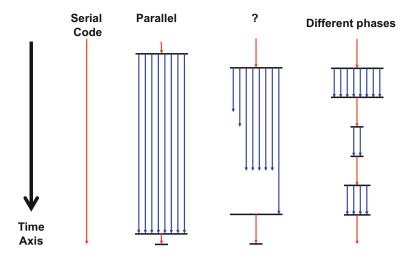

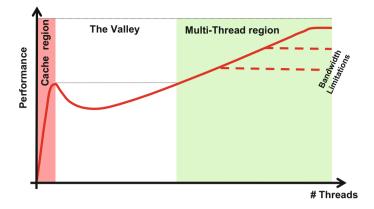

|   |      | 8.2.3 The Challenge of Parallelism                           | 208   |  |

|   |      | 8.2.4 A Unified Machine Model                                | 210   |  |

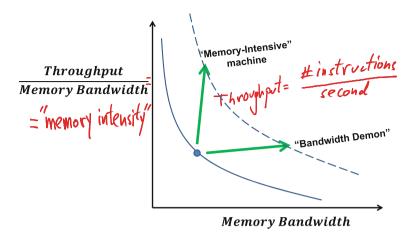

|   |      | 8.2.5 Memory Intensive Systems                               | 211   |  |

|   |      | 8.2.6 Applying the Principles in Large Data Center           | 010   |  |

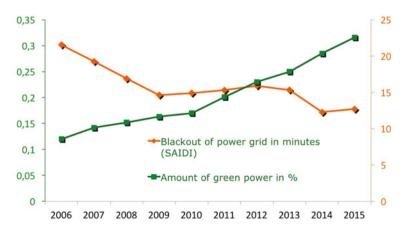

|   | ъć   | Computing                                                    | 213   |  |

|   | Refe | erences                                                      | 213   |  |

| 9 | Low  | 7-Cost Harvesting of Solar Energy: The Future of Global      |       |  |

|   |      | Photovoltaics                                                |       |  |

|   | Eick | e R. Weber, Stefan Glunz, HM. Henning, A. Palzer             |       |  |

|   | and  | R. Schindler                                                 |       |  |

|   | 9.1  | Introduction: The Needed Transformation of Our Energy        |       |  |

|   |      | System, Limited Fossil Fuels, the Climate Problem            | 215   |  |

|   | 9.2  | The Role of Photovoltaics in Our Future Energy System, Based |       |  |

|   |      | on Simulation of the German Energy System for 80% and More   |       |  |

|   |      | of Renewable Energy                                          | 219   |  |

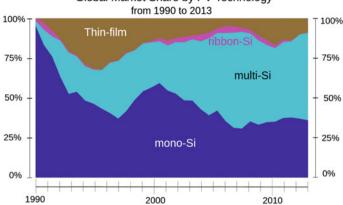

|   | 9.3  | Crystalline Silicon Photovoltaics.                           | 228   |  |

|   |      | 9.3.1 Al-Back Surface Field Technology                       | 230   |  |

|   |      | 9.3.2 Partial Rear Contact Technologies (PRC, PERC, PERL,    |       |  |

|   |      | PERT)                                                        | 230   |  |

|   |      | 9.3.3 Solar Cells on n-type Si                               | 233   |  |

|   |      | 9.3.4 Heterojunction Solar Cells.                            | 233   |  |

|   |      | 9.3.5 Crystalline Si PV Beyond the Shockley-Queisser Limit   | 235   |  |

|   | 9.4  | High-Concentration PV: CPV Technology                        | 236   |  |

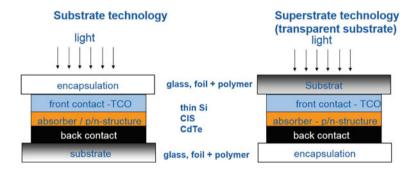

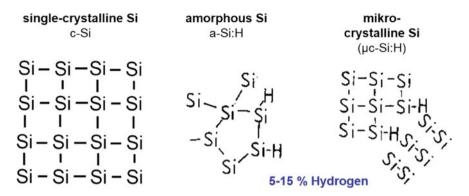

|   | 9.5  | Thin Film PV Technologies                                    | 245   |  |

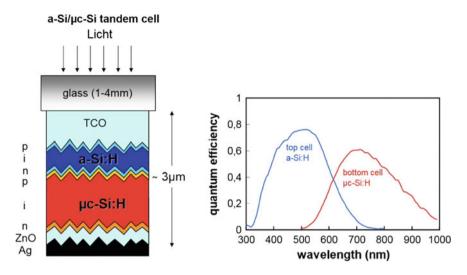

|   |      | 9.5.1 Thin Film Silicon Solar Cells                          | 247   |  |

|   |      | 9.5.2 Cupper Indium Diselenide (CIS) Solar Cells.            | 249   |  |

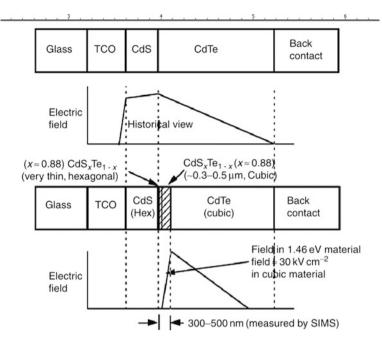

|   |      | 9.5.3 Cadmium Telluride Solar Cells                          | 250   |  |

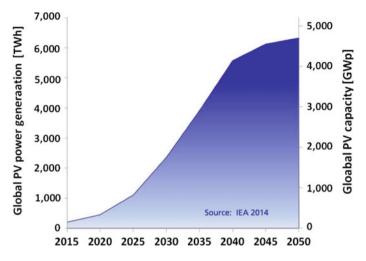

|   | 9.6  | The Future of PV: Further Market Development, PV Going into  |       |  |

|   | _    | the Terawatt Range                                           | 250   |  |

|   | Refe | erences                                                      | 255   |  |

| 10  | Novel Thin-Film Photovoltaics—Status and Perspectives<br>Benjamin Oesen, Sascha Ullbrich, Johannes Widmer and Karl Leo |     |

|-----|------------------------------------------------------------------------------------------------------------------------|-----|

|     |                                                                                                                        |     |

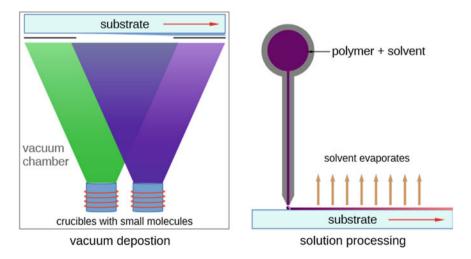

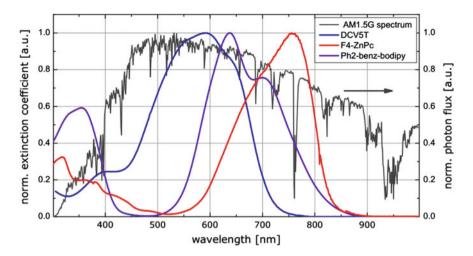

|     | 10.2 Organic Photovoltaics                                                                                             | 266 |

|     | 10.2.1 Basics of Organic Photovoltaics                                                                                 | 266 |

|     | 10.2.2 Thin Film Optics and Interference.                                                                              | 271 |

|     | 10.2.3 Morphology of the Blend Layer                                                                                   | 272 |

|     | 10.2.4 Optimized p-i-n Cells                                                                                           | 274 |

|     | 10.2.5 Tandem and Multi-junction Cells—Maximizing the                                                                  |     |

|     | Power Output                                                                                                           | 275 |

|     | 10.3 Perovskite Photovoltaics                                                                                          | 278 |

|     | 10.4 Application of Different Solar Cell Technologies                                                                  | 279 |

|     | 10.4.1 Application Scenarios                                                                                           | 279 |

|     | 10.4.2 Energy Harvesting Under Real Application Conditions                                                             | 281 |

|     | 10.5 Conclusion                                                                                                        | 285 |

|     | References                                                                                                             | 285 |

| Ind | ex                                                                                                                     | 289 |

### Contributors

Markus C. Amann Walter Schottky Institut, Technische Universität München, Munich, Germany

**Dejan Arsenijević** Department of Solid-State Physics, Technische Universität Berlin, Berlin, Germany

**Dieter Bimberg** Institut für Festkörperphysik, Technische Universität Berlin, Berlin, Germany; King Abdulaziz University Jeddah, Jeddah, Saudi Arabia

Sylvain Combrié Thales Research and Technology, Palaiseau, France

Alfredo De Rossi Thales Research and Technology, Palaiseau, France

Alexander Fish Faculty of Engineering Bldg, Bar-Ilan University, Ramat-Gan, Israel

**Eby G. Friedman** Department of Electrical and Computer Engineering, University of Illinois at Chicago, Chicago, IL, USA

S. Glunz ISE Fraunhofer Institute, Freiburg, Germany

H. -M. Henning ISE Fraunhofer Institute, Freiburg, Germany

Avinoam Kolodny Electrical Engineering department, Technion, Haifa, Israel

**Karl Leo** Dresden Integrated Center for Applied Physics and Photonic Materials (IAPP) and Institute for Applied Physics, TU Dresden, Dresden, Germany

Itamar Levi Faculty of Engineering Bldg, Bar-Ilan University, Ramat-Gan, Israel

James A. Lott Institut für Festkörperphysik, Technische Universität Berlin, Berlin, Germany

Grégory Moille Thales Research and Technology, Palaiseau, France

**Philip Moser** Institut für Festkörperphysik, Technische Universität Berlin, Berlin, Germany

**Benjamin Oesen** Dresden Integrated Center for Applied Physics and Photonic Materials (IAPP) and Institute for Applied Physics, TU Dresden, Dresden, Germany

A. Palzer ISE Fraunhofer Institute, Freiburg, Germany

Inna Partin-Vaisband Department of Electrical and Computer Engineering, University of Illinois at Chicago, Chicago, IL, USA

R. Schindler ISE Fraunhofer Institute, Freiburg, Germany

**Holger Schmeckebier** Department of Solid-State Physics, Technische Universität Berlin, Berlin, Germany

Silvia Spiga Walter Schottky Institut, Technische Universität München, Munich, Germany

Sascha Ullbrich Dresden Integrated Center for Applied Physics and Photonic Materials (IAPP) and Institute for Applied Physics, TU Dresden, Dresden, Germany

**Eicke R. Weber** ISE Fraunhofer Institute, Freiburg, Germany; Berkeley Education Alliance for Research in Singapore BEARS, Singapore, Singapore

Johannes Widmer Dresden Integrated Center for Applied Physics and Photonic Materials (IAPP) and Institute for Applied Physics, TU Dresden, Dresden, Germany

# Chapter 1 Energy-Efficient Vertical-Cavity Surface-Emitting Lasers for Optical Interconnects

#### Philip Moser, James A. Lott and Dieter Bimberg

**Abstract** General rules that describe how to achieve extremely energy-efficient data transmission with oxide-confined VCSELs are derived, explained, and verified by data transmission experiments. We demonstrate that VCSELs with smaller oxide-aperture diameters are more energy-efficient than similar VCSELs with larger oxide-aperture diameters and introduce a new method for analyzing the suitability of different VCSELs for application in different optical interconnect configurations by introducing the modulation factor M. Applying the derived rules for energy-efficient VCSEL operation enables record energy-efficient data transmission with less than 100 femto-Joules per bit in a wide range of bit rates and multimode optical fiber lengths.

#### **1.1 VCSEL Energy Efficiency**

Energy-efficient operation with low dissipated and consumed energy per transmitted bit is a prerequisite for future optical interconnects. Vertical-cavity surface-emitting lasers (VCSELs) are a key component for optical computer interconnects. Although additional performance requirements such as long transmission distances across multimode optical fiber, high error-free bit rates, and operation at elevated temperatures over a wide range of temperatures exist, all these goals must be achieved at a simultaneously high energy efficiency.

In the fields of optical data transmission and semiconductor lasers the term "energy efficiency" is not a firmly set term with one established definition. For a complete optical interconnect the energy efficiency could for instance refer to the complete consumed or dissipated energy to transfer one unit of information from

P. Moser (🖂) · J.A. Lott · D. Bimberg

Institut für Festkörperphysik, Technische Universität Berlin, Berlin, Germany e-mail: p.moser@tu-berlin.de

J.A. Lott e-mail: james.lott@tu-berlin.de

D. Bimberg e-mail: bimberg@physik.tu-berlin.de

© Springer International Publishing AG 2017

G. Eisenstein and D. Bimberg (eds.), *Green Photonics and Electronics*, NanoScience and Technology, DOI 10.1007/978-3-319-67002-7\_1

the transmitter to the receiver and would then have the units of energy per bit. The true energy efficiency depends on the overall performance of the entire VCSEL-based optical communication system including for example the transmitter (that is the VCSEL and the VCSEL driver circuit), the receiver, the characteristics of the interconnecting optical medium, and the attributes of the particular modulation scheme employed to encode the information. In this Chapter we focus on the intrinsic energy efficiency of the VCSEL.

Large progress has been achieved in the past years in increasing the modulation bandwidth of oxide-confined VCSELs resulting in modulation bandwidths exceeding 25 GHz [1, 2]. Since the major concern of the past research was on increasing the modulation bandwidth and the error-free bit rate, these record results are achieved at large bias currents and large power dissipations and energy consumptions that exceed the practical limits for commercial applications in future novel optical interconnects. Even larger modulation bandwidths up to 37 GHz have been demonstrated with coupled-cavity VCSELs [3, 4]. The largest bit rate achieved with transversely coupled VCSELs is 25 Gb/s [5, 6], thus the large modulation bandwidths of these coupled-cavity devices does not yet fully translate into large bit rates. Thus at present, optically coupled VCSELs have not yet been demonstrated that achieve bit rates superior to conventional directly current-modulated VCSELs and the large modulation bandwidths therefore do not lead to energy-efficient data transmission with low consumed energy per bit.

#### **1.2 Energy Efficiency Figures of Merit**

In order to compare the suitability of VCSEL designs for low energy consuming optical interconnects we define the electrical energy-to-data ratio *EDR* (fJ/bit), and the dissipated heat-to-bit rate ratio HBR (expressed in units of mW/Tbps or fJ/bit) as [7]:

$$EDR = \frac{I \cdot V}{BR} = \frac{P_{el}}{BR} = \frac{I \cdot V}{M \cdot f_{3dB}}$$

(1.1)

$$HBR = \frac{I \cdot V - P_{opt}}{BR} = \frac{P_{el} - P_{opt}}{BR} = \frac{P_{diss}}{BR} = \frac{I \cdot V - P_{opt}}{M \cdot f_{3dB}}$$

(1.2)

where *V* and *I* are the direct current (DC) operating voltage and bias current of the VCSEL,  $IV - P_{opt}$  is the dissipated power  $P_{diss}$ ,  $P_{opt}$  is the optical output power of the VCSEL, BR is the bit rate of error-free data transmission, and  $f_{3dB}$  is the modulation bandwidth. The modulation energy that in a typical laboratory test set up is delivered from a bit pattern generator and that finally generates the bits is not included in the *EDR* and *HBR* definitions given by 1.1 and 1.2. The term *M* in 1.1 and 1.2, where  $BR = M \cdot f_{3dB}$  is the *modulation factor* (M-factor) that relates the

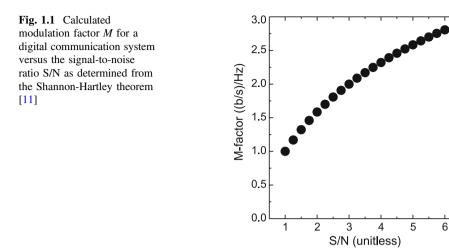

intrinsic  $f_{3dB}$  to the error-free bit rate of a given optical interconnect technology [8]. We note that M simply replaces the term  $log_2(1 + S/N)$  in the classic Shannon-Hartley Theorem [9] in the field of Information Theory. The maximum channel capacity C of a communication channel subject to additive white Gaussian noise (i.e. white thermal noise) and with an "arbitrarily small frequency of errors" (see [9], p. 43) is written as  $C = B \log_2(1 + S/N)$ , where B is the bandwidth of the channel ( $B = f_{3dB}$  in our present case; written as W by Shannon [9]), S (written as P by Shannon [9]) is the average signal power in Watts, and N is the average noise power in Watts. The channel capacity C is equal to the bit rate for our purposes since in our case the VCSELs are employed to transmit simple binary data using a two-level nonreturn-to-zero (NRZ) coding scheme and thus C = BR is naturally given in units of bit/s. The modulation factor M (in units of (bit/s)/Hz) is then equivalent to the "spectral efficiency" given by  $\eta = M = C/B$  [10]. We also note that  $\eta = log_2(1 + M E_b/N_0)$ , where  $E_b$  is the energy (in Joules) to transfer a bit and  $N_0$  is the noise spectral density (also in Joules) [10]. Thus we may relate the energy efficiency to the spectral efficiency by writing  $N_0/E_b = (2^M - 1)/M = SNR/M$ , where the signal-to-noise ratio SNR = S/N. The calculated M-factor for a digital communication system is plotted versus the signal-to-noise ratio in Fig. 1.1.

Assuming that a constant minimum average noise power exists in a given information channel, then energy efficient data transmission, i.e. low energy consumption per transmitted bit, corresponds to a small average signal power and thus a small signal-to-noise ratio and consequently a small M-factor. Thus information can be transported very energy efficiently for systems with small M-factors only [11]. Therefore, if the M-factor is small, according to 1.1 and 1.2, the VCSEL needs to provide a large  $f_{3dB}$  at simultaneously low consumed energy and low dissipated power. In this Chapter we demonstrate that VCSELs with smaller oxide-aperture diameters and therefore smaller optical mode volumes achieve larger  $f_{3dB}$  at significantly lower consumed energy and dissipated power than similar VCSELs of the same epitaxial design but with larger oxide-aperture diameters. We present general rules applicable to all oxide-confined VCSELs that describe how to operate such small oxide-aperture diameter VCSELs in order to achieve record low *EDR* and *HBR* values.

#### 1.3 Resonance Frequency and Modulation Bandwidth

The relaxation resonance frequency  $f_r$  of a semiconductor laser increases with the square-root of the current above the threshold current  $I_{th}$  [12]. The rate at which  $f_r$  increases is given by the D-factor. In order to achieve a large relaxation resonance frequency  $f_r$  and thus a potentially large modulation bandwidth  $f_{3dB}$  at simultaneously low bias currents the D-factor is desired to be as large as possible.

$$f_r = D \sqrt{(I - I_{th})} \tag{1.3}$$

The D-factor of a semiconductor laser depends on the epitaxial design and the geometrical design of the device and is given by 1.4:

$$D = \frac{1}{2\pi} \sqrt{\frac{\eta_i \Gamma v_g}{q V_a} \frac{\partial g / \partial n}{\chi}}$$

(1.4)

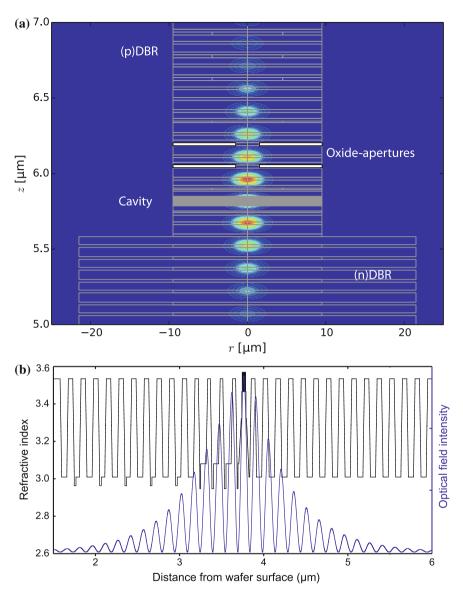

where  $\eta_i$  (unitless) is the internal quantum efficiency,  $\Gamma$  (unitless) is the optical confinement factor,  $v_{g}$  (cm/s) is the group velocity of light, q is the elementary charge (coulomb),  $V_a$  (cm<sup>3</sup>) is the active volume,  $\partial g/\partial n$  (cm<sup>2</sup>) is the differential gain, and  $\chi$ (unitless) is the transport factor. For an oxide-confined VCSEL the active volume  $V_{\rm a}$ is the product of the aperture area and the thickness of the active material, given for example by the cumulative quantum well thickness. The main factors that determine the D-factor are the differential gain and the active volume. While the differential gain is determined by the active region design and therefore cannot be changed for a given epitaxial design, the active volume  $V_a$  can easily be varied by changing the oxide-aperture diameter. The oxide-aperture restricts the area of the active material that is electrically pumped and therefore the area that can provide positive optical gain. In addition, the oxide-aperture may provide a lateral optical confinement due to the lateral refractive index step, depending on the placement of the oxide layer relative to the nodes and antinodes of the resonant optical field intensity for a given optical mode, and on the thickness of the oxide layer. Figure 1.2 shows the two-dimensional and one-dimensional optical field intensity distributions in an example VCSEL with a double-mesa structure for the fundamental LP01 lasing mode. The schematics show two oxide-aperture layers that simultaneously constrict the charge carrier flow in the device and provide lateral optical confinement.

The D-factor increases with decreasing oxide-aperture diameter and therefore VCSELs with smaller oxide-aperture diameters achieve larger relaxation resonance frequencies at a given bias current compared to neighbor VCSELs from the same area on the same wafer but with larger oxide-aperture diameters [13]. In order to

**Fig. 1.2** Optical field intensity distribution in an example GaAs-based vertical-cavity surface-emitting laser with a double mesa structure in two dimensions (**a**) and in one-dimension (**b**) along a rotationally-symmetric center line where the top mesa radius  $r = 10 \mu m$ . Two oxide-apertures in the top p-doped DBR confine the light laterally

estimate the potential for error-free operation at high bit rates we use the modulation bandwidth  $f_{3dB}$  rather than the relaxation resonance frequency, because  $f_{3dB}$  is directly related to the maximum possible bit rate that the VCSEL is able to support.

The modulation bandwidth  $f_{3dB}$  is the bandwidth at which the small-signal modulation response is -3 dB. As with the relaxation resonance frequency  $f_r$ , the modulation bandwidth  $f_{3dB}$  increases with the square-root of the current above the threshold current, until thermal and other effects cause the modulation bandwidth to saturate. The proportionality factor for  $f_{3dB}$  that is equivalent to the D-factor is the modulation-current efficiency-factor *MCEF* [14] as shown in 1.5:

$$f_{3dB} = MCEF \ \sqrt{(I - I_{th})} \tag{1.5}$$

The *MCEF* cannot be analytically expressed by geometrical or epitaxial VCSEL design parameters but must be determined experimentally by small-signal modulation response measurements.

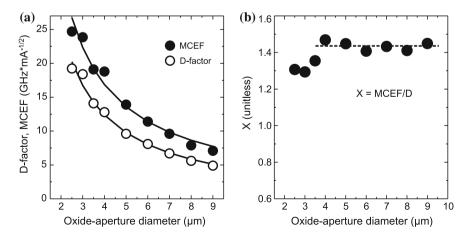

At bias currents smaller than the thermal rollover current where the relaxation resonance frequency  $f_r$  and the modulation bandwidth  $f_{3dB}$  both follow the linear theory given by 1.4 and 1.5, the modulation bandwidth is larger than the relaxation resonance frequency and we have:

$$f_{3dB} > f_r \Rightarrow MCEF > D \Rightarrow X = \frac{MCEF}{D} > 1$$

(1.6)

$$f_{3dB} = X \cdot f_r \tag{1.7}$$

Since both the D-factor and the *MCEF* are constant values at lower forward bias currents before the saturation of  $f_r$  and  $f_{3dB}$  occurs the ratio X of the *MCEF* and the D-factor is a constant as well and can be used to calculate  $f_{3dB}$  from  $f_r$ . Therefore, a large D-factor also leads to a large  $f_{3dB}$  and thus to large bit rates at low bias currents above the threshold current. The dependence of the D-factor and *MCEF* on the oxide-aperture diameter is shown in Fig. 1.3 for neighbor VCSELs with

Fig. 1.3 a D-factor and modulation-current efficiency factor (*MCEF*) versus the oxide-aperture diameter. b Ratio X = MCEF/D versus the oxide-aperture diameter [11]

oxide-aperture diameters ranging from 2.5 to 9.0  $\mu$ m. For oxide-aperture diameters larger than approximately 4  $\mu$ m, e.g. for typical multimode VCSELs, *X* does not vary with the diameter of the oxide-aperture. For smaller oxide-aperture diameters *X* slightly decreases with the oxide-aperture diameter [11] but *X* still remains above 1.2.

#### 1.4 Energy Efficiency Analysis

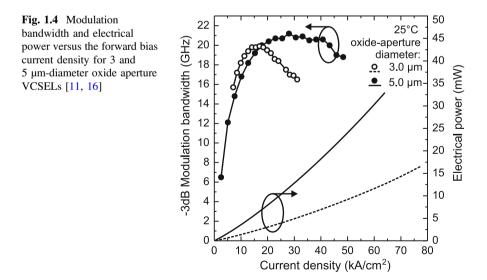

In order to compare the potential of VCSELs for application in energy-efficient optical interconnects not only the absolute value of  $f_{3dB}$  but the ratio of the modulation bandwidth to the electrical and dissipated power is important. At a given bias current the electrical power increases with decreasing oxide-aperture diameter  $d_A$  because the differential resistance increases as  $d_A$  decreases, roughly by a factor of the inverse oxide-aperture radius squared  $(r^{-2})$ . For commercial applications of oxide-confined VCSELs the current density J is more important than the bias current, because J is directly related to the reliability of the VCSEL [15]. For a given current density the electrical power of a VCSEL decreases with decreasing oxide-aperture diameter. The modulation bandwidth  $f_{3dB}$  and the electrical power  $P_{\rm el}$  are plotted versus the current density for two VCSELs with oxide-aperture diameters of 3 and 5 µm in Fig. 1.4. The VCSEL with the smaller oxide-aperture diameter reaches the maximum modulation bandwidth at a smaller current density and at a significantly smaller electrical power than the VCSEL of the same epitaxial design but with a larger oxide-aperture diameter. At low current densities as required for commercial data communication applications the modulation bandwidth of the smaller oxide-aperture diameter VCSELs exceeds that of the VCSEL with the larger oxide-aperture diameter. The VCSEL with the larger oxide-aperture

diameter achieves a larger maximum modulation bandwidth, but at a larger current density and at a significantly larger operating power as compared to the VCSEL with the smaller oxide-aperture diameter [11, 16]. Since the energy-efficiency of the VCSEL is at least as important as the modulation bandwidth, it is not a viable strategy to make use of the larger modulation bandwidth of the larger oxide-aperture diameter VCSEL. The 5  $\mu$ m oxide-aperture diameter VCSEL of the given example has a 5% larger modulation bandwidth, but at the cost of an almost 6 times larger operating power [11, 16]. At a current density of approximately 17 kA/ cm<sup>2</sup> both VCSELs achieve about the same modulation bandwidth *f*<sub>3dB</sub>, but at a power of 2.5 and 6.6 mW for the VCSELs with oxide-aperture diameters of 3 and 5  $\mu$ m, respectively [11, 16].

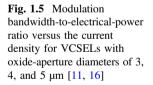

For energy-efficient data transmission the ratio of the modulation bandwidth and the driving electrical power is important. The bandwidth-to-electrical power ratio is given by the modulation bandwidth of a VCSEL at a given bias current divided by the electrical power. Figure 1.5 shows the bandwidth-to-electrical power ratio of VCSELs with different oxide-aperture diameters versus the current density [11]. At a given current density VCSELs with smaller oxide-aperture diameters have a larger modulation bandwidth-to-electrical power ratio than VCSELs of the same epitaxial design but with larger oxide-aperture diameters. The advantage of using VCSELs with a small oxide-aperture diameter is especially significant at small current densities (J values) as small J values are required for reliable commercial applications.

As already illustrated in Fig. 1.4, the modulation bandwidth of a VCSEL reaches a maximum at a certain current density and a further increase in the bias current will eventually even lead to a decrease of  $f_{3dB}$ . The ratio of the modulation bandwidth to the electrical power consumption  $f_{3dB}/P_{el}$  decreases monotonically with increasing bias current, whereas  $f_{3dB}$  first increases, saturates and then decreases again with increasing bias current. This dependence of  $f_{3dB}$  limits the practical bias current range for application of the particular VCSEL as an energy-efficient light source for optical

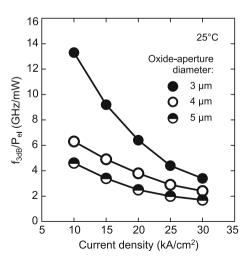

Fig. 1.6 Modulation bandwidth to electrical power ratio  $\mathbf{a}$  versus the modulation bandwidth and the calculated energy-to-data ratio (*EDR*) versus the calculated bit rate  $\mathbf{b}$  for M-factors of 1.7, 1.8, 1.9, and 2.0 (b/s)/Hz, respectively

interconnects. Thus ideally VCSELs must be operated at bias currents before the saturation of  $f_{3dB}$  sets in, in order to be energy-efficient and achieve a high bit rate.

The ratio  $f_{3dB}/P_{el}$  is plotted versus the modulation bandwidth  $f_{3dB}$  of a VCSEL with an oxide-aperture diameter of 3 µm in Fig. 1.6a. The electrical power  $P_{el}$  and the modulation bandwidth  $f_{3dB}$  both reflect purely intrinsic properties of the VCSEL without any impact of the measurement setup or configuration. That is why we refer to the bandwidth-to-electrical power ratio as the *intrinsic dynamic energy-efficiency*. From these measured intrinsic values of  $f_{3dB}$  and  $P_{el}$  we can calculate the bit rate and the *EDR* of a VCSEL for any given M-factor, assuming 1.1 is valid. The *EDR* is plotted in Fig. 1.6b versus the bit rate for M-factors of 1.7, 1.8, 1.9, and 2.0 (b/s)/Hz, respectively, calculated from the  $f_{3dB}/P_{el}$  ratio shown in Fig. 1.6a.

Given an M-factor that serves to characterize the performance of a complete optical interconnect system and the measured  $f_{3dB}$  and  $P_{el}$  characteristics for a given experimental or commercial VCSEL technology, a maximum anticipated bit rate  $(BR_{max} = M \cdot f_{3dB})$  and a maximum anticipated energy efficiency  $(EDR_{min} = P_{el}/BR_{max})$  may be estimated. Both *EDR* and the bit rate are calculated from the M-factor and therefore the maximum bit rates and *EDR* values at these bit rates change with different interconnect system configurations represented by the respective M-factors. In order to compare the potential of different VCSELs for use in different energy-efficient optical interconnects, i.e. for systems with different M-factors, the bit rates the VCSEL would achieve at a given *EDR* can be compared. Plotting these bit rates at a given fixed *EDR* value versus the M-factor allows us to compare the suitability of VCSELs for use in different optical interconnect systems [8, 11].

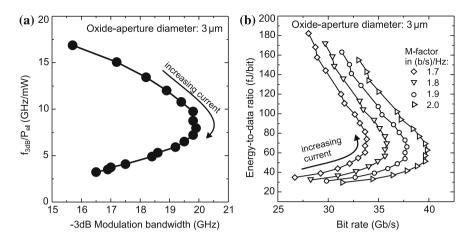

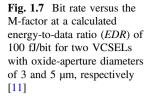

In Fig. 1.7 [11] we plot the bit rate at a constant *EDR* of 100 fJ/bit versus the M-factor for the two VCSELs with oxide-aperture diameters of 3 and 5  $\mu$ m (i.e. for

the same VCSELs as in Fig. 1.4). At an M-factor of 2.17 (bit/s)/Hz both VCSELs achieve exactly the same bit rate at the same *EDR*, whereas at smaller M-factors the 3  $\mu$ m oxide-aperture diameter VCSEL achieves larger bit rates than the VCSEL with an oxide-aperture diameter of 5  $\mu$ m. At M-factors larger than 2.17 (bit/s)/Hz the VCSEL with the larger oxide-aperture diameter achieves larger bit rates than the VCSEL with the smaller oxide-aperture diameter. For our large signal modulation setups that we use to perform data transmission experiments with VCSELs, we typically achieve M-factors between 1.4 and 2.0 (bit/s)/Hz. Typically, M-factors larger than 2.0 (bit/s)/Hz are not achieved with simple standard binary coding schemes, but with higher order modulation formats such as 4-PAM and 8-PAM [17], which require more complex and more energy-consuming interconnect configurations. Higher M-factors larger than 2.0 (bit/s)/Hz for the standard nonreturn-to-zero modulation coding scheme have been enabled by the use of driver and receiver circuits that employ equalization [18].

#### 1.5 Energy Efficient Data Transmission Results

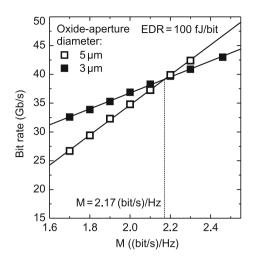

In order to verify the impact of the oxide-aperture diameter on the energy efficiency of the large-signal modulation performance of VCSELs, we measure VCSELs with an identical epitaxial design but with different oxide-aperture diameters using the exact same large-signal modulation measurement system configuration for each device [19]. Figure 1.8 shows bit error ratio (*BER*) curves versus the received optical power for VCSELs with different oxide-aperture diameters of an estimated 3.5, 4.0, and 5.0 µm operated in a back-to-back testing configuration at 25 Gb/s. The VCSELs are all measured with the same measurement setup configuration and the same modulation peak-to-peak voltage. The VCSELs are operated at the lowest

**Fig. 1.8 a** Bit error ratio (*BER*) versus received optical power at 25 Gb/s in a back-to-back testing configuration for VCSELs with oxide-aperture diameters of 3.5, 4.0, and 5.0  $\mu$ m [17]. **b** Energy-to-data ratio (*EDR*) and heat-to-bit rate ratio (*HBR*) at error-free operation at 25 Gb/s in a back-to-back testing configuration versus the oxide-aperture diameter [11]

possible bias currents that still allow error-free operation, leading to the maximum energy efficiency, *HBR*, and *EDR* of these devices at this given bit rate and for this given measurement setup configuration. A record-low 56 fJ of dissipated energy per bit is demonstrated with the VCSEL having an oxide-aperture of 3.5  $\mu$ m [19]. Both the *HBR* and *EDR* increase with increasing oxide-aperture diameter [19] as does the received optical power at error-free operation. The measured *EDR* and *HBR* values at 25 Gb/s are shown versus the oxide-aperture diameter in Fig. 1.8b.

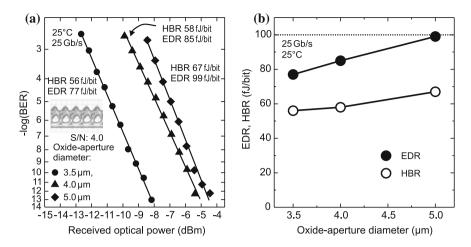

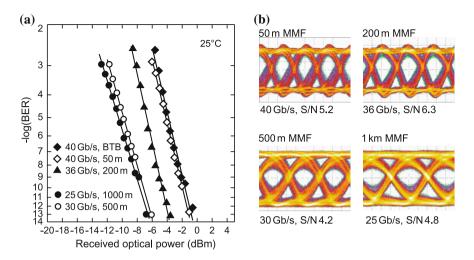

The smaller mode-volume of smaller oxide-aperture diameter VCSELs enables error-free data transmission with lower operating power and lower dissipated energy per bit. Because small oxide-aperture diameters also lead to small spectral widths of the optical emissions, e.g. single-mode emission or only a few modes in the optical spectrum, such VCSELs are also well-suited to transmit data across long distances of multimode optical fiber at simultaneously high energy efficiency [20, 21]. At 25 Gb/s we have demonstrated energy-efficient error-free data transmission across up to 1 km of multimode optical fiber with an *HBR* of 100 fJ/bit [22]. The maximum possible fiber transmission distance decreases with increasing bit rate. It is for example, 500 m at 30 Gb/s at an *HBR* of 85 fJ/bit [22]. Using VCSELs with small oxide-aperture diameters it is also possible to achieve energy-efficient operation at relatively high bit rates such as at 40 Gb/s with an *HBR* of only 108 fJ/bit [23]. The measured *BER* versus the received optical power and the accompanying optical eye diagrams at error-free operation are shown in Fig. 1.9a and b, respectively.

Small mode volumes as a result of small oxide-aperture diameters enable extremely energy-efficient operation of VCSELs at low current densities, long multimode fiber distances, and high bit rates. This is due to the higher D-factors

**Fig. 1.9 a** Bit error ratio (*BER*) versus received optical power for data transmission up to 40 Gb/s and across up to 1000 m of multimode optical fiber [11]. **b** Optical eye diagrams at the point of error-free detection for the *BER* curves shown in (**a**) [11]

resulting in larger modulation bandwidths at simultaneously low consumed energy and low operating power. For applications in future short-distance optical computer interconnects that are placed close to the integrated circuit processors, which are a main heat source inside a computer, the VCSELs need to perform best at elevated temperatures of 55 to 85 °C or at even higher temperatures. For a VCSEL that is optimized to operate at its highest bit rates at room temperature, the D-factor typically decreases with increasing external temperature which results in a significant decrease of the error-free bit rate and thus of the energy efficiency.

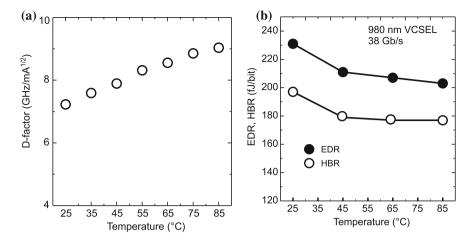

We have demonstrated that via a large detuning between the VCSEL's peak active region gain wavelength (estimated from the room temperature photoluminescence measurements of epitaxially-grown calibration wafers) and the VCSEL's cavity etalon wavelength, the dynamic performance of the VCSEL can be optimized for operation at elevated temperatures. For our 980-nm VCSELs with a large detuning of -15 nm [24] the D-factor increases monotonically with increasing ambient temperature [25]. The D-factor is plotted versus the ambient temperature in Fig. 1.10a. Due to the -15 nm detuning, the threshold current reaches a minimum value at a temperature of 60 °C. As a result, the energy efficiency of the VCSEL increases for a given bit rate with temperature, i.e. the consumed energy and the dissipated energy per bit both become smaller for elevated ambient temperatures between approximately 55-85 °C. The EDR and HBR for error-free operation at 38 Gb/s are plotted for our detuned 980 nm VCSEL with an oxide-aperture diameter of 5.5 µm versus the ambient temperature in Fig. 1.10b. In a wide temperature range from 55 to 85 °C the HBR is only 177 fJ/bit and highly insensitive to a temperature variation [26]. Thus the increasing D-factor as temperature increases successfully compensates for increased VCSEL thermal losses at higher temperatures.

**Fig. 1.10** a The D-factor versus heat-sink temperature for a 980 nm VCSEL with an oxide-aperture diameter of 5.5  $\mu$ m and a room temperature peak photoluminescence wavelength-to-etalon wavelength detuning of -15 nm. b Energy-to-data ratio (*EDR*) and heat-to-bit rate ratio (*HBR*) at error-free operation at 38 Gb/s versus heat-sink temperature for a 980 nm VCSEL [26]

#### 1.6 Summary

We have demonstrated that VCSELs with smaller oxide-aperture diameters are more energy efficient than similar VCSELs with larger oxide-aperture diameters. The reason is the smaller VCSELs have a larger D-factor and simultaneously they operate at a smaller energy consumption, a result of their smaller mode volume. Especially at low current densities that are required for reliable commercial applications, small oxide-aperture diameter VCSELs are superior to larger oxide-aperture diameter VCSELs with respect to energy efficiency and bandwidth. The small oxide-apertures also lead to a small spectral width of the optical emission allowing the transmission of data across longer distances of up to at least 1000 m of multimode optical fiber. Using VCSELs with small oxide-aperture diameters we have demonstrated that it is possible to transmit error-free data at up to 40 Gb/s across 50 m of multimode optical fiber and at up to 25 Gb/s across up to 1000 m of multimode optical fiber while dissipating less than or close to 100 fJ of heat energy per bit. The temperature dependence of the D-factor can be tuned via the photoluminescence peak wavelength-to-cavity resonance wavelength detuning. A large detuning leads to an increase of the D-factor with temperature, resulting in a highly temperature insensitive energy efficiency by compensating for increasing thermal losses.

#### References

- A. Larsson, M. Geen, J.S. Gustavsson, E.P. Haglund, A. Joel, P. Westbergh, E. Haglund, 30 GHz bandwidth 850 nm VCSEL with sub-100 fJ/bit energy dissipation at 25–50 Gbit/s. Electron Lett. 51(14), 1096–1098 (2015)

- E. Haglund, P. Westbergh, J. Gustavsson, E. Haglund, A. Larsson, High-speed VCSELs with strong confinement of optical fields and carriers. J. Lightw. Technol. 34(2), 269–277 (2016)

- S.T.M. Fryslie, M.P. Tan, D.F. Siriani, M.T. Johnson, K.D. Choquette, 37-GHz modulation via resonance tuning in single-mode coherent vertical-cavity laser arrays. IEEE Photonics Technol. Lett. 27(4), 415–418 (2015)

- S.T.M. Fryslie, and K.D. Choquette, Breakthroughs in photonics 2014: coherent vertical-cavity Surface-emitting laser arrays. IEEE Photonics J. 7(3), 0700105-1–0700105-5 (2015)

- H. Dalir, F. Koyama, 29 GHz directly modulated 980 nm vertical-cavity surface emitting lasers with bow-tie shape transverse coupled cavity. Appl. Phys. Lett. 103(9), 091109 (2013)

- F. Koyama, H. Dalir, Highly stable operations of transverse-coupled cavity VCSELs with enhanced modulation bandwidth. Electron Lett. 50(11), 823–824 (2014)

- P. Moser, W. Hofmann, P. Wolf, J.A. Lott, G. Larisch, A. Payusov, N.N. Ledentsov, D. Bimberg, 81 fJ/bit energy-to-data ratio of 850-nm vertical-cavity surface-emitting lasers for optical interconnects. Appl. Phys. Lett. 98(23), 231106 (2011)

- P. Moser, J.A. Lott, G. Larisch, D. Bimberg, Impact of the oxide-aperture diameter on the energy-efficiency, bandwidth, and temperature stability of 980 nm VCSELs. J. Lightw. Technol. 33(4), 825–831 (2015)

- 9. C.E. Shannon, Communication in the presence of noise, in *Proceeding of IRE*, vol. 37, no. 1 (1949), pp. 10–21

- F.R. Yu, X. Zhang, V. Leung, Green Communications and Networking (CRC Press, Florida, USA, 2012)

- 11. P. Moser, *Energy-Efficient VCSELs for Optical Interconnects* (Springer, Berlin, Heidelberg, 2016)

- 12. L.A. Coldren, S.W. Corzine, Dynamic effects, in *Diode Lasers and Photonic Integrated Circuits*, ed. by K. Chang (Wiley, New York, 1995), pp. 185–213

- P. Moser, J.A. Lott, D. Bimberg, Energy efficiency of directly modulated oxide-confined high bit rate 850-nm VCSELs for optical interconnects. IEEE J. Sel. Top. Quantum Electron 19(4), 1702212-1–1702212-12 (2013)

- T.R. Chen, B. Zhao, L. Eng, Y.H. Zhuang, J. O'Brien, A. Yariv, Very high modulation efficiency of ultralow threshold current single quantum well InGaAs lasers. Electron Lett. 29(17), 1525–1526 (1993)

- B.M. Hawkins, R.A. Hawthorne, J.K. Guenter, J.A. Tatum, J.R. Biard, Reliability of various size oxide aperture VCSELs, in *Proceeding of IEEE 52nd Electronic Components and Technology Conference*, 28–31, San Diego, USA, CA (2002), pp. 540–550

- P. Moser, P. Wolf, G. Larisch, H. Li, J.A. Lott, D. Bimberg, Energy-efficient oxide-confined high-speed VCSELs for optical interconnects, in *Proceeding of SPIE 9001, Vertical-Cavity Surface-Emitting Lasers XVIII*, 7–12 Feb 2014, San Francisco, CA, USA, p. 900103

- D.M. Kuchta, A.V. Rylyakov, C.L. Schow, J.E. Proesel, C.W. Baks, P. Westbergh, J.S. Gustavsson, A. Larsson, A 50 Gb/s NRZ modulated 850 nm VCSEL transmitter operating error free to 90 °C. J. Lightw. Technol. 33(4), 802–810 (2015)

- K. Szczerba, P. Westbergh, M. Karlsson, P.A. Andrekson, A. Larsson, 70 Gbps 4-PAM and 56 Gbps 8-PAM using an 850 nm VCSEL. J. Lightw. Technol. 33(7), 1395–1401 (2015)

- P. Moser, J.A. Lott, P. Wolf, G. Larisch, H. Li, N.N. Ledentsov, D. Bimberg, 56 fJ dissipated energy per bit of oxide-confined 850-nm VCSELs operating at 25 Gb/s. Electron Lett. 48(20), 1292–1294 (2012)

- P. Moser, J.A. Lott, P. Wolf, G. Larisch, A.S. Payusov, N.N. Ledentsov, W. Hofmann, D. Bimberg, 99 fJ/(bit km) Energy to data-distance ratio at 17 Gb/s across 1 km of multimode

optical fiber with 850-nm single-mode VCSELs. IEEE Photonics Technol. Lett. **24**(1), 19–21 (2012)

- P. Moser, J.A. Lott, P. Wolf, G. Larisch, A. Payusov, N. Ledentsov, D. Bimberg, Energy-efficient oxide-confined 850 nm VCSELs for long distance multimode fiber optical interconnects. IEEE J. Sel. Top. Quantum Electron 1292–1294 (2012)

- P. Moser, J.A. Lott, P. Wolf, G. Larisch, H. Li, D. Bimberg, 85-fJ dissipated energy Per Bit at 30 Gb/s across 500-m multimode fiber using 850-nm VCSELs. IEEE Photon Technol. Lett. 25(16), 1638–1641 (2013)

- P. Wolf, P. Moser, G. Larisch, H. Li, J.A. Lott, D. Bimberg, Energy efficient 40 Gbit/s transmission with 850 nm VCSELs at 108 fJ/bit dissipated heat. Electron Lett. 49(10), 666–667 (2013)

- 24. A. Mutig, High Speed VCSELs for Optical Interconnects (Springer, Berlin, Heidelberg, 2011)

- 25. H. Li, P. Wolf, P. Moser, G. Larisch, A. Mutig, J.A. Lott, D.H. Bimberg, Impact of the quantum well gain-to-cavity etalon wavelength offset on the high temperature performance of high bit rate 980-nm VCSELs. IEEE J. Ouantum Electron 50(8), 613–621 (2014)

- H. Li, P. Wolf, P. Moser, G. Larisch, A. Mutig, J.A. Lott, D. Bimberg, Energy-efficient and temperature-stable oxide-confined 980 nm VCSELs operating error-free at 38 Gbit/s at 85 °C. Electron Lett. 50(2), 103–105 (2014)

## Chapter 2 High-Speed InP-Based Long-Wavelength VCSELs

#### Silvia Spiga and Markus C. Amann

**Abstract** The rapid growth of internet and cloud computing applications drives a huge demand for bandwidth capacity in communication networks, while power consumption, cost, and space density must scale down. This growth leads to an increase in the size of data centers (longer optical links), and of the fibers' channel data rate, rooted in Moore's Law. Until now, multi-mode fibers (MMF) have been largely employed in datacom applications due to the large coupling tolerance. However, the data-carrying capability of MMF decreases with the transmission distance due to pulse broadening resulting from modal and chromatic dispersion. In order to overcome those limits, transceivers based on single mode fiber (SMF) are under development and the first systems are on the market. Vertical-cavity surface-emitting lasers (VCSELs) are the transmitters of choice for short-reach applications due to their low cost, energy efficiency, and small footprint. InP-based VCSELs emitting at long wavelengths (i.e. 1.3 and 1.55 µm) have gained large interest due to their intrinsic lower power consumption (lower band gap) and low losses in silicon waveguides and silica-based optical fibers, which allows longer transmission distances. While short-wavelength GaAs-based VCSELs have achieved small-signal modulation bandwidths up to 30 GHz [1], InP-based VCSELs show inferior modulation capabilities [2, 3]. Up to date, the highest small-signal bandwidth demonstrated on InP-based devices is 22 GHz [3]. The distributed Bragg reflectors (DBRs) commonly used for GaAs-based VCSELs are made of binary and ternary semiconductor compounds, which offer several advantages such as high refractive-index contrast between the layers, good electrical conductivity and low thermal resistivity. The inferiority of semiconductor DBRs lattice matched to InP challenges the modulation bandwidth enhancement of InP-based devices which suffer of poor thermal conductivity, and high lateral spreading resistance. A further challenge is the single-mode laser operation that has motivated the transition from MMF to SMF in datacom systems. In this chapter, the

S. Spiga · M.C. Amann (∞)

© Springer International Publishing AG 2017

Walter Schottky Institut, Technische Universität München, Munich, Germany e-mail: amann@wsi.tum.de

S. Spiga e-mail: Silvia.Spiga@wsi.tum.de

G. Eisenstein and D. Bimberg (eds.), *Green Photonics and Electronics*, NanoScience and Technology, DOI 10.1007/978-3-319-67002-7\_2

challenges related to InP-based VCSELs are discussed with focus on active region design, cavity engineering, and current and optical confinement. These arguments apply to all InP-based VCSELs with emission wavelength between 1.3 and 2.0  $\mu$ m. Stationary and dynamic characteristics are presented for a 1.55  $\mu$ m VCSEL. Finally, datacom and telecom transmission experiments are presented.

#### 2.1 InP-Based VCSELs

The absorption spectrum of silica-based optical fibers presents two main windows for datacom and telecom with low absorption around 1.3 and 1.55  $\mu$ m. GaAs-based VCSELs shows excellent stationary and dynamic performances on the short wavelength regime (i.e. 850 and 980 nm) and take full advantage of their well-established technology. Wavelengths up to 1.3  $\mu$ m have been achieved for GaAs-based VCSELs by means of highly strained GaInAs quantum wells (QWs) [4], GaInNAs QWs [5], and InAs-GaInAs quantum dots [6]. InP-based VCSELs offer, on the other hand, the advantage of growing quantum wells consisting of moderately (compressively) strained quaternary-materials such as AlGaInAs and InGaAsP emitting at wavelengths between 1.3 and 2.0  $\mu$ m fully covering the optical fibers low-loss windows.

The key rules for designing a high-speed energy-efficient VCSEL are well known. First, the laser active region has to be able of properly confining the carrier and providing high differential gain. Second, the laser's cavity has to be as short as possible to reduce the photon lifetime boosting the laser relaxation resonance frequency and decreasing the intrinsic damping. Finally, current and optical field have to be properly confined. This allows electrical excitation of the optical mode that contributes to carry the transmitted information, and in guiding the relative longitudinal mode in the laser's cavity such that optical losses are minimal.

The active region composition, the cavity design concepts as wells as electrical and optical confinement to achieve high-speed energy-efficient InP-based VCSELs will be discussed in this section.

#### 2.1.1 Active Region

The design of the active region plays a crucial role for stationary and dynamic performances of VCSELs. Different material systems have been proposed and demonstrated. QWs are used in VCSELs to produce a 2-D density of state (DOS) [7], and to allow high strain ( $\varepsilon$ ) [8]. The step-like DOS of QWs enhances the differential gain. The strain reduces the valence-band DOS enabling population inversion to be reached with smaller carrier concentration, and has the effect of decreasing linewidth, chirp and the threshold current, and increasing slope efficiency, output power, and differential gain [9].

QWs based on quaternary materials offer the advantage of freely designing the emission wavelength and the strain. For the quaternary material system AlGaInAs, Aluminum is used to increase the energy gap while Indium increases the compressive strain in the active region or decreases the energy gap. Unfortunately, a high Aluminum content leads to alloy scattering and lowers the carrier confinement in the active region. On the other hand, an increasing Indium content requires a reduction of the growth temperature and a higher V/III ratio. This means that only wave lengths between 1.3 and 2.2  $\mu$ m can be achieved with relative high gain and a low photoluminescence linewidth [10].

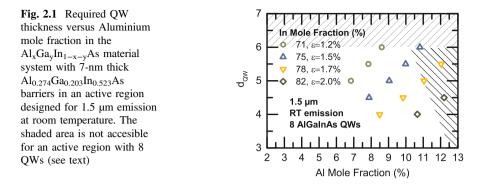

The quaternary material system AlGaInAs lattice matched to InP for 1.5 µm emission wavelength provides good electron confinement in the active region thanks to its high  $\Delta E_c / \Delta E_c$  ratio, compared with the almost equivalent material system GaInAsP. Furthermore, comprising only one group-V element, AlGaInAs grown with solid source MBE enables sharp interfaces and gives the possibility of implementing very high strain in the active region (up to 2%). The required thickness of an 1.5-µm AlGaInAs QW with 7-nm thick Al<sub>0.274</sub>Ga<sub>0.203</sub>In<sub>0.523</sub>As barrier is plotted in Fig. 2.1 versus the Aluminium mole fraction and for compressive strain ranging from 1.2 to 2.0%, generated by increasing the Indium content. Assuming an active region with 8 QWs to enhance the differential gain [11], the lateral shaded area represents thickness-strain combinations which exceed the dislocation-free critical thickness [12]. Under the same assumption, the upper shaded area would lead to an active region thicker than one quarter of the emission wavelength, which means a negligible increase of confinement factor at the cost of high threshold current density. The thickness of the QWs can be optimized within these boundaries.

#### 2.1.2 Hybrid-Cavity Concepts

A common approach used to boost the small-signal modulation bandwidth of semiconductor lasers is the reduction of the photon lifetime. On one hand, the

**Fig. 2.2** Schematic of a DBR with quarter-wave stacks of layers with pairwise varying refractive index

relaxation resonance frequency of VCSELs is inversely proportional to the square root of the photon lifetime. On the other hand, the damping increases proportionally to the square of the relaxation resonance frequency, and the slope of its growth is proportional to the photon lifetime. The different approaches used to decrease the photon lifetime are the increase of mirror losses [13, 14] or the reduction of the effective cavity length [2, 15]. The last approach is the subject of this subsection. A hybrid dielectric/semiconductor cavity is introduced where a semiconductor cavity is combine with dielectric DBRs to achieve a strong confinement of the field in the active region.

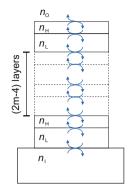

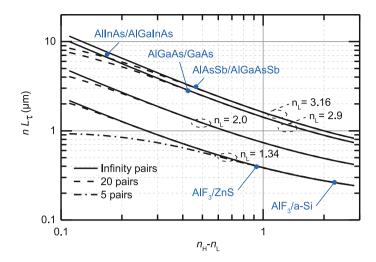

DBRs are quarter-wave stacks of layers with alternating refractive index, as shown schematically in Fig. 2.2. The light is incident from a medium with refractive index  $n_{\rm I}$  and penetrates in a DBR made of *m* layers with alternating low and high refractive indexes  $n_{\rm L}$  and  $n_{\rm H}$ . The light is than outcoupled to a medium with an index  $n_{\rm O}$ . The *phase penetration depth* is defined as the depth at which the optical field appears to be reflected by a constant-phase mirror. It is common practice to define the *energy penetration depth* as the depth at which the energy density falls to 1/e of its initial value. These definitions give similar results for a large number of mirror pairs or for an outcoupling interface with high refractive index ratio. The reflection delay time  $\tau_m$  of a DBR with m/2 pairs at the Bragg frequency  $f_B$  is given from the exact relation [16]:

$$\tau_m = \frac{1}{2f_B} \cdot \frac{q}{1-p} \cdot \frac{(1-a^2p^{m-1})(1-p^m)}{(1-q^2a^2p^{2m-2})}$$

(2.1)

where

$$q = \frac{n_{\rm L}}{n_{\rm I}}, p = \frac{n_{\rm L}}{n_{\rm H}}, a = \frac{n_{\rm O}}{n_{\rm H}}.$$

(2.2)

The optical phase penetration depth  $L_{\tau}$  is defined as  $nL_{\tau} = c\tau_m/2$  where *n* is assumed, for simplicity, to be a common refractive index of the cavity. The optical phase penetration depth is plotted in Fig. 2.3 as a function of the difference between

**Fig. 2.3** Optical phase penetration depth in a DBR as a function of the difference between the refractive indexes of the two mirror's material for different  $n_L$  and for fixed values  $n_I = 3.16$  and  $n_O = 1.00$  at the Bragg wavelength of 1.55 µm for infinite number of layers (*solid line*), 20 pairs (*dash line*) and 5 pairs (*dash-dot line*). Commonly used material' pairs for DBRs are shown

the refractive indexes of the two mirror's materials and for different refractive indexes  $n_L$ . This plot refers to DBRs placed on top of InP and outcoupling to air, and designed at the Bragg wavelength of 1.55 µm. It gives a nice overview of the penetration depth linked to several DBR' material systems. Properly chosen dielectric DBRs, such as AlF<sub>3</sub>/Si, have optical penetration depths that are one order of magnitude shorter than semiconductor ones, such as AlInAs/AlGaInAs.

The DBRs commonly used for GaAs-based VCSELs consist of binary and ternary semiconductor compounds such as AlAs and AlGaAs alloys. They offer several advantages such as high refractive-index contrast between the layers and low thermal resistivity. Semiconductor DBRs for InP-based devices are instead based on ternary and quaternary compounds such as AlInAs and AlGaInAs alloys, which have low refractive-index contrast that is long propagation depth, and high thermal resistivity. The latter is due to phonon-phonon interactions and phonon scattering with lattice defects, and increases with the number of foreign atoms added to a host lattice [10]. AlGaAsSb/AlAsSb DBRs latticed-matched to InP offer a higher refractive-index contrast but have poor electrical and thermal conductivities [17]. Different approaches such as InP/air-gaps [18] or dielectric DBRs [2] have been explored to shorten the propagation length of the field in the mirror, but the low thermal conductivity of those DBRs challenges the VCSEL's stationary and dynamic performance. In order to overcome this limitation, wafer-fused AlGaAs/ GaAs DBRs have been demonstrated to combine high-refractive index contrast and low thermal resistance [19].

An alternative to DBRs are high-contrast gratings (HCGs). A HCG is a near-wavelength grating made of a high refractive-index material and surrounded by a low-index material. 1.55-µm InP-based HCG VCSELs feature broadband and high reflectivity for surface-normal incident light with field polarization that can be designed to be either parallel or orthogonal to the elongated elements of the grating [20].

#### 2.1.3 Tunnel-Junction Laser

For energy-efficient and single-mode operation, current and optical field have to be confined such that the fundamental optical mode is electrically excited, and optical losses are minimized. Both current and optical confinement can be achieved in VCSELs by means of current apertures realized by structured buried tunnel junctions (BTJ).

For GaAs-based VCSELs, a current aperture is typically achieved through radial *selective oxidation* of  $Al_xGa_{1-x}As$  layers where *x* is near to 0.98 [21]. The oxidation rate changes by more than two orders of magnitude by varying *x* from 0.8 to 1 [22]. The large lattice constant mismatch between AlGaAs alloy and InP prevents the integration of this material system on InP-based long wavelength devices. The related material system  $Al_xIn_{1-x}As$  is lattice matched to InP for x = 0.5, leading to a low oxidation rate. Furthermore, the AlInAs native oxide differs from that reported for AlGaAs due to the composite structure of the oxide related to the low Al content [23]. Another technique used to achieve current confinement in GaAs-and InP-based devices is *ion implantation*, which produces highly resistive regions in the semiconductor cavity. These VCSELs present the advantage of a planar device geometry. However, the lack of inherent optical confinement can lead to varying threshold and modulation limitations [24].

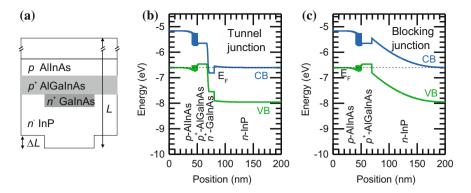

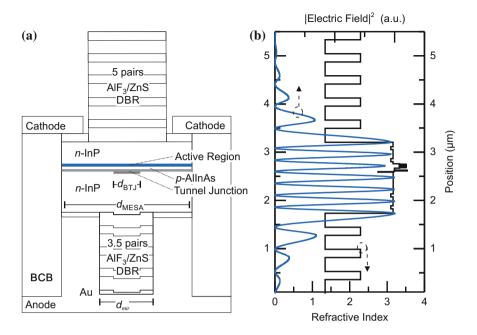

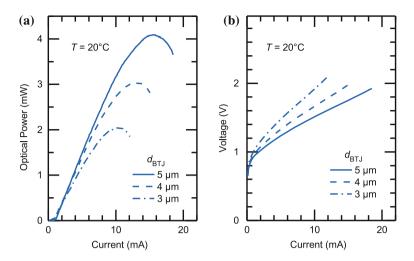

For InP-based VCSELs, tunnel junctions consisting of  $p^+$ -AlGaInAs and  $n^+$ -GaInAs have been demonstrated [25]. Current and optical confinement are achieved by etching the  $n^+$ -layer of the tunnel junction in circular-shaped areas and re-growing with *n*-InP to match the desired cavity length as shown in Fig. 2.4a. The etched area acts as a reverse biased *pn*-junction enabling current confinement to the *not* etched area. The band diagrams for the tunnel and blocking junctions are plotted in Fig. 2.4b and c, respectively. This method offers the great advantage of defining the aperture by simple optical lithography but raises the challenges related to re-grow of the structured junction. Re-growing with solid source MBE will *not* flatten the etched structure, which is reproduced at the upper mirror/semiconductor interface. The effect will be an effective fiber-like waveguiding with refractive index contrast  $\Delta n_{eff}$  depending on the height of the overgrown tunnel junction ( $\Delta L$ ):

$$\frac{\Delta n_{eff}}{n_{eff}} = \frac{\Delta L}{L},\tag{2.3}$$

where L is the cavity length and  $n_{eff}$  is the effective refractive index [26]. Corresponding to the diameter of the fiber's core, the diameter of the tunnel junction will

Fig. 2.4 a Schematic cross-section of a BTJ. Simulated band diagram b of a  $p^+$ -AlGaInAs/ $n^+$ -GaInAs tunnel junction, and c of a reverse-biased  $p^+$ -AlGaInAs/n-InP diode

determine how many transverse modes can propagate in the cavity. Single mode operation and high output power can be achieved by choosing this diameter sufficiently small as will be shown in the next section.

One of the main advantages of a tunnel junction is the reduction of the series resistance of VCSELs. The active region of long-wavelength VCSELs is typically embedded between an *n*-InP and a *p*-AlInAs, which, due to their band offset, offer effective carrier confinement to the active region. However, the poor electrical, thermal and optical properties of AlInAs motivate the need for reducing its thickness. This can be achieved by means of a low-resistive tunnel junction allowing to reduce the thickness of the AlInAs layer to less than one quarter of the emission wavelength, and to match the desired total cavity length using low-resistive *n*-InP instead.

#### 2.2 Single-Mode 1.55-µm Short-Cavity VCSELs

Short-reach communication links and networks can employ 850-nm or 980-nm VCSELs, which emit typically in multiple transverse modes. However, signals carried by fundamental transverse modes with narrow linewidths can be transmitted over longer distances by limiting the chromatic dispersion of the fiber. For this reason, access and metropolitan networks are established on single-mode fiber motivating the need for single-mode 1.3- and 1.55-µm VCSELs.

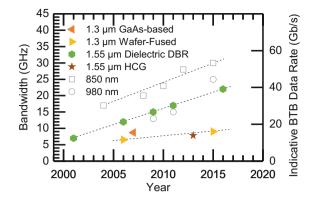

The historical growth of the small-signal modulation bandwidth of short- and long-wavelength VCSELs is shown in Fig. 2.5. While short-wavelength devices have achieved bandwidths up to 30 GHz [1] by 2015, long-wavelength VCSELs show inferior modulation capabilities. The technological issues related to the bandwidth scaling of InP-based devices have been discussed in Sect. 2.1 and are related to the lack of semiconductor DBRs with low thermal resistivity, high

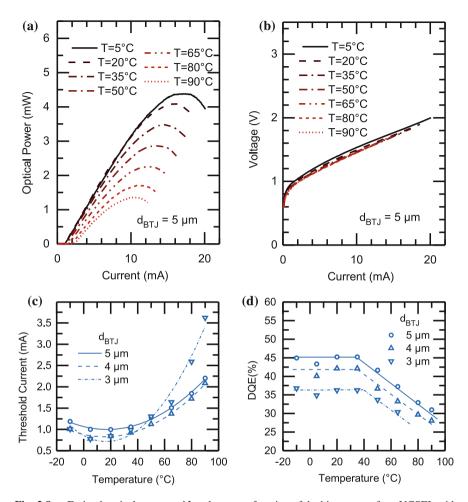

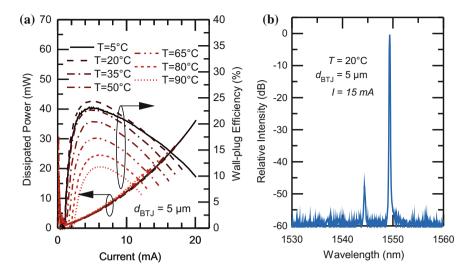

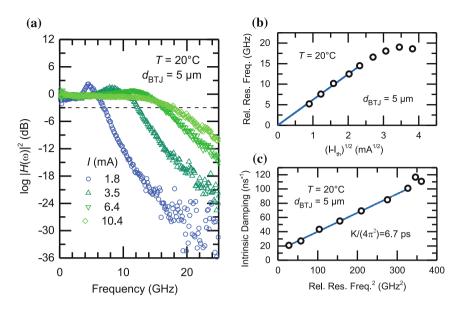

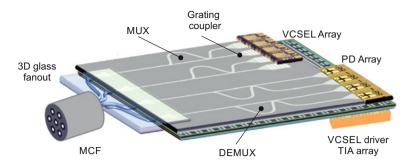

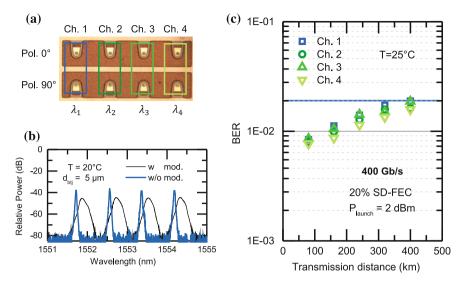

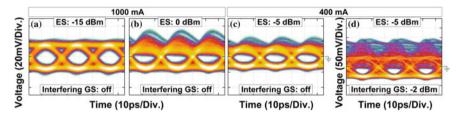

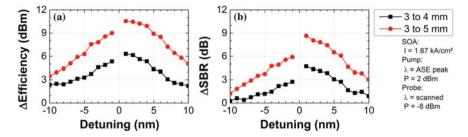

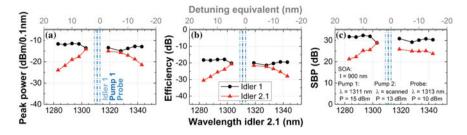

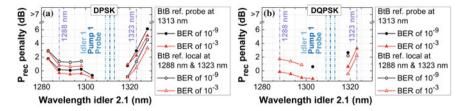

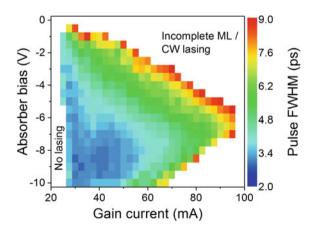

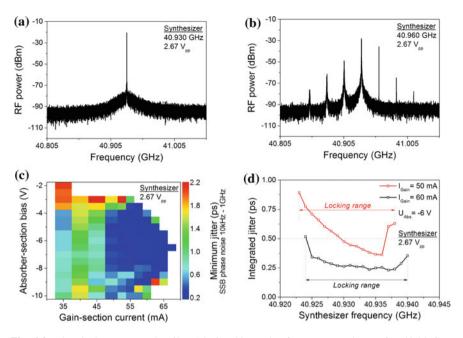

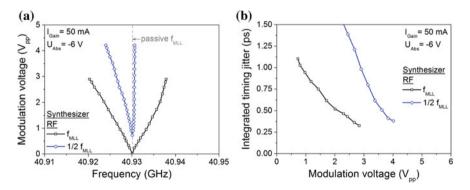

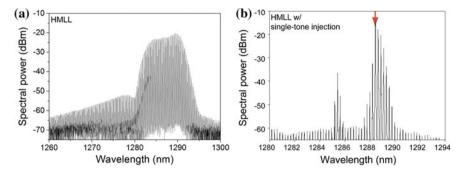

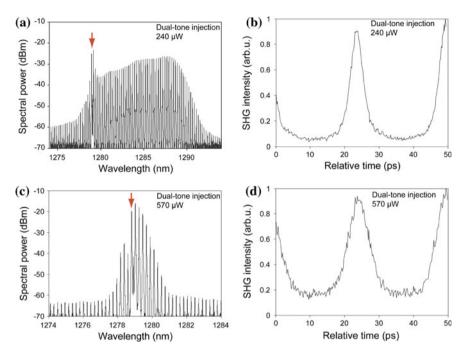

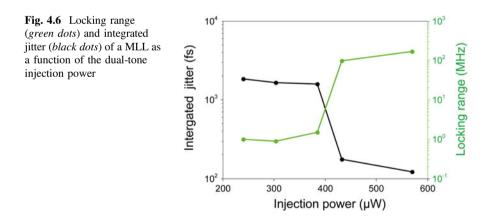

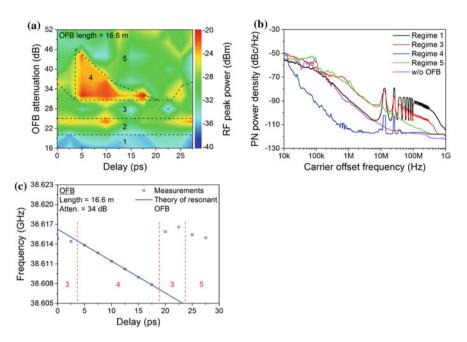

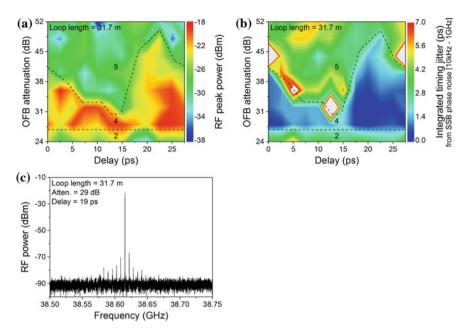

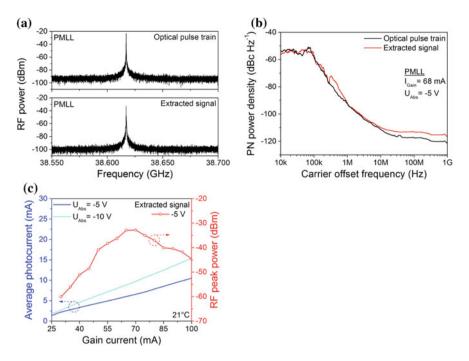

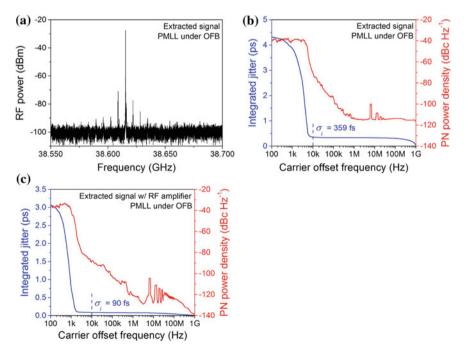

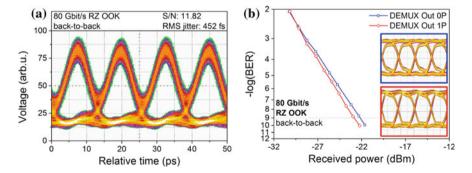

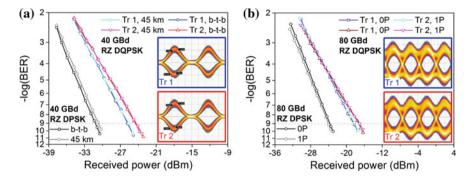

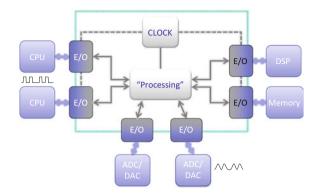

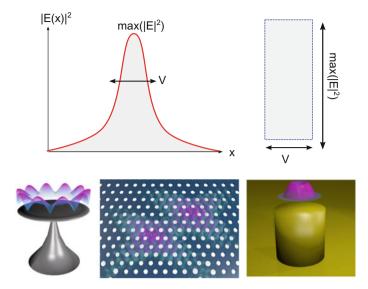

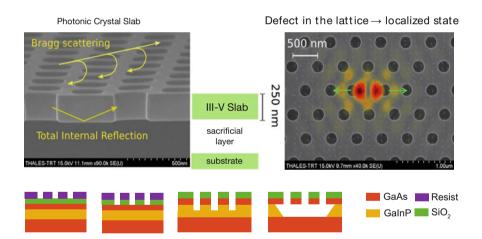

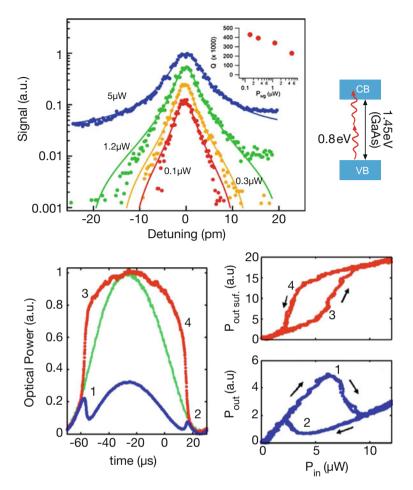

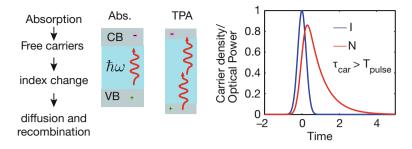

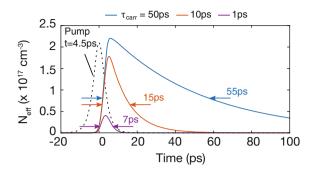

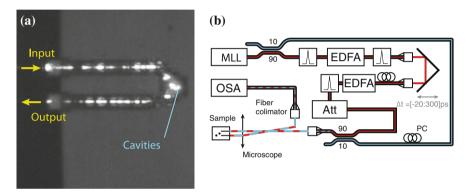

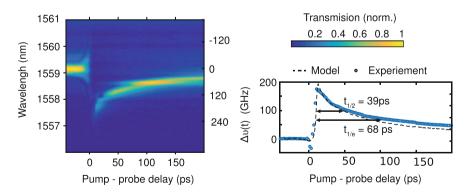

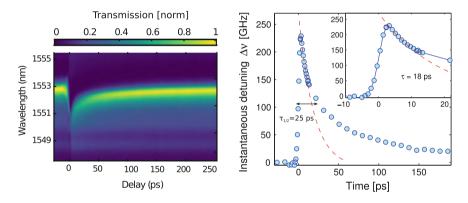

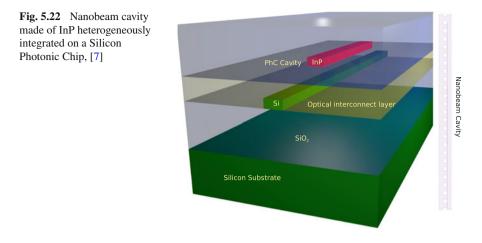

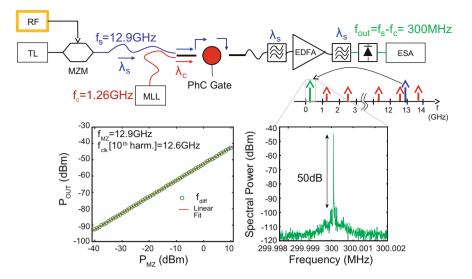

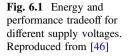

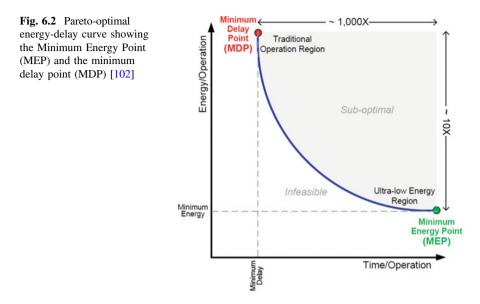

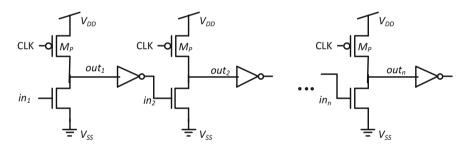

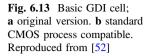

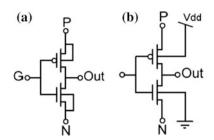

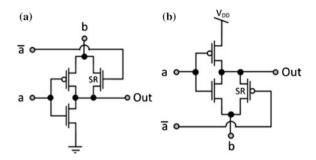

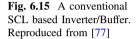

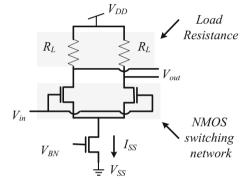

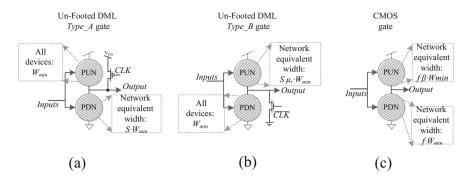

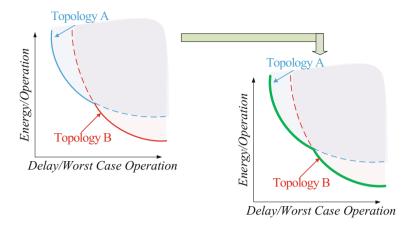

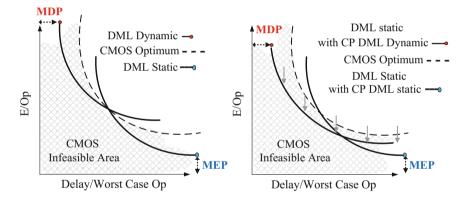

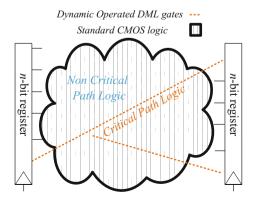

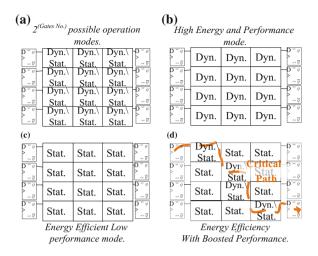

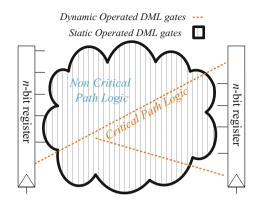

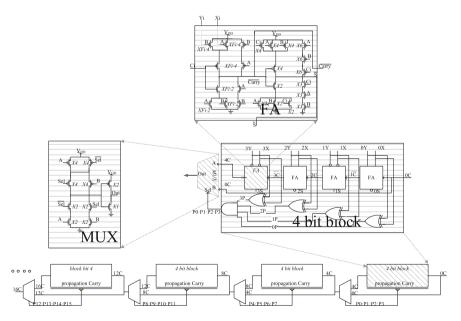

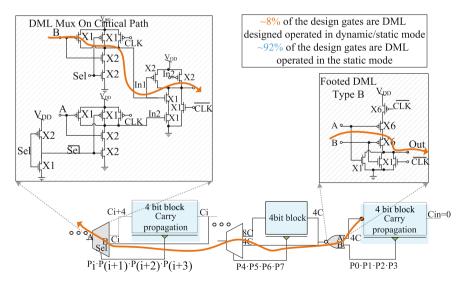

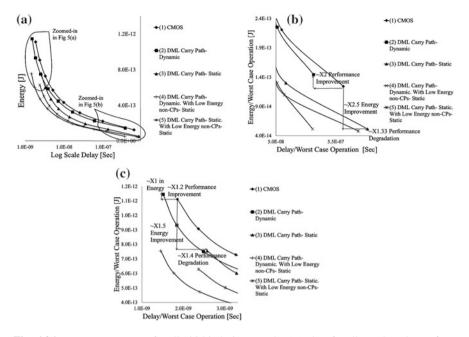

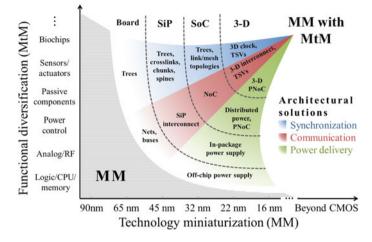

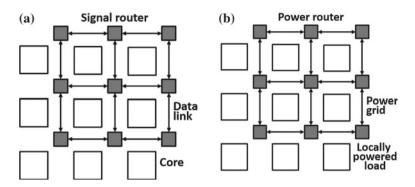

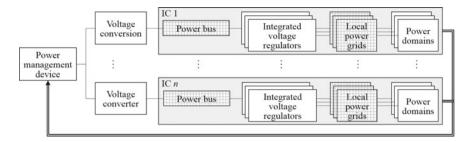

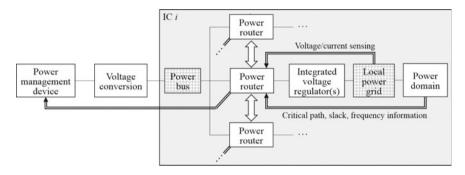

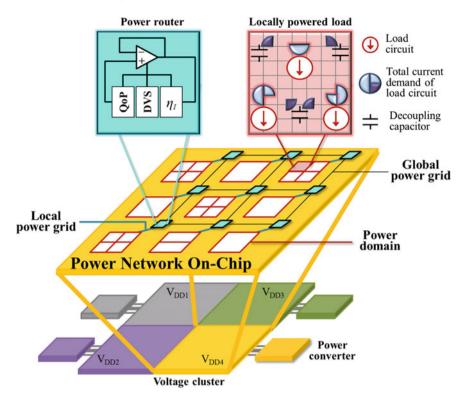

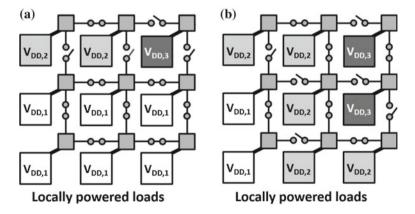

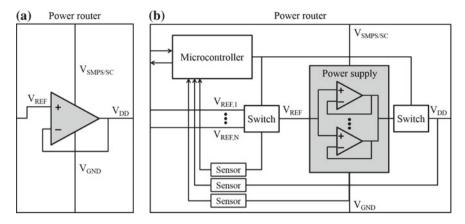

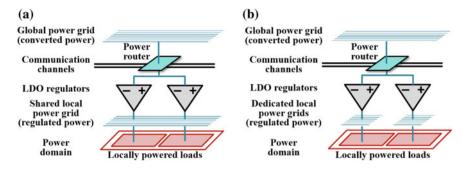

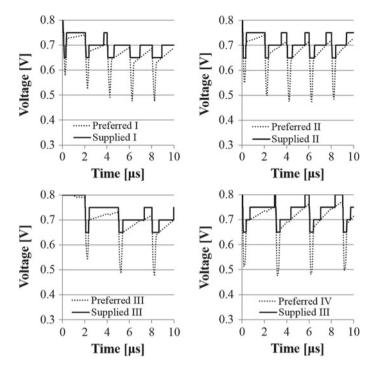

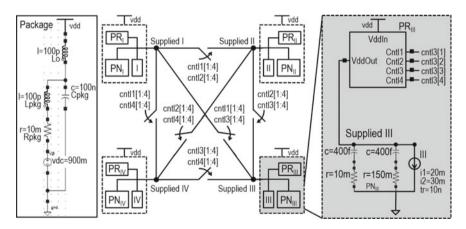

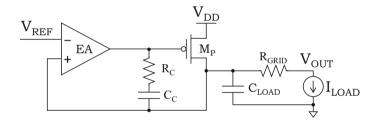

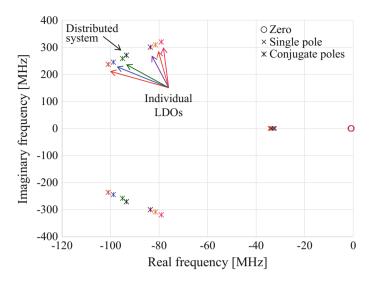

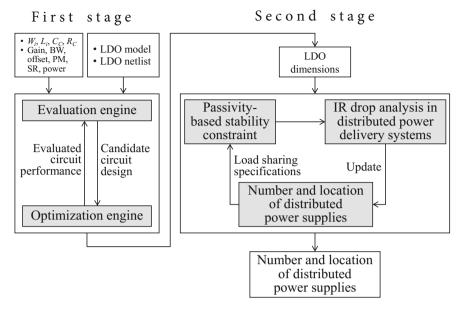

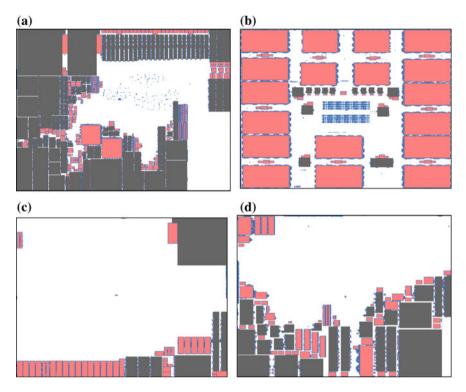

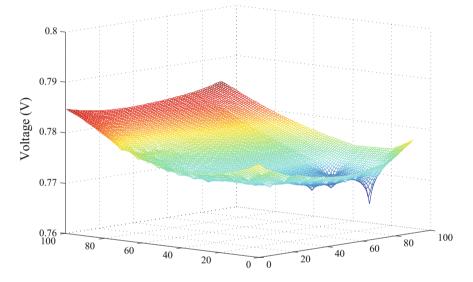

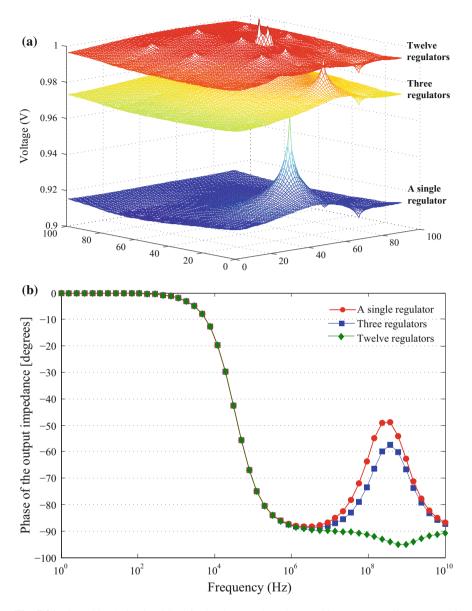

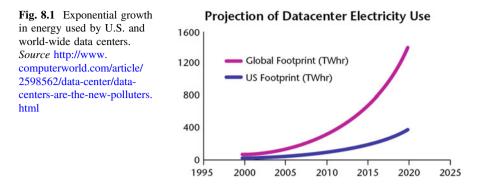

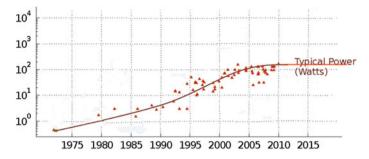

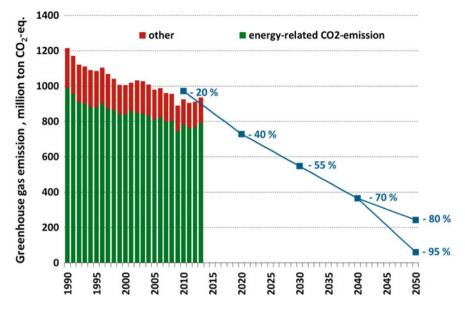

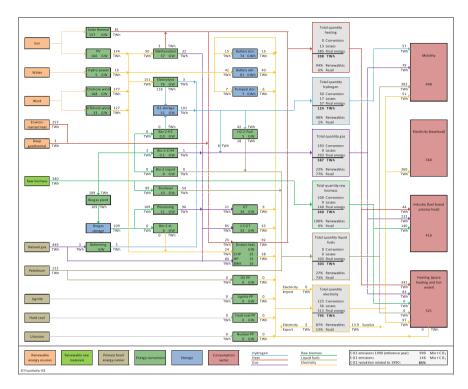

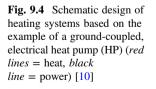

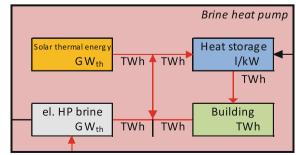

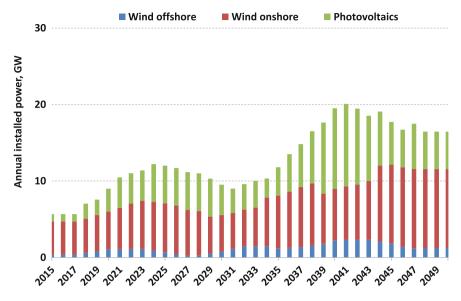

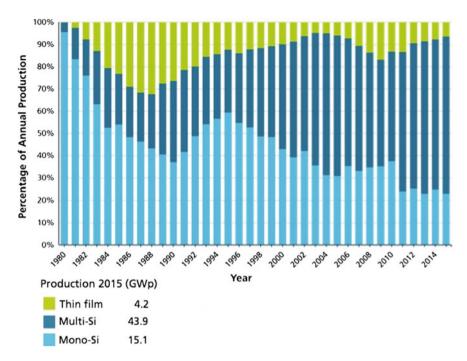

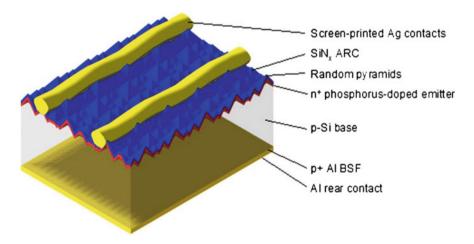

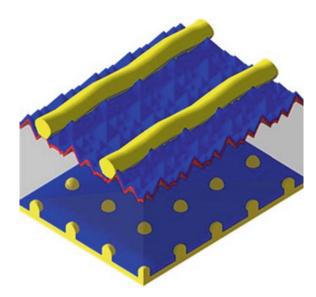

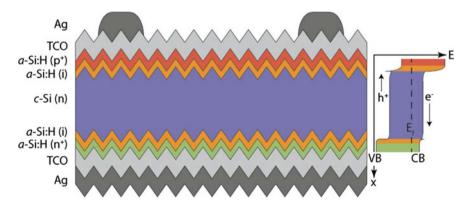

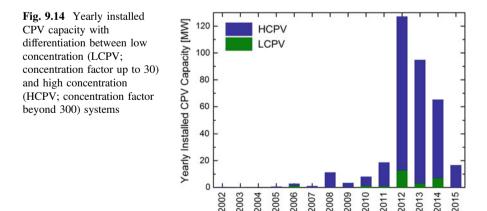

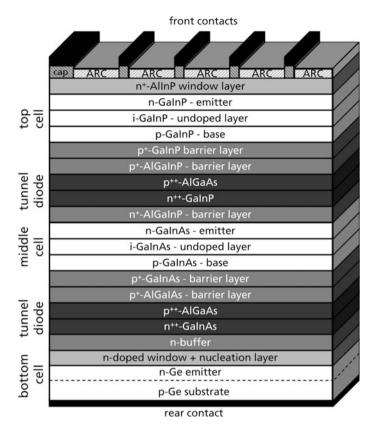

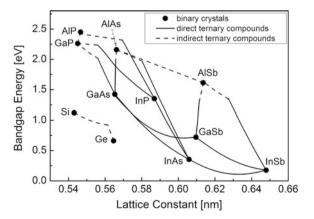

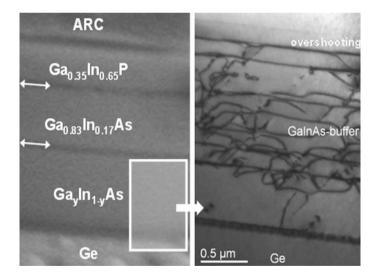

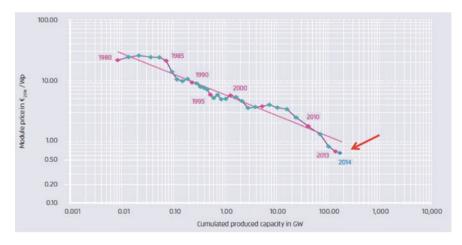

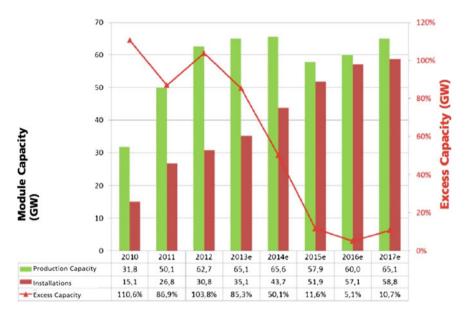

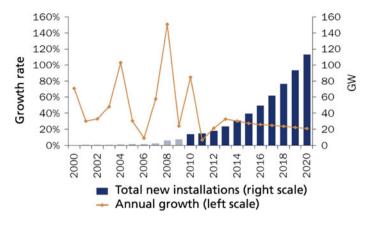

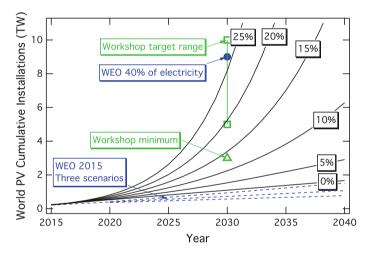

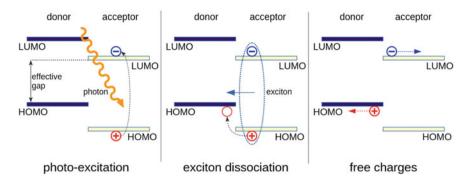

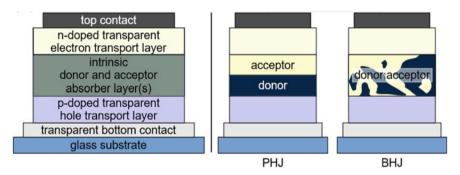

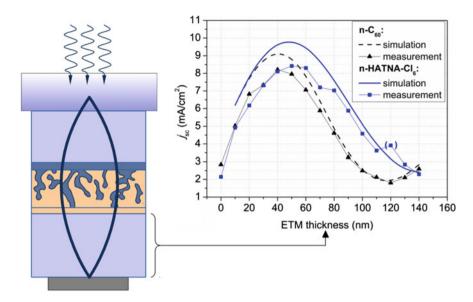

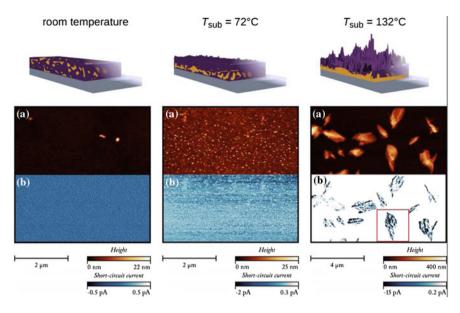

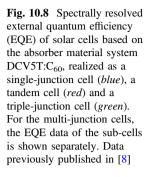

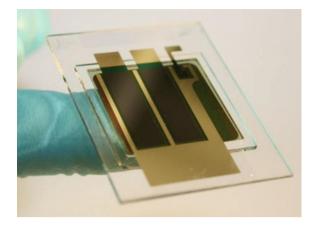

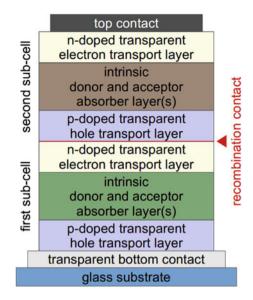

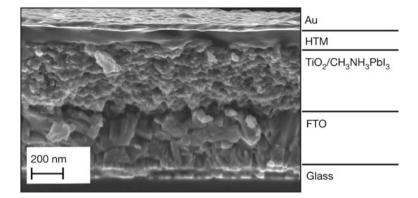

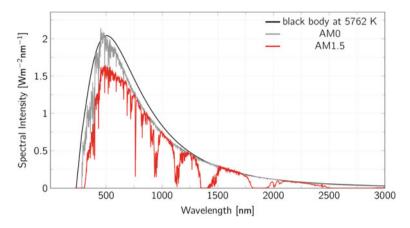

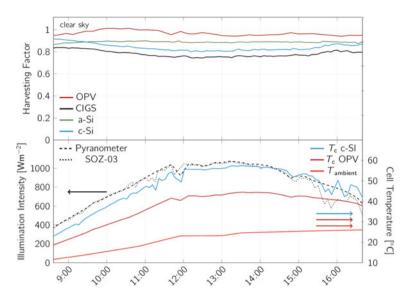

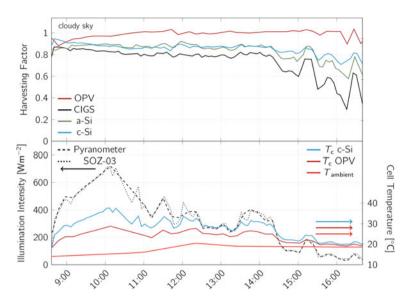

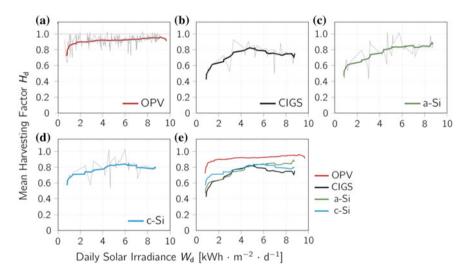

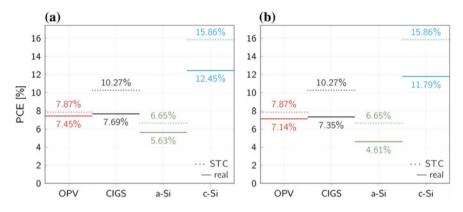

**Fig. 2.5** Temporal evolution of the small-signal bandwidth for 1.3- and 1.55-μm VCSEL. For comparison, GaAs-based VCSELs are included (grey)