# Chemical Mechanical Polishing in Silicon Processing

Volume Editors

Shin Hwa Li

**Robert O. Miller**

SEMICONDUCTORS AND SEMIMETALS VOLUME 63 Treaties Editors: Robert K. Willardson and Elsie R. Weber

## **Chemical Mechanical Polishing in Silicon Processing**

SEMICONDUCTORS AND SEMIMETALS Volume 63

### Semiconductors and Semimetals

A Treatise

Edited by R. K. Willardson Consulting Physicist Spokane, Washington

Eicke R. Weber Department of Materials Science and Mineral Engineering University of California at Berkeley

## **Chemical Mechanical Polishing in Silicon Processing**

SEMICONDUCTORS AND SEMIMETALS

Volume 63

Volume Editors SHIN HWA LI ROBERT O. MILLER

ACADEMIC PRESS San Diego San Francisco New York Boston London Sydney Tokyo This book is printed on acid-free paper.  $(\infty)$

COPYRIGHT (C) 2000 BY ACADEMIC PRESS

ALL RIGHTS RESERVED.

NO PART OF THIS PUBLICATION MAY BE REPRODUCED OR TRANSMITTED IN ANY FORM OR BY ANY MEANS, ELECTRONIC OR MECHANICAL, INCLUDING PHOTOCOPY, RECORDING, OR ANY INFORMATION STORAGE AND RETRIEVAL SYSTEM, WITHOUT PERMISSION IN WRITING FROM THE PUBLISHER.

Requests for permission to make copies of any part of the work should be mailed to: Permissions Department, Harcourt, Inc., 6277 Sea Harbor Drive, Orlando, Florida, 32887-6777

The appearance of the code at the bottom of the first page of a chapter in this book indicates the Publisher's consent that copies of the chapter may be made for personal or internal use of specific clients. This consent is given on the condition, however, that the copier pay the stated per-copy fee through the Copyright Clearance Center, Inc. (222 Rosewood Drive, Danvers, Massachusetts 01923), for copying beyond that permitted by Sections 107 or 108 of the U.S. Copyright Law. This consent does not extend to other kinds of copying, such as copying for general distribution, for advertising or promotional purposes, for creating new collective works, or for resale. Copy fees for pre-1999 chapters are as shown on the title pages; if no fee code appears on the title page, the copy fee is the same as for current chapters. 0080-8784/00 \$30.00

ACADEMIC PRESS A Harcourt Science Technology Company 525 B Street, Suite 1900, San Diego, CA 92101-4495, USA http://www.academicpress.com

ACADEMIC PRESS 24–28 Oval Road, London NW1 7DX, UK http://www.academicpress.com

International Standard Book Number: 0-12-752172-0 International Standard Serial Number: 0080-8784

PRINTED IN THE UNITED STATES OF AMERICA 99 00 01 02 03 04 EB 9 8 7 6 5 4 3 2 1

## Contents

| Preface                                                                                           | xi<br>xiii |

|---------------------------------------------------------------------------------------------------|------------|

| Chapter 1 Introduction                                                                            | 1          |

| Frank B. Kaufman                                                                                  |            |

| I. CMP: A UNIQUE AND EVOLVING SEMICONDUCTOR FABRICATION<br>TECHNOLOGY—PAST, PRESENT, AND FUTURE   | 1          |

| Fabrication Technology                                                                            | . 2        |

| 2. CMP: The Current State of the Art<br>3. The Evolution of CMP Technology into the New Millenium | 3          |

| Chapter 2 Equipment                                                                               | 5          |

| Thomas Bibby and Karey Holland                                                                    |            |

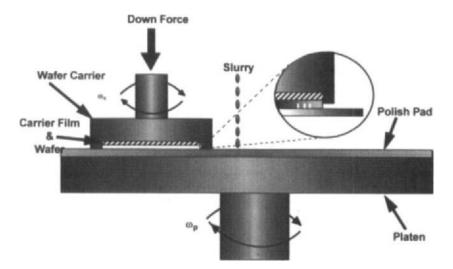

| I. INTRODUCTION                                                                                   | 5<br>8     |

| 1. Throughput Improvement                                                                         | 9<br>10    |

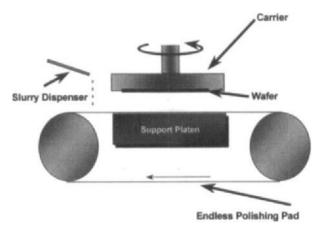

| 3. Second-Generation Polishers                                                                    | 11         |

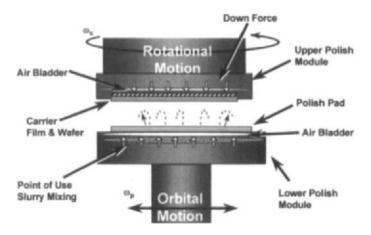

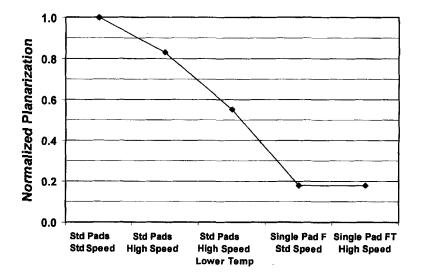

| 4. Third-Generation CMP Equipment                                                                 | 13         |

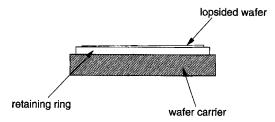

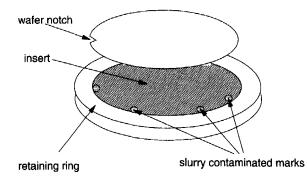

| III. CARRIERS                                                                                     | 16         |

| 1. Gimbaled Carriers                                                                              | 20<br>21   |

| 3. Linear Polisher and Pressure Control                                                           | 21         |

| IV. PLATENS                                                                                       | 24         |

| 1. Temperature Control                                                                            | 24         |

| 2. Orbital Polisher and Direct Slurry Delivery                                                    | 25         |

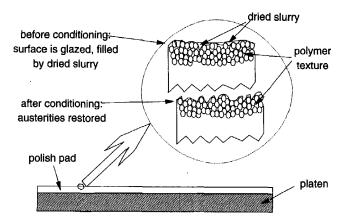

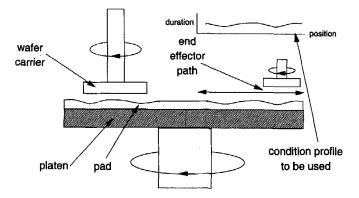

| V. Pad Conditioning                                                                               | 25         |

| VI. CMP Equipment Integration                                                                     | 30         |

| 1. Post-CMP Cleaning                                                                              | 30         |

| 2. Integrated Metrology                                                                           | 35         |

| 3. Slurry Reprocessing                                                                            | 37         |

| VII. COPPER POLISHING AND CMP TOOL REQUIREMENTS | 38  |

|-------------------------------------------------|-----|

| VIII. 300-MM CMP Tools                          | 40  |

| IX. CONCLUSION                                  | 41  |

| <b>References</b>                               | 42  |

|                                                 |     |

|                                                 |     |

| Chapter 3 Facilitization                        | 47  |

| John P. Bare                                    |     |

| L INTRODUCTION                                  | 47  |

| II. OUTLINE                                     | 48  |

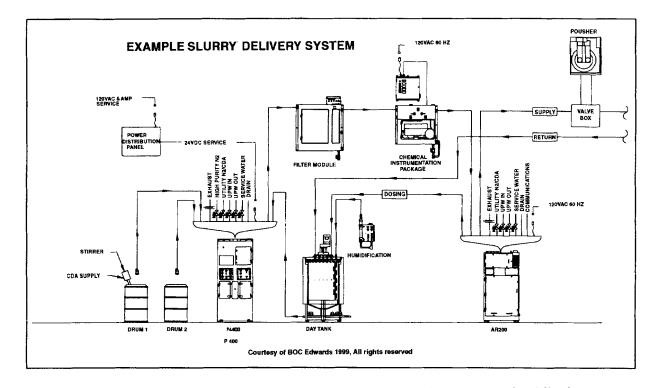

| III. SLURRY DISTRIBUTION SYSTEM OVERVIEW        |     |

| IV. SLURRY HANDLING                             | 49  |

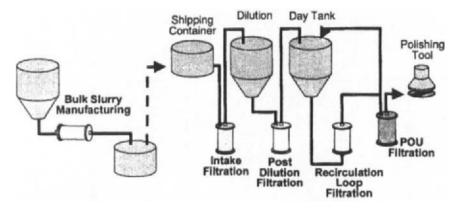

| V. SLURRY DISTRIBUTION SYSTEMS                  | 52  |

| VI. SLURRY DISPENSE ENGINES                     | 53  |

| VII. SLURRY BLENDING TECHNOLOGY                 | 54  |

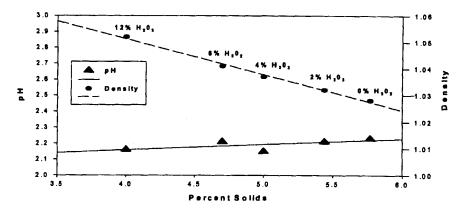

| VIII. SLURRY MEASURING TECHNIQUES               | 55  |

| IX. DAYTANK REPLENISHMENT                       | 59  |

| X. MIX ORDER                                    | 61  |

| XI. PIPING SYSTEMS                              | 62  |

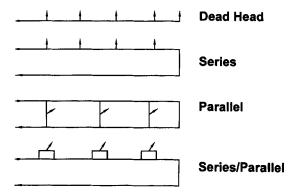

| XII. PIPING SYSTEM VARIATIONS                   | 63  |

| XIII. MATERIALS OF CONSTRUCTION                 | 64  |

| XIV. Slurry Settling                            | 65  |

| XV. SLURRY ROOM LOCATION                        | 66  |

| XVI. Pressure and Flow Consistency              | 66  |

| XVII. BACK-PRESSURE DEVICES                     | 67  |

| XVIII. SLURRY CONSUMPTION RAMP                  | 68  |

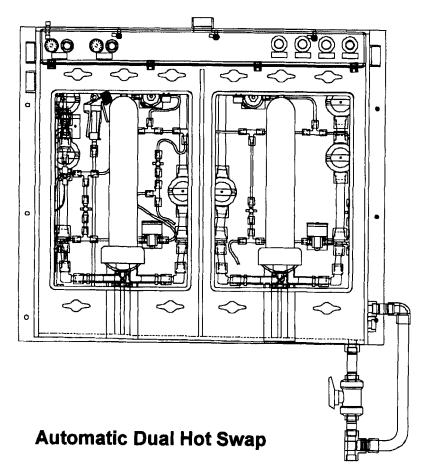

| XIX. System Redundancy                          | 69  |

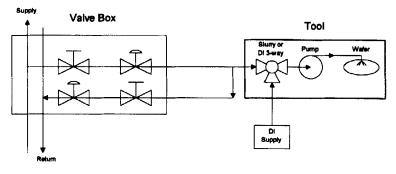

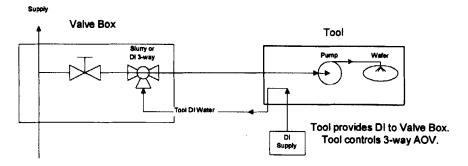

| XX. VALVE BOXES                                 | 69  |

| XXI. STORAGE TANKS                              | 71  |

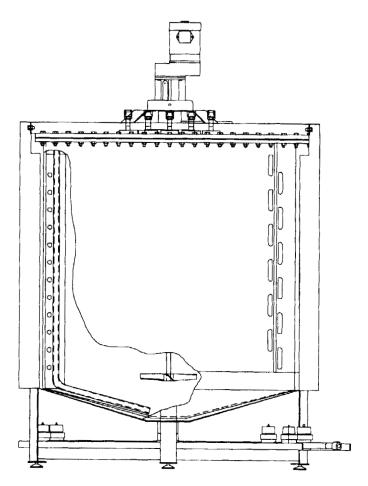

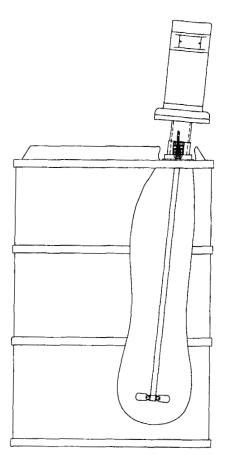

| XXII. AGITATION                                 |     |

| XXIII. METROLOGY                                | 76  |

| XXIV. FILTRATION                                | 78  |

| XXV. SLURRY SYSTEM MAINTENANCE                  | 83  |

| XXVI. WASTE DISPOSAL                            |     |

| References                                      | 87  |

|                                                 |     |

|                                                 |     |

| Chapter 4 Modeling and Simulation               | 89  |

| Duane S. Boning and Okumu Ouma                  |     |

|                                                 | 89  |

| I. INTRODUCTION                                 |     |

| 1. Macroscopic–Bulk Polish Models               |     |

| 2. Sources of Wafer-Scale Nonuniformity         |     |

| 3. Empirical Approaches to Wafer-Level Modeling |     |

| 4. Status of Wafer-Level Modeling               |     |

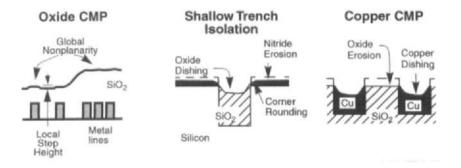

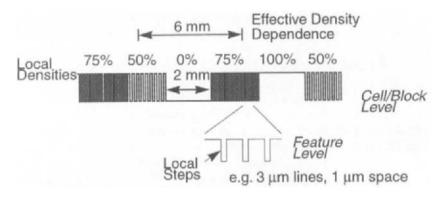

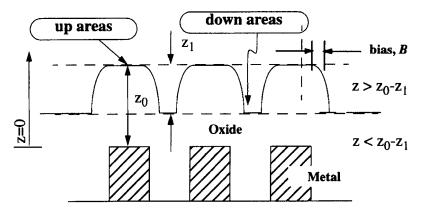

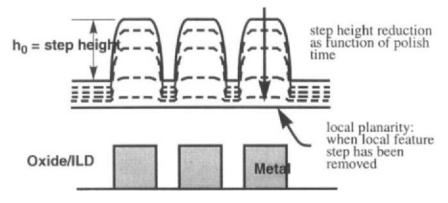

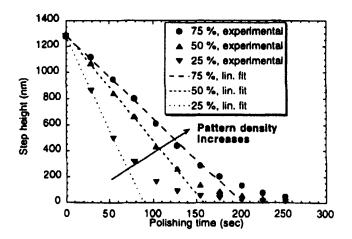

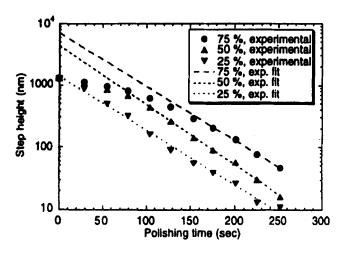

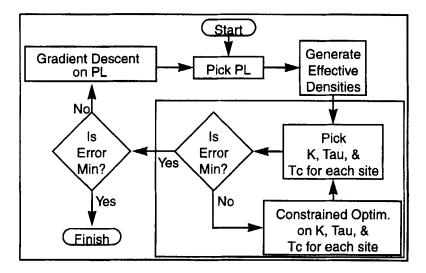

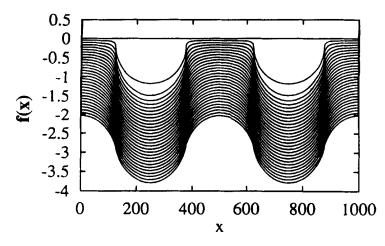

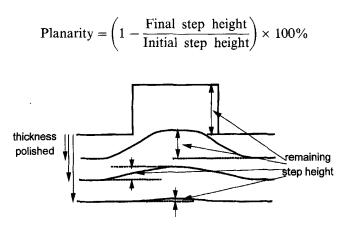

| III. PATTERNED WAFER CMP MODELING               |     |

| 1. Feature-Scale Models                         | 100 |

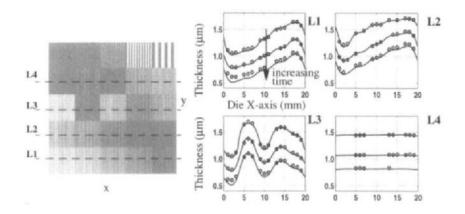

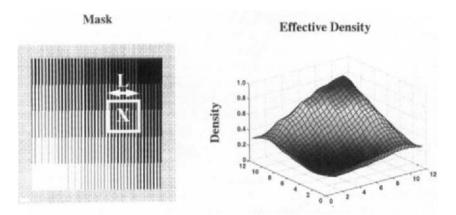

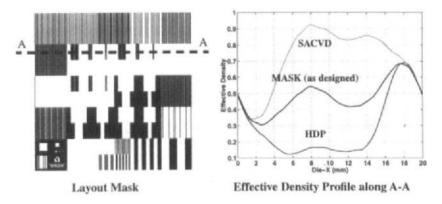

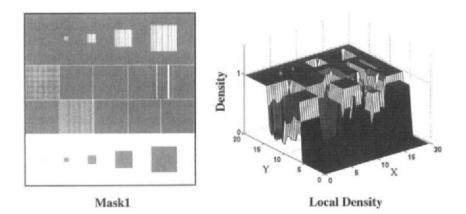

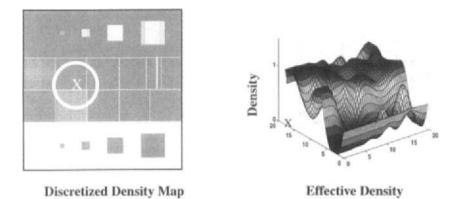

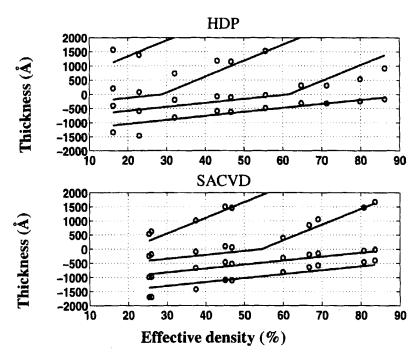

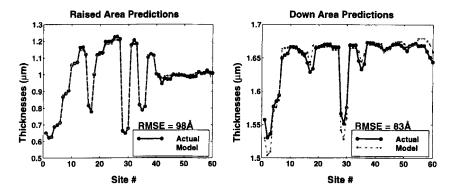

| IV. Die-Level Modeling of ILD CMP               | 104 |

|                                                 |     |

vi

#### CONTENTS

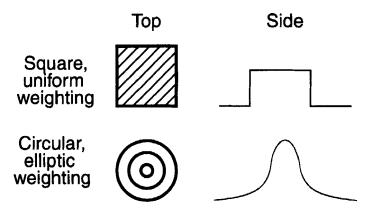

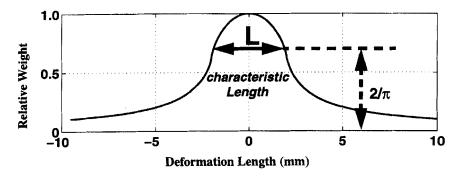

|             | 3. Planarization Length and Response Function               |

|-------------|-------------------------------------------------------------|

|             | 4. Characterization — Determination of Planarization Length |

|             | 5. STI CMP Modeling                                         |

|             | 6. Models for Step Height Reduction                         |

|             | 7. Applications of Density Models                           |

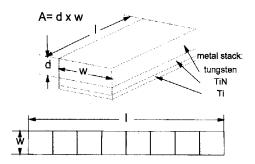

| V.          | MODELS FOR METAL POLISHING                                  |

|             | 1. Tungsten CMP Modeling                                    |

|             | 2. Tungsten CMP — Contact Wear Model                        |

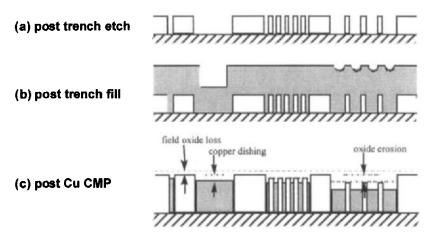

|             | 3. Copper CMP Modeling                                      |

| <b>∕</b> I. | SUMMARY AND STATUS                                          |

|             | References                                                  |

| Cha  | pter 5 Consumables I: Slurry                                           |

|------|------------------------------------------------------------------------|

| Shir | ı Hwa Li, Bruce Tredinnick, and Mel Hoffman                            |

|      |                                                                        |

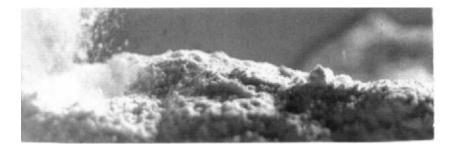

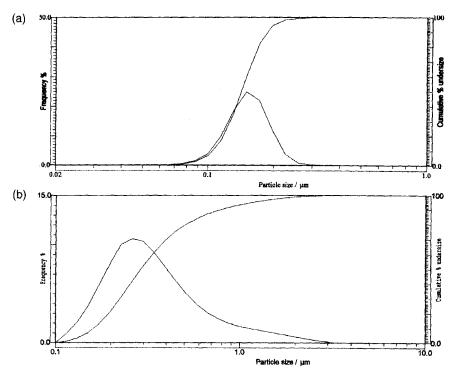

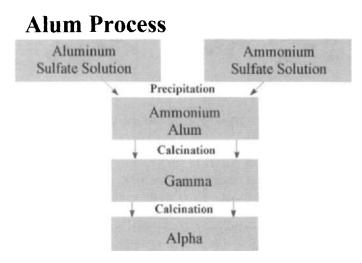

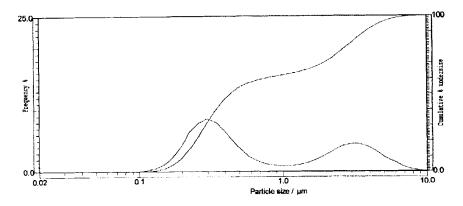

| II.  | Abrasives                                                              |

|      | 1. For Oxide Slurry                                                    |

|      | 2. For Metal Shurry                                                    |

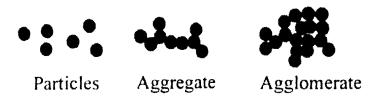

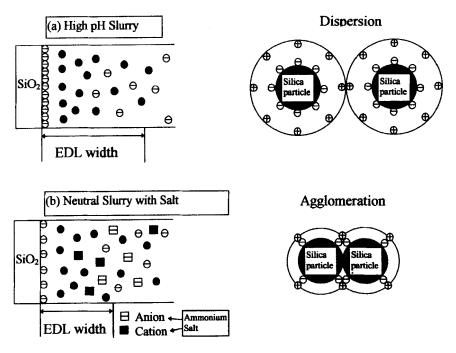

|      | 3. Agglomeration                                                       |

|      | 4. Milling                                                             |

| III. | Slurry Solution                                                        |

|      | 1. For Oxide Slurry                                                    |

|      | 2. For Metal Slurry                                                    |

| IV.  | COMPARISONS AMONG SLURRIES                                             |

|      | 1. Oxide Slurries                                                      |

|      | 2. Tungsten Slurries                                                   |

|      | REFERENCES                                                             |

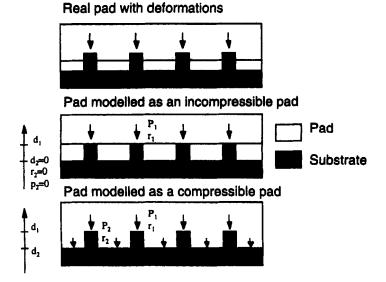

|      | pter 6       CMP ConsumablesII: Pad                                    |

|      |                                                                        |

|      |                                                                        |

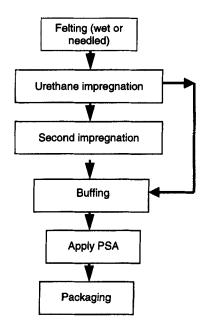

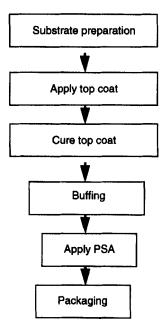

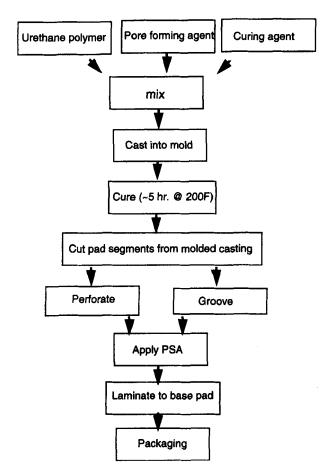

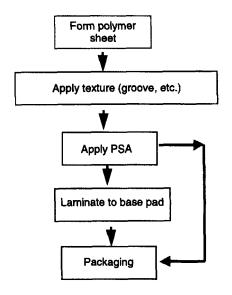

| 11.  | CLASSES OF PADS AND THEIR MANUFACTURE                                  |

|      | 1. Classes of Pads                                                     |

|      | 2. Primary Manufacturing Processes                                     |

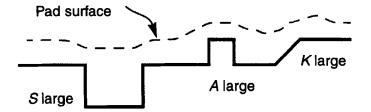

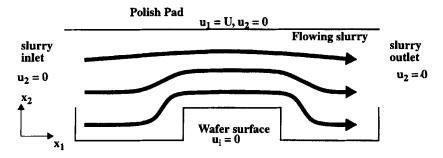

| 111. | STRUCTURE, PROPERTIES, AND THEIR RELATIONSHIP TO THE POLISHING PROCESS |

|      | 1. Local-Level Models for the Polishing Process                        |

|      | 2. Die-Scale Models                                                    |

|      | 3. Wafer-Scale Models                                                  |

|      | 4. Impact of Structure and Properties on the Polishing Process         |

| IV.  | Application to Semiconductor Processing                                |

|      | 1. Dielectric CMP                                                      |

|      | 2. Metal CMP                                                           |

|      |                                                                        |

#### vii

#### CONTENTS

| Chapter 7 Post-CMP Clean                              | 183 |

|-------------------------------------------------------|-----|

| François Tardiff                                      |     |

| I. INTRODUCTION                                       | 183 |

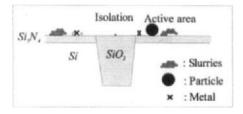

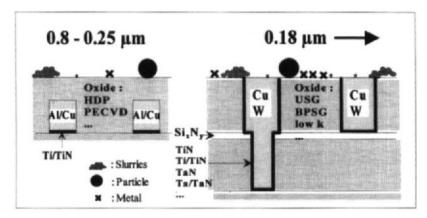

| II. SURFACE CONFIGURATIONS AFTER CMP PROCESSES        | 184 |

| III. CLEANING REQUIREMENTS AFTER CMP PROCESSES        | 184 |

| 1. Particle Effects                                   | 184 |

| 2. Metallic Contamination Effects                     | 185 |

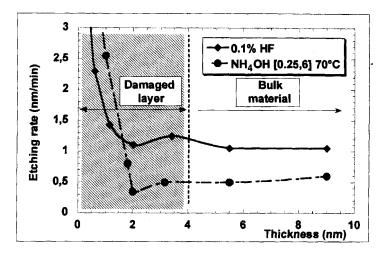

| 3. Damaged-Laver Effects                              | 186 |

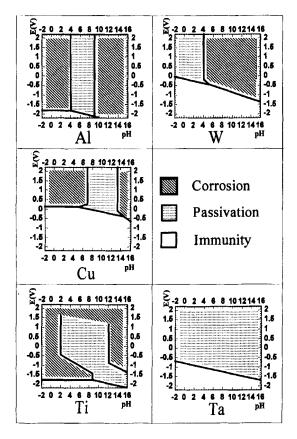

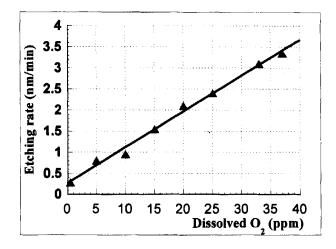

| IV. Corrosion Effects                                 | 186 |

| 1. Electrochemical Corrosion                          | 186 |

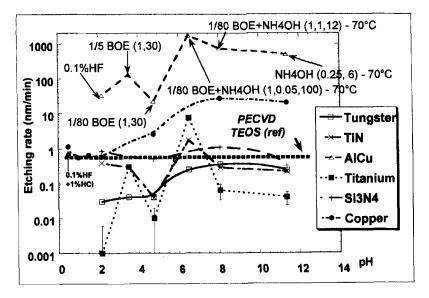

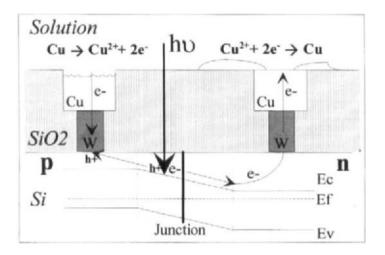

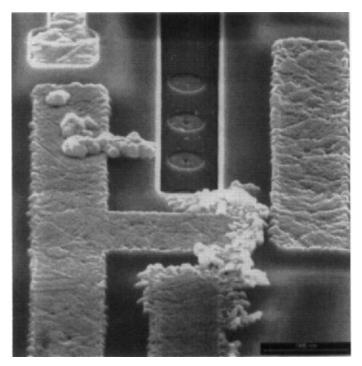

| 2. Photoassisted Corrosion                            | 190 |

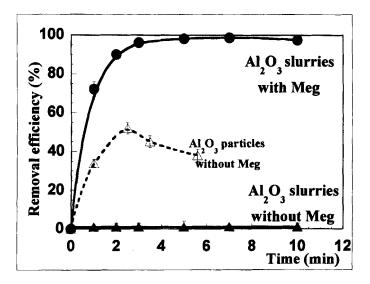

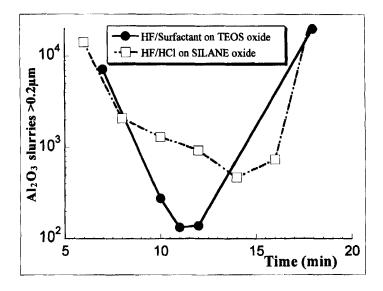

| V. SLURRY REMOVAL                                     | 193 |

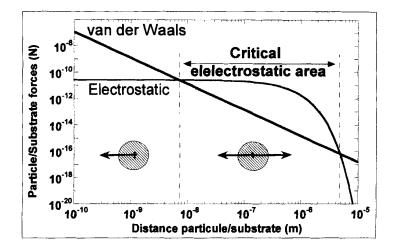

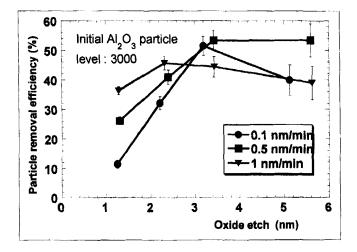

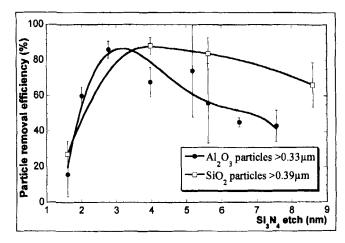

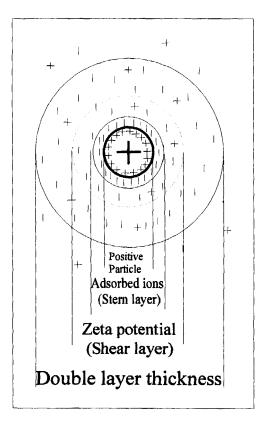

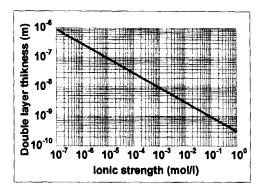

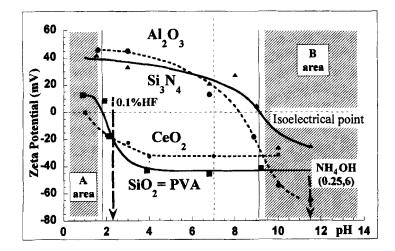

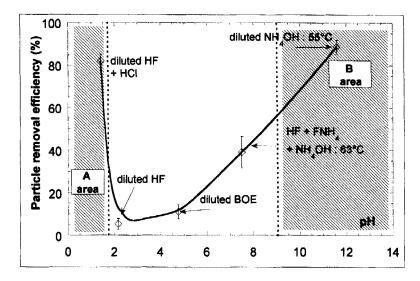

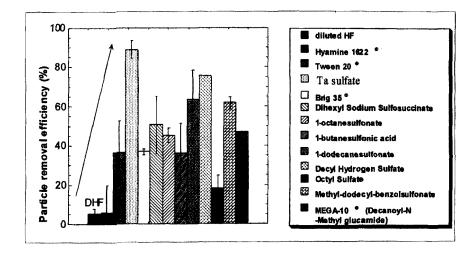

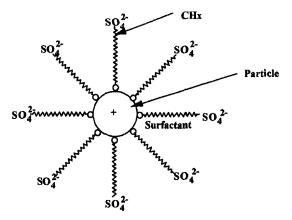

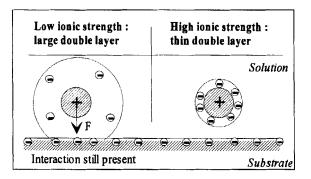

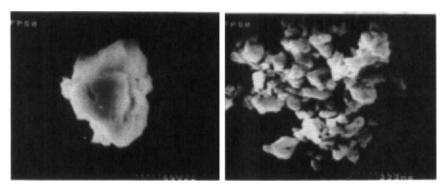

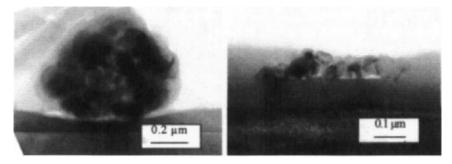

| 1. Particle-Removal Mechanisms                        | 193 |

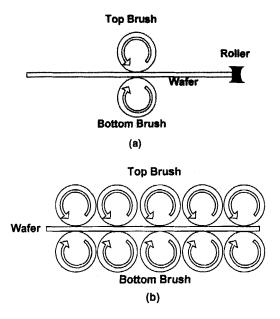

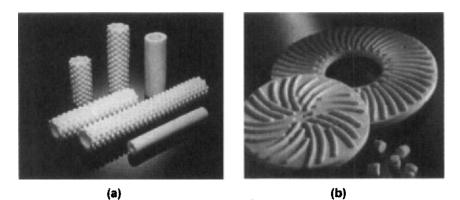

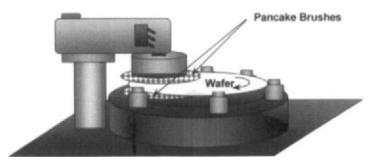

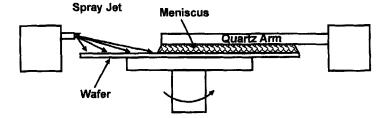

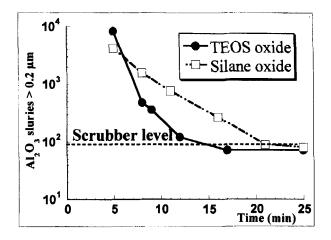

| 2. Scrubber Cleanings                                 | 202 |

|                                                       | 202 |

|                                                       |     |

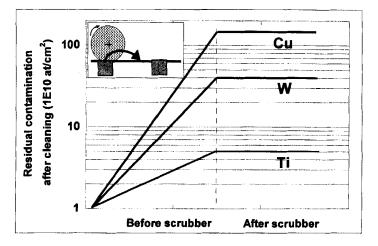

| VI. METALLIC CONTAMINATION REMOVAL                    | 206 |

| 1. Metallic Contamination during the Full CMP Step    | 206 |

| 2. Metallic Contamination Cleaning                    | 207 |

| VII. DAMAGED LAYER REMOVAL                            | 208 |

| 1. Practical Determination of the Damaged Layer       | 209 |

| 2. Elimination of the Damaged Layer                   | 209 |

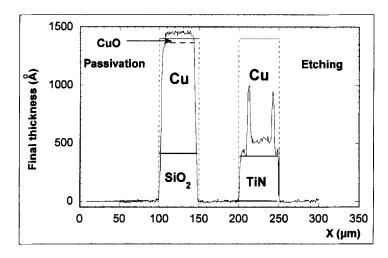

| VIII. FINAL PASSIVATION                               | 210 |

| IX. EXAMPLES OF PRACTICAL POST-CMP CLEANING PROCESSES | 210 |

| 1. STI and Silicon Oxide CMP                          | 211 |

| 2. Tungsten CMP                                       | 212 |

| 3. Copper CMP                                         | 212 |

| X. Conclusion                                         | 213 |

| References                                            | 213 |

| REPERENCES                                            | 215 |

|                                                       |     |

| Chapter 8 CMP Metrology                               | 215 |

| Shin Hwa Li, Tara Chhatpar, and Frederic Robert       |     |

| I. INTRODUCTION                                       | 215 |

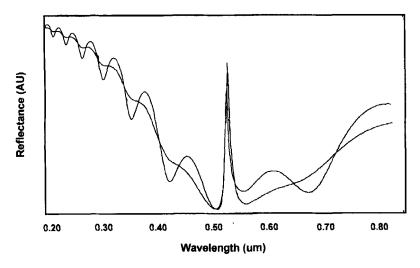

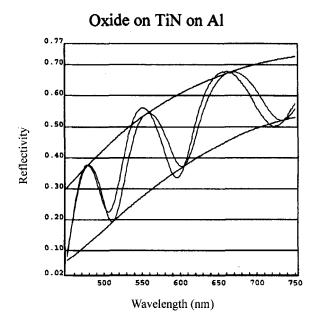

| II. REFLECTOMETRY                                     | 216 |

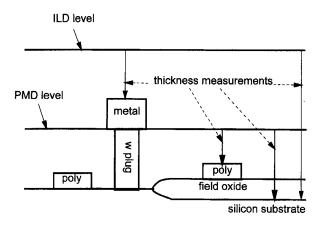

| 1. Substrate Modeling                                 | 218 |

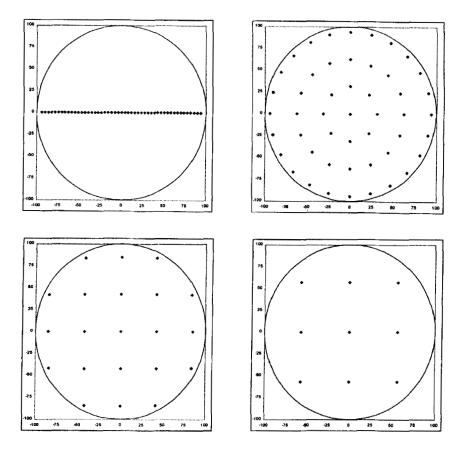

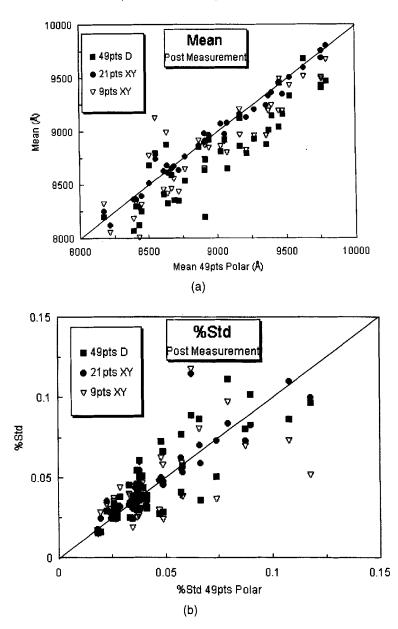

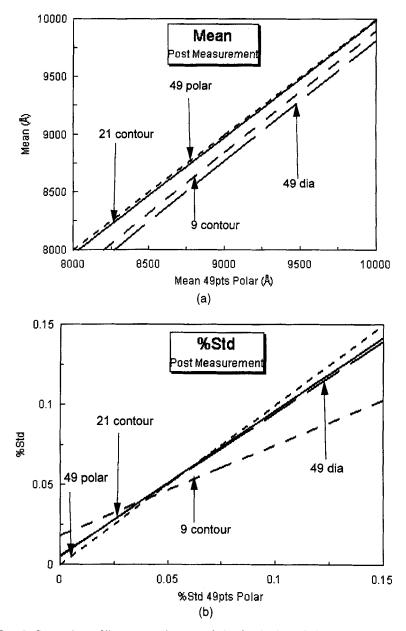

| 2. Measurement Patterns and Points                    | 220 |

|                                                       | 220 |

| 3. Measurement of Patterned Wafers                    |     |

| 4. Integration Issues                                 | 225 |

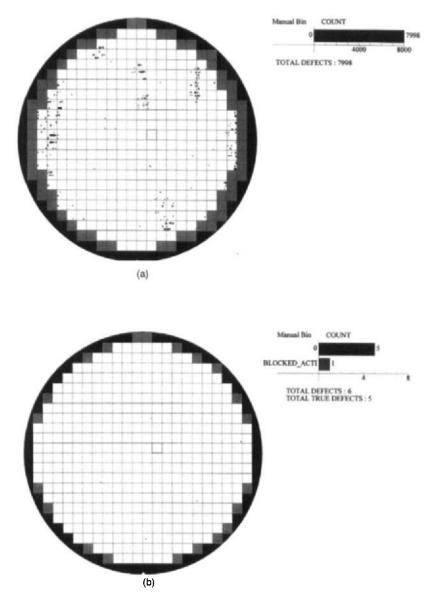

| III. DEFECTIVITY MONITORING                           | 226 |

| 1. Laser Scanning Method                              | 228 |

| 2. Digital Image Comparison Method                    | 228 |

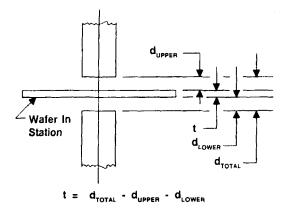

| IV. NONCONTACT CAPACITIVE MEASUREMENT                 | 229 |

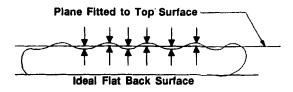

| 1. Flatness                                           | 231 |

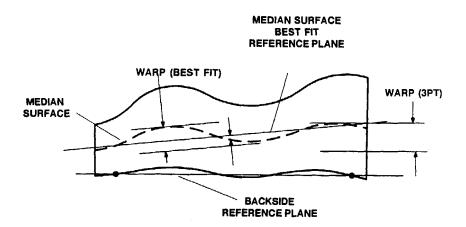

| 2. Bow and Warp                                       | 232 |

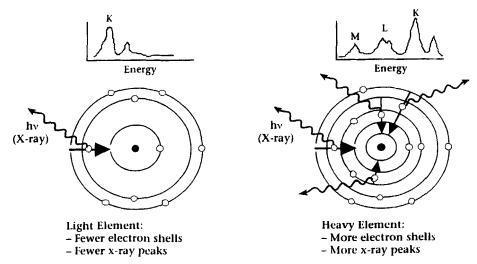

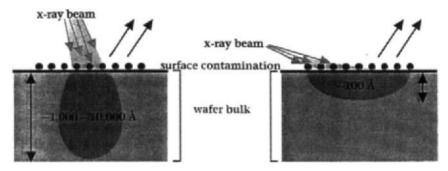

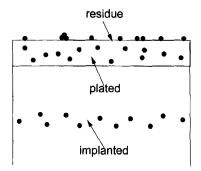

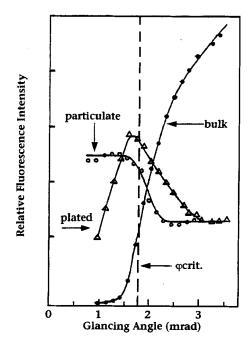

| V. TOTAL X-RAY FLUORESCENCE                           | 233 |

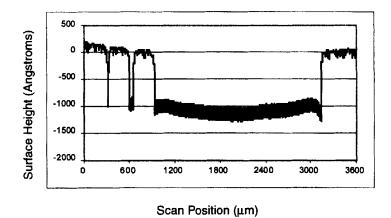

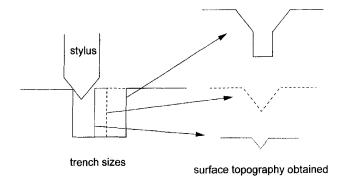

| VI. STYLUS PROFILOMETRY (FORCE MEASUREMENT)           | 236 |

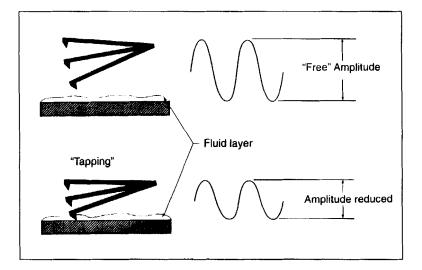

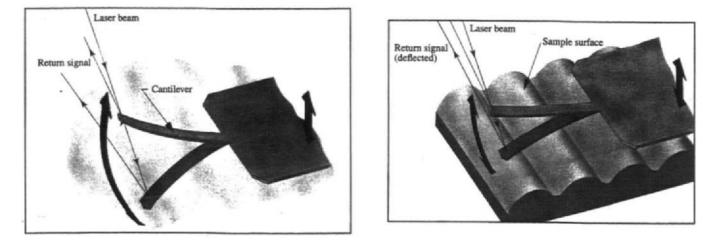

| VII. ATOMIC FORCE MICROSCOPY                          | 236 |

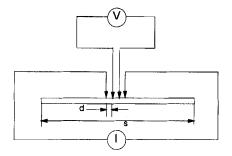

| VIII. FOUR-POINT PROBE                                | 241 |

| REFERENCES                                            | 243 |

|                                                       |     |

| II. 0<br>1<br>2<br>2<br>2<br>2<br>2<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | NTRODUCTION<br>DXIDE CMP WITHIN<br>Equipment and Co<br>Recipe Parameters<br>Effect of the End I<br>Deposit Less, Polit<br>(Uniformity vs Pla<br>BPSG vs TEOS<br>POST-CMP OXIDE TH<br>Lack of Endpoint<br>Wafer-to-Wafer Th<br>DEFECTIVITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | nsumable.<br>S<br>Effector .<br>sh Less vs<br>anarity)<br><br>HICKNESS<br>Detection | NON<br>s<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>· | iun<br><br>epo:<br><br>NTR<br>ster    | IFOF<br>sit N | . MIT<br><br><br><br> | ГҮ  | (W | 1 W<br>list | V N<br><br><br> | U)<br>   | e |   |             |   |   | • | • •<br>• • | <br><br> | • | • |

|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------|---------------|-----------------------|-----|----|-------------|-----------------|----------|---|---|-------------|---|---|---|------------|----------|---|---|

| 1<br>2<br>3<br>2<br>111. 1<br>1<br>2<br>1V. 1                                                        | <ol> <li>Equipment and Co</li> <li>Recipe Parameters</li> <li>Effect of the End I</li> <li>Deposit Less, Politi<br/>(Uniformity vs Platic)</li> <li>BPSG vs TEOS</li> <li>POST-CMP OXIDE THE<br/>Lack of Endpoint</li> <li>Wafer-to-Wafer The</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | nsumable.<br>S<br>Effector .<br>sh Less vs<br>anarity)<br><br>HICKNESS<br>Detection | s<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·   | <br>epo:<br><br><br><br><br>          | s <i>it 1</i> |                       |     | Po | list        | <br><br>h M     | 10r      | e |   | •<br>•<br>• |   |   | • | • •        | · ·      | • |   |

| 2<br>2<br>2<br>111. 1<br>1<br>2<br>1V. 1                                                             | 2. Recipe Parameters<br>3. Effect of the End I<br>4. Deposit Less, Polit<br>(Uniformity vs Pla<br>5. BPSG vs TEOS<br>POST-CMP OXIDE TH<br>1. Lack of Endpoint I<br>2. Wafer-to-Wafer Th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | s<br>Effector .<br>sh Less vs<br>anarity)<br><br>HICKNESS<br>Detection              | ; Da<br>Co:<br>Sy                                                                                  | <br>epo:<br><br><br><br><br>          | sit 1<br>OL   | <br>101               |     | Po | list        | <br>h M<br>     | 10r      | e |   |             |   | • | • | •••        | · ·      | • | • |

| 3<br>2<br>111. 1<br>1<br>2<br>1V. 1                                                                  | <ol> <li>Effect of the End I</li> <li>Deposit Less, Polis<br/>(Uniformity vs Pla</li> <li>BPSG vs TEOS</li> <li>POST-CMP OXIDE TH</li> <li>Lack of Endpoint</li> <li>Wafer-to-Wafer T</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Effector<br>sh Less vs<br>anarity)<br><br>HICKNESS<br>Detection                     | 5 D<br>Co<br>Sy                                                                                    | <br>epo:<br><br>NTR<br>ster           | sit 1<br>OL   | 1.<br>101<br>         | е,  | Po | list        | <br>h M<br>     | 1or<br>1 | e | • |             | • |   | • | •••        | <br>     | • | • |

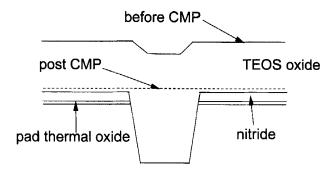

| 2<br>111. 1<br>1<br>2<br>1V. 1                                                                       | <ol> <li>Deposit Less, Polix<br/>(Uniformity vs Pla<br/>BPSG vs TEOS .</li> <li>BPSG vs TEOS .</li> <li>POST-CMP OXIDE TH<br/>L. Lack of Endpoint .</li> <li>Wafer-to-Wafer The second seco</li></ol> | sh Less vs<br>anarity)<br><br>HICKNESS<br>Detection                                 | s Da<br>Co:<br>Sy                                                                                  | epo:<br>· · ·<br>· · ·<br>NTR<br>ster | sit 1         | 10r<br><br>           | 'е, | Ро | list        | h M<br>         | 1or<br>  | e |   |             | • |   |   |            |          |   |   |

| 111. 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1                    | (Uniformity vs Pla<br>5. BPSG vs TEOS<br>Post-CMP OXIDE TH<br>1. Lack of Endpoint<br>2. Wafer-to-Wafer T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | anarity)<br><br>HICKNESS<br>Detection                                               | Co:<br>Sy                                                                                          | <br><br>NTR<br>ster                   | .OL           | <br>                  |     |    | •           | <br>            | •••      |   |   |             |   |   |   |            |          |   |   |

| III. I<br>1<br>2<br>IV. I                                                                            | 5. BPSG vs TEOS<br>Post-CMP OXIDE TH<br>1. Lack of Endpoint 2<br>2. Wafer-to-Wafer T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <br>HICKNESS<br>Detection                                                           | Co:<br>Sy                                                                                          | <br>NTR<br>ster                       | OL            | , .<br>               |     |    |             |                 | •••      |   |   |             |   |   |   |            |          |   | • |

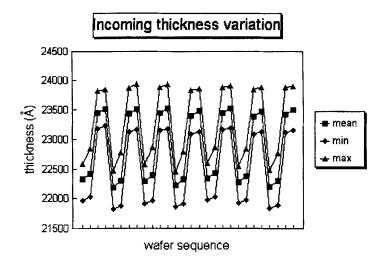

| III. I<br>1<br>2<br>IV. I                                                                            | Post-CMP Oxide Th<br>L. Lack of Endpoint 1<br>2. Wafer-to-Wafer Th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | HICKNESS<br>Detection                                                               | Co:<br>Sy                                                                                          | NTR<br>ster                           | OL            |                       |     |    |             |                 |          | • | • | •           |   | • | • |            |          |   |   |

| 1<br>2<br>IV. 1                                                                                      | . Lack of Endpoint .<br>2. Wafer-to-Wafer Th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Detection                                                                           | Sy                                                                                                 | ster                                  |               |                       | •   |    |             |                 |          |   |   |             |   |   |   |            |          |   |   |

| 2<br>IV. 1                                                                                           | 2. Wafer-to-Wafer T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                     | -                                                                                                  |                                       |               |                       |     |    |             |                 |          |   |   |             |   |   |   |            |          |   |   |

| IV. I                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | menness 1                                                                           |                                                                                                    | nıni                                  |               |                       |     |    |             |                 |          |   |   |             |   |   |   |            |          |   |   |

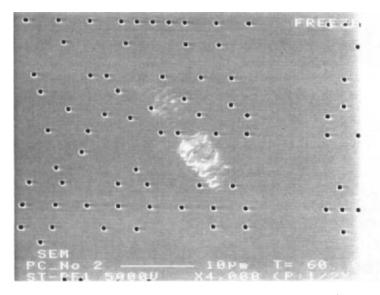

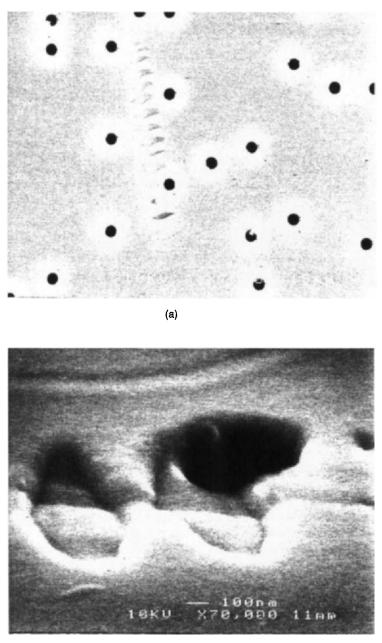

|                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     |                                                                                                    |                                       |               |                       |     |    |             |                 | ,        |   |   |             |   |   |   |            |          |   |   |

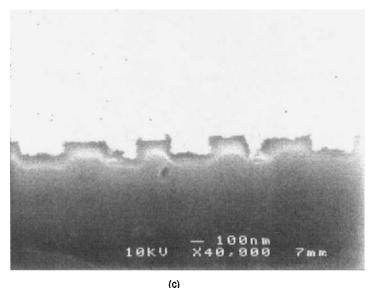

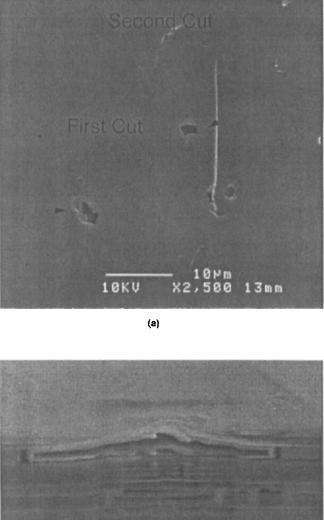

| 1                                                                                                    | . Scratches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                     |                                                                                                    |                                       |               |                       |     |    |             |                 |          |   |   |             |   |   |   |            |          |   |   |

|                                                                                                      | Other Defects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                     |                                                                                                    |                                       |               |                       |     |    |             |                 |          |   |   |             |   |   |   |            |          |   |   |

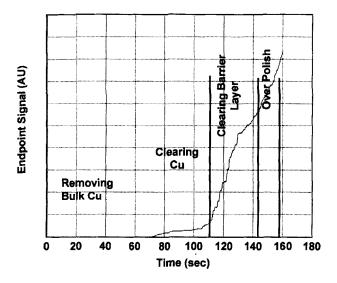

|                                                                                                      | FUNGSTEN CMP PRO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                     |                                                                                                    |                                       |               |                       |     |    |             |                 |          |   |   |             |   |   |   |            |          |   |   |

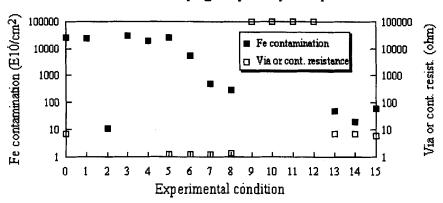

|                                                                                                      | . Metal Contaminat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                     |                                                                                                    |                                       |               |                       |     |    |             |                 |          |   |   |             |   |   |   |            |          |   |   |

|                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     |                                                                                                    |                                       |               |                       |     |    |             |                 |          |   |   |             |   |   |   |            |          |   |   |

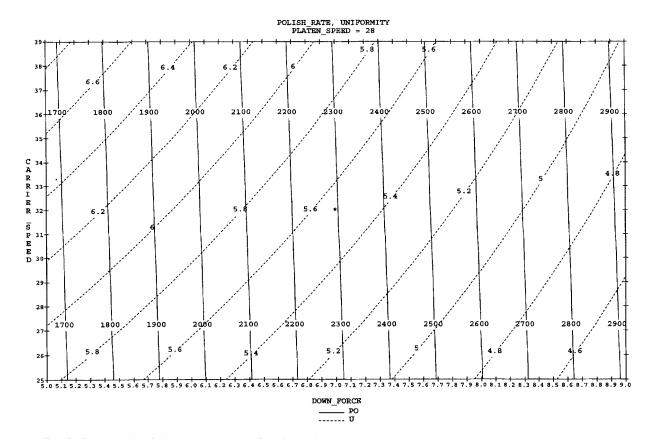

|                                                                                                      | 3. Polish Rate and U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                     |                                                                                                    |                                       |               |                       |     |    |             |                 |          |   |   |             |   |   |   |            |          |   |   |

|                                                                                                      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                     |                                                                                                    |                                       |               |                       |     |    |             |                 |          |   |   |             |   |   |   |            |          |   |   |

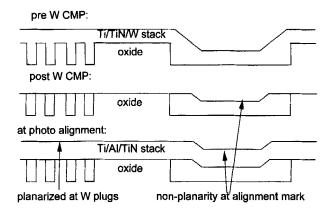

|                                                                                                      | . Missing Alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                     |                                                                                                    |                                       |               |                       |     |    |             |                 |          |   |   |             |   |   |   |            |          |   |   |

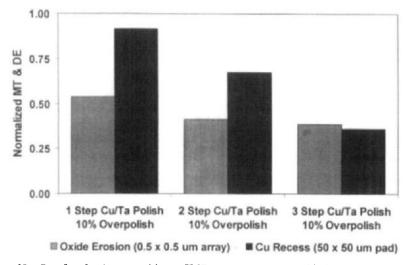

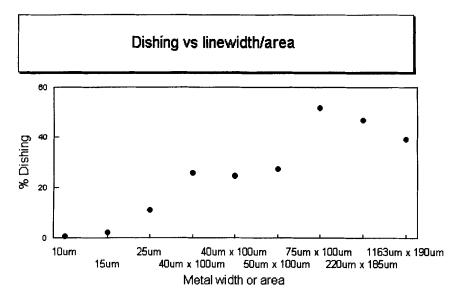

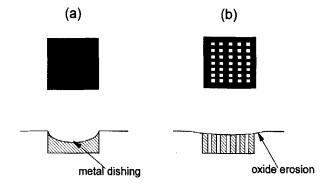

|                                                                                                      | Dishing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                     |                                                                                                    |                                       |               |                       |     |    |             |                 |          |   |   |             |   |   |   |            |          |   |   |

|                                                                                                      | REFERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                     |                                                                                                    |                                       |               |                       |     |    |             |                 |          |   |   |             |   |   |   |            |          |   |   |

| 1                                                                                                    | CEFERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                     | ·                                                                                                  | •••                                   | ·             | • •                   | ·   | ·  | ·           | •••             | •        | · | · | •           | • | • | · | • •        | •        |   | · |

CONTENTS

ix

This Page Intentionally Left Blank

### Preface

In the engineering world, many ideas and plans are conceived in the information exchanges that occur over lunch. In the summer of 1997, one of the editors (Shin Hwa Li) was assigned to assist our CMP module at the Crolles facility of STMicroelectronics near Grenoble, France. One day, in the company cafeteria, while sitting near the window and taking in the gorgeous sub-Alpine scenery with a delicious French meal, he was joined by several site engineers. Having become aware that he was the CMP engineer responsible for both oxide and metal processes in another fab, they asked him questions regarding CMP fundamentals, equipment, consumables, application and the like. At that moment, the thought occurred to him that a CMP textbook would be very useful. To his knowledge, such a book did not yet exist. Ironically, while he was fielding and responding to the many questions, one of the engineers (Jimmy Huang) remarked somewhat joking-ly that he should write a book about CMP.

The idea remained fixed in Li's mind, and after returning to the United States, he seriously considered the possibility. He discussed this with his manager (and coeditor, Bob Miller), who, being of the mindset that almost any idea is worth pursuing, immediately liked the idea. In performing a literature search, we found only one such book extant (*Chemical Mechanical Planarization of Microelectronic Materials*, by J. M. Steigerwald, S. P. Murarka, and R. J. Gutmann, John Wiley & Sons, New York, 1997). We read it and discovered that the book, although an excellent reference, is academically oriented. We felt that since the CMP technology was becoming a major and critical part of the semiconductor manufacturing environment, a practical, industrially oriented text, directed more toward the level of sustaining engineers, should be made available.

It is true that many industrial papers and articles have been published, but each one is usually focused on a single specific subject; furthermore, the literature is diffused into many different journals and/or conference proceedings. At some point, a textbook becomes an essential tool for imparting a coherent and comprehensive understanding. On the other hand, since CMP technology is currently still in its early stage of use, a book with only one or two authors would lack some of the insights that come from multiple sources, so we elected to edit a book that combined the inputs of a number of authors who are recognized experts in the field.

This book is designed primarily to help all engineers whose work impinges on CMP in the semiconductor industry: process, process development, and integration engineers; device and product engineers; and equipment, vendor applications, and vendor field engineers. At the same time, it is written at a level where students in colleges should find it a useful aid in bridging their knowledge between academic principles and actual practice. Perhaps more importantly, we intend this book to generate interest in the subject and to usher more people into joining and exploring the CMP world.