Stephan Wong · Antonio Carlos Beck Koen Bertels · Luigi Carro (Eds.)

# **Applied Reconfigurable Computing**

13th International Symposium, ARC 2017 Delft, The Netherlands, April 3–7, 2017 Proceedings

# **Lecture Notes in Computer Science**

10216

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, Lancaster, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Zurich, Switzerland

John C. Mitchell

Stanford University, Stanford, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

TU Dortmund University, Dortmund, Germany

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Gerhard Weikum

Max Planck Institute for Informatics, Saarbrücken, Germany

More information about this series at http://www.springer.com/series/7407

Stephan Wong · Antonio Carlos Beck Koen Bertels · Luigi Carro (Eds.)

# Applied Reconfigurable Computing

13th International Symposium, ARC 2017 Delft, The Netherlands, April 3–7, 2017 Proceedings

Editors

Stephan Wong Delft University of Technology

Dalft

The Netherlands

Antonio Carlos Beck

Federal University of Rio Grande do Sul

Porto Alegre

Brazil

Koen Bertels

Delft University of Technology

Delf

The Netherlands

Luigi Carro

Federal University of Rio Grande do Sul

Porto Alegre

Brazil

ISSN 0302-9743 ISSN 1611-3349 (electronic) Lecture Notes in Computer Science ISBN 978-3-319-56257-5 ISBN 978-3-319-56258-2 (eBook) DOI 10.1007/978-3-319-56258-2

Library of Congress Control Number: 2017935847

LNCS Sublibrary: SL1 - Theoretical Computer Science and General Issues

#### © Springer International Publishing AG 2017

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by Springer Nature

The registered company is Springer International Publishing AG

The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

#### **Preface**

Reconfigurable computing technologies offer the promise of substantial performance gains over traditional architectures via customizing, even at runtime, the topology of the underlying architecture to match the specific needs of a given application. Contemporary adaptive systems allow for the definition of architectures with functional and storage units that match in function, bit-width, and control structures the specific needs of a given computation. They aim to exploit these novel and innovative resources to achieve the highest possible performance and energy efficiency.

Many are the challenges faced by reconfigurable computing in these days: design methods and tools, which include high-level languages and compilation, simulation and synthesis, estimation techniques, design space exploration, and run-time systems and virtualization; architectures, which may be self-adaptive and evolvable, heterogeneous, low-power, approximate, fine/coarse grained, embedded in an MPSOC and use an NOC, or even resilient and fault tolerant; applications that comprise security and cryptography, big data and HPC, embedded and DSP, robotics and automotive, mission critical, among many others; and trends in teaching, benchmarks, and other emerging technologies.

Over the past 12 years, the International Applied Reconfigurable Computing (ARC) Symposium series (www.arc-symposium.org) has provided a forum for dissemination and discussion of this transformative research area. The ARC symposium was first held in 2005 in Algarve, Portugal. The second edition took place in Delft, The Netherlands, in 2006, and was the first edition to have its proceedings published by Springer as a volume in its *Lecture Notes in Computer Science* series. Subsequent ARC yearly editions were held in Rio de Janeiro, Brazil (2007); London, UK (2008); Karlsruhe, Germany (2009); Bangkok, Thailand (2010); Belfast, UK (2011); Hong Kong, China (2012); Los Angeles, USA (2013); Algarve, Portugal (2014); Bochum, Germany (2015); Rio de Janeiro, Brazil (2016).

This LNCS volume includes the papers selected for the 13th edition of the symposium (ARC 2017), held in Delft, The Netherlands, during April 3–7, 2017. The symposium succeeded in attracting a significant number of high-quality contributions related to reconfigurable computing. A total of 49 papers were submitted to the symposium from 22 countries: Algeria (1), Brazil (5), Canada (1), China (9), Denmark (1), France (3), Germany (7), Greece (1), India (1), Iran(1), Italy(1), Japan (2), South Korea (1), Malaysia (1), The Netherlands (2), Pakistan (1), Poland (2), Singapore (2), Switzerland (1), Turkey (1), UK (4), and USA (1). All submissions were carefully evaluated by at least three members of the Program Committee. In all, 17 papers were accepted as full papers (acceptance rate of 34.7%) and 11 as short papers (global acceptance rate of 57.1%). The accepted papers composed a very interesting symposium program, which we consider to constitute a representative overview of ongoing research efforts in reconfigurable computing.

#### VI Preface

We would like to acknowledge the support of all the members of this year's Steering and Program Committees in reviewing papers, in helping with the paper selection, and in giving valuable suggestions. Special thanks also to the additional researchers who contributed to the reviewing process, to all the authors who submitted papers to the symposium, and to all the symposium attendees.

Last but not least, we are especially indebted to Juergen Becker from the University of Karlsruhe and to Alfred Hoffmann and Anna Kramer from Springer for their support and work in publishing this book as part of the LNCS series.

February 2017

Stephan Wong Antonio Carlos Beck Koen Bertels Luigi Carro

## **Organization**

**General Chairs**

Koen Bertels Delft University of Technology, The Netherlands Luigi Carro Federal University of Rio Grande do Sul, Brazil

**Program Chairs**

Stephan Wong Delft University of Technology, The Netherlands Antonio Carlos Beck Federal University of Rio Grande do Sul, Brazil

**Finance Chair**

Joost Hoozemans Delft University of Technology, The Netherlands

**Proceedings Chair**

Hamid Mushtaq Delft University of Technology, The Netherlands

**Sponsorship Chair**

Pedro Diniz USC Information Sciences Institute, USA

**Publicity Chairs**

Sorin Cotofana Delft University of Technology, The Netherlands

Pedro Diniz USC Information Sciences Institute, USA

Chao Wang University of Science and Technology of China, China

Web Chair

Johan Peltenburg Delft University of Technology, The Netherlands

**Steering Committee**

Hideharu Amano Keio University, Japan

Jürgen Becker Universität Karlsruhe (TH), Germany

Mladen Berekovic Braunschweig University of Technology, Germany Koen Bertels Delft University of Technology, The Netherlands

João M.P. Cardoso University of Porto, Portugal

Katherine Morrow University of Wisconsin-Madison, USA

George Constantinides Imperial College London, UK

#### VIII Organization

Pedro C. Diniz USC Information Sciences Institute, USA

Philip H.W. Leong University of Sydney, Australia

Walid Najjar University of California Riverside, USA

Roger Woods Queen's University Belfast, UK

#### **Program Committee**

Hideharu Amano Keio University, Japan

Zachary Baker Los Alamos National Laboratory, USA Juergen Becker Karlsruhe Institute of Technology, Germany

Mladen Berekovic TU Braunschweig, Germany

Joao Bispo Universidade Técnica de Lisboa, Portugal

Michaela Blott Xilinx, Ireland

Vanderlei Bonato

Christos Bouganis

João Canas Ferreira

Cyrille Chavet

Daniel Chillet

University of Sao Paulo, Brazil

Imperial College London, UK

University of Porto, Portugal

Université de Bretagne-Sud, France

Université de Rennes, France

Rene Cumplido Inst. Nacional de Astrofísica, Óptica y Electrónica, Mexico

Florent de Dinechin

Steven Derrien

Université de Lyon, France

Université de Rennes, France

Universidade de Aveiro, Portugal

Ricardo Ferreira

Universidade Federal de Vicosa, Brazil

Roberto Giorgi University of Siena, Italy

Diana Goehringer Ruhr University Bochum, Germany

Marek Gorgon AGH University of Science and Technology, Poland Frank Hannig Friedrich Alexander University Erlangen-Nürnberg,

Germany

Jim Harkin University of Ulster, UK

Dominic Hillenbrand Karlsruhe Institute of Technology, Germany

Christian Hochberger TU Darmstadt, Germany

Michael Huebner Ruhr University Bochum, Germany

Waqar Hussain Tampere University of Technology, Finland Fernanda Kastensmidt Federal University of Rio Grande do Sul, Brazil

Krzysztof Kepa GE Global Research, USA

Georgios Keramidas Technological Educational Institute of Western Greece,

Greece

Andreas Koch TU Darmstadt, Germany Dimitrios Kritharidis Intracom Telecom, Greece

Tomasz Kryjak AGH University of Science and Technology, Poland

Vianney Lapotre Université de Bretagne-Sud, France

Philip Leong The Chinese University of Hong Kong, SAR China

Eduardo Marques University of Sao Paulo, Brazil Konstantinos Masselos University of the Peloponnese, Greece

Cathal McCabe Xilinx, Ireland

Daniel Mesquita Universidade Federal do Pampa, Brazil

Antonio Miele Politecnico di Milano, Italy

Takefumi Miyoshi e-trees.Japan, Inc., Japan

Razvan Nane Delft University of Technology, The Netherlands

Horacio Neto Technical University of Lisbon, Portugal Smail Niar University of Valenciennes, France Seda Ogrenci-Memik Northwestern University, USA

Kyprianos Technical University of Crete, Greece

Papadimitriou

Monica Pereira Universidade Federal do Rio Grande do Norte, Brazil

Christian Pilato Columbia University, USA

Thilo Pionteck Otto-von-Guericke Universität Magdeburg, Germany

Kyle Rupnow Advanced Digital Sciences Center, Singapore

Kentaro Sano Tohoku University, Japan Politecnico di Milano, Italy Marco D. Santambrogio Yuichiro Shibata Nagasaki University, Japan Politecnico di Milano, Italy Cristina Silvano **Dimitrios Soudris** University of Patras, Greece Dirk Stroobandt Ghent University, Belgium Imperial College London, UK David Thomas Imperial College London, UK Tim Todman

Chao Wang University of Science and Technology of China

Roger Woods Queen's University Belfast, UK Yoshiki Yamaguchi University of Tsukuba, Japan

#### **Additional Reviewers**

Ahmed, Nauman Martin, George Allouani, Ihsen McCarroll, Niall

Anantharajaiah, Nidhi Melo Costa, Thadeu A.F.

Baklouti, Mouna Migliore, Vincent

Bapp, Falco Oliveira de Souza Junior, Carlos Alberto

Barber, Paul Oliveira, Cristiano B. De

Bileki, Guilherme Perina, Andre B.

Blochwitz, Christopher Procaccini, Marco

Chaib Draa, Ismat Yahia Reder, Simon

Del Sozzo, Emanuele Rettkowski, Jens

Di Tucci, Lorenzo Rohde, Johanna

Durelli, Gianluca Rosa, Leandro

Fraser, Nicholas Scolari, Alberto

Gambardella, Giulio Siddiqui, Fahad Manzoor

Gottschling, Philip Stock, Florian

Hernández-Munive, Roberto Wehner, Philipp

Joseph, Moritz Wenzel, Jakob

Jung, Lukas Yu, Jintao

Kalb, Tobias Zhang, Kaicheng

Kalms, Lester Özkan, M. Akif

Korinth, Jens

# Rethinking Memory System Design (and the Computing Platforms We Design Around It)

#### Onur Mutlu

ETH Zurich, Zurich, Switzerland

**Abstract.** The memory system is a fundamental performance and energy bottleneck in almost all computing systems. Recent system design, application, and technology trends that require more capacity, bandwidth, efficiency, and predictability out of the memory system make it an even more important system bottleneck. At the same time, DRAM and flash technologies are experiencing difficult technology scaling challenges that make the maintenance and enhancement of their capacity, energy efficiency, and reliability significantly more costly with conventional techniques. In fact, recent reliability issues with DRAM, such as the RowHammer problem, are already threatening system security and predictability. In this talk, we first discuss major challenges facing modern memory systems in the presence of greatly increasing demand for data and its fast analysis. We then examine some promising research and design directions to overcome these challenges and thus enable scalable memory systems for the future. We discuss three key solution directions: (1) enabling new memory architectures, functions, interfaces, and better integration of memory and the rest of the system, (2) designing a memory system that intelligently employs emerging non-volatile memory (NVM) technologies and coordinates memory and storage management, (3) reducing memory interference and providing predictable performance to applications sharing the memory system. If time permits, we will also touch upon our ongoing related work in combating scaling challenges of NAND flash memory. An accompanying paper, slightly outdated (circa 2015), can be found at http://people.inf.ethz.ch/omutlu/pub/ memory-systems-research\_superfri14.pdf.

# Acceleration Through Hardware Multithreading

#### Walid Najjar

Department of Computer Science and Engineering, University of California Riverside, Riverside, USA

Abstract. Long memory latencies, as measured in CPU clock cycles, is probably the most daunting challenge to modern computer architecture. In multicore designs, the long memory latency is mitigated with the use of massive cache hierarchies. This solution pre-supposes some forms of temporal or spatial localities. Irregular applications, by their very nature, suffer from poor data locality that results in high cache miss rates and long off-chip memory latency. Latency masking multithreading, where threads relinquish control after issuing a memory request, has been demonstrated as an effective approach to achieving a higher throughput. Multithreaded CPUs are designed for a fixed maximum number of threads tailored for an average application. FPGAs, however, can be customized to specific applications. Their massive parallelism is well-known, and ideally suited to dynamically manage hundreds, or thousands, of threads. Multithreading, in essence, trades off memory bandwidth for latency. In this talk I describe how latency masking multithreaded execution on FPGAs can achieve a higher throughput than CPUs and/or GPUs on two sets of applications: sparse linear algebra and database operations.

# **Enabling Software Engineers to Program Heterogeneous, Reconfigurable SoCs**

#### Patrick Lysaght

Xilinx Research Labs, San Jose, USA

Abstract. In this talk, modern software trends will be explored with a focus on how we can enable software developers to exploit the benefits of reconfigurable hardware. This talk introduces PYNQ, a new open-source framework for designing with Xilinx Zynq devices, a class of All Programmable Systems on Chip (APSoCs) which integrates multiple processors and Field Programmable Gate Arrays (FPGAs) into single integrated circuits. The main goal of the framework is to make it easier for designers of embedded systems to use APSoCs in their applications. The APSoC is programmed in Python and the code is developed and tested directly on the embedded system. The programmable logic circuits are imported as hardware libraries and programmed through their APIs, in essentially the same way that software libraries are imported and programmed. The framework combines three main elements:

- The use of a high-level productivity language, Python in this case

- Python-callable hardware libraries based on FPGA overlays

- A web-based architecture incorporating the open-source Jupyter Notebook infrastructure served from Zynq's embedded processors

The result is a programming environment that is web-centric so it can be accessed from any browser on any computing platform or operating system. It enables software programmers to work at higher levels of design abstraction and to re-use both software and hardware libraries for reconfigurable computing. The framework is inherently extensible and integrates coherently with hardware-dependent code written in C and C++. The talk concludes with an outline of areas for continued development, and a call for community participation.

## **Contents**

| Improving the Performance of Adaptive Cache in Reconfigurable VLIW Processor                              | 3  |

|-----------------------------------------------------------------------------------------------------------|----|

| Sensen Hu, Anthony Brandon, Qi Guo, and Yizhuo Wang                                                       |    |

| LP-P <sup>2</sup> IP: A Low-Power Version of P <sup>2</sup> IP Architecture Using Partial Reconfiguration | 16 |

| NIM: An HMC-Based Machine for Neuron Computation                                                          | 28 |

| VLIW-Based FPGA Computation Fabric with Streaming Memory Hierarchy for Medical Imaging Applications       | 36 |

| Embedded Computing and Security                                                                           |    |

| Hardware Sandboxing: A Novel Defense Paradigm Against Hardware Trojans in Systems on Chip                 | 47 |

| Rapid Development of Gzip with MaxJ                                                                       | 60 |

| On the Use of (Non-)Cryptographic Hashes on FPGAs                                                         | 72 |

| An FPGA-Based Implementation of a Pipelined FFT Processor for High-Speed Signal Processing Applications   | 81 |

## Simulation and Synthesis

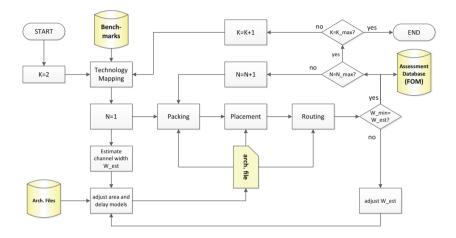

| Soft Timing Closure for Soft Programmable Logic Cores:  The ARGen Approach                                                                                                                                              | 93  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

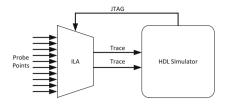

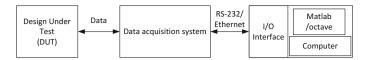

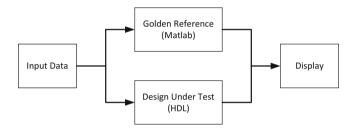

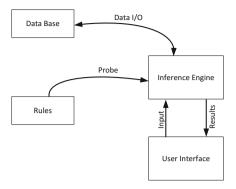

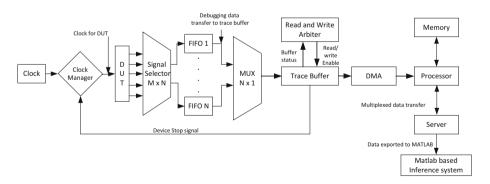

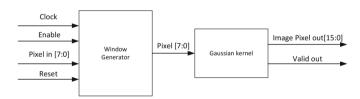

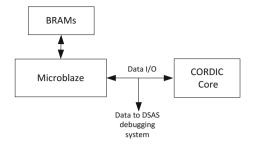

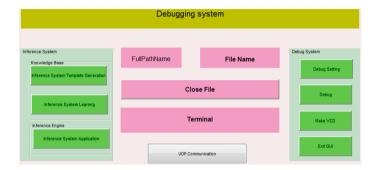

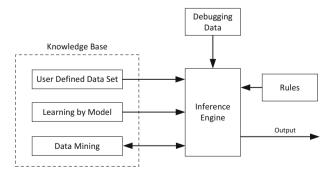

| FPGA Debugging with MATLAB Using a Rule-Based Inference System Habib Ul Hasan Khan and Diana Göhringer                                                                                                                  | 106 |

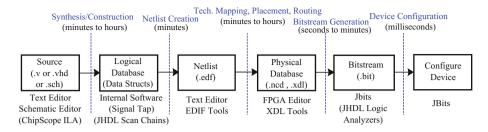

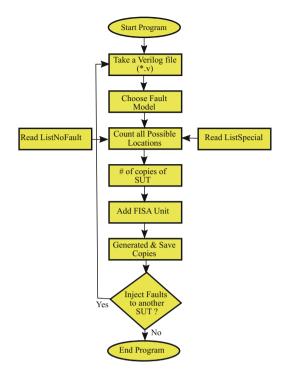

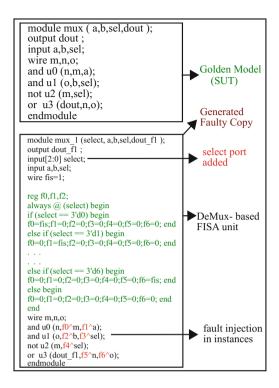

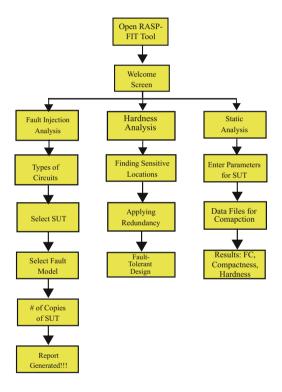

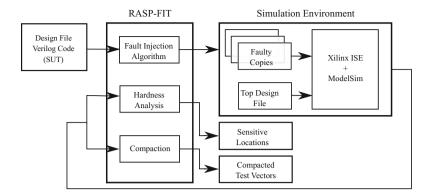

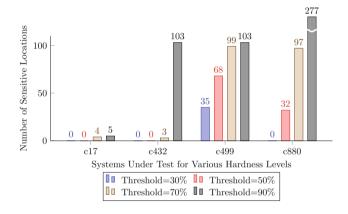

| Hardness Analysis and Instrumentation of Verilog Gate Level Code for FPGA-based Designs                                                                                                                                 | 118 |

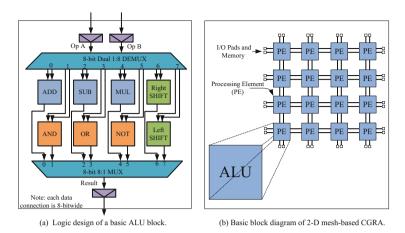

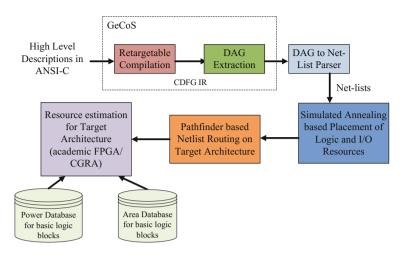

| A Framework for High Level Simulation and Optimization of Coarse-Grained Reconfigurable Architectures                                                                                                                   | 129 |

| Design Space Exploration                                                                                                                                                                                                |     |

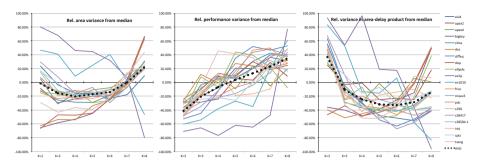

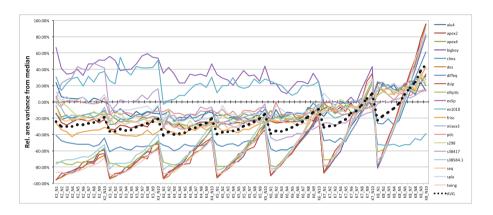

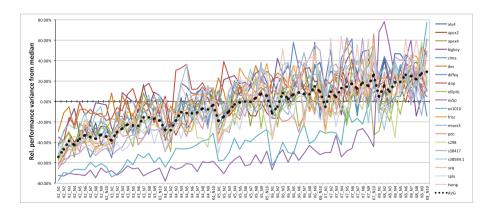

| Parameter Sensitivity in Virtual FPGA Architectures                                                                                                                                                                     | 141 |

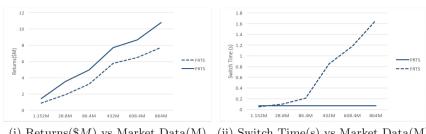

| Custom Framework for Run-Time Trading Strategies                                                                                                                                                                        | 154 |

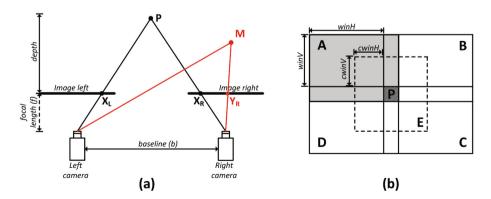

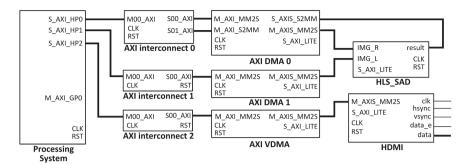

| Exploring HLS Optimizations for Efficient Stereo Matching Hardware Implementation                                                                                                                                       | 168 |

| Architecture Reconfiguration as a Mechanism for Sustainable Performance of Embedded Systems in case of Variations in Available Power Dimple Sharma, Victor Dumitriu, and Lev Kirischian                                 | 177 |

| Fault Tolerance                                                                                                                                                                                                         |     |

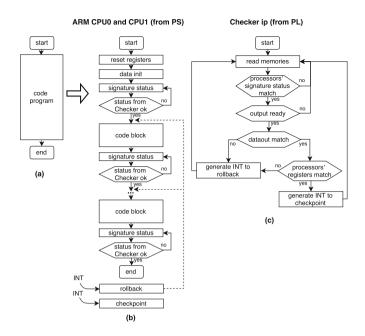

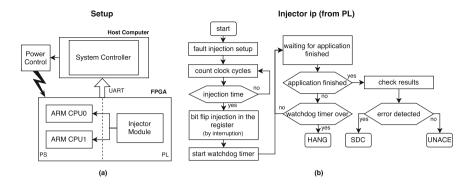

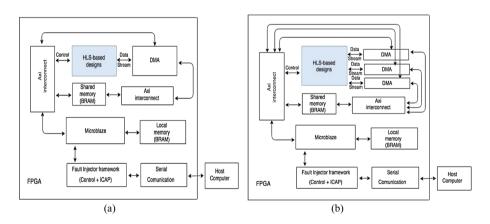

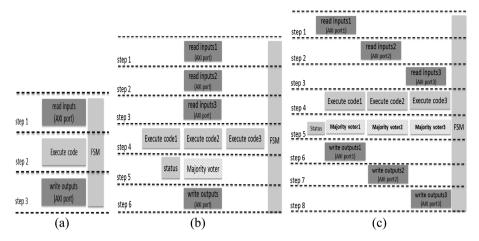

| Exploring Performance Overhead Versus Soft Error Detection in Lockstep Dual-Core ARM Cortex-A9 Processor Embedded into Xilinx Zynq APSoC Ádria Barros de Oliveira, Lucas Antunes Tambara, and Fernanda Lima Kastensmidt | 189 |

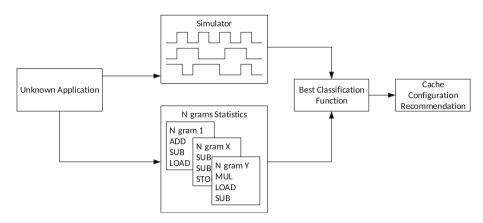

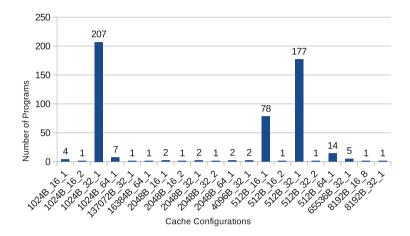

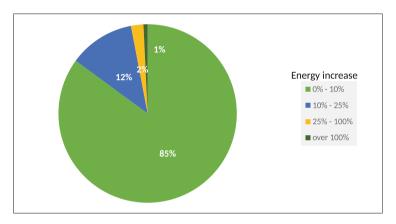

A Machine Learning Methodology for Cache Recommendation . . . . . . . . . .

Osvaldo Navarro, Jones Mori, Javier Hoffmann, Fabian Stuckmann,

and Michael Hübner

311

### XX Contents

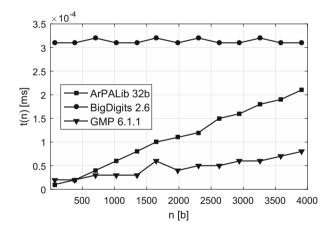

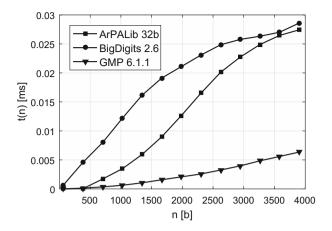

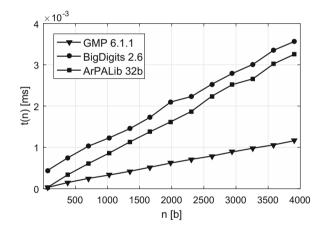

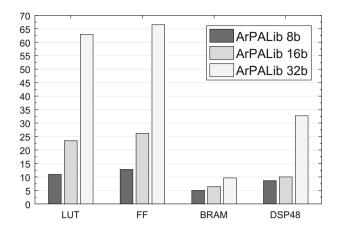

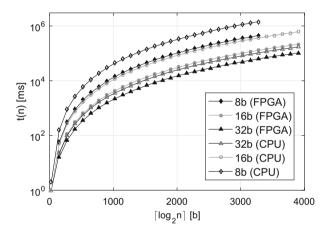

| ArPALib: A Big Number Arithmetic Library for Hardware and Software |     |

|--------------------------------------------------------------------|-----|

| Implementations. A Case Study for the Miller-Rabin Primality Test  | 323 |

| Jan Macheta, Agnieszka Dąbrowska-Boruch, Paweł Russek,             |     |

| and Kazimierz Wiatr                                                |     |

| Author Index                                                       | 331 |

# Improving the Performance of Adaptive Cache in Reconfigurable VLIW Processor

Sensen Hu<sup>1(⋈)</sup>, Anthony Brandon<sup>2</sup>, Qi Guo<sup>3</sup>, and Yizhuo Wang<sup>1</sup>

School of Computer Science and Technology, Beijing Institute of Technology, Beijing, China

{foresthss,frankwyz}@bit.edu.cn

- <sup>2</sup> EEMCS, Delft University of Technology, Delft, The Netherlands

A.A.C.Brandon@tudelft.nl

- <sup>3</sup> University of Science and Technology of China, Heifei, China guoqiustc@hotmail.com

Abstract. In this paper, we study the impact of cache reconfiguration on the cache misses when the issue-width of a VLIW processor is changed. We clearly note here that our investigation pertains the local temporal effects of the cache resizing and how we counteract the negative impact of cache misses in such resizing instances. We propose a novel reconfigurable d-cache framework that can dynamically adapt its least recently used (LRU) replacement policy without much hardware overhead. We demonstrate that using our adaptive d-cache, it ensures a smooth cache performance from one cache size to the other. This approach is orthogonal to future research in cache resizing for such architectures that take into account energy consumption and performance of the overall application.

**Keywords:** VLIW · Cache · Cache resizing · Downsizing · Reconfiguration · Issue-width ·  $\rho$ -VEX

#### 1 Introduction

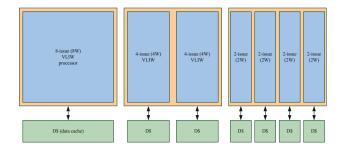

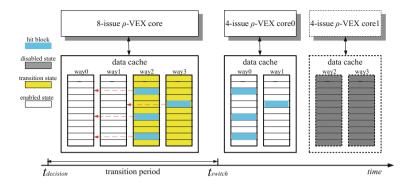

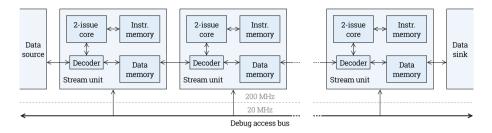

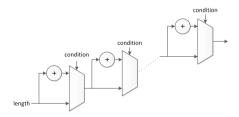

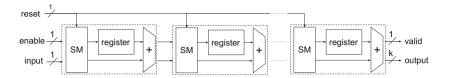

$\rho$ -VEX processor [1] is a reconfigurable and extensible softcore very long instruction word (VLIW) processor. It differs from traditional VLIW processors, in that the issue-width is parameterized from 2 to 4 to 8 - the core contains a maximum of 8 datapaths. A key motivation of the  $\rho$ -VEX processor design is to utilize only the necessary resources when needed. The dynamic nature of the  $\rho$ -VEX processor requires an adaptive cache organization that can combine several caches into a larger sized one, or separate a larger cache into smaller sized ones as depicted in Fig. 1—this is commonly referred to as cache resizing.

With these considerations, we investigated the effects of cache resizing triggered by the issue-width mode changes (caused by external factors) of the  $\rho$ -VEX

This work is supported in part by the National Natural Science Foundation of China under grant NSFC-61300011 and NSFC-61300010. The authors would like to thank the China Scholarship Council (CSC) for their financial support.

<sup>©</sup> Springer International Publishing AG 2017

S. Wong et al. (Eds.): ARC 2017, LNCS 10216, pp. 3-15, 2017.

**Fig. 1.** The dynamic architecture of  $\rho$ -vex.

core in different scenarios. In the case of upsizing (combining multiple ways to form a larger cache), no detrimental effects are expected as no live data was removed and the additional cache resources will gradually decrease the cache miss rates. However, in the case of downsizing (disabling one or more ways), we observe immediately increases in the cache miss rates. The main reason for the increased miss rates is the elimination of live data when disabling certain ways in the downsizing process.

We reiterate here that the resizing decision is made by an external source, i.e., either by the processor or by the operating system. In both cases it is a fact that a transition time can be introduced between the decision for a (processor) mode change and the actual moment of change. Furthermore, we propose a mechanism to dynamically adapt the d-cache replacement policy to reduce the negative effects of downsizing in set-associative caches. We exploit this transition time to bolster the amount of live data in the (cache) ways that remain active by giving them a higher preference when loading new data (when a miss occurs) and by moving data to these ways from the to-be-disabled ways (when a hit occurs). To the best of our knowledge, this paper is the first to propose a dynamic adaptation of the cache replacement policy in relation to core reconfiguration. Moreover, we are not attempting to reduce the overall single application performance or energy consumption as other cache resizing approaches do. We are considering scenarios in which mode changes occur frequently (due to external factors) and attempt to limit the impact of these mode changes on the d-cache performance per occurrence. Consequently, our approach is orthogonal to other cache resizing approaches.

Our approach reduces the (sudden) increase in cache misses during a cache downsizing event in order to reduce (locally in time) the performance impact of such an event. The experimental results show that we can reduce the number of cache misses by between 10% and 63% compared to immediate cache downsizing without taking any measures. More specifically, the contributions of this paper are as follows:

To the best of our knowledge, our proposal is the first to take the issue-width mode change of VLIW processor event as an external trigger to reconfigure the d-cache instead of monitoring the cache miss ratio, and resizes the d-cache to react to varying demand for cache size both within and across applications.

- We propose a transition period before the actual moment of resizing. This period of preparation before the actual cache resize ensures a smooth cache performance from one cache size to the other. In particular, we demonstrate that our main results can be achieved with a transition period of just 2000 clock cycles up to 4000 clock cycles.

- We implement a novel, simple, yet effective cache replacement policy, which migrates the accessed data to the enabled (active) cache ways after resizing, to reduce the transition cache misses in order to smoothen and thereby improve the performance (of the application) during the transition period and right after the downsizing event.

- Our approach allows for immediate cache downsizing without the need to maintain "live" portions of the cache after the downsizing event. In the  $\rho$ -VEX processor design philosophy, the "disabled" cache ways can be immediately used by other tasks as they are logically connected to other cores.

#### 2 Related Work

Previous studies on the strategy of "when to resize" almost all relied on the miss ratio or profiling to determine the correct time to resize the cache. In [3,4], these methods made the decision solely based on monitoring cache miss rate, which are all miss-driven resizing approaches. [5] used dynamic profiling for predicting cache usage and energy efficiency of the application under multiple cache configurations. However, cache miss rate is not always a good performance indictor [3]. While many factors can affect the cache miss rate, even the minor changes in program behavior or available cache size probably causes large changes in miss rate [2,6]. Such miss-driven resizing approach probably thrashes the performance. The profiling approaches increase the overheads of hardware or software as well as miss-driven approaches. Unlike prior work, as far as we are aware, our work is the first to introduce two events as external trigger to dynamically reconfigure cache when the issue-width mode of VLIW processor changes. Meanwhile, our method considers reducing the miss rate while downsizing cache in order to decrease miss penalty and to smoothen the performance.

Finally, our work is implemented on the  $\rho$ -VEX VLIW processor [1,7], which is open-source and has a complete tool chain (compiler, simulator and assembler). The issue-width of  $\rho$ -VEX can be reconfigured dynamically to be 2-issue, 4-issue and 8-issue at run-time [8]. In [9], the authors implemented generic binaries, which can execute the same binary on different issue-width processors without much hardware modifications. This design allows for maintaining live data within existing cache blocks when the amount of computing resources in the core are changed. This by itself already results in an improvement of the execution times by on average 16% (with outliers of 0.7% and 42%) for the MiBench benchmark suite (also used in this paper) compared to a case in which each resizing event results in cold starts of the d-cache (and not taking into account i-cache misses).

#### 3 General Approach

#### 3.1 When to Resize

In some cases, more frequent reconfiguration may be desirable due to frequent context switches between applications or aggressive adaptive reconfiguration for the same application. As mentioned earlier, we assume that external factors (from the d-cache's point of view) determine whether the d-cache should be resized. At the same time, our approach relies on the possibility that there is enough time given to our approach to "prepare" the caches before the actual resizing action in order to minimize the negative effects.

First, an operating system (OS) can claim resources to execute kernel thread, but instead of completely switching out the context of the running program, it can temporarily reduce the resources for the running program. In this manner, the running program remains responsive. This simple fact must not be overlooked as it represents a key aspect of the  $\rho$ -VEX core design. Single core context switching always results in huge context switching overheads and the active application being swapped out, therefore, not responsive at all. Second, applications running on the  $\rho$ -VEX processor most likely will have different phases in which the ILP varies. Low ILP within the running application can lead the core to decide to reduce resource utilization in order to save core power. In both cases, the core resizing will lead to a corresponding cache resizing.

#### 3.2 How to Resize

In the case of upsizing (combining multiple ways to form a larger cache), no detrimental effects are expected as no live data was removed and the additional cache resources will gradually decrease the cache miss rates. The key idea to reduce the cache misses after downsizing is to maintain as much as possible the live data within the downsized d-cache. In order to achieve this goal, we first have to find a way to identify the live data and subsequently decide how to treat the live data.

Before we discuss these two objectives we introduce the terminology used throughout this paper. For simplicity, we take a switching of mode from 8-issue to 4-issue to illustrate the transition mechanism in Fig. 2. There are two crucial instant times in the graph. One is  $t_{decision}$ , the other one is  $t_{switch}$ .  $t_{decision}$  indicates the moment in time the decision is taken to perform the mode change of the core.  $t_{switch}$  indicates that the actual moment that the core switches its mode. The interval from  $t_{decision}$  to  $t_{switch}$  is the transition period proposed in this paper. In Fig. 2, way0 and way1 will remain active after downsizing. Hence, the state of way0 and way1 during the transition period remains in the enabled state, while the state of way2 and way3 go to the transition state. Note that when  $t_{decision}$  equals  $t_{switch}$ , our strategy equals the traditional strategy of cache resizing, i.e., immediate cache resizing.

In order to identify the live data, we can use active methods as outlined by [10] that require an additional address correlation table. This adds hardware

Fig. 2. Migration mechanism from 8 issue-width to 4 issue-width.

overhead and in turn increases power consumption. In our opinion, it is much easier to perform this identification by exploiting the temporal likelihood of re-accessing data—this information is already kept by the least recently used (LRU) replacement policy. We therefore correlate the most live data with the most recently used data.

#### 4 Framework of Cache Resizing

#### 4.1 Hardware Implementation

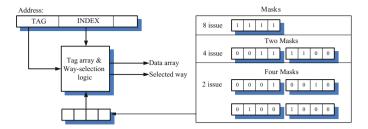

As depicted in Fig. 3, the way-selection logic (WSL) is in charge of carrying the active/inactive way-enable signal to each way. The way-mask register is provided to set which way is assigned to the corresponding core. It is a 4-bit vector that equals the associativity of cache. Each combination of bits in the way mask register is responsible for the corresponding cache ways. Given the core of 8 issue-widths, the value of way mask register is 1111, which denotes all of the ways are available. In such case, the d-cache acts as a four-way set-associative cache. If the issue-width of core is specified as 4, the available values of the way mask register are 1100 or 0011, which denotes the left ways or the right ways of the way-associative cache, respectively. In such case, the d-cache acts as a two-way set-associative cache. The core0 can hold the value 0011, while the core1 to take the value 1100. When the issue-width is specified as 2, there are four available values (0001, 0010, 0100, and 1000) since the four 2-issue cores can be run independently. The d-cache acts as a direct-mapped cache. Similarly, one core can hold one of 4 values while the rest of cores to hold the other values.

#### 4.2 Resizing-LRU Replacement Algorithm

We have designed a novel replacement algorithm based on LRU and way-resizing, called resizing-LRU (R-LRU), which satisfies the cache downsizing requirement during the transition period. The key idea of this new policy is to migrate the

Fig. 3. Tag and index of data cache.

accessed block to the enabled part of cache during the transition period while consider the intrinsic temporal locality of the workloads. There are three cases in the R-LRU replacement algorithm, as Algorithm 1 shows:

- Case 1: hit in the disabled part.

- Case 2: hit in the enabled part.

- Case 3: miss in the whole d-cache.

R-LRU maintains a LRU list L. More precisely, a block in the head of L means it has been accessed recently while the one in the rear of L means it has the least access recently. Let block be the referenced cache block. We introduce three states: taking state enabled (E) to denote a cache way that one core can access, taking state disabled (D) to denote a cache way that one core can not access, and taking state transition (T) to denote a cache way that is in the transition period when downsizing the cache. Therefore, the transition state is a transient state to downsize the d-cache.

| MRU                                                                                                  | 1 | 2 | LRU | hit in enabled part | hit in disabled part | miss in whole cache |

|------------------------------------------------------------------------------------------------------|---|---|-----|---------------------|----------------------|---------------------|

|                                                                                                      |   |   |     | -                   | evict LRU block      | -                   |

|                                                                                                      |   |   |     | -                   | evict LRU block      | -                   |

|                                                                                                      |   |   |     | _                   | evict block 2        | evict block 2       |

|                                                                                                      |   |   |     | _                   | evict LRU block      | -                   |

|                                                                                                      |   |   |     | _                   | evict block 2        | evict block 2       |

|                                                                                                      |   |   |     | -                   | evict block 1        | evict block 1       |

|                                                                                                      |   |   |     |                     |                      |                     |

|                                                                                                      |   |   |     |                     |                      |                     |

| block in transition state block in enabled block performance maintain case performance promoted case |   |   |     |                     |                      |                     |

Fig. 4. Benefit from R-LRU algorithm.

To show the benefit of the R-LRU algorithm, we explain the advantages using LRU-based stack as depicted in Fig. 4. There are six different LRU stacks for R-LRU during the transition period. On the left of the graph, MRU position stands

#### Algorithm 1. Resizing-LRU Replacement Algorithm

```

Input: block: memory reference address. L: LRU list.

Output: L: LRU list.

// LRU The pointer to the LRU position

// MRU The pointer to the MRU position

ptr = FindBlock(block, L);

if (ptr! = NULL) then

if (ptr - > state == T) then

/* case1, hit in the disabled part of

cache */

Block * tmp = LRU;

while (tmp - > state! = E) do /* find the last enabled block in

tmp = tmp - > prev;

end

\text{Evict}(tmp);

ptr - > invalid = true;

tmp = ptr;

MRU = tmp;

/* case2, hit in the enabled part of cache */

MRU = ptr;

end

/* case3,miss in the whole cache */

else

Block * tmp = LRU;

while (tmp - > state! = E) do

/* find the last enabled block in L

tmp = tmp - > prev;

end

\text{Evict}(tmp);

tmp = ptr;

MRU = tmp;

end

Update(L);

return L;

```

for the most recently used block while LRU position stands for the least recently used block. The position next to MRU in the recency position is referred as position 1 and the next position as position 2. The shaded block is in transition state while switch to disabled state after the transition period. On the right of the graph, the 18 scenarios of cache accesses are listed. In the following, we will discuss the three cases individually:

Case 1 (hit in the disabled part). A hit in the disabled part is identical to a miss in the enabled part. The last enabled block of the LRU list is evicted and we replicate the hit data of to-be-disabled part to this position. Although the capacity of the hit set probably decreases, R-LRU only replicates the hit data rather than accessing the next level cache. Hence, the cost of this case is less than a real miss. Furthermore, there are three scenarios that evict the LRU

block and only one scenario that evict block located the secondary of the LRU list, as shown in the second column of the table. An accessed block exhibits temporal locality if it is likely to be accessed again in the near future. In this way, R-LRU increases the amount of most recently used data in the enabled part, which suggests a benefit from R-LRU replacement algorithm.

Case 2 (hit in the enabled part). For a hit in this part, the R-LRU algorithm just need to update the LRU list, moving the hit blocks to the head of list. This is not different from traditional LRU replacement algorithms. The more hits in the enabled part, the better the locality is in this part. It is effortless to maintain the performance after downsizing. There is no extra overhead using R-LRU in this case. As a result, R-LRU maintains cache performance as shown in the first column of the table.

Case 3 (miss in the whole d-cache). While on a cache miss, the referenced block is only brought into the enabled part. R-LRU finds the last enabled block in the LRU list and evicts it. In this case, there are three scenarios that the evicted blocks occur in the LRU position, which are the same as the conventional LRU replacement policy. In the rest of three scenarios, there is one eviction occurring at Position1 and two evictions occurring at Position2. Considering the LRU block is evicted immediately, R-LRU slightly adjusts the sequence of the LRU list and brings the new block into the enabled way in advance. In this manner, we are able to benefit from the R-LRU replacement policy if the LRU block is no longer accessed before being evicted.

In our framework, the R-LRU policy allows in the transition period to transfer the accessed data from the to-be-disabled way of cache to the enabled way or boost the live-ness of the data in the enabled way. Ideally, all the enabled blocks will be included in the first N nodes of the LRU list after the transition period. In other words, the entire recently used nodes are located at the head of the LRU list. When the  $t_{switch}$  approaches, this optimization minimizes cache miss penalty introduced by downsizing.

#### 5 Evaluation

#### 5.1 Experimental Platform Setup

Our baseline of 8-issue core configuration is presented in Table 1. As explained above, the largest  $\rho$ -VEX core has a four-way set-associative d-cache in the 8-issue mode. While in the 4-issue mode, the cache is divided over the two cores and therefore also half cache size (32 Kbytes, 2-way) for each core. Similarly, in the 2-issue mode each core has a 16 Kbyte direct-mapped cache. We choose MiBench benchmark suite [11]. The benchmarks were compiled with the vex-3.43 compiler (Hewlett-Packard compiler) using -O3 optimization level and -fno-xnop-fexpand-div flags. Our experimental platform comprises the following elements:

- ρ-VEX prototype: We use an FPGA to prototype the ρ-VEX and run applications on actual hardware. The design runs on a Virtex 6 (ML605 development

| Parameters          | 8-issue core                                             |

|---------------------|----------------------------------------------------------|

| Processor frequency | 37.5MHz                                                  |

| ALUs                | 8                                                        |

| MULs                | 4                                                        |

| Load/Store unit     | 1                                                        |

| Branch unit         | 1                                                        |

| L1 I-cache          | 32 Kbytes, 4-way, 32 bytes 1 cycle latency               |

| L1 D-cache          | 64 Kbytes, 4-way, 32 bytes 1 cycle latency write-through |

| Memory access time  | 10 cycles                                                |

Table 1. System configuration

board) at 37.5 MHz. A hardware trace unit collects all the executed instructions for each benchmark on the FPGA prototype of  $\rho$ -VEX.

- Cache simulator: We extracted the memory read and write operations from this traces for use as input to the cache simulator. We extended the DineroIV [12] cache simulator, which is a sequential trace-driven cache simulator, to be able to simulate the reconfigurable cache as presented in Sect. 3.

- Core phase predictor [13]: We implemented a simple phase predictor to measure the ILP of the benchmark traces and predict/decide the most suitable mode for the  $\rho$ -VEX core to execute in. In addition, this predictor takes into account the trade-offs in terms of delay, energy consumption, and the energy delay product (EDP) to make the phase predictions.

#### 5.2 Methodology

Our framework supports the dynamic reconfiguration of both cache downsizing and cache upsizing. When the cache upsizing occurs, which means the associativity is increased, tags and data arrays keep the data residing in it without degrading the performance. Henceforth, we only evaluate the scenario of d-cache downsizing. According to the trigger signal of the mode change, we perform the reconfiguration of d-cache downsizing in the framework proposed which combines the R-LRU replacement policy with varying transition periods. For the sake of fair comparisons, we also simulate the benchmark with the immediate d-cache upsizing/downsizing method at the same (time) points. Finally, we perform several different measurements after skipping the initialization part and warming up of the cache and the  $\rho$ -VEX processor is always initialized to the 8-issue mode.

#### 6 Results

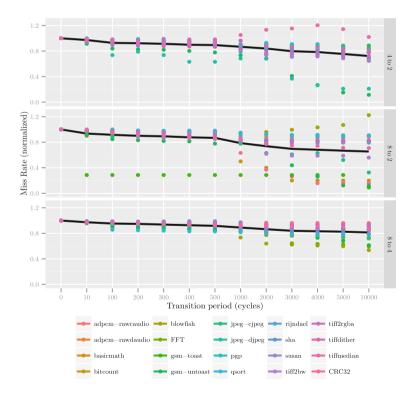

#### 6.1 The Impact of the Interval of Transition

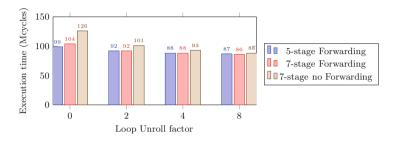

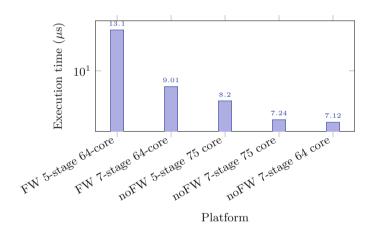

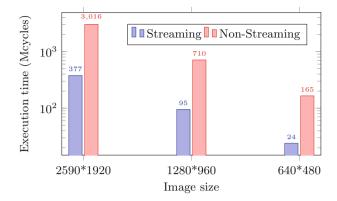

Figure 5 depicts how the interval of transition affects the performance, i.e., the cache downsizing occurs when the mode switched from 8-issue mode to 4-issue mode, from 8-issue mode to 2-issue mode and from 4-issue mode to 2-issue mode, respectively. The y-axis of three graphs represents the decreasing number of misses in 2000 cycles (bundles) after the actual downsizing compared to the immediate cache downsizing (normalized to immediate cache downsizing in the same execution point). We vary the interval of transition period ranging from 10 cycles to 10000 cycles (x-axis).

In the three scenarios of downsizing, our framework presents the same decreasing tendency of cache misses, which clearly demonstrates an advantage over the immediate cache downsizing approach. The longer the transition period is, the more the reduction in cache miss rate is. When the transition period is set to 2000 cycles, the majority of the benchmarks result in a near-optimal performance. More specifically, as shown in Fig. 5, our framework achieves a reduction

Fig. 5. The impact of the transition interval on cache misses with the mode change. The black lines indicate the average for all benchmarks.

in misses of on average 13% for 8-issue to 4-issue, 26% for 8-issue to 2-issue and 16% for 4-issue to 2-issue, respectively. The figure shows that for switches from 8-issue to 4-issue, for 16 benchmarks, the number of cache misses continuously decrease. It is also true for 11 benchmarks in when switching from 8-issue to 2-issue and for 12 benchmarks when switching from 4-issue to 2-issue.

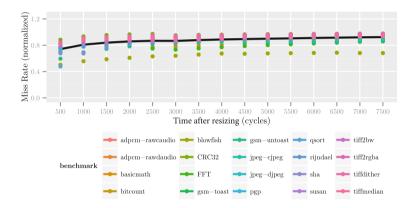

#### 6.2 About the Lasting Effect

Figure 6 depicts the MiBench benchmark's cumulative lasting effect for every mode change given the transition period is 2000 (bundle) cycles, from which we can observe that the cache misses curve of our approach (normalized to the cache miss rate due to immediate cache resizing without using our approach) gradually approaches y=1 (the immediate resizing curve) rather than jumps to it directly. The area between every curve and y=1 shows the advantages by using our framework.

**Fig. 6.** The lasting effect with execution time. The black line indicates the average for all benchmarks.

For all the benchmarks, we can also achieve the decline of cache miss by about, on average, 16% (2000 cycles after resizing), 14% (4000 cycles) and 9% (7500 cycles after resizing). From our experiments, our framework can improve the performance of the cache more than 6000 (bundle) cycles after cache resizing given the transition interval is 2000 (bundle) cycles. Such framework could be particularly useful in the scenario from a four-way set-associative cache to a two-way set-associative cache.

Without the transition period provided by our framework, the downsizing moments will result in sharp jumps in cache misses (y = 1 in Fig. 6). The upsizing moments will not result in immediate recovery of the cache miss rates either as the newly added cache resources need to be populated again. Using our framework, we smoothen the cache miss rate graph and when an upsizing

event happens before the (lasting) effect of our approach subsided, the cache miss rate can improve again from a much lower point. For example, the recovery can start from any point on the cache miss curve. In this manner, our approach can greatly reduce the cache miss rates in a dynamic environment in which the cache must be resized very quickly. This point is further strengthened by our measured result that a transition period of about 1000–3000 cycles is adequate to reach the main results of our approach.

#### 7 Conclusions

In this paper, we presented a novel reconfigurable d-cache framework combined with an adaptive R-LRU replacement policy without additional hardware overhead. We demonstrated that our framework has the capability to maintain a low miss rate with a transition period up to 6000 cycles while a period of 2000 cycles is enough to achieve good results. Moreover, our approach prevents the sharp miss rate increase as a result of the cache downsizing by on average between 10% to 63%. The short periods in which we achieved our results can lead to computing systems that more frequently perform core resizing (and therefore also cache resizing) in order to maintain a high level of responsiveness without sacrificing performance too much. Finally, when our framework is used in a scenario in which mode changes occur frequently, the improvement of cache performance is further amplified.

**Acknowledgement.** We would like to thank Prof. Wong for his valuable suggestions and kind help. We also thank TU Delft for their  $\rho$ -VEX platform.

#### References

- Anjam, F., Wong, S., et al.: Simultaneous reconfiguration of issue-width and instruction cache for a VLIW processor. In: Embedded Computer Systems (SAMOS) (2012)

- Zang, W., Gordon-Ross, A.: A survey on cache tuning from a power/energy perspective. ACM Comput. Surv. 45(3), 32 (2013)

- Keramidas, G., Datsios, C.: Revisiting cache resizing. Int. J. Parallel Program. 43(1), 59–85 (2015)

- Yang, S., Powell, M., et al.: Exploiting choice in resizable cache design to optimize deep-submicron processor energy-delay. In: High Performance Computer Architecture (2002)

- 5. Mittal, S., Zhang, Z.: EnCache: improving cache energy efficiency using a software-controlled profiling cache. IEEE EIT (2012)

- Beckmann, N., Sanchez, D.: Talus: a simple way to remove cliffs in cache performance. In: High Performance, Computer Architecture (HPCA) (2015)

- Wong, S., Van As, T., et al.: p-VEX: a reconfigurable and extensible softcore VLIW processor. In: FPT 2008 (2008)

- 8. Anjam, F., Nadeem, M., et al.: Targeting code diversity with run-time adjustable issue-slots in a chip multiprocessor. In: Design, Automation and Test in Europe Conference Exhibition (DATE) (2011)

- 9. Brandon, A., Wong, S.: Support for dynamic issue width in VLIW processors using generic binaries. In: Design, Automation Test in Europe Conference Exhibition (DATE) (2013)

- Kharbutli, M., Sheikh, R.: LACS: a locality-aware cost-sensitive cache replacement algorithm. IEEE Trans. Comput. 63, 1975–1987 (2014)

- 11. Guthaus, M., Ringenberg, J., et al.: MiBench: a free, commercially representative embedded benchmark suite. In: 2001 IEEE International Workshop on Workload Characterization, WWC-4, December 2001

- 12. Hill, M., Edler, J.: Dineroiv trace-driven uniprocessor cache simulator (2015)

- 13. Guo, Q., Sartor, A., et al.: Run-time phase prediction for a reconfigurable vliw processor. Design, Automation Test in Europe Conference Exhibition (DATE) (2016)

# LP-P<sup>2</sup>IP: A Low-Power Version of P<sup>2</sup>IP Architecture Using Partial Reconfiguration

Álvaro Avelino<sup>1(⊠)</sup>, Valentin Obac², Naim Harb³, Carlos Valderrama³, Glauberto Albuquerque³, and Paulo Possa³

<sup>1</sup> Technology and Science of Rio Grande do Norte, Federal Institute of Education, Nova Cruz, RN, Brazil alvaro.medeiros@ifrn.edu.br

<sup>2</sup> Electrical Engineering Department,

Federal University of Rio Grande do Norte, Natal, RN, Brazil

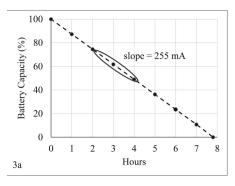

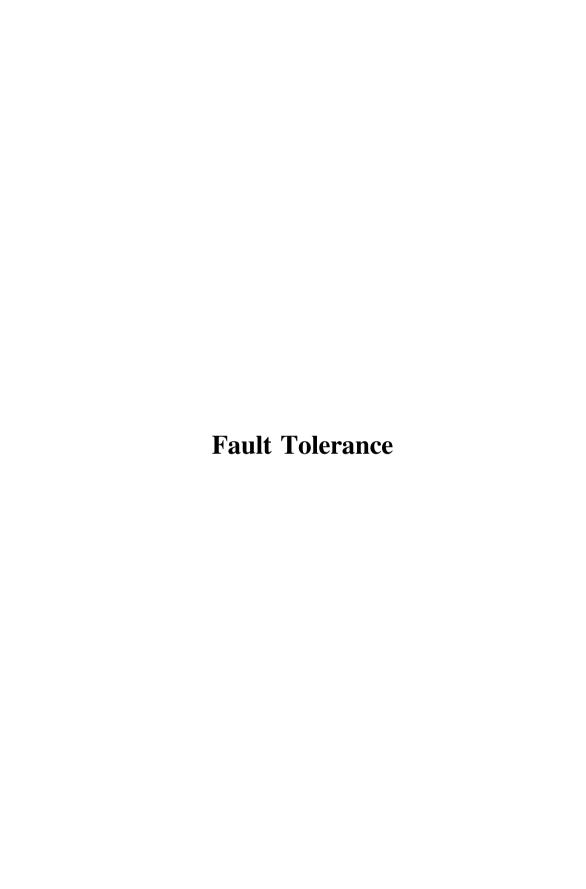

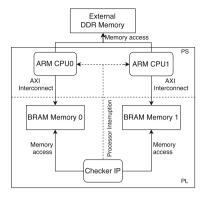

**Abstract.** Power consumption reduction is crucial for portable equipments and for those in remote locations, whose battery replacement is impracticable. P<sup>2</sup>IP is an architecture targeting real-time embedded image and video processing, which combines runtime reconfigurable processing, low-latency and high performance. Being a configurable architecture allows the combination of powerful video processing operators (Processing Elements or PEs) to build the target application. However, many applications do not require all PEs available. Remaining idle, these PEs still represent a power consumption problem that Partial Reconfiguration can mitigate. To assess the impact on energy consumption, another P<sup>2</sup>IP implementation based on Partial Reconfiguration was developed and tested with three different image processing applications. Measurements have been made to analyze energy consumption when executing each of three applications. Results show that compared to the original implementation of the architecture use of Partial Reconfiguration leads to power savings of up to 45%.

**Keywords:** Energy efficiency  $\cdot$  Low-power consumption  $\cdot$  FPGA  $\cdot$  Partial reconfiguration  $\cdot$  Embedded real-time video processing system

#### 1 Introduction

The Programmable Pipeline Image Processor (P<sup>2</sup>IP) is a systolic Coarse-Grained Reconfigurable Architecture (CG-RA) for real-time video processing embedded in FPGA. It features low-latency systolic array inherent structures, runtime reconfigurable data-path, high-performance CG operators and short compilation times of software applications. Its data path, operating at the pixel clock frequency, can deliver, after the initial latency of a 3-line pipeline, one processed pixel per clock cycle [2–4]. The architecture processing core consists of identical

© Springer International Publishing AG 2017 S. Wong et al. (Eds.): ARC 2017, LNCS 10216, pp. 16–27, 2017.

DOI: 10.1007/978-3-319-56258-2\_2

<sup>&</sup>lt;sup>3</sup> Electronics and Microelectronics Department, Université de Mons, Mons, Belgium

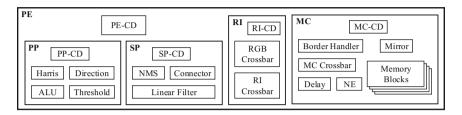

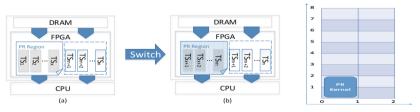

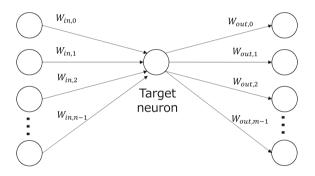

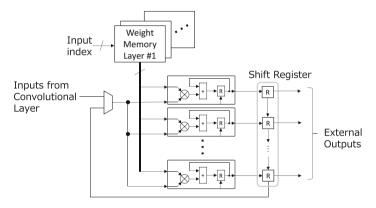

Processing Elements (PEs). Each PE contains an optimized set of essential image processing operators (see Fig. 1) that can be parameterized in run time by software, using virtual reconfiguration. The number and content of PEs is defined before synthesis. Thus, although available and contributing to the overall power consumption, not all PEs are in use depending on the processing performed on the video stream.

**Fig. 1.** Processing Element (PE) and its internal blocks. The main blocks are the Pixel Processor (PP), Memory Controller (MC), Spatial Processor (SP), Reconfigurable Interconnection (RI) and Configuration Decoder (PE-CD).

Applications for which there are power consumption restrictions, or where it is not possible to replace the battery that powers the circuit, such as a drone or a satellite, require circuit components with the highest energy-efficiency possible. Indeed, the use of smaller devices or a small number of enhanced devices reduces system cost and power consumption. On some modern FPGA devices, Partial Reconfiguration (PR) is a feature that allows changing the configuration of part of the device while the rest continues to operate. This feature can improve logic density by removing functions that do not operate simultaneously in the FPGA. In the context of P<sup>2</sup>IP, PR could lead to power savings by just replacing the content of an idle PE by a bypass using PR. This implies the use of a PE that implements no functionality other than a latched input driving its output. In a certain application, if there is one or more idle PEs, these can, using PR, assume the bypass configuration, reducing the overall power consumption.

We propose in this article a novel FPGA-based P<sup>2</sup>IP implementation using PR to reduce energy consumption. During configuration, the content of a PE can now be replaced by a bypass core, plus the possibility of assigning an optimized functionality. The latter represents a future enhancement as heterogeneous PEs can extend the architecture to support novel processing capabilities. To validate our proposal, we show comparative results concerning resources allocation, energy consumption and reconfiguration latency for three reference applications.

## 2 Energy Efficiency in FPGAs

Power consumption is a combination of static (which depends on the temperature T) and dynamic power, as stated by (1). The static power is caused by leakage

currents inside transistors and the dynamic power is caused by the switching activity when charging and discharging the load capacitance C, as well as short-circuit currents when transistors commute.

$$P_{total} = P_{static}(T) + P_{dynamic}(f) \tag{1}$$

Dynamic power, as stated in (2), has linear dependency on the clock frequency f and a quadratic dependency on the supply voltage V. In an FPGA, the load capacitance depends on the number of logic and routing elements used. The factor  $\alpha$  is the activity or toggle rate of an element; it depends on the topology and its input stimuli.

$$P_{dynamic} = \alpha \times C \times V^2 \times f \tag{2}$$

#### 2.1 Related Works

The Partial Reconfiguration capability can be beneficial to P<sup>2</sup>IP in two aspects, not only it can help to reduce power consumption but also extend its original functionality. Indeed, we report many related techniques that can be used in FPGAs to achieve more efficient power consumption while preserving functionality. However, while PR allows the reuse of the underlying logic, design granularity, reconfiguration support infrastructure and reconfiguration speed may be limiting factors.

One way to compensate the power consumption increase during PR is to maximize the partial bitstream transfer bandwidth from external memory to the PR interface [6]. In [5], the authors propose an intelligent Internal Configuration Access Port (ICAP) controller using DMA for a Virtex-4 board. This is a good solution for Virtex-4, which does not support DMA when copying partial bitstreams, but imposes additional logic to synthesize the modified ICAP interface. [18] describes an alternative way to load a partial bitstream in a Virtex-5 board. A customized PR controller is developed, which uses DMA to load the partial bitstream from external memory (DDR) to the ICAP interface, being more efficient than the traditional approach from Xilinx for the Virtex-5 family.

Concerning granularity and reconfiguration speed, in [7] it is proposed a 1-cycle reconfiguration scheme, although all reconfigurable elements are mapped into DSP48E1 cells. Thus, a fast reconfiguration can be carried out by updating the parameters of the DSP cells, but at the cost of high power consumption and high-end (and therefore costly) FPGA. Another approach, [1], proposes an alternative ICAP interface (called AC-ICAP) capable of applying PR to single LUTs without requiring pre-computed partial bitstreams. According to the authors, it imposes an acceleration of 380x with respect to the Xilinx ICAP controller. The disadvantage is that it consumes 5% additional cells on a Virtex-5 FPGA. With regard to structures using more complex PR components, the authors in [8] implement a FIR filter applied to Software-Defined Radio and conclude that using PR leads to a half of the original power consumption.

Compared to the works mentioned above  $P^2IP$  is already a software-configurable and customizable hardware architecture. This implies that it is

already inherently scalable and flexible, so we assume a very small resources overhead by supporting PR. Due to requiring few or no additional controllers, when extended, its impact on energy consumption will be limited. As demonstrated by previous works, granularity has an impact on the size of partial bitstreams as well as on reconfiguration speed. The proposed architecture using regular components of intermediate granularity (greater than a DSP cell or a LUT) maintains PR time and partial bit-streams restricted. Moreover, the scalable aspect of the architecture makes it possible to combine various strategies to save static and dynamic power. However, this is a real-time configurable architecture, so, PR time can have an impact on the resulting image stream processing. Since the reconfiguration task is executed by the software side and several partial bitstream loading strategies are already available, the potential need to speed up the PR process is left out of the scope of this work.

#### 3 Modifications on P<sup>2</sup>IP

The original  $P^2IP$  architecture was enhanced to be used as AXI compliant IP for an FPGA implementation with extended configurable functionality including PR (for details about the original implementation refer to [4]).

#### 3.1 Configuration Mechanism

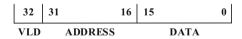

The configuration mechanism allows to enable/disable operators as well as the input/outputs of a PE. It consists of a configuration tree composed by Configuration Decoders (CDs) organized hierarchically. In the original version it communicates via an 8-bit serial interface [3]. The extended version provides an AXI4-Lite 32-bit interface clocked at 100 MHz and the configuration word carries two bytes of data (instead of one in the original implementation), as shown in Fig. 2.

Fig. 2. Configuration word. The Configuration Block reads the word when the VLD bit is high. ADDRESS corresponds to the operator ID, and DATA is the configuration info.

On Fig. 1 it is possible to see the PE Configuration Decoder (PE-CD) and four (Module + Register) dedicated CDs (for the PP, RI, SP and the MC modules). Each CD can decode one (e.g. NE), two (e.g. ALU) or three words of data (e.g. Reconfigurable Interconnect crossbar), and this limit is defined during instantiation of the component.

### 3.2 PR Applied on P<sup>2</sup>IP

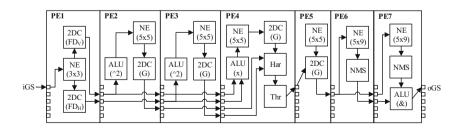

The runtime flexibility of  $P^2IP$  requires that the number of PEs and the provided functionality be enough to withstand all possible stream operations. For that reason, the number of PEs is defined before synthesis. Although, depending on the video processing algorithm to be executed, PEs are not completely in use. Considering, for instance, basic algorithms such as Edge Sharpening (Sharp), Canny Edge Detection (Edge) or Harris Corner Detection (Corner), they just share some operations. Sharp uses just three PEs to data processing, while the others use five (Edge) and seven (Corner), respectively. In that context, unused PEs still contribute to both, dynamic and static power consumption. For details about mapping each application onto  $P^2IP$  refer to [3].

To make possible the execution of the three aforementioned applications, seven PEs are defined. This number is chosen according to the *Corner* application, which, among the three, requires the greatest amount of PEs [3]. At runtime, the PEs or its content cannot simply be removed: it would interrupt the video stream continuity. Thus, in addition to the regular content of a PE core (all the blocks as shown in Fig. 1), a modified version (core+bypass) is proposed, in which the output buffers the input, to ensure a continuous video stream before removing the core. Indeed, the core of each PE is contained in a Reconfigurable Region (RR), as suggested in [4]. So, seven RRs are defined in the FPGA area. PEs are equal in size and content, hence, all RRs resource requirements are the same. However, resources allocated to each RR may vary, depending on where the RR is allocated in the FPGA area (and, consequently, the available resources in the referred area).

To achieve the three mentioned applications examples using PR, three configurations are defined:

- Sharp: RR1, RR2, RR3 in default configuration; RR4, RR5, RR6 and RR7 bypassed;

- Edge: RR1, ..., RR5 in default configuration; RR6 and RR7 bypassed;

- Corner: RR1, ..., RR7 in default configuration.

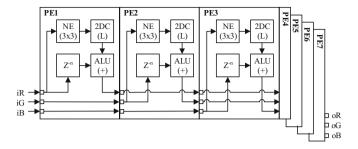

Figures 3, 4 and 5 show, respectively *Sharp*, *Canny* and *Corner* applications mapped onto P<sup>2</sup>IP using PR. The software-driven configuration mechanism is responsible for activating the inputs, outputs and internal blocks of each PE.

### 4 Methodology

The new architecture is able to allocate resources (PEs) to reconfigurable regions (RRs) defined in the FPGA area. Resources allocated to each RR can be of type bypass or original PE core.

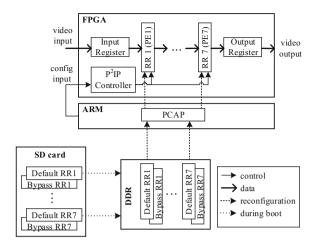

Fourteen partial bitstreams (Default RR1..7 and Bypass RR1..7, in Fig. 6) are initially stored in an SD card. During boot, the ARM processor copies these partial bitstreams to the DDR memory.

After that, the ARM also loads a full bitstream (the initial configuration containing static and dynamic parts) before the FPGA starts running.

Fig. 3. Sharp application mapped onto  $P^2IP$ : the first three PEs are in default configuration; the four last are configured as bypass.

**Fig. 4.** Canny application mapped onto P<sup>2</sup>IP: the first five PEs are in default configuration; the two last are configured as bypass.

By default, the Xilinx Zynq platform offers two options to load a bitstream into the FPGA: the Internal Configuration Access Port (ICAP) or the Processor Configuration Access Port (PCAP). The first one is in use, for a long time, by the previous FPGA families [1,5,17,18]. It consists of an IP softcore and, consequently, spends some FPGA resources. The PCAP interface is native, does not consume any FPGA resources and uses a DMA engine [10]. This process is more efficient than the one adopted by the previous Xilinx FPGA families, since these generations did not use DMA natively, turning the partial bitstream transfer slower [9] while forcing the designer to consume more FPGA resources to allocate a custom DMA engine or the ICAP interface [17].

Fig. 5. Corner application: all PEs are in default configuration.

**Fig. 6.** P<sup>2</sup>IP using PR: during boot, the ARM reads the partial bitstreams from the SD Card and loads them into the DDR. On demand, during runtime, the partial bitstreams are loaded from DDR into the RRs.

More details about the bitstream copy from the SD card to the DDR memory and from the DDR memory to the PCAP interface (valid for the Xilinx 7-series FPGAs) can be found on [19].

Since the purpose of this work is to reduce energy consumption, additional logic must be minimized, therefore the PCAP interface was chosen to transfer (static and partial) bitstreams from the memory to the FPGA, under the ARM supervision. The ARM is also used to activate the inputs/outputs, internal interconnections and blocks of each PE via an AXI4-Lite [14] interface.

For details about how the configuration mechanism works refer to [3]. Since all the video processing is done on the FPGA side, we have chosen to use a baremetal implementation on the ARM side, instead of using an Operating System. Figure 6 shows the block diagram of the architecture using PR, detailing how the ARM loads a partial bitstream into P<sup>2</sup>IP.

### 5 Results

A P<sup>2</sup>IP implementation based on PR was developed and tested with multiple configuration scenarios. Synthesis has been performed using Vivado 2015.2.1 and Zynq 7020 System on Chip (SoC). It consists of a SoC containing an Artix-7 FPGA, from Xilinx, and a dual-core ARM Cortex-A9 processor. To demonstrate that the use of PR applied to P<sup>2</sup>IP implies energy savings without disrupting the real-time feature of the architecture, results regarding resource allocation, power measurement and reconfiguration time analysis are shown in this section.

### 5.1 Resource Analysis

Among the three applications, *Sharp* requires less resources, since four out of seven PEs are partially reconfigured as bypass. *Edge* still uses less logic resources than the static implementation, since the two last PEs are bypassed. *Corner* is more resource-consuming than the static implementation because all PEs are in the default configuration.

This application demands a higher number of resources than the original implementation, but in the worst case the resource increase is less than 5%, due to the extra logic added when using PR, and, in the best case, there is a resource utilization reduction of more than 50%.

The left side of Table 1 shows the resources utilized by each application compared to the static implementation. Sharp requires less than a half resources, when compared to the original implementation. Edge uses less than 80% of the resources required by the static implementation. Corner introduces almost 5% more FFs and 2% LUTs than the static implementation.

**Table 1.** Allocated resources, compared to the original implementation (left side) and measured power, in mW (right side).

|        | Allocated resources |         |        | Measured power, in mW |     |         |

|--------|---------------------|---------|--------|-----------------------|-----|---------|

|        | LUTs                | FFs     | RAMB18 | Original              | PR  | Δ       |

| Sharp  | 43.59%              | 48.31%  | 42.85% | 371                   | 204 | -45.01% |

| Edge   | 70%                 | 76.62%  | 71.42% |                       | 280 | -24.52% |

| Corner | 101.94%             | 104.73% | 100%   |                       | 373 | +0.54%  |

### 5.2 Power Consumption Measurement

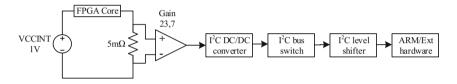

Previously, it has been shown that Sharp and Edge use less active resources than the static implementation. It leads to energy savings. To measure the energy consumption, we used the ZC702 board from Xilinx, which has current and voltage monitoring circuits [11]. One of these circuits is able to measure current and voltage applied to the FPGA core, as shown in Fig. 7. VCCINT is a 1 V voltage applied to the FPGA core. The voltage drop across a  $5\,m\Omega$  is fed to an Instrumentation Amplifier (IA), whose gain is 23.7. The IA output serves as input to an I<sup>2</sup>C DC/DC converter, which monitors VCCINT and turns the analog voltage into digital data (I<sup>2</sup>C). Since there are other I<sup>2</sup>C components on the board, an 1-to-8 channel I<sup>2</sup>C multiplexer is present.

Data can be accessed by the ARM [12], the FPGA or by means of a USB Interface Adapter, from Texas Instruments [13]. As stated before the monitored information is accessed through  $\rm I^2C$  protocol. Getting data using the FPGA is not the most efficient solution, since it means adding logic resources to define in hardware  $\rm I^2C$  communication interface and, consequently, it would contribute to

power consumption increasing. Using the ARM is a good alternative if the USB Interface Adapter is not available.

In this work we have used the USB Interface Adapter. Fusion Power Digital Design software, from Texas Instruments, links to the USB Interface Adapter and gets voltage and current information, making possible to calculate the power consumption. It is possible to define measurement parameters and acquisition rate. Minimum acquisition rate is 10 ms, but it is important to highlight that the USB Interface Adapter is plugged to a computer running Microsoft Windows, which is not a Real Time Operating System (RTOS), and, thus, there is no guarantee that the acquisition rate will be respected. Due to this restriction during tests the minimum acquisition rate used was 100 ms. An advantage of this method compared to the ARM reading current and voltage is that the first does not interfere in the ARM power consumption [15].

Fig. 7. FPGA core current measurement circuit on ZC702 board. Current can be read by the ARM processor or by an external hardware from Texas Instruments, both through the  $\rm I^2C$  bus.

The right side of Table 1 shows the measured power for the three configurations using PR (third column), compared to the original implementation (second column). The last column of the referred Table shows how much power savings it is possible to achieve using PR into P<sup>2</sup>IP. For each configuration 200 samples have been acquired using a sample rate of 100 ms, totalizing a 20 s acquisition (for each application). The values shown on Table 1 are the average of the 200 samples.

As can be seen in the previous Table, the power overhead for the *Corner* algorithm, due to the extra partial reconfiguration logic, is negligible.

### 5.3 Reconfiguration Latency

Another important point to be discussed is the amount of time necessary for changing configurations. Transitions require loading two partial bitstreams (such as from *Sharp* to *Edge*) or four partial bitstreams (such as from *Sharp* to *Corner*). According to Xilinx the bitstream transfer rate using PCAP interface in non-secure mode is 400 MB/s [16]. Partial bitstream size for RR1, RR2 and RR3 is 306 KB; for RR4, 309 KB; and, for RR5, RR6 and RR7, 409 KB. To measure the time necessary to load one partial bitstream a 64-bit general purpose ARM timer was used. Time to reconfigure each partial bitstream was measured and the average data rate is 128.51 MB/s.

Table 2 shows the time necessary to change configurations. To load one partial bitstream it is necessary: 2.381 ms, for RR1, RR2 or RR3; 2.404 ms, for RR4; and 3.175 ms for RR5, RR6 and RR7.

|        | Sharp  | Edge  | Corner |

|--------|--------|-------|--------|

| Sharp  | -      | 5.579 | 11.929 |

| Edge   | 5.579  | -     | 6.350  |

| Corner | 11.929 | 6.350 | _      |

Table 2. Latency, when changing configurations, in ms.

To assure that, using PR, the system remains a real time one, the following Equation is used:

$$t_{total} = t_{reconfig} + t_{config} \tag{3}$$

where  $t_{total}$  is the total reconfiguring latency,  $t_{reconfig}$  is the time necessary to apply PR to the RRs and  $t_{config}$  is the time necessary to configuring internal PE blocks.

Time necessary to apply PR depends on how many RRs will be configured and is described in (4):

$$t_{reconfig} = \sum t_{RR_i} \tag{4}$$

where  $t_{RR_i}$  is the time necessary to apply PR to each RR.

Time necessary to apply PR to one RR depends on the external memory (which stores the partial bitstream) access and also on the time to load the partial bitstream on the respective RR and is shown in (5):

$$t_{RR_i} = t_{DDR} + t_{load_{PR}} \tag{5}$$

To maintain the real time feature of the system the following Equation must be respected:

$$t_{total} < t_{frame} \tag{6}$$

If (6) is respected then only one frame will be lost during reconfiguration, using PR or not. If the time overhead introduced by PR is less than the frame timing the extra time necessary to apply PR is admissible and does not imply in additional delay, that is, the system remains real time.

It is necessary  $t_{config} = 0.27 \,\mu s$  for each operator to be configured. In terms of latency the worst case is to change from *Sharp* to *Corner*, in which it is necessary to apply PR to four RRs and configure 21 operators (see Fig. 5). In this case  $t_{total} = 11.935 \, ms$ . So, only one frame will be lost when applying PR. When changing the configuration (the number of active PEs or event an internal block) of the architecture (using PR or not) one frame will be lost. This work proves that it is possible to apply PR without losing additional frames.

### 6 Conclusions

In this article we have presented a low-power P<sup>2</sup>IP architecture based on the use of the PR strategy. The original architecture was extended to support PR: processing elements were designated as PR components resulting on less than 5% resources overhead. To demonstrate the advantages of this novel architecture in terms of power consumption, three image processing algorithms were mapped and executed on both architectures. Power consumption comparison of original and PR implementations has been carried out and attested that PR implementation leads to power savings of up to 45%. The worst-case scenario, which takes into account the use of all available resources, implies an additional energy cost of less than 1%. Furthermore, PR latency does not affect the real-time feature of the system.

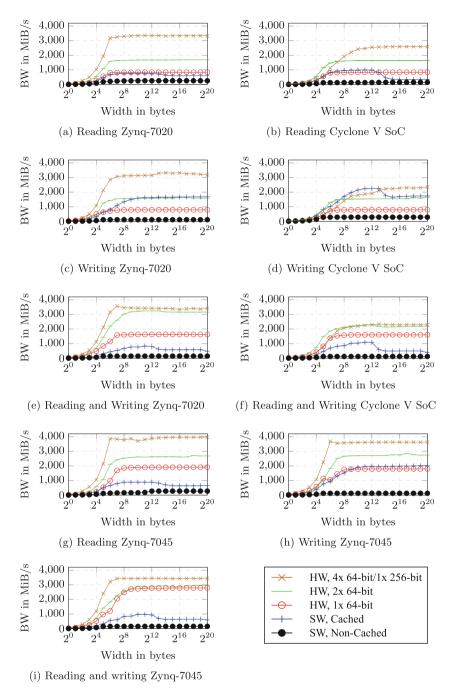

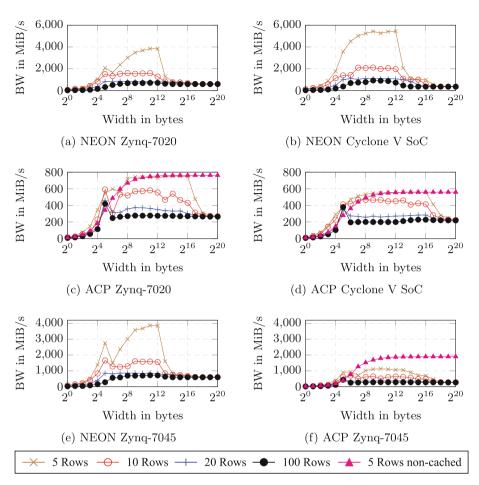

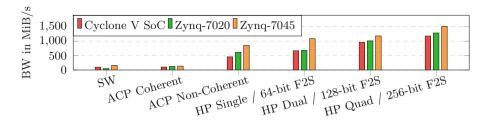

The PR strategy should not only be applied to lower the power consumption, it also serves to combine multiple alternative implementations of PEs that can be interchanged according to particular execution and quality requirements. Thus, future work should investigate the balance between power saving and required processing power.