**Signals and Communication Technology**

Bogdan Belean

## Application-Specific Hardware Architecture Design with VHDL

#### Signals and Communication Technology

More information about this series at http://www.springer.com/series/4748

#### Bogdan Belean

# Application-Specific Hardware Architecture Design with VHDL

Bogdan Belean National Institute for Research and Development of Isotopic and Molecular Technologies Cluj-Napoca Romania

ISSN 1860-4862 ISSN 1860-4870 (electronic) Signals and Communication Technology ISBN 978-3-319-65023-4 ISBN 978-3-319-65025-8 (eBook) https://doi.org/10.1007/978-3-319-65025-8

Library of Congress Control Number: 2017949155

#### © Springer International Publishing AG 2018

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by Springer Nature

The registered company is Springer International Publishing AG

The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

#### **Contents**

| 1 Introduction to Digital Design with VHDL |      |                                                         |    |

|--------------------------------------------|------|---------------------------------------------------------|----|

|                                            | 1.1  | Digital Systems—Introductory Notes                      | 1  |

| 1.2 Levels of Abstraction                  |      |                                                         | 3  |

| 1.3 The VHDL Hardware Description Language |      |                                                         | 6  |

|                                            |      | 1.3.1 Overview of Hardware Description Languages        | 6  |

|                                            |      | 1.3.2 VHDL Code Structure                               | 8  |

|                                            |      | 1.3.3 Data Types and Operators                          | 10 |

|                                            | 1.4  | Combinational Logic, Sequential Logic and VHDL          | 14 |

|                                            |      | 1.4.1 Concurrent VHDL Code                              | 15 |

|                                            |      | 1.4.2 Sequential VHDL Code                              | 19 |

|                                            | 1.5  | Structural Description with VHDL                        | 25 |

|                                            | 1.6  | VHDL Code for Simulation Test-Benches                   | 32 |

|                                            | 1.7  | Finite State Machines                                   | 40 |

|                                            | 1.8  | Methodology for Digital Design with VHDL                | 47 |

|                                            | 1.9  | Conclusions                                             | 48 |

|                                            | App  | endix A                                                 | 49 |

|                                            | App  | endix B                                                 | 50 |

|                                            | App  | endix C                                                 | 53 |

|                                            | Refe | erences                                                 | 54 |

| 2                                          | Har  | dware Architectures for Channel Encoding in Information |    |

| _                                          |      | nsmission Systems                                       | 55 |

|                                            | 2.1  | Introduction to Information Transmission System         | 55 |

|                                            |      | 2.1.1 Modelling an Information Transmission System      | 56 |

|                                            | 2.2  | ·                                                       | 58 |

|                                            |      | 2.2.1 Representation of Error Control Codes             | 58 |

|                                            |      | 2.2.2 Classification of Error Control Codes             | 59 |

|                                            |      | 2.2.3 Error Control Codes Parameters                    | 60 |

viii Contents

|   | 2.3  |          | Codes                                                | 61  |

|---|------|----------|------------------------------------------------------|-----|

|   |      | 2.3.1    | Coding Equations                                     | 61  |

|   |      | 2.3.2    | Decoding Equations                                   | 63  |

|   | 2.4  |          | ning Coder/Decoder Implementations                   | 64  |

|   |      | 2.4.1    | Encoder Implementation                               | 65  |

|   | 2.5  |          | Codes Principles                                     | 71  |

|   | 2.6  |          | Codes Encoder and Decoder Implementations            | 72  |

|   |      |          | Cyclic Decoder Architectures                         | 77  |

|   | 2.7  |          | usions                                               | 77  |

|   | Refe | erences. |                                                      | 78  |

| 3 | High |          | ughput Hardware Architecture for LDPC Decoders       | 79  |

|   | 3.1  |          | uction to LDPC Codes for Digital Communication       | 80  |

|   | 3.2  |          | ling Algorithms Description                          | 82  |

|   | 3.3  |          | Complexity Approach for LDPC Decoding Process        | 83  |

|   | 3.4  | Conclu   | usions                                               | 96  |

|   | Refe | rences.  |                                                      | 96  |

| 4 | Har  | dware .  | Architecture for Edge Detection                      | 99  |

|   | 4.1  |          | uction—Microarray Image Processing System            | 99  |

|   | 4.2  |          | vare Architecture for Image Convolution              | 102 |

|   |      | 4.2.1    | Convolution in Digital Image Processing              | 102 |

|   |      | 4.2.2    | Hardware Implementation for Convolution              | 104 |

|   | 4.3  | Hardw    | vare Architecture for the Canny Filter               | 110 |

|   |      | 4.3.1    | Canny Edge Detection                                 | 110 |

|   |      | 4.3.2    | Hardware Implementation of the Canny Edge            |     |

|   |      |          | Detector                                             | 113 |

|   |      | 4.3.3    | Timing Considerations for the Canny Edge             |     |

|   |      |          | Detection Architecture                               | 116 |

|   |      | 4.3.4    | System-on-a-Chip (SoC) for Edge Detection            | 120 |

|   | 4.4  | Canny    | Architecture Applied in Microarray Image             |     |

|   |      |          | ssing                                                | 126 |

|   | App  |          | )                                                    | 128 |

|   |      |          |                                                      | 140 |

| 5 | Har  | dware    | Architectures for Iterative Algorithms               |     |

| J |      |          | ations                                               | 141 |

|   | 5.1  |          | vare Architecture for Shock Filters Applied          |     |

|   |      |          | croarray Image Processing                            | 141 |

|   |      | 5.1.1    | Partially Differential Equations in Image Processing | 141 |

|   |      | 5.1.2    | Shock Filters                                        | 142 |

|   |      | 5.1.3    | Shock Filter Application—Microarray Grid             |     |

|   |      |          | Alignment                                            | 144 |

|   |      | 5.1.4    | Hardware Architecture for Shock Filters              | 149 |

|   |      | 5.1.5    | Timing Considerations                                | 151 |

|   |      |          |                                                      |     |

Contents ix

| 5.2 Hardware Architecture for Anisotropic Diffusion Applied |                 |                                                             |                                                       |     |  |

|-------------------------------------------------------------|-----------------|-------------------------------------------------------------|-------------------------------------------------------|-----|--|

|                                                             |                 | in Satellite Imagery                                        |                                                       |     |  |

|                                                             |                 | 5.2.1                                                       | Introduction to Satellite Imagery                     | 152 |  |

|                                                             |                 | 5.2.2                                                       | Perona and Malik Filter Formulation                   | 153 |  |

|                                                             |                 | 5.2.3                                                       | Hardware Implementation for Parallel Computation      |     |  |

|                                                             |                 |                                                             | of Anisotropic Diffusion                              | 156 |  |

|                                                             |                 | 5.2.4                                                       | Application-Specific Hardware Architecture for Perona |     |  |

|                                                             |                 |                                                             | and Malik Filter in Satellite Imagery—Case Study      | 158 |  |

|                                                             | 5.3             | Concl                                                       | usions                                                | 160 |  |

|                                                             | Refe            | erences.                                                    |                                                       | 161 |  |

| 6                                                           | Effic           | Efficient Hough Transform Implementation Using CAM Memories |                                                       |     |  |

|                                                             |                 |                                                             | Satellite Imagery                                     | 163 |  |

|                                                             | 6.1             |                                                             | te Imagery for Oil Slick Detection                    | 164 |  |

|                                                             |                 | 6.1.1                                                       |                                                       | 164 |  |

|                                                             |                 | 6.1.2                                                       | CAM-Based Approach for Efficient Hough Transform      |     |  |

|                                                             |                 |                                                             | Implementation                                        | 165 |  |

|                                                             | 6.2             | Memo                                                        | ory Implementation Using FPGA                         | 167 |  |

|                                                             |                 | 6.2.1                                                       | Memory Types                                          | 168 |  |

|                                                             |                 | 6.2.2                                                       | Inferred and Instantiated Memories Using VHDL         | 168 |  |

|                                                             |                 | 6.2.3                                                       | Memory Organization                                   | 174 |  |

|                                                             | 6.3             | CAM                                                         | Memory Implementation Using VHDL                      | 177 |  |

|                                                             | 6.4 Conclusions |                                                             | usions                                                | 181 |  |

| References                                                  |                 |                                                             |                                                       | 181 |  |

#### **About the Author**

**Bogdan Belean** was born in Tirgu-Mures, Romania, on February 7, 1983. He received the B.E. and Ph.D. degrees in Electronics and Telecommunication Engineering from the Technical University of Cluj-Napoca, Romania, in 2006 and 2010, respectively. Since 2008, he is involved in didactic activates as a research assistant and later as a Lecturer within the Technical University of Cluj-Napoca, Department of Communications. In 2011, Dr. Belean joined the Department of Mass Spectrometry, Chromatography and Applied Physics within the National Institute for Research and Development of Isotopic and Molecular Technology, Cluj-Napoca. In 2014, he became a member of the Center for Research and Advanced Technologies for Alternative Energies (CETATEA) within the same national institute. His research interests include signal and image processing, bioinformatics, application-specific hardware architectures for parallel computing and advanced technologies for alternative energies. His research results include over 30 publications and two open-source software solutions for biomedical image analysis.

### **Chapter 1 Introduction to Digital Design with VHDL**

The first chapter starts with an introduction to digital systems. The levels of abstraction commonly used for the description of a digital system are presented. Each abstraction level includes both a structural description and a behavioral one. The structural description consists of the components and their interconnections used for the digital system design, whereas the behavioral description is used for the representations of the system functionality as a whole. The most important tools in designing digital systems are the hardware description languages (HDLs). They allow the system description at a high abstraction level, where no technology information such as gate level circuit footprints and propagation delays is needed. Meanwhile, based on the HDL descriptions, the synthesis software tools are able to generate more detailed representation of the system, at lower abstraction levels. Considering these abstraction levels, details such as the gate level circuits used by different development technologies (e.g. FPGA or ASIC) are included in the digital system description. Once we established how digital systems are described using different abstraction levels, we proceed to the VHDL language constructs and semantics used to design digital logic. Examples of VHDL codes are provided along this chapter so the reader will get familiar on how to design and test the functionality of digital logic blocks.

#### 1.1 Digital Systems—Introductory Notes

A signal, as referred to in electrical engineering, communications and signal processing, represents a function which gives information about specific phenomena from the physical world. In other words, signals provide information about the variation in time and space of the physical systems. In mathematical terms, signals can be defined as continuous-valued or discrete-valued functions which correspond to the analog or the digital signals, respectively. A digital system is composed of interconnected modules designed to handle digital (discrete) signals in order to

1

© Springer International Publishing AG 2018

B. Belean, *Application-Specific Hardware Architecture Design with VHDL*, Signals and Communication Technology, https://doi.org/10.1007/978-3-319-65025-8\_1

analyze and describe specific physical phenomena. These modules are most often based on electronic circuits such as, memories, computing units (e.g. processors), digital audio-video devices or telecommunication devices. The main advantages of such digital modules (devices), where information representation is achieved trough digital signals, are: the reproducibility of information, flexibility, functionality (e.g. easier to store, transmit and manipulate) and the reduced cost. Taking into account these advantages, converting the information into a digital signal (i.e. digitization) has spread to a wide range of applications mainly in the field of computer science, telecommunication and control systems. A major trend in digital design is to use hardware description languages to describe the functionality of digital circuits. The present book is focused in developing digital modules by means of hardware description language, for both real-time image processing application and efficient implementations of channel coders and decoders, specific to the field of digital communication. To understand the methodology for developing digital modules, basic knowledge of digital circuits and their functionality are mandatory. Consequently, simple examples are used in the first chapter in order to ease the reader understanding on the basic concepts of designing digital circuits specific for a given application. Further on, the next chapters present in detail more complex digital circuits, called application specific hardware architectures which fulfill a specific task in a digital system (e.g. real-time edge detection in image processing systems).

A digital system can be analyzed from different perspectives or views: behavioral view, structural view and physical view [1]. The behavioral view examines the system at the most abstract level since it does not take into consideration the internal representation of the system. Practically, it describes the input—output functionality of the system. The structural view specifies how the system is internally represented by its components and their interconnections. This is also known as the diagram of the system. The physical view adds to the system description detailed information like components size, locations on the board or connection line paths. The layout of a printed circuit board is a suggestive example for a physical view of a digital system.

Describing such a complex system using one single process which accounts for all of the systems' views is a complex task. A common approach to ease the design of digital systems is to make use of several levels of simplified models, called abstraction levels. Before proceeding to the description of the abstraction levels, an example is given in order to underline the benefits of this approach. Thus, the process of designing digital logic starts with the behavioral description of the system to be designed. Building blocks such as, registers, multiplexors, and logic blocks with their input output signals are interconnected in order to implement the desired functionality. In this type of description, details such as footprints of the gate level components (e.g. AND logic gate), propagation path delays or other physical characteristics of the target device do not affect the implementation. This description is part of a high abstraction level, where not all the implementation details are accounted. In case of lower abstraction levels, the description of the same

digital logic is performed using different building block such as, logic gates and flip-flops, which leads to a more detailed description of the same digital logic.

#### 1.2 Levels of Abstraction

Due to its complexity, a digital system is described by taking into consideration several abstractions levels. Each abstraction level is characterized by (1) the building blocks used to construct the digital system, (2) the representation of the signals that the building blocks operate with, and (3) the behavioural representation of the digital logic functionality.

Considering the building blocks used, the levels of abstraction for digital systems description are [1]:

- Transistor level;

- Gate level;

- Register transfer level (RTL);

- Processor level.

The lowest description level is the transistor level, which includes all the details for the digital systems implementation on the target device and represents the more accurate description. The highest level (i.e. processor level) represents a summarized description of the whole digital system, meaning building blocks such as processors make use of computing units and memories to apply a specific algorithm (computational steps) on the input data.

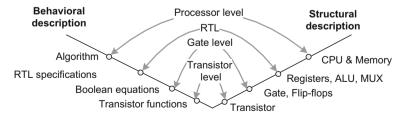

It is worth mentioning, each digital system can be seen either through its structural description (the building blocks used for its description) or through its behavioural description (behavioural representation of its functionality) [1]. Keeping this in mind, Fig. 1.1 shows both the digital system views and the corresponding abstraction levels.

Considering the transistor level, the main building blocks are transistors, resistors, capacitors etc., whereas the signals are represented by time varying voltages. The behavioural representation and the physical representation are given by differential equations and transistor detailed layouts respectively.

Fig. 1.1 Digital systems views and their corresponding abstraction levels

The second abstraction level, namely the gate level, involves simple logic blocks like logic gates, multiplexers or flip-flop as basic building blocks for digital system description. The signals are represented as logic values 0 or 1, whereas Boolean equations are used for behavioral representation.

The RTL abstraction level has building blocks constructed from simple gates such as arithmetic logic units, multiplexers, comparators or registers. In this case, the signals are interpreted as specific data types, whereas time representation is interpreted using number of clock cycles as time unit. The behavioral representation of the building block from the RTL level is described by finite state machines.

The processor level is characterized by building blocks such as processors, memory modules, intellectual properties and bus interfaces. The behavioral representation at this level of abstraction is performed through a program or algorithm coded in a conventional programming language.

Up to this point, we have a general view on how the digital systems can be described. Thus, the next step is to develop digital systems by using a hardware description language and specific software tools. Developing a digital system supposes the following design tasks to be fulfilled [1]:

- (i) Synthesis

- (ii) Physical design

- (iii) Verification

- (iv) Testing

#### Synthesis

The synthesis process is a transformation of the system either from a description in the behavioural domain to a description of the same design in the structural domain or from a description which makes use of a high-level abstraction to one which uses a low-level abstraction [1]. The synthesis process can be divided into several steps [1], presented as follows: high-level synthesis (i.e. transforms an algorithm into an processor level description with the control and data paths); RTL level synthesis (i.e. transforms the behavioural description of the RTL level to a structural implementation using RTL level components like adders, registers, multiplexers); gate-level (logic) synthesis (i.e. transforms the RTL level description into a descriptions which uses gate-level components and which have the behavioural representations given by Boolean equations); technology mapping (i.e. the gate level circuits are build using the cells of the technology used for the implementation of the digital design under development).

#### Physical design

The physical design refers to the refinement process between the structural and physical representations, but also an analysis of the circuit's electrical characteristics. The main steps that should be performed are [1]:

- Floor planning—provides a layout at the processor and RT levels; at this step the system is partitioned into function blocks;

- Placement and routing—provides a layout at the gate-level;

#### Verification

The verification process has to determine if the design accomplishes the specification and the performance required [1].

- Functional verification: check the functionality of the initial design by comparing the output obtained with the output desired; converts the initial design to a gate-level structural representation through the refinement process;

- Performance/Timing verification: the performance is measured by analyzing some timing constraints like maximal propagation delay or minimal clock frequency; at the RT-level the delay of an input-output path is calculated by summing the individual components delays; at the gate-level the propagation delays depend on the components but also on the interconnection wires.

The specific methods of verification for digital designs are:

- Simulation, which examines a system's functionality and performance without

effectively building it; practically, the simulation constructs a model of the

system but like any model, it involves also limitations (e.g. the simulations does

not necessary illustrate the exact same functionality as the real life circuit).

- Timing analysis, which verifies if the system accomplishes the timing goals, by

calculating the propagation delays on the circuit paths and by determining the

timing parameters;

- Formal verification which is based on mathematical methods for verifying if two representations of a system have the same functionality.

- Hardware emulation, which implements a prototyping circuit which reproduces the system's functionality (e.g. an FPGA circuit may be used to emulate an ASIC design before its prototyping).

#### **Testing**

Testing appears to be easy, since the whole design has already been build. Nevertheless, the detection of the physical errors during the fabrication process which affect the functionality of the design is not a trivial task. Thus, considering a large number of inputs and an increased complexity of the designed system, the addition of auxiliary circuits and processes as test pattern generation are demanded.

As a concluded remark, the digital systems are analyzed from different perspectives (behavioural, structural, physical) and they are represented at different abstraction levels. Also, the development of a digital system requires several steps and each step has a very important contribution in constructing a system which meets the specifications and the desired performance. These steps are: synthesis, physical design, verification and testing. Certain tasks of the designing process may be automated, but, the automation process is limited so the digital systems cannot be designed without the amazing work of the human mind.

#### 1.3 The VHDL Hardware Description Language

Knowing that a digital signal can be described from different point of views, perspectives and levels of abstraction we can observe that, the evolution of the design process, is determined both by human minds and software tools. It is a great help to have a standard framework, so that information can be exchanged between peers or software. The common framework is represented by a *hardware description language* (HDL). In the next chapter, a hardware description language will be described in general, so that we get a better picture if its capabilities. The particular case of a hardware description language is VHDL language. A series of language constructs and semantics together with VHDL code examples will be approached to get a closer view of a specific HDL.

#### 1.3.1 Overview of Hardware Description Languages

An HDL is different than any traditional programming language because it's being modeled after hardware. It describes a circuit that was already built or that is in its developing stage. Moreover, with the help of the HDL and synthesis software tools, the circuit can be modeled with high precision at the desired level of abstraction. This means it can be described using any type of buildings blocks (e.g. registers, logic gates or even transistors).

As we already know, there are many programming languages like C, Java, Python and so on, but neither of those are suitable for modeling hardware due to their limitations (they are build exclusively to program general purpose processors). Before the HDL programming languages have been developed, the characteristics of the common programming languages were studied by the designers in order to provide the best syntactic constructs and their associated semantics for building digital logic.

A common programming language is characterized by two features:

- Syntax—syntactic constructs and grammatical rules used to write a program;

- Semantics—the meaning associated with the syntactic constructs.

These two characteristics have definitely been accounted for building the hardware description languages and, naturally, they are found in any HDL. Other than these, there are more differences than similarities.

The majority of programming languages are using a sequential process to describe an algorithm to be used on a classic computer model (for example the C language). In this way the operations are performed one at a time (i.e. sequentially) having two important benefits: at abstract level, it helps the human mind to develop an algorithm one step at a time, whereas at the implementation level, the algorithm being sequential it suitable for the implementation on the basic computer model (one instruction at a given time).

Digital systems work completely different than the sequential ones, having smaller modules with input and output ports, which are connected through customized wiring. These parts/modules with input and output are commonly known as black-boxes. Here we can talk about a propagation delay, due to fact that operations associated with each module are performed concurrently. When signal changes appear at the inputs, new operations are initiated by the black-box for which the inputs changed. When the process is completed, there will be values generated at each output port that can initiate other operations so timing and connection of parts are essential when modeling digital hardware. This is why traditional programming is not suitable for digital systems, leading to the creation of a special language like VHDL, for digital hardware description.

#### The use of an HDL program

As previously mentioned, HDL programs work in a different way as compared to classic computer architectures. Any hardware description language has three major roles in digital system design:

- Formal documentation: at the beginning of the circuit design, a clear description is needed and, because the HDL semantics and syntax are precisely defined, this program (HDL description) will be rigorous and explicit (perfect documentation that can be shared between designers and software tools)

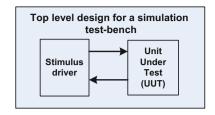

- *Input to a simulator*: before having a physical system, a simulation of the circuit will be needed, making the HDL description ideal to model concurrent operations in a sequential host computer. The input for the HDL description will be generated through a HDL test-bench formed by all test vector generation applied at the inputs of our design described by the HDL program.

- *Input to a synthesizer*: refinement process converts high-level behavioral description to a low-level structural description, those steps being performed by the synthesis software. The input for the synthesis software is the HDL program; the synthesis translates the HDL behavioral description into the structural description using specific libraries for the components used in the HDL program/description.

Before getting into details regarding the particular case of the VHDL hardware description language, we present the common features of a hardware description language in general. Thus the components of a digital logic description will be defined as entities. Connectivity, concurrency and timing characterize each entity and they are also defined in what follows.

The entity is the main independent block modeled after a real life digital circuit which has no information about any other blocks. It describes the inputs and outputs of a given logic block.

Connectivity is the term which defines how different entities interact. More than one entity can be active at the same time, having operations processed in parallel; this is possible because of the way entities communicate with each other through

wires; the wires defined by the hardware description language are associated with connectivity parts from real life.

Concurrency characterizes the behavior for all entities placed on a given design. Each entity performs specific operations on the input signals, whereas all operations corresponding to all the entities in the design are executed in a concurrent manner.

*Timing* specifies the initiation and completion of each operation, providing the order and the schedule of execution in case of multiple operations.

As we have seen so far, digital systems can be described at four different levels of abstraction and, consequently, the hardware description language together with the programming framework (software tools) need to cover all of them. Thus, the language semantics are demanded to encapsulate the concepts of entity, connectivity, concurrency and timing. Moreover, the structural implementation of a circuit can be expressed by language constructs, whereas the operations and structures at the gate and RT levels can be efficiently described by the language. An important characteristic for the description language is to support a hierarchical design process. For example, an entity representing the top level design may be composed of multiple other entities incorporated in the top level one.

The most frequent used HDLs are VHDL and Verilog which have similar capabilities and scopes, even if the syntax of the languages is very different. Both being supported by the same software synthesis tools, they are used in industrial standards, but further on VHDL will be discussed because it is more suitable for parameterized design.

The programming language VHDL stands for VHSIC (very high speed integrated circuit) HDL. It was developed by US Department of Defense as a hardware documentation standard in the 80's, being passed late on to IEEE (Institute of Electrical and Electronics Engineers). After being adopted as a standard, several extensions were developed over the years to meet the latest requirements of the digital design and modeling.

#### 1.3.2 VHDL Code Structure

The VHDL language is constructed from the hardware perspective of digital circuits. The fundamental building block that can be used in a VHDL program is called *design unit*. The skeleton of a basic synthesizable VHDL program consists of three collections of design units:

- library declarations,

- · entity declarations and

- architectural bodies associated with the entities.

Each VHDL program is processed according to the following three steps: analysis, elaboration and execution. Consequently, at first the VHDL code is analyzed and translated into design units that are either stored in the libraries or declared as entities. Next step is the elaboration process which designates the

top-level entities and associates the corresponding architectural bodies. The last step, execution, creates a single description of the overall design which can be executed, meaning that its functionality can be tested through simulation.

To start with, each type of design units is described, followed by examples which are given to reflect the semantic differences between HDLs and traditional programming languages and to provide the big picture of VHDL.

A *library* represents a collection of pieces of VHDL code which can be re-used or shared between different designs. The pieces of code included in a library are written in the form of components (i.e. entities, data types), functions or procedures grouped inside different packages.

For a library declarations, two identifiers are used, namely "*library*" and "*use*". Note that any VHDL reserved word (i.e. identifier) is mentioned in text using italic fonts (e.g. "*library*"). The example below shows the library definition:

```

library_library_name;

use library_name.library_package.package_part;

```

First the library name is specified followed by the package and package parts to be used in the design. Note that, in case of VHDL code sections, VHDL reserved words will be written in bold. The most common examples of library instantiation are *std* library, *work* library and *ieee* library. The first two libraries are included by default in any design and correspond to a resource library and the user defined library, respectively. The first one includes data types and the second one includes all the user defined files. The *ieee* library comprises various packages, out of which the most important are: *std\_logic\_1164* with standard logic values ('U'—uninitialized, 'X'—strong drive, unknown logic value, '0'—strong drive, logic zero, '1'—strong drive, logic one, 'Z'—high impedance, 'W'—weak drive, unknown logic value, 'L'—weak drive, logic zero, 'H'—weak drive, logic one, '-'—don't care) and *std\_logic\_arith* which contains the *signed* and *unsigned* data types and related arithmetic and comparison operations together with several data conversion functions.

An entity specifies all inputs and outputs pins of the circuit to be designed. Its corresponding syntax starts with the *entity* identifier and is presented as follows:

```

entity entity_name is

port ( port_name : signal_mode signal_type;

port_name : signal_mode signal_type;

...);

end entity_name;

```

The circuit pins are defined using the *port* identifier. The signal mode can be unidirectional or bidirectional and is defined using the identifiers *in*, *out*, *inout*, or *buffer*. The type of the signal can be for example *bit*,  $std\_logic$ ,  $std\_logc\_vector$ , etc. More data types will be discussed in detail in the next Sect. 1.3.3, data types and operators.

Finally, the *architecture* for each entity is defined, and it specifies how the designed circuit behaves. The corresponding syntax for any architecture is presented next:

```

architecture architecture_name of entity_name is

[declarations]

begin

(code)

end architecture_name;

```

In the declaration section, the internal signals are defined whereas the code section is composed of concurrent statements and processes. Each concurrent statement or process describes an individual part of the architecture; the architecture can be seen as a collection of interconnected parts of a circuit which are executed in a concurrent manner. If all the architecture statements are concurrent, we cannot say the same thing for the statements within a process. Thus a process is sequential, its statements being executed one after another. More details about processes are presented in Sect. 1.4.2.

#### 1.3.3 Data Types and Operators

We have seen so far that, the entity declaration involves the input/output port description of the design logic circuit, whereas the architecture for each entity describes the behavior of the concurrent statements and processes. Next we will focus on the objects the entities and architectures work with. In this light, three types of objects can be distinguished in case of the VHDL language: <code>signals—which</code> represent the interconnection wires to connect the ports of the design unit together, <code>variables—which</code> are used for local storage of data, visible inside processes within the behavioral description of the design units and <code>constants—which</code> define specific values.

A signal declaration is done as follows:

```

signal signal_name : signal_type [: = initial_value];

```

Signals are declared in entity declaration sections, architecture declarations or in package declarations. The signals are globally visible in all the design entities in case they are declared in the package declaration, whereas if the declaration is done within the architecture section, the signals will be visible only within the architecture they are defined in.

In order to assign a value to signal, the following syntax is used within the architecture of any entity:

```

signal_name <= initial_value;

signal_name <= other_signal_name;

signal_name <= input_port;</pre>

```

A declaration and the assignment of a variable look like this:

```

variable variable_name : variable_type[: = value];

variable_name : = value;

```

Variables can be declared only inside architecture or within a sub-program. Note that there is an important difference between variables and signals. The variables are assigned immediately, whereas signals are only scheduled for assignment at the end of the architecture or process. More details about signal assignment scheduling and variable assignment are provided in Sect. 1.3.4.

The three objects discussed so far (the signal, the variable and the constant) can be declared using a type specification. VHDL contains a wide range of types that can be used to be associated with each object. Further on, the fundamental data types of VHDL are presented together with the conversion possibilities between different data types.

Commonly used data types definitions are found in the following packages:

- standard package of std library with bit, boolean, integer, and real data types;

- *std\_logic\_1164* package of *ieee* library with *std\_logic* and *std\_ulogic* data types;

- numeric\_std package of ieee library with signed and unsigned data types.

A type of a VHDL objects is defined by the set of values which may be assigned to the object in question and by the operations that can be performed with these objects. Each of the VHDL objects can be assigned only a value of its type, meaning that VHDL is a strongly typed language.

It is important for the reader to be informed that, not all data types are synthesizable, meaning that digital logic is inferred only to some of the existing data types. A relevant example for an un-synthesizable data type is the *file* data type. An object of type *file* represents a file containing sequential streams of a particular type. A file object can be read from and written to with special procedures and functions. The content of the file may be delivered to the designed logic block using test-benches. The VHDL code for test-benches is not synthesizable and is used only for delivering input and output data to the designed logic blocks. Writing test-benches with VHDL code is discussed in 1.6. Further on we will focus on synthesizable VHDL data types.

Predefined data types of std library

The predefined synthesizable VHDL data types included in the *std* library are:

- integer from— $(2^{31}-1)$  to  $(2^{31}-1)$  with the subtypes natural and positive;

- boolean defined as false and true:

- bit: defined as 0 and 1;

- bit-vector: defined as one-dimentional array of the bit data type.

The operators associated with the previously mentioned data types are listed in Appendix A.

Standard logic data types

In real life a signal may have also different values than 0 or 1. Consequently, in the  $std\_logic\_1164$  package introduces the  $std\_logic$  data type which consists of the following values: 'U', 'X', 'O', 'I', 'Z', 'W', 'L', 'H', '-'. '0' and '1' stand for 0 and 1 logic values. 'U' stands for uninitialized logic value, 'X' and 'W' stand for unknown values, 'Z' stands for high impedance, 'L' and 'H' mean weak 0 logic and weak 1 logic respectively, '-' stands for don't care logic value.

An array of elements with the data type std\_logic is called *std\_logic\_vector*. The dimension of the array is specified in brackets using *to* or *downto* reserved words. Examples of signal declarations having the data type *std\_logic* and *std\_logic\_vectors* are presented next:

```

signal a : std_logic : = '0';

signal b : std_logic_vector (7 downto 0) :="00000000";

```

Considering the VHDL is a strongly typed language, the definition of an object having a specific data types includes also the operators that can be used with the data type in question. Thus, it is important to know the operators that can be used with each data type. For the  $std\_logic$  data types, we can apply any logic operator (e.g. not, and, or, xor, nand, nor, xnor). Regarding arithmetic operators, it is important to know that they cannot be applied. The conversion to an arithmetic data type is needed (e.g. signed or unsigned, discussed in numeric standard package).

If we consider the *std\_logic\_vector* data type, we have to mention the specific operators for the array data types, namely relational operators, concatenation operators. Examples of relational operators are equal ('='), not equal ('<>'), greater ('<'), smaller ('>'), whereas the concatenation operator is '&', which is used to combine parts or elements of different arrays to form a larger array.

Numeric standard data types

Digital hardware involves arithmetic operations, thus it comes natural to use the integer data types for two *a* and *b* signals considered as the addition terms. Nevertheless, the range of integer not being specified, it is difficult to implement this in hardware. Consequently, *signed* and *unsigned* data types are included n the IEEE *numeric\_std* package. These types represent an array of elements having the *std\_logic* type. Declaration of such data type is similar with the std\_logic\_vector, as denoted by the line of code:

```

signal a,b: signed(15 downto 0);

```

The difference between signed and unsigned is that for the signed type, the bits are interpreted as a signed binary number in 2's complement format. These two types support arithmetic operations, whereas the operators to be used are *abs*

(absolute value), \*, /, +, -, mod and rem. Moreover, the relational operators such as = , < , > and similar ones can be used with the signed and unsigned data types. Type conversion

Having the synthesizable data types detailed in the previous sections, the next step is to discuss the conversions between different data types. Type conversion is mandatory in VHDL considering that direct operation between data of different types cannot be performed. Type conversions are performed either using a *type conversion function* or *type casting*. A simple example is given next, in order to have a better view on type conversion. Let's assume we need to access a memory location for which the address is computed by an address computation unit *addr\_comp\_unit*. In other words, the memory address is given by an arithmetic operation, a multiplication for example. In case the memory address port is of *std\_logic\_vector* type, the *addr\_comp\_unit* needs to deliver an output of type *std\_logic\_vector* for the memory port. The next code example, example 1.1, makes use of type casting in order to convert the multiplication result (i.e. *unsigned* data) into *std\_logic\_vector* data type.

Example 1.1—Type casting unsigned to standard logic vector

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity addr_comp_unit is

port (

a : in unsigned (7 downto 0);

b : in unsigned (7 downto 0);

addr : out std_logic_vector (15 downto 0));

end addr_comp_unit;

architecture behavioral of addr_comp_unit is

signal mult: unsigned(15 downto 0);

begin

mult <=a*b;

addr <= std_logic_vector(mult);

end behavioral;</pre>

```

Note that for the previous example the *numeric\_std* package was used. Considering *numeric\_std* package, the type conversions of numeric data types are performed using the conversion functions or type casting operators summarized in Table 1.1.

| From data type             | To data type     | Conversion function/type casting |

|----------------------------|------------------|----------------------------------|

| unsigned, signed           | std_logic_vector | std_logic_vector()               |

| signed, std_logic_vector   | unsigned         | unsigned()                       |

| unsigned, std_logic_vector | signed           | signed()                         |

| Unsigned, signed           | integer          | to_integer()                     |

| natural                    | unsigned         | to_unsigned()                    |

| integer                    | Signed           | to_signed()                      |

Table 1.1 Conversion functions for VHDL data types

#### 1.4 Combinational Logic, Sequential Logic and VHDL

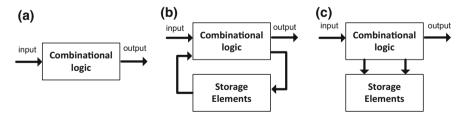

Combinational logic refers to circuits whose output is a function of the present value of the inputs only. Whenever the inputs are changed, the information about the previous inputs is lost, meaning that a combinational logic circuit has no memory. It can, therefore, easy be implemented using conventional logic gates.

Sequential logic circuits are those whose outputs are also dependent upon current and previous inputs. This means that they have memory, so storage elements are required, which are connected to a combinational logic block through a feedback loop. In this way, the stored states, created by previous inputs, will affect the output of the circuit. Note that not any circuit that has storage elements is a sequential circuit. For example, memories obviously store data, but their output depends only on the address bits applied as input data. A better view on the two types of logic circuits can be depicted in Fig. 1.2.

Corresponding to the two types of digital logic, combinational or sequential, the VHDL code is classified either as *concurrent* or *sequential* [2]. In what follows both concurrent and sequential VHDL code are detailed and code examples are also provided.

Fig. 1.2 a Combinational logic representation, b sequential logic representation, c memory representation

#### 1.4.1 Concurrent VHDL Code

In general, all VHDL code is concurrent, meaning each line of code placed inside the behavioral description of logic blocks is executed in parallel. The only exceptions are statements placed inside a PROCESS, FUNCTION, or PROCEDURE which rerpesent the sequential VHDL code and which are detailed in the *Sequential VHDL code* section. Within curret section, the concurrent VHDL code know also as *dataflow* code is discussed.

The VHDL statements used to create combinational circuits (i.e. concurrent VHDL code) are: (i) the assignments using different type of operators (logical, arithmetic, etc.), (ii) the WHEN statement and (iii) the GENERATE statement. Example for each type of cocnurrent VHDL code are given next.

(i) Within current paragraf the description of a *Gray code converter* is presented as an example of combinational logic circuit. In 1947, Frank Gray from Bell Laboratories, introduced the term reflected binary code in a patented application, based on the fact that it may be built up from the conventional binary code by a sort of reflexion process. The main feature of this code is that a transition from one state to a consecutive one, involves only one bit change. The conversion procedure from binary natural to Gray is the following: the most significant bit, MSB, from the binary code is the same with the MSB from the Gray code. Starting from the MSB towards the least significant bit, LSB, any bit change (0 to 1 or 1 to 0) in binary natural, generates an '1' and any lack of change generates a '0', in Gray code. The conversion from Gray to binary natural is the reverse: the MSB is the same in binary natural code as well as in Gray code; further on, from MSB to LSB, the next bit in binary natural code will be the complement of the previous bit, if the corresponding bit from Gray code is 1 or, it will be identical with the previous bit, if the corresponding bit from Gray code is 0.

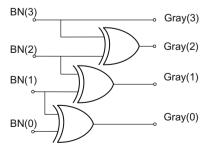

In order to build a combinational logic circuit which transforms any 4 bits input vector  $[b_3b_2b_1b_0]$  from binary natural representation into Gray code representation  $[g_3g_2g_2g_0]$ , the truth table for the binary to Gray conversion is build. Based on function minimisation, each binary output  $g_i$  is expressed as  $g_i = f(b_3, b_2, b_1, b_0)$ , where f is a logic function of the 4  $b_i$  inputs. Consequently the equations for a binary to Gray conversion in case of a 4 bits logic vector are as follows:

$$g_3 = b_3$$

$g_2 = b_2 \oplus b_3$

$g_1 = b_1 \oplus b_2$

$g_0 = b_0 \oplus b_1$

$$(1.1)$$

The VHDL code for the combinational logic cirrcuit (CLC), which describes the binary to Gray conversion according to previous equations set, is presented. Firstly, the *CLC* entity describes the input and output ports of the binary to Gray converter.

Thus, the BN is a 4 bits input vector, whereas the Gray output returns the Gray code representation of the BN input. Once the entity is described, we may proceed to the behavioral description of the circuit. In our case, the architecture of our entity includes concurrent VHDL code which includes 4 assignments, each coressponding to one of the output bits. Moreover, the xor operator is also used to describe the set of conversion Eq. (1.1).

Example 1.2—Concurrent VHDL code for binary to Gray converter

```

entity CLC is

Port ( BN : in STD_LOGIC_vector (3 downto 0);

Gray : out STD_LOGIC_vector (3 downto 0));

end lab1;

architecture Behavioral of CLC is

begin

Gray(3) <= BN(3);

Gray(2) <= BN(3) xor BN(2);

Gray(1) <= BN (2) xor BN(1);

Gray(0) <= BN (1) xor BN(0);

end Behavioral;</pre>

```

The previous concurrent VHDL code corresponds to the combinational logic circuit descibed in Fig. 1.3.

(ii) Another concurrent VHDL code is the *when* statement. Commonly, these statements are used when multiplexers (i.e. combinational logic) need to be described with VHDL. Moreover, the tri-state buffers are also combinational logic circuits that can be described using *when* statements. Examples of both multiplexer and tri-state buffer are given next. Before proceeding to the examples description, it is to be mentioned the two forms of the *when* statemet. There is the simple *when /else* statement and the *with /select /when* statement also known as *selected when*. The syntax for the two when statement is provided next:

**Fig. 1.3** Combinational logic for binary to Gray conversion

• for the simple when /else statement

```

assignment when condition else assignment when condition else ...;

```

• for the selected when statement (with /select /when)

```

with identifier select

assignment when value,

assignment when value,

...;

```

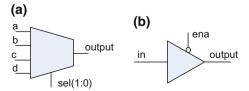

The simple when /else statement is used for the description of the tri-state buffer presented in Fig. 1.4a, whereas the multiplexer from Fig. 1.4b is described using a selected when statement.

Example 1.3—VHDL code for multiplexer

```

library ieee;

use ieee.std_logic_1164.all;

entity multiplexer is

port (a, b, c, d: in std_logic;

sel: in integer range 0 to 3;

output: out std_logic);

end mux;

architecture mux of multiplexer is

begin

with sel select

output <= a when 0,

b when 1,

c when 2,

d when 3;

end mux;</pre>

```

**Fig. 1.4** a Multiplexer, **b** tri-state buffer

The behaviour of the logic crcuit described by the previous VHDL code is as follows. The *output* is one of the 4 inputs a, b, c or d, depending on the *sel* input. If the *sel* input is 0, the output is a; if the *sel* input is 1 the *output* is b and so on. Note that in case of the *with /select /when* statement all the possibilities for the *sel* input must be tested. This is why the keyword *others* is often used as one of the *sel* identifier values (e.g. **with** sel **select** output <= 0 **when** *others*).

**Example 1.4**—VHDL code for multiplexer

```

library ieee;

use ieee.std_logic_1164.all;

entity tri_state is

port ( ena: in std_logic;

input: in std_logic;

output: out std_logic);

end tri_state;

architecture tri_state of tri_state is

begin

output <= input when (ena = '0') else 'z';

end tri_state;</pre>

```

This examples illustrates another way of using the *when* statement. The tri-states logic circuit provides the *input* at the circuit *output* if the *ena* is '0' and high impedance 'Z' otherwise.

(iii) the *generate* statement is another concurrent statement used for repeating a section of code for a number of times. In this way multiple instances of the same assignment are created. In other words, generate statement may be used to replicate logic. The syntax for this type of concurrent code is specified below, whereas further on, an example (1.4) on how to use generate statement to replicate logic is provided.

```

label: for identifier in range generate

(concurrent assignments)

end generate;

```

**Example 1.5**—Generate statement to replicate logic

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity converter is

Port (input : in STD_LOGIC_VECTOR (7 downto 0);

output : out STD_LOGIC_VECTOR (7 downto 0));

```

```

end converter;

architecture Behavioral of converter is

begin

U1: for i in 0 to 7 generate

begin

output(i) <=input(7-i);

end generate;

end Behavioral;</pre>

```

The previous VHDL code example describes a combinational logic circuit which takes as input a logic vector *input* and returns another logic vector, the *output*, with the same bit values as the input but in reverse order. The code line output(i) <= input (7-i) assigns to the output bit output(i) the logic value from input(7-i). The generate statement multiplicates the previous assignments for all i values from 0 to 7, the result beeing the output logic vector with the bit values from the input in reverse order.

#### 1.4.2 Sequential VHDL Code

As mentioned before, VHDL code is concurrent, all the statements placed in logic blocks architectures being executed in parallel. Nevertheless, it is also important to have statements executed one after another; this is the case of sequential circuits. A common example is a shift register which sequentially changes its content each clock cycle by means of bits shift. Also, arithmetic operations need to be executed one after another since one operation may depend on the results of a previous one (see the logarithm computation unit from Chap. 3). In order to describe sequential logic with VHDL, the statements have to be included within a *process*, *function* or a *procedure* section. The statements placed in one of these three types of code sections are sequential. Notice that not any kind of statement can be included in processes, function or procedures; the statement are restricted to *if*, *wait*, *case*, *loop* together with *variables* and *signals assignments*. Further on, a process is defined in the context of VHDL coding and also, all sequential statements (signal and variable assignments, if, wait, case and loop statements) which can be placed within a process, are defined.

The *process* statement or simply a process is composed of 3 parts: sensitivity list, process declarative part and the statements part. The process begins with the *process* keyword, followed by a parenthesized list of signals called the sensitivity list. The process is activated on any change of the signals in the sensitivity list. After the process sensitivity list, the declarative part comes followed by the sequential statements part. The syntax for a process declaration is presented next.

```

[label:] process (sensitivity list)

variable declarations;

begin

(sequential code)

end process [label];

```

#### Remark

Answering the question "How the processes are executed?" is the key for understanding the VHDL code. We have so far how sequential logic is described using processes. How these processes are executed is explained next. A process execution is triggered by any change in the signals from the sensitivity list. Once a change occurs in the sensitivity list, the process starts. Variable and signals are assigned during the process execution in case some given conditions are met (e.g. if reset = '1' then a signal or variable is initialized with a given value). Commonly, these variables and signals are passed to the output of the entity from which the process belongs. Notice that there is an important difference concerning variables and signals assignments within a given process. Thus, in case of signal assignments, the assigned values are only scheduled for instantiation; the scheduled values are instantiated only at the end of the process. On the other hand, in case of variable assignment, the assigned values are immediately instantiated to the variable in question, their new values being available in the next line of code.

Signal and variable assignments

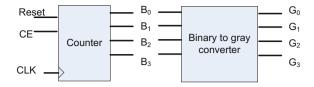

Signal and variable assignments are used to pass non-static values between logic components described with VHDL code. Signals can be declared in a package, entity or architecture, whereas variables can be declared only inside a sequential code section (process, function or procedure). Considering the signals assignment, it can be done either inside or outside of a process. In the first case, combinational logic circuits are described, meaning the assigned value is instantly visible. In case signals are assigned in a process, the assigned value is available only after the conclusion of the process run. Notice that for signal assignment the operator is "<=". Variables assignment on the other hand, can only be performed within sequential code section. The update of a variable is immediate, thus the new value is available promptly after the assignment. Another important aspect regarding variables is that they represent local information, and they are only visible inside the process they are assigned in. In order to pass values outside the process, the signals are used which are globally declared within the architecture declaration section. For variable assignment the operator is ":=". Further on two examples are provided in order to underline both the signal and the variable assignment. Both examples are used to describe a counter used to deliver input data to the combinational logic circuit aiming for a binary to Gray conversion (Fig. 1.3). The counter and the combinational logic block for the binary to Gray conversion are both illustrated in Fig. 1.5.

**Fig. 1.5** Conversion of 4 bits binary numbers to Gray code representation

**Example 1.6**—Counter description with variable assignment

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity cnt is

port (clk: in std_logic;

CE : in std_logic;

reset : in std_logic;

Counter: out std_logic_vector(3 downto 0));

end cnt:

architecture Behavioral of cnt is

begin

process (clk, reset, CE)

variable temp_a: std_logic_vector (3 downto 0): = "0000";

if reset = '1' then

temp a: = "0000";

elsif clk = '1' and clk'event then

if CE = '1' then

temp a := temp a + 1;

end if:

end if;

counter <= temp_a;</pre>

end process;

end behavioral;

```

The logic circuit name *counter* described by the previous VHDL code is used to consecutive binary numbers to the binary to Gray converter. The inputs are CE (count enable), reset and clk, which are found also in the sensitivity list of the process used to increment or to reset the counter output. The '1' logic value on the reset port sets the counter output to "0000", whereas the '1' logic value on CE port enables the counting, meaning each clk cycle the output value is incremented by 1. The variable  $temp\_a$  is used for incrementing, and its value is passed outside the process to the counter output counter by the following assignment  $counter <= temp\_a$ . Similar

behavior can be achieved using the following VHDL code, where the counter description uses signal assignment instead of variable assignment.

Example 1.7—Counter description with signal assignment

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity cnt is

port (clk: in std_logic;

CE: in std logic;

reset : in std_logic;

Counter: out std logic vector(3 downto 0));

end cnt.:

architecture Behavioral of cnt is

signal temp b: std logic vector(3 downto 0);

begin

process (clk, reset, CE)

begin

if reset = '1' then

temp_b <= "0000";

elsif clk = '1' and clk'event then

if CE = '1' then

temp_b <= temp_b + 1;

end if:

end if;

end process;

counter <= temp_b;

end behavioral;

```

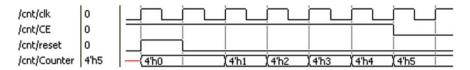

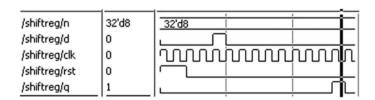

In case of the second counter description, the  $temp\_b$  signal was used to increment the counter output (counter). Notice that the  $temp\_b$  signal was declared in the architecture section as opposed to the variable  $temp\_a$  from the first counter example  $(temp\_a$  declared in the process declaration section). Consequently the signal  $temp\_b$  was visible outside the process statement. Thus, the concurrent assignment  $counter <= temp\_b$ , assures that the counter output is the signal  $temp\_b$  incremented each clk cycle within the sequential process. The process is triggered by any change in the signals from the sensitivity list. Thus, a teset value '1' sets the output to "0000", whereas a CE value '1' enables the counting each test cycle, as it can be seen on the simulation results from Fig. 1.6.

Fig. 1.6 Counter simulation results

#### If statement

The *if* statement is used for sequential logic description, and, therefore it can be used only inside a process. The syntax of *if* is presented next:

```

if conditions then assignments;

elsif conditions then assignments;

...

else assignments;

end if;

```

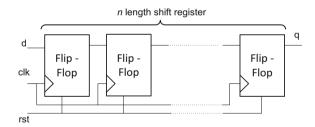

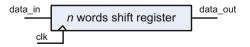

The VHDL code for a shift register implementation is provided next for the exemplification of the *if* statement. Moreover, the *generic* statement is used within the shift register in order to define the shift register length. The generic is generally used for the parameterization of the VHDL code. Thus, let us consider we want to build a register which may be used in different logic blocks, and its length may vary depending on the logic block the register is used in. In this case, using generic, the length of the register is once defined as n in the entity section (generic (n: integer := 8);). This n value is considered for all the VHDL code description which follows further on. In this way, the VHDL code is easily reusable if we want to describe a shift register of any length, given by n. A single change of n in the entity section is visible in all the VHDL code. This leads to a parameterized VHDL code for any shift register of length n (see the next VHDL code section for exemplification of *generic*).

We describe further on a shift register of variable length n. The inputs are d, clk, rst and the output is q. The behavior of the circuit is described using the if statement; the circuit reset is performed if '1' is applied on the rst input. Moreover, on rising clock edge (code line: elsif (clk'event and clk = '1')), the input d is feed to the n'th register cell, whereas the register content is shifted to the right (code line: (temp <= d & temp (n downto 1);). The circuit output q is assigned with the first register cell (temp(0)) outside of the register's corresponding process.

**Example 1.8**—VHDL code for *n* variable length shift register

```

entity shiftreg is

generic (n: integer : = 8);

port (d, clk, rst: in std_logic;

q: out std_logic);

end shiftreg;

```

```

architecture behavior of shiftreg is

signal temp: std_logic_vector (n downto 0);

begin

process (clk, rst)

begin

if (rst = '1') then

temp <= (others => '0');

elsif (clk'event and clk = '1') then

temp <= d & temp (n downto 1);

end if;

end process;

q <= temp(0);

end behavior;

— end of shift register example</pre>

```

The shift register and its behavior are described in the Figs. 1.7 and 1.8, respectively. As expected, in Fig. 1.8 it can be seen that, the 'I' logic input of the circuit is available at the output with an n = 8 clock cycles delay.

#### Wait statement

The wait statement is also part of the sequential VHDL code. Placed inside processes, the wait statement comes with a specific request concerning the process that is used in. The process cannot have a sensitivity list. The syntax for the wait statement has three forms, mentioned further on:

Fig. 1.7 Counter simulation results

Fig. 1.8 Shift register simulation results

```

wait until signal_condition;

wait on signal1 [, signal2, ...];

wait for time;

```

The first wait statement syntax accepts only one signal condition, and it s mandatory to place the statement at the beginning of the process, since as mentioned before, the process has no sensitivity list. This process is executed when the wait condition is met.

The second wait statement involves multiple signals, any change on the *signal1*, *signal2*, etc. signals list causes the process execution.

The last wait statement, *wait for time*, is used only for simulation purposes. Thus it is not synthesizable; its use is detailed in the sub-Sect. 1.5 *Writing test-benches*.

#### 1.5 Structural Description with VHDL

Digital systems are commonly described by multiple sub-components and their interconnection links. Like in any other programming languages where a program is composed of multiple sub-programs, a VHDL description of the architecture of a given entity may be hierarchically described by different components (entities) which interact with each other through interconnection links. This type of description is known as a *structural description*. Further on we will discuss how the declaration and the instantiation of a given component is done within the architecture body of an entity that uses structural description.

We've seen so far that, an entity specifies the input output ports of a digital circuit, whereas the circuit behavior is described in the architecture body. In the example what follows, structural VHDL code is used to describe the behavior of the entity named *structural\_description*. Two components, *comp1* and *comp2* are declared within the declarative section of the entity's architecture. The syntax for component instantiation is:

```

component comp is port ( port name : signal mode signal_type;

...);

```

Within the architecture body section, the components *comp1* and *comp2* are instantiated. Through instantiation, the input and output signals of the entity *structural\_description* are assigned to the components ports. Internal interconnection links between components are drawn using the declared signals such as *w1* signal declared as: "signal w1: std\_logic;". The syntax for component instantiation is given next:

```

inst1: comp port map (signals list);

```

As it can be noticed, a labeled is used for component instantiation (*inst1*) followed bt the component name (*comp*), *port map* identifier and the *signals list* in between brackets. The signals found in the *signal list*, associate signals to all of the component's input and output ports.

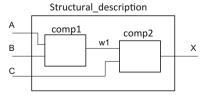

For the exemplification of components declaration and instantiation, let us consider the logic circuit from Fig. 1.9. Here, the logic circuit named *structural\_description*, having 3 inputs ports A, B, C and an output X, is illustrated. The circuit behavior is described by two components *comp1* and *comp2*, and their interconnection using the wire *w1*. In order to describe this circuit using VHDL code, a structural description is used (see the next VHDL code section *VHDL code for structural description*). An entity entitled *structural\_description* is used to define the input and output ports of our circuit (A, B, C, D and X). Two components *comp1* and *comp2* are declared in the architecture section together with a signal *w1* used for interconnection link between the two components. After the declaration section the architecture description begins. Here, the two components are instantiated. The instantiation assigns the input and outputs for each of the components, using the ports of the *structural\_description* entity and the interconnection wires defined as signals (e.g. *w1* signal).

Example 1.9— VHDL code for structural description

```

entity structural_description is

Port (A, B, C: in STD_LOGIC;

X: out STD_LOGIC);

end structural descripton;

architecture Behavioral of structural_description is

component comp1 is port (C1, C2: in std_logic;

Out1: out std_logic);

end component comp1;

component comp2 is port(C3, C4 : in std_logic;

Out2: out std_logic);

end component comp2;

signal w1: std_logic;

begin

inst1: comp1 port map (A, B, w1);

inst2: comp2 port map (w1, C, X);

end Behavioral:

```

**Fig. 1.9** Example of a structural description

The previous example can be used as the starting point to describe more complex digital circuits using structural description. Consequently, a digital logic circuit is described next using VHDL structural description, in order to accomplish an image processing task, image profile computation. In the next section the computation of image profiles is described, followed by the description of the digital logic which performs the computation.

A digital image is commonly represented as a two dimensional array of intensities (pixels) denoted by  $I = (p_{x,y})$ , where  $p_{xy}$  is the pixel intensity values for the pixel found at the (x,y) location. In case of a color image denoted by  $I_c$ , a given pixels (x,y) is described by a set of 3 intensity values  $(r_{x,y}, g_{x,y}, b_{x,y})$ , corresponding to the colorimetric information red (R), green (G) and blue (B), respectively. The luminance information in case of a color image  $I_c$  is obtained as a weighted sum of the R, G and B intensities for all (x,y) image pixels as in Eq. (1.2).

$$lum_{x,y} = 0.299 \cdot r_{x,y} + 0.587 \cdot g_{x,y} + 0.114 \cdot b_{x,y}$$

(1.2)

Summing up pixel intensities representing luminance information along x and y image direction lead to the vertical and horizontal luminance function profiles of an image, as expressed by Eqs. (1.3) and (1.4), respectively.

$$V(y) = \sum_{x} lum_{x,y} \tag{1.3}$$

$$H(x) = \sum_{y} lum_{x,y} \tag{1.4}$$

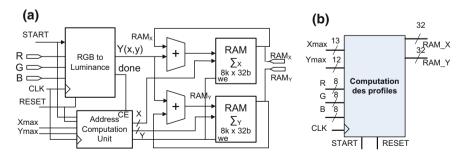

The overall view of the corresponding digital logic for image profile computation is illustrated in Fig. 1.10. The logic blocks used are the *RGB to Luminance*, the *Address Computation Unit*, and the *Accumulators* for each of the profiles, vertical and horizontal one.

The image colorimetric information is delivered pixel-wise as input to the RGB to Luminance logic block, which delivers the luminance information for each (x,y) image pixel. The clk and the start inputs are also present for the RGB to Luminance

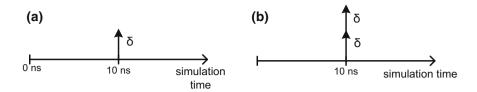

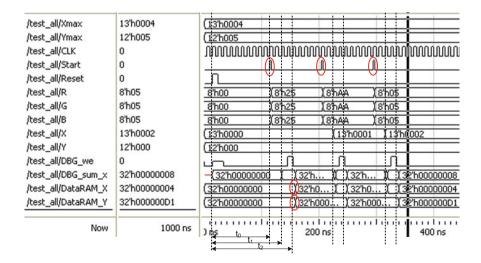

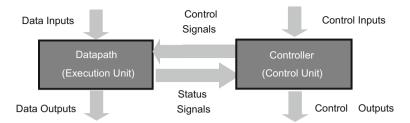

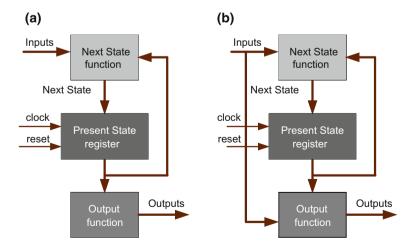

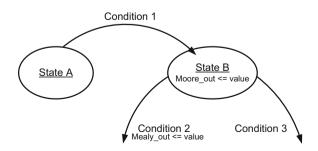

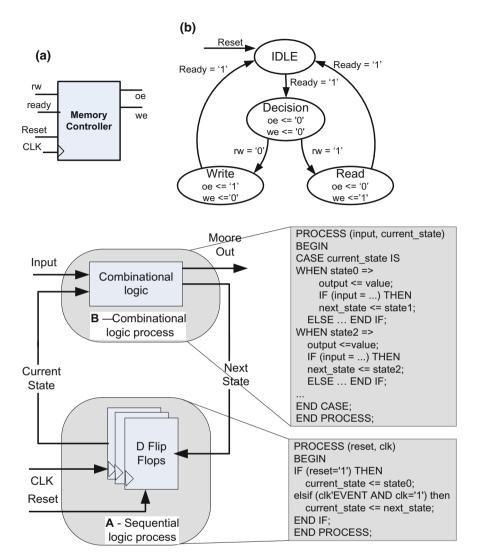

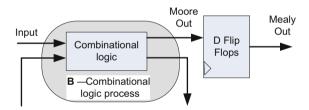

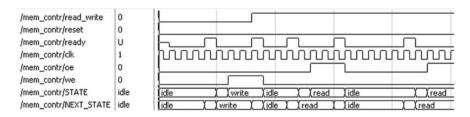

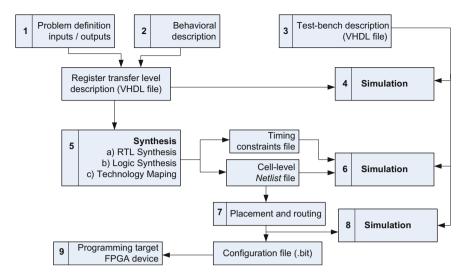

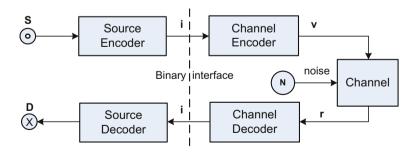

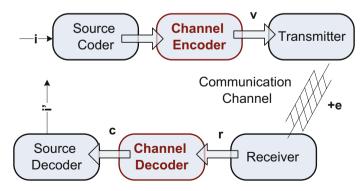

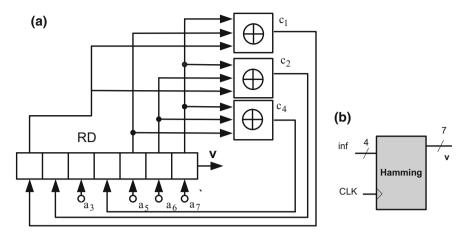

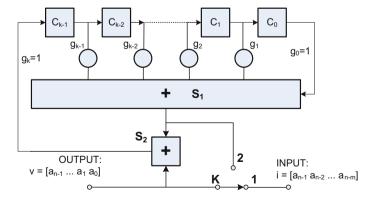

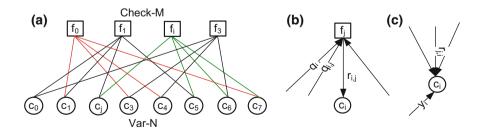

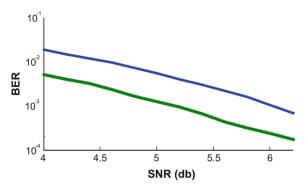

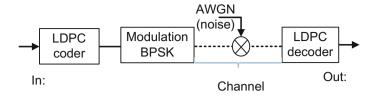

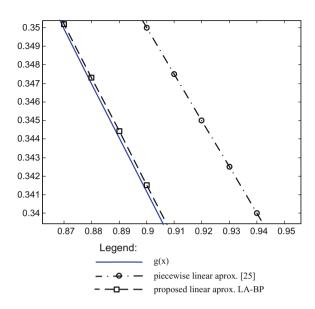

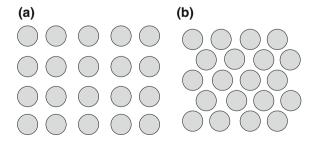

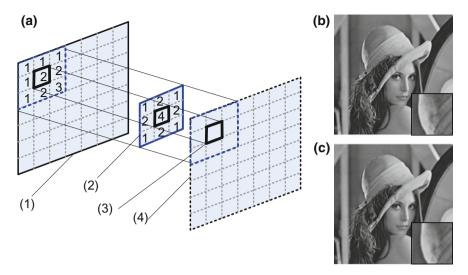

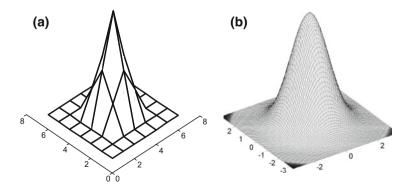

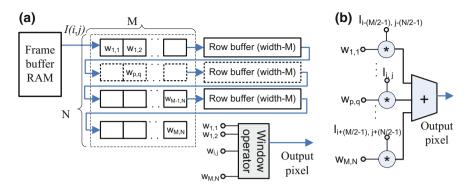

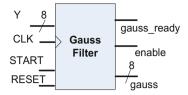

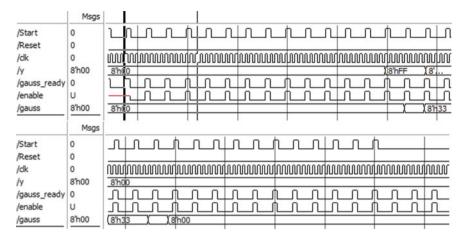

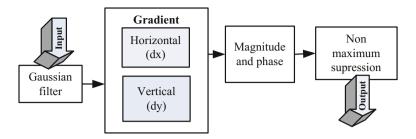

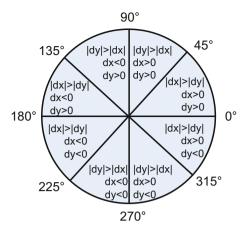

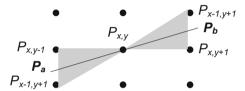

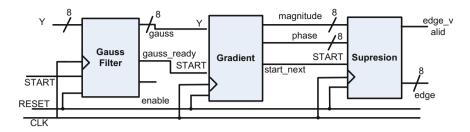

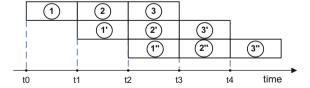

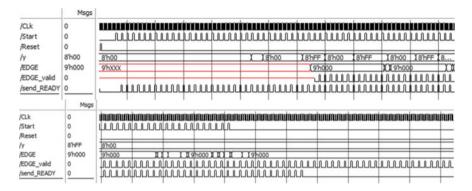

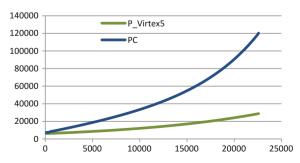

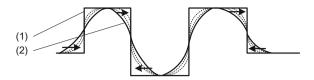

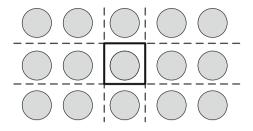

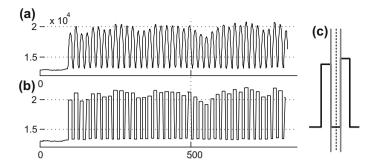

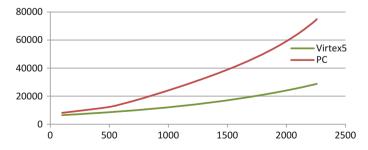

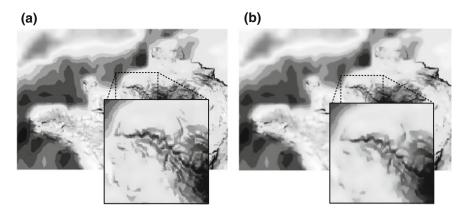

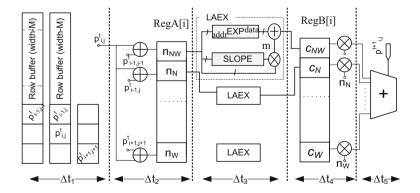

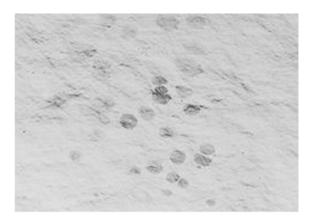

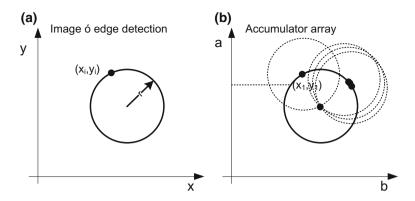

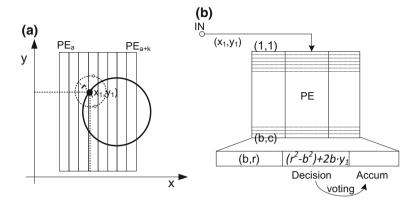

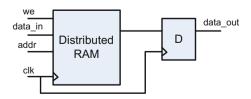

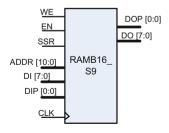

Fig. 1.10 Block diagram for image profile computation