Patrick P. Mercier Anantha P. Chandrakasan *Editors*

# Ultra-Low-Power Short-Range Radios

# **Integrated Circuits and Systems**

### **Series Editor**

Anantha P. Chandrakasan Massachusetts Institute of Technology Cambridge, Massachusetts

Patrick P. Mercier • Anantha P. Chandrakasan Editors

# Ultra-Low-Power Short-Range Radios

Editors

Patrick P. Mercier

University of California

San Diego

La Jolla, CA, USA

Anantha P. Chandrakasan Massachusetts Institute of Technology Cambridge, MA, USA

ISSN 1558-9412 Integrated Circuits and Systems ISBN 978-3-319-14713-0 ISBN 978-3-319-14714-7 (eBook) DOI 10.1007/978-3-319-14714-7

Library of Congress Control Number: 2015942638

Springer Cham Heidelberg New York Dordrecht London © Springer International Publishing Switzerland 2015

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

Springer International Publishing AG Switzerland is part of Springer Science+Business Media (www. springer.com)

### **Preface**

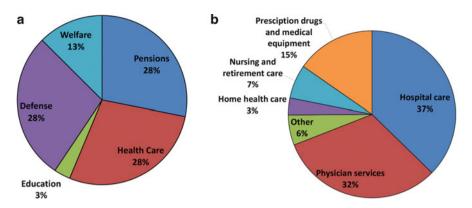

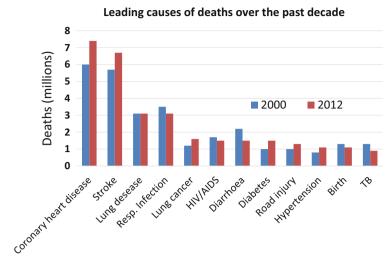

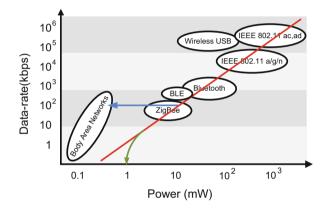

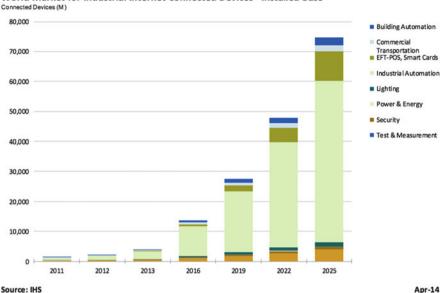

Wireless communication is becoming increasingly ubiquitous today, with many consumer, industrial, medical, and military devices leveraging newly found untethered freedoms to enable exciting new applications and opportunities. To date, the cellular and computer industries have been the primary driver of advances in wireless functionality, exemplified by the popularity and continuing advances in 4G carrier aggregation and next-generation WiFi products. While these (and other) standards support the high throughput and range necessary for cellular and computing applications, there are emerging classes of applications including sensor networks, Internet of Things (IoT), and body-area networks that have very different requirements. Specifically, devices used in these applications are not necessarily looking for the fastest throughput, but instead focus on achieving sufficient throughput under ultra-low-power budgets. To reduce power, these devices typically operate over shorter ranges, pushing the power requirements of long-haul communications to more energy-rich gateways. It is expected that these ultra-lowpower, short-range radios will begin to comprise a large fraction of total volume of radios as these emerging application spaces mature.

To support these application spaces, there are currently a number of standards specifically responsive to the needs of low-power short-range communications. Examples include Bluetooth, Bluetooth Low Energy, and IEEE 802.15.6 (Wireless Body Area Networks), with a few other standards that support low-power though not necessarily short-range (e.g., Zigbee and 802.11ah). However, in many cases strictly adhering to standards can limit design creativity, potentially resulting in solutions with higher-than-desired power. Thus, the majority of this book does not focus on developing radios for specific standards, but instead focuses on circuit and system techniques that achieve ultra-low-power while not sacrificing too much on other important metrics. Many of the discussed techniques can then be applied to standards-based radios, though some techniques are naturally better suited for custom, proprietary solutions.

vi Preface

In either case, the purpose of this book is not to act as a textbook or a design manual for specific radios, but should instead be used by engineers who have a background in RF to better understand the challenges, requirements, circuits, and system-level techniques that can be used to design ultra-low-power short-range radios.

### **Organization of the Book**

This book is organized into 12 chapters. To set the tone, the first chapter begins with an overview of general trends in low-power radio design, including a benchmarking section that covers state-of-the-art performance in this space. Then, chapter "Channel Modeling for Wireless Body Area Networks" discusses channel modeling, with a specific emphasis on the body channel, in order to help the reader better understand the requirements placed on ultra-low-power short range radios. Following these discussions, the book dives into the details of specific use-cases and implementations of ultra-low-power short-range radios, starting with narrowband radios, then moving to alternative forms of wireless communication, and concluding with very short-range communications and energy management.

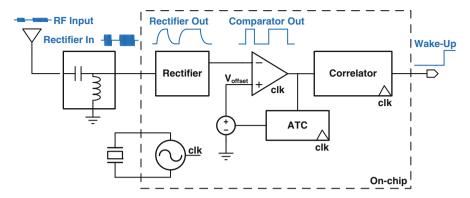

On the topic of narrowband radios, chapter "Circuit Techniques for Ultra-Low Power Radios" discusses design techniques that, through crystal-based injection-locking approaches, enable the achievement of ultra-low-power operation without the use of phase-locked loops (PLLs). As an alternative approach, chapter "Architectures for Ultra-Low-Power Multi-Channel Resonator-Based Wireless Transceivers" introduces a similar concept, but in this case using higher frequency high-Q resonators as PLL and front-end filter replacements. Chapter "Ultra-Low Power Wake-Up Radios" then considers low-power wake-up radios for applications that have asynchronous, event-driven communication needs. Chapter "Commercially Viable Ultra-Low Power Wireless" reviews trends and techniques that are appropriate for commercial, standards-driven radios, and chapter "Synchronization Clocks for Ultra-Low Power Wireless Networks" discusses ultra-low-power timing circuits necessary for synchronization amongst radios in both standards-based and custom radio networks.

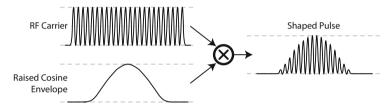

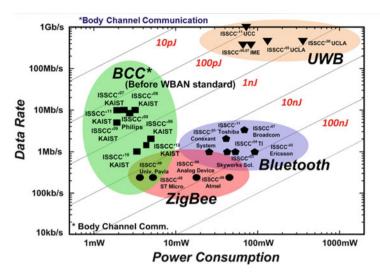

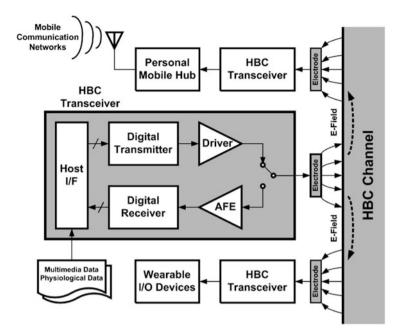

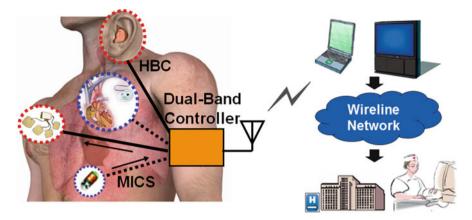

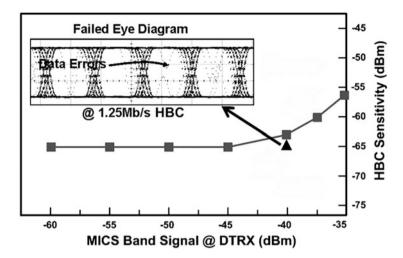

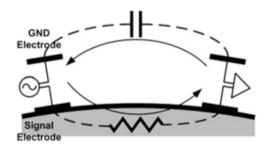

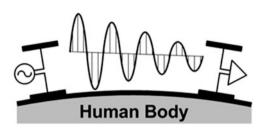

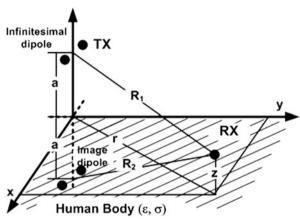

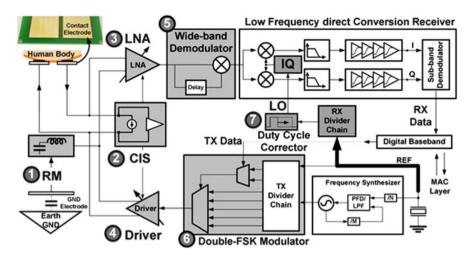

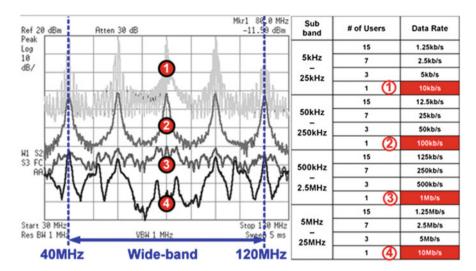

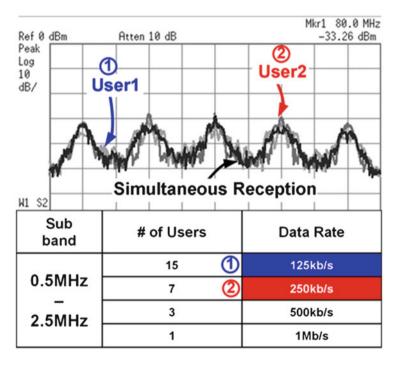

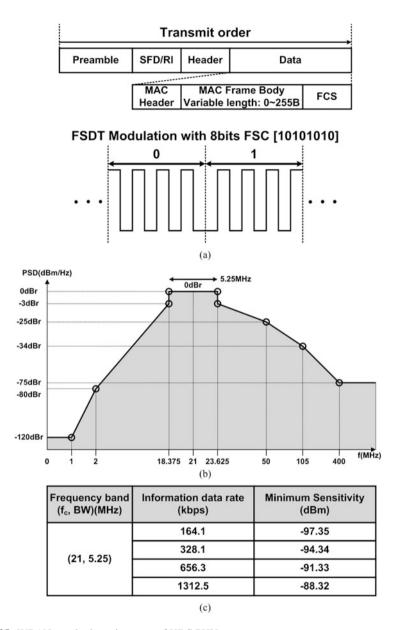

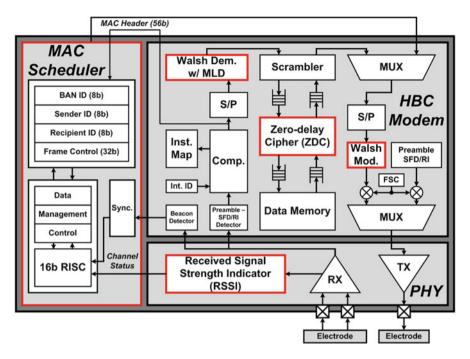

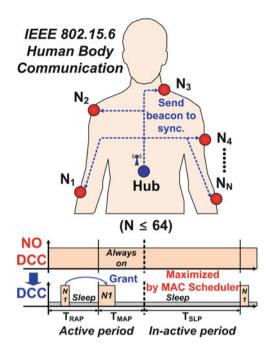

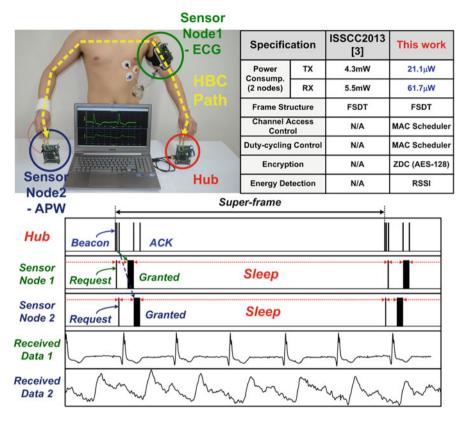

In applications that require ultra-high throughput or secure, non-radiating communication, techniques other than narrowband communication may offer superior performance. To this end, chapter "Pulsed Ultra-Wideband Transceivers" discussed ultra-wideband (UWB) circuits and systems for use in ultra-low-power short-range applications. For on-body communication applications, chapter "Human Body Communication Transceiver for Energy Efficient BAN" reviews the history and recent trends regarding human-body communications (HBC) and its application to wearable, biomedical monitoring devices.

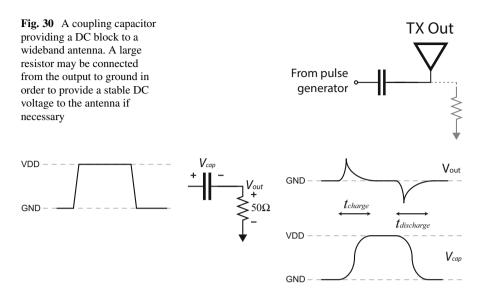

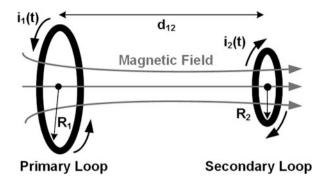

Chapters "Centimeter-Range Inductive Radios" and "Near-Field Wireless Power Transfer" then introduce near-field communication (NFC) and power delivery concepts for applications where communication over a few centimeters is desired.

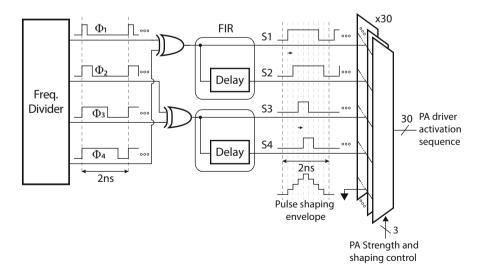

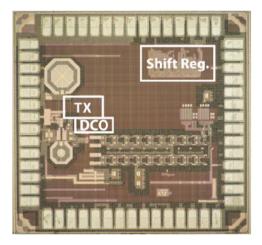

Preface vii

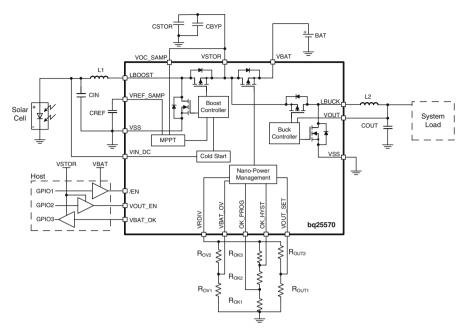

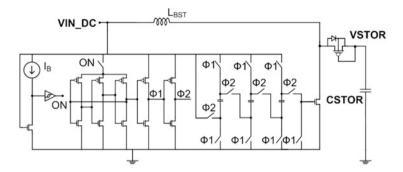

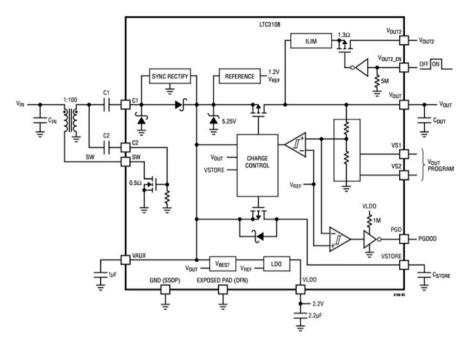

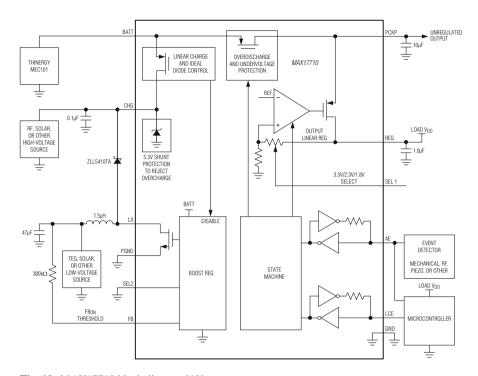

Specifically, chapter "Centimeter-Range Inductive Radios" focuses on increasing the throughput of NFC links, while chapter "Near-Field Wireless Power Transfer" reviews resonant coupling theory and derives formulae describing optimal conditions for efficient or maximal delivery of wireless power. Finally, chapter "Energy Harvesting Opportunities for Low-Power Radios" concludes the book with a discussion on energy harvesting and energy management circuits and devices that are appropriate to extend operational lifetime of many ultra-low-power short-range wireless devices.

### Acknowledgements

Putting together a book of this size and scope would not have been possible without the help of many people. We would first and foremost like to thank all of the contributing authors for their insightful content that comprises the majority of the book—your efforts are greatly appreciated. We would also like to thank the editing and support staff at Springer, especially Charles Glaser and Jessica Lauffer.

San Diego, CA, USA Cambridge, MA, USA Patrick P. Mercier Anantha P. Chandrakasan

### **About the Authors**

Patrick P. Mercier is an Assistant Professor of Electrical and Computer Engineering, and the Associate Director of the Center for Wearable Sensors, both at the University of California, San Diego (UCSD). His research interests include the design of energy-efficient microsystems, focusing on the design of RF circuits, power converters, and sensor interfaces for mobile electronics and biomedical applications. Prior to joining UCSD, he completed his Ph.D. degree in Electrical Engineering and Computer Science at the Massachusetts Institute of Technology (MIT). Prof. Mercier has received numerous awards include the IEEE International Solid-State Circuits Conference (ISSCC) Jack Kilby Award for Outstanding Student Paper, a Beckman Young Investigator Award, the Hellman Foundation Award, a UCSD ECE Graduate Teaching Award, an Intel Ph.D. Fellowship, a Natural Sciences and Engineering Council of Canada (NSERC) Julie Payette and Post Graduate fellowships, amongst others. He has over 70 publications and invited presentations at venues such as ISSCC, IEEE Journal of Solid-State Circuits, and Nature Biotechnology. Prof. Mercier currently serves as an Associated Editor for the IEEE Transactions on Biomedical Circuits and Systems and the IEEE Transactions on VLSI.

Anantha P. Chandrakasan is the Joseph F. and Nancy P. Keithley Professor of Electrical Engineering at the Massachusetts Institute of Technology, Cambridge. He is the Head of the MIT EECS Department. He has received several awards including the 2009 Semiconductor Industry Association (SIA) University Researcher Award and the 2013 IEEE Donald O. Pederson Award in Solid-State Circuits. His research interests include micro-power digital and mixed-signal integrated circuit design, wireless microsensor system design, portable multimedia devices, energy efficient radios, and emerging technologies. He has served as the Conference Chair for the *IEEE International Solid-State Circuits Conference (ISSCC)* since 2010.

# **Contents**

| Dhongue Lee and Patrick P. Mercier                                                                                                                                        | 1   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Channel Modeling for Wireless Body Area Networks                                                                                                                          | 25  |

| Circuit Techniques for Ultra-Low Power Radios  Jagdish Pandey and Brian Otis                                                                                              | 57  |

| Architectures for Ultra-Low-Power Multi-Channel Resonator-Based Wireless Transceivers Phillip M. Nadeau, Arun Paidimarri, Patrick P. Mercier, and Anantha P. Chandrakasan | 97  |

| Ultra-Low Power Wake-Up Radios                                                                                                                                            | 137 |

| Commercially Viable Ultra-Low Power Wireless                                                                                                                              | 163 |

| Synchronization Clocks for Ultra-Low Power Wireless Networks  Danielle Griffith                                                                                           | 209 |

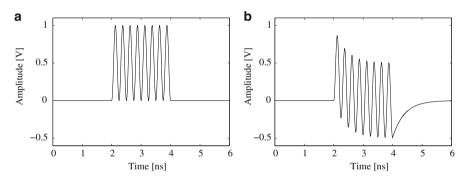

| Pulsed Ultra-Wideband Transceivers Patrick P. Mercier, Denis C. Daly, Fred S. Lee, David D. Wentzloff, and Anantha P. Chandrakasan                                        | 233 |

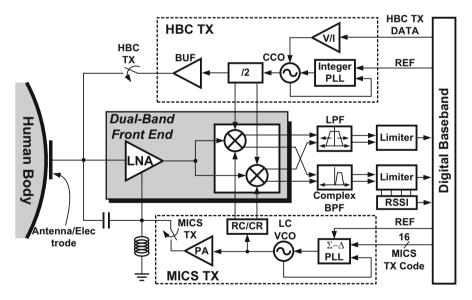

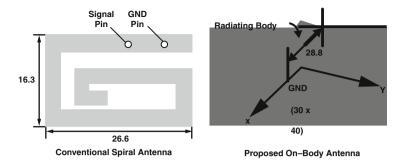

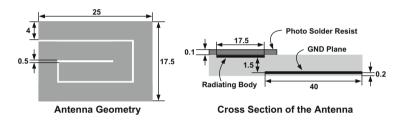

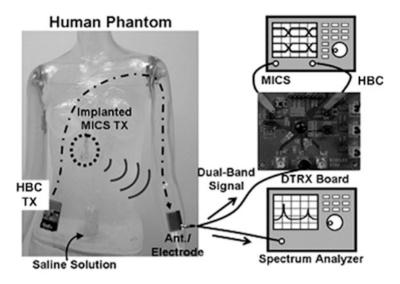

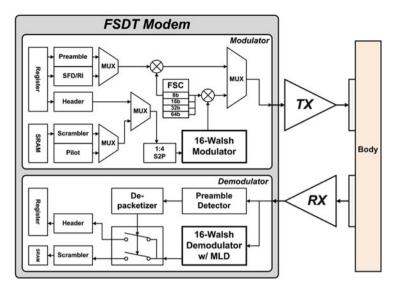

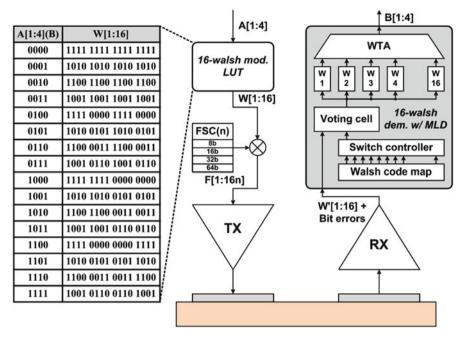

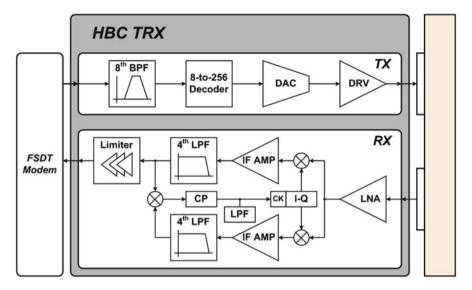

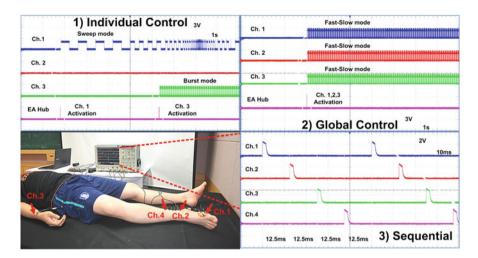

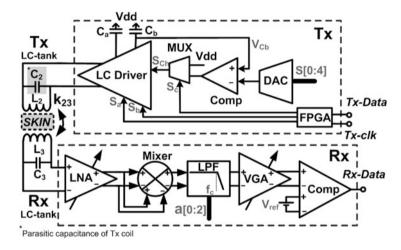

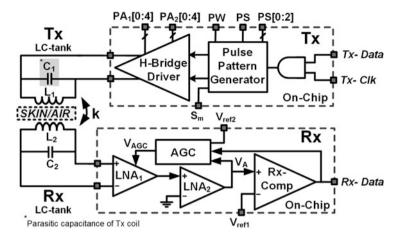

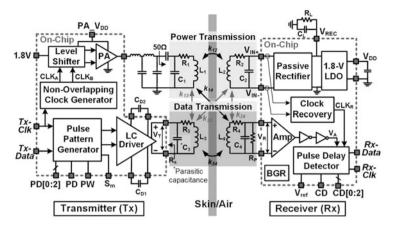

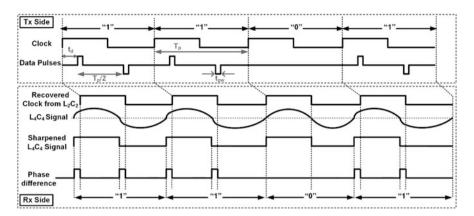

| Human Body Communication Transceiver for Energy Efficient BAN<br>Hyungwoo Lee, Seong-Jun Song, Namjun Cho, Joonsung Bae,<br>and Hoi-Jun Yoo                               | 281 |

| Centimeter-Range Inductive Radios                                                                                                                                         | 313 |

| xii Contents |

|--------------|

|--------------|

| Near-Field Wireless Power Transfer                   | 343 |

|------------------------------------------------------|-----|

| Energy Harvesting Opportunities for Low-Power Radios | 377 |

## **Introduction to Ultra Low Power Transceiver Design**

**Dhongue Lee and Patrick P. Mercier**

Abstract Design of radios with ultra-low-power consumption can enable many new and exciting applications ranging from wearable healthcare to Internet of Things devices and beyond. Achieving low power operation is usually an exercise in trading-off important performance metrics with power. This chapter presents an overview of state-of-the-art narrowband architectures and techniques that achieve ultra-low-power operation, and concludes with a section that benchmarks recent state-of-the-art designs in order to illustrate power-performance trade-offs.

**Keywords** Low power transceiver • Ultra low power radio design

### 1 Introduction

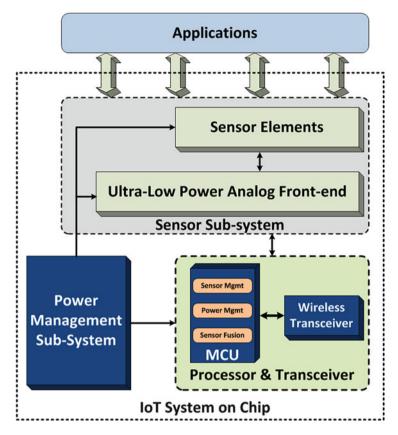

Recent advancements in integrated radio design have enabled many new applications ranging from wearable healthcare or fitness monitors to Internet of Things (IoT) devices, structural integrity monitors, and beyond. In many of these applications, device size and battery life are of critical importance. Since radios often consume a significant portion of the power budget in small sensing nodes [1], reducing radio power consumption can be an impactful way to effectively decrease device size or increase operational lifetime. Reducing radio power can be challenging, however, as there are important tradeoffs between power consumption and performance metrics such as radiated output power, linearity, sensitivity, channelization capabilities, and interference sensitivity. Low-power radio designs often sacrifice one or more of these metrics in the pursuit of low overall power consumption.

The purpose of this chapter is to briefly introduce the main challenges facing narrowband ultra-low-power (ULP) design. This chapter will begin by first defining what is meant by ULP, will introduce common architectures that achieve lowpower operation, and will conclude with some benchmarking data across various

1

D. Lee • P.P. Mercier (⋈)

Department of Electrical and Computer Engineering, University of California, San Diego (UCSD), La Jolla, CA, USA

e-mail: dhl034@ucsd.edu; pmercier@ucsd.edu

architectures. More detailed descriptions of circuit techniques for narrowband ULP radios can be found in chapters "Circuit Techniques for Ultra-Low Power Radios", "Architectures for Ultra-Low-Power Multi-Channel Resonator-Based Wireless Transceivers", "Ultra-Low Power Wake-Up Radios", "Commercially Viable Ultra-Low Power Wireless", and "Synchronization Clocks for Ultra-Low Power Wireless Networks", while chapters "Pulsed Ultra-Wideband Transceivers", "Human Body Communication Transceiver for Energy Efficient BAN", and "Centimeter-Range Inductive Radios" focus on non-narrowband applications. A more detailed overview of ULP transmitters that includes PA design challenges can be found in [2], from which the first part of this chapter is based.

### 2 Link Budgeting

Wireless sensor networks (WSN) and body area networks (BAN) are two common areas that generally require short-range ULP transceivers. The purpose of this section is to briefly review path loss models and link budgets for these representative applications to derive minimum required output power. A more detailed discussion on path loss models is presented in chapter "Channel Modeling for Wireless Body Area Networks".

### 2.1 Wireless Sensor Networks

To come up with a general WSN link budget, consider a *representative* WSN system operating with a carrier frequency of 2.4 GHz at a communication distance of 10 m. Most WSN nodes operate in peer-to-peer ad-hoc networks, where each node can potentially act as a relay between other nodes. Consequently, WSN transceivers must balance power specifications evenly between transmit and receive modes in order to optimize system-level energy efficiency. As a result, receivers are typically designed to have an input sensitivity close to -90 dBm. The minimum transmitter output power can then be calculated by preparing a link budget using the Friis equation for free space as a baseline case:

$$P_{\textit{transmit}} = P_{\textit{receiver}} - G_{\textit{antenna}} - 20 \log_{10} \frac{\lambda}{4\pi D},$$

where  $\lambda$  is the carrier wavelength and D is the distance between nodes. This equation tells us that, in free space, a 10 m link suffers from 60 dB of path loss at 2,450 MHz. A typical surface-mount antenna at 2,450 MHz has a gain of 0 dBi, which leads to the minimum transmit power of -30 dBm under ideal condition. However, a WSN transceiver working in a hostile environment could experience as much as 30 dB of

additional loss, for a total of 90 dB of path loss [3]. Therefore, a WSN transmitter should have a maximum output power of 0 dBm, our definition of a ULP transmitter.

### 2.2 Body-Area Networks

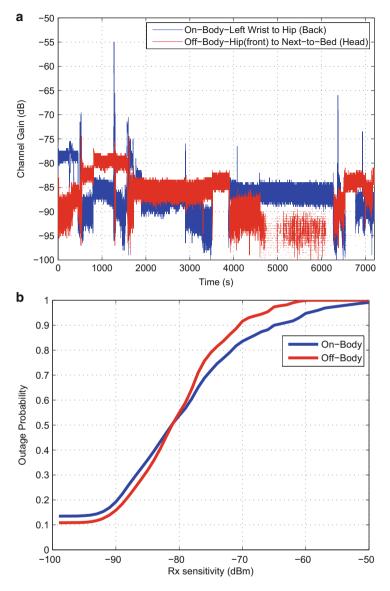

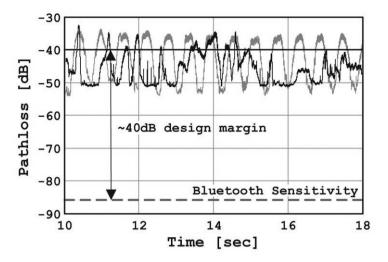

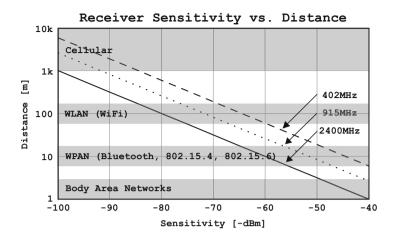

On the other hand, BAN applications have much lower transmission distances: 1-2 m is often sufficient to communicate information around the human body. This should theoretically result in a lower path loss than in WSNs: 40–46 dB in free space at 2.4 GHz. Unfortunately, the presence of the human body in BANs adds significant attenuation, resulting in a measured path loss that range from 40 to 80 dB [4]. As an added complication, this path loss is highly variable and depends not only on the carrier frequency and the distance between nodes, but also on the relative position of the body and its surrounding environment (discussed in [4] and chapter "Channel Modeling for Wireless Body Area Networks"). Fortunately, the frequency of this variation is limited by the response time of a human (hundreds of milliseconds), enabling relatively low-complexity automatic gain control loops to compensate for such variation. Additionally, while the channel itself has high losses, it can generally be modeled as a non-frequency selective channel with no resolvable multipath, eliminating the requirement for complex multi-path cancellation schemes [5]. Other studies have shown slightly lower path loss results (by 10–15 dB) at 900 and 400 MHz [6] as a result of lower tissue conductivity and higher relative permeability. Operating at these frequencies, however, reduces the radiation efficiency of electrically small antennas, which may negate the path loss advantage when computing the system-level energy efficiency. As a result, there is no clear rule-of-thumb regarding carrier frequency selection in BANs, as the available size and location of the antenna affects this decision dramatically.

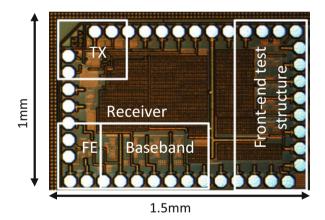

To calculate the generally required PA output power range in a BAN, we first exploit a natural property of the system: most BAN users will be wearing a smartphone or smartwatch platform that is energy-rich, at least in comparison to a wearable or implantable sensor node. Thus, we can utilize these smart devices in an energy-asymmetric star topology network, where the smart watch/phone platform acts as a highly-sensitive centralized base-station. Assuming a base-station receiver sensitivity of  $-100 \, \mathrm{dBm}$ , as typically encountered in commercial Bluetooth receivers, along with path loss of 40–80 dB and 10 dB link margin, the most efficient PA implementation would dynamically alter its output power between  $-10 \, \mathrm{and}$   $-50 \, \mathrm{dBm}$  depending on instantaneous channel conditions;  $-10 \, \mathrm{dBm}$  is also the recommended transmit power according to IEEE802.15.6 BAN standard [7].

To put these number in perspective, recall that -10~dBm corresponds to  $100~\mu W$  output power. It is very challenging to design all downstream blocks to consume well under  $100~\mu W$  in order to limit the overall system power consumption. The rest of this chapter will thus review architectures and circuits that help address this problem.

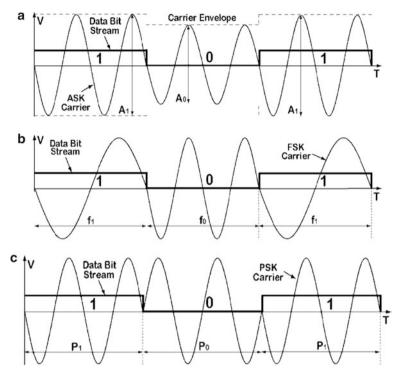

### 3 Modulation Schemes

Achieving ULP operation requires optimization across all design layers, ranging from modulation schemes and architectures, to circuits and devices. One of the most direct ways to reduce power is to reduce the complexity of the modulation schemes, which usually also reduces the overall architectural complexity.

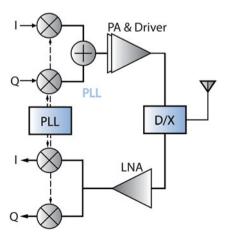

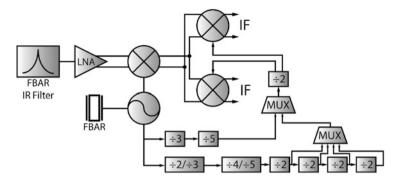

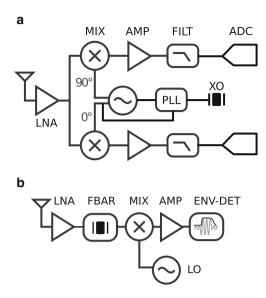

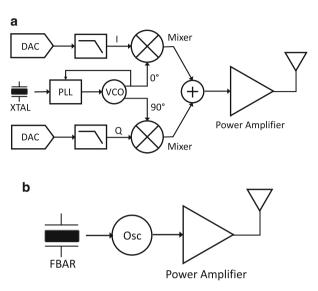

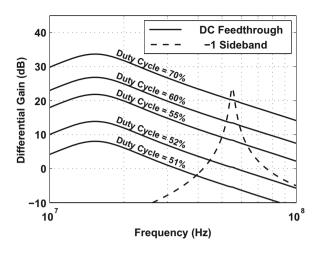

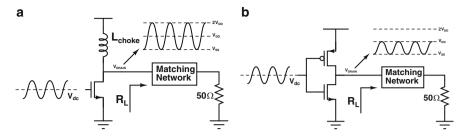

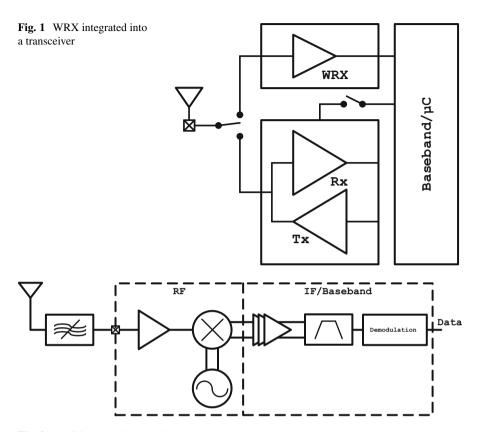

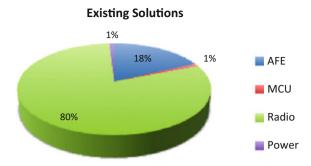

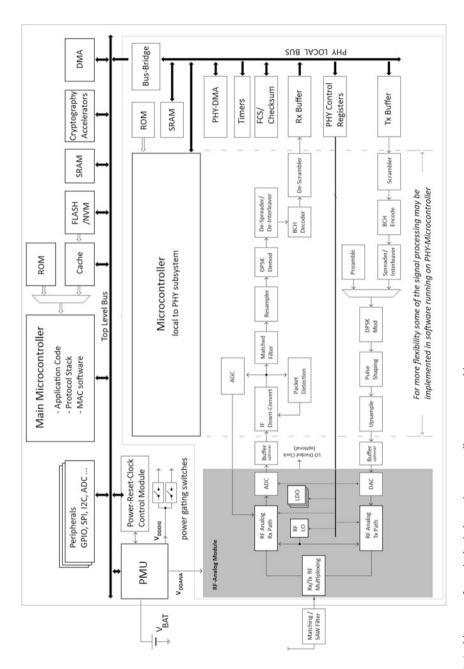

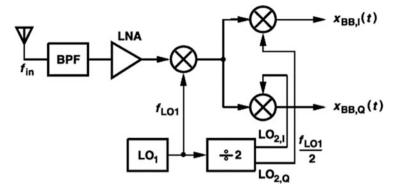

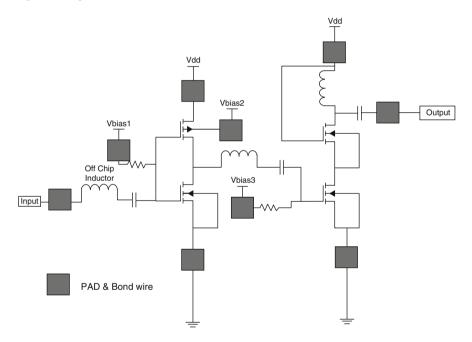

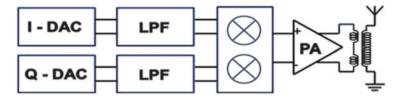

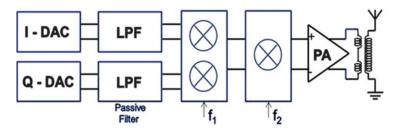

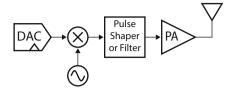

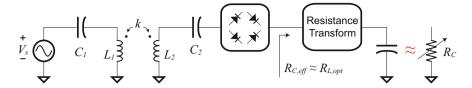

Figure 1 shows an example of a conventional superheterodyne transceiver architecture that adopts quadrature amplitude modulation (QAM) or phase-shift keying (PSK) modulation. These modulations schemes are spectrally efficient, and are therefore appealing in high throughput applications and/or in crowded frequency bands. They do, however, bring additional complexities into the architecture such as the requirement of a phase-locked loop (PLL) and a linear PA, and therefore generally have a higher power consumption than if simpler modulation schemes were employed. For example, low-power PLLs in the 900-MHz range typically consume 800  $\mu W$  [8, 9], which approaches the total power budget of typical ULP transceivers. Furthermore, the long start-up time of most PLLs discourages their use in aggressively duty-cycled systems. Additionally, linearization techniques associated with the PA add additional power consumption, making QAM modulation difficult to incorporate without significant power overhead.

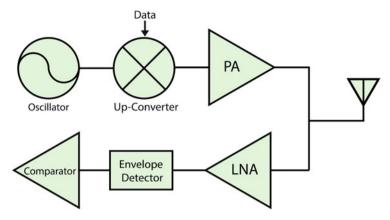

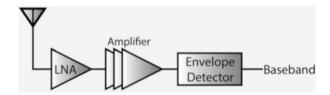

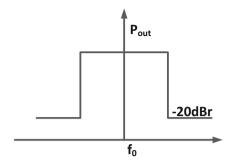

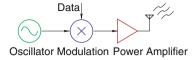

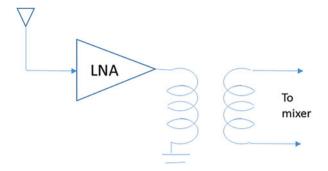

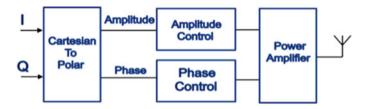

Adopting a non-coherent modulation scheme such as on-off keying (OOK) or frequency-shift keying (FSK) can greatly simplify the architecture, potentially eliminating the PLL and the requirement of a quadrature path, as illustrated in Fig. 2. These simple modulation schemes are also compatible with nonlinear but highly efficient PAs, enabling a further reduction in power consumption. Thus, designers of ULP transceivers generally favor direct-modulation transmitter architectures utilizing OOK or FSK modulation schemes (or in some cases, binary PSK (BPSK) if a high-stability local oscillator (LO) is used), instead of architectures that feature more spectrally efficient modulation schemes. For the same reason, receiver designers often favor envelope-detector and super-regenerative architectures for ULP

**Fig. 1** A generic IQ transceiver architecture

Fig. 2 A generic low-complexity transceiver architecture

applications. Unfortunately, adopting non-coherent modulation schemes and low-complexity architectures directly trade-off performance (in terms of throughput, spectral efficiency, etc.) for ULP operation. The next generation of ULP radios must find a way to achieve both high throughput/spectral efficiency at ultra-low powers in order to satisfy the throughput and efficiency demands of next-generation applications.

The method of generating an LO usually defines the architecture and ultimate power limits of a transmitter, and thus, various architectures that aim to minimize the power consumed in LO generation are discussed in Sect. 4. Section 5 will subsequently discuss ULP receiver architectures.

### 4 Low Power TX Architectures

There are four popular methods to synthesize the carrier frequency in ULP transmitters (TXs):

- 1. Phase-locked loops. The most popular LO generation method, at least at higher output powers, is to employ a PLL to synthesize a carrier frequency that is locked to an on-board reference circuit such as a crystal [10, 11]. Although this is the most robust carrier synthesis solution, continuously operating a PLL is too energy expensive for many ULP applications. Section 4.1 will discuss methods to duty-cycle the PLL for reduced power consumption.

- 2. Free-running DCOs. In applications employing non-coherent signaling with relatively wide bandwidths, it may not be necessary to achieve low phase noise or ultra-high LO precision. In such cases, employing a free-running Digitally Controlled Oscillator (DCO) may be an appropriate solution. Section 4.2 will present an example free-running DCO.

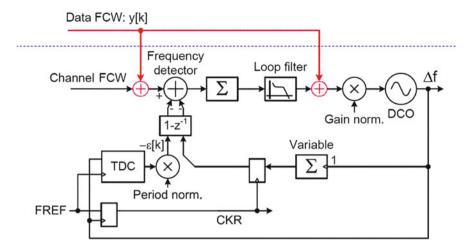

3. **Slow frequency correction loops**. In cases where good phase noise and/or BPSK modulation is required, it is possible to periodically calibrate what is an otherwise free-running DCO using a slow frequency-correction loop from either on-board reference or from a base-station, thereby stabilizing the oscillator without the power/complexity overhead of a full PLL. Section 4.3 will discuss two such possibilities.

4. **High-Q resonators**. Alternatively, a stable and low noise LO can be generated directly from a high-Q resonator without requiring a PLL, generally at the expense of frequency tunability. Section 4.4 will discuss methods to use low-frequency (e.g., crystal) or high-frequency (e.g., FBAR) resonators to generate low-power and stable RF LOs.

### 4.1 Duty-Cycled PLLs

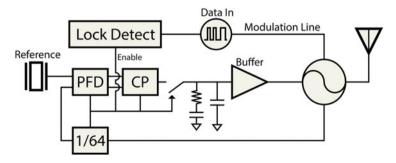

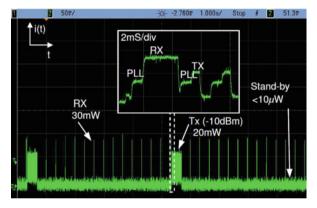

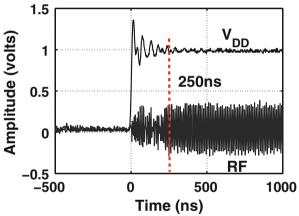

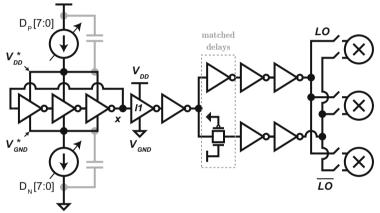

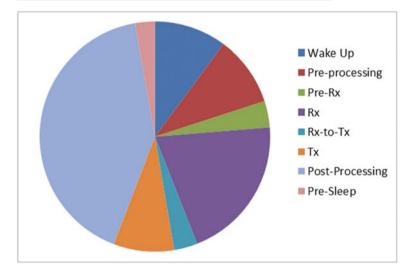

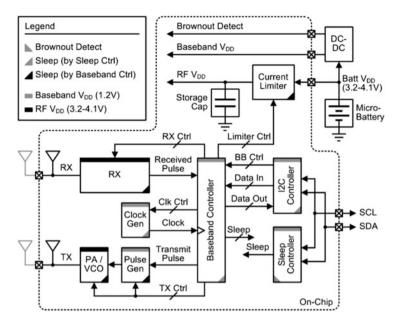

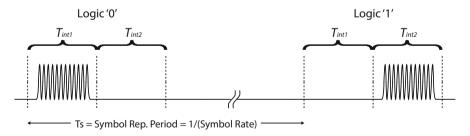

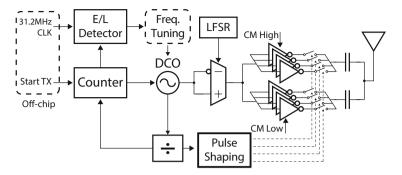

Although they are power hungry, PLLs can robustly synthesize arbitrary RF carrier frequencies with low phase noise. One possible method to utilize a PLL in an energy-constrained system is to duty-cycle its operation as shown in [12, 13]. Figure 3 shows a representative binary FSK (BFSK) transmitter topology where a PLL is locked to an oscillator only prior to transmitting data [12].

With the loop open, the oscillation frequency of the voltage controlled oscillator (VCO—or the analog version of a DCO) can experience frequency-pulling by both noise and strong signals in adjacent channels. In the absence of the latter, the frequency drift can be minimized at 2.5 Hz/ $\mu$ s for a low-voltage multi-gigahertz VCO in a modern CMOS process [12, 14]. The system is designed with an assumption that only one TX is expected to operate in the area. However, in an area with a congested bandwidth, frequency pulling by a nearby strong interferer may become an issue and require multiple calibrations per data transmission.

**Fig. 3** A generic direct modulation transmitter architecture (from [12])

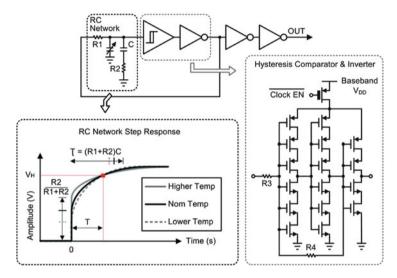

### 4.2 Free-Running DCOs

Free-running DCOs offer the ultimate in terms of a low-complexity design, and as a result can achieve extremely low active- and standby-mode power consumption [15–18]. Typically, using a free-running oscillator restricts modulation schemes to non-coherent FSK or OOK, and can only realistically be used when operating with a sufficiently wide bandwidth such that precise setting of phase and even frequency is not required. Since the human body is an excellent temperature regulator [19], implanted devices often exploit this architecture along with a well-regulated supply voltage to help stabilize the oscillator [15, 19, 20].

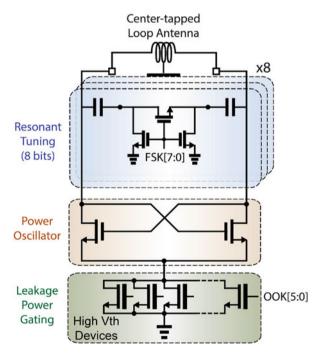

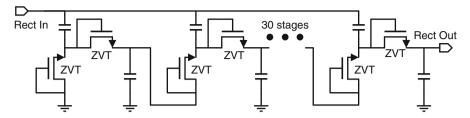

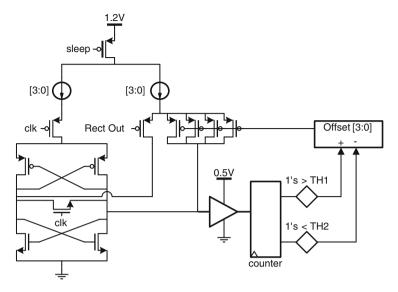

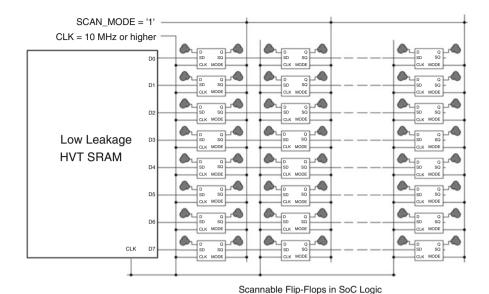

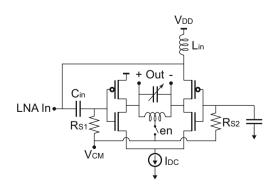

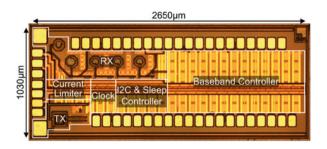

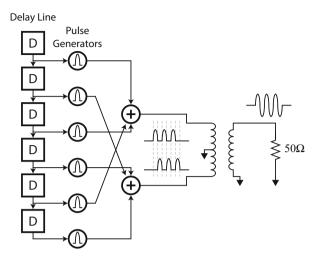

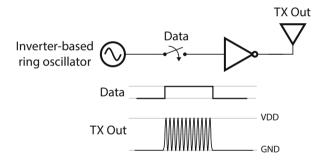

A representative free-running oscillator architecture is described in [15] and achieves an average power consumption of 78 pW through aggressive duty-cycling and ultra-low-leakage design. This particular transmitter was designed as part of a system that operated off of harvested energy from the endocochlear potential located within the inner-ear of mammals [21]. Figure 4 shows a simplified schematic of the single-stage, direct-RF transmitter consisting of a cross coupled NMOS pair loaded by an on-board inductive element that acts as both a resonant element and an antenna, further limiting the overall transmitter complexity and minimizing the number of stages that must operate at RF for minimal standby power consumption.

Fig. 4 Power oscillator architecture with a free running DCO (from [15])

Fig. 5 Frequency calibration through FPGA (from [22])

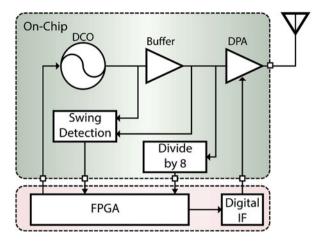

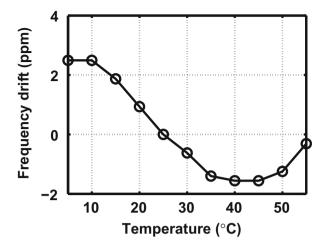

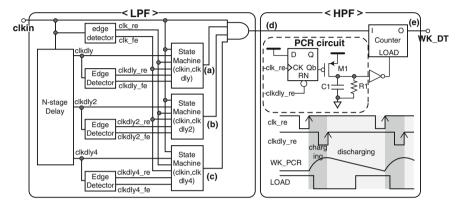

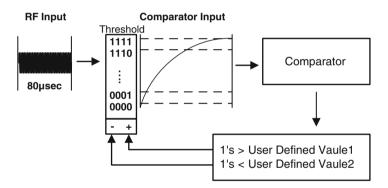

### 4.3 Slow Frequency Correction Loops

In nonimplanted or temperature/voltage-regulated environments, the frequency of a free-running DCO is susceptible to frequency shifts, and may require periodic calibration. While such calibrations will not improve phase noise, they may be necessary to avoid drifting into an adjacent channel. An on-board microcontroller, if available, can be used for calibration as suggested in [22] and shown in Fig. 5. Here, a swing-detector and a divide-by-8 circuit are used to provide digital information to the FPGA for calibration purposes [22].

An alternative method of frequency calibration in star networks first recognizes that the base station likely has an accurate onboard timing reference. The sensor node can thus receive transmitted signals from the base station to extract timing information for calibration purposes [23, 24]. Of course, this requires an onboard receiver (which not all ULP sensing nodes may have) and time/power overhead. A representative FSK transmitter operating at 920 MHz is presented in [23]. This technique is nominally only reasonable in networks with a base station (e.g., star networks) and is not suitable in mesh or ad-hoc networks.

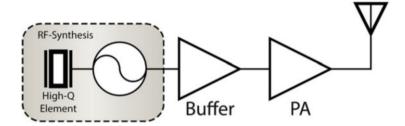

### 4.4 High-Q Resonator-Based TX

Utilizing higher-order PSK modulation schemes in ULP transmitter applications is often desirable due to their superior spectral density compared with OOK and FSK, while maintaining a constant envelop necessary to still incorporate efficient, nonlinear PAs. However, the architectures presented in the preceding two subsections are not well suited to PSK modulation, in part due to the lack of a well-defined

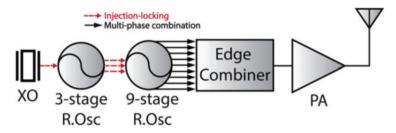

Fig. 6 Injection-locking-based transmitter architecture

LO phase throughout an entire packet. To combat this without requiring the use of a PLL, several architectures have proposed free-running LOs synthesized directly from high-Q resonators.

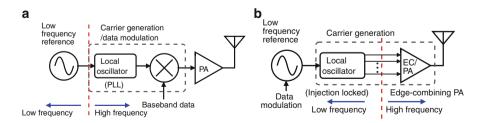

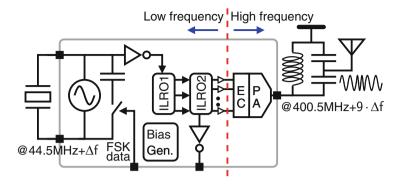

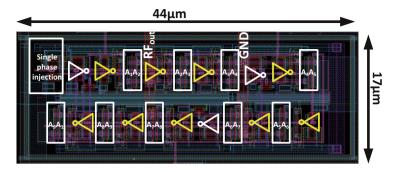

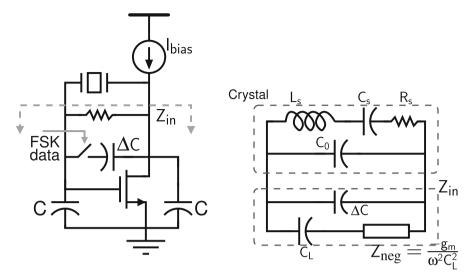

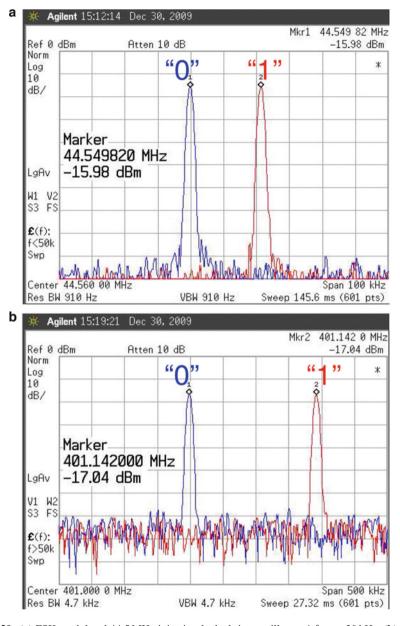

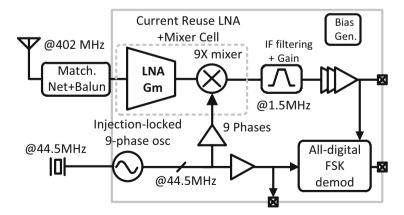

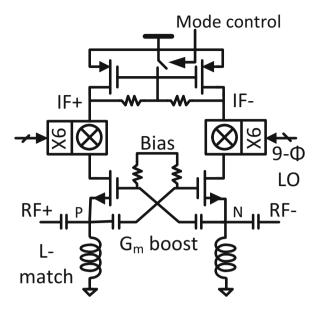

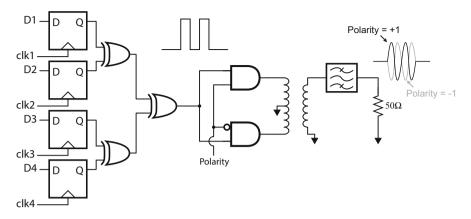

Figure 6 shows a high-level block diagram of an injection-locking based transmitter that was first introduced in [25] and also implemented with some modifications using sub-harmonic injection in [26, 27]. A radio-frequency identification (RFID) tag transmitter based on the same principle can be seen in [28].

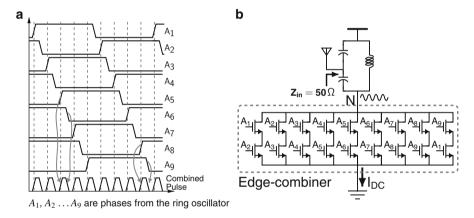

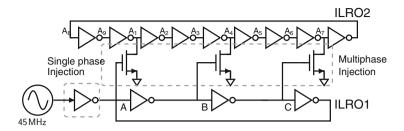

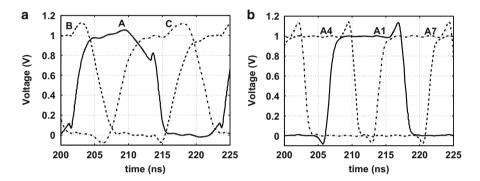

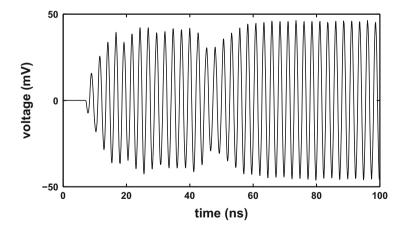

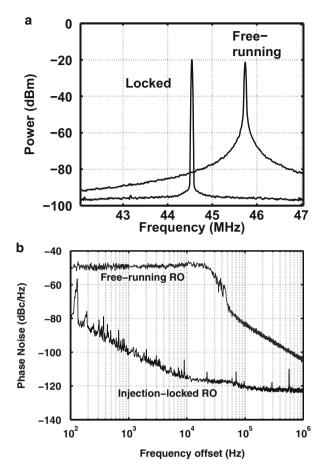

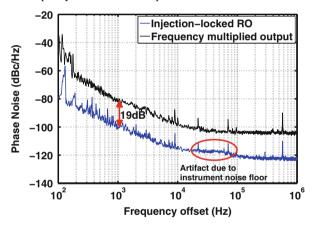

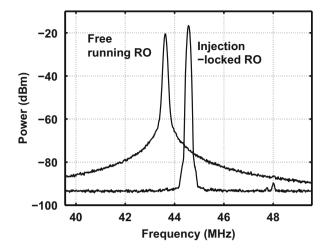

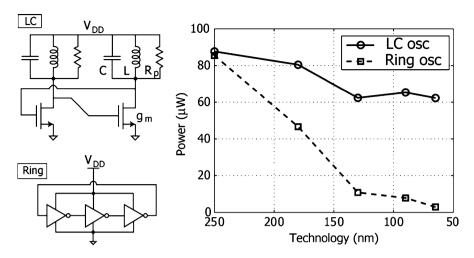

In [25], a three-stage ring oscillator is injection-locked to an external crystal oscillator. Injection locking allows the ring oscillator, which can have very low power especially in advanced process nodes, to inherent the good phase noise performance of the crystal oscillator at low power. The three phases of the ring oscillator are used as an injection signal to lock a 9-stage ring oscillator, producing 9 phases that, when edge combined, multiply the frequency by  $9\times$ , thereby producing the desired RF carrier. It should be noted, however, that the limited tunability of crystal resonators prevents this architecture from being used in applications that demand multi-channel access, which is a very significant drawback in congested environments.

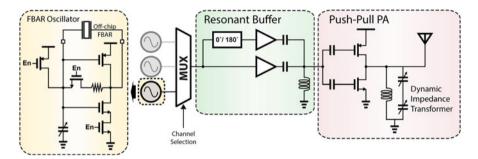

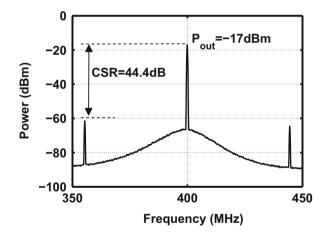

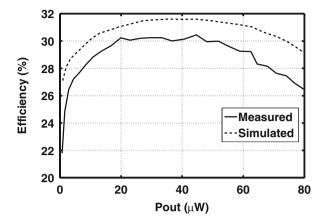

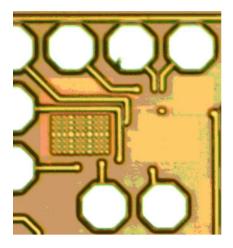

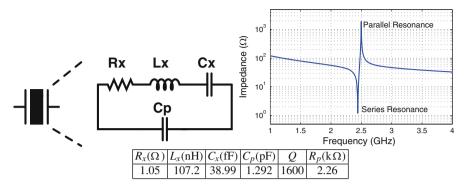

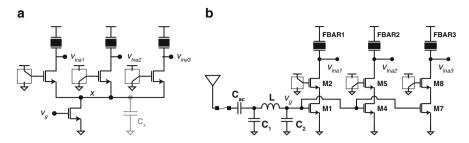

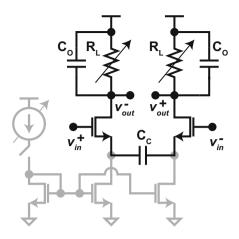

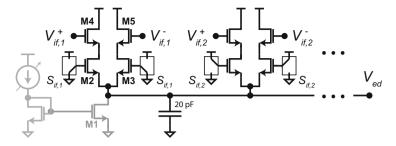

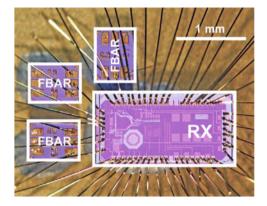

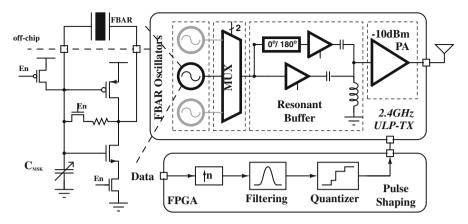

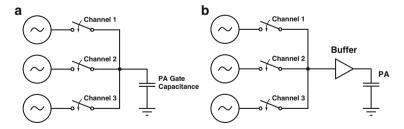

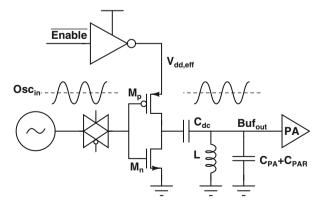

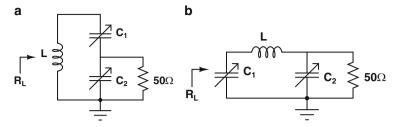

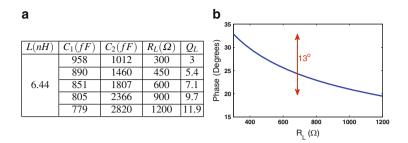

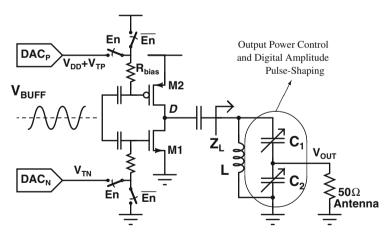

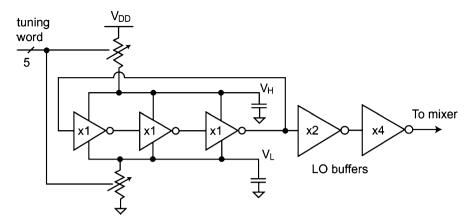

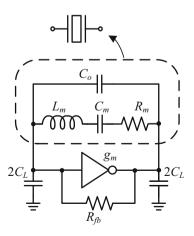

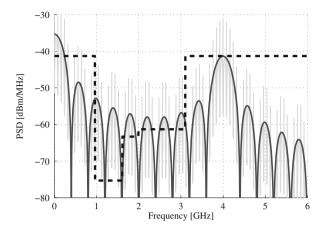

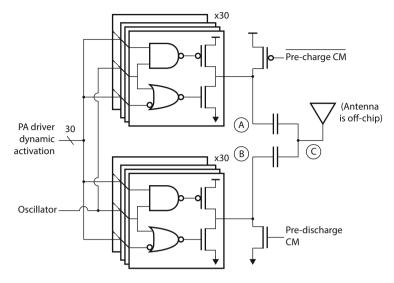

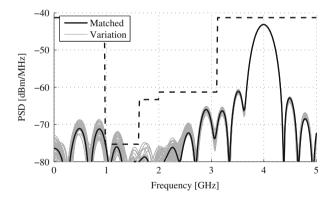

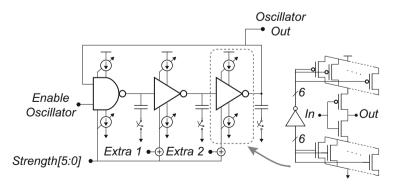

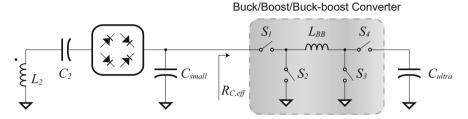

Another promising way to achieve good LO frequency stability without requiring a PLL is to use a high-Q resonator operating directly at RF. For example, Film Bulk Acoustic Resonator (FBAR) or Surface Acoustic Wave resonator (SAW) have high quality factors and operate directly at common RF frequencies. Thus, they can be used in simple direct-modulation architectures, as shown in Fig. 7 [29–32]. Due to their limited tunability, multiple resonators may be needed to achieve channel selection, as demonstrated in [31] and illustrated in Fig. 8. In this architecture, the MSK (Minimum Shift Keying: an FSK modulation with minimum spacing between frequencies) transmitter multiplexes the FBARs by using transmission gates and a buffer.

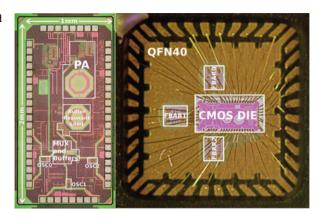

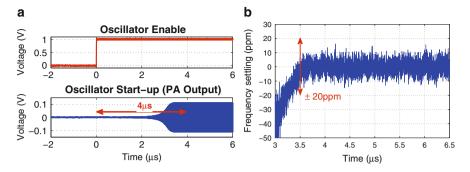

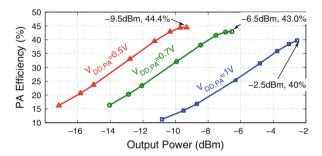

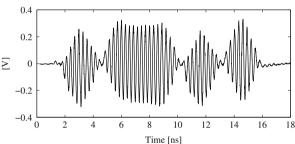

The MSK transmitter achieves data rate of 1 Mbps and output power up to -2.5 dBm while consuming 550  $\mu$ W. The use of high-Q resonators enable a phase noise of -132 dBc/Hz at 1 MHz offset, but also comes with 4  $\mu$ s start-up time and may not be compatible with deeply duty-cycled systems. More details about this architecture are described in chapter "Architectures for Ultra-Low-Power Multi-Channel Resonator-Based Wireless Transceivers".

Fig. 7 FBAR-based transmitter architecture

**Fig. 8** Schematics of multichannel FBAR-based transmitter (from [31] and discussed in detail in chapter "Architectures for Ultra-Low-Power Multi-Channel Resonator-Based Wireless Transceivers")

### 5 Low Power RX Architectures

As was the case for transmitters, the power consumption of a receiver (RX) is highly influenced by the modulation scheme chosen, which then defines the overall receiver architecture. Receivers can be broadly categorized by the following demodulation schemes:

- Clocked demodulation. Broadly, RF energy is first mixed down to a lower frequency (or two) before demodulation occurs. In general, a low phase noise LO is desired, though not strictly required. This category can be further subcategorized into the following architectures:

- a. Super-heterodyne/heterodyne RX. Although the traditional dual down-conversion architecture is extremely robust, as seen in Fig. 1, it requires two LOs and an additional mixer and thus has difficulty achieving ULP operation. Section 5.1 discusses several techniques to minimize the power consumption in such architectures.

- b. *Homodyne (zero-IF) RX*. It is generally more energy-efficient to operate at baseband than at RF, and for this reason, homodyne architectures save power by directly down-converting the input signal to baseband. However, homodyne receivers are well-known to suffer from DC offsets, flicker noise,

LO leakage, and other issues. Thus, low-power methods to address these issues are required, several of which are also discussed in Sect. 5.1.

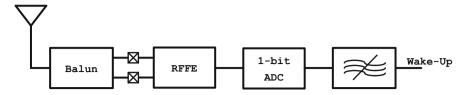

- 2. Energy/Envelope detection. A PLL can be amongst the most power hungry blocks in ULP receivers, and as a result, receiver architectures that eliminate the requirement of a PLL can more easily achieve ULP operation. Eliminating the PLL, however, generally either reduces LO precision, making coherent demodulation difficult, or through high-Q resonators precludes multi-channel operation. Instead, it is possible to perform non-coherent demodulation by observing the signal's energy level either directly at RF, or after down conversion to an imprecise intermediate frequency. Naturally, doing so relies on less spectrally efficiency modulation schemes (e.g., OOK), and has difficulty dealing with blockers. Section 5.2 describes methods to perform envelope/energy detection in more detail.

- 3. **Super-regenerative receiver**. A super-regenerative receiver (SRR) achieves ultra-high gain using a low-complexity unstable network in an efficient and controlled manner. While most SRRs indeed have envelope/energy detectors, SRRs have sufficiently different requirements to consider them separately. Section 5.3 describes the basic operation of a super-regenerative receiver and presents examples from the recent literature.

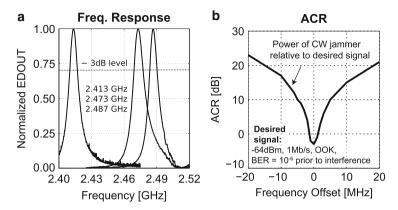

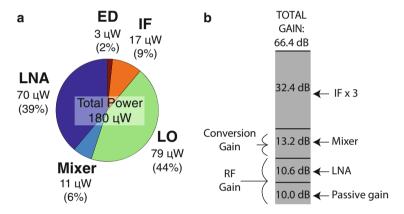

### 5.1 Clocked Demodulator

The power consumption of a receiver is normally dominated by frequency synthesis, RF amplification, and the LO buffer. Although the dual down-conversion architecture is very robust for demodulating data while rejecting unwanted signals, the requirement of multiple down-conversion mixers and two reference signals is often prohibitively expensive from a power perspective in ULP applications. Consequently, low-IF and zero-IF architectures have gained popularity in ULP radio design due to their low implementation complexity (i.e., the minimal number of blocks that consume power). Image rejection problems associated with low-IF receiver architectures can be solved by using high-Q resonators as image rejection filters. Furthermore, certain low power standards, such as ZigBee, require very loose specifications of image rejection and channel filtering [33], potentially saving implementation complexity, though at the expense of an increased chance of interference. Additional power can be saved by adopting simpler modulation schemes such as OOK, FSK, and low-index PSKs, though at the expense of reduce spectral efficiency.

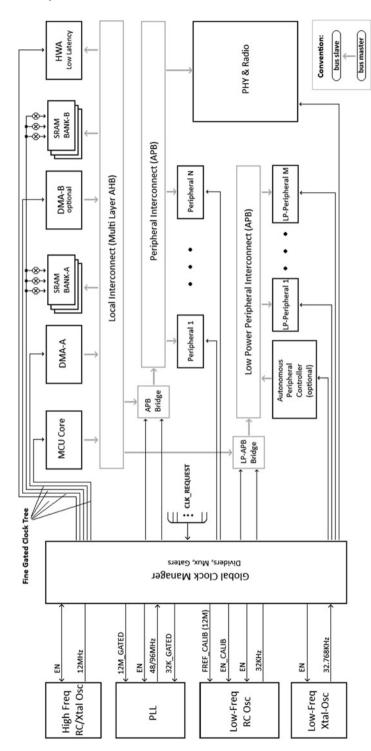

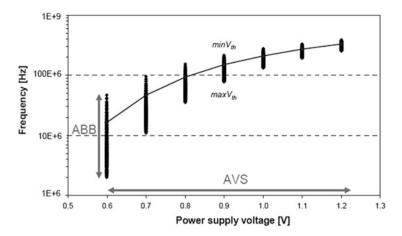

While such system-level simplifications can decrease power consumption, they may not be sufficient to meet ULP power budget constraints. Thus, efforts have been made to further lower the power consumption in such architectures by replacing a PLL with a clever method of frequency synthesis [34–36], lowering the supply voltage [17, 37, 38], and replacing the LNA with a passive mixer front end [17].

Fig. 9 PLL-less FBAR-based super-heterodyne RX schematics [36]

Fig. 10 Schematics of envelope-detector-based RX frontend

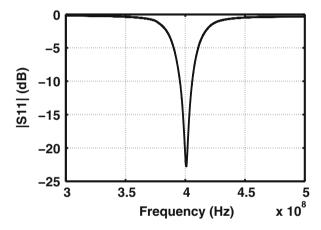

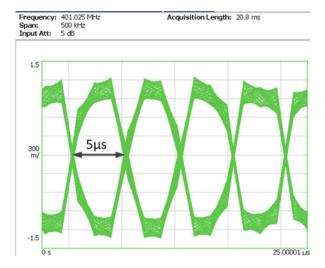

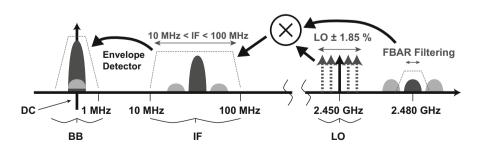

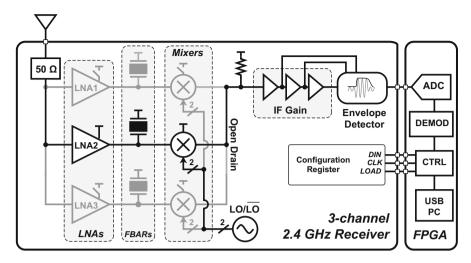

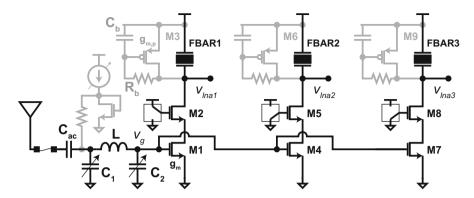

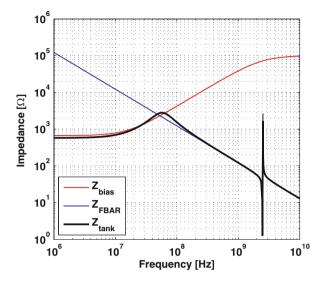

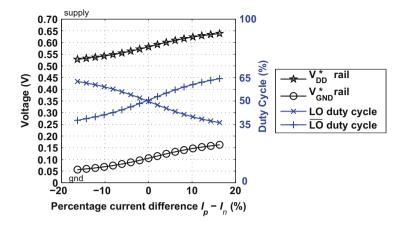

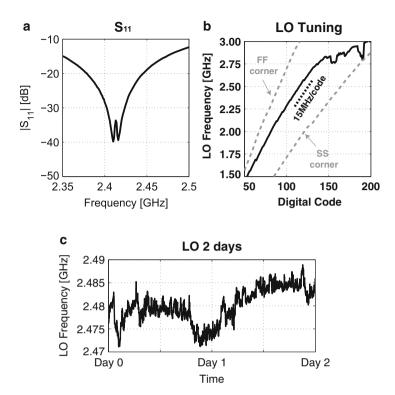

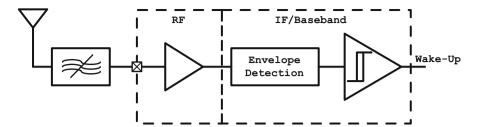

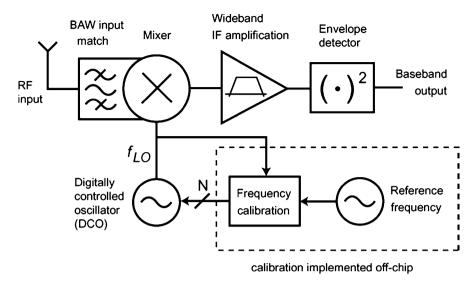

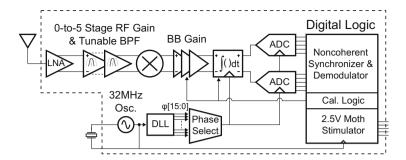

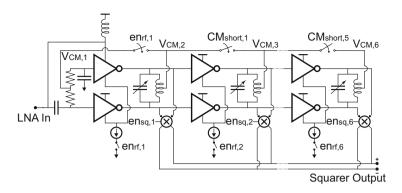

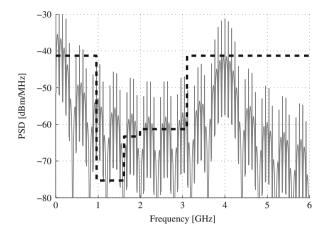

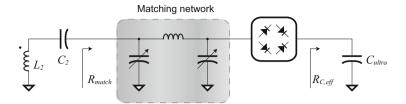

Figure 9 shows an example of a representative FBAR-based multi-channel super-heterodyne receiver architecture [36]. Here, multi-channel operation has been achieved by first down-converting the whole channel band to a wideband IF (5–80 MHz), while using multiple frequency dividers driven by the resonator in order to define all necessary channels in the 2.4 GHz ISM band, as illustrated in Fig. 9.

### 5.2 Energy/Envelope Detector-Based RX

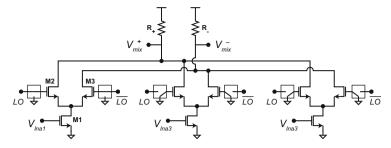

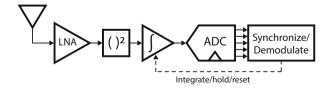

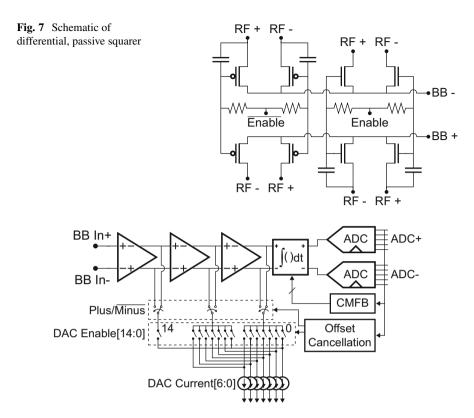

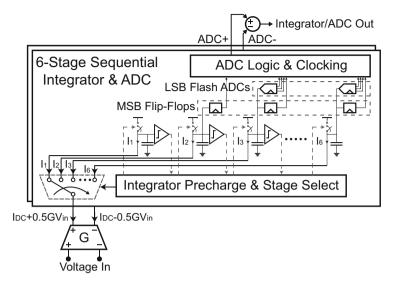

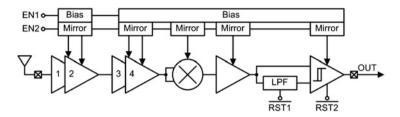

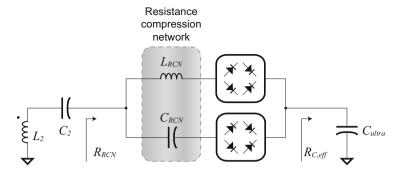

The high power consumption associated with coherent demodulation often steers designers to choose simpler non-coherent modulation scheme such as OOK or FSK at the cost of reduced spectral efficiency. Energy or envelope detector-based receiver architectures further save power consumption by removing the need for an accurate high frequency clock. The key difference between energy and envelope detection is whether a self-mixer or an envelope detector is used, where the former implements an actual squaring operation.

Figure 10 shows a schematic of a generic envelope-detector-based receiver. Envelop and energy detectors generally offer extremely low-power operation compared to all other demodulators, though they suffer from poor blocker rejection and SNR due to translation of blockers to DC and minimum detectable signals set

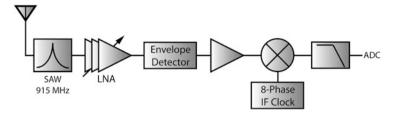

Fig. 11 Schematics of 2-tone FSK receiver [22]

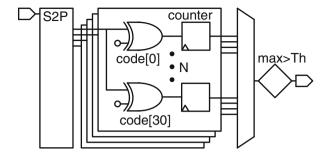

by non-linear elements. These problems can potentially be mitigated by using a 2-tone modulation scheme with a high-gain LNA [22], or by using an uncertain-IF architecture [39].

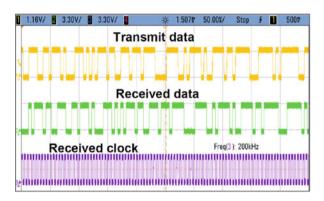

An example 2-tone receiver architecture is shown in Fig. 11. Unlike a traditional envelope detector that down-converts any signal (potentially including interferers) to DC, in a 2-tone system the signal is transmitted at two separate frequencies with a known frequency offset, such that the intermodulation between these two signals lies at a known-IF, which can then be filtered and demodulated with substantial blocker rejection. The implementation in [22] uses the best phase-aligned LO signal amongst 8 phases in order to demodulate the signal without using a quadrature path.

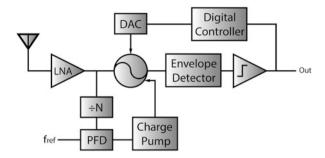

An uncertain-IF architecture utilizes an imprecise and thus power-efficient LO (e.g., a ring oscillator) to down-convert the desired signal to a wide, uncertain IF to take advantage of the large gain attainable at such frequencies. However, down-conversion introduces image content, and a high-Q RF filter, such as bulk acoustic wave resonators (BAW), must be used as image rejection filters [39], which in some cases may be cost or area prohibitive.

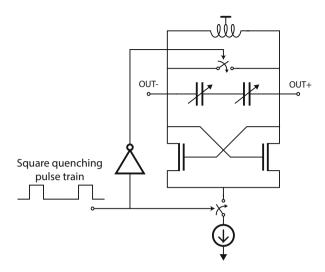

### 5.3 Super-Regenerative Receiver

Super-regenerative receivers (SRR) use an oscillator with a variable bias current to steer the two complex poles of the oscillator from the left half *s*-plane to the right half plane, effectively "oscillating" and "quenching" the system in a non-linear fashion. During the start-up of the super-regenerative oscillator (SRO), any small signal and noise in the vicinity of the oscillator's natural frequency is exponentially amplified, thereby achieving enormous gain—much higher gain than an open loop amplifier. A representative SRR is shown in Fig. 12. Most SRRs use an envelope detector to demodulate OOK or other amplitude modulated signals. Unlike other envelope-detector-based receivers, an SRR can have an arbitrarily large gain (limited by the quench period and power supply rail) and does not nominally suffer from an envelope detector's low detection threshold.

Fig. 12 Schematics of super-regenerative receiver with BW calibration [41]

While super-regenerative amplifiers achieve the largest gain-to-current ratio of any competing amplifier topology by exploiting the positive feedback growth characteristics of a building oscillation, any blocker in a nearby channel can force an oscillation independent of the presence of a signal at the desired band. Consequently, SRR architectures are very susceptible to blockers, and the susceptibility is inversely proportional to the rate at which the transconductance of the oscillator, or the quench signal, grows [40]. An effort has been made to mitigate this problem at the cost of additional complexity and data rate by calibrating the quench signal with a digital feedback loop as shown in Fig. 12 [41].

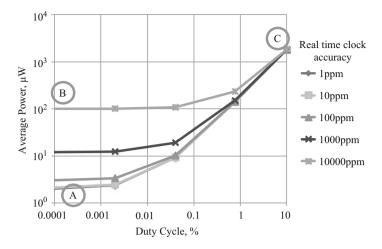

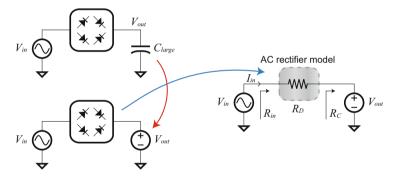

### 6 Benchmarking

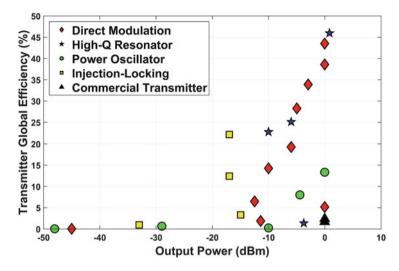

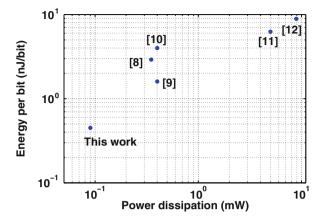

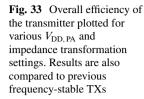

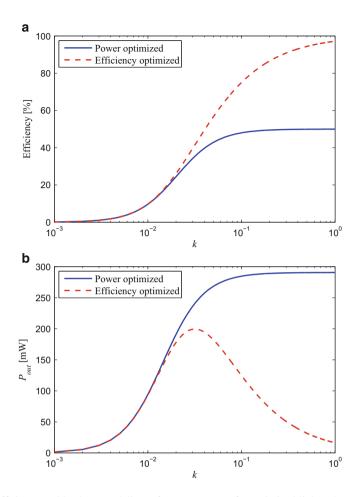

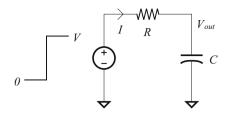

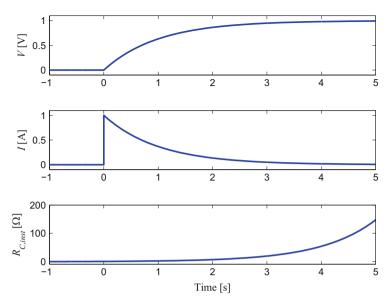

In contrast to traditional high-output-power systems where PAs dominate system power budgets and maximizing their efficiency is imperative, the absolute efficiency of PAs in ULP transmitters is not as critically important. For example, if LO generation, mixing, and baseband circuits require 1 mW, the difference in overall system power consumption for a PA radiating -10 dBm  $(100 \mu W)$  at a PA efficiency of 40 versus 50 % is approximately 4 %. Thus, a more important figure of merit in ULP transmitter design is transmitter efficiency:  $\eta_{TX} = P_{rad,out}/P_{total}$ , where  $P_{rad,out}$  is the radiated output power, and  $P_{total}$  is the total transmitter power consumption. Figure 13 plots this metric for recently published ULP transmitters and two representative commercial transmitters [42, 43], illustrating the difficulty of achieving high transmitter efficiency at low output powers. Next-generation designs should thus endeavor to further minimize the power consumption of the downstream blocks to further increase the overall transmitter efficiency.

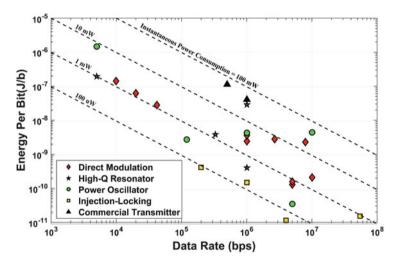

Another metric of critical importance when designing energy-constrained systems is the energy required to transmit a bit of information:  $E_{bit} = P_{total}/DR$ , where DR is the data rate. While providing useful information to system designers,  $E_{bit}$  does not facilitate a fair or direct comparison between transmitter designs, as output power and bandwidth can both have a substantial effect on  $E_{bit}$ . For

Fig. 13 A survey of the global transmitter efficiency of recently-published ULP transmitters

Fig. 14 A survey of the energy efficiency of recently-published ULP transmitters

example, a low output power and wideband TX will have a very low  $E_{bit}$ ; however, communication distance will be short, and the radiated spectrum may violate standards, limiting FDMA opportunities, and increasing the possibility of interference.

To illustrate this, Fig. 14 shows a plot of  $E_{bit}$  versus data rate for recently published transmitters. Since  $E_{bit}$  is inversely proportional to data rate, it is generally possible to increase the data rate with little power overhead to achieve a lower  $E_{bit}$ . For example, it does not cost much in power to increase the modulation rate from

1 to 10 Mbps in an OOK transmitter. Doing so, however, significantly increases the occupied bandwidth, and may not be practical in multi-user scenarios. Thus, when interpreting an  $E_{bit}$  transmitter plot, one should draw a vertical line at the data rate compatible with the spectral resource available in the given application/standard, and only look at transmitter to the left of this line.

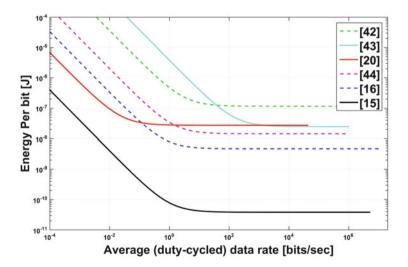

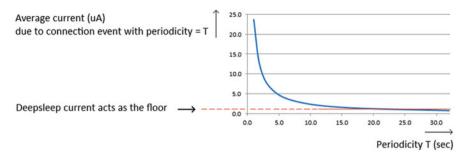

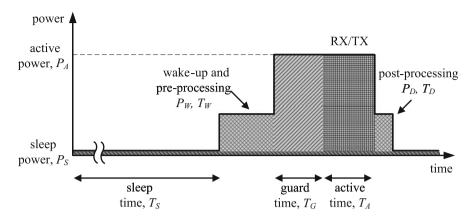

The required data rate in many WSN and BAN cases is often much lower than the maximum achievable radio data rates. Does this mean such applications fundamentally require higher energy-per-bit? The answer is decidedly no, since the above  $E_{bit}$  plot illustrates active-mode energy only, at the instantaneous data rate reported in the published work. Duty-cycling can be employed to effectively shift a data point to the left—that is, a radio that is efficient at 1 Mbps can likely also be efficient at 100 kbps, provided it is capable of rapid and/or efficient duty-cycling. Figure 15 illustrates this by plotting duty-cycled energy-per-bit,  $E_{bit,DC}$ , versus a very wide range of duty-cycled data rates for representative transmitters that publish standby power numbers [15, 16, 20, 42–44]. Specifically, the plot is constructed by computing:

$$E_{bit,DC} = E_{bit} + \frac{P_{standby}}{DR_{DC}}$$

where  $E_{bit}$  is the active-mode energy-per-bit (=  $P_{active}/DR_{instantaneous}$ ),  $P_{standby}$  is the transmitter's standby power, and  $DR_{DC}$  is the duty-cycled data rate. For simplicity, the overhead for duty-cycling is assumed to be negligible, though this may not be the case in practice, particularly in designs that have long start-up times (e.g., those with PLLs). Most of the published ULP transmitters that specify standby power

Fig. 15 Energy per bit vs. average (duty-cycled) data rate

Fig. 16 Normalized energy per bit vs. data rate for representative transmitters

scale nicely down to low data rates, though eventually quiescent and leakage power, integrating over very long time intervals, result in increased energy-per-bit at very low average data rates.

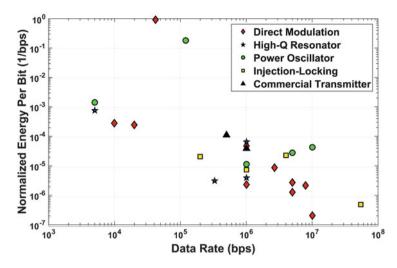

Duty-cycling, however, still does not address the issue that low output power designs naturally achieve superior  $E_{bit}$ . To facilitate a more fair comparison between competing designs,  $E_{bit}$  can be normalized by the radiated output power to create the following normalized energy-per-bit figure of merit [13, 45]:

$$FOM_{E_{nom}} = \frac{E_{bit}}{P_{rad,out}}.$$

A lower  $FOM_{E_{nom}}$  is preferable, as less energy is required to transmit a bit of information at a higher radiated output power. Figure 16 illustrates this FOM for representative transmitters. The same data rate caveat applies here as above.

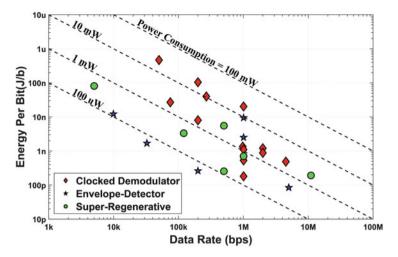

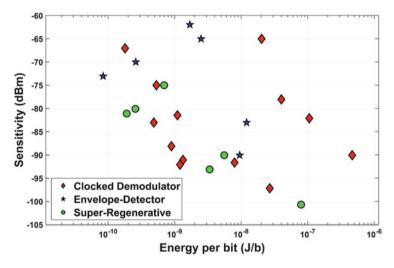

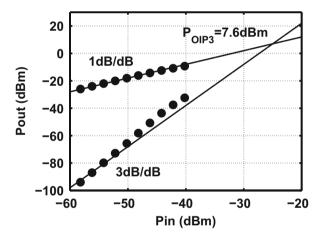

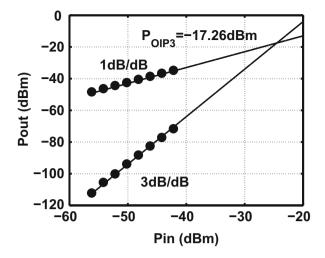

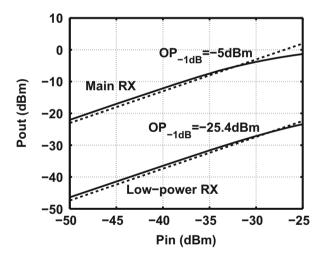

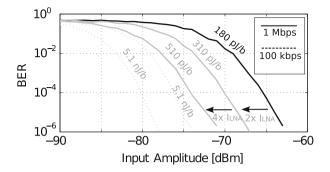

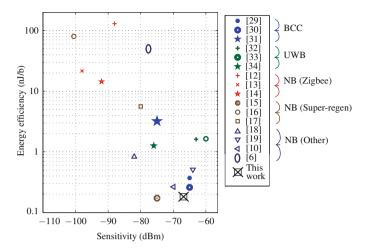

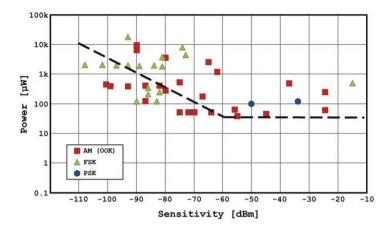

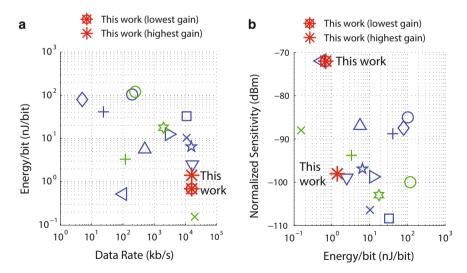

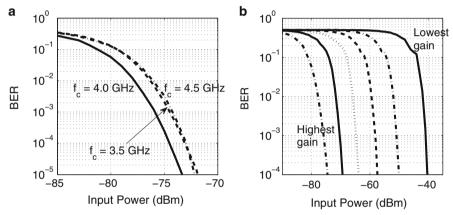

When it comes to ULP receivers, the specifications of interests are power consumption, data rate, and sensitivity. For this reason, energy-per-bit and sensitivity are plotted against data rate in Figs. 16 and 17 respectively. Receivers are categorized into three architectures: Clocked-demodulators [13, 34–36, 46–54], envelope-detectors [3, 22, 23, 30, 39, 55], and super-regenerative [19, 26, 32, 41, 56, 57].

Figure 17 shows that some clocked-demodulator-based receivers consume just as low power as envelope-detector-based and super-regenerative receivers by replacing a PLL with a high-Q resonator [34], or turning off the PLL during the receiver operation [13]. Figure 18 shows that super-regenerative receiver and clocked demodulator architectures attain similar levels of performance given the trade-off

Fig. 17 A survey of the energy efficiency of recently-published ULP receivers

Fig. 18 A survey of the sensitivity of recently-published ULP receivers

between sensitivity and energy-per-bit. Envelope/energy detectors consume the least amount of power, but also generally exhibit inferior sensitivity than the other architectures. Consequently, an envelope detector can be used at the expense of nonlinearity, blocker rejection, and sensitivity when the absolute power consumption is the most important constraint. However, a more favorable trade-off between power consumption and sensitivity can be achieved by using super-regenerative or high-Q resonator-based clocked demodulation architectures for a given energy-per-bit.

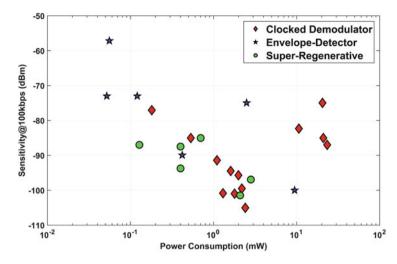

Fig. 19 A survey of the scaled sensitivity @ 100 kbps of recently-published ULP receivers

To foster a better comparison between the architectures, receiver sensitivity can be normalized to the same data rate, in this example arbitrarily chosen as 100 kbps. The normalized sensitivity can be derived for each receiver since data rate scales linearly with bandwidth and thus inversely with sensitivity [58]:

$$Sensitivity_{@100kbps} = Sensitivity - 10 \log_{10} \frac{Data \ Rate}{100 \ kbps}$$

For example, a 10 times increase in data rate would result in 10 dB higher sensitivity. Figure 19 shows a plot of normalized sensitivity at 100 kbps versus power consumption. Here it can be seen more clearly that envelope-detectors suffer a slight degradation in sensitivity compared to the best performance of other receiver architectures from the recent literature.

### 7 Conclusions

Ultra-low-power narrowband radios can open up many unique applications ranging from Internet-of-Things and industrial sensor networks, to wearable sensors, healthcare devices, and beyond. Achieving ultra-low-power consumption while maintaining robust operation involves difficult trade-offs between output power, data rate, bandwidth, channel selectivity, sensitivity, and energy efficiency that must be overcome through a combination of innovative circuit design, novel architectures, and system-level considerations. This chapter has introduced typical architectures used in ULP radios, discussed their relative merits, and provided some

benchmarking data to help identify what architectures might make the most sense given system-level specifications. While optimal implementations depend strongly on the given application, in general the most efficient radios employ low-complexity modulation schemes (e.g., OOK, FSK, and possibly BPSK), and are run by an efficient LO stabilized without a PLL.

That being said, this chapter was just an introduction. Chapters "Circuit Techniques for Ultra-Low Power Radios", "Architectures for Ultra-Low-Power Multi-Channel Resonator-Based Wireless Transceivers", "Ultra-Low Power Wake-Up Radios", "Commercially Viable Ultra-Low Power Wireless", and "Synchronization Clocks for Ultra-Low Power Wireless Networks" describe trade-offs and techniques in narrowband radios in more detail. Before doing so, chapter "Channel Modeling for Wireless Body Area Networks" describes channels models typically found in BAN applications in order to better appreciate the communication requirements in representative ULP environments.

### References

- J.M. Rabaey, J. Ammer, T. Karalar, S. Li, B. Otis, M. Sheets, T. Tuan, PicoRadios for wireless sensor networks: the next challenge in ultra-low power design, in *IEEE International Digest of Technical Papers*. Solid-State Circuits Conference, 2002, pp. 2001–2002

- D.-G. Lee, L.G. Salem, P.P. Mercier, Ultra-low-power transmitter design. *Microwave Magazine*, April 2015

- S. Sayilir, W.-F. Loke, J. Lee, H. Diamond, B. Epstein, D.L. Rhodes, B. Jung, A -90 dBm sensitivity wireless transceiver using VCO-PA-LNA-switch-modulator co-design for low power insect-based wireless sensor networks. IEEE J. Solid-State Circuits 49(4), 996-1006 (2014)

- P.S. Hall, Y.I. Nechayev, A. Alomainy, C.C. Constantinou, C. Parini, M.R. Kamarudin, T.Z. Salim, D.T.M. Hee, R. Dubrovka, A.S. Owadally, A. Serra, P. Nepa, M. Gallo, M. Bozzetti, Antennas and propagation for on-body communication systems. IEEE Antenn. Propag. Mag. 49(3), 41–58 (2007)

- D. Smith, D. Miniutti, L. Hanlen, A. Zhang, D. Lewis, D. Rodda, B. Gilbert, Power delay profiles for dynamic narrowband body area network channels. *IEEE 802.15.6 standard*, 2009

- A. Fort, F. Keshmiri, G.R. Crusats, C. Craeye, C. Oestges, A body area propagation model derived from fundamental principles: analytical analysis and comparison with measurements. IEEE Trans. Antenn. Propag. 58(2), 503–514 (2010)

- IEEE Standard for Local and metropolitan area networks Part 15.6: Wireless Body Area Networks. IEEE Std 802.15.6, 2012

- G. Devita, A.C.W. Wong, N. Kasparidis, P. Corbishley, A. Burdett, P. Paddan, A 0.9 mW PLL integrated in an ultra-low-power SoC for WPAN and WBAN applications, in 2010 Proceedings of ESSCIRC, 2010, pp. 158–161

- 9. W. Deng, D. Yang, T. Ueno, T. Siriburanon, S. Kondo, K. Okada, A. Matsuzawa, 15.1 A 0.0066 mm<sup>2</sup> 780 μW fully synthesizable PLL with a current-output DAC and an interpolative phase-coupled oscillator using edge-injection technique, in *IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC)*, 2014, pp. 266–267

- J. Gil, J.-H. Kim, C.S. Kim, C. Park, J. Park, H. Park, H. Lee, S.-J. Lee, Y.-H. Jang, M. Koo, J.-M. Gil, K. Han, Y.W. Kwon, I. Song, A fully integrated low-power high-coexistence 2.4-GHz ZigBee transceiver for biomedical and healthcare applications. IEEE Trans. Microw. Theory Tech. 62(9), 1879–1889 (2014)

- 11. A. Molnar, B. Lu, S. Lanzisera, B. W. Cook, K.S.J. Pister, An ultra-low power 900 MHz RF transceiver for wireless sensor networks, in *Proceedings of the IEEE 2004 Custom Integrated Circuits Conference (IEEE Cat. No.04CH37571)*, 2004, pp. 401–404

- V. Karam, P.H.R. Popplewell, A. Shamim, J. Rogers, C. Plett, A 6.3 GHz BFSK transmitter with on-chip antenna for self-powered medical sensor applications, in *IEEE Radio Frequency Integrated Circuits (RFIC) Symposium*, 2007, pp. 101–104

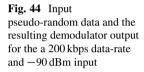

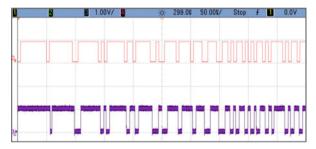

- 13. M. Vidojkovic, X. Huang, P. Harpe, S. Rampu, C. Zhou, L. Huang, J. van de Molengraft, K. Imamura, B. Busze, F. Bouwens, M. Konijnenburg, J. Santana, A. Breeschoten, J. Huisken, K. Philips, G. Dolmans, H. de Groot, A 2.4 GHz ULP OOK single-chip transceiver for healthcare applications. IEEE Trans. Biomed. Circuits Syst. 5(6), 523–534 (2011)

- A. Yamagishi, M. Ugajin, T. Tsukahara, A 1-V 2.4-GHz PLL synthesizer with a fully differential prescaler and a low-off-leakage charge pump, in *IEEE MTT-S International Microwave Symposium Digest*, 2003, vol. 2, pp. 733–736

- P.P. Mercier, S. Bandyopadhyay, A.C. Lysaght, K.M. Stankovic, A.P. Chandrakasan, A sub-nW

GHz transmitter for low data-rate sensing applications. IEEE J. Solid-State Circuits 49(7), 1463–1474 (2014)

- G. Chen, H. Ghaed, R. Haque, M. Wieckowski, Y. Kim, G. Kim, D. Fick, D. Kim, M. Seok, K. Wise, D. Blaauw, D. Sylvester, A cubic-millimeter energy-autonomous wireless intraocular pressure monitor, in 2011 IEEE International Solid-State Circuits Conference, 2011, pp. 310–312

- B.W. Cook, A. Berny, A. Molnar, S. Lanzisera, K.S.J. Pister, Low-power 2.4-GHz transceiver with passive RX front-end and 400-mV supply. IEEE J. Solid-State Circuits 41(12), 2757–2766 (2006)

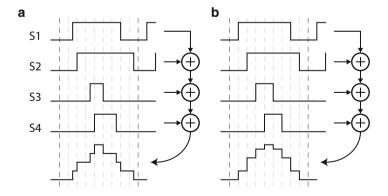

- X. Huang, P. Harpe, X. Wang, G. Dolmans, H. de Groot, A 0 dBm 10 Mbps 2.4 GHz ultra-low power ASK/OOK transmitter with digital pulse-shaping, in *IEEE Radio Frequency Integrated Circuits Symposium*, 2010, pp. 263–266

- J.L. Bohorquez, A.P. Chandrakasan, J.L. Dawson, A 350 µW CMOS MSK transmitter and 400 µW OOK super-regenerative receiver for medical implant communications. IEEE J. Solid-State Circuits 44(4), 1248–1259 (2009)

- E.Y. Chow, S. Chakraborty, W.J. Chappell, P.P. Irazoqui, Mixed-signal integrated circuits for self-contained sub-cubic millimeter biomedical implants, in *IEEE International Solid-State Circuits Conference* – (ISSCC), 2010, pp. 236–237

- P.P. Mercier, A.C. Lysaght, S. Bandyopadhyay, A.P. Chandrakasan, K.M. Stankovic, Energy extraction from the biologic battery in the inner ear. Nat. Biotechnol. 30(12), 1240–1243 (2012)

- X. Huang, A. Ba, P. Harpe, G. Dolmans, H. de Groot, J.R. Long, A 915 MHz, ultra-low power 2-tone transceiver with enhanced interference resilience. IEEE J. Solid-State Circuits 47(12), 3197–3207 (2012)

- J. Bae, L. Yan, H.-J. Yoo, A low energy injection-locked FSK transceiver with frequency-toamplitude conversion for body sensor applications. IEEE J. Solid-State Circuits 46(4), 928–937 (2011)

- G. Papotto, F. Carrara, A. Finocchiaro, G. Palmisano, A 90-nm CMOS 5-Mbps crystal-less RF-powered transceiver for wireless sensor network nodes. IEEE J. Solid-State Circuits 49(2), 335–346 (2014)

- 25. J. Pandey, B.P. Otis, A sub-100  $\mu$ W MICS/ISM band transmitter based on injection-locking and frequency multiplication. IEEE J. Solid-State Circuits **46**(5), 1049–1058 (2011)

- C. Ma, C. Hu, J. Cheng, L. Xia, P.Y. Chiang, A near-threshold, 0.16 nJ/b OOK-transmitter with 0.18 nJ/b noise-cancelling super-regenerative receiver for the medical implant communications service. IEEE Trans. Biomed. Circuits Syst. 7(6), 841–850 (2013)

- 27. M.M. Izad, C.-H. Heng, A 17 pJ/bit 915 MHz 8PSK/O-QPSK transmitter for high data rate biomedical applications, in *Proceedings of the IEEE 2012 Custom Integrated Circuits Conference*, 2012, pp. 1–4

- 28. F. Zhang, M.A. Stoneback, B.P. Otis, A 23 μA RF-powered transmitter for biomedical applications, in 2011 IEEE Radio Frequency Integrated Circuits Symposium, 2011, pp. 1–4

Y. Chee, A. Niknejad, J. Rabaey, A 46% efficient 0.8 dBm transmitter for wireless sensor networks, in Symposium on VLSI Circuits, 2006. Digest of Technical Papers, 2006, pp. 43–44

- D.C. Daly, A.P. Chandrakasan, An energy-efficient OOK transceiver for wireless sensor networks. IEEE J. Solid-State Circuits 42(5), 1003–1011 (2007)

- 31. A. Paidimarri, P.M. Nadeau, P.P. Mercier, A.P. Chandrakasan, A 2.4 GHz multi-channel FBAR-based transmitter with an integrated pulse-shaping power amplifier. IEEE J. Solid-State Circuits **48**(4), 1042–1054 (2013)

- 32. B. Otis, Y.H. Chee, J. Rabaey, A 400 μW-RX, 1.6 mW-TX superregenerative transceiver for wireless sensor networks, in *ISSCC. IEEE International Digest of Technical Papers. Solid-State Circuits Conference*, 2005, pp. 396–398

- 33. I. Nam, K. Choi, J. Lee, H.-K. Cha, B.-I. Seo, K. Kwon, K. Lee, A 2.4-GHz low-power low-IF receiver and direct-conversion transmitter in 0.18-μm CMOS for IEEE 802.15.4 WPAN applications. IEEE Trans. Microw. Theory Tech. 55(4), 682–689 (2007)

- P.M. Nadeau, A. Paidimarri, P.P. Mercier, A.P. Chandrakasan, Multi-channel 180 pJ/b 2.4 GHz FBAR-based receiver, in *IEEE Radio Frequency Integrated Circuits Symposium*, 2012, pp. 381–384

- A. Heragu, D. Ruffieux, C. Enz, A 2.4-GHz MEMS-based PLL-free multi-channel receiver with channel filtering at RF, in *Proceedings of the ESSCIRC (ESSCIRC)*, 2012, pp. 137–140

- K. Wang, J. Koo, R. Ruby, B. Otis, 21.7 A 1.8 mW PLL-free channelized 2.4 GHz ZigBee receiver utilizing fixed-LO temperature-compensated FBAR resonator, in *IEEE International* Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2014, pp. 372–373

- N. Stanic, A. Balankutty, P.R. Kinget, Y. Tsividis, A 2.4-GHz ISM-band sliding-IF receiver with a 0.5-V supply. IEEE J. Solid-State Circuits 43(5), 1138–1145 (2008)

- 38. Z. Lin, P.-I. Mak, R. Martins, 9.4 A 0.5 V 1.15 mW 0.2 mm<sup>2</sup> sub-GHz ZigBee receiver supporting 433/860/915/960 MHz ISM bands with zero external components, in *IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC)*, 2014, pp. 164–165

- N.M. Pletcher, S. Gambini, J. Rabaey, A 52 μW wake-up receiver with -72 dBm sensitivity using an uncertain-IF architecture. IEEE J. Solid-State Circuits 44(1), 269–280 (2009)

- F.X. Moncunill-Geniz, P. Pala-Schonwalder, O. Mas-Casals, A generic approach to the theory of superregenerative reception. IEEE Trans. Circuits Syst. Regul. Pap. 52(1), 54–70 (2005)

- 41. J.-Y. Chen, M.P. Flynn, J.P. Hayes, A fully integrated auto-calibrated super-regenerative receiver in 0.13-μm CMOS. IEEE J. Solid-State Circuits **42**(9), 1976–1985 (2007)

- 42. Texas Instrument, CC2550. [Online]. Available: http://www.ti.com/product/cc2550? keyMatch=cc2550&tisearch=Search-EN

- 43. Nordic Semiconductor, nRF24E2. [Online]. Available: http://www.nordicsemi.com/eng/Products/2.4GHz-RF/nRF24E2/(language)/eng-GB

- 44. P.D. Bradley, An ultra low power, high performance Medical Implant Communication System (MICS) transceiver for implantable devices, in *IEEE Biomedical Circuits and Systems Conference*, 2006, pp. 158–161

- J. Tan, W.-S. Liew, C.-H. Heng, Y. Lian, A 2.4 GHz ULP reconfigurable asymmetric transceiver for single-chip wireless neural recording IC. IEEE Trans. Biomed. Circuits Syst. 8(4), 497–509 (2014)

- 46. J. Masuch, M. Delgado-Restituto, A 1.1-mW -81.4-dBm sensitivity CMOS transceiver for Bluetooth low energy. IEEE Trans. Microw. Theory Tech. **61**(4), 1660–1673 (2013)

- 47. J. Cheng, L. Xia, C. Ma, Y. Lian, X. Xu, C.P. Yue, Z. Hong, P.Y. Chiang, A near-threshold, multi-node, wireless body area sensor network powered by RF energy harvesting, in *Proceedings of the IEEE 2012 Custom Integrated Circuits Conference*, 2012, pp. 1–4

- 48. F. Zhang, K. Wang, Y. Miyahara, B. Otis, A 1.6 mW 300 mV-supply 2.4 GHz receiver with —94 dBm sensitivity for energy-harvesting applications, in *IEEE International Solid-State Circuits Conference Digest of Technical Papers*, 2013, pp. 456–457

- T. Copani, S. Shashidharan, S. Chakraborty, M. Stevens, S. Kiaei, B. Bakkaloglu, A CMOS low-power transceiver with reconfigurable antenna interface for medical implant applications. IEEE Trans. Microw. Theory Tech. 59(5), 1369–1378 (2011)

- 50. Y.-H. Liu, A. Ba, J.H. van den Heuvel, K. Philips, G. Dolmans, H. de Groot, 9.5 A 1.2 nJ/b 2.4 GHz receiver with a sliding-IF phase-to-digital converter for wireless personal/body-area networks, in *IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC)*, 2014, pp. 166–167

- P. Choi, H.C. Park, S. Kim, S. Park, I. Nam, T.W. Kim, S. Park, S. Shin, M.S. Kim, K. Kang, Y. Ku, H. Choi, S.M. Park, K. Lee, An experimental coin-sized radio for extremely low-power WPAN (IEEE 802.15.4) application at 2.4 GHz. IEEE J. Solid-State Circuits 38(12), 2258– 2268 (2003)

- M. Flatscher, M. Dielacher, T. Herndl, T. Lentsch, R. Matischek, J. Prainsack, W. Pribyl, H. Theuss, W. Weber, A bulk acoustic wave (BAW) based transceiver for an in-tire-pressure monitoring sensor node. IEEE J. Solid-State Circuits 45(1), 167–177 (2010)

- 53. M. Vidojkovic, X. Huang, X. Wang, C. Zhou, A. Ba, M. Lont, Y.-H. Liu, P. Harpe, M. Ding, B. Busze, N. Kiyani, K. Kanda, S. Masui, K. Philips, H. de Groot, 9.7 A 0.33 nJ/b IEEE802.15.6/proprietary-MICS/ISM-band transceiver with scalable data-rate from 11 kb/s to 4.5 Mb/s for medical applications, in *IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC)*, 2014, pp. 170–171

- W.-Z. Chen, T.-Y. Lu, W.-W. Ou, S.-T. Chou, S.-Y. Yang, A 2.4 GHz reference-less receiver for 1 Mbps QPSK demodulation. IEEE Trans. Circuits Syst. Regul. Pap. 59(3), 505–514 (2012)

- J.H. Jang, D.F. Berdy, J. Lee, D. Peroulis, B. Jung, A wireless sensor node for condition monitoring powered by a vibration energy harvester, in *IEEE Custom Integrated Circuits Conference (CICC)*, 2011, pp. 1–4

- F.X. Moncunill-Geniz, P. Pala-Schonwalder, C. Dehollain, N. Joehl, M. Declercq, An 11-Mb/s 2.1-mW synchronous superregenerative receiver at 2.4 GHz. IEEE Trans. Microw. Theory Tech. 55(6), 1355–1362 (2007)

- 57. H.-G. Park, J. Lee, J.-A. Jang, J.-H. Jang, D.-S. Lee, H. Kim, S.J. Kim, S.-G. Lee, K.-Y. Lee, An ultra-low-power super regeneration oscillator-based transceiver with 177 μW leakage-compensated PLL and automatic quench waveform generator. IEEE Trans. Microw. Theory Tech. 61(9), 3381–3390 (2013)

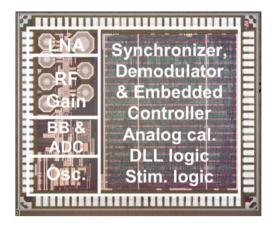

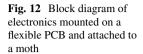

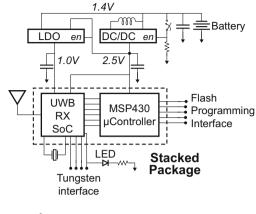

- D.C. Daly, P.P. Mercier, M. Bhardwaj, A.L. Stone, Z.N. Aldworth, T.L. Daniel, J. Voldman, J.G. Hildebrand, A.P. Chandrakasan, A pulsed UWB receiver SoC for insect motion control. IEEE J. Solid-State Circuits 45(1), 153–166 (2010)

## Channel Modeling for Wireless Body Area Networks

David B. Smith and Leif W. Hanlen

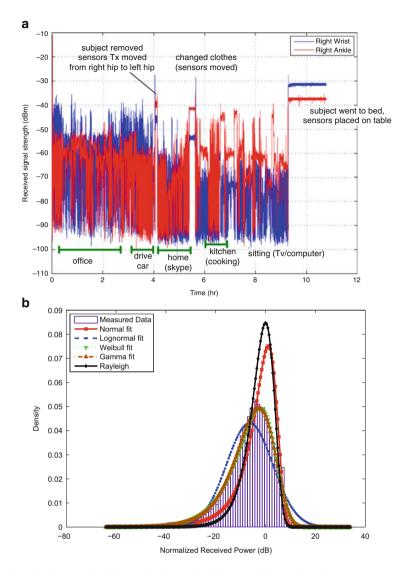

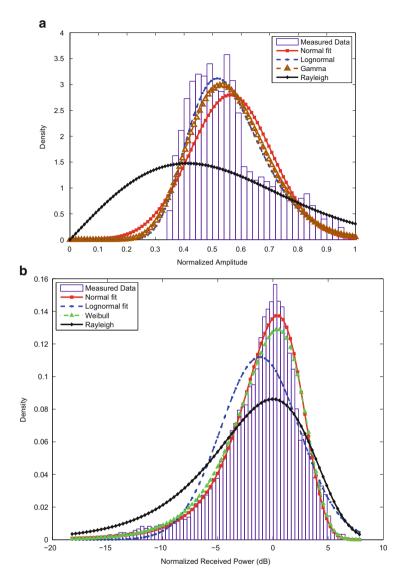

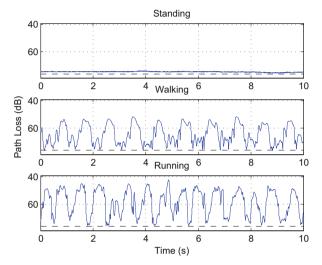

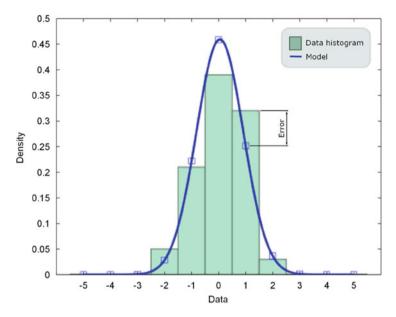

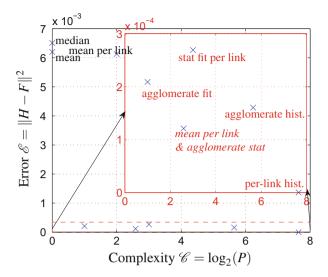

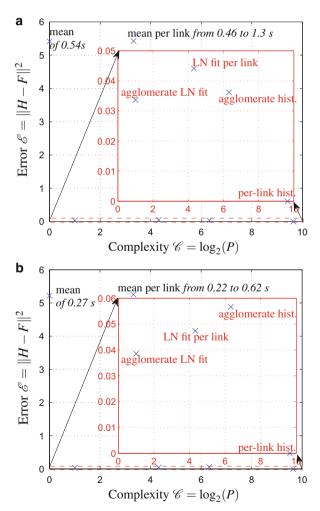

**Abstract** Wireless body area networks (BANs) are the latest generation of personal area networks (PANs) and describe radio networks of sensors, and/or actuators, placed in, on, around and some-times near the human body. BANs are motivated by the health-care application domain where reliable, long-term, operation is paramount. Hence understanding, and modeling, the body-area radio propagation channel is vital. In this chapter we describe channel models for wireless body area networks, in terms of operating scenarios—including on the human body, off the body, in the body, and body-to-body (or interfering); carrier frequencies from hundreds of MHz to several GHz; and bandwidth of operation, including narrowband and ultra-wideband. We describe particular challenges for accurate channel modeling such as the absence of wide-sense-stationarity in typical onbody narrowband BANs. We describe results following from a large amount of empirical data, and demonstrate that the BAN channel is dominated by shadowing with slowly-changing dynamics. Finally two particularly challenging scenarios for BAN operation are described: sleep-monitoring and also where there is a large number of co-located BANs.

**Keywords** Channel modeling • Radio propagation • Wireless body area networks

D.B. Smith  $(\boxtimes)$

NICTA, 7 London Circuit, Canberra, ACT 2601, Australia

Australian National University (ANU), Canberra, ACT 0200, Australia e-mail: David.Smith@nicta.com.au

L.W. Hanlen

NICTA, 7 London Circuit, Canberra, ACT 2601, Australia

Australian National University (ANU), Canberra, ACT 0200, Australia

University of Canberra, University Drive, Bruce, ACT 2617, Australia e-mail: Leif.Hanlen@nicta.com.au

#### 1 Introduction

Wireless body area networks (BANs) are radio networks of sensors and/or actuators, placed on, in, around and/or near the human body, and represent the latest generation of personal area networks. As such, BANs describe radio networks that will often employ ultra-low-power short-range radios. One of the principal application domains of BANs is for use in health-care, with other applications including consumer fitness, emergency services and consumer entertainment. Considering application in health-care, long-term, reliable operation at low-power is very important. We will show that reliable operation is a real challenge for BANs by considering typical characteristics of the radio channel. It is also then very important, so that system design can respond to these characteristics, to derive appropriate channel models for the BAN radio channel.

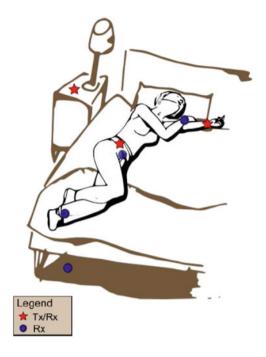

The main focus of this chapter will be the on-body radio channel, for communications from one location on a given subject's body to another location on the subjects body, which is envisaged as the most common BAN implementation. However there will be some focus on the off-body channel and the body-to-body channel. The body-to-body channel is important due to the anticipated prevalence of body area networks, where this interfering channel, with multiple co-located BANs, can dominate the on-body radio channel. It will be shown that there are various difficulties in channel modeling for BAN, which are particular to the BAN channel, underlining the importance of BAN reliability and life-time enhancing system design, such as relay-assisted communications, transmit power control and link adaptation. Important first and second-order statistics can be derived from extensive empirical campaigns, and alternate evaluations can be given directly from empirical data. The "everyday" BAN channel scenario presents a challenging environment for radio propagation and system design, but there are even more challenging environments in which BANs can operate, namely monitoring a person sleeping, and where there is a large number of coexisting BANs, which we will address.

## 2 Operational Scenarios for Wireless Body Area Network Channels

There are four scenarios for wireless body area network channels, namely

- 1. **On-body:** for radio communications from one part on the surface of the human body to another part on the surface of the human body;

- 2. **In-body:** for radio communications from inside the human body, typically to the body surface;

- 3. **Off-body:** for radio communications from the surface of the human body to a device closely located to the body, typically within 3 m of the body (or viceversa, i.e., from off the body to on the body);

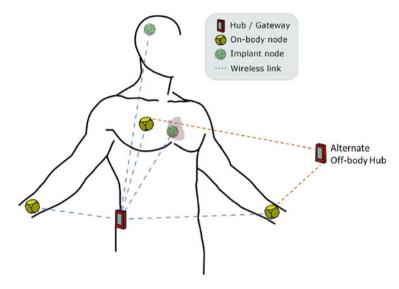

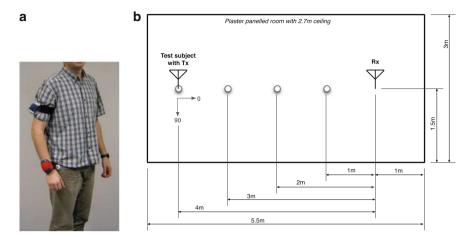

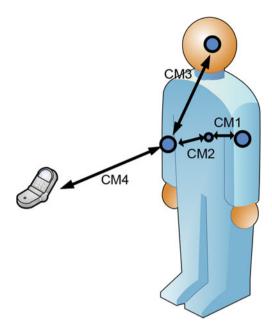

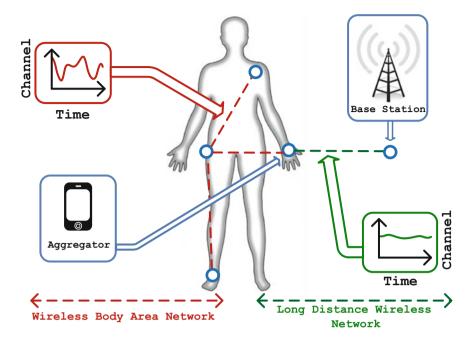

Fig. 1 BAN on a male subject, illustrating gateway (hub), sensors and in-body, on-body and off-body links, adapted from [44]

4. **Body-to-body or interfering:** for radio communications, target or interfering, from one subject's body to another subject's body.

A BAN on a subject, illustrating a gateway (hub), sensor nodes, on,-body in-body and off-body links, is shown in Fig. 1. The hub locations will be typically near the torso, either at the hips or on the chest; places where a subject could comfortably wear a device that is expected to be larger than a sensor node. These locations are also reasonably central on the human body.

We now describe the four scenarios in more detail, particularly with respect to challenges, operating environments and applications for each.

## 2.1 On-Body Channel

The on-body channel is the most prevalent channel for wireless body area networks and is the focus in this chapter. This channel will operate in various environments and will be dominated by slowly-varying dynamics from human-body movement and variations in shadowing by body parts. It presents significant difficulties to the radio systems designer, but there are also some benefits as follows:

• **Difficulties:** When operating with small low-power radios, long sensor/actuator radio lifetime is desired, thus requiring small power demands on the battery of the radio, as well as desired low electromagnetic radiation specific absorption rate (SAR) to the subject's body. This all leads to a desired transmit power

significantly less than  $0\,\mathrm{dBm}$  (or  $1\,\mathrm{mW}$ ),  $-10\,\mathrm{dBm}$  (or  $0.1\,\mathrm{mW}$ ) may often be desirable. Further, as will be described later, at typical carrier frequencies of several hundreds of MHz up to a few gigahertz, communication on the human body provides a difficult radio channel, where instantaneous path losses can become very significant and typical (or median) path losses for a lot of on-body radio links are still (relatively) very large. Further the variations in signal strength are not uniform, from one time interval to the next, such that the channel is in general not wide-sense-stationarity.

- **Benefits:** However there are a few benefits/aids available to the radio system designer from the typical on-body radio channel, particularly with narrowband communications in everyday environments:

- 1. The channel shows reciprocity, that is the radio channel for communications from position a. to position b. on the body, has the same channel profile as for communications b. to a.;

- 2. The channel, for the majority of on-body BAN usage, is stable for at least hundreds of milliseconds (typically more than 0.5 s), enabling relatively accurate channel prediction across multiple communications frames, simply with the last channel gain sample, which can help transmit power control and resource allocation;

- 3. Although the direct, sensor-to-hub, link may be in outage, the slowly varying on-body channel, and possible postures of the human body, means there will often be another dual-hop link between source and hub, through suitably located relay/s transmission paths, giving significant reliability benefit to radio communications;

- 4. Although the overall information transfer over the whole on-body BAN may be large, for typical applications such as in health-care, high data rates for particular links may not be required (often in orders of tens of kilobits per second);

- 5. Finally for narrowband BAN communications, although the on-body channel is slowly time-selective, it is frequency non-selective, with no resolvable multipath, and one channel tap, such that inter-symbol interference (ISI) does not need to be mitigated.<sup>1</sup>

## 2.2 In-Body Channel

The in-body channel will be, almost always, applied for medical applications, and mostly operate at lower carrier frequencies than the on-body channel. The main frequency of operation is most likely to be the medical implant communication system (MICS) band, which operates from 402–405 MHz. The in-body channel will

<sup>&</sup>lt;sup>1</sup>However, we note that for typical IR-UWB, broadband, communications, IEEE 802.15.6 compliant, there are approximately ten resolvable channel taps.

also predominantly be from implants/devices, with miniature radios, to radios on the surface of, or just outside the body. Transmission from one radio in the body directly to a radio in another location inside the body will be highly uncommon. The in-body channel, apart from transmissions at tens of MHz, will suffer from significant attenuation for radiowaves propagating through the body, and will often depend on radio propagation from the nearest body surface to the implant radio device [32].

With respect to the mentioned challenging properties of the on-body channel, the in-body channel will be affected by similar challenges. However restrictions with respect to output Tx power, and reducing battery power consumption are even further magnified, as it is desirable for batteries inside the human body to have a lifetime of several years (frequent surgery is not desirable), as well as reducing radio-wave absorption inside the human body.

As the in-body communication channel includes various additional components (e.g., creeping waves) we shall not discuss this further in this chapter as it is significantly different to the other parts. We note that there is some good description of in-body communications in, e.g. [4, 32].

## 2.3 Off-Body Channel

The off-body channel is the radio channel the most similar to standard small cell and personal area networks radio communications. However transmission from one part of the human body to a gateway/hub radio at a small distance from the human body will also often be dominated by shadowing, similar as for the on-body channel. It is also slowly time selective and a one-tap channel—but it can reasonably be expected that it is more wide-sense-stationary than the on-body channel, and also median path losses will often be lower, even though often over a greater distance than on-body links. In applications such as health-care, suitable placement of the radio device/s off the body may be particularly important to maximize the typical channel gains from desired off-body transmission, or to enhance the on-body communications, where one or more relays is placed off the human body. Also the off-body channel may have less energy-constrained relays than the on-body radio channel. All the other benefits for radio systems design for the on-body channel also apply for the off-body channel, such as reciprocity—but the data rates may sometimes be larger than for the on-body channel.

## 2.4 Body-to-Body (or Interference) Channel

In most wireless body area networks, it is unlikely that one network will be spread over multiple human bodies, apart from obvious exceptions for uses such as in the military and emergency services. But the body-to-body radio channel characteristics

are still very important, as in many cases for BAN operation there will be some, or significant, mobility, which coupled with the large anticipated large take-up of BANs, implies there will often be multiple people wearing BANs closely located, requiring coexistence without coordination between BANs. Thus, understanding radio propagation from one BAN to the sensor, relay or hub, of another BAN becomes very important.

This interfering channel will often demonstrate lower path losses than for an on-body Tx/Rx radio link-of-interest, due to on-body shadowing, and a lack of shadowing from the body-to-body interfering channel. Further the body-to-body channel does not demonstrate free-space path loss, and is strictly not distance dependent, unless a slowly varying shadowing factor is added to a distance-based path loss description with a larger path loss exponent than free space. The dynamics of the on-body channel, and body-to-body channel, are also similar to each other in that they are slowly time selective and frequency non-selective when considering narrowband communications.

The operation of BANs can also be significantly enhanced, when co-located with other BANs experiencing body-to-body interference, by both transmit power control and relay-assisted communications. In fact these two techniques may be particularly important to achieve performance benchmarks for on-body BANs to coexist with other BANs.

## 3 Technical Requirements for IEEE 802.15.6 BANs

There are various technical requirements, or, more precisely, guidelines for BANs from the IEEE 802.15.6 [47]. These broadly represent how BANs should operate and significantly influence key parameters for channel modeling.

- BANs should be scalable up to 256 nodes.

- A BAN link should support bit-rates between 10 kb/s and 10 Mb/s.

- The packet error rate (PER) should be ≤10 % for a 256 octet payload (i.e., 256×8 bits of data) for the 95 % best-performing links according to PER (i.e., at a given signal-to-noise ratio, those 5 % of channels that give the worst PER performance should not be used to determine whether this PER guideline is met).

- Maximum radiated Tx power should be 0 dBm (or 1 mW), and all devices should be able to transmit at -10 dBm (or 0.1 mW).<sup>2</sup> This automatically meets specificabsorption-rate (SAR) guideline of the FCC of 1.6 W/kg in 1 g of body tissue [13] (which equates to a max Tx radiated power of 1.6 mW).

- Nodes should be able to be added and removed (insertion/de-insertion) to/from the network in less than 3 s.

- Reliability, latency (delay) and jitter (variation of one-way transmission delay) should be supported for those BAN applications that need them. Latency in

<sup>&</sup>lt;sup>2</sup>Please note this maximum Tx power is a requirement in the standard.

medical applications should be less than 125 ms, and should be less than 250 ms in non-medical applications. Jitter should be less than 50 ms.

- Power saving mechanisms (such as duty cycling) should be provided.

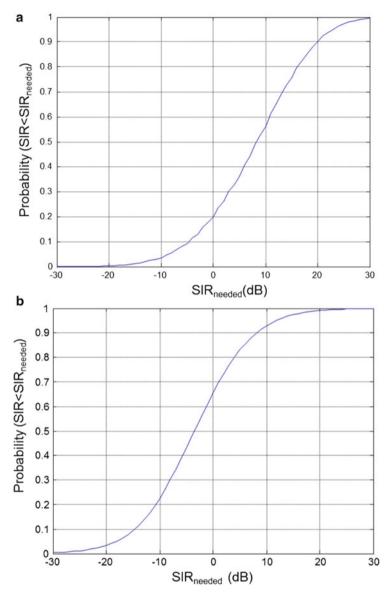

- The physical layer should support co-located operation of at least ten randomly distributed BANs (i.e. up to 2,560 nodes) in a  $6 \times 6 \times 6m^3$  volume.

- In-body BAN and on-body BAN should coexist in and around the body.

#### 4 Narrowband and UWB Radio Channels for BANs

BANs can use narrowband communications or UWB communications, classifications in terms of carrier frequencies and bandwidths are given in Table 1. We exclude mm-wave communications, such as at 60 GHz carrier frequency, as there is no BAN specification for this, and with very large path losses around the body at these frequencies, reliable communications is very difficult. We also exclude optical wireless and human-body communications (using body conduction), as typical radios do not use these techniques.

## 4.1 BAN Propagation Scenarios

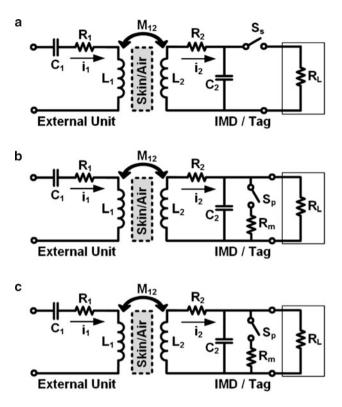

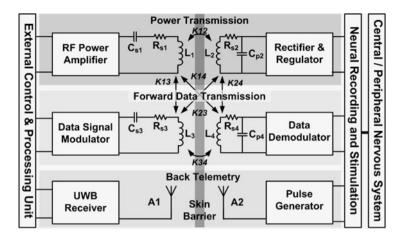

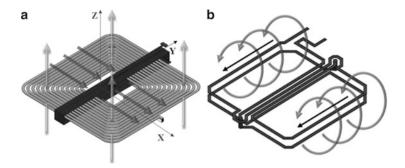

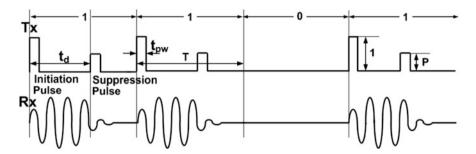

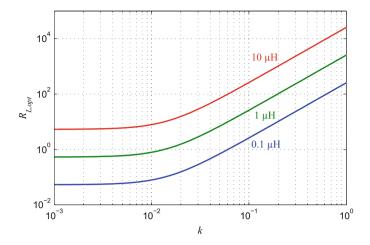

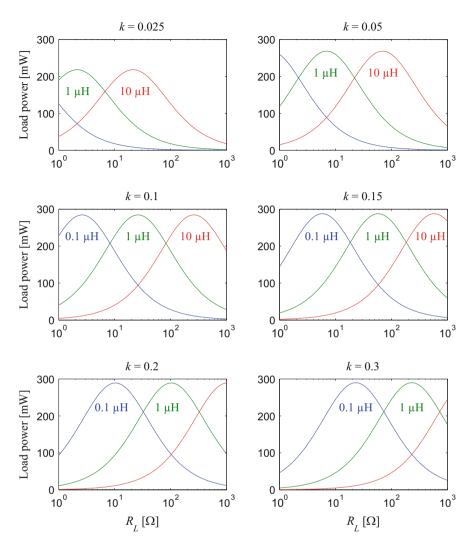

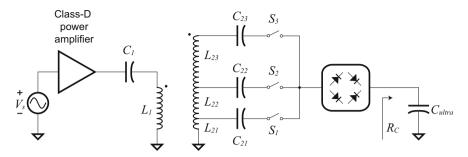

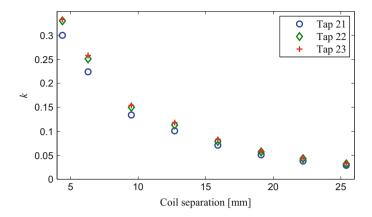

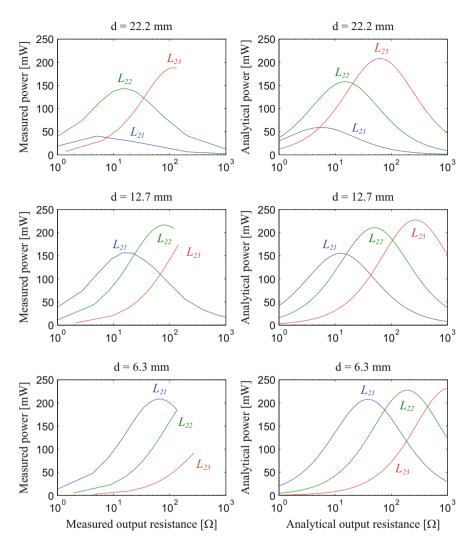

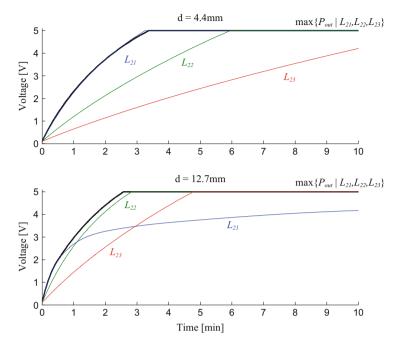

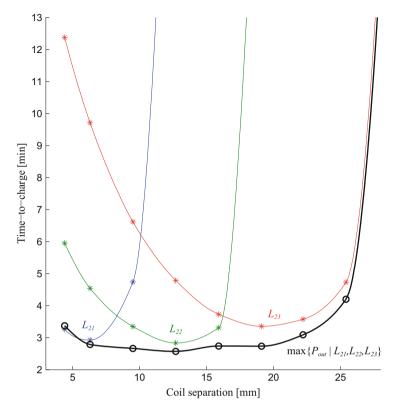

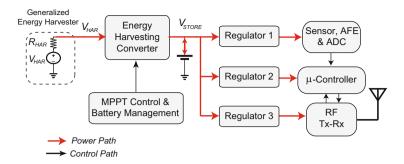

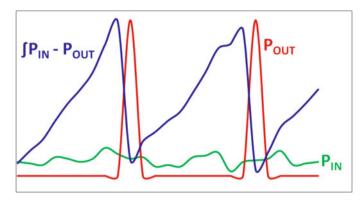

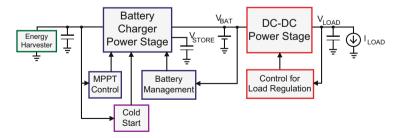

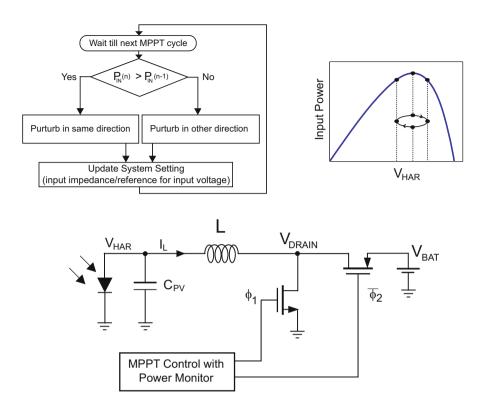

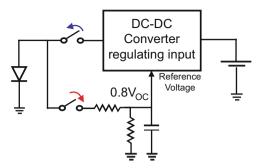

There are two physical layer radio propagation methods defined by the IEEE 802.15.6 BAN standard [23],