## semiconductor electronics by worked example

SEMICONDUCTOR ELECTRONICS by Worked Example

Other Macmillan books on Electronics

DIGITAL ELECTRONIC CIRCUITS AND SYSTEMS Noel M. Morris LINEAR ELECTRONIC CIRCUITS AND SYSTEMS G. D. Bishop ESSENTIAL FORMULAE FOR ELECTRONIC AND ELECTRICAL ENGINEERS Noel M. Morris

# SEMICONDUCTOR ELECTRONICS by Worked Example

F. Brogan

B.Eng., C.Eng., M.I.E.E.

Senior Lecturer in Electronics and Computer Engineering, Wigan and District Mining and Technical College

Macmillan Education

© F. Brogan 1974

All rights reserved. No part of this publication may be reproduced or transmitted, in any form or by any means, without permission

First published 1974 by THE MACMILLAN PRESS LTD London and Basingstoke Associated companies in New York Dublin Melbourne Johannesburg and Madras

> ISBN 978-1-349-81538-8 (eBook) DOI 10.1007/978-1-349-81538-8

ISBN 978-1-349-81540-1

The paperback edition of this book is sold subject to the condition that it shall not, by way of trade or otherwise, be lent, re-sold, hired out, or otherwise circulated without the publisher's prior consent in any form of binding or cover other than that in which it is published and without a similar condition including this condition being imposed on the subsequent purchaser.

## Contents

| Pre | face     |                                                      | ix |

|-----|----------|------------------------------------------------------|----|

| Key | ∕ to soi | urce of examination questions                        | xi |

| 1   | Semic    | conductor diodes, rectifiers, and stabilisers        | 1  |

|     | 1.1      | Current conduction in a semiconductor                | 1  |

|     | 1.2      | Junction diode                                       | 2  |

|     | 1.3      | Full-wave rectifier circuits                         | 4  |

|     | 1.4      | Operation of Zener stabiliser                        | 5  |

|     | 1.5      | Zener stabiliser calculations                        | 7  |

|     | 1.6      | Other Zener circuits                                 | 8  |

|     | 1.7      | Zener protection circuit                             | 9  |

|     | 1.8      | Stabilisation ratio of a Zener stabiliser            | 9  |

|     | 1.9      | Voltage-doubling circuit                             | 10 |

|     | 1.10     | Voltage-quadrupling circuit                          | 10 |

|     | 1.11     | Exercises                                            | 11 |

| 2   | Volta    | ge and current common-emitter amplifiers             | 13 |

|     | 2.1      | Load line; dissipation, current gain, and input      |    |

|     |          | resistance                                           | 13 |

|     | 2.2      | Load line; voltage, current, and power gains         | 14 |

|     | 2.3      | Amplifier with fixed bias                            | 15 |

|     | 2.4      | Amplifier with emitter resistor                      | 16 |

|     | 2.5      | Amplifier with collector-base resistor               | 17 |

|     | 2.6      | Amplifier with potential-divider stabilisation       | 18 |

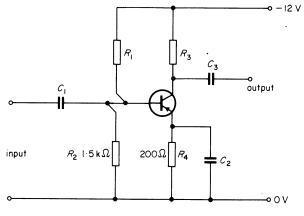

|     | 2.7      | Design of practical amplifier                        | 19 |

|     | 2.8      | Voltage, current, and power gains                    | 20 |

|     | 2.9      | Stability factor of amplifier with collector-base    |    |

|     |          | resistor                                             | 20 |

|     | 2.10     | Stability factor of amplifier with potential-divider |    |

|     |          | stabilisation                                        | 21 |

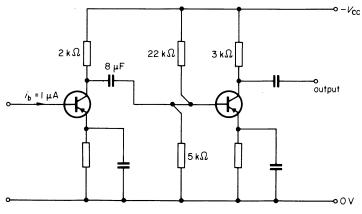

|     | 2.11     | Directly coupled amplifier                           | 23 |

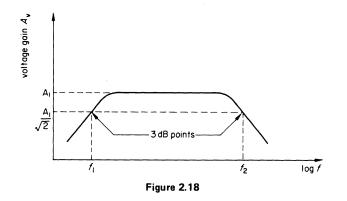

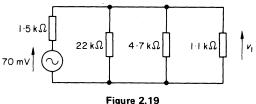

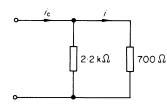

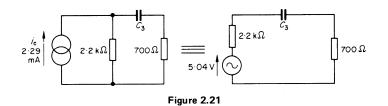

|     | 2.12     | Frequency-response curve of RC-coupled amplifier     | 24 |

|     | 2.13     | Exercises                                            | 25 |

| 3   | Equiv    | alent circuits of small-signal, low-frequency        |    |

| -   | ampli    |                                                      | 29 |

|     | 3.1      | Common-base equivalent-T circuit                     | 29 |

|     | 3.2      | Common-emitter equivalent-T circuit                  | 29 |

| 3.3  | Measurement of <i>h</i> -parameters from transistor   |    |

|------|-------------------------------------------------------|----|

|      | characteristics                                       | 30 |

| 3.4  | h-parameter equations for a network                   | 31 |

| 3.5  | Calculation of common-emitter amplifier voltage       |    |

|      | gain and input resistance using <i>h</i> -parameters  | 32 |

| 3.6  | Analysis of emitter-follower and common-emitter       |    |

|      | amplifiers using <i>h</i> -parameters                 | 33 |

| 3.7  | Equivalent <i>h</i> -parameter circuit of common-     |    |

|      | emitter amplifier                                     | 34 |

| 3.8  | Voltage and current gains of common-emitter           |    |

|      | amplifier                                             | 35 |

| 3.9  | Equivalent <i>h</i> -parameter circuit of common-base |    |

|      | amplifier                                             | 35 |

| 3.10 | Equivalent <i>h</i> -parameter circuit of two-stage   |    |

|      | common-emitter amplifier                              | 36 |

| 3.11 | Exercises                                             | 37 |

|      |                                                       |    |

| 4 | Trans | istor power amplifiers                        | 40 |

|---|-------|-----------------------------------------------|----|

|   | 4.1   | Amplifier classification                      | 40 |

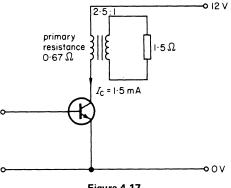

|   | 4.2   | Transformer ratio for power amplifiers        | 40 |

|   | 4.3   | Load-line analysis of power amplifier         | 41 |

|   | 4.4   | Efficiency of class-A power amplifier         | 42 |

|   | 4.5   | Output power, efficiency and distortion of    |    |

|   |       | class-A power amplifiers                      | 43 |

|   | 4.6   | Class-B push-pull amplifier                   | 45 |

|   | 4.7   | Efficiency of class-B push-pull amplifier     | 46 |

|   | 4.8   | Transformerless push-pull amplifier           | 47 |

|   | 4.9   | Equivalent thermal circuit of power amplifier | 47 |

|   | 4.10  | Heat-sink design                              | 48 |

|   | 4.11  | Exercises                                     | 49 |

| 5 | Tune | d circuits and high-frequency transistor amplifiers | 52 |

|---|------|-----------------------------------------------------|----|

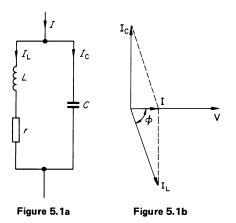

|   | 5.1  | Relationship between <i>Q</i> -factor and bandwidth | 52 |

|   | 5.2  | Tuned-collector amplifier                           | 53 |

|   | 5.3  | Skin effect and dynamic impedance                   | 54 |

|   | 5.4  | Parallel tuned circuit as amplifier load impedance  | 54 |

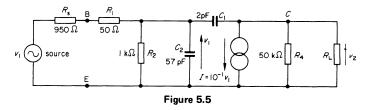

|   | 5.5  | Radio-frequency amplifier                           | 55 |

|   | 5.6  | <i>Q</i> -factor of series tuned circuit            | 55 |

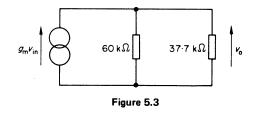

|   | 5.7  | Hybrid- $\pi$ equivalent circuit                    | 56 |

|   | 5.8  | Exercises                                           | 58 |

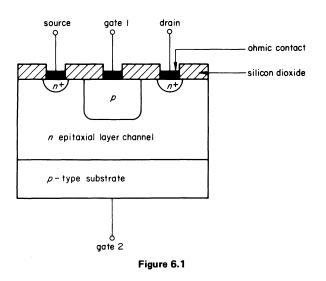

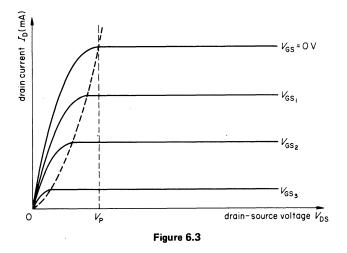

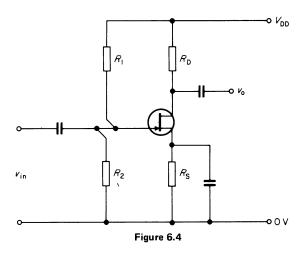

| 6 | Field-     | effect transistors                                                                        | 60         |

|---|------------|-------------------------------------------------------------------------------------------|------------|

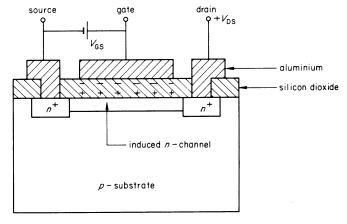

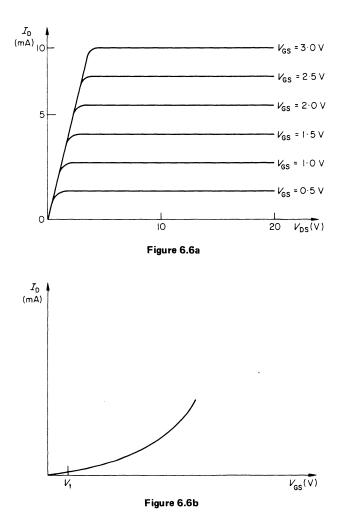

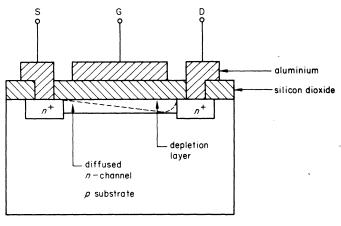

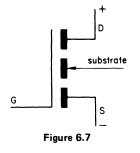

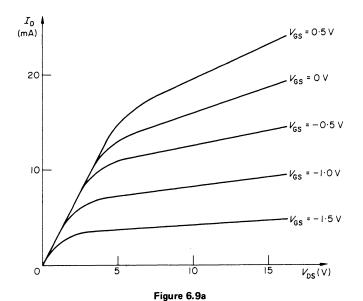

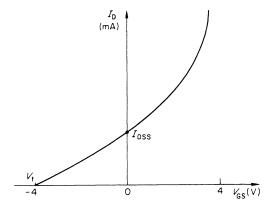

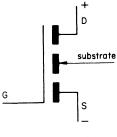

|   | 6.1<br>6.2 | Junction FET and common-source amplifier<br>Depletion and enhancement type insulated gate | 60         |

|   |            | FETs                                                                                      | 61         |

|   | 6.3        | Mutual conductance of an FET                                                              | 63         |

|   | 6.4        | Equivalent circuit of common-source amplifier                                             | 64         |

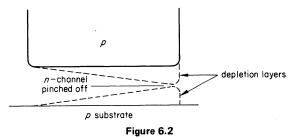

|   | 6.5        | Pinch-off region of junction FET                                                          | 64         |

|   | 6.6        | Voltage gain and input resistance of common-<br>source amplifier                          | 65         |

|   | 6.7        | Voltage gain and upper cut-off frequency of                                               |            |

|   |            | common-source amplifier                                                                   | 66         |

|   | 6.8        | Source-follower amplifier                                                                 | 67         |

|   | 6.9        | Voltage gain of common-drain amplifier                                                    | 68         |

|   |            | Common-gate amplifier                                                                     | 6 <b>9</b> |

|   | 6.11       | Voltage gain, input and output impedances of                                              |            |

|   |            | source-follower                                                                           | 70         |

|   | 6.12       | Exercises                                                                                 | 71         |

| 7 | Negat      | ive feedback                                                                              | 74         |

|   | 7.1        | Gain of amplifier with negative feedback                                                  | 74         |

|   | 7.2        | Effect of negative feedback on amplifier input-                                           |            |

|   |            | impedance                                                                                 | 74         |

|   | 7.3        | Effect of negative feedback on amplifier output-                                          |            |

|   |            | impedance                                                                                 | 75         |

|   | 7.4        | Shunt-series negative feedback                                                            | 76         |

|   | 7.5        | Emitter-follower amplifier                                                                | 77         |

|   | 7.6        | Gain stabilisation by negative feedback                                                   | 78         |

|   | 7.7        | Negative feedback in an integrated-circuit                                                |            |

|   |            | amplifier                                                                                 | 78         |

|   | 7.8<br>7.9 | Instability in feedback amplifier                                                         | 79         |

|   |            | Compound negative feedback                                                                | 80         |

|   | 7.10       | Exercises                                                                                 | 80         |

| 8 | Transi     | stor oscillators                                                                          | 83         |

|   | 8.1        | Amplifier gain with positive feedback                                                     | 83         |

|   | 8.2        | Tuned-collector oscillator                                                                | 83         |

|   | 8.3        | Colpitts oscillator                                                                       | 84         |

|   | 8.4        | Hartley oscillator                                                                        | 85         |

|   | 8.5        | h-parameter analysis of common-emitter                                                    |            |

|   |            | oscillator                                                                                | 86         |

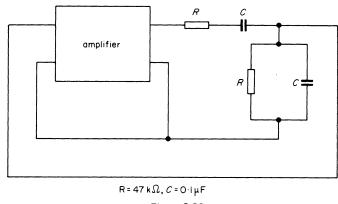

|   | 8.6        | Wien-bridge oscillator                                                                    | 87         |

|   | 8.7        | Phase-shift oscillator                                                                    | 89         |

|   |            |                                                                                           |            |

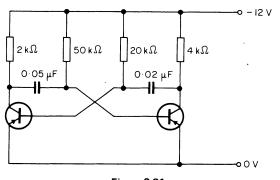

|    | 8.8           | Astable multivibrator                            | 90  |

|----|---------------|--------------------------------------------------|-----|

|    | 8.9           | Astable multivibrator with separate base and     |     |

|    |               | collector supply-voltages                        | 91  |

|    | 8.10          | Blocking oscillator                              | 92  |

|    | 8.11          | Exercises                                        | 93  |

| ~  |               |                                                  |     |

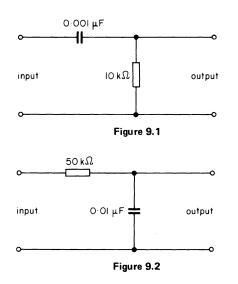

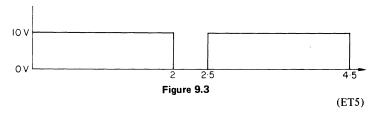

| 9  | Wave-         | shaping and computing circuits                   | 97  |

|    | 9.1           | Differentiating and integrating circuits         |     |

|    | 9.2           | Graphical analysis of RC circuits                | 98  |

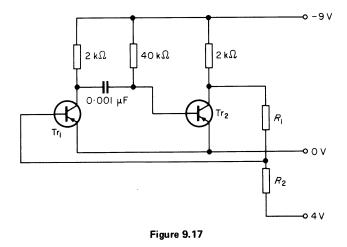

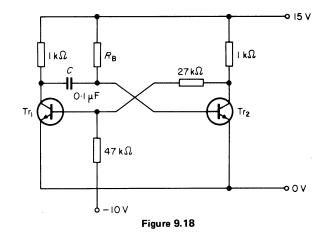

|    | 9.3           | Monostable multivibrator                         | 99  |

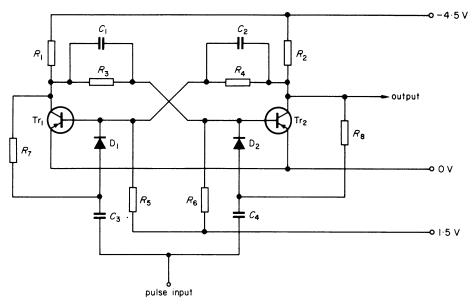

|    | 9.4           | Bistable multivibrator                           | 100 |

|    | 9.5           | Schmitt-trigger circuits                         | 102 |

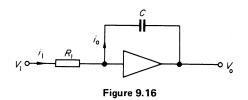

|    | 9.6           | Operational amplifier as an inverter             | 103 |

|    | 9.7           | Operational amplifier as a summer and integrator | 104 |

|    | 9.8           | Exercises                                        | 104 |

|    |               |                                                  |     |

| 10 | Boole         | an algebra and logic circuits                    | 107 |

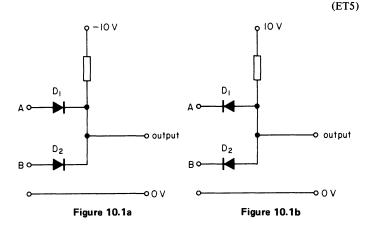

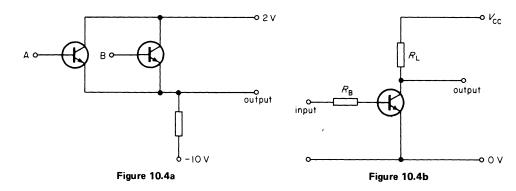

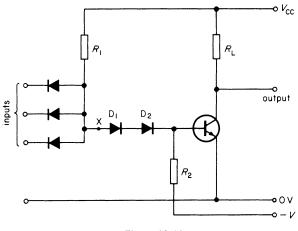

|    | 10.1          | Diode logic gates                                | 107 |

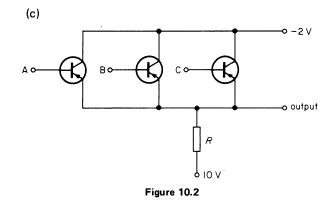

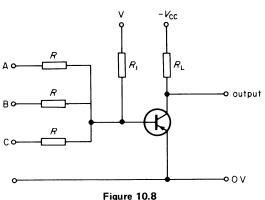

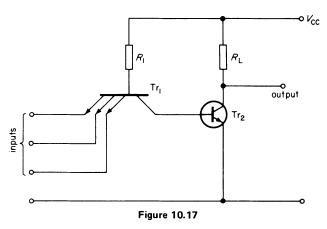

|    | 10.2          | Transistor logic gates                           | 107 |

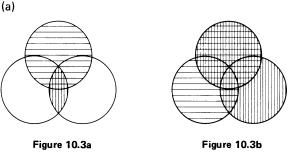

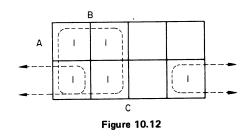

|    | 10.3          | Venn diagrams                                    | 108 |

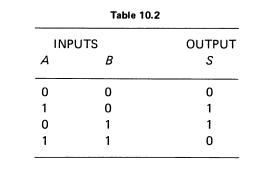

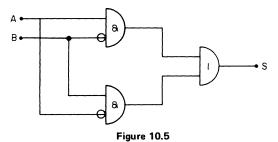

|    | 10.4          | Logic design from truth table                    | 109 |

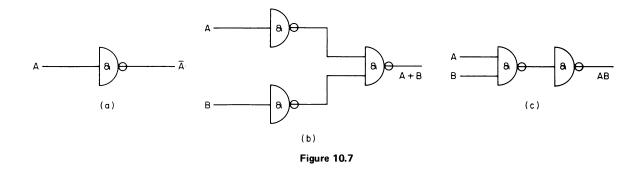

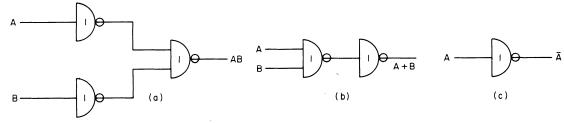

|    | 10.5          | De Morgan's theorems                             | 109 |

|    | 10.6 <i>,</i> | Resistor-transistor logic                        | 110 |

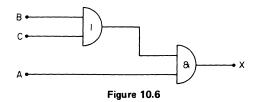

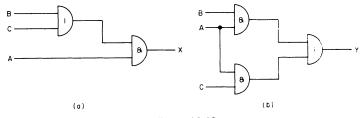

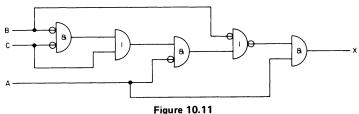

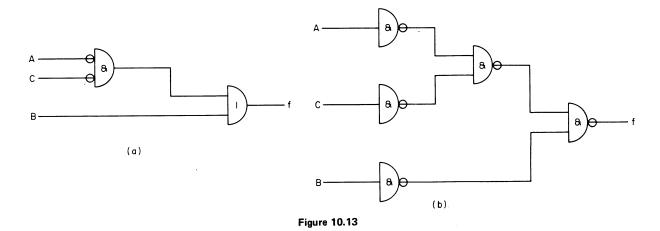

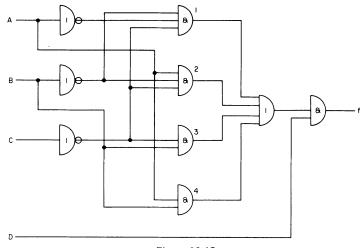

|    | 10.7          | Logic design from Boolean expression             | 111 |

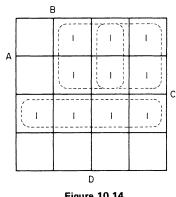

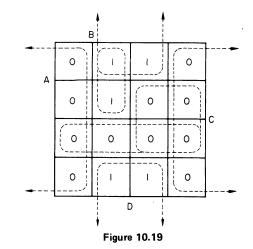

|    | 10.8          | Karnaugh maps                                    | 112 |

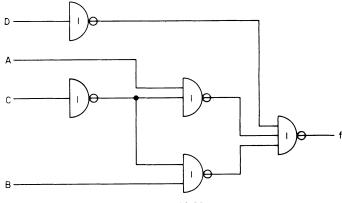

|    | 10.9          | Simplification of Boolean expressions            | 112 |

|    | 10.10         | Diode-transistor and transistor-transistor logic |     |

|    |               | gates                                            | 113 |

|    |               | Use of logic gates                               | 114 |

|    | 10.12         | Exercises                                        | 115 |

|    |               |                                                  |     |

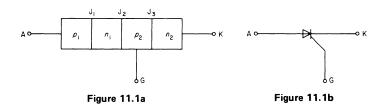

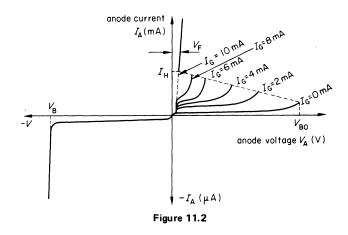

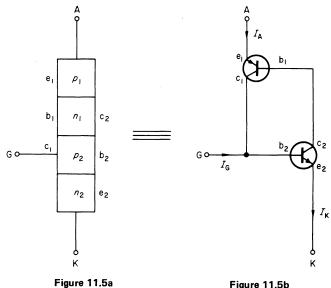

| 11 | Princi | ples and applications of thyristors          | 117 |

|----|--------|----------------------------------------------|-----|

|    | 11.1   | Operation of the thyristor                   | 117 |

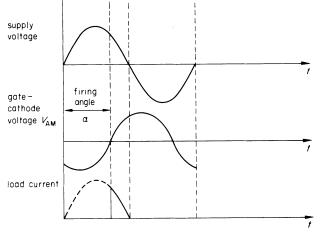

|    | 11.2   | Two-transistor analogy of thyristor and a.c. |     |

|    |        | control of gate                              | 118 |

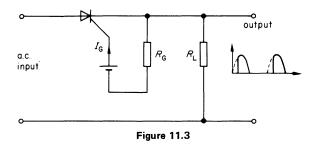

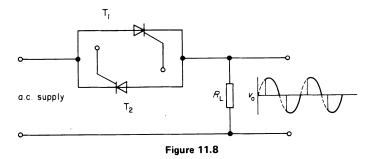

|    | 11.3   | Thyristor inverse parallel a.c. controller   | 119 |

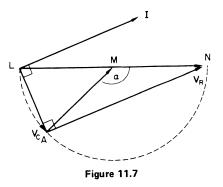

|    | 11.4   | Pulse firing of thyristors                   | 120 |

|    | 11.5   | Thyristor speed control                      | 120 |

|    | 11.6   | Spurious firing of thyristors                | 121 |

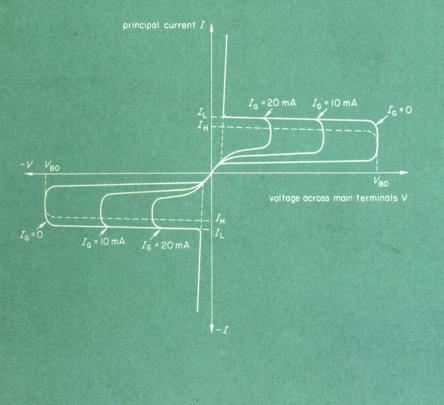

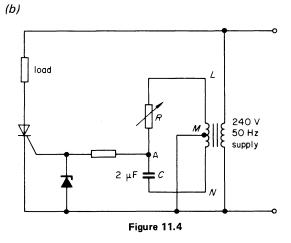

|    | 11.7   | Triac theory and application                 | 122 |

|    | 11.8   | Exercises                                    | 123 |

| 12 | Photoelectric devices and solid-state manufacturing techniques |                                          |     |

|----|----------------------------------------------------------------|------------------------------------------|-----|

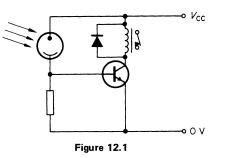

|    | 12.1                                                           | Photoemissive cell and control circuit   | 125 |

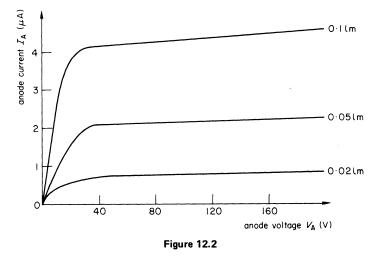

|    | 12.2                                                           | Photoconductive cell and photodiode      | 125 |

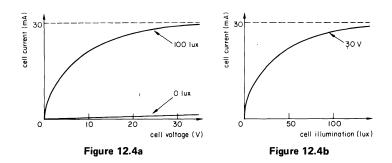

|    | 12.3                                                           | Photovoltaic cell and control circuit    | 127 |

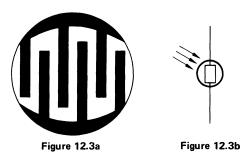

|    | 12.4                                                           | Phototransistor and light-emitting diode | 127 |

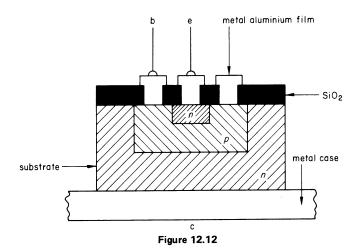

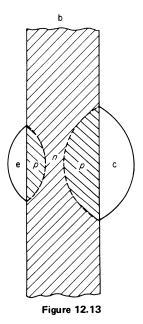

|    | 12.5                                                           | Alloy-junction and planar transistors    | 129 |

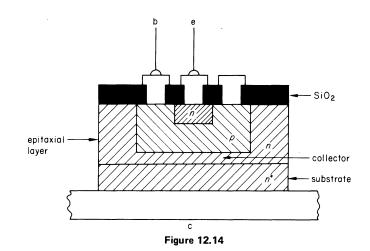

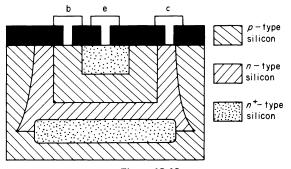

| 12.6  | Construction of planar epitaxial transistor     | 130 |

|-------|-------------------------------------------------|-----|

| 12.7  | Formation of capacitors, resistors, and diodes, |     |

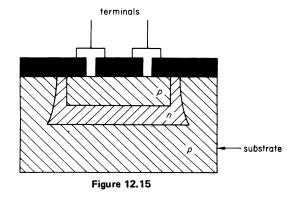

|       | on an integrated circuit                        | 130 |

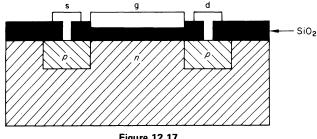

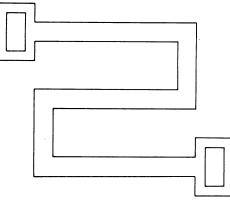

| 12.8  | Enhancement-type MOST and bipolar transistors   | ;   |

|       | in integrated circuits                          | 131 |

| 12.9  | Exercises                                       | 132 |

| Index |                                                 | 134 |

### Preface

The stimulus for this book was provided by two annual requests from students, the first being to recommend a suitable textbook to cover the contents of a given electronics syllabus, and the second to provide tutorial periods which in their opinion provided a successful way of teaching electronic theory and circuits.

As most modern electronics syllabuses cover mainly semiconductor devices, I have attempted to meet both these requests by devoting the contents of this book entirely to the treatment of semiconductor devices and their associated circuitry by means of worked examples, the majority of which are taken from past papers of various examining bodies. Wherever possible, the examples in each chapter have been graded to lead the student through the simpler to the more difficult questions. Both qualitative and quantitative examples are solved and further questions are posed at the end of each chapter for the student to attempt.

The majority of the questions are taken from past examination papers of the City and Guilds of London Institute Electronic Technician Course No. 281, and Telecommunication Technician Course No. 271, the rest being from past examination papers of the Institution of Electrical Engineers, the Institution of Electronic and Radio Engineers, the Union of Lancashire and Cheshire Institutes and Wigan and District Mining and Technical College. In this respect, I would like to thank the boards of the above bodies and the Principal of Wigan and District Mining and Technical College for permitting me to reproduce these problems; the responsibility for the accuracy of the solutions is entirely mine.

Finally, I would like to thank my wife for her encouragement during my preparation of the manuscript and for her subsequent typing of it.

Wigan 1974

F. BROGAN

# Key to source of examination questions

| ET3      | City and Guilds of London Institute Industrial Elec-<br>tronics 1 paper                        |

|----------|------------------------------------------------------------------------------------------------|

| ET4      | City and Guilds of London Institute Industrial Elec-<br>tronics II paper                       |

| ET5      | City and Guilds of London Institute Industrial Elec-<br>tronics III paper                      |

| TT3      | City and Guilds of London Institute Telecommunica-<br>tions course third year                  |

| TT4      | City and Guilds of London Institute Telecommunica-<br>tions course fourth year                 |

| TT5      | City and Guilds of London Institute Telecommunica-<br>tions course fifth year                  |

| U.L.C.I  | Higher National Certificate papers of the Union of<br>Lancashire and Cheshire Institutes       |

| H.N.C.   | Higher National Certificate                                                                    |

| I.E.E.   | Part Three Applied Electronics paper of the Institution<br>of Electrical Engineers             |

|          | <b>.</b>                                                                                       |

| I.E.R.E. | Electronics and Communication papers of the Institu-<br>tion of Electronic and Radio Engineers |

## **1** Semiconductor diodes, rectifiers and stabilisers

#### 1.1 Current conduction in a semiconductor

Explain the differences between intrinsic p-type and n-type conduction in a semiconductor such as germanium.

(ET3)

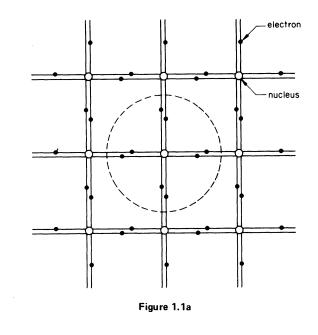

Every atom contains a nucleus of neutrons and positively charged protons. This is surrounded by electrons, which are negatively charged, moving in orbits or shells around the nucleus. Each shell is at a fixed radius from the nucleus and can contain only a fixed number of electrons. The number of electrons in the outer shell of the atom determines whether the atom is a *conductor* or an *insulator*: for if the outer shell contains only a few electrons, these are easily attracted from the atom and the material is therefore a conductor; but if the outer shell is full of electrons, these will not easily be attracted from it, and the material is therefore an insulator. To see what constitutes a *semiconductor*, however, consider the germanium atom, which is a positive nucleus surrounded by 32 electrons.

For any atom

Shell 1 contains2 electronsShell 2 contains8 electronsShell 3 contains18 electronsShell 4 contains18 electrons

The germanium atom will therefore have only 4 electrons in shell 4, and these are termed *valence electrons*.

Figure 1.1a shows that a crystal of germanium is built up by an atom sharing each of its four valence electrons with one valence electron from each of the four neighbouring atoms, so that the central atom now has effectively eight valence electrons. This sharing of two electrons is called a *covalent bond*, and the crystal of germanium is built up from these atoms. In this state the germanium crystal would be an insulator as there are no free electrons. However, the covalent bonds are weak, and the thermal energy that electrons receive at room temperature is sufficient to enable some of them to break free from the bonds and to become free electrons. When such an electron leaves the shell it leaves a gap into which another electron can move, and such a gap is termed a *positive hole*. This explains why the resistance of a semiconductor

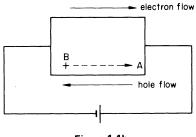

Figure 1.1b

decreases with increase in temperature, that is as temperature increases more covalent bonds break down and more free electrons are provided thereby causing resistance to decrease.

In a semiconductor material the current flow consists of both a movement of electrons and a movement of holes. Electrons can flow towards the positive terminal of the battery, as they normally do in metals, without moving into any positive holes; this is known as *electron motion* or *electron flow*. Some electrons, however, move towards the positive holes. For example in figure 1.1b an electron moving from an atom at B into a hole at A leaves a positive hole at B; so that, although an electron has actually moved from B to A, it appears that the hole has moved from A to B. This is known as *hole motion* or *hole flow*.

#### Doping

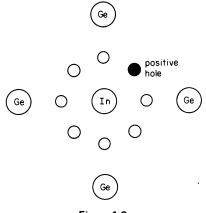

The indium atom has only 3 electrons in its outer shell. If this atom is substituted for one of the germanium atoms in a germanium crystal (as shown in figure 1.2a) then, as it has only 3 electrons to share, a positive hole will appear at the place where the fourth

Figure 1.2a

electron should be. If this is repeated many times, the germanium is said to be *doped* positively and is known as *p*-*type germanium*. (In practice, there is only one impurity atom for every  $10^7$  germanium atoms.)

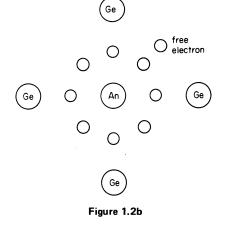

In figure 1.2b an antimony atom, which has 5 electrons in its outer shell, is substituted in place of a germanium atom. Four of

these electrons form covalent bonds and the fifth remains free. If this process is repeated many times, the germanium is said to be doped negatively, and is known as *n*-type germanium.

In a *p*-type material the holes are referred to as *majority carriers*, because there are many more holes than electrons, while electrons are referred to as *minority carriers*. Thus, current flow in a *p*-type material can be considered to consist mainly of a flow of majority carriers which are holes.

Similarly, in *n*-type materials electrons are the majority carriers and holes are the minority carriers. Current flow in *n*-type materials can therefore be considered to consist mainly of a flow of majority carriers which are electrons.

#### 1.2 Junction diode

Describe with a cross-sectional diagram the structure and principle of operation of a junction diode. Mention the materials used and explain why a very high degree of purity is necessary in them. State, with reasons, the effect of excess voltage on a junction diode. (TT2)

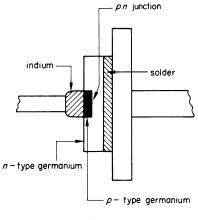

The structure of a *pn*-junction diode is shown in figure 1.3a and its corresponding circuit symbol appears in figure 1.3b.

Figure 1.3a

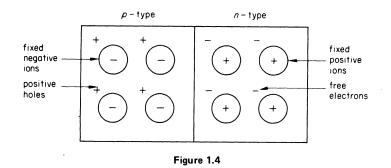

Consider a piece of semiconductor, half of it doped n-type and the other half doped p-type; the initial situation is shown in figure 1.4 with both pieces electrically neutral. When one of the free

Figure 1.3b

electrons moves away from its associated atom, the remaining part of the atom is left relatively positively charged and is then known as a *positive ion* (note that this is fixed in the crystal and cannot move). Similarly, when a hole moves away from its atom in the *p*type material, the remaining part is a fixed *negative ion*. The holes in the *p*-type and the electrons in the *n*-type are known as *majority carriers*.

At room temperature, thermal energy causes the breakdown of some covalent bonds in both the *p*-type and *n*-type materials (as previously described), thereby causing the formation of a few holeelectron pairs in both types of material (note that these are also formed if there are any impurities in the germanium initially). In the *p*-type, the few extra holes produced will be insignificant compared with the millions of holes present already. However, the few electrons do play an important part in current conduction. These few electrons in the *p*-type and the few holes in the *n*-type are known as *minority carriers*.

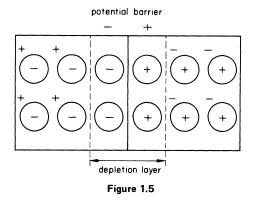

Consider the semiconductor shown in figure 1.4; initially, majority holes from p-type diffuse into n-type and majority electrons from the n-type diffuse into the p-type, and these holes and electrons recombine when they meet. This flow of majority carriers across the junction eventually stops because of the force exerted by the ions near the junction, because the holes and the electrons in a very narrow layer near the junction have all recombined, leaving a row of negative ions on the p-side of the junction and a row of positive ions on the n-side of the junction (as shown in figure 1.5).

These ions form a potential barrier at the junction, known as the junction or *barrier potential*, which prevents the flow of further majority carriers. As there are no majority carriers in this region near the junction, it can be considered to be an insulator. This region is known as the *depletion layer*. (Note that although this junction potential will help the movement of the few minority carriers across the junction, this movement is balanced out by the flow of an equal number of majority carriers in the opposite directions.)

#### Reversed biased pn junction

When the battery is connected as in figure 1.6, it will cause holes in the p-type and electrons in the n-type to move away from the junction, thereby increasing the depletion layer and reinforcing

Figure 1.6

the barrier potential. Thus, no flow of majority carriers can take place across the junction, and the only current that does flow across it consists of the small movement of minority carriers which is aided by the barrier potential. Hence, to ensure that the reverse current flow in a junction diode is small (that is a few  $\mu$ A), the initial semiconductor material should be extremely pure and the temperature should be as low as possible.

#### Forward biased pn junction

With the battery connected as in figure 1.7 it tends to overcome barrier potential, and when it is greater than the barrier potential (that is, between 0.2 and 1.0 V), a large flow of majority carriers

Figure 1.7

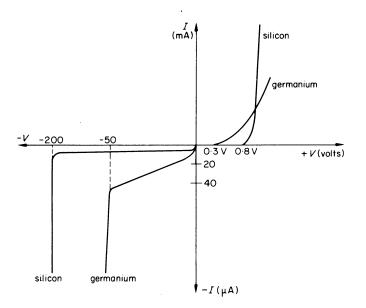

occurs. In practice, the forward voltage-drop across a diode is nearly equal to the barrier potential. As can be seen from figure 1.8, a *silicon* diode normally has a larger forward voltage drop than a *germanium* diode and can normally withstand larger forward currents.

Figure 1.8

In the reverse direction however, the small current through a germanium diode tends to increase with voltage whereas the lower silicon-diode current remains fairly constant with voltage. If the reverse voltage becomes too large however, it accelerates the minority carriers to such a high speed that when they collide with other atoms in the depletion layer they dislodge electrons, thereby causing the formation of other hole-electron pairs. The effect is cumulative and is known as *avalanche breakdown*; it results in destruction of the diode unless the reverse current is limited.

#### 1.3 Full-wave rectifier circuits

Give the meaning of the term 'peak inverse voltage' as applied to the diode in a rectifier circuit. With the aid of suitable wave and circuit diagrams, explain the differences between a full-wave rectifier which uses (a) two diodes; (b) four diodes. In particular mention the transformer required and the peak inverse voltage across the diodes, if the d.c. output voltage is the same in each case. (ET3)

The peak inverse voltage of a diode is the maximum reverse voltage that may be applied across it without reverse breakdown occurring.

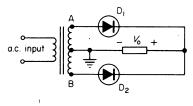

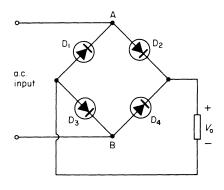

Figure 1.9b

Figure 1.9a is the circuit diagram of a full-wave bi-phase rectifier employing two diodes. This circuit uses a transformer with a centretapped secondary. Assuming a mains input voltage of 240 V, 240 V will be developed across each half of this secondary winding. On the first half cycle of the input voltage, point A goes positive with respect to earth and diode D<sub>1</sub> conducts, thereby passing current down the load. Meanwhile, voltage point B remains negative with respect to earth and D<sub>2</sub> is cut off. At the peak input voltage, the peak inverse voltage across D<sub>2</sub> will be  $2 \times 240\sqrt{2}$  V; that is  $240\sqrt{2}$  V across the lower half of the secondary winding, and  $240\sqrt{2}$  V across the load. Also, the peak forward current through D<sub>1</sub> will be  $240\sqrt{2/R}$  A (where R is the forward resistance of the diode) and the average current will be  $240\sqrt{2/\pi R}$  A.

On the second half cycle of the input voltage, point B will go positive with respect to earth and  $D_2$  will conduct, thereby passing current down the load (that is, in the same direction as during the first half-cycle). Meanwhile, voltage point A will go negative with respect to earth and  $D_1$  will be cut off. Thus, though the conditions of the diodes are reversed the direction of the load current is the same, so that the output voltage is as shown in figure 1.9b.

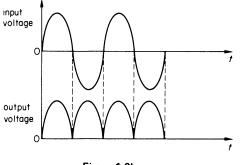

Figure 1.10 is the circuit diagram of a full-wave bridge rectifier employing four diodes. This circuit either uses a 1-to-1 input transformer or can have the mains input-voltage applied directly to its input.

On the first half-cycle, as point A goes positive with respect to earth, current flows in through diode  $D_2$ , down the load, and out through diode  $D_3$ . Meanwhile, diodes  $D_1$  and  $D_4$  are cut off. In this circuit, the peak inverse voltage across diodes  $D_1$  and  $D_4$  is only  $240\sqrt{2}$  V, but the values of the peak forward-current and average current through diodes  $D_2$  and  $D_3$  are the same as the corresponding values in the bi-phase rectifier circuit.

On the second half cycle, as point B goes positive with respect to earth, current flows in through diode  $D_4$ , down the load, and out through diode  $D_1$ . Again, although the conditions of the diodes are reversed, the direction of the load current is the same, and the output voltage is as shown in figure 1.9b.

Thus, the advantages of the bridge rectifier circuit over the biphase rectifier circuit are that it does not require a centre-tapped transformer, and that the peak inverse-voltage across each diode is only half of that existing in the bi-phase rectifier circuit. When semiconductor diodes are employed the bridge rectifier is more commonly used as the cost of the two extra diodes is then not excessive.

#### 1.4 Operation of Zener stabiliser

Briefly explain how the operation of a Zener diode differs from that of a conventional silicon diode.

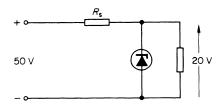

Draw the circuit diagram of a simple Zener-diode stabilisingcircuit and calculate suitable component values to provide a 20 V d.c. stabilised supply to a variable load, from a 50 V d.c. input. A 20 V, 4 W Zener is to be used, whose voltage remains constant down to a diode current of 0.5 mA.

Explain how the circuit stabilises.(a) against supply voltage variations; (b) against load current variations.

Also calculate (c) the maximum and minimum supply voltage between which stabilisation is satisfactory if the load resistance is  $1.5 \text{ k}\Omega$ ; (d) the minimum value of load resistance when the supply voltage is 50 V.

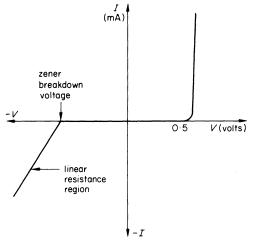

In the forward direction the Zener diode has a similar characteristic to any other silicon diode, with a forward voltage drop of about 0.5 V, as shown in figure 1.11. In the reverse direction however, the Zener diode breaks down at much lower reverse voltages (from about -2 V). This is because the Zener diode is manufactured with a much narrower junction than a normal silicon diode by using an impurity content of only 1 in  $10^5$ . Hence, at relatively small reverse voltages, the electric-field strength across the junction is sufficient to cause electrons to break away from their covalent bonds, thereby giving rise to what is known as *field* emission. Breakdown in a normal silicon diode occurs at much higher voltages, and it is caused by the minority carriers colliding with ions in the depletion layer, thereby releasing more electrons from the covalent bonds, and

Figure 1.11

giving rise to what is termed *avalanche breakdown*. After breakdown, as the voltage across the Zener diode increases only slightly with further increase in current through it, it can subsequently be treated as a linear resistor. Therefore

$$\Delta V_z / \Delta I_z = R_z$$

= slope resistance of Zener

Figure 1.12

The basic Zener-diode voltage-stabiliser circuit is shown in figure 1.12. Consider an open-circuit load; the Zener will then take its maximum current, which is given by

$$I_{max}$$

= Power/Voltage = 4/20 = 1/5 = 200 mA

To stabilise at 20 V from a 50 V input, 30 V must be dropped across  $R_s$  therefore

$$R_{\rm s} = 30/200 \times 10^{-3} = 150 \,\Omega$$

To understand the action of the above circuit, the Zener can be considered to be a *current reservoir* as long as it remains broken down. Its response to supply-voltage and load-current variations is as follows:

(a) When the supply voltage increases, the Zener diode takes the extra current while the increase in voltage appears across  $R_s$ . Similarly, when the supply voltage decreases, the Zener supplies the extra current required by the load and the voltage across  $R_s$  decreases.

(b) When the load current decreases because of increase in load resistance, the Zener current must increase by the same amount. Similarly, when the load current increases because of fall in load resistance, the Zener must shed an equal amount of current to the load.

Figure 1.13

(c) For minimum value of supply voltage, the data requires that the Zener must still pass 0.5 mA. In figure 1.13

therefore

and

$$V_{\rm min} = (13.83 \times 10^{-3} \times 150) + 20 = 22.07 \text{ V}$$

For maximum value of supply voltage, the Zener will pass its maximum current of 200 mA. Therefore

and

$$V_{\rm max} = 0.2133 \times 150 + 20 = 52 V$$

(d) When V = 50 V, minimum value of  $R_L$  occurs when Zener current is 0.5 mA; then

$$I_{\rm s} = 30/150 = 200 \, \rm mA$$

and

/<sub>L</sub> = 199∙5 mA

therefore

$$R_{\rm L} = \frac{20}{199.5 \times 10^{-3}} \approx 100 \ \Omega$$

#### Zener-stabiliser calculations 1.5

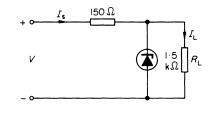

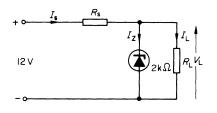

A Zener diode has a reverse breakdown-voltage of 5.8 V and after this can be considered to be a linear resistance of 10  $\Omega$ . It is to be used in a simple voltage stabilising circuit to stabilise the load voltage at 6 V from a 12 V supply. If the load resistor is 2 k $\Omega$ , draw a suitable circuit diagram and calculate the value of the required series resistor. Also determine (a) the change in load voltage, if the supply voltage increases by 10 per cent; (b) the minimum value of load resistor for which stabilisation will still be effective, with a 12 V supply; (c) the minimum value of supply voltage for which stabilisation will still be effective, with a 2 k $\Omega$  load resistor.

In figure 1.14, when  $V_{\rm L}$  = 6 V

$$I_{\rm L} = \frac{6}{2 \times 10^3} = 3 \, {\rm mA}$$

Also

$$V_{\rm L} = V_{\rm B} + I_z R_z$$

where

$V_{\rm B}$  = Zener breakdown-voltage

$R_z$  = Zener slope-resistance

therefore

$$6 = 5 \cdot 8 + I_z 10$$

$$I_z = 0 \cdot 2/10 = 20 \text{ mA}$$

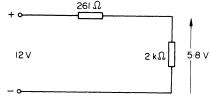

$$R_s = \frac{12 - 6}{(3 + 20)10^{-3}} = \frac{6000}{23} = 261 \Omega$$

(a) When supply voltage increases by 10 per cent to 13.2 V

$$13.2 = (/_{\rm L} + /_{\rm z})261 + 2000 /_{\rm L}$$

(1.1)

Also

....

$$V_{\rm L} = 2000 /_{\rm L} = 5.8 + 10 /_{\rm z}$$

$/_{\rm z} = 200 /_{\rm L} - 0.58$

Substituting for  $I_z$  in equation 1.1

$$13.2 = (/_{L} + 200 /_{L} - 0.58)261 + 2000 /_{L}$$

$$= 52\ 461 /_{L} - 151.4$$

then

$$I_{\rm L} = \frac{164 \cdot 6}{52 \cdot 461} = 3.13 \text{ mA}$$

$V_{\rm L} = 6.26 \text{ V}$

Change in the load voltage is 0.26 V.

(b) the minimum value of load resistance will be when Zener diode just breaks down; that is, when  $V_L$  = 5.8 V and  $I_z$  = 0. Hence, conditions will be as shown in figure 1.15.

$$I_{\rm L} = I_{\rm s} = \frac{12 - 5 \cdot 8}{261} = 23 \cdot 8 \text{ mA}$$

Minimum  $R_{\rm L} = \frac{5 \cdot 8}{(23 \cdot 8) 10^{-3}} = 244 \ \Omega$

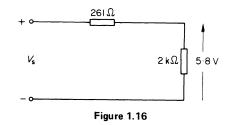

(c) Similarly, for minimum supply-voltage, Zener just breaks down and conditions are shown in figure 1.16.

therefore

$$I_{\rm s} = \frac{5 \cdot 8}{2000} = 2 \cdot 9 \text{ mA}$$

$V_{\rm s} = (261 \times 2 \cdot 9 \times 10^{-3}) + 5 \cdot 8 = 0 \cdot 757 + 5 \cdot 8 = 6 \cdot 557 \text{ V}$

#### 1.6 Other Zener circuits

Explain two distinct uses for a Zener diode other than as a simple stabiliser.

A Zener diode has a reverse characteristic equation V = 10 + 61(V in volts, I in amps) for values of I greater than 5 mA. It is used as a simple stabiliser for a load which can vary between 0 and 200 mA from a d.c. supply of nominal voltage 36 V which may vary by ±6 V. Estimate the maximum value of the series resistor which may be used if the Zener-diode current is not to fall below 5 mA for all input and load conditions. For this value of series resistor determine (a) the minimum power-rating of the Zener diode; (b) the maximum variation in output voltage.

There are three common uses of the Zener diode other than in the simple stabiliser circuit

- (1) as a voltage reference device in transistor stabilisers;

- (2) as a protection device against overload;

- (3) in a clipper circuit.

In (1), a sample of the output voltage is compared with the Zener voltage and the difference between the two is used as the input to a transistor amplifier which is then used to restore the output voltage to its correct level.

In (2), the Zener diode can be used to prevent overloading of sensitive meter movements without affecting meter linearity (see section 1.7).

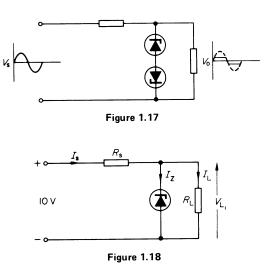

In (3), two identical back-to-back Zener diodes can be used in the circuit configuration shown in figure 1.17 to produce an approximate square-wave from a sine-wave input.

To determine the maximum value of series resistor, the worst conditions of supply voltage and load current must be considered; that is, when the supply voltage is a minimum of 30 V and the load is taking maximum current of 200 mA, the Zener must still pass a current of 5 mA.

Considering figure 1.18

$V_{L_1} = 10 + (6 \times 0.005) = 10.03 \text{ V}$

therefore voltage drop across  $R_s = 30 - 10.03 = 19.97$  V

$$R_{\rm s} = \frac{19.97}{(200+5)10^{-3}} = 97.4 \ \Omega$$

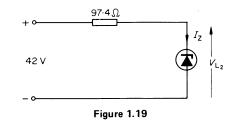

(a) to calculate the minimum power-rating of the Zener diode, the conditions when the Zener diode has maximum.voltage across it and maximum current through it must be considered. This will apply when the load is open circuit and the supply voltage is a maximum of 42 V, as shown in figure 1.19.

From this figure

$$42 = 97.4 /_{z} + (10 + 6 /_{z})$$

$$/_{z} = \frac{32}{103.4} = 309.5 \text{ mA}$$

when

$$V_{L_2} = 10 + (6 \times 0.3095) = 11.857 \text{ V}$$

therefore

minimum power rating =  $VI_z = 3.7$  W

(b) The maximum variation in output voltage will be the change occurring between the two extreme circuit conditions; that is, between minimum supply-voltage with maximum load-current, and maximum supply-voltage with zero load-current. Therefore

maximum variation in output voltage =  $V_{L_2} - V_{L_1}$ = 11.857 - 10.03

= 1.827 V

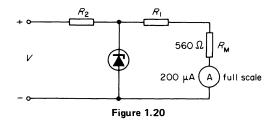

#### 1.7 Zener protection circuit

The circuit shown in figure 1.20 represents a d.c. voltmeter which reads 20 V full scale. The meter resistance is 560  $\Omega$  and  $R_1 + R_2 =$ 99.5 k $\Omega$ . If the diode is a 16 V Zener, find  $R_1$  and  $R_2$  so that when V = 20 V, the Zener diode conducts and the overload current is shunted away from the meter.

When the input voltage is 20 V, the Zener diode just breaks down; that is, the voltage across it will be 16 V but it will not be taking any current. At that time the meter must indicate full-scale deflection. The current through  $R_1$ ,  $R_2$  and the meter will therefore be 200  $\mu$ A. Then

$$R_2 = \frac{20 - 16}{20 \times 10^{-6}} = 20 \text{ k}\Omega$$

$$R_1 = 79.5 \text{ k}\Omega$$

(Check)

$(R_{1} + R_{M}) = 80 \,\mathrm{k}\Omega$

#### therefore

$$(R_1 + R_M) \ge 200 \ge 10^{-6} = 16$$

#### 1.8 Stabilisation ratio of a Zener stabiliser

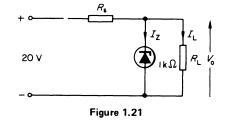

Draw and describe the current/voltage characteristic of a Zener diode. Explain the operation of the voltage-stabiliser circuit shown in figure 1.21 and calculate the value of  $R_s$  if the stabilisation ratio is to be 0.005. What would be the effect of doubling  $R_s$ ? The dynamic resistance of the diode, beyond its breakdown voltage of 6 V, is 10  $\Omega$ .

The first part of this question is answered in section 1.4. Stabilisation ratio

$$S = \frac{\text{small change in output voltage}}{\text{small change in input voltage}} = \frac{\Delta V_0}{\Delta V_1}$$

for constant value of load resistor. From figure 1.21

$$V_1 = (I_L + I_z)R_s + V_0$$

(1.2)

Current flowing through the Zener,  $I_z$ , is given by

$$I_z = \frac{V_0 - V_z}{R_z}$$

where  $V_z$  = Zener breakdown voltage. Also, current through the load,  $I_L = V_0/R_L$ . Substituting these values of  $I_z$  and  $I_L$  in equation 1.2

$$V_{1} = \left(V_{0}/R_{L} + \frac{V_{0} - V_{2}}{R_{z}}\right)R_{s} + V_{0}$$

$$V_{1} = V_{0}(1 + R_{s}/R_{L} + R_{s}/R_{z}) - \frac{V_{z}R_{s}}{R_{z}}$$

To calculate the approximate effect of a change in the input voltage, it may be assumed that  $V_z$  is constant and that  $R \ll R_L$ , so that  $R_s/R_L$  may be neglected compared with  $R_s/R_z$ . Then, considering small changes of voltage

$$\Delta V_1 \approx \Delta V_0 (1 + R_s/R_z)$$

$$S = \Delta V_0 / \Delta V_1 = \frac{R_z}{R_s + R_z}$$

(1.3)

Substituting the values given

$$0.005 = \frac{10}{R_s + 10}$$

therefore

$$0.005 R_{s} + 0.05 = 10$$

$R_{s} = \frac{9.95}{0.005} = 1.99 \text{ k}\Omega$

From equation 1.3, if  $R_s$  is doubled, as it is large compared with  $R_z$ , the stabilisation ratio S will be halved, which doubles the effectiveness of the circuit.

#### 1.9 Voltage-doubling circuit

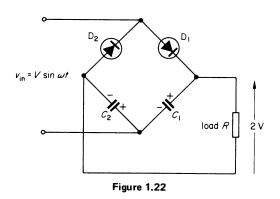

With the aid of a circuit diagram, describe the action of a voltagedoubler circuit using capacitors and diodes.

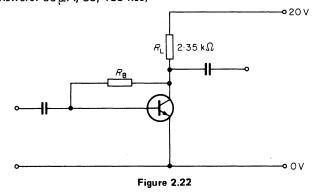

Considering figure 1.22, on the positive half-cycle of the input voltage,  $C_1$  will charge up through  $D_1$  to a voltage V volts, which is the maximum value of the a.c. input voltage. Similarly, on the

negative half-cycle of the input voltage,  $C_2$  charges through  $D_2$  to a voltage V volts. After one cycle of input voltage, the voltage across the load resistor R will be 2 V volts. However, this assumes that the capacitors do not discharge through R in the time when they are not being charged. This circuit is only effective for very high load-resistor values, and its regulation deteriorates rapidly at low values of R. The peak inverse voltage across the diodes in this circuit will be 2 V volts.

#### 1.10 Voltage-quadrupling circuit

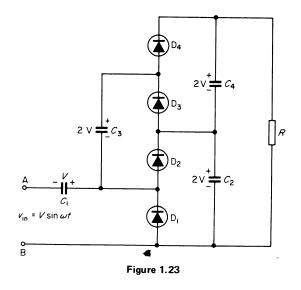

Give a circuit diagram of a voltage-quadrupler circuit employing diodes and capacitors. Describe the action of the circuit, stating its limitations, and suggest one practical use of it.

(H.N.C.)

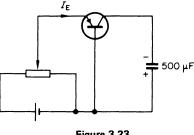

Figure 1.23 shows the circuit diagram of a voltage-quadrupler circuit. The main limitation on this circuit to ensure its effective operation, is that the load should take negligible current. To explain the operation of the circuit, it will be assumed that the load is a very high value, so that the capacitors do not discharge through it.

On the first half-cycle of supply voltage,  $C_1$  charges through  $D_1$  to V volts. On the second half-cycle,  $C_2$  charges through  $D_2$  to 2 V volts, due to supply voltage and the voltage across  $C_1$ . On the third half-cycle,  $C_3$  charges through  $D_3$  to 2 V volts due to supply volt-

(ET3)

age, voltage across  $C_2$  minus the voltage across  $C_1$ . On the fourth half-cycle,  $C_4$  charges through  $D_4$  to 2 V volts due to supply voltage, voltage across  $C_1$ , voltage across  $C_3$  minus the voltage across  $C_2$ . Therefore after two cycles of input voltage, the voltage across the load will be 4 V volts.

This circuit could be used for the E.H.T. supply in a television receiver where the current requirement is very small. In practice the circuit can be extended to give multiplication factors up to approximately 10.

#### 1.11 Exercises

#### Exercise 1.1

Explain the construction of a germanium *pn*-junction diode and how it functions as a rectifier.

Show, with the aid of sketches, any differences between the current/voltage characteristics of a germanium diode and a vacuum diode valve. Comment on the shape of the characteristic.

(ET3)

#### Exercise 1.2

Give the circuit diagram of a rectifier bridge circuit and add wave diagrams to show how it operates. How does the transformer supplying the bridge-rectifier circuit differ from that required for a full-wave rectifier using two diodes? State what is meant by *peak inverse voltage* and calculate its value in the circuit you have drawn, if the transformer secondary voltage is 20 V r.m.s. (Answer: 28:3 V) (ET3)

#### Exercise 1.3

A Zener diode has a breakdown voltage of 5 V and after this can be considered to have linear resistance of 25  $\Omega$ . It is to be used in a voltage-stabilising circuit to provide a load voltage of 5.5 V. If the supply voltage is 9 V and the load resistor is 1.1 k $\Omega$ , draw the circuit diagram and calculate the value of series resistor required. Also determine (a) the change in load voltage, if the supply voltage increases by 10 per cent; (b) the minimum value of supply voltage for which stabilisation will still be effective, with a 1.1 k  $\Omega$  load; (c) the minimum value of load resistor for which stabilisation will still be effective, with a 9 V supply.

(Answers: 140  $\Omega$ , 0.13 V, 5.64 V, 175  $\Omega$ ) (ET3)

#### Exercise 1.4

Explain, with the aid of a suitable characteristic, how the operation of a Zener diode differs from that of a rectifying diode.

The following data apply to a Zener diode nominal voltage at 5 mA = 9 V maximum slope-resistance at 5 mA = 10  $\Omega$ characteristic linear above 0.5 mA.

Sketch a circuit diagram showing how this diode may be employed to supply a load of 15 mA at an almost constant voltage of 9 V from a d.c. source of 24 V (nominal).

Explain how the circuit stabilises (a) against supply-voltage variations; (b) against load-current variations.

Calculate the load voltage variation when the supply voltage varies by 2 V. What are the advantages of Zener diodes over gas stabilising-valves? (Answer: 0.03 V) (ET5)

#### Exercise 1.5

A Zener diode and one resistor are joined in series to provide a 16 V stabilised output from a 20 V supply. If the load resistor is 200  $\Omega$  and the current through the stabiliser is 8 mA, determine the value of the series resistor and the power dissipated in it.

If the load is increased to 250  $\Omega$ , the output voltage rises to 16·2 V. Determine the current which then flows through the stabiliser diode, the power dissipated in it and its slope resistance, given that the Zener breakdown voltage is 15·9 V. (Answers: 45·5  $\Omega$ , 352 mW, 20·9 mA, 338 mW, 14·3  $\Omega$ )

#### Exercise 1.6

Explain, with the aid of a suitable characteristic, how the operation of a Zener diode differs from that of a rectifying semiconductordiode.

A 56 V, 8 W Zener is to be used to supply a variable load from a nominal 100 V d.c. source. Design a suitable circuit so that the Zener diode is not overloaded under any load conditions if the source voltage is 100 V. Explain how the circuit stabilises (a) against supply-voltage variations; (b) against load-current variations. If the diode can be assumed to stay constant down to a diode current of 1 mA, estimate (i) the maximum and minimum supply voltage between which stabilisation is satisfactory if the load resistance is 560  $\Omega$ ; (ii) the minimum value of load resistance when the supply voltage is 100 V.

Exercise 1.8

(Answers:  $R_{\rm s}$  = 308  $\Omega$ , 130·8 V, 87·1 V, 395  $\Omega$ ) (ET5)

#### Exercise 1.7

Explain two distinct uses for a Zener diode other than as a simple stabiliser.

A Zener diode has a reverse characteristic equation V = 9.1 +5.01/ (V in volts, / in amps) for values of / greater than 0.01 A. It is used as a simple stabiliser for a load which can vary between 0 and 150 mA from a d.c. supply of nominal voltage 25 V which may vary by  $\pm 5$  V.

Estimate the maximum value of the series resistor which may be used if the Zener-diode current is not to fall below 0.01 A for all input and load conditions. For this value of series resistor, determine (a) the minimum power rating of the Zener diode; (b) the maximum variation in output voltage. (Answers: 67·8 Ω, 3 W, 1·385 V)

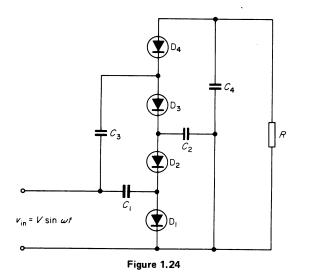

Figure 1.24 shows an alternative form of voltage-quadrupler circuit. Describe its operation.

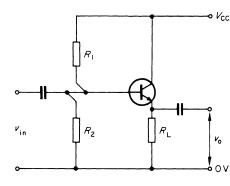

# **2** Voltage and current common-emitter amplifiers

#### 2.1 Load line; dissipation, current gain, and input resistance

The characteristics of a pnp transistor (assumed to be linear over the given range) are tabulated below. It is used in the commonemitter mode with a resistive load of  $2 \text{ k}\Omega$  and a supply voltage of 10 V. Estimate, using a load line (a) the total power dissipated in the circuit under quiescent conditions when the base is biased to  $-50 \text{ }\mu\text{A}$ ; (b) the amplifier current gain; (c) the a.c. input resistance if the voltage gain is 80. Briefly state how a reduction in load resistance would affect your answers to (a) and (b).

| Base current |      | rent (mA) for<br>voltages of |

|--------------|------|------------------------------|

| (μΑ)         | -2 V | -8 V                         |

| -20          | -0.9 | -1·5                         |

| -40          | -1·8 | -2·55                        |

| -60          | -2·8 | -3·85                        |

| -80          | -3.9 | —5·1                         |

The load line equation is

$$V_{\rm CC} = I_{\rm C} R_{\rm L} + V_{\rm C} \tag{2.1}$$

where

$V_{\rm CC}$  = the supply voltage

$I_{C}$  = collector current

$V_{\rm C}$  = collector potential

$R_{\rm L}$  = load resistor

To fix the two points on the load line which lie on the axes of the graph, use equation 2.1 as follows when

when

$V_{\rm C} = 0, \qquad V_{\rm C} = V_{\rm CC} = 10 \text{ V}$

when

۱

$$V_{\rm C} = 0, \qquad V_{\rm C} = \frac{V_{\rm CC}}{R_{\rm L}} = \frac{10}{2 \times 10^3} = 5 \text{ mA}$$

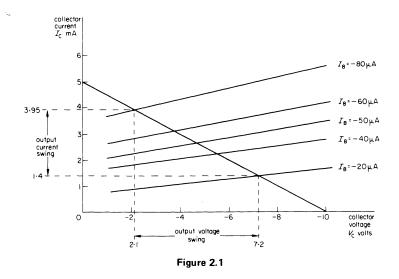

Hence the load line can be superimposed on the characteristics as shown in figure 2.1. The characteristic for a base current of  $-50 \,\mu\text{A}$  is drawn by taking the mean of those for base currents of  $-40 \text{ and } -60 \,\mu\text{A}$ . At a collector voltage of -2 V the collector current will be -2.3 mA, and at a collector voltage of -10 V the collector current will be -3.5 mA.

(a) From the characteristics and the load line, the quiescent collector current  $I_Q$  is 2.7 mA. Therefore, total power dissipated in the circuit under quiescent conditions is

$$V_{\rm CC}/_{\rm O} = 10 \text{ x } 2.7 \text{ x } 10^{-3} = 27 \text{ mW}$$

(b) From the characteristics and load line for an input basecurrent swing of 60  $\mu$ A, the collector current varies from 1.4 to 3.95 mA. Therefore current gain

$$A_{i} = i_{o}/i_{in} = \frac{2 \cdot 5 \times 10^{3}}{60 \times 10^{-6}} = \frac{2550}{60}$$

= 42.5

(c) Voltage gain

$$A_{v} = v_{o}/v_{in} = \frac{i_{0}R_{L}}{i_{in}R_{in}}$$

where

$R_{in}$  = input resistance of the amplifier

therefore

$$A_{v} = A_{i} \frac{R_{L}}{R_{in}}$$

$$80 = 42.5 \times \frac{2000}{R_{in}}$$

$$R_{in} = \frac{42.5 \times 2000}{80} = 1.06 \text{ k}\Omega$$

$$I_{c}$$

$$I_{q}$$

$$I$$

As can be seen from figure 2.2, if load was reduced to  $1 k\Omega$ , then the point on the collector-current axis would move up to 10 mA. Therefore the quiescent current in part (a) would increase and so would the power dissipation.

Similarly, the output-current swing, for the same input-current swing, would increase; and hence, in part (b), the current gain would also increase.

#### 2.2 Load line; voltage, current, and power gains

A pnp transistor has the following characteristics which may be assumed to be linear between the values of collector voltage given

| Base current | Collector curre<br>collector vo |       |

|--------------|---------------------------------|-------|

| (μΑ)         | -1 V                            | -6 V  |

| -20          | -0.9                            | -1·27 |

| -40          | 1·9                             | -2·4  |

| 60           | -3·0                            | -3·65 |

| -80          | -4.0                            | -4·79 |

The transistor is used as a common-emitter type amplifier with a load resistor of  $1.5 \text{ k}\Omega$  and a collector supply of 7.5 V. The a.c. input resistance may be taken as  $1.25 \text{ k}\Omega$ . Determine the voltage gain, current gain and power gain, when an input current of  $30 \mu \text{A}$ peak varies sinusoidally about mean value of  $50 \mu \text{A}$ .

If this transistor were used as a common-base type amplifier with the same load resistor and supply voltage, what values of the voltage gain, current gain, power gain and input resistance would be expected?

Hence explain why the common-base circuit is not used for multi-stage RC-coupled amplifiers.

The load-line equation is  $V_{CC} = I_C R_L + V_C$  (as in section 2.1), which enables the points on the two axes to be determined. When

$$V_{\rm C} = 0$$

,  $V_{\rm C} = V_{\rm CC} = -7.5 \,\rm V$

when

ν

$$V_{\rm C} = 0, \qquad I_{\rm C} = \frac{V_{\rm CC}}{R_{\rm L}} = \frac{7.5}{1.5 \times 10^3} = 5 \text{ mA}$$

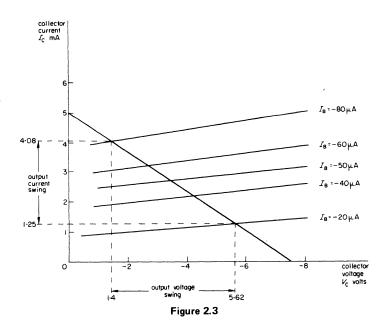

The characteristic for a base current of  $-50 \,\mu\text{A}$  can again be drawn by taking the mean of the ones corresponding to base currents of -40 and  $-60 \,\mu\text{A}$ . The load line can be superimposed

on the characteristics as shown in figure 2.3. From figure 2.3, output-voltage swing  $v_0$  is 4.22 V. The input-voltage swing  $v_{in}$  is  $i_b r_{in}$ , where  $i_b$  is the base-current swing, and  $r_{in}$  is the a.c. input resistance of the amplifier.

Therefore

$$v_{in} = 60 \times 10^{-6} \times 1.25 \times 10^3 = 75 \text{ mV}$$

voltage gain  $A_v = \frac{v_o}{v_{in}} = \frac{4.22}{75 \times 10^{-3}} = 56.3$

From figure 2.3, output-current swing  $i_0$  is 2.83 mA. Input basecurrent swing  $i_{in}$  is 60  $\mu$ A

therefore

current gain

$$A_{L} = \frac{i_{o}}{i_{in}} = \frac{2 \cdot 83 \times 10^{-3}}{60 \times 10^{-6}} = 47 \cdot 2$$

power gain  $A_{p} = v_{o}i_{o}/v_{in}i_{in} = A_{v}A_{i}$

$= 56 \cdot 3 \times 47 \cdot 2$

$= 2657$

If this transistor were used in a common-base amplifier with the same load resistor and supply voltage, the voltage gain would be of similar value (that is, approximately 50). However, as the current gain of the common-base amplifier is approximately 0.95 to 0.98, the power gain would be of the order of 45. Also the input resistance is very low, at approximately 30 to 100  $\Omega$ .

Hence, the common-base circuit is unsuitable for multistage amplifiers because its current and power gains are low when compared with the corresponding common-emitter values. Also its low input resistance seriously shunts the load resistor of the previous stage, thereby reducing the output voltage from that stage and causing a corresponding fall in overall gain.

#### 2.3 Amplifier with fixed bias

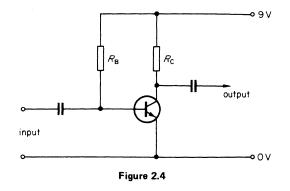

The circuit shown in figure 2.4 is that of a simple transistor amplifier. Estimate the value of the collector load-resistor  $R_c$  and the bias resistor  $R_B$ , if the mean (quiescent) d.c. collector current and voltage values are 9.2 mA and 4.4 V respectively. The transistor has a d.c. current gain of 115 and  $V_{BE}$  is 0.7 V.

To improve the d.c. stabilisation of the circuit the bias is to be obtained by returning the bias resistor to the collector. Draw a circuit diagram to show how this can be done without introducing unwanted a.c. feedback. Calculate suitable values for the components required and compare the relative merits of this method of d.c. stabilisation with other methods. (ET5)

Voltage drop across  $R_C = 9 - 4.4 = 4.6$  V therefore

$$R_{\rm C} = \frac{4.6}{9.2 \times 10^{-3}} = 500 \ \Omega$$

Base potential = 0.7 V

therefore

voltage drop across  $R_{\rm B} = 9 - 0.7 = 8.3 \text{ V}$

Base current

$$I_{\rm B} = I_{\rm C} / h_{\rm FE} = \frac{9 \cdot 2 \times 10^{-3}}{115} = 80 \,\mu \text{A}$$

therefore

$$R_{\rm B} = \frac{8.3}{80 \times 10^{-6}} = 103.8 \,\rm k\Omega$$

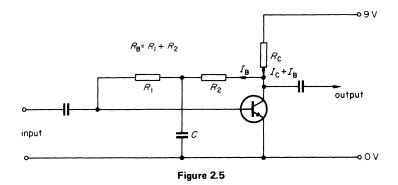

Assuming the values of base and collector currents in figure 2.5 to be the same as those in figure 2.4

collector potential  $V_{\rm C} = 9 - (/_{\rm C} + /_{\rm B})0.5$ = 9 - (9.28 x 0.5) = 4.36 V voltage drop across  $R_{\rm B} = 4.36 - 0.7$ = 3.66 V

therefore

$$R_{\rm B} = \frac{3.66}{80 \times 10^{-6}} = 45.8 \, \rm k\Omega$$

The capacitor C has to provide a low-resistance path to earth for the a.c. feedback component. If  $R_1$  (which shunts  $R_L$ ) is small, it seriously reduces the effective collector load-resistance. Similarly, a small  $R_2$  reduces the input resistance of the amplifier. Usually therefore,  $R_1$  and  $R_2$  are made approximately equal, and the capacitor is chosen so that its reactance at the lowest signalfrequency is small compared with the resistance value. In this example,  $R_1$  and  $R_2$  would each be approximately 23 k $\Omega$ . A 4  $\mu$ F capacitor could then be chosen, as it would have a reactance of approximately 800  $\Omega$  at a signal frequency of 50 Hz.

Two alternative methods of stabilisation are

(1) the use of a decoupled emitter-resistor alone (see section 2.4)

(2) the use of a decoupled emitter-resistor together with potential-divider stabilisation (see section 2.6).

Both the collector-base resistor method used in this example and the decoupled emitter-resistor method are equally effective, but the latter method involves using one extra resistor (the emitter-resistor). In both uses, the value of the bias resistor  $R_B$  is determined by the required base current. When potential-divider stabilisation is used however, a bleed current as well as the base current flows through the upper bias-resistor, and this widens the choice of resistor value. This is the best method of stabilisation and is the most used in practical amplifier circuits.

#### 2.4 Amplifier with emitter resistor

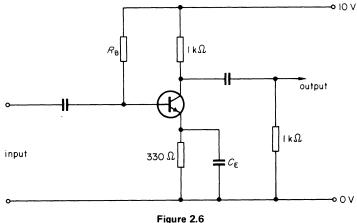

Explain why the circuit of figure 2.6 gives better d.c. stability than one in which the emitter is connected directly to the 0 V line.

The transistor used has negligible leakage current at room temperature and a d.c. current gain ( $h_{\rm FE}$ ) of 100. Under quiescent

conditions the collector current is 4 mA and  $V_{BE}$  is 660 mV. Determine a suitable value for R <sub>B</sub>.

If the amplifier a.c. current gain  $(A_i)$  is 90 and the a.c. input resistance is 800  $\Omega$ , calculate the voltage gain, assuming that all capacitors have negligible reactance at the working frequency of operation.

Explain briefly what the effect would be of removing  $C_{\rm E}$  from the circuit.

Figure 2.0

In the circuit of figure 2.4, in which the emitter is connected directly to the 0 V line, the quiescent point is fixed by the base current flowing through  $R_{\rm B}$ . If the base-emitter voltage drop is negligible, then the value of the base current can be calculated from  $I_{\rm B} = V_{\rm CC}/R_{\rm B}$ .

However, if the *temperature* of the transistor increases, the leakage current also increases, thereby changing the values of collector current, collector voltage, and base current; for d.c. collector current =  $I_{\rm C} + I_{\rm CO}'$  (where  $I_{\rm C}$  is the component due to the amplifying action on the base current  $I_{\rm B}$ , and  $I_{\rm CO}'$  is the leakage current), and d.c. base current =  $I_{\rm B} - I_{\rm CO}'$ . Hence, with increase in leakage current, the total collector current increases and the total base current decreases.

These changes cause the operating point of the amplifier to drift, and this can distort the output voltage. In power amplifiers, the increase in collector current can cause a further increase in temperature, which again increases the leakage current, thus producing a cumulative effect that can lead to the eventual destruction of the transistor, and is known as *thermal runaway*. When the emitter resistor is employed, as shown in figure 2.6, any increase in collector current produces an increase in emitter current, which thereby causes a larger voltage drop across the emitter resistor  $R_E$ . This reduces the forward bias voltage  $V_{BE}$ , reducing the collector current and restoring it very nearly to its original value. This reasoning applies equally well to variations in collector current gain of the transistor. Thus, the circuit of figure 2.6 gives better d.c. stability than the one in which  $R_E$  is connected directly to the 0 V line.

In the circuit of figure 2.6, the emitter current  $I_{\rm E}$  is given by

$$l_{\rm E} = \frac{(h_{\rm FE} + 1)l_{\rm C}}{h_{\rm FE}}$$

=  $\frac{101 \times 4 \times 10^{-3}}{100}$  = 4.04 mA

emitter voltage = 4.04 x 10^{-3} x 330

= 1.33 V

base voltage = 1.33 + 0.66

$\approx 2 V$

therefore voltage drop across  $R_{\rm B}$  is 8 V

base current

$$I_{\rm B} = I_{\rm C} / h_{\rm FE} = \frac{4 \times 10^{-3}}{100} = 40 \,\mu \text{A}$$

therefore

$$R_{\rm B} = \frac{8}{40 \times 10^{-6}} = 200 \,\rm k\Omega$$

output voltage  $v_0 = i_c R_L$

where

$R_{\rm L}$  = load resistor

$R_{in}$  = a.c. input resistance of the amplifier

$i_c$  = a.c. collector current

$$i_{\rm b}$$

= a.c. base current

therefore

voltage gain

$$A_V = v_o/v_{in} = \frac{l_c R_L}{l_b R_{in}}$$

$$= \frac{A_i R_L}{R_{in}} = \frac{90 \times 500}{800}$$

$$= 56.25$$

(*Note*:  $R_L$  comprises the 1 k $\Omega$  load resistor and the parallel output resistor of 1 k $\Omega$ ; that is, 500  $\Omega$ .)

If  $C_{\rm E}$  were removed, an a.c. voltage would be developed across  $R_{\rm E}$  and this would oppose the a.c. input voltage to the transistor. Therefore the net a.c. base-emitter voltage would fall and so would the a.c. output voltage, thereby effectively reducing the voltage gain of the amplifier. This effect is known as *negative feedback*.

#### 2.5 Amplifier with collector-base resistor

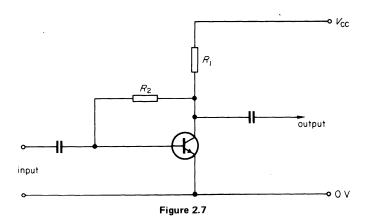

What is meant by the expression 'stabilisation of the operating point' when used in conjunction with a common-emitter connected transistor amplifier? Explain how d.c. stability is obtained in the amplifier circuit shown in figure 2.7.

The circuit is modified by connecting a resistor in series with the emitter and increasing the supply voltage so that the value of quiescent base current is unchanged. State how the following amplifier properties will alter (i) d.c. stability; (ii) voltage gain; (iii) input and output a.c. resistances.

Stabilisation of the operating point implies maintaining the d.c. conditions in the amplifier as constant as possible, when supply voltage, temperature, transistor d.c. current gain, or any other parameter, varies.

In figure 2.7, if the collector current increases because of change in any of the above mentioned parameters, the collector voltage  $V_{\rm C}$  will fall. Therefore, the d.c. base current  $I_{\rm B}$  will fall (as  $I_{\rm B} = V_{\rm C}/R_2$ ; neglecting the base-emitter voltage  $V_{\rm BE}$ ). Hence, the collector current  $I_{\rm C}$  (that is,  $h_{\rm FE}I_{\rm B}$ ) will also fall towards its original value. Similarly, if  $I_{\rm C}$  decreases,  $V_{\rm C}$  and  $I_{\rm B}$  will rise, so that  $I_{\rm C}$  then rises to offset the original decrease. Thus, the operating point has been stabilised.

If a resistor is connected in series with the emitter

(i) d.c. stability will be improved because of the d.c. negative feedback;

(ii) voltage gain will be decreased because of the a.c. negative feedback;

(iii) input and output a.c. resistances will both decrease.

#### 2.6 Amplifier with potential-divider stabilisation

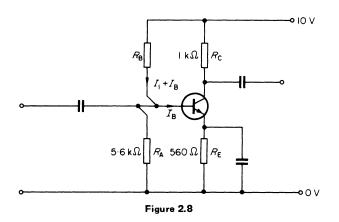

Explain why stabilisation of the operating point is necessary in a transistor amplifier and how it is achieved in the circuit shown in figure 2.8.

The input characteristics of the silicon transistor used in the circuit of figure 2.8 are shown in the graph of figure 2.9. Under quiescent operating conditions, the d.c. voltage across  $R_E$  is  $3 \cdot 5 \text{ V}$  and the base current is  $30 \mu$ A. Assuming zero leakage current, estimate the value of  $R_B$ . Calculate the voltage gain of the stage, assuming that it is coupled to an identical stage via a capacitor of negligible impedance, that  $R_E$  is adequately decoupled, and that the a.c. and d.c. current gains are the same.

(ET5)

The necessity for stabilisation of the operating point in a transistor amplifier has been dealt with in the first part of section 2.4.

In the amplifier shown in figure 2.8, which employs potentialdivider and emitter-resistor stabilisation, the values of  $R_{\rm B}$  and  $R_{\rm A}$ are chosen such that the total current flowing through them is very much larger than the d.c. base current of the transistor (usually by a factor of 10). Thus variations in d.c. base current arising from change in leakage current have little effect on the d.c. conditions.

The effect of the emitter resistor  $R_{\rm E}$  is to compensate for any change in d.c. collector current (that results from leakage current change, supply voltage variations, etc.) by producing a change in transistor drive-voltage  $V_{\rm BE}$ , and thereby restoring the collector current towards its original value (as discussed in section 2.4).

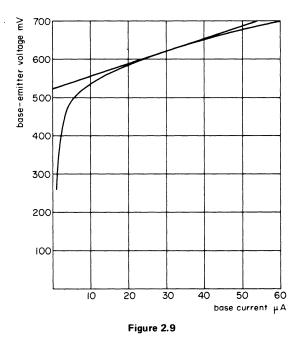

From figure 2.9, when  $I_B = 30 \mu A$ ,  $V_{BE} = 625 \text{ mV}$

therefore

voltage at the junction of  $R_A$  and  $R_B = 3.5 + 0.625$ = 4.125 V

$l = \frac{4.125}{5.6 \times 10^3} = 0.737 \text{ mA}$

current through

$$R_{\rm A}$$

therefore

$$R_{\rm B} = \frac{10 - 4.125}{/+/_{\rm B}} = \frac{5.875}{767 \times 10^{-6}}$$

$$= 7.7 \text{ k}\Omega$$

The transistor d.c. current gain

$$h_{\rm FE} = I_{\rm C}/I_{\rm B} \approx I_{\rm E}/I_{\rm B}$$

$I_{\rm E} = 3.5/560 = 6.25 \,{\rm mA}$

therefore

$h_{\rm FE} = 6250/30 = 208$

To determine the transistor a.c. input resistance  $h_{ie}$ , a tangent is drawn on figure 2.9 at the point corresponding to a d.c. base current of  $30 \mu A$ .

$$h_{ie} = \frac{\text{change in base-emitter voltage } V_{BE} \text{ (in mV)}}{\text{corresponding change in base current } I_{B} \text{ (in } \mu \text{A)}}$$

$$= \frac{(700 - 525) \, 10^{-3}}{(53 - 0) \, 10^{-6}} = 3.3 \, \text{k}\Omega$$

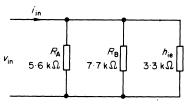

For the amplifier, the effective a.c. input circuit is shown in figure 2.10.

Figure 2.10

The amplifier a.c. input resistance  $r_{in}$  is given by

$$\frac{1}{r_{in}} = \frac{1}{5 \cdot 6} + \frac{1}{7 \cdot 7} + \frac{1}{3 \cdot 3}$$

$$= 0.179 + 0.130 + 0.303$$

$$= 0.612 \text{ mS}$$

$$r_{in} = 1.6 \text{ k}\Omega$$

When this amplifier is loaded by an identical stage, the input resistance of the second stage will shunt the load resistor of the first stage, thereby reducing the net resistance to  $R'_{\rm L}$ , where

$$\frac{1}{R'_{\rm L}} = \frac{1}{R_{\rm L}} + \frac{1}{r_{\rm in}} = \frac{1}{1} + \frac{1}{1.6}$$

$$= 2.6/1.6$$

therefore

$$R'_{\rm L} = 615 \,\Omega$$

Consider an r.m.s. input voltage  $V_{in}$  of 33 mV, then r.m.s. base current

$$l_{\rm b} = V_{\rm in}/h_{\rm ie} = \frac{33 \times 10^{-3}}{3 \cdot 3 \times 10^3} = 10 \,\mu{\rm A}$$

As a.c. current gain  $h_{fe}$  = d.c. current gain  $h_{FE}$  = 208, r.m.s. collector current

therefore r.m.s. output voltage

$$V_{\rm o} = I_{\rm c} R'_{\rm L}$$

= 2.08 x 10<sup>-3</sup> x 615

= 1.28 V

Amplifier voltage gain  $A_v = V_o/V_{in} = \frac{1.28}{33 \times 10^{-3}}$

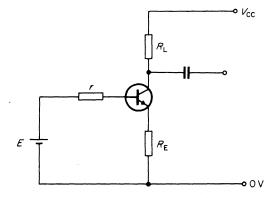

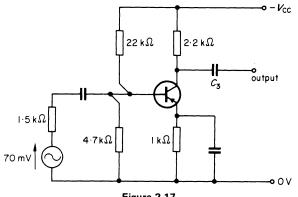

#### 2.7 Design of practical amplifier

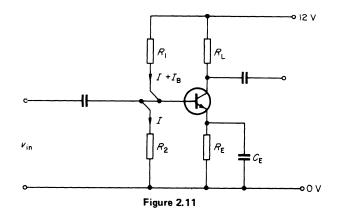

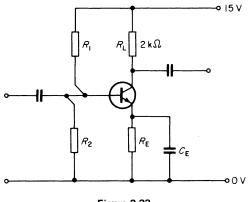

In the common-emitter amplifier shown in figure 2.11, the collector current of the transistor is 5 mA and its d.c. current gain  $h_{\rm FE}$  = 50. If the voltage drop across  $R_{\rm E}$  is 2 V, and the collector-emitter and base-emitter voltages of the transistor are 4 V and 0.5 V respectively, determine the values of all the labelled components if the lowest signal frequency is 50 Hz.

Voltage drop across load resistor = 12 - 4 - 2

= 6 V

therefore

$$R_{\rm L} = \frac{6}{5 \times 10^{-3}} = 1.2 \,\rm k\Omega$$

Transistor base current

$$I_{\rm B} = I_{\rm C} / h_{\rm FE} = \frac{5 \times 10^{-3}}{50}$$

= 100 μ A

Emitter current

$$I_{\rm E} = I_{\rm B} + I_{\rm C} = 5.1 \, \rm{mA}$$

therefore

$$R_{\rm E} = \frac{2}{5.1 \times 10^{-3}} = 392 \ \Omega$$

At the lowest signal frequency of 50 Hz, the reactance of  $C_E$  should be approximately one tenth of  $R_E$ . Therefore

$$39 \cdot 2 = \frac{1}{2\pi \times 50 C_{\rm E}}$$

$$C_{\rm E} = 81 \,\mu\,{\rm F}$$

In practice,  $C_E$  would be a 100  $\mu\text{F}$  capacitor.

Let the bleed current / =  $10/_B$  = 1 mA

Voltage on the base  $V_{\rm B}$  = 2 +  $V_{\rm BE}$  = 2.5 V

therefore

$$R_2 = \frac{2.5}{1 \times 10^{-3}} = 2.5 \text{ k}\Omega$$

voltage drop across  $R_1$  is (12 - 2.5) = 9.5 V therefore

$$R_1 = \frac{9.5}{1.1 \times 10^{-3}} = 8.6 \text{ k}\Omega$$

In a practical circuit, the nearest *preferred* values of each resistor would be used (that is, the nearest values contained in the standard 'list of preferred values' would be selected).

#### 2.8 Voltage, current, and power gains

In a common-emitter amplifier, an a.c. input voltage of 10 mV produces an output current of 2 mA in the 500  $\Omega$  load resistor. If the a.c. input resistance of the amplifier is 900  $\Omega$ , determine the voltage gain, current gain, and power gain of the amplifier in dB.

Amplifier output voltage

$$v_0 = 2 \times 10^{-3} \times 500 = 1 \text{ V}$$

therefore

voltage gain

$$A_v = v_o / v_{in} = \frac{1}{10 \times 10^{-3}} = 100$$

voltage gain  $A_v$  in dB = 20 log 100 = 40 dB

Input current

$$\dot{v}_{in} = v_{in} / r_{in} = \frac{10 \times 10^{-3}}{900} = 11.1 \,\mu\text{A}$$

therefore

current gain

$$A_i = i_0 / i_{in} = \frac{2 \times 10^{-3}}{11 \cdot 1 \times 10^{-6}} = 180$$

current gain  $A_i$  in dB = 20 log 180 = 45 \cdot 1 dB

Power gain  $A_p = v_0 i_0 / v_{in} i_{in} = A_v A_i = 18\ 000$

power gain  $A_p$  in dB = 10 log 18\ 000 = 42 \cdot 55\ dB

#### 2.9 Stability factor of amplifier with collector-base resistor

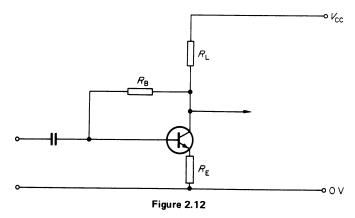

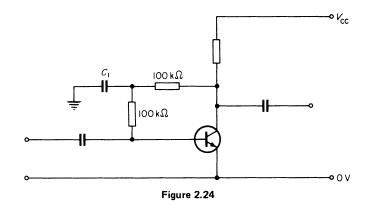

A silicon transistor ( $V_{BE} = 0.6$  V) is used in the circuit of figure 2.12.

Given  $V_{CC} = 24$  V,  $R_L = 10$  k $\Omega$ ,  $R_E = 270 \Omega$  and  $h_{FE} = 45$ . If under quiescent conditions  $V_{CE}$  is 5 V, find from first principles (a) the value of the bias resistor  $R_B$  and (b) the stability factor  $S = \delta I_C / \delta I_{CO}$ .

(H.N.C.)

(a) In figure 2.12

$$V_{\rm CC} = (I_{\rm C} + I_{\rm B})R_{\rm L} + V_{\rm CE} + (I_{\rm C} + I_{\rm B})R_{\rm E}$$

(2.2)

Also

$l_{\rm C} = h_{\rm FE} l_{\rm B} = 45 l_{\rm B}$

therefore substituting in equation 2.2

$$24 = 46I_{B} \times 10 + 5 + 46I_{B} \times 0.27$$

$$I_{B} = \frac{19}{472.4} = 0.04 \text{ mA}$$

Also

2.2

$$V_{\rm CE} = I_{\rm B}R_{\rm B} + V_{\rm BE}$$

5 = 0.04 $R_{\rm B}$  + 0.6 (2.3)

$$R_{\rm B} = 4.4/0.04 = 110 \,\rm k\Omega$$

(b) Substituting for  $V_{\rm CE}$  from equation 2.3 into equation

$$V_{\rm CC} = (I_{\rm C} + I_{\rm B})R_{\rm L} + I_{\rm B}R_{\rm B} + V_{\rm BE} + (I_{\rm C} + I_{\rm B})R_{\rm E}$$

$$(V_{\rm CC} - V_{\rm BE}) = I_{\rm B}(R_{\rm E} + R_{\rm B} + R_{\rm L}) + I_{\rm C}(R_{\rm E} + R_{\rm L})$$

Multiply both sides by  $h_{\rm FE}$

$$h_{\rm FE}(V_{\rm CC} - V_{\rm BE}) = h_{\rm FE} I_{\rm B} (R_{\rm E} + R_{\rm B} + R_{\rm L})$$

+  $h_{\rm FE} I_{\rm C} (R_{\rm E} + R_{\rm L})$  (2.4)

Now

collector current = d.c. component + leakage current

therefore

$$I_{\rm C} = h_{\rm FE} I_{\rm B} + (h_{\rm FE} + 1) I_{\rm CO}$$

where  $I_{\rm CO}$  is the value of common-base leakage current. Then

$$h_{\rm FE}/B = I_{\rm C} - (h_{\rm FE} + 1)/_{\rm CO}$$

Substituting in equation 2.4 for  $h_{\rm FE}/B$

$$\begin{split} h_{\rm FE}(V_{\rm CC}-V_{\rm BE}) &= (R_{\rm E}+R_{\rm B}+R_{\rm L})[I_{\rm C}-(h_{\rm FE}+1)I_{\rm CO}] \\ &+ h_{\rm FE}I_{\rm C}(R_{\rm E}+R_{\rm L}) \\ &= I_{\rm C}[(R_{\rm E}+R_{\rm B}+R_{\rm L})+h_{\rm FE}(R_{\rm E}+R_{\rm L})] \\ &- I_{\rm CO}(h_{\rm FE}+1)(R_{\rm E}+R_{\rm B}+R_{\rm L}) \end{split}$$

Considering small changes in  $I_{\rm C}$  and  $I_{\rm CO}$ ,  $\delta I_{\rm C}$  and  $\delta I_{\rm CO}$ , respectively

$$0 = \delta I_{\rm C}[R_{\rm B} + (h_{\rm FE} + 1)(R_{\rm E} + R_{\rm L})] - \delta I_{\rm CO}(h_{\rm FE} + 1)(R_{\rm E} + R_{\rm B} + R_{\rm L})$$

therefore stability factor

$$S = \delta I_{\rm C} / \delta I_{\rm CO} = \frac{46 \times 120.27}{110 + 46(10.27)} = 9.5$$

Note that the stability factor is a measure of the d.c. stability of the circuit when leakage current changes. In this example, if  $I_{CO}$ increased by 1  $\mu$ A, the collector current would increase by only 9.5  $\mu$ A. Therefore, a circuit should have as low a value of stability factor as possible, the minimum value being achieved in the common-base amplifier (where S = 1).

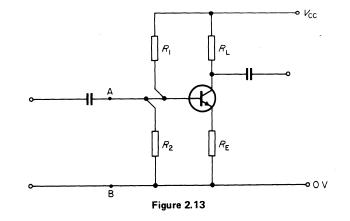

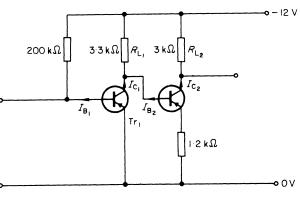

### 2.10 Stability factor of amplifier with potential-divider stabilisation

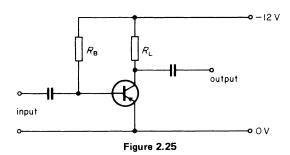

The circuit of figure 2.13 uses a silicon transistor with  $h_{\rm FE} = 60$ ,  $V_{\rm BE} = 0.6$  V,  $V_{\rm CC} = 20$  V and  $R_{\rm L} = 4$  k $\Omega$ . It is desired to establish a quiescent point at  $V_{\rm CE} = 10$  V,  $I_{\rm C} = 2$  mA with a stability factor S = 5. Calculate the values of  $R_{\rm E}$ ,  $R_1$  and  $R_2$ , proving any formula used. (H.N.C.)

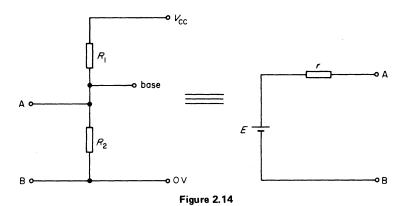

The circuit shown in figure 2.13 contains three independent loops which makes the analysis fairly complicated. Thus, it is far easier to use the Thévenin equivalent of the input circuit; that is, an active network, having two terminals A and B with a load connected across them, can be considered to be a single source of e.m.f. E with an internal resistance r. E is equal to the potential difference between A and B with the load disconnected, and r is the resistance of the network measured between A and B with the load disconnected and any sources of e.m.f. replaced by their internal resistances. In this example

$$= V_{CC} R_0 / (R_1 + R_2)$$

and

Ε

$$r = R_1 R_2 / (R_1 + R_2)$$

Therefore, the circuit of figure 2.13 now becomes effectively the circuit of figure 2.15.

Figure 2.15

In figure 2.15 the current through  $R_{\rm E}$  is  $(I_{\rm C} + I_{\rm B}) \approx I_{\rm C}$  = 2 mA. Now

$$V_{\rm CC} - V_{\rm CE} = I_{\rm C}(R_{\rm E} + R_{\rm L})$$

therefore

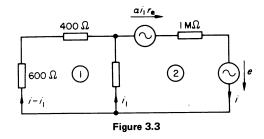

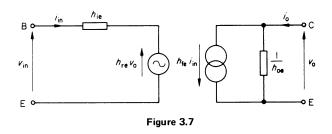

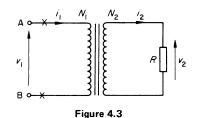

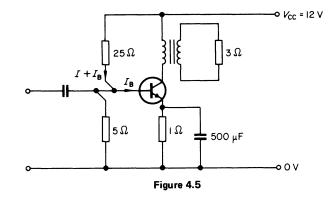

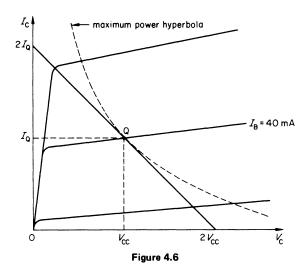

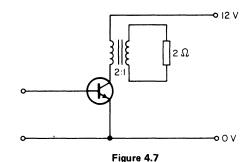

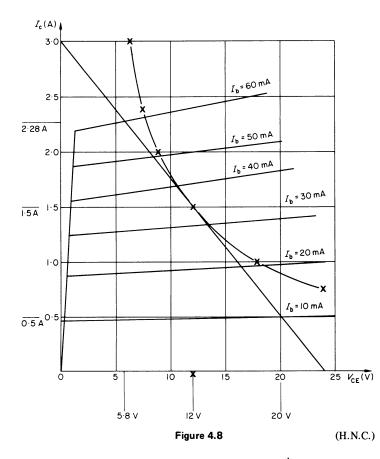

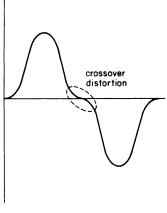

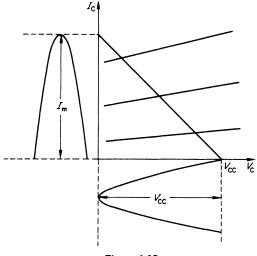

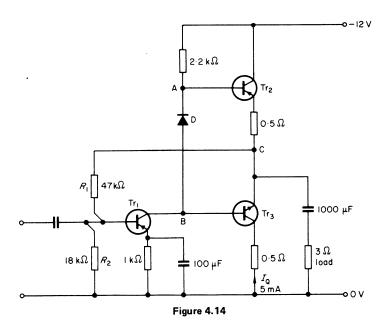

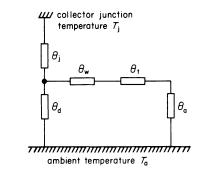

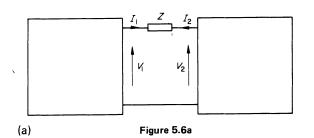

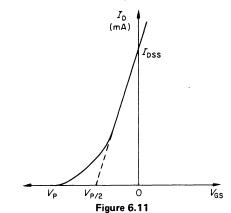

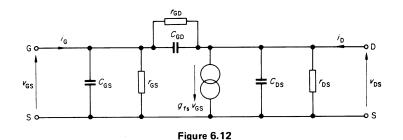

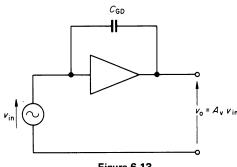

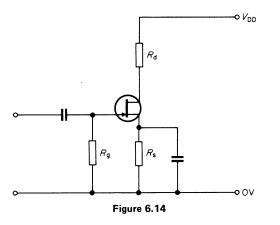

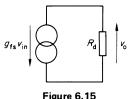

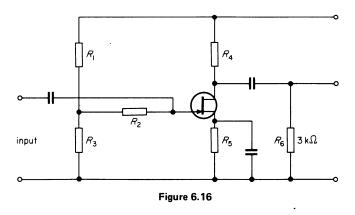

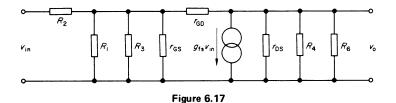

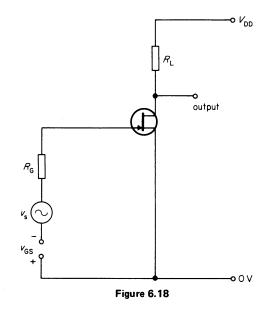

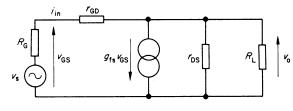

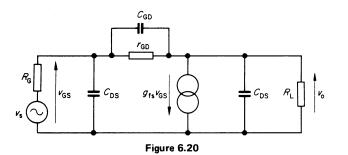

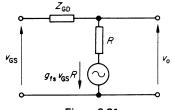

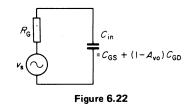

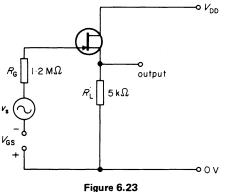

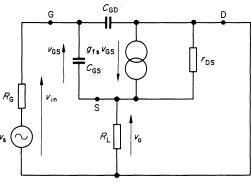

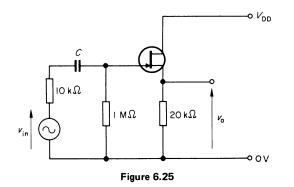

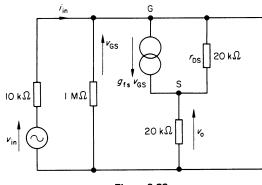

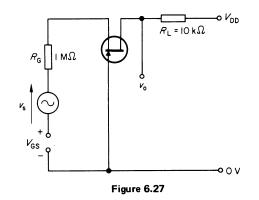

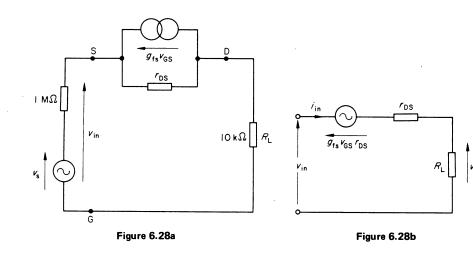

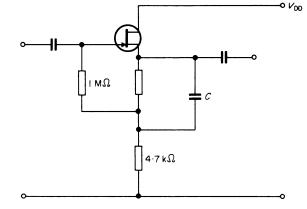

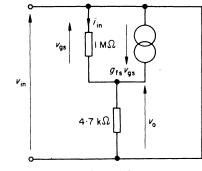

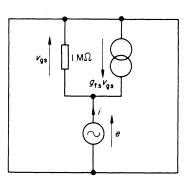

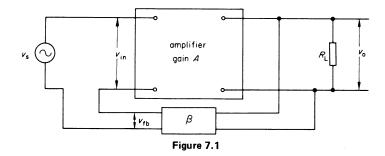

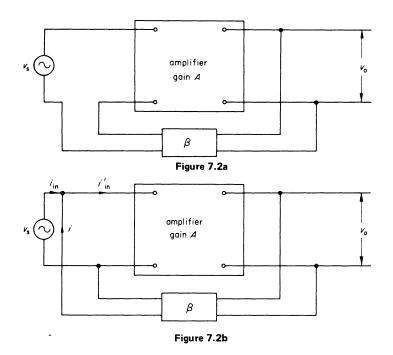

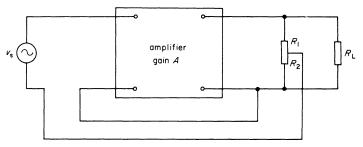

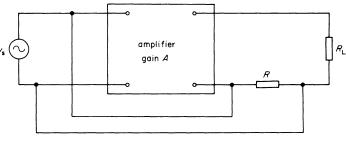

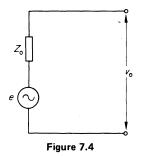

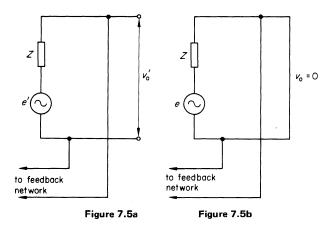

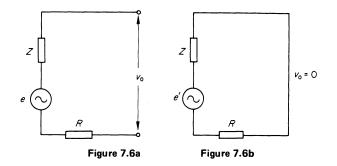

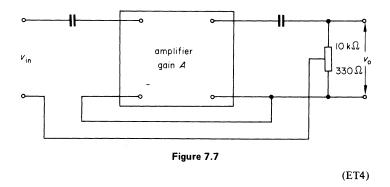

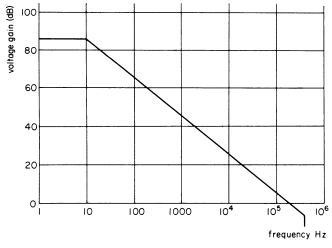

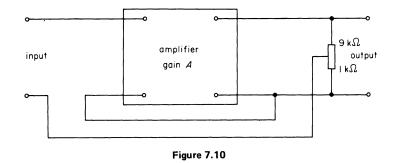

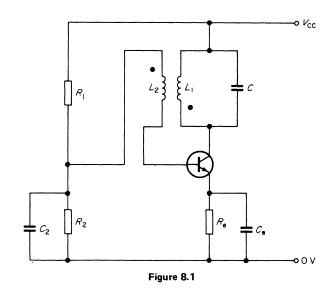

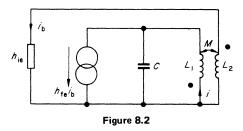

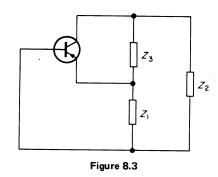

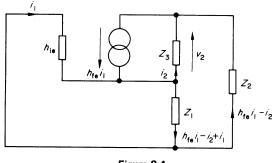

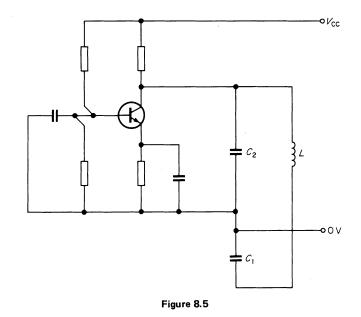

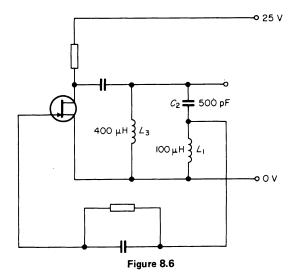

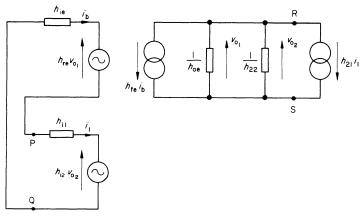

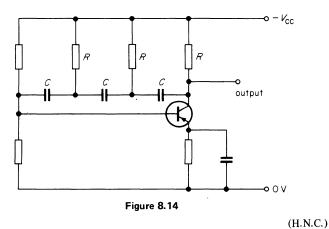

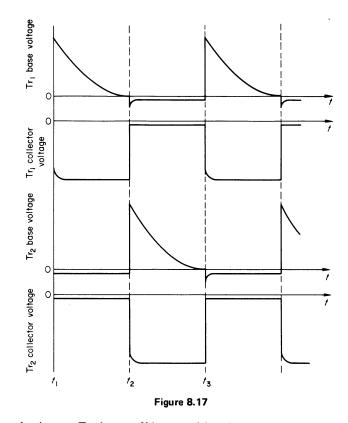

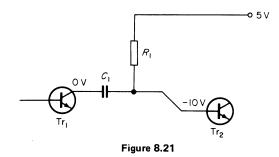

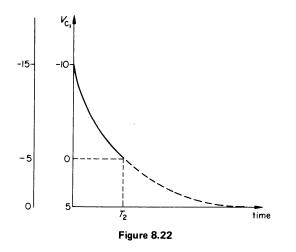

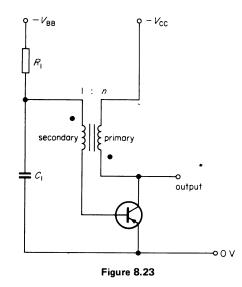

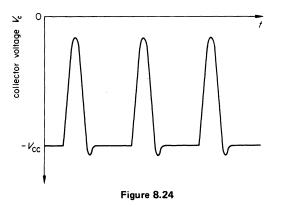

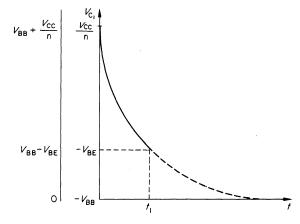

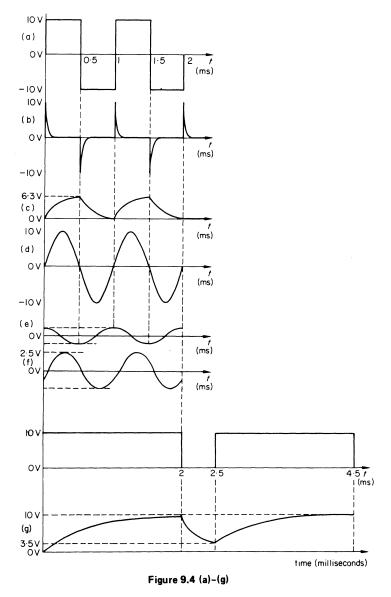

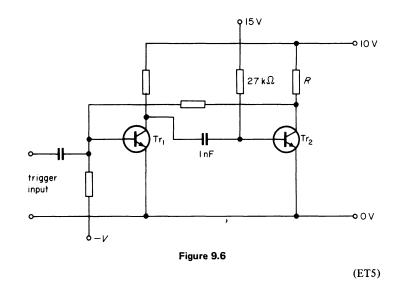

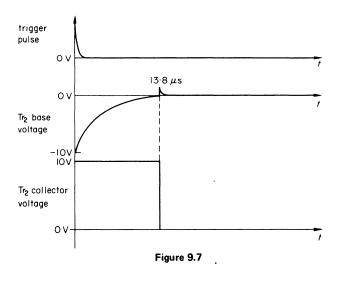

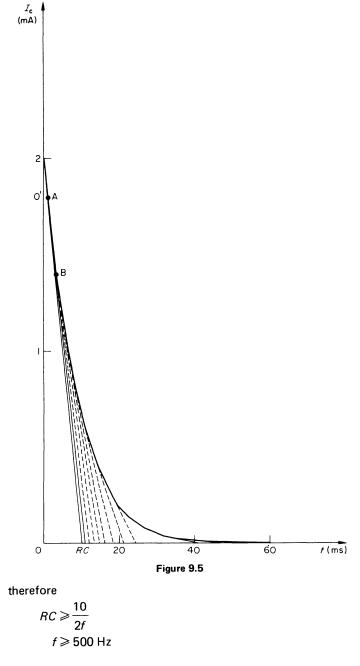

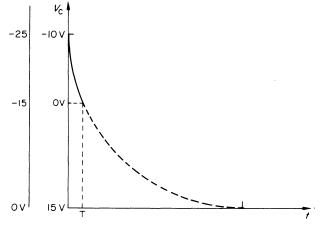

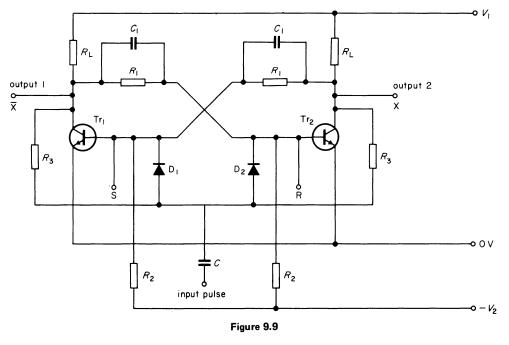

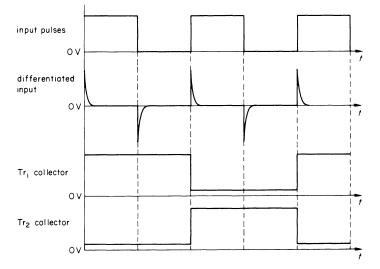

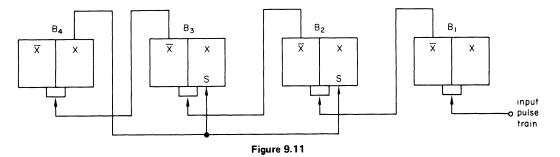

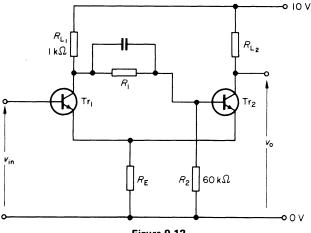

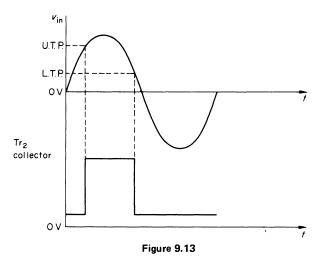

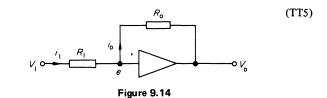

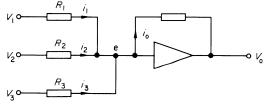

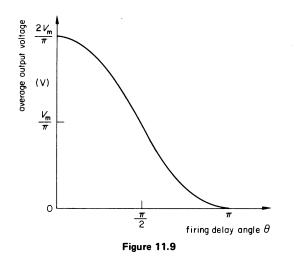

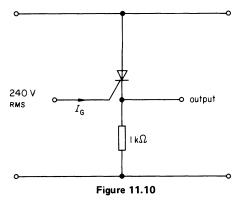

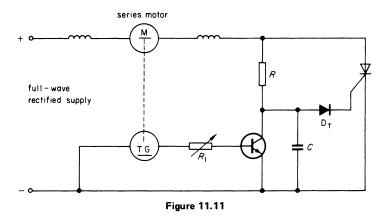

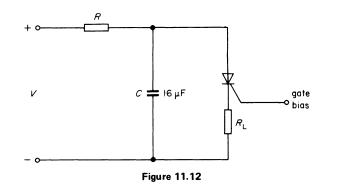

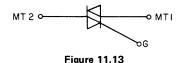

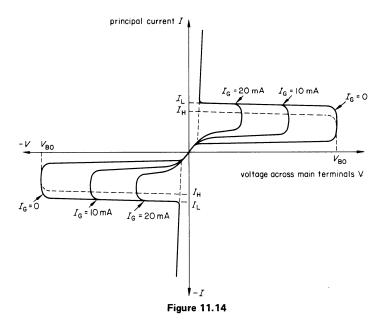

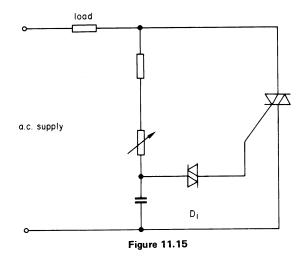

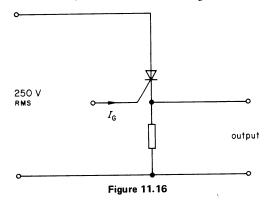

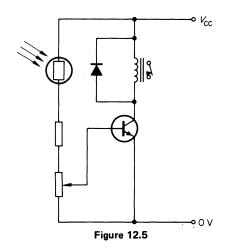

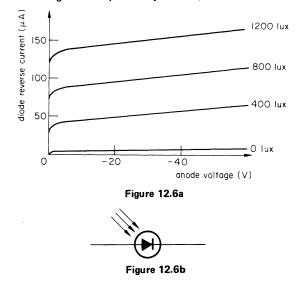

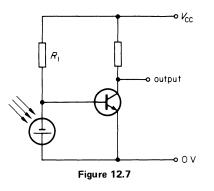

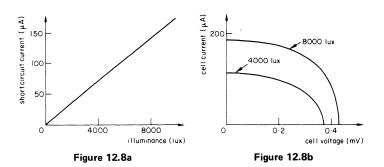

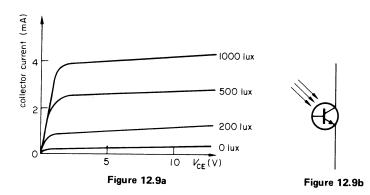

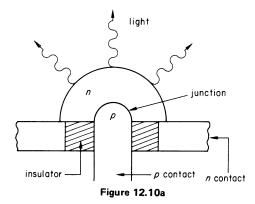

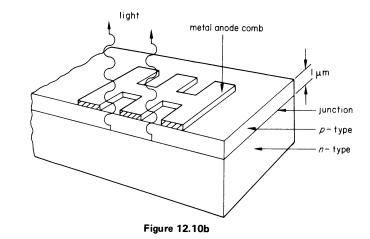

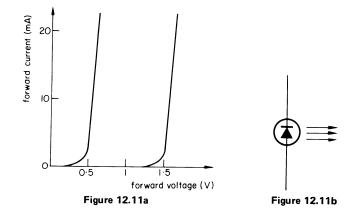

$$R_{\rm E} + R_{\rm L} = \frac{10}{2 \times 10^{-3}} = 5 \,\mathrm{k}\Omega$$