**MEMS Reference Shelf**

# Ai-Qun Liu

# RF MEMS Switches and Integrated Switching Circuits Design, Fabrication, and Test

MEMS Reference Shelf

#### **MEMS Reference Shelf**

Editor-in-Chief

Stephen D. Senturia Massachusetts Institute of Technology Professor of Electrical Engineering Emeritus

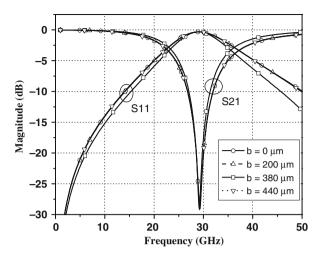

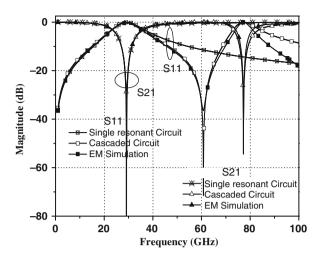

Series Editors:

Roger T. Howe Department of Electrical Engineering Stanford University Stanford, California

Antonio J. Ricco Small Satellite Division NASA Ames Research Center Moffett Field, California

For other titles in this series, go to: www.springer.com/series/7724

Ai Qun Liu

# RF MEMS Switches and Integrated Switching Circuits

Design, Fabrication, and Test

Chapter Co-Authors

Aibin Yu Institute of Microelectronics, Singapore

Ming Tang Institute of Microelectronics, Singapore

Muhammad Faeyz Karim Institute for Infocomm Research, Singapore

Selin Teo Hwee Gee Institute of Microelectronics, Singapore

<sup>‡</sup> The co-authors are PhD students of Ai Qun Liu

Dr. Ai Qun Liu School of Electrical & Electronic Engineering Nanyang Technological University Nanyang Avenue Singapore 639798 eaqliu@ntu.edu.sg

ISSN 1936-4407 ISBN 978-0-387-46261-5 e-ISBN 978-0-387-46262-2 DOI 10.1007/978-0-387-46262-2 Springer New York Dordrecht Heidelberg London

Library of Congress Control Number: 2010930386

#### © Springer Science+Business Media, LLC 2010

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

This book is dedicated to my beloved mother and late father

## Preface

Wireless communication has led to an explosive technological advancement and breakthrough in radio frequency microelectromechanical systems (RF MEMS) technology. The technology is seen to have the potential of replacing the mechanical, wireless, and semiconductor technology in future communication systems as well as communication satellites. In many cases, the RF MEMS technology does not only offer devices with substantial reduction in size, weight, cost, and power consumption but also promises more superior performance compared to those offered by the conventional technology. By combining high RF performance, low cost, and low power consumption, RF MEMS devices allow one to explore new architectures and configurations which were not possible with the traditional technology and expand its potential applications from defense-related products to personal communication devices.

This book, *RF MEMS Switches and Integrated Switching Circuits – Design, Fabrication and Test*, presents our latest accomplishments in RF MEMS switches and integrated switching circuits. The state of the art of RF MEMS switches and integrated switching circuits are described. Through this book, we wish to acquaint readers with the basics of RF MEMS and knowledge of how to design practical RF switches and switching circuits.

This book owes much to many.

I am grateful to all my PhD students Aibin, Min, and Faeyz for their excellent research work and dedicated contributions. I am particularly indebted to Selin for her help in coordinating the book project. Thanks also go to my excellent colleagues Alphones, Geok Ing, Zhong Xiang, Yi Long, Aditya, Chao Lu, Radhakrishnan, Hong Wang, and Joachim (KTH, Sweden) for their expert advice and friendly help. I am also not forgetting my debts to Joseph Ting and Gim Pew from DSO National Laboratories for directing me to the research field of RF MEMS while it was still in its infancy. I would also like to acknowledge my debts to Steven Elliot, the Senior Engineering Editor of Springer, who has been so persistent and supportive in giving me his support to accomplish the writing of this book. Working with him is a pleasure, even when the pressure is on. My final particular thanks are to my research group members, both past and present, for contributing their effort and full support to me.

Although I have made my best effort in writing this book, I have undoubtedly made errors or omission and sincerely apologize for them. I welcome comments and suggestions from readers about such errors and key concepts that may have been omitted. Updates, corrections, and other information will be available at my web site, http://nocweba.ntu.edu.sg/laq\_mems.

Singapore March 18, 2010 Ai Qun Liu

# Contents

| 1 | Intro | duction                                                   | 1   |

|---|-------|-----------------------------------------------------------|-----|

|   | 1.1   | RF MEMS Switches                                          | 2   |

|   | 1.2   | Capacitive Shunt Switches                                 | 5   |

|   | 1.3   | Coplanar Waveguide Transmission Lines                     | 7   |

|   | 1.4   | Single-Pole-Multi-Throw Switching Circuit (SPMT)          | 8   |

|   | 1.5   | Electromagnetic Band Gap (EBG) Structures for RF Circuits | 11  |

|   | 1.6   | Tunable EBG Bandpass Filters and Reconfigurable Circuits  | 12  |

|   | 1.7   | Capacitive Switching Bandpass Filters                     | 13  |

|   | 1.8   | Substrate Transfer Process                                | 13  |

|   | 1.9   | Surface Planarization Process                             | 15  |

|   | Refer | rences                                                    | 15  |

| 2 | Later | ral Series Switches                                       | 21  |

| - | 2.1   | Electrical Design and Simulation                          | 21  |

|   | 2.2   | Mechanical Design and Simulation                          | 30  |

|   | 2.3   | Device Fabrication Processes                              | 44  |

|   | 2.4   | Lateral Switch Characterization                           | 46  |

|   | 2.5   | Mechanical Measurements                                   | 58  |

|   | 2.6   | Summary                                                   | 62  |

|   | Refer | rences                                                    | 62  |

| 3 | Cana  | ncitive Shunt Switches                                    | 65  |

| 5 | 3.1   | Broadband DC-Contact Capacitive Switch                    | 65  |

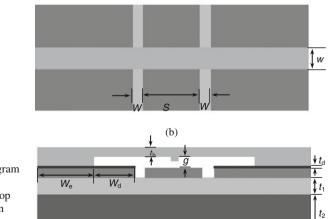

|   | 3.2   | DOG Switch on Low-Resistivity Silicon Substrate           | 77  |

|   | 3.3   | Summary                                                   | 81  |

|   |       | rences                                                    | 82  |

|   |       |                                                           |     |

| 4 | -     | anar Waveguide Transmission Line                          | 83  |

|   | 4.1   | Design of the Si-Core CPW                                 | 83  |

|   | 4.2   | Losses of the Si-Core CPW                                 | 86  |

|   | 4.3   | Effect of Material Properties and Fabrication Processes   | 89  |

|   | 4.4   | Experimental Results and Discussions                      | 94  |

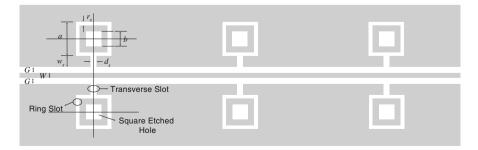

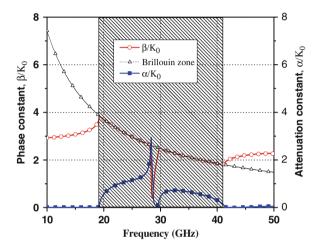

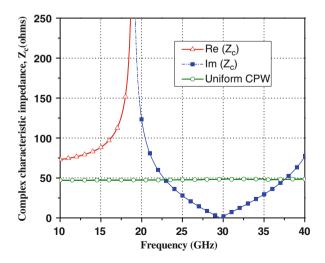

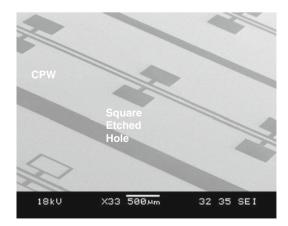

|   | 4.5   | Surface-Micromachined CPW Transmission Line               | 102 |

|   | 4.6   | Summary                                                   | 112 |

|   | Refer | rences                                                    | 112 |

| 5   | Single-Pole-Multi-Throw Switching Circuits       | 15               |

|-----|--------------------------------------------------|------------------|

|     |                                                  | 15               |

|     |                                                  | 21               |

|     | 5.3 Design of the SP4T Switching Circuit         | 23               |

|     |                                                  | 23               |

|     | 5.5 Summary                                      | 31               |

|     | •                                                | 31               |

| 6   | Tunable Electromagnetic Band Gap Bandstop Filter | 33               |

|     |                                                  | 33               |

|     | *                                                | 41               |

|     |                                                  | 48               |

|     | 6.4 Design of Tunable Bandstop Filter            | 51               |

|     | 6.5 Summary                                      | 57               |

|     | References                                       | 58               |

| 7   | Tunable Electromagnetic Bandpass Filter          |                  |

| -   |                                                  | 159              |

|     |                                                  | 59               |

|     |                                                  | 61               |

|     |                                                  | 64               |

|     |                                                  | 70               |

|     | *                                                | 73               |

|     |                                                  | 86               |

|     | •                                                | 86               |

| 8   | Capacitive Switching Bandpass Filters            | 89               |

| U   |                                                  | 89               |

|     |                                                  | 93               |

|     |                                                  | 206              |

|     | 5                                                | 206              |

| 9   | Substrate Transfer Process                       | 207              |

| ,   |                                                  | 207              |

|     | 6                                                | 211              |

|     | •                                                | 216              |

|     |                                                  | 220              |

|     | 1                                                | 220<br>226       |

|     | ······································           | 220<br>226       |

| 10  |                                                  |                  |

| 10  |                                                  | 229              |

|     |                                                  | 229              |

|     |                                                  | 232              |

|     |                                                  | 235              |

|     | e                                                | $\frac{246}{2}$  |

|     | 5                                                | $\frac{263}{62}$ |

|     | References                                       | 263              |

| Ind | <b>ex</b>                                        | 265              |

# Chapter 1 Introduction

This book compiles the latest advancements in the field of radio frequency (RF) microelectromechanical systems (MEMS) technology and devices, spanning a comprehensive range of RF MEMS topics. Highlights of contributions include areas such as (1) lateral series switches, (2) capacitive shunt switches, (3) coplanar waveguide transmission line switches, (4) multi-throw switches, (5) tunable electromagnetic bandstop and bandpass filters, (6) capacitive switching filters, and (7) different types of switches and fabrication processes.

In the following sections, the background and literature necessary as foundations for each of the subsequent chapters detailing the various technologies developed are organized as follows: Section 1.1 gives the overview and literature background of RF MEMS switches, especially for their relevance to lateral series switches as will be presented in detail in Chapter 2. Section 1.2 provides the ground works for research into areas of improvement for capacitive shunt switches - such as in reliability, power handling and degradation – which will be presented in Chapter 3. Section 1.3 gives the background on coplanar waveguide transmission lines before Chapter 4 presents new designs, optimizations, and their results. Section 1.4 introduces the single-pole-multi-throw switching RF circuits, so that works on SP3T and SP4T switching circuits may be developed fully in Chapter 5. Sections 1.5 and 1.6 give the background for electromagnetic band gap (EBG) circuits, which is the foundation of the technologies developed in Chapters 6 and 7, respectively, for both tunable bandstop and bandpass filter circuits. Section 1.7 provides the introduction to capacitive switching bandpass filters which research developments made will be covered in Chapter 8. Finally, Sections 1.8 and 1.9 present the initiation for fabrication technologies necessary to the realization of RF MEMS devices, in particular by substrate transfer processes and surface planarization techniques. The intricacies required of such technologies are then accordingly detailed in Chapters 9 and Chapters 10.

Selin Teo Hwee Gee and Ai Qun Liu

#### 1.1 RF MEMS Switches

A radio frequency (RF) microelectromechanical switch is a switching device that is fabricated using the micromachining technology, where the switching between the on- and off-states is achieved via the mechanical displacement of a freely movable structure. The displacement is induced by a microactuator. Various actuation mechanisms then exist, including electrostatic [1-3], electrothermal [4], magnetostatic [5], and electromagnetic [6-10] means. Most often, the RF MEMS switches rely on electrostatic actuation, which is based on the attractively electrostatic force existing between charges of opposite polarity. An electrostatic drive offers extremely low power consumption since power is required only during switching. The other advantages of using electrostatic actuation are its simple fabrication technology, compared to electromagnetic excitation: the high degree of compatibility with a standard IC process line and its ease of integration with planar and microstrip transmission lines. For many applications, the main drawback is to overcome the high driving voltage. When the available supply voltage is limited, for instance, within the range of 3-5 V in mobile phones, on-chip high-voltage generators [11] may be incorporated either monolithically or in a hybrid fashion [12].

The RF MEMS switches can be classified as vertical switches and lateral switches based on the motion direction of the switching structure. The vertical switches perform out of wafer plane displacement and surface contact. The lateral switches perform in wafer plane displacement and sidewall contact. The vertical RF MEMS switches are usually fabricated using surface micromachining process and metal is used as its structural material. On the other hand, the lateral RF MEMS switches are usually fabricated using bulk micromachining process, using single-crystal silicon or polysilicon as its structural material. Most RF MEMS switches developed in the last decades are vertical switches due to their excellent RF performance. However, the lateral switches have shown some promising performance in dynamics, together with fabrication processes which are simpler compared to its vertical switching counterparts. As such, much recent research interest has been geared toward the lateral switches.

The lateral switches have the benefit of co-fabrication. The movable switching structure, the contacts, the transmission line, and the support structures can be fabricated in a single lithographic step. Besides, the actuator design is more flexible. It is easy to get a mechanical force in opposing directions even when electrostatic designs are used. The lateral RF MEMS switches can use different elements as the structural material, for instance, nickel, polysilicon, and single-crystal silicon. To date, three main types of lateral switches have been reported. All of them are the resistive series switches.

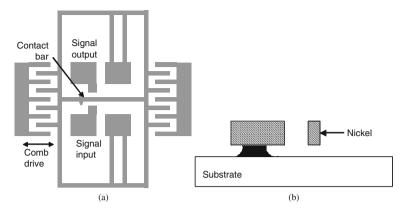

The first type of lateral switch is the comb-drive or cantilever beam-actuated lateral switch which uses electroless plated nickel as its structure material [13–14]. The schematic illustration of a comb-drive-actuated lateral switch [13] is shown in Fig. 1.1; in the plating process, the nickel height is restricted to 10–50  $\mu$ m and the smallest possible width is limited to 5  $\mu$ m. The actuation voltage is within the range of 35–150 V. The contact resistance is 5–20  $\Omega$ .

Fig. 1.1 The schematic illustration of a comb-drive-actuated lateral switch fabricated using nickel surface micromachining process: (a) top view and (b) cross-sectional view [13]

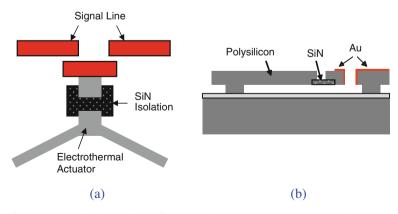

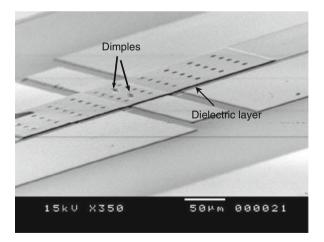

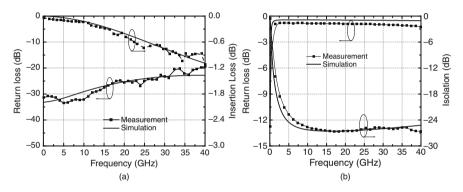

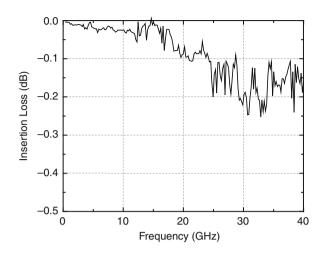

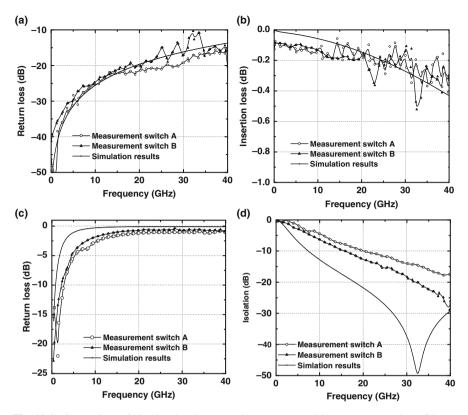

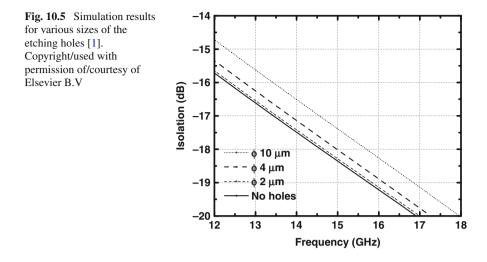

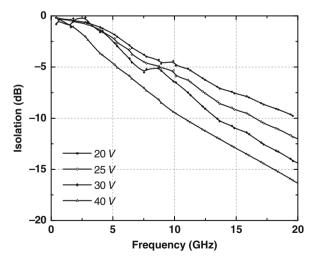

The second type of the lateral switch is the electrothermally or electrostatically actuated switch using polysilicon as the structural material [15–24]. The electrothermally actuated switch has demonstrated RF performance up to 50 GHz [22–24], as shown in Fig. 1.2. The switch utilizes a parallel six-beam thermal actuator which requires actuation voltage of 2.5–3.5 V. The mechanical structures are fabricated using 2- $\mu$ m polysilicon surface micromachining process and four masks. Silicon nitride is used as a structural connection to isolate the RF signal and the DC bias. Gold of thickness 0.3–0.5  $\mu$ m is deposited on the polysilicon to form a transmission line and contact bumps. The switch has an isolation of –20 dB at 40 GHz. The insertion loss is –0.1 dB at 50 GHz after de-embedding the substrate effect and –1.0 dB before de-embedding the substrate effect. The switching "on" time is 300  $\mu$ s. Although this type of lateral switch exhibits high RF performance and

Fig. 1.2 The schematic illustration of a thermally actuated lateral switch: (a) 3D view and (b) cross-sectional view [22]

requires low actuation voltage, its drawbacks are the complicated fabrication process, the high power consumption due to thermal actuation, slow switching speed, and also a fragile switching structure.

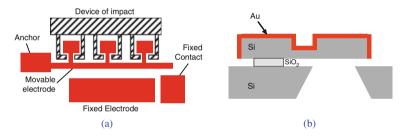

The third type of the lateral switch is an electrostatically actuated switch using single-crystal silicon as its structural material [25–27] and fabricated using a single-mask bulk micromachining process. The electrostatic actuator can be either a combdrive or a cantilever beam. The switching structures are typically fabricated using deep reactive ion etching (DRIE) process on silicon-on-insulator (SOI) wafer. The metal contact is realized by depositing a thin layer of metal directly on the entire surface of the switch structure, as shown in Fig. 1.3. Compared to other RF MEMS switches, the fabrication process of this type of lateral switch is the simplest. Single-crystal silicon has negligible biaxial stress and vertical stress gradient, and superior thermal characteristics. Adapting a silicon process in fabricating the lateral switch can reduce the deformation of the switch structure caused by either thermal effects or stress gradients. As a result, the third type of lateral switch can provide better mechanical characteristics. However, most of the time, such lateral switches can only work at DC.

Fig. 1.3 The schematic illustration of an electrostatically actuated lateral switch: (a) top view and (b) cross-sectional view [25]

To investigate the possibility of such lateral switch being worked at high frequencies, the literature survey was extended to the RF behavior of non-solid-metal-core structures which consist of metal-coated structures with non-metal material as the core. A metal-coated silicon-core high-aspect-ratio transmission line was first developed in 1995 [28], followed by an improved version in 1998 [29, 30]. The transmission line was fabricated by a single-crystal reactive etching and metallization (SCREAM) process. It consists of pairs of parallel-plate waveguide formed from two deep (150- $\mu$ m) suspended single-crystal silicon beams with 0.5- $\mu$ mthick metal coating on the sidewalls. The attenuation was found to be less than -0.18 dB/cm at 10-50 GHz. A step impedance filter and a continuous microactuated phase shifter were realized using this transmission line [28-30]. High Q (quality factor) inductors with polysilicon as the core material and copper as the surface metal were demonstrated in [31]. The spiral structure of an inductor was formed using polysilicon surface micromachining process and suspended over a 30-µm-deep cavity in the silicon substrate beneath. Copper was electrolessly plated onto the polysilicon spiral to achieve low resistance. High quality factors (*Os*) over

| References                    | [13]          | [22]              | [25]              | [27]                       | [28]             |

|-------------------------------|---------------|-------------------|-------------------|----------------------------|------------------|

| Actuation<br>mechanism        | Electrostatic | Thermal           | Electrostatic     | Magnetic+<br>electrostatic | Electrostatic    |

| Structure material            | Nickel        | Poly-Si           | Silicon           | Silicon                    | Silicon          |

| Power<br>consumption          | $\mu W$       | 18–99 mW          | $\mu W$           | 11.3 nJ/cycle              | $\mu W$          |

| Frequency (GHz)               | DC            | DC to 40          | DC                | DC                         | DC to 25         |

| Insertion loss (dB)           | _             | 0.1               | _                 | -                          | 0.1-1.0          |

| Return loss (dB)              | _             | _                 | _                 | -                          | 22               |

| Isolation (dB)                | _             | 20                | _                 | -                          | 22               |

| Switching voltage (V)         | 35-150        | 2.5–3.5           | 50-260            | 10                         | 23.3             |

| Contact resistance $(\Omega)$ | 5–20          | 0.1–0.3           | 1000              | 2-8                        | 1–2              |

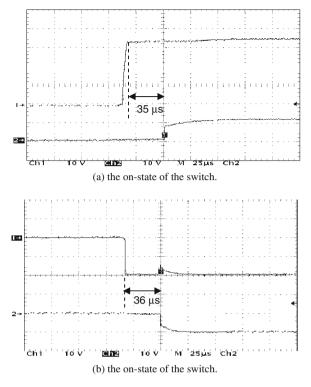

| Switching speed (µs)          | -             | 300               | 30                | 100 (close)<br>20 (open)   | 36               |

| Size (mm <sup>2</sup> )       | -             | $0.8 \times 0.34$ | $>1.2 \times 0.6$ | >2 × 2                     | $0.8 \times 0.4$ |

Table 1.1 Comparison of characteristics of lateral RF MEMS switches

30 and self-resonant frequencies higher than 10 GHz were achieved. It is expected that the lateral switch using the metal-coated silicon-core structures may work at high frequencies when the device is designed properly. Table 1.1 compares the characteristics between different lateral switches.

#### **1.2 Capacitive Shunt Switches**

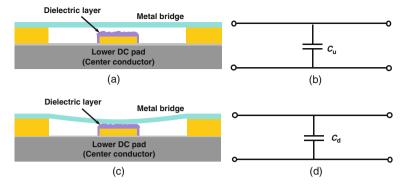

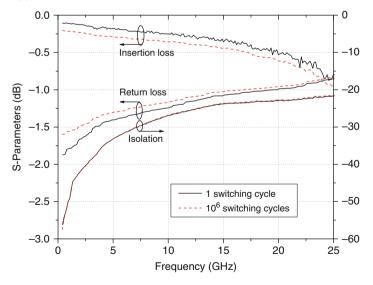

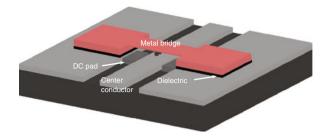

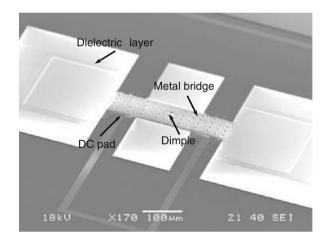

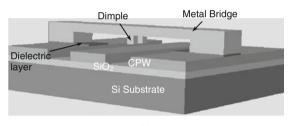

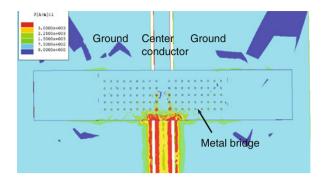

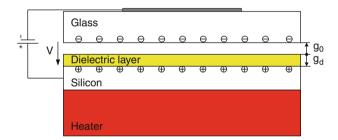

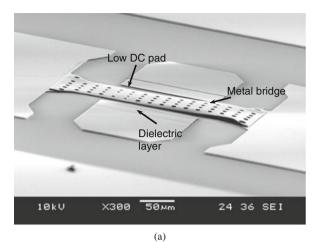

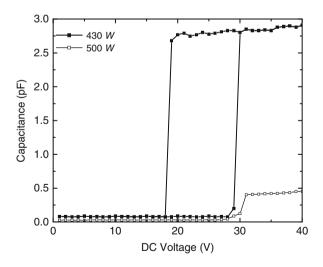

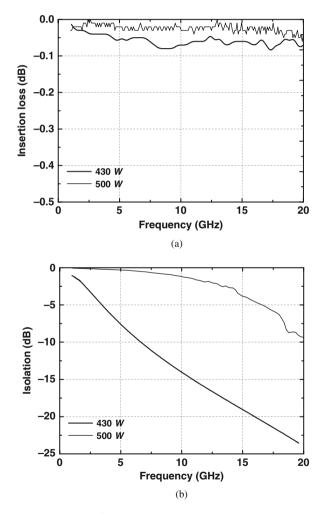

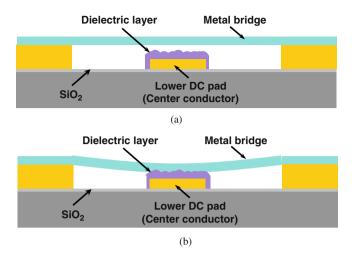

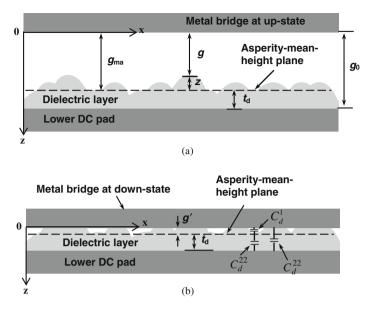

Capacitive switches are key elements in various applications such as tunable capacitors and tunable bandpass filter. Most of the capacitive switches are implemented in shunt configuration. In this construction, when the metal bridge is at the up-state position, the RF signal can go through from an input port to an output port, which is called switch on-state; when the metal bridge is driven down, then most of the RF signal is shorted to ground, which is called switch off-state, as shown in Fig. 1.4.

An important figure of merit of the RF MEMS capacitive switch is the ratio of on-state capacitance to off-state capacitance, that is,  $R = C_d / C_u$ , where  $C_d$  is the on-state capacitance with a typical value of several pico-farads and  $C_u$  is the off-state capacitance with a typical value of tens of femto-farads.

The larger the capacitance ratio, the smaller the off-state insertion loss and the higher the on-state isolation, and therefore broader frequency band can be obtained. In most cases, the RF capacitive switches are more suitable for high-frequency (>10 GHz) applications because of its capacitive coupling nature. Especially, at W-band, only the capacitive switches can be implemented because the DC-contact switches have large contact resistance, which gives rise to high loss at W-band. Therefore, to develop capacitive switches suitable for low-frequency (<10 GHz)

Fig. 1.4 Schematic of shunt capacitive switch with its equivalent circuits: (a) the *on*-state of the switch; (b) the *on*-state of the capacitance; (c) the *off*-state of the switch; and (d) the *off*-state capacitance

applications, one method is to increase the capacitance ratio by using dielectric material with high dielectric constant.

#### 1.2.1 Reliability of Capacitive Switches

The reliability of MEMS switches is of major concern for long-term applications. The reliability of the capacitive switch is mainly determined by stiction between the dielectric layer and the metal layer, which is due to charge injection and charge trapping in the dielectric layer [32]. There are two cases of failure in capacitive switches [33]. The first one is that the metal bridge actuates and then returns to the off-state position, irrespective of the polarity of the applied voltage; the second failure mechanism is due to charge injection in the dielectric layer and results in the metal bridge remaining in the down-state position when the actuation voltage is removed (sticking) or the metal bridge does not actuate under an applied bias voltage.

The dielectric charging problem can be minimized by (i) using silicon dioxide as the dielectric layer. However, using silicon dioxide instead of silicon nitride as the dielectric layer results in smaller on-state capacitance; (ii) another solution to minimize the dielectric charging problem is to use a bipolar voltage when biasing the capacitive switch; and (iii) finally, using side pull-down electrodes can also minimize the dielectric charging problem.

#### **1.2.2** Power Handling of Capacitive Switches

Power handling capabilities of RF MEMS switches are another major concern for the application of RF MEMS switches. Compared with that of p-i-n diode and FET,

RF MEMS switches can handle less RF power. The power handling capability of an RF MEMS switch is determine by self-actuation, stiction in the on-state, and hot switching [34].

Besides the DC driven of the switch, the RF signal can also lead to the pulldown of the metal bridge and hence the failure of the switch. Decoupling the RF and DC-actuation pads can substantially increase the power handling capability of the MEMS switch.

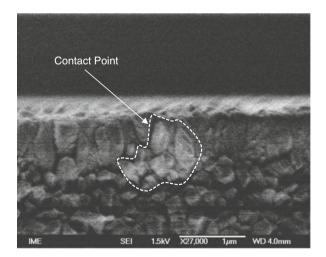

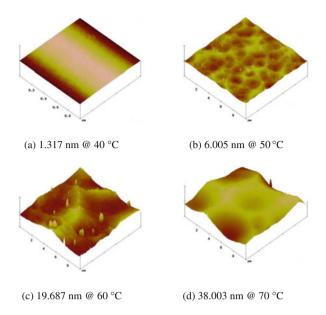

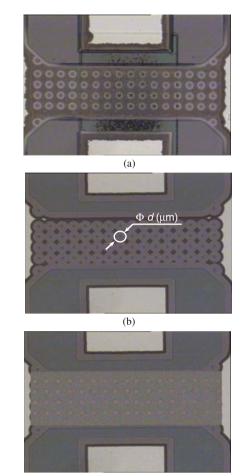

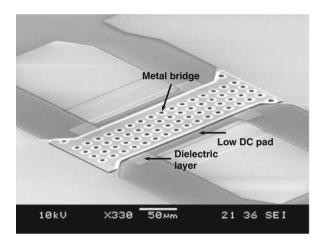

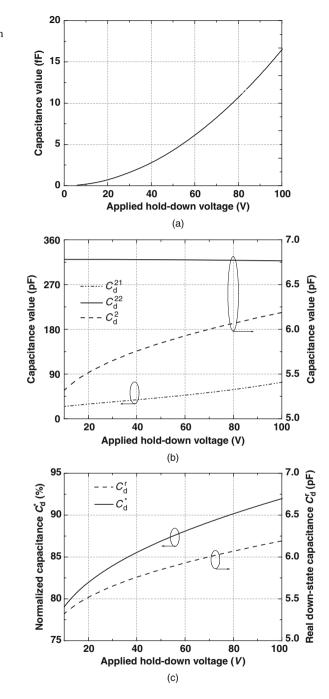

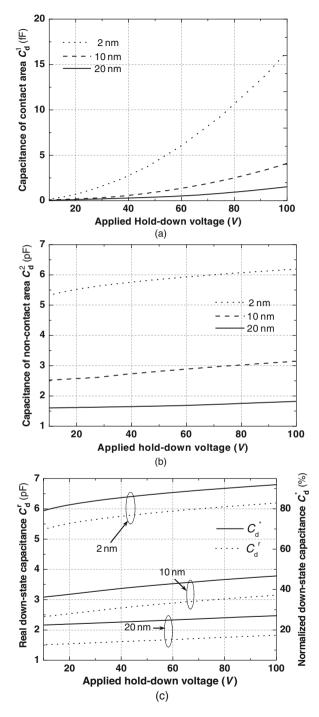

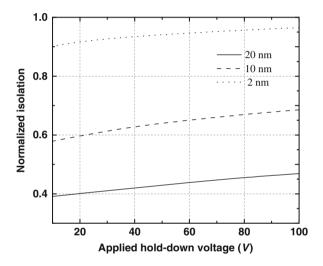

#### **1.2.3 Degradation of Down-State Capacitance**

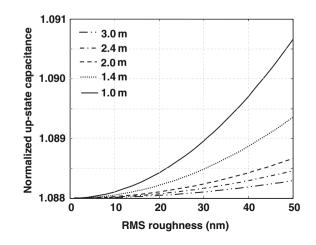

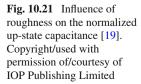

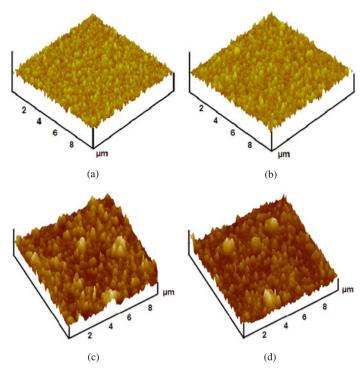

As mentioned, large down/up capacitance ratio is important for a capacitive switch to achieve low insertion loss and high isolation. Unfortunately, because of the onstate capacitance degradation problem, which means the actual on-state capacitance is always smaller than the designed value, it is difficult to obtain the capacitance ratio which is larger than 150 for conventional capacitive switches. The on-state capacitance degradation is mainly caused by nonplanarization of metal bridge, surface roughness of capacitance area, etching hole in the metal bridge, etc. For the capacitive switch, it is believed that a flat metal bridge and small roughness of dielectric layer are important to reduce the on-state capacitance degradation [35].

#### **1.3 Coplanar Waveguide Transmission Lines**

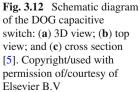

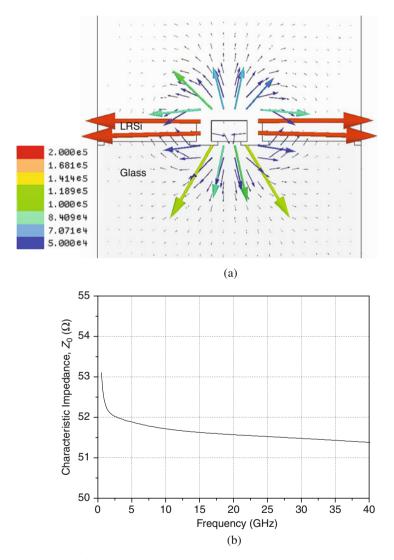

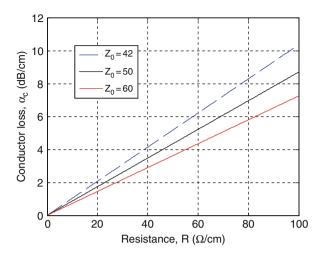

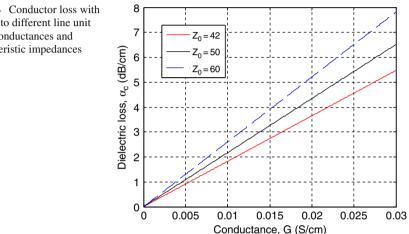

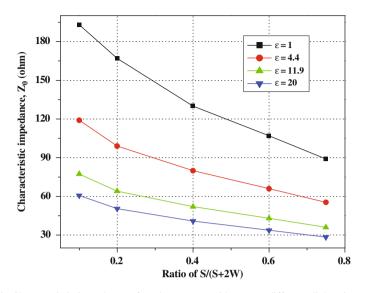

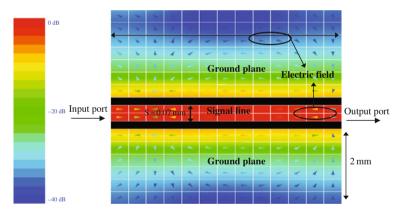

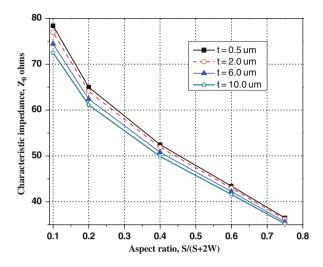

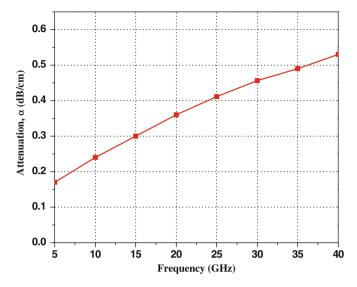

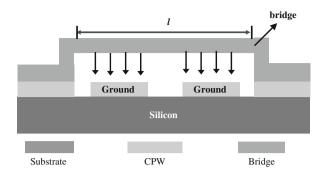

At RF and microwave frequencies, transmission lines are used to carry electrical signal from one point to another. Transmission lines have to be impedance matched, that is, all transmission lines in a circuit are designed to be 50  $\Omega$  of characteristic impedance to prevent unwanted reflections in high-frequency circuits. To do this, the signal line and the ground lines are arranged in a certain configuration where dielectric is in between. Coplanar waveguide (CPW) is a planar transmission line which is compatible with microwave and millimeter wave-integrated circuit technology. CPW is relatively insensitive to variations in substrate thickness. It has low radiation loss and allows circuit elements to be easily connected in shunt as well as in series. These characteristics have made CPW an exceptional candidate for high-frequency low-cost high-performance circuits.

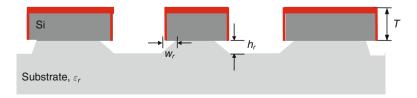

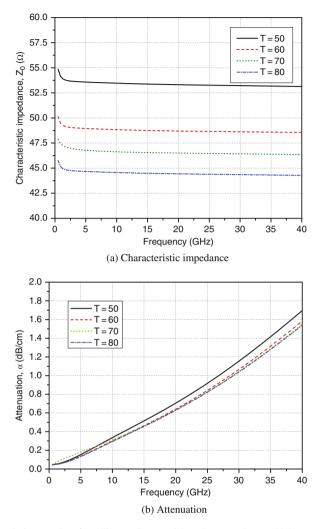

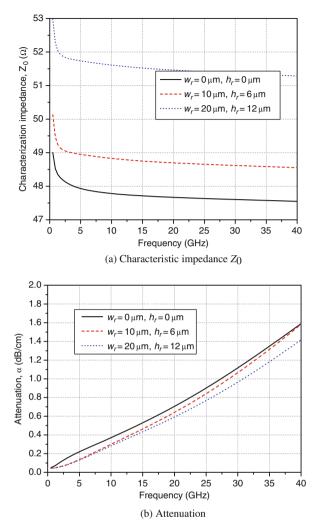

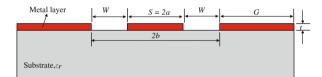

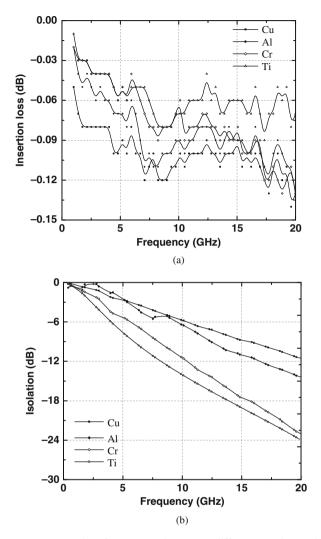

In coplanar lines, the field is tightly concentrated in the apertures between conductors, leading to current crowding for the conventional thin film techniques. When the conductor thickness is larger, the current can be distributed and the loss can be reduced. This makes it possible to work in high power applications due to the increased conduction interface. A new type of CPW transmission line with Si-core and metal overcoat is introduced in this book, in which the signal and ground lines' thickness is  $50-75 \,\mu\text{m}$ . The Si-core CPW transmission line demonstrates all advantages that include balanced propagation and coplanar configuration. The Si-core CPW can be implemented using a silicon back-bone structure patterned in desired shapes followed by a metal overcoat. The design and characterization of the Si-core CPW transmission line will be discussed.

#### **1.4 Single-Pole-Multi-Throw Switching Circuit (SPMT)**

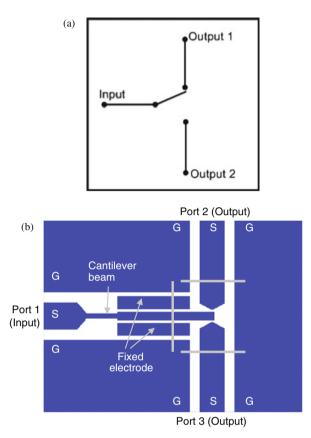

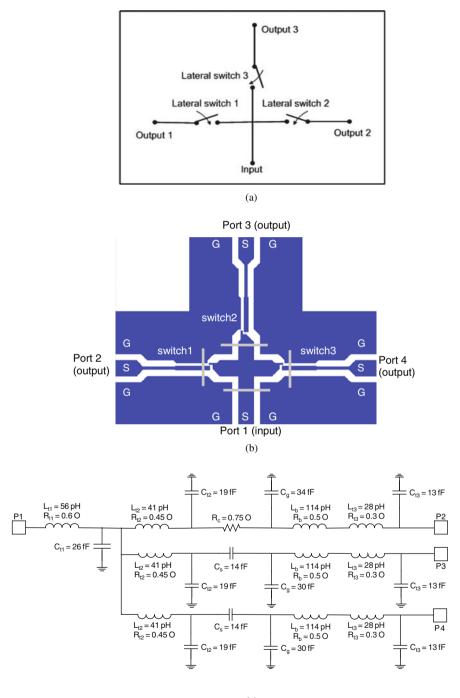

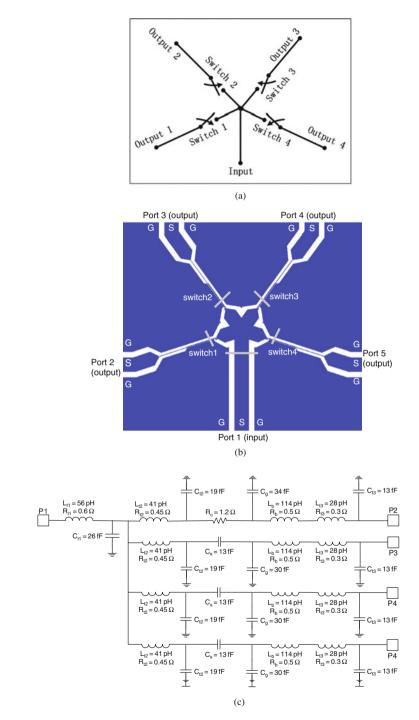

Integrating RF switches in a transmission line network forms an RF switching circuit, such as an SPMT switching circuit, a tunable filter, and a phase shifter. The SPMT switching circuits are the key components in transmitting/receiving (T/R) circuits, switchable filters, reconfigurable antennas, switching matrices, etc. In the SPMT switching circuit, a total of *m* switches are incorporated in an (m + 1) port junction device. When an SPMT switching circuit works, one switch is closed and the remaining (m - 1) switches are open.

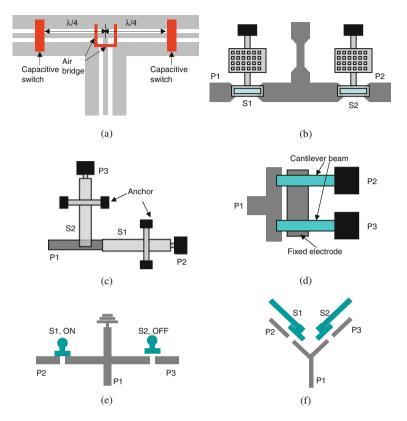

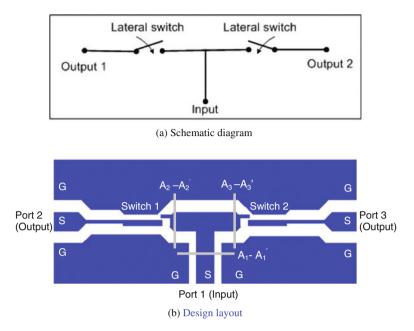

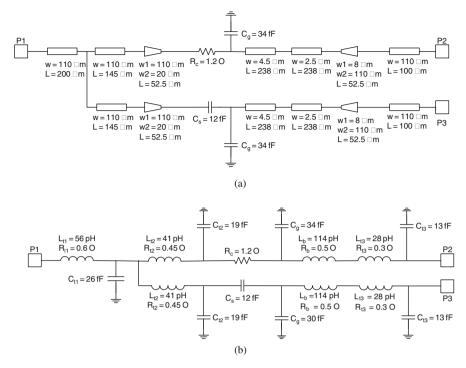

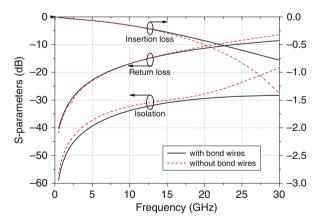

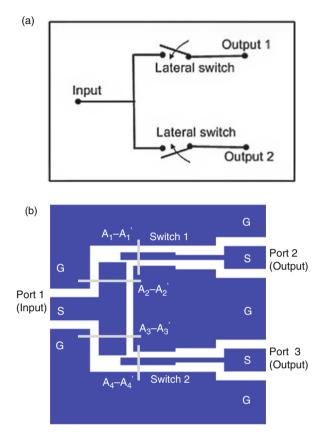

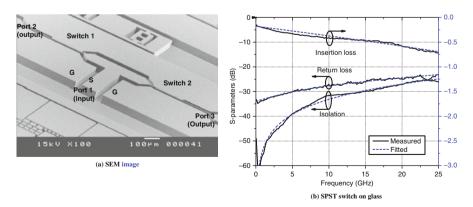

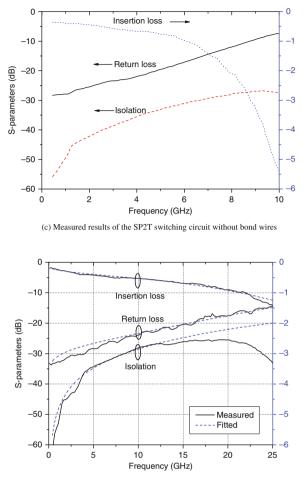

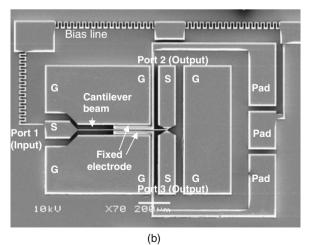

The major part of SPMT switching circuits is the single-pole-double-throw (SP2T) switching circuit. So far, six types of RF MEMS SP2T switching circuits have been developed. The first type is the most common one with two capacitive shunt MEMS switches placed a quarter wavelength from the center of the T-junction [36, 37], as shown in Fig. 1.5a. When one switch is actuated, the virtual RF short is transformed to an open at the T-junction, thus blocking almost all the signals from passing to that port. An insertion loss of 0.81 dB and an isolation of 20.3 dB at X-band and an insertion loss of 0.43 dB and an isolation of 28.7 dB at K-band have been demonstrated. A pull-in voltage of 9 V is achieved through changing the shape of the beam. The second design is a monolithic SP2T MEMS switching circuit [38, 39], which places two MEMS resistive series switches at two output armatures to operate in a 2.3-GHz diversity antenna, as shown in Fig. 1.5b. This switching circuit has an insertion loss of 0.2 dB and an isolation of 50 dB from DC to 4 GHz. The pull-in voltage is 30 V and the switching time is 20  $\mu$ s. The mechanical life span is 10<sup>9</sup> switching cycles. The third design is a Ku-band SP2T switching circuit based on the toggle switch [40], as shown in Fig. 1.5c. Two toggle switches are perpendicular to each other where both have fixed connections with a flexible metal band to two output ports. When one toggle switch is on, the switch can be connected to the input port and the signal is routed to the output port. This SP2T switching circuit exhibits the insertion loss of 0.96 dB and the isolation of 30 dB from 7 to 20 GHz. The switching voltages are 30 V to close and 35 V to open. The fourth design is a double cantilever beam MEMS switching circuit developed for wireless applications, as shown in Fig. 1.5d. Two beams are controlled by a single actuation electrode. An RF performance with 50-dB isolation below 5 GHz and <0.18-dB insertion loss up to 30 GHz was observed [41]. The fifth design is a 35- to 60-GHz SP2T MEMS switching circuit [42] in which two resistive series switches are placed at the end of each output line and a short-ended 50  $\Omega$  line is connected at the cross-junction, as shown in Fig. 1.5e. When one switch is actuated, the open-ended line formed by the open state of the switch and the short-ended line

Fig. 1.5 Schematic of different types of SP2T switching circuits

comprises double resonance pair which transforms to be open at the cross-junction. This circuit presents the insertion loss below 1 dB and the isolation higher than 19 dB from 35 to 60 GHz. The actuation voltage is 35 V. All SP2T switching circuits use vertical MEMS switches. Only one lateral SP2T MEMS switching circuit was reported for satellite-based communications [43], as shown in Fig. 1.5 f. It uses thermal-actuated lateral MEMS switch fabricated by silicon deep reactive ion etching (DRIE) process. The microstrip transmission is fabricated on a glass wafer separately. The two wafers are bonded together and the device is packaged using an alumina cavity package, with DC and RF contacts on opposite sides. The isolation of this SP2T switching circuit is better than 50 dB at 1–6 GHz. The insertion loss is 1 dB at 2 GHz and 1.7 dB at 6 GHz. Table 1.2 compares the characteristics of different types of RF MEMS SPDT switching circuits.

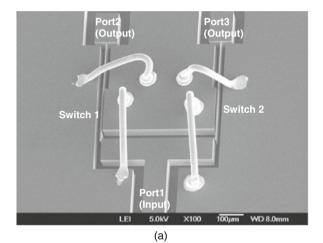

There is very limited work on other single-pole-multiple-throw switching circuits. A single-pole-three-throw (SP3T) switching circuit has been implemented in hybrid form where three cantilever beams are micromachined separately and then

|                           | lable 1.2        | Comparisor | I OI CHAFACIEH | SUICS DELWEED C |         | Comparison of characteristics between different MEMO 3F21 switching circuits | ning circuits |           |           |

|---------------------------|------------------|------------|----------------|-----------------|---------|------------------------------------------------------------------------------|---------------|-----------|-----------|

| References                | [1]              | [1]        | [2]            | [3]             | [5]     | [7]                                                                          | [8]           | [6]       | This work |

| Actuation mechanism       | ES               | ES         | ES             | ES              | ES      | ES                                                                           | ES            | Therm     | ES        |

| Frequency (GHz)           | 8-12             | 18 - 26    | 26 - 40        | DC to 15        | 12 - 18 | DC to 30                                                                     | 35-60         | 1-6       | 0.05 - 20 |

| Insertion loss (dB)       | 0.81             | 0.43       | 0.3            | 0.1 - 0.2       | 0.96    | 0.18                                                                         | 0.5 - 1       | 0.2 - 1.7 | 0.2 - 0.9 |

| Return loss (dB)          | I                | I          | 40             | I               | 17      | 30                                                                           | 10 - 24       | Ι         | 16.3 - 33 |

| Isolation (dB)            | 20.3             | 28.7       | 30             | 40              | 30      | 50                                                                           | 19-26         | 50        | 65-26     |

| Switching voltage (V)     | 6                | 6          | Ι              | 30              | 30/on   | 15                                                                           | 35            | б         | 23        |

|                           |                  |            |                |                 | 35/off  |                                                                              |               |           |           |

| Switching speed (µs)      | 52/on<br>213/off | I          | I              | 20              | I       | 60                                                                           | I             | I         | 35        |

| Size (mm <sup>2</sup> )   | 17.4             | 4.4        | I              | I               | I       | I                                                                            | 2             | 64        | 1.48      |

| ES – electrostatic; therm | ierm – thermal   |            |                |                 |         |                                                                              |               |           |           |

Table 1.2Comparison of characteristics between different MEMS SP2T switching circuits

integrated on an alumina substrate using flip-chip technology [44]. It exhibits the insertion loss of 0.5 dB at 16 GHz and the isolation of 20 dB at 18 GH. An SP3T switching circuit is proposed in [45], where the circuit consists of three resistive series switches based on fixed–fixed beam architecture in a coplanar environment. A single-pole-four-throw (SP4T) switching circuit using four series switches is developed in [46], which shows good match up to 20 GHz with an isolation of 50 dB at 10 GHz. A single-pole-eight-throw (SP8T) switching circuit using the rotary switch is reported [47], which has an insertion loss of 2.16 dB and an isolation of 31 dB at 20 GHz.

#### 1.5 Electromagnetic Band Gap (EBG) Structures for RF Circuits

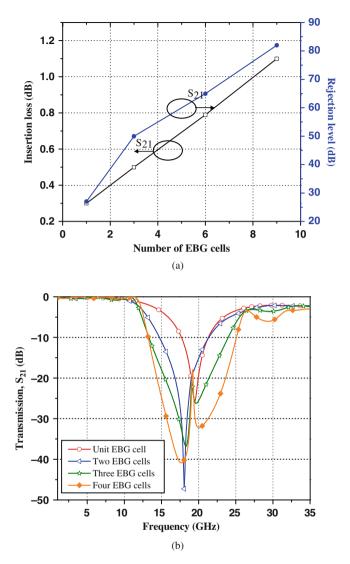

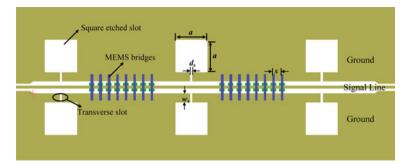

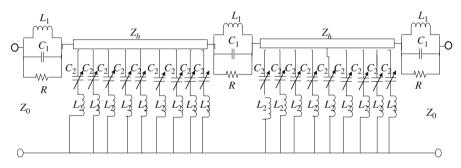

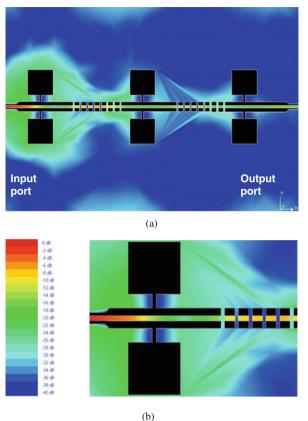

Electromagnetic band gap (EBG) structures are periodic structures that have attracted much attention in the microwave and millimeter-wave community due to their filtering properties or inhibition of signal propagation in certain directions. Electromagnetic crystal structures are invented for microwave and optical wavelengths [48–51]. Planar EBG structures offer tremendous application possibilities for active and passive devices because these structures exhibit wide bandpass and band rejection properties at microwave and millimeter wave frequencies [52-56]. For compact design, the passband of the EBG structures is used as a slow wave medium. On the other hand, the stopband is used to suppress the surface waves, leakage, and spurious transmission. EBG structures can have various design structures such as bumpy or corrugated surfaces, metal pads or high impedances surface, and planar EBG structures. Generally, the ground plane is perturbed by EBG structures with different shape and different lattice structures. The shape may be uniform or non-uniform circular, square, rectangular, triangular patterned and the structures are named on the basis of the grid arrangement such as square, rectangular, triangular, and honey-comb. Different shapes and sizes of EBG structures provide different S-parameter performances. Due to their unique properties, the EBG structures can be used to design microwave components and devices for different applications such as filters [57–60], mixers, antennas [61, 62], oscillator, power amplifiers [63, 64], and phase array.

Tunable band gap and bandpass performances are desirable in many applications. Semiconductor varactor diodes have been considered in tunable EBGs. Although semiconductor varactors offer integration possibilities, EBG structures based on such varactors suffer from high losses and small tunability at high microwave frequencies, where integration is potentially possible due to the small wavelengths and sizes. By incorporating RF MEMS switches and the EBG filters, a new paradigm has been opened for the development of state-of-the-art tunable filters. These tunable filters are miniaturized with high Q, wider rejection level, low insertion loss and enable the generation of tunable bandstop filters.

#### 1.6 Tunable EBG Bandpass Filters and Reconfigurable Circuits

The goal of many commercial and military systems is the ability to easily reconfigure or switch the frequency of operation, the output power, and the input impedance of the system [65–67]. Changing the frequency of operation means the resonant frequency must be reconfigured, together with the bandpass filter central frequency, the local oscillator frequency, and the matching networks for the low noise amplifiers and power amplifiers. In satellite systems, the switching networks are used for coaxial switches, while in base station systems, they are implemented using PIN diodes except after the power amplifiers. PIN diode switches are less expensive compared to coaxial switches, but require input and output amplifiers to compensate for the loss introduced by the switching networks. Coaxial switches result in outstanding isolation, insertion loss and can handle high power, but they are heavy, bulky, and expensive. RF MEMS switches can easily meet the isolation requirement of  $N \times N$ switching matrices making the system smaller and lighter which is essential for satellite communications [68].

In many portable applications, the antenna input impedance is strongly dependent on the position of the portable device, and low-loss reconfigurable matching network at the input of the antenna would result in substantial performance improvement. Reconfigurable MEMS switching circuits can be used to generate a large range of impedance loci which are necessary for transistor and diode characterization (gain, noise, conversion loss, etc.). Moreover, the RF MEMS devices generate low intermodulation products which are essential when the reconfigurable circuit comes before the low noise amplifier/mixer chain.

The filters are custom-machined, carefully assembled, tuned, and calibrated. Typically tracking filters are mechanically tuned by adjusting the cavity dimensions of the resonator or magnetically altering the resonant frequency of a ferromagnetic YIG element, which have multioctave bandwidths and high quality factor (Q) resonators [69, 70]. They also consume considerable amount of DC power (0.75–3 W) and their linearity is not high. Neither of these approaches can result in miniaturization or produced in large volumes for wireless communication systems. Solid-state varactors can provide a wide tuning range, but there are losses and linearity problems at microwave frequencies [71, 72]. The semiconductor-based varactors have a quality factor (Q) as low as 2 or 3 which can be associated with fixed capacitors in series in order to increase the Q of the resulting resonator, but in this case the tuning range is decreasing. In general, losses can reduced by using a weak coupling between the resonator and the varactor; higher Q means lower tuning. In contrast, employing MEMS technology enables the construction of miniaturized tunable filters that exhibit low-loss, low power consumption, and excellent linearity. The successful application of MEMS fabrication processes can reduce the overall size, weight, and cost of RF-integrated systems and making them attractive for many commercial and military applications [73, 74].

The RF MEMS switching circuits may also allow the development of low power systems based on tunable antennas, low-noise tunable oscillators, tunable filters, and tunable matching networks. The ultimate goal is to integrate the whole front-end system on a chip. The main bottleneck is represented not by the inductors or switches but by the low-loss (high Q) filters, diplexers, and crystal reference. The filters are currently being addressed using film bulk acoustic resonator (FBAR) technology and MEMS resonators. However, using the RF MEMS fabrication allows the elimination of off-chip inductor in the oscillator circuit making the integration of the tunable filter on a single chip possible. EBG structures and MEMS switches will be used to design tunable bandpass and reconfigurable filters.

#### 1.7 Capacitive Switching Bandpass Filters

When frequency spectrum gets crowded with a large number of communication devices operating in a particular band, filter is becoming more and more critical. Tunable bandpass filters greatly simplify the design of transceiver and play a major role, especially in the area of wideband and multimode transceivers. In signal processing and communication systems, it is often desirable to reject unwanted frequencies from a signal. However, it is undesirable to use multiple filters since large surface area are occupied. Therefore, it is desirous to use a tunable filter to track blocks for multi-band telecommunication systems, radiometers, and wideband radar systems.

Many civil and military telecommunication and radar systems, such as electronic warfare, software programmable RF front-end and digital receivers, require RF tunable bandpass filters to be as flexible as possible in terms of center frequencies and bandwidth. The tunable bandpass filter which is tunable over a wide frequency range also offers high rejection [75, 76]. Generally, the tunable bandpass filters can be classified into three basic categories: mechanically tunable filters, magnetically tunable filters and electronically tunable filters [77–89]. However, none of these satisfies the requirements of miniaturization and mass production.

In recent years, tunable bandpass filters based on MEMS technology which brings much improvement in the trade-offs between the tuning range and the losses in filter designs are widely studied. Capacitive switch and DC-contact switch can be used to construct these MEMS tunable bandpass filters.

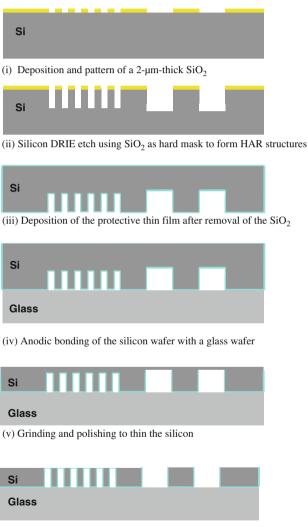

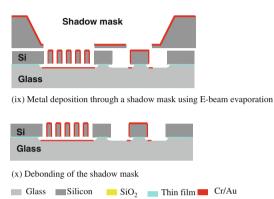

#### **1.8 Substrate Transfer Process**

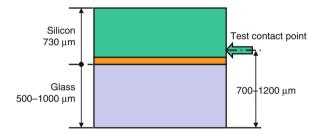

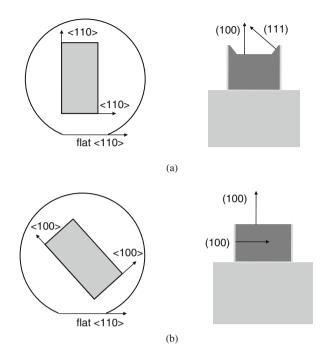

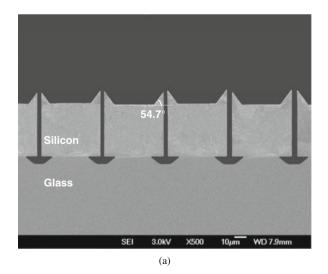

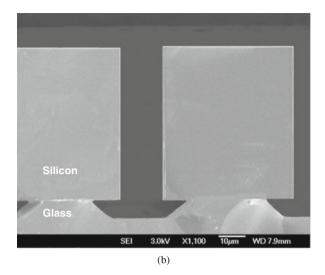

High aspect ratio (HAR) is desired to provide sufficient lateral capacitance, to increase the sensitivity of the sensor and to suppress the out-of-plane motion for many MEMS devices and components, such as the comb-drive actuators, the inertial sensors, and the variable capacitors. Different fabrication processes such as DRIE for silicon-on-insulator (SOI)-based process and silicon-on-glass (SOG)-based process are developed for high aspect ratio suspended silicon structures.

The high aspect ratio structures are etched in a silicon wafer using reactive ion etching (RIE) technique, followed by the deposition of a thin layer of silicon dioxide

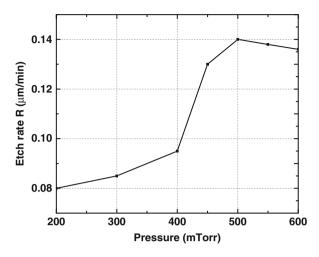

$(SiO_2)$ . After removal of SiO<sub>2</sub> at the trench bottom, MEMS structures are released using a silicon isotropic dry etching. Finally, metal is deposited [90, 91]. Only a normal silicon wafer and single mask are needed to form suspended structures with thickness of 20 µm and aspect ratio greater than 10. However, this process has two shortcomings. First, the etching depth varies with the trench width of the structures due to the aspect-ratio-depending-etching (ARDE) effect of the DRIE. Second, the release process sacrifices some silicon of the structures and results in irregular shape at the bottom of the silicon structures. The two problems lead to the deviation of the mechanical performance of the device. SOI-based process can avoid those problems well. In the SOI wafer, the device silicon layer with uniform thickness is separated from the handle silicon layer by a buried oxide layer. After deposition and patterning of the hard mask, the device layer is etched using DRIE. Then, the MEMS structures are released using wet etching of the buried oxide or DRIE over-etching [92, 93]. A glass substrate is more favorable than a silicon substrate for high-frequency applications because of its low-loss characteristic [94–96]. The straightforward method to construct devices or circuits is to first build RF circuits on a silicon wafer or a SOI wafer and then transfer them to a glass substrate [94]. Bulk silicon dissolved wafer process is developed in such a way to fabricate 1- to  $25-\mu$ mthick MEMS structures on a glass substrate, in which device structures are etched on a silicon wafer and heavily boron doped, then the silicon wafer is anodically bonded to a glass followed by the silicon dissolving to leave heavily boron-doped devices attached to the glass substrate [97]. However, it is difficult to fabricate thick MEMS structures using the silicon-dissolved wafer process due to the limitation of the diffusion process. The typical diffusion time is 15-20 h for a diffusion depth of 15–20  $\mu$ m. In order to supply thick device silicon layer (>30  $\mu$ m) on the glass, the conventional SOG process is widely used [98–100]. In the conventional SOG process, some shallow trenches are etched in a glass wafer or the backside of a silicon wafer first. After the silicon wafer is anodically bonded to a glass wafer, the silicon wafer is thinned from the backside using either mechanically grinding or chemically etching with KOH. Then, the MEMS structures are aligned to the shallow trenches through a double-side alignment, followed by the formation of the high-aspect-ratio structures by etching through the silicon layer using DRIE process. However, the conventional SOG-based process has three shortcomings. First, the Si-glass stack always bows or warps after anodic bonding due to residual stress of the bonding. Therefore, double-side alignment and yield are restrained. Second, since the glass is a poor thermal conductor, the substrate temperature ramps rapidly during the DRIE process. Therefore, it worsens the DRIE etching quality of the high-aspect-ratio structures. Third, since glass is an insulating material, the notching effect is hash. Ionization of low frequencies (380 kHz) in the high-density inductively coupled plasma (ICP) etch tool can reduce the notching effect by removing the accumulated charges on the insulating surfaces. However, when the etching depth is large  $(>100 \ \mu m)$  and over-etching lasts long time, notching effect damages structures. To avoid the notching effect, a metal layer can be deposited and patterned on glass or on silicon before anodic bonding [100].

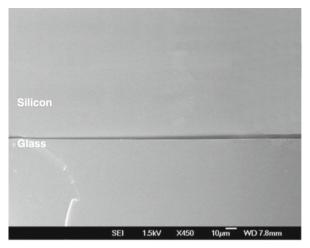

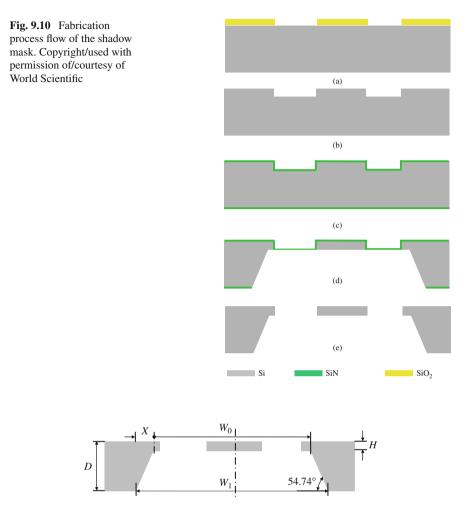

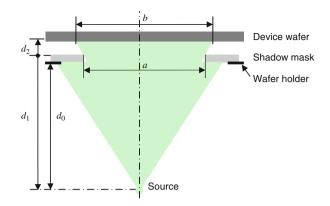

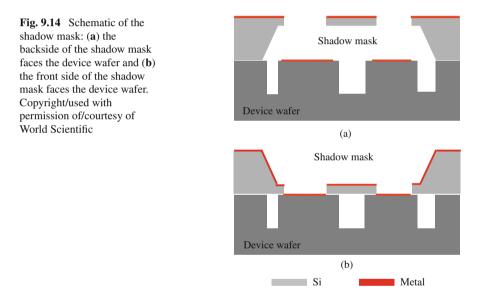

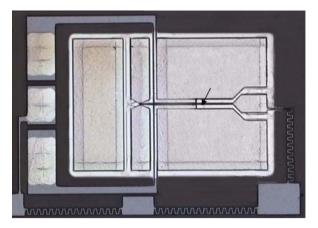

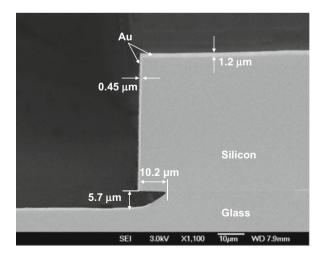

In Chapter 9, a new substrate transfer process is developed to fabricate highaspect-ratio silicon-suspended structures with large thickness (>30  $\mu$ m) on a glass substrate. This fabrication process is to first pattern the high-aspect-ratio silicon structure in desired shapes using the DRIE process. Then, the silicon structure is transferred to the glass substrate using a Si/thin film/glass anodic bonding process followed by two silicon thinning processes. Finally, the suspended structure is released by a self-aligned etching of the glass. This fabrication process voids all the problems in the conventional SOG-based process. The design of the fabrication process is described in Section 9.1. The three key unit processes – silicon/thin film/glass anodic bonding, silicon thinning using KOH etch, and metal deposition using a shadow mask – are explored in Sections 9.2, 9.3, and 9.4, respectively. The summary is drawn in Section 9.5.

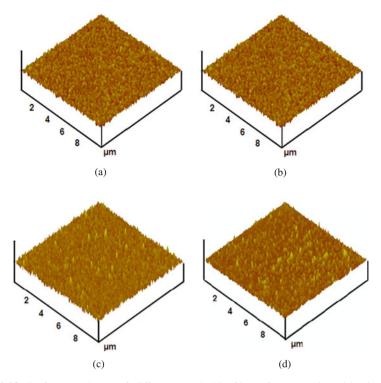

#### **1.9 Surface Planarization Process**

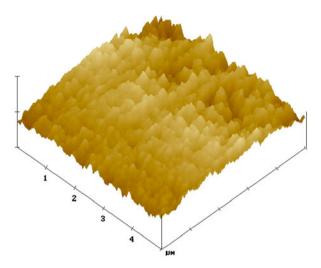

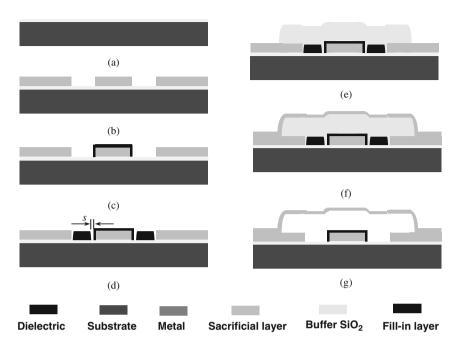

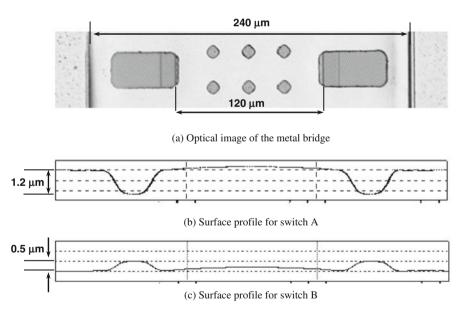

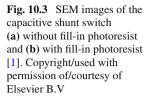

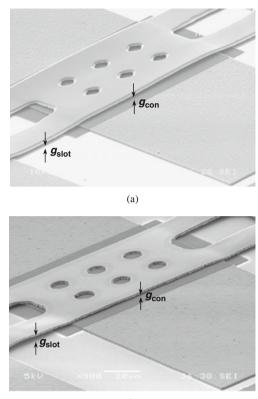

MEMS fabrication processes can be divided into surface micromachining process and bulk micromachining process. In this work, the surface micromachining process is used for the fabrication of the capacitive switches and the switch circuits. The planarization of the metal bridge plays a significant role in reducing the contact area between the bridge and the dielectric layer. Specially, the surface planarization processes are developed for a flat metal bridge and reduces the roughness of the dielectric layer [101–104]. In this book, a new planarization process is proposed by filling the CPW slot with photoresist that can effectively improve the flatness of the bridge. Besides the surface planarization, surface roughness is another important consideration to improve the intimate contact between the metal bridges and the dielectric layer when the metal bridges are driven down. Therefore, all fabrication issues related to the RF effects of the metal bridge flatness and the surface roughness of the dielectric layer will be discussed in Chapter 10.

#### References

- K. E. Petersen, "Micromechanical membrane switches on silicon," IEEE Trans. Electron Devices Vol. 23(4), 1976, pp. 376–386.

- K. E. Petersen, "Dynamic micromechanics on silicon: techniques and devices," IEEE Trans. Electron Devices Vol. ED-25, 1978, pp.1241–1250.

- 3. M.-A. Grétillat, F. Grétillat and N. F. de Rooij, "Micromechanical relay with electrostatic actuation and metallic contacts," J. Micromech. Microeng. Vol. 9, 1999, pp. 324–331.

- H. Sehr, A. G. R. Evans, A. Brunnschweiler, G. J. Ensell, C. G. J. Schabmueller, "Design and fabrication of a thermally actuated microrelay based on vertical bimorphs," Eurosensors XVI, the 16th European Conference on Solid-State Transducers, Prague, Czech Republic, 2002, pp. 752–755.

- J. A. Wright and Y.-C. Tai, "Magnetostatic MEMS relays for the miniaturization of brushless DC motor controllers," Tech. Digest, 12th IEEE Int. Conf. on Microelectromechanical Systems, Orlando Florida, USA, 1999, pp. 594–599.

- H. Hosaka, K. Kuwano and K. Yanagisawa, "Electromagnetic microrelays: concepts and fundamental characteristic," Sensor. Actuator. A Vol. 40, 1994, pp. 41–47.

- W. P. Taylor, M. G. Allen and C. R. Dauwalter, "Batch fabricated electromagnetic microrelays," Proc. 45th Relay Conf., Lake Buena Vista Florida, USA, 1997, pp. 8.1–8.6.

- W. P. Taylor and M. G. Allen, "Integrated magnetic microrelays: normally open, normally closed, and multi-pole devices," Tech. Digest 1997 Int. Conf. on Solid-State Sensors and Actuators, Chicago, USA, 1997, pp. 1149–1152.

- H. A. C. Tilmans et al., "A fully-packaged electromagnetic microrelay," Tech. Digest. 12th IEEE Int. Conf. on Microelectromechanical Systems, Orlando Florida, USA, 1999, pp. 25–30.

- S. N. Qiu, C. X. Qiu, I. Shih, M. Yu, G. Brassard and G. Seguin, "Development of a microwave microelectromechanical system switch," J. Vac. Sci. Technol. A Vol. 20(3), 2002, pp. 966–970.

- J. F. Dickson, "On-chip high-voltage generation in NMOS integrated circuits using an improved voltage multiplier technique," IEEE J. Solid State Circuits Vol. SC-11(3), 1976, pp. 374–378.

- C. Vaughan, "RF MEMS components for radio architecture," 2001 Sensors Expo, Chicago, IL, USA, 5–7 June, 2001.

- S. Roy and M. Mehregany, "Fabrication of electrostatic nickel microrelays by nickel surface micromachining," Proc. IEEE Int. Conf. Micro-electro-mechanical Systems, Amsterdam, Netherlands, 1995, pp. 353–357.

- S. Roth, C. Marxer, G. Feusier and N. F. de Rooij, "One mask nickel micro-fabricated reed relay," Proc. 13th IEEE Int. Conf. Micro-electro-mechanical Systems, Miyazaki, Japan, 2000, pp. 176–180.

- R. Wood, R. Mahadevan, V. Dhuler, B. Dudley, A. Cowen, E. Hill and K. Markus, "MEMS microrelay," Mechatronics Vol. 8, 1998, pp. 535–547.

- J. Simon, S. Saffer and C.-J. Kim, "A micromechanical relay with a thermally-driven mercury micro-drop," Proc. IEEE, 9th Ann. Int. Workshop on Microelectromechanical Systems, San Diego CA, USA, 1996, pp. 515–520.

- S. Saffer, J. Simon and C.-J. Kim, "Mercury-contact switching with gap-closing microcantilever," Proc. SPIE, Vol. 2882, 1996, pp. 204–208.

- J. Simon, S. Saffer, F. Sherman and C.-J. Kim, "Lateral polysilicon microrelay with a mercury microdrop contact," IEEE Trans. Ind. Electron. Vol. 45(6), 1998, pp. 854–860.

- J. Kim, W. Shen, L. Latorre and C.-J. Kim, "A micromechanical switch with electrostatically driven liquid-metal droplet," Sensor. Actuator. Vol. 97–98, 2002, pp. 672–679.

- N. D. Masters and L. L. Howell, "A self-retracting fully compliant bistable micromechanism," J. MEMS Vol. 12(3), 2003, pp. 273–280.

- C.-L. Dai, K. Yen and P.-Z. Chang, "Applied electrostatic parallelogram actuators for microwave switches using the standard CMOS process, J. Micromech. Microeng. Vol. 11, 2001, pp. 697–702.

- Y. Wang, Z. Li, D. T. McCormick and N. C. Tien, "A low-voltage lateral MEMS switch with high RF performance," J. MEMS Vol. 13(6), 2004, pp. 902–911.

- Y. Wang, Z. Li, D. T. McCormick and N. C. Tien, "A micromachined RF microrelay with electrothermal actuation," Sensor. Actuator. A Vol. 103, 2003, pp. 231–236.

- Y. Wang, Z. Li, D. T. McCormick and N. C. Tien, "Low-voltage lateral-contact microrelays for RF applications," 15th IEEE Int. Conf. on Micro-electro-mechanical Systems, 2002, pp. 645–648.

- I. Schiele and B. Hillerich, "Comparison of lateral and vertical switches for application as microrelays," J. Micromech. Microeng. Vol. 10, 1999, pp. 146–150.

- Z. Li, D. Zhang, T. Li, W. Wang and G. Wu, "Bulk micromachined relay with lateral contact," J. Micromech. Microeng. Vol. 10, 2000, pp. 329–333.

- R. L. Borwick III, P. A. Stupar and J. De Natale, "A hybrid approach to low-voltage MEMS switches," Proc. 12th Int. Conf. Solid-State Sensors, Actuators and Microsystems (Transducer'03), Boston, MA, 2003, pp. 859–862.

- A. A. Ayon, N. J. Kolias and N. C. MacDonald, "Tunable, micromachined parallel-plate transmission lines," Proc. IEEE, 1995, pp. 201–208.

- 29. T. D. Kudrle, H. P. Neves and N. C. MacDonald, "Microfabricated single crystal silicon transmission lines," RAWCON'98 Proc., Colorado Springs CO, USA, 1998, pp. 269–272.

- A. Q. Liu, M. Tang, A. Agarwal and A. Alphones, Low-loss lateral micromachined switches for high frequency applications, J. Micromech. Microeng. Vol. 15, 2005, pp. 157–167.

- T. D. Kudrle, H. P. Neves and N. C. MacDonald, "A micromachined millimeter wave phase shifter," Transducers'99, Sendai, Japan, 1999, pp. 1276–1279.

- 32. J. R. Reid, "Dielectric charging effects on capacitive MEMS actuators," IEEE MTT-S International Microwave Symposium, RF MEMS Workshop, Phoenix, AZ, May 2001.

- G. M. Rebeiz, RF MEMS Theory, Design and Technology, Wiley-Interscience, New York, NY, 2003.

- D. Peroulis, S. P. Pacheco and L. P. B. Katehi, "RF MEMS switches with enhanced powerhandling capabilities," IEEE Trans. Microwave Theory Tech. Vol. 52(1), 2004, pp. 59–68.

- A. B. Yu, A. Q. Liu, Q. X. Zhang, A. Alphones, L. Zhu and S. A. Peter, "Improvement of isolation MEMS capacitive switch via membrane planarization," Sensor. Actuator. A: Phys. Vol. 119, 2005, pp. 206–213.

- S. P. Pacheco, D. Peroullis and L. P. B. Katehi, "MEMS single-pole double-throw (SPDT) X and K-band switching circuits," IEEE MTT-S Int. Microwave Symp. Dig., Phoenix AZ, USA, 2001, pp. 321–324.

- M. C. Scardelletti, G. E. Ponchak and N. C. Varaljay, "MEMS, Ka-band single-pole doublethrow (SPDT) switch for switched line phase shifters," IEEE Antenna. Propagat. Soc. Int. Symp., Kanagawa, Japan, June 2002, Vol. 2, pp. 2–5.

- D. Sievenpiper, H. J. Song, H. P. Hsu, G. Tangonan, R. Y. Loo and J. Schaffner, "MEMSbased switched diversity antenna at 2.3 GHz for automotive applications," The 5th Int. Symp. Wireless Personal Multimedia Communications, Honolulu Hawaii, USA, October 2002, Vol. 2, pp. 762–765.

- D. Hyman, A. Schmitz, B. Warneke, T. Y. Hsu, J. Lam, J. Brown, J. Schaffner, A. Walston, R. Y. Loo, G. L. Tangonan, M. Mehregany and J. Lee, "GaAs-compatible surface-micromachined RF MEMS switches," Electron. Lett. Vol. 35(3), 1999, pp. 224–226.

- B. Schauwecher, K. M. Strohm, T. Mack, W. Simon and J.-F. Luy, "Single-pole double-throw switch based on toggle switch," Electron. Lett. Vol. 39(8), 2003, pp. 668–670.

- K. Lee, R. Liu and B. C. Kim, "RF MEMS switch for wireless LAN applications," Proc. Int. Conf. MEMS, NANO Smart Systems (ICMENS'03), Banff Alberta, Canada, 2003.

- J.-H. Park, S. Lee and J.-M. Kim, "A 35-60 GHz single-pole double-throw (SPDT) switching circuit using direct contact MEMS switches and double resonance technique," 12th Int. Conf. Transducers, Solid-State Sensors, Actuators and Microsystems, Boston, USA, Vol. 2, June 2003, pp. 1796–1799.

- R. W. Moseley, E. M. Yeatman, A. S. Holmes, R. R. A. Syms, A. P. Finlay and P. Boniface, "Laterally actuated, low voltage, 3-port RF MEMS switch," Proc. MEMS, Turkey, Istanbul, 22–26 January 2006, pp. 878–880.

- M. Daneshmand and R. R. Mansour, "Fabrication and modeling of an SP3T RF MEMS switch," IEEE AP-Symposium and North American Radio Science Meeting, Columbus Ohio, USA, 2003, pp. 391–394.

- 45. E. K. I. Hamad, G. E. Nadim and A. S. Omar, "A proposed SP3T wideband RF MEMS switch," Proc. IEEE Vol. 3, 2004, pp. 2839–2842.

- 46. G. L. Tan, R. E. Mihailovich, J. B. Hacker, J. F. De Natale and G. M. Rebeiz, "Low-loss 2- and 4-bit TTD MEMS phase shifters based on SP4T switches," IEEE Trans. Microwave Theory Tech. Vol. 51(1), 2003, pp. 297–304.

- S. Pranonsatit, A. S. Holmes, I. D. Robertson and S. Lucyszyn, "Single-pole eight-throw RF MEMS rotary switch," IEEE J. MEMS Vol. 15(6), 2006, pp. 1735–1744.

- L. Brillouin, Wave Propagation in Periodic Structures, 2nd edn., Dover Publications, Inc., New York, NY, 1953.

- 49. D. Sievenpiper, L. Zhang, R. F. J. Broas, N. G. Alexopolous and E. Yablonovitch, "High impedance electromagnetic surface with a forbidden frequency band," IEEE Trans. Microwave Theory Tech. Vol. 47(11), 1999, pp. 2059–2074.

- A. Bayers, I. Rumsey, Z. Popvic and M.-P. May, "Surface wave guiding using periodic structures," IEEE–APS Dig., Salt Lake City Utah, USA, Vol. 1, 2000, pp. 342–345.

- D. Sivenpiper and E. Yablonovitch, "Eliminating surface currents with metallodielectric photonics crystal," IEEE-MTT-S Int. Microwave Symp. Dig., Baltimore MD, USA, Vol. 1, 1998, pp. 663–666.

- N. C. Karmakar, "Improved performance of photonic bandgap microstripline structures using Chebyshev distribution," Microwave Opt. Technol. Lett. Vol. 33(1), 2002, pp. 1–5.

- V. Radisic, Y. Qian, R. Coccioli and T. Itoh, "A novel 2-D photonic bandgap structures for microstrip lines," IEEE Microwave Guide Wave Lett. Vol. 8, 1998, pp. 66–71.

- B. Elamaran, I. M. Chio, L. Y. Chen and J. C. Chiao, "A beam-steerer using reconfigurable PBG ground plane," IEEE MTT-S Int. Microwave Symp. Dig., Boston MA, USA, 2000, pp. 835–838.

- 55. I. Chang and B. Lee, "Design of defected ground structures for harmonic control of active microstrip antenna," IEEE AP-S Int. Symp. Dig., Texas, USA, 2002, pp. 852–855.

- N. C. Karmakar and M. N. Mollah, "Investigations into nonuniform photonic-bandgap microstripline low-pass filters," IEEE Trans. Microwave Theory Tech. Vol. 51, 2003, pp. 564–572.

- M. L. Her, Y. Z. Wang, C. M. Chang and K. Y. Lin, "Coplanar waveguide (CPW) defected ground plane structure (DGS) for bandpass filter applications," Microwave Opt. Tech. Lett. Vol. 42, 2004, pp. 331–334.

- C. S. Kim, J. S. Park, D. Ahn and J. Lim, "A novel 1-D periodic defected ground structure for planar circuits," IEEE Microwave Wireless Comp. Lett. Vol. 10(4), 2000, pp. 131–133.

- D. Ahn, J. S. Park, C. S. Kim, J. Kim, Y. Qian and I. Itoh, "A design of low pass filter using novel microstrip defected ground structure," IEEE Trans. Microwave Theory Tech. Vol. 49(1), 2001, pp. 86–93.

- L. Garde, M. J. Yabar and C. D. Rio, "Simple modeling of DGS to design 1D PBG low pass filter," Microwave Opt. Tech. Lett. Vol. 37(3), 2003, pp. 228–232.

- H. Y. D. Yang, N. G. Alexopoulos and E. Yablonovitch, "Photonic bandgap materials for high gain printed circuit antennas," IEEE Trans. Antenna. Propagat. Vol. 45(1), 1997, pp. 185–187.

- S. Y. Lin and K. L. Wong, "A conical pattern annular ring microstrip antenna with a photonic bandgap ground plane," Microwave and Optical Tech. Lett. Vol. 30(3), 2001, pp. 159–161.

- V. Radisic, Y. Qian and I. Itoh, "Novel architectures for high efficiency amplifiers for wireless applications," IEEE Trans. Microwave Theory. Tech. Vol. 46(11), 1998, pp. 1901–1909.

- 64. C. Y. Hang, W. R. Deal, Y. Qian and I. Itoh, "High efficiency transmitter front end integrated with planar antennas and PBG," Asia-Pacific Microwave Conf., Australia, 2000.

- 65. R. E. Collin, Foundations for Microwave Engineering, McGraw-Hill, New York, NY, 1992.

- 66. D. M. Pozar, Microwave Engineering, Wiley, New York, NY, 1998.

- G. L. Matthaei, L. Yong and E. M. T. Jones, Microwave Filters, Impedance-Matching Networks, and Coupling Structures, McGraw-Hill, New York, NY, 1964.

- G. M. Rebeiz, RF MEMS Theory, Design, and Technology, 1st edn., Wiley, New York, NY, 2002.

- Y. Ishikawa, T. Nishikawa, T. Okada and S. Shinmura, "Mechanically tunable MSW bandpass filter with combined magnetic units," IEEE-MTT-S Int. Microwave. Symp. Dig., 1990, pp. 143–146.

- W. J. Keane, "YIG filters aid wide open receivers," Microwave J. Vol. 17(8), 1980, pp. 50–54.

- S. R. Chandler, I. C. Hunter and J. C. Gardiner, "Active varactor tunable bandpass filters," IEEE Microwave Guided Wave Lett. Vol. 3(3), 1993, pp. 70–71.

- A. R. Brown and G. M. Rebeiz, "A varactor-tuned RF filter," IEEE Trans. Microwave Theory Tech. Vol. 48(7), 2000, pp. 1157–1160.

- H. J. D. Santos, Introduction to Microelectromechanical (MEMS) Microwave Systems, Artech House, Norwood, MA, 1999.

- 74. H. J. D. Santos, "MEMS-A wireless vision," Proc. Int. MEMS Workshop, Singapore, 2001.

- 75. I. C. Hunter, L. Biloner, B. Jarry and P. Guillan, "Microwave filters application and technology," IEEE Trans. Microwave Theory Tech. Vol. 50, 2002, pp. 794–805.

- J. Uher and J. R. Hofer, "Tunable microwave and millimeter-wave bandpass filters," IEEE Trans. Microwave Theory Tech. Vol. 39, 1991, pp. 643–653.

- J. B. Tsui, Microwave Receivers with Electronic Warfare Applications, Wiley, New York, NY, 1992.

- H. Tanbakachi et al., "A broadband tracking YIG-tuned mixer for a state of the art spectrum analyzer," European Microwave Conference Dig., Rome, Italy, Sept. 1987, pp. 482–490.

- R. W. de Greese, "Low-loss gyromagnetic coupling through single crystal garnets," J. Appl. Phys. Vol. 30, 1958, pp. 1555–1559.

- P. S. Carter, "Equivalent circuit of orthogonal-loop-coupled magnetic resonance filters and bandwidth narrowing due to coupling resonance," IEEE Trans. Microwave Theory Tech. Vol. 18, 1970, pp. 100–105.

- R. F. Fierstal, "Some design considerations and realizations of iris-coupled YIG-tuned filters in the 12–40 GHz region," IEEE Trans. Microwave Theory Tech. Vol. 18, 1970, pp. 205–212.

- 82. H. Tanbakuchi D. Nicholson, B. Kunz and W. Ishak, "Magnetically tunable oscillators and filters," IEEE Trans. Magn. Vol. 25, 1989, pp. 3248–3253.

- S. R. Chandler, L. C. Hunter and J. C. Gordiner, "Active varactor tunable bandpass filters," IEEE Microwave Guided Wave Lett. Vol. 3, 1993, pp. 70–71.

- A. R. Brown and G. M. Rebeiz, "A varactor-tuned RF filter," IEEE Trans. Microwave Theory Tech. Vol. 48, 2000, pp. 1157–1160.

- I. C. Munter and J. D. Rhodes, "Electronically tunable microwave bandpass filters," IEEE Trans. Microwave Theory Tech. Vol. 30, 1982, pp. 1354–1360.

- K. Shen, F. Hui, W. Wong, Z. Chen, J. Lau, P. C. H. Chan and P. K. Ko, "A three-terminal SOI gated varactor for RF applications," IEEE Trans. Electron Devices Vol. 48, 2001, pp. 289–293.

- B. H. Mockly and Y. Zhang, "Strontium titanate thin films for tunable YBa2Ca3O7 microwave filters," IEEE Trans. Appl. Supercond. Vol. 11, 2001, pp. 450–453.

- A. Kozyrev, A. Ivanov, V. Keis, M. Khazov, V. Osadchy, T. Samoilova, O. Soldatenkov, A. Pavlov, G. Koepf, C. Mueller, D. Galt, T. Rivkin, "Ferroelectric films: nonlinear properties and applications in microwave devices," IEEE MTT-S Int. Microwave Symp. Dig., Baltimore MD, USA, Vol. 2, 1998, pp. 985–988.

- A. Tombak, J. Maria, F. T. Ayguavives, Z. Z. Jin, G. T. Stauf, A. I. Kingo and A. Mortazawi, "Voltage-controlled RF filter employing thin-film Barium-Strontium-titanate tunable capacitors," IEEE Trans. Microwave Theory Tech. Vol. 51, 2005 pp. 462–467.

- Z. L. Zhang and N. C. MacDonald, "A RIE process for submicron, silicon electromechanical structures," J. Micromech. Microeng. Vol. 2, 1992, pp. 31–38.

- K. A. Shaw, Z. L. Zhang and N. C. MacDonald, "SCREAM I: a single mask, singlecrystal silicon, reactive ion etching process for microelectromechanical structures," Sensor. Actuator. A Vol. 40(1), 1994, pp. 63–70.

- S. A. McAuley, H. Ashraf, L. Atabo, A. Chambers, S. Hall, J. Hopkins and G. Nicholls, "Silicon micromachining using a high-density plasma source," J. Phys. D: Appl. Phys. Vol. 34, 2001, pp. 2769–2774.

- A. A. Ayon, K. Ishihara, R. A. Braff, H. H. Sawin and M. A. Schmidt, "Microfabrication and testing of suspended structures compatible with silicon-on-insulator technology," J. Vac. Sci. Technol. B Vol. 17, 1999, pp. 1589–1593.

- R. Dekker, P. G. M. Baltus and H. G. R. Maas, "Substrate transfer for RF technology," IEEE Trans. Electron Devices Vol. 50(3), 2003, pp. 747–757.

- S. Seok, W. Choi and K. Chun, "A novel linearly tunable MEMS variable capacitor," J. Micromech. Microeng. Vol. 12, 2002, pp. 82–86.

- J. Kim, J. Park, C. Baek and Y. Kim, "The SiOG-based single-crystalline silicon (SCS) RF MEMS switch with uniform characteristics," J. Microelectromech. Syst. Vol. 13(6), 2004, pp. 1036–1042.

- Y. B. Gianchandani, K. Najafi, "A bulk silicon dissolved wafer process for microelectromechanical devices," J. Microelectromech. Syst. Vol. 1(2), 1992, pp. 77–85.

- B. Y. Majis, B. Bais and A. S. Tamsir, "Area-changed capacitive accelerometer using 3-mask fabrication process," Proc. SPIE Vol. 5276, 2004, pp. 482–488.

- 99. J. Chae, H. Kulah, and K. Najafi, "A CMOS-compatible high aspect ratio silicon-on-glass in-plane micro-accelerometer," J. Micromech. Microeng. Vol. 15, 2005, pp. 336–345.

- M. C. Lee, S. J. Kang, K. D. Jung, S. Choa and Y. C. Cho, "A high yield rate MEMS gyroscope with a packaged SiOG process," J. Micromech. Microeng. Vol. 15, 2005, pp. 2003–2010.

- 101. J. Y. Park, G. H. Kim, K. W. Chung and J. U. Bu, "Monolithically integrated micromachined RF MEMS capacitive switches," Sensor. Actuator. A: Phys. Vol. 89, 2001, pp. 88–94.

- E. J. J. Kruglick and K. S. J. Pister, "Lateral MEMS microcontact considerations," IEEE J. Microelectromech. Syst. Vol. 8, 1999, pp. 264–271.

- 103. S. L. Firebaugh, H. K. Charles, R. L. Edwards, A. C. Keeney and S. F. Wilderson, "Fabrication and characterization of a capacitive micromachined shunt switch," J. Vac. Sci. Technol. A Vol. 22(4), 2004, pp. 1383–1387.

- Z. J. Yao, S. Chen, S. Eshelman, D. Denniston and C. Goldsmith, "Micromachined low-loss microwave switches," J. Microelectromech. Syst. Vol. 8(2), 1999, pp. 129–134.

## Chapter 2 Lateral Series Switches

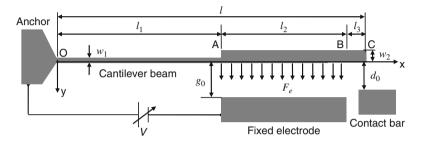

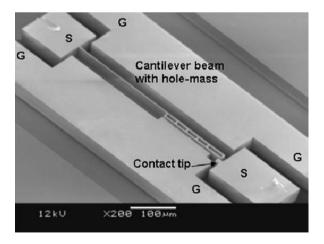

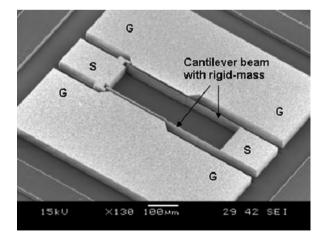

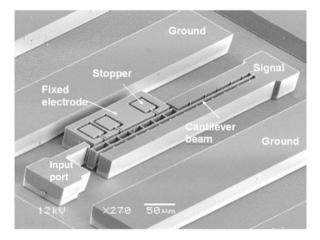

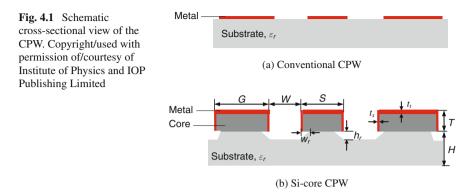

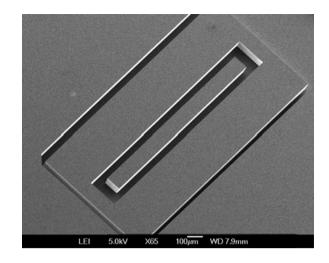

The objective of this chapter is to study the lateral RF MEMS series switch [1-14]. The switch consists of a silicon-core (Si-core) transmission line and a cantilever beam. The switch connects or disconnects with the RF circuit by the in-plane motion of the cantilever beam. The Si-core coplanar waveguide (CPW) transmission line is used to configure the switch. The Si-core CPW has the same advantage as the normal CPW, that is, it enables series and shunt elements connection without metal coating. The main advantages of the lateral switch are reliable mechanical performance and simple fabrication process.

This chapter is organized as follows. First, the RF design, circuit modeling and simulation of the lateral RF MEMS switch are presented. The RF performance of the switch can be improved by optimizing the electrical parameters of the switch. Second, the mechanical design and optimization of the cantilever beam of the lateral switch are discussed. The dynamic responses such as the switching time and the release time of the switch are studied. Finally, the experimental results of the lateral switch such as its insertion loss, return loss, isolation, threshold voltage, switching speed are discussed. Comprehensive modeling and design of the lateral switch are verified by extensive experiments for both electrical and mechanical characteristics.

#### 2.1 Electrical Design and Simulation

In this section, the RF circuit design and the lumped-element modeling of the lateral switch are discussed. The main purpose is to study the effect of the design parameters and to realize lateral switches with low insertion loss, high return loss, and high isolation. Since the switch is a metal-contact series switch, the on-state and the down-state of the switch and the off-state and the up-state of the switch are used interchangeably.

Min Tang and Ai Qun Liu

#### 2.1.1 RF Circuit Design of the Lateral Switch

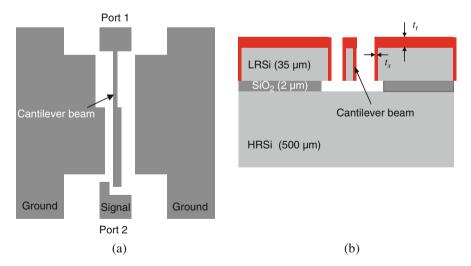

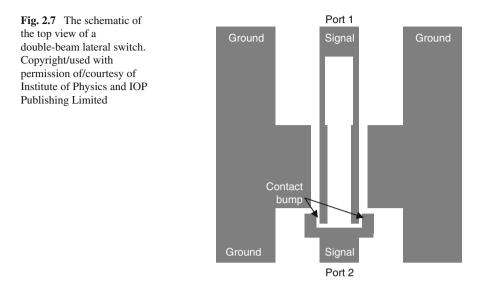

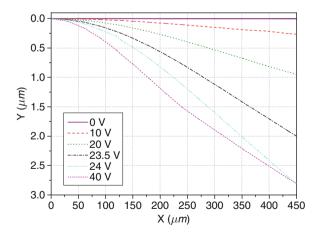

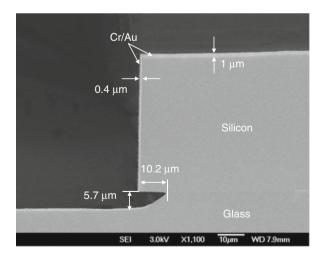

A lateral switch consists of a Si-core CPW and an electrostatic actuator, as shown in Fig. 2.1a. A cantilever beam is fixed at one port. The free end of the cantilever beam comes into contact with the contact bump at the other port upon turning on the switch. The cantilever beam serves as the signal line alone. The ground lines beside the cantilever beam are extended toward the cantilever beam to avoid drastic increase in the characteristic impedance. The width of the gaps between the cantilever beam and the ground lines is  $20-30 \,\mu$ m. The characteristic impedance of the cantilever beam section,  $Z_1$ , is about 78  $\Omega$  simulated by a 3D full-wave finite element method (FEM) analysis tool – Ansoft's high-frequency structure simulator (HFSS) V8.0 [15]. At the free end of the cantilever beam, one ground line protrudes toward the cantilever beam further to serve as a fixed electrode. Therefore, no additional fixed electrode is required. When sufficient DC bias voltage is applied between the cantilever beam and the ground line, the cantilever beam is pulled toward the fixed electrode by electrostatic force until its free end hits the contact bump, resulting in the on-state of the switch. When DC bias voltage is removed, the mechanical stress of the beam overcomes the stiction forces and pulls the cantilever beam away, resulting in the off-state of the switch. Due to the asymmetrical layout of the two ports, the S-parameters obtained from the two ports are not reciprocal. The return loss of port 2 is better than that of port 1 at the off-state since the open stub at port 2 is shorter than port 1. Hence, generally port 2 acts as the input port and port 1 acts as the output port to block more RF signal at the off-state of the switch. Figure 2.1 (b) shows the cross sectional view of the lateral switch. The switch is on a SOI wafer.

Fig. 2.1 Schematics of a lateral switch: (a) top view and (b) cross-sectional view. Copyright/used with permission of/courtesy of Institute of Physics and IOP Publishing Limited

The substrate is 500-µm-thick high-resistivity silicon (HRSi). The device layer is 35-µm-thick low-resistivity silicon (LRSi). The switch structures are made of LRSi. A thin layer of metal is coated on the top and sidewalls of the switch structures to propagate RF signal.

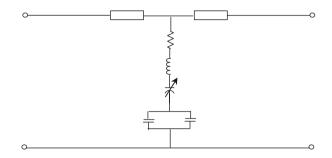

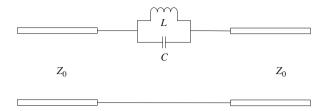

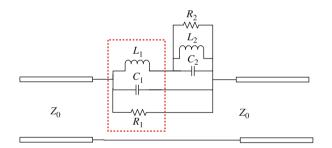

#### 2.1.2 RF Circuit Model of the Lateral Switch

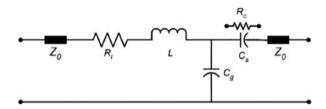

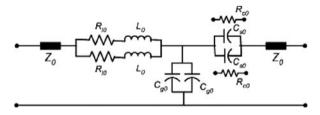

Figure 2.2 shows the equivalent circuit of the lateral switch. The model consists of a characteristic impedance,  $Z_0$ , for the input and output sections of the Si-core CPW; a line resistor,  $R_1$ , of the cantilever beam; a line inductor, L, of the cantilever beam; a switch series capacitor,  $C_s$  (off-state) or a contact resistor,  $R_c$  (on-state); and a shunt coupling capacitor,  $C_g$ . Except  $Z_0$ , other parameters are allowed to vary to fit the measurement results or the simulation results. The equivalent circuit is modeled using the design tool of Agilent EESof's Advanced Design System (ADS).

Fig. 2.2 The equivalent circuit of the lateral switch. Copyright/used with permission of/courtesy of Institute of Physics and IOP Publishing Limited

According to the *T*-equivalent circuit model,  $S_{21}$  of the circuit can be given by [16]

$$S_{21} = \frac{2}{2 + (Z_0 + Z_1 + Z_2)/Z_3 + \left(Z_1 + Z_2 + \frac{Z_1 Z_2}{Z_3}\right)/Z_0}$$

(2.1a)

where

$$Z_1 = R_1 + j\omega L \tag{2.1b}$$

$$Z_2 = \begin{cases} \frac{1}{j\omega C_{\rm s}} & \text{at the open state} \\ R_{\rm c} & \text{at the close state} \end{cases}$$

(2.1c)

$$Z_3 = \frac{1}{j\omega C_{\rm g}} \tag{2.1d}$$

$\omega$  is the angular frequency ( $\omega = 2\pi f$ , f is the signal frequency).

At the off-state of the switch, the switch capacitance,  $C_s$ , is an important factor that affects the isolation of the switch. When

$$S_{21} << -10 \,\mathrm{dB} \text{ and } \omega C_{\mathrm{s}} Z_0 \left[ 2 - \omega^2 C_{\mathrm{g}} L + \frac{C_{\mathrm{g}}}{C_{\mathrm{s}}} + \frac{R_{\mathrm{l}}}{Z_0} \left( 1 + \frac{C_{\mathrm{g}}}{C_{\mathrm{s}}} \right) \right] << 1$$

the isolation of switch can be approximately expressed as

$$S_{21} \approx j2\omega C_{\rm s} Z_0 \tag{2.2}$$

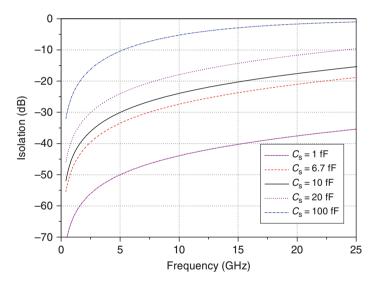

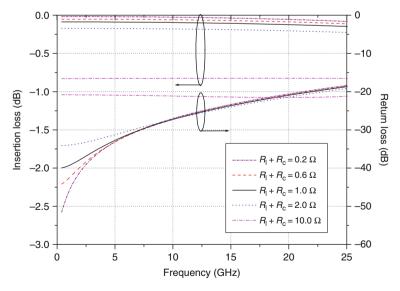

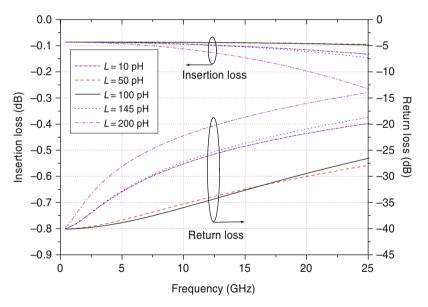

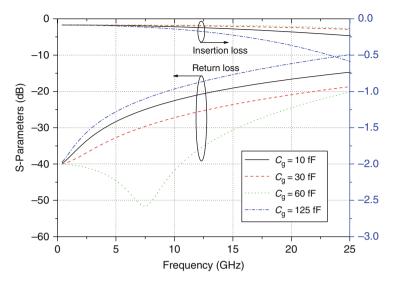

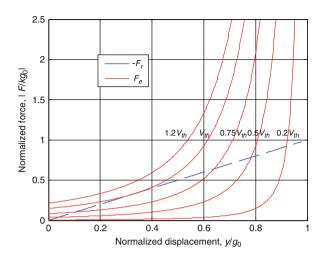

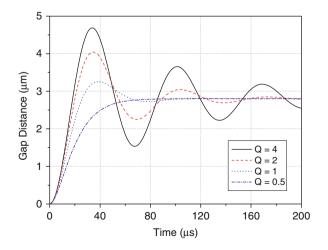

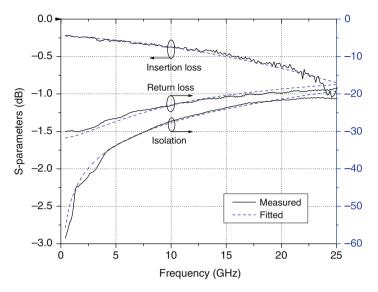

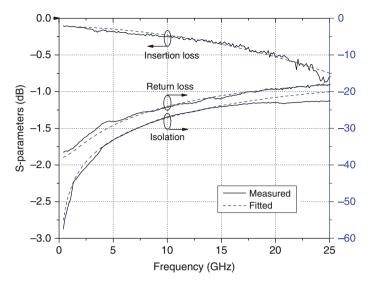

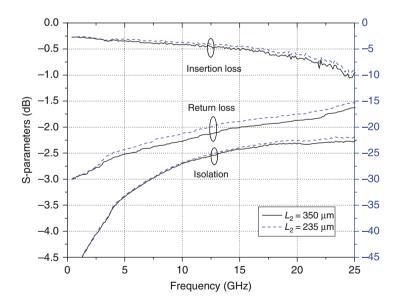

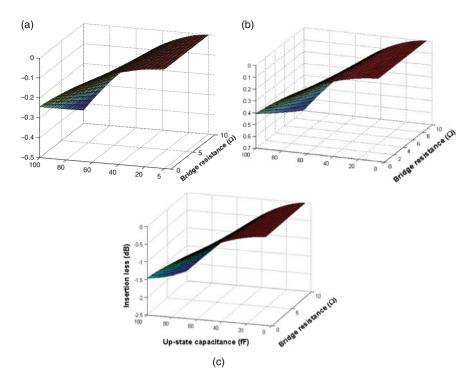

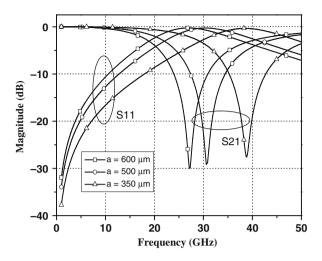

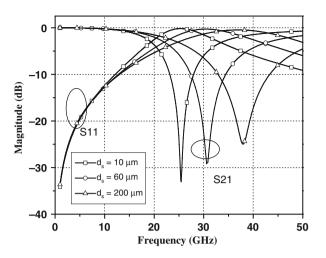

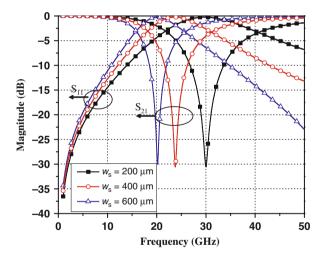

Therefore, the series capacitance,  $C_s$ , of the off-state switch can be extracted from the simulated or measured isolation of the switch using Eq. (2.2). Figure 2.3 shows the simulated isolation of an off-state switch with various series capacitances of  $C_s$ . The isolation of the off-state switch increases with the decrease in  $C_s$ . The equivalent series capacitance  $C_s$  of our practical lateral switches is 3–10 fF. Up to 25 GHz, the isolation is higher than 25 dB for  $C_s = 3$  fF and 15 dB for  $C_s = 10$  fF.

**Fig. 2.3** Simulation results of *S*-parameters with various capacitances  $C_s$  at the off-state of the lateral switch ( $R_l = 1 \ \Omega$ , L = 148 pH,  $C_g = 30 \text{ fF}$ )

At the on-state of the switch, the insertion loss and the return loss can be expressed as

$$S_{21} = \frac{2}{2 + K_1 + j \cdot K_2} \tag{2.3a}$$

$$S_{11} = \frac{K_1 + j \cdot K_3}{2 + K_1 + j \cdot K_2}$$

(2.3b)

#### 2.1 Electrical Design and Simulation

where

$$K_{1} = \frac{R_{1} + R_{c}}{Z_{0}} - \omega^{2} C_{g} L \left( 1 + \frac{R_{c}}{Z_{0}} \right)$$

(2.3c)

$$K_{2} = \omega \left[ C_{g} \left( R_{l} + R_{c} + Z_{0} + \frac{R_{l}R_{c}}{Z_{0}} \right) + \frac{L}{Z_{0}} \right]$$

(2.3d)

$$K_{3} = \omega \left[ C_{g} \left( R_{l} - R_{c} - Z_{0} + \frac{R_{l}R_{c}}{Z_{0}} \right) + \frac{L}{Z_{0}} \right]$$

(2.3e)

At low frequencies, when  $2+K_1 \gg 0$  and  $K_2 \ll 2 + (R_1 + R_c)/Z_0$ , the insertion loss and the return loss of the switch can be simplified as

$$S_{21} \approx 2/[2 + (R_1 + R_c)/Z_0]$$

(2.4a)

$$S_{11} \approx (R_{\rm l} + R_{\rm c}) / [2Z_0 + (R_{\rm l} + R_{\rm c})]$$

(2.4b)