### **REUSE METHODOLOGY MANUAL**

### FOR SYSTEM-ON-A-CHIP DESIGNS

### **SECOND EDITION**

#### **Trademark Information**

Synopsys, COSSAP, and Logic Modeling are registered trademarks of Synopsys, Inc.

Cyclone, Formality, Floorplan Manager, Module Compiler, Power Compiler, SWIFT Interface, Test Compiler, VSS Expert, and VSS Professional are trademarks of Synopsys, Inc.

Mentor Graphics is a registered trademark of Mentor Graphics Corporation.

DFTAdvisor, FastScan, FISPbus, FlexTest, QuickPower, QuickSim II, and Seamless CVE are trademarks of Mentor Graphics Corporation.

All other trademarks are the exclusive property of their respective holders and should be treated as such.

### **REUSE METHODOLOGY MANUAL**

### FOR SYSTEM-ON-A-CHIP DESIGNS

### **SECOND EDITION**

by

Michael Keating Synopsys, Inc.

### **Pierre Bricaud**

Mentor Graphics Corporation

SPRINGER SCIENCE+BUSINESS MEDIA, LLC

ISBN 978-1-4613-7289-9 ISBN 978-1-4615-5037-2 (eBook) DOI 10.1007/978-1-4615-5037-2

#### Library of Congress Cataloging-in-Publication Data

A C.I.P. Catalogue record for this book is available from the Library of Congress.

**Copyright** <sup>©</sup> 1999 by Springer Science+Business Media New York Originally published by Kluwer Academic Publishers in 1999 Softcover reprint of the hardcover 2nd edition 1999 All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, mechanical, photo-copying, recording, or otherwise, without the prior written permission of the publisher, Springer Science+Business Media, LLC.

Printed on acid-free paper.

# Table of Contents

|   | Forewordxv |       |                                   |      |  |

|---|------------|-------|-----------------------------------|------|--|

|   | Pr         | eface | to the Second Edition             | xvii |  |

|   | Ac         | know  | ledgements                        | xxi  |  |

| 1 | In         | trodu | ction                             | 1    |  |

|   | 1.1        | Goals | of This Document                  | 2    |  |

|   |            | 1.1.1 | Assumptions                       | 3    |  |

|   |            | 1.1.2 | Definitions                       |      |  |

|   |            | 1.1.3 | Virtual Socket Interface Alliance | 4    |  |

|   | 1.2        | Desig | n for Reuse: The Challenge        | 4    |  |

|   |            | 1.2.1 | Design for Use                    | 5    |  |

|   |            | 1.2.2 | Design for Reuse                  | 5    |  |

|   |            | 1.2.3 | Fundamental Problems              | 6    |  |

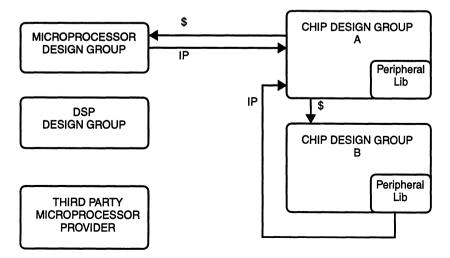

|   | 1.3        | Desig | n Reuse: A Business Model         | 7    |  |

|   |            | 1.3.1 | Changing Roles in SoC Design      | 7    |  |

|   |            | 1.3.2 | Retooling Skills for New Roles    |      |  |

|   |            | 1.3.3 | Sources of IP for SoC Designs     |      |  |

|   |            | 1.3.4 | Cost Models Drive Reuse           |      |  |

|   |            | 1.3.5 | How Much Reuse and When           |      |  |

|   |            |       |                                   |      |  |

| 2 | Tł  | ne Syst | em-on-a-Chip Design Process                             | 11   |

|---|-----|---------|---------------------------------------------------------|------|

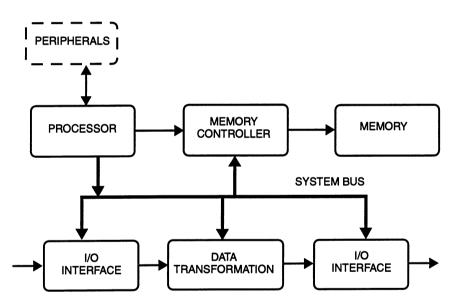

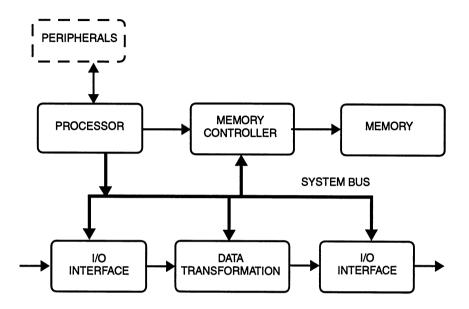

|   | 2.1 | A Can   | onical SoC Design                                       | 11   |

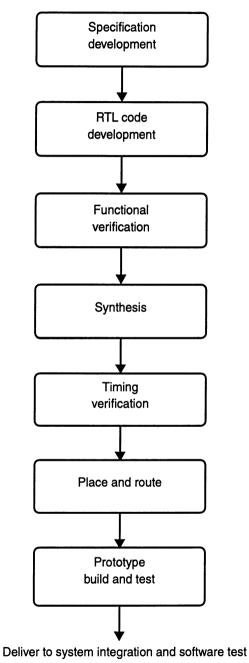

|   | 2.2 |         | 1 Design Flow                                           |      |

|   |     | 2.2.1   | Waterfall vs. Spiral                                    |      |

|   |     | 2.2.2   | Top-Down vs. Bottom-Up                                  |      |

|   |     | 2.2.3   | Construct by Correction                                 |      |

|   |     | 2.2.4   | Summary                                                 | 17   |

|   | 2.3 | The Sp  | ecification Problem                                     | 18   |

|   |     | 2.3.1   | Specification Requirements                              | 19   |

|   |     | 2.3.2   | Types of Specifications                                 | 19   |

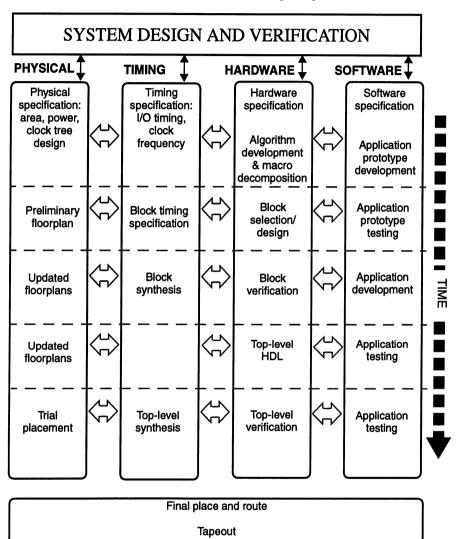

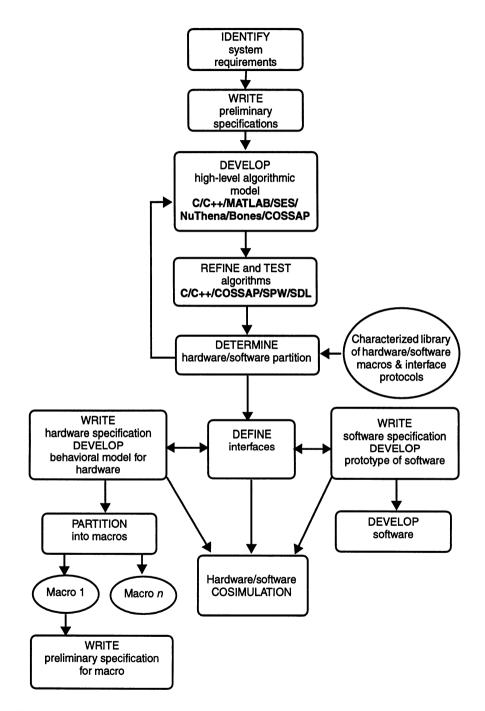

|   | 2.4 | The Sy  | stem Design Process                                     |      |

| 3 | Sy  | stem-I  | Level Design Issues: Rules and Tools                    | 25   |

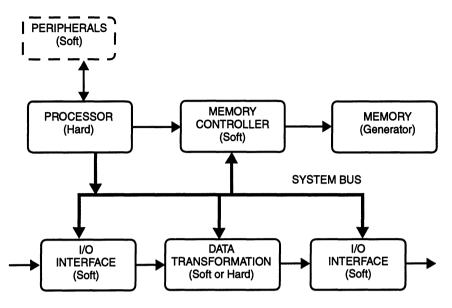

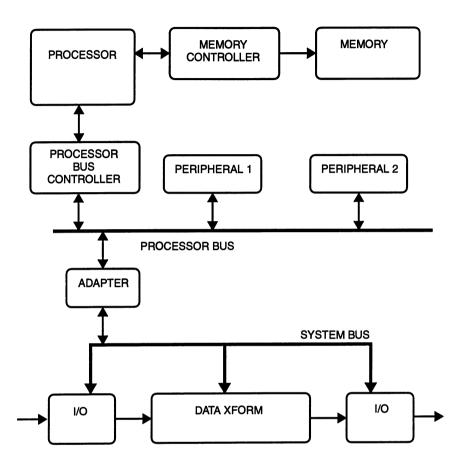

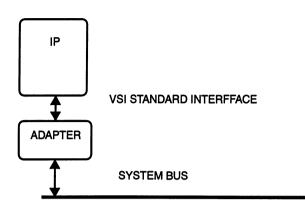

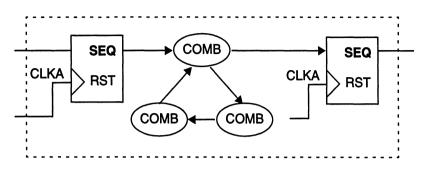

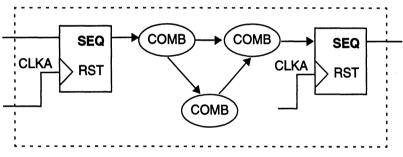

|   | 3.1 | The St  | andard Model                                            | 25   |

|   |     | 3.1.1   | Soft IP vs. Hard IP                                     | 27   |

|   |     | 3.1.2   | The Role of Full Custom Design in Reuse                 | 28   |

|   | 3.2 | Design  | for Timing Closure: Logic Design Issues                 | 29   |

|   |     | 3.2.1   | Interfaces and Timing Closure                           |      |

|   |     | 3.2.2   | Synchronous vs. Asynchronous Design Style               | 33   |

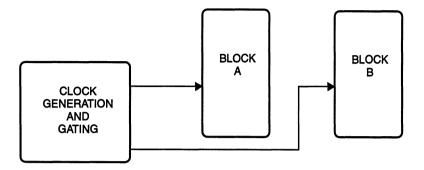

|   |     | 3.2.3   | Clocking                                                | 34   |

|   |     | 3.2.4   | Reset                                                   | 35   |

|   |     | 3.2.5   | Timing Exceptions and Multicycle Paths                  | 36   |

|   | 3.3 | Design  | for Timing Closure: Physical Design Issues              | 36   |

|   |     | 3.3.1   | Floorplanning                                           | 36   |

|   |     | 3.3.2   | Synthesis Strategy and Timing Budgets                   | 36   |

|   |     | 3.3.3   | Hard Macros                                             | 37   |

|   |     | 3.3.4   | Clock Distribution                                      | 37   |

|   | 3.4 | Design  | for Verification: Verification Strategy                 | 38   |

|   | 3.5 | System  | Interconnect and On-Chip Buses                          | 39   |

|   |     | 3.5.1   | Basic Interface Issues                                  | 39   |

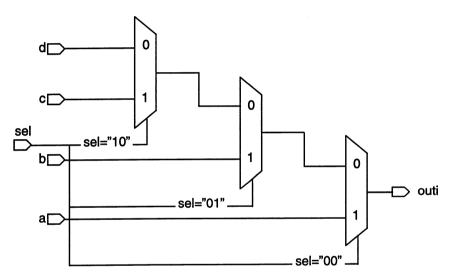

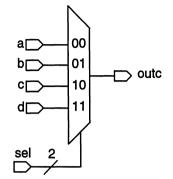

|   |     | 3.5.2   | Tristate vs. Mux Buses                                  | 40   |

|   |     | 3.5.3   | Reuse Issues and On-Chip Buses                          | . 41 |

|   |     | 3.5.4   | IP-to-IP Interfaces                                     | . 42 |

|   |     | 3.5.5   | Design for Bring-Up and Debug: On-Chip Debug Structures | . 43 |

|   | 3.6 | Design  | for Low Power                                           |      |

|   |     | 3.6.1   | Lowering the Supply Voltage                             |      |

|   |     | 3.6.2   | Reducing Capacitance and Switching Activity             |      |

|   |     | 3.6.3   | Sizing and Other Synthesis Techniques                   |      |

|   |     | 3.6.4   | Summary                                                 | . 48 |

|   | 3.7 | Design  | for Test: Manufacturing Test Strategies | 49 |

|---|-----|---------|-----------------------------------------|----|

|   |     | 3.7.1   | System Level Test Issues                | 49 |

|   |     | 3.7.2   | Memory Test                             | 49 |

|   |     | 3.7.3   | Microprocessor Test                     | 49 |

|   |     | 3.7.4   | Other Macros                            | 49 |

|   |     | 3.7.5   | Logic BIST                              | 50 |

|   | 3.8 | Prerequ | isites for Reuse                        | 50 |

|   |     | 3.8.1   | Libraries                               | 50 |

|   |     | 3.8.2   | Physical Design Rules                   | 51 |

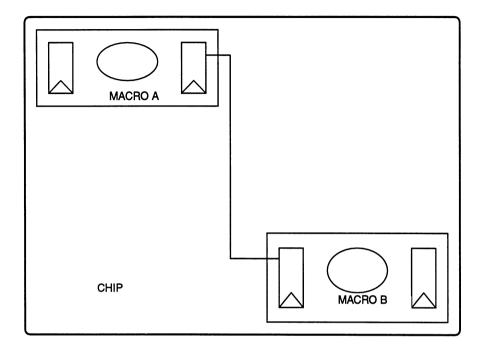

| 4 | Th  | e Mac   | ro Design Process                       | 53 |

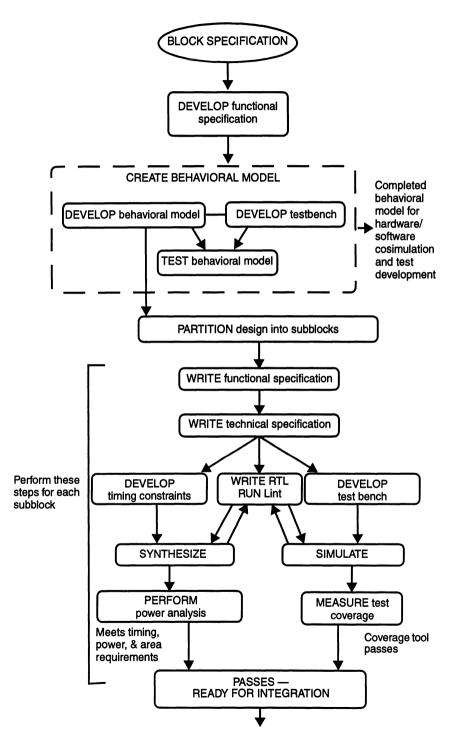

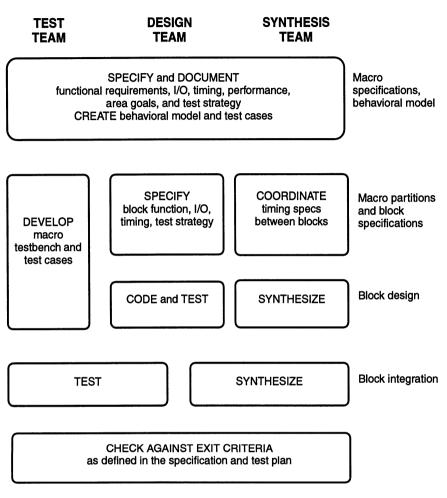

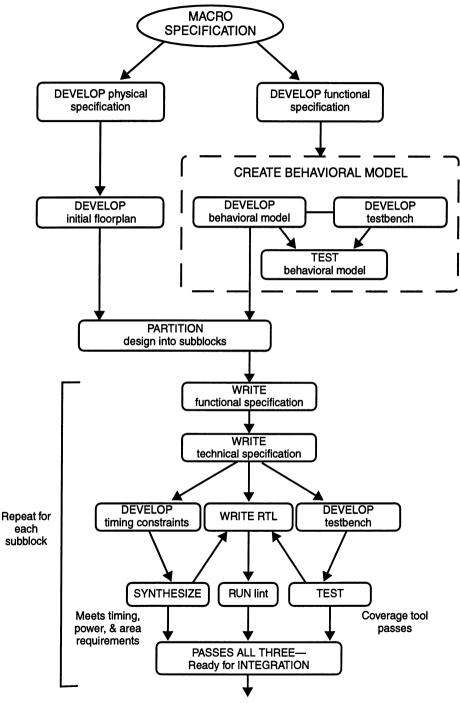

|   | 4.1 | Design  | Process Overview                        | 53 |

|   | 4.2 | •       | ts of a Design Specification            |    |

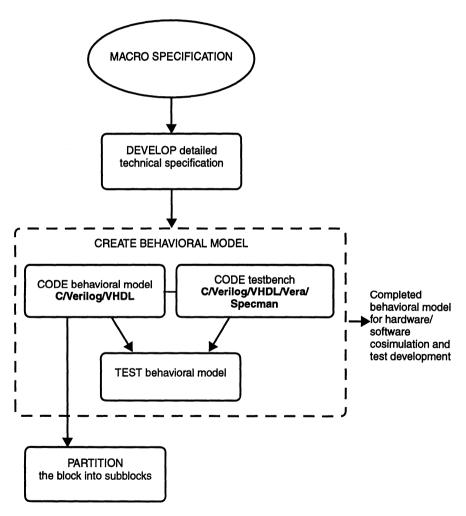

|   | 4.3 |         | vel Macro Design                        |    |

|   |     | 4.3.1   | Top-Level Macro Design Process          |    |

|   |     | 4.3.2   | Activities and Tools                    |    |

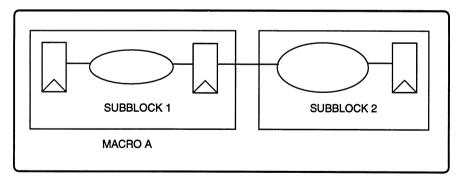

|   | 4.4 |         | ck Design                               |    |

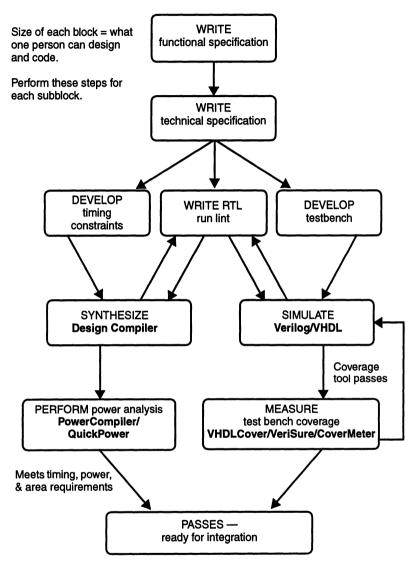

|   |     | 4.4.1   | Subblock Design Process                 |    |

|   |     | 4.4.2   | Activities and Tools                    |    |

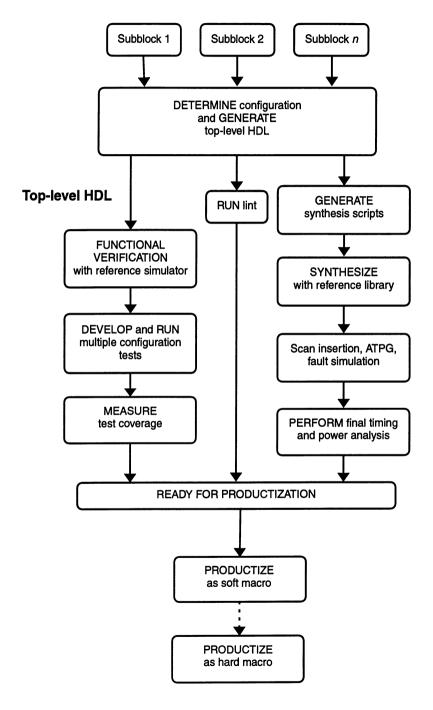

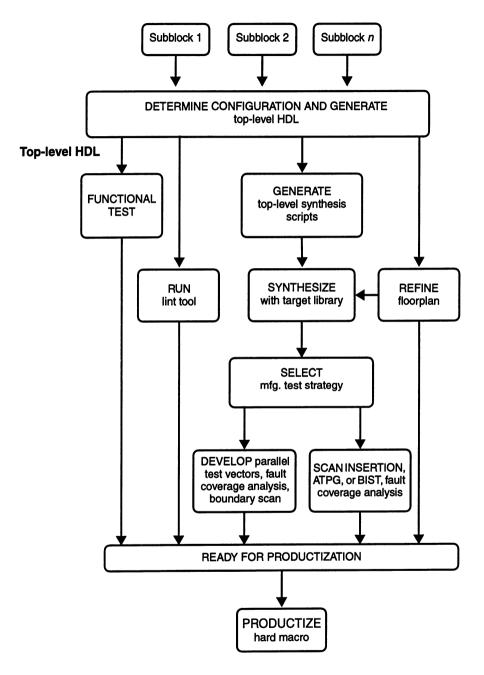

|   | 4.5 | Macro   | Integration                             |    |

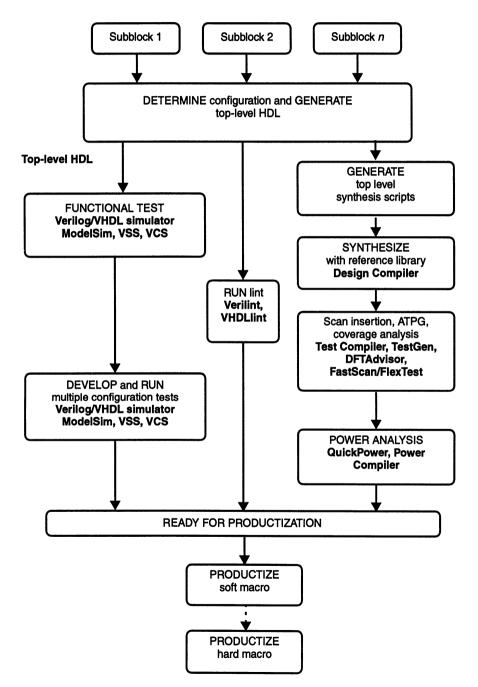

|   |     | 4.5.1   | Integration Process                     |    |

|   |     | 4.5.2   | Activities and Tools                    |    |

|   | 4.6 | Soft M  | acro Productization                     | 69 |

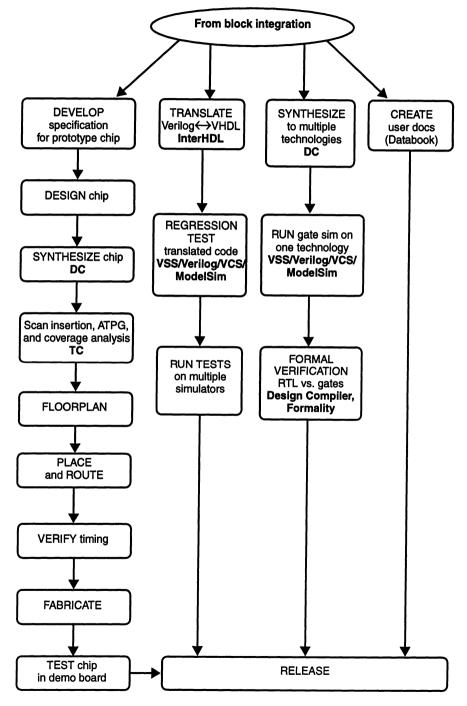

|   |     | 4.6.1   | Productization Process                  |    |

|   |     | 4.6.2   | Activities and Tools                    | 71 |

| 5 | R   | L Cod   | ling Guidelines                         | 73 |

|   | 5.1 | Overvi  | ew of the Coding Guidelines             | 73 |

|   | 5.2 | Basic C | Coding Practices                        | 74 |

|   |     | 5.2.1   | General Naming Conventions              | 74 |

|   |     | 5.2.2   | Naming Conventions for VITAL Support    | 76 |

|   |     | 5.2.3   | Architecture Naming Conventions         | 77 |

|   |     | 5.2.4   | Include Headers in Source Files         | 77 |

|   |     | 5.2.5   | Use Comments                            |    |

|   |     | 5.2.6   | Keep Commands on Separate Lines         | 79 |

|   |     | 5.2.7   | Line Length                             |    |

|   |     | 5.2.8   | Indentation                             |    |

|   |     | 5.2.9   | Do Not Use HDL Reserved Words           |    |

|   |     | 5.2.10  | Port Ordering                           | 81 |

|     | 5.2.11   | Port Maps and Generic Maps                              | 82   |

|-----|----------|---------------------------------------------------------|------|

|     | 5.2.12   | VHDL Entity, Architecture, and Configuration Sections   | . 83 |

|     | 5.2.13   | Use Functions                                           | . 84 |

|     | 5.2.14   | Use Loops and Arrays                                    | . 85 |

|     | 5.2.15   | Use Meaningful Labels                                   | 86   |

| 5.3 | Coding   | for Portability                                         | 87   |

|     | 5.3.1    | Use Only IEEE Standard Types                            |      |

|     | 5.3.2    | Do Not Use Hard-Coded Numeric Values                    |      |

|     | 5.3.3    | Packages                                                |      |

|     | 5.3.4    | Include Files                                           |      |

|     | 5.3.5    | Avoid Embedding dc_shell Scripts                        | 89   |

|     | 5.3.6    | Use Technology-Independent Libraries                    |      |

|     | 5.3.7    | Coding For Translation (VHDL to Verilog)                | 90   |

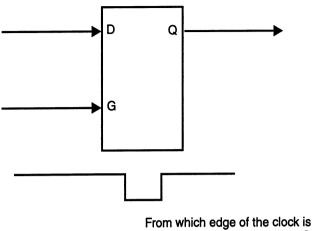

| 5.4 | Guideli  | nes for Clocks and Resets                               | 91   |

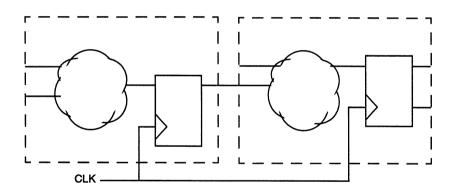

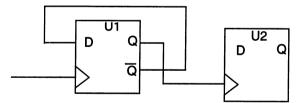

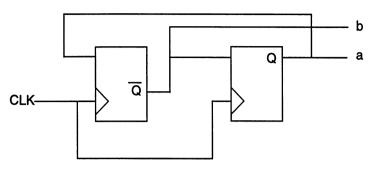

|     | 5.4.1    | Avoid Mixed Clock Edges                                 | 91   |

|     | 5.4.2    | Avoid Clock Buffers                                     | 93   |

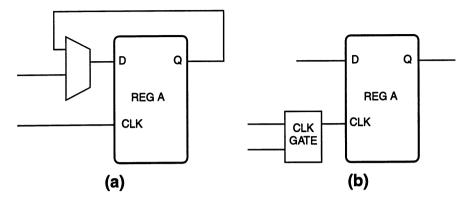

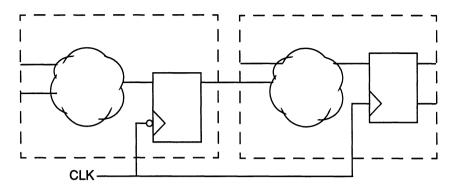

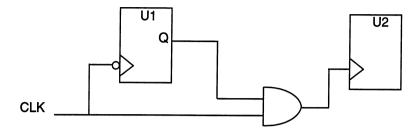

|     | 5.4.3    | Avoid Gated Clocks                                      | 93   |

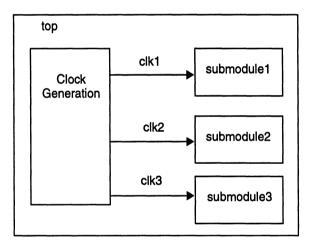

|     | 5.4.4    | Avoid Internally Generated Clocks                       | 94   |

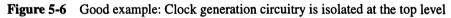

|     | 5.4.5    | Gated Clocks and Low Power Designs                      | 94   |

|     | 5.4.6    | Avoid Internally Generated Resets                       | 96   |

| 5.5 | Coding   | for Synthesis                                           | 97   |

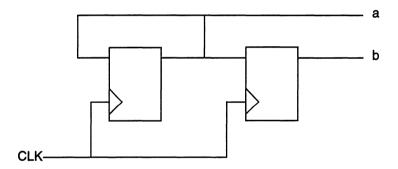

|     | 5.5.1    | Infer Registers                                         | 97   |

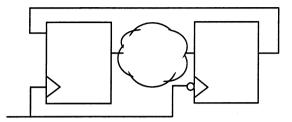

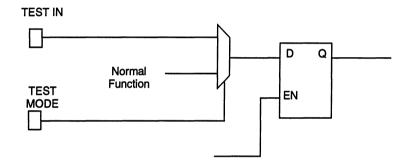

|     | 5.5.2    | Avoid Latches                                           | 99   |

|     | 5.5.3    | If you must use a latch 1                               | 02   |

|     | 5.5.4    | Avoid Combinational Feedback 1                          | 02   |

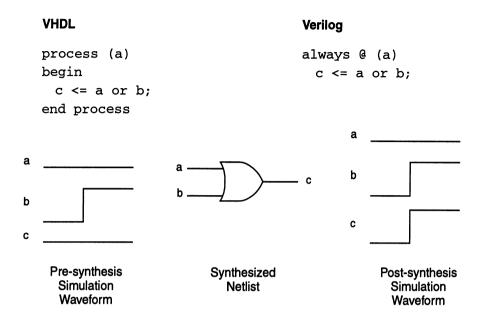

|     | 5.5.5    | Specify Complete Sensitivity Lists 1                    | 03   |

|     | 5.5.6    | Blocking and Nonblocking Assignments (Verilog)1         | .05  |

|     | 5.5.7    | Signal vs. Variable Assignments (VHDL) 1                | .07  |

|     | 5.5.8    | Case Statements versus if-then-else Statements 1        |      |

|     | 5.5.9    | Coding State Machines 1                                 | 10   |

| 5.6 | Partitio | ning for Synthesis 1                                    | .14  |

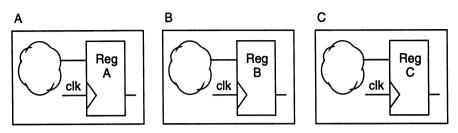

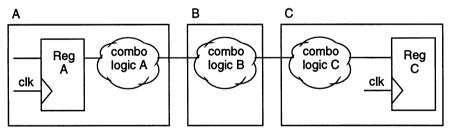

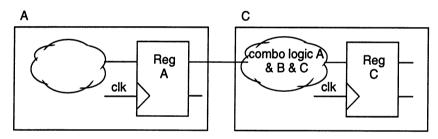

|     | 5.6.1    | Register All Outputs 1                                  | .14  |

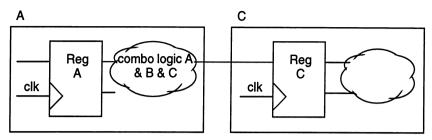

|     | 5.6.2    | Locate Related Combinational Logic in a Single Module 1 | .15  |

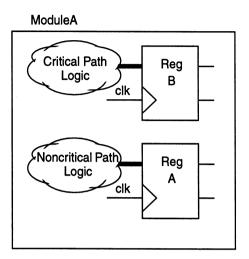

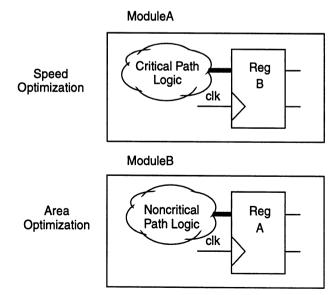

|     | 5.6.3    | Separate Modules That Have Different Design Goals 1     | .16  |

|     | 5.6.4    | Asynchronous Logic 1                                    | .18  |

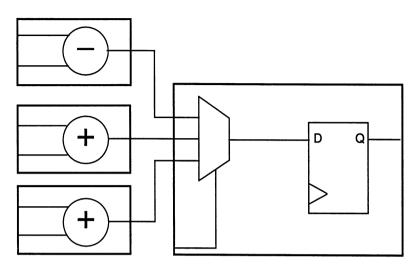

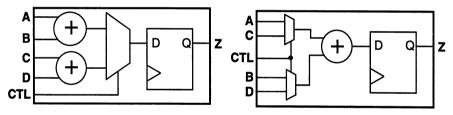

|     | 5.6.5    | Arithmetic Operators: Merging Resources 1               |      |

|     | 5.6.6    | Partitioning for Synthesis Runtime 1                    |      |

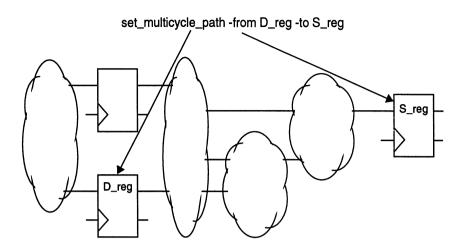

|     | 5.6.7    | Avoid Point-to-Point Exceptions and False Paths 1       |      |

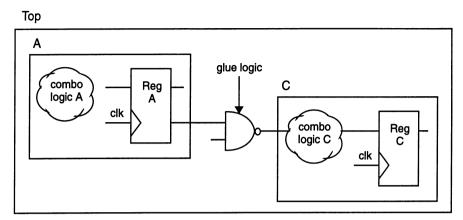

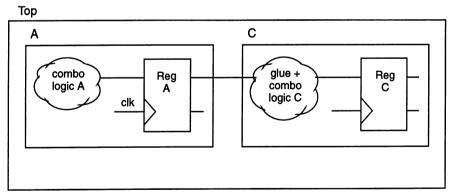

|     | 5.6.8    | Eliminate Glue Logic at the Top Level 1                 |      |

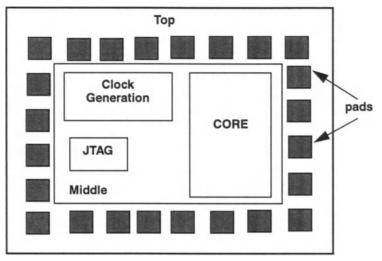

|     | 5.6.9    | Chip-Level Partitioning 1                               | .22  |

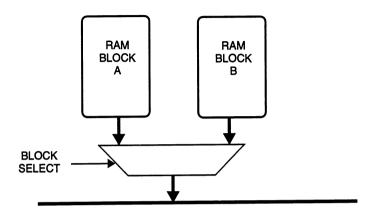

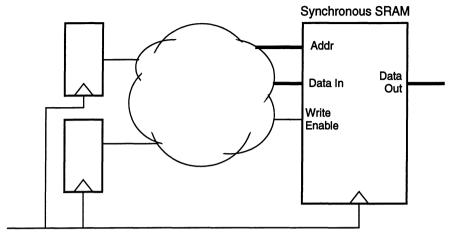

| 5.7 | Designi  | ing with Memories1                                      | .23  |

|   | 5.8 | Code I  | Profiling                                    | 125 |

|---|-----|---------|----------------------------------------------|-----|

| 6 | Ma  | acro Sj | ynthesis Guidelines                          | 127 |

|   | 6.1 | Overvi  | iew of the Synthesis Problem                 | 127 |

|   | 6.2 |         | Synthesis Strategy                           |     |

|   |     | 6.2.1   | Macro Timing Budget                          |     |

|   |     | 6.2.2   | Subblock Timing Budget                       |     |

|   |     | 6.2.3   | Synthesis in the Design Process              |     |

|   |     | 6.2.4   | Subblock Synthesis Process                   |     |

|   |     | 6.2.5   | Macro Synthesis Process                      | 130 |

|   |     | 6.2.6   | Wire Load Models                             | 131 |

|   |     | 6.2.7   | Preserve Clock and Reset Networks            | 131 |

|   |     | 6.2.8   | Code Checking Before Synthesis               | 132 |

|   |     | 6.2.9   | Code Checking After Synthesis                | 132 |

|   | 6.3 | High-l  | Performance Synthesis                        | 133 |

|   |     | 6.3.1   | Classical Synthesis                          | 133 |

|   |     | 6.3.2   | High-Performance Synthesis                   | 134 |

|   |     | 6.3.3   | Tiling                                       | 134 |

|   | 6.4 | RAM     | and Datapath Generators                      | 134 |

|   |     | 6.4.1   | Memory Design                                | 134 |

|   |     | 6.4.2   | Datapath Design                              | 135 |

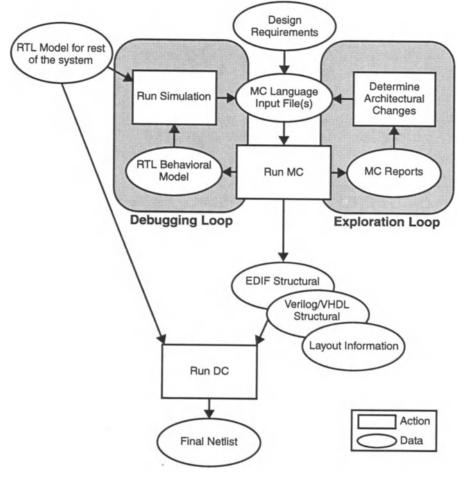

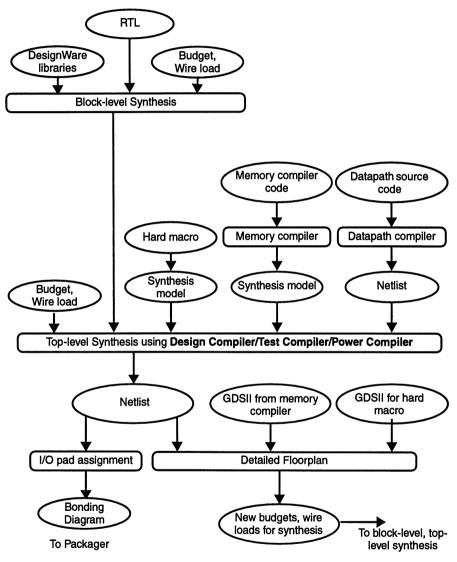

|   |     | 6.4.3   | Design Flow Using Module Compiler            | 138 |

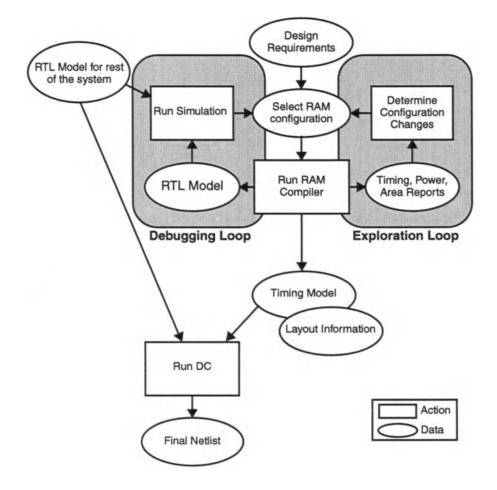

|   |     | 6.4.4   | RAM Generator Flow                           | 140 |

|   |     | 6.4.5   | Design Reuse with Datapath and RAM Compilers | 140 |

|   | 6.5 | Codin   | g Guidelines for Synthesis Scripts           |     |

| 7 | Μ   | acro V  | /erification Guidelines                      | 145 |

|   | 7.1 | Overv   | view of Macro Verification                   | 145 |

|   |     | 7.1.1   | Verification Plan                            | 146 |

|   |     | 7.1.2   | Verification Strategy                        | 147 |

|   |     | 7.1.3   | Subblock Simulation                          | 151 |

|   |     | 7.1.4   | Macro Simulation                             | 151 |

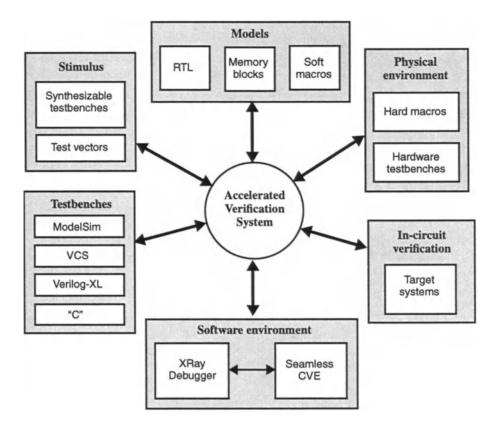

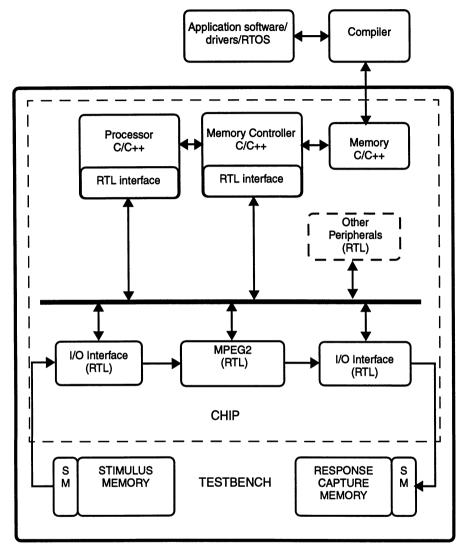

|   |     | 7.1.5   | Prototyping                                  | 152 |

|   |     | 7.1.6   | Limited Production                           | 152 |

|   | 7.2 | Inspec  | ction as Verification                        | 152 |

|   | 7.3 | Adver   | rsarial Testing                              |     |

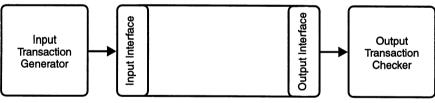

|   | 7.4 |         | ench Design                                  |     |

|   |     | 7.4.1   | Subblock Testbench                           |     |

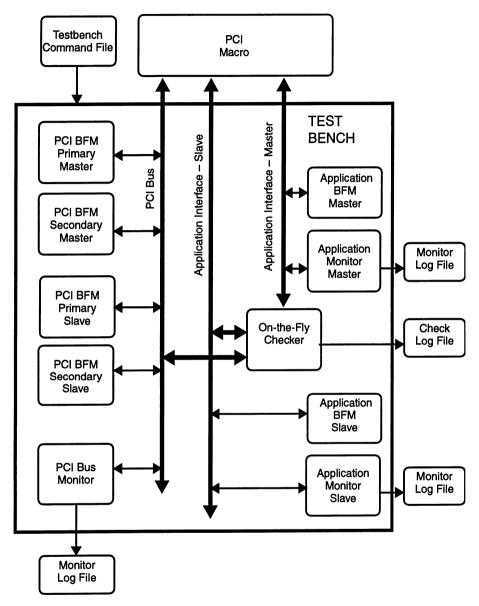

|   |     | 7.4.2   | Macro Testbench                              | 156 |

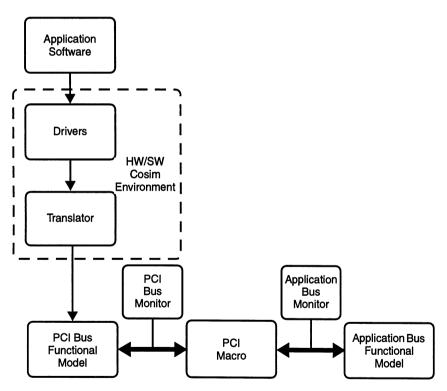

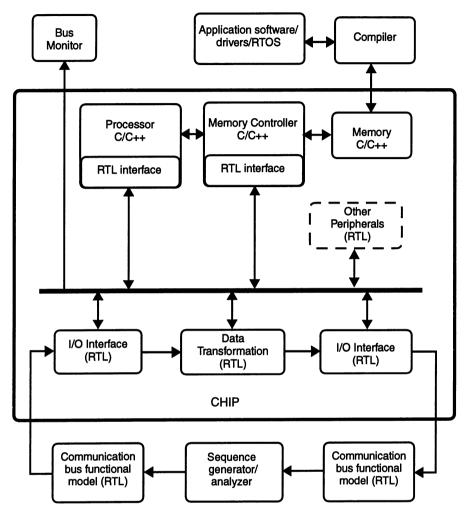

|   |     | 7.4.3   | Bus Functional Models                   |     |

|---|-----|---------|-----------------------------------------|-----|

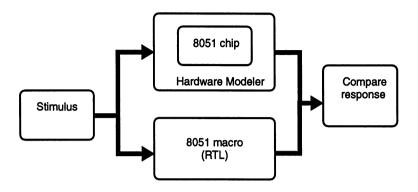

|   |     | 7.4.4   | Automated Response Checking             | 160 |

|   |     | 7.4.5   | Verification Suite Design               | 161 |

|   |     | 7.4.6   | Code Coverage Analysis                  | 166 |

|   | 7.5 | Timin   | g Verification                          | 169 |

|   |     |         |                                         |     |

| 8 | De  | evelopi | ing Hard Macros                         | 171 |

|   | 8.1 | Overv   | riew                                    |     |

|   |     | 8.1.1   | Why and When to use Hard Macros         |     |

|   |     | 8.1.2   | Design Process for Hard vs. Soft Macros |     |

|   | 8.2 | Desig   | n Issues for Hard Macros                |     |

|   |     | 8.2.1   | Full Custom Design                      |     |

|   |     | 8.2.2   | Interface Design                        |     |

|   |     | 8.2.3   | Design For Test                         |     |

|   |     | 8.2.4   | Clock and Reset                         | 176 |

|   |     | 8.2.5   | Aspect Ratio                            |     |

|   |     | 8.2.6   | Porosity                                |     |

|   |     | 8.2.7   | Pin Placement                           | 178 |

|   |     | 8.2.8   | Power Distribution                      |     |

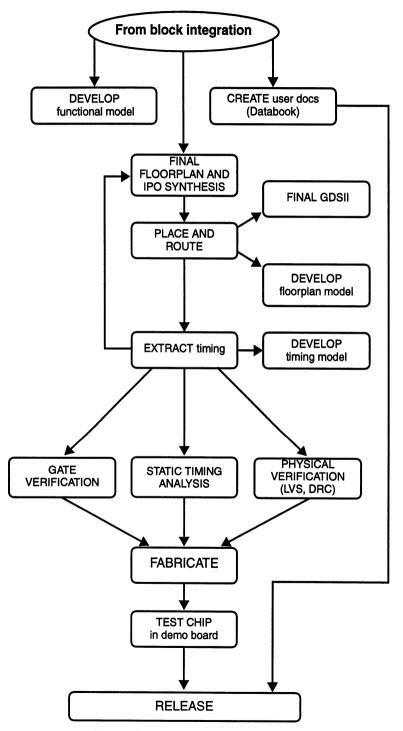

|   | 8.3 | The H   | ard Macro Design Process                | 179 |

|   | 8.4 | Block   | Integration for Hard Macros             | 181 |

|   | 8.5 | Produc  | ctization of Hard Macros                | 181 |

|   |     | 8.5.1   | Physical Design                         | 181 |

|   |     | 8.5.2   | Verification                            |     |

|   |     | 8.5.3   | Models                                  | 185 |

|   |     | 8.5.4   | Documentation                           | 185 |

|   | 8.6 | Model   | Development for Hard Macros             | 186 |

|   |     | 8.6.1   | Functional Models                       | 186 |

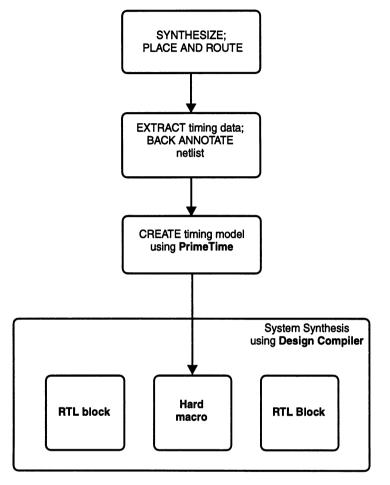

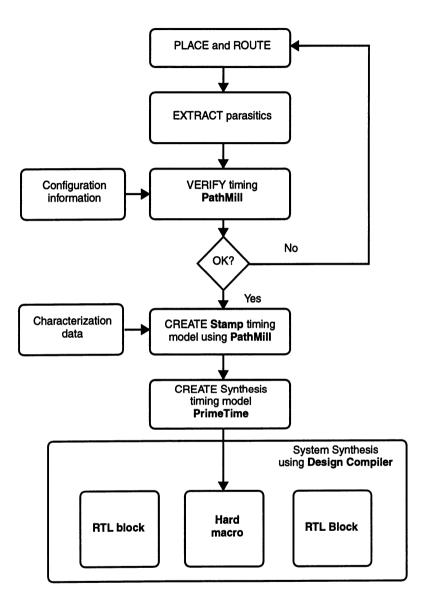

|   |     | 8.6.2   | Synthesis and Floorplanning Models      | 194 |

|   | 8.7 | Porting | g Hard Macros                           | 197 |

|   |     |         |                                         |     |

| 9 | Ma  | acro D  | Peployment: Packaging for Reuse         | 199 |

|   | 9.1 | Delive  | ring the Complete Product               | 199 |

|   |     | 9.1.1   | Soft Macro Deliverables                 |     |

|   |     | 9.1.2   | Hard Macro Deliverables                 | 202 |

|   |     | 9.1.3   | The Design Archive                      |     |

|   | 9.2 | Conter  | nts of the User Guide                   | 205 |

| 10 | S                                    | ystem ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Integration with Reusable Macros                                                                                                                                                                                                                                                                                                                                                                            | 7                               |

|----|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|    | 10.1                                 | Integrat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | tion Overview                                                                                                                                                                                                                                                                                                                                                                                               | 7                               |

|    |                                      | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ting Macros into an SoC Design 208                                                                                                                                                                                                                                                                                                                                                                          |                                 |

|    |                                      | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Problems in Integrating IP                                                                                                                                                                                                                                                                                                                                                                                  |                                 |

|    |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Strategies for Managing Interfacing Issues                                                                                                                                                                                                                                                                                                                                                                  |                                 |

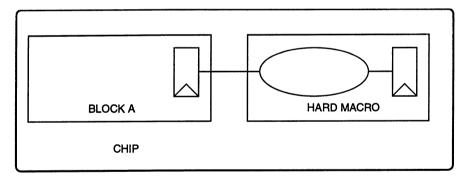

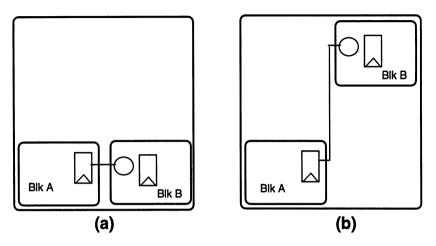

|    |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Interfacing Hard Macros to the Rest of the Design                                                                                                                                                                                                                                                                                                                                                           |                                 |

|    | 10.3                                 | Selectio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ng IP                                                                                                                                                                                                                                                                                                                                                                                                       | 1                               |

|    |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Hard Macro Selection                                                                                                                                                                                                                                                                                                                                                                                        |                                 |

|    |                                      | 10.3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Soft Macro Selection                                                                                                                                                                                                                                                                                                                                                                                        | 2                               |

|    |                                      | 10.3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Soft Macro Installation                                                                                                                                                                                                                                                                                                                                                                                     | 2                               |

|    |                                      | 10.3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Soft Macro Configuration                                                                                                                                                                                                                                                                                                                                                                                    | 3                               |

|    |                                      | 10.3.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Synthesis of Soft Macros                                                                                                                                                                                                                                                                                                                                                                                    | 3                               |

|    | 10.4                                 | Integra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ting Memories                                                                                                                                                                                                                                                                                                                                                                                               | 3                               |

|    | 10.5                                 | Physica                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | al Design 214                                                                                                                                                                                                                                                                                                                                                                                               | 4                               |

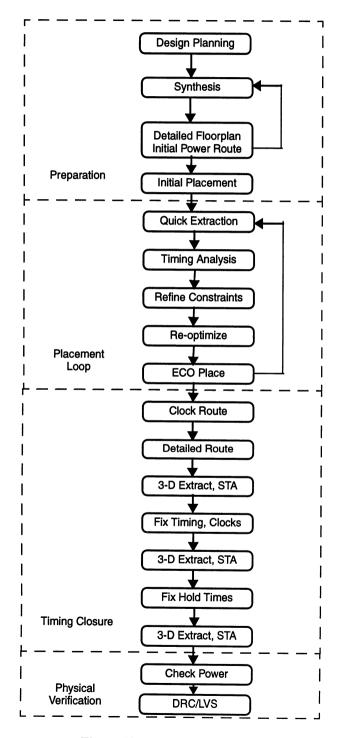

|    |                                      | 10.5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Design Planning to Initial Placement                                                                                                                                                                                                                                                                                                                                                                        | 6                               |

|    |                                      | 10.5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Placement Loop                                                                                                                                                                                                                                                                                                                                                                                              | 3                               |

|    |                                      | 10.5.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Timing Closure                                                                                                                                                                                                                                                                                                                                                                                              | 5                               |

|    |                                      | 10.5.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Verifying the Physical Design                                                                                                                                                                                                                                                                                                                                                                               | 7                               |

|    |                                      | 10.5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Summary                                                                                                                                                                                                                                                                                                                                                                                                     | 8                               |