# Rapid Thermal Processing for Future Semiconductor Devices

Edited by Hisashi Fukuda

# RAPID THERMAL PROCESSING FOR FUTURE SEMICONDUCTOR DEVICES

This Page Intentionally Left Blank

# RAPID THERMAL PROCESSING FOR FUTURE SEMICONDUCTOR DEVICES

Proceedings of the 2001 International Conference on Rapid Thermal Processing for Future Semiconductor Devices (RTP 2001) held at Ise-Shima, Mie, Japan, November 14-16, 2001.

Edited by

## Hisashi Fukuda

Muroran Institute of Technology Department of Electrical and Electronic Engineering 27-1 Mizumoto-cho Muroran, Hokkaido 050-8585 Japan

Amsterdam – Boston – Heidelberg - London – New York – Oxford Paris - San Diego – San Francisco – Singapore - Sydney – Tokyo

| ELSEVIER B.V.               | ELSEVIER Inc.            | ELSEVIER Ltd                 | ELSEVIER Ltd      |

|-----------------------------|--------------------------|------------------------------|-------------------|

| Sara Burgerhartstraat 25    | 525 B Street, Suite 1900 | The Boulevard, Langford Lane | 84 Theobalds Road |

| P.O. 211, 1000 AE Amsterdam | San Diego, CA 92101-4495 | Kidlington, Oxford OX5 1GB   | London WC1X 8RR   |

| The Netherlands             | USA                      | UK                           | UK                |

© 2003 Elsevier B.V. All rights reserved.

This work is protected under copyright by Elsevier B.V., and the following terms and conditions apply to its use:

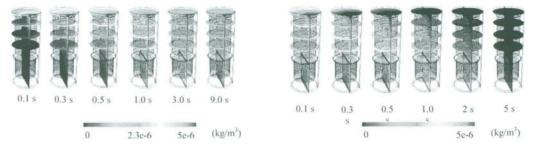

#### Photocopying

Single photocopies of single chapters may be made for personal use as allowed by national copyright laws. Permission of the Publisher and payment of a fee is required for all other photocopying, including multiple or systematic copying, copying for advertising or promotional purposes, resale, and all forms of document delivery. Special rates are available for educational institutions that wish to make photocopies for non-profit educational classroom use.

Permissions may be sought directly from Elsevier's Rights Department in Oxford, UK: phone (+44) 1865 843830, fax (+44) 1865 853333, e-mail: permissions@elsevier.com. Requests may also be completed on-line via the Elsevier homepage (http://www.elsevier.com/locate/permissions).

In the USA, users may clear permissions and make payments through the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923, USA; phone: (+1) (978) 7508400, fax: (+1) (978) 7504744, and in the UK through the Copyright Licensing Agency Rapid Clearance Service (CLARCS), 90 Tottenham Court Road, London W1P 0LP, UK; phone: (+44) 20 7631 5555; fax: (+44) 20 7631 5500. Other countries may have a local reprographic rights agency for payments.

#### Derivative Works

Tables of contents may be reproduced for internal circulation, but permission of the Publisher is required for external resale or distribution of such material. Permission of the Publisher is required for all other derivative works, including compilations and translations.

Electronic Storage or Usage

Permission of the Publisher is required to store or use electronically any material contained in this work, including any chapter or part of a chapter.

Except as outlined above, no part of this work may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without prior written permission of the Publisher.

Address permissions requests to: Elsevier's Rights Department, at the fax and e-mail addresses noted above.

#### Notice

No responsibility is assumed by the Publisher for any injury and/or damage to persons or property as a matter of products liability, negligence or otherwise, or from any use or operation of any methods, products, instructions or ideas contained in the material herein. Because of rapid advances in the medical sciences, in particular, independent verification of diagnoses and drug dosages should be made.

First edition 2003 Second impression 2003

Library of Congress Cataloging in Publication Data A catalog record is available from the Library of Congress.

British Library Cataloguing in Publication Data A catalogue record is available from the British Library.

ISBN: 0 444 51339 6

The paper used in this publication meets the requirements of ANSI/NISO Z39.48-1992 (Permanence of Paper). Printed in Hungary.

# Preface

This volume is a collection of papers which were presented at the 2001 International Conference on Rapid Thermal Processing (RTP 2001) held at Ise Shima, Mie, on November 14-16, 2001. This symposium is 2<sup>nd</sup> conference followed the previous successful 1<sup>st</sup> International RTP conference held at Hokkaido in 1997. The RTP 2001 covered the latest developments in RTP and other short-time processing continuously aiming to point out the future direction in the Silicon ULSI devices and II-VI, III-V compound semiconductor devices.

The first day of the symposium covered the future trend of shallow junction technology, advance MOS integration and novel metallization technology. Two invited papers are presented in the session related to future technology trend of RTP toward 21<sup>st</sup> century and single wafer process in DRAM manufacturing.

The second day of the symposium is the presentation of novel TFT fabrication, process monitoring and thin dielectric film formation technologies including two invited papers related to TFT fabrication and ferroelectric thin film formation. Poster session is covering the novel MOCVD processing, junction technology, novel oxidation, optoelectronics application etc.

The symposium ended with a session of novel RTP equipment and epitaxial thin film technologies, which included the invited paper related to wafer floating processing, and contributed papers for SiGe epitaxial process for HBT and quantum devices.

The symposium was sponsored by the 131<sup>st</sup> University-Industry Cooperative Research Committee on Thin Films and the 154<sup>th</sup> University-Industry Cooperative Research Committee on Semiconductor Interfaces and Their Applications organized in Japan Society for the Promotion of Science (JSPS). The symposium was successful from many aspects. Friendships were successfully formed through fruitful discussions and the social activities including a welcome-reception and banquet. The success of the symposium was greatly dependent on the efforts of organizing, steering and program committees, and also financial support of 10 organizations.

M. Jasuda

Yukio Yasuda Chairperson of RTP 2001

This Page Intentionally Left Blank

# **RTP2001** Organization

Chairperson: Y. Yasuda (Nagoya Univ.) Vice chairperson: J. Murota (Tohoku Univ.)

#### Steering Committee:

S. Zaima (Nagoya Univ.)

A. Agarwal (Axcelis Technol.)

J. Hata (Tokyo Electron Ltd.)

S. Hirokawa (Canon Sales Co.,Inc.)

I. Kawai (Applied Materials Japan Inc.)

#### Program Committee:

H. Fukuda (Muroran Inst. of Technol.)

A. Agarwal (Axcelis Technol.)

K. Ando (NEC Corp.)

Y. Kunii (Hitachi Kokusai Electric Inc.)

S. Miyazaki (Hiroshima Univ.)

Y. Nakata (Altedec Co.,Ltd.)

#### Advisory Committee:

Y. Shiraki (Univ. of Tokyo) A. Hiraki (Kouchi Inst. of Technol.) T. Hara (Hosei Univ.)

#### Supported Organizations:

Applied Materials Japan Inc. ASM Japan K.K. Canon Sales Co.,Ltd. Hitachi Kokusai Electric Inc. Koyo Thermo Systems Co.,Ltd.

RTP2001 Secretariat: K. Fukozu (SIPEC Corp.) N. Yamamoto (SIPEC Corp.) Y. Mimura (Ushio Inc.)

- O. Takai (Nagoya Univ.)

- L. Yasue (Dainippon Screen MFG. Co., Ltd.)

- K. Yoneda (Matsushita Electronics Corp.)

- N. Shah (Axcelis Technol.)

- K. Suguro (Toshiba Corp.)

- K. Takasaki (Fujitsu Lab., Ltd.)

- Y. Tanabe (Hitachi,Ltd.)

- J. Tsuchimoto (Mitsubishi Electric Corp.)

Mattson Technology Japan NEC Corp. Sumitomo Heavy Industries,Ltd. Universal Systems Co.,Ltd. Ushio Inc. This Page Intentionally Left Blank

# CONTENTS

Preface RTP2001 Organization

| 1. | Role of Rapid Thermal Processing in the Development of Disruptive and<br>Non-disruptive Technologies for Semiconductor Manufacturing in the 21 <sup>st</sup> Century |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2. | Analytical Model for Spike Annealed Diffusion Profiles of Low-Energy<br>and High-Dose Ion Implanted Impurities                                                       |

| 3. | Process and Technology Drivers for Single Wafer Processes in DRAM Manufacturing                                                                                      |

| 4. | Ultra-high vacuum rapid thermal chemical vapor deposition for formation of<br>TiN as barrier metals29                                                                |

|    | S. Naito, M. Okada, O. Nakatsuka, T. Okuhara, A. Sakai, S. Zaima and Y. Yasuda                                                                                       |

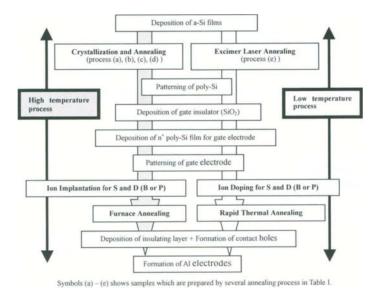

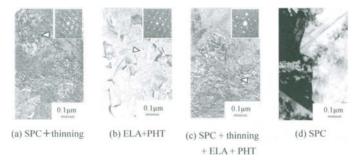

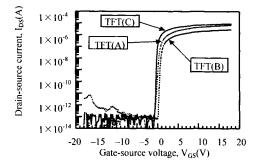

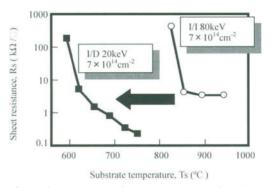

| 5. | Implementations of Rapid Thermal Processes in Polysilicon TFT Fabrication                                                                                            |

| 6. | High-Performance Poly-Si TFT and its Application to LCD                                                                                                              |

| 7. | Rapid Low Temperature Photo Oxidation Processing for Advanced Poly-Si TFTs                                                                                           |

| 8  | Properties of Phosphorus-Doped Polycrystalline Silicon Films Formed by<br>Catalytic Chemical Vapor Deposition and Successive Rapid Thermal Annealing                 |

| 9. | Evaluation of Crystalline Defects in Thin, Strained Silicon-Germanium Epitaxial<br>Layers by Optical Shallow Defect Analyzer                                         |

| 1  | <ol> <li>Novel UV-assisted Rapid Thermal Annealing of Ferroelectric Materials</li></ol>                                                                              |

|     | Rapid Thermal Annealing of (1-x)Ta <sub>2</sub> O <sub>5</sub> -xTiO <sub>2</sub> Thin Films Formed by<br>Metalorganic Decomposition                                                                                                                                                           |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | K. M. A. Salam, H. Konishi, H. Fukuda and S. Nomura                                                                                                                                                                                                                                            |

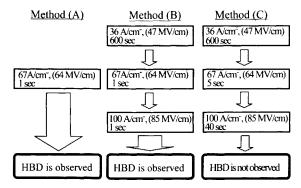

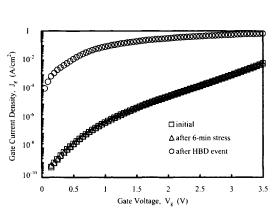

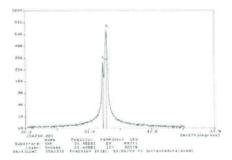

|     | Hard Breakdown Characteristics in a 2.2-nm-thick SiO <sub>2</sub> film93<br>K. Komiya, M. Nagahara and Y. Omura                                                                                                                                                                                |

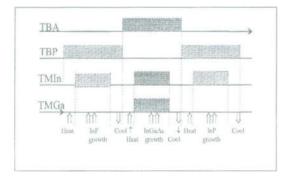

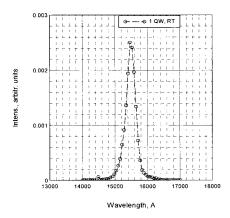

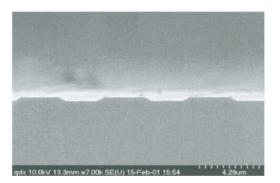

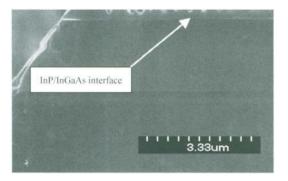

|     | Rapid Thermal MOCVD Processing for InP-Based Devices                                                                                                                                                                                                                                           |

|     | Sb Pile-up at the SiO <sub>2</sub> /Si Interface during Drive-in Process after Predeposition using SOG Source 107                                                                                                                                                                              |

|     | T. Ichino, H. Uchida, M. Ichimura and E. Arai                                                                                                                                                                                                                                                  |

| 15. | Large Refractive Index C-S-Au Composite Film Formation by Plasma Processes 115<br>M. Matsushita, Md. A. Kashem and S. Morita                                                                                                                                                                   |

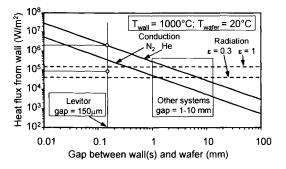

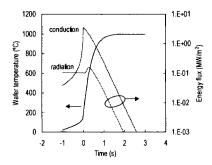

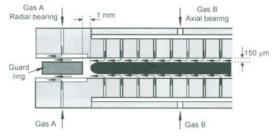

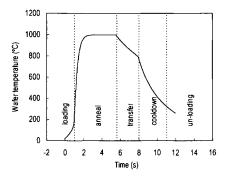

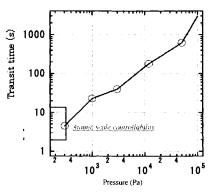

| 16. | The LEVITOR 4000 system, Ultra-fast, Emissivity-independent,<br>heating of substrates via heat conduction through thin gas layers                                                                                                                                                              |

| 17. | Steady and Transient Gas Flow Simulation of SiGe Vertical Reactor 129<br>A. Miyauchi, H. Yamazaki, Y. Inokuchi and Y. Kunii                                                                                                                                                                    |

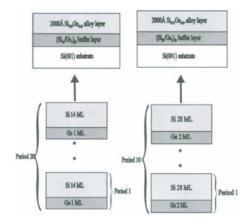

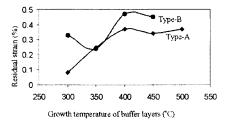

| 18. | The Short-period (Si <sub>14</sub> /Ge <sub>1</sub> ) <sub>20</sub> and (Si <sub>28</sub> /Ge <sub>2</sub> ) <sub>10</sub> superlattices as Buffer Layers<br>for the Growth of Si <sub>0.75</sub> Ge <sub>0.25</sub> Alloy Layers 133<br>M.M. Rahman, K. Kurumatani, T. Tambo and C. Tatsuyama |

| 19. | Si Epitaxial Growth on the Atomic-Order Nitrided Si(100) Surface in SiH <sub>4</sub> Reaction                                                                                                                                                                                                  |

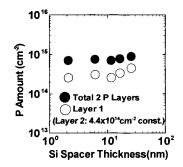

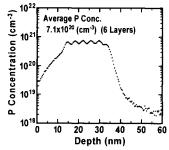

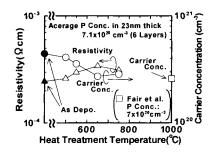

| 20. | Heavy Doping Characteristics of Si Films Epitaxially Grown at 450°C by Alternately<br>Supplied PH <sub>3</sub> and SiH <sub>4</sub>                                                                                                                                                            |

|     | r, omnumente, m. oukulava, r. maisuula allu J. muivia                                                                                                                                                                                                                                          |

## Role of Rapid Thermal Processing in the Development of Disruptive and Non-disruptive Technologies for Semiconductor Manufacturing in the 21<sup>st</sup> Century

Rajendra Singh †, Mohammed Fakhruddin and Kelvin F. Poole

Center for Silicon Nanoelectronics, and Holcombe Department of Electrical and Computer Engineering,

Clemson University, Clemson, SC 29634-0915, U. S. A.

† Phone: 1-864-656-0919 Fax: 1-864-656-5910 E-mail: srajend@clemson.edu

#### **1.Introduction**

Rapid thermal processing, popularly known as RTP has been around for more than two decades. In the context of silicon integrated circuit manufacturing, the equipment manufacturers and R&D groups from chip manufacturers as well as from universities have demonstrated a number of advantages over conventional furnace processing. As of today, RTP has not penetrated deep in Silicon IC manufacturing as it was forecasted and predicted by industry experts. Other than silicon ICs, the market size is very small. From the business point of view, the current status of RTP market is not very surprising since we operate in a world where only one out of 10 predicted markets ever come to fruition [1]. The introduction of 300 mm wafers in manufacturing (potential of 450 mm diameter wafer in future manufacturing), 70 nm gate length transistors in current 130 nm silicon integrated circuit manufacturing, the announcement of industrial researchers [2-3] for fabricating 15-20 nm gate length transistors, non-silicon IC technologies (display, storage, photovoltaics, optoelectronics etc.) and the issue of bringing disruptive technologies in production are some interesting issues that need to be considered for overall future of RTP. Thus, it is important to examine RTP technology from the current and future semiconductor manufacturing needs. In this paper, we have attempted to predict the future role of RTP in disruptive and non-disruptive semiconductor technologies.

#### 2. Global Picture of Semiconductor Manufacturing

An examination of the growth of the semiconductor industry shows that the ability to reduce the feature size (leading to lower cost/per function) is largely responsible for the sustained growth in the last four decades. The market size in 1959 was less than \$1 B and the current market size is about \$200 B. In spite of several negative growth cycles, over the last 40 years the semiconductor industry has maintained 17 % compound annual growth rate [4]. The overall semiconductor market consists of silicon ICs for low-power applications as well

as for power-electronics, micro electro mechanical systems (MEMS), compound semiconductor ICs, optical devices and optoelectronics, flat panel display, solar cells as well as disruptive technologies. In principle RTP has potential to meet thermal processing and chemical vapor deposition (CVD) needs of all the above-mentioned technologies. However, our discussion in this paper is focused mainly on silicon ICs for low power applications and disruptive technologies. In a recent paper we have discussed the role of RTP for photovoltaic applications [5].

In recent years researchers are raising an open question about how far the feature size reduction trends of silicon based CMOS will continue [6-7]. Alternate device structures (e.g. single electron transistors (SETs)), alternate materials (e.g. carbon nanotubes, magnetic materials, biological materials), molecular electronics, optical switches, quantum computers etc. have been proposed as an answer to the question, "what after silicon CMOS? ". Careful examination of all the published results show that none of the proposed solutions can lead to manufacturing. The best results published to date involve the use of self-assembled monolayers of conjugated polymers in a vertical CMOS structure [8]. Due to small channel length ('1-2 nm), the drain current is higher than the smallest silicon based CMOS reported to date. However, due the unstable nature of the organic semiconductor, the drain was deposited at 100K. Thus, from defects and reliability considerations [9], it is unlikely that the work reported in reference 8 can lead to manufacturing. The feature sizes of Si CMOS in 1980 and year 2000 were about 2 micron, and 0.2 micron respectively. It is expected that by the year 2020, the feature of Si CMOS will be about 20 nm.

#### 3. Current Trends in Semiconductor Manufacturing

During the last 40 years, due to increased wafer size, decreased line widths and larger capacities in wafer out per month have driven a decrease in capital cost per normalized unit (e.g. cost per transistor of an IC chip). However, the cost of semiconductor facilities is increasing exponentially with time. In recent years, the most difficult challenge for IC manufacturer is to meet the demands of time-to-market of a particular product. The current mega fabs are dominated by batch processing. In future, batch processing will play a reduced role in mega fabs. The agile manufacturing based on mini fabs will be driven by shorter products life and dominated by single wafer processing. In the context of current manufacturing trends the key features of agile manufacturing are [10]: (i) driven by quick turn around time and low-cost, (ii) small size fab supported by a virtual fab, (iii) multi-task and muti-functional tools, (iii) minimization and smoothing of raw process time

Historically, the concept of agile manufacturing for microelectronics was introduced in 1989 [11]. Funded partially by US Department of Defense, Texas Instruments completed microelectronics manufacturing science and technology (MMST) project in 1993. Using home built single wafer processing tools, TI demonstrated a cycle time of 3 days. The details of earlier work of TI and the limits of single wafer processing are discussed in a recent paper by Doering and Nishi [12].

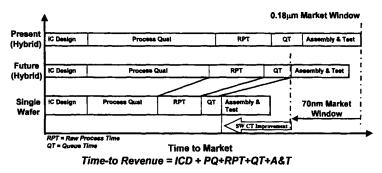

Fig.1 Single Wafer Processing shortens time-to-revenue and enables users to hit the accelerate cash inflow [14].

Currently the equipment manufacturers are divided on the issue of single wafer processing vs batch processing. Current vendors of thermal batch processing tools advocates that with innovation, the batch processing can meet the future needs of microelectronics manufacturing. Some of the innovative steps are: (i) small load size and high speed transfer, (ii) ultra fast heater and thermo plug combination valve, (iii) fast ramp down, soft back fill injector and small reactor volume, and (iv) rapid cooling units [13]. Although, the details of the approximations used in fab simulations are not known, it is claimed that after production wafer in progress reaches steady state levels, the batch processing actually provides shorter turn around time than single wafer processing [13]. As shown in Fig. 1 [14] the single wafer processing (SWP) vendors advocates that SWP shortens the time- to -revenue and enables users to hit the accelerate cash inflow.

In addition to the early work of Texas Instruments, currently there are many chip manufacturers who are advocating SWP over batch processing. As an example, Koike [15] has recently demonstrated the cycle time reduction features of SWP. These results are summarized in Table I. Our own general observation about cost vs raw processing time is that currently single wafer processing cost is generally 2-4 times higher than the batch processing. On the other hand, SWP raw processing time is about 2-4 times less than batch processing. For manufacturing beyond 70 nm node, we expect the dominance of SWP. In the ultimate limit of IC manufacturing, the SWP will take over batch processing.

#### 4.Lessons from the History of RTP

It is important to look at the history of RTP. The first paper dealing with the use of lowthermal mass graphite heater for annealing GaAs ion-implanted wafers was reported in 1977 [16]. In 1980, Nishiyama and co-workers [17] used halogen lamps as a continuous source of radiation to anneal boron-implanted Si for a very short time (6 sec.). The use of incoherent lamps as the source of energy led to the field of rapid thermal processing. For the early history of RTP, one is refereed to Ref. [18]. In the 80s, the availability of R&D commercial tools by AG Associates was one prime reason that a number of researchers contributed in this field.

|                      | 25 wfs/lot | 13 wfs/lot | 3 wfs/lot |

|----------------------|------------|------------|-----------|

| Batch Process        | 43         |            |           |

| Single Wafer Process | 25         | 17         | 10        |

Table I Cycle Time (arbitrary unit) Simulation of 300 nm Fab [15]

Most of the researchers attributed low-thermal mass leading to high heating cooling rates as the only difference between RTP and conventional furnace processing (CFP). As early as 1985 [19], one of us pointed out the fundamental difference in the energy spectrum of resistive heater based CFP systems and incoherent lamp based RTP systems. We pointed out the reduction of cycle time and process activation energy as the two distinct advantages of RTP over CFP [20]. Temperature measurement, and temperature uniformity were identified as the major issues in the use of RTP in manufacturing. Although, termed as Cinderella Technology [21], RTP did not find any manufacturing [22]. However, the introduction of better control systems in CFP, use of the mini-furnaces, and partial or no use of photo effects in RTP are the main reasons that RTP could not replace CFP as it was expected in earlier studies.

#### 5.Key Issues for the Development of Future RTP Systems

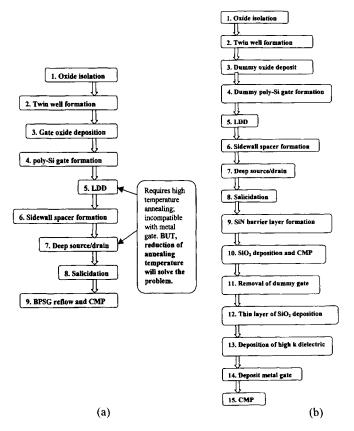

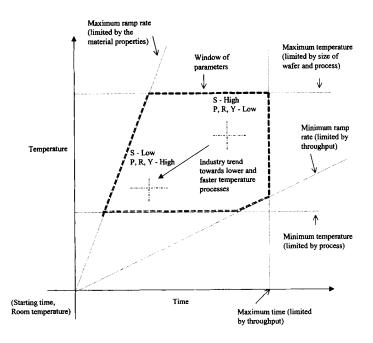

The introduction of new interconnect materials (copper as well as low dielectric constant materials) has already allowed the continuous feature size reduction of silicon ICs. At the gate stack level, high-dielectric constant materials and new gate materials are absolute necessities for sub-50 nm node technologies. As shown in Fig. 2 [modified from Ref. 23], for cost-effective manufacturing (minimization of process steps) reduction of processing temperature is a very important process integration issue.

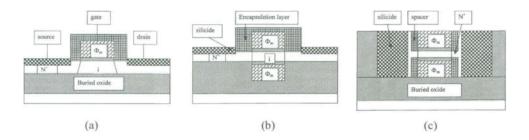

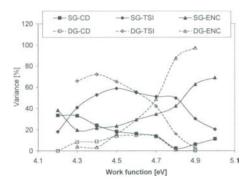

For the manufacturing of ultimate minimum feature size silicon ICs it is widely believed that alternate transistor structure (e.g. double gate CMOS) will be required. A comparison of single and double gate CMOS devices is given in Fig. 3 [24]. As shown in Fig. 4 [24], the use of current RTP tools does not provide minimum variance for double gate CMOS devices. Thus future RTP systems should provide reduced variance of the critical device design parameters.

In a recent publication [9], we have addressed the most important issues for semiconductor manufacturing in the 21<sup>st</sup> century For obtaining improved performance, reliability and yield of any semiconductor device, use of homogenous microstructure is a necessity. This can be achieved by optimizing the thermal cycle for obtaining minimum and uniform thermal stress. Fig. 5 depicts the essential features of our approach in obtaining homogenous microstructure materials. A complete details of the process outlined in Fig. 5 is given in Ref. [25] and other related publications [26-28].

#### **6.New RTP Markets**

From an equipment manufacturer's point of view (different chemistries provide a number of applications), all the current and future applications of RTP can be divided in two categories: (i) single wafer substrates, and (ii) multi-wafer or larger size substrates. The first category is the driver of current applications of RTP. The introduction of new materials in manufacturing is possible when RTP can provide significant advantages over other processing technologies. As an example, the introduction of high dielectric constant as the gate dielectric material can provide ultimate Si CMOS devices for manufacturing. As pointed out in Ref. [2], the sub-threshold slope of current devices is 100 mV/decade. If the RTP based CVD systems can provide a value close to 60-70 mV/decade, a whole new CVD based market will open. This will require a change in the current practice. In addition to Si ICs, basically the same equipment (with change of chemistry and some other details) can open new markets for compound semiconductor processing.

Fig.2 CMOS process flow: (a) Standard process flow (b) Proposed [23]-process flow, using dummy gate.

The second category involves areas such as solar cells, and display technologies. The tolerance for temperature variations is greater than what is required for applications discussed earlier. However, these applications require order of magnitudes higher throughputs. By significant reduction of activation energy and using lower-cost control systems (compared to single wafer based RTP) these applications are possible.

#### 7.Conclusions

In this paper we have analyzed the current and future prospects of RTP for semiconductor manufacturing. Current trends are in the direction of single wafer processing based manufacturing and RTP will play a very important role. We have pointed out the essential features that need to be introduced in the design of future RTP systems. Specifically, reduction of processing temperature, reduction of variance of critical device parameters and obtaining homogenous microstructures are the key issues for designing future RTP systems.

Fig.3 Schematics of Single Gate (SG) and Double Gate (DG) devices: (a) an ultra thin body SOI single-gate device; (b) the same device with two gates; (c) an ideal double-gate device [24].

Fig.4 Study of Variance of I<sub>off</sub> for 40 nm single gate (SG) and double gate (DG) technologies [24]. The three dominant sources of variations are silicon thickness (TSI), critical dimension (CD), and encapsulating spacer thickness (ENC) control.

S- Stress, P- Performance, R-Reliability, Y- Yield

Fig.5 Optimization of thermal cycle in RTP

#### Acknowledgements

One of us (RS) would like to thank former students, research associates and a number of colleagues in industry and academia. Special thanks to Drs. Chu, Thakur, Shrangpani, Chen and Parihar whose research contributions provided the framework of this work. The authors would like to thanks Anthony Dip and Sanjeev Kaushal of Tokyo Electron America, Zoran Kirvokapic of AMD, Kamal Rajkanan of KLA-Tencor, Randhir Thakur of Applied Materials, and Masahiro Yoshimura of Tokyo Institute of Technology for providing their pre-published research results. NSF, DARPA, ATP, ARO and AG Associates supported this work.

#### References

- [1] M. Moritz, Forbes ASAP, October 2, 2000, 41.

- [2] B. Yu, H. Wang, A. Joshi, Q. Xiang, J. Jeon, and M. Lin, Late News Paper, Int. Electron Devices Meeting, December 2001.

- [3] Intel Researchers Build World's Fastest Silicon Transistors, June 11,2001 http://www.intel.com/pressroom/archive/releases/20010611tech.htm

- [4] M. S. Malone, Forbes ASAP, September 10, 2001, 44

- [5] R. Singh, A. Rohatgi, K. Rajan and K. F. Poole, *Electrochemical Society Proc.* Vol. # PV 99-11, (1999), 33.

- 8

- [6] P. A. Packan, Science, 285, (1999) 2079.

- [7] M. Schultz, Nature, 99, (1999) 729.

- [8] J. H. Schon, H. Meng and Z. Bao, *Science* 294 (2001), 2138.

- [9] R. Singh, V. Parihar, K. F. Poole and K. Rajkanan, Semiconductor Fabtech, 9th Edition (1999) 223

- [10] Y. Mikata, K. Mitsutake, T. Arikado, and K. Okumura, Conf. Proc. IEEE Int. Symp. on Semiconductor manufacturing, (2001), 7.

- [11] K. Saraswat, SPIE Rapid Isothermal Processing Conf. Proc. vol. 1189, edited by R. Singh (1989) 1.

- [12] R. Doering and Y. Nishi, Proc. IEEE, 89 (2001) 375.

- [13] Anthony Dip, Tokyo Electron America, personal communication, October 2001.

- [14] P. Meissener, Workbook of Workshop on Manufacturing Issues Beyond the 70 nm Node, ISSM, October 2001

- [15] A. Koike, VLSI Techno. Symp., 2001, 1.

- [16] R. K. Surridge, et al., Proc. Int. Symp. GaAs and Related Compounds, 33a, (1977) 161.

- [17] K. Nishiyama, M. Ari, and N. Watanabe, Jpn. J. App. Phys., 19, (1980) L563.

- [18] R. Singh, J. App. Phys. 63 (1988), R59.

- [19] R. Singh, *Electronics* 58 (1985), 19.

- [20] R. Singh, Semiconductor Int. 9(1) (1986) 28.

- [21] P. H. Singer, Semiconductor Int. 12(4) (1989) 28.

- [22] P. H. Singer, Semiconductor Int. 16(6) (1993) 64.

- [23] K. Matsuo, T. Satio, A. Yagishita, T. Iinuma, A. Murakoshi, K. Nakajima, S. Omoto, and K. Suguro, Symp. on VLSI Tech, (2000) 70.

- [24] Z. Krivokapic, and W. D. Heavlin, *IEEE Trans. on Semiconductor Manufacturing*, to be published (May 2002).

- [25] R. Singh, V. Parihar, Y. Chen, K.F.Poole, S. Nimmigadda, and L. Vedula, *IEEE Trans. Semiconductor Manufacturing*, 12 (1999), 36.

- [26] R. Singh, Chap. 9, Hand Book of Compound Semiconductors, Noyce Pub. (1995) 442.

- [27] R. Singh, and V. Parihar, Vol. 2, Chap. 1, Hand Book of Low and High Dielectric Constant Materials, Academic Press (1999) 1.

- [28] R. Singh, M. Fakhruddin and K. F. Poole, Applied Surface Science, 168 (2000) 198.

### Analytical Model for Spike Annealed Diffusion Profiles of Low-Energy and High-Dose Ion Implanted Impurities

Kunihiro Suzuki and Hiroko Tashiro Fujitsu Laboratories Ltd. 10-1 Morinosato-Wakamiya Atsugi 243-0197, Japan Tel: +82-463-250-8236, E-mail: suzuki@flab.fujitsu.co.jp

#### 1.Introduction

Scaling theory requires shallow junctions [1-4]. Spike annealing, where the isothermal time period is zero or quite short, enables us to obtain these shallow junctions. Combined with low-energy ion implantation, this technology is hence frequently used in the high-speed MOSFET processes [5]. Temperature is always time dependent in these processes, and we need to acquire accurate parameters over a wide temperature range including the transient effects of the processes to analyze these processes. This kind of rigorous treatment has been performed in commercial process simulators [6-8]. However, many ambiguous models and their related parameters exist. Therefore, it is difficult to obtain a clear idea of how to optimize the spike annealing conditions.

Many researchers have studied high concentration diffusion profiles using analytical approaches [9-16]. However, the diffusion coefficient depends on the doping concentration [17], and the diffusion equation thus becomes nonlinear and difficult to solve. Nakajima and Fair proposed models for the profiles [9-12]. These models are functions to express the profiles and are not based on the diffusion equation. Anderson solved the nonlinear equation in the case of a constant total dose condition [13, 14]. However, the common boundary condition for the high concentration diffusion is the constant surface concentration instead of the constant total dose in high dose conditions. We derived a diffusion model with the constant surface concentration based on the nonlinear diffusion equation [15, 16].

Here, we extend our model for high-concentration-diffusion profiles to accommodate spike annealed diffusion profiles and the corresponding junction depth,  $x_j$ , and show the optimum condition to obtain shallow the junctions with abrupt profiles.

#### 2.Experimental

We used Si(100) substrates, and ion implanted B at 0.5, 1, 3, 5 keV or As 1, 3, 5 keV and a dose of  $1 \times 10^{15}$  cm<sup>-2</sup>. The substrates were then subjected to rapid thermal annealing with the ramp-up rate of 60°C/sec and isothermal process time was 1 sec. The impurity profiles were evaluated using secondary ion mass spectrometry (SIMS). The junction depth x<sub>j</sub> was defined

by the depth where impurity concentration is  $10^{18}$  cm<sup>-3</sup>.

#### **3.Results**

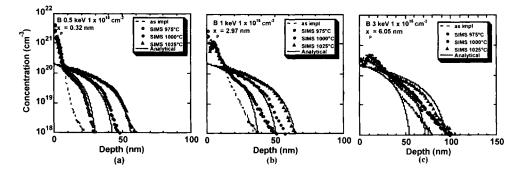

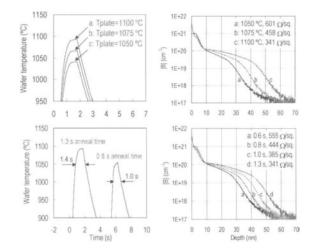

Figure 1 shows B SIMS diffusion profiles at the energies of 0.5, 1, and 3 keV for the maximum temperatures of 975, 1000, and  $1025^{\circ}$ C. At the energy of 0.5 keV,  $x_j$  decreased with decreases of the maximum temperature as was expected. However,  $x_j$  became insensitive to the maximum temperature with increases of the acceleration energy, and finally, it became invariant at 3 keV. This is because transient enhanced diffusion (TED) dominates  $x_j$ , and TED starts and finishes during the ramp-up time period before reaching 975°C [17]. The thermal equilibrium diffusion dominates  $x_j$  at low energy since TED is suppressed in the low-energy region [18-20].  $x_j$  then becomes dependent on the annealing condition. On the other hand,  $x_j$  is less dependent on acceleration energy in the low energy range of less than 1 keV. Therefore, it is good to reduce energy to be free of TED and control  $x_i$  by temperature.

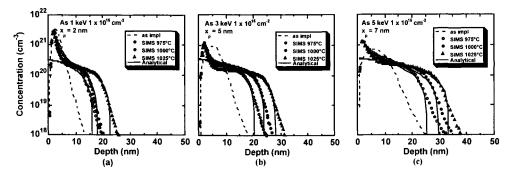

Figure 2 shows As SIMS diffusion profiles at the energies of 1, 3, and 5 keV for the maximum temperatures of 975, 1000,  $1025^{\circ}$ C.  $x_j$  always decreased with decreases of the maximum temperature for all energy ranges as was expected. This is because As is insensitive to TED.

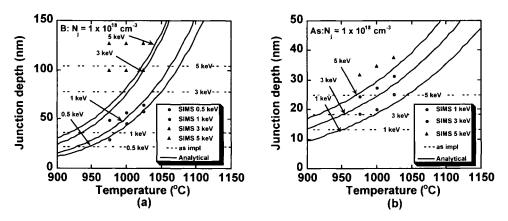

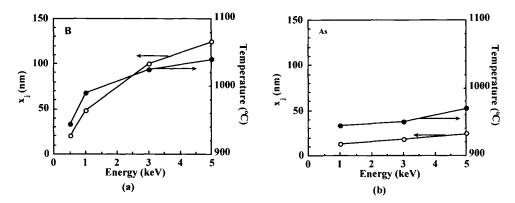

Figure 3(a) summarizes the dependence of  $x_j$  associated with B diffusion profiles for the maximum annealing temperatures. Dashed lines correspond to the  $x_j$  of as-implanted profiles. In the low-energy region of less than 1 keV,  $x_j$  increases with increases of temperature, and the difference of  $x_j$  between 0.5 and 1 keV becomes at the increased maximum temperature. This is because the diffusion length is much deeper than the  $x_j$  of the as-implanted profiles.  $x_j$  is independent of temperature in the higher energy range of 3 to 5 keV. This is because TED dominates  $x_j$ , as mentioned before.

Figure 3(b) summarizes the dependence of  $x_j$  of the As diffusion profiles on the maximum annealing temperature. Dashed lines correspond to  $x_j$  of as-implanted profiles.  $x_j$  increased with increases of temperature over the whole acceleration energy range as was expected.

Fig.1 Boron diffusion profiles. Analytical models are also shown. (a) 0.5 keV, (b) 1 keV, (c) 3 keV

Fig.2 Arsenic diffusion profiles. Analytical models are also shown. (a) 1 keV, (b) 3 keV, (c) 5 keV.

Fig.3 Summary of junction depths of impurity diffusion profiles. (a) B, (b) As.

#### 4.Discussion

We developed a model for high-concentration-impurity diffusion profiles [15] given by

$$N = N_{\rm s} \left( 1 - \rho Z_{\rm Y} Y - Y^2 \right)^{1/\gamma} \tag{1}$$

where  $N_s$  is the maximum diffusion concentration, Y is the normalized depth, and  $\gamma$  is the parameter which expresses the significance of the impurity diffusion coefficient on concentration and is 0.5 for B and 1 for As [16]. Y is expressed by

$$Y = \frac{x}{\sqrt{\frac{4(\gamma+2)\eta_{yr}}{\gamma} (\frac{N_s}{n_r})^{\gamma} D_{rt}}}$$

(2)

where  $\eta_{\gamma a}$  is a constant number and depends on  $\gamma$ , however it is around 1.7 [15]. Equation 1 is valid for the isothermal process. In the spike annealing processes, it is unclear what are  $D_i$  and t in our model. It may be possible to include the time dependent  $N_s$ ,  $n_i$ , and  $D_i$  in the model. However, we need to have accurate values for  $N_s$ ,  $n_i$ , and  $D_i$  over a wide temperature range

and accurate time-temperature curves, which are very difficult to obtain. Therefore, we adopt an empirical approach with the aid of experimental data.

The denominator of Y in Eq. 1 is related to the diffusion length, and we express the denominator as  $x_0$ , therefore, Y is then expressed by

$$Y = \frac{x - x_p}{x_0(T_m, E)}$$

(3)

$x_p$  is the depth at the maximum concentration, and we use the projected range  $R_p$  of ion implantation for  $x_p$ .  $x_0$  empirically expresses the diffusion length that should be related to the ramp-up, ramp-down, and  $T_m$ . Inspecting Eqs. 2 and 3,  $x_0$  is a function of  $N_s$ ,  $n_i$ , and  $D_i$ , and they are all expressed by their corresponding activation energies. Therefore, we expect that  $x_0$  is expressed by an activation energy, which is t be verified later.

$x_j$  can be estimated as N = 0 in Eq. 1. The corresponding Y,  $Y_j$ , is given by

$$Y_{j} = \frac{\sqrt{2}}{\sqrt{7 + 2}}$$

and hence x<sub>j</sub> is given by

(4)

$$x_{j} = x_{j}(E) + \frac{f_{2}}{f_{1}^{\gamma} + \sqrt{\gamma + 2}} x_{0}(T, E)$$

(5)

The definition of  $x_j$  is the difference between the analytical model and the experimental data. However, the profile based on the analytical model is abrupt near the junction, and hence the value is insensitive to the concentration. We extracted  $x_0$  so that Eq. 1 fits the SIMS data in the high-concentration region shown in Fig. 4, and they are given by

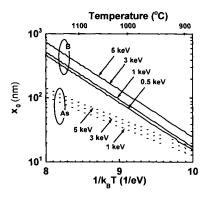

Fig.4 Dependence of extracted diffusion length on temperature

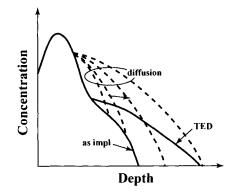

Fig.5 Schematic diffusion profiles. TED starts and finishes before normal diffusion occurs. The normal diffusion proceeds in the high concentration region, and the junction depth is invariant before the normal diffusion reaches the junction depth associated with the as-implanted profile or TED.

$$x_{0}(B) = \begin{cases} \left(3.3 + 0.9E\right) \times 10^{8} \exp\left[-\frac{1.7(eV)}{k_{B}T}\right] & nm \quad for \ E \le 3 \ keV \\ 6 \times 10^{8} \exp\left[-\frac{1.7(eV)}{k_{B}T}\right] & nm \qquad for \ E > 3 \ keV \end{cases}$$

(6)

$$x_0(As) = (4.2 + 0.4E) \times 10^5 \exp\left[-\frac{1.05(eV)}{k_BT}\right] nm$$

(7)

$x_0$  depends on temperature and energy.  $x_0$  for As is smaller than that for B, which is plausible since the diffusion length of As is smaller than that of B.  $x_0$  weakly depends on the energy value. We do not know what is the physical meaning of the energy dependence.

The analytical model agrees well with the experimental data for 0.5 keV for the B diffusion profiles. Our model reproduces the experimental data in the high-concentration region for the higher energy regions. However, it deviates from the experimental data in the low concentration region. The profiles suffer from TED and our model does not include TED. The analytical model agrees well with the experimental data in the high-concentration region of the As diffusion profiles. However, the experimental data deviate from the analytical model in the low-concentration region. The experimental data may suffer resolution limit of SIMS measurement. However, we do not know its significance, or if the tail profile in the low-concentration region is real or not.

Our model focuses on the profiles associated with normal diffusion and assumes that the initial junction depth is  $x_p$ , which is the peak position of as-implanted profiles, and it does not include TED. Therefore, the information associated with as-implanted profiles and TED should be obtained experimentally.

We denote the junction depth associated with the as-implanted profile  $x_j$ (as-impl), that with TED  $x_j$ (TED) and that with the thermal equilibrium diffusion  $x_j$ (diff). TED starts and finishes within quite a short time, and the thermal equilibrium diffusion occurs dominantly in the high-concentration region and  $x_j$ (as-impl) and  $x_j$ (TED) are invariant during the thermal equilibrium diffusion, as shown by the schematic in Fig. 5. Therefore, each junction depth can be treated independently and the final junction depth is the maximum value among the junction depths, expressed by

$$x_{j} = Max \left[ x_{j} (as impl), x_{j} (TED), x_{j} (diff) \right]$$

(8)

Note that the abruptness of the diffusion profile is better than that of as-implanted or TED profiles. Therefore, we can regard the optimum profile as the normal diffusion profile that dominates  $x_j$ . Therefore, the diffusion condition should be selected so that thermal equilibrium diffusion dominates  $x_j$ , that is

$$Max\left[x_{j}(as \ impl), \ x_{j}(TED), \ x_{j}(diff)\right] = x_{j}(diff)$$

(9)

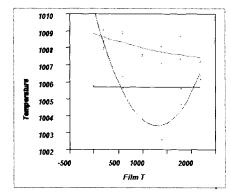

Fig.6 Dependence of optimum junction depth on acceleration energy. The corresponding maximum temperature is also shown.(a) B, (b) As.

Figure 3(a) shows the analytical model for the dependence of  $x_j$  on maximum temperature for B diffusion profiles. We can draw lines that correspond to  $x_j$  associated with normal diffusion. We can estimate the optimum diffusion condition graphically as a cross point of the line and junction depth associated with the as-implanted profiles or TED profiles. For 0.5 keV, the optimum point was the cross point of the junction depth associated with the as-implanted profile and that with the normal diffusion profile. For 1 keV, we observed TED at 975°C, and the optimum point was the cross point of TED and the normal diffusion. For 3, and 5 keV, the optimum point clearly was the normal diffusion condition where the diffusion reached  $x_j$ associated with TED.

Figure 3(b) shows the analytical model for the dependence of  $x_j$  on the maximum temperature for the As diffusion profiles. The optimum diffusion condition is the cross point of the line of  $x_j$  associated with the normal diffusion and that with as-implanted profiles, as TED does not affect the diffusion profiles significantly for As diffusion.

Figure 6 summarizes the optimum junction depth. As the energy decreases, the junction depth decreases accordingly with lower maximum temperatures. For 0.5 keV B, a 20-nm junction depth can be expected at 945°C spike annealing, and 13 nm junction depth can be expected for As 1 keV at 945°C.

#### 5.Summary

We showed systematic spike annealed diffusion data and showed that low-energy B ion implantation is effective to be free from transient enhanced diffusion. We extended our highconcentration diffusion model to spike annealing profiles by introducing an effective diffusion length. Our model well expresses the diffusion data in the high-concentration region, but deviates from the data in the low-concentration region, where transient enhanced diffusion or the as-implanted profile dominates the junction depth. Optimum points are evaluated as the cross point of the junction associated with the normal diffusion junction and junctions associated with the as-implanted profiles or the transient enhanced diffusion. We can realize 20-nm junction depth with 0.5 keV and 945°C spike annealing for B, and 13 nm junction depth with 1 keV and 945°C spike annealing for As.Since our model is empirical, we should obtain similar data related to annealing equipment used, and corresponding the ramp-up period and ramp-down process.

#### References

- R. H. Dennard, F. H. Gaensslen, H. N. Yu, V. L. Rideout, E. Bassous, and A. L. Blanc, "Design of ion-implanted MOSFETs with very small physical dimensions," IEEE J. Solid-State Circuits, vol. SC-9, pp. 256-268, 1974.

- [2] J. R. Brews, W. Fichtner, E. H. Nicollian, and S. M. Sze, "Generalized guide for MOSFET miniaturization," IEEE Electron Dev. Lett., vol. EDL-1, pp. 2-4, 1980.

- [3] P. Chatterjee, W. R. Hunter, T. C. Holloway, and Y. T. Lin, "The impact of scaling laws on the choice of n-channel or p-channel for MOS VLSI," IEEE Electron Dev. Lett., vol. EDL-1, pp. 220-223, 1980.

- [4] G. Baccarani, M. R. Wordeman, and R. H. Dennard, "Generalized scaling theory and its application to a 1/4 micrometer MOSFET design," IEEE Trans. Electron Dev., vol. ED-31, pp. 452-462, 1984.

- [5] A. Agarwal, H. J. Gossmann, and A. T. Fiory, Tech. Digest of Solid-State Devices and Materials, p. 508, 1999.

- [6] TSUPREM IV USERS' manual, AVANT!.

- [7] SSUPREM IV USERS' manual, SILVACO.

- [8] DIOS USERS' manual, ISE.

- [9] Y. Nakajima, S. Ohkawa, and Y. Fukukawa, "Simplified expression for the distribution of diffused impurity," Japan J. Appl. Phys., vol. 10, pp. 162-163, 1971.

- [10] R. B. Fair and J. C. C. Tsai, "The diffusion of ion-implanted arsenic in silicon," J. Electrochem. Society, vol. 122, pp. 1689-1696, 1975.

- [11] R. B. Fair and J. C. C. Tsai, "Profile parameters of implanted-diffused arsenic layers in silicon," J. Electrochem. Society, vol. 123, pp. 583-586, 1976.

- [12] R. B. Fair, "Boron diffusion in silicon-concentration and orientation dependence, background effects, and profile estimation," J. Electrochem. Society, vol. 122, pp. 800-805, 1975.

- [13] D. Anderson and M. Liasak "Approximate solutions of some nonlinear diffusion equations," Physical Review A, vol. 22, pp. 2761-2768, 1980.

- [14] D. Anderson and K. O. Jeppson, "Nonlinear two-step diffusion in semiconductors," J. Electrochem. Society, vol. 131, pp. 2675-2679, 1984.

- [15] K. Suzuki, "High concentration impurity diffusion model," Solid-State Electronics, vol. 44, pp. 457-463, 2000.

- [16] K. Suzuki, "High concentration diffusion profiles of low energy ion-implanted B, As, and BF2 in bulk Silicon," Solid-State Electronics, vol. 45, pp.1747-1751, 2001.

- [17] S. K. Ghandhi, VLSI Fabrication Principles, John Wiley&Sons, Inc., New York, 1994.

- [18] K. Suzuki, M. Aoki, Y. Kataoka, N. Sasaki, A. Hoefler, T. Feudel, N. Strecker, and W. Fichtner, "Analytical models for transient diffusion and activation of ion-implanted boron during rapid thermal annealing considering ramp-up period," International Electron Device Meeting, pp.799-802, 1996.

- [19] K. Suzuki, T. Miyashita, Y. Tada, A. Hoefler, N. Strecker, and W.Fichtner, "Damage calibration concept and novel B cluster reaction model for B transient enhanced diffusion over thermal process range from 600°C (839 h) to 1100 (5s) with various Ion implantation doses and energies," International Electron Device Meeting, pp.501-504, 1997.

- [20] A. Agarwal, H. J. Gossmann, D. J. Eaglesham, L. Pelaz, D. C. Jacobson, T. E. Haynes, and Y. E. Erokhin, Appl. Phys. Lett., vol. 71, p. 3141, 1997.

# **Process and Technology Drivers for Single Wafer Processes in DRAM Manufacturing**

R. A. Weimer<sup>1</sup>, D. C. Powell<sup>1</sup>, and P. M. Lenahan<sup>2</sup>

<sup>1</sup>Micron Technology, Inc., 8000 S. Federal Way, MS 306, Boise, ID 83707-0006, USA Phone: 208-368-5605 Fax: 208-368-2548 E-mail: rweimer@micron.com <sup>2</sup>The Pennsylvania State University, University Park, PA 16802, USA Phone: 814-863-4630 E-mail: pmlesm@engr.psu.edu

#### **1.Introduction**

Cost of ownership (COO) continues to determine that batch wafer systems dominate front-end-of-the-line (FEOL) DRAM processes such as low pressure chemical vapor deposition (LPCVD) of films, oxidation cycles, and wafer anneal cycles. As of today, process advantage for a single wafer technology can only be gained by an enabling process that is not available in a batch system. Therefore, to displace the batch system, single wafer technologies must show some unique process capability or significant process advantage. As DRAM devices shrink below the  $0.15\mu$ m technology node, however, the process control of the transistor devices becomes more critical for optimal DRAM performance. Thus, one potential process advantage may be gained by a reduced thermal budget for single wafer tools in process areas still dominated by batch processing. In this paper, we review the current status of single wafer FEOL processes in DRAM production as well as possible paths for current batch processes to move toward single wafer tools.

#### 2. Current Rapid Thermal Processing (RTP) Anneal Technologies

As shown in Table I, each RTP anneal technology has potential advantages and disadvantages for processing wafers. In choosing an RTP tool set for DRAM manufacturing, cost of ownership and tool footprint are two very important parameters to consider. As reviewed in previous work, DRAM devices to date have not needed the advanced temperature control and temperature uniformity that logic devices need due to the high thermal processing associated with construction of the DRAM cell capacitor (for non-trench cells) [1]. As projected, however, the need for high-temperature uniformity is close at hand due to decreasing gate lengths in DRAM technology.

| Technology<br>ontrol)                            | (heating/temperature               | Advantages               | Possible issues                    |

|--------------------------------------------------|------------------------------------|--------------------------|------------------------------------|

| Axi-symmetric lamps/ reflecting plate            |                                    | Ease of rotation         | Coating of reflecting plate        |

|                                                  |                                    | No interference between  | More susceptible to pattern effect |

|                                                  |                                    | temperature control and  | Power requirements                 |

|                                                  |                                    | wafer                    | Lamp/quartz interactions           |

|                                                  |                                    | MIMO temperature control |                                    |

| Double-sided lamps/ripple pyrometer <sup>™</sup> | amps/ripple pyrometer <sup>™</sup> | Known technologies       | Coating of quartz ware/temperature |

|                                                  |                                    | Reduced complexity       | control                            |

|                                                  |                                    | Reduced pattern effect   | No MIMO                            |

| Furnace core/augmented pyrometer                 |                                    | Very simple              | No MIMO                            |

|                                                  |                                    | Low power                | Uniformity changes very difficult  |

|                                                  |                                    | Little pattern effect    |                                    |

| Isothermal heater(s) front and/or back           | ter(s) front and/or back           | Very simple              | Emissivity issues on ramp          |

|                                                  |                                    | Low power                | Uniformity cannot be changed       |

|                                                  |                                    | No pattern effect        |                                    |

Table I. Brief review of the current commercially available RTP technologies for BPSG reflow and spike anneal.

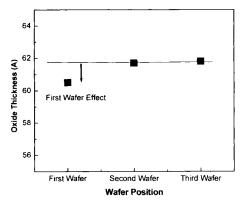

Most of the temperature control systems in RTP systems as of today can safely claim  $<4^{\circ}$ C total temperature variation wafer-to-wafer as a result of wafer emissivity change. As shown in Fig. 1, this particular technology has a 4°C variation due to backside emissivity changes and an approximate 3°C offset with variation of front side films. However, even the most advanced temperature control systems can have issues resulting from chamber conditioning. As shown in Fig. 2, even with a relatively simple process such as oxide growth, the most advanced RTP technologies may suffer from mundane issues such as first wafer effect. Another area of continuing emphasis should be in the area of tool-to-tool matching. Although temperature control on individual tools is excellent, process variation tool-to-tool may be more than the individual chamber variation specifications, depending on the calibration-matching technique for the given RTP technology.

Fig.1 Emissivity testing of an RTP technology with bare silicon (blue), emissivities ranging from 0.36–0.6 (red ), and front side emissivities (0.36–0.6) (green).

Fig.2 Oxide growth in RTP system showing first wafer effect even with advanced RTP temperature control.

#### **3.BPSG Reflow**

RTP technology has now been in production for doped-glass reflow for over ten years. The need for high-temperature reflow of doped oxide is due to the very tight wordline-towordline pitch in a DRAM device relative to that of a logic device. Inadequate reflow can result in shorts between the wordlines or digit contacts. Due to the high temperatures needed to reflow the doped glass, a batch system would densify the BPSG before the reflow could be achieved. As shown in previous publications, this RTP anneal is typically the first major heat step post-transistor implants and thus can account for up to 30% of the final transistor variation [1]. The temperature uniformity of this anneal has not been a critical issue in the past. As mentioned, however, as DRAM technologies continue to shrink, the temperature uniformity of the doped glass reflow will become more critical.

#### 4.Gate Dielectrics

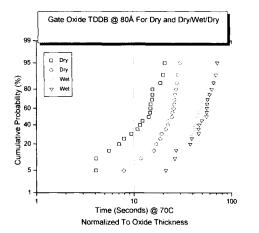

One of the potential future applications for single wafer processing for DRAMs would be gate-oxidation. It is known that oxides grown with steam (and usually some post-treatment or anneal) perform better in reliability testing than do dry oxides. As shown in Fig. 3, the charge-to-breakdown (Qbd) of these wet oxides is greatly improved over dry ( $O_2$  oxides) when subjected to DRAM processing.

Fig.3 Charge-to-breakdown (Qbd) from a constant electric field stress of gate oxides that have gone through a simulated DRAM process flow. Wet oxides (H<sub>2</sub>O, blue-green) clearly have a higher Qbd than dry (O<sub>2</sub> only, red-black) oxides.

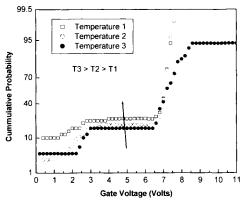

Fig.4 Cumulative probability of breakdown for gate oxides from a DRAM process flow. Decreasing the temperature (T3>T2>T1) at which these oxides were grown is shown to increase the defect density for the early defect failures of the oxides. However, it is also true that higher temperatures of growth also may provide an advantage to gate oxides. As shown in Fig. 4, decreasing oxide growth temperature increases the defect tail of the intrinsic defect strength of the oxide subjected to a ramped voltage stress. Thus, DRAM gate oxide performance drives the gate oxide growth regions to higher temperatures with steam. Obviously, as DRAM technology continues to scale down, the decreasing gate oxide thickness may eventually make a higher temperature, single wafer steam process preferable to that of a lower temperature batch system. The shorter processing time also increases the throughput and therefore lowers the COO.

An ideal single wafer system for DRAM gate oxides should have at least the following characteristics:

- Quartz-lined chamber for steam processing as well as possible use of chlorine source for metals gettering.

- A small volume for rapid ambient changes such that a substantial portion of the growth is in the ideal regime.

- Load lock and ambient control for staging with pre-gate oxide growth cleans.

- Multi-chambers (>2) on a small platform for improved throughput and foot print (COO).

Another process necessity that may drive DRAMs to single wafer gate oxides is the need for surface P-channel devices. For boron penetration, conventional anneals in nitric or nitrous have been shown to be effective in stopping boron. However, relative to a logic process, the higher thermal budget of a DRAM requires a higher amount of nitrogen at the oxide-silicon interface. This high amount of nitrogen will lead to device transconductance loss and

Fig.5 Electron spin resonace spectra from a gate oxide on silicon, as grown (blue) and post-UV light stress (red). The E` (oxygen vacancies) and Pb (interface states) are clearly shown in these 40Å oxides.

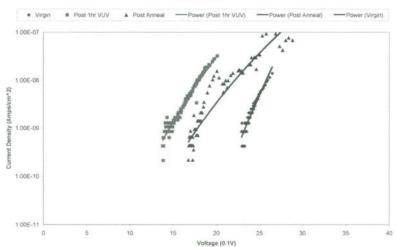

Fig.6 Measurement of corona ion leakage through the gate oxide, virgin (diamonds), post 1-hour UV stress (square), and post-atmospheric anneal at 250°C (triangle).

Fig.7 Electron spin resonace spectra from a gate oxide with nitric oxide anneal on silicon as grown (blue) and post-UV light stress (red). The E' (oxygen vacancies are reduced relative to the standard gate oxide.

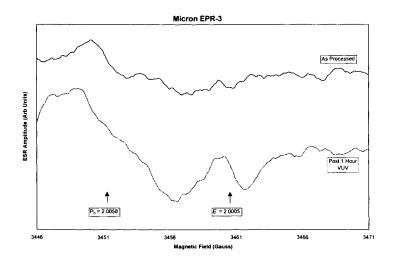

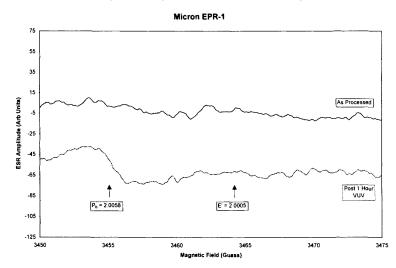

reliability issues as shown in the literature [2–5]. As shown in Fig. 5, a 40Å oxide grown by conventional means shows the typical interface states (Pb centers) and oxide vacancies (E' centers) as analyzed by electron spin resonance [6–8]. These oxides were then subjected to a UV-light stress (carrier injection). The relative number of interface states, as well as the relative number of oxygen vacancies in the film, is shown to increase post-UV stress. This

increase in oxide defects is reflected in the increase in Corona leakage through the films as shown in Fig. 6. As shown, however, the leakage degradation can be recovered through an atmospheric anneal at 250°C.

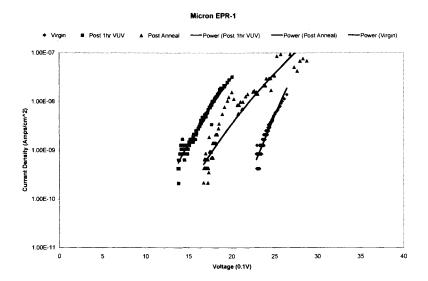

For nitric annealed wafers, though, the relative number of E' and Pb centers are lower prior to stress and do not increase as much as the standard oxide post-UV stress, as shown in Fig. 7 and Fig. 8. This is consistent with previous published estimations of interface traps/states [9]. However, in the case of the nitric annealed wafers, the atmospheric anneal does not recover fully the leakage current. Thus, some unpassivated leakage paths exist post-stressing in these films. This may ultimately lead to reliability issues with the DRAM process flow. This issue compounds the issue of transconductance loss for DRAM applications.

As one potential alternative process, composite gate dielectrics of oxide and higher K material may be potential candidates for DRAM devices. Although composite nitride-oxide gates may be precluded from logic applications due to the high effective oxide thickness (EOT), these may be useful for the relatively thick DRAM gate dielectrics [10–11]. Many parameters have made single wafer processing the choice for these composite gates. The most prevalent are the choice of nitride growth precursor for high nucleation on oxide and the need for pre- and/or post-nitride treatments for reduced dielectric charges in the final composite film.

#### **5.Advanced Oxidation**

For standard wordlines with tungsten silicide gates, it is known that oxidation of the poly

Fig.8 Measurement of corona ion leakage through the gate oxide with nitric oxide anneal, virgin (diamonds), post-1 hour UVstress (square) and post-atmospheric anneal at 250°C (triangle).

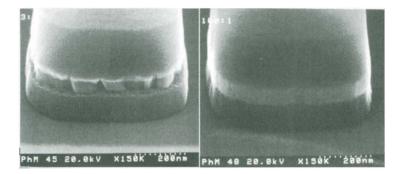

gate sidewall and gate oxide edge post-patterning with dry etch is needed for improved reliability of the device. As these device widths shrink, the amount of oxidation under the gate becomes critical. The process demands a minimal amount of oxidation under the gate while still oxidizing the sidewall of the poly silicon wordline. To achieve this goal, many logic companies have turned to single wafer systems [12]. These systems allow for higher oxidation temperatures with a minimal thermal budget. The higher oxidation temperatures therefore allow for higher poly oxidation rates (reaction rates) relative to the oxide thickening (diffusion limited). DRAM devices may ultimately find such advantages with single wafer solutions.

Device speed improvements may ultimately push DRAM devices to move to advanced gate stacks such as TiSix, CoSix, or tungsten. Equipment manufacturers are already exploring selective oxidation of silicon (relative to tungsten) to use in the oxidation of the wordline and gate oxide [12]. As shown in Fig. 9, selective oxidation may be a very successful single wafer application. The need for strict ambient control in isolating wafers from free oxygen as well as reportedly nitrogen would favor the use of a smaller, single wafer chamber over the large volume batch systems.

The advantage of high temperature oxidation in a single wafer tool may ultimately be needed for STI oxidation liners. The potential for a more uniform oxidation of the trench sidewall relative to the corner rounding of the trench may ultimately show a large process advantage for future DRAM generations.

#### **6.Ultra-Shallow Junctions**

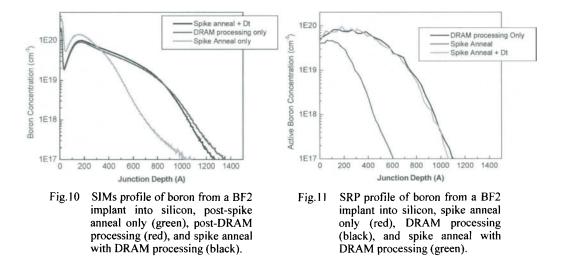

To date, the DRAM thermal processing budget post-critical transistor implants (for DRAMs with non-trench cells) is still too high to benefit from a spike anneal of the boron implant [13–16]. To demonstrate this, BF2 was implanted into silicon through a thin oxide surface and processed as follows: one wafer was spike annealed, one wafer was run through a simulated DRAM process flow, and one wafer was spike annealed immediately post-implant and then run concurrently through the DRAM process flow. As shown in Fig. 10, the SIMs

Fig.9 Comparison of SEM cross section after RTP oxidation in (a) a non-selective regime (950°C 30% steam) and (b) selective regime (950°C 1% steam) for test structure.

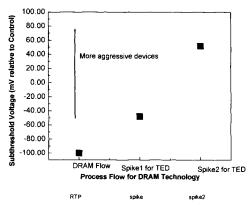

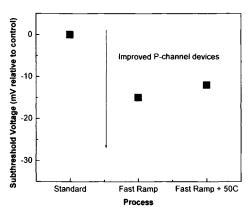

profile of the boron in the wafer showed little if any difference between the DRAM process and the spike anneal + DRAM process. The SRP profiles of Fig. 11 also show that the active carrier concentration profiles are very similar. Previous work has shown that the P-channel subthreshold voltage of a DRAM device is a good measure of thermal budget. Transistor devices show that the subthreshold voltage for two different spike anneals immediately posttransistor implants do not improve the DRAM device performance (Fig. 12). The devices are actually made more aggressive by the additional thermal budget as shown by the increase (more positive) subthreshold voltages.

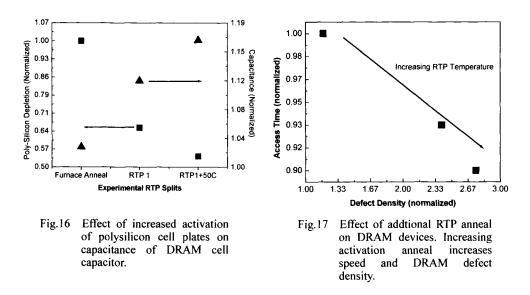

Fig.12 Sub-threshold voltage of DRAM device with a spike anneal of critical implant prior to DRAM processing relative to standard DRAM processing only.

Fig.13 Subthreshold voltage of DRAM device with additional RTP anneal in process flow.

#### **7.RTP Activation Anneals**

A rapid thermal anneal can be used as a possible activation for the doped polysilicon or active areas in a DRAM device. As shown in Fig. 13, placement of the RTP activation anneal can be critical for the DRAM transistors. For the same thermal budget, the RTP can have drastically different effects on the transistor leakage characteristics (important for DRAM refresh) as measured by the change in the subthreshold voltage.

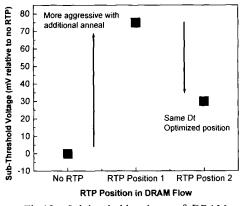

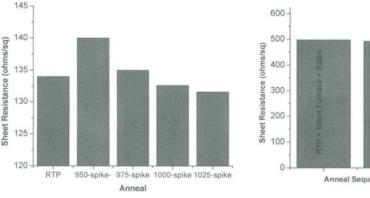

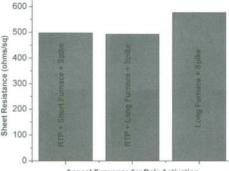

One potential application of spike anneals would be to activate dopants with reduced overall thermal budget. As shown in Fig. 14, doped poly is activated with a spike anneal with the resulting Rs measured relative to a more conventional RTP anneal. Again, the placement of the RTP relative to the other thermal processing is important. In Fig. 15, the resulting crystal structure from the initial crystallization anneal affects the final Rs in addition to the final activation anneal. In Fig. 16, however, it is shown that increased cell plate activation due to RTP activation reduces the poly cell plate depletion while improving the capacitance. These gains in speed and capacitance are not limitless [17]. As explored previously, increased thermal budget can increase the number of DRAM manufacturing defects even as overall speed of the devices increases as shown in Fig. 17.

#### **8.LPCVD Processes**

In general, the advantage of an LPCVD single wafer technology over the batch process is not clearly established for FEOL DRAM production. The COO of most single wafer processes, such as polysilicon, nitride, LPCVD oxide, and so on, are very large relative to a batch process. The cost of ownership is not only the cost of single wafer tools and the number of tools needed relative to batch technologies, but it is also the cost of down time; the need for cleans, chamber pre-treatments, and equipment maintenance; and consumable costs.

Fig.14 Sheet resistance of doped poly silicon.Comparison of standard

Anneal Sequence for Poly Activation

Fig.15 Sheet resistance of doped polysilicon relative to position of RTP anneal in DRAM process flow.

Established single wafer technologies for FEOL are ones that have deposition chemistries that are not conducive to batch processing, such as silicide deposition for the wordline. However, other processes such as selective rough polysilicon and ultra-thin cell dielectrics that may benefit from stringent ambient control may ultimately benefit from single wafer processing.

For LPCVD batch processes, reducing the deposition parameters of temperature and time is only now becoming important for DRAM production. While much less critical to the overall DRAM thermal budget than oxidation and RTP reflow processes, single wafer tools may at some future point provide some advantage for DRAMs. As shown in Fig. 18, the thermal budget saved by a fast ramp LPCVD process over a standard furnace already noticeably affects advanced DRAM devices.

The focus for single wafer tools for these established LPCVD batch processes should, however, be on advanced chemistries that fundamentally alter the property of the material. For example, to benefit DRAMs that rely on a hard mask pattern for dry etch control, advanced chemistries for silicon nitride or alternative materials should be explored on single wafer to provide more margin for dry etch chemistries.

#### 9.Summary

Advanced DRAM processing will migrate toward single wafer processing only when process requires the advantages of single wafer technologies. Ultimately, processes such as the oxidations of the wordline poly or active area for gate dielectric formation may become single wafer processes due to the need for ambient control in future DRAM devices. Other processes that are post-critical DRAM transistor implants will benefit eventually from the lower thermal budget of the single wafer processing relative to batch systems. Most processes

Fig.18 Improvement in DRAM transistors due to fast ramp furnace for process post-critical transistor implants.

to date, however, will need to show some distinct process advantage for a single wafer technology to overcome the large COO associated with a single wafer technology relative to a batch system.

#### References

- Ronald A. Weimer, Proc. Electrochemical Society Meeting, ULSI Process Integration, p. 59, Honolulu, HI (1999).

- [2] T. Hori, IEEE Trans. Electron Devices, 37, p. 2058 (1990).

- [3] H. S. Momose, T. Morimoto, K. Yamabe, and H. Iwai, IEDM Tech. Dig., p. 65 (1990).

- [4] M. Khare, X. W. Wang, and T. P. Ma, IEEE Electron Device Lett., 20 (1), p. 57 (1999).

- [5] Mariko Takayanagi-Takagi and Yoshiaki Toyoshima, IEDM Tech. Dig. (1998).

- [6] P. M. Lenahan, J. J. Mele, J. P. Campbell, A. Y. Kang, R. K. Lowry, D. Woodbury, S. T. Liu, R. Weimer, P. M. Lenahan, and J. F. Conley, Jr., *J. Vac. Sci. Technol.* B16 (4), Jul/Aug, p. 2134 (1998).

- [7] W. L. Warren, M. R. Shaneyfelt, D. M. Fleetwood, J. R. Schwank, P. S. Winokur, and R. A. B. Devine, *IEEE Transactions on Nuclear Science*, 41 (6), p. 1817 (1994).

- [8] D. M. Fleetwood and N. S. Saks, J. Appl. Phys. 79 (3), p. 1583 (1996).

- [9] G. Lucovsky, IBM J. Res. Develop., 43 (3), p. 301 (1999).

- [10] Anri Makajima, Takashi Yoshimoto, Toshiro Kidera, Katsumori Obata, Shin Yokoyama, Hideo Sunami, and Masataka Hirose, *Applied Physics Letters*, 77 (18), p. 2855 (2000).

- [11] John H. Das, Carl Powell, Vidula Kirtikar, April D. Daniel, Ron Weimer, and Sing Pin Tay, IEEE 8<sup>th</sup> International Conf. on Adv. Thermal Proc. of Semiconductors RTP2000, p. 154, Gathersberg, MD, Sept 20–22, (2000).

- [12] Richard B. Fair, IEEE Transactions on Electron Devices, 37 (10), p. 2237 (1990).

- [13] P. M. Fahey, P. B. Griffin, and J. D. Plummer, Rev. Mod. Phys., 61 (2), p. 289 (1989).

- [14] K. S. Jones and G. A. Rozgonyi, *Rapid Thermal Processing Science and Technology*, Ch. 5, Academic Press, NY (1993).

- [15] J. Hebb and K. F. Jensen, 4<sup>th</sup> Int. Conf. on Advanced Thermal Processing of Semiconductors RTP '96, edited by R. B. Fair, M. L. Green, B. Lojek, and R. P. S. Thakur, Boise, ID (1996).

- [16] R. A. Weimer, D. Ratakonda, C. Powell, M. Nuttal, R. P. S. Thakur, P. J. Timans, and N. Shah, 5<sup>th</sup> Int. Conf. on Rapid Thermal Processing of Semiconductors RTP '97, p. 91, New Orleans, LA (1997).

# Ultra-high vacuum rapid thermal chemical vapor deposition for formation of TiN as barrier metals

S. Naito<sup>1</sup>, M. Okada<sup>1</sup>, O. Nakatsuka<sup>2</sup>, T. Okuhara<sup>4</sup>, A. Sakai<sup>1</sup>, S. Zaima<sup>3</sup>, and Y. Yasuda<sup>1</sup>

<sup>1</sup>Department of Crystalline Materials Science, Graduate School of Engineering, Nagoya University

<sup>2</sup>Center for Integrated Research in Science and Engineering, Nagoya University

<sup>3</sup>Center for Cooperative Research in Advanced Science and Technology, Nagoya University

Furo-cho, Chikusa-ku, Nagoya, 464-8603, Japan

TEL: +81-52-789-3923, FAX: +81-52-789-5592, e-mail: nakatuka@alice.xtal.nagoya-u.ac.jp

<sup>4</sup>Toyoko Kagaku Co., Ltd.

1280 Nakamaruko, Nakahara-ku, Kawasaki, 211-8502, Japan

TEL: +81-44-435-5866, FAX: +81-44-434-6303

## **1.Introduction**

In recent years, there are increasing demands for future ULSI devices such as decreased size of ULSI circuits and wide variety of functions on a device chip. It is necessary to develop ultra thin film growth technologies which offer several critical requirements; high controllability of the film thickness, high controllability of the grain orientation, low contaminants in the films, good step-coverage, uniformity of the film thickness, and flexibility of the selection of materials used for sorts and impurities. Ultra-high vacuum rapid thermal chemical vapor deposition (UHV-RTCVD) is expected to be one of powerful methods which meet these requirements and has several advantages. First, the ultra-high vacuum system provides low partial pressure of  $H_2O$  and  $O_2$  during growth, which avoids hydrolysis of reactive source gases and suppresses unintentional oxidation of deposited films and substrates. Second, the rapid thermal process (RTP) [1-2] with rapid heating and quenching provides accurate control of reaction source gases so that the incorporation of contaminants due to by-product of the reaction are greatly suppressed. Therefore it is possible to deposit thin films with excellent quality by the UHV-RTCVD.

In this work, we have developed an UHV-RTCVD system and grown TiN films using the system. CVD-TiN films grown using  $TiCl_4$  and  $NH_3$  as source materials are attractive candidates used for the multilevel metallization in the ULSI devices. Especially, the TiN film as a diffusion barrier metal for metallized Cu has been required to be thin enough and have low resistivity, low contaminants in the films, and good step-coverage. We have applied the UHV-RTCVD method to the TiN film growth and investigated structural and electrical properties.

## 2.Experimental

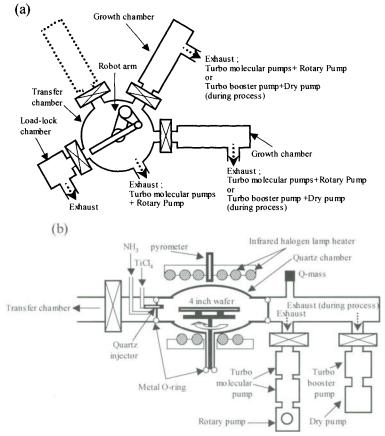

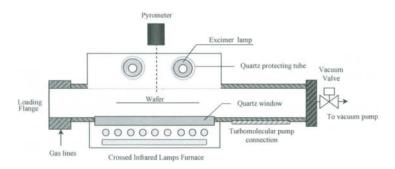

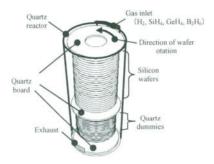

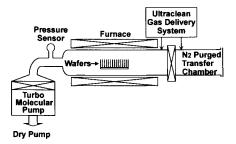

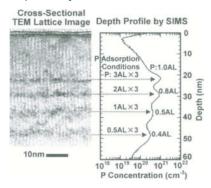

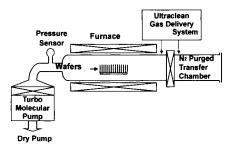

#### UHV-RTCVD system

Figures 1 shows a schematic illustration of an UHV-RTCVD system which we developed. It can be equipped with three growth chambers, each of which is bakeble to attain ultra-high vacuum as shown in Fig. 1(a). Each growth chamber is connected through transfer chamber and wafers are transferred from a load-lock chamber into the growth chambers by a robot arm. The growth chambers can be evacuated with alternative pumping systems; two turbo molecular pumps with a rotary pump or turbo booster pump with a dry pump.

Figure 1(b) shows a detailed structure of the TiN growth chamber which is mainly made with quartz and placed between infrared halogen lamp heaters for rapid heating. Five circle heaters with 900–4000W can be controlled separately for ensuring temperature uniformity of

- Fig.1 Schematic of the UHV-RTCVD system.

- (a) Schematic of the UHV-RTCVD system including load-lock chamber, transfer chamber, and growth chambers.

- (b) Schematic of TiN growth chamber.

Figure 1(b) shows a detailed structure of the TiN growth chamber which is mainly made with quartz and placed between infrared halogen lamp heaters for rapid heating. Five circle heaters with 900–4000W can be controlled separately for ensuring temperature uniformity of the substrate surface. The substrate table can be rotated to provide the uniformity of film's characteristics in a 4-inch wafer scale. The substrate temperature is measured by a pyrometer sensitive to long wavelength infrared radiation in order to permit the measurement of temperature ranging from 400°C to 1100°C. The pyrometer is set up to view the substrate surface through the quartz chamber. During film growth, the growth chamber is evacuated by a turbo booster pump and a dry pump. This realizes an oil-free environment and thus prevents unintentional carbon contamination in the growth chamber. TiCl<sub>4</sub> and NH<sub>3</sub> as source gases to form TiN films are introduced into the growth chamber through separate lines and gas injectors so that reaction takes place near the hot substrate surface. The TiCl<sub>4</sub> gas injector is made with quartz which is transparent for the infrared radiation in order to prevent thermal decomposition of TiCl<sub>4</sub> by inside the gas injector.

#### TiN film growth

SiO<sub>2</sub> layers with a thickness of 80 nm formed by thermal oxidation on Si (100) wafers were used as substrates. The base pressure was less than  $1 \times 10^{-8}$  Torr before deposition. The deposition was performed at substrate temperatures ranging from 450°C to 650°C with a TiCl<sub>4</sub> gas flow of 3 sccm and a NH<sub>3</sub> gas flow of 20 sccm with a N<sub>2</sub> carrier gas. The total pressure during the deposition was 10 mTorr and the partial pressures of TiCl<sub>4</sub> and NH<sub>3</sub> were, respectively, 0.73 mTorr and 4.9 mTorr which were calculated by the method of Builting [3].

The thickness of the deposited films was measured by a stylus surface profiler. The crystalline structure of the TiN films was analyzed by X-ray diffraction (XRD) and transmission electron microscope (TEM). The surface morphology was observed by atomic force microscope (AFM). A four points probe method was used for the measurement of the resistivity. The contaminant in the film was measured by Auger electron spectroscopy (AES).

#### **3.Results and Discussion**

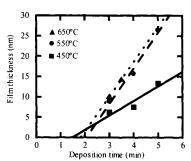

Figure 2 shows deposition time dependence of the thickness of TiN films deposited at various substrate temperatures. The growth rates were determined from the gradient of each plot, which were 3.6 nm/min, 8.8 nm/min, and 8.5 nm/min for the temperatures of 450°C, 550°C, and 650°C, respectively. The growth rate increases with the increase in the substrate temperature and appears to be constant at the temperatures over 550°C, suggesting that the growth is limited by the gas flow rates of TiCl<sub>4</sub> and NH<sub>3</sub>. These values of the growth rates are lower than those in low pressure CVD (LPCVD) reported previously [3-6], which comes from the lower partial pressure in our RTCVD compared with that of the LPCVD, typically about 100 mTorr.

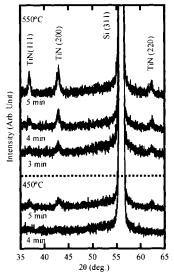

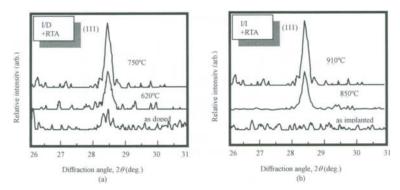

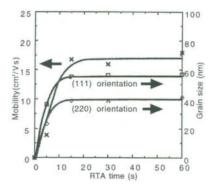

Figure 3 shows low incident angle XRD profiles taken from the films grown at 450°C and 550°C for various deposition times. The peaks related with TiN (111), (200) and (220) were

clearly observed in all profiles of 550°C samples, which indicates that polycrystalline phases with a NaCl type structure are formed. On the other hand, in the case of 450°C, peaks related to TiN are hardly observed not only for the 4-min-deposited film but also for the 5-min-deposited film whose thickness is nearly equal to that of the sample grown at 550°C for 4 min. This result suggests that a growth temperature above 550°C, at least, is required to obtain crystalline TiN films.

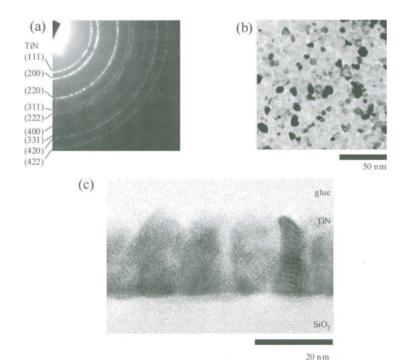

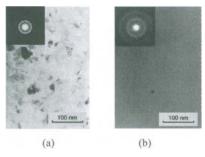

Figure 4(a) shows a transmission electron diffraction pattern taken from a TiN film deposited at 550°C for 5 min. Diffraction spots corresponding to TiN (111), (200), (220), (311), (222), (400), (331), (420), and (422) with a NaCl type structure are observed and this is consistent with the XRD results shown in Fig. 3. A bright-field plan-view TEM image of the same sample is shown in Fig. 4(b). Textures consisting of polycrystalline TiN grains are clearly observed. An average grain size was measured to be about 12 nm in diameter. Compared to the value (9.4 nm) for the 3-min deposited sample measured from its TEM image (not shown), the increase in the grain size in plan-view is smaller than that in the film thickness. This suggests that the film TiN has columnar grain structures. Figure 4(c) is a bright-field cross-sectional TEM image for the same sample as that shown in Fig. 4(b). Polycrystalline TiN films and grain boundaries are clearly observed and the TiN layer was confirmed to have columnar grain structures.

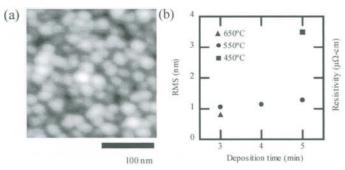

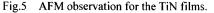

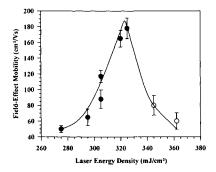

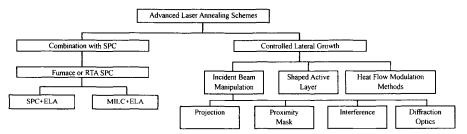

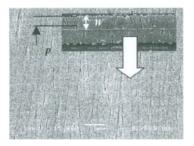

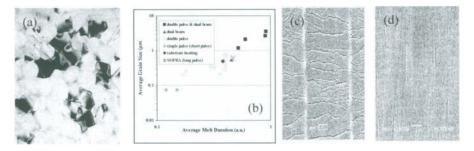

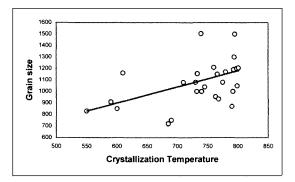

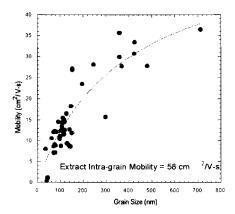

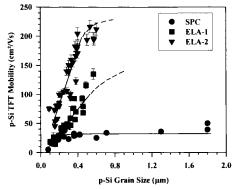

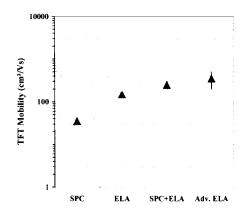

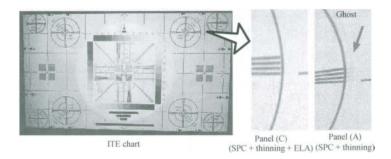

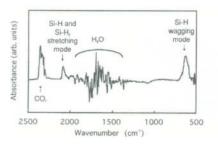

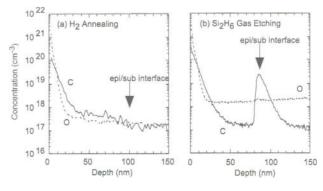

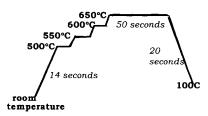

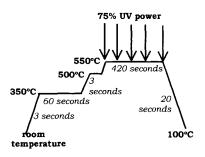

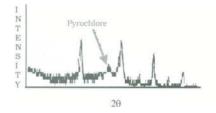

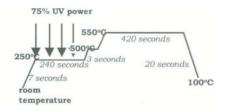

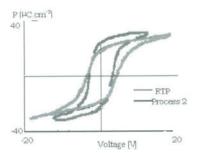

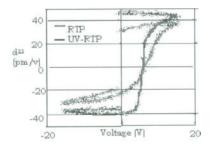

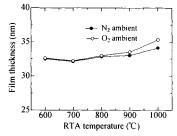

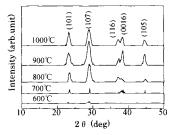

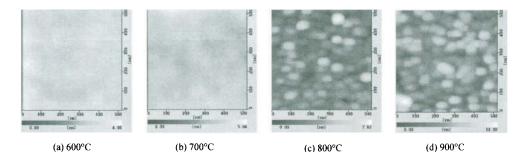

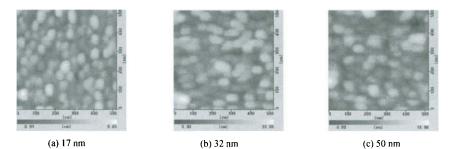

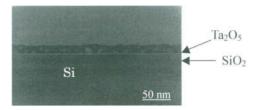

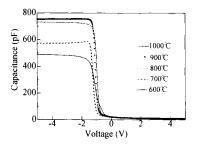

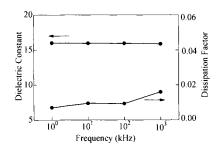

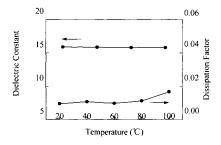

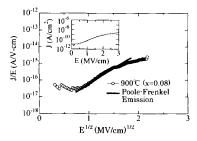

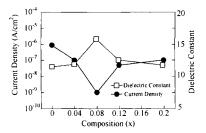

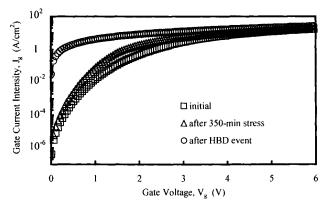

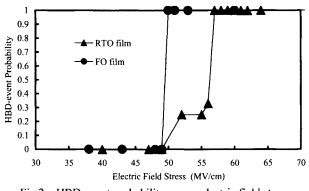

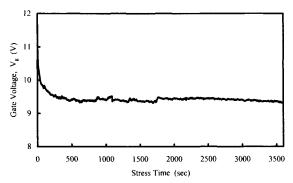

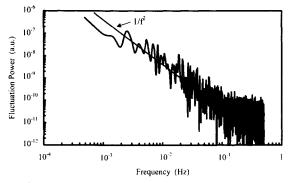

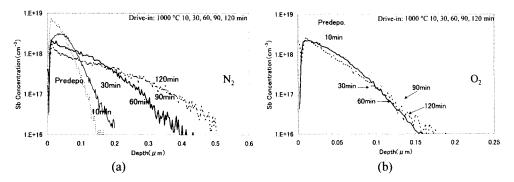

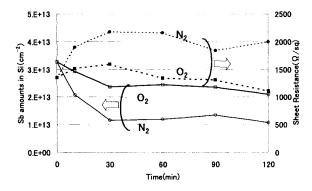

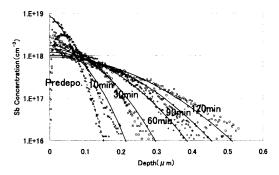

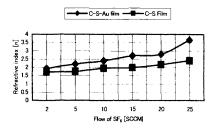

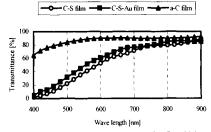

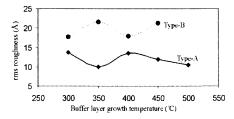

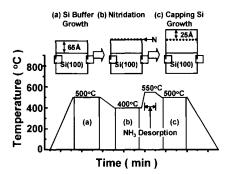

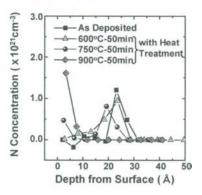

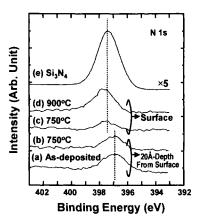

AFM images of TiN films deposited at 550°C for 5 min are shown in Fig. 5(a). An average diameter of the observed dots was measured to be about 20 nm and this value does not agree with that obtained by the plan-view TEM image show in Fig. 4(b). This results suggests that