# NONBLOCKING ELECTRONIC AND PHOTONIC Switching Fabrics

Wojciech Kabaciński

# NONBLOCKING ELECTRONIC AND PHOTONIC SWITCHING FABRICS

# NONBLOCKING ELECTRONIC AND PHOTONIC SWITCHING FABRICS

WOJCIECH KABACIŃSKI Poznan University of Technology

Wojciech Kabaciński Poznan University of Technology Poland

Kabaciński, Wojciech.

Nonblocking electronic and photonic switching fabrics / Wojciech Kabaciński. p. cm.

Includes bibliographical references and index.

ISBN 0-387-25431-5 (alk. paper) -- ISBN 0-387-26530-9 (e-book) 1. Telecommunication--Switching systems. 2. Photonics. I. Title.

TK5103.8.K33 2005 621.382'16--dc22

2005049798

| ISBN 0-387-25431-5    | e-ISBN 0-387-26530-9 | Printed on acid-free paper. |

|-----------------------|----------------------|-----------------------------|

| ISBN 978-0387-25431-9 |                      |                             |

© 2005 Springer Science+Business Media, Inc.

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, Inc., 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed in the United States of America.

9 8 7 6 5 4 3 2 1 SPIN 11342403

springeronline.com

To my parents, Renata, Rafał, and Przemysław

# Contents

| De | edicat            | ion    |                                               | v  |

|----|-------------------|--------|-----------------------------------------------|----|

| Pr | eface             |        |                                               | xi |

| 1. | INT               | RODU   | CTION                                         | 1  |

|    | 1.1               | What   | Is Switching?                                 | 1  |

|    | 1.2               | Evolu  | tion of Switching Technologies                | 4  |

|    | 1.3               | Trans  | fer Modes and Switching                       | 5  |

|    |                   | 1.3.1  | Synchronous Transfer Mode                     | 5  |

|    |                   | 1.3.2  | Packet Transfer Mode                          | 7  |

|    |                   | 1.3.3  | Asynchronous Transfer Mode                    | 7  |

|    | 1.4               | Archit | ectures of Switching Nodes                    | 8  |

|    |                   | 1.4.1  | General Switch Architecture                   | 8  |

|    |                   | 1.4.2  | Telephone Exchange                            | 9  |

|    |                   | 1.4.3  | ATM Switches                                  | 10 |

|    |                   | 1.4.4  | IP Routers                                    | 12 |

|    |                   | 1.4.5  | Cross-connect Systems                         | 13 |

|    |                   | 1.4.6  | Switching in Multiprocessor Systems           | 15 |

|    |                   | 1.4.7  | Switching in Storage Area Networks            | 16 |

|    | 1.5               | The C  | Contents of the Book                          | 18 |

| 2. | $\mathrm{CL}_{A}$ | ASSIFI | CATION AND TAXONOMY                           | 21 |

|    | 2.1               | Switch | ning Elements and Switching Fabrics           | 21 |

|    | 2.2               | Classi | fication of Switching Fabrics                 | 24 |

|    | 2.3               | Conne  | ection Types                                  | 34 |

|    |                   | 2.3.1  | Connection Set-up Models                      | 34 |

|    |                   | 2.3.2  | Unicast, Multicast, and Broadcast Connections | 35 |

|    |                   | 2.3.3  | Single-rate and Multirate Connections         | 36 |

|    | 2.4 | Control Algorithms                          | 37  |

|----|-----|---------------------------------------------|-----|

|    | 2.5 | Notation, Terminology, and Models           | 39  |

|    |     | 2.5.1 Switching Fabrics and Connections     | 39  |

|    |     | 2.5.2 Multi-slot Switching Model            | 40  |

|    |     | 2.5.3 Multirate Switching Model             | 44  |

|    |     | 2.5.4 Graph Representation                  | 45  |

| 3. |     | IGLE-PATH AND STANDARD PATH                 |     |

|    | SW  | ITCHING FABRICS                             | 51  |

|    | 3.1 | Introduction                                | 51  |

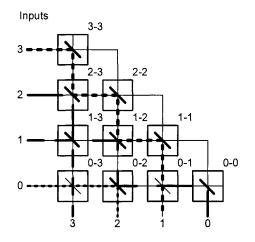

|    | 3.2 | Crossbar Switches                           | 51  |

|    | 3.3 | Triangular Switches                         | 55  |

|    | 3.4 | Tree-type Switching Fabrics                 | 61  |

|    | 3.5 | One-stage Switching Fabrics                 | 63  |

|    | 3.6 | Banyan-type Switching Fabrics               | 65  |

|    |     | 3.6.1 Structures                            | 65  |

|    |     | 3.6.2 Properties and Control                | 69  |

|    |     | 3.6.3 Graph Representation                  | 71  |

|    | 3.7 | Implementations                             | 78  |

| 4. | ΤW  | O-STAGE SWITCHING FABRICS                   | 81  |

|    | 4.1 | Two-sided Switching Fabrics                 | 81  |

|    | 4.2 | One-sided Switching Fabrics                 | 82  |

|    |     | 4.2.1 Space-division Switching              | 82  |

|    |     | 4.2.1.1 Switching Fabric's Architecture     | 82  |

|    |     | 4.2.1.2 Path Searching Algorithms           | 82  |

|    |     | 4.2.1.3 Strict-sense Nonblocking Conditions | 84  |

|    |     | 4.2.1.4 Wide-sense Nonblocking Conditions   | 87  |

|    |     | 4.2.1.5 Rearrangeable Switching Fabrics     | 91  |

|    |     | 4.2.2 Time-division Switching               | 91  |

|    |     | 4.2.2.1 Switching Fabric's Architecture     | 91  |

|    |     | 4.2.2.2 Strict-sense Nonblocking Conditions | 93  |

|    |     | 4.2.2.3 Wide-sense Nonblocking Conditions   | 98  |

|    |     | 4.2.2.4 Rearrangeable Switching Fabrics     | 101 |

|    |     | 4.2.3 Multirate Switching                   | 101 |

|    |     | 4.2.3.1 Switching Fabric Architecture       | 101 |

|    |     | 4.2.3.2 Strict-sense Nonblocking Conditions | 103 |

|    |     | 4.2.3.3 Wide-sense Nonblocking Conditions   | 111 |

|    | 4.3 | Switching Fabrics with More Than Two Stages | 113 |

| Co | ntent | 8       |                                                  | ix  |

|----|-------|---------|--------------------------------------------------|-----|

| 5. | THI   | REE-ST  | AGE SWITCHING FABRICS                            | 117 |

|    | 5.1   | Space-  | division Switching                               | 117 |

|    |       | 5.1.1   | 0                                                | 117 |

|    |       | 5.1.2   | Path Searching Algorithms                        | 119 |

|    |       | 5.1.3   | Strict-sense Nonblocking Conditions              | 124 |

|    |       | 5.1.3.1 | Unicast Connections                              | 124 |

|    |       | 5.1.3.2 | Multicast Connections                            | 130 |

|    |       | 5.1.4   | Wide-sense Nonblocking Conditions                | 131 |

|    |       | 5.1.4.1 | Unicast Connections                              | 131 |

|    |       | 5.1.4.2 | Multicast Connections                            | 136 |

|    |       | 5.1.5   | Rearrangeable Switching Fabrics                  | 144 |

|    |       | 5.1.5.1 | Unicast Connections                              | 144 |

|    |       | 5.1.5.2 | Multicast Connections                            | 145 |

|    |       | 5.1.6   | Rearrangeable Algorithms                         | 147 |

|    |       | 5.1.6.1 | Single Connections                               | 147 |

|    |       | 5.1.6.2 | Simultaneous Connections                         | 153 |

|    |       | 5.1.7   | Repackable Switching Fabrics                     | 164 |

|    | 5.2   | Time-d  | livision Switching                               | 167 |

|    |       | 5.2.1   | Switching Fabrics Composed of Digital Switches   | 167 |

|    |       | 5.2.2   | Path Searching Algorithms                        | 168 |

|    |       | 5.2.3   | Strict-sense Nonblocking Conditions              | 169 |

|    |       | 5.2.4   | Wide-sense Nonblocking Conditions                | 172 |

|    |       | 5.2.5   | Rearrangeable Switching Fabrics                  | 174 |

|    |       | 5.2.6   | Repackable switching fabrics                     | 177 |

|    | 5.3   | Multira | ate Switching                                    | 179 |

|    |       | 5.3.1   | Multirate Switching Fabrics                      | 179 |

|    |       | 5.3.2   | Strict-sense Nonblocking                         | 180 |

|    |       |         | Wide-sense Nonblocking Conditions                | 190 |

|    |       |         | Unicast Connections                              | 190 |

|    |       | 5.3.3.2 | Multicast Connections                            | 191 |

|    |       | 5.3.4   | Rearrangeable Switching Fabrics                  | 194 |

|    |       | 5.3.5   | Repackable Switching Fabrics                     | 197 |

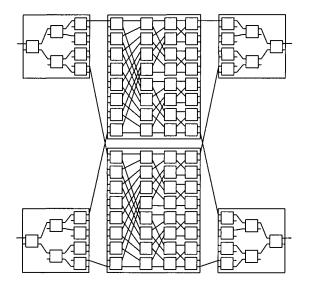

|    | 5.4   | Practic | cal Implementations of Clos Networks             | 198 |

| 6. | REF   | PLICAT  | ED BASELINE SWITCHING FABRICS                    | 201 |

|    | 6.1   | Switch  | ing Fabric Topologies                            | 201 |

|    |       | 6.1.1   | Vertically Replicated Baseline Switching Fabrics | 201 |

|    |       | 6.1.2   | Extended Baseline Switching Fabrics              | 202 |

|    | 6.2   | Contro  | l Algorithms                                     | 207 |

|    |       |         | -                                                |     |

| Space-  | division Switching                                                                                                | 211                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.3.1   | Strict-sense Nonblocking Conditions                                                                               | 211                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.3.1.1 | Unicast Connections                                                                                               | 211                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.3.1.2 | Multicast Connections                                                                                             | 215                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.3.2   | Wide-sense Nonblocking Conditions                                                                                 | 217                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.3.3   | Rearrangeable Conditions                                                                                          | 227                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.3.4   | Rearranging Algorithms                                                                                            | 229                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Multir  | ate Switching                                                                                                     | 235                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.4.1   | Switching Fabrics                                                                                                 | 235                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.4.2   | Strict-sense Nonblocking                                                                                          | 236                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.4.2.1 | Unicast Connections                                                                                               | 236                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.4.2.2 | Multicast Connections                                                                                             | 252                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.4.3   | Wide-sense Nonblocking Conditions                                                                                 | 252                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ces     |                                                                                                                   | 253                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |                                                                                                                   | 267                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | 6.3.1<br>6.3.1.1<br>6.3.1.2<br>6.3.2<br>6.3.3<br>6.3.4<br>Multir<br>6.4.1<br>6.4.2<br>6.4.2.1<br>6.4.2.2<br>6.4.3 | <ul> <li>6.3.1.1 Unicast Connections</li> <li>6.3.1.2 Multicast Connections</li> <li>6.3.2 Wide-sense Nonblocking Conditions</li> <li>6.3.3 Rearrangeable Conditions</li> <li>6.3.4 Rearranging Algorithms</li> <li>Multirate Switching</li> <li>6.4.1 Switching Fabrics</li> <li>6.4.2 Strict-sense Nonblocking</li> <li>6.4.2.1 Unicast Connections</li> <li>6.4.2.2 Multicast Connections</li> <li>6.4.3 Wide-sense Nonblocking Conditions</li> </ul> |

## Preface

Switching fabrics first appeared in telephone exchanges, where there was a need to interconnect many pairs of telephones installed in the network. Due to the large number of connected subscribers and interexchange links, switching fabrics in telephone exchanges have to serve a great number of input and output ports. Because of the scale, large switching fabrics were constructed from smaller ones. The way of building switching fabrics from elements of smaller capacity and different characteristics of switching fabrics topologies has been for a long time a rich area of theoretical research. The seminal work is due to C. Clos [23], who first considered multistage strict-sense nonblocking switching networks, and V. E. Beneš [9], who first introduced the mathematical theory of switching networks. From that time, many research was conducted in this field. Switching fabrics found its application not only in telecommunication, starting from telephone exchanges through ATM switches and IP routers to optical cross-connect systems and optical packet switches, but also in other areas of knowledge like computation and control. Theory of switching fabrics becomes also a part of applied mathematics. Results of studies carried out by researchers from these area were published in numerous papers and some books.

This book is intended for people interested in the switching theory, and especially combinatorial characteristics of switching networks. It contains a considerable amount of already known results. Some of them are presented in more detailed form, other are only mentioned. The book contains many original results accrued by the author during his work at Poznan University of Technology on combinatorial properties of switching fabrics. The contents of the book is partially taken from the author's lecture notes given at Poznan University of Technology for post-graduate and doctoral students. I hope this book will be useful to not only post-graduate and PhD students but also to engineers and switching fabrics designers who want to gain knowledge on switching theory and especially on combinatorial properties of switching fabrics.

Wojciech Kabaciński Branaowo, 2004

# List of Symbols

| eta             | _          | normalized capacity of input and output terminals of                                  |

|-----------------|------------|---------------------------------------------------------------------------------------|

|                 |            | two-sided switching fabrics or terminals in one-sided switching fabrics               |

| $eta_1$         |            | normalized capacity of an input terminal of two-sided switching fabrics               |

| $\beta_2$       | -          | normalized capacity of an output terminal of two-sided<br>switching fabrics           |

| Ь               | _          | minimum weight of a multirate connection                                              |

| B               |            | maximum weight of a multirate connection                                              |

| $\mathbb{BW}_i$ | _          | the <i>i</i> -th blocking window                                                      |

| C               |            | The state matrix of a crossbar switch                                                 |

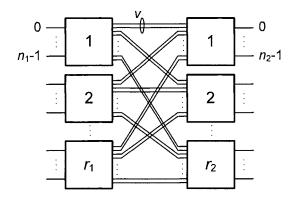

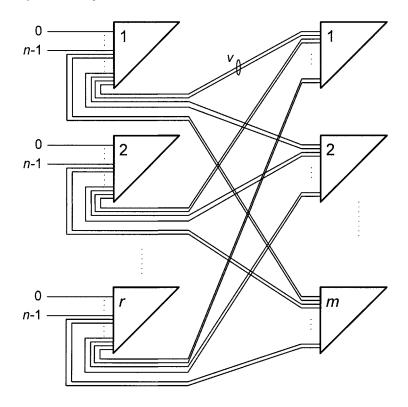

| $C_{SD}(n_1,$   | $r_1,$     | $(m, n_2, r_2, v)$ – an asymmetrical three-stage space-division                       |

|                 |            | v-dilated Clos switching fabric                                                       |

| $C_{SD}(n, r)$  | ,m         | (v) – a symmetrical three-stage space-division v-dilated                              |

|                 |            | Clos switching fabric                                                                 |

| $C_{TD}(n_1,$   | $r_1$ ,    | $f_1, m, n_2, r_2, f_2, v, f_0)$ – an asymmetrical three-stage                        |

|                 |            | time-division $v$ -dilated switching fabric                                           |

| $C_{TD}(n, r$   | f, f,      | $m, v, f_0$ ) – a symmetrical three-stage time-division<br>v-dilated switching fabric |

| $C_{MR}(n_1,$   | $r_{1},$   | $\beta_1, m, n_2, r_2, \beta_2, v)$ – an asymmetrical three-stage                     |

|                 |            | multirate v-dilated switching fabric                                                  |

| $C_{MR}(n, n)$  | $r, \beta$ | (m, v) – a symmetrical three-stage multirate v-dilated switching fabric               |

| d               |            | number of inputs and outputs in a crossbar switch used                                |

|                 |            | to construct a $d$ -nary switching fabric                                             |

| $\mathbf{E}_r$  | _          | an elementary permutation matrix of size $r \times r$                                 |

| Ē               | _          | a set of edges in $\mathcal{G}$                                                       |

|                 |            |                                                                                       |

| xiv                                                              |          | NONBLOCKING SWITCHING FABRICS                                                                                                                       |

|------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| $f_1$                                                            |          | number of time slots in an input terminal of a two-sided<br>switching fabric or of a terminal of one-sided switching<br>fabrics                     |

| $f_2$                                                            |          | number of time slots in an output terminal of a two-sided switching fabric                                                                          |

| $egin{array}{c} f_0 \ f \end{array}$                             |          | number of time slots in an inter-stage link<br>number of time slots in input and output terminals of                                                |

| -                                                                |          | two-sided switching fabrics                                                                                                                         |

| $\mathcal{G}$                                                    |          | a graph                                                                                                                                             |

| $\mathcal{G}(\mathbb{V},\mathbb{E})\ \mathcal{G}(,\mathbb{O}_j)$ | _        | a graph with a set of $\mathbb{V}$ nodes and $\mathbb{E}$ edges<br>a graph representing connecting paths between input                              |

|                                                                  |          | terminals in $\mathbb{I}_i$ and output terminals in $\mathbb{O}_j$                                                                                  |

| $\mathbf{H}_{r}^{(n)}$                                           |          | a matrix of size $r \times r$ representing a maximal assignment                                                                                     |

| $I_i$                                                            |          | switch $i$ of the first stage of a multistage switching fabric                                                                                      |

| $\mathbb{I}_i$                                                   | _        | $\mathbf{F}$ $\mathbf{O}$ $\mathbf{O}$                                                                                                              |

|                                                                  |          | with the same values on bits $x_{n-1}x_{n-2} \dots x_{\lfloor n/2 \rfloor}$ of their binary representation, where <i>i</i> is binary represented by |

|                                                                  |          | $x_{n-1}x_{n-2}\ldots x_{\lfloor n/2 \rfloor}$                                                                                                      |

| $(I_i, O_j)$                                                     |          | a connection between any input terminal of the first stage                                                                                          |

|                                                                  |          | switch $i$ and any output terminal of the last stage                                                                                                |

| (T, O)                                                           | <b>`</b> | switch $j$ in a two-sided switching fabric                                                                                                          |

| $(I_i, O_j, s)$                                                  | ) —      | an $s$ -slot connection between any input terminal of<br>the first stage switch $i$ and any output terminal of the                                  |

|                                                                  |          | last stage switch $j$ in a two-sided switching fabric                                                                                               |

| $(I_i, O_j, \omega$                                              | )-       |                                                                                                                                                     |

|                                                                  |          | the first stage switch $i$ and any output terminal of the                                                                                           |

|                                                                  |          | last stage switch $j$ in a two-sided switching fabric                                                                                               |

| $(I_i, I_j)$                                                     | -        | a connection between any terminal of the first stage<br>switch $i$ and any terminal of the first stage switch $j$ in                                |

|                                                                  |          | a one-sided switching fabric                                                                                                                        |

| $(I_i, I_j, s)$                                                  |          | an s-slot connection between any terminal of                                                                                                        |

|                                                                  |          | the first stage switch $i$ and any terminal of the first                                                                                            |

|                                                                  |          | stage switch $j$ in a one-sided switching fabric                                                                                                    |

| $(I_i, I_j, \omega)$                                             |          | a connection of weight $\omega$ between any terminal<br>of the first stage switch $i$ and any terminal of the first                                 |

|                                                                  |          | stage switch $j$ in a one-sided switching fabric                                                                                                    |

| $(\mathbb{I}_i, \mathbb{O}_j)$                                   | _        | a connection between any input terminal in $\mathbb{I}_i$ and any                                                                                   |

| -                                                                |          | output terminal in $\mathbb{O}_j$                                                                                                                   |

| $\hat{i}$                                                        |          | complement to $i$ , i.e., when $i$ is binary represented by                                                                                         |

|                                                                  |          | $i_{n-1}i_{n-2}\ldots i_10$ than $\hat{i}$ is binary represented by                                                                                 |

|                                                                  |          | $i_{n-1}i_{n-2}\dots i_11$                                                                                                                          |

|                                                                  |          |                                                                                                                                                     |

| $M_k$                | - | switch $k$ of the second stage of a three-stage two-sided<br>switching fabric or a two-stage one-sided switching fabric                             |

|----------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| m                    |   | number of the second stage switches in two-stage<br>switching fabrics composed of triangular switches or in<br>three-stage Clos switching fabrics   |

| m                    |   | number of additional stages in $\log_2 N$ switching fabrics                                                                                         |

| Ν                    |   | number of input terminals and output terminals in<br>a symmetrical two-sided switching fabric or terminals<br>in one-sided switching fabrics        |

| $N_1$                | - | number of input terminals in an asymmetrical switching fabric                                                                                       |

| $N_2$                | - | number of output terminals in an asymmetrical switching fabric                                                                                      |

| n                    |   | number of inputs and outputs in a switch                                                                                                            |

| n                    | _ | number of stages in banyan-type switching fabrics                                                                                                   |

| $n_1$                | _ | number of inputs in a switch of the first stage                                                                                                     |

|                      |   | in multistage switching fabrics                                                                                                                     |

| $n_2$                | _ | number of outputs in a switch of the last stage                                                                                                     |

|                      |   | in multistage switching fabrics                                                                                                                     |

| $\mathbb{NP}_i$      | — | a set of connecting paths which goes through the nodes<br>of shell <i>i</i> of the $\log_2(N, m, p)$ switching fabric                               |

| $O_{j}$              | _ | switch $j$ of the last stage of a multistage switching fabric                                                                                       |

| $\mathbb{O}_{j}^{'}$ | _ | the set of input terminals in a $\log_2 N$ switching fabric<br>with the same values on bits $y_{n-1}y_{n-2} \dots y_{\lfloor n/2 \rfloor}$ of their |

|                      |   | binary representation, where $j$ is binary represented by                                                                                           |

| p                    | _ | $y_{n-1}y_{n-2} \cdots y_{\lfloor n/2 \rfloor}$<br>a number of planes in $\log_2(N, m, p)$ switching fabrics                                        |

| $\Pi^{p}$            | _ | a permutation; a maximal assignment                                                                                                                 |

| $\Pi^{-1}$           |   | inverse permutation of permutation $\Pi$                                                                                                            |

| $\pi(x)$             |   | an output terminal input terminal $x$ is to be connected to                                                                                         |

|                      |   | in Π                                                                                                                                                |

| $\pi^{-1}(y)$        | - | an input terminal output terminal $y$ is to be connected with in $\Pi$                                                                              |

| q                    | _ | number of output terminals in multicast connection;                                                                                                 |

| 1                    |   | q-cast connection                                                                                                                                   |

| $q_1$                | _ | maximum number of input terminals which may take part                                                                                               |

| <u>,</u> ,           |   | in a multiconnection                                                                                                                                |

| $q_2$                | - | maximum number of output terminals which may take                                                                                                   |

| -                    |   | part in q-cast connection                                                                                                                           |

|                      |   |                                                                                                                                                     |

| xvi                              |          | NONBLOCKING SWITCHING FABRICS                                                                                                      |

|----------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------|

| $r_1$                            |          | number of switches at the first stage of a multi-stage<br>two-sided switching fabric                                               |

| $r_2$                            | -        | number of switches at the last stage of a multi-stage<br>two-sided switching fabric                                                |

| r                                |          | number of switches at first and last stages of<br>a symmetrical multi-stage two-sided switching fabric or                          |

| S                                | _        | at the first stage of a one-sided switching fabric<br>matrix representing the state of a two-sided three-stage<br>switching fabric |

| $\mathbb{SBW}_i$                 | _        | a subblocking window                                                                                                               |

| $\mathbb{SI}_i$                  | _        | the set of input terminals accessible from stage $i$<br>in a $\log_2 N$ switching fabric                                           |

| $\mathbb{SI}_i^m$                | -        | the set of input terminals accessible from stage $i$<br>in a $\log_2(N, m, p)$ switching fabric                                    |

| $\mathbb{SO}_i$                  | _        | the set of output terminals accessible from stage $i$<br>in a $\log_2 N$ switching fabric                                          |

| $\mathbb{SO}_i^m$                | _        | the set of output terminals accessible from stage $i$<br>in a $\log_2(N, m, p)$ switching fabric                                   |

| s                                | _        | number of stages in a multi-stage switching fabric                                                                                 |

| s                                |          | number of time slots used by a multi-slot connection;<br>s-slot connection                                                         |

| $s_{\max}$                       | -        | maximum number of time slots used by a multi-slot connection                                                                       |

| t                                | -        | a size of a blocking window                                                                                                        |

| $T_{SD}(n, n)$                   | n, r,    | v) – a $v$ -dilated one-sided space-division switching fabric                                                                      |

|                                  |          | composed of triangular switches with $r$ first stage                                                                               |

|                                  |          | switches, $m$ second stage switches, and $n$ terminal                                                                              |

| m (                              |          | per each first stage switch                                                                                                        |

| $T_{TD}(n, n)$                   | n, r,    | $v, f_0$ ) – a v-dilated one-sided time-division switching fabric                                                                  |

|                                  |          | composed of triangular switches with $r$ first stage                                                                               |

|                                  |          | switches, $m$ second stage switches, $n$ terminal<br>per each first stage switch, and $f_0$ time slots                             |

|                                  |          | per each terminal                                                                                                                  |

| $T_{MR}(n, l)$                   | 3. m     | (v, r, v) - a v-dilated one-sided multirate switching fabric                                                                       |

| 1110( ))                         | <i>,</i> | composed of triangular switches with $r$ first stage                                                                               |

|                                  |          | switches, $m$ second stage switches, $n$ terminal                                                                                  |

|                                  |          | per each first stage switch, each terminal of capacity $\beta$                                                                     |

| $\mathbb{V}_{\langle x,y angle}$ | _        | a set of nodes on a connecting path in bipartite graph                                                                             |

| \#,9/                            |          | representation of $\log_2(N, m, p)$ switching fabrics                                                                              |

| v                                       | _ | number of links between two switches in successive stages       |

|-----------------------------------------|---|-----------------------------------------------------------------|

| $\omega$                                |   | a weight of multirate connection                                |

| $ \mathbb{X} $                          | _ | the cardinality of set $\mathbb{X}$                             |

| $\lfloor x \rfloor$                     | _ | the greatest integer lower than or equal to $x$                 |

| $\lceil x \rceil$                       | _ | the lowest integer greater than or equal to $x$                 |

| $x\oplus y$                             | _ | the rest from dividing $x$ by $y$                               |

| $\langle x, y \rangle$                  |   | a connection between input terminal $x$ and output              |

|                                         |   | terminal $y$ in a two-sided switching fabric or terminals       |

|                                         |   | x and $y$ in a one-sided switching fabric                       |

| $\langle x, y, s \rangle$               | _ | an $s$ -slot connection between input terminal $x$ and          |

|                                         |   | output terminal $y$                                             |

| $\langle x, y, \omega \rangle$          | _ | a multirate connection of weight $\omega$ between input         |

|                                         |   | terminal $x$ and output terminal $y$                            |

| $\langle x, \mathbb{Y} \rangle$         | _ | a multicast connection between input terminal $x$ and           |

|                                         |   | a set of output terminals $\mathbb{Y}$                          |

| $\langle x, \mathbb{Y}, \omega \rangle$ | _ | a multicast connection of weight $\omega$ between input         |

|                                         |   | terminal $x$ and a set of output terminals $\mathbb{Y}$         |

| $\mathbb{Y}$                            | _ | a set $\{y_0, \ldots, y_k\}$ of output terminals taking part in |

|                                         |   | a multicast connection                                          |

|                                         |   |                                                                 |

## Chapter 1

# INTRODUCTION

#### 1.1 What Is Switching?

Telecommunication networks are designed to convey information This information is provided by the user through between users. appropriate terminal unit (telephone set, PC, for example). When two users want to exchange information, their terminals are to be connected by a transmission system. When there are more than two users connected to the network who want to exchange information, transmission systems are to be provided between each pair of them. The example of the network with six telephone users is shown in Fig. 1.1. In this approach N(N-1)/2 links are needed when N users are to be connected. This is not practical since links are rarely used by users, and for large number of users such realization is infeasible. Therefore, switching nodes were introduced in telecommunication networks (see Fig. 1.2). A switching node provides, on request, connecting path between a pair of users. Users are connected to the node by one transmission system, which is called a subscriber loop in case of the telephone network. Depending on the way information is conveyed in a telecommunication network, this connecting path may be provided for the duration of a connection (circuit switching), or only when information is really transmitted (packet switching).

Practical telecommunication networks contain many switching nodes, usually connected between themselves in the hierarchical order. One example is the telephone network with local exchanges and different classes of transit exchanges, as is shown in Fig. 1.3. Another example is the Internet network with many core and edge routers used to convey IP packets between users (see Fig. 1.4).

*Figure 1.1.* The example of the telephone network with six telephone subscribers

Figure 1.2. The example of the telephone network with six telephone subscribers and a switching node

Figure 1.3. The telephone network

Figure 1.4. The Internet network

Telecommunication networks are only one example where switching fabrics are used. Another area is computer industry, where switching fabrics are implemented for instance in processor/memory interconnects for vector supercomputers, multicomputers and distributed sharedmemory multiprocessors, clusters of personal computers or workstations, local, metropolitan or wide area networks (LANs, MANs, WANs) [39]. Switching fabrics are also used in other areas, for example in Viterbi decoders [3].

Different names are used for devices which perform switching functions. In telephone exchanges this part of exchange which performs switching was called a *switching network*. In multiprocessor systems the term an interconnection network or a multistage interconnection network (MIN) was used. When the speed rates of switched signals became greater and new transferring modes were introduced in the network (ATM networks, IP networks) the term a switching fabric or a switch fabric was introduced. In this book the term a switching fabric will be mostly used.

#### **1.2** Evolution of Switching Technologies

The first switching technology implemented in telecommunication networks was *manual switching*. It was used in both telegraph and telephone networks. The first telephone exchange was installed in 1878, only two years after A. G. Bell invented the telephone. Telephone connections were set up by an operator on a manual switchboard by plugging a patch cord into respective jacks.

The next switching technology was *electromechanical switching*. Two kinds of electromechanical switching systems were installed in the telephone network. The first one was a step-by-step system invented by A. B. Strawger and implemented in the telephone network in 1892. This switching system was build from elements called Strawger switches. The other system is called the crossbar switching system. The first such system was installed in 1938. The crossbar switch used horizontal and vertical bars to select the contact. Such implementation of a switch is still used in switching, but the technology used has changed from electromechanical to electronic and photonic.

Invention of the vacuum tube and later the transistor started the electronic era not only in telecommunication industry. Binary devices in logic circuits, like gates and flip-flops, were used in different parts of switching systems for controlling and also for switching. First, electronic switching systems used analog electronic gates to switch analog signals from inputs to outputs. Implementation of digital transmission of voice signals in PCM systems made analog switching inconvenient, since digital signals had to be converted into analog form for switching, and then they had to be back digitized for transmission to the next switching exchange. Integrated circuits and electronic memories enabled to move from analog switching to digital switching. The first digital switching system was installed in 1976. Digital switching allowed substantial growth on the size of electronic switching systems. This switching technology is currently used in switching systems, not only in telephone exchanges but also in packet switches (IP routers) and digital cross-connect systems used in transport networks based on SDH/SONET systems.

Optical fibers introduced in transmission systems offer a huge transmission bandwidth unavailable for copper cables. Transmission bit rates of 2.5, 10 and 40 Gbps are now available and soon rates of 160 Gbps will be available commercially. Electronic switching cannot be used at such high rates, so incoming signals have to be not only converted from optical to electrical form but also have to be demultiplexed to lower bit rates. To omit this inconvenient and expensive signal conversion and demultiplexing, switching systems based on the optical technology have been elaborated in research laboratories and industry. *Optical*

| Transfer<br>Modes       | STM                                                                        | PTM                                                   | ATM           |

|-------------------------|----------------------------------------------------------------------------|-------------------------------------------------------|---------------|

| Switching<br>Techinques | Circuit switching<br>Multirate circuit switching<br>Fast circuit switching | Packet switching<br>Frame switching<br>Frame relaying | ATM switching |

Table 1.1. Transfer modes and switching techniques

switching, called also photonic switching, enables optical signals to be switched directly from inputs to outputs without conversion to electronic form. Optical switching technology is used in optical cross-connect systems installed in emerging automated switched optical transport networks (AOTN). Much research is also carried out to implement optical switching in switching nodes using packet and ATM switching.

#### 1.3 Transfer Modes and Switching

The term transfer mode is used by ITU-T to describe a technique which is used in a telecommunication network, covering aspects related to transmission, multiplexing, and switching [33]. Three main transfer modes are called *Synchronous Transfer Mode* (STM), *Packet Transfer Mode* (PTM), and *Asynchronous Transfer Mode* (ATM). Different switching techniques are connected with these transfer modes. They are summarized in Table 1.1 and will be described in following sections.

## 1.3.1 Synchronous Transfer Mode

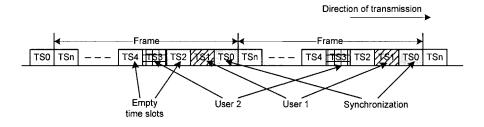

In STM transmission bandwidth is organized into periodic frames. Each frame consists of certain number of bits grouped into time slots, each of the same number of bits. The general architecture of the STM frame is shown in Fig. 1.5. The first time slot, denoted by TSO, usually contains synchronization pattern, which enables determination of the beginning of each frame at the receiver. Remaining time slots of each frame are used for conveying data.

Two types of STM systems are used in telecommunication networks. Duration of the frame is 125  $\mu$ s, since 8 kHz sampling frequency was normalized for PCM systems used for voice circuits. Two formats of PCM systems are used worldwide. One format uses frames composed of 24 time slots (used in North America), the other uses 32 8-bit time slots (Europe). The latter system, called also PCM 30/32 or E1, uses TS0 for synchronization (called also synchronization channel), one time slot (usually TS16) for signalling (signalling channel), and the remaining

Figure 1.5. Synchronous Transfer Mode

time slots (called also data channels) are used for conveying user data. Another frame is STM-1 frame used in SDH systems. Both, E1 and STM-1 systems, are further multiplexed and form so cold digital hierarchies, called Plesiochronous Digital Hierarchy (PDH) and Synchronous Digital Hierarchy (SDH), respectively.

*Circuit switching* technique is used in STM mode. In circuit switching time slots are assigned to users on the call-by-call basis. When a time slot is not assigned, it is free but it is always present in the frame. Assigned time slots carries only user information. Source and destination addresses are determined by the number of time slot which is assigned to the connection during a call set-up phase. In other words, the time slot number is a label which is used to route data in this time slot, since each connection always use the same time slot in the frame during the complete duration of the connection.

Circuit switching provides a fixed bit rate for transmission. For instance, in E1 system this rate is 64 kbps (8 bits per frame, 8000 frames per second). *Multirate circuit switching* was proposed to overcome the inflexibility of this single bit rate when services with different bit rate requirements were introduced. In multirate circuit switching, called also *multi-channel* or *multi-slot switching*, one connection may occupy more than one channel of basic bit rate. This type of switching is used in N-ISDN (Narrowband Integrated Services Digital Networks) for example, for videotelephony.

Another inconvenience in circuit switching is that occupied channels cannot be used by other connections when no information is being sent by users. To use channels more efficiently, fast circuit switching has been proposed [133]. In *fast circuit switching* information on the required bandwidth, destination, and label identifying the connection are assigned during the connection set-up phase, but channels are allocated dynamically only when information is being sent from the source to the

Figure 1.6. Packet Transfer Mode

destination. This approach, however, has not found practical implementation in the telecommunication network.

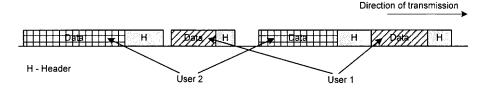

#### 1.3.2 Packet Transfer Mode

In PTM user data are transferred by structured sequences of bits called packets. Each packet, apart from user data, also contains additional information which is used inside the network for routing, error control, flow control, etc. This information is placed at the front of packets and is called a header (some additional bits, like error correcting codes, are located at the end of packets). Packets have a variable length and may be transmitted at any time, provided that no other packet is transmitted in a transmission link. The concept of PTM is shown in Fig. 1.6. Unlike in STM mode, a new packet may appear on the link at any time, and when there is no information to send, no packet is transmitted in a link.

Packet switching technique is used with PTM. Different types of telecommunication networks were based on PTM, starting from telegraph network which may be considered as a packet switching network. Other networks like X.25 and its alternative solutions (i.e., *frame relaying* and *frame switching*) or Internet also use PTM.

#### 1.3.3 Asynchronous Transfer Mode

Asynchronous Transfer Mode combines features of STM and PTM. In ATM data are transferred in fixed length packets called cells. Similarly, as in STM mode, cells are transmitted synchronously one after another, and a time for transmitting one cell is called a time slot. When no information is to be sent an empty cell is transmitted. However, transmitted cells are not structured into frames, like in STM mode. Users can insert data into any empty cell, so cells transmitted from a user may appear at any time when new cell (time slot) is started, similarly as in PTM, and time slot number cannot be in this mode used as the label (address information). Therefore, each cell contains a header

Figure 1.7. Asynchronous Transfer Mode

with a label, which is used to direct a cell to a destination user. A label is assigned to the connection at the connection set-up phase and is released after the connection is terminated. When no information is to be sent when a connection is set up, empty cells are sent. This approach enables the use of transmission bandwidth more efficiently than in STM, where time slots occupied by connections cannot be used by other connection even if no data is being transmitted. The concept of ATM is shown in Fig. 1.7.

#### **1.4** Architectures of Switching Nodes

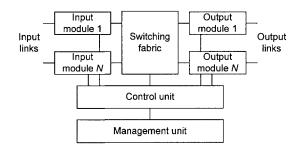

#### 1.4.1 General Switch Architecture

The general architecture of a switching node is presented in Fig. 1.8. It contains N input modules, N output modules, a switching fabric, a control unit, and a management unit. Each input link is connected to one input module. Functions realized in the input module depends on the transmission method used in the link. In general, it converts line signals to signals suitable for processing and transmitting in the switching node. It also synchronizes frames, extracts signalling information and passes it to the control unit, and prepares signals for transmission through the switching fabric. The switching fabric transfers input signals to requested output modules through connecting paths, which are set up for this purpose. At the output module, signals received from the switching fabric are prepared for further transmission through the output link. This includes framing, insertion of signalling information if required, and transcoding signals to the line code and form appropriate for the output link. The control unit processes connections, sets up connecting paths through the switching fabric, processes signalling information, handles errors in call processing, and performs traffic routing and management functions. The management unit manages the configuration of the switching node, performs testing, billing and security management. Some other units, not shown in Fig. 1.8, like main distribution frame and powering, are also parts of the switching node.

Figure 1.8. The general switching node architecture

We will now describe architectures and functions of switching nodes in several telecommunication networks, and give also some other examples where switching fabrics are used.

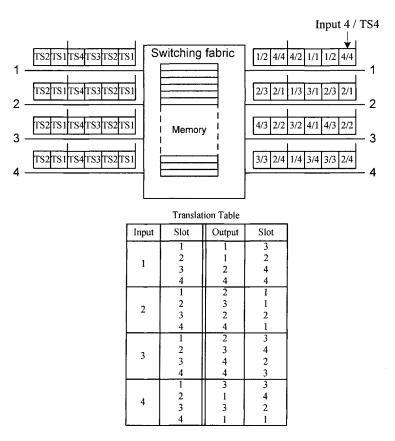

#### **1.4.2** Telephone Exchange

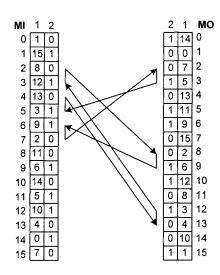

Telephone subscribers used to be connected to the telephone exchange through subscriber line interface circuits (SLIC) placed in remote units called concentrators. Concentrators were connected to the main exchange by means of the set of E1 links. This type of links was also used for connections with other exchanges. Switching fabrics used mainly circuit switching with time-division multiplexing TDM (called also TDM switching). The principle of TDM switching is shown in Fig. 1.9. The switching of a time slot from incoming link to outgoing link is controlled by a translation table, which contains the relation between the slot number of an incoming link and the associated slot number in an outgoing link [33]. For instance time slot TS1 of input link 1 will always be switched to TS3 of output link 1. This relation is established during connection set-up phase and is maintained until the connection is terminated. The contents of the translation table is modified when a connection is set up or released. In the switching fabric switching can be done in switching elements which performs this function only in space (i.e., they move a time slot form one input link to the same time slot of any output link), time (a time slot form the input link is switched to any time slot of the output link), or in a combination of both. The switching fabric of Fig. 1.9 performs the switching function in both domains. The same approach is used in mobile switching centers (MSC) of GSM networks.

Currently, subscribers are more often connected to the remote subscribers modules which are connected to a main exchange by means of access networks.

Figure 1.9. TDM switching - principle of operation

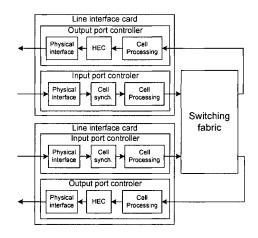

#### 1.4.3 ATM Switches

Functions of the input and output modules of ATM switch, called input and output port controllers, respectively, are shown in Fig. 1.10. Input and output port controllers may be fabricated on one circuit board called the line interface card. Input line is connected to the physical interface which converts incoming bit stream from line code to binary code (optical to electronic conversion is also performed when optical fiber is used), synchronizes bits and frames (when cells are transmitted in the frame, for instance SDH/SONET or E1), end process information in the header of the frame. Extracted cells are passed to the cell synchronization units, which delimits cells' boundaries, checks correctness of received cells, discards cells with errors in header and empty cells, and passes remaining cells to the cell processing unit. In the cell processing unit cells are prepared for transmission through the switching fabric.

Figure 1.10. ATM switch

The destination output port for each cell is determined using routing information table and an internal header is added. Depending on the switch organization buffers may be also placed in input module to overcome output contention problems.

At the output port controller, cells from the switching fabric are passed to the cell processing unit, which removes internal header and inserts new header with the label assigned to the cell on the outgoing link. In HEC unit header error check code is calculated and inserted in the respective field of cell's header, and empty cells are generated if necessary. Then cells are put into frames (if framed transmission is used) and converted to the signal appropriate for transmission in the output link. Output buffers are also located at the port controller.

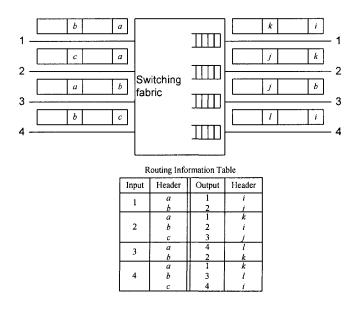

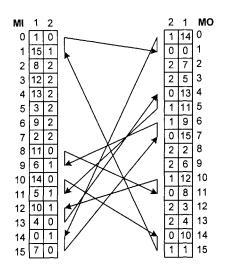

The principle of ATM switch operation is shown in Fig. 1.11 [18, 33]. Each cell is directed to the requested output according to the label located in its header. This label contains VCI (virtual channel identifier) and VPI (virtual path identifier). The label has a local meaning, is assigned during connection set-up, and is placed in the routing information table together with output port number and the new label which is to be used in the output link. The example of such routing table is also shown in Fig. 1.11. In each time slot, destination ports for cells from each input port are taken from the routing table, routes through the switching fabric is self-routing, connecting paths are set up (in case the switching fabric is switch-by-switch from the output port address placed in the header at the cell processing unit of the input port controller), and cells

Figure 1.11. ATM switching - principle of operation

are transferred to output ports. In ATM switching it may happen that in a given time slot, two or more cells should be directed to the same output port. This phenomenon is called output port contention and is solved by buffering cells. Buffers may be placed in different units of the switch, for instance at inputs, at outputs, or inside the switching fabric.

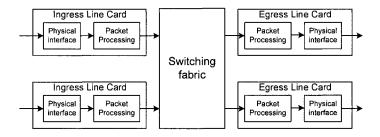

#### 1.4.4 IP Routers

IP routers can be categorized depending on their size into low-end routers, middle-size routers, and high-end routers [18]. The first two classes performs switching functions in software. Line cards are connected to the central processing unit through a shared bus. Processing units can be also placed on line cards for packet forwarding, in order to reduce the central processing unit load. The capacity of the processing unit and central bus speed limits the capacity of such types of routers. In high-end routers of large capacity a switching fabric is used to switch packets between inputs and outputs. The general architecture of such a router is shown in Fig. 1.12 [16, 18]. Ingress line card contains physical interface and packet processor. The physical interface performs optical-to-electrical and serial to parallel conversions. It also synchronizes incoming bits, processes frame overhead and delineates packets. Packets are then processed by the packet processor, which performs table lookup and packet classification. The packet processor also performs

Figure 1.12. High-end IP router

various control functions like traffic access control, buffer management, and packet scheduling. All these functions may be implemented in more than one unit. Most switching fabrics use synchronized packet switching, i.e., variable length input packets are segmented into fixed length packets for transferring through the switching fabric. This function is also realized in the packet processor.

After switching, fixed length packets are again processed by packet processor at the egress line card. They are reassembled to original variable length packets, buffered and scheduled for transmission. At the physical interface packets are placed in appropriate frame (SDH/ SONET), frame header is generated, and then the bit stream is converted from parallel to serial and from electrical to optical form.

Fixed length packets are called cells, but they do not have the same length as ATM cells. The principle of switching is the same as for ATM switching.

#### 1.4.5 Cross-connect Systems

Cross-connect systems are switching nodes used in transport networks. When transport networks is based on SDH/SONET systems and switching is made in electronic form, the switching nodes are called digital cross-connect systems (DXCs) and digital add/drop multiplexers (ADMs). The principle of switching in these systems is similar to TDM switching. Currently optical transmission is used in transport networks and DXCs are being replaced with optical cross-connect systems (OXCs) and optical ADMs (OADMs). The optical transport network is shown in Fig. 1.13. It provides connecting paths between users (telephone exchanges, IP routers). This connecting path is also called the lightpath, and it uses one optical channel (one wavelength) in an optical fiber. The optical transport network may use ring or mesh topology. OADMs are placed on the network edge, and provide access to the optical transport

Figure 1.13. An Optical Transport Network

network. OADMs are also useful in building simple optical networks with small numbers of nodes and wavelengths.

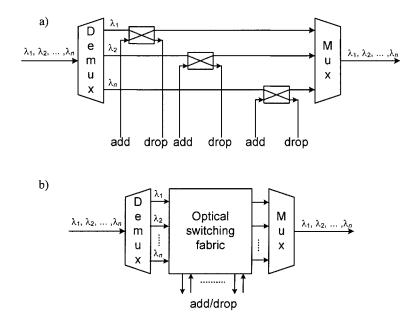

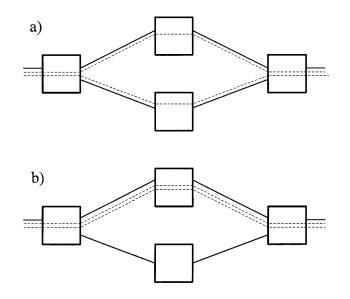

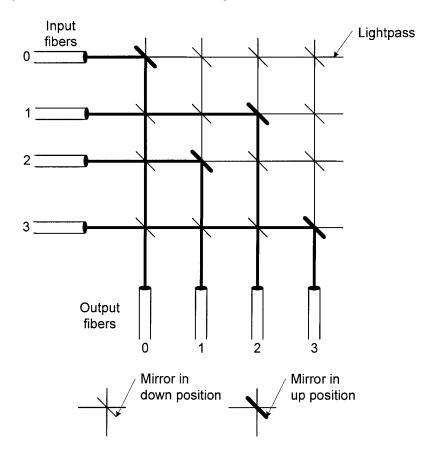

Different architectures of OADMs were proposed in literature and implemented in practice [142]. Some of them use optical switching fabric to switch wavelengths. Two examples of such architectures are shown in Fig. 1.14. In the first example simple  $2 \times 2$  switching elements are used. After wavelength demultiplexing each wavelength passes through the switching element and depending on the state of this element the wavelength is either switched through or dropped. When the wavelength is dropped, the same wavelength is also added through the switch. After switching, wavelengths are back multiplexed to the output fiber. The same function can be realized using the switching fabric of greater capacity, as is shown in Fig. 1.14b.

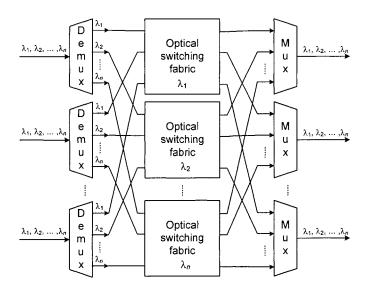

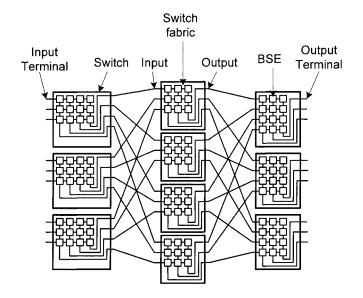

Several architectures were also considered for OXCs. One of these architectures with several switching fabrics, each for switching signals on different wavelengths, is shown in Fig. 1.15. Wavelengths from each input fiber are firstly demultiplexed and then each wavelength is switched by the different switching fabric. Each switching fabric switches only the same wavelength. After switching, wavelengths are back multiplexed to optical fiber. Instead of n switching fabrics (when n wavelengths are multiplexed in one optical fiber), one switching fabric of greater capacity can be used. Optical wavelength converters may be also used at outputs

Figure 1.14. OADMs architectures with switching elements (a) and with the switching fabric (b) (a) = 1

or inputs of the switching fabric to convert incoming or outgoing signals from one wavelength to another.

OXCs uses mostly circuit switching technique, however, optical packet switching and optical burst packet switching are considered for use in core routers [176, 131, 171]. Optical packet switching, however, will require faster optical switching elements and optical buffers.

## 1.4.6 Switching in Multiprocessor Systems

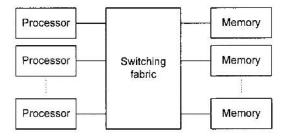

The growing need for fast computing and the limited speed of processors lead to the proposition of the new architecture of computer systems. Parallel computers were designed to increase processing power. Such a computer contains multiple processors connected to memory and other input/output devices. Processors cooperate to solve a large problem and memory components are distributed among processors. In such architecture, some kind of communication subsystem is required to connect processors with memories and other peripherals. It may be done using system buses, but when the number of processors and devices connected to the bus increases, then the bus becomes the communication bottleneck that degrades the performance of the system. The number of devices connected to the bus is also limited by electrical load character-

Figure 1.15. OXC with separate switching fabrics for each wavelength

istics. Another solution is to use switching fabric in which connections between processors and memory components will be done on request. Such a multiprocessor system is shown in Fig. 1.16. Communications between devices connected to the switching fabric is realized by means of messages. The switching may use circuit switching technique, where circuit connection is established between devices before a message is sent. Another option is packet switching of fixed length packets. Different variations of switching packets in the switching fabrics where proposed, like virtual-cut through switching, wormhole switching or mad postman switching [39]. Their purpose is to reduce the latency and increase the performance of the switching fabric. For instance, in virtual-cut through switching the decision were the packet is to be directed is made up when the packet header with routing information is received (the whole packet does not need to be in the node when this decision is made up). In wormhole switching fixed length packets are further divided into so called flits, where *flit* is the unit of message flow control.

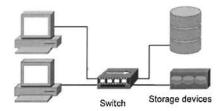

#### 1.4.7 Switching in Storage Area Networks

A Storage Area Network (SAN) is a network whose primary purpose is the transfer of data between computer systems and storage elements. A SAN consists of a communication infrastructure, which provides physical connections, and a management layer, which organizes the connec-

Figure 1.16. A multiprocessor system with shared memory

Figure 1.17. A small SAN

tions, storage elements, and computer systems so that data transfer is secure and robust [157]. A SAN allows any-to-any connections across the network using network elements such as routers, gateways, hubs, and switches. These networks are built by enterprises having medium to large data centers. They eliminate the traditional dedicated connection between a server and DAS (direct access storage). Servers have no longer their own storage devices but are connected by a switch to various types of peripheral and storage devices. This architecture is shown in Fig. 1.17. Different standards were developed for this purpose by companies, like ESCON (enterprise serial connection), Fiber Channel, or HIPPI (high performance parallel interface). First SAN operated within a building or campus, but today SANs operate over a wider area like metropolitan or even long-haul networks and operate at bit rates ranging from 200 Mbps to 1 Gbps. This architecture spread over a wider area is shown in Fig. 1.18.

The channel set up through a SAN makes that applications see storage devices attached to the SAN as if they are locally attached storage [47]. A SAN supports direct, high speed transfers between servers and storage devices in the following ways: server to storage, server to server, and storage to storage [158]. Switches used in SANs are usually divided into two types, depending on their port number: directors and fabric

Figure 1.18. A wide SAN

switches. Directors are usually devices of greater capacity, with 100 or more ports, and they're really designed to run in the core of the data center. The important features of directors are their high availability and high scalability. Fabric switches have lower port counts than directors, and their main design point is cost. Fabric switches are used in smaller SANs, in small or medium-sized enterprises, or at the edge of the data center.

#### 1.5 The Contents of the Book

Many architectures of switching fabrics were proposed in the literature. Description of all these architectures, their principles of operation and characteristics, are far beyond the scope of one book. When designing a switching fabric, many designing criteria should be considered. Some of these criteria are common to all switching fabrics, other depends on the technology used or switching fabric's application.

One measure which is used to compare the switching fabric is their cost. This cost depends on the number of required switches, but other factors like packaging, ease of fabrication and control should also be

taken into account. Scalability, expandability, and reliability are also important characteristics which are considered when designing switching fabrics. An important characteristic in photonic switching is losses introduced by connecting paths and difference between maximal and minimal losses of different connecting paths. This difference is often expressed in the difference between the maximum and minimum number of switching elements in the optical path of different input terminal and output terminal pairs. When switch fabric is integrated on a single substrate, waveguides connecting switching elements may intersect between themselves. The number of such waveguide crossovers is also the measure considered in the switch fabric design and should be minimized since they introduce additional power losses and crosstalk. In packet switching a switching fabric should provide bounded delay and small cell or packet loss probability while achieving a maximum throughput close to 100%. The switching fabric should also provide a correct packet sequence at the output ports.

This book covers only several switching fabric architectures and concentrates on their combinatorial properties. Properties like rearrangebility or nonblockingness are connected with control algorithms used for finding a connecting path through a switching fabric. Some control algorithms used in architectures discussed in this book are also described. Only few books, to the author's knowledge, were devoted entirely to mathematical theory of switching fabrics. The first book, published in 1965, is written by V. E. Beneš [9]. Other books covering this subject were written by F.K. Hwang [56], A. Pattavina [138], and S.-Y. R. Li [99], and were published in 1998, 1998 and 2001, respectively. Some other books contains collections of papers concerning combinatorial properties of different switching fabrics [37, 38].

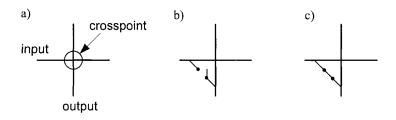

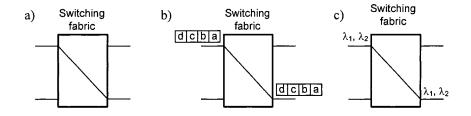

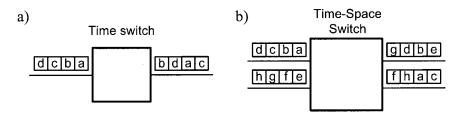

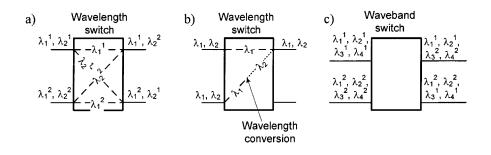

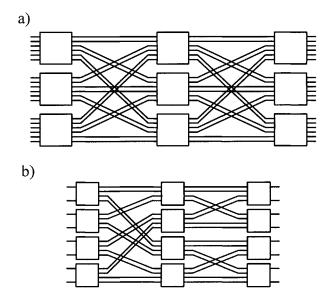

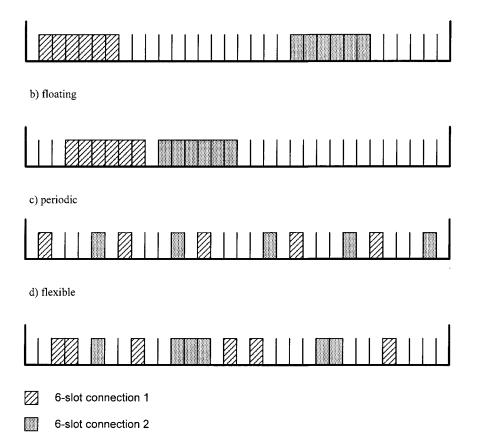

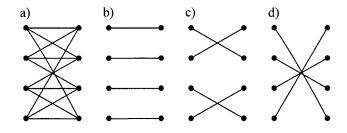

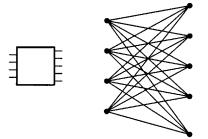

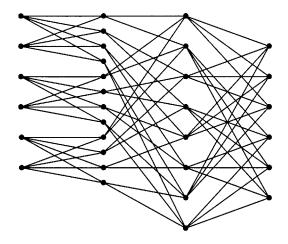

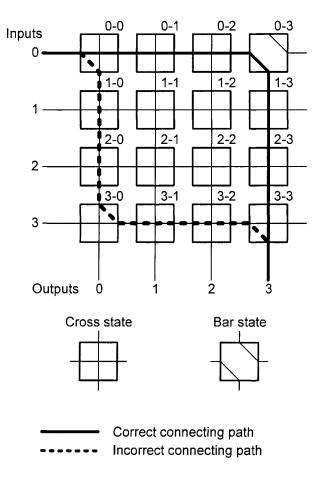

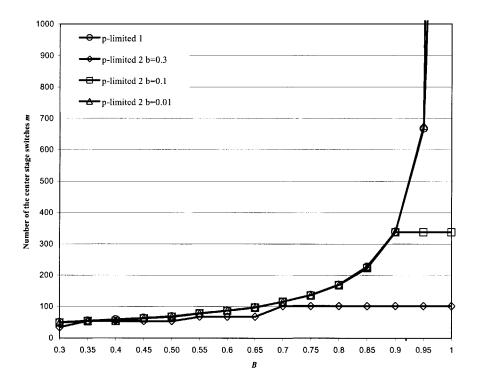

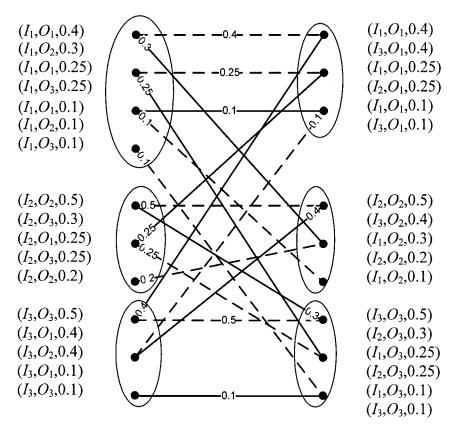

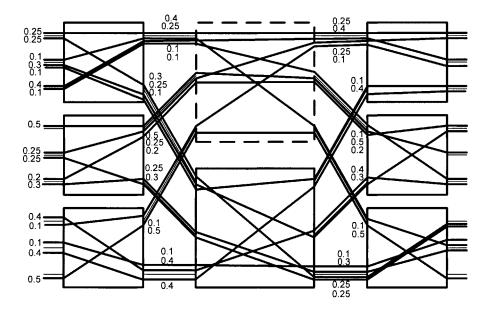

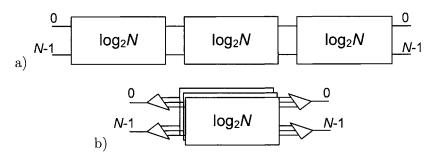

In this book some known results concerning nonblockingness and rearrangeability of switching fabrics are surveyed, but it also contains new results published recently in scientific journals and conference proceedings. Many of these results were obtained by the author during his own research studies and when supervising PhD students.